PRACTICE OF FPGA-BASED COMPUTING

# RECONFIGURABLE COMPUTING

SYSTEMS ON SILICON

EDITED BY SCOTT HAUCK ANDRÉ DEHON

### RECONFIGURABLE COMPUTING

#### The Morgan Kaufmann Series in Systems on Silicon

Series Editor: Wayne Wolf, Georgia Institute of Technology

The Designer's Guide to VHDL, Second Edition Peter J. Ashenden

The System Designer's Guide to VHDL-AMS

Peter J. Ashenden, Gregory D. Peterson, and Darrell A. Teegarden

Modeling Embedded Systems and SoCs Axel Jantsch

ASIC and FPGA Verification: A Guide to Component Modeling Richard Munden

Multiprocessor Systems-on-Chips Edited by Ahmed Amine Jerraya and Wayne Wolf

Functional Verification

Bruce Wile, John Goss, and Wolfgang Roesner

Customizable and Configurable Embedded Processors Edited by Paolo Ienne and Rainer Leupers

Networks-on-Chips: Technology and Tools Edited by Giovanni De Micheli and Luca Benini

VLSI Test Principles & Architectures Edited by Laung-Terng Wang, Cheng-Wen Wu, and Xiaoqing Wen

Designing SoCs with Configured Processors Steve Leibson

ESL Design and Verification

Grant Martin, Andrew Piziali, and Brian Bailey

Aspect-Oriented Programming with **e** David Robinson

Reconfigurable Computing: The Theory and Practice of FPGA-Based Computation Edited by Scott Hauck and André DeHon

#### **Coming Soon ...**

System-on-Chip Test Architectures Edited by Laung-Terng Wang, Charles Stroud, and Nur Touba

Verification Techniques for System-Level Design Masahiro Fujita, Indradeep Ghosh, and Mukul Prasad

### RECONFIGURABLE COMPUTING THE THEORY AND PRACTICE OF FPGA-BASED COMPUTATION

Edited by

Scott Hauck and André DeHon

Publisher: Denise E. M. Penrose

Senior Acquisitions Editor: Charles B. Glaser

Publishing Services Manager: George Morrison

Project Manager: Marilyn E. Rash

Assistant Editors: Michele Cronin, Matthew Cater

Copyeditor: Dianne Wood

Proofreader: Jodie Allen

Indexer: Steve Rath

Cover Image: © istockphoto

Typesetting: diacriTech

Illustration Formatting: diacriTech

Interior Printer: Maple-Vail Book Manufacturing Group

Cover Printer: Phoenix Color Corp.

Morgan Kaufmann Publishers is an imprint of Elsevier. 30 Corporate Drive, Suite 400, Burlington, MA 01803-4255

This book is printed on acid-free paper.

Copyright © 2008 by Elsevier Inc. All rights reserved.

Designations used by companies to distinguish their products are often claimed as trademarks or registered trademarks. In all instances in which Morgan Kaufmann Publishers is aware of a claim, the product names appear in initial capital or all capital letters. Readers, however, should contact the appropriate companies for more complete information regarding trademarks and registration.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means—electronic, mechanical, photocopying, scanning, or otherwise—without prior written permission of the publisher.

Permissions may be sought directly from Elsevier's Science & Technology Rights Department in Oxford, UK: phone: (+44) 1865 843830, fax: (+44) 1865 853333, e-mail: permissions@elsevier.com. You may also complete your request on-line via the Elsevier homepage (http://elsevier.com), by selecting "Support & Contact" then "Copyright and Permission" and then "Obtaining Permissions."

#### Library of Congress Cataloging-in-Publication Data

Reconfigurable computing: the theory and practice of FPGA-based computation/edited by Scott Hauck. André DeHon.

p. cm. — (Systems on silicon)

Includes bibliographical references and index.

ISBN 978-0-12-370522-8 (alk. paper)

1. Adaptive computing systems. 2. Field-programmable gate arrays. I. Hauck, Scott.

II. DeHon, André.

QA76.9.A3R43 2008 2007029773

For information on all Morgan Kaufmann publications, visit our Web site at www.mkp.com or www.books.elsevier.com.

### Working together to grow libraries in developing countries

www.elsevier.com | www.bookaid.org | www.sabre.org

**ELSEVIER**

BOOK AID International

Sabre Foundation

### **CONTENTS**

|      | Pre | t of Contributors<br>eface<br>roduction                                                        | xx<br>xxiii<br>xxv |

|------|-----|------------------------------------------------------------------------------------------------|--------------------|

| Part |     | Reconfigurable Computing Hardware vice Architecture                                            | 1                  |

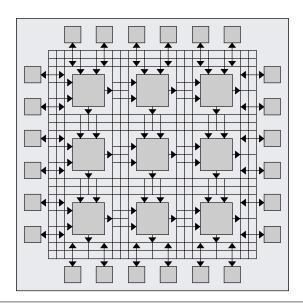

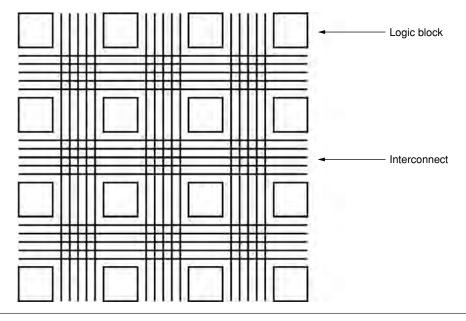

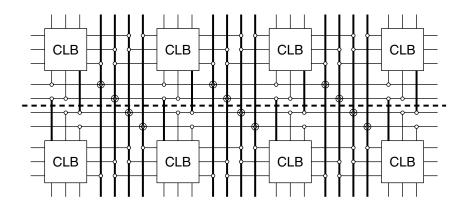

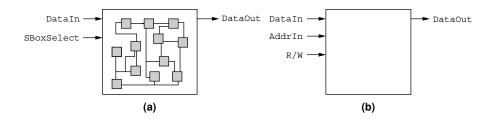

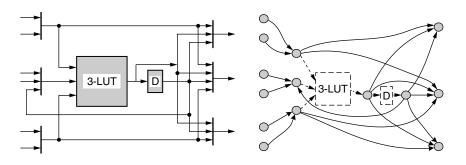

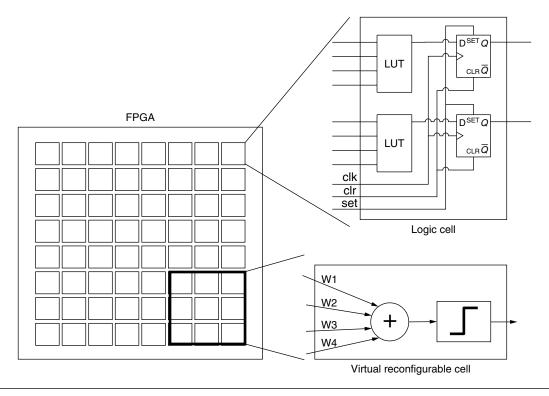

|      | 1.1 | Logic—The Computational Fabric                                                                 | 3                  |

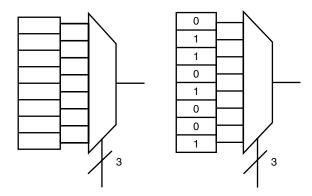

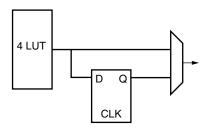

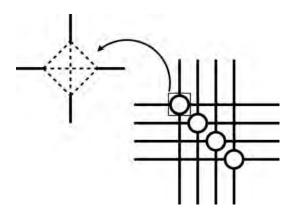

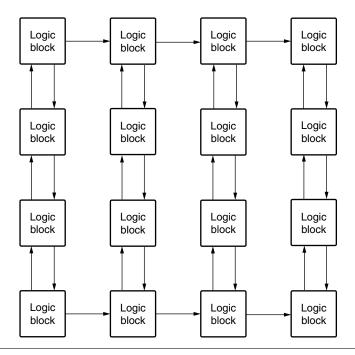

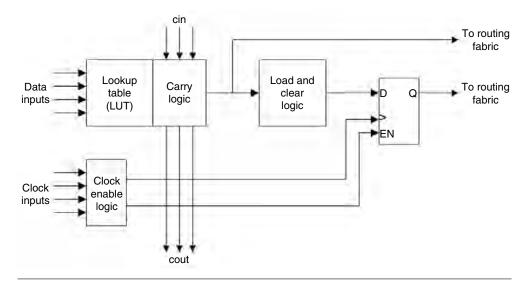

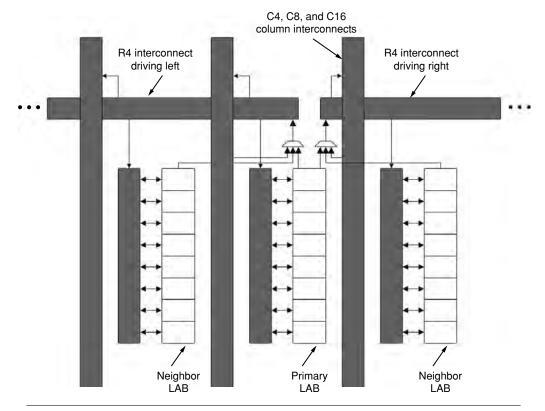

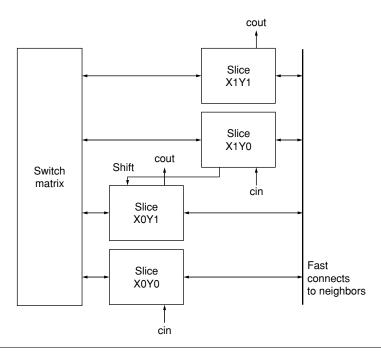

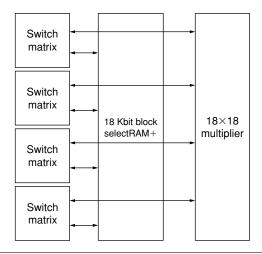

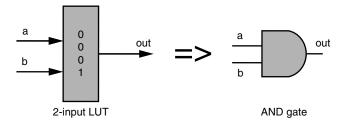

|      |     | 1.1.1 Logic Elements                                                                           | 4                  |

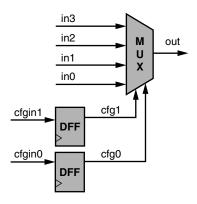

|      |     | 1.1.2 Programmability                                                                          | 6                  |

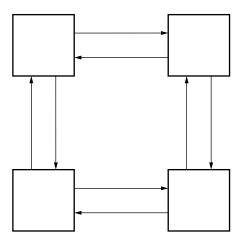

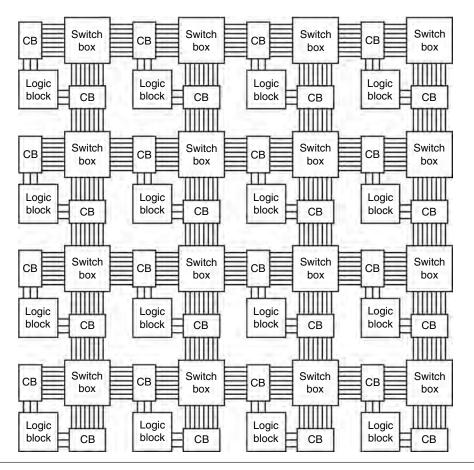

|      | 1.2 | The Array and Interconnect                                                                     | 6                  |

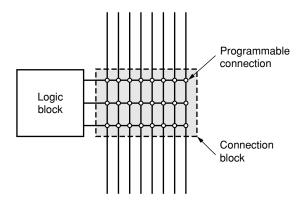

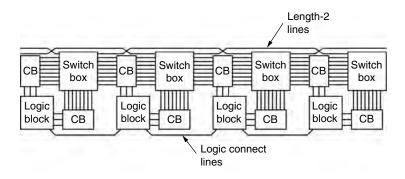

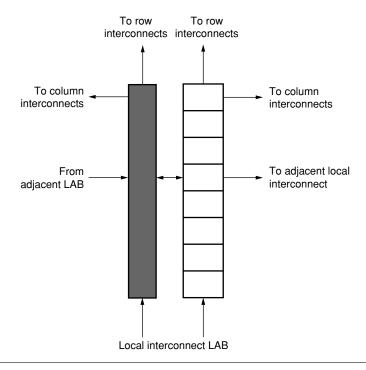

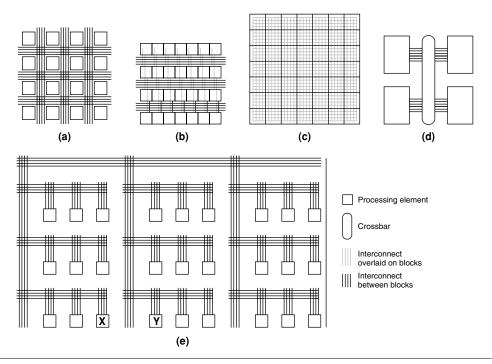

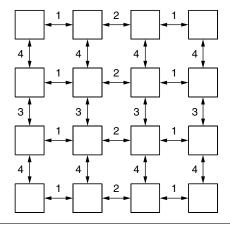

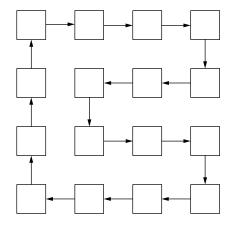

|      |     | 1.2.1 Interconnect Structures                                                                  | 7                  |

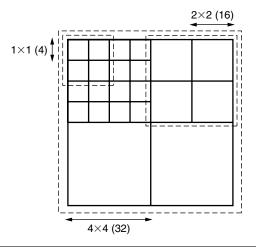

|      |     | 1.2.2 Programmability                                                                          | 12<br>12           |

|      | 1.3 | 1.2.3 Summary                                                                                  | 12                 |

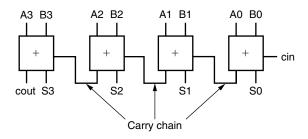

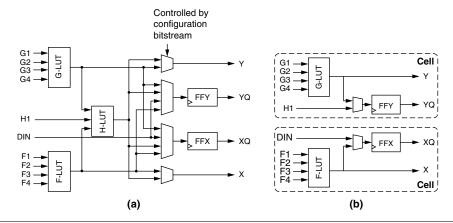

|      | 1.5 | 1.3.1 Extended Logic Elements                                                                  | 12                 |

|      |     | 1.3.2 Summary                                                                                  | 16                 |

|      | 1.4 | Configuration                                                                                  | 16                 |

|      |     | 1.4.1 SRAM                                                                                     | 16                 |

|      |     | 1.4.2 Flash Memory                                                                             | 17                 |

|      |     | 1.4.3 Antifuse                                                                                 | 17                 |

|      |     | 1.4.4 Summary                                                                                  | 18                 |

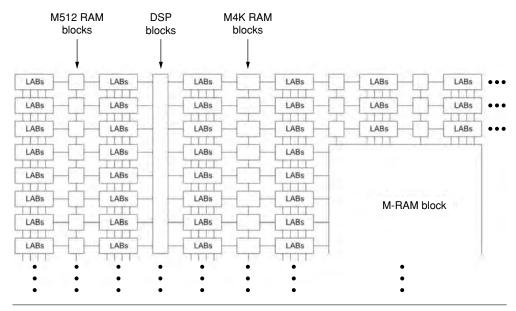

|      | 1.5 | Case Studies                                                                                   | 18<br>19           |

|      |     | 1.5.1       Altera Stratix         1.5.2       Xilinx Virtex-II Pro                            | 23                 |

|      | 1.6 | Summary                                                                                        | 26                 |

|      | 1.0 | References                                                                                     | 27                 |

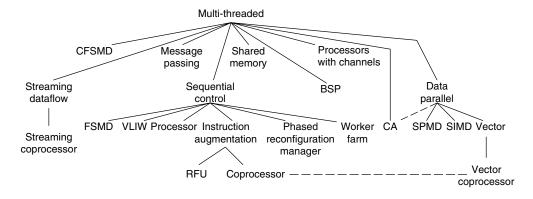

| 2    | Rec | configurable Computing Architectures                                                           | 29                 |

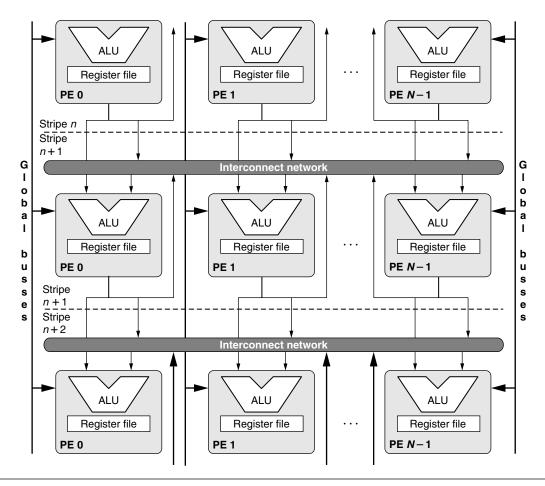

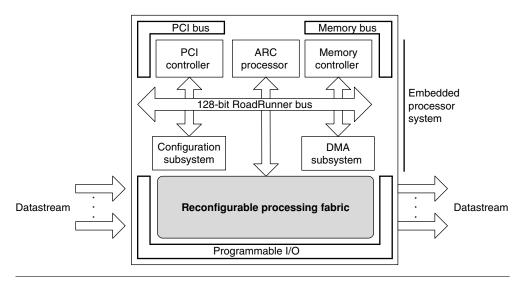

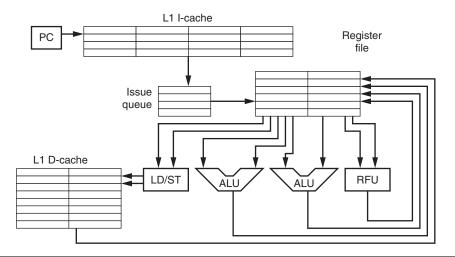

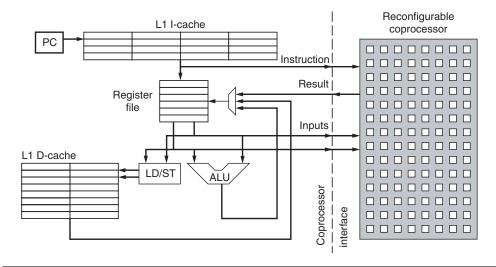

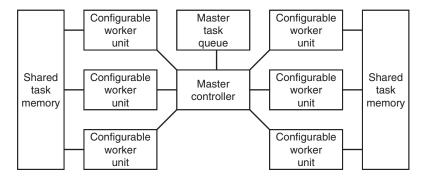

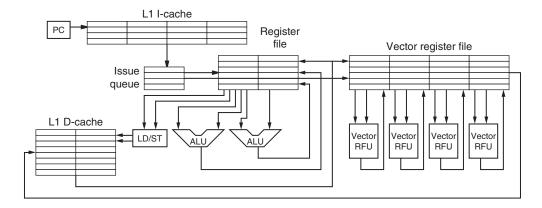

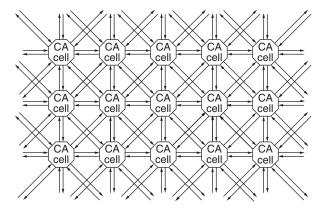

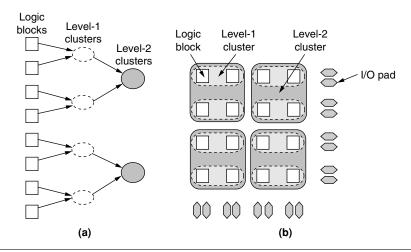

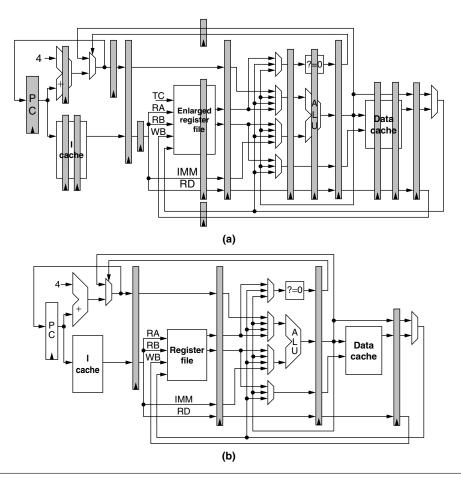

|      | 2.1 | Reconfigurable Processing Fabric Architectures                                                 | 30                 |

|      |     | 2.1.1 Fine-grained                                                                             | 30                 |

|      |     | 2.1.2 Coarse-grained                                                                           | 32                 |

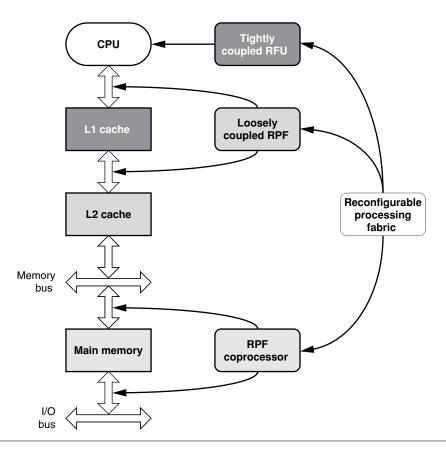

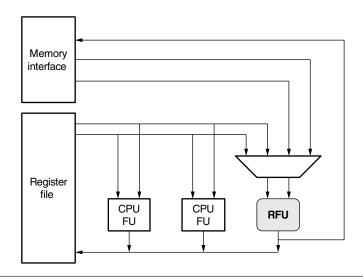

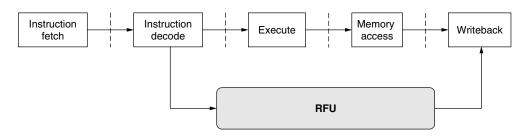

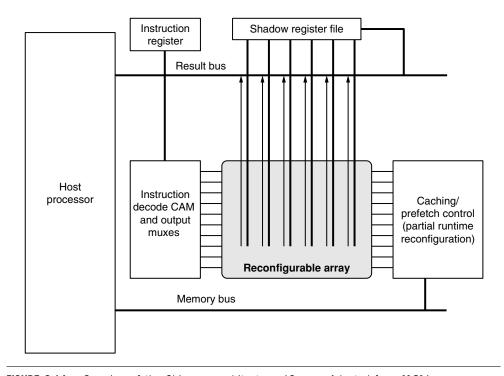

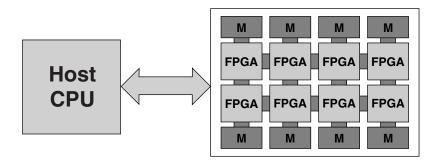

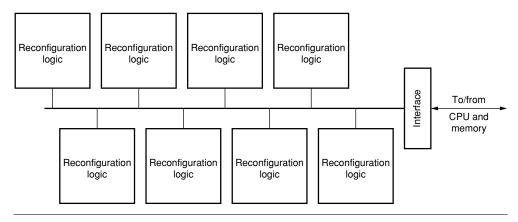

|      | 2.2 | RPF Integration into Traditional Computing Systems                                             | 35                 |

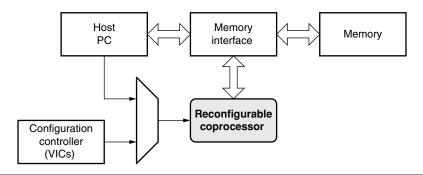

|      |     | 2.2.1 Independent Reconfigurable Coprocessor Architectures 2.2.2 Processor + RPF Architectures | 36<br>40           |

|      | 2.3 | 2.2.2 Processor + RPF Architectures                                                            | 40                 |

|      | 2.5 | References                                                                                     | 45                 |

| 3    | Rec | configurable Computing Systems                                                                 | 47                 |

|      | 3.1 | Early Systems                                                                                  | 47                 |

|      | 3.2 | PAM, VCC, and Splash                                                                           | 49                 |

|      |     | 3.2.1 PAM                                                                                      | 49                 |

|      |     | 3.2.2 Virtual Computer                                                                         | 50                 |

|      |     | 3.2.3 Splash                                                                                   | 51                 |

|     | 3.3     | Small-scale Reconfigurable Systems                  | 52  |

|-----|---------|-----------------------------------------------------|-----|

|     |         | 3.3.1 PRISM                                         | 53  |

|     |         | 3.3.2 CAL and XC6200                                | 53  |

|     |         | 3.3.3 Cloning                                       | 54  |

|     | 3.4     | Circuit Emulation                                   | 54  |

|     |         | 3.4.1 AMD/Intel                                     | 55  |

|     |         | 3.4.2 Virtual Wires                                 | 56  |

|     | 3.5     | Accelerating Technology                             | 56  |

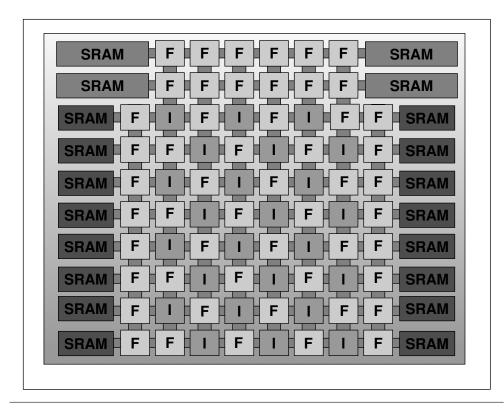

|     |         | 3.5.1 Teramac                                       | 57  |

|     | 3.6     | Reconfigurable Supercomputing                       | 59  |

|     |         | 3.6.1 Cray, SRC, and Silicon Graphics               | 60  |

|     |         | 3.6.2 The CMX-2X                                    | 60  |

|     | 3.7     | Non-FPGA Research                                   | 61  |

|     | 3.8     | Other System Issues                                 | 61  |

|     | 3.9     | The Future of Reconfigurable Systems                | 62  |

|     |         | References                                          | 63  |

| 4   | Rec     | configuration Management                            | 65  |

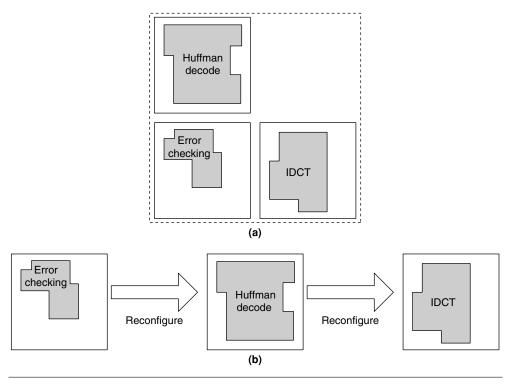

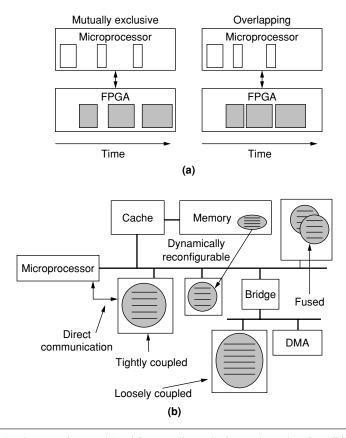

|     | 4.1     | Reconfiguration                                     | 66  |

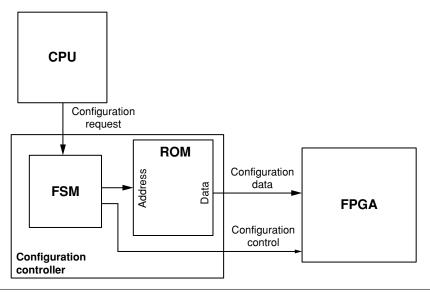

|     | 4.2     | Configuration Architectures                         | 66  |

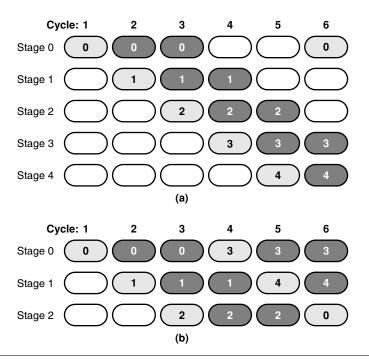

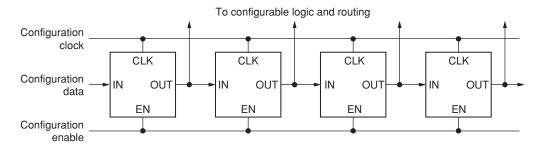

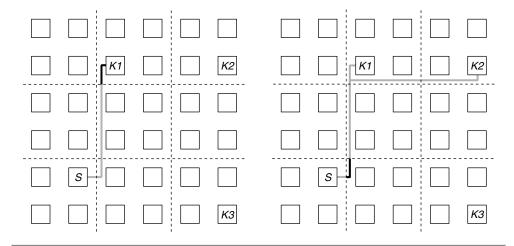

|     |         | 4.2.1 Single-context                                | 67  |

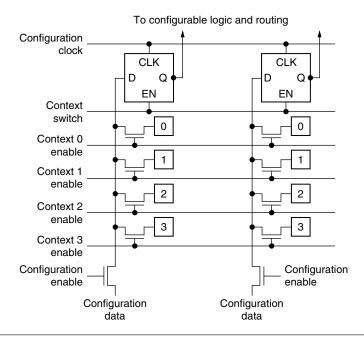

|     |         | 4.2.2 Multi-context                                 | 68  |

|     |         | 4.2.3 Partially Reconfigurable                      | 70  |

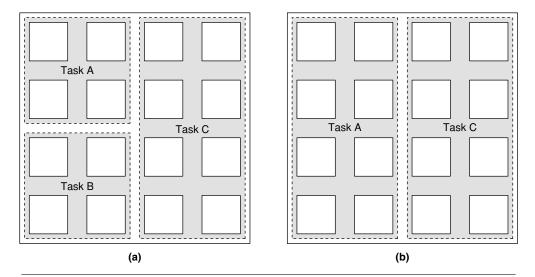

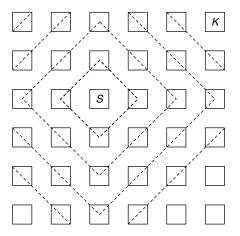

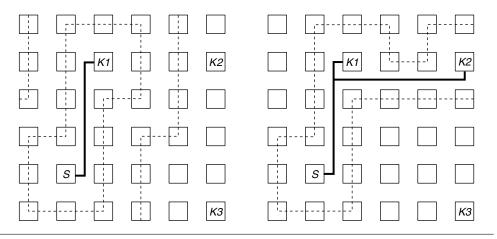

|     |         | 4.2.4 Relocation and Defragmentation                | 71  |

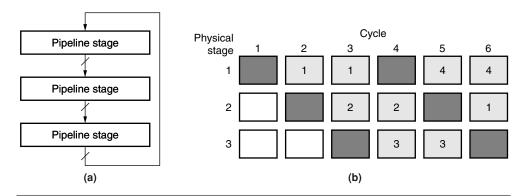

|     |         | 4.2.5 Pipeline Reconfigurable                       | 73  |

|     |         | 4.2.6 Block Reconfigurable                          | 74  |

|     |         | 4.2.7 Summary                                       | 75  |

|     | 4.3     | Managing the Reconfiguration Process                | 76  |

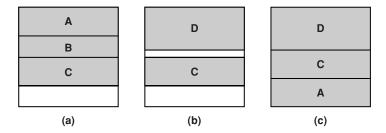

|     |         | 4.3.1 Configuration Grouping                        | 76  |

|     |         | 4.3.2 Configuration Caching                         | 77  |

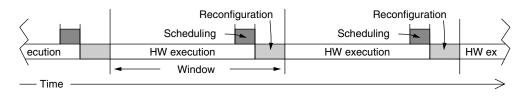

|     |         | 4.3.3 Configuration Scheduling                      | 77  |

|     |         | 4.3.4 Software-based Relocation and Defragmentation | 79  |

|     |         | 4.3.5 Context Switching                             | 80  |

|     | 4.4     | Reducing Configuration Transfer Time                | 80  |

|     | 7.7     | 4.4.1 Architectural Approaches                      | 81  |

|     |         | 4.4.2 Configuration Compression                     | 81  |

|     |         | 4.4.3 Configuration Data Reuse                      | 82  |

|     | 4.5     | Configuration Security                              | 82  |

|     | 4.6     | Summary                                             | 83  |

|     | 4.0     | ·                                                   | 84  |

|     |         | References                                          | 04  |

| Par | t II: F | Programming Reconfigurable Systems                  | 87  |

|     |         |                                                     |     |

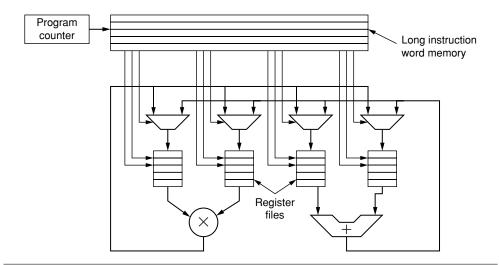

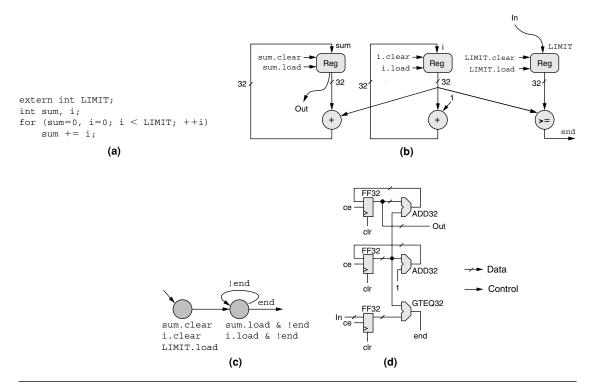

| 5   |         | npute Models and System Architectures               | 91  |

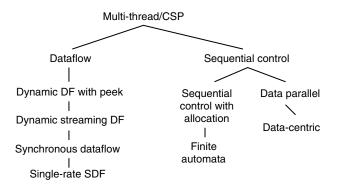

|     | 5.1     | Compute Models                                      | 93  |

|     |         | 5.1.1 Challenges                                    | 93  |

|     |         | 5.1.2 Common Primitives                             | 97  |

|     |         | 5.1.3 Dataflow                                      | 98  |

|     |         | 5.1.4 Sequential Control                            | 103 |

| vii |

|-----|

| 105 |

| 105 |

| 106 |

| 106 |

| 107 |

| 107 |

| 110 |

| 118 |

| 119 |

| 122 |

| 123 |

| 125 |

| 125 |

| 129 |

| 130 |

| 130 |

| 133 |

| 136 |

| 138 |

| 150 |

| 150 |

| 152 |

| 153 |

| 153 |

| 155 |

| 156 |

| 157 |

| 157 |

| 158 |

| 159 |

| 161 |

| 162 |

| 162 |

| 164 |

| 164 |

| 169 |

| 173 |

| 175 |

| 175 |

| 176 |

| 180 |

| 180 |

|     |

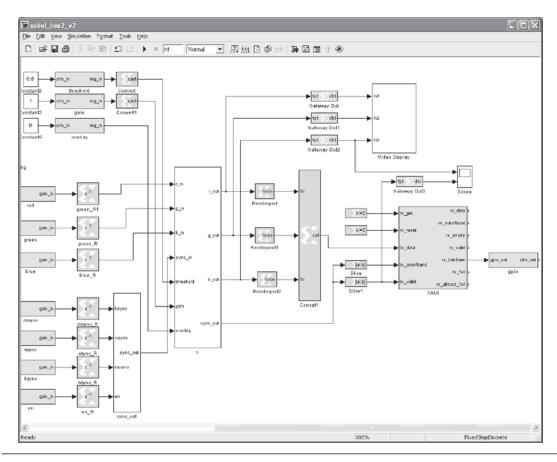

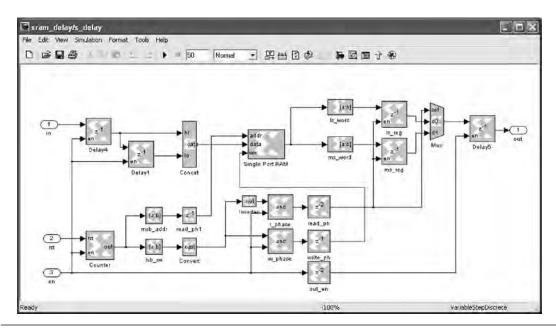

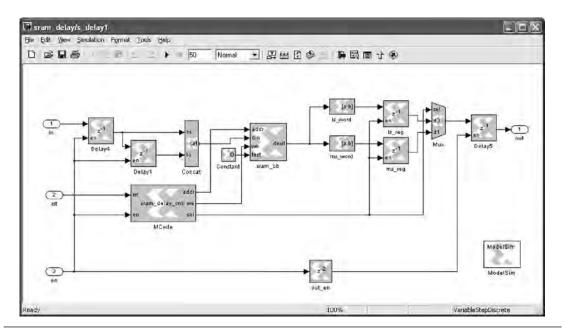

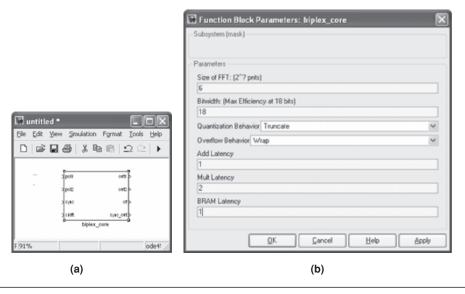

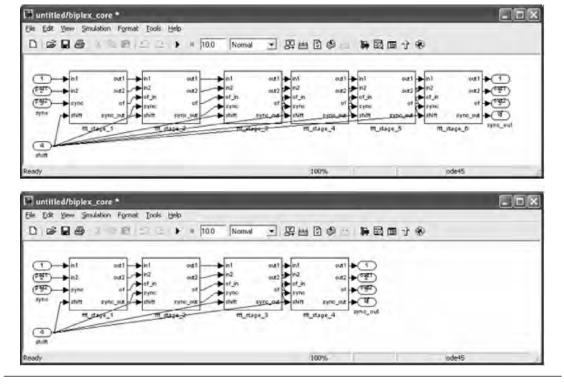

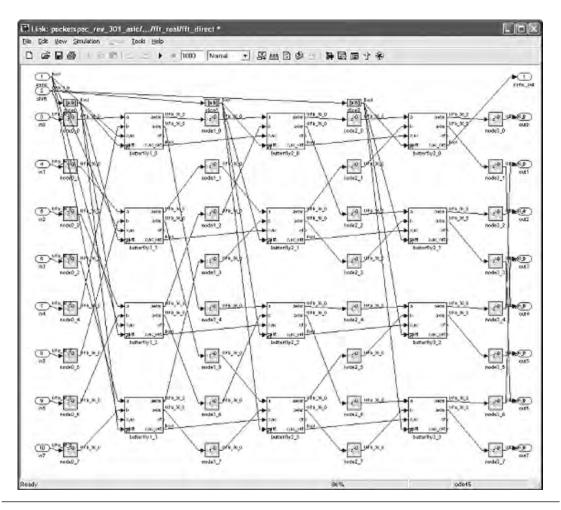

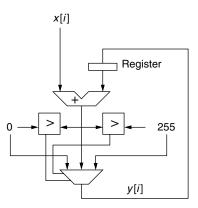

|      | gramming Streaming FPGA Applications<br>ng Block Diagrams in Simulink | 183 |

|------|-----------------------------------------------------------------------|-----|

| 8.1  | Designing High-performance Datapaths Using Stream-based               |     |

|      | Operators                                                             | 184 |

| 8.2  | An Image-processing Design Driver                                     | 185 |

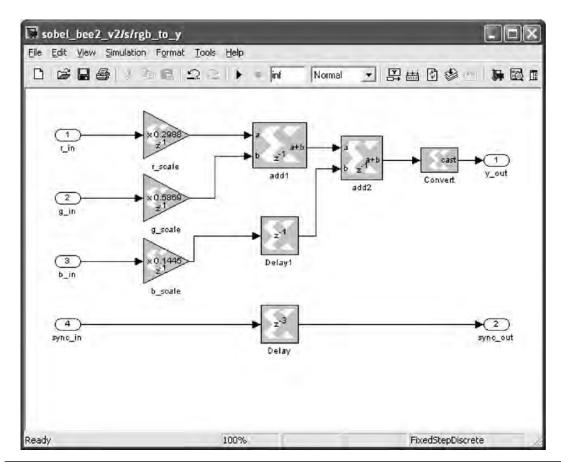

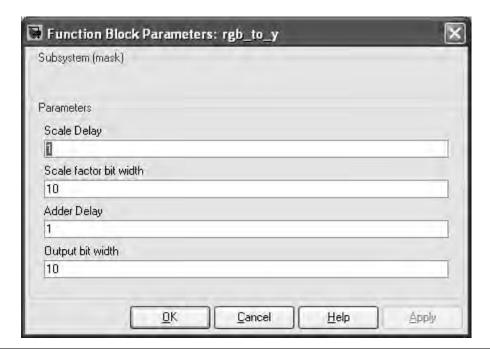

|      | 8.2.1 Converting RGB Video to Grayscale                               | 185 |

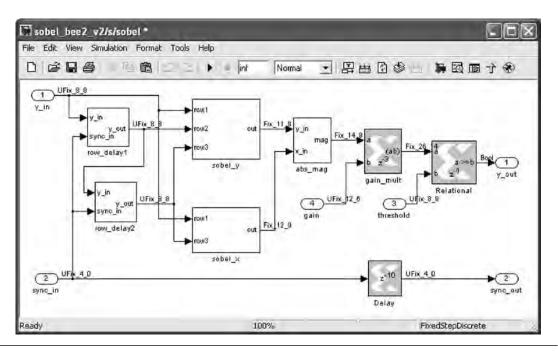

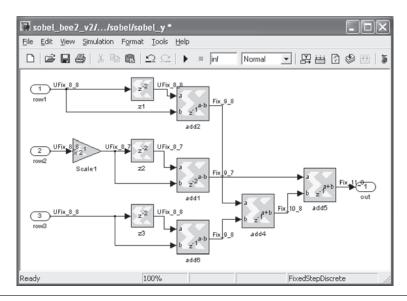

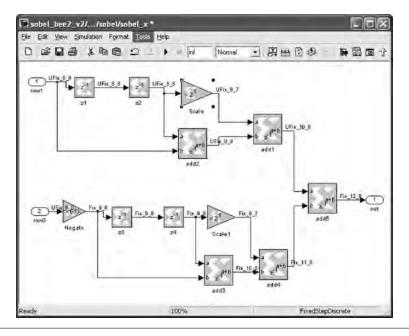

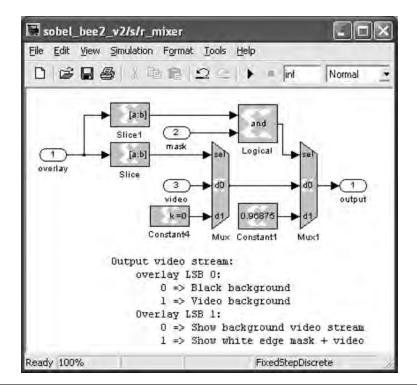

|      | 8.2.2 Two-dimensional Video Filtering                                 | 187 |

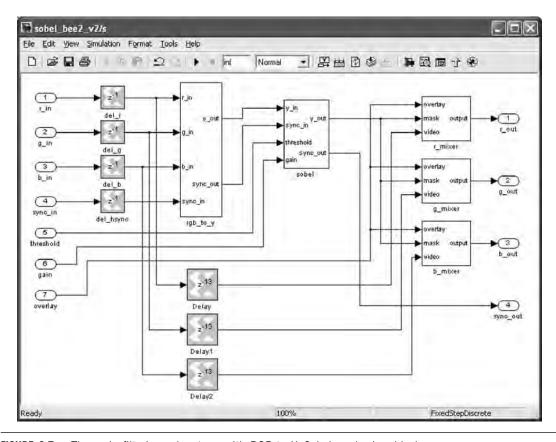

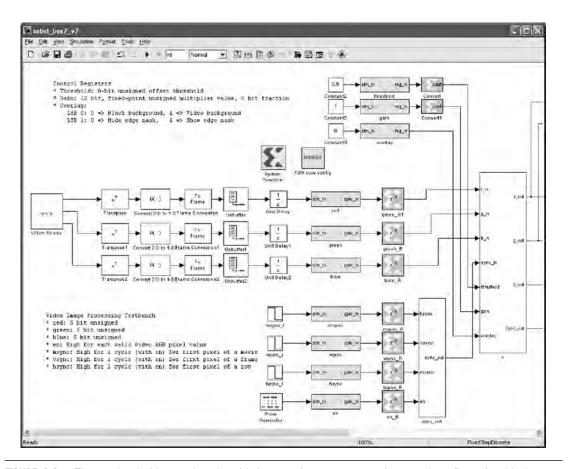

|      | 8.2.3 Mapping the Video Filter to the BEE2 FPGA Platform              | 191 |

| 8.3  | Specifying Control in Simulink                                        | 194 |

|      | 8.3.1 Explicit Controller Design with Simulink Blocks                 | 194 |

|      | 8.3.2 Controller Design Using the Matlab M Language                   | 195 |

|      | 8.3.3 Controller Design Using VHDL or Verilog                         | 197 |

|      | 8.3.4 Controller Design Using Embedded Microprocessors                | 197 |

| 8.4  | Component Reuse: Libraries of Simple and Complex Subsystems .         | 198 |

|      | 8.4.1 Signal-processing Primitives                                    | 198 |

|      | 8.4.2 Tiled Subsystems                                                | 198 |

| 8.5  | Summary                                                               | 201 |

|      | References                                                            | 202 |

|      | eam Computations Organized for                                        |     |

| Rec  | configurable Execution                                                | 203 |

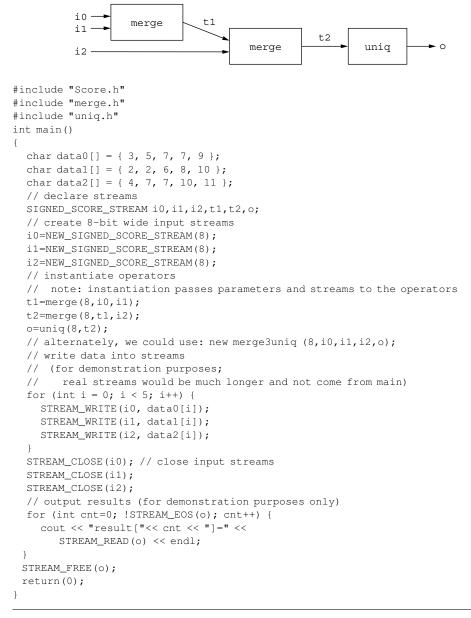

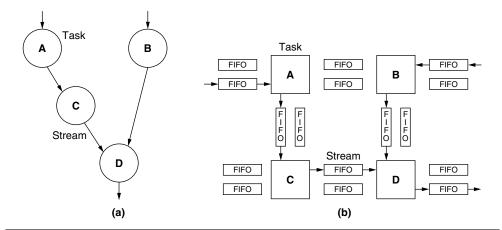

| 9.1  | Programming                                                           | 205 |

|      | 9.1.1 Task Description Format                                         | 205 |

|      | 9.1.2 C++ Integration and Composition                                 | 206 |

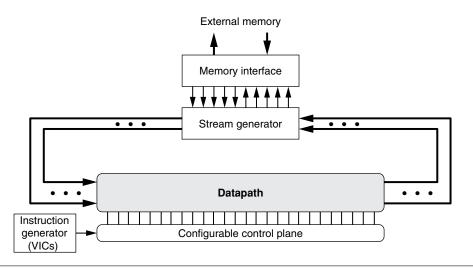

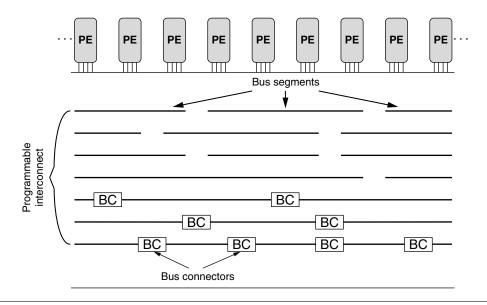

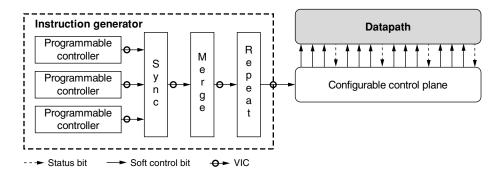

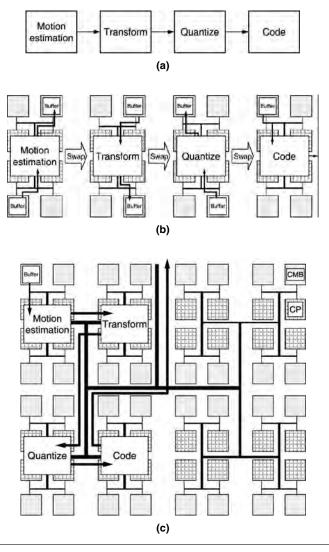

| 9.2  | System Architecture and Execution Patterns                            | 208 |

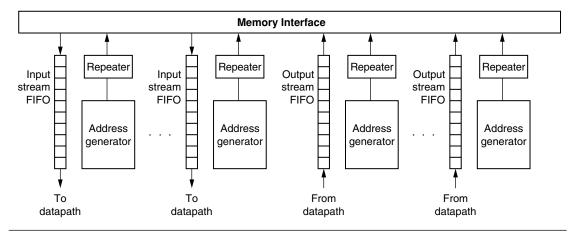

|      | 9.2.1 Stream Support                                                  | 209 |

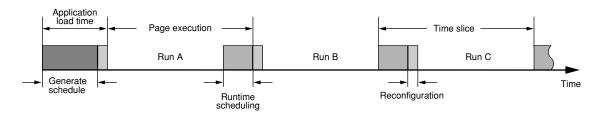

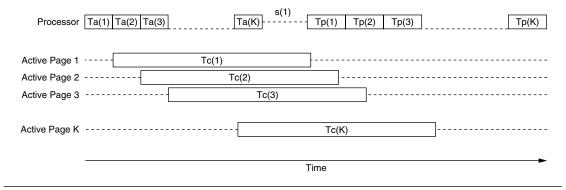

|      | 9.2.2 Phased Reconfiguration                                          | 210 |

|      | 9.2.3 Sequential versus Parallel                                      | 211 |

|      | 9.2.4 Fixed-size and Standard I/O Page                                | 211 |

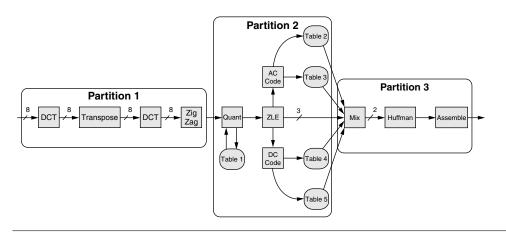

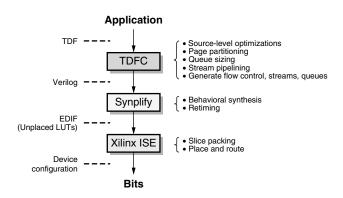

| 9.3  | Compilation                                                           | 212 |

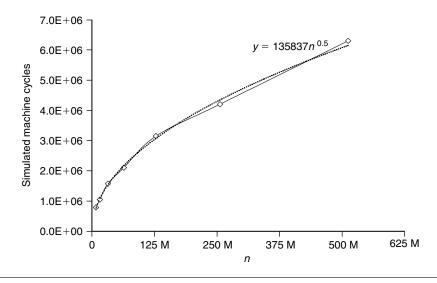

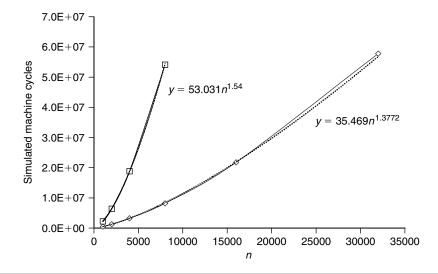

| 9.4  | Runtime                                                               | 213 |

|      | 9.4.1 Scheduling                                                      | 213 |

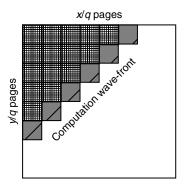

|      | 9.4.2 Placement                                                       | 215 |

|      | 9.4.3 Routing                                                         | 215 |

| 9.5  | Highlights                                                            | 217 |

|      | References                                                            | 217 |

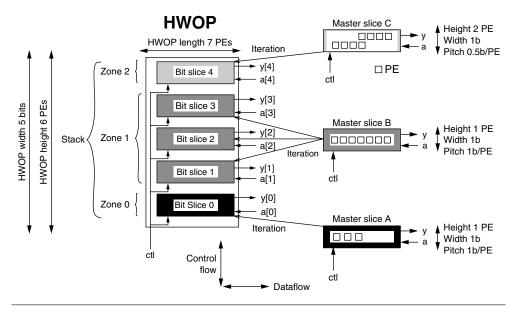

|      | gramming Data Parallel FPGA Applications                              |     |

| Usi  | ng the SIMD/Vector Model                                              | 219 |

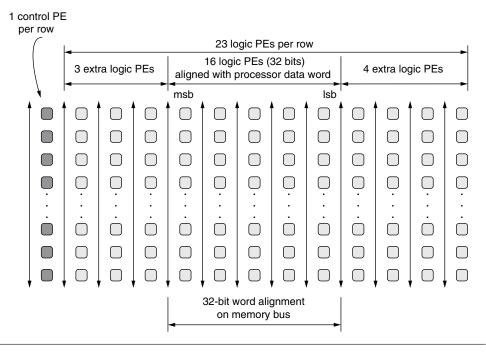

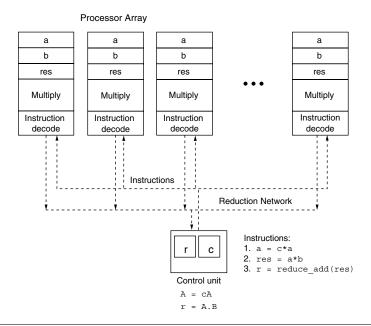

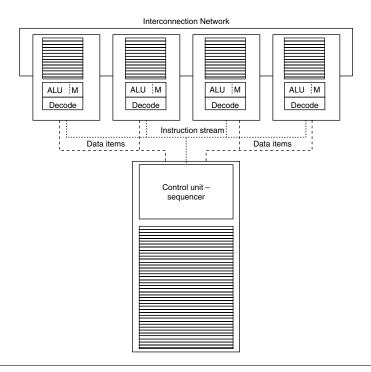

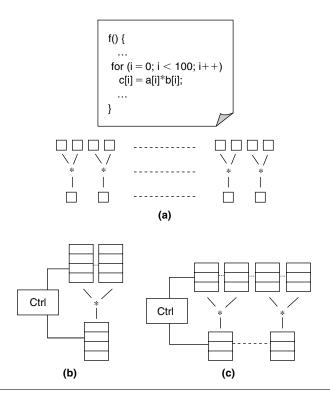

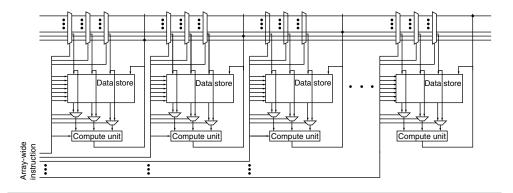

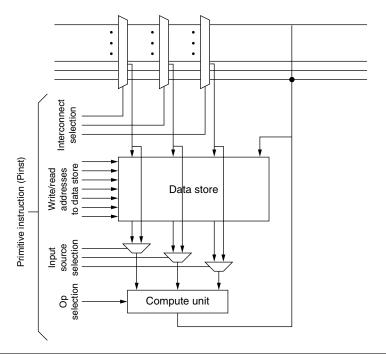

| 10.1 | SIMD Computing on FPGAs: An Example                                   | 219 |

| 10.2 | SIMD Processing Architectures                                         | 221 |

| 10.3 | Data Parallel Languages                                               | 222 |

| 10.4 | Reconfigurable Computers for SIMD/Vector Processing                   | 223 |

| 10.5 | Variations of SIMD/Vector Computing                                   | 226 |

|      | 10.5.1 Multiple SIMD Engines                                          | 226 |

|      | 10.5.2 A Multi-SIMD Coarse-grained Array                              | 228 |

|      | 10.5.3 SPMD Model                                                     | 228 |

|    |                     | Contents                                               | ix  |

|----|---------------------|--------------------------------------------------------|-----|

|    | 40.4                |                                                        | 220 |

|    | 10.6                | Pipelined SIMD/Vector Processing                       | 228 |

|    | 10.7                | Summary                                                | 229 |

|    |                     | References                                             | 230 |

| 11 | _                   | erating System Support for Reconfigurable              |     |

|    | Con                 | nputing                                                | 231 |

|    | 11.1                | History                                                | 232 |

|    | 11.2                | Abstracted Hardware Resources                          | 234 |

|    |                     | 11.2.1 Programming Model                               | 234 |

|    | 11.3                | Flexible Binding                                       | 236 |

|    |                     | 11.3.1 Install Time Binding                            | 236 |

|    |                     | 11.3.2 Runtime Binding                                 | 237 |

|    |                     | 11.3.3 Fast CAD for Flexible Binding                   | 238 |

|    | 11.4                | Scheduling                                             | 239 |

|    |                     | 11.4.1 On-demand Scheduling                            | 239 |

|    |                     | 11.4.2 Static Scheduling                               | 239 |

|    |                     | 11.4.3 Dynamic Scheduling                              | 240 |

|    |                     | 11.4.4 Quasi-static Scheduling                         | 241 |

|    |                     | 11.4.5 Real-time Scheduling                            | 241 |

|    |                     | 11.4.6 Preemption                                      | 242 |

|    | 11.5                | Communication                                          | 243 |

|    |                     | 11.5.1 Communication Styles                            | 243 |

|    |                     | 11.5.2 Virtual Memory                                  | 246 |

|    |                     | 11.5.3 I/O                                             | 247 |

|    |                     | 11.5.4 Uncertain Communication Latency                 | 247 |

|    | 11.6                | Synchronization                                        | 248 |

|    |                     | 11.6.1 Explicit Synchronization                        | 248 |

|    |                     | 11.6.2 Implicit Synchronization                        | 248 |

|    |                     | 11.6.3 Deadlock Prevention                             | 249 |

|    | 11.7                | Protection                                             | 249 |

|    | 11.7                | 11.7.1 Hardware Protection                             | 250 |

|    |                     | 11.7.2 Intertask Communication                         | 251 |

|    |                     | 11.7.3 Task Configuration Protection                   | 251 |

|    | 11.8                | Summary                                                | 252 |

|    | 11.0                | References                                             | 252 |

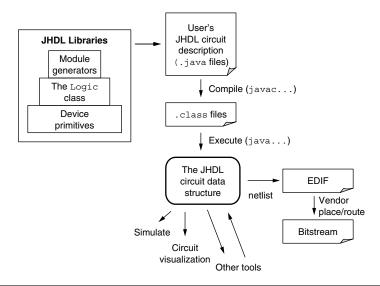

| 12 | The                 | JHDL Design and Debug System                           | 255 |

| _  | $\frac{1110}{12.1}$ | JHDL Background and Motivation                         | 255 |

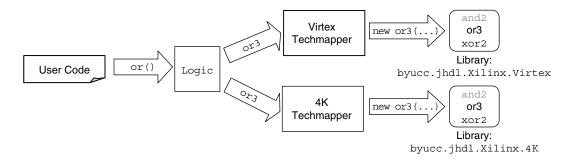

|    | 12.1                | The JHDL Design Language                               | 257 |

|    | 12.2                |                                                        | 257 |

|    |                     | $\epsilon$                                             | 231 |

|    |                     | 12.2.2 Level-2 Design: Using the Logic Class and Its   | 250 |

|    |                     | Provided Methods                                       | 259 |

|    |                     | 12.2.3 Level-3 Design: Programmatic Circuit Generation |     |

|    |                     | (Module Generators)                                    | 261 |

|    |                     | 12.2.4 JHDL Is a Structural Design Language            | 263 |

|    |                     | 12.2.5 JHDL Is a Programmatic Circuit Design Language  | 264 |

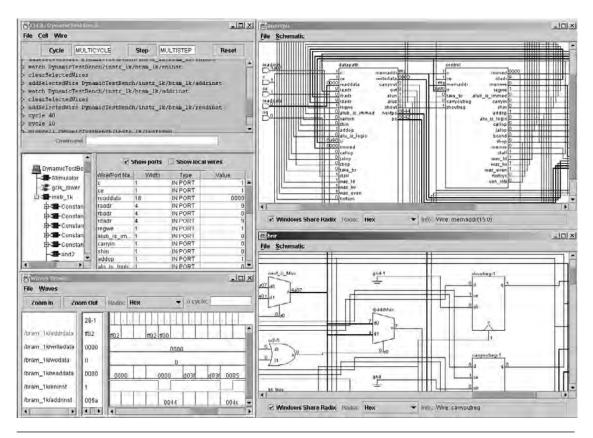

|    | 12.3                | The JHDL CAD System                                    | 265 |

|    |                     | 12.3.1 Testbenches in JHDL                             | 265 |

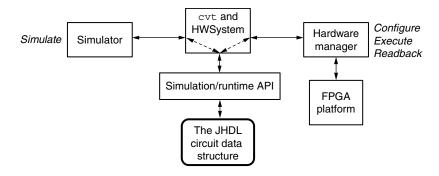

|    |                     | 12.3.2 The cvt Class                                   | 266 |

|      | 12.4<br>12.5 | JHDL's Hardware Mode  Advanced JHDL Capabilities  12.5.1 Dynamic Testbenches  12.5.2 Behavioral Synthesis | 268<br>269<br>269<br>270 |

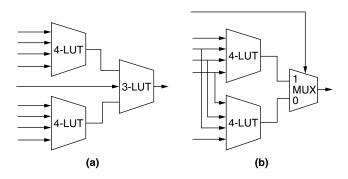

|------|--------------|-----------------------------------------------------------------------------------------------------------|--------------------------|

|      | 12.6         | 12.5.3 Advanced Debugging Capabilities                                                                    | 270<br>272<br>273        |

| Part | III:         | Mapping Designs to Reconfigurable Platforms                                                               | 275                      |

| 13   | Tec          | hnology Mapping                                                                                           | 277                      |

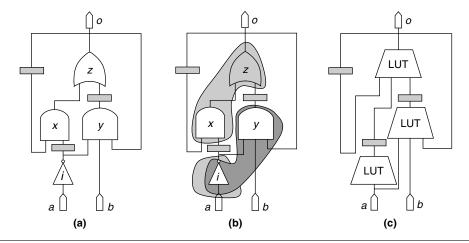

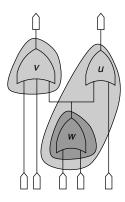

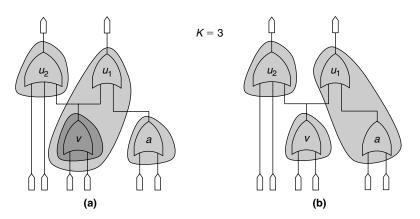

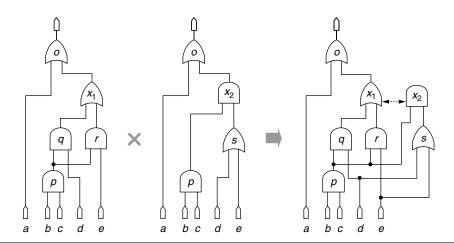

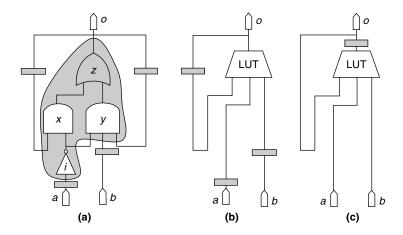

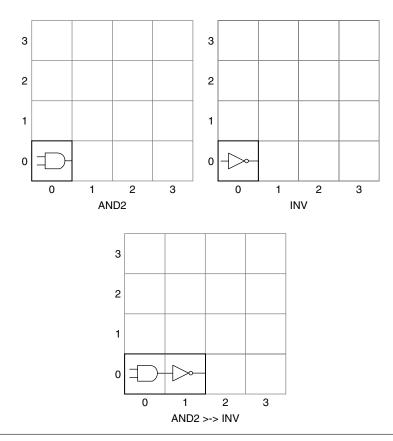

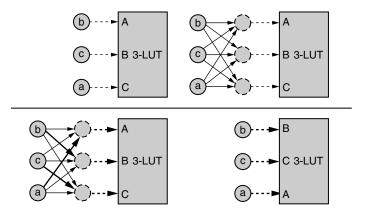

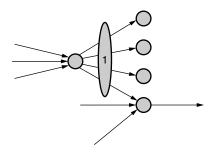

|      | 13.1         | Structural Mapping Algorithms                                                                             | 278                      |

|      |              | 13.1.1 Cut Generation                                                                                     | 279                      |

|      |              | 13.1.2 Area-oriented Mapping                                                                              | 280                      |

|      |              | 13.1.3 Performance-driven Mapping                                                                         | 282                      |

|      |              | 13.1.4 Power-aware Mapping                                                                                | 283                      |

|      | 13.2         | Integrated Mapping Algorithms                                                                             | 284                      |

|      |              | 13.2.1 Simultaneous Logic Synthesis, Mapping                                                              | 284                      |

|      |              | 13.2.2 Integrated Retiming, Mapping                                                                       | 286                      |

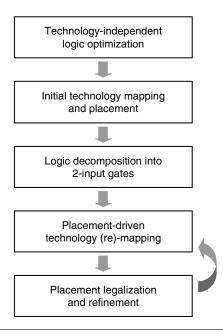

|      |              | 13.2.3 Placement-driven Mapping                                                                           | 287                      |

|      | 13.3         | Mapping Algorithms for Heterogeneous Resources                                                            | 289                      |

|      |              | 13.3.1 Mapping to LUTs of Different Input Sizes                                                           | 289                      |

|      |              | 13.3.2 Mapping to Complex Logic Blocks                                                                    | 290                      |

|      |              | 13.3.3 Mapping Logic to Embedded Memory Blocks                                                            | 291                      |

|      |              | 13.3.4 Mapping to Macrocells                                                                              | 292                      |

|      | 13.4         | Summary                                                                                                   | 293                      |

|      |              | References                                                                                                | 293                      |

|      | FPC          | GA Placement                                                                                              | 297                      |

| 14   |              | cement for General-purpose FPGAs                                                                          | 299                      |

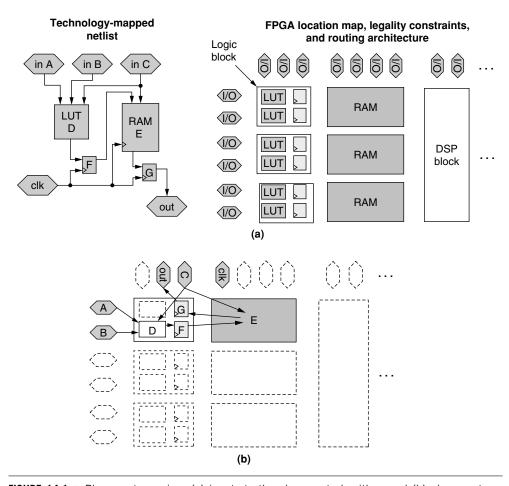

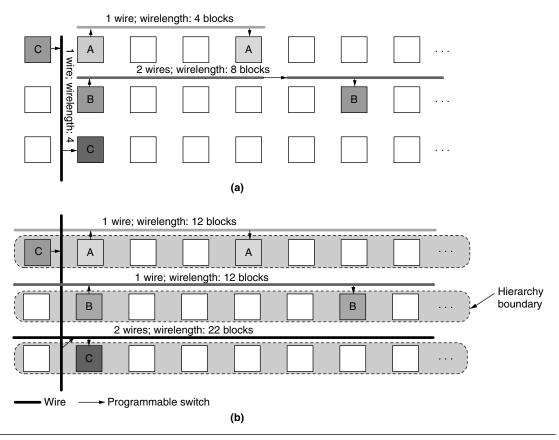

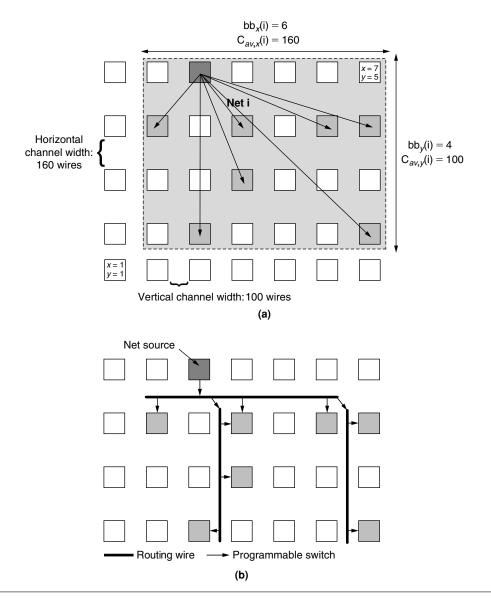

|      | 14.1         | The FPGA Placement Problem                                                                                | <br>299                  |

|      | 1 1.1        | 14.1.1 Device Legality Constraints                                                                        | 300                      |

|      |              | 14.1.2 Optimization Goals                                                                                 | 301                      |

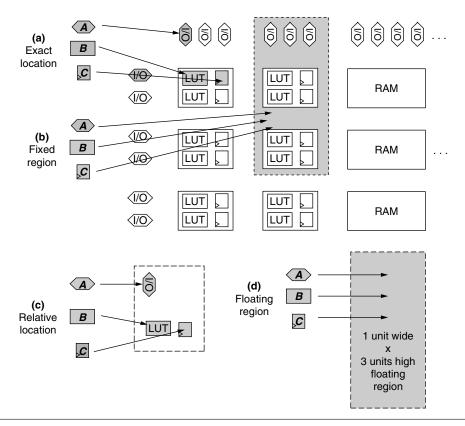

|      |              | 14.1.3 Designer Placement Directives                                                                      | 302                      |

|      | 14.2         | Clustering                                                                                                | 304                      |

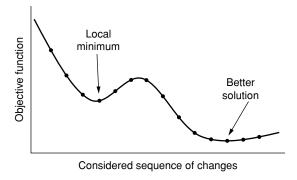

|      | 14.3         | Simulated Annealing for Placement                                                                         | 306                      |

|      |              | 14.3.1 VPR and Related Annealing Algorithms                                                               | 307                      |

|      |              | 14.3.2 Simultaneous Placement and Routing                                                                 |                          |

|      |              | with Annealing                                                                                            | 311                      |

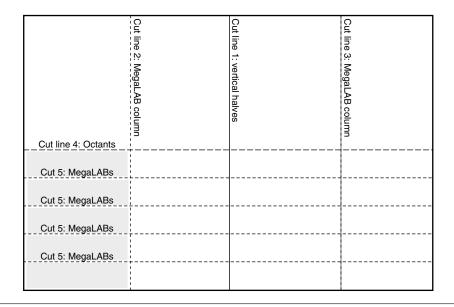

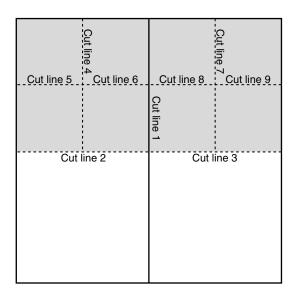

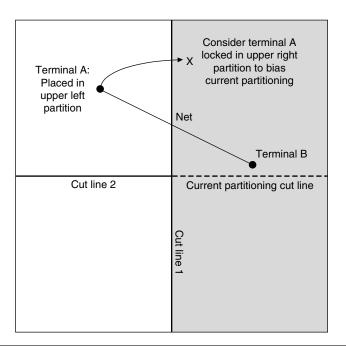

|      | 14.4         | Partition-based Placement                                                                                 | 312                      |

|      | 14.5         | Analytic Placement                                                                                        | 315                      |

|      | 14.6         | Further Reading and Open Challenges                                                                       | 316                      |

|      |              | References                                                                                                | 316                      |

| Contents | xi |

|----------|----|

| Contents | A. |

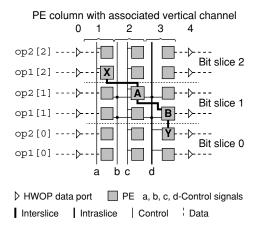

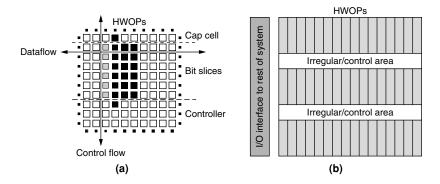

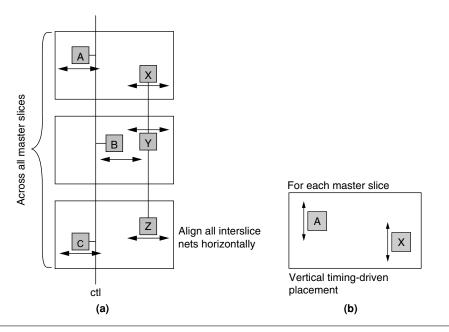

| Da   | tapath Composition                                | 319 |

|------|---------------------------------------------------|-----|

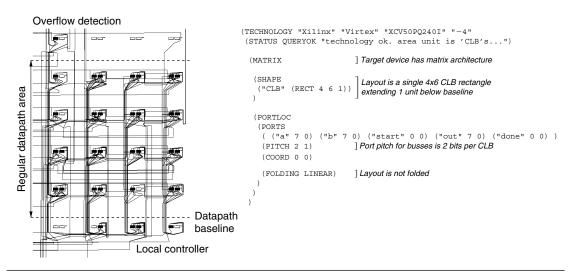

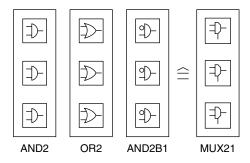

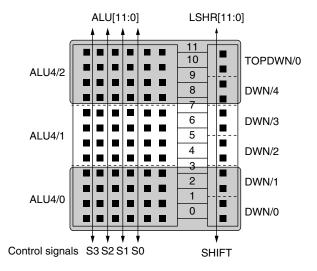

| 15.1 | Fundamentals                                      | 319 |

|      | 15.1.1 Regularity                                 | 320 |

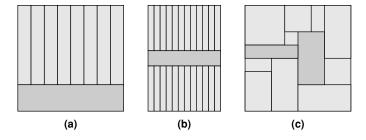

|      | 15.1.2 Datapath Layout                            | 322 |

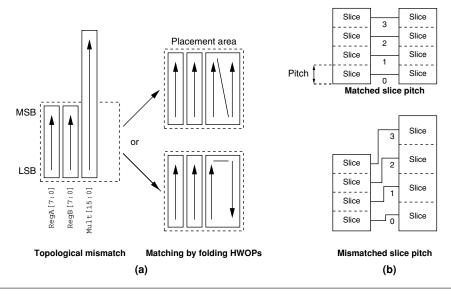

| 15.2 |                                                   | 323 |

| 15.3 |                                                   | 324 |

| 13.3 | 15.3.1 Architecture Irregularities                | 325 |

| 15 / | <del>-</del>                                      |     |

| 15.4 |                                                   | 320 |

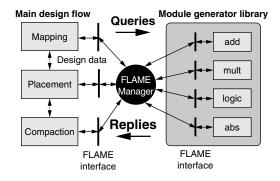

|      | 15.4.1 The Flow Interface                         | 32' |

|      | 15.4.2 The Data Model                             | 32' |

|      | 15.4.3 The Library Specification                  | 328 |

|      | 15.4.4 The Intra-module Layout                    | 328 |

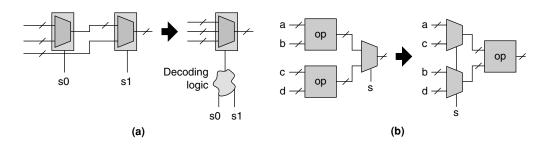

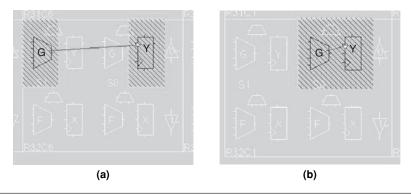

| 15.5 | The Mapping                                       | 329 |

|      | 15.5.1 1:1 Mapping                                | 329 |

|      | 15.5.2 <i>N</i> :1 Mapping                        | 330 |

|      | 15.5.3 The Combined Approach                      | 332 |

| 15.6 |                                                   | 333 |

| 10.0 | 15.6.1 Linear Placement                           | 333 |

|      | 15.6.2 Constrained Two-dimensional Placement      | 33  |

|      |                                                   | 330 |

| 155  |                                                   |     |

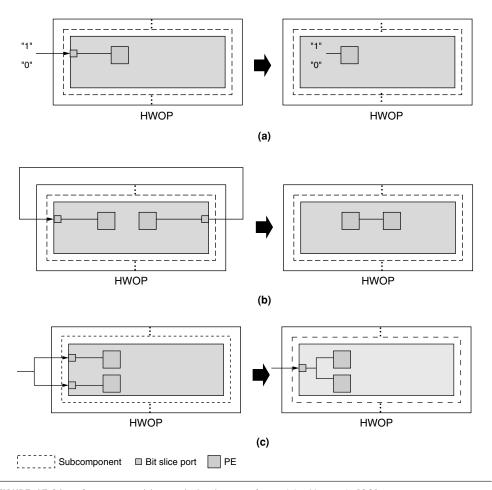

| 15.7 |                                                   | 33' |

|      | 15.7.1 Selecting HWOPs for Compaction             | 338 |

|      | 15.7.2 Regularity Analysis                        | 338 |

|      | 15.7.3 Optimization Techniques                    | 338 |

|      | 15.7.4 Building the Super-HWOP                    | 342 |

|      | 15.7.5 Discussion                                 | 34. |

| 15.8 | Summary and Future Work                           | 344 |

|      | References                                        | 344 |

| Sp   | ecifying Circuit Layout on FPGAs                  | 347 |

| 16.1 | The Problem                                       | 34  |

| 16.2 |                                                   | 35  |

| 16.3 |                                                   | 352 |

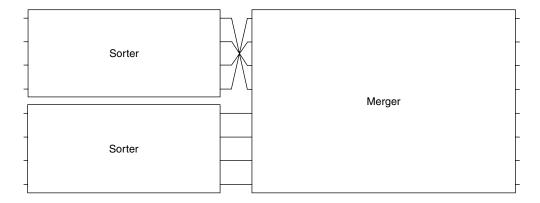

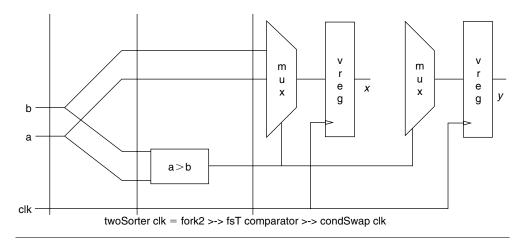

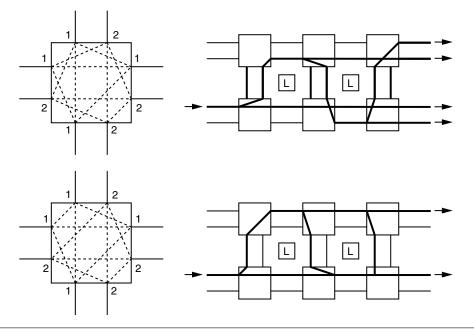

| 10.0 | 16.3.1 Case Study: Batcher's Bitonic Sorter       | 35  |

| 16.4 |                                                   | 360 |

| 16.5 | · · · · · · · · · · · · · · · · · · ·             | 362 |

| 10.5 | · ·                                               |     |

|      | References                                        | 36. |

|      | thFinder: A Negotiation-based, Performance-driven | 24  |

| Ko   | outer for FPGAs                                   | 365 |

| 17.1 | The History of PathFinder                         | 360 |

| 17.2 |                                                   | 36' |

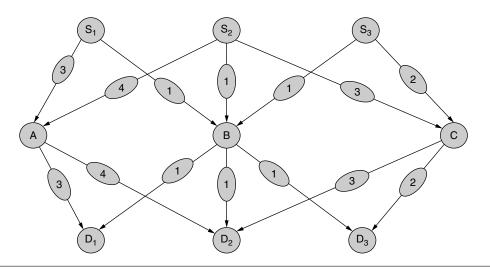

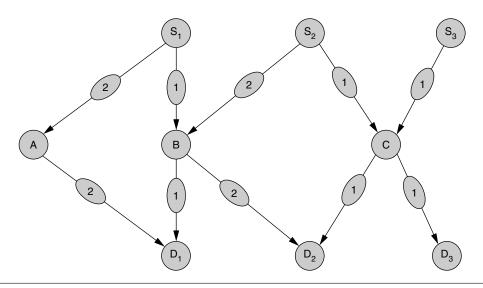

|      | 17.2.1 The Circuit Graph Model                    | 36  |

|      | 17.2.2 A Negotiated Congestion Router             | 36  |

|      | 17.2.2 A Negotiated Congestion Router             | 372 |

|      |                                                   |     |

| 17.3 | 17.2.4 Applying A* to PathFinder                  | 373 |

| 17.3 |                                                   | 374 |

|      | 17.3.1 Incremental Rerouting                      | 374 |

|     |       | 17.3.2 The Cost Function                            | 375 |

|-----|-------|-----------------------------------------------------|-----|

|     |       | 17.3.3 Resource Cost                                | 375 |

|     |       | 17.3.4 The Relationship of PathFinder to Lagrangian |     |

|     |       | Relaxation                                          | 376 |

|     |       | 17.3.5 Circuit Graph Extensions                     | 376 |

|     | 17.4  | Parallel PathFinder                                 | 377 |

|     | 17.5  | Other Applications of the PathFinder Algorithm      | 379 |

|     | 17.5  |                                                     |     |

|     | 17.0  | Summary                                             | 379 |

|     |       | References                                          | 380 |

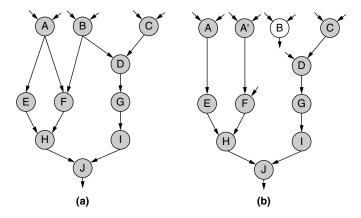

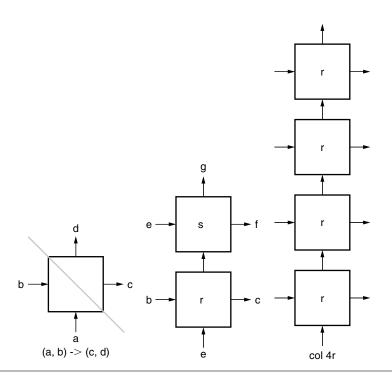

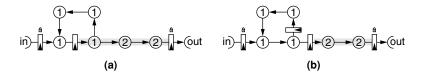

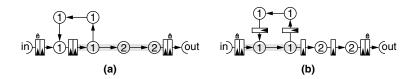

| 18  | Ret   | iming, Repipelining, and C-slow Retiming            | 383 |

|     | 18.1  | Retiming: Concepts, Algorithm, and Restrictions     | 384 |

|     | 18.2  | Repipelining and <i>C</i> -slow Retiming            | 388 |

|     |       | 18.2.1 Repipelining                                 | 389 |

|     |       | 18.2.2 <i>C</i> -slow Retiming                      | 390 |

|     | 18.3  | Implementations of Retiming                         | 393 |

|     | 18.4  | Retiming on Fixed-frequency FPGAs                   | 394 |

|     | 18.5  | C-slowing as Multi-threading                        | 395 |

|     |       |                                                     |     |

|     | 18.6  | Why Isn't Retiming Ubiquitous?                      | 398 |

|     |       | References                                          | 398 |

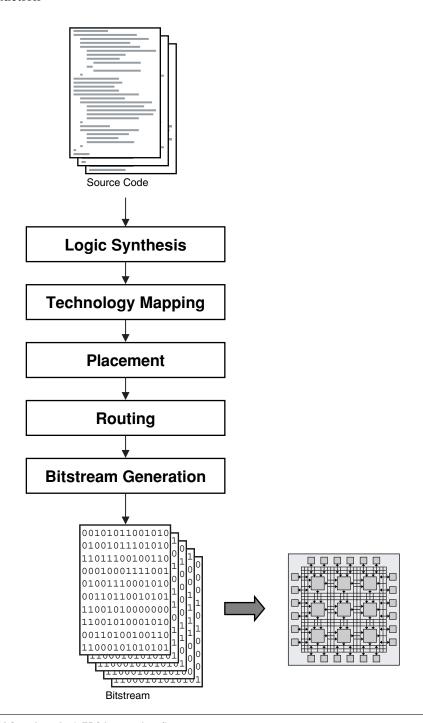

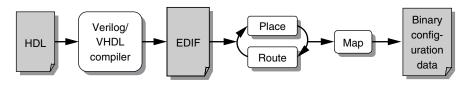

| 19  | Con   | figuration Bitstream Generation                     | 401 |

|     | 19.1  | The Bitstream                                       | 403 |

|     | 19.2  | Downloading Mechanisms                              | 406 |

|     | 19.3  | Software to Generate Configuration Data             | 407 |

|     | 19.4  | Summary                                             | 409 |

|     | 17.7  | References                                          | 409 |

|     |       | References                                          |     |

| 20  | Fas   | t Compilation Techniques                            | 411 |

|     | 20.1  | Accelerating Classical Techniques                   | 414 |

|     |       | 20.1.1 Accelerating Simulated Annealing             | 415 |

|     |       | 20.1.2 Accelerating PathFinder                      | 418 |

|     | 20.2  | Alternative Algorithms                              | 422 |

|     |       | 20.2.1 Multiphase Solutions                         | 422 |

|     |       | 20.2.2 Incremental Place and Route                  | 425 |

|     | 20.3  | Effect of Architecture                              | 427 |

|     | 20.3  | Summary                                             | 431 |

|     | 20.4  |                                                     |     |

|     |       | References                                          | 432 |

| Par | t IV: | Application Development                             | 435 |

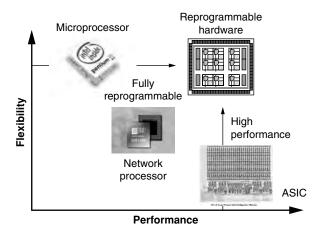

| 21  | Imp   | plementing Applications with FPGAs                  | 439 |

|     | 21.1  | Strengths and Weaknesses of FPGAs                   | 439 |

|     | -1.1  | 21.1.1 Time to Market                               | 439 |

|     |       |                                                     | 440 |

|     |       |                                                     |     |

|     |       | 21.1.3 Development Time                             | 440 |

|     |       | 21.1.4 Power Consumption                            | 440 |

|     |       | 21.1.5 Debug and Verification                       | 440 |

|     |       | 21.1.6 FPGAs and Microprocessors                    | 441 |

|     |      | Contents                                                 | xiii       |

|-----|------|----------------------------------------------------------|------------|

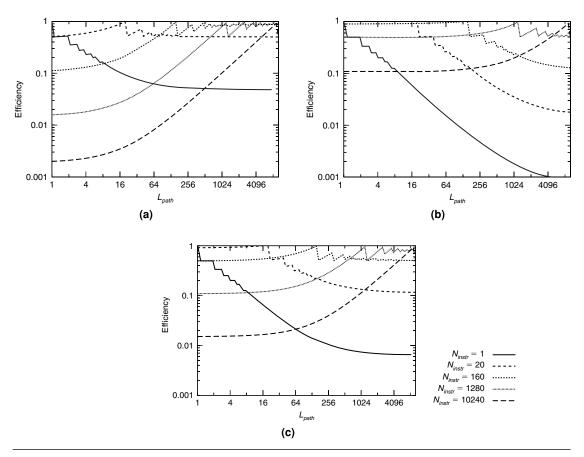

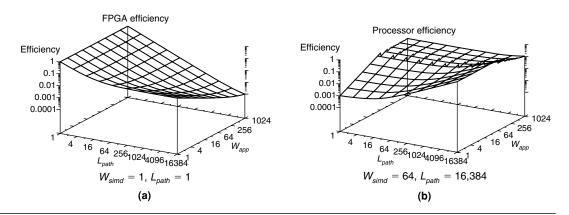

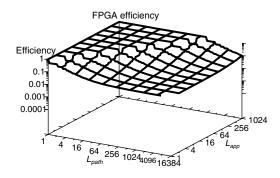

|     | 21.2 | Application Characteristics and Performance              | 441<br>441 |

|     |      | 21.2.2 I/O and Performance                               | 443        |

|     | 21.3 | General Implementation Strategies for FPGA-based Systems | 445        |

|     |      | 21.3.1 Configure-once                                    | 445        |

|     |      | 21.3.2 Runtime Reconfiguration                           | 446        |

|     |      | 21.3.3 Summary of Implementation Issues                  | 447        |

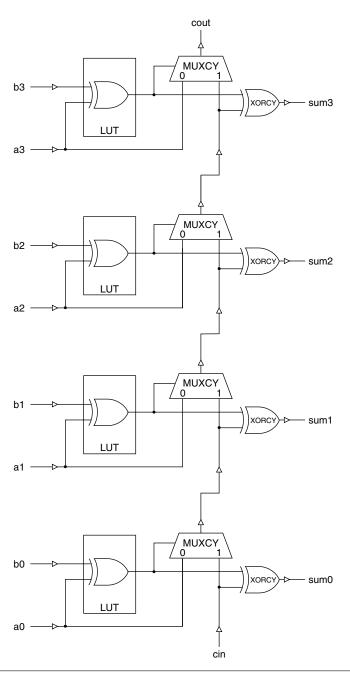

|     | 21.4 | Implementing Arithmetic in FPGAs                         | 448        |

|     |      | 21.4.1 Fixed-point Number Representation and Arithmetic  | 448        |

|     |      | 21.4.2 Floating-point Arithmetic                         | 449        |

|     |      | 21.4.3 Block Floating Point                              | 450        |

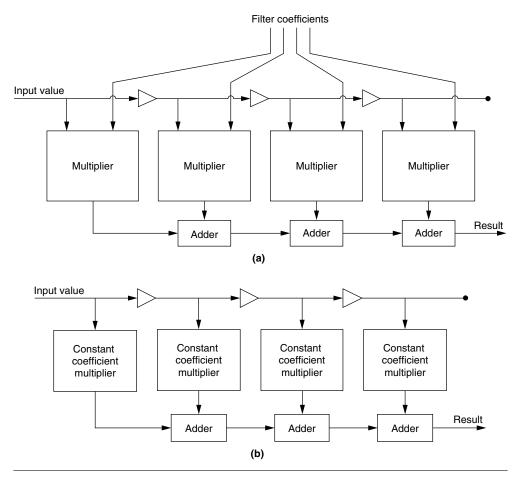

|     |      | 21.4.4 Constant Folding and Data-oriented Specialization | 450        |

|     | 21.5 | Summary                                                  | 452        |

|     |      | References                                               | 452        |

| 22  | Inst | tance-specific Design                                    | 455        |

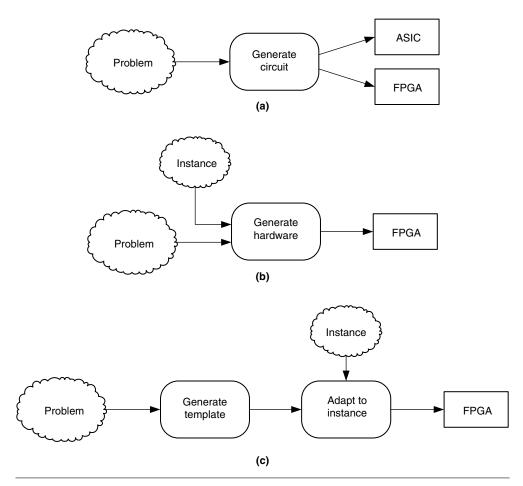

|     | 22.1 | Instance-specific Design                                 | 455        |

|     |      | 22.1.1 Taxonomy                                          | 456        |

|     |      | 22.1.2 Approaches                                        | 457        |

|     |      | 22.1.3 Examples of Instance-specific Designs             | 459        |

|     | 22.2 | Partial Evaluation                                       | 462        |

|     |      | 22.2.1 Motivation                                        | 463        |

|     |      | 22.2.2 Process of Specialization                         | 464        |

|     |      | 22.2.3 Partial Evaluation in Practice                    | 464        |

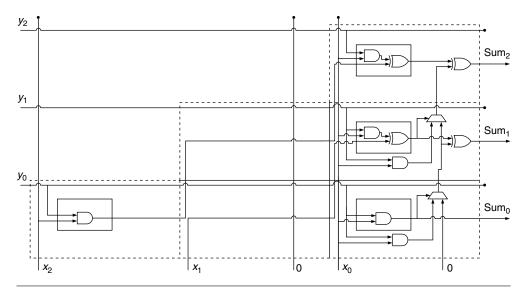

|     |      | 22.2.4 Partial Evaluation of a Multiplier                | 466        |

|     |      | 22.2.5 Partial Evaluation at Runtime                     | 470        |

|     | 22.2 | 22.2.6 FPGA-specific Concerns                            | 471        |

|     | 22.3 | Summary                                                  | 473<br>473 |

|     |      | References                                               | 4/3        |

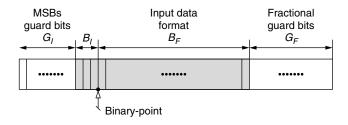

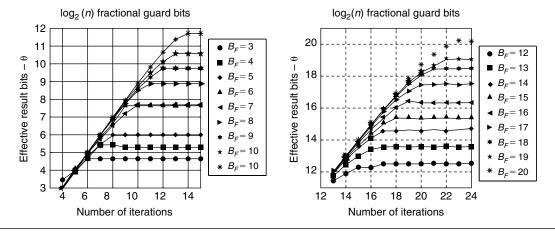

| 23  | Pre  | cision Analysis for Fixed-point Computation              | 475        |

|     | 23.1 | Fixed-point Number System                                | 475        |

|     |      | 23.1.1 Multiple-wordlength Paradigm                      | 476        |

|     |      | 23.1.2 Optimization for Multiple Wordlength              | 478        |

|     | 23.2 | Peak Value Estimation                                    | 478        |

|     |      | 23.2.1 Analytic Peak Estimation                          | 479        |

|     |      | 23.2.2 Simulation-based Peak Estimation                  | 484        |

|     | 22.2 | 23.2.3 Summary of Peak Estimation                        | 485        |

|     | 23.3 | Wordlength Optimization                                  | 485        |

|     |      |                                                          | 485        |

|     | 23.4 | 23.3.2 Search Techniques                                 | 496<br>498 |

|     | 23.4 | Summary                                                  | 498<br>499 |

| 24  | Dist | tributed Arithmetic                                      | 503        |

| - • | 24.1 | Theory                                                   | 503        |

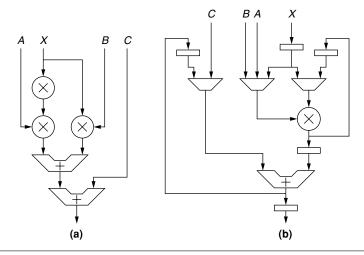

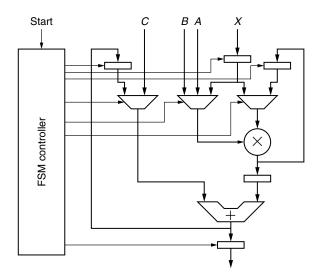

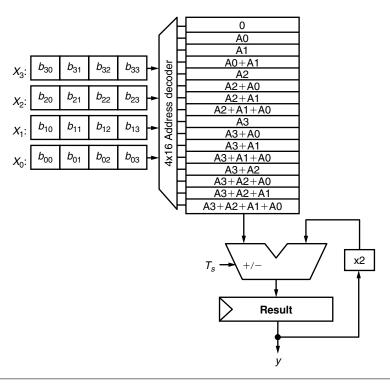

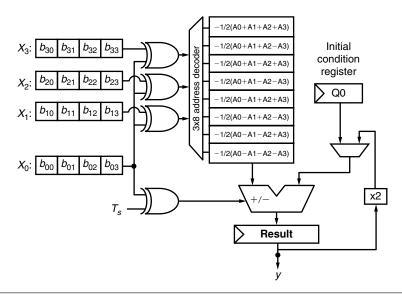

|     | 24.2 | DA Implementation                                        | 504        |

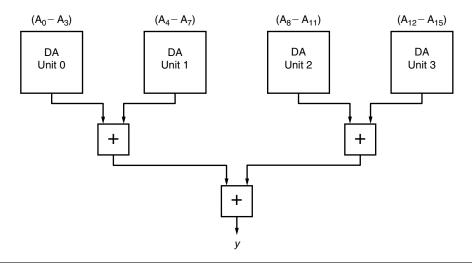

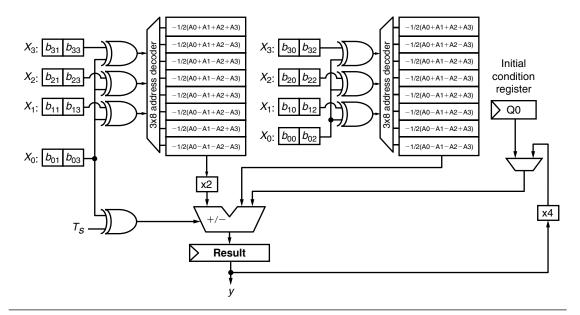

|     | 24.3 | Mapping DA onto FPGAs                                    | 507        |

|     | 24.4 | Improving DA Performance                                 | 508        |

|     |      |                                                          |            |

|           | 24.5 | An Application of DA on an FPGA                      | 511        |

|-----------|------|------------------------------------------------------|------------|

|           |      | References                                           | 511        |

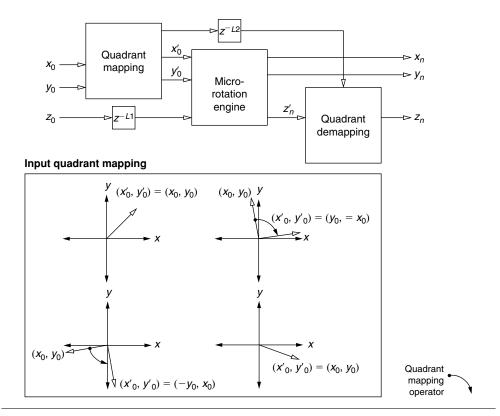

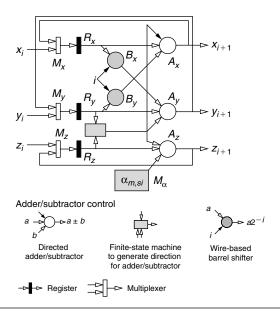

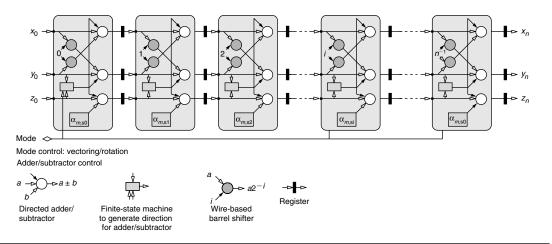

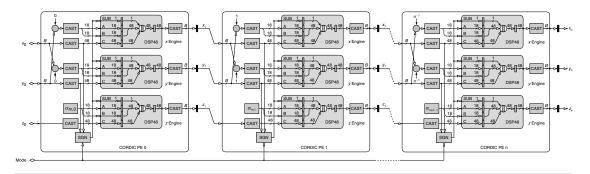

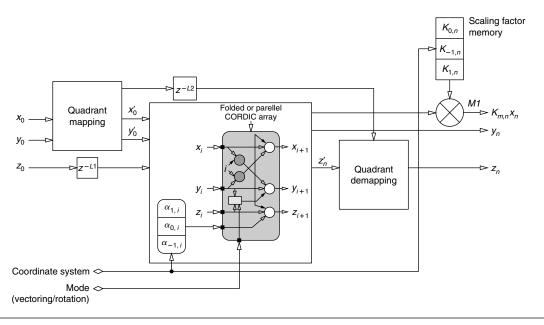

| 25        | COI  | RDIC Architectures for FPGA Computing                | 513        |

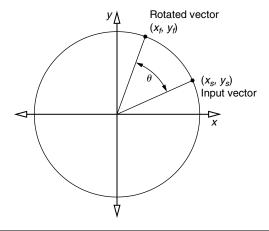

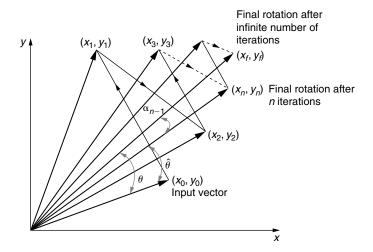

|           | 25.1 | CORDIC Algorithm                                     | 514        |

|           |      | 25.1.1 Rotation Mode                                 | 514        |

|           |      | 25.1.2 Scaling Considerations                        | 517        |

|           |      | 25.1.3 Vectoring Mode                                | 519        |

|           |      | 25.1.4 Multiple Coordinate Systems and a Unified     |            |

|           |      | Description                                          | 520        |

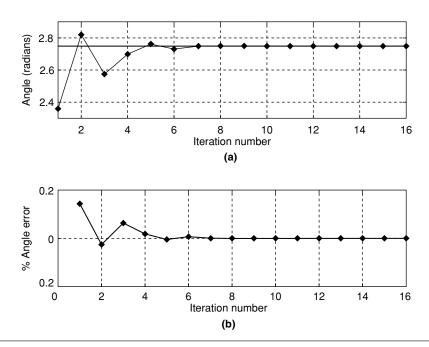

|           |      | 25.1.5 Computational Accuracy                        | 522        |

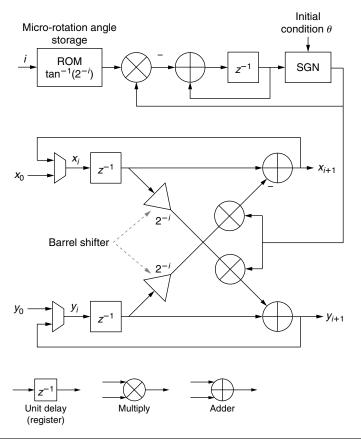

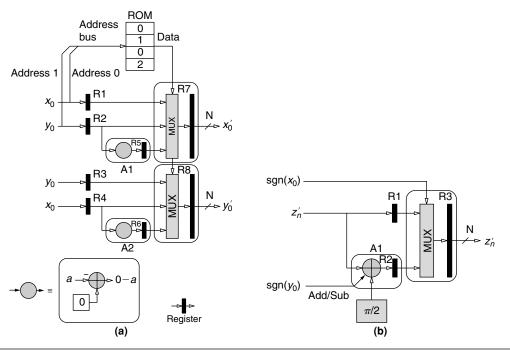

|           | 25.2 | Architectural Design                                 | 526        |

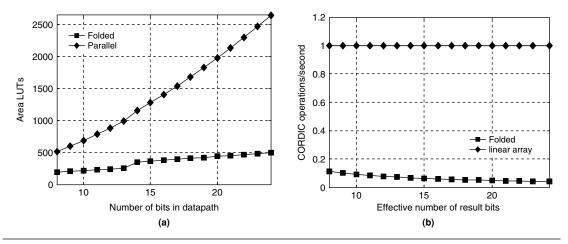

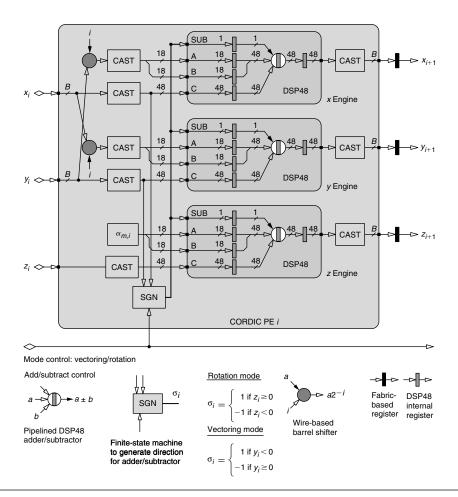

|           | 25.3 | FPGA Implementation of CORDIC Processors             | 527        |

|           |      | 25.3.1 Convergence                                   | 527        |

|           |      | 25.3.2 Folded CORDIC                                 | 528        |

|           |      | 25.3.3 Parallel Linear Array                         | 530        |

|           |      | 25.3.4 Scaling Compensation                          | 534        |

|           | 25.4 | Summary                                              | 534        |

|           |      | References                                           | 535        |

| 21        | **   | 1 10 % P 111                                         | <b>530</b> |

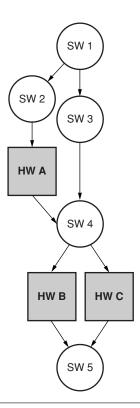

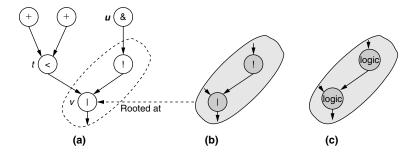

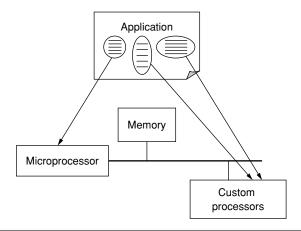

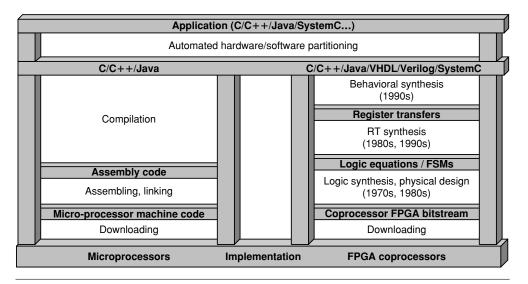

| 26        |      | dware/Software Partitioning                          | 539        |

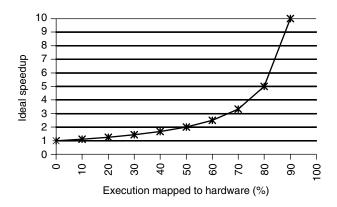

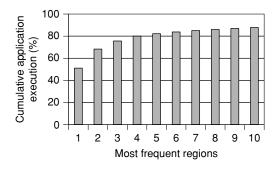

|           | 26.1 | The Trend Toward Automatic Partitioning              | 540        |

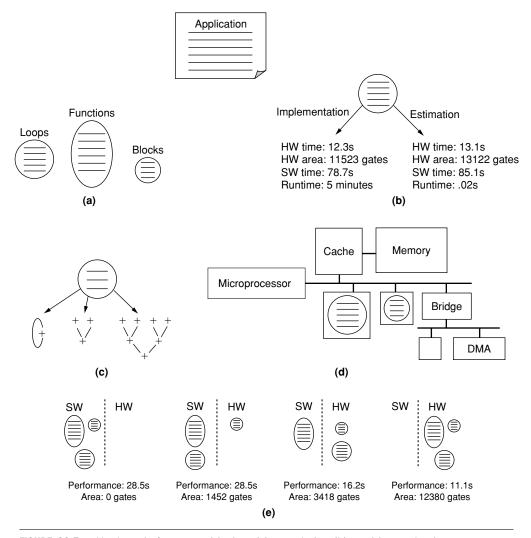

|           | 26.2 | Partitioning of Sequential Programs                  | 542        |

|           |      | 26.2.1 Granularity                                   | 545        |

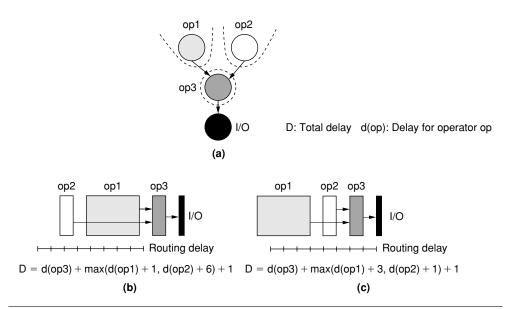

|           |      | 26.2.2 Partition Evaluation                          | 547        |

|           |      | 26.2.3 Alternative Region Implementations            | 549        |

|           |      | 26.2.4 Implementation Models                         | 550        |

|           |      | 26.2.5 Exploration                                   | 552        |

|           | 26.3 | Partitioning of Parallel Programs                    | 557        |

|           |      | 26.3.1 Differences among Parallel Programming Models | 557        |

|           | 26.4 | Summary and Directions                               | 558        |

|           |      | References                                           | 559        |

|           |      |                                                      |            |

| Par       |      | ase Studies of FPGA Applications                     | 561        |

| <b>27</b> | SPI  | HT Image Compression                                 | 565        |

|           | 27.1 | Background                                           | 565        |

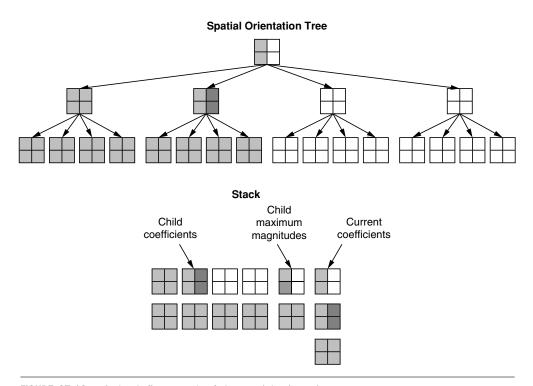

|           | 27.2 | SPIHT Algorithm                                      | 566        |

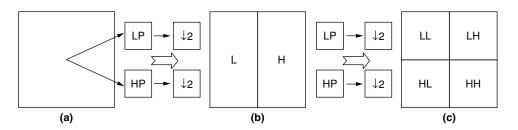

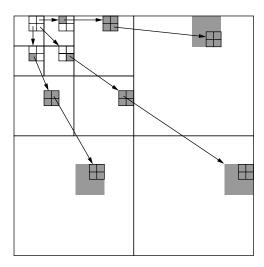

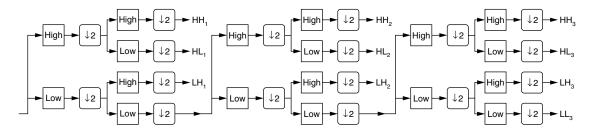

|           |      | 27.2.1 Wavelets and the Discrete Wavelet Transform   | 567        |

|           |      | 27.2.2 SPIHT Coding Engine                           | 568        |

|           | 27.3 | Design Considerations and Modifications              | 571        |

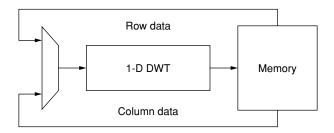

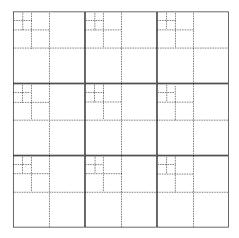

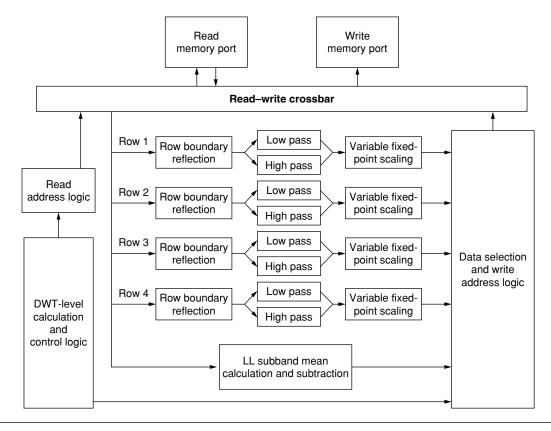

|           |      | 27.3.1 Discrete Wavelet Transform Architectures      | 571        |

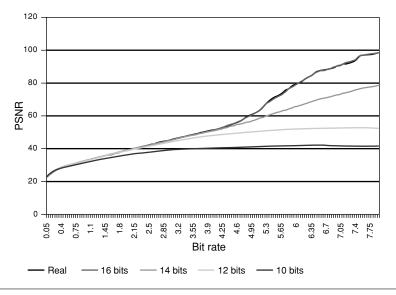

|           |      | 27.3.2 Fixed-point Precision Analysis                | 575        |

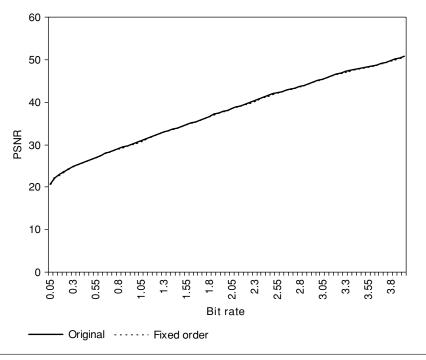

|           |      | 27.3.3 Fixed Order SPIHT                             | 578        |

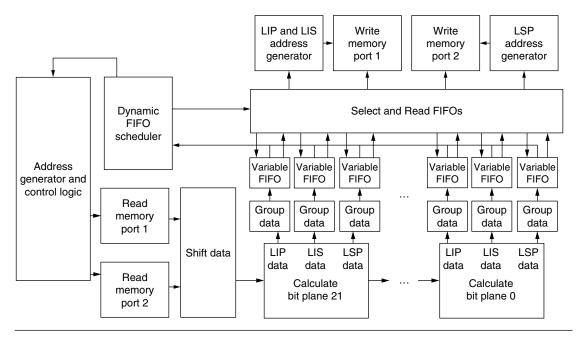

|           | 27.4 | Hardware Implementation                              | 580        |

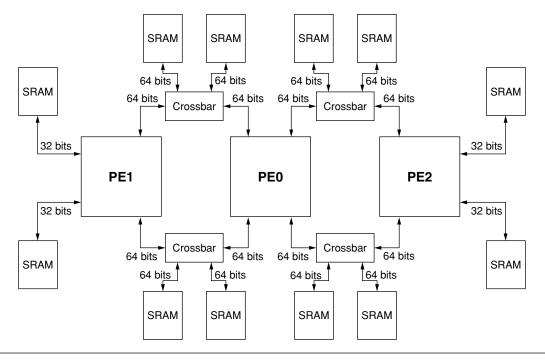

|           | ∠1.¬ | 27.4.1 Target Hardware Platform                      | 581        |

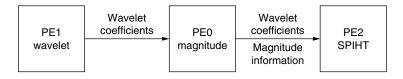

|           |      | 27.4.2 Design Overview                               | 581        |

|           |      | 27.4.2 Design Overview                               | 582        |

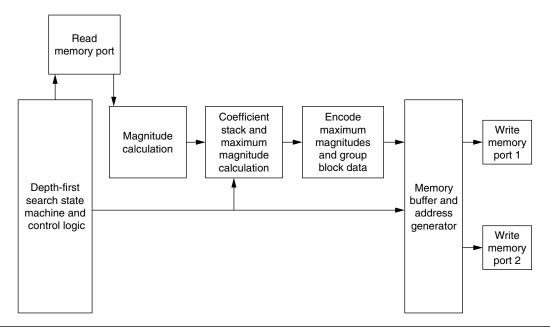

|           |      | 27.4.4 Maximum Magnitude Phase                       | 583        |

|           |      | 27.4.5 The SPIHT Coding Phase                        | 585        |

|      | Contents                                                  | XV         |

|------|-----------------------------------------------------------|------------|

| 27.5 | Decign Pacults                                            | 587        |

| 27.6 | Design Results                                            | 588        |

| 21.0 | References                                                | 589        |

|      |                                                           | 367        |

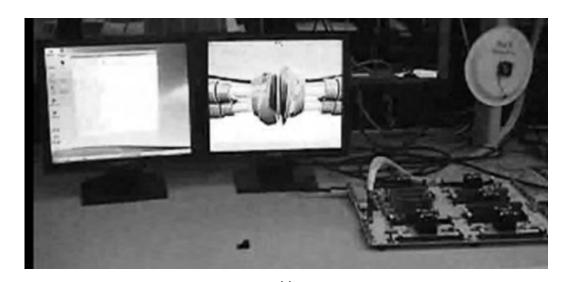

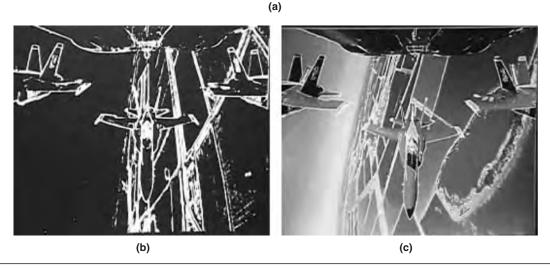

|      | comatic Target Recognition Systems Reconfigurable Devices | 591        |

| -    |                                                           |            |

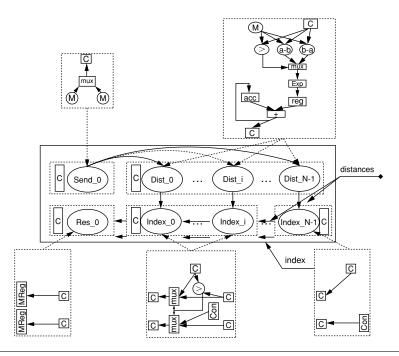

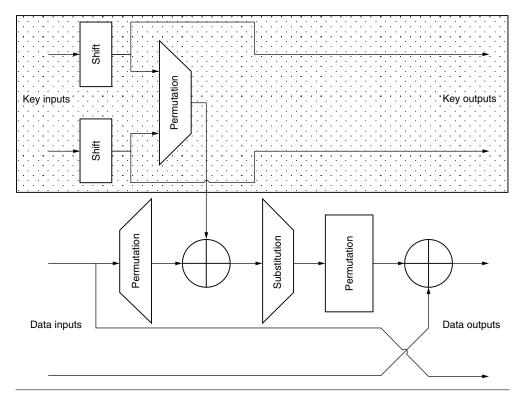

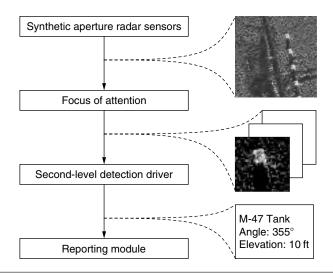

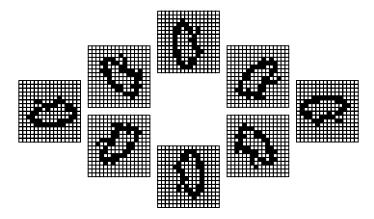

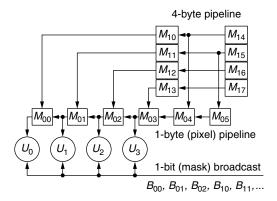

| 28.1 | Automatic Target Recognition Algorithms                   | 592<br>592 |

|      | 28.1.1 Focus of Attention                                 | 592<br>592 |

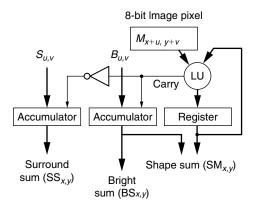

| 28.2 |                                                           | 592<br>594 |

| 20.2 | Dynamically Reconfigurable Designs                        | 594<br>594 |

|      | S                                                         |            |

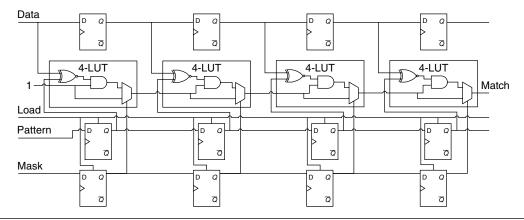

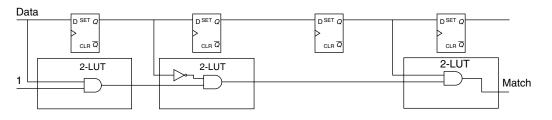

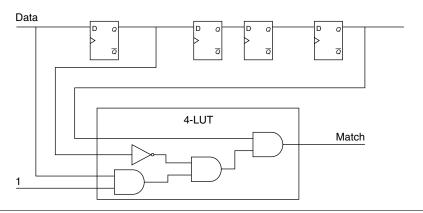

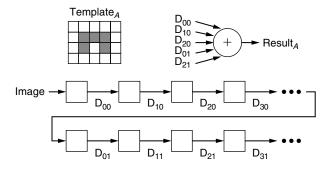

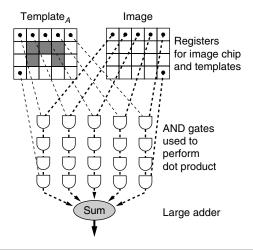

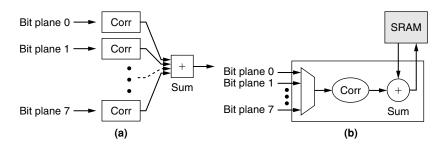

|      | 28.2.2 Image Correlation Circuit                          | 594        |

|      | 28.2.3 Performance Analysis                               | 596        |

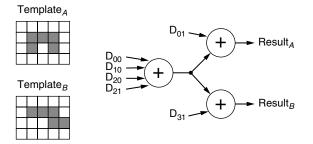

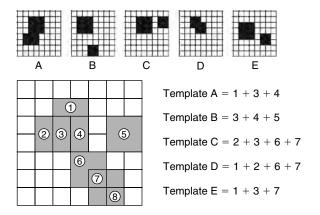

|      | 28.2.4 Template Partitioning                              | 598        |

|      | 28.2.5 Implementation Method                              | 599        |

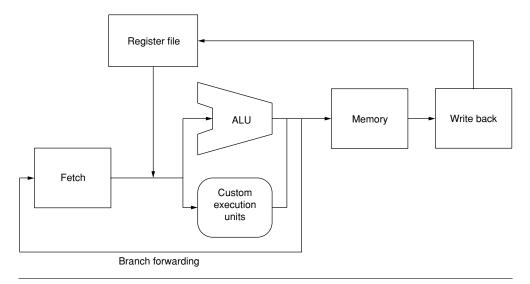

| 28.3 | Reconfigurable Static Design                              | 600        |

|      | 28.3.1 Design-specific Parameters                         | 601        |

|      | 28.3.2 Order of Correlation Tasks                         | 601        |

|      | 28.3.3 Reconfigurable Image Correlator                    | 602        |

|      | 28.3.4 Application-specific Computation Unit              | 603        |

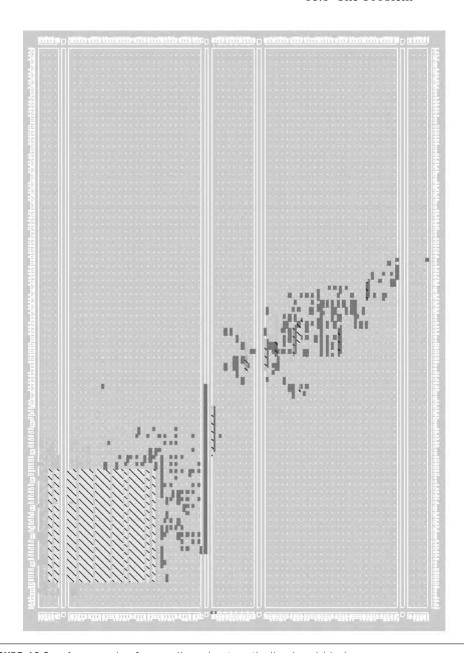

| 28.4 | ATR Implementations                                       | 604        |

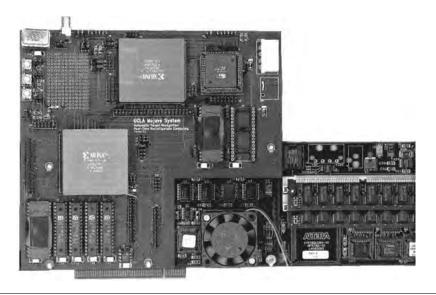

|      | 28.4.1 A Dynamically Reconfigurable System                | 604        |

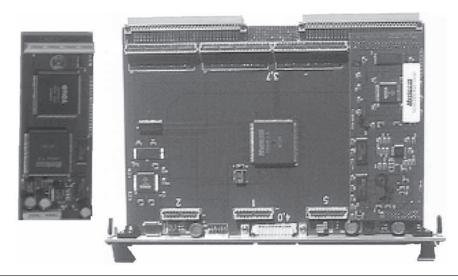

|      | 28.4.2 A Statically Reconfigurable System                 | 606        |

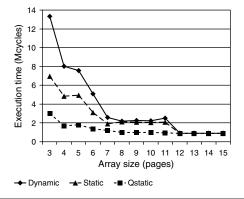

|      | 28.4.3 Reconfigurable Computing Models                    | 607        |

| 28.5 | Summary                                                   | 609        |

|      | References                                                | 610        |

| Boo  | olean Satisfiability: Creating Solvers Optimized          |            |

| for  | <b>Specific Problem Instances</b>                         | 613        |

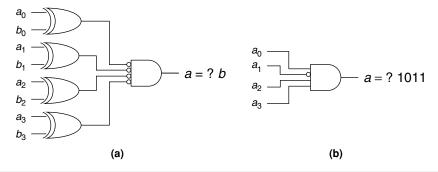

| 29.1 | Boolean Satisfiability Basics                             | 613        |

|      | 29.1.1 Problem Formulation                                | 613        |

|      | 29.1.2 SAT Applications                                   | 614        |

| 29.2 | SAT-solving Algorithms                                    | 615        |

|      | 29.2.1 Basic Backtrack Algorithm                          | 615        |

|      | 29.2.2 Improving the Backtrack Algorithm                  | 617        |

| 29.3 | A Reconfigurable SAT Solver Generated According to an     |            |

| _,.0 | SAT Instance                                              | 618        |

|      | 29.3.1 Problem Analysis                                   | 618        |

|      | 29.3.2 Implementing a Basic Backtrack Algorithm with      | 010        |

|      | Reconfigurable Hardware                                   | 619        |

|      | 29.3.3 Implementing an Improved Backtrack Algorithm       | 017        |

|      | with Reconfigurable Hardware                              | 624        |

| 29.4 | A Different Approach to Reduce Compilation Time and       |            |

|      | Improve Algorithm Efficiency                              | 627        |

|      | 29.4.1 System Architecture                                | 627        |

|      | 29.4.2 Performance                                        | 630        |

|      | 29.4.3 Implementation Issues                              | 631        |

| 29.5 | Discussion                                                | 633        |

|      |                                                           |            |

|      | References                                                | 635        |

| Mu   | lti-FPGA Systems: Logic Emulation                       | 637 |

|------|---------------------------------------------------------|-----|

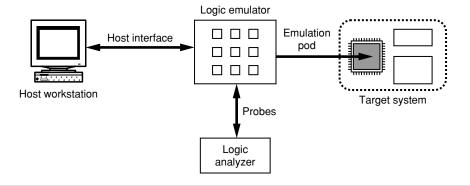

| 30.1 | Background                                              | 637 |

| 30.2 | Uses of Logic Emulation Systems                         | 639 |

| 30.3 | Types of Logic Emulation Systems                        | 640 |

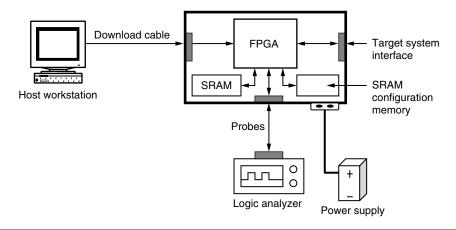

|      | 30.3.1 Single-FPGA Emulation                            | 640 |

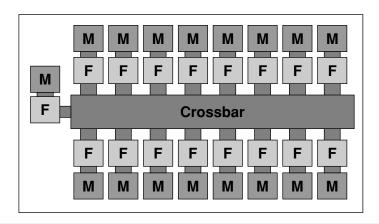

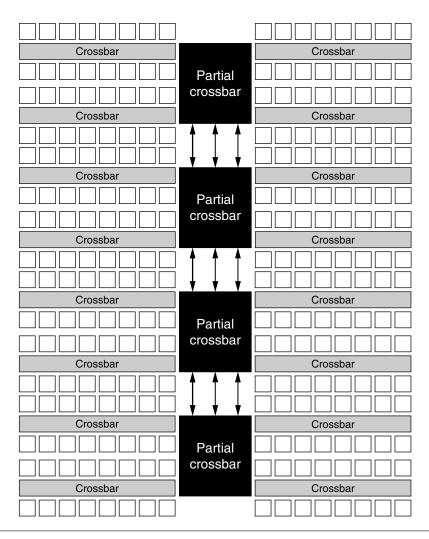

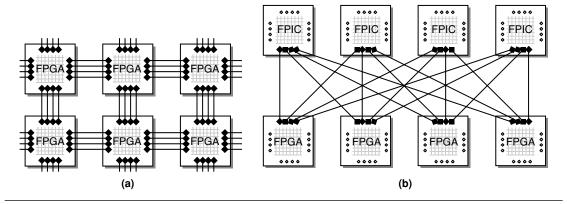

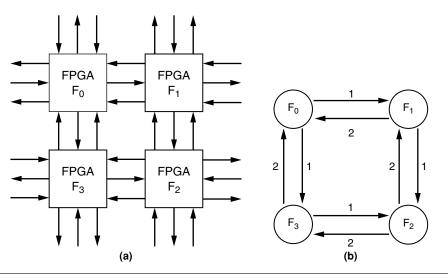

|      | 30.3.2 Multi-FPGA Emulation                             | 641 |

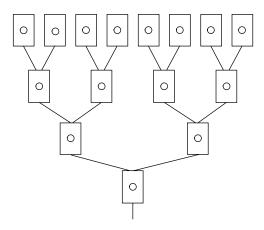

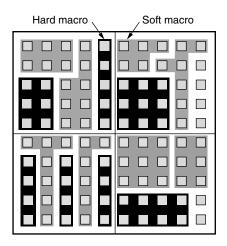

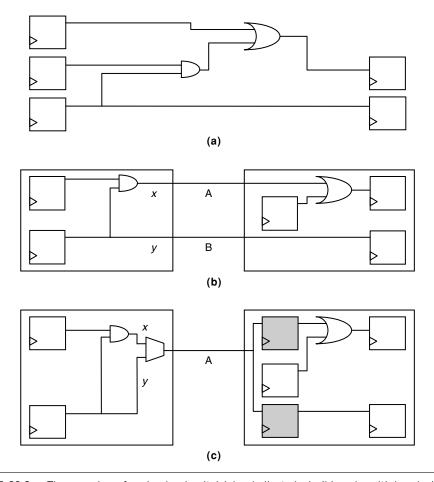

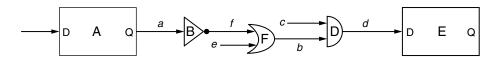

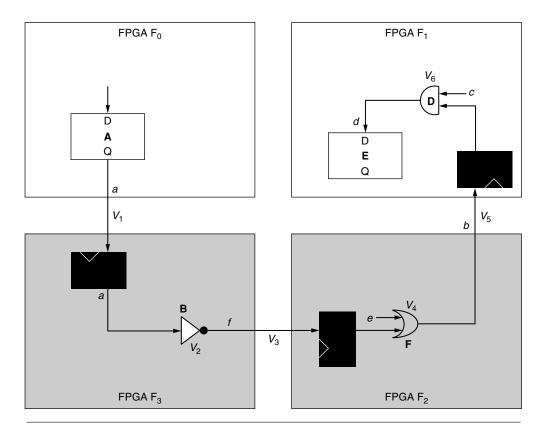

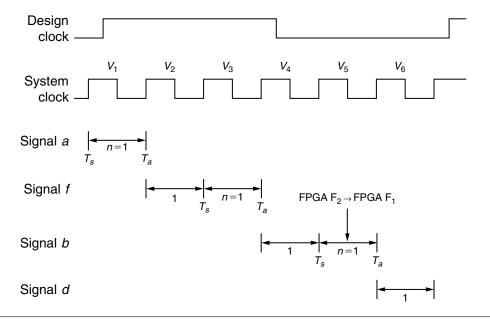

|      | 30.3.3 Design-mapping Overview                          | 644 |

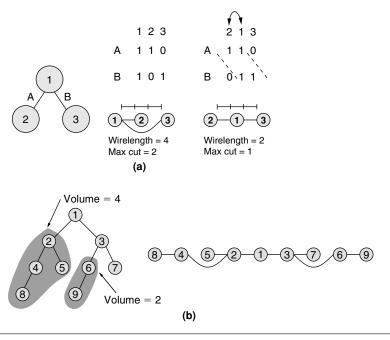

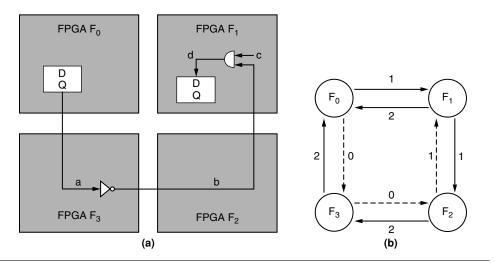

|      | 30.3.4 Multi-FPGA Partitioning and Placement Approaches | 645 |

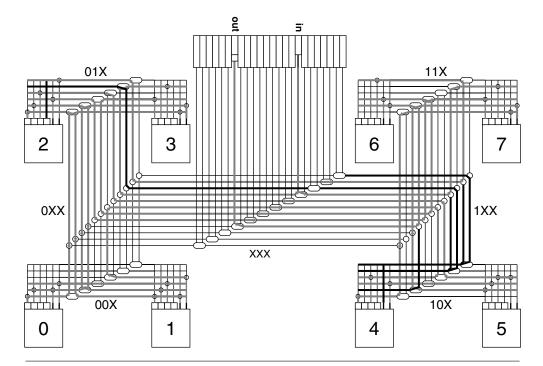

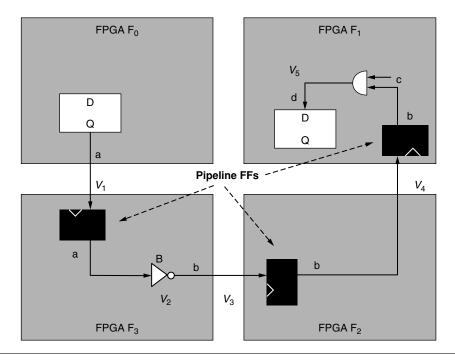

|      | 30.3.5 Multi-FPGA Routing Approaches                    | 646 |

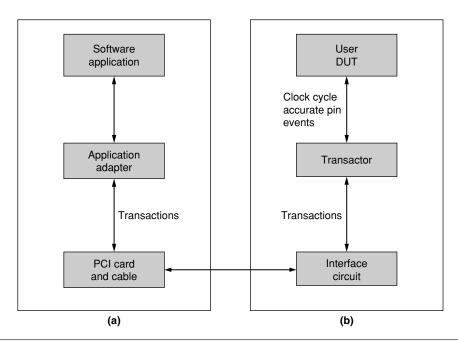

| 30.4 | Issues Related to Contemporary Logic Emulation          | 650 |

|      | 30.4.1 In-circuit Emulation                             | 650 |

|      | 30.4.2 Coverification                                   | 650 |

|      | 30.4.3 Logic Analysis                                   | 651 |

| 30.5 | The Need for Fast FPGA Mapping                          | 652 |

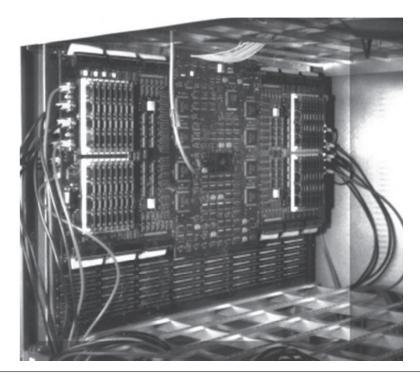

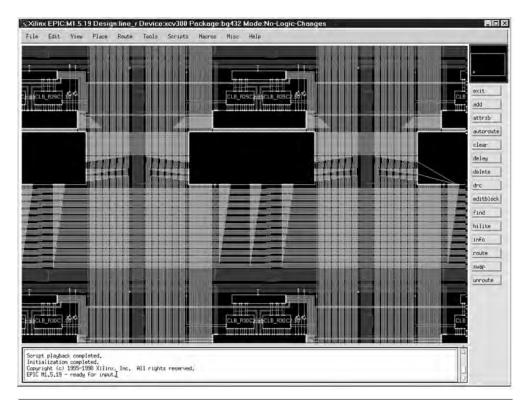

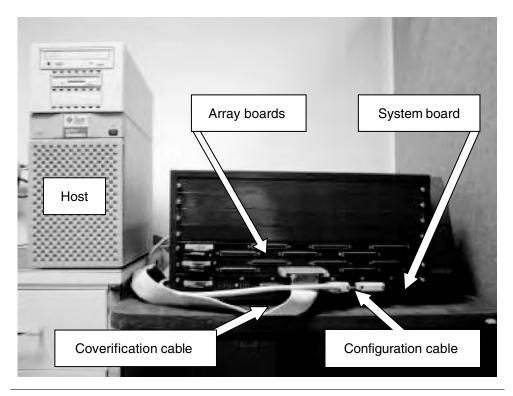

| 30.6 | Case Study: The VirtuaLogic VLE Emulation System        | 653 |

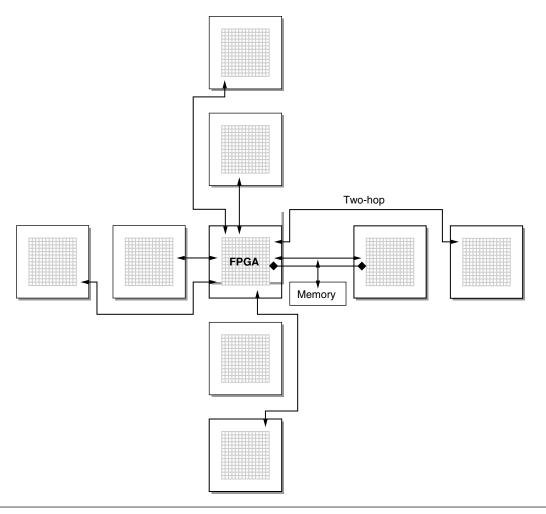

| 30.0 | 30.6.1 The VirtuaLogic VLE Emulation System Structure   | 653 |

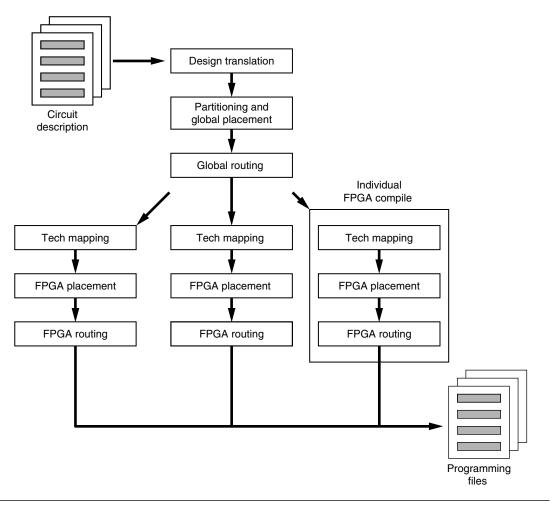

|      | 30.6.2 The VirtuaLogic Emulation Software Flow          | 654 |

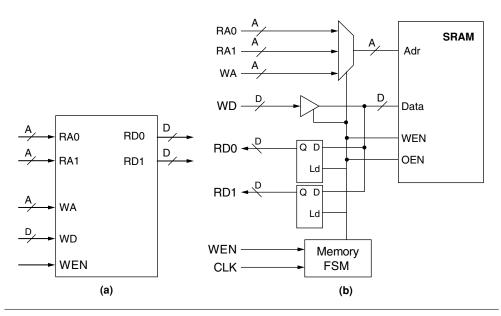

|      | 30.6.3 Multiported Memory Mapping                       | 657 |

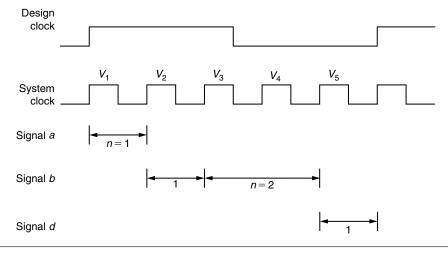

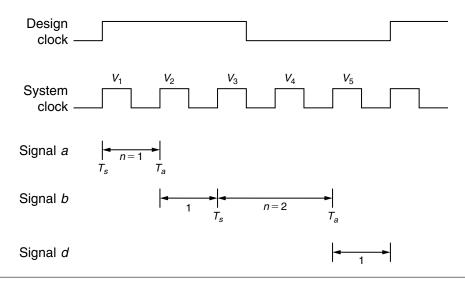

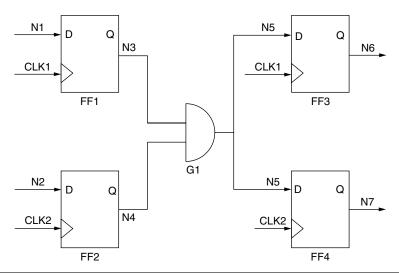

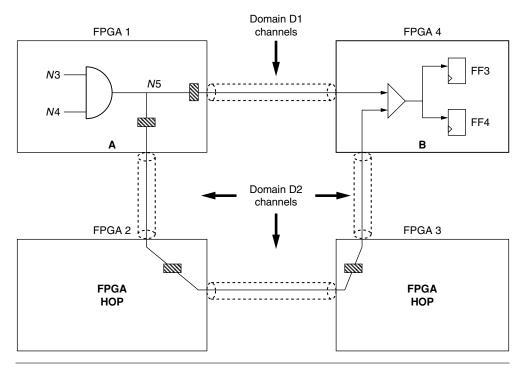

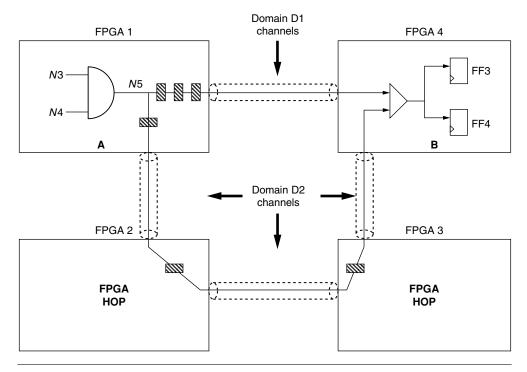

|      | 30.6.4 Design Mapping with Multiple Asynchronous Clocks | 657 |

|      |                                                         |     |

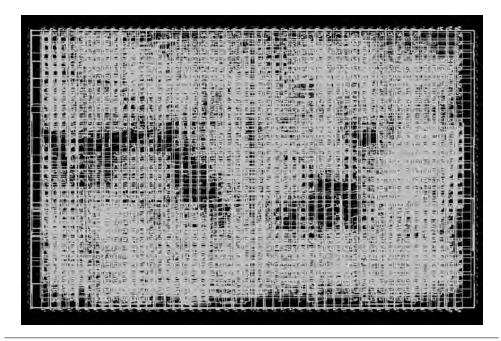

|      | 30.6.5 Incremental Compilation of Designs               | 661 |

|      | 30.6.6 VLE Interfaces for Coverification                | 664 |

| 20.7 | 30.6.7 Parallel FPGA Compilation for the VLE System     | 665 |

| 30.7 | Future Trends                                           | 666 |

| 30.8 | Summary                                                 | 667 |

|      | References                                              | 668 |

| The  | Implications of Floating Point for FPGAs                | 671 |

| 31.1 | Why Is Floating Point Difficult?                        | 671 |

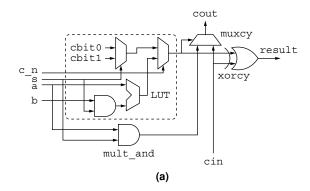

|      | 31.1.1 General Implementation Considerations            | 673 |

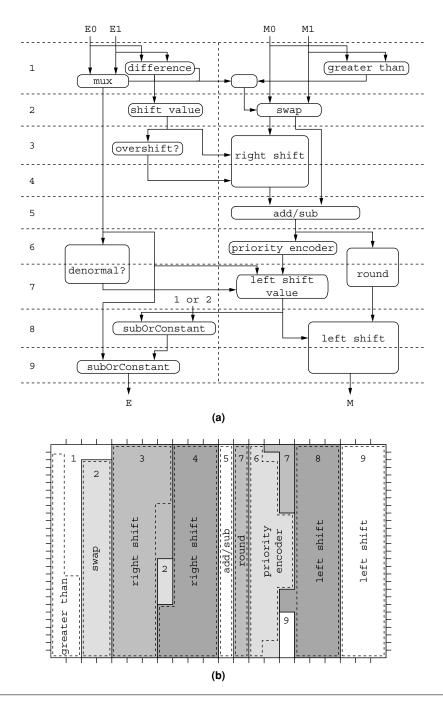

|      | 31.1.2 Adder Implementation                             | 675 |

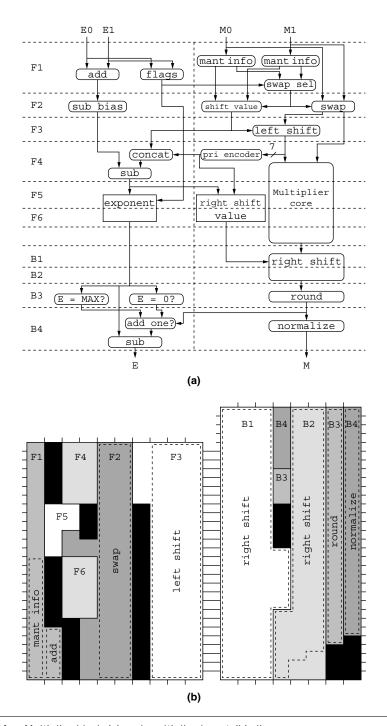

|      | 31.1.3 Multiplier Implementation                        | 677 |

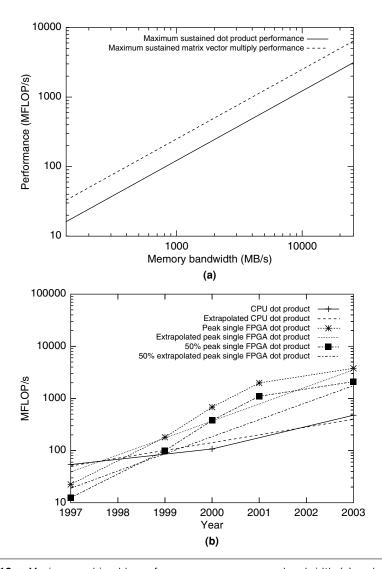

| 31.2 | Floating-point Application Case Studies                 | 679 |

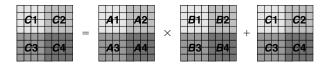

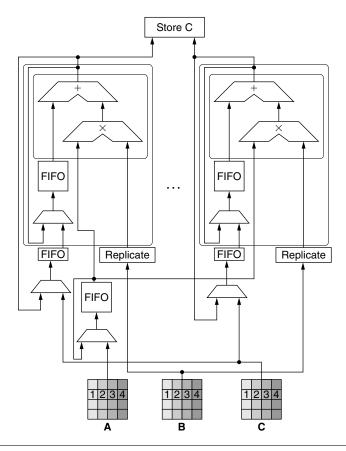

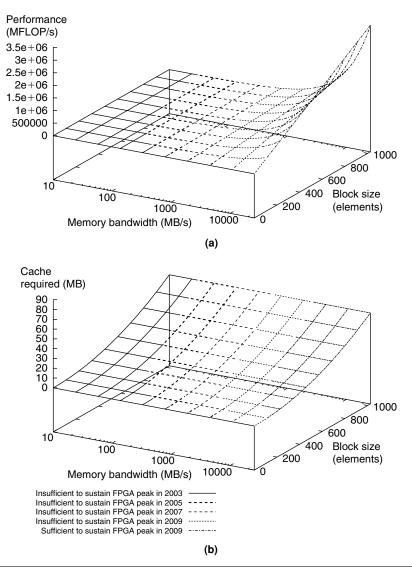

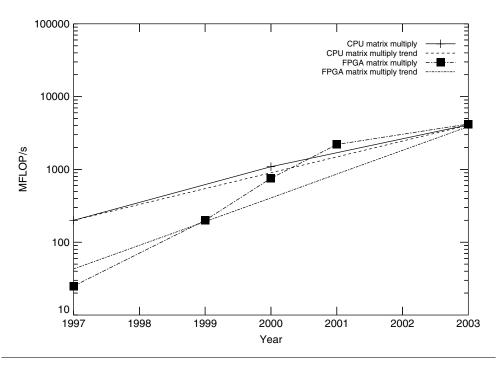

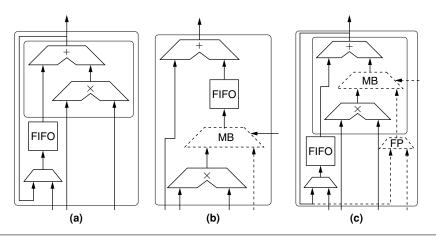

| 31.2 | 31.2.1 Matrix Multiply                                  | 679 |

|      | 31.2.2 Dot Product                                      | 683 |

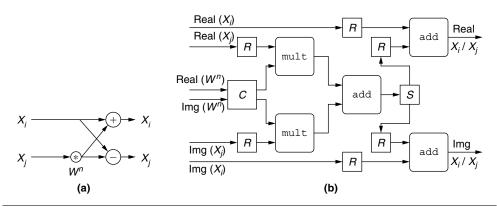

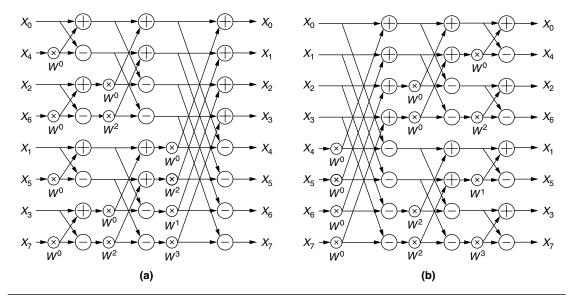

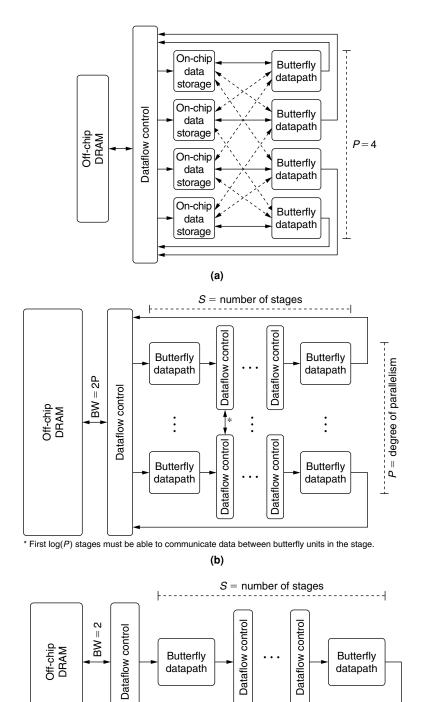

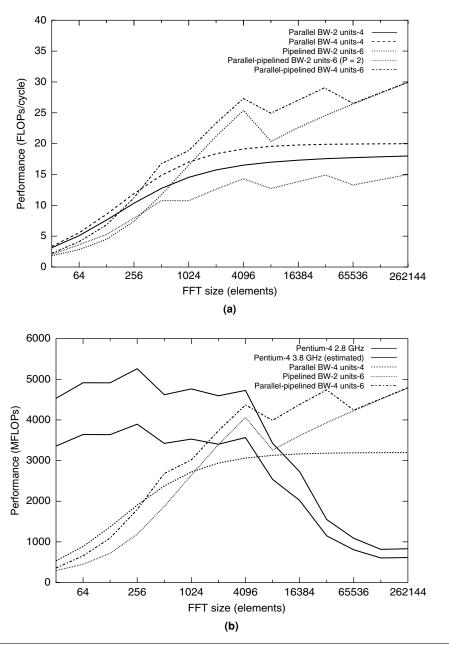

|      | 31.2.3 Fast Fourier Transform                           | 686 |

| 31.3 | Summary                                                 | 692 |

| 31.3 | References                                              | 694 |

| Ei-  |                                                         |     |

|      | ite Difference Time Domain: A Case Study ng FPGAs       | 697 |

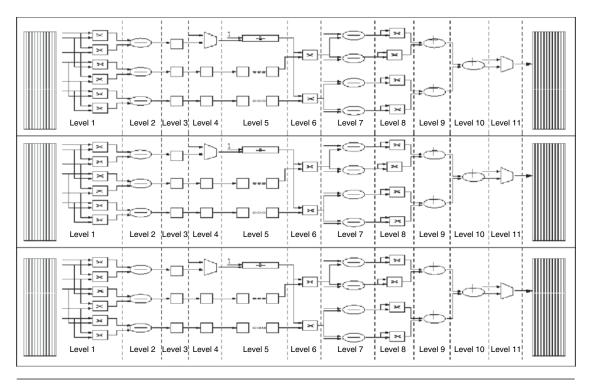

|      |                                                         |     |

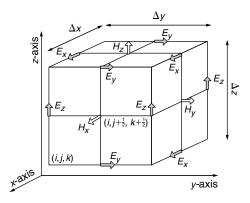

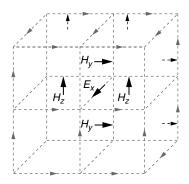

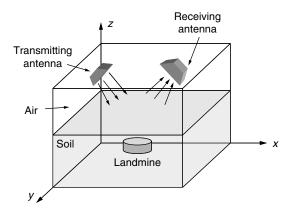

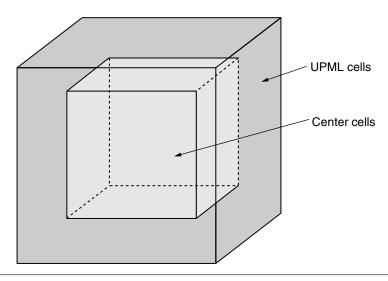

| 32.1 | The FDTD Method                                         | 697 |

|      | 32.1.1 Background                                       | 697 |

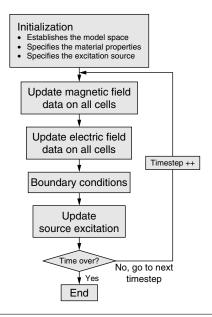

|      | 32.1.2 The FDTD Algorithm                               | 701 |

|      | 32.1.3 FDTD Applications                                | 703 |

|      | 32.1.4 The Advantages of FDTD on an FPGA                | 705 |

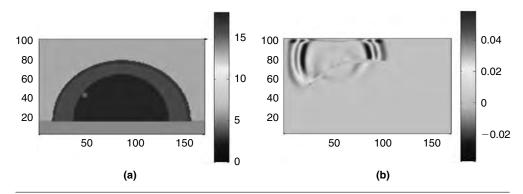

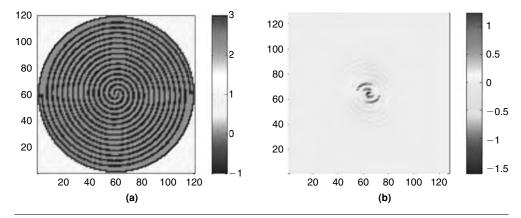

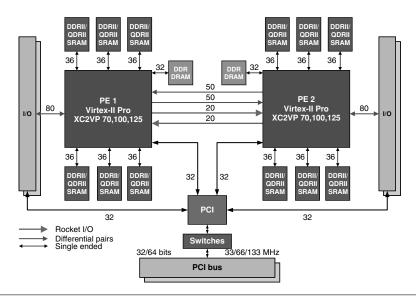

| 32.2 | FDTD Hardware Design Case Study                         | 707 |

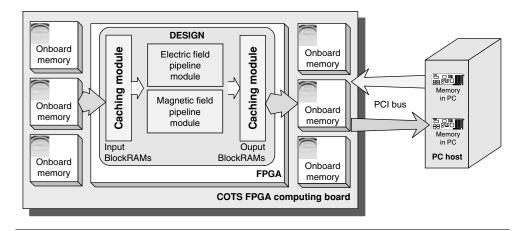

|      | 32.2.1 The WildStar-II Pro FPGA Computing Board         | 708 |

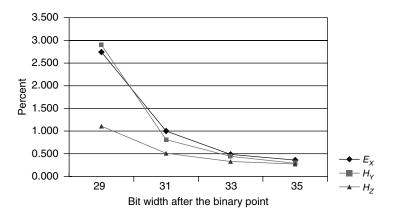

|      | 32.2.2 Data Analysis and Fixed-point Quantization       | 709 |

|     |                      | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xvii                                                                                                         |

|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|     |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

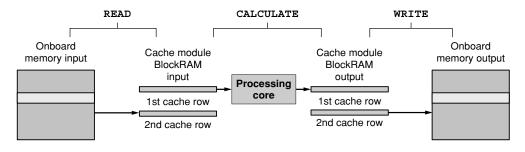

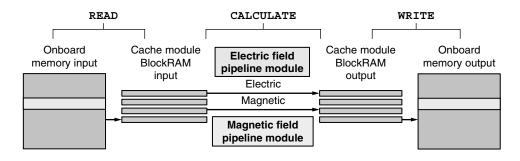

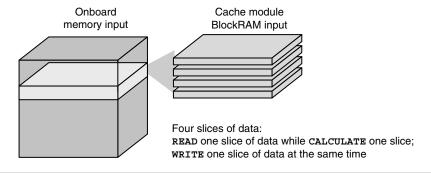

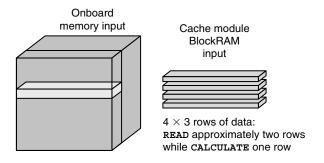

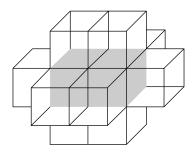

|     |                      | 32.2.3 Hardware Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 712                                                                                                          |

|     |                      | 32.2.4 Performance Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 722                                                                                                          |

|     | 32.3                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 723                                                                                                          |

|     |                      | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 723                                                                                                          |

| 33  | Evo                  | lvable FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 725                                                                                                          |

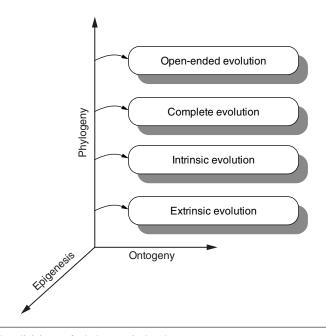

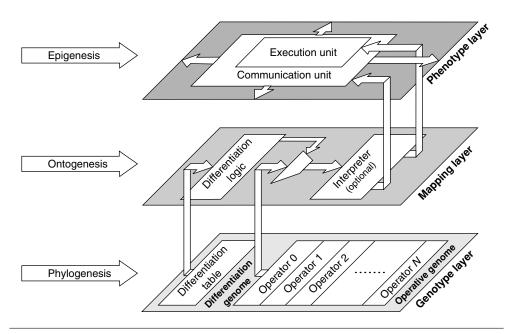

|     | 33.1                 | The POE Model of Bioinspired Design Methodologies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 725                                                                                                          |

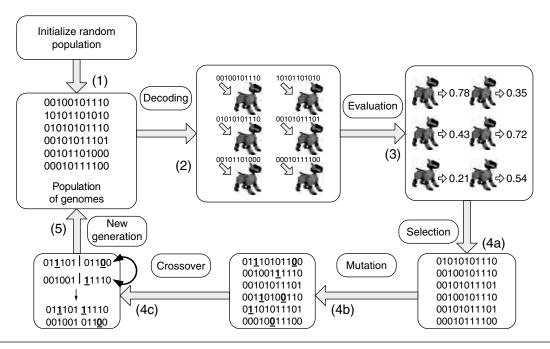

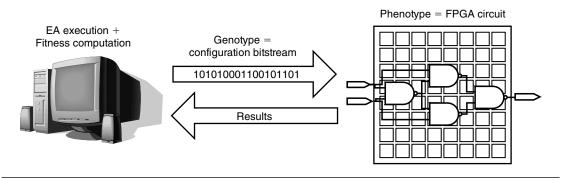

|     | 33.2                 | Artificial Evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 727                                                                                                          |

|     |                      | 33.2.1 Genetic Algorithms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 727                                                                                                          |

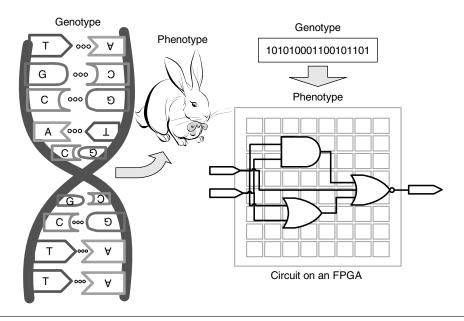

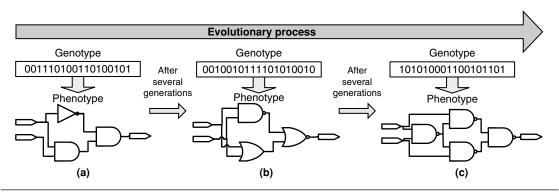

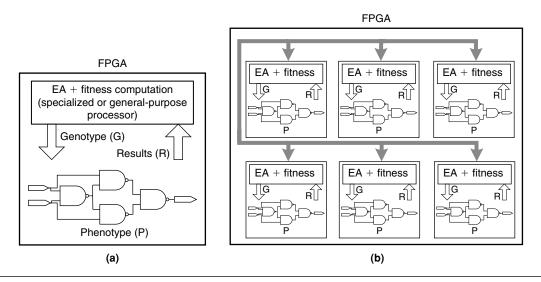

|     | 33.3                 | Evolvable Hardware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 729                                                                                                          |

|     | 22.4                 | 33.3.1 Genome Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 731                                                                                                          |

|     | 33.4                 | Evolvable Hardware: A Taxonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 733<br>733                                                                                                   |

|     |                      | 33.4.2 Intrinsic Evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 734                                                                                                          |

|     |                      | 33.4.3 Complete Evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 734                                                                                                          |

|     |                      | 33.4.4 Open-ended Evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 738                                                                                                          |

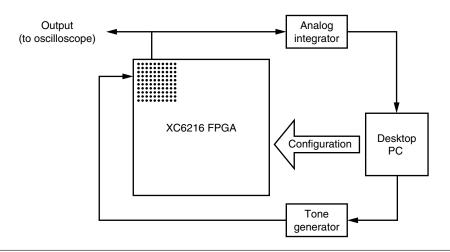

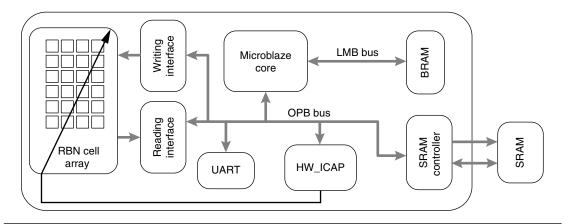

|     | 33.5                 | Evolvable Hardware Digital Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 739                                                                                                          |

|     |                      | 33.5.1 Xilinx XC6200 Family                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 740                                                                                                          |

|     |                      | 33.5.2 Evolution on Commercial FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 741                                                                                                          |

|     |                      | 33.5.3 Custom Evolvable FPGAs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 743                                                                                                          |

|     | 33.6                 | Conclusions and Future Directions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 745                                                                                                          |

|     |                      | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 747                                                                                                          |

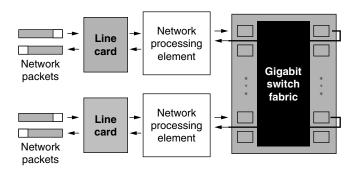

| 34  | Not                  | work Packet Processing in Reconfigurable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                              |

| . 7 |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

| ٠.  |                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 752                                                                                                          |