### Preface

#### Vision

Compiler construction brings together techniques from disparate parts of Computer Science. The compiler deals with many big-picture issues. At its simplest, a compiler is just a computer program that takes as input one potentially executable program and produces as output another, related, potentially executable program. As part of this translation, the compiler must perform syntax analysis to determine if the input program is valid. To map that input program onto the finite resources of a target computer, the compiler must manipulate several distinct name spaces, allocate several different kinds of resources, and synchronize the behavior of different run-time components. For the output program to have reasonable performance, it must manage hardware latencies in functional units, predict the flow of execution and the demand for memory, and reason about the independence and dependence of different machine-level operations in the program.

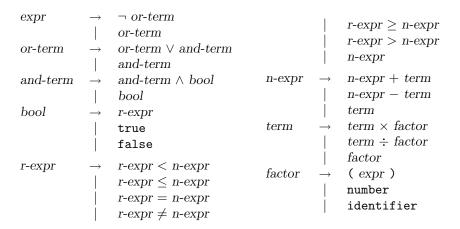

Open up a compiler and you are likely to find greedy heuristic searches that explore large solution spaces, finite automata that recognize words in the input, fixed-point algorithms that help reason about program behavior, simple theorem provers and algebraic simplifiers that try to predict the values of expressions, pattern-matchers for both strings and trees that match abstract computations to machine-level operations, solvers for diophantine equations and Pressburger arithmetic used to analyze array subscripts, and techniques such as hash tables, graph algorithms, and sparse set implementations used in myriad applications,

The lore of compiler construction includes both amazing success stories about the application of theory to practice and humbling stories about the limits of what we can do. On the success side, modern scanners are built by applying the theory of regular languages to automatic construction of recognizers. Lar parsers use the same techniques to perform the handle-recognition that drives a shift-reduce parser. Data-flow analysis (and its cousins) apply lattice theory to the analysis of programs in ways that are both useful and clever. Some of the problems that a compiler faces are truly hard; many clever approximations and heuristics have been developed to attack these problems.

On the other side, we have discovered that some of the problems that compilers must solve are quite hard. For example, the back end of a compiler for a modern superscalar machine must approximate the solution to two or more

interacting NP-complete problems (instruction scheduling, register allocation, and, perhaps, instruction and data placement). These NP-complete problems, however, look easy next to problems such as algebraic reassociation of expressions. This problem admits a huge number of solutions; to make matters worse, the desired solution is somehow a function of the other transformations being applied in the compiler. While the compiler attempts to solve these problems (or approximate their solution), we constrain it to run in a reasonable amount of time and to consume a modest amount of space. Thus, a good compiler for a modern superscalar machine is an artful blend of theory, of practical knowledge, of engineering, and of experience.

This text attempts to convey both the art and the science of compiler construction. We have tried to cover a broad enough selection of material to show the reader that real tradeoffs exist, and that the impact of those choices can be both subtle and far-reaching. We have limited the material to a manageable amount by omitting techniques that have become less interesting due to changes in the marketplace, in the technology of languages and compilers, or in the availability of tools. We have replaced this material with a selection of subjects that have direct and obvious importance today, such as instruction scheduling, global register allocation, implementation object-oriented languages, and some introductory material on analysis and transformation of programs.

#### **Target Audience**

The book is intended for use in a first course on the design and implementation of compilers. Our goal is to lay out the set of problems that face compiler writers and to explore some of the solutions that can be used to solve these problems. The book is not encyclopedic; a reader searching for a treatise on *Earley's algorithm* or *left-corner parsing* may need to look elsewhere. Instead, the book presents a pragmatic selection of practical techniques that you might use to build a modern compiler.

Compiler construction is an exercise in engineering design. The compiler writer must choose a path through a decision space that is filled with diverse alternatives, each with distinct costs, advantages, and complexity. Each decision has an impact on the resulting compiler. The quality of the end product depends on informed decisions at each step of way.

Thus, there is no *right* answer for these problems. Even within "well understood" and "solved" problems, nuances in design and implementation have an impact on both the behavior of the compiler and the quality of the code that it produces. Many considerations play into each decision. As an example, the choice of an intermediate representation (IR) for the compiler has a profound impact on the rest of the compiler, from space and time requirements through the ease with which different algorithms can be applied. The decision, however, is given short shrift in most books (and papers). Chapter 6 examines the space of IRs and some of the issues that should be considered in selecting an IR. We raise the issue again at many points in the book—both directly in the text and indirectly in the questions at the end of each chapter.

This book tries to explore the design space – to present some of the ways problems have been solved and the constraints that made each of those solutions attractive at the time. By understanding the parameters of the problem and their impact on compiler design, we hope to convey both the breadth of possibility and the depth of the problems.

This book departs from some of the accepted conventions for compiler construction textbooks. For example, we use several different programming languages in the examples. It makes little sense to describe call-by-name parameter passing in C, so we use Algol-60. It makes little sense to describe tail-recursion in Fortran, so we use Scheme. This multi-lingual approach is realistic; over the course of the reader's career, the "language of the future" will change several times. (In the past thirty years, Algol-68, APL, PL/I, Smalltalk, C, Modula-3, C++, and even ADA have progressed from being "the language of the future" to being the "language of the future of the past.") Rather than provide ten to twenty homework-level questions at the end of each chapter, we present a couple of questions suitable for a mid-term or final examination. The questions are intended to provoke further thought about issues raised in the chapter. We do not provide solutions, because we anticipate that the best answer to any interesting question will change over the timespan of the reader's career.

#### **Our Focus**

In writing this book, we have made a series of conscious decisions that have a strong impact on both its style and its content. At a high level, our focus is to prune, to relate, and to engineer.

Prune Selection of material is an important issue in the design of a compiler construction course today. The sheer volume of information available has grown dramatically over the past decade or two. David Gries' classic book (Compiler Construction for Digital Computers, John Wiley, 1971) covers code optimization in a single chapter of less than forty pages. In contrast, Steve Muchnick's recent book (Advanced Compiler Design and Implementation, Morgan Kauffman, 1997) devotes thirteen chapters and over five hundred forty pages to the subject, while Bob Morgan's recent book (Building an Optimizing Compiler, Digital Press, 1998) covers the material in thirteen chapters that occupy about four hundred pages.

In laying out *Engineering a Compiler*, we have selectively pruned the material to exclude material that is redundant, that adds little to the student's insight and experience, or that has become less important due to changes in languages, in compilation techniques, or in systems architecture. For example, we have omitted operator precedence parsing, the LL(1) table construction algorithm, various code generation algorithms suitable for the PDP-11, and the UNION-FIND-based algorithm for processing Fortran Equivalence statements. In their place, we have added coverage of topics that include instruction scheduling, global register allocation, implementation of object-oriented languages, string manipulation, and garbage collection.

Relate Compiler construction is a complex, multifaceted discipline. The solutions chosen for one problem affect other parts of the compiler because they shape the input to subsequent phases and the information available in those phases. Current textbooks fail to clearly convey these relationships.

To make students aware of these relationships, we expose some of them directly and explicitly in the context of practical problems that arise in commonly-used languages. We present several alternative solutions to most of the problems that we address, and we discuss the differences between the solutions and their overall impact on compilation. We try to select examples that are small enough to be grasped easily, but large enough to expose the student to the full complexity of each problem. We reuse some of these examples in several chapters to provide continuity and to highlight the fact that several different approaches can be used to solve them.

Finally, to tie the package together, we provide a couple of questions at the end of each chapter. Rather than providing homework-style questions that have algorithmic answers, we ask exam-style questions that try to engage the student in a process of comparing possible approaches, understanding the tradeoffs between them, and using material from several chapters to address the issue at hand. The questions are intended as a tool to make the reader think, rather than acting as a set of possible exercises for a weekly homework assignment. (We believe that, in practice, few compiler construction courses assign weekly homework. Instead, these courses tend to assign laboratory exercises that provide the student with hands-on experience in language implementation.)

Engineer Legendary compilers, such as the BLISS-11 compiler or the Fortran-H compiler, have done several things well, rather than doing everything in moderation. We want to show the design issues that arise at each stage and how different solutions affect the resulting compiler and the code that it generates.

For example, a generation of students studied compilation from books that assume stack allocation of activation records. Several popular languages include features that make stack allocation less attractive; a modern textbook should present the tradeoffs between keeping activation records on the stack, keeping them in the heap, and statically allocating them (when possible).

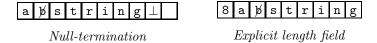

When the most widely used compiler-construction books were written, most computers supported byte-oriented load and store operations. Several of them had hardware support for moving strings of characters from one memory location to another (the <u>move character long</u> instruction – mvcl). This simplified the treatment of character strings, allowing them to be treated as vectors of bytes (sometimes, with an implicit loop around the operation). Thus, compiler books scarcely mentioned support for strings.

Some RISC machines have weakened support for sub-word quantities; the compiler must worry about alignment; it may need to mask a character into a word using boolean operations. The advent of register-to-register load-store machines eliminated instructions like mvcl; today's RISC machine expects the compiler to optimize such operations and work together with the operating system to perform them efficiently.

#### Trademark Notices

In the text, we have used the registered trademarks of several companies.

IBM is a trademark of International Business Machines, Incorporated.

Intel and IA-64 are trademarks of Intel Corporation.

**370** is a trademark of International Business Machines, Incorporated.

MC68000 is a trademark of Motorola, Incorporated.

PostScript is a registered trademark of Adobe Systems.

PowerPC is a trademark of (?Motorola or IBM?)

**PDP-11** is a registered trademark of Digital Equipment Corporation, now a part of Compaq Computer.

Unix is a registered trademark of someone or other (maybe Novell).

$\mathbf{VAX}$  is a registered trademark of Digital Equipment Corporation, now a part of Compaq Computer.

**Java** may or may not be a registered trademark of SUN Microsystems, Incorporated.

## ${m Acknowledgements}$

We particularly thank the following people who provided us with direct and useful feedback on the form, content, and exposition of this book: Preston Briggs, Timothy Harvey, L. Taylor Simpson, Dan Wallach.

## Contents

| 1 | $\mathbf{A}\mathbf{n}$ | Overview of Compilation                       |  |  |  |  |  |

|---|------------------------|-----------------------------------------------|--|--|--|--|--|

|   | 1.1                    | Introduction                                  |  |  |  |  |  |

|   | 1.2                    | Principles and Desires                        |  |  |  |  |  |

|   | 1.3                    | High-level View of Translation                |  |  |  |  |  |

|   | 1.4                    | Compiler Structure                            |  |  |  |  |  |

|   | 1.5                    | Summary and Perspective                       |  |  |  |  |  |

| 2 | Lex                    | Lexical Analysis 19                           |  |  |  |  |  |

|   | 2.1                    | Introduction                                  |  |  |  |  |  |

|   | 2.2                    | Specifying Lexical Patterns                   |  |  |  |  |  |

|   | 2.3                    | Closure Properties of REs                     |  |  |  |  |  |

|   | 2.4                    | Regular Expressions and Finite Automata       |  |  |  |  |  |

|   | 2.5                    | Implementing a DFA                            |  |  |  |  |  |

|   | 2.6                    | Non-deterministic Finite Automata             |  |  |  |  |  |

|   | 2.7                    | From Regular Expression to Scanner            |  |  |  |  |  |

|   | 2.8                    | Better Implementations                        |  |  |  |  |  |

|   | 2.9                    | Related Results                               |  |  |  |  |  |

|   | 2.10                   | Lexical Follies of Real Programming languages |  |  |  |  |  |

|   |                        | Summary and Perspective                       |  |  |  |  |  |

| 3 | Par                    | Parsing 53                                    |  |  |  |  |  |

|   | 3.1                    | Introduction                                  |  |  |  |  |  |

|   | 3.2                    | Expressing Syntax                             |  |  |  |  |  |

|   | 3.3                    | Top-Down Parsing                              |  |  |  |  |  |

|   | 3.4                    | Bottom-up Parsing                             |  |  |  |  |  |

|   | 3.5                    | Building an LR(1) parser                      |  |  |  |  |  |

|   | 3.6                    | Practical Issues                              |  |  |  |  |  |

|   | 3.7                    | Summary and Perspective                       |  |  |  |  |  |

| 4 | Con                    | text-Sensitive Analysis 105                   |  |  |  |  |  |

|   | 4.1                    | Introduction                                  |  |  |  |  |  |

|   | 4.2                    | The Problem                                   |  |  |  |  |  |

|   | 4.3                    | Attribute Grammars                            |  |  |  |  |  |

|   | 1.1                    | Ad hoe Syntax directed Translation 116        |  |  |  |  |  |

xii CONTENTS

|   | 4.5  | What Questions Should the Compiler Ask?    |

|---|------|--------------------------------------------|

|   | 4.6  | Summary and Perspective                    |

| 5 | Тур  | pe Checking 133                            |

| 6 | Inte | ermediate Representations 133              |

|   | 6.1  | Introduction                               |

|   | 6.2  | Taxonomy                                   |

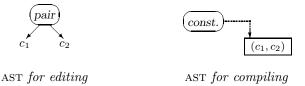

|   | 6.3  | Graphical IRs                              |

|   | 6.4  | Linear IRs                                 |

|   | 6.5  | Mapping Values to Names                    |

|   | 6.6  | Universal Intermediate Forms               |

|   | 6.7  | Symbol Tables                              |

|   | 6.8  | Summary and Perspective                    |

| 7 | The  | e Procedure Abstraction 165                |

|   | 7.1  | Introduction                               |

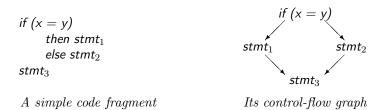

|   | 7.2  | Control Abstraction                        |

|   | 7.3  | Name Spaces                                |

|   | 7.4  | Communicating Values Between Procedures    |

|   | 7.5  | Establishing Addressability                |

|   | 7.6  | Standardized Linkages                      |

|   | 7.7  | Managing Memory                            |

|   | 7.8  | Object-oriented Languages                  |

|   | 7.9  | Summary and Perspective                    |

| 8 | Coc  | le Shape 203                               |

|   | 8.1  | Introduction                               |

|   | 8.2  | Assigning Storage Locations                |

|   | 8.3  | Arithmetic Expressions                     |

|   | 8.4  | Boolean and Relational Values              |

|   | 8.5  | Storing and Accessing Arrays               |

|   | 8.6  | Character Strings                          |

|   | 8.7  | Structure References                       |

|   | 8.8  | Control Flow Constructs                    |

|   | 8.9  | Procedure Calls                            |

|   | 8.10 | Implementing Object-Oriented Languages 249 |

| 9 | Inst | cruction Selection 251                     |

|   | 9.1  | Tree Walk Schemes                          |

|   | 9.2  | Aho & Johnson Dynamic Programming          |

|   | 9.3  | Tree Pattern Matching                      |

|   | 9.4  | Peephole-Style Matching                    |

|   | 9.5  | Bottom-up Rewrite Systems                  |

|   | 9.6  | Attribute Grammars, Revisited              |

| COMMENIA  | •••   |

|-----------|-------|

| CONTENTS  | X111  |

| 001112112 | 11111 |

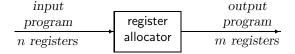

| 10 Register Allocation                         |   | 253   |

|------------------------------------------------|---|-------|

| 10.1 The Problem                               |   | . 253 |

| 10.2 Local Register Allocation and Assignment  |   | . 258 |

| 10.3 Moving beyond single blocks               |   |       |

| 10.4 Global Register Allocation and Assignment |   |       |

| 10.5 Regional Register Allocation              |   |       |

| 10.6 Harder Problems                           |   |       |

| 10.7 Summary and Perspective                   |   |       |

| 10.7 Summary and rerspective                   | • | . 204 |

| 11 Instruction Scheduling                      |   | 289   |

| 11.1 Introduction                              |   |       |

| 11.2 The Instruction Scheduling Problem        |   |       |

| ŭ                                              |   |       |

| 11.3 Local List Scheduling                     |   |       |

| 11.4 Regional Scheduling                       |   |       |

| 11.5 More Aggressive Techniques                |   |       |

| 11.6 Summary and Perspective                   |   | . 315 |

| 10 T + -1 - 4' - + - C   1 - O + 4' + -4'      |   | 015   |

| 12 Introduction to Code Optimization           |   | 317   |

| 12.1 Introduction                              |   |       |

| 12.2 Redundant Expressions                     |   |       |

| 12.3 Background                                |   |       |

| 12.4 Value Numbering over Larger Scopes        |   |       |

| 12.5 Lessons from Value Numbering              |   |       |

| 12.6 Summary and Perspective                   |   | . 323 |

| 12.7 Questions                                 |   | . 323 |

| 12.8 Chapter Notes                             |   | . 323 |

|                                                |   |       |

| 13 Analysis                                    |   | 325   |

| 13.1 Data-flow Analysis                        |   | . 325 |

| 13.2 Building Static Single Assignment Form    |   |       |

| 13.3 Dependence Analysis for Arrays            |   | . 325 |

| 13.4 Analyzing Larger Scopes                   |   | . 326 |

|                                                |   |       |

| 14 Transformation                              |   | 329   |

| 14.1 Example Scalar Optimizations              |   |       |

| 14.2 Optimizing Larger Scopes                  |   | . 329 |

| 14.3 Run-time Optimization                     |   | . 331 |

| 14.4 Multiprocessor Parallelism                |   | . 331 |

| 14.5 Chapter Notes                             |   | . 332 |

|                                                |   |       |

| 15 Post-pass Improvement Techniques            |   | 333   |

| 15.1 The Idea                                  |   |       |

| 15.2 Peephole Optimization                     |   | . 333 |

| 15.3 Post-pass Dead Code Elimination           |   | . 333 |

| 15.4 Improving Resource Utilization            |   |       |

| 15.5 Interprocedural Optimization              |   |       |

| xiv | CONTENTS |

|-----|----------|

|     |          |

| $\mathbf{A}$ | ILOC                                                                                                                                                              | 335                 |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

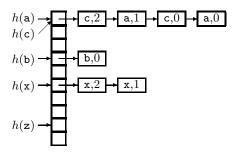

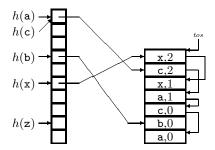

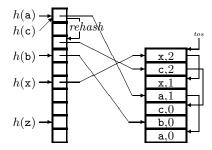

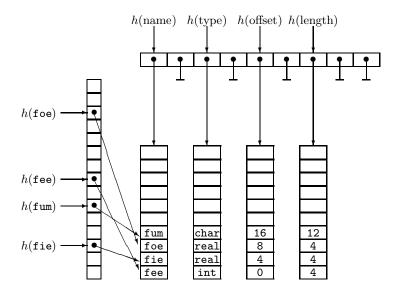

| В            | Data StructuresB.1 IntroductionB.2 Representing SetsB.3 Implementing Intermediate FormsB.4 Implementing Hash-tablesB.5 Symbol Tables for Development Environments | $341 \\ 341 \\ 341$ |

| $\mathbf{C}$ | Abbreviations, Acronyms, and Glossary                                                                                                                             | 353                 |

| D            | Missing Labels                                                                                                                                                    | 357                 |

## Chapter 1

# $oldsymbol{An}$ Overview of Compilation

#### 1.1 Introduction

The role of computers in daily life is growing each year. Modern microprocessors are found in cars, microwave ovens, dishwashers, mobile telephones, GPSS navigation systems, video games and personal computers. Each of these devices must be programmed to perform its job. Those programs are written in some "programming" language – a formal language with mathematical properties and well-defined meanings – rather than a natural language with evolved properties and many ambiguities. Programming languages are designed for expressiveness, conciseness, and clarity. A program written in a programming language must be translated before it can execute directly on a computer; this translation is accomplished by a software system called a *compiler*. This book describes the mechanisms used to perform this translation and the issues that arise in the design and construction of such a translator.

A compiler is just a computer program that takes as input an executable program and produces as output an equivalent executable program.

In a traditional compiler, the input language is a programming language and the output language is either assembly code or machine code for some computer system. However, many other systems qualify as compilers. For example, a typesetting program that produces PostScript can be considered a compiler. It takes as input a specification for how the document should look on the printed page and it produces as output a PostScript file. PostScript is simply a language for describing images. Since the typesetting program takes an executable specification and produces another executable specification, it is a compiler.

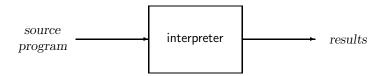

The code that turns PostScript into pixels is typically an interpreter, not a compiler. An interpreter takes as input an executable specification and produces as output the results of executing the specification.

Interpreters and compilers have much in common. From an implementation perspective, interpreters and compilers perform many of the same tasks. For example, both must analyze the source code for errors in either syntax or meaning. However, interpreting the code to produce a result is quite different from emitting a translated program that can be executed to produce the results. This book focuses on the problems that arise in building compilers. However, an implementor of interpreters may find much of the material relevant.

The remainder of this chapter presents a high-level overview of the translation process. It addresses both the problems of translation—what issues must be decided along the way—and the structure of a modern compiler—where in the process each decision should occur. Section 1.2 lays out two fundamental principles that every compiler must follow, as well as several other properties that might be desirable in a compiler. Section 1.3 examines the tasks that are involved in translating code from a programming language to code for a target machine. Section 1.4 describes how compilers are typically organized to carry out the tasks of translation.

#### 1.2 Principles and Desires

Compilers are engineered objects—software systems built with distinct goals in mind. In building a compiler, the compiler writer makes myriad design decisions. Each decision has an impact on the resulting compiler. While many issues in compiler design are amenable to several different solutions, there are two principles that should not be compromised. The first principle that a well-designed compiler must observe is inviolable.

The compiler must preserve the meaning of the program being compiled

The code produced by the compiler must faithfully implement the "meaning" of the source-code program being compiled. If the compiler can take liberties with meaning, then it can always generate the same code, independent of input. For example, the compiler could simply emit a nop or a return instruction.

The second principle that a well-designed compiler must observe is quite practical.

The compiler must improve the source code in some discernible way.

If the compiler does not improve the code in some way, why should anyone invoke it? A traditional compiler improves the code by making it directly executable on some target machine. Other "compilers" improve their input in different ways. For example, tpic is a program that takes the specification for a drawing written in the graphics language pic, and converts it into LATEX; the "improvement" lies in LATEX's greater availability and generality. Some compilers produce output programs in the same language as their input; we call these "source-to-source" translators. In general, these systems try to restate the program in a way that will lead, eventually, to an improvement.

These are the two fundamental principles of compiler design.

This is an exciting era in the design and implementation of compilers. In the 1980's almost all compilers were large, monolithic systems. They took as input one of a handful of languages—typically Fortran or C—and produced assembly code for some particular computer. The assembly code was pasted together with the code produced by other compiles—including system libraries and application libraries—to form an executable. The executable was stored on a disk; at the appropriate time, the final code was moved from disk to main memory and executed.

Today, compiler technology is being applied in many different settings. These diverse compilation and execution environments are challenging the traditional image of a monolithic compiler and forcing implementors to reconsider many of the design tradeoffs that seemed already settled.

- Java has reignited interest in techniques like "just-in-time" compilation and "throw-away code generation." Java applets are transmitted across the Internet in some internal form, called Java bytecodes; the bytecodes are then interpreted or compiled, loaded, and executed on the target machine. The performance of the tool that uses the applet depends on the total time required to go from bytecodes on a remote disk to a completed execution on the local machine.

- Many techniques developed for large, monolithic compilers are being applied to analyze and improve code at link-time. In these systems, the compiler takes advantage of the fact that the <a href="entire program">entire program</a> is available at link-time. The "link-time optimizer" analyzes the assembly code to derive knowledge about the run-time behavior of the program and uses that knowledge to produce code that runs faster.

- Some compilation techniques are being delayed even further—to run-time. Several recent systems invoke compilers during program execution to generate customized code that capitalizes on facts that cannot be known any

earlier. If the compile time can be kept small and the benefits are large, this strategy can produce noticeable improvements.

In each of these settings, the constraints on time and space differ, as do the expectations with regard to code quality.

The priorities and constraints of a specific project may dictate specific solutions to many design decisions or radically narrow the set of feasible choices. Some of the issues that may arise are:

- 1. Speed: At any point in time, there seem to be applications that need more performance than they can easily obtain. For example, our ability to simulate the behavior of digital circuits, like microprocessors, always lags far behind the demand for such simulation. Similarly, large physical problems such as climate modeling have an insatiable demand for computation. For these applications, the runtime performance of the compiled code is a critical issue. Achieving predictably good performance requires additional analysis and transformation at compile-time, typically resulting in longer compile times.

- 2. Space: Many applications impose tight restrictions on the size of compiled code. Usually, the constraints arise from either physical or economic factors; for example, power consumption can be a critical issue for any battery-powered device. Embedded systems outnumber general purpose computers; many of these execute code that has been committed permanently to a small "read-only memory" (ROM). Executables that must be transmitted between computers also place a premium on the size of compiled code. This includes many Internet applications, where the link between computers is slow relative to the speed of computers on either end.

- 3. Feedback: When the compiler encounters an incorrect program, it must report that fact back to the user. The amount of information provided to the user can vary widely. For example, the early Unix compilers often produced a simple and uniform message "syntax error." At the other end of the spectrum the Cornell PL/C system, which was designed as a "student" compiler, made a concerted effort to correct every incorrect program and execute it [23].

- 4. Debugging: Some transformations that the compiler might use to speed up compiled code can obscure the relationship between the source code and the target code. If the debugger tries to relate the state of the broken executable back to the source code, the complexities introduced by radical program transformations can cause the debugger to mislead the programmer. Thus, both the compiler writer and the user may be forced to choose between efficiency in the compiled code and transparency in the debugger. This is why so many compilers have a "debug" flag that causes the compiler to generate somewhat slower code that interacts more cleanly with the debugger.

5. Compile-time efficiency: Compilers are invoked frequently. Since the user usually waits for the results, compilation speed can be an important issue. In practice, no one likes to wait for the compiler to finish. Some users will be more tolerant of slow compiles, especially when code quality is a serious issue. However, given the choice between a slow compiler and a fast compiler that produces the same results, the user will undoubtedly choose the faster one.

Before reading the rest of this book, you should write down a prioritized list of the qualities that you want in a compiler. You might apply the ancient standard from software engineering—evaluate features as if you were paying for them with your own money! Examining your list will tell you a great deal about how you would make the various tradeoffs in building your own compiler.

#### 1.3 High-level View of Translation

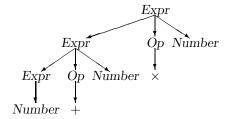

To gain a better understanding of the tasks that arise in compilation, consider what must be done to generate executable code for the following expression:

$$w \leftarrow w \times 2 \times x \times y \times z$$

.

Let's follow the expression through compilation to discover what facts must be discovered and what questions must be answered.

#### 1.3.1 Understanding the Input Program

The first step in compiling our expression is to determine whether or not

$$w \leftarrow w \times 2 \times x \times y \times z$$

.

is a legal sentence in the programming language. While it might be amusing to feed random words to an English to Italian translation system, the results are unlikely to have meaning. A compiler must determine whether or not its input constitutes a well-constructed sentence in the source language. If the input is well-formed, the compiler can continue with translation, optimization, and code generation. If it is not, the compiler should report back to the user with a clear error message that isolates, to the extent possible, the problem with the sentence.

Syntax In a compiler, this task is called syntax analysis. To perform syntax analysis efficiently, the compiler needs:

- 1. a formal definition of the source language,

- 2. an efficient membership test for the source language, and

- 3. a plan for how to handle illegal inputs.

Mathematically, the source language is a set, usually infinite, of strings defined by some finite set of rules. The compiler's front end must determine whether the source program presented for compilation is, in fact, an element in that set of valid strings. In engineering a compiler, we would like to answer this membership question efficiently. If the input program is not in the set, and therefore not in the language, the compiler should provide useful and detailed feedback that explains where the input deviates from the rules.

To keep the set of rules that define a language small, the rules typically refer to words by their syntactic categories, or parts-of-speech, rather than individual words. In describing English, for example, this abstraction allows us to state that many sentences have the form

```

sentence → subject verb object period

```

rather than trying to enumerate the set of all sentences. For example, we use a syntactic variable, verb, to represent all possible verbs. With English, the reader generally recognizes many thousand words and knows the possible parts-of-speech that each can fulfill. For an unfamiliar string, the reader consults a dictionary. Thus, the syntactic structure of the language is based on a set of rules, or a grammar, and a system for grouping characters together to form words and for classifying those words into their syntactic categories.

This description-based approach to specifying a language is critical to compilation. We cannot build a software system that contains an infinite set of rules, or an infinite set of sentences. Instead, we need a finite set of rules that can generate (or specify) the sentences in our language. As we will see in the next two chapters, the finite nature of the specification does not limit the expressiveness of the language.

To understand whether the sentence "Compilers are engineered objects." is, in fact, a valid English sentence, we first establish that each word is valid. Next, each word is replaced by its syntactic category to create a somewhat more abstract representation of the sentence—

#### noun verb adjective noun period

Finally, we try to fit this sequence of abstracted words into the rules for an English sentence. A working knowledge of English grammar might include the following rules:

```

subject verb object

1

sentence

2

subject

noun

3

subject

modifier noun

object

4

noun

object

modifier noun

5

modifier

adjective

modifier

adjectival phrase

```

. . .

Here, the symbol  $\rightarrow$  reads "derives" and means that an instance of the right hand side can be abstracted to the left hand side. By inspection, we can discover the following *derivation* for our example sentence.

| F | Rule | Prototype Sentence              |  |

|---|------|---------------------------------|--|

|   | _    | sentence                        |  |

|   | 1    | subject verb object period      |  |

|   | 2    | noun verb object period         |  |

|   | 5    | noun verb modifier noun period  |  |

|   | 6    | noun verb adjective noun period |  |

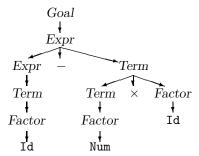

At this point, the prototype sentence generated by the derivation matches the abstract representation of our input sentence. Because they match, at this level of abstraction, we can conclude that the input sentence is a member of the language described by the grammar. This process of discovering a valid derivation for some stream of tokens is called parsing.

If the input is not a valid sentence, the compiler must report the error back to the user. Some compilers have gone beyond diagnosing errors; they have attempted to correct errors. When an error-correcting compiler encounters an invalid program, it tries to discover a "nearby" program that is well-formed. The classic game to play with an error-correcting compiler is to feed it a program written in some language it does not understand. If the compiler is thorough, it will faithfully convert the input into a syntactically correct program and produce executable code for it. Of course, the results of such an automatic (and unintended) transliteration are almost certainly meaningless.

Meaning A critical observation is that syntactic correctness depended entirely on the parts of speech, not the words themselves. The grammatical rules are oblivious to the difference between the noun "compiler" and the noun "tomatoes". Thus, the sentence "Tomatoes are engineered objects." is grammatically indistinguishable from "Compilers are engineered objects.", even though they have significantly different meanings. To understand the difference between these two sentences requires contextual knowledge about both compilers and vegetables.

Before translation can proceed, the compiler must determine that the program has a well-defined meaning. Syntax analysis can determine that the sentences are well-formed, at the level of checking parts of speech against grammatical rules. Correctness and meaning, however, go deeper than that. For example, the compiler must ensure that names are used in a fashion consistent with their declarations; this requires looking at the words themselves, not just at their syntactic categories. This analysis of meaning is often called either semantic analysis or context-sensitive analysis. We prefer the latter term, because it emphasizes the notion that the correctness of some part of the input, at the level of meaning, depends on the context that both precedes it and follows it.

A well-formed computer program specifies some computation that is to be performed when the program executes. There are many ways in which the expression

$$w \leftarrow w \times 2 \times x \times y \times z$$

might be ill-formed, beyond the obvious, syntactic ones. For example, one or more of the names might not be defined. The variable  $\mathbf{x}$  might not have a value when the expression executes. The variables  $\mathbf{y}$  and  $\mathbf{z}$  might be of different types that cannot be multiplied together. Before the compiler can translate the expression, it must also ensure that the program has a well-defined meaning, in the sense that it follows some set of additional, extra-grammatical rules.

Compiler Organization The compiler's front end performs the analysis to check for syntax and meaning. For the restricted grammars used in programming languages, the process of constructing a valid derivation is easily automated. For efficiency's sake, the compiler usually divides this task into lexical analysis, or scanning, and syntax analysis, or parsing. The equivalent skill for "natural" languages is sometimes taught in elementary school. Many English grammar books teach a technique called "diagramming" a sentence—drawing a pictorial representation of the sentence's grammatical structure. The compiler accomplishes this by applying results from the study of formal languages [1]; the problems are tractable because the grammatical structure of programming languages is usually more regular and more constrained than that of a natural language like English or Japanese.

Inferring meaning is more difficult. For example, are w, x, y, and z declared as variables and have they all been assigned values previously? Answering these questions requires deeper knowledge of both the surrounding context and the source language's definition. A compiler needs an efficient mechanism for determining if its inputs have a legal meaning. The techniques that have been used to accomplish this task range from high-level, rule-based systems through ad hoc code that checks specific conditions.

Chapters 2 through 5 describe the algorithms and techniques that a compiler's front end uses to analyze the input program and determine whether it is well-formed, and to construct a representation of the code in some internal form. Chapter 6 and Appendix B, explore the issues that arise in designing and implementing the internal structures used throughout the compiler. The front end builds many of these structures.

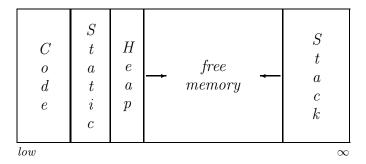

#### 1.3.2 Creating and Maintaining the Runtime Environment

Our continuing example concisely illustrates how programming languages provides their users with abstractions that simplify programming. The language defines a set of facilities for expressing computations; the programmer writes code that fits a model of computation implicit in the language definition. (Implementations of QuickSort in scheme, Java, and Fortran would, undoubtedly, look quite different.) These abstractions insulate the programmer from low-level details of the computer systems they use. One key role of a compiler is to put in place mechanisms that efficiently create and maintain these illusions. For example, assembly code is a convenient fiction that allows human beings to read and write short mnemonic strings rather than numerical codes for operations;

somehow this is more intuitive to most assembly programmers. This particular illusion—that the computer understands alphabetic names rather than binary numbers—is easily maintained by a lookup-table in a symbolic assembler.

The example expression showcases one particular abstraction that the compiler maintains, symbolic names. The example refers to values with the names  $\mathbf{w}$ ,  $\mathbf{x}$ ,  $\mathbf{y}$ , and  $\mathbf{z}$ . These names are not just values; a given name can take on multiple values as the program executes. For example,  $\mathbf{w}$  is used on both the right-hand side and the left-hand side of the assignment. Clearly,  $\mathbf{w}$  has one value before execution of the expression and another afterwards (unless  $\mathbf{x} \times \mathbf{y} \times \mathbf{z} \cong \frac{1}{2}$ ). Thus,  $\mathbf{w}$  refers to whatever value is stored in some named location, rather than a specific value, such as 15.

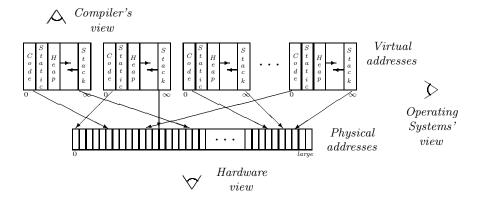

The memories of modern computers are organized by numerical addresses, not textual names. Within the address space of an executing program, these addresses correspond uniquely to storage locations. In a source-level program, however, the programmer may create many distinct variables that use the same name. For example, many programs define the variables i, j, and k in several different procedures; they are common names for loop index variables. The compiler has responsibility for mapping each use of the name j to the appropriate instance of j and, from there, into the storage location set aside for that instance of j. Computers do not have this kind of name space for storage locations; it is an abstraction created by the language designer and maintained by the compiler-generated code and its run-time environment.

To translate  $w \leftarrow w \times 2 \times x \times y \times z$ , the compiler must assign some storage location to each name. (We will assume, for the moment, that the constant two needs no memory location since it is a small integer and can probably be obtained using a *load immediate* instruction.) This might be done in memory, as in

$$0$$

$\mathbf{w}$   $\mathbf{x}$   $\mathbf{y}$   $\mathbf{z}$

or, the compiler might elect to keep the named variables in machine registers with a series of assignments:

$$r_1 \leftarrow w$$

;  $r_2 \leftarrow x$ ;  $r_3 \leftarrow y$ ; and  $r_4 \leftarrow z$ ;

The compiler must choose, based on knowledge of the surrounding context, a location for each named value. Keeping  $\mathbf{w}$  in a register will likely lead to faster execution; if some other statement assigns  $\mathbf{w}$ 's address to a pointer, the compiler would need to assign  $\mathbf{w}$  to an actual storage location.

Names are just one abstraction maintained by the compiler. To handle a complete programming language, the compiler must create and support a variety of abstractions, Procedures, parameters, names, lexical scopes, and control-flow operations are all abstractions designed into the source language that the compiler creates and maintains on the target machine (with some help from the other system software). Part of this task involves the compiler emitting the appropriate instructions at compile time; the remainder involves interactions between that compiled code and the run-time environment that supports it.

```

\Rightarrow r<sub>w</sub>

loadAI

\mathtt{r}_{arp}, \mathtt{@w}

// load 'w'

// constant 2 into r_2

loadI

\Rightarrow r_2

loadAI

r_{arp}, load 'x'

loadAI

r_{arp}, load 'y'

r_{arp}, load 'z'

loadAI

// r_w \leftarrow w \times 2

mult

r_w, r_2

\Rightarrow r_w

// r_w \leftarrow (w \times 2) \times x

mult

\mathbf{r}_w, \mathbf{r}_x

\Rightarrow r<sub>w</sub>

mult

\mathbf{r}_w, \mathbf{r}_y

\Rightarrow r<sub>w</sub>

// r_w \leftarrow (w \times 2 \times x) \times y

mult

\Rightarrow r_w

// r_w \leftarrow (w \times 2 \times x \times y) \times z

\mathbf{r}_w, \mathbf{r}_z

\Rightarrow r<sub>arp</sub>, 0 // write r<sub>w</sub> back to 'w'

storeAI

\mathbf{r}_w

```

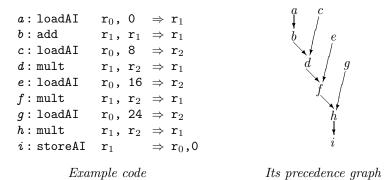

Figure 1.1: Example in ILOC

Thus, designing and implementing a compiler involves not only translation from some source language to a target language, but also the construction of a set of mechanisms that will create and maintain the necessary abstractions at run-time. These mechanisms must deal with the layout and allocation of memory, with the orderly transfer of control between procedures, with the transmission of values and the mapping of name spaces at procedure borders, and with interfaces to the world outside the compiler's control, including input and output devices, the operating system, and other running programs.

Chapter 7 explores the abstractions that the compiler must maintain to bridge the gap between the programming model embodied in the source language and the facilities provided by the operating system and the actual hardware. It describes algorithms and techniques that the compilers use to implement the various fictions contained in the language definitions. It explores some of the issues that arise on the boundary between the compiler's realm and that of the operating system.

#### 1.3.3 Creating the Output Program

So far, all of the issues that we have addressed also arise in interpreters. The difference between a compiler and an interpreter is that the compiler emits executable code as its output, while the interpreter produces the result of executing that code. During code generation, the compiler traverses the internal data structures that represent the code and it emits equivalent code for the target machine. It must select instructions to implement each operation that appears in the code being compiled, decide when and where to move values between registers and memory, and choose an execution order for the instructions that both preserves meaning and avoids unnecessary hardware stalls or interlocks. (In contrast, an interpreter would traverse the internal data structures and simulate the execution of the code.)

Instruction Selection As part of code generation, the compiler must select a sequence of machine instructions to implement the operations expressed in the code being compiled. The compiler might choose the instructions shown in

#### Digression: About ILOC

Throughout the book, low-level examples are written in an notation that we call ILOC—an acronym that William LeFebvre derived from "intermediate language for an optimizing compiler." Over the years, this notation has undergone many changes. The version used in this book is described in detail in Appendix A.

Think of ILOC as the assembly language for a simple RISC machine. It has a standard complement of operations Most operations take arguments that are registers. The memory operations, loads and stores, transfer values between memory and the registers. To simplify the exposition in the text, most examples assume that all data is integer data.

Each operation has a set of operands and a target. The operation is written in five parts: an operation name, a list of operands, a separator, a list of targets, and an optional comment. Thus, to add registers 1 and 2, leaving the result in register 3, the programmer would write

add

$$r_1, r_2 \Rightarrow r_3$$

// example instruction

The separator,  $\Rightarrow$ , precedes the target list. It is a visual reminder that information flows from left to right. In particular, it disambiguates cases like load and store, where a person reading the assembly-level text can easily confuse operands and targets.

Figure 1.1 to implement

$$w \leftarrow w \times 2 \times x \times y \times z$$

on the ILOC virtual machine. Here, we have assumed the memory layout shown earlier, where w appears at memory address zero.

This sequence is straight forward. It loads all of the relevant values into registers, performs the multiplications in order, and stores the result back to the memory location for w. Notice that the registers have unusual names, like  $\mathbf{r}_w$  to hold w and  $\mathbf{r}_{arp}$  to hold the address where the data storage for our named values begins. Even with this simple sequence, however, the compiler makes choices that affect the performance of the resulting code. For example, if an immediate multiply is available, the instruction mult  $\mathbf{r}_w$ ,  $\mathbf{r}_2 \Rightarrow \mathbf{r}_w$  could be replaced with multI  $\mathbf{r}_w$ ,  $\mathbf{2} \Rightarrow \mathbf{r}_w$ , eliminating the need for the instruction loadI  $\mathbf{2} \Rightarrow \mathbf{r}_2$  and decreasing the number of registers needed. If multiplication is slower than addition, the instruction could be replaced with add  $\mathbf{r}_w$ ,  $\mathbf{r}_w \Rightarrow \mathbf{r}_w$ , avoiding the loadI and its use of  $\mathbf{r}_2$  as well as replacing the mult with a faster add instruction.

Register Allocation In picking instructions, we ignored the fact that the target machine has a finite set of registers. Instead, we assumed that "enough" registers existed. In practice, those registers may or may not be available; it depends on how the compiler has treated the surrounding context.

In register allocation, the compiler decides which values should reside in the registers of the target machine, at each point in the code. It then modifies the code to reflect its decisions. If, for example, the compiler tried to minimize the number of registers used in evaluating our example expression, it might generate the following code

```

{\tt r}_{arp}, {\tt @w}

// load 'w'

loadAI

\Rightarrow r_1

// r_1 \leftarrow w \times 2

add

r_1, r_1

\Rightarrow r_1

// load 'x'

loadAI

r_{arp}, @x \Rightarrow r_2

// r_1 \leftarrow (w \times 2) \times x

mult

r_1, r_2

\Rightarrow r_1

// load 'y'

loadAI

r_{arp}, @y

\Rightarrow r_2

mult

\Rightarrow r_1

// r_1 \leftarrow (w \times 2 \times x) \times y

\mathbf{r}_1, \mathbf{r}_2

r_{arp}, @z \Rightarrow r_2

// load 'z'

loadAI

// r_1 \leftarrow (w \times 2 \times x \times y) \times z

\Rightarrow \mathbf{r}_1

mult

r_1, r_2

\Rightarrow r<sub>arp</sub>, @w // write r<sub>w</sub> back to 'w'

storeAI

```

This sequence uses two registers, plus  $\mathbf{r}_{arp}$ , instead of five.

Minimizing register use may be counter productive. If, for example, any of the named values,  $\mathbf{w}$ ,  $\mathbf{x}$ ,  $\mathbf{y}$ , or  $\mathbf{z}$ , are already in registers, the code should reference those registers directly. If all are in registers, the sequence could be implemented so that it required no additional registers. Alternatively, if some nearby expression also computed  $\mathbf{w} \times \mathbf{2}$ , it might be better to preserve that value in a register than to recompute it later. This would increase demand for registers, but eliminate a later instruction.

In general, the problem of allocating values to registers is NP-Complete. Thus, we should not expect the compiler to discover optimal solutions to the problem, unless we allow exponential time for some compilations. In practice, compilers use approximation techniques to discover good solutions to this problem; the solutions may not be optimal, but the approximation techniques ensure that some solution is found in a reasonable amount of time.

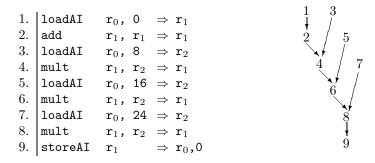

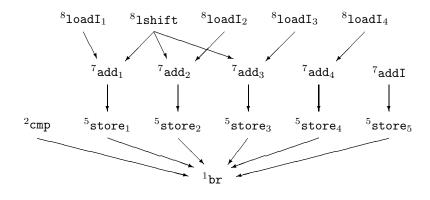

Instruction Scheduling In generating code for a target machine, the compiler should be aware of that machine's specific performance constraints. For example, we mentioned that an addition might be faster than a multiplication; in general, the execution time of the different instructions can vary widely. Memory access instructions (loads and stores) can take many cycles, while some arithmetic instructions, particularly mult, take several. The impact of these longer latency instructions on the performance of compiled code is dramatic.

Assume, for the moment, that a load or store instruction requires three cycles, a mult requires two cycles, and all other instructions require one cycle. With these latencies, the code fragment that minimized register use does not look so attractive. The *Start* column shows the cycle in which the instruction begins execution and the *End* column shows the cycle in which it completes.

| Start | End |                                                                           |                                                             |

|-------|-----|---------------------------------------------------------------------------|-------------------------------------------------------------|

| 1     | 3   | loadAI r $_{arp}$ , @w $\Rightarrow$ r $_{1}$                             | // load 'w'                                                 |

| 4     | 4   | add $r_1, r_1 \Rightarrow r_1$                                            | $// r_1 \leftarrow w \times 2$                              |

| 5     | 7   | loadAI r $_{arp}$ , @x $\Rightarrow$ r $_{2}$                             | // load 'x'                                                 |

| 8     |     | $\texttt{mult}  \texttt{r}_1, \ \texttt{r}_2  \Rightarrow \ \texttt{r}_1$ | $// r_1 \leftarrow (w \times 2) \times x$                   |

| 10    | 12  | loadAI r $_{arp}$ , @y $\Rightarrow$ r $_{2}$                             | // load 'y'                                                 |

| 13    | 14  | $\texttt{mult}  \texttt{r}_1, \ \texttt{r}_2  \Rightarrow \ \texttt{r}_1$ | $// r_1 \leftarrow (w \times 2 \times x) \times y$          |

| 15    | 17  | loadAI r $_{arp}$ , @z $\Rightarrow$ r $_{2}$                             | // load 'z'                                                 |

| 18    | 19  | $\texttt{mult}  \texttt{r}_1, \ \texttt{r}_2  \Rightarrow \ \texttt{r}_1$ | $// r_1 \leftarrow (w \times 2 \times x \times y) \times z$ |

| 20    | 22  | $oxed{storeAIr_1} \qquad \Rightarrow  r_{arp} ,  \mathtt{@w}$             | // write ${	t r}_w$ back to 'w'                             |

This nine instruction sequence takes twenty-two cycles to execute.

Many modern processors have the property that they can initiate new instructions while a long-latency instruction executes. As long as the results of a long-latency instruction are not referenced until the instruction completes, execution proceeds normally. If, however, some intervening instruction tries to read the result of the long-latency instruction prematurely, the processor "stalls", or waits until the long-latency instruction completes. Registers are read in the cycle when the instruction starts and written when it ends.

In instruction scheduling, the compiler reorders the instructions in an attempt to minimize the number cycles wasted in stalls. Of course, the scheduler must ensure that the new sequence produces the same result as the original. In many cases, the scheduler can drastically improve on the performance of "naive" code. For our example, a good scheduler might produce

| Start | End |                                                                                      |                                                             |

|-------|-----|--------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 1     | 3   | loadAI r $_{arp}$ , @w $\Rightarrow$ r $_{1}$                                        | // load 'w'                                                 |

| 2     | 4   | loadAI r $_{arp}$ , $\mathtt{0x} \Rightarrow \mathtt{r}_2$                           | // load 'x'                                                 |

| 3     | 5   | loadAI r $_{arp}$ , @y $\Rightarrow$ r $_{3}$                                        | // load 'y'                                                 |

| 4     | 4   | add $r_1$ , $r_1 \Rightarrow r_1$                                                    | $//$ r $_1$ $\leftarrow$ w $	imes$ 2                        |

| 5     | 6   | $\texttt{mult}  \texttt{r}_1 \texttt{, } \texttt{r}_2  \Rightarrow \texttt{r}_1$     | $// r_1 \leftarrow (w \times 2) \times x$                   |

| 6     | 8   | loadAI r $_{arp}$ , @z $\Rightarrow$ r $_{2}$                                        | // load 'z'                                                 |

| 7     | 8   | $\texttt{mult}  \texttt{r}_1 \texttt{, r}_3  \Rightarrow  \texttt{r}_1$              | $// r_1 \leftarrow (w \times 2 \times x) \times y$          |

| 9     | 10  | $\texttt{mult}  \texttt{r}_1 \texttt{,} \; \texttt{r}_2 \; \Rightarrow \texttt{r}_1$ | $// r_1 \leftarrow (w \times 2 \times x \times y) \times z$ |

| 11    | 13  | $	exttt{storeAIr}_1 \Rightarrow 	exttt{r}_{arp}, 	exttt{Qw}$                         | // write ${\sf r}_w$ back to 'w'                            |

This reduced the time required for the computation from twenty-two cycles to thirteen. It required one more register than the minimal number, but cut the execution time nearly in half. It starts an instruction in every cycle except eight and ten. This schedule is not unique; several equivalent schedules are possible, as are equal length schedules that use one more register.

Instruction scheduling is, like register allocation, a hard problem. In its general form, it is NP-Complete. Because variants of this problem arise in so many fields, it has received a great deal of attention in the literature.

*Interactions* Most of the truly hard problems that occur in compilation arise during code generation. To make matters more complex, these problems inter-

#### Digression: Terminology

A careful reader will notice that we use the word "code" in many places where either "program" or "procedure" might naturally fit. This is a deliberate affectation; compilers can be invoked to translate fragments of code that range from a single reference through an entire system of programs. Rather than specify some scope of compilation, we will continue to use the ambiguous term "code."

act. For example, instruction scheduling moves load instructions away from the arithmetic operations that depend on them. This can increase the period over which the value is needed and, correspondingly, increase the number of registers needed during that period. Similarly, the assignment of particular values to specific registers can constrain instruction scheduling by creating a "false" dependence between two instructions. (The second instruction cannot be scheduled until the first completes, even though the values in the overlapping register are independent. Renaming the values can eliminate this false dependence, at the cost of using more registers.)

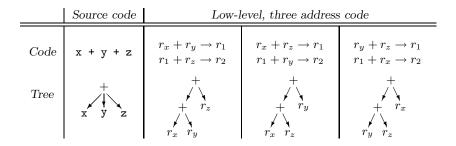

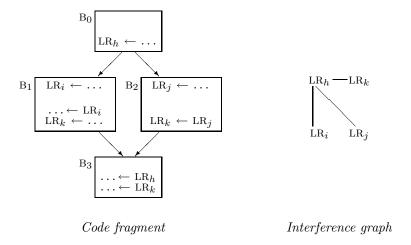

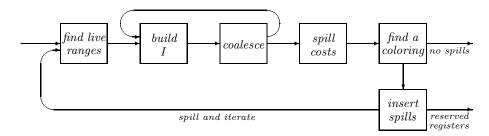

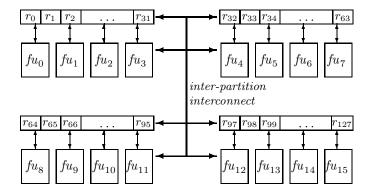

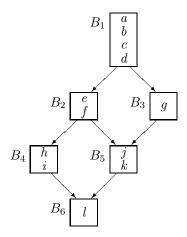

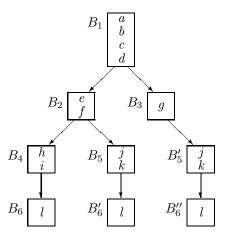

Chapters 8 through 11 describe the issues that arise in code generation and present a variety of techniques to address them. Chapter 8 creates a base of knowledge for the subsequent work. It discusses "code shape," the set of choices that the compiler makes about how to implement a particular source language construct. Chapter 9 builds on this base by discussing algorithms for instruction selection—how to map a particular code shape into the target machine's instruction set. Chapter 10 looks at the problem of deciding which values to keep in registers and explores algorithms that compilers use to make these decisions. Finally, because the order of execution can have a strong impact on the performance of compiled code, Chapter 11 delves into algorithms for scheduling instructions.

#### 1.3.4 Improving the Code

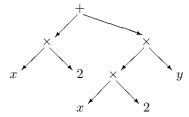

Often, a compiler can use contextual knowledge to improve the quality of code that it generates for a statement. If, as shown on the left side of Figure 1.2, the statement in our continuing example was embedded in a loop, the contextual information might let the compiler significantly improve the code. The compiler could recognize that the subexpression  $2 \times x \times y$  is invariant in the loop – that is, its value does not change between iterations. Knowing this, the compiler could rewrite the code as shown on the right side of the figure. The transformed code performs many fewer operations in the loop body; if the loop executes more than once, this should produce faster code.

This process of analyzing code to discover facts from context and using that knowledge to improve the code is often called *code optimization*. Roughly speaking, optimization consists of two distinct activities: analyzing the code to understand its runtime behavior and transforming the code to capitalize on knowledge derived during analysis. These techniques play a critical role in the

```

x \leftarrow \cdots

v \leftarrow \cdots

y \leftarrow \cdots

w \leftarrow 1

t_i \leftarrow 2 \times x \times y

w \leftarrow 1

for i = 1 to n

for i = 1 to n

read z

read z

w \leftarrow w \times 2 \times x \times y \times z

w \leftarrow w \times z \times t_i

end

end

Surrounding context

Improved code

```

**Figure 1.2:** Context makes a difference

performance of compiled code; the presence of a good optimizer can change the kind of code that the rest of the compiler should generate.

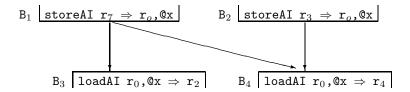

Analysis Compilers use several kinds of analysis to support transformations. Data-flow analysis involves reasoning, at compile-time, about the flow of values at runtime. Data-flow analyzers typically solve a system of simultaneous set equations that are derived from the structure of the code being translated. Dependence analysis uses number-theoretic tests to reason about the values that can be assumed by subscript expressions. It is used to disambiguate references to elements of arrays and indexed structures.

Transformation Many distinct transformations have been invented that try to improve the time or space requirements of executable code. Some of these, like discovering loop-invariant computations and moving them to less frequently executed locations, improve the running time of the program. Others make the code itself more compact. Transformations vary in their effect, the scope over which they operate, and the analysis required to support them. The literature on transformations is rich; the subject is large enough and deep enough to merit a completely separate book.

The final part of the book introduces the techniques that compilers use to analyze and improve programs. Chapter 13 describes some of the methods that compilers use to predict the runtime behavior of the code being translated. Chapter 14 then presents a sampling of the transformations that compilers apply to capitalize on knowledge derived from analysis.

#### 1.4 Compiler Structure

Understanding the issues involved in translation is different than knowing their solutions. The community has been building compilers since 1955; over those years, we have learned a number of lessons about how to structure a compiler. At the start of this chapter, the compiler was depicted as a single box that translated a source program into a target program. Reality is, of course, more complex than that simple pictogram.

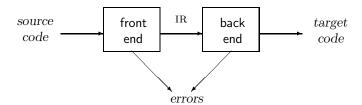

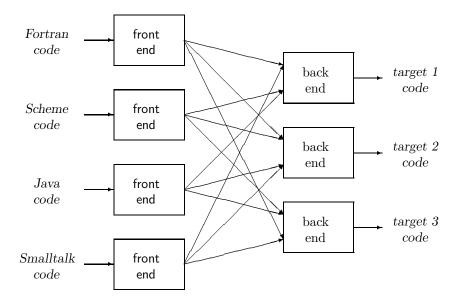

The discussion in Section 1.3 suggested a dichotomy between the task of understanding the input program and the task of mapping its functionality onto the target machine. Following this line of thought leads to a compiler that is decomposed into two major pieces, a *front end* and a *back end*.

The decision to let the structure reflect the separate nature of the two tasks has several major implications for compiler design.

First, the compiler must have some structure that encodes its knowledge of the code being compiled; this *intermediate representation* (IR) or *intermediate language* becomes the definitive representation of the code for the back end. Now, the task of the front end is to ensure that the source program is well formed and to map that code into the IR, and the task of the back end is to map the IR onto the target machine. Since the back end only processes IR created by the front end, it can assume that the IR contains no errors.

Second, the compiler now makes multiple passes over the code before committing itself to target code. This should lead to better code; the compiler can, in effect, study the code in its first pass and record relevant details. Then, in the second pass, it can use these recorded facts to improve the quality of translation. (This idea is not new. The original FORTRAN compiler made several passes over the code [3]. In a classic 1961 paper, Floyd proposed that the compiler could generate better code for expressions if it made two passes over the code [31].) To achieve this, however, the knowledge derived in the first pass must be recorded in the IR, where the second pass can find it.

Finally, the two pass structure may simplify the process of retargeting the compiler. We can easily envision constructing multiple back ends for a single front end; doing so would produce compilers that accepted the same language but targeted different machines. This assumes that the same IR program is appropriate for both target machines; in practice, some machine-specific details usually find their way into the IR.

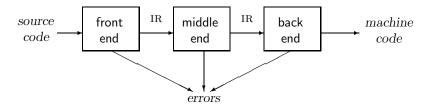

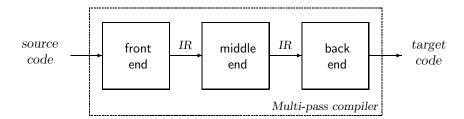

The introduction of an IR into the compiler makes possible further passes over the code. These can be implemented as transformers that take as input an IR program and produce an equivalent, but improved, IR program. (Notice that these transformers are, themselves, compilers according to our definition in Section 1.1.) These transformers are sometimes called *optimizations*; they can be grouped together to form an *optimizer* or a *middle end*. This produces a structure that looks like:

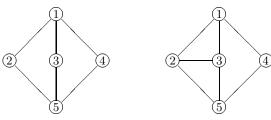

We will call this a three-pass compiler; it is often called an optimizing compiler. Both are misnomers. Almost all compilers have more than three passes. Still, the conceptual division into front end, middle end, and back end is useful. These three parts of the compiler have quite different concerns. Similarly, the term "optimization" implies that the compiler discovers an optimal solution to some problem. Many of the problems in that arise in trying to improve compiled code are so complex that they cannot be solved to optimality in a reasonable amount of time. Furthermore, the actual speed of the compiled code depends on interactions among all of the techniques applied in the optimizer and the back-end. Thus, when a single technique can be proved optimal, its interactions with other techniques can produce less than optimal results. As a result, a good optimizing compiler can improve the quality of the code, relative to an unoptimized version. It will often fail to produce optimal code.

The middle end can be a monolithic structure that applies one or more techniques to improve the code, or it can be structured as a series of individual passes that each read and write IR. The monolithic structure may be more efficient, in that it avoids lots of input and output activity. The multi-pass structure may lend itself to a less complex implementation and a simpler approach to debugging the compiler. The choice between these two approaches depends on the constraints under which the compiler is built and operates.

#### 1.5 Summary and Perspective

A compiler's primary mission is to translate its input program into an equivalent output program. Many different programs qualify as compilers. Most of these can be viewed as either two pass or three pass compilers. They have a front end that deals with the syntax and meaning of the input language and a back end that deals with the constraints of the output language. In between, they may have a section that transforms the program in an attempt to "improve" it.

Different projects, of course, aim for different points in the compiler design space. A compiler that translates C code for embedded applications like automobiles, telephones, and navigation systems, might be concerned about the size of the compiled code, since the code will be burned into some form of read-only memory. On the other hand, a compiler that sits inside the user-interface of a network browser and translates compressed application code to drive the display might be designed to minimize the sum of compile time plus execution time.

#### Questions

- 1. In designing a compiler, you will face many tradeoffs. What are the five qualities that you, as a user, consider most important in a compiler that you purchased? Does that list change when you are the compiler writer? What does your list tell you about a compiler that you would implement?

- 2. Compilers are used in many different circumstances. What differences might you expect in compilers designed for the following applications?

- (a) a *just-in-time* compiler used to translate user interface code downloaded over a network

- (b) a compiler that targets the embedded processor used in a cellular telephone

- (c) a compiler used in the introductory programming course at a high school

- (d) a compiler used to build wind-tunnel simulations that run on a massively parallel processors (where all the processors are identical)

- (e) a compiler that targets numerically-intensive programs to a large network of diverse machines

## Chapter 2

## Lexical Analysis

#### 2.1 Introduction

The scanner takes as input a stream of characters and produces as output a stream of words, along with their associated syntactic categories. It aggregates letters together to form words and applies a set of rules to determine whether or not the word is legal in the source language and, if so, its syntactic category. This task can be done quickly and efficiently using a specialized recognizer.

This chapter describes the mathematical tools and the programming techniques that are commonly used to perform lexical analysis. Most of the work in scanner construction has been automated; indeed, this is a classic example of the application of theoretical results to solve an important and practical problem—specifying and recognizing patterns. The problem has a natural mathematical formulation. The mathematics leads directly to efficient implementation schemes. The compiler writer specifies the lexical structure of the language using a concise notation and the tools transform that specification into an efficient executable program. These techniques have led directly to useful tools in other settings, like the Unix tool grep and the regular-expression pattern matching found in many text editors and word-processing tools. Scanning is, essentially, a solved problem.

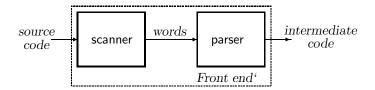

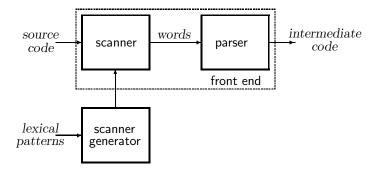

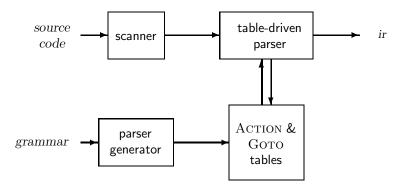

Scanners look at a stream of characters and recognize words. The rules that govern the lexical structure of a programming language, sometimes called its *micro-syntax*, are simple and regular. This leads to highly efficient, specialized recognizers for scanning. Typically, a compiler's front end has a scanner to handle its micro-syntax and a parser for its context-free syntax, which is more complex to recognize. This setup is shown in Figure 2.1. Separating micro-syntax from syntax simplifies the compiler-writer's life in three ways.

• The description of syntax used in the parser is written in terms of words and syntactic categories, rather than letters, numbers, and blanks. This lets the parser ignore irrelevant issues like absorbing extraneous blanks, newlines, and comments. These are hidden inside the scanner, where they

Figure 2.1: Structure of a typical front end

are handled cleanly and efficiently.

- Scanner construction is almost completely automated. The lexical rules are encoded in a formal notation and fed to a scanner generator. The result is an executable program that produces the input for the parser. Scanners generated from high-level specifications are quite efficient.

- Every rule moved into the scanner shrinks the parser. Parsing is harder than scanning; the amount of code in a parser grows as the grammar grows. Since parser construction requires more direct intervention from the programmer, shrinking the parser reduces the compiler-writer's effort.

As a final point, well-implemented scanners have lower overhead (measured by instructions executed per input symbol) than well-implemented parsers. Thus, moving work into the scanner improves the performance of the entire front end.

Our goal for this chapter is to develop the notations for specifying lexical patterns and the techniques to convert those patterns directly into an executable scanner. Figure 2.2 depicts this scenario. This technology should allow the compiler writer to specify the lexical properties at a reasonably high level and leave the detailed work of implementation to the scanner generator—without sacrificing efficiency in the final product, the compiler.

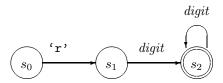

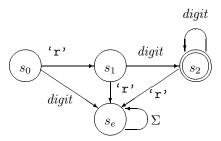

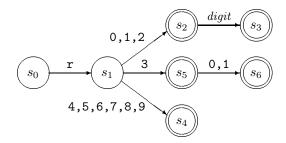

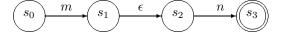

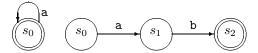

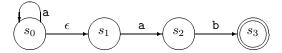

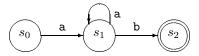

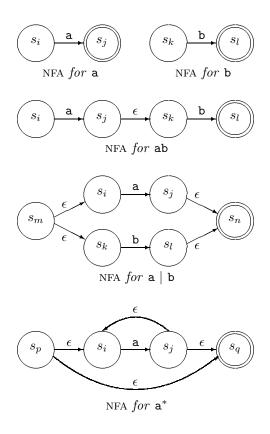

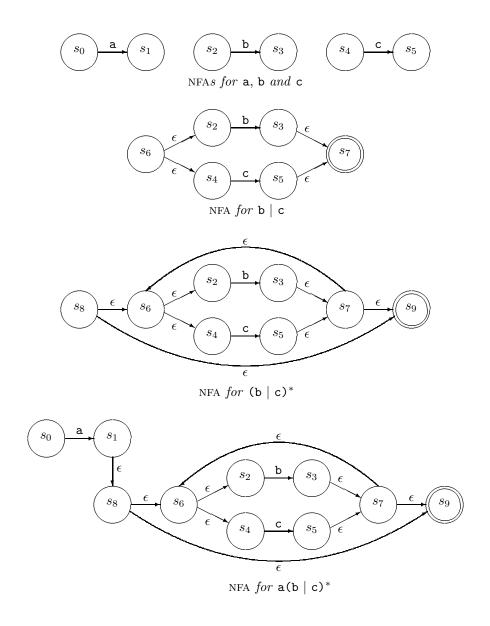

First, we will introduce a notation, called regular expressions, that works well for specifying regular expressions. We will explore the properties of regular expressions and their relationship to a particular kind of recognizer, called a finite automaton. Next, we will develop the techniques and methods that allow us to automate the construction of efficient scanners from regular expressions. We show some additional results that relate regular expressions and automata, and conclude with an example of how complex the task of lexical analysis can be in FORTRAN, a language designed before we had a good understanding of the mathematics of lexical analysis.

#### 2.2 Specifying Lexical Patterns

Before we can build a scanner, we need a way of specifying the micro-syntax of the source language—of specifying patterns that describe the words in the language. Some parts are quite easy.

• Punctuation marks like colons, semi-colons, commas, parentheses, and square brackets can be denoted by their unique character representations:

Figure 2.2: Automatic scanner generation

:;,()[]

• Keywords, like if, then, and integer are equally simple. These words have a unique spelling, so we can represent them as literal patterns—we simply write them down.

Some simple concepts have more complicated representations. For example, the concept of a blank might require a small grammar.

where blank and tab have the obvious meanings.