| Ernesto  | Sanchez | Giovanni  | Sauillero | and Alberto  | Tonda  |

|----------|---------|-----------|-----------|--------------|--------|

| LITICSTO | January | Giovailli | Judilicio | , and moento | IUIIua |

Industrial Applications of Evolutionary Algorithms

# Intelligent Systems Reference Library, Volume 34

#### **Editors-in-Chief**

Prof. Janusz Kacprzyk Systems Research Institute Polish Academy of Sciences

ul. Newelska 6 01-447 Warsaw

Poland

E-mail: kacprzyk@ibspan.waw.pl

Prof. Lakhmi C. Jain

University of South Australia

Adelaide

Mawson Lakes Campus South Australia 5095

Australia

E-mail: Lakhmi.jain@unisa.edu.au

Further volumes of this series can be found on our homepage: springer.com

Vol. 10. Andreas Tolk and Lakhmi C. Jain Intelligence-Based Systems Engineering, 2011 ISBN 978-3-642-17930-3

Vol. 11. Samuli Niiranen and Andre Ribeiro (Eds.) Information Processing and Biological Systems, 2011 ISBN 978-3-642-19620-1

Vol. 12. Florin Gorunescu Data Mining, 2011 ISBN 978-3-642-19720-8

Vol. 13. Witold Pedrycz and Shyi-Ming Chen (Eds.) Granular Computing and Intelligent Systems, 2011 ISBN 978-3-642-19819-9

Vol. 14. George A. Anastassiou and Oktay Duman Towards Intelligent Modeling: Statistical Approximation Theory, 2011

ISBN 978-3-642-19825-0

Vol. 15. Antonino Freno and Edmondo Trentin Hybrid Random Fields, 2011 ISBN 978-3-642-20307-7

Vol. 16. Alexiei Dingli

Knowledge Annotation: Making Implicit Knowledge Explicit, 2011

ISBN 978-3-642-20322-0

Vol. 17. Crina Grosan and Ajith Abraham Intelligent Systems, 2011

ISBN 978-3-642-21003-7

Vol. 18. Achim Zielesny

From Curve Fitting to Machine Learning, 2011

ISBN 978-3-642-21279-6 Vol. 19. George A. Anastassiou

Intelligent Systems: Approximation by Artificial Neural Networks. 2011

ISBN 978-3-642-21430-1

Vol. 20. Lech Polkowski

Approximate Reasoning by Parts, 2011

ISBN 978-3-642-22278-8

Vol. 21. Igor Chikalov

Average Time Complexity of Decision Trees, 2011 ISBN 978-3-642-22660-1

Vol. 22. Przemysław Rżewski,

Emma Kusztina, Ryszard Tadeusiewicz,

and Oleg Zaikin

Intelligent Open Learning Systems, 2011

ISBN 978-3-642-22666-3

Vol. 23. Dawn E. Holmes and Lakhmi C. Jain (Eds.) Data Mining: Foundations and Intelligent Paradigms, 2011 ISBN 978-3-642-23165-0

Vol. 24. Dawn E. Holmes and Lakhmi C. Jain (Eds.)

Data Mining: Foundations and Intelligent Paradigms, 2011

ISBN 978-3-642-23240-4

Vol. 25. Dawn E. Holmes and Lakhmi C. Jain (Eds.) Data Mining: Foundations and Intelligent Paradigms, 2011 ISBN 978-3-642-23150-6

Vol. 26. Tauseef Gulrez and Aboul Ella Hassanien (Eds.) *Advances in Robotics and Virtual Reality*, 2011 ISBN 978-3-642-23362-3

Vol. 27. Cristina Urdiales

Collaborative Assistive Robot for Mobility Enhancement (CARMEN), 2011

ISBN 978-3-642-24901-3

Vol. 28. Tatiana Valentine Guy, Miroslav Kárný and David H. Wolpert (Eds.)

Decision Making with Imperfect Decision Makers, 2012 ISBN 978-3-642-24646-3

Vol. 29. Roumen Kountchev and Kazumi Nakamatsu (Eds.) Advances in Reasoning-Based Image Processing Intelligent Systems, 2012

ISBN 978-3-642-24692-0

Vol. 30. Marina V. Sokolova and Antonio Fernández-Caballero Decision Making in Complex Systems, 2012

ISBN 978-3-642-25543-4

Vol. 31. Ludomir M. Laudański Between Certainty and Uncertainty, 2012 ISBN 978-3-642-25696-7

Vol. 32. José J. Pazos Arias, Ana Fernández Vilas, and Rebeca P. Díaz Redondo Recommender Systems for the Social Web, 2012 ISBN 978-3-642-25693-6

Vol. 33. Jie Lu, Lakhmi C. Jain, and Guangquan Zhang Handbook on Decision Making, 2012 ISBN 978-3-642-25754-4

Vol. 34. Ernesto Sanchez, Giovanni Squillero, and Alberto Tonda

Industrial Applications of Evolutionary Algorithms, 2012 ISBN 978-3-642-27466-4

Ernesto Sanchez, Giovanni Squillero, and Alberto Tonda

# Industrial Applications of Evolutionary Algorithms

Authors

Prof. Ernesto Sanchez Politecnico di Torino - DAUIN Italy

Prof. Giovanni Squillero Politecnico di Torino - DAUIN Italy Dr. Alberto Tonda Politecnico di Torino - DAUIN Italy

e-ISSN 1868-4408

e-ISBN 978-3-642-27467-1

ISSN 1868-4394 ISBN 978-3-642-27466-4 DOI 10.1007/978-3-642-27467-1

OI 10.1007/978-3-642-27467-1

Library of Congress Control Number: 2011945155

Springer Heidelberg New York Dordrecht London

### © Springer-Verlag Berlin Heidelberg 2012

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

# **Foreword**

My mother was a very simple plain person, with a hearth of gold. She was proud of my academic successes and research career; she often asked me "But what does your work consist of?". I am an expert in Computational Intelligence, i.e., neural networks, fuzzy logic and evolutionary computation, and although I am a full professor at the Faculty of Engineering of the University of Pisa, it was not easy to answer my mother's question. She used to think that her world ("the real world") and my world ("the artificial, intellectual world") were so far from each other that no means could ever exist to let these worlds interact. But one day, by chance, evolutionary computation made the miracle happen! Yes, that day I went to visit my mother and found her completely busy doing a lot of things. So I proposed her a sort of game. I said to her: "You have to perform a set of tasks (such as cleaning up the house, cooking the dinner, etc), each consisting of a series of more elementary operations, which can be performed in parallel or sequentially. You need an operation sequence plan that specifies the collection and the order of operations to carry out. Actually, not all the combinations of operations are feasible, e.g., you cannot start cooking the pasta before putting a saucepan on to cook. Further, some feasible and valid sequences can be better, e.g., less time-consuming or demanding fewer tool changes, than others. Of course your desire is to finish your work as good and as early as possible. How do you choose the operation plan?"

"I do not follow any rule, it is just habit", she answered.

"Then, consider all the single operations making the specific tasks to perform, and write down on a piece of paper a few randomly-generated sequences of these operations. Now rank the generated operation sequences based, e.g., on feasibility and time/fatigue effort requirements. If the best sequence satisfies your desire, follow that operation plan. Otherwise let an Evolutionary Algorithm (EA) generate a new list of operation sequences obtained by automatically combining the current sequences in an appropriate way. Check if the best sequence is good for you, otherwise repeat the process again, and so on. You can be sure that the EA will find a good solution sooner or later."

She looked at me astonished, without speaking. I went on saying "This is a simple way to mimic natural evolution, and EAs do exactly this in an automatic way."

VI Foreword

What had happened that day? I and my mother had simply managed to make our worlds interact, a thing that appeared impossible up to that moment. It is like Columbus's egg.

Probably this is the right and only way to fill the gap between apparently different worlds like that of modern industrial applications and that of EAs. EAs can perform systematic random search in order to improve the likelihood of finding globally optimal solutions. On the other hand experience has shown that awareness of real-world industrial problems and knowledge of traditional computation techniques are not always enough to cope with the growing complexity of modern industrial processes and products. Then, why not to use the potentiality of EAs? Probably industrial experts are simply not aware of how EAs could be applied to solve their problems. In fact the key point to applying EAs to solve otherwise intractable problems is just representing and assessing the candidate solutions to a problem in an appropriate way.

It is just like Columbus's egg. Let the experts of EAs show industrial engineers and operators what EAs can do! The current book makes exactly this by presenting a collection of real significant industrial problems and their EA-based solutions. The considered case studies help the reader learn to employ EAs with a minimal investment in time and effort. This is what makes the current book useful and valuable for effective technology transfer into industrial organizations. Described applications include automatic software verification, test program generation for microprocessors, test generation for hardware and circuits, antenna array synthesis and optimization, drift correction of chemical sensors, and generation of test sets for on-line test of microprocessors.

Now that EAs represent a pretty mature field this is the right book for all post-graduates, research scientists and practitioners who want to tackle challenging industrial problems, of whatever complexity, with the most up-to-date, powerful and easy-to-use optimization technology.

Pisa, Italy, September 2011

Beatrice Lazzerini

# **Preface**

The increasing complexity of products and processes leads directly to the growing intricacy of the problems and issues the industrial world is facing. More and more often, traditional computational techniques prove unable to cope with real world situations, either because the time needed to reach an optimal solution is not compatible with the frantic development processes of a company, or because the modeling of complex systems to the degree of precision needed is unfeasible. Evolutionary Algorithms (EA) comprehend a wide class of stochastic bio-inspired optimization techniques, firstly developed by J. H. Holland, L. J. Fogel, I. Rechenberg and H. Schwefel during the late 1960s and early 70s. Over the course of the last 35 years, EAs demonstrated their effectiveness in an extended variety of problems, ranging from airfoil design to credit card fraud detection. The industrial world, however, is still reluctant to introduce these powerful techniques into real procedures, mainly due to the sensation of insufficient controllability, scarce repeatability of the results, and the lack of experts with deep knowledge of both EAs and modern industrial needs. This book presents different case studies of EAs successfully applied to real world problems, hopefully showing the untapped potential of these techniques in various industrial fields.

Chapter 1 comprehends a description of typical complex industrial problems, a brief history of EAs, a comparison with traditional methods, and a discussion on the application of evolutionary techniques to real world problems.

Chapter 2 presents what is meant to be a surely incomplete, but extremely useful list of resources relevant for further elaboration and understanding of the multifaceted world of EAs.

The first section groups industrial problems related to the verification of hardware and software working prototypes.

The case study presented in chapter 3 deals with the software verification of a whole operative system and all applications running on a mobile phone prototype. The chapter focus specifically on the problems concerning the application of an EA to a "needle in a haystack" kind of problem; on how to make the EA perform; and on how EAs can complete human expertise in the software verification field. The activity is carried out in cooperation with Motorola Research Labs, Torino, Italy.

VIII Preface

The verification of microprocessors is a growing field of study, mainly because design capability outperforms current verification techniques. Most studies on the correct behavior of a microprocessor are thus run on working prototypes, in the attempt to locate critical paths by making the device fail its computations. In chapter 4, an EA-based method to identify critical speed-paths in a multi-core microprocessor, exceeding the performance of state-of-the-art stress tests, is described.

The second section presents a collection of real-world case studies pertaining design and reliability.

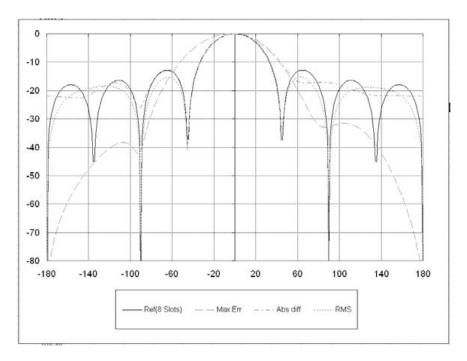

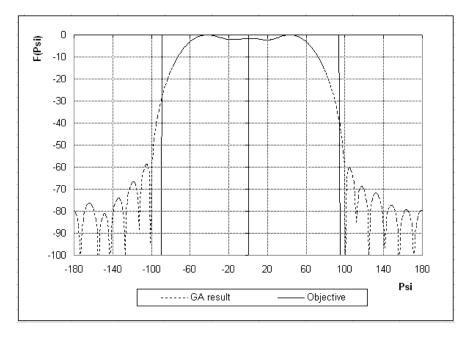

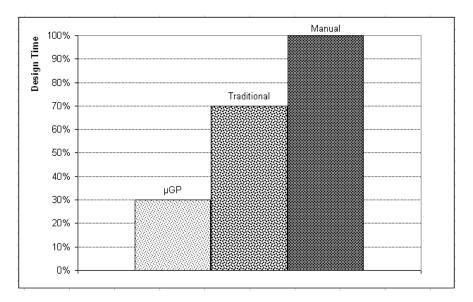

The design of an antenna array is the topic of chapter 5. When devising such a complex system, often manual or automatic optimization methods do not yield satisfactory results, being either too labour-intensive or unsuitable for some specific class of problems. When an evolutionary algorithm is used to optimize parameters of the antenna array, the results show that these techniques are able to obtain better results than both manual and automatic approaches.

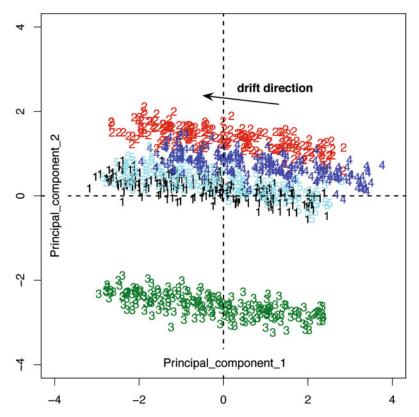

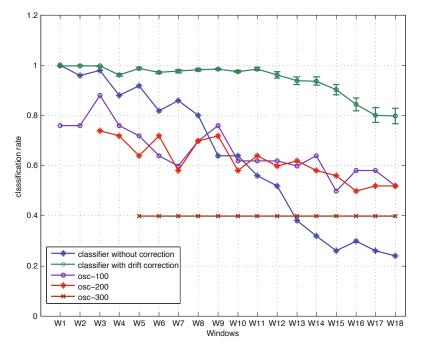

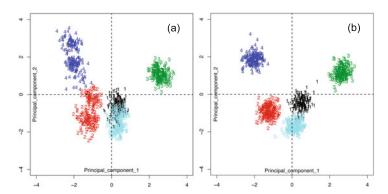

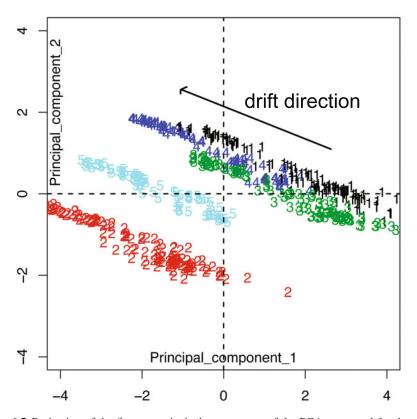

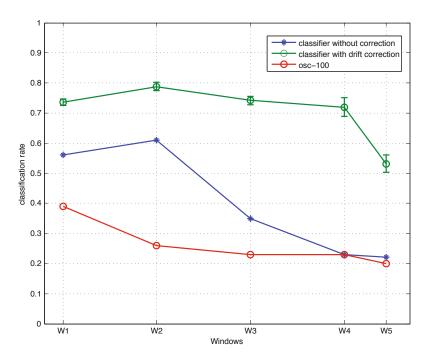

In chapter 6, an EA-based technique to lengthen the lifespan of *electronic noses*, complex olfactory sensor arrays, is presented. Sensor arrays are affected by the *drift* problem, a degenerative error in the measurements, hard to model and predict. The proposed solution is to dynamically adjust the sensor readings with a state-of-the art Evolutionary Strategy proves to be effective. The experience is performed with the collaboration of Sensor CNR-INFM Lab, Brescia, Italy.

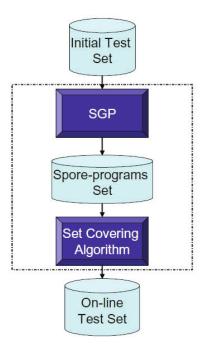

Chapter 7 tackles the problem of automatically devising online test sets for microprocessor-based systems. While existing manufacturing test set can be used for this purpose, several additional constraints must be considered for an online application, including test length, duration, and intrusiveness. The proposed methodology, here applied to an Intel 8051 microcontroller, exploits an EA to create online test sets starting from tests devised by the manufacturer.

The third section introduces results obtained through the application of EAs to test generation problems for hardware and circuits.

Chapter 8 concerns the study of path delay faults in electronic devices, misbehaviors where a device produces a correct result without conforming to time specifications. Devising test to uncover the presence of these faults is challenging, exspecially when only a high-level description of the device is provided. To tackle this problem, where the ideal result is a set of equally feasible solutions, a Multi-Objective Evolutionary Algorithm (MOEA) is employed.

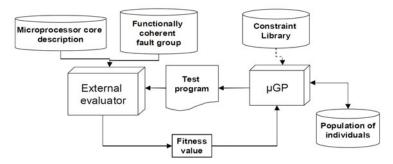

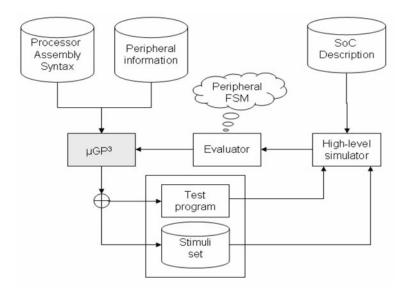

In chapter 9, EAs are applied to the field of Software-Based Self Testing (SBST), an established test technique for various hardware architectures. SBST's principle is to apply a suitable series of stimuli to the device under test, comparing the produced output to the expected one. Finding a minimal set of stimuli to thoroughly excite a device is not a trivial problem: EAs prove successful once again, showing that the proposed methodology is effective on a wide range of hardware peripherals.

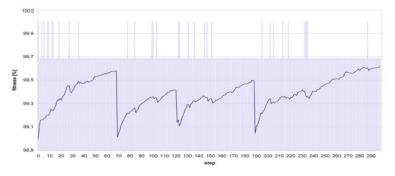

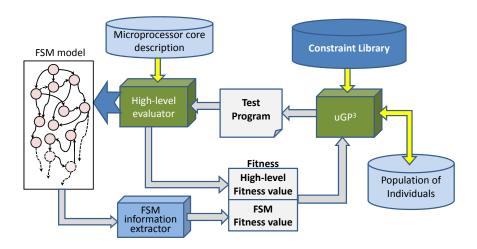

Chapter 10 deals again with stimuli generation for SBST, this time tackling a much more complex system, such as a microprocessor pipeline. Using a high-level representation of the target device, and a dynamically built Finite State Machine (FSM), fault coverage of the candidate stimuli are evaluated without resorting to time-expensive simulations on low-level models. Experimental results show that

the evolved test obtains a nearly complete fault coverage against the targeted fault model.

# Acknowledgments

The authors would like to express their gratitude towards their families and colleagues for their invaluable support, useful ideas and intriguing discussion. A particular thank to A. Aimo, P. Bernardi, A. Cerato, K. Christou, S. Di Carlo, S. Drappero, M. Falasconi, G. Fisanotti, M. Grosso, S. Loiacono, M. K. Michael, L. Manetta, A. Moscatello, L. Motta, L. Ollino, D. Ravotto, T. Rosato, W. Ruzzarin, M. Schillaci, A. Scionti and M. Sonza Reorda; without their help, this book would have not been possible.

# **Contents**

| 1   | Intr   | duction                                             | 1  |  |

|-----|--------|-----------------------------------------------------|----|--|

|     | 1.1    | Industrial Problems                                 | 1  |  |

|     | 1.2    | A Brief History of Evolutionary Algorithms          |    |  |

|     |        | 1.2.1 Natural and Artificial Evolution              | 3  |  |

|     |        | 1.2.2 Genetic Algorithms                            | 5  |  |

|     |        | 1.2.3 Evolutionary Programming                      | 6  |  |

|     |        | 1.2.4 Evolution Strategies                          | 7  |  |

|     |        | 1.2.5 Genetic Programming                           | 9  |  |

| 2   | Res    | urces                                               | 11 |  |

|     | 2.1    | Books                                               | 11 |  |

|     | 2.2    | Journals                                            | 12 |  |

|     | 2.3    | International Conferences and Workshops             | 12 |  |

|     | 2.4    | Software                                            | 13 |  |

|     | 2.5    | Suggested Readings on Natural Evolution and Biology | 13 |  |

| Pai | rt I P | ototype-Based Validation Problems                   |    |  |

| 3   | Aut    | matic Software Verification                         | 17 |  |

|     | 3.1    |                                                     | 17 |  |

|     | 3.2    |                                                     | 18 |  |

|     |        | 3.2.1 Mobile Phones                                 | 18 |  |

|     |        | 3.2.2 Verification Techniques                       | 19 |  |

|     | 3.3    | 1                                                   |    |  |

|     |        |                                                     | 23 |  |

|     |        | 3.3.2 Candidate Solutions                           | 25 |  |

|     |        | 3.3.3 Evaluator                                     | 25 |  |

|     | 3.4    | Experimental Results                                | 27 |  |

|     |        | 3.4.1 Video Recording Bug                           | 28 |  |

|     |        | 3.4.2 Voice Call Bug                                | 28 |  |

XII Contents

|     |        | 3.4.3 Incorrect Menu Behavior                                  |

|-----|--------|----------------------------------------------------------------|

|     | 3.5    | Conclusions                                                    |

| 4   | Post   | -silicon Speed-Path Analysis in Modern Microprocessors         |

|     |        | ugh Genetic Programming 31                                     |

|     | 4.1    | Background                                                     |

|     | 4.2    | Introduction                                                   |

|     | 4.3    | Generation and Evaluation of Test Programs                     |

|     | 4.4    | Evolutionary Approach                                          |

|     |        | 4.4.1 Fitness Function                                         |

|     |        | 4.4.2 Individual Evaluation                                    |

|     |        | 4.4.3 Evolution Start                                          |

|     |        | 4.4.4 Internal Representation, Multithreading and Multicore 37 |

|     |        | 4.4.5 Assembly Language                                        |

|     |        | 4.4.6 Cache                                                    |

|     | 4.5    | Experimental Evaluation                                        |

|     |        | 4.5.1 Overclockers' Stress Tests                               |

|     |        | 4.5.2 Target System                                            |

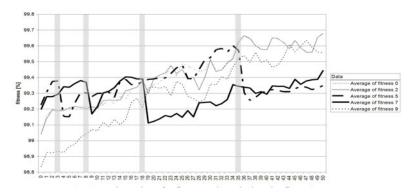

|     |        | 4.5.3 Experimental Results                                     |

|     | 4.6    | Conclusions and Future Works 44                                |

|     |        |                                                                |

| Par | t II I | Design and Reliability Problems                                |

| 5   | Ante   | enna Array Synthesis with Evolutionary Algorithms              |

| J   | 5.1    | Introduction                                                   |

|     | 5.2    | Antenna Arrays                                                 |

|     | 5.3    | Evolutionary Algorithm                                         |

|     | 5.4    | Experimental Setup                                             |

|     | 5.5    | Experimental Results                                           |

|     | 5.6    | Conclusions                                                    |

|     | 5.0    | Conclusions                                                    |

| 6   | Drif   | t Correction of Chemical Sensors                               |

|     | 6.1    | Introduction                                                   |

|     | 6.2    | Method and Theory                                              |

|     |        | 6.2.1 Correction Factor                                        |

|     |        | 6.2.2 Classification                                           |

|     |        | 6.2.3 Correction Factor Optimization                           |

|     |        | 6.2.4 Distance Functions                                       |

|     | 6.3    | Case Studies and Experimental Results 63                       |

|     |        | 6.3.1 Artificial Dataset                                       |

|     |        | 6.3.2 Real Dataset                                             |

|     | 6.4    | CMA-ES                                                         |

|     | 6.5    | Conclusions                                                    |

| Contents | XIII |

|----------|------|

|----------|------|

| 7   | Deve  | elopment of On-Line Test Sets for Microprocessors               | 75  |

|-----|-------|-----------------------------------------------------------------|-----|

|     | 7.1   | Introduction                                                    | 75  |

|     | 7.2   | Proposed Methodology                                            | 77  |

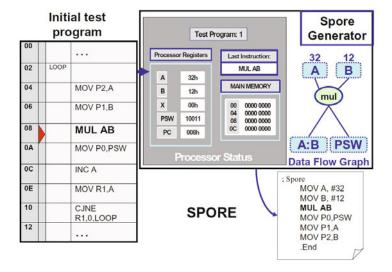

|     |       | 7.2.1 Spore Generator Description                               | 79  |

|     |       | 7.2.2 Set Covering                                              | 81  |

|     | 7.3   | Case Study                                                      | 82  |

|     | 7.4   | Conclusions                                                     | 84  |

| Par | t III | Test Generation Problems                                        |     |

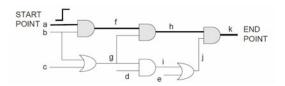

| 8   | Unc   | overing Path Delay Faults with Multi-Objective EAs              | 89  |

|     | 8.1   | Introduction                                                    | 89  |

|     | 8.2   | Background                                                      | 90  |

|     |       | 8.2.1 Software-Based Path Delay Testing                         | 90  |

|     |       | 8.2.2 Exploiting Gate- and RT Level Descriptions for            |     |

|     |       | Path-Delay Testing                                              | 91  |

|     |       | 8.2.3 BDDs for Structural Path Delay Fault Tests                | 92  |

|     |       | 8.2.4 Basic Concepts on MOEAs                                   | 93  |

|     | 8.3   | Proposed Approach                                               | 93  |

|     | 8.4   | Experimental Data                                               | 96  |

|     | 8.5   | Conclusions                                                     | 99  |

|     | ~ .   |                                                                 |     |

| 9   |       | ware-Based Self Testing of System Peripherals                   | 101 |

|     | 9.1   | Introduction                                                    | 101 |

|     | 9.2   | Peripheral Testing                                              | 102 |

|     |       | 9.2.1 Basics                                                    | 102 |

|     |       | 9.2.2 Previous Works                                            | 103 |

|     | 9.3   | Proposed Approach                                               | 104 |

|     |       | 9.3.1 Evolutionary Tool                                         | 105 |

|     |       | 9.3.2 Evaluator                                                 | 107 |

|     | 9.4   | Experimental Analysis                                           | 108 |

|     |       | 9.4.1 Test Case                                                 | 108 |

|     |       | 9.4.2 Experimental Results                                      | 108 |

|     | 9.5   | Conclusions                                                     | 110 |

| 10  | Soft  | ware-Based Self-Testing on Microprocessors                      | 111 |

|     |       | Introduction                                                    | 111 |

|     | 10.2  | Background                                                      | 112 |

|     |       | 10.2.1 Software-Based Self Testing                              | 112 |

|     |       | 10.2.2 Evolutionary Algorithms on Software-Based Self Testing . | 114 |

|     | 10.3  | Proposed Approach                                               | 115 |

|     |       | 10.3.1 μGP                                                      | 117 |

|     |       | 10.3.2 FSM Extractor                                            | 118 |

|     | 10.4  | Case Study and Experimental Results                             | 119 |

|     |       | rences                                                          | 121 |

# Chapter 1 Introduction

This first chapter provides the reader with a survey of current industrial problems, hinting at their complexity and variety. It is shown how traditional computational techniques often fail to deliver the expected results in modern real-world applications, while computational intelligence show an increasing amount of interesting results. Some background and a brief history of Evolutionary Algorithms (EAs) are then provided, introducing these interesting stochastic optimization techniques.

#### 1.1 Industrial Problems

In the modern industrial world, the complexity of problems faced by companies is growing accordingly with the complexity of products they sell. This holds particularly true for the IT field: considering hardware components, the number of connections per silicon wafer is doubling each year, following closely the famous "Moore's Law"; and with a more and more inexpensive and powerful hardware at disposal, the number of applications manageable by operative systems, even on mobile devices, is increasing at almost the same rate.

Such a growth in complexity directly leads to difficulties in every step of product development, starting from the design step. Even determining the correct combination of parameters to obtain the desired behavior for a device is not a straightforward process, because each choice could have intricate and sometimes not foreseeable repercussions. More and more, industry must resort to heuristic and meta-heuristic techniques to find the best alternative between different possibilities. Evolutionary algorithms proved successful in solving several design-related issues, from antennas optimization [101] to fine-tuning of product details to maximize its recycling possibilities [163].

Verification and testing, for which considerable amounts of time and money are invested during the development of a new product, are also heavily influenced by the increasing complexity of devices: microprocessors' designers, for example, candidly acknowledge that "very few chips ever designed function or meet their

2 1 Introduction

performance goal the first time" [106]. In practice, production capacity outperforms testing capacity by several orders of magnitude, and activities once performed on models are now applied to physical prototypes, despite the enormous costs involved in prototyping.

When the single parts of a device become so intricate, the interaction between them could also lead to extreme difficulties in making predictions on the behavior and the lifespan of the device itself. Time to market is a pressing issue for the industry, and the possibilities of studying throughly a system are often limited. Issues in the functionalities of a product can arise in an unexpected way, at unexpected moments: thus, the necessity arises for ways to solve unexpected problems when they appear.

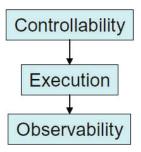

Even when reliable models of devices are available, developing efficient verification sets is not trivial. Often the methodologies applied must adhere to strict constraints of time and memory occupation, since their results could be used under different conditions. In other contexts, some crucial parts of a device are so embedded that even observing the tests' result becomes a non-trivial activity. An example are peripherals in Systems-on-Chip, devices that integrate all components of a computer or other electronic system into a single integrated circuit.

When the product is a software application, although development steps are significantly different, the call for complexity is still in place, transposed to algorithmic level. Image analysis, for example, is one of the fields where traditional techniques are lagging behind: computational intelligence, on the other hand, showed promising results in complicate tasks such as fractal approximation [37], pattern recognition [24] and tracking of moving objects in videos [117].

Classification and data mining also suffer from the increment of available data: in a heavily connected world, statistics obtained from social networks and other websites can be of great interest for companies which desire to advertise their products to a specific audience. Identifying meaningful patterns in such a huge amount of information, however, is a hard problem, and even here classical approaches are showing their limits and the first applications of computational intelligence are appearing in fields such as credit card fraud detection [19].

Several other interesting industrial applications of computational intelligence can be found among the case studies reported in [163], ranging from design of optical fibers to optimization of store performances, from planning of railway track intervention to applications in chemical industries.

# 1.2 A Brief History of Evolutionary Algorithms

The *Theory of evolution* postulates that all living organisms have their origin in other preexisting beings: differences between current lifeforms have their origin in modifications inherited through successive generations. *Evolutionary computation* is the branch of Computer Science that focuses on algorithms inspired by the natural world and the theory of evolution: while this definition may seem vague, the field

of study has boundaries that are not, and cannot be, defined clearly. Evolutionary computation is included in the broader group of *bio-inspired heuristics*, which are in turn a sub-section of *computational intelligence*. In the following, the distinction between *natural evolution* and *artificial evolution* will be stressed out for clarity whenever necessary.

This section is meant to be a brief presentation of the basics of evolutionary computation and its terminology: a thorough description of the topic is out of the scope of this book, and most concepts are detailed only to the extent they are required in the following. Readers interested in a comprehensive coverage of the field will find several fascinating books on the topic, for example [56]. For a survey of the vast and alluring world of biology studies, [48] and [66] can be two interesting starting points.

# 1.2.1 Natural and Artificial Evolution

Scientists show a remarkable consensus on the theory of natural evolution, which is considered a cornerstone of modern biology. The current theory is the sum of several concepts: *evolution* and *natural selection* were introduced almost concurrently and independently by Charles Robert Darwin and Alfred Russel Wallace in 19th century; *selectionism* is an idea of Charles Weismann [160]; *genetics* have been analyzed first by Gregor Mendel [159]. This coherent corpus, often referred to as *Neo-Darwinism*, is able to explain the variety and characteristics of life on Earth starting from a limited number of relatively simple and plausible ideas: *reproduction*, *variation*, *competition*, and *selection*. In this context, reproduction is the process of generating an offspring from parents where the progeny inherit traits of their predecessors. Variation is the unexpected alteration of a trait. Competition and selection are the inevitable results of the strive for survival caused by an environment with limited resources.

By these concepts, evolution appears to be a set of random forces shaped by deterministic pressures: or, in other words, a sequence of steps, some mostly deterministic and some mostly random [105]. It is interesting to notice how similar ideas have been applied to describe phenomena not pertaining to biology, for example alternatives conceived during learning [26], ideas striving to survive in our culture [48], or even possible universes [167] [143].

Eminent biologists, such as Richard Dawkins and Stephen Jay Gould in recent times, repeatedly warned the non-specialist community against mistaking evolution for a process of improvement or optimization, going from raw to perfected features. Nevertheless, assuming for an instant that evolution *is* in fact a force pushing towards an objective, its results are astonishing: over the course of billion years, it turned unorganized groups of cells into startlingly complex structures such as wings and eyes, without the need of any a-priori design. Following this idea, the neo-Darwinistic paradigm itself can be seen as an effective optimization tool, producing

4 1 Introduction

great results from scratch, advancing without a plan, exploiting a mix of random and deterministic techniques.

Setting aside biologists' warnings, evolutionary computation makes use of these powerful ideas to search for optimal solutions in various sets of problems. All these problems often have one common feature: the best way to reach the optimum is not known, at least not in detail. By exploiting neo-Darwinian principles, sets of candidate solutions are cultivated in artificial environments, modified in discrete steps, and selected by an environment defined by the characteristics of the problem itself. Good solutions at a given step inherit positive traits from their ancestors, and optimal results eventually arise from the artificial primordial soup. Unlike evolution, this process has a precise goal; also, these simulated evolutions are often simplified to the extent that they become unrealistic: nevertheless, scientific literature routinely reports success stories of evolutionary computation applied to a vast number of fields.

A small set of terms specific to evolutionary computation is now introduced, since they will be consistently used in the following chapters. Most of the terminology follows closely that of biology. A single candidate solution to a considered problem is called *individual*; a *population* is a group of individuals; and each step of the simulated evolution is termed a *generation*. The *fitness function* measures the effectiveness of an individual in solving the problem. Individuals with high fitness values are more likely to propagate their characteristics to the next generation. The word *genome* always denotes all the genetic information of the individual, even if different approaches use different techniques to store and manage this data. The smallest fragment of the genome that can be modified during the evolution is called *gene*: a gene can also be seen as the functional unit of inherited characteristics. The specific position where a gene is placed in the genome is known as *locus* (plural *loci*). The alternative genes that may appear in a given locus are called *alleles*.

While in biology there is a significant difference between *genotype*, all the genetic material of an organism, and *phenotype*, the observable characteristics that emerge from the interaction between the genotype and its environment, in evolutionary computation this distinction is often disregarded. Genotype and phenotype often coincide, even if sometimes the numerical value representing the fitness of an individual is assimilated to its phenotype.

When the offspring of individuals in evolutionary computation must be produced, often the algorithms exploit the paradigms of sexual and asexual reproduction in nature. Sexual reproduction is usually referred to as *recombination* or *crossover*: the resulting individual will inherit different characteristics from two or more parent individuals. Asexual reproduction is named *replicaton* or *mutation*: a copy of a parent individual is created and slightly altered. Some implementations consistently combine the two approaches, using mutation only after sexual recombination. Very few evolutionary algorithms assign distinct reproductive roles to individuals, so gender is almost never taken into account. Other implementations do not store a collection of individuals, but only a set of statistical parameters that describe the current population: in that case reproduction is performed by altering the parameters. All

algorithmic techniques used to model natural reproduction can be called *evolutionary operators* or *genetic operators*, since they influence the genotype of individuals.

It is clear how variability in the evolutionary process is introduced by mutation and recombination; parent selection also uses a stochastic approach, even if often weighted by the fitness values of individuals in the population, e.g. fittest individuals have a greater probability of being selected. In population-based evolutionary algorithms, the number of individuals in the system varies regularly at each generation: first, offspring is generated, adding new individuals to the population; then, the less fit individuals are discarded. This last step is deterministic: it models the struggle for survival in a hostile environment and it is often referred to as *survivor selection*, *selection* or *slaughtering*.

Evolutionary algorithms may be classified as local search algorithms, since they explore a portion of the search space which is dependent on their actual state, with the offspring loosely defining the concept of neighborhood. Also, since they make use of a *trial and error* paradigm, and that they are not usually able to mathematically guarantee to find an optimal solution in a finite amount of time, evolutionary algorithms can be put into the group of heuristic algorithms: over the years, however, experts of the field have demonstrated the presence of several useful mathematical properties in their processes.

It is noticeable how the definition of evolutionary computation has no clear boundaries, and this branch of computational intelligence also lacks a single recognizable origin. In 1950, the great computer scientist Alan Turing was probably the first to point out the similarities between the processes of learning and evolution [154]. Near the end of the same decade, inspiring ideas in that direction began to appear [61] [111] [18], even if their diffusion among the broader scientific community was blocked by the lack of computational power available at the time. While some scholars point at this time frame as the origin of evolutionary computation, most of them agree that its birth is to be placed in the 1960s, with the appearance of three independent research lines: *genetic algorithms*, *evolutionary computation*, and *evolution strategies*. While an unanimous consensus on the matter is hard to reach, the fundamental importance of these contributions is unquestionable. A fourth paradigm, that appeared in the 1980s, must be also considered for both its novelty and its closeness to the aforementioned ideas.

# 1.2.2 Genetic Algorithms

Genetic algorithms (GA) are probably the most popular technique in evolutionary computation: they are so renowned that in non-specialized literature the term is sometimes used to denote any kind of evolutionary algorithm. John Holland attested the importance of this paradigm in his 1975 book [75], but the methodology was used and described in previous years by a great number of researchers, including many of Holland's students [59] [60] [20]. In the beginning, genetic algorithms have been used as a step in the process of *classifier systems*, a technique also devised by

6 1 Introduction

Holland, and they have been exploited more to study the mechanisms of evolution, than to solve actual problems. In the first experiments a set of simple test benches, e.g. trying to set a number of bits to a specific value, were used to analyze different strategies and schemes.

In a genetic algorithm, an individual (i.e., the evolving entity), is represented as a sequence of bits. This is probably the only feature that was common to all the early implementations, while other choices may vary: the offspring produced at each step usually outnumbers the original population, various crossover and combination operators have been exploited by different researchers, and parents are often selected throughout a fitness-based probability distribution. During the selection of parents, highly fit individuals are favored by a bigger or smaller factor, depending on the *selective pressure* adopted in the algorithm. After the evaluation of new individuals, the population is shrank back to its original size. Several techniques to perform survivor selection have been used, but interestingly all methods to determine the survival of individuals are deterministic. Sometimes, all parents in the population are discarded, regardless of their fitness: if that cases, the approach is called *generational*. Conversely, if all individuals compete for survival independently from their age, the approach is named *steady-state*. All mechanisms that preserve the best individuals through subsequent generations fall under the scope of *elitism*.

# 1.2.3 Evolutionary Programming

Lawrence J. Fogel, in a series of works published at the beginning of 1960s [57] [58], proposed an algorithm that he called *evolutionary programming* (EP). The focus of Fogel's work was the evolution of predictive capabilities, since he was arguing that intelligent behavior requires the ability to forecast modifications in the environment: he used finite state machines (also called automata) as evolving entities, trying to evolve individuals able to anticipate the next symbol in an input sequence provided to them, thus showing a predictive capability. In later years, the same technique was successfully used to solve several combinatorial problems.

The original algorithm proposed by Fogel considered a set of *P* finite state machines: each individual in the set was tested against a sequence of symbols in input, i.e., its environment. The predictive capability was mapped to a single numerical value called fitness through different payoff functions that considered a penalty for too complex machines. Individuals were then ranked according to their fitness values, and subsequently *P* new automata were added to the population. Offspring generation was accomplished by mutation, whose type and extent were regulated by given probability distributions, so each new individual was obtained by modifying one existing automaton. In the first version of the algorithm, each selected parent created exactly one offspring, but the same automaton could be selected multiple times as the parent of different new individuals. Finally, half of the population was preserved and half discarded, so that its size returned to *P*. Survivors were chosen at random, with a probability related to their fitness value. The selective pressure

in evolutionary programming is thus represented by the likeliness of a highly fit individual to be preserved in the next generation.

The steps described above were repeated until a specified number of generation had elapsed: at that moment, the best individual in the population was used to predict the actual next symbol, which was then added to the environment while the process restarted from the last population.

# 1.2.4 Evolution Strategies

Evolution strategies (ES) were proposed by Ingo Rechenberg and Hans-Paul Schwefel in the early 1960s [139] [128]. Originally developed as an optimization tool to solve practical problems, evolution strategies describe each individuals as a set of parameters, usually encoded as integer or real numbers. The mutation operator simultaneously modifies all parameters of a selected individual, with a high probability of inserting tiny alterations and a smaller probability of major modifications. On the other hand, several techniques are possible for the recombination operator: for example, copying a subset of parameters from each parent or computing an average of all the numbers. Interestingly, the very first experiment with evolution strategies featured a population of one individual and all random operations performed with a roll of six-sided dice.

A unique formalism was developed to describe the characteristics of evolution strategies. The Greek letter  $mu(\mu)$  commonly denotes the size of the population, while for the size of the offspring generated at each generation the Greek letter lambda  $(\lambda)$  is used. A  $(\mu + \lambda)$ -ES is an evolution strategy where the offspring is added to the current population before survivor selection for the next generation. In this case, a particularly good solution could survive throughout several generations, as it could happen in a steady-state genetic algorithm or in evolutionary programming. The label  $(\mu, \lambda)$ -ES, on the other hand, denotes an evolution strategy where the offspring completely replaces the current population before survivor selection. The latter approach has several similarities with a generational genetic algorithm or evolutionary programming, as the optimal solution may be discarded during the run. In a commonly used notation, the two approaches are called plus(+) and comma(,)respectively. These two terms spread in the evolutionary computation community, and in recent year they have been used in the description of various evolutionary algorithm, not necessarily related to evolution strategies. When comma selection is used,  $\mu < \lambda$  must hold. In almost all the implementations of evolution strategies, however, the size of the offspring is much larger than the size of the population at each step.

When the recombination operator is implemented, the number of parents required is denoted with the Greek letter  $rho(\rho)$ , and the algorithm with  $(\mu/\rho + \lambda)$ -ES. The number of parents is always smaller than the size of the population, i.e.,  $\rho < \mu$ .  $(\mu + 1)$ -ES are sometimes referred to as *steady-state evolution strategies*.

8 1 Introduction

An interesting approach, almost unique to evolution strategies, is *nesting*: instead of performing offspring generation with conventional operators, an evolution sub-strategy is started and its result is used as offspring for the main strategy. The inner strategy is in fact acting as a tool for local optimizations, and commonly it adopts parameters unrelated to those of the outer strategy. In different applications, this technique has been named *nested evolution strategies*, *hierarchical evolution strategies* and *meta evolution strategies*. An algorithm that exploits a sub-strategy running for  $\gamma$  generations is referred to as  $(\mu/\rho + (\mu/\rho + \lambda)^{\gamma})$ -ES, with  $\gamma$  is often called *isolation time*. A deeper nesting may be theoretically possible, but usually only one level of recursion is implemented. Such a technique is almost never used in evolutionary programming or genetic algorithms, but in rare cases has been successfully exploited in peculiar approaches [148].

Evolution strategies' offspring generation is mainly based on mutations: thus, different solution to determine the optimal amplitude of the perturbations were extensively explored during years of research. In real-valued search spaces, mutation is usually described as a random perturbation that follows a normal probability distribution centered on zero. In this way, small alterations are more probable than larger ones, while the variance may be used to tweak the average magnitude. This variance be evolved concurrently with individuals' parameters, and a dedicated variance may even be assigned to each parameter, since sometimes the same problem needs different amplitudes in different loci. In several implementations, this *variance vector* is modified using a fixed scheme, while the *object parameter vector*, i.e. the values that should be optimized, is modified using the variance vector: both vectors are then evolved concurrently as different parts of the same individual. This idea has been extended to take into account the correlation between optimal magnitudes of mutation, and modern evolution strategies often exploit a *covariance matrix*.

The capability to adapt to different problems is common to all evolutionary algorithms: thus, they can be sensibly called *adaptive*. When an evolutionary algorithm is able to adapt the mechanism of its adaptation, i.e., its internal parameters, is labeled as *self-adaptive*. Self-adapted parameters are sometimes called *endogenous*, from the term that describes hormones synthesized within an organism. Self-adaptation mechanisms have been exhaustively explored both in evolution strategies and evolutionary programming, and sometimes they appeared also in genetic algorithms.

From the 2000s there has been a growing interest in the use of evolution strategies as numerical optimization tools for continuous problems. Several versions of the most popular evolution strategies are freely available, with implementations ranging from general-purpose programming languages to commercial mathematical toolboxes, such as MatLab. Evolutionary programming also enjoyed a relatively widespread adoption as a numerical optimization tool, and the practical implementations of the two have mostly converged, even if the respective scientific communities remain deeply distinct.

This hybridization is not unique to evolution strategies and evolutionary programming. Ideas developed for one paradigm, if not directly applicable in other evolutionary algorithms, are at least a source of inspiration of the whole

community. The various original approaches may be too different to interbreed, but many key ideas are now shared, and a great number of intermediate algorithms, not easily classifiable, have been described over the years. The scope of genetic algorithm also broadened, and researchers applied them to problems with highly structured solutions, e.g. the traveling salesman problem, whose solution is a permutation of nodes in a graph. The term genetic algorithm, however, remained strongly linked to the idea of bit strings of fixed length.

# 1.2.5 Genetic Programming

Genetic programming (GP) is the last paradigm appeared in the field of evolutionary computation, in order of time. John Koza, who applied for a patent in 1989, described this approach and made it popular in the community. The goal of the methodology is to automatically create computer programs, applying neo-Darwinistic concepts as optimization techniques. The first version of genetic programming was developed in Lisp, an interpreted computer language that dates back to the end of the 1950s. One of the characteristics of Lips it the capability to handle fragments of code as data, making it possible for a program to build up subroutines before evaluating them. Except variables and constants, everything in Lisp is treated as a prefix expression: since the first individuals in genetic programming were blocks of Lisp code, they were also prefix expressions. While the flexibility of Lisp has its advantages, the language is plagued by a severe inefficiency: during the development of genetic programming, researchers moved to alternative solutions, mostly featuring compiled languages. Since the origin of this paradigm, actually, the need for computational power and the effort to acquire efficiency have been important factors in the advancement of research. In these later implementations, the difference between a program and an expression became more evident than in Lisp: genetic programming algorithms in literature tackle mainly expressions.

Individuals in genetic programming are almost always internally represented as trees, despite the differences in the computer languages adopted. In the simplest forms, leaves (terminal nodes) encode numbers, while internal nodes describe operations. Variables, functions and programming structures appear in more complex variations. Offspring may be generated via recombination or mutation: the former is modeled as a swap of sub-trees between parents; the latter appears only in recent implementations, and usually involves a random modification of the tree, the promotion of a sub-tree to a new individual or the collapse of a sub-tree to a single terminal node. The first versions of genetic programming featured huge populations and made an extensive use of recombination, with a scarce presence of mutations: the substitution of a sub-tree may introduce a significant amount of novelty, since it is a potentially disruptive operation; while populations of significant size ensure that all possible symbols are available in the gene pool.

In recent years, many researchers have been attracted by the genetic programming paradigm. Various topics have been tackled, including representation of individuals,

10 1 Introduction

behavior of selection in numerous populations, techniques to avoid excessive growth of trees and different types of initializations. Results of these research lines has been used as test benches for practical techniques, or for foundation of theoretical studies. The genetic programming paradigm stimulated and brought new ideas to the whole evolutionary computation community.

# Chapter 2 Resources

#### 2.1 Books

- T. Back, D. Fogel, Z. Michalewicz, *Handbook of Evolutionary Computation*, Oxford University Press, 1997

- M. Bushnell, V. Agrawal, Essentials of Electronic Testing for Digital, Memory, and Mixed-Signal VLSI Circuits, Springer, 2000

- D. Dumitrescu, B. Lazzerini, L.C. Jain, A. Dumitrescu, *Evolutionary Computation*, CRC Press, 2000

- D. Fogel, Evolutionary Computation: Toward a New Philosophy of Machine Intelligence, Wiley, 2005

- D. Gizopoulos (Ed.), Advances in Electronic Testing, Springer, 2006

- D. Gizopoulos, A. Paschalis, A., T. Zorian, *Embedded Processor-Based Self-Test*, Springer, 2004

- E. Sanchez, M. Schillaci, G. Squillero, *Evolutionary Optimization: the μGP toolkit*, Springer, 2011

- J. D. Kraus, Antennas, McGraw-Hill Companies, 1988

- J. W. Gardner, P. N. Bartlett, *Electronic Noses: Principles and Applications*, Oxford University Press, 1999

- J. O. Smith III, *Introduction to Digital Filters: with Audio Applications*, W3K Publishing, 2007

12 2 Resources

# 2.2 Journals

### Genetic Programming and Evolvable Machines

http://www.springer.com/computer/ai/journal/10710

#### IEEE Design and Test of Computers

http://www.computer.org/portal/web/dt

#### **IEEE Transactions on Computers**

http://www.computer.org/portal/web/tc

# IEEE Transactions on Evolutionary Computation

http://www.ieee-cis.org/pubs/tec/

### IEEE Transactions on Very Large Scale Integration Systems

http://www.ieee.org

#### Journal of Electronic Testing

http://www.springer.com/engineering/circuits+%26+systems/journal/10836

# 2.3 International Conferences and Workshops

CEC: Congress on Evolutionary Computation <website changes every year>

#### DAC: Design Automation Conference

http://www.dac.com/

# DATE: Design Automation & Test in Europe

http://www.date-conference.com/

#### EvoSTAR: The main European events on Evolutionary Computation

http://www.evostar.org/

# GECCO: Genetic and Evolutionary Computation Conference

http://www.sigevo.org/gecco-XXXX/ (changes every year)

#### ITC: International Test Conference

http://www.itctestweek.org/about

#### 2.4 Software

### Eureqa

http://creativemachines.cornell.edu/eureqa\_download

#### MicroGP ( $\mu$ GP)

http://ugp3.sourceforge.net/

# **Starting Points on the Web**

```

http://www.genetic-programming.com/

```

http://www.kesinternational.net/

# 2.5 Suggested Readings on Natural Evolution and Biology

- C. Darwin, On the Origin of Species by Means of Natural Selection, or the Preservation of Favoured Races in the Struggle for Life, John Murray, 1859

- R. Dawkins, The Selfish Gene, Oxford University Press, 1976

- R. Dawkins, The Extended Phenotype, Oxford University Press, 1982

- S. Gould, Ever Since Darwin, W. W. Norton & Company Incorporated, 1977

- S. Gould, Punctuated Equilibrium, Belknap Press of Harvard University Press, 2007

# Part I Prototype-Based Validation Problems

# **Chapter 3 Automatic Software Verification**

The complexity of cell phones is continually increasing, with regards to both hardware and software parts. As many complex devices, their components are usually designed and verified separately by specialized teams of engineers and programmers. However, even if each isolated part is working flawlessly, it often happens that bugs in one software application arise due to the interaction with other modules. Those software misbehaviors become particularly critical when they affect the residual battery life, causing power dissipation. An automatic approach to detect power-affecting software defects is proposed. The approach is intended to be part of a qualifying verification plan and complete human expertise. Motorola, always at the forefront of researching innovations in the product development chain, experimented the approach on a mobile phone prototype during a partnership with Politecnico di Torino. Software errors unrevealed by all human-designed tests have been detected by the proposed framework, two out of three critical from the power consumption point of view, thus enabling Motorola to further improve its verification plans. Details of the tests and experimental results are reported.

#### 3.1 Introduction

Verifying all the software running on a given apparatus is a complex problem, especially when the system under test is a mobile device, in which a software misbehavior can affect residual battery life. Traditional software verification techniques are often unable to work on a great number of applications at the same time, and since some software modules could be developed by third parties, verification engineers could not always have access to all data needed for the verification process. Evolutionary computation techniques proved able to tackle difficult problems with relevant degrees of success [43], even if some data of the problem is not completely known. Specialized literature routinely reports techniques that deliver high-return human-competitive machine intelligence simply starting from a high-level statement of what needs to be done and subsequently solving the problem without further need

of human intervention [86]. In the industrial world, however, the majority of existing processes employ no machine intelligence techniques, even if such approaches have been reported able to provide reliable results when facing complex problems.

The resistance in incorporating evolutionary computation in industrial processes may arise from the lack of experts with deep knowledge in both the machine intelligence and the industrial field. Automatic methodologies are perceived as scarcely controllable, and computational-intelligence techniques are regarded as "black magic", able to deliver impressive results sometimes, but definitely not reliable. In recent years, however, the interest of the industrial world towards automatic techniques has been steadily growing and some computational intelligence techniques have been successfully applied to some niche cases (e. g. credit card fraud detection performed by neural networks [19]).

An automatic approach based on an Evolutionary Algorithm (EA) is proposed, to add content to a human-designed verification plan for a mobile phone software system. The approach makes use of the EA to effectively [85] generate stimuli for a physical prototype of a cell phone, running simulations whose results are fed back to the EA and used to generate new stimuli. Data obtained from the simulations include physical measures and logs of all running applications. To explore effectively the solutions space, measures extracted from the prototype are integrated with data obtained from a model of the phone dynamically derived from simulation results.

Three different software misbehaviors, previously unrevealed by human-designed tests, are detected by the proposed approach. Incorporating this procedure in an existing set of tests allows Motorola [109] to further improve the effectiveness of qualifying verification plans. Preliminary results have been presented in [63] and [64].

# 3.2 Background

#### 3.2.1 Mobile Phones

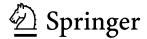

Since 1997, the mobile devices market has been steadily growing. Market researches projected that shipments of cell phones exceeded 1 billion units in 2009, so that mobile phones could become the most common consumer electronic device on the planet. Esteems from Gartner, shown in Fig. 3.1, predicted that there will be 2.6 billion mobile phones in use by the end of 2009 [161].

A great share of mobile devices sold nowadays is represented by the so-called smartphones, able to offer PC-like functionalities at the expense of an ever-growing complexity at both hardware and software level. Devices support more and more functions, running a great number of different applications: hardware miniaturization improves constantly, and thus battery life and power consumption related issues become more and more critical [36]. Thus, prediction of battery life [55] and

3.2 Background 19

Fig. 3.1 Projection of cell phone sales by Gartner

improvement of energy supplies for mobile devices [90] [129] are research topics of great interest with significant contributions in literature.

Since the introduction of smartphones, the increasing number of applications run by mobile systems led to a great number of possible misbehaviors caused by software bugs. The most displeasing errors for the user are obviously those related to battery life, and in particular incorrect behaviors happening during the state where the cell phone consumes a minimal quantity of energy, called deep sleep. A mobile device enters deep sleep mode when it is left idle for a given amount of time or when a certain signal is given by the user (e. g. when the cap of a mobile phone is closed). Errors that arise in deep sleep can completely exhaust the battery of a cell phone while the user is oblivious to what is happening: a customer could find out that her mobile phone is discharged even if it was fully charged a few hours before.

# 3.2.2 Verification Techniques

Verification is the process that aims at guaranteeing the correctness of the design. Verification techniques exploit different paradigms, but, roughly speaking, it is possible to state that almost all can be classified either as formal or simulation-based. The former exploits mathematical methodologies to prove the correctness of the design with respect to a formal specification or property, while the latter is based on a simulation that aims at uncovering incorrect behaviors. Exploiting formal methods allows to verify the module with all possible inputs passing through all possible states. Therefore, these techniques in theory guarantee the highest levels of confidence in the correctness of the results, but when a formal method fails to prove a property, nothing can be determined about it, not even with a low amount of confidence. The human and computational effort required to apply formal verification

techniques, severely limit their applicability. Such methods, as a result, are applied in the industrial field only when facing few software or hardware modules, when validation task can be significantly constrained by boundary conditions or when oversimplified models are employed, thus significantly impairing the confidence of the results [50]. Systems composed of a great number of modules usually cannot be tackled by formal verification, due to the growth of complexity of these techniques. To maximize their efficiency, formal verification techniques are usually applied to the source code of the model description. However, in the mobile phone prototyping arena, the very first time a mobile phone prototype is implemented, some applications running on the phone are developed by third parties and their original code is often non accessible [3]. Therefore, it is not always feasible to exploit formal verification techniques during the verification plan of a mobile phone.

Simulation-based techniques rely on the generation of a set of stimuli able to thoroughly excite the device under verification: the stimuli set is simulated exploiting the considered module. Subsequently, all data obtained from the simulation is gathered and analyzed, aiming to unearth misbehaviors by comparison with the expected results. A simulation-based approach may be able to demonstrate the presence of a bug even in frameworks with a great number of applications or hardware modules running simultaneously, but will never be able to prove its absence. Indeed, verification engineers may assume that no bugs exist depending on the level of confidence related to the quality of the simulated test set. Stimuli sets can be applied to either a physical prototype or a simulable model of the device. Both approaches have advantages and disadvantages: while models often describe only some aspects of the system, they may allow verification engineers to control all details of the simulation and gather a large amount of information. On the other hand, a physical prototype may be more difficult to control, but results of the physical emulation are completely unbiased, and the computational time required to apply the stimuli set is lower compared to model simulation. Either using a model or a prototype, the generation of a qualifying set of stimuli is the key problem with simulation-based techniques.

As mentioned by Piziali in [122], the real success of a simulation-based verification process relies on the adequacy of the initial verification route-map, called functional verification plan. A verification plan must define important test cases targeting specific functions of the design, and it must also describe a specific set of stimuli to apply to the design model. The verification plan can also allocate specific tasks to specialized engineers.

One of the most important tasks of the verification plan is the generation of the stimuli that thoroughly exercise the device, obeying the directives defined in the route-map.

According to the defined plan, different methodologies may be used to properly generate verification stimuli sets, for example deterministic, pseudo-random, or constrained-random. The generation of stimuli can be driven by past experience of the verification engineers or by exploiting the extracted information of a given model of the system. The latter technique is called model-based testing, and for complex software systems it is still an actively evolving field [52].

3.2 Background 21

A typical verification plan usually starts by tackling corner cases with hand-written tests. The verification stimuli set is then improved by adding information automatically generated exploiting simulation-based approaches. At last, the automatically generated test set requires an additional analysis by the verification engineers. Tests developed in such a way require a considerable amount of expertise related to the device under test, they are not always portable, and their preparation is time-consuming and expensive.

Completely automated approaches for stimuli generation can follow several methodologies: constrained-random generation, sometimes simply referred to as random or pseudo-random test generation, and feedback-based generation are the most widely adopted.

In a constrained-random test generation [69], random stimuli set are created by following a constrained generation process. Templates and constraints previously specified are exploited to define the structure of each stimuli fragment which is then randomized. When targeting real designs, such techniques have been proved to be really challenging, and are outperformed by feedback-based approaches [114].

Feedback-based approaches initially apply stimuli to the system, check the output produced and obtain information that is eventually exploited to produce new, and probably better, stimuli. This process is repeated, generating a set of stimuli able to stress the system very effectively: considerable proofs support the predominance of feedback-based techniques over other simulation-based ones [145]. Another important advantage of feedback-based approaches is that at the end of the process, a very compact set of data is produced: even though a large number of stimuli is simulated, most of the results are fed back to the system and exploited internally. Thus, verification engineers are required to analyze smaller quantities of information.

In a typical hand-written test for a new mobile phone, the phone is woken up from deep sleep mode, a sequence of key pressures is given in input to it, it is turned back to deep sleep and power consumption is eventually determined. Frequently, these sequences of keys mimic actions that will be likely performed on the phone, e. g. starting a video call, inserting a new field in the address book, etc. Once a number of similar devised tests are completed, a test set is created thanks to an automated approach that generates stimuli similarly structured to the hand-written ones.

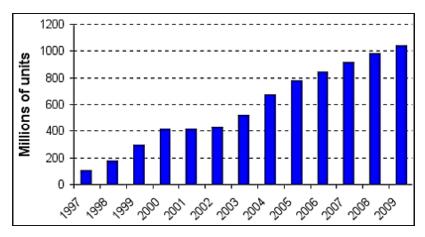

**Fig. 3.2** Flowchart of a generic EA. During the evaluation step, individuals with lowest values of goodness are removed from the population.

Verification plans focused on simulation-based techniques are developed by industries to provide a set of stimuli able to excite completely the functionalities of the device under verification, consequently locating possible software bugs. When tackling the software of mobile phones, first of all verification engineers perform module-oriented verification procedures on single software application: this process is often developed separately for each component. In a second step, different applications are run at the same time, studying reciprocal influences among the modules and performing new verification tests on the whole system. In a third step, technical experts use the device, trying to locate weaknesses of the complete framework. During each step, verification engineers may rely on techniques available in literature on a single phase.

Among feedback-based techniques, Evolutionary Algorithms (EAs) are stochastic search techniques that mimic the metaphor of natural biological evolution to solve optimization problems [107]. Initially conceived at the end of 1960s, the term EAs now embraces genetic algorithms, evolutionary strategies, evolutionary programming, and genetic programming. Scientific literature reports several success stories in different domains, for instance [131].

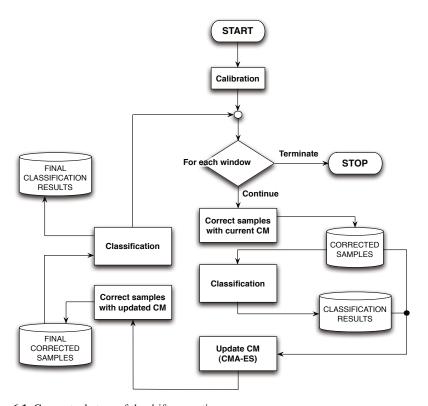

Despite great differences, all EAs have many properties in common. EAs operate on a population of individuals; underlying each individual encodes a possible solution for the given problem. The goodness of every solution is expressed by a numeric value called fitness, usually obtained through an evaluator able to estimate how well the solution performs when applied to the problem. An evolutionary step, called generation, always consists of two phases: a stochastic one where some of the best individuals are chosen at random to generate new solutions; and a deterministic one, where solutions are ranked by their fitness and the worst ones are removed from the population. The process is then repeated until a user-defined stop condition is met. Fig. 3.2 shows a classical flow for an EA. When facing verification problems, stimuli created by an EA explore the solution space very efficiently. Moreover, the solutions found by EAs are somewhat very different from, and thus complementary to, human-made solutions [97].

# 3.3 Proposed Approach

The objective of the proposed approach is to find a set of stimuli able to detect errors triggered by the interaction of software applications on a mobile phone by stressing the functionalities of all the modules as much as possible. The approach is feedback-based, driven by an EA that evolves a population of candidate stimuli, coded as sequences of key pressures and pauses, similar to hand-written tests devised by expert engineers. The approach is also model-based: a finite-state machine (FSM) representing the system under verification is exploited to extract measures for the goodness of each solution. The FSM is automatically generated from scratch thanks to the data obtained by running simulations with the stimuli as an input to a physical prototype of the phone itself. The model supplies information on the

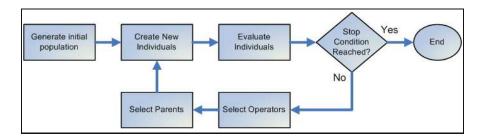

number of different applications' features activated by each stimulus; this data is later used to assign a value to the stimulus, expressing its goodness. Fig. 3.3 shows a schema of the proposed framework: the EA manages a population of individuals that map stimuli. Such stimuli are evaluated by the model dynamically extracted from the physical device.

Fig. 3.3 Schema of the proposed framework

#### 3.3.1 Model

The device under verification is modeled with a FSM, where each state defines a situation in which all active software modules are waiting for new inputs. A transition is a series of inputs that connect a state to another, turning on/arresting different applications or exciting some functionalities of the active ones. The FSM is exploited to evaluate the number of distinct states traversed and the transitions activated during the simulation of a stimulus [127].

Creating a complete model of all the software running on the mobile phone with the classical methodologies of software engineering would be impractical, requiring an excessive amount of time: the source code of each software module on the device should be provided and analyzed. Since some applications are developed by third parties, not all the software modules' source code is obtainable, thus critical data to build a complete model is missing. On the contrary, the FSM in the proposed framework is created as the simulations go on, and each time a new state is discovered the model is dynamically updated. Since this approach does not rely on a-priori knowledge, errors that could occur in the model-building phase are avoided.

The Operating System (OS) and most applications on mobile phones can run in a test mode where they write a log of their execution to ease the debugging process. By reading system messages recording applications starting and closing, called events in the following, it is possible to create a list of states. Each state is identified by a status word, obtained by parsing the debug logs. Every time an event is raised or a new feature of an active application is activated, the debug log register the changes. When all applications active on the phone are waiting for new input, the status word is collected by parsing the logs.

Starting with an empty FSM, new states and transitions are added each time a new status word is discovered. Old status words are stored, thus the framework can add transitions returning to states already known. Since the proposed framework makes mainly use of the number of different transitions fired, it does not require the supporting model to be complete or perfect.