## **SPRINGER BRIEFS IN APPLIED SCIENCES AND TECHNOLOGY** • COMPUTATIONAL INTELLIGENCE

Frederico A. E. Rocha Ricardo M. F. Martins Nuno C. C. Lourenço Nuno C. G. Horta

Electronic Design

Automation of Analog

ICs Combining Gradient

Models with MultiObjective Evolutionary

Algorithms

# **SpringerBriefs in Applied Sciences** and Technology

Computational Intelligence

Series Editor

Janusz Kacprzyk

For further volumes: http://www.springer.com/series/10618

Frederico A. E. Rocha · Ricardo M. F. Martins Nuno C. C. Lourenço · Nuno C. G. Horta

Electronic Design

Automation of Analog ICs

Combining Gradient Models

with Multi-Objective

Evolutionary Algorithms

Frederico A. E. Rocha Instituto de Telecomunicações Instituto Superior Técnico Lisbon Portugal

Ricardo M. F. Martins Instituto de Telecomunicações Instituto Superior Técnico Lisbon Portugal Nuno C. C. Lourenço Instituto de Telecomunicações Instituto Superior Técnico Lisbon Portugal

Nuno C. G. Horta Instituto de Telecomunicações Instituto Superior Técnico Lisbon Portugal

ISSN 2191-530X ISSN 2191-5318 (electronic) ISBN 978-3-319-02188-1 ISBN 978-3-319-02189-8 (eBook) DOI 10.1007/978-3-319-02189-8

Springer Cham Heidelberg New York Dordrecht London

Library of Congress Control Number: 2013947787

#### © The Author(s) 2014

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed. Exempted from this legal reservation are brief excerpts in connection with reviews or scholarly analysis or material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work. Duplication of this publication or parts thereof is permitted only under the provisions of the Copyright Law of the Publisher's location, in its current version, and permission for use must always be obtained from Springer. Permissions for use may be obtained through RightsLink at the Copyright Clearance Center. Violations are liable to prosecution under the respective Copyright Law. The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

While the advice and information in this book are believed to be true and accurate at the date of publication, neither the authors nor the editors nor the publisher can accept any legal responsibility for any errors or omissions that may be made. The publisher makes no warranty, express or implied, with respect to the material contained herein.

Printed on acid-free paper

Springer is part of Springer Science+Business Media (www.springer.com)

To my parents and Susana

Frederico Rocha

To Nádia and Daniela

Ricardo Martins

To Alina

Nuno Lourenço

To Carla, João and Tiago

Nuno Horta

## **Preface**

In the last years, the world has observed the increasing complexity of integrated circuits (ICs), strongly triggered by the proliferation of consumer electronic devices. The design of complex system on a chip (SoC) is widespread in multimedia and communication applications, where the analog and mixed-signal (AMS) blocks are integrated together with digital circuitry. However, the analog blocks development cycles are larger when compared to the digital counterpart. The two main reasons identified are the lack of effective computer-aided-design (CAD) tools for electronic design automation (EDA), and that analog circuits are being integrated using technologies optimized for digital circuits. Given the economic pressure for high-quality yet cheap electronics and challenging time-to-market constraints, there is an urgent need for CAD tools that increase the analog designers' productivity and improve the quality of resulting ICs.

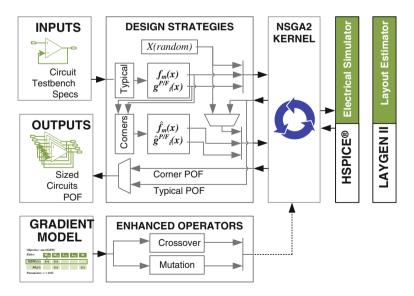

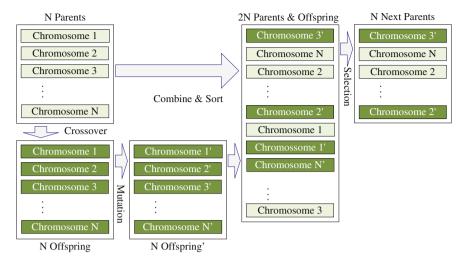

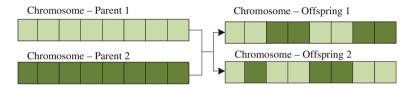

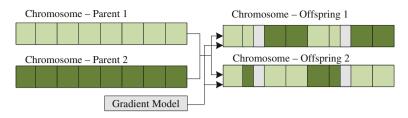

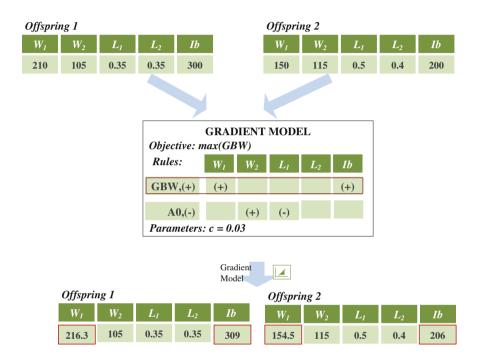

The work presented in this book belongs to the scientific area of electronic design automation and addresses the circuit-level sizing and optimization of analog ICs. Particularly, an innovative approach to enhance a state-of-the-art layout-aware analog IC circuit-level optimizer, by embedding statistical knowledge from an automatically generated gradient model into the multi-objective multi-constraint optimization kernel based on a modified NSGA-II algorithm. The gradient model is automatically generated by, first, using a design of experiments (DOE) approach with two alternative sampling strategies, the full factorial design and the fractional factorial design, which define the samples that will be accurately evaluated using a circuit simulator (e.g., HSPICE®), second, extracting and ranking the contributions of each design variable to each performance measure or objective, and, finally, building the model based on series of gradient rules. The gradient model is then embedded into the modified NSGA-II optimization kernel, by acting on the mutation operator. The approach was validated with typical analog circuit structures for an industry standard 0.13 µm integration process, showing that, by enhancing the circuit sizing evolutionary kernel with the gradient model, the optimal solutions are achieved, considerably, faster and with identical or superior accuracy.

The book is organized into six chapters.

Chapter 1 gives a brief introduction to the area of analog IC design automation, with special emphasis to the design flow hierarchy and the circuit-level sizing and optimization.

viii Preface

Chapter 2 presents an extensive state-of-the-art review on analog integrated circuit (IC) design automation tools applied to the circuit-level synthesis problem. Particularly, several circuit-level sizing techniques are sketched and compared, and then, different model-based optimization approaches are outlined.

Chapter 3 illustrates the Gradient Model generation. The circuit is first sampled using either the full factorial or the fractional factorial Design of Experiments (DOE) techniques, and then the main effect is used to extract the gradient rules which compose the Gradient Model.

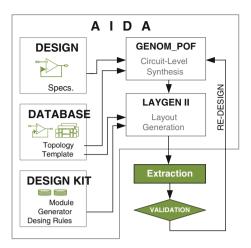

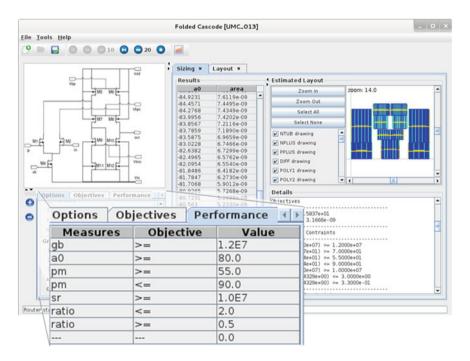

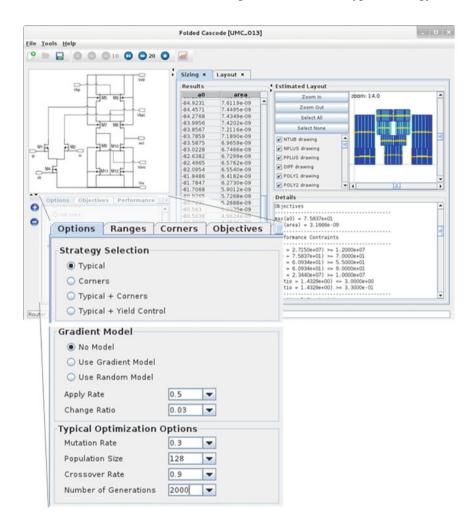

Chapter 4 describes how the Gradient Model is used to enhance the circuit-level optimization tool, GENOM-POF. GENOM-POF is part of the Analog Integrated circuit Design Automation environment (AIDA), developed in the Integrated Circuits Group at Instituto de Telecomunicações, Lisboa, Portugal. The integration of the gradient model includes both embedding the model in the optimization kernel, and add the model's setup options to AIDA's graphical user interface (GUI), which allows the visualization of the results and the configuration of the parameters, such as the objectives, constraints and input variables, ranges, etc.

Chapter 5 illustrates the application of the proposed methodology to practical examples. The framework of the proposed methodology for the automatic generation of analog ICs layout has been coded in JAVA and is running, for the presented examples, on an Intel<sup>®</sup> Core<sup>TM</sup> 2 Quad CPU 2.4 GHz with 6 GB of RAM.

Chapter 6 summarizes the provided book and supplies the respective conclusion and future work.

Frederico A. E. Rocha Ricardo M. F. Martins Nuno C. C. Lourenço Nuno C. G. Horta

## **Contents**

| 1 | Intr | roduction                                                 | 1  |

|---|------|-----------------------------------------------------------|----|

|   | 1.1  | Analog IC Design                                          | 1  |

|   | 1.2  | The Analog IC Design Automation Flow                      | 3  |

|   | 1.3  | Research Contributions                                    | 4  |

|   | 1.4  | Conclusions                                               | 5  |

|   | Refe | erences                                                   | 6  |

| 2 | Stat | e-of-the-Art on Automatic Analog IC Sizing                | 7  |

|   | 2.1  | Automatic Circuit-Level Sizing                            | 7  |

|   |      | 2.1.1 Knowledge-Based Sizing                              | 8  |

|   |      | 2.1.2 Optimization-Based Sizing                           | 9  |

|   | 2.2  | Motivation for Model-Based Optimization                   | 12 |

|   | 2.3  | Conclusions                                               | 18 |

|   | Refe | erences                                                   | 19 |

| 3 | Gra  | dient Model Generation                                    | 23 |

|   | 3.1  | Overview of Design of Experiments (DOE)                   | 23 |

|   | 3.2  |                                                           | 25 |

|   |      | 3.2.1 Characterization and Construction of the DOE Matrix | 25 |

|   |      | 3.2.2 Analysis of the DOE Matrix                          | 27 |

|   | 3.3  |                                                           | 29 |

|   |      | 3.3.1 Characterization and Construction of the DOE Matrix | 29 |

|   |      | 3.3.2 Analysis of the DOE Matrix                          | 29 |

|   | 3.4  |                                                           | 30 |

|   | 3.5  | Conclusions                                               | 33 |

|   | Refe | erences                                                   | 33 |

| 4 | Enh  | nanced AIDA's Circuit-Level Optimization Kernel           | 35 |

|   | 4.1  |                                                           | 35 |

|   |      | 4.1.1 Inputs                                              | 37 |

|   |      |                                                           | 38 |

|   |      | 1                                                         | 30 |

x Contents

|   | 4.2  | Integration of the Gradient Model in the Optimization        |   |

|---|------|--------------------------------------------------------------|---|

|   |      | Kernel                                                       | 0 |

|   |      | 4.2.1 Gradient Model Applied to the Crossover Operator 4     | 1 |

|   |      | 4.2.2 Gradient Model Applied to the Mutation Operator 4      | 2 |

|   | 4.3  | Graphical User Interface (GUI)                               | 5 |

|   | 4.4  | Conclusions                                                  | 9 |

|   | Refe | ences                                                        | 9 |

| 5 | Resi | ts                                                           | 1 |

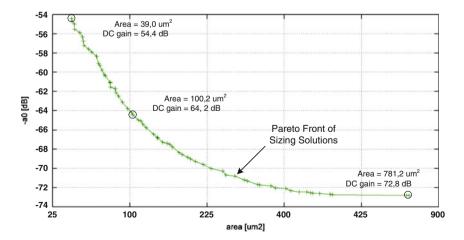

|   | 5.1  | POFs Analysis                                                | 1 |

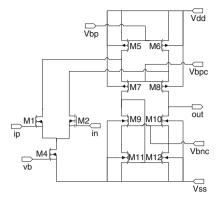

|   | 5.2  | Circuit Under Test: Single-Ended Folded Cascode Amplifier 5. | 3 |

|   | 5.3  | Case Study I: 15 Input Variables                             | 4 |

|   |      | 5.3.1 GENOM-POF                                              | 4 |

|   |      | 5.3.2 GENOM-POFGM                                            | 6 |

|   |      | 5.3.3 Random Model 5                                         | 8 |

|   |      | 5.3.4 Comparison of Different Optimization/Sizing            |   |

|   |      | Approaches                                                   | 9 |

|   | 5.4  | Case Study II: 12 Input Variables 6                          | 1 |

|   |      | 5.4.1 GENOM-POF                                              | 2 |

|   |      | 5.4.2 GENOM-POFGM                                            | 3 |

|   |      | 5.4.3 Comparison of Different Optimization/Sizing            | 2 |

|   |      | Approaches                                                   | _ |

|   | 5.5  | Conclusions                                                  | _ |

|   | Refe | ence                                                         | b |

| 6 |      | lusions and Future Work                                      |   |

|   | 6.1  | Conclusions                                                  |   |

|   | 6.2  | Future Work                                                  |   |

|   | Refe | ence                                                         | 9 |

## **Abbreviations**

AMS Analog and Mixed-Signal CAD Computer Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

DOE Design of Experiments

DSP Digital Signal Processing

EDA Electronic Design Automation

FFNN Feed Forward Neural Networks

GA Genetic Algorithm

GP Geometrical Programming GUI Graphical User Interface

IC Integrated Circuit

MARS Multivariate Adaptive Regression Splines NSGA Nondominated Sorting Genetic Algorithm PRSA Parallel Re-combinative Simulated Annealing

POF Pareto Optimal Front

PVT Process Voltage Temperature

RF Radio Frequency

SA Simulated Annealing

SoC System-on-a-Chip

SVM Support Vector Machine

VLSI Very Large-Scale Integration

## Chapter 1 Introduction

**Abstract** This chapter presents a brief introduction to analog integrated circuits (ICs) design and to the area of analog IC design automation. First, the analog IC design problem is presented, that led to the research in this area, then, the traditional analog design flow is sketched and, finally, the features of the proposed methodology to enhance the circuit-sizing task are outlined.

**Keywords** Analog IC design • Circuit sizing • Gradient rules • Electronic design automation • Computer-aided-design

#### 1.1 Analog IC Design

In the last decades, Very Large Scale Integration (VLSI) technologies have been widely improved, allowing the proliferation of consumer electronics and enabling the growth of integrated circuits (IC) market from \$10 billion in 1980 to over \$300 billion in 2013 [1]. IC designers are building systems that are increasingly more complex and integrated. The need of new functionalities, smaller devices, longer battery life, e.g., more power efficiency, less production and integration costs, and less design cost makes the design of electronic systems a truly challenging task, which must be completed within strict time-to-market constraints.

Although most of the functionalities in a modern electronic system are implemented using digital and digital signal processing (DSP) circuitry, analog and radio frequency (RF) circuitry, being essentially the link between digital circuitry and the continuous-valued external world, is integrated in the same chip. In such systems on a chip (SoC), the analog part occupies only about 10 % of the circuit area, however, the development time of analog blocks is considerably higher when compared to the development time of the digital part. The three main reasons identified for the larger development time of analog blocks are: the lack of effective Computer Aided Design (CAD) tools for Electronic Design Automation (EDA); analog circuits are being integrated using technologies optimized for

2 1 Introduction

digital circuits; and, analog blocks are difficult to reuse because they are more sensitive to environmental and process variations than its digital counterpart [2].

In digital IC design, several EDA tools and design methodologies are available that help the designers keeping up with the new capabilities offered by the technology processes. By its part, electrical simulators are the only analog design automation tool really established, despite the algorithms and techniques introduced in the last 25 years [3]. Due to the lack of automation, designers keep exploring the solution space almost manually. This method causes long design cycles, and allied to the non-reusable nature of analog IC, makes analog IC design a cumbersome task.

Designers have been replacing functions of analog circuits for digital processing whenever possible; however, there are some typical blocks that are appointed as remaining forever analog, such as [4]:

- On the input side of a system, the signals of a sensor, microphone or antenna have to be detected or received, amplified and filtered, to enable digitalization with good signal-to-noise and distortion ratio. Typical applications of these circuits are in sensor interfaces, telecommunication receivers or sound recording;

- Mixed-signal circuits like sample-and-hold, analog-to-digital converters, phase-locked loops and frequency synthesizers. These blocks provide the interface between the input/output of a system and digital processing parts of a SoC;

- On the output side of a system, the signal from digital processing must be converted and strengthened to analog so that the signal achieves the output with low distortion;

- Voltage/current reference circuits and crystal oscillators offer stable and absolute references for the sample-and-hold, analog-to-digital converters, phase-locked loops and frequency synthesizers;

The developments on the IC industry enabled the design of extremely complex Analog and Mixed-Signal (AMS) systems, which are established in telecommunications, medical and multimedia applications. To increase the performance of the ICs, i.e., enhance the functionalities but with lower power consumption, there is an exponential increase in the number of devices contained in a IC, as described by Moore's law. This means that the designers deal with the IC projects containing billions of transistors, under extreme competitive market conditions.

Despite the developments in the recent years, analog design automation tools and methodologies are still far from achieving a mature state, as there is no automation tool really established to support the analog design flow. Today's analog design is supported by circuit simulators, layout editing environments and verification tools, however the design cycle for AMS ICs is still long and error-prone.

In order to understand the automation of analog IC design, the steps in the design flow must be clear. After this brief introduction to the analog IC design problem, the systematic approach to the analog design automation flow [4], which intends to ease design automation, is covered in the next section.

#### 1.2 The Analog IC Design Automation Flow

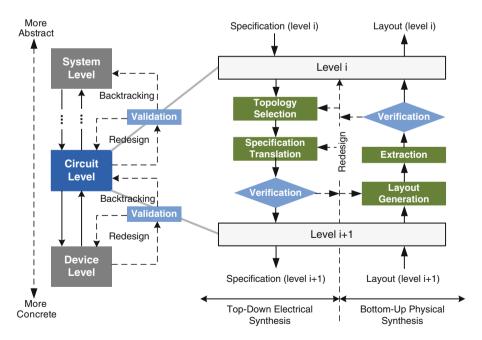

A typical and well accepted design flow for AMS ICs is presented in Fig. 1.1. This design flow consists of a series of top-down topology selection and specification translation steps, repeated from system level to the device level, and bottom-up layout generation, extraction and verification steps. Adopting a hierarchical top-down design methodology is possible to perform system architectural exploration, obtaining a better overall system optimization at a higher abstraction level before starting more detailed implementations at the device level. Thus, problems are found early in the design flow and, as a result, design have a higher chance of first-time success, with fewer or no overall time consuming redesign iterations.

On the top-down path, the topology selection is the process where a set of blocks and the connections between them in defined in order to implement the input specifications of the current hierarchy level. In the specification translation task, the higher-level specifications are translated in the specifications for each of the blocks. Block specifications may be the definition of the Gain and bandwidth for an amplifier, or the sizes of the transistors, depending of the models used in that abstraction level. The sizing is then verified to ensure the fulfillment of the input specifications.

At this point, the bottom-up flow is executed. Layout generation consists of creating the geometrical layout of the block under design at the lowest level in the

Fig. 1.1 System-level to device-level tasks of the analog IC design flow [4]

4 1 Introduction

design hierarchy, or place and route the layouts of the sub-blocks at higher levels. Typically, the desired layout for a circuit is the one that minimizes the total area, while reducing the parasitic effects in the circuit performance. Then, the layout needs to be verified, which is done with design rule checkers and the layout-versus-schematic tools. Finally, the layout parasitics are extracted and simulated to verify its impact on the overall performance of the circuit.

The ascension to higher hierarchical levels is done when no potential problems are detected at the lowest levels and the layout meet the target requirements. When the topmost level verification is complete, the system is designed and ready for fabrication.

#### 1.3 Research Contributions

This work addresses the problem of automatic specification translation at circuit level, also known as circuit sizing, where from the set of specifications, the designer finds out the sizes for the components, e.g., widths and lengths of the transistors, resistors, capacitors, etc. In the industry, this task is commonly done manually. The designers start by finding an approximate solution using simplified analytical expressions, and then, iteratively, adjust the solution until it meets all specifications, which sometimes can be very time consuming. The verification is done using circuit simulations that provide extra accuracy to the simplified (but treatable) equations used to derive the initial solution. The analog designer is aided by CAD frameworks comprised by many tools such as electrical simulators (e.g., Spectre<sup>®</sup> [5], HSPICE<sup>®</sup> [6]), layout editors (e.g., Virtuoso Layout Editor [5]), or tools for layout verification (e.g., CALIBRE [7], DIVA [5]). Despite its functionalities to support the manual IC design, these tools have limited automation options, and the ones available are usually overlooked by the majority of the designers. The time required to manually implement an analog project is usually of weeks or months, which is in opposition to the market pressure to accelerate the release of new and high performance ICs.

The designer's experience and knowledge are of the utmost importance, as they allow simplifications that speed up the design process, without compromising the quality of the solution, particularly, in the specification translation at the circuit-level, i.e., circuit sizing, the designer interacts manually with the available tools in order to achieve the project objectives, e.g., achieve the best set of device sizes, such that the circuit will meet the desired performance specifications (DC Gain, power, area, etc.). However, the search space of the objective function, which relates the design variables and the performance specifications of the circuit, is characterized by a complex multidimensional and irregular space, turning the manual search for the best solution into a cumbersome task.

In this research, GENOM-POF [8], which is a tool that performs a layout-aware circuit-level optimization that stems from Barros et al. GENOM [9–11], is enhanced by adding circuit specific knowledge that is automatically extracted using

machine learning techniques. The circuit sizing is done using the Nondominated Sorting Genetic Algorithm (NSGA-II) [12] for multi-objective multi-constraint optimization, which addresses robust design requirements by considering Process Voltage Temperature (PVT) corner analysis, where Mentor Graphics® ELDO<sup>TM</sup> and Synopsys® HSPICE® circuit simulators are used for accurate evaluation of the circuit performance. This work aims to demonstrate the advantage of embedding simple statistical models, representing design knowledge, into the optimization kernel in order to improve the performance of the sizing optimization. The main objectives for this work are detailed below:

- Create a simple model that is capable of extracting a set of gradients rules, automated and autonomously, i.e., without any human knowledge. This set of gradients rules extracted should contain knowledge about any analog circuit in study;

- Create a model of rules and integrate it with the mutation operator of the (NSGA-II), in order to improve its efficiency during the optimization of the analog circuit. Compare the performance of reference NSGA-II with the modified NSGA-II with the model of gradients, created in the previous paragraph, and verify potential benefits of this modification;

- Evaluate and analyze the robustness of the models created previously, through its application in highly complex analog circuits;

- Improve the quality of the achieved sizing solutions.

The designer provides the chosen topology for the project, the variables for optimization and their ranges, the specifications to be met and the objective functions, e.g., minimize area/power, maximize DC Gain, etc., the tool instantiates the components to size, ensures that specifications are met and performs the search objectives space for the optimum solutions. The modified GENOM-POF, produced within this work, aims at helping the designer in his/her circuits sizing task, not only by generating solutions faster but also by achieving better Pareto optimal solutions.

#### 1.4 Conclusions

The complexity of electronic systems imposes the use of CAD tools to support the design process. In digital IC design, several EDA tools and design methodologies are available that help the designers keeping up with the new capabilities offered by the technology, however the analog design automation tools strive to close the gap created due to the large investment made in the digital domain. This cause the manual exploration of the solution space, that in its turn creates expensively long designs that are difficult to reuse. In this context, the contributions of this research were presented, that aim to ease the efforts of analog designers to successfully complete this time-consuming task.

6 1 Introduction

#### References

B. McClean, IC market to top \$300 billion for first time in 2013 (2011), [Online]. Available: http://www.icinsights.com

- International Technology Roadmap for Semiconductors 2009 Edition (2009), [Online]. Available: http://public.itrs.net/

- G.G.E. Gielen, CAD tools for embedded analogue circuits in mixed-signal integrated systems on chip. IEEE Proc. Comput. Digit. Tech, 152(3), 317–332 (2005)

- G.G.E. Gielen, R.A. Rutenbar, Computer-aided design of analog and mixed-signal integrated circuits. Proc. IEEE, 88, 1825–1854 (2000)

- 5. Cadence Design Systems Inc, http://www.cadence.com

- 6. Synopsis, http://www.synopsys.com

- 7. Mentor Graphics, http://www.mentor.com

- 8. N. Lourenço, N. Horta, GENOM-POF: multi-objective evolutionary synthesis of analog ICs with corners validation, in *GECCO' 12: Proceedings of the fourteenth international conference on Genetic and evolutionary computation conference*, July 2012

- 9. M.F.M. Barros, J.M.C. Guilherme, N.C.G. Horta, Analog circuits and systems optimization based on evolutionary computation techniques (Springer, Berlin, 2010)

- M. Barros, J. Guilherme, N. Horta, Analog circuits optimization based on evolutionary computation techniques, Integr. VLSI J, 43(1), 136–155 (2010)

- 11. M. Barros, J. Guilherme, N. Horta, GA-SVM feasibility model and optimization kernel applied to analog IC design automation, in *Proceedings of ACM Great Lakes symposium on VLSI*, Stresa-Lago Maggiore, 2007

- 12. K. Deb, A. Pratap, S. Agarwal, T. Meyarivan, A fast and elitist multiobjective genetic algorithm: NSGA-II. Evol. Comput. IEEE Trans, 6(2), 182–197 (2002)

## Chapter 2 State-of-the-Art on Automatic Analog IC Sizing

Abstract In this chapter a state-of-the-art review on analog integrated circuit (IC) design automation tools applied to the specification translation problem is presented. Having the right topology for a given set of specifications is indispensable for a high performance design. An inadequate topology makes the design more difficult (or even impossible), and may require unnecessary resources, which is not acceptable in high performance designs. Once the topology is selected, the specifications for the overall block are translated to the specifications for the subblocks. The specifications are, in this way, passed through the hierarchy. At the lowest level, the translation reduces to circuit sizing, whereas at the higher levels it produce the sub-blocks performance parameters. In the last years, the scientific community proposed many techniques for the automation of the translation task; some apply only at circuit-level or only at system level, while others apply to both. In this study, several circuit-level sizing techniques are sketched and compared, and then, different model-based optimization approaches are outlined.

**Keywords** Analog IC design  $\cdot$  Automatic specification translation  $\cdot$  Knowledge-based sizing  $\cdot$  Optimization-based sizing  $\cdot$  Electronic design automation  $\cdot$  Computer-aided-design

## 2.1 Automatic Circuit-Level Sizing

The techniques for the automation of circuit-level IC sizing are classified into two main groups [1], knowledge-based and optimization-based based on the techniques used to address the problem.

#### 2.1.1 Knowledge-Based Sizing

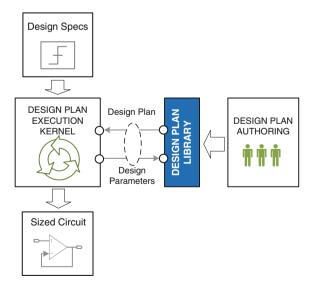

Early strategies tried to systematize the design by using a design plan derived from expert knowledge. In these methods, a pre-designed plan is built with design equations and a design strategy that produce the component sizes that meet the performances requirements. Figure 2.1 shows the strategy flow of knowledge-based sizing methodologies.

In IDAC [2], the designer expertise is captured in a design plan where all design equations are explicitly solved during the execution of the plan. Once the topology is selected, the plan is executed for the given specifications to produce a first design. The tool also included local optimization around this first design. IDAC includes a vast library of plans, featuring voltage references, opAmps, comparators, oscillators, DACs and ADCs. OASYS [3] uses the same overall strategy, but defines the circuits hierarchically, with a design plan for each sub-block. It also adds backtracking with design-reuse methodologies to recover from failed designs. OASYS was extended to include data converters in addition to the original operational amplifiers. TAGUS [4–6] applies the design plan successfully at system-level for CMOS data converters. A slightly different approach is found in BLADES [7], CAMP [8] or ISAID [9, 10], these tools capture the designer's knowledge in expert systems using artificial intelligence techniques.

The knowledge-based approach was applied with moderate success. The main advantage of this approach is the short execution time. On the other hand, deriving the design plan is hard and time-consuming, the design plan requires constant maintenance in order to keep it up to date with technological evolution, and the results are not optimal, suitable only as a first-cut-design.

**Fig. 2.1** Automatic circuit sizing: knowledge-based methodology

#### 2.1.2 Optimization-Based Sizing

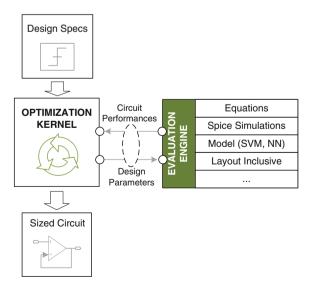

Aiming for optimality, the next generations of sizing tools apply optimization techniques to analog IC sizing. The optimization-based sizing can be classified into three major subclasses based on different techniques, namely, equation-based, simulation-based and model-based, which are addressed in the following subsections. A general flow of an optimization-based strategy can be found in Fig. 2.2.

#### 2.1.2.1 Equation-Based

The equation-based methods use analytic design equations to evaluate the circuit performance. Different optimization techniques are used, the optimization in OPASYN [11] is done using steepest descent, whereas in STAIC [12] it is used a successive solution refinements technique. OPTIMAN [13] uses simulated annealing (SA) applied to analytical models created automatically by ISAAC [14]. DONALD [15] is an interactive design space exploration tool that assists the designer during circuit sizing by automatic analytical manipulations of the circuit equations. Maulik et al. [16] define the sizing problem as a constrained nonlinear optimization problem using spice models and DC operating point constraints, solving it using sequential quadratic programming. In ASTRX/OBLX [17] a simulated annealing optimization is performed using and cost function defined by equations for dc operation point, and small signal Asymptotic Waveform Evaluation based simulation. This evaluation technique is also used in DARWIN [18].

In GPCAD [19] a posynomial circuit model is optimized using Geometrical Programming (GP), the execution time is in the order of few seconds, but the

**Fig. 2.2** Automatic circuit sizing: optimization-based methodology

general application of posynomial models is difficult and the time to derive the model for new circuits is still high. To reduce the long time spent in model development, automatic techniques were proposed (Gielen et al. in [20] provide a good overview on symbolic analysis applied to analog ICs). However, some design characteristics are still not easy to describe in analytical expressions with sufficient accuracy automatically. Kuo-Hsuan et al. [21] revisited the posynomial modeling recently, surpassing the accuracy issue by introducing an additional generation step, where local optimization using simulated annealing and a circuit simulator is performed. The same strategy is applied in FASY [22, 23] were analytical expressions are solved to generate an initial solution and a simulation-based optimization is performed to fine tune the solution.

The equation-based approaches are applied mostly at circuit-level, but some applications at system-level are also found. In SD-OPT [24] the optimal  $\Delta\Sigma$  modulator sub-blocks' specifications are derived using symbolic equations solved using stochastic optimization. The sub-blocks itself are then generated using simulation based techniques. Doboli et al. [25] applies genetic programming techniques to simultaneously derive the sub-blocks specifications, sub-block topology selection and transistor sizing. Matsukawa et al. [26] design  $\Delta\Sigma$  and pipeline analog to digital converters solving via convex optimization the equations that relate the performance of the converter to the size of the components.

The equation-based methods' strong point is the short evaluation time, making them, like the knowledge-based approaches, extremely suited to derive first-cut designs. The main drawback is that, despite the advances in symbolic analysis, not all design characteristics can be easily captured by analytic equations, in addition, the approximations introduced in the equations yield low accuracy designs especially for complex circuits.

#### 2.1.2.2 Simulation-Based

With the availability of computing resources simulation based optimization gained ground. In simulation-based sizing a circuit simulator, like SPICE [27], is used to evaluate the circuit. In DELIGTH.SPICE [28] the optimization algorithm (phase I-II-III method of feasible directions) is used to perform local design optimization around a user provided starting point. Kuo-Hsuan et al. [21] and FASY [22, 23] use equation-based techniques to derive an approximate solution, and then use simulation within a simulated annealing optimization kernel to optimize the design. Cheng et al. [29] use the transistor bias conditions to constrain the problem and instead of solving the circuit by finding transistor sizes, the problem is solved by finding the bias of the transistors. The transistor sizes are derived from the bias point using electric simulation.

FRIDGE [30] on the other hand aims for global optimality by using an annealing-like optimization without any restriction to the starting point. However, to restrict the dimensionality of the problem the user still must provide the range for the optimization variables. In MAELSTROM [31] and ANACONDA [32] the

evaluation time is reduced by a parallel mechanism that shares the evaluation load among multiple computers. Given the affinity evolutionary algorithms have with parallel implementations, it was the base technique chosen in MAELSTROM, however and because the success of simulated annealing is demonstrated in many implementations the authors option was to use parallel re-combinative simulated annealing (PRSA). In ANACONDA the approach is similar but instead of the PRSA it is applied a variation of pattern search algorithms, named by the authors as stochastic pattern search.

In order to account for layout induced effects and layout characteristics Castro-Lopez et al. [33] include the layout effects and parameters in the optimization. A template based layout generator is integrated in the optimization loop and the geometrical properties of the layout can be used as constraints or optimized. In addition layout parasitic are also extracted and used during the circuit's evaluation. They use simulated annealing followed by a deterministic method for fine-tuning to perform the optimization. The layout extraction is done using analytical equations and layout sampling or using 3-D geometric extraction models.

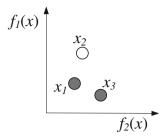

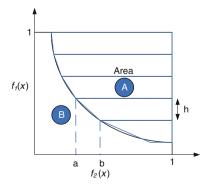

A different approach is taken in GENOM-POF [34], where a multi-objective strategy is applied through the use of evolutionary algorithms. The objectives and constraint functions are evaluated by HSPICE<sup>®</sup>. GENOM-POF outputs the Pareto optimal fronts (POF) with the tradeoff during the synthesis, so the designer has a wider range of solutions and choices to the problem of sizing.

Generality and easy-and-accurate model (the circuit netlist), are the strong points of simulation-based techniques. However, the execution time is large for complex circuits ( $\sim 100$  variables) and prohibitive at system level, and without the proper constraints the algorithm may not converge to a good result. Some heuristic schemes exist to automate the process of defining the constraints [35]. However, automatic constraint defining mechanisms are not integrated in sizing tools and their application is somewhat circuit class specific. Cheng et al. [29] uses manually derived DC point equations to limit the search space for the transistors dimensions.

Being the high execution time the weaker point of these methods, some techniques had been proposed to cope with it. Kuo-Hsuan et al. [21] used equation-based techniques to derive an approximate initial solution. Cheng et al. [29] instead of solving the circuit by finding transistor sizes, solved it by finding the bias of the transistors first, and then, the transistor sizes are derived from the bias point using electric simulation. In MAELSTROM [31] and ANACONDA [32] the evaluation time is reduced by a parallel mechanism that shares the evaluation load among multiple computers.

#### 2.1.2.3 Model-Based

For some simulation-based approaches, macro models, like neural-networks or support vector machines (SVM), are also used to reduce the execution time caused by the use of circuit simulator in the loop. These models are automatically generated using an electric simulator to evaluate the performance of the training set.

Unlike the equations-based modeling the learning based modeling application to general circuits is easier; however, there is still the tradeoff between accuracy and model size and generation time.

Alpaydin et al. [36] use a neural-fuzzy model combined with an evolutionary optimization strategy where some of the AC performance metrics are computed using an equation-based approach. De Bernardinis et al. [37] use a learning tool based in SVMs to represent the performance space of analog circuits. The performance space is modeled using the knowledge acquired from a training set via circuit simulation.

Wolfe et al. [38] present a performance macro-model based in a neural network. This model once constructed, is to be used to replace the SPICE [27] simulation during the synthesis of analog circuits, increasing the efficiency of the performance parameter estimates' computation. The training and validation data sets are constructed with discrete points, sampled over the design space. The work explores several sampling methodologies to adaptively improve model quality and applies a sizing rules methodology in order to reduce the design space and ensure the correct operation of analog circuits.

Barros et al. [1, 39] present a cell-level synthesis and optimization approach based on SVMs and evolutionary strategies. The SVM is used to dynamically model performance space and identify the feasible design space regions while at the same time the evolutionary techniques are looking for the global optimum. The evaluation is still done with HSPICE® to ensure accuracy, but the number of evaluation is reduced by using the SVM to prune the candidate solutions.

A different approach is the use of POFs to explore circuit tradeoffs during synthesis [40], and instead of using a model for the circuits, the non-dominated solutions are generated (prior to the design task) and the suitable solution is selected from the already sized solutions. In [41], hierarchically POFs are used to perform system-level sizing. The POF-based-design execution time is large if the setup time (the generation of the POFs) is considered, however with the correct models, the POFs can be generated in a context free manner making then suitable for reuse.

In Tables 2.1, 2.2 and 2.3 the several tools for analog sizing automation are summarized and, in Table 2.4, the specification translation tools based on the techniques applied are compared.

## 2.2 Motivation for Model-Based Optimization

According to McConaghy and Gielen [42], there is a great improvement on the efficiency of an optimization cycle for analog IC sizing using electrical simulators, if models containing knowledge about the circuit are used. In [42] is presented a study to analyze the impact of different models in the optimization process, which were conducted for several different techniques: polynomials [43], posynomials [44], genetic programming [45], feedforward neural networks [46], boosted feedforward

|   | _           |

|---|-------------|

| , | part        |

|   | tools,      |

|   | sızıng 1    |

|   | gon         |

|   | r anal      |

|   | ew of       |

| • | vervie      |

| ( | $\subseteq$ |

|   | _           |

| • | 'i          |

| • | ple 7.      |

|   | Table 7.    |

| E | aple        |

| THE CICLUISM OF MININGS SERVING WOLLS, PART I | on or ar | S11175 S11115   | toors, part 1                                |                           |             |                        |        |                    |                 |

|-----------------------------------------------|----------|-----------------|----------------------------------------------|---------------------------|-------------|------------------------|--------|--------------------|-----------------|

| Tool/author                                   | _        | Circuits        | Design plan/optimization                     | Evaluation                | Robust      | Robust Topology Layout | Layout | Time setup/        | Code            |

|                                               |          |                 |                                              |                           | design gen. | gen.                   | gen.   | execution          |                 |

| IDAC [2]                                      | 1987     | Analog          | Design plan plus SA                          | Equations                 | 0           | ×                      | After  | Months/few         | Pascal          |

|                                               |          | cells           | post-optimization                            |                           |             |                        | sizing | sec                |                 |

| DELIGTH.SPICE 1988 [28]                       |          | Analog<br>cells | Feasible directions optimization             | SPICE-like                | 7           | ×                      | ×      | Moderate/18 h      | I               |

| OASYS [3]                                     | 1989 (   | OPAMP           | Design plan (includes backtracking features) | Equations                 | 7           | Before                 | ×      | 6 months/3 s       | LISP            |

| BLADES [7]                                    | 1989 (   | OPAMP           | Expert system for analog design              | Equations                 | $\oslash$   | Before                 | ×      | Long/20 min        | LISP            |

| OPASYN [11]                                   | 1990     | OPAMP           | Steepest descent                             | Equations                 | 7           | Before                 | After  | 2 weeks/5 min      | C/LISP          |

|                                               |          |                 |                                              |                           |             |                        | sizing |                    |                 |

| CAMP [8]                                      | 1990     | OPAMP           | Expert system, flexible                      | SPICE-like                | 0           | During                 | After  | -/-                | TURBO           |

|                                               |          |                 | architecture                                 |                           |             |                        | sizing |                    | PROLOG          |

| OPTIMAN [13]                                  | 1990 (   | OPAMP           | SA                                           | Analytical<br>models      | ×           | ×                      | ×      | <b>–</b> /1 min    | PASCAL          |

| CE A C [52]                                   | 1001     | OBAMB           | × o                                          | Lanotions                 | >           | <u> </u>               | >      | _/_                | ر               |

| SEAS [32]                                     |          | Jr Alvir        | AS.                                          | Equations                 | •           | Dui ing                | •      | l /                | ر               |

| DONALD [15]                                   | 1991 (   | OPAMP           | Equation solver (Newton–Raphson variant)     | Equations                 | 0           | ×                      | ×      | -/-                | LISP/<br>FORTAN |

| Chang [53]                                    | 1992     | ADC             | Top-down constraint driven                   | Behavior models $\otimes$ | 0           | During                 | After  | -/4-89 h           | C++             |

|                                               |          |                 |                                              |                           |             |                        | sizing |                    |                 |

| STAIC [12]                                    | 1992 (   | OPAMP           | 2 step optimization                          | Equations                 | 0           | ×                      | After  | Long/2 min         | C++             |

|                                               |          |                 |                                              |                           |             |                        | SIZING |                    |                 |

| MINLP [54, 55] 1992                           |          | OPAMP           | Branch & bound                               | Equations and BSIM models | 0           | During                 | ×      | 6 months/<br>1 min | I               |

|                                               |          |                 |                                              |                           |             |                        |        |                    |                 |

| art II   |

|----------|

| tools, p |

| sizing   |

| analog   |

| ot       |

| erview   |

| ó        |

| 2.5      |

| Table    |

| trans commence commen |         | 2            | corp, bear as                       |                             |           |          |         |                              |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------|-------------------------------------|-----------------------------|-----------|----------|---------|------------------------------|----------|

| Tool/author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Ü       | Circuits     | Design plan/optimization Evaluation | Evaluation                  | Robust    | Topology | Latyout | Topology Latyout Time setup/ | Code     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |              |                                     |                             | design    | gen.     | gen.    | execution                    |          |

| Maulik et al.<br>[16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1993 OI | <b>JPAMP</b> | Sequential quadratic programming    | Equations and BSIM models   | 0         | ×        | ×       | 6 months/<br>1 min           | C        |

| FRIDGE [30]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1994 OI | <b>DPAMP</b> | SA                                  | SPICE-like                  | ×         | ×        | ×       | 1 h/45 min                   | ı        |

| DARWIN [18]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1995 OI | OPAMP        | Genetic Algorithm (GA)              | Small signal,<br>analytical | ×         | During   | ×       | -/-                          | 1        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |              |                                     | expressions                 |           |          |         |                              |          |

| ISAID [9, 10]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1995 OI | <b>DPAMP</b> | Qualitative                         | Equation and                | $\oslash$ | ×        | ×       | -/-                          | C/PROLOG |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |              | reasoning + post                    | qualitative                 |           |          |         |                              |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |              | optimization                        | reasoning                   |           |          |         |                              |          |

| SD-OPT [24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1995    | ∑ ∆-         | SA                                  | Equation adn                | ×         | ×        | ×       | Long/                        | I        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | modulator    |                                     | behavioral                  |           |          |         | 1,5 week                     |          |

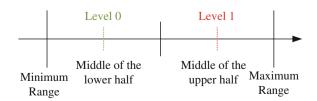

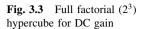

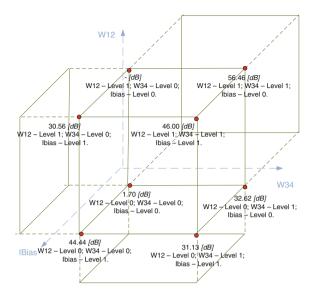

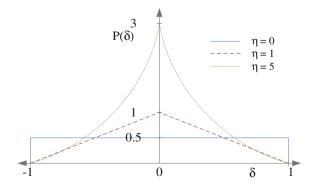

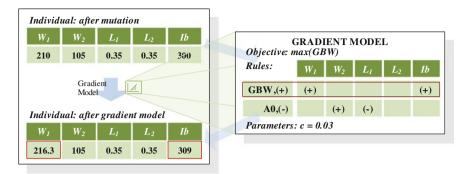

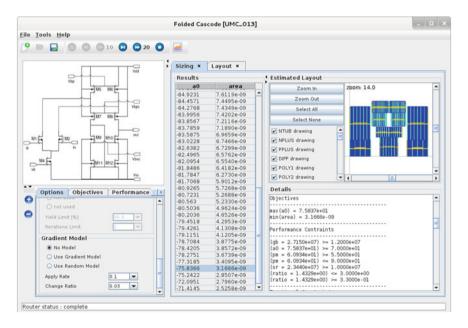

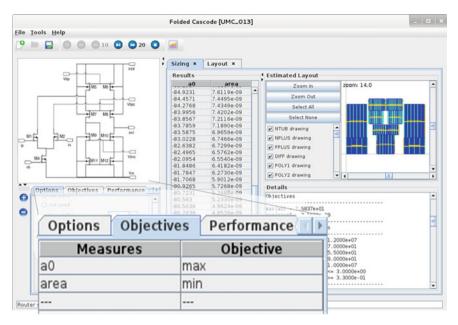

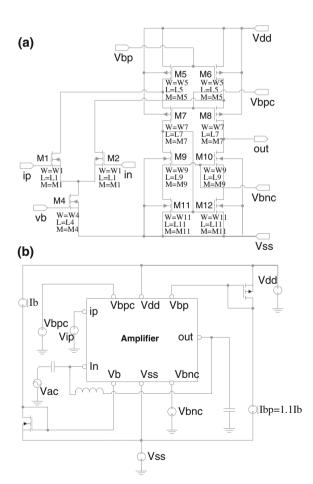

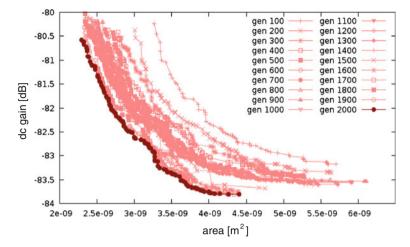

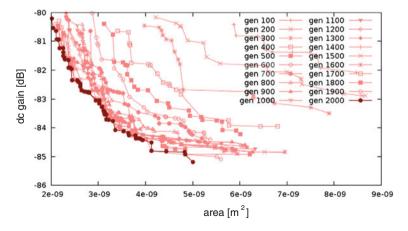

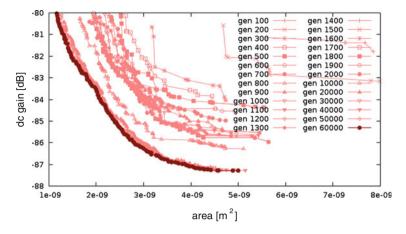

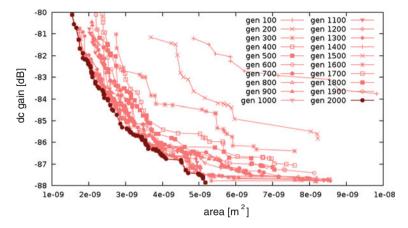

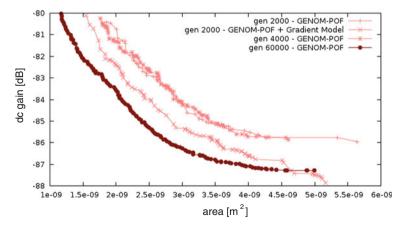

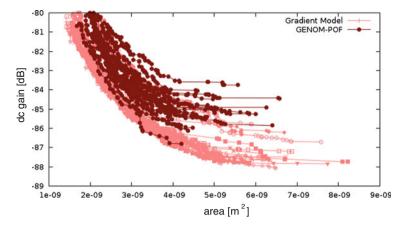

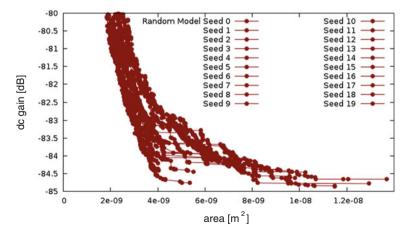

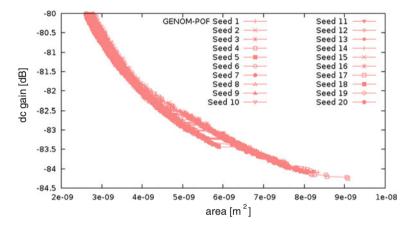

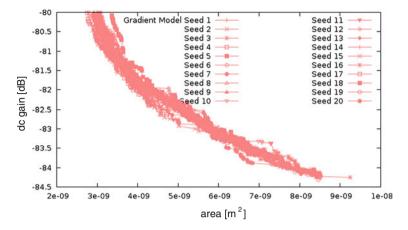

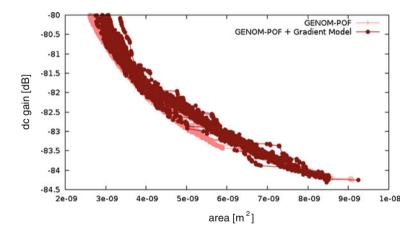

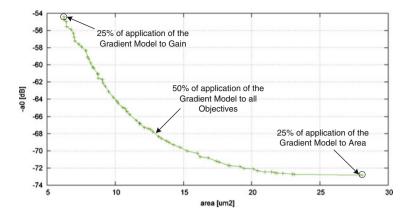

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |              |                                     | simulation                  |           |          |         |                              |          |