## The OIS Processor Principles of Operation

REVIEW DRAFT - COMMENTS PLEASE

April 9, 1977 Version 2.0

This document describes the interior architecture of the OIS System Element Digital Processor. It includes a description of the virtual storage system, the instruction set, and the input-output facilities.

7,55

## **XEROX**

INFORMATION TECHNOLOGY GROUP SYSTEMS DEVELOPMENT DIVISION 3406 Hillview Ave. / Palo Alto / California 94304

## Table of Contents

| Introduction & and                           | -        |  |  |  |

|----------------------------------------------|----------|--|--|--|

| Information formats, syntactic conventions   | 2        |  |  |  |

| Number system                                |          |  |  |  |

| Special Characters                           | 2        |  |  |  |

| Terms                                        | 2        |  |  |  |

| Virtual Storage                              |          |  |  |  |

| Introduction                                 | 4        |  |  |  |

| Mesa's Use of the Virtual Memory System      |          |  |  |  |

| Address Translation                          | 5        |  |  |  |

| Requests                                     | 6        |  |  |  |

| Operations on the Map                        | 6        |  |  |  |

| Mapping Examples ·                           | 7        |  |  |  |

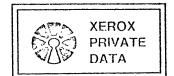

| Pointer Formats                              | 8        |  |  |  |

| Central Processor                            |          |  |  |  |

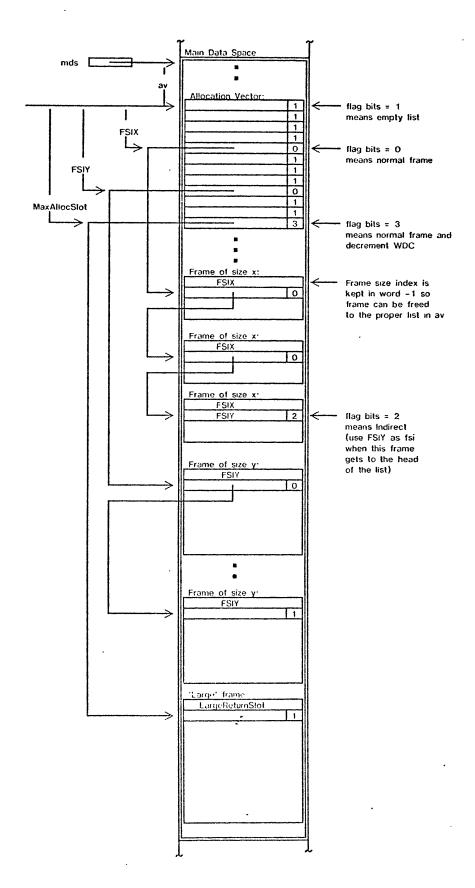

| Data Structures and Associated Registers     | 9        |  |  |  |

| Code Segments                                | 9        |  |  |  |

| Global Frames                                | 10       |  |  |  |

| Local Frames                                 | 10       |  |  |  |

| System Dispatch                              | 10       |  |  |  |

| Global Frame Table                           | 10       |  |  |  |

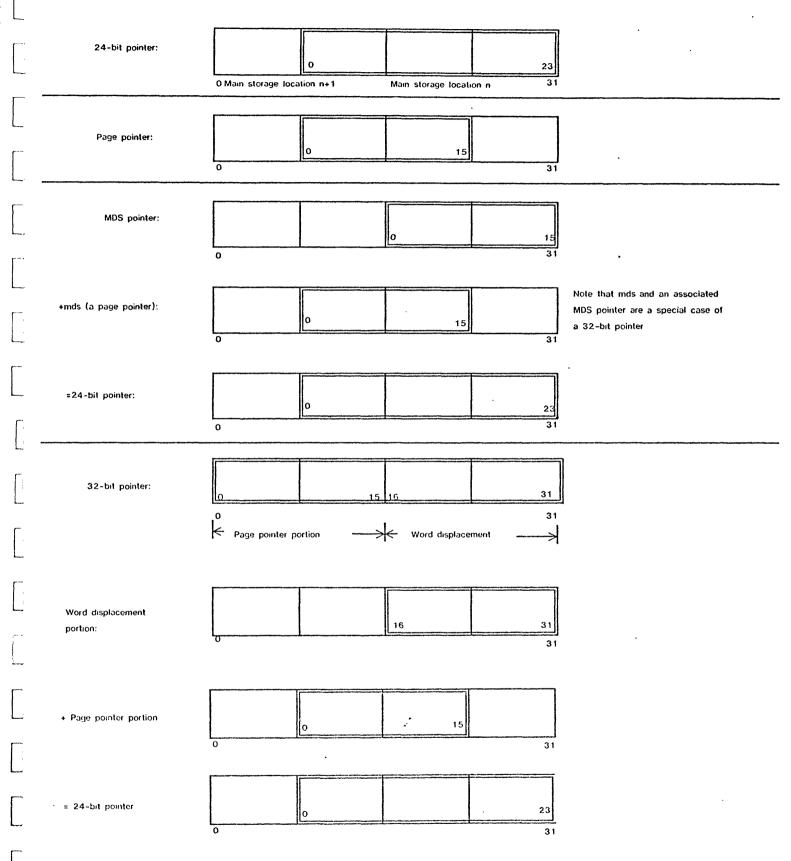

| Allocation Vector                            | 10       |  |  |  |

| The Processor Stack                          | 11       |  |  |  |

| The Machine State                            | 12       |  |  |  |

|                                              |          |  |  |  |

| Instruction Format and Classes               | 4.4      |  |  |  |

| Load/Store Instructions                      | 14       |  |  |  |

| Load/Store Global Word                       | 15<br>16 |  |  |  |

| Load/Store Local Word                        | 17       |  |  |  |

| Load Immediate  Load/Store Global Doubleword | 18       |  |  |  |

| Load/Store Local Doubleword                  | 18       |  |  |  |

| Read/Write Word                              | 19       |  |  |  |

| Read/Write Doubleword                        | 21       |  |  |  |

| Read/Write Indexed                           | 23       |  |  |  |

| Read/Write Indirect                          | 24       |  |  |  |

| Read/Write String                            | 26       |  |  |  |

| Read/Write Field                             | 27       |  |  |  |

| Jump Instructions         36           Unconditional Jumps         36           Conditional Jumps         36           Jump Indexed Byte/Word         41           FOR Loop Control Instructions         42           Miscellaneous Instructions         43           Bit Boundary Block Transfer         48           Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers         50           Control Links         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Types of Trap         62           Trap Processing <td< th=""><th>Data Modification Instructions</th><th>30</th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Data Modification Instructions        | 30         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------|

| Conditional Jumps   36   Jump Indexed Byte/Word   41   FOR Loop Control Instructions   42   42   43   44   50R Loop Control Instructions   43   44   45   45   46   46   46   46   46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                     |            |

| Jump Indexed Byte/Word         41           FOR Loop Control Instructions         42           Miscellaneous Instructions         43           Bit Boundary Block Transfer         48           Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers         50           Control Links         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port In         61           Traps         62           Types of Trap         62           Trap Processing         63           Breakpoints         64           Process Switching         64           Process States         65           Registers         66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ·                                     |            |

| FOR Loop Control Instructions         42           Miscellaneous Instructions         43           Bit Boundary Block Transfer         48           Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers           Control Links         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         Types of Trap           Trap Processing         63           Breakpoints         64           Process Switching         Process States           Registers         66           Scheduler         66           Interruptible Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ·                                     |            |

| Miscellaneous Instructions         43           Bit Boundary Block Transfer         48           Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers         50           Control Links         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Trap Processing         63           Breakpoints         64           Process Switching         64           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       | • •        |

| Bit Boundary Block Transfer         48           Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers           Control Transfers         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Call         59           Kernel Function Call         60           Return         60           Port Out         60           Port In         61           Trap Processing           Breakpoints         64           Process Switching           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         70           Types of Errors         69           Er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                                     |            |

| Display Bitmap Format         48           Font Format         48           BitBLT         49           BitBLT Examples         50           Extensions to BitBLT         50           Control Transfers           Control Transfers         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Call         59           Kernel Function Call         60           Return         60           Port Out         60           Port In         61           Trap         62           Trap Processing         63           Breakpoints         64           Process Switching         64           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         70           Types of Errors         69           Error Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |            |

| Font Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |            |

| BitBLT       49         BitBLT Examples       50         Extensions to BitBLT       50         Control Transfers         Control Links       51         Procedure Descriptors       51         Stored Program Counters       52         Frame Allocation       52         XFER       55         Control Transfer Instructions       57         Local Function Calls       58         Global Function Call       59         Kernel Function Call       60         Return       60         Port Out       60         Port In       61         Traps       62         Trap Processing       63         Breakpoints       64         Process Switching       Process States         Registers       66         Scheduler       66         Interruptible Instructions       68         Errors and Error Handling       Types of Errors       69         Error Logging       69         Software Notification of Errors       70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · · · · · · · · · · · · · · · · · · |            |

| BitBLT Examples       50         Extensions to BitBLT       50         Control Transfers       50         Control Links       51         Procedure Descriptors       51         Stored Program Counters       52         Frame Allocation       52         XFER       55         Control Transfer Instructions       57         Local Function Calls       58         Global Function Call       59         Kernel Function Call       60         Return       60         Port Out       60         Port In       61         Traps       62         Trap Processing       63         Breakpoints       64         Process Switching       Process Switching         Process States       65         Registers       66         Scheduler       66         Interruptible Instructions       68         Errors and Error Handling       Types of Errors       69         Error Logging       69         Software Notification of Errors       70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |            |

| Extensions to BitBLT         50           Control Transfers         51           Control Links         51           Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Trap Processing         63           Breakpoints         64           Process Switching         6           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         7           Types of Errors         69           Error Logging         69           Software Notification of Errors         70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |            |

| Control Transfers  Control Links 51 Procedure Descriptors 51 Stored Program Counters 52 Frame Allocation 52 XFER 55 Control Transfer Instructions 57 Local Function Calls 58 Global Function Calls 58 Stack Function Call 59 Kernel Function Call 60 Return 60 Port Out 60 Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                     |            |

| Control Links 51 Procedure Descriptors 51 Stored Program Counters 52 Frame Allocation 52 XFER 55 Control Transfer Instructions 57 Local Function Calls 58 Global Function Calls 58 Stack Function Call 59 Kernel Function Call 60 Return 60 Port Out 60 Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Extensions to BitBLI                  | 50         |

| Procedure Descriptors         51           Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Trap Processing         63           Breakpoints         64           Process Switching         65           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         7ypes of Errors         69           Error Logging         69           Software Notification of Errors         70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |            |

| Stored Program Counters         52           Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Calls         58           Stack Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Trap Processing         63           Breakpoints         64           Process Switching         65           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         7ypes of Errors         69           Error Logging         69           Software Notification of Errors         70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | •          |

| Frame Allocation         52           XFER         55           Control Transfer Instructions         57           Local Function Calls         58           Global Function Call         58           Stack Function Call         60           Kernel Function Call         60           Return         60           Port Out         60           Port In         61           Traps         62           Trap Processing         63           Breakpoints         64           Process Switching         64           Process States         65           Registers         66           Scheduler         66           Interruptible Instructions         68           Errors and Error Handling         7ypes of Errors         69           Error Logging         69           Software Notification of Errors         70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ~                                     |            |

| XFER 55 Control Transfer Instructions 57 Local Function Calls 58 Global Function Calls 58 Stack Function Call 59 Kernel Function Call 60 Return 60 Port Out 60 Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _                                     | •          |

| Control Transfer Instructions  Local Function Calls  Global Function Calls  Stack Function Call  Stack Function Call  Kernel Function Call  Return  Port Out  Port In  60  Port In  61  Traps  Types of Trap  Trap Processing  Breakpoints  62  Process Switching  Process States  Registers  Scheduler  Interruptible Instructions  63  Errors and Error Handling  Types of Errors  Error Logging  Software Notification of Errors  58  58  58  58  57  69  57  69  57  69  56  57  69  56  57  69  56  57  69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |            |

| Local Function Calls Global Function Calls Stack Function Call Stack Function Call Stack Function Call Kernel Function Call Return Port Out Port In  Traps Types of Trap Trap Processing Breakpoints  62  Compared to the process Switching Process States Registers Scheduler Interruptible Instructions  63  Errors and Error Handling Types of Errors Error Logging Software Notification of Errors  58  58  58  58  58  58  58  58  59  59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                       |            |

| Global Function Calls Stack Function Call Kernel Function Call Return Port Out Port In  Traps Types of Trap Types of Trap Trap Frocessing Breakpoints  62  63  64  Process Switching Process States Registers Federal Functions  65  66  66  66  66  67  68  68  68  69  69  69  69  69  69  69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | _          |

| Stack Function Call Kernel Function Call Return 60 Port Out Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States Registers 65 Registers 66 Scheduler Interruptible Instructions 69 Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |            |

| Kernel Function Call       60         Return       60         Port Out       60         Port In       61         Traps         Types of Trap       62         Trap Processing       63         Breakpoints       64         Process Switching         Process States       65         Registers       66         Scheduler       66         Interruptible Instructions       68         Errors and Error Handling       69         Types of Errors       69         Error Logging       69         Software Notification of Errors       70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |            |

| Return 60 Port Out 60 Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |            |

| Port Out 60 Port In 61  Traps Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |            |

| Traps Types of Trap Types of Trap Trap Processing Breakpoints  62 Trap Processing 63 Breakpoints  64  Process Switching Process States Fregisters Fregisters 65 Registers 66 Scheduler Finterruptible Instructions 68  Errors and Error Handling Types of Errors Fror Logging Foftware Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |            |

| Traps Types of Trap Trap Processing Breakpoints  63 Breakpoints  64  Process Switching Process States Fregisters Fregiste |                                       |            |

| Types of Trap 62 Trap Processing 63 Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Port In                               | 61         |

| Trap Processing Breakpoints  63 Breakpoints  64  Process Switching Process States Frocess States Fregisters Fr | Traps                                 |            |

| Breakpoints 64  Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                       |            |

| Process Switching Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Trap Processing                       | 63         |

| Process States 65 Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Breakpoints                           | 64         |

| Registers 66 Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Process Switching                     |            |

| Scheduler 66 Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Process States                        | 65         |

| Interruptible Instructions 68  Errors and Error Handling Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Registers                             | 66         |

| Errors and Error Handling Types of Errors Error Logging Software Notification of Errors  69 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Scheduler                             | <b>6</b> 6 |

| Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interruptible Instructions            | 68         |

| Types of Errors 69 Error Logging 69 Software Notification of Errors 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Errors and Error Handling             |            |