# DATABOOK

## Numeric Index

| ADP-7409TB7 - 35                 | LPM-PIO26 - 77    |

|----------------------------------|-------------------|

| Analog-ADP                       | LPM-SBC3          |

| BP-XX                            | LPM-SBC40A        |

| C-Thru-ROM3 - 3                  | LPM-SBC41         |

| CBL-XXX-YY                       | LPM-SBC42         |

| CC-XX                            | LPM-SBC5          |

| CC-XX                            | LPM-SBC53         |

|                                  |                   |

| CDU-258 - 3                      | LPM-SBC6          |

| CX-XX                            | LPM-SBC8          |

| CX-XX-PS                         | LPM-SBX           |

| Enclosures                       | LPM-SCSI          |

| FD3-144                          | LPM-SIO2          |

| FD3-21M6 - 23                    | LPM-SIO46 - 81    |

| FD3-7206 - 21                    | LPM-SPIO6 - 83    |

| HDAT6 - 25                       | LPM-SSD           |

| HDXT6 - 25                       | LPM-SX3864 - 39   |

| LPM-1024 - 85                    | LPM-UMC           |

| LPM-12806 - 91                   | LPM-UMC25 - 15    |

| LPM-286AT4 - 27                  | LPM-UMC45 - 17    |

| LPM-3865X4 - 11                  | LPM-USSD6 - 19    |

| LPM-4886 - 49                    | LPM-VGA           |

| LPM-71096 - 87                   | MB-XX             |

| LPM-7304                         | MCM-102           |

| LPM-7312                         | MCM-1260          |

| LPM-7314                         | MCM-2400          |

| LPM-7507                         | MCM-2400MNP6 - 47 |

| LPM-7508                         | MCM-286AT         |

| LPM-7604                         | MCM-2865X         |

| LPM-7605                         | MCM-486DX/SX      |

| LPM-7614                         | MCM-488           |

| LPM-7709                         | MCM-7109          |

| LPM-7815                         | MCM-7304 6 - 53   |

| LPM-7904                         | MCM-7312          |

| LPM-A/D12M                       | MCM-7314          |

| LPM-AIO                          | MCM-7418          |

| LPM-AIO-8                        | MCM-7419          |

| LPM-ANET                         | MCM-7507          |

| LPM-CLK                          | MCM-7508          |

| LPM-CPU2A                        | MCM-7604 6 - 63   |

| LPM-CTC                          | MCM-7605 6 - 65   |

| LPM-D/A12                        | MCM-7614          |

| LPM-D/A8                         | MCM-7706          |

|                                  | MCM-77095 - 7     |

| LPM-DISK-AT                      |                   |

| LPM-DISK-XT                      | MCM-7815          |

| LPM-DLPT6 - 69<br>LPM-DPRAM5 - 9 | MCM-7904          |

|                                  |                   |

| LPM-DSIO                         | MCM-AIO           |

| LPM-DSKIO                        | MCM-AIO-8         |

| LPM-DSPIO                        | MCM-ANET          |

| LPM-EGA                          | MCM-CLK           |

| LPM-ENET                         | MCM-CPU2A4 - 91   |

| LPM-FPC6 - 29                    | MCM-CTC           |

| LPM-FPVGA6 - 31                  | MCM-D/A126 - 99   |

| LPM-KYBLCD                       | MCM-D/A86 - 101   |

| LPM-M/CGA6 - 33                  | MCM-DISK-AT6 - 7  |

| LPM-MODEM                        | MCM-DISK-XT 6 - 9 |

| LPM PIO6 - 75                    | MCM-DLPT6 - 69    |

|                                  |                   |

|                | 9   |

|----------------|-----|

| MCM-DRAM1285 - | 11  |

| MCM-DRAM645 -  | 11  |

| MCM-DSIO       | 71  |

|                | 11  |

| MCM-DSP32C4 -  | 35  |

| MCM-DSPIO 6 -  | 73  |

|                | 35  |

| MCM-ENET       | 41  |

|                | 29  |

| MCM-FPVGA6 -   | 31  |

| MCM-KYBLCD6 -  | 111 |

| MCM-M/CGA6 -   | 33  |

|                | 43  |

| МСМ-РЮ6 -      | 75  |

| МСМ-РЮ26 -     |     |

| MCM-SBC34 -    |     |

| MCM-SBC40A4 -  |     |

| MCM-SBC414 -   |     |

| MCM-SBC424 -   |     |

|                | 105 |

| MCM-SBC534 -   | 41  |

|                | 97  |

| MCM-SBC84 -    | 75  |

|                | 113 |

|                | 13  |

| MCM-SIO2       | -   |

| MCM-SIO4       | 81  |

| МСМ-ЅРЮ6 -     | 83  |

| MCM-SSD        |     |

| MCM-STATUS     |     |

|                | 39  |

|                | 13  |

|                | 15  |

| MCM-UMC4       | 17  |

| MCM-USSD       | 19  |

| MCM-VGA6 -     | 35  |

| PC-STD ADP6 -  | 117 |

| PS12T126 -     | 119 |

| PS24T126 -     | 119 |

| PS48T126 -     | 119 |

| ROM-DOS3 -     | 7   |

| SBC258 -       | 3   |

| SBC888 -       | 9   |

| SBX-A/D129 -   | 3   |

| SBX-D/A129 -   | 5   |

| SBX-ОРТО9 -    | 7   |

| SBX-PIO        | 9   |

| SBX-SCC        | 11  |

| SBX-SCSI       | 13  |

| SBX-WWI        | 15  |

| STD-AT         | 3   |

| STD-EXT        | 121 |

| STD-QNX        | 13  |

| STD-WW2        | 123 |

| TRM Series7 -  |     |

|                |     |

## **Ordering Information**

#### Placing an Order

Orders should be placed with WinSystems, Inc. at the following location:

WinSystems, Inc. 715 Stadium Drive Suite 100 Arlington, Texas 76011 Phone: 817-274-7553 FAX: 817-548-1358

All orders should have the complete model number, quantity, purchase order number, a bill-to address, ship-to address, method of shipment, desired ship date, Federal Tax ID \*, and for Texas customers include the sales tax exempt ID number. Orders are subject to acceptance in writing by WinSystems, Inc.

#### Outside the USA

In countries without a WinSystems' sales representative, orders may be placed by guarantee of payment in US dollars such as letters of credit, sight draft or advance payment.

#### Terms

Terms with prior credit approval are net 30 days from the date of invoice. Credit must be established prior to shipment. WinSystems, Inc. maintains the right to require partial or full payment in advance if the financial condition of the Buyer does not warrant net terms. A MasterCard, VISA, money order, certified check, or company check is accepted for prepaid orders.

#### Prices

All prices are in U.S. dollars and F.O.B. Arlington, Texas. Applicable federal, state, and local taxes are extra and paid by the buyer. Prices are subject to change without notification.

#### Discounts

Quantity and OEM discounts are available on an order or contract basis. Consult the WinSystems' Sales Department for details.

#### **Product Availability**

WinSystems' normal delivery for most products in quantities of less than ten is stock to two weeks after

receipt of order. Shipping dates are approximate and are based upon prompt receipt by WinSystems of all necessary information. Partial shipments may be made unless instructed otherwise.

#### Shipping

All products are shipped in rugged containers suitable for ensuring safe delivery under normal shipping conditions. Unless otherwise directed, all products are shipped via UPS or Federal Express. Depending upon the shipping method, charges are collect or prepaid and added to the invoice.

#### **Product Demonstration**

The STD-AT and other WinSystems' products are best evaluated through demonstrations. If you would like a demonstration or a 30-day evaluation unit, call WinSystems' Sales Department.

#### **Technical Support**

WinSystems' has an Applications Engineering staff to answer your technical questions concerning hardware, software, and systems products and configurations both before and after purchase. Please call 817-274-7553, FAX 817-548-1358, or write your questions to the Applications Engineering Department.

#### 24-Hour Bulletin Board

A WinSystems' Electronic Bulletin Board System is accessible 24 hours a day. It offers on-line technical support, application articles, and example code. Modem transmissions speeds supported are 300, 1200 or 2400 baud. The communication settings are: 8-bits, no parity, and one-stop bit. The phone number is 817-861-8739. If you have trouble gaining access to the bulletin board, call 817-274-7553 and ask for the Applications Engineering Department.

#### **Federal Supply Code**

WinSystems' CAGE/FSCM number is 1AU87.

#### **Facsimile Transmission**

WinSystems' FAX machine is capable of supporting CCITT G3, G2, and North American FM compatibility. The direct telephone number is 817-548-1358.

©1992/93 WinSystems, Inc. Printed in USA

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of WinSystems, Inc. The information in this document is subject to change without notice. The information furnished by WinSystems, Inc. in this publication is believed to be accurate and reliable. However, WinSystems, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. WinSystems, Inc. makes no warranty of merchantability or fitness for any purpose. WinSystems, Inc. assumes no responsibility for any errors that may appear in this document.

## WinSystems, Inc.

P.O. Box 121361 / Arlington, Texas 76012 / (817) 274-7553

"THE STD BUS AUTHORITY""

### A Message from the President

To Our Customers:

In response to the challenge of the 90's, we are proud to furnish our latest catalog of STD Bus products representing over a decade of growth and development for the ever changing STD Bus marketplace.

We thank you, our customers, for your role as "partners" in development, and for your input and response to our commitment to customer oriented, superior innovation and highest quality products at a competitive price.

We pledge to continue this commitment to you.

Sincerely, 0 Jerry Winfield

President

715 Stadium Drive, Suite 100 / Arlington, Texas 76011-6225 / (817) 274-7553 / FAX (817) 548-1358

÷

## **STD BUS Data Book**

## **Table of Contents**

## **General Information**

## Chapter 1

| General Information                 | 1-3   |

|-------------------------------------|-------|

| Product Overview                    | 1-5   |

| New Products                        | 1-7   |

| Non-Standard Products               | .1-13 |

| Warranty and Life Support Statement | .1-15 |

| Interchangeability Guide            | .1-17 |

## **Product Datasheets**

| DOS Systems                              | Chapter 2                                         |

|------------------------------------------|---------------------------------------------------|

| STD-AT                                   | STD Bus PC-AT Compatible System2-3                |

| Software                                 | Chapter 3                                         |

| C-Thru-ROM<br>ROM-DOS<br>STD-QNX         | Remote Symbolic C Debugger                        |

| Processors                               | Chapter 4                                         |

| <b>16- and 32-bi</b><br>16/32-Bit Proces | t <b>Processors</b><br>sor Selection Guide        |

| MCM 40(CV/DV                             |                                                   |

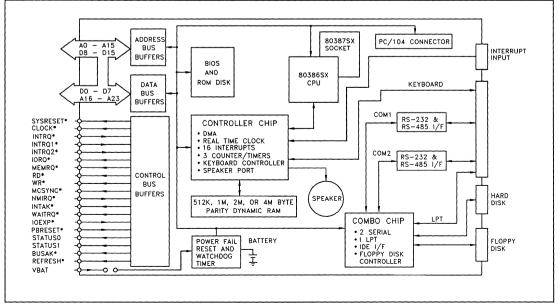

| MCM-486SX/DX<br>LPM-386SX                | AT Compatible 804865X SBC                         |

| MCM-386SX                                | AT Compatible 803865X SBC                         |

| LPM-286AT                                | AT Compatible CMOS 80C286 SBC                     |

| MCM-286AT                                | AT Compatible 80286 SBC                           |

| MCM-DSP32C                               | STD Bus 50 MHz AT&T DSP32C Processor $\dots 4-35$ |

| LPM-SX386                                | Low Cost CMOS 803865X SBC $\dots 4-39$            |

| MCM-SX386                                | Low Cost 803865X SBC                              |

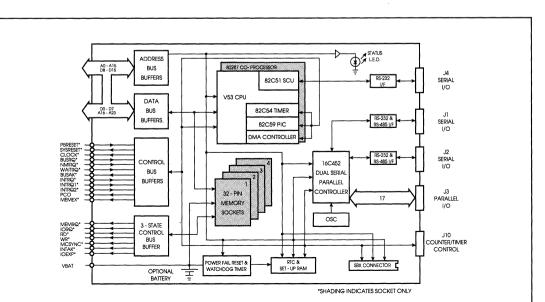

| LPM-SBC53                                | 16-bit, V53 CMOS SBC                              |

| MCM-SBC53                                | 16-bit, V53 SBC                                   |

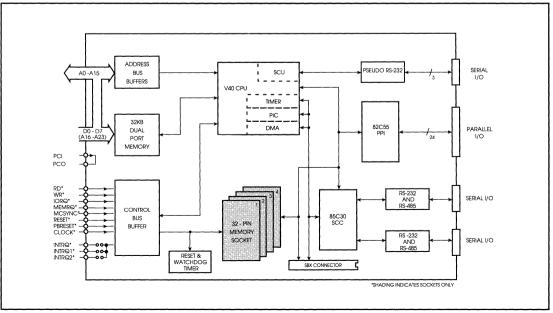

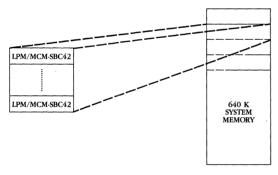

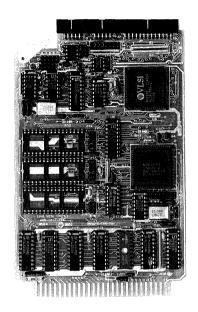

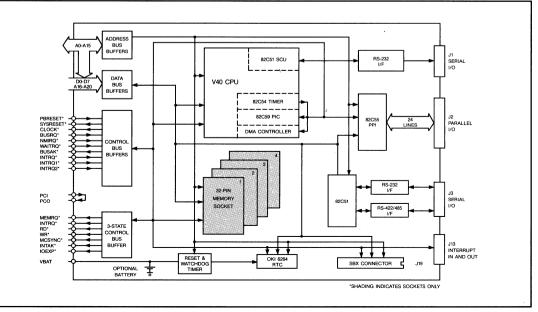

| LPM-SBC42                                | V40 CMOS Slave I/O Processor $\dots 4-47$         |

| MCM-SBC42                                | V40 Slave I/O Processor                           |

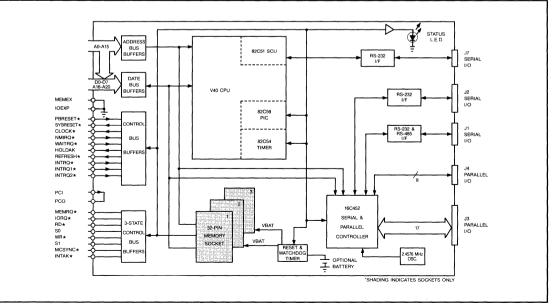

| LPM-SBC41  | Low Cost CMOS V40 Multifunction SBC4-51       |

|------------|-----------------------------------------------|

| MCM-SBC41  | Low Cost V40 Multifunction SBC                |

| LPM-SBC40A | CMOS V40 Multifunction SBC                    |

| MCM-SBC40A | V40 Multifunction SBC                         |

| LPM-SBC8   | CMOS 80C88 Single Board Computer $\dots 4-71$ |

| MCM-SBC8   | 8088 Single Board Computer                    |

### **8-Bit Processors**

| 8-Bit | Processor | Selection | Guide | <b>4</b> – | · 79 | ) |

|-------|-----------|-----------|-------|------------|------|---|

|-------|-----------|-----------|-------|------------|------|---|

| LPM-7815  | Low Cost CMOS 80C85 CPU                    |

|-----------|--------------------------------------------|

| MCM-7815  | Low Cost 8085 CPU                          |

| LPM-102   | CMOS Z80 Single Board Computer             |

| MCM-102   | Z80 Single Board Computer                  |

| LPM-CPU2A | CMOS Z80 Single Board Computer             |

| MCM-CPU2A | Z80 Single Board Computer                  |

| LPM-SBC6  | CMOS 64180 Single Board Computer           |

| MCM-SBC6  | 64180 Single Board Computer                |

| LPM-SBC5  | CMOS 64180 Single Board Computer           |

| MCM-SBC5  | 64180 Single Board Computer                |

| LPM-SBC3  | CMOS Z80 Multifunction SBC $\dots 4 - 109$ |

| MCM-SBC3  | Z80 Multifunction SBC                      |

|           |                                            |

### Memory

## Chapter 5

| Memory Selection Guide |                                  |  |

|------------------------|----------------------------------|--|

| MCM-7706               | 64KB Battery Backed Memory       |  |

| LPM-7709               | 256KB CMOS Battery Backed Memory |  |

| MCM-7709               | 256KB Battery Backed Memory      |  |

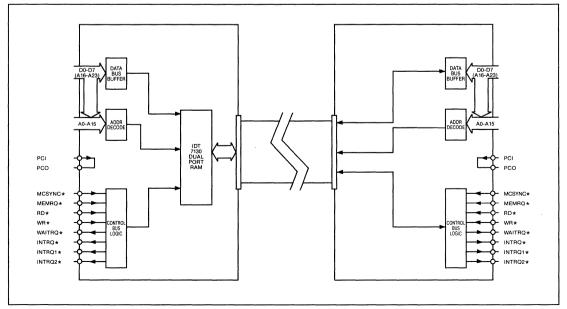

| LPM-DPRAM              | 1KB CMOS Dual Port RAM           |  |

| MCM-DPRAM              | 1KB Dual Port RAM                |  |

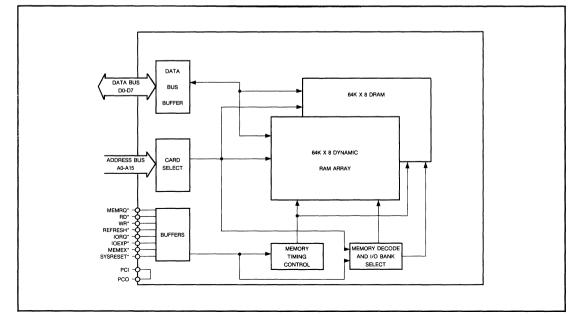

| MCM-DRAM128            | 128KB DRAM (Z80)                 |  |

| MCM-DRAM64             | 64KB DRAM (Z80)                  |  |

| LPM-UMC                | 64KB CMOS Universal Memory       |  |

| MCM-UMC                | 64KB Universal Memory            |  |

| LPM-UMC2               | 512KB CMOS Universal Memory      |  |

| MCM-UMC2               | 512KB Universal Memory           |  |

| LPM-UMC4               | 1MB CMOS Universal Memory        |  |

| MCM-UMC4               | 1MB Universal Memory             |  |

|                        |                                  |  |

| Disk Controllers/Mass Storage   |                                        |  |

|---------------------------------|----------------------------------------|--|

| Disk Controller Selection Guide |                                        |  |

| Mass Storage Dev                | vice Selection Guide $\dots 6-6$       |  |

|                                 |                                        |  |

| LPM-DISK-AT                     | CMOS IDE/Floppy Disk Controller        |  |

| MCM-DISK-AT                     | IDE/Floppy Disk Controller $\dots 6-7$ |  |

| LPM-DISK-XT                     | CMOS SCSI/Floppy Disk Controller       |  |

| MCM-DISK-XT                     | SCSI/Floppy Disk Controller            |  |

| LPM-DSKIO                       | CMOS Disk I/O Support Controller       |  |

| MCM-DSKIO                       | Disk I/O Support Controller            |  |

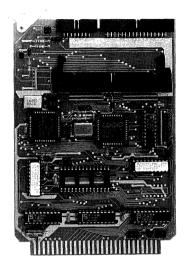

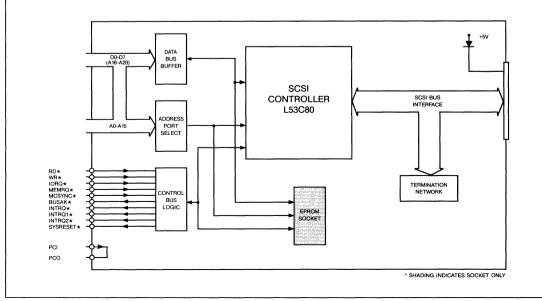

| LPM-SCSI                        | CMOS SCSI Host Adapter                 |  |

| MCM-SCSI                        | SCSI Host Adapter                      |  |

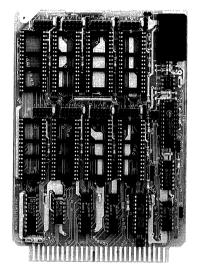

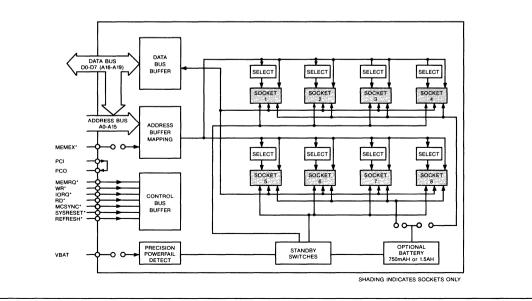

| LPM-SSD                         | CMOS Solid State Disk (RAM/ROM)        |  |

| MCM-SSD                         | Solid State Disk (RAM/ROM)             |  |

| LPM-USSD                        | Universal CMOS Solid State Disk        |  |

| MCM-USSD                        | Universal Solid State Disk             |  |

| FD3-144                         | 1.44MB STD Bus Board Mounted Drive     |  |

| FD3-720                         | 720KB STD Bus Board Mounted Drive      |  |

| FD3-21M                         | 21 Megabyte Floptical Disk Drive       |  |

| HDAT                            | 40/100/200 MByte 3.5" IDE Drive        |  |

|                                 | Mounted on STD Bus Card                |  |

| HDXT                            | 40 MByte 3.5" SCSI Drive               |  |

|                                 | Mounted on STD Bus Board               |  |

|                                 |                                        |  |

## Video/Graphics Controllers

| Video/Graphics Controller Selection Guide | - 2 | 27 | 7 |

|-------------------------------------------|-----|----|---|

|-------------------------------------------|-----|----|---|

| LPM-EGA   | EGA, CGA, MDA, HGC Video Adapter           |

|-----------|--------------------------------------------|

| MCM-EGA   | EGA, CGA, MDA, HGC Video Adapter           |

| LPM-FPC   | CMOS Flat Panel Controller                 |

| MCM-FPC   | Flat Panel Controller                      |

| LPM-FPVGA | Flat Panel/CRT CMOS VGA Controller         |

| MCM-FPVGA | Flat Panel/CRT VGA Controller              |

| LPM-M/CGA | Low Cost CGA Video Adapter                 |

| MCM-M/CGA | Low Cost CGA Video Adapter                 |

| LPM-VGA   | VGA, EGA, CGA, & HGC Graphics $\dots 6-35$ |

| MCM-VGA   | VGA, EGA, CGA, & HGC Graphics $\dots 6-35$ |

|           |                                            |

## **I/O**

## Networking/Communications Controllers

| Networking/Communications Controller Guide |                                             |  |

|--------------------------------------------|---------------------------------------------|--|

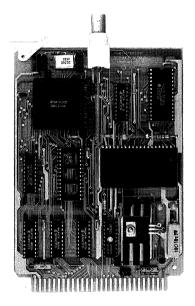

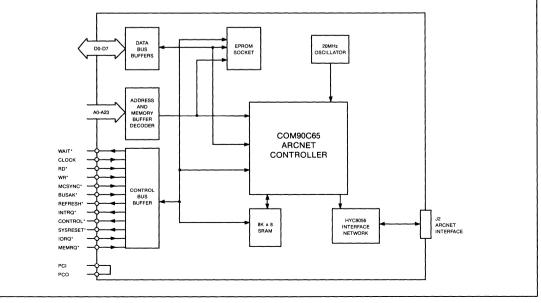

| LPM-ANET                                   | CMOS STD Bus ARCNET Controller              |  |

| MCM-ANET                                   | STD Bus ARCNET Controller                   |  |

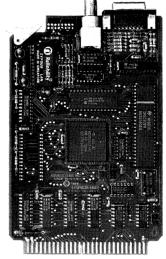

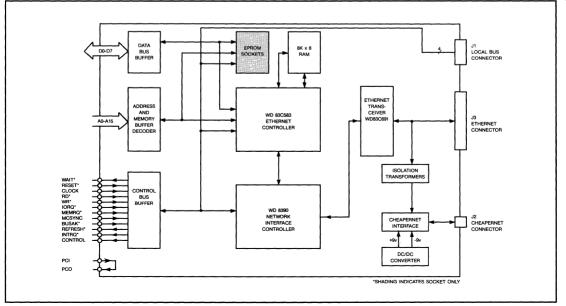

| LPM-ENET                                   | CMOS STD Bus Ethernet Controller            |  |

| MCM-ENET                                   | STD Bus Ethernet Controller                 |  |

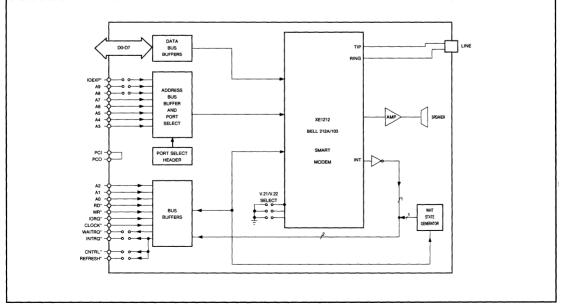

| LPM-MODEM                                  | 1200/300 Bps Smart Modem                    |  |

| MCM-MODEM                                  | 1200/300 Bps Smart Modem                    |  |

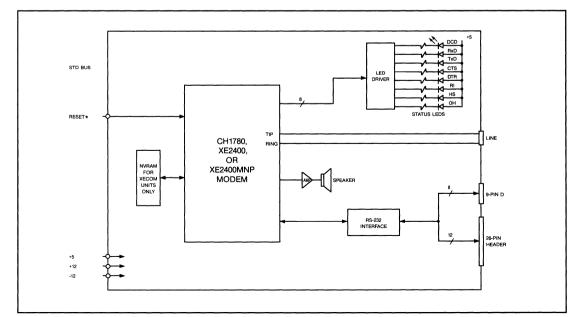

| MCM-2400                                   | 2400 Bps Smart Modem                        |  |

| MCM-2400MNP                                | 2400 Bps With Error Correction $\dots 6-47$ |  |

| LPM-488                                    | CMOS Talker/Listener/Controller IEEE-488    |  |

| MCM-488                                    | STD Bus Talker/Listener/Controller IEEE-488 |  |

## Serial and Parallel I/O

| -3CHAI AHU FAIAHEI I/O SCIECUUH GUIUC | Serial and Parallel I/O | Selection Guide | 6- | 51 |

|---------------------------------------|-------------------------|-----------------|----|----|

|---------------------------------------|-------------------------|-----------------|----|----|

| LPM-7304  | Dual 82C51 Async RS-232/485            |

|-----------|----------------------------------------|

| MCM-7304  | Dual 8251A Async RS-232/485            |

| LPM-7312  | Dual 85C30 SCC Multiprotocol RS-232    |

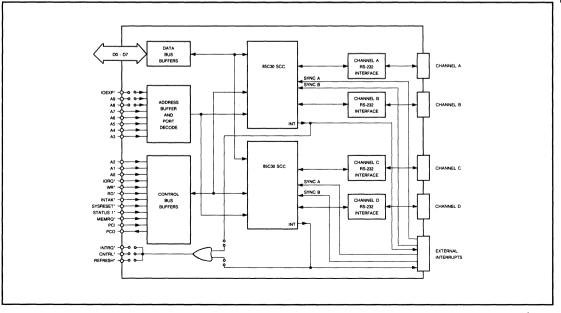

| MCM-7312  | Dual 8530 SCC Multiprotocol RS-232     |

| LPM-7314  | Quad 85C30 SCC Multiprotocol RS-232    |

| MCM-7314  | Quad 8530 SCC Multiprotocol RS-232     |

| LPM-7507  | 24 Line Parallel (Opto-22) Interface   |

| MCM-7507  | 24 Line Parallel (Opto-22) Interface   |

| LPM-7508  | 48 Line Parallel (Opto-22) Interface   |

| MCM-7508  | 48 Line Parallel (Opto-22) Interface   |

| LPM-7604  | 64 Line Parallel I/O                   |

| MCM-7604  | 64 Line Parallel I/O                   |

| LPM-7605  | 32 Line Programmable Parallel I/O      |

| MCM-7605  | 32 Line Programmable Parallel I/O      |

| LPM-7614  | 64 Line Parallel I/O                   |

| MCM-7614  | 64 Line Parallel I/O                   |

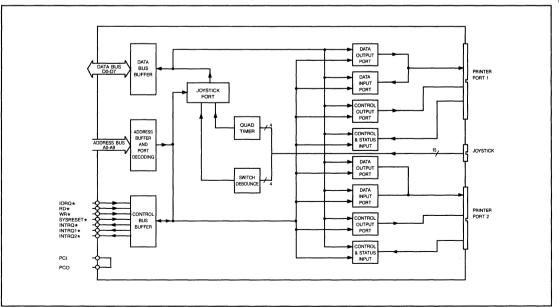

| LPM-DLPT  | CMOS STD Bus Dual Line Printer         |

| MCM-DLPT  | Dual Line Printer and Joystick I/F     |

| LPM-DSIO  | CMOS Dual Asynchronous RS-232/20mA     |

| MCM-DSIO  | Dual Asynchronous RS-232/20mA          |

| LPM-DSPIO | Dual RS-232/485 COM and one LPT        |

| MCM-DSPIO | Dual RS-232/485 COM and one LPT        |

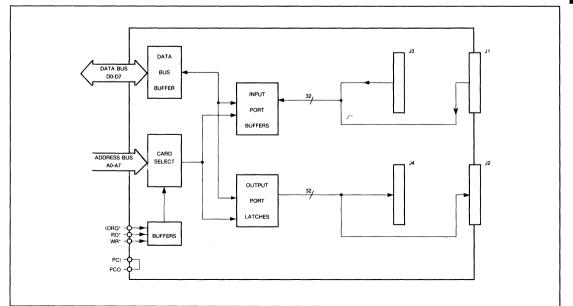

| LPM-PIO   | 32 Line Programmable CMOS Z80-PIO      |

| MCM-PIO   | 32 Line Programmable Z80-PIO           |

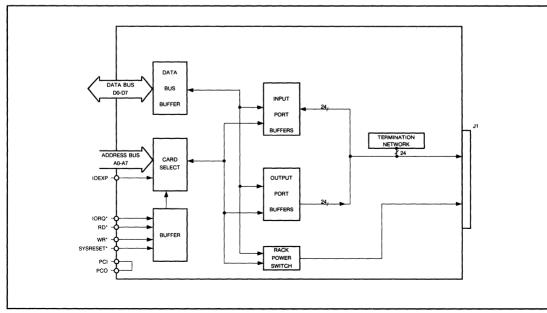

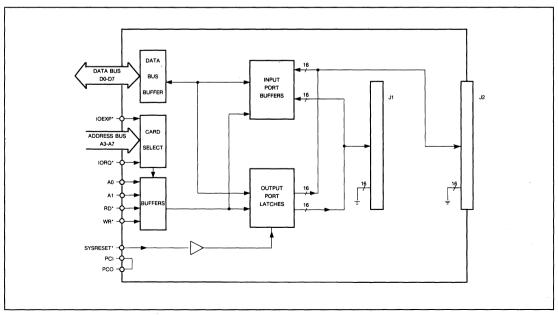

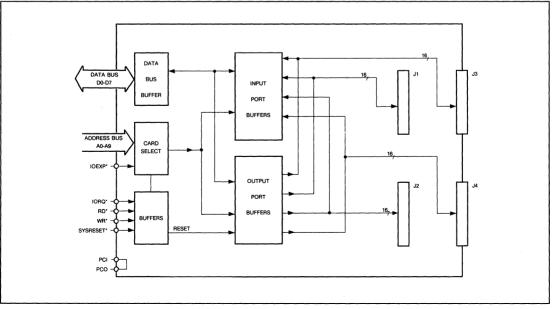

| LPM-PIO2  | 32 Input & 32 Output Lines             |

| MCM-PIO2  | 32 Input & 32 Output Lines             |

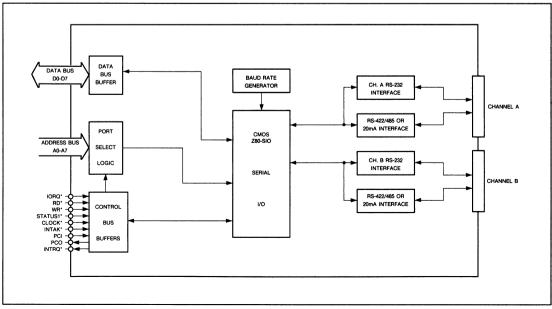

| LPM-SIO2  | Z80-SIO Dual Multiprotocol RS-232/20mA |

| MCM-SIO2  | Z80-SIO Dual Multiprotocol RS-232/20mA |

|           |                                        |

| LPM-SIO4 | Quad 82C52 Async RS-232/485    |

|----------|--------------------------------|

| MCM-SIO4 | Quad 82C52 Async RS-232/485    |

| LPM-SPIO | One RS-232 & 32 Parallel lines |

| MCM-SPIO | One RS-232 & 32 Parallel lines |

## Analog Input/Output

| Analog | Input/Output | Selection | Guide | - 85 |

|--------|--------------|-----------|-------|------|

|--------|--------------|-----------|-------|------|

| LPM-1280   | LPM-A/D12M with RTI Compatible Input                  |

|------------|-------------------------------------------------------|

| MCM-1260   | MCM-A/D12 with RTI Compatible Input                   |

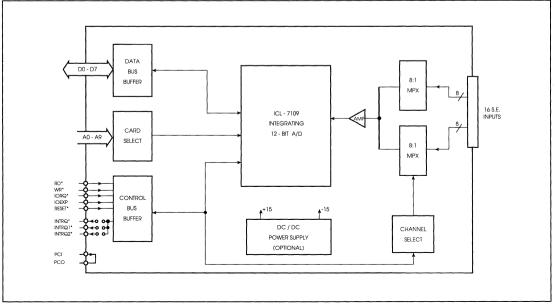

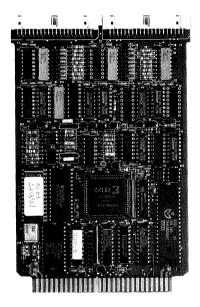

| LPM-7109   | CMOS 12-bit (plus sign) Integrating A/D Converter6-87 |

| MCM-7109   | 12-bit (plus sign) Integrating A/D Converter          |

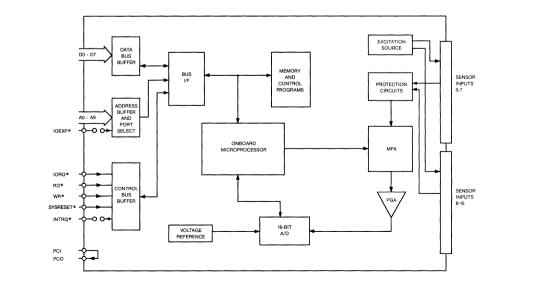

| MCM-7418   | 16-bit, 8-Channel Smart Sensor Interface              |

| MCM-7419   | 16-bit, 16-Channel Smart Sensor Interface             |

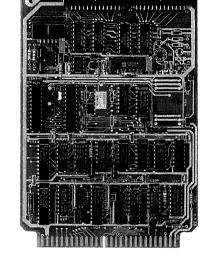

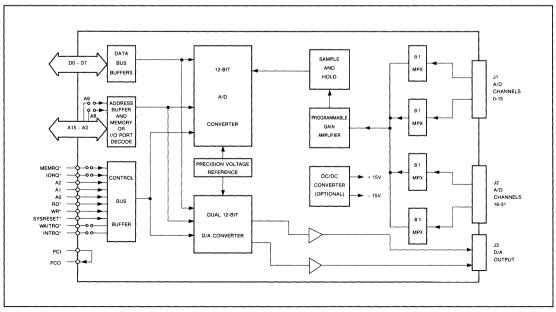

| LPM-A/D12M | 12-bit; 16 S.E. or 8 Differential A/D In              |

| MCM-A/D12  | 12-bit; 16 S.E. or 8 Differential A/D In              |

| LPM-AIO    | 12-bit; 32 Analog In, 2 Analog Out                    |

| MCM-AIO    | 12-bit; 32 Analog In, 2 Analog Out                    |

| LPM-AIO-8  | 12-bit; 8, 16, or 32 Analog In                        |

| MCM-AIO-8  | 12-bit; 8, 16, or 32 Analog In                        |

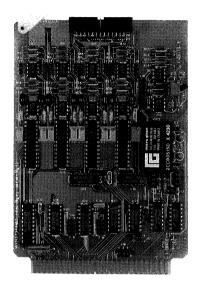

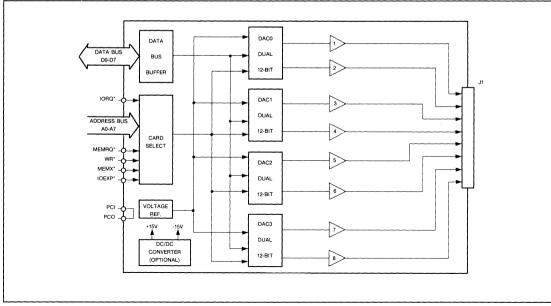

| LPM-D/A12  | 12-bit; 4 or 8 D/A Output Channels                    |

| MCM-D/A12  | 12-bit; 4 or 8 D/A Output Channels                    |

| LPM-D/A8   | 8-bit; 8 D/A Output Channels                          |

| MCM-D/A8   | 8-bit; 8 D/A Output Channels                          |

|            |                                                       |

## Miscellaneous

| Miscellaneous S | election Guide $\dots 6 - 103$                |

|-----------------|-----------------------------------------------|

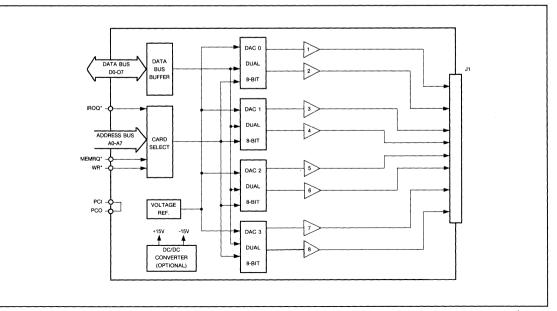

| LPM-7904        | CMOS STD Decoded I/O Utility Card             |

| MCM-7904        | Decoded I/O Utility Card                      |

| LPM-CLK         | Battery Backed Calendar Clock                 |

| MCM-CLK         | Battery Backed Calendar Clock                 |

| LPM-CTC         | Nine Channel, 16-Bit Counter/Timer            |

| MCM-CTC         | Nine Channel, 16-bit Counter/Timer            |

| LPM-KYBLCD      | CMOS Keyboard and LCD Operator Interface6-111 |

| MCM-KYBLCD      | Keyboard and LCD Operator Interface           |

| LPM-SBX         | Dual SBX Interface Card                       |

| MCM-SBX         | Dual SBX Interface Card                       |

| MCM-STATUS      | 32 LEDs and 32 Switch Inputs                  |

| PC-STD ADP      | PC to STD Bus Adapter                         |

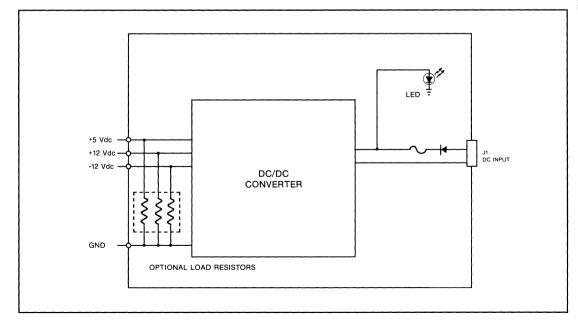

| PS12T12         | 12 VDC Input DC/DC Supply                     |

| PS24T12         | 24 VDC Input DC/DC Supply                     |

| PS48T12         | 48 VDC Input DC/DC Supply                     |

| STD-EXT         | STD Bus Extender Card                         |

| STD-WW2         | General Purpose Wire Wrap Card                |

. . .

## Card Cages and Accessories

## **Card Cages**

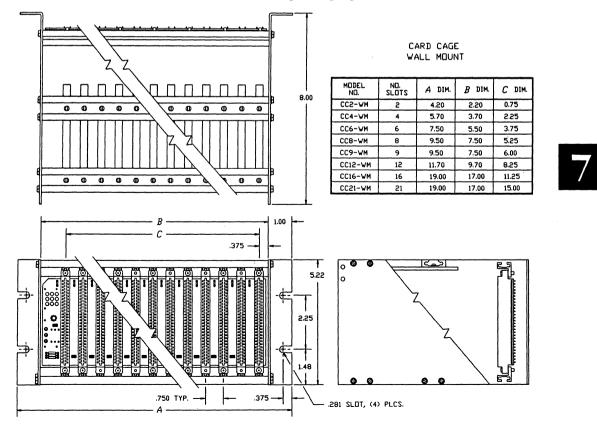

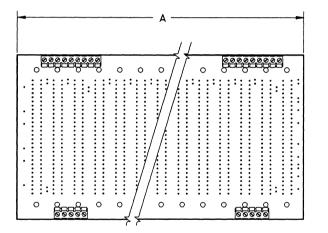

| MB-X            | STD Bus 3/4" Backplanes              |

|-----------------|--------------------------------------|

| CC-XX           | 3/4'' Card Cages with Backplanes     |

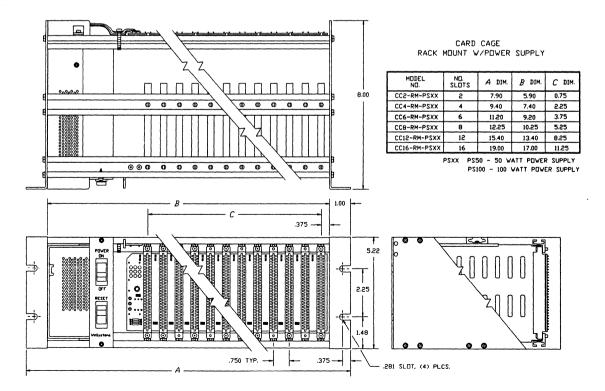

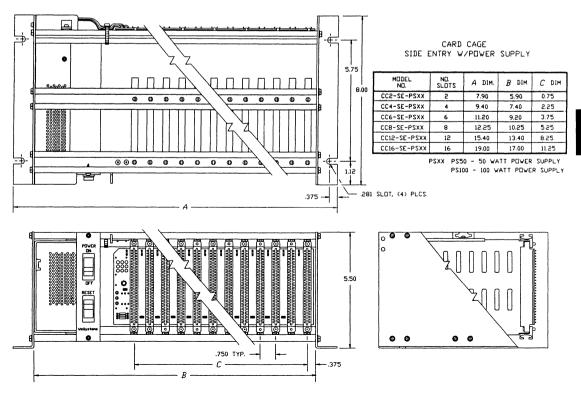

| CC-XX-PS        | 3/4'' Card Cages with Power Supplies |

| CC Series Chart | Backplane and Card Cage7-14          |

|                 | Quick Reference                      |

| BP-XX           | STD Bus 5/8" Backplanes              |

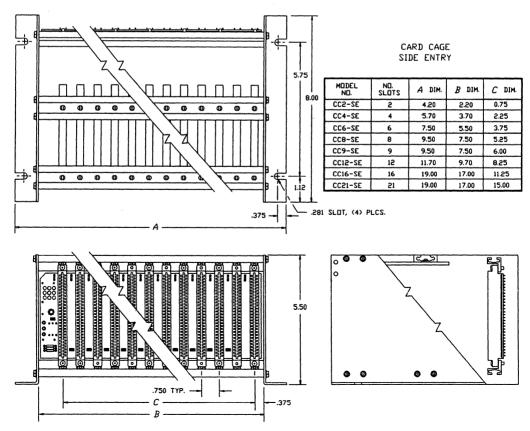

| CX-XX           | 5/8'' Card Cages with Backplanes     |

| CX-XX-PS        | 5/8'' Card Cages with Power Supplies |

| CX Series Chart | Backplane and Card Cage7-25          |

|                 | Quick Reference                      |

| Enclosures      | Enclosures and Rack Mount Chassis    |

### Accessories

| ADP-7409TB        | 8-Channel Field Termination Panel     |

|-------------------|---------------------------------------|

| Analog-ADP        | Analog Terminator                     |

| CBL-XXX-YY        | Cables for WinSystems' Products       |

| Cable Chart       | Quick Reference Guide                 |

| <b>TRM-Series</b> | Analog and Digital Termination Boards |

## Single Board Computers

## Chapter 8

| SBC25 | V25 Very Low Power SBC  | j |

|-------|-------------------------|---|

| SBC88 | 80C88 Multifunction SBC | ) |

### **SBX Modules**

## Chapter 9

| SBX-A/D12 | 12-Bit; 8 A/D Input Channels            |

|-----------|-----------------------------------------|

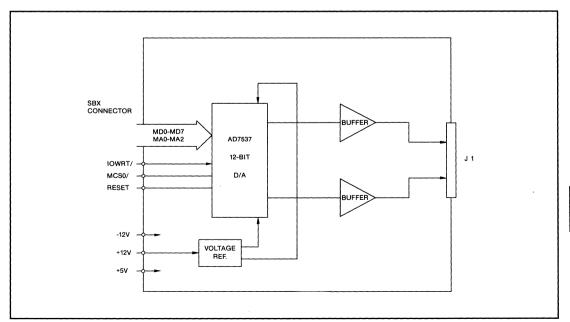

| SBX-D/A12 | 12-Bit; 2 D/A Output Channels           |

| SBX-OPTO  | 48 Channel Opto-22 Rack Interface Card  |

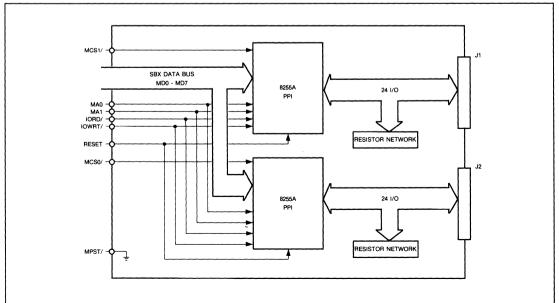

| SBX-PIO   | 48 Line 82C55A Programmable I/O9-9      |

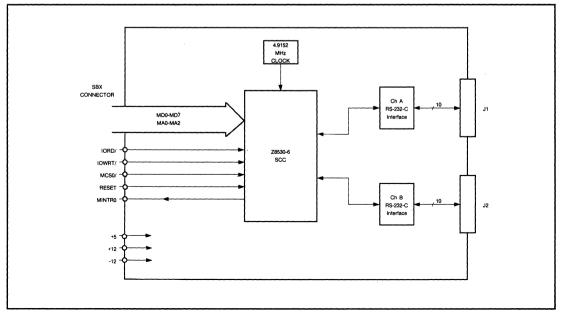

| SBX-SCC   | Dual 85C30 SCC Multiprotocol RS-2329-11 |

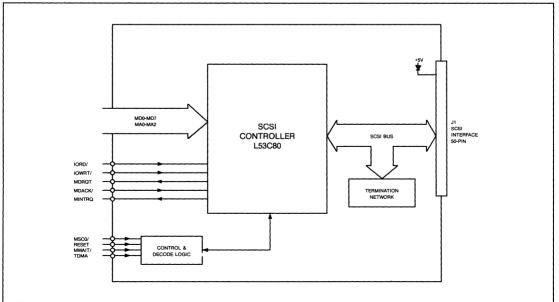

| SBX-SCSI  | SCSI Host Adapter                       |

| SBX-WW1   | General Purpose Wire-Wrap Card9-15      |

## STD Bus Specification and Application Notes Chapter 10

### STD Bus Specifications:

| STD Bus Specifications                            | 10 – 3 |

|---------------------------------------------------|--------|

| STD Bus Recommended Practice10                    | 0 - 17 |

| STD Bus 16-bit Data Transfer10                    | ) — 31 |

| STD-80 Series Multiprocessor Extension Addendum10 | 0-39   |

#### **Application Notes:**

#### 100 Series Marketing/Trends

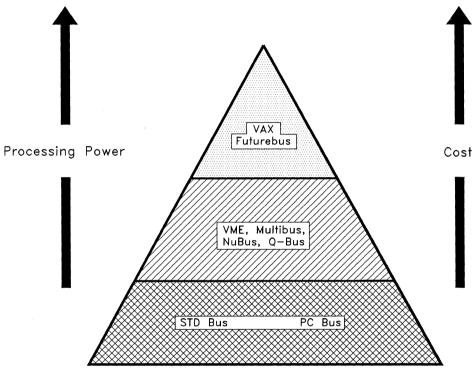

| AN0101: | STD Bus, the Industrial I/O Bus $\dots 10-55$                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0102: | STD Bus Directions for the 1990s $\dots 10-59$                                                                                                       |

| AN0103: | Do you really need a 32-bit Bus? $\dots \dots \dots$ |

| AN0104: | Important Questions about 32-bit Processing $\dots \dots 10-67$                                                                                      |

#### 200 Series STD Bus Specifications

| AN0201: WinSystems' 3/4" Card Cage Functional Consideration | s10-6 | 59 |

|-------------------------------------------------------------|-------|----|

|-------------------------------------------------------------|-------|----|

#### 300 Series Software - Programming

| AN0301: Ir | nportant ( | Duestions | about | ROM-DOS |  |

|------------|------------|-----------|-------|---------|--|

|------------|------------|-----------|-------|---------|--|

#### 400 Series Non-STD Bus Hardware

| AN0401: | Why ARCNET on the Factory Floor?                | · 73 |

|---------|-------------------------------------------------|------|

| AN0402: | What is MNP?                                    | · 75 |

| AN0403: | 28/32 PIN JEDEC Footprint Standard for SRAMs10- | - 77 |

| AN0404: | EPROM Memory Socket Configuration10 –           | · 79 |

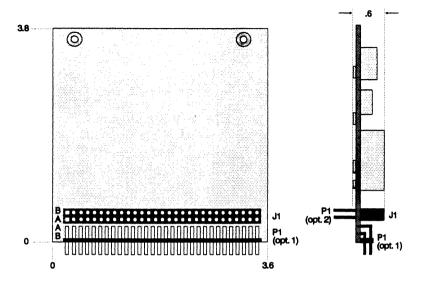

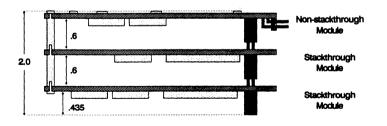

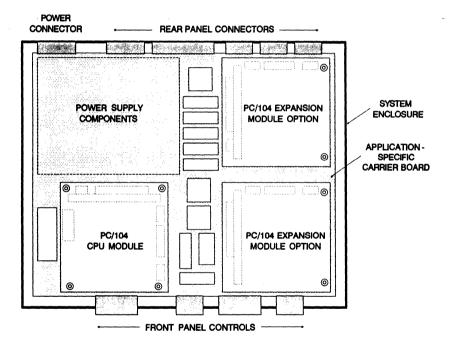

|         | About the PC/104 Standard10-                    |      |

## **General Information**

| General Information                 | 1-3    |

|-------------------------------------|--------|

| Product Overview                    | 1-5    |

| New Products                        | 1-7    |

| Non-Standard Products               | 1 – 13 |

| Warranty and Life Support Statement | 1 – 15 |

| Interchangeability Guide            | 1-17   |

## **General Information**

#### WinSystems

Since its founding in 1982, WinSystems has designed and manufactured a wide range of STD and CMOS STD Bus products. The company has gained an excellent reputation for innovative design and engineering skills and has become recognized as a leading supplier of STD Bus products.

WinSystems' products and customer support are superior in many areas:

- Full range of product solutions. WinSystems offers solutions from high-end 80486 fully compatible PC-AT systems to low cost single board computers running the ROM-DOS embedded operating system.

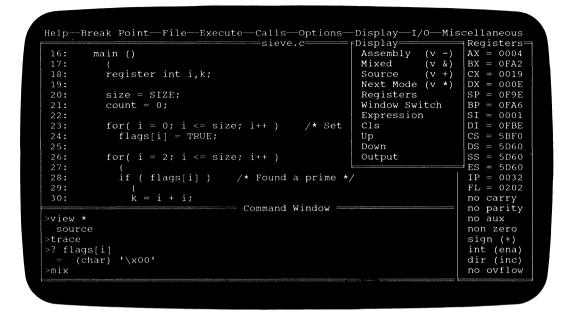

- Software Solutions. WinSystems supports PCcompatible operating systems, networks, and development tools to allow the customer to quickly and easily design, develop and debug applications. WinSystems also offers drivers for selected I/O cards, and example start-up code and application examples to facilitate the programmers' job.

- Ruggedized Design. WinSystems' products are designed and manufactured to lead performance and reliability standards. Our LPM series of CMOS product will operate from battery power and at temperature extremes from -40° to +85° Centigrade.

- Total Engineering Support. Every customer's application is unique requiring special solutions. WinSystems' Applications Engineers standby their customers with assistance before, during, and after the installation is complete.

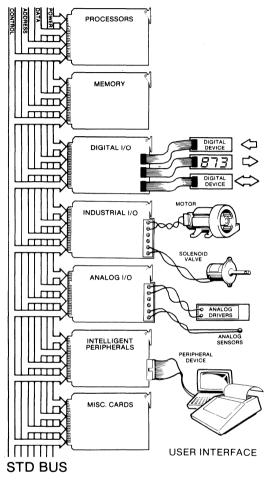

#### The STD Bus

In the late 1970s, Mostek and Pro-Log Corporation developed the STD Bus in a joint effort to produce a reliable, electronic data bus for industrial applications. Jerry Winfield, President of WinSystems, was the system architect for Mostek of the STD Bus who defined and developed the first products ever introduced to this industry standard.

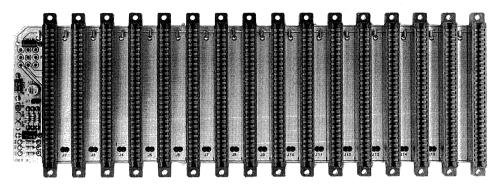

The STD Bus is the approved, IEEE-961 standard microcomputer bus which is popular worldwide with

over 150 manufacturers. The STD Bus has a number of advantages over other bus architectures used in industrial applications such as the PCBus and Multibus. Its simple interface, smaller card size  $(4.5" \times 6.5")$ ; solid, nearly square peripheral cards, and strong card mounts tolerate shock and vibrations, making the STD Bus ideal for rugged industrial environments.

The STD system is also more modular than existing busses because its smaller cards contain fewer functions. This allows systems designers and integrators to select precisely the functions they need. In addition, the card is less expensive -- an important consideration in industrial and OEM markets.

The STD Bus has evolved from 8-bit 8085/Z80 performance to 16/32-bit PC/AT minicomputer performance levels while retaining compatibility with the earliest product designs. This migration path philosophy protects the user's time and hardware investment. This continuity is important in applications where a long product life cycle and assured source of supply is required.

The STD Bus has an active manufacturers' group, STDMG, (which WinSystems supports and is an active member) to monitor standards, specifications, and new technical developments which assures an orderly, evolutionary growth. This evolution has occurred by adapting to newer technologies for higher performance and more cost-effective solutions. The net result is a lasting standard for industrial applications that will work with bus products today and in the future.

#### Quality

WinSystems' manufacturing expertise and aggressive quality control have produced a respected line of STD Bus products known for their reliability and their tolerance of the rigors of industrial, military and scientific applications. WinSystems demands the highest quality workmanship standards in all of its products. All elements of the product from design, layout, fabrication, testing, and inspection are carefully checked and monitored for conformance to standards. The boards and systems are burned-in and tested before shipping.

## **Product Overview**

Drawing from our application-focused engineering expertise, we have developed an inventory of hardware "building blocks" which can be configured into products which solve industrial automation problems in response to your specific needs. We offer a wide variety of both software and hardware on the STD Bus and non-bus single board computers. The products exhibited throughout this catalog can be configured in many different ways to provide specific solutions to your needs.

We think it's important to look at our products from the customer's perspective. Feedback from our customers on their current and future requirements is integral to our product planning and development. In fact, every product in this catalog was directly influenced by our customers.

#### **IEEE 961 STD Bus**

We are a full line supplier of the industry standard IEEE 961 STD products. Our "MCM" product line includes 8-bit to 32-bit CPUs, memories, I/O, and special function cards. A wide selection of backplanes, card cages and card cages with power supplies complement the over 150 different WinSystems' STD Bus cards.

#### **CMOS STD Bus**

We are also the largest supplier of CMOS STD Bus products in the world with our "LPM" Series of boards. CMOS is needed in harsh environments where low power, wide temperature operation (-40° to +85°C), supply voltage tolerance (+10%), and high electrical noise immunity are required. Low power means low system operating temperatures, no fans, smaller power supplies, and sealed enclosures to meet the rigors of the factory floor.

#### **Replacement Products**

We offer over 100 replacement boards for the most popular Mostek (Mizar), Analog Devices, Pro-Log, and DY-4 STD and CMOS STD Bus cards. This option provides you with a cost-effective alternative when price, delivery, and continued support is critical. Also, we offer a 30-day trial evaluation period for these plug replacement cards so that you can have a no risk comparison of these products.

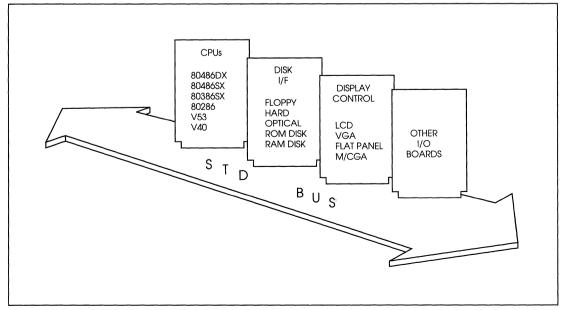

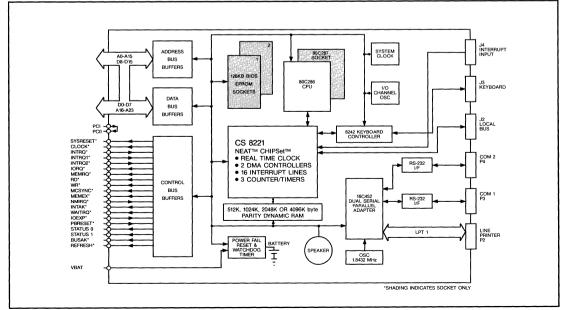

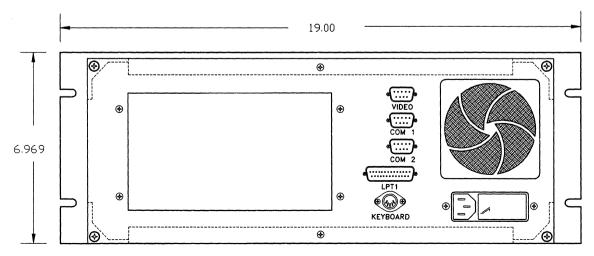

#### STD-AT Systems

Our STD-AT is a true PC-AT software compatible, rugged, industrial computer on the STD Bus. It combines the powerful processing capability of the 80286/386/486 and vast library of PC-DOS software with the reliability and industrial I/O interfaces of the open architecture IEEE 961 STD Bus. This PC compatibility provides you with the ability to use the extensive pool of PC applications software, utilities, networking, and development tools without modification. The result is a completely AT-compatible system with CPU operational speeds from 10 to 50 MHz.

#### Single Board Computers

We offer a number of single board computers for special applications requirements. These are units that are optimized for low cost and high functionality. The SBC25 and SBC88 are two non-STD Bus products. We also offer a number of STD and CMOS STD Bus Single Board Computers (SBCs) that can function in a standalone mode without the need for additional I/O or memory cards for embedded systems applications. We are a manufacturer of standard products but we additionally welcome the opportunity to examine special configurations to your existing product modifications or totally new designs of SBCs.

#### **SBX Multimodules**

Our SBX cards are small  $(3.7" \times 2.85")$  specialized, I/O mapped boards that plug into a host via the IEEE P959 Bus. These cards enable you to economically expand or modify a system with a standard product while obtaining maximum performance. These SBX boards can be used on our STD Bus, CMOS STD Bus, SBCs, and Multibus boards as well.

## New Products in this Databook

#### 80486DX/SX SBC

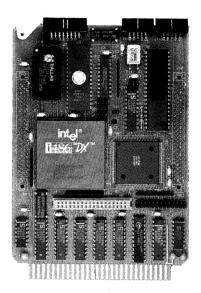

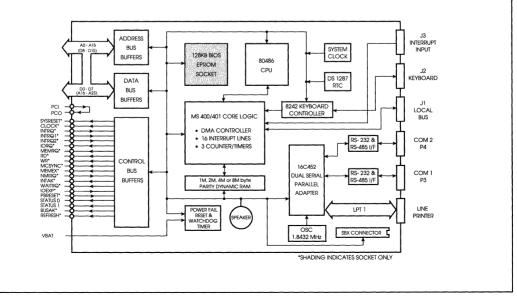

The MCM-486DX offers up to a 50 MHz microprocessor which comes equipped with a maximum of 8 Mbytes of onboard parity-protected DRAM configured. With an onboard Mosel MS401 32/64-bit datapath chip, automatic interleaving creates an effective 64-bit-wide memory bus. The 64-bit data path permits one-clock burst reads and memory post-write operations to nearly double the memory accesses compared with just using 32-bit data paths. This capability offers lower cost and high performance in non-cache modes. (See page 4-5)

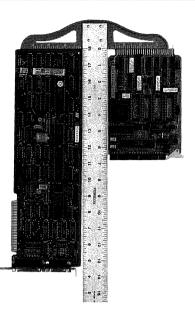

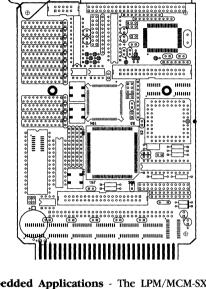

#### Low Cost 80386SX SBC

The LPM/MCM SX386 is an unbeatable multi-purpose board for use with either a STD Bus system or as a standalone controller with PC/104 expansion modules. It is fully functional for industrial applications and will run without disks, keyboard, or monitor. It is designed for applications where PC power and performance are needed in a small system, but offers rugged hardware suitable for operation in harsh or remote environments. (See page 4-39)

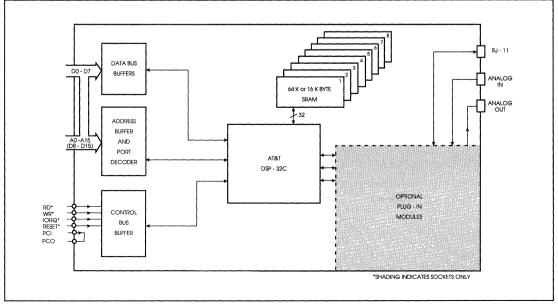

#### **Digital Signal Processor**

Our new MCM-DSP32C single board processor can handle computation-intensive embedded applications at the high speed of a DSP chip. It plugs into a STD Bus, and its 32-bit architecture operates at a clock frequency of 50 MHz. In key benchmark tests, this board can execute a 1024-point complex FFT in 3.3 msec, multiply two 4x4 matrices in 6.16 microseconds, and compute the response of a complex adaptive FIR filter in real-time at 80 nanoseconds/tap. The MCM-DSP32C offers a high performance and cost effective solution to many traditional and emerging signal-processing applications. (See page 4-35)

#### Low Cost V-53 SBC

Bringing IBM PC/AT performance to the STD Bus, the LPM/MCM-SBC53 is a high performance, 16-bit, V53 STD Bus single board computer designed for harsh embedded applications where small size, economical prices, and 80286 performance are required. It combines the most popular I/O functions used in most applications onto a single card. And it dissipates a maximum of only 1.5W. The combination of the CPU and peripheral mix makes it ideal for high performance data control applications. (See page 4-41)

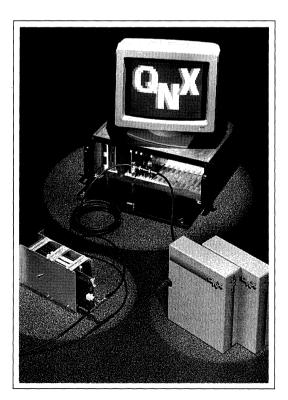

#### **Real-Time Embedded O.S.**

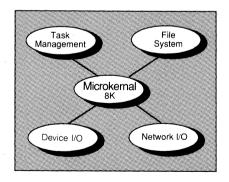

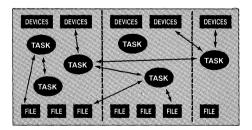

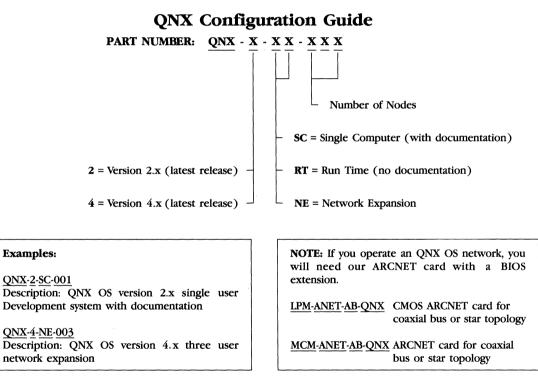

QNX is a distributed processing real-time multiuser and multi-tasking operating system which is now available on our industrial STD-AT systems. It can operate on a network or as a standalone unit. Configurations vary from small diskless embedded systems to complete rack mounted disk-based systems with graphics. The combination provides you with the perfect blend of software and hardware platforms designed for use in factory automation and harsh industrial environments. (See page 3-13)

#### Flat Panel/CRT VGA Controller

The LPM/MCM-FPVGA is a versatile LCD VGA controller that provides support for basic VGA modes for an LCD or CRT, and extended 800 x 600 resolution graphics on the CRT. It provides excellent display quality, with up to 64 shades of gray on monochrome Super-Twist Nematic (STN) LCD panels and a direct connection capability for active matrix color LCD panels. The board can display on the flat panel and on an VGA CRT simultaneously. (See page 6-31)

#### **Flat Panel Controller**

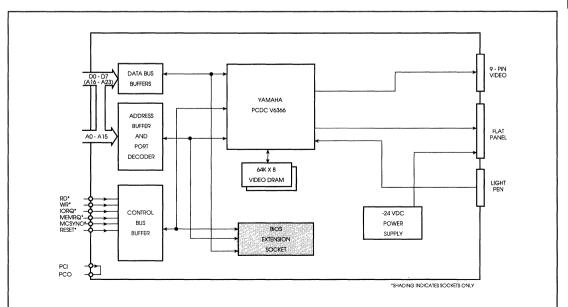

The LPM/MCM-FPC is a low cost universal display card that functions as a flat panel display controller. CGA, Hercules and MDA graphics modes are supported. An onboard state machine performs autoinitialization, thereby eliminating the need for special driver software. Based upon the Yamaha V6366, the LPM/MCM-FPC will support all three flat panel display technologies (EL, Plasma, and Liquid Crystal) with full text and graphics. (See page 6-29)

#### Keyboard/LCD Interface

The LPM/MCM-KYBLCD board is well suited for applications where both an inexpensive keyboard and LCD interface are needed — such as system control, data entry, status display, and operator prompting. It is also useful for system development, testing and training applications. It supports  $4 \times 4$  or  $5 \times 4$  matrix keyboard inputs and 1 to 4 line parallel LCD displays with up to 80 characters from companies such as Hitachi, Epson, Seiko, Densitron, Sharp and others. (See page 6-111)

#### **IEEE-488** Controller

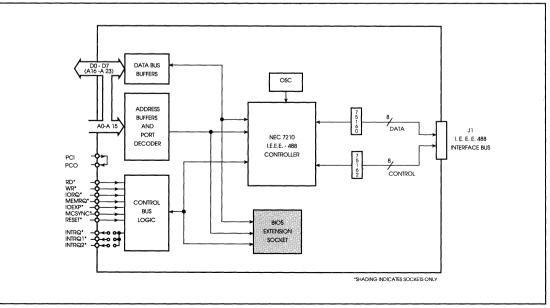

Designed to meet all of the control specifications required for talker, listener and controller as specified by IEEE 488-1978, our LPM/MCM-488 is an IEEE-488 interface board for the STD Bus. This interface makes possible the transfer of data between thousands of IEEE-488 compatible devices. The board is based upon the NEC 7210 allowing its use with STD Bus DOS compatible and ROM-DOS embedded STD Bus systems. (See page 6-49)

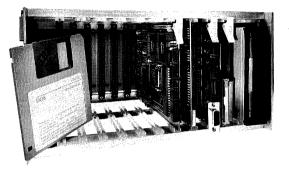

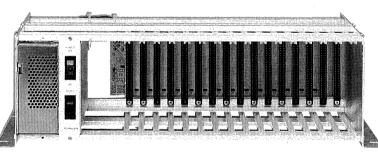

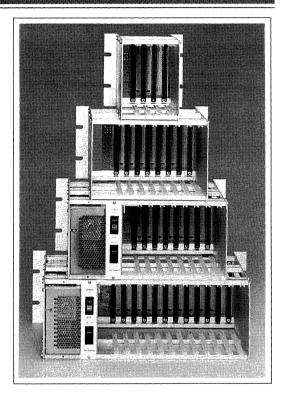

#### **Racks and Backplanes**

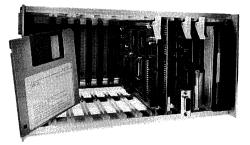

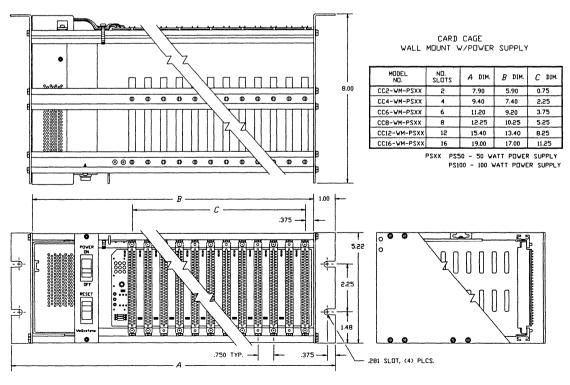

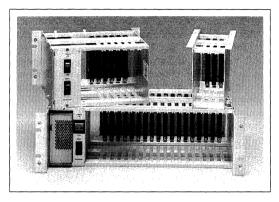

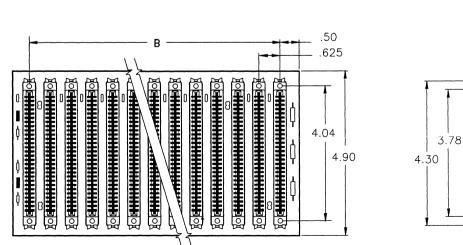

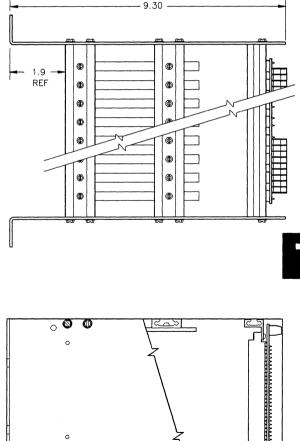

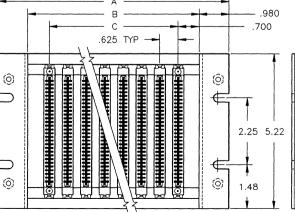

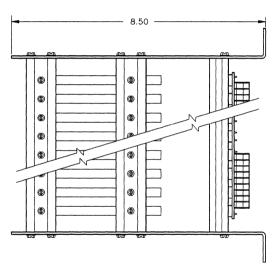

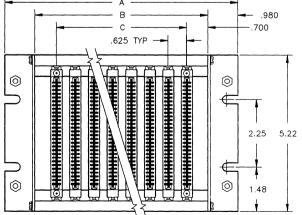

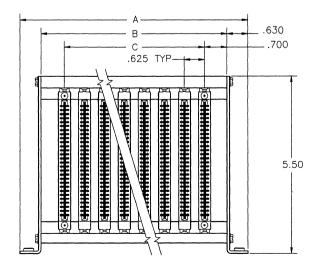

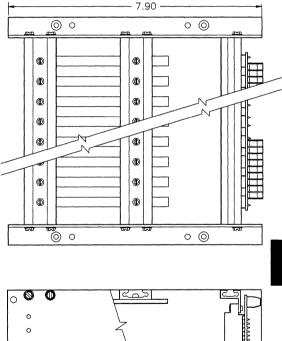

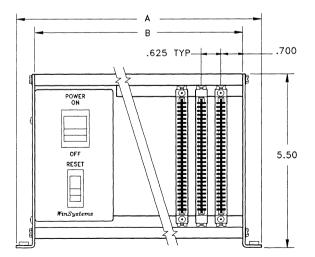

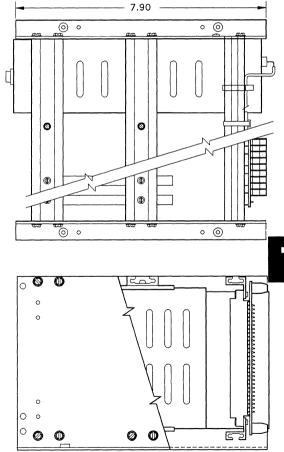

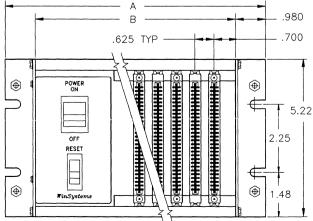

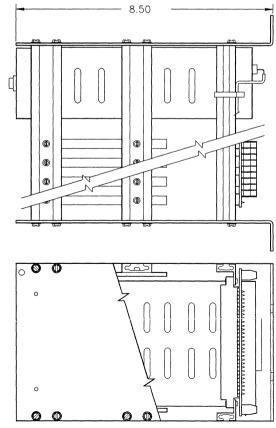

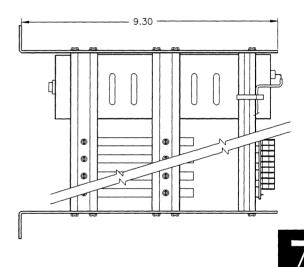

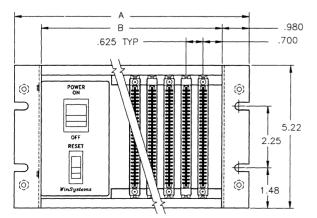

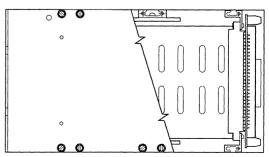

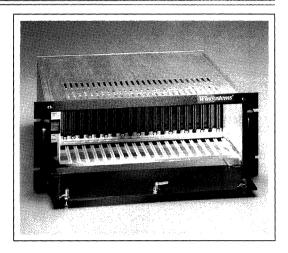

The CX Series is a new line of STD Bus card racks and backplanes. Based on 0.625" centers with vertical card orientation to take advantage of convection cooling, the CX card cages allow either a smaller enclosure size or provide more card slots when compare to other card cages. They are available in 3-to 26-slot versions in 3-slot increments. In addition, 50W or 100W power supplies are available to power the racks. Backplanes support high-performance STD Bus processors, including the new 16/32-bit types with full 16-bit data transfers. (See page 7-15)

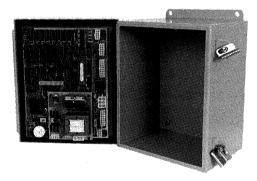

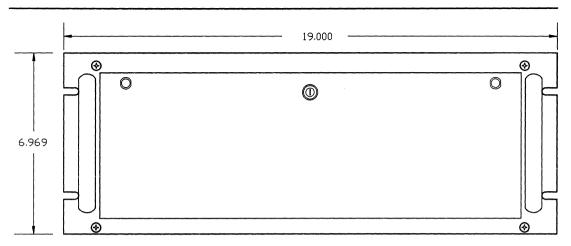

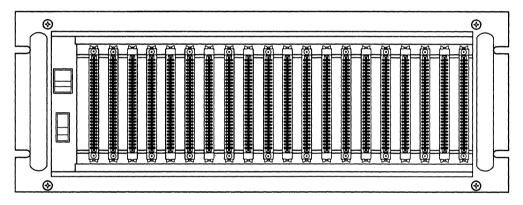

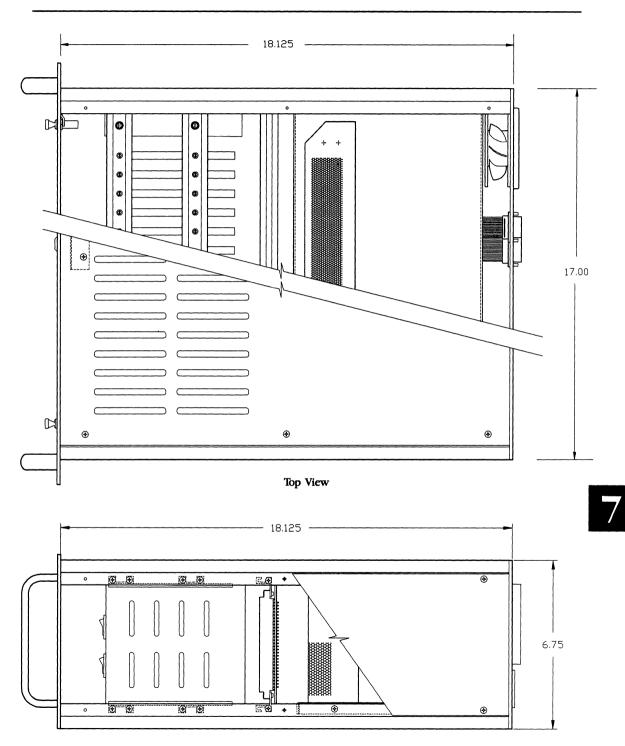

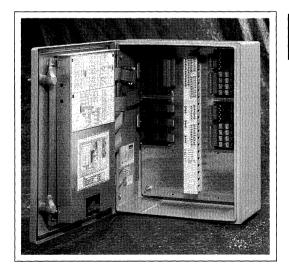

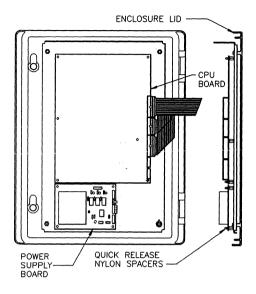

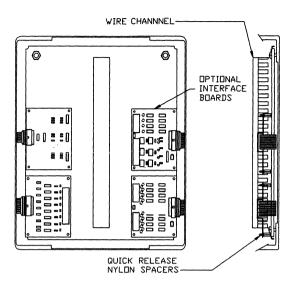

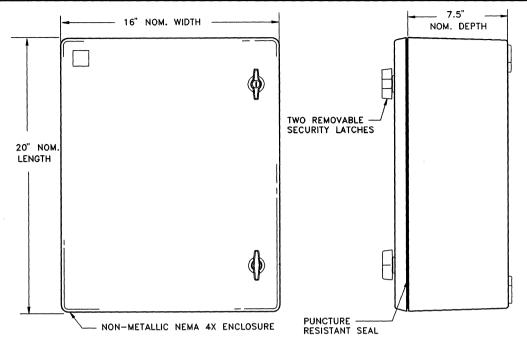

#### **STD Bus Enclosures**

Our STD Bus enclosures provide a foundation for STD DOS XT/AT and non-DOS embedded systems. They serve as a platform for industrial computer based products, enclosures for self-contained OEM systems, or as a prototyping shell for systems development. They are user configurable since the CPU, I/O and memory boards, disk drives, power supplies can all be added to the unit to customize it to the specific application. (See page 7-27)

#### 12-Bit SBX A/D card

The SBX-A/D12 card provides up to eight channels of 12-bit analog input on a single SBX module. Any channel can be configured as unipolar or bipolar for maximum flexibility. The board is designed to serve as a complete data acquisition system with a 100KHz sampling rate. (See page 9-3)

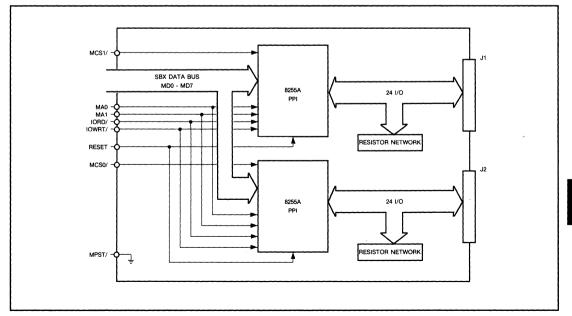

#### **Opto-22 Rack Interface SBX Card**

The SBX-OPTO is a compact, SBX multimodule, general purpose 48-line parallel I/O controller based upon two 82C55A Programmable Peripheral Interface (PPI) devices. These lines are organized as 2 groups of three 8-bit I/O ports that interface directly to 2 independent industry standard 4, 8, 16, and 24-I/O module mounting racks (Opto-22, Gordos, etc.). (See page 9-7)

## 1

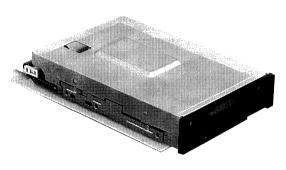

#### 21 Megabyte Floptical Disk Drive

Providing hard disk storage capacity with the removable, low cost convenience of a floppy, the FD3-21M is a high capacity floppy designed for escalating storage demands. It combines optical and magnetic recording technologies to achieve very high capacities (21 MB), yet still reads and writes 3.5" double density (720 KB) and high-density (1.44 MB) floppy disk formats. (See page 6-23)

#### Disk I/O Support Controller

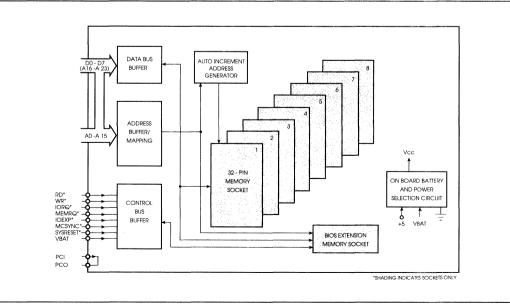

The LPM/MCM-DSKIO is a general purpose DOS system support card for use with the LPM/MCM-SBC41, LPM/MCM-SBC53 and other V40/V53 class CPUs. The card provides the peripheral interface electronics for floppy and hard disks, keyboard interface, real time clock, and BIOS ROM extension socket. It allows embedded SBCs to be configured to work with rotational media for complete PC-software compatible systems. (See page 6-11)

#### Universal Solid State Disk

Our LPM/MCM-USSD is an I/O mapped, universal STD Bus Solid State Disk (SSD). It can be populated by the user with up to 4 megabytes of RAM, EPROM, or PEROM (Flash). And four cards can be grouped for 16 MByte of SSD. The card allows you to substitute onboard semiconductor devices in applications where the environment is too harsh for mechanical hard disks or floppy disk drives, plus it has significant speed advantages. It is designed to store programs and data for applications such as data collection and logging, diagnostics, etc. (See page 6-19)

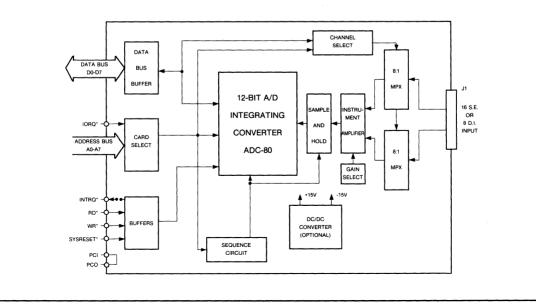

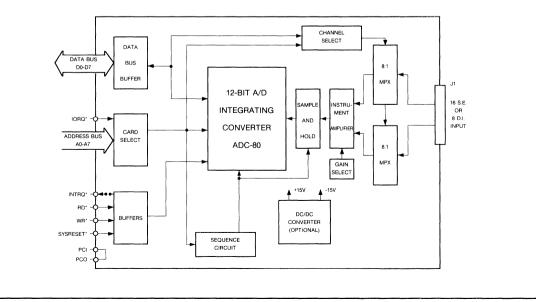

#### Integrating A/D Converter

The LPM/MCM-7109 is a very low cost, 12-bit (plus sign) integrating A/D converter for use in data acquisition and control applications. A dual slope integrating converter provides the benefits of high frequency noise reduction through signal averaging while offering a rate of up to 30 conversions per second. (See page 6-87)

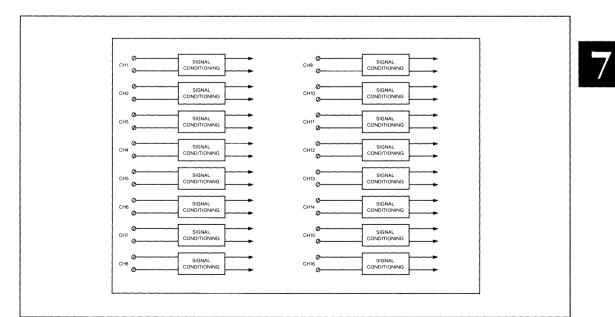

#### Analog and Digital Termination Boards

Our series of termination boards provide both connection and signal conditioning from field wiring to our STD Bus I/O cards and standalone single board computers such as the SBC25 and SBC88. For ease of mechanical layout and packaging, all termination boards are the same size (only  $4.1" \ge 5.65"$ ) and mounting style, offering excellent configuration flexibility. (See page 7-47)

## **Non-Standard Products**

In addition to our standard products, we welcome the opportunity to examine and quote special purpose product designs, modifications, configurations and packaging. These opportunities may involve small modifications to existing cards, to complete designs of totally new STD Bus and non-STD Bus products such as CMOS STD Bus, CMOS PC Bus or other standalone single board computers.

Examples of special product configurations are as followings:

Special card cage mounting configurations Power supplies in card cages Card cages with no motherboards Card cages with multiple motherboards Cards with all sockets Cards with special latching connectors Special memory card decode options

Contact our Marketing Department so that a quote for specialized product configurations, special packaging or additional products can be obtained.

#### MACHINE TOOL SOCKETS

We use production double leaf low profile dip sockets for selected NMOS and TTL devices on the PC boards. These give 100% more contact area than the regular single leaf sockets used by other STD manufacturers; however, certain applications require an even higher quality socket. We can supply machine tool sockets which have pin sockets for high reliability and high retention. This type of socket design gives the best gripping action on the integrated circuit and is used where extra protection is needed from extreme shock and vibration.

#### **CONFORMAL COATING**

Our boards can be coated with a transparent lacquer type material to protect the boards against air, dirt, oxidation, water, salt spray, acids, alkalais and fungi. This material is ideal for protection of these boards in harsh environments. It is non-conductive, nonflammable, and has a low order of toxicity. It has a dielectric strength of 1500 volts/mil. Furthermore, it does not attack plastic, rubber, paints, or metals and facilitates compliance with environmental OSHA standards. We use a Miller-Stephenson chemical MS-470 urethane coating that meets MIL-I46058C type UR. It is applied as an aerosol. Spot recoating of areas is quick and easy. It contains an ultraviolet indicator that is visible under U.V. light for inspection purposes. The coating can be readily removed with MS-114 Stripper.

#### **PIN-AND-SOCKET CONNECTORS**

Some customers' applications require pin-and-socket connectors rather than the regular edge STD Bus card connectors for certain hardened and non-tactical military environments. We have adapted selected boards and backplanes to support a 56-pin military grade M55302/57 connector.

The combination of this connector with our industry standard CMOS STD Bus architecture provides the best performance, reliability, and cost-effective solutions if a Mil-Spec computer is not required. Compared to equivalent Mil-Spec solutions, this approach is over 20 times less expensive. We have chosen the MIL-55302 for these reasons:

- Pin-and-socket connectors

- Low insertion and extraction force

- High reliability closed entry socket

- Multiplicity of pin-to-socket contact points

- 5 amps current per pin

- Low contact resistance due to greater average contact area

- Unsurpassed shock and vibration characteristics

- Superior performance to DIN 41612-style connectors

- Optional polarization keys

- Multiple sources for connectors

- Easy modification to existing PCB designs

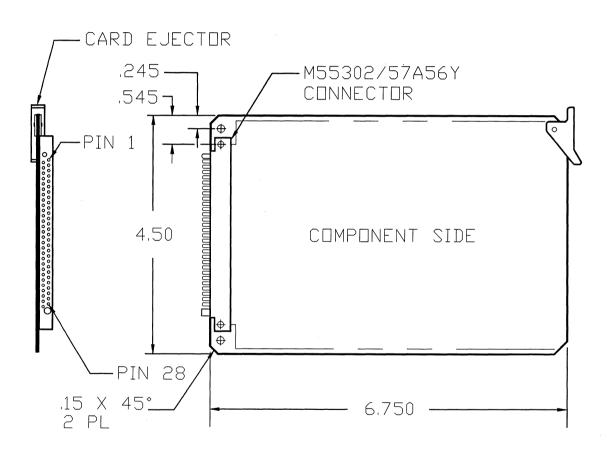

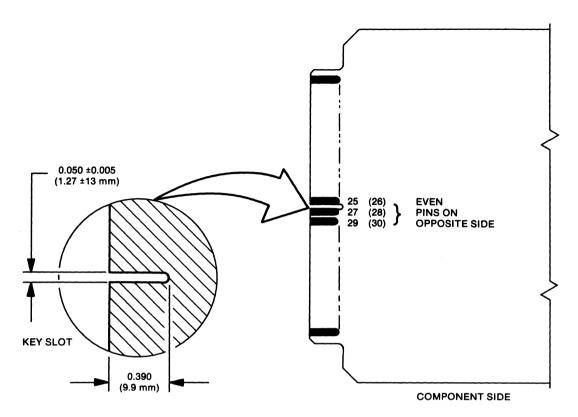

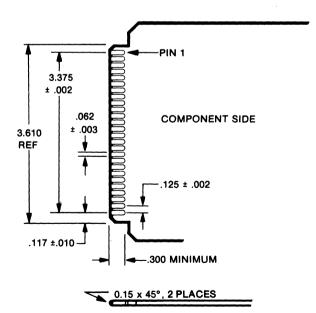

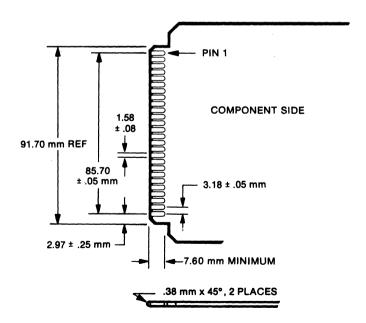

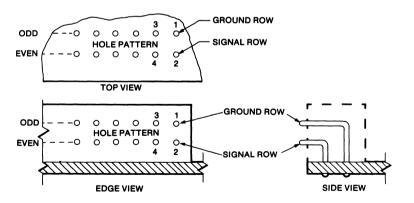

**Pin-and-Socket Connector** - The MIL-55302 type connector is a dual row, high density interconnection system on 0.100 inch centers. This differs from the STD Bus 0.156 inch standard. The interconnect system has polarizing shrouds to prevent plugging the card in backwards. The STD Bus board is lengthened by 0.25 inches and a male connector has been added.

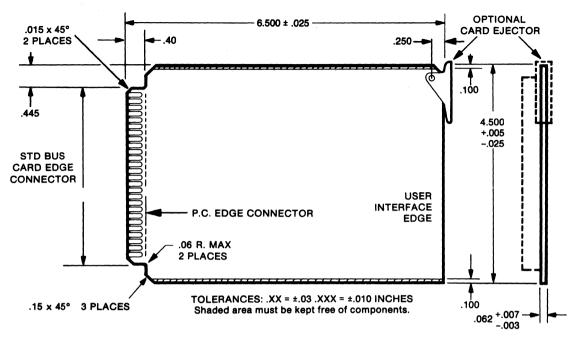

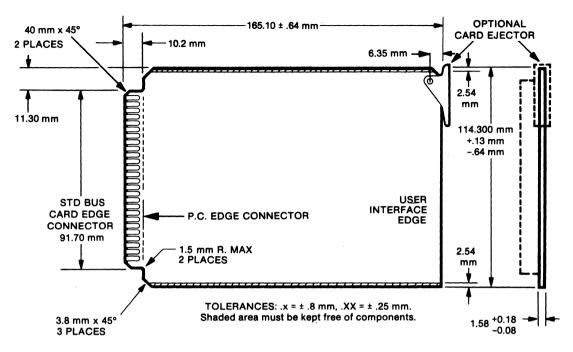

**Card Dimensions** - The circuit card is now  $4.5 \ge 6.75$  inches. This length dimension is increased by 0.25 inches from the standard STD Bus  $4.5 \ge 6.5$  inch card. The additional length permits a designer to use the same basic card design artwork and choose either a card edge or pin-and-socket connector.

Polarization - The construction of the connector along with the mounting of the STD Bus card guides prevents boards from being plugged in backwards. Optional polarization pin hardware allows keying of the individual card to a specific slot on the backplane for maximum safety.

**Ordering information** - Contact our application engineers for more information about this XIM product family.

## Warranty

1

WinSystems warrants products manufactured by WinSystems against defects in materials or workmanship for two years from the date of purchase from WinSystems. This limited warranty is subject to the following terms and conditions:

- A. If the product has defects in materials or workmanship, WinSystems will repair or replace the products, at WinSystems' sole option, at no charge to you for the duration of this warranty.

- 1. To obtain service under this warranty, obtain a return authorization number (RMA). In the United States, contact the WinSystems' Service Center for a return authorization number. Outside the United States, contact your local sales agent for a return authorization number.

- 2. You must send the product postage prepaid and insured. You must enclose the product in an anti-static bag to protect it from damage by static electricity. WinSystems is not responsible for damage to the product due to static electricity.

- B. This warranty does not apply to any products which have been modified, altered or tampered with; to any products which have been subject to abuse, accident, improper installation or misuse; to any products whose serial numbers have been removed; or to any products which have been repaired or serviced by other than an authorized representative of WinSystems.

- C. This warranty does not extend to and shall not apply to products or components of systems not

manufactured by WinSystems. Products not manufactured by WinSystems are limited to the warranty provided by the original manufacturer.

- D. For the repair or replacement of any products not covered by this warranty, WinSystems will repair or replace such products, at WinSystems' sole option, at WinSystems' current charges for labor and materials.

- E. THERE ARE NO WARRANTIES BY WINSYSTEMS EXCEPT AS STATED HEREIN. THERE ARE NO OTHER WARRANTIES EXPRESSED OR IMPLIED INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND OF FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT SHALL WINSYSTEMS BE LIABLE FOR CONSEQUENTIAL, INCIDENTAL OR SPECIAL DAMAGES INCLUDING, BUT NOT LIMITED TO, DAMAGES FOR LOSS OF DATA. PROFITS OR GOODWILL. WINSYSTEMS' MAXIMUM LIABILITY FOR ANY SUCH BREACH OF THIS AGREEMENT OR OTHER CLAIM RELATED TO ANY PRODUCTS, SOFTWARE, OR THE SUBJECT MATTER HEREOF, SHALL NOT EXCEED THE PURCHASE PRICE OR LICENSE FEE PAID BY CUSTOMER TO WINSYS-TEMS FOR THE PRODUCTS OF SOFTWARE OR PORTION THEREOF TO WHICH SUCH BREACH PERTAINS.

## Life Support Policy

WINSYSTEMS' PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF WINSYSTEMS CORPORATION. As used herein.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonable expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

## Interchangeability Guide

WinSystems offers a growing line of over 90 plug replacement cards for the most popular Mostek (Mizar), Pro-Log, Analog Devices, DY-4, and Data Translation STD and CMOS STD Bus cards. Processor, memory, I/O cards and card cages are included in the list. The concept of a generic alternate source of product was begun by WinSystems to give the customer a choice of vendor.

The real benefit to the volume users of industrial standard STD Bus products is that another source of supply can be secured without costly redesign or lengthy evaluation cycles. This provides a cost effective alternative when price, delivery, and continued support are critical.

WinSystems, Inc. offers a free 30 day trial evaluation period for its plug replacement cards. This allows a no risk comparison of the product. Contact WinSystems' for further information on this program. WinSystems has defined two categories of replacement boards: Functional and Nearest Replacement. They are defined as follows:

- Functional Replacement: Suggestions are based upon the similiarity of mechanical and electrical characteristics as reported by the manufacturer's published data. Interchangeability is not guaranteed. Before selecting a device as a substitute, compare the specifications and programming considerations.

- Nearest Replacement: Suggestions are based on the similarity of electrical characteristics as reported in the manufacturer's published data. Interchangeability is not guaranteed as these parts usually have slightly different I/O pin configurations and/or programming considerations. Before selecting a device as a substitute, compare the specifications. Since STD bus designs vary widely, it is possible that similar boards from two or more manufactures will satisfy an application. Therefore slight mechanical or electrical variations should not disqualify the nearest equivalent.

## STD BUS

## **CROSS REFERENCE/INTERCHANGEABILITY GUIDE**

| Manufacturer's<br>Product | Functional<br>Replacement | Nearest<br>Replacement | Manufacturer's<br>Description |

|---------------------------|---------------------------|------------------------|-------------------------------|

| MOSTEK (Mizar)            |                           |                        |                               |

| MK77650-00                | MCM-PIO                   |                        | MDX-PIO; 2.5 MHz              |

| MK77650-04                | MCM-PIO                   |                        | MDX-PIO-4; 4 MHz              |

| MK77651-00                | MCM-SIO2                  |                        | MDX-SIO; 2.5 MHz              |

| MK77651-04                | MCM-SIO2                  |                        | MDX-SIO; 4.0 MHz              |

| MK77666                   | MCM-D/A8                  |                        | MDX-D/A2727/8; 8-bit D/A      |

| MK77670-00                | MCM-SIO2                  |                        | MDX-SIO2 dual serial I/O      |

| MK77670-04                | MCM-SIO2                  |                        | MDX-SIO2-4; 4 MHz             |

| MK77674                   |                           | MCM-A/D12              | MDX-A/D8; 8-bit A/D           |

| MK77676                   | MCM-SIO2A                 |                        | MDX-422N; dual RS-422         |

| MK77754-00                | MCM-DRAM64                |                        | MDX-DRAM16; 16Kb, 2.5 MHz     |

| MK77754-04                | MCM-DRAM64                |                        | MDX-DRAM16-4; 16Kb, 4 MHz     |

| MK77759                   | MCM-UMC                   |                        | MDX-UMC; 8 24-pin sockets     |

| MK77760                   | MCM-7706-4L               |                        | MDX-BRAM4; 4K battery RAM     |

| MK77761-00                | MCM-DRAM64                |                        | MDX-DRAM32A; 32Kb dynamic     |

| MK77761-04                | MCM-DRAM64                |                        | MDX-DRAM32A-4; 32Kb, 4 MHz    |

| MK77762                   | MCM-7706-4L               |                        | MDX-BRAM2; 2K battery RAM     |

| MK77763                   | MCM-UMC                   |                        | MDX-UMC2; 28-pin sockets      |

| MK77764                   | MCM-DRAM64                |                        | MDX-RAM64; 64Kb dynamic RAM   |

| MK77765                   | MCM-DRAM128               |                        | MDX-RAM128; 128Kb dynamic     |

| MK77767-04                | MCM-7706-4L               |                        | MDX-ZRAM4; 4K battery RAM     |

| MK77767-08                | MCM-7706-8L               |                        | MDX-ZRAM8; 8K battery RAM     |

| MK77767-16                | MCM-7706-16L              |                        | MDX-ZRAM16; 16K battery RAM   |

| MK77850-00                |                           | MCM-CPU2A-2            | MDX-CPU1; 2.5 MHz Z-80        |

| MK77850-04                |                           | MCM-CPU2A-4            | MDX-CPU1; 4.0 MHz Z-80A       |

| MK77853-00                | MCM-CPU2A-2               |                        | MDX-CPU2; 2.5 MHz Z-80        |

| MK77853-04                | MCM-CPU2A-4               |                        | MDX-CPU2; 4.0 MHz Z-80A       |

| MK77855-00                |                           | MCM-CPU2A-2            | MDX-CPU1A; 2.5 MHz Z-80       |

| MK77855-04                |                           | MCM-CPU2A-4            | MDX-CPU1A; 4.0 MHz Z-80A      |

| MK77856-00                | MCM-CPU2A-2               |                        | MDX-CPU2A; Z-80, 2.5 MHz      |

| MK77856-04                | MCM-CPU2A-4               |                        | MDX-CPU2A-4; Z-80A, 4 MHz     |

| MK77857                   |                           | MCM-SBC2               | MDX-CPU3; Z-80A SBC           |

| MK77858                   |                           | MCM-SBC3               | MDX-CPU4; Z-80A SBC           |

| MK77859-00                | MCM-CPU2A-2               |                        | MDX-CPU2B; Z-80, 2.5 MHz      |

| MK77859-04                | MCM-CPU2A-4               |                        | MDX-CPU2B; Z-80A, 4.0 MHz     |

| MK77952                   | STD-WW2                   |                        | Wire Wrap card                |

| MK77953                   | STD-EXT                   |                        | Extender card                 |

| MK77955                   | CBL-101-3                 |                        | RS-232 cable (DTE)            |

| MK77970                   | CBL-101-3                 |                        | RS-232 cable (DCE)            |

| MK77973                   | CC6-SE                    |                        | MD-CC6; 6 slot, 0.75" ctr     |

| MK77976                   |                           | MCM-CLK                | MDX-BCLK; battery clock       |

| MK77977                   | CC16-RM                   |                        | MD-CC16; 16 slot, 0.75"       |

| MK77978                   | 5510 101                  | CC6-WM                 | MD-CC6WM; 6 slot, 0.75"       |

| MK77989                   |                           | CC16-RM                | MD-CC10; 10 slot, 0.75"       |

| MK77990                   | CC12-RM                   | COTO IUN               | MD-CC12A; 12 slot, 0.75"      |

1

# WinSystems®

| 7706-08L         MCM-           7706-16L         MCM-           7707-64K         7707-128K           7709-00         MCM-           7709-08N         MCM-           7709-16N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7709-64N         MCM-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7507<br>7508<br>7604<br>7604<br>7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC                             | MCM-DSIO    | Dual UART card<br>Opto-22 I/F card<br>Dual Opto-22 I/F card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card<br>4Kb battery RAM |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7507         MCM-           7508         MCM-           7601A         MCM-           7602A         MCM-           7603A         MCM-           7604A         MCM-           7605         MCM-           7606         MCM-           7605         MCM-           7606         MCM-           7607         MCM-           7606         MCM-           7607         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         T           7709-00         MCM-           7709-16N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7710         MCM-           7710         MCM-           7803A         MCM-           7805         MCM-           7806         T           7862         T           7862         T           7864-1         T                          | 7507<br>7508<br>7604<br>7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L | MCM-DSIO    | Opto-22 I/F card<br>Dual Opto-22 I/F card<br>TIL I/O card<br>TIL I/O card<br>TIL I/O card<br>TIL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card                                                               |

| 7507         MCM-           7508         MCM-           7601A         MCM-           7602A         MCM-           7603A         MCM-           7603A         MCM-           7604A         MCM-           7605         MCM-           7606         MCM-           7605         MCM-           7606         MCM-           7607         MCM-           7606         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         T           7709-00         MCM-           7709-128K         T           7709-16N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7710         MCM-           7710         MCM-           7803A         MCM-           7805         MCM-           7806         T           7807         T           7862         T           7864-1         T                           | 7507<br>7508<br>7604<br>7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L |             | Dual Opto-22 I/F card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                          |

| 7601A       MCM-         7602A       MCM-         7603A       MCM-         7604A       MCM-         7605       MCM-         7606       MCM-         7606       MCM-         7606       MCM-         7606       MCM-         7704       MCM-         7705A       MCM-         7706-04L       MCM-         7706-08L       MCM-         7706-04L       MCM-         7707-64K       TOT-         7709-00       MCM-         7709-016N       MCM-         7709-32N       MCM-         7710       MCM-         7710       MCM-         7803A       MCM-         7804A-0       TS0-         7805       MCM-         7806       TS0-         7880       TS0-         7885       TO-         7901                                                                               | 7604<br>7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                        |             | Dual Opto-22 I/F card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                          |

| 7602A         MCM-           7603A         MCM-           7604A         MCM-           7605         MCM-           7606         MCM-           7605         MCM-           7606         MCM-           7606         MCM-           7607         MCM-           7606         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-64K           7707-128K         7707-128K           7709-00         MCM-           7709-08N         MCM-           7709-32N         MCM-           7710         MCM-           7710         MCM-           7803A         MCM-           7805         MCM-           7806         7806           7862         7864-1           7880         7885           7901         STD-K           7903         STD-W           7904         | 7604<br>7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                        |             | TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                   |

| 7603A         MCM-           7604A         MCM-           7605         MCM-           7606         MCM-           7605         MCM-           7606         MCM-           7606         MCM-           7614         MCM-           7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-64K           7707-64K         7707-128K           7709-00         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7710         MCM-           7803A         MCM-           7805         MCM-           7806         7806           7862         7864-1           7880         7885           7901         STD-K           79 | 7604<br>7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                |             | TTL I/O card<br>TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                   |

| 7604A         MCM-           7605         MCM-           7606         MCM-           7606         MCM-           7606         MCM-           7614         MCM-           7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-64K           7707-128K         7709-00           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7803A         MCM-           7805         MCM-           7806         7806           7862         7864-1           7880         7885           7901         STD-W           7903         STD-W      | 7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                        |             | TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                                   |

| 7604A         MCM-           7605         MCM-           7606         MCM-           7606         MCM-           7606         MCM-           7614         MCM-           7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-64K           7707-128K         7709-00           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7803A         MCM-           7805         MCM-           7806         7806           7862         7864-1           7880         7885           7901         STD-W           7903         STD-W      | 7604<br>7605<br>PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                        |             | TTL I/O card<br>32 line TTL I/O card<br>32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                                   |

| 7606         MCM-           7614         MCM-           7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-128K           7709-00         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7710         MCM-           7716         MCM-           7804A-0         7804A-0           7804A-1         7805           7805         MCM-           7805         MCM-           7805         MCM-           7807         788-           7805         MCM-           7804         T           7862         7864-1           7880         7885           7901         STD-W           7904         MCM-                                                   | PIO<br>7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                                        |             | 32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                                                                           |

| 7614         MCM-           7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-128K           7707-128K         7709-00           7709-08N         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7710         MCM-           7710         MCM-           7803A         MCM-           7804A-0         7805           7805         MCM-           7806         7808-01           7885         7862           7864-1         7880           7885         7901           7903         STD-W           7904         MCM-                                                                                                                             | 7614<br>UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                                               |             | 32 line prog. TTL I/O<br>TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                                                                           |

| 7702A         MCM-           7704         MCM-           7705A         MCM-           7706-04L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7706-08L         MCM-           7707-64K         7707-128K           7709-00         MCM-           7709-08N         MCM-           7709-08N         MCM-           7709-32N         MCM-           7709-64N         MCM-           7709-64N         MCM-           7710         MCM-           7716         MCM-           7803A         MCM-           7804A-0         7804A-0           7805         MCM-           7805         MCM-           7805         MCM-           7885         7862           7862         7864-1           7880         7885           7901         STD-E           7903         STD-W           7904         MCM-                                                                                                                                     | UMC<br>UMC<br>UMC<br>7706-4L<br>7706-8L                                                                       |             | TTL I/O card<br>Universal memory card<br>Universal memory card<br>Universal memory card                                                                                                                                                                                                    |