## **VOLUME I**

# Technical Manual for DPS-2402 COMPUTER

1 February 1966

# WESTINGHOUSE ELECTRIC CORPORATION SURFACE DIVISION

P.O. Box 1897

Baltimore, Md. 21203

# LIST OF SECTIONS

| Section |                           |   |   |   | Volume |

|---------|---------------------------|---|---|---|--------|

| 1.      | GENERAL DESCRIPTION       |   |   |   | I      |

| 2.      | INSTALLATION              |   |   |   | I      |

| 3.      | OPERATOR'S SECTION        |   |   |   | I      |

| 4.      | PRINCIPLES OF OPERATION . |   |   |   | I      |

| 5.      | TROUBLESHOOTING           |   | • | • | . I    |

| 6.      | REPAIR                    | _ |   |   | Π      |

# **TABLE OF CONTENTS**

| SECT | 1OI | N 1 - GENERAL INFORMATION                                                                                                                         |                                               | SECT                          | TON 1 - GENERAL INFORMATION                                                                                                                                                                                |                                   |

|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| Para | gra | oh                                                                                                                                                | Page                                          | Para                          | graph                                                                                                                                                                                                      | Page                              |

| 1-1. |     | ecifications General Features Machine Structure  (1) Arithmetic Unit  (2) Control Unit  (3) Input-Output  (4) Memory Unit                         | 1-1<br>1-1<br>1-2<br>1-2<br>1-2<br>1-2<br>1-2 |                               | <ol> <li>Address Indexing</li> <li>Multiple Level</li> <li>Indirect Addressing</li> <li>Enter Class Instructions (DATA TRANSFER)</li> <li>Arithmetic Instructions</li> <li>Logical Instructions</li> </ol> | 1-9<br>1-9<br>1-9<br>1-14<br>1-16 |

|      |     | Symbolism for Registers Register Descriptions                                                                                                     | 1-2<br>1-2<br>1-2<br>1-2                      |                               | <ul> <li>(6) Shift Instructions</li> <li>(7) Increment and Decrement<br/>Instructions</li> <li>(8) Skip Instructions</li> </ul>                                                                            | 1-17<br>1-21<br>1-22              |

|      |     | (3) D-Register (24 bits)                                                                                                                          | 1-2<br>1-2<br>1-5<br>1-5<br>1-5               |                               | (9) Jump Instructions (JMP, JSR)                                                                                                                                                                           | 1-25<br>1-26<br>1-27              |

|      | е.  | (9) X-Register (24 bits) (10) Z-Register (24 bits) Word Formats                                                                                   | 1-5<br>1-5<br>1-5                             |                               | Instructions in Machine Code j. Operator and Maintenance                                                                                                                                                   | 1-30                              |

|      |     | <ol> <li>The Basic Instruction Format</li> <li>B Designator</li></ol>                                                                             | 1-5<br>1-5<br>1-6                             | SECT                          | Panels                                                                                                                                                                                                     | 1-30                              |

|      |     | Addressing                                                                                                                                        | 1-6<br>1-6<br>1-7<br>1-7                      | Parag<br>2-1.<br>2-2.<br>2-3. | graph Unpacking Procedure Mounting Remote Operation Console                                                                                                                                                | Page 2-1 2-1                      |

|      | f.  | (8) M Designator                                                                                                                                  | 1-7<br>1-7<br>1-7<br>1-8                      | 2-4.<br>2-5.<br>2-6.          | Connection  Power Input Connection  Installation Procedure  Operating Checks                                                                                                                               | 2-1<br>2-1<br>2-1<br>2-1          |

|      |     | Interrupt                                                                                                                                         | 1-8<br>1-8                                    | SECT<br>Para                  | TON 3 - OPERATOR'S SECTION graph                                                                                                                                                                           | Page                              |

|      |     | <ul><li>(4) Manual Interrupt</li><li>(5) Power Failure Interrupt</li><li>(6) Real Time Clock Interrupt</li><li>(7) Input/Output Channel</li></ul> | 1-8<br>1-8<br>1-8                             | 3-1.<br>3-2.<br>3-3.          | Function                                                                                                                                                                                                   | 3-1<br>3-1<br>3-4                 |

|      |     | Interrupt                                                                                                                                         | 1-8<br>1-8                                    |                               | Description                                                                                                                                                                                                | 3-4                               |

|      | g.  | Locations and Sense Switches                                                                                                                      | 1-8                                           |                               | Control                                                                                                                                                                                                    | 3-6<br>3-6<br>3-6                 |

|      | h.  | Detailed Descriptions of                                                                                                                          | 1_8                                           |                               | (4) I/O Control                                                                                                                                                                                            | 3-0<br>3-7                        |

| SECTION 3-OPERATOR'S SECTION (Cont.) |           |                                                                                                            |                              | SECTION 4-PRINCIPLES OF OPERATION (Cont.)                                                                                                     |

|--------------------------------------|-----------|------------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Parag                                | grapi     | h (5) Arithmetic Control                                                                                   | Page<br>3-7                  | Paragraph Page (1) S-Register                                                                                                                 |

| 3-4.<br>3-5.                         | Ope<br>a. | e Panel                                                                                                    | 3-9<br>3-9<br>3-9<br>3-9     | (2) Address Translation 4-27<br>(3) M-Register 4-32<br>(a) M-Register Inputs 4-32<br>(b) M-Register Outputs 4-32<br>(4) Memory Timing 4-32    |

| SECT                                 | 'ION      | 4-PRINCIPLES OF OPERATION                                                                                  |                              | (a) Manual Memory                                                                                                                             |

| Paraş<br>4-1.                        | Gen       | h eral Information                                                                                         | Page 4-1 4-1 4-1 4-1 4-1     | Reference 4-32 (b) Memory Reference by the Computer 4-33 (c) Read Portion of the Memory Cycle 4-33 (d) Write Portion of the Memory Cycle 4-34 |

|                                      |           | (d) Timing                                                                                                 | 4-1<br>4-1                   | (5) Core Theory 4-35<br>(6) Summary 4-37                                                                                                      |

|                                      |           | (a) Registers                                                                                              | 4-1<br>4-2<br>4-2            | 4-3. Control Section Operation 4-38 a. General                                                                                                |

|                                      |           | <ul><li>(3) Arithmetic Section</li><li>(a) Registers</li><li>(4) Input/Output Section</li></ul>            | 4-2<br>4-2<br>4-3<br>4-3     | Registers 4-38 (2) Timing Control 4-38 (3) Instruction Word                                                                                   |

|                                      |           | (a) Registers                                                                                              | 4-3<br>4-3                   | Translator (I Translator) 4-38  (4) Parity Check Logic 4-38  (5) Sequencer Control 4-38                                                       |

|                                      |           | <ul><li>(5) Summary of Computer</li><li>(6) Functional Schematics</li><li>(7) Basic Circuits and</li></ul> | 4-4<br>4-4                   | (6) The Auto Load (Bootstrap Logic) 4-38 (7) Instruction Execution                                                                            |

|                                      |           | Symbology                                                                                                  | 4-4<br>4-4<br>4-10           | Control 4-38 (8) Fixed Location Gates 4-38 b. Detailed Description of Control Section Operation 4-38                                          |

|                                      |           | (One Shot)                                                                                                 | 4-10<br>4-10<br>4-11         | (1) Components 4-38<br>(a) P-Register 4-38<br>(b) I-Register 4-41                                                                             |

|                                      |           | (a) Master Clear                                                                                           | 4-11<br>4-11<br>4-11         | (2) Instruction (I) Translator (Decoder) 4-41 (3) Parity Test Logic 4-42                                                                      |

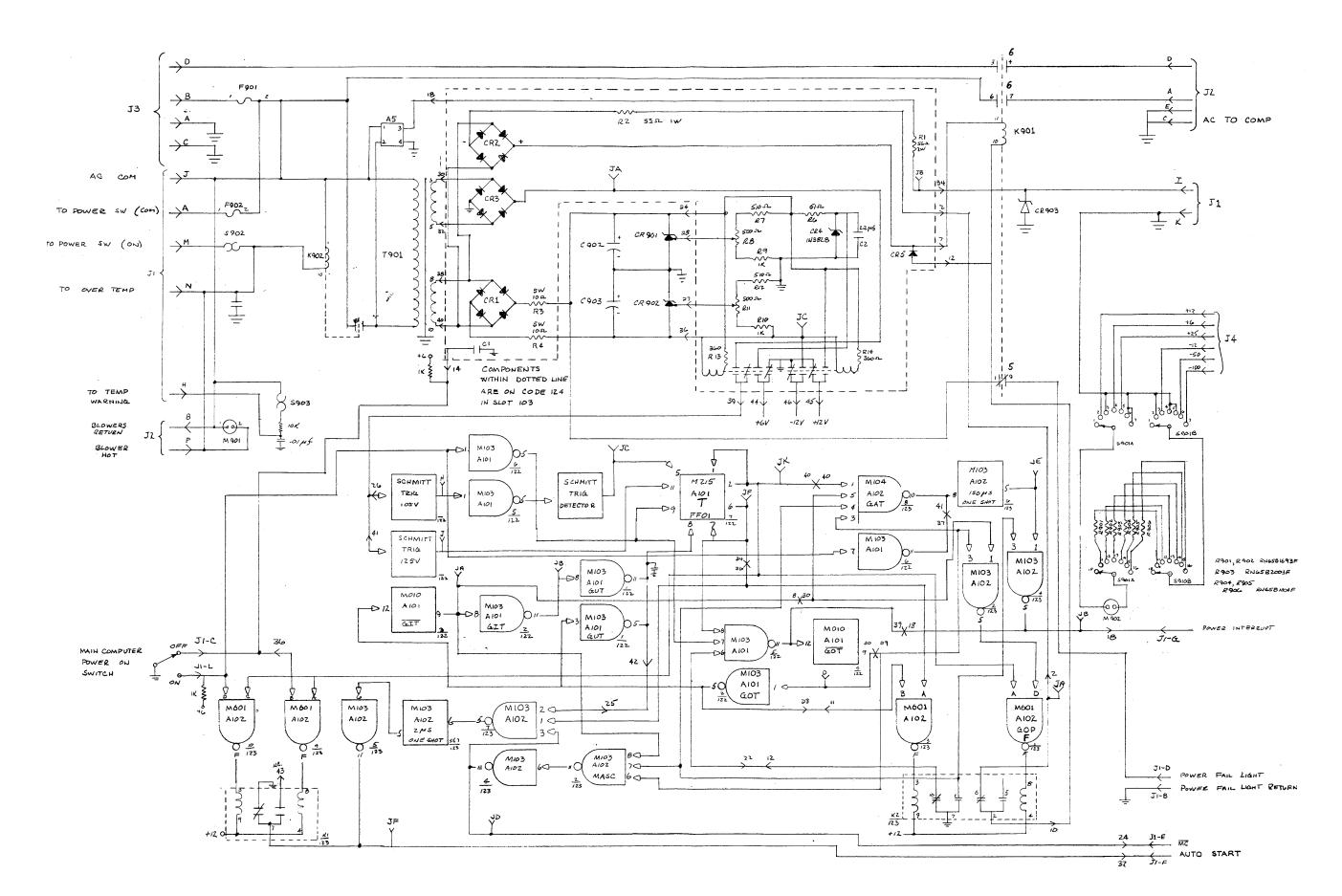

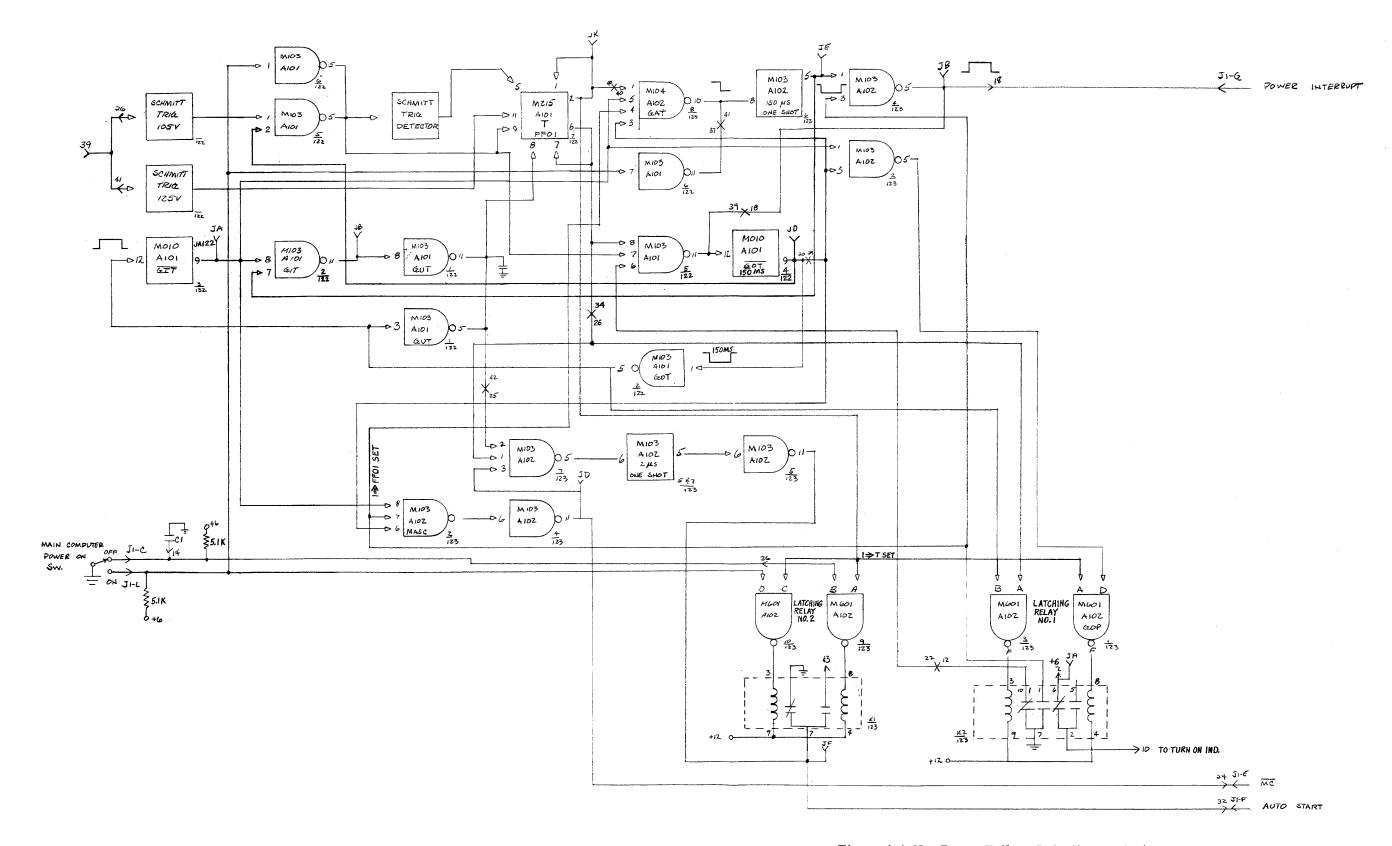

|                                      | b.        | Computer Power Supplies (1) Requirements (2) Power Failure Detection                                       | 4-11<br>4-11<br>4-11         | (4) Automatic Load Control Control (Bootstrap) 4-42 (5) Skip Conditional Control                                                              |

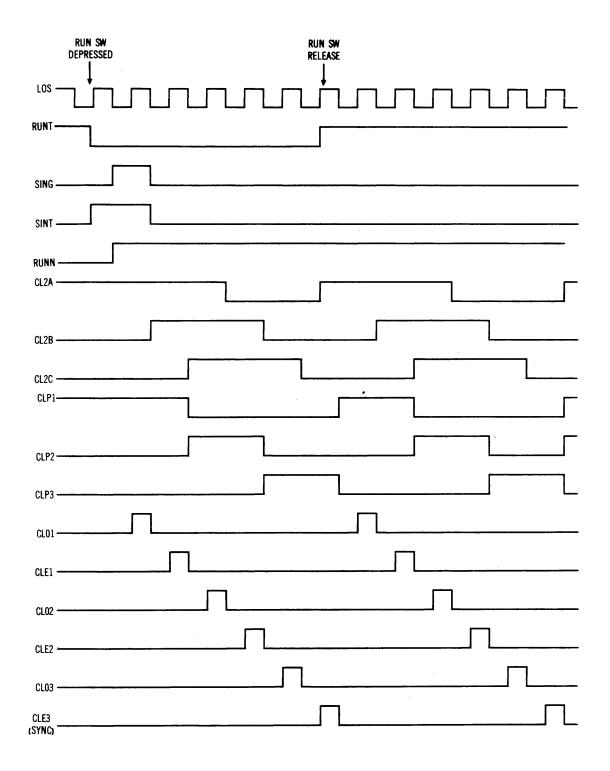

|                                      | c.        | Master Clock                                                                                               | 4-12<br>4-14<br>4-14<br>4-16 | Gates                                                                                                                                         |

|                                      |           | <ul><li>(4) Instruction LO RUN</li><li>(5) Program LO RUN Operation .</li></ul>                            | 4-17<br>4-18                 | (a) Sequence Timing Operation 4-46                                                                                                            |

| 4-2.                                 | Me:       | mory Section Operation  General Information  (1) Memory Stock                                              | 4-18<br>4-18<br>4-21         | 4-4 Arithmetic Section Operation 4-52 a. General Information 4-52 b. Arithmetic Section Compon-                                               |

|                                      | b.        | (2) Memory Board DPS-2402 Memory Section Detailed Analysis                                                 | 4-21<br>4-27                 | ents                                                                                                                                          |

| SECTION 4-PRINCIPLES OF OPERATION | (Cont.) | SECTION 4-PRINCIPLES OF OPERATION ( | Cont. |

|-----------------------------------|---------|-------------------------------------|-------|

|-----------------------------------|---------|-------------------------------------|-------|

| Paragraph                                                                                                                                         | Page                         | Paragraph Pa                                                                                   | ıge                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------|------------------------------|

| (b) Adder                                                                                                                                         | 4-56<br>4-62<br>4-62<br>4-63 | (1) General                                                                                    | 99<br>99<br>99               |

| (a) Inputs                                                                                                                                        | 4-63<br>4-63<br>4-63         | (d) Buffer Mode                                                                                |                              |

| (b) Outputs                                                                                                                                       | 4-64<br>4-64<br>4-64         |                                                                                                | 102<br>103                   |

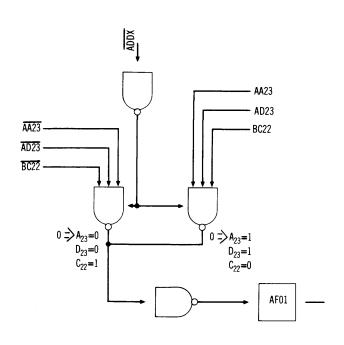

| (5) Arithmetic Function Register (AF)                                                                                                             | 4-64<br>4-64<br>4-64         | (b) Z-Register Transfer and                                                                    | 103                          |

| (b) Outputs                                                                                                                                       | 4-64                         | (Channel Control) 4- (d) Priority Logic 4- (e) Timing and Control                              | 103<br>104<br>105            |

| Execution                                                                                                                                         | 4-64<br>4-64<br>4-67<br>4-68 | (3) Execution of I/O Instructions 4- (a) EXF Instruction 4- (b) Buffer Instructions 4-         | ·105<br>·106<br>·106         |

| <ul> <li>(4) Enter Q (ENQ)</li> <li>(5) Substitute (SBT)</li> <li>(6) Logical Inclusive OR(IOR)</li> <li>(7) Logical Exclusive OR(EOR)</li> </ul> | 4-68<br>4-68<br>4-68         | (5) Interrupt Mode Processing 4- (a) Power Failure Interrupt 4- (b) Manual Interrupt 4-        | -106<br>-107<br>-107<br>-107 |

| (8) Shifts                                                                                                                                        | 4-68<br>4-73<br>4-73<br>4-73 | (d) External Interrupt (Output). 4-<br>(e) Real Time Clock Updating . 4-                       | -107<br>-108<br>-108<br>-108 |

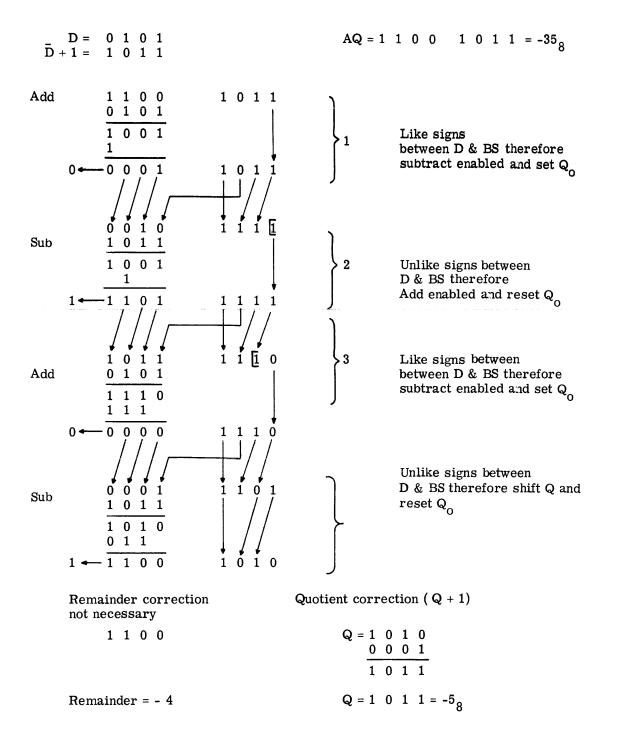

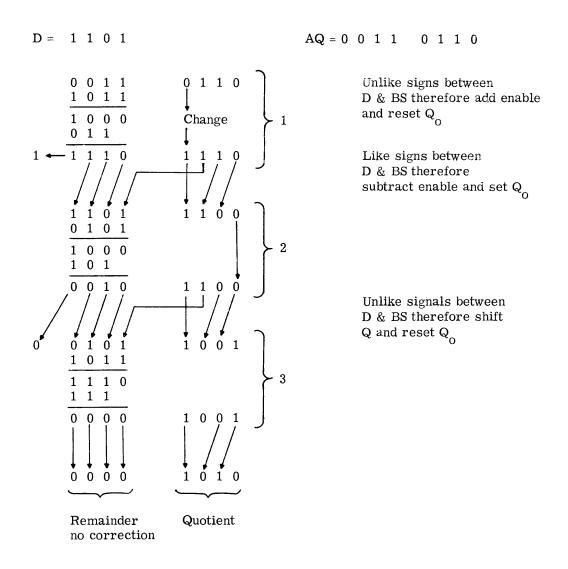

| (a) General Philosophy (11) NEGATE A                                                                                                              | 4-79<br>4-79                 | SECTION 5-TROUBLESHOOTING                                                                      |                              |

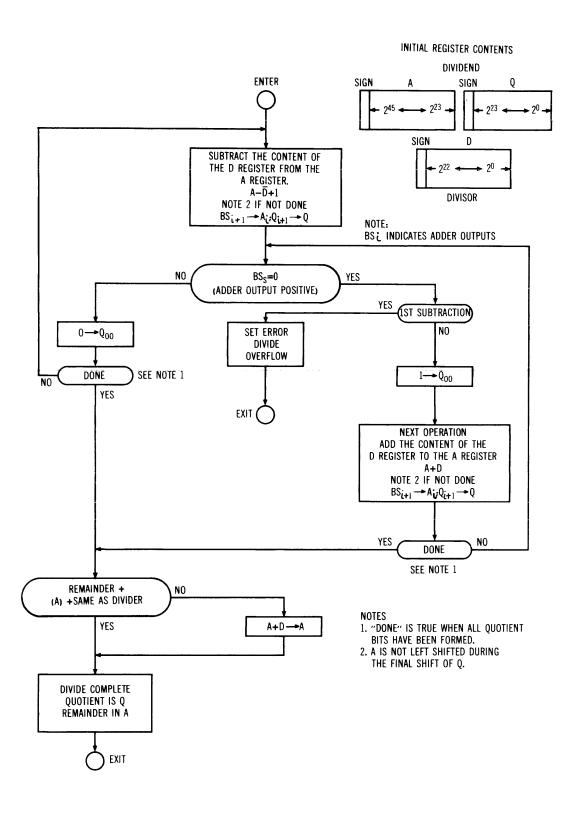

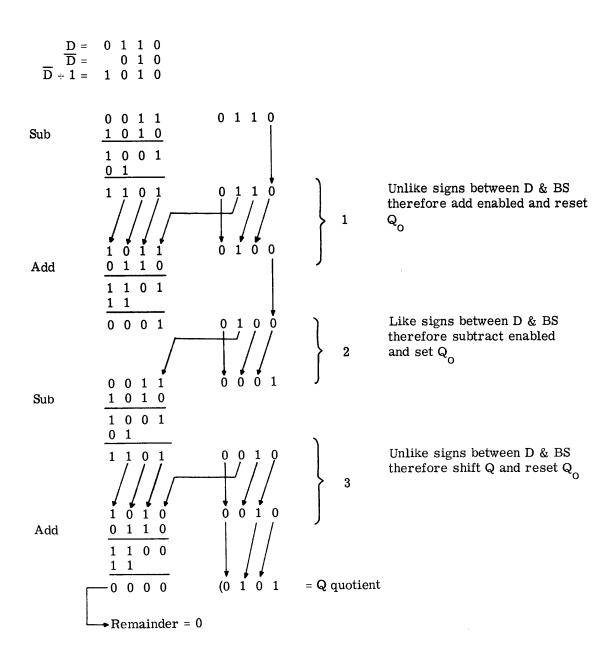

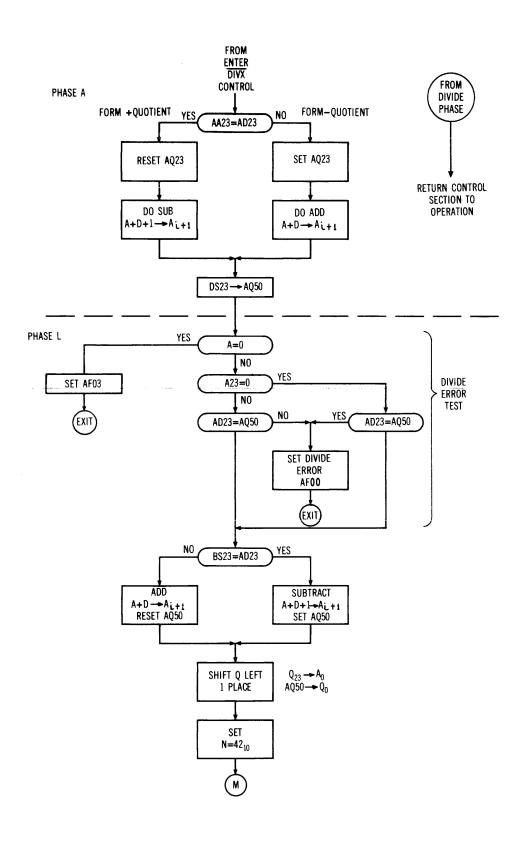

| (a) General Philosophy of Computer Division                                                                                                       | 4-81                         | 5-1. Introduction and General                                                                  | age<br>1                     |

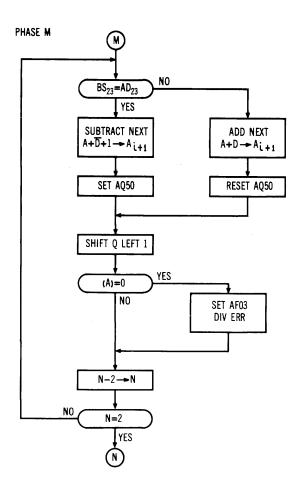

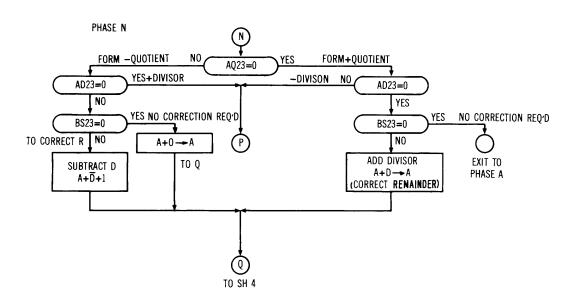

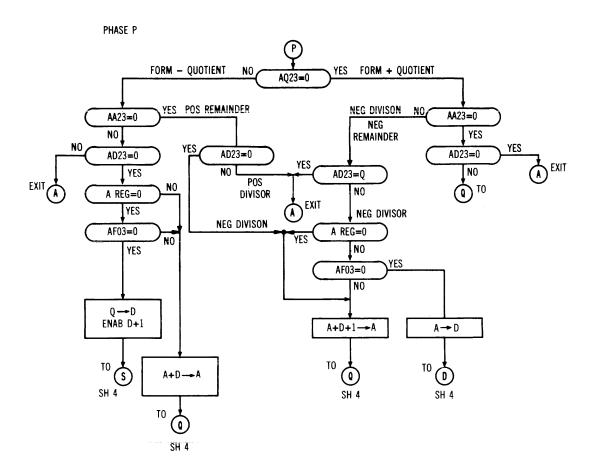

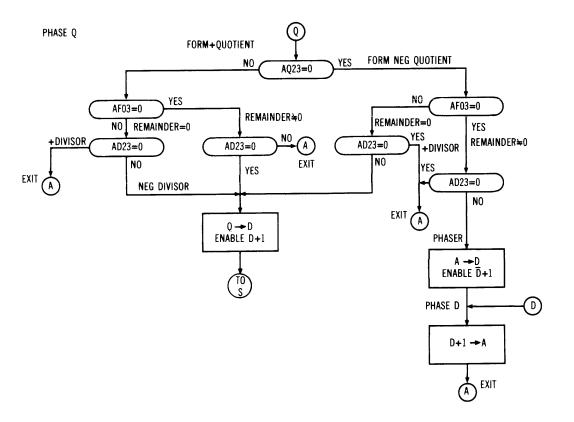

| (b) General Analysis of Division by the DPS-2402 Computer                                                                                         | 4-84                         | Information 5- 5-2. Test Equipment 5- 5-3. Test Conditions 5-                                  | -1                           |

| (c) Detailed Analysis of DPS-2402 Division                                                                                                        | 4-84<br>4-92                 | 5-4. Visual Inspections 5-<br>5-5. Electrical Tests 5-<br>5-6. Power Control Assembly 5-       | -1                           |

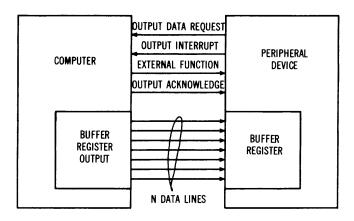

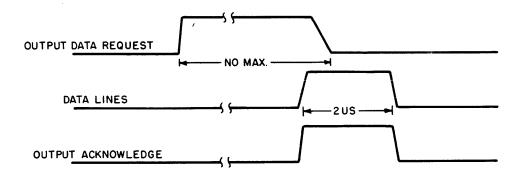

| 4-5. Input-Output Section Operation a. Input-Output Section Operation                                                                             | 4-92<br>4-92                 | a. Computer Power Switch 5-<br>b. Time Totalizing Meter 5-<br>c. Overtemperature Indicator 5-  | -1                           |

| (a) Output Channel Timing (NORMAL MODE)  (2) Input Channels                                                                                       | 4-93<br>4-94<br>4-95         | d. Temperature Fault 5-5-7. Console Controls and Indicators 5-5-8. Testing the Master Clock 5- | -1<br>-7                     |

| (3) Block Buffer Mode                                                                                                                             | 4-96<br>4-96                 | a. Testing NORMAL RUN Condition                                                                |                              |

| 2402 Computer                                                                                                                                     | 4-96<br>4 <b>-</b> 96        | Operation                                                                                      |                              |

# LIST OF ILLUSTRATIONS

| SECTIO           | N 1 - GENERAL INFORMATION                    |                    | SECTIO           | N 4 - PRINCIPLES OF OPERATION                          |              |

|------------------|----------------------------------------------|--------------------|------------------|--------------------------------------------------------|--------------|

| Figure           |                                              | Page               | Figure           |                                                        | Page         |

| 1-1-A.           | Basic Westinghouse DPS-2402 Computer         | 1-3                | 4-2-K.<br>4-2-L. | 3-Bit Selection                                        | 4-30<br>4-31 |

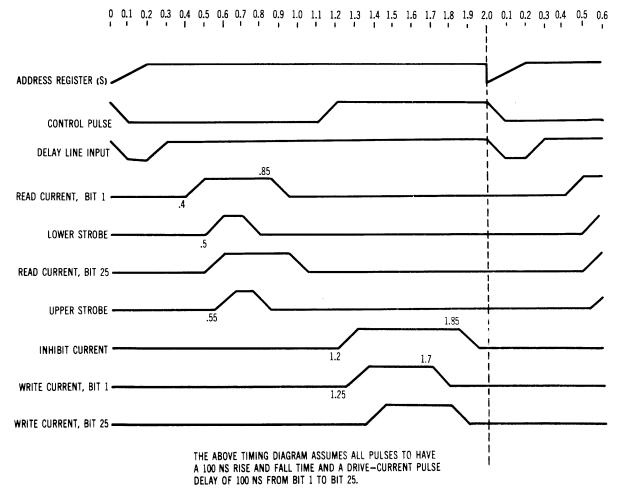

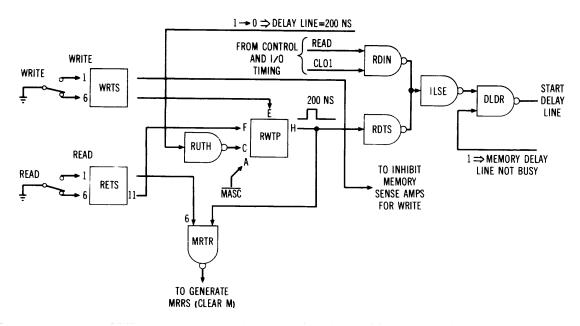

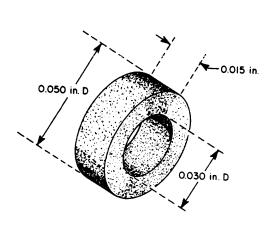

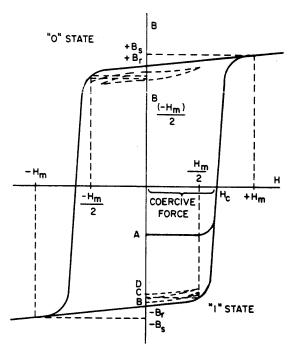

| 1-1-B.           | Westinghouse DPS-2402 Computer Block Diagram |                    | 4-2-M.<br>4-2-N. | 2402 Memory Timing Diagrams<br>Manual Memory Reference | 4-33         |

| 1-1-C.           | Composite List of all Instructions           | 1-11               |                  | (Read-Write Test Switch Logic)                         | 4-34         |

| SECTIO           | N 3 - OPERATORS SECTION                      |                    | 4-2-O.<br>4-2-P. | Inhibit Selection A Magnetic Core                      | 4-35<br>4-36 |

| Figure           |                                              | Page               | 4-2-P.<br>4-2-Q. | Idealized Hystersis Loop of a                          | 1 00         |

| -                | Oceanation Danol                             |                    |                  | Ferrite Core                                           | 4-36         |

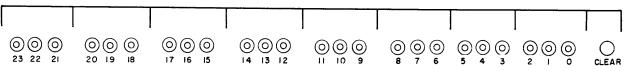

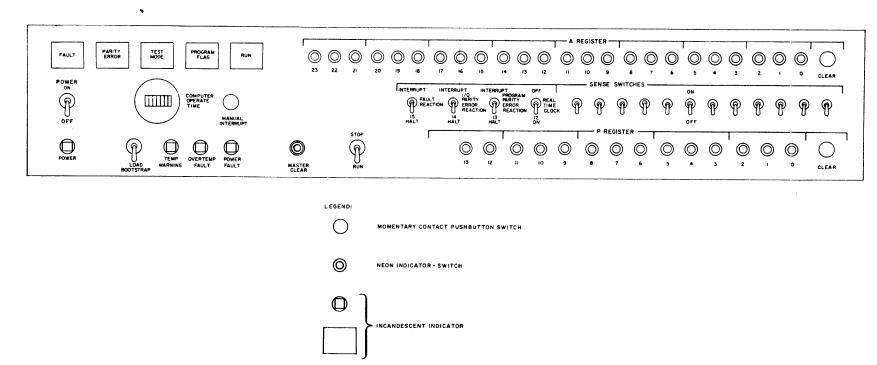

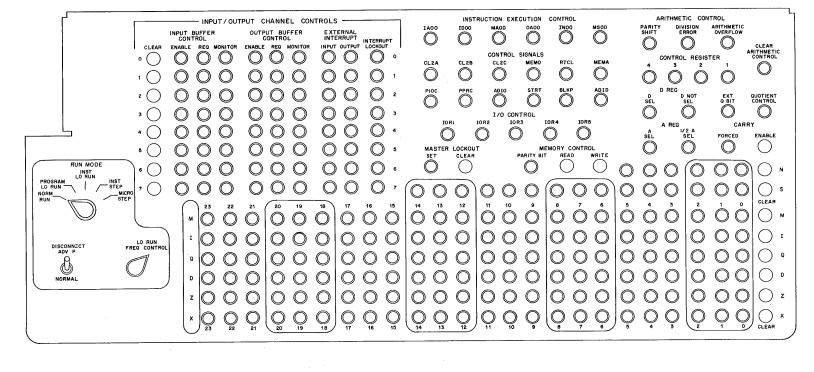

| 3-2-A.<br>3-2-B. | Operation Panel                              | 3-5                | 4-2-R.           | A Typical Magnetic Core Output                         | 4-37         |

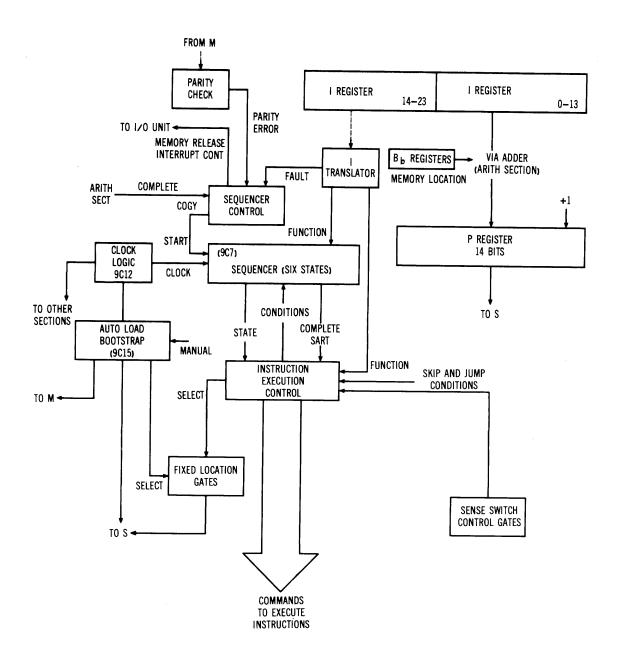

| SECTIO           | N 4 - PRINCIPLES OF OPERATION                |                    | 4-3-A.           | Control Unit Block Diagram                             | 4-39         |

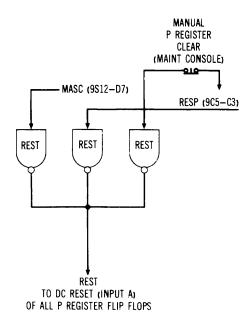

| Figure           |                                              | Page               | 4-3-B.           | Incrementing P-Register                                | 4-40         |

| _                | To act of Council of Lorent                  | _                  | 4-3-C.           | from 0-4                                               |              |

| 4-1-A.<br>4-1-B. | Logic Symbology                              | 4-5                | 4-3-C.<br>4-3-D. | Basic Parity Element (Three                            |              |

| 4-1-B.<br>4-1-C. | Dual NAND Circuit                            | 4-5                |                  | Input Checked)                                         | 4-42         |

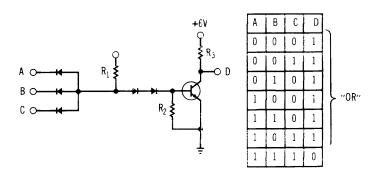

| 4-1-D.           | OR Logic Function                            | 4-5                | 4-3-E.           | Parity Tree                                            | 4-43         |

| 4-1-E.           | AND Logic Function                           | 4-6                | 4-3-F.           | Parity Check Logic                                     | 4-43         |

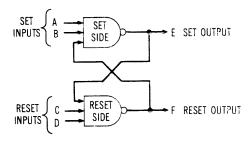

| 4-1-F.           | R-S Flip Flop (Logic Connections).           |                    | 4-3-G.           | Automatic Load Control                                 |              |

| 4-1-G.           | R-S Flip Flop (Microelectric                 |                    |                  | Timing (Bootstrap)                                     | 4-44         |

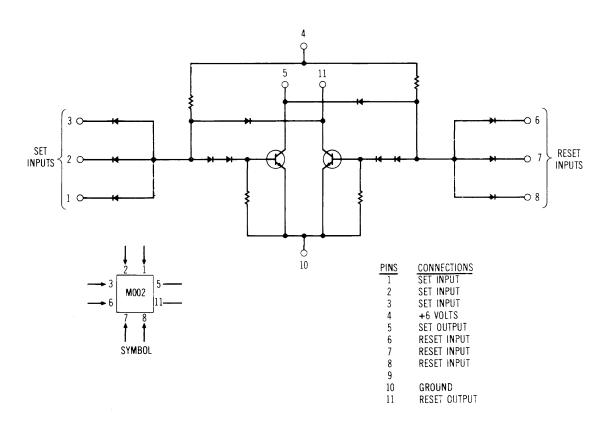

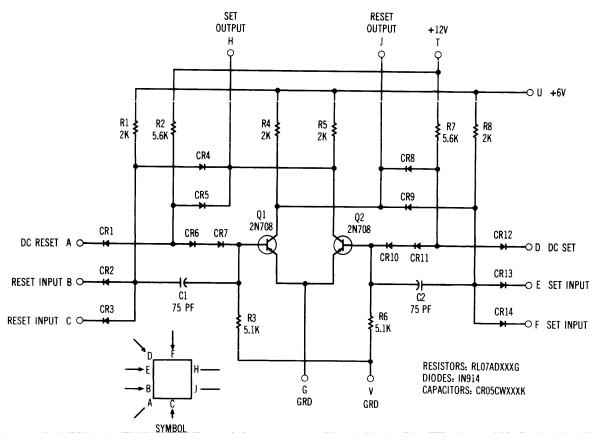

| 1-1-0.           | Device)                                      | 4-7                | 4-3-H.           | Instruction Execution Timing                           |              |

| 4-1-H.           | M001 J-K Flip Flop                           | 4-8                |                  | Control                                                | 4-46         |

| 4-1-I.           | J-K Flip Flop Analysis                       | 4-9                | 4-3-I.           | Sequence of Instruction Cycles                         | 4-47         |

| 4-1-J.           | J-K Logic Symbols                            | 4-9                | 4-3-J.           | Sequence Enable Condition                              | 4-49         |

| 4-1-K.           | One Shot Multivibrator                       | 4-10               | 4-4-A.           | Major Arithmetic Control Signals.                      | 4-53         |

| 4-1-L.           | Delay Line Symbol                            |                    | 4-4-B.           | Arithmetic Section Block Diagram                       | 4-55         |

| 4-1-M.           | Neon Switch-Indicator                        |                    | 4-4-C.           | A-Register Transfer Logic                              |              |

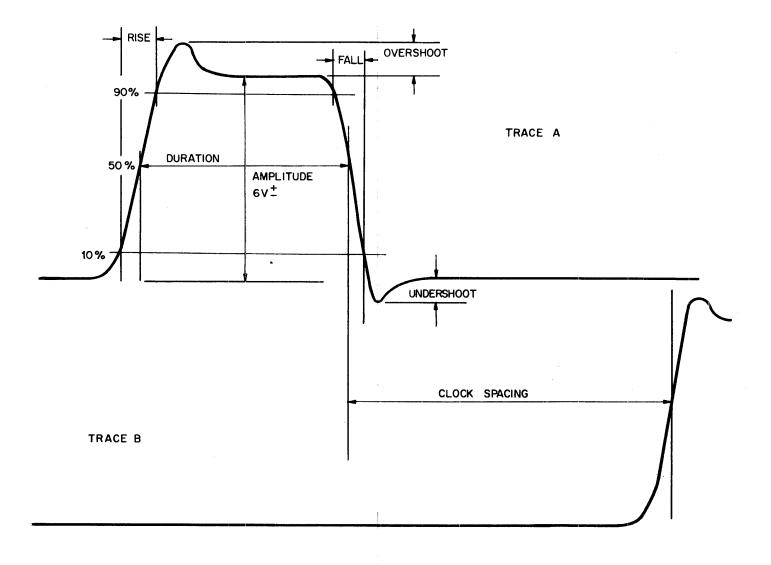

| 4-1-0.           | Clock Waveforms, Free Running                |                    |                  | (Input)                                                | 4-56         |

|                  | Operation                                    | 4-15               | 4-4-D.           | ADDER Logic                                            | 4-57         |

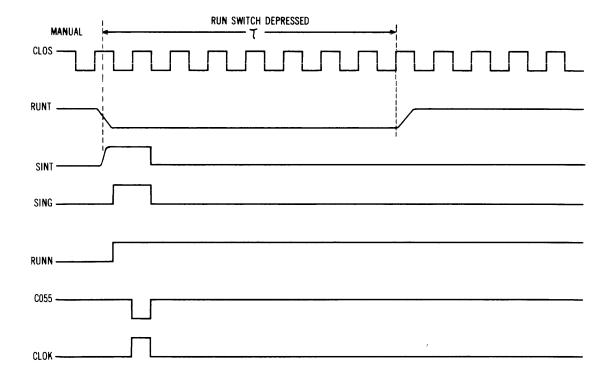

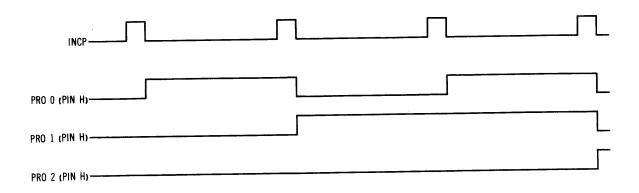

| 4-1-P.           | Microstep Operation                          | 4-16               | 4-4-E.           | Full Adder Truth Table and                             | 4 = 0        |

| 4-1-Q.           | Instruction Step Operation                   | . 4-17             |                  | Logic Equations                                        | 4-58         |

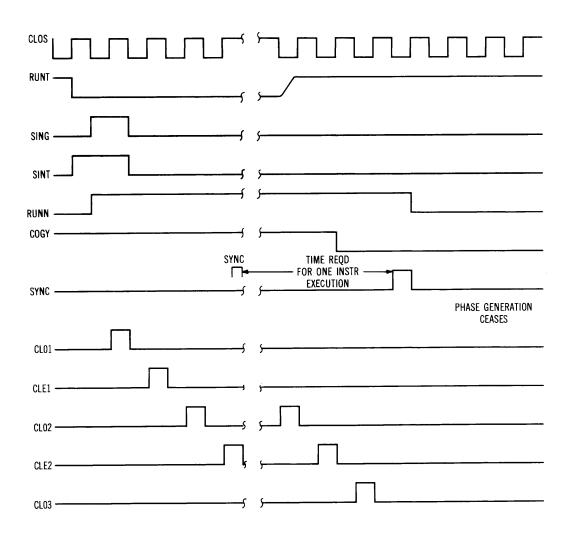

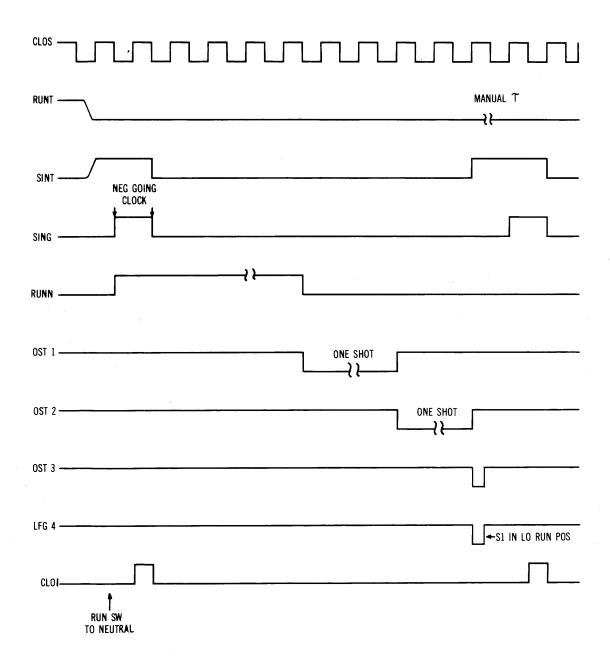

| 4-1-R.           | Lo-Run Operation                             | . 4-19             | 4-4-F.           | Arithmetic Adder Block                                 | 4 = 0        |

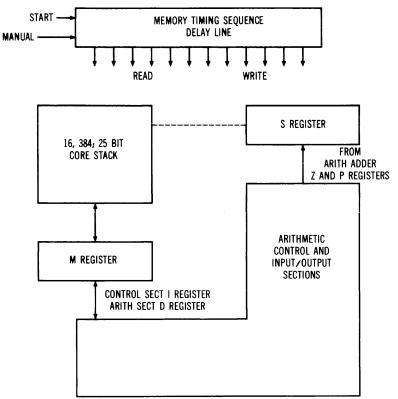

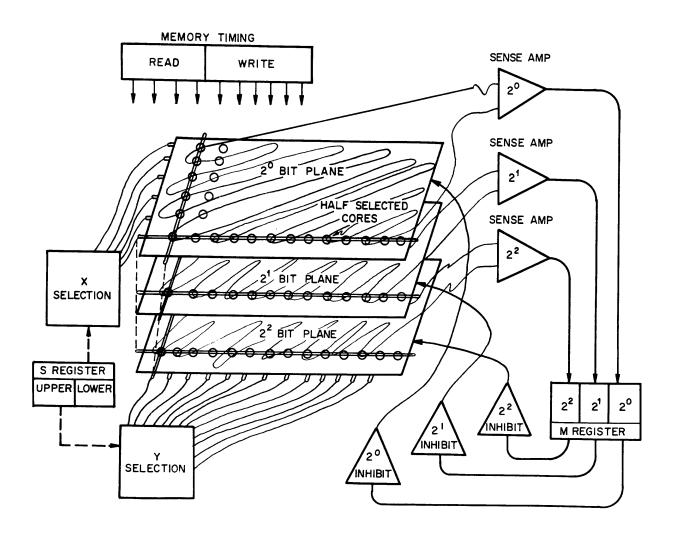

| 4-2-A.           | Memory Section Simplified                    |                    |                  | Diagram                                                | 4-59         |

|                  | Block Design                                 | . 4-20             | 4-4-G.           | Boolean Equation for Parallel                          | 4 66         |

| 4-2-B.           | Memory Selection                             | . 4-22             |                  | Carry Logic                                            |              |

| 4-2-C.           | 128 x 128 Array, Top View                    | . 4-23             | 4-4-H.           | Sample Adder Element                                   | 4-61<br>4-62 |

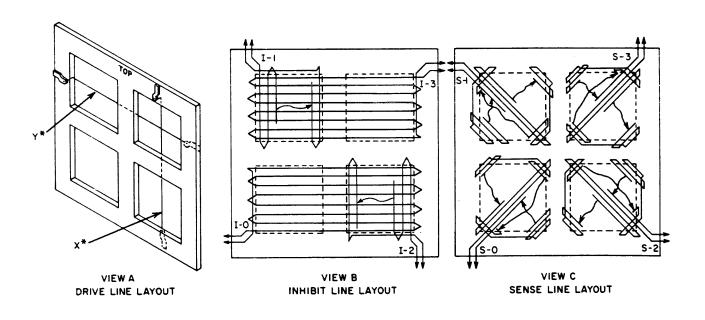

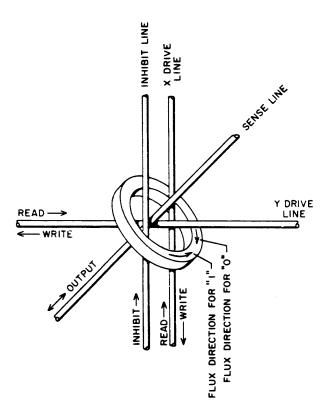

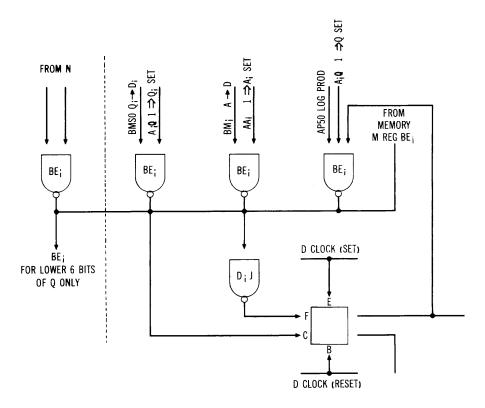

| 4-2-D.           | Sensing and Inhibiting Functions             | . 4-24             | 4-4-I.           | Q-Register Stage                                       |              |

| 4-2-E.           | Three-Bit Memory                             |                    | 4-4-J.           | D-Register Stage                                       | 4-65         |

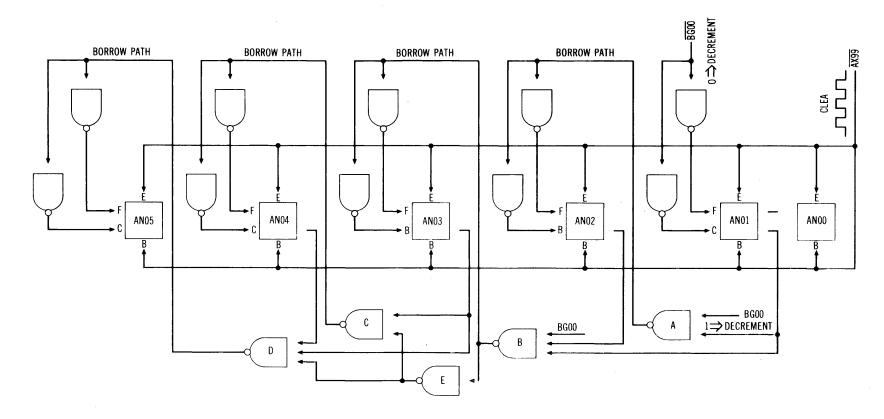

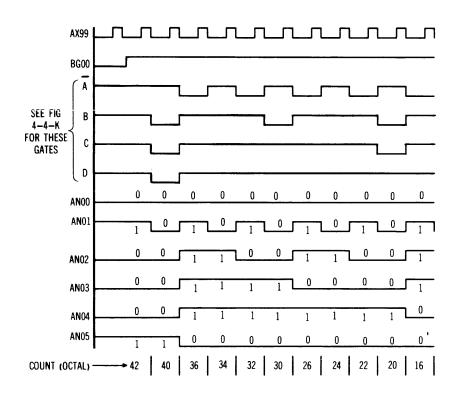

| 4-2-F.           | Quadrant 64 by 64 Array, Top View            |                    | 4-4-K.           | N-Register Counter Logic                               |              |

| 4-2-G.           | Sense Line Orientation                       | . 4-26             | 4-4-L.           | Decrementing Process                                   | 4-00         |

| 4-2-H.           | A Typical Ferrite Core, Inhibit              | 4 97               | 4-4-M.           | AF-Register and Extended  O Bit (AQ50)                 | 4-66         |

|                  | Line X-Oriented                              |                    | 1 1 NT           | Q Bit (AQ50)                                           | 4-67         |

| 4-2-I.           | Transfer Logic                               | . 4-28             | 4-4-N.           | Arithmetic Overflow                                    | 4-67         |

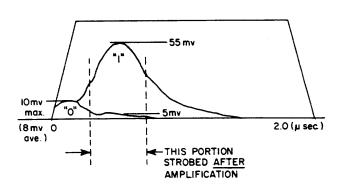

| 4-2-J.           | 2402 Memory Unit 2- $\mu$ sec                | 4 <b>9</b> 0       | 4-4-O.<br>4-4-P. | Right Shift A-Timing (N count=6).                      |              |

|                  | CVCIE Time                                   | . <del>५</del> -४४ | ユーオード.           | Tuelle pittle 11 Timing (1, come-o).                   |              |

| SECTION          | N 4 - PRINCIPLES OF OPERATION(Cont.)                                 | SECTION                    | N 4- PRINCIPLES OF OPERATION(Cont.)                                                    |

|------------------|----------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------------|

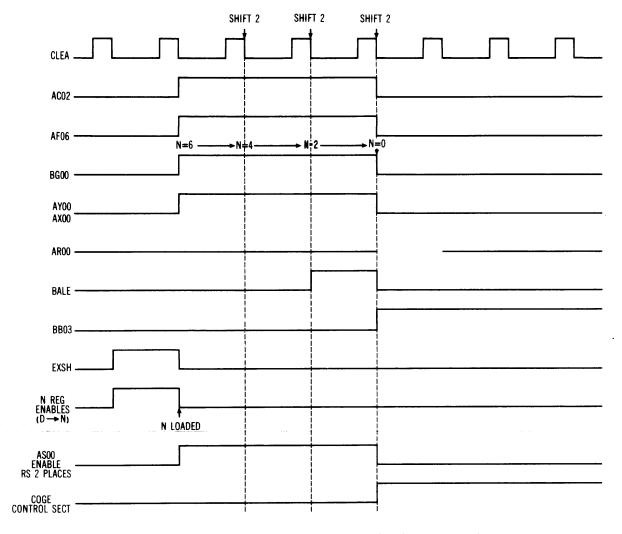

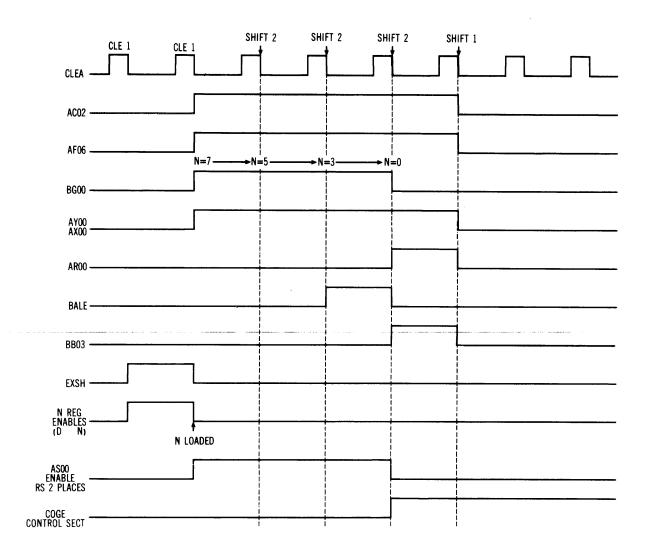

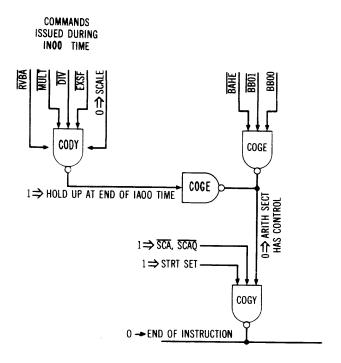

| Figure<br>4-4-Q. | Page Right Shift A-Timing                                            | Figure 4-5-A.              | Page Output Channel Block Diagram 4-92 Output Timing Date                              |

| 4-4-R.           | (N Count = 7)                                                        | 4-5-B.<br>4-5-C.<br>4-5-D. | Output Timing Data 4-94 External Function Timing 4-94 Input Channel Block Diagram 4-95 |

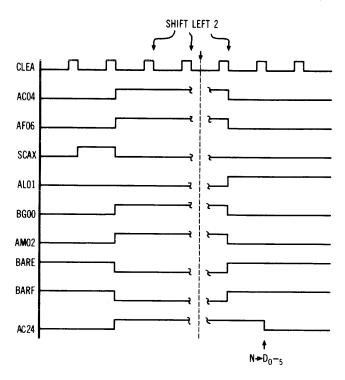

| 4-4-S.           | Scale A (Even Number of Shifts Required to Bring MSB into AA22) 4-74 | 4-5-E.<br>4-5-F.           | Input Timing                                                                           |

| 4-4-T.           | Adder and Four Registers 4-75                                        | 4-5-G.                     | Channel Interface                                                                      |

| 4-4-U.           | Multiply Timing for Example 4-76                                     | 4-5-H.                     | Buffer Input Timing and Signals 4-100                                                  |

| 4-4-V.           | Negate the A-Register 4-79                                           | 4-5-I.                     | Buffer Output Timing and Signals . 4-100                                               |

|                  | <b>RVBA</b> Timing 4-80                                              | 4-5-J.                     | Z-Register Incrementing from                                                           |

|                  |                                                                      |                            | <b>Zero</b> to Six                                                                     |

|                  | Divide Flow (For Positive Numbers Only)                              | SECTIO                     | N 5-TROUBLESHOOTING                                                                    |

| 4-4-Z.           | Pos Quotient (No Remainder) 4-85                                     | Figure                     | Page                                                                                   |

| 4-4-AA.          | Divide Flow 4-86                                                     | 5-5-A.                     | DC Voltages at Chassis Bus 5-2                                                         |

| 4-4-AB.          | Negative Quotient with Remainder (Pos Division) 4-90                 |                            | Power Supply Assemblies 5-2<br>Clock Waveforms - Normal Run                            |

| 4-4-AC.          | Quotient Negative 4-91                                               |                            | Condition 5-4                                                                          |

|                  |                                                                      |                            |                                                                                        |

### I. GENERAL DESCRIPTION

This section contains DPS-2402 Computer specifications, a general block diagram discussion and a detailed description of the repertoire of instructions.

### 1-1. SPECIFICATIONS

- General Features. The following summarizes the technical characteristics of the Westinghouse DPS-2402 Computer:

- (1) Type:

- \*General-purpose, stored program, integrated circuit, medium scale, binary, parallel.

- i Memory

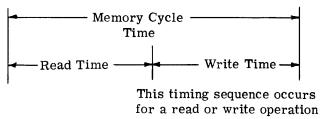

Section:\*1.0 microsecond access time

- \*2.0 microsecond read-write cycle time

- \*Parity Check Feature

- \*24-bit word length, parallel transfer (plus 1 parity bit)

- \*4,096, 8,192 or 16,384 words expandable to 32, 768 words.

- \*Coincident current mode.

- ii Arithmetic

Section: \*Organization: 24 bit, parallel, 2's complement, binary, fixed-

- \*Registers Two arithmetic (A and Q)

- One transient (D)

- One shift count (N)

- \*Instruction Execution Time (Including procurement of instruction and operand)

- \*Add Time

- 4.0  $\mu$ sec

- \*Multiply Time 12.0  $\mu$ sec

- \*Divide Time 22.0  $\mu$ sec

- iii Control

- Section: \*Word length: 24 bits

- \*Single address instructions: one instruction per word.

- \*Addressable index registers: 3 (B-boxes)

- \*Parallel operation

- \*Multiple-level indirect address capability with indexing of primary and indirect addresses.

- \*38 basic instructions, or a total of 74 instructions by using modifiers.

- iv Input/Output

Section:\*Eight (8) channels (expandable to

- \*Any channel may be used in fully buffered, express, or external function mode.

- \*Both input and output buffers may be enabled on any channel simultaneously.

- \*Buffer mode operation, once initiated proceeds without program intervention.

- \*Internal and external interrupts on each channel.

- \*Real-time clock, set by program, with interrupt on zero count.

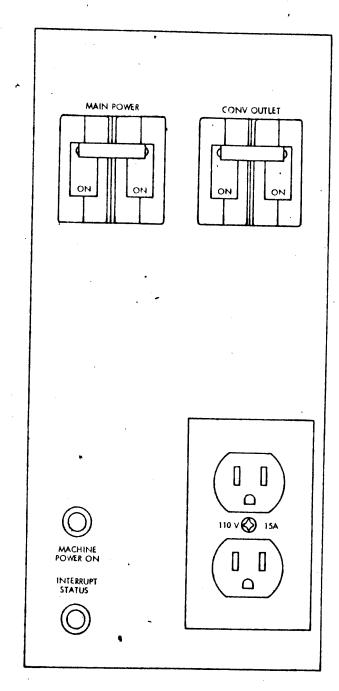

- (2)Physical

Characteristics:\*Size: 72 x 28.75 x 25 inches

- \*Weight: 750 pounds

- \*Power Consumption: 1200 watts 120 volt, single phase, 60 cycle.

- (3)Environmental

- Requirements: \*Non-volatile core memory with power failure lockup feature which saves the contents of operational registers. The mechanical design of the DPS-2402 was performed using the requirements of the following specifications as a guide.

- \*General:

MIL-E-16400E

\*Vibration:

MIL-STD-167,

Type I

\*Shock:

MIL-S-901 or MIL-E-5400, paragraph

3. 2. 21. 6

\*RF Interference: MIL-I-16910A

\*Temperature: 0°-50°C Room

Ambient

\*Humidity:

To 95%

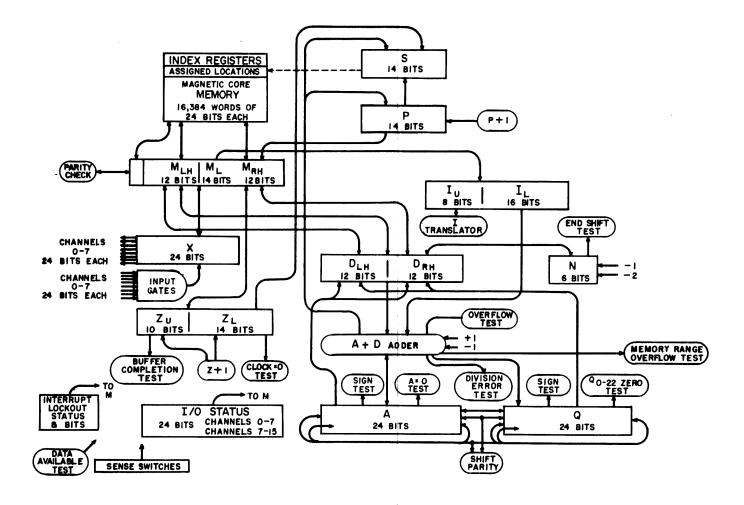

- b. Machine Structure. Figure 1-1-A is a photograph of the Basic Westinghouse DPS-2402 Computer System and Figure 1-1-B is a functional system block diagram. The DPS-2402 Computer is organized into four main units, the arithmetic, control, input-output, and the memory units.

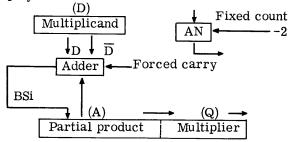

- (1) Arithmetic Unit. The arithmetic unit contains control and numerical registers, a high-speed adder, and logical gating necessary for high-speed execution of the arithmetic and logical commands. The registers required by the unit include two addressable registers (A and Q), one transient register (D), a shift count register (N), and two control registers (AC and AF).

- (2) Control Unit. The control unit interprets commands and directs the cycles of operation which execute the commands. The control unit includes two working registers (I and P), the core memory parity logic, the function code and designator translators, and the sequence generators. The fault and parity interrupts are processed by the control unit.

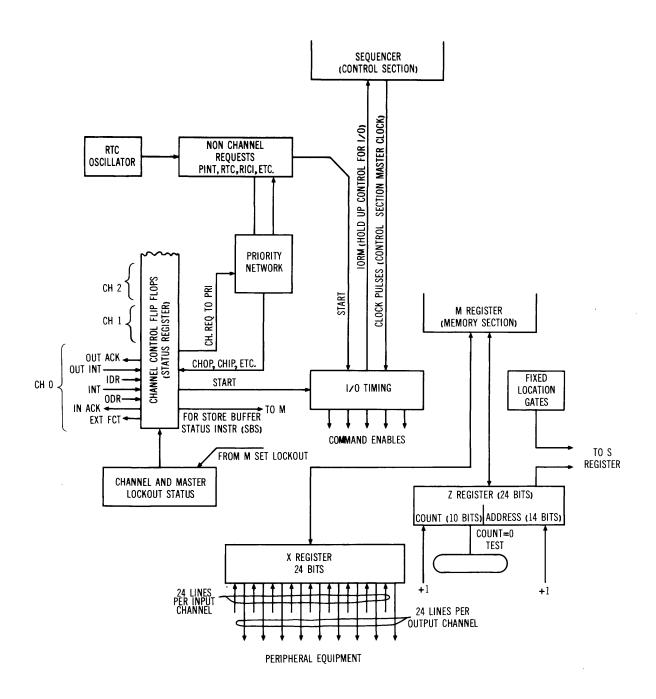

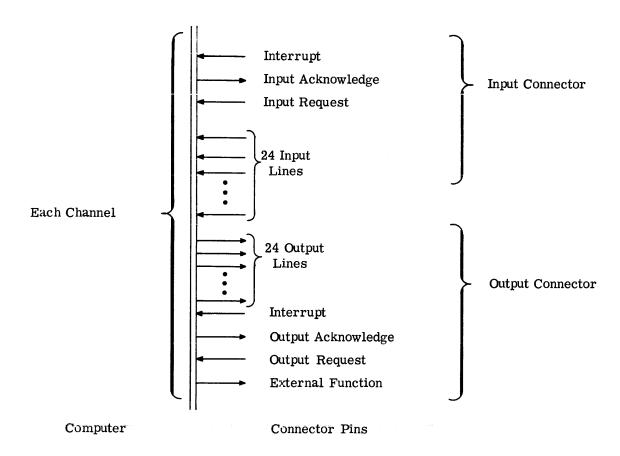

- (3) Input-Output. The input-output unit consist of a data exchange register (X), a register for updating the buffer control word (Z), input amplifiers, level converters, output drivers, priority gating, buffer control, external function control, and interrupt control.

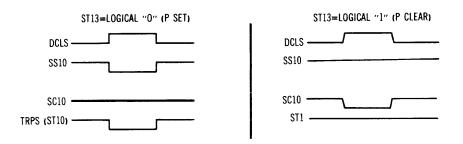

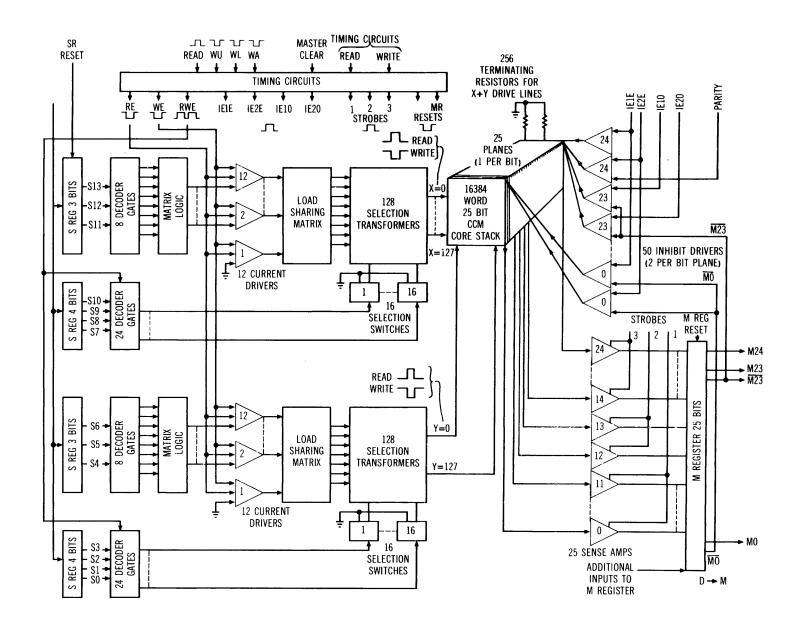

- (4) Memory Unit. The DPS-2402 Computer contains a magnetic core memory operating in a coincident-current mode for storage. The memory has a capacity of 16,384 words of 24 bits (plus one parity bit) each and requires 2 microseconds for one complete read-write cycle.

### c. Symbolism for Registers

- A Accumulator (A-Register)

- (A) Content of the accumulator

- B<sub>b</sub> Specified Index Register (location) i. e., B1, B2, or B3.

- I Instruction Register

- P Program Register

- Q Multiplier-Quotient Register

- S Storage Address Register

- M Memory Register

- D Arithmetic Transient Register

- N Shift Count Register Counter

- X Input-Output Transfer Register

- Z Buffer Control & Real Time Clock Register

### d. Register Descriptions

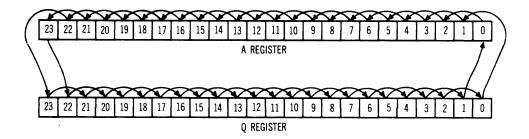

(1) A-Register (24 Bits). - This accumulator, referred to as the A-register, is the principle arithmetic register. Inputs to this register are

derived from the adder selection gates which provide parallel addition and shifting capability. With the exception of multiplication, all arithmetic operations call for one operand to be in this register prior to execution of that instruction.

After addition or subtraction, the A-register contains the sum or difference; after a multiplication, the most significant half of the product remains in the accumulator. Additionally, this register contains both the remainder after the execution of a divide and the number on which logical operations are performed.

The contents of the accumulator may be shifted either left or right, closed or open, as described by the shift operations.

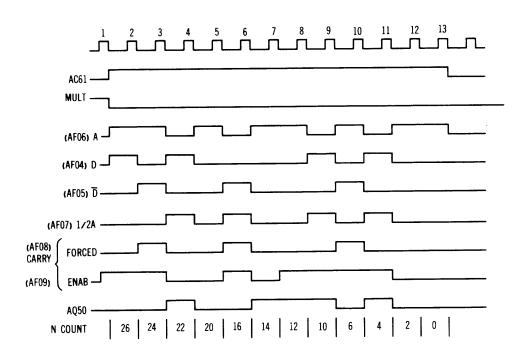

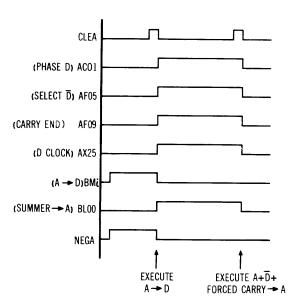

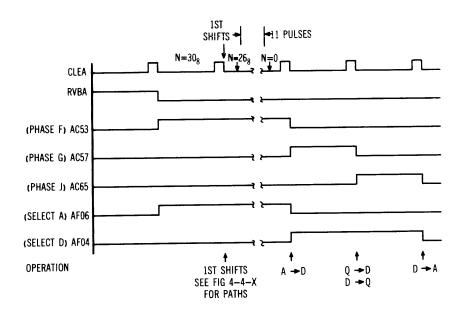

(2) Q-Register (24 Bits). - This register serves as the multiplier-quotient register. Prior to multiplication, the register contains the multiplier. During multiplication, the multiplier is shifted right, two positions at a time. The three least-significant bits are examined during each shift to determine if the multiplicand should be applied to the partial product. At the same time, the significant part of the partial product is shifted right into the Q-register. At the completion of the high-speed multiplication process, facilitated by the two-bit look-ahead feature, the least significant half of the product is found in the Q-register.

The Q-register contains the least significant half of the dividend prior to the division process. This register is used to assemble and hold the quotient, and the sign of the quotient is found in the most significant bit position.

Shifting of the Q-register contents is similar to that of the A-register. There are cases in which the A and Q register are shifted as a single 48-bit register.

(3) D-Register (24 Bits). - The D-register is an intermediate register which contains the operand from memory (Y) while the sum, difference, product, or quotient is being formed. This register also contains the B-modifier while it is being added to the address.

A second function of this register is that it serves to transfer data for instruction words to and from the memory unit and all of the arithmetic and control unit registers.

(4) N-Register (6 Bits). - This register is implemented in the form of a counter and is used to control the shifting during multiplication, division, and shift command execution.

To readily facilitate a programmed floating point, a "scale factor" instruction is included

Figure 1-1-A. Basic Westinghouse DPS-2402 Computer

Figure 1-1-B. Westinghouse DPS-2402 Computer Block Diagram

in the repertoire. After execution of this instruction, the N-register contains the number of positions shifted in the scaling operation. The N-register is not addressable; therefore, the scale factor count is stored in location Y.

- (5) I-Register (24 Bits). The I-register stores the current instruction word and is the source for the interpretor. This register acquires the instruction from memory through the M-register. In addition to serving as an input to the function code and designator translators, this register also inputs to the adder circuit to provide modification of the operand address.

- (6) P-Register (14 Bits). The address of the next instruction is stored in the P-register. This register is loaded through the adder from the I-register and is incremented by 1, automatically, as the instructions are sequentially executed. Execution of a skip instruction causes the P-register to be incremented by an additional 1. The parallel loading of this register is accomplished by the execution of a jump instruction. The contents of the P-register may be stored allowing a jump and set return instruction.

- (7) S-Register (14 Bits). The S-register holds a storage address during memory references. The address is received from the input-output or control units at the beginning of a storage access period. The contents of the S-register then are decoded by the memory address selection system.

- (8) M-Register (25 Bits). The M-register serves as buffer for storage references. At the beginning of each memory access period, the Mregister is cleared. During the read-access period, the contents of the desired memory location are sensed, destroyed, and loaded into the M-register. The contents of M then are written back into memory; the M-register controls the inhibit circuits used to restore the information in the memory location. During the write-access period, the contents of the desired memory location are sensed by the memory sense circuits, but not loaded into the M-register. The M-register is loaded from the input-output or control units; then the contents of M are written into the desired memory location. Twenty-four bits are transmitted between M and D or Z. The 25th bit is a parity check bit.

- (9) X-Register (24 Bits). The X-register is an exchange register which functions to transfer data and commands between the core memory and peripheral equipment.

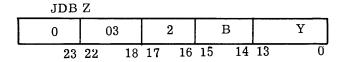

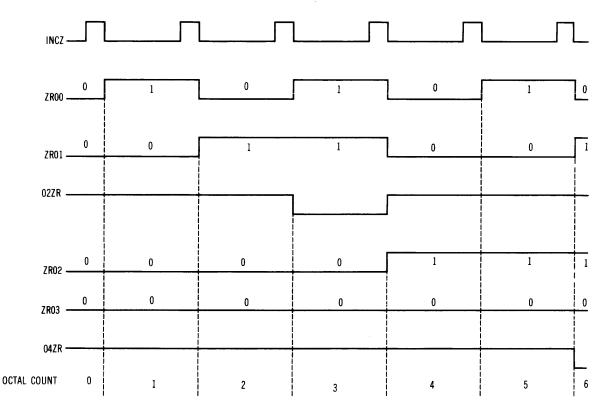

- (10) Z-Register (24 Bits). The Z-register is a 24-bit register which functions to increment a count and an address in buffer mode control and

the contents of the real time clock location.

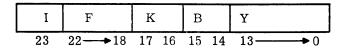

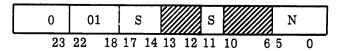

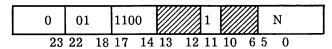

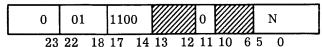

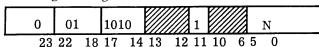

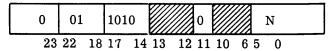

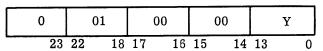

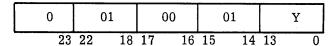

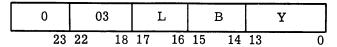

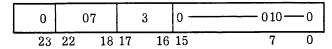

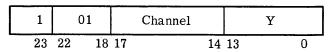

e. Word Formats. - The DPS-2402 has five word formats. One is used frequently and may be regarded as basic. The remaining formats are less common and will be explained later.

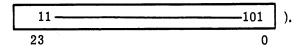

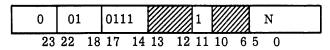

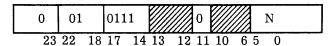

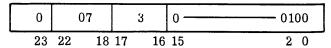

The 24 bit positions of the DPS-2402Computer word are numbered 0 to 23 from right to left. Each instruction is contained in a single 24-bit word.

23 0

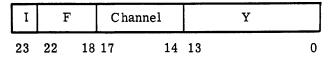

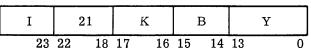

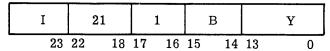

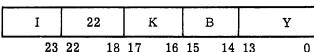

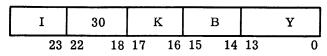

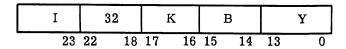

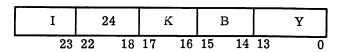

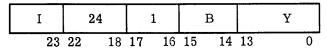

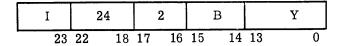

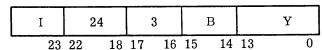

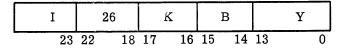

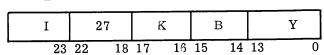

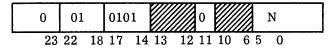

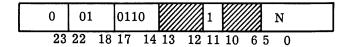

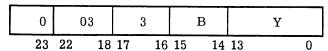

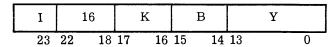

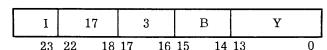

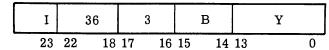

(1) The Basic Instruction Format. - The basic instruction format has an I, F, K, B, and Y field, as shown below.

The I field is used to specify indirect addressing on certain instructions.

The F field specifies the basic function or operation to be performed by the instruction.

The K field contains a designator which modifies or qualifies the instruction in the F field.

The B field is used to specify a B-index which will modify the address given in the Y field by a fixed amount.

The Y field specifies the address of the operand to which the function in the F-field applies.

(2) B Designator. - Three memory locations; 00001, 00002, and 00003, are used as B index registers. These locations may be addressed normally, as well as being used as B index registers.

Instructions whose function specifies an operation on the index registers are not susceptible to relative addressing. All other instructions with a B field are performed as follows:

If B = 0, no indexing occurs.

If B=1, the bits 0 to 13 of location 1 are obtained from memory and added to bits 0 to 13 (the Y-field) of the instruction. If the number added to the Y-field is too large, and a bit needs to be carried into bit 14 position, the memory range overflow indicator will lightup. Bits 0 to 13 of the sum are used as the instruction address.

If B = 2 or B = 3 the operation is similar to the case B=1, using locations 2 and 3, respectively. B-Indexing requires one additional memory reference and is performed before indirect addressing. If an indirect address specifies an index register, one additional memory reference is required, and indexing is affected, before consideration is given the K field option.

(3) Indirect Addressing. - For those instructions which permit indirect addressing (f = 10 through 37), a logical "1" in bit position 23 will specify the indirect option.

Indirect addressing may be explained by the following examples: Unless otherwise noted, all numbers of the examples are octal.

The direct "Enter A" instruction (21000350) will place the contents of memory address 0350 in the A register. The indirect Enter A (61000350) will obtain a location (address) at 0350. Assume the content of 0350 to be 00000150. The computer will place the contents of 150 in the A register.

If the instruction has specified indexing by a b register, this operation would be performed prior to the indirect address cycle. For example if  $B_1=00000005$ , the indirect Enter A instruction 61040350 would obtain the address at 350 + 5 = 355. Assume the content of address 355 is 00007776. The operand to be entered into the A register would be obtained from the contents of address 7776.

If the contents of address 355 had specified a b register, a second indexing process would have occurred. For example if address 355 would have contained 00047776, the operand would have been obtained from address 7776 + 5 = 10003. Thus the content of address 10003 would be entered into the A register,

(4) Multi-Level Indirect Addressing. - The preceding examples all assumed that bit 23 of the <u>location</u> specified by the y field was a logical "O", the machine will continue performing indirect cycles or index and indirect cycles until a logical "O" in the address bit 23 is found. This logical "O" specifies the effective operand address. For example, consider the execution of the instruction 61041000 where the contents of the following locations are:

$B_1 (00001) = 00000001$   $B_2 (00002) = 00000120$   $B_3 (00003) = 00000056$  (01001) = 46742050 (2126) = 43103520 (3640) = 36010250 (10250) = 25432102

The machine will first index the y field of the instruction by  $B_1$  and will obtain the content of address 01001 which is another indirect (bit 23 set). The machine will obtain the next level location after indexing by  $B_3$ , or 2050 + 0056 = 2126; address 2126 also contains an indirect type address (bit 23 set) and calls for indexing by  $B_2$ . Therefore, the address 3520 + 0120 = 3640 would be obtained. This is a "direct" type address (bit 23 clear) and no indexing is specified. Therefore, the operand is finally found at address 10250 and the final content of the A register is 25432102 upon completion of the execution. Each indirect operation requires two microseconds.

There is no limit to the number of indirect operations that can be accomplished. As long as the indirect process is in progress, the computer cannot be stopped by depressing the STOP switch and all Input/Output operations are suspended including real time clock updating and interrupt processing.

(5) K Designator. - The K designators specify which bits of the 24 bit operand word will be used. Four options are available. The options apply after the B and I fields have had their effect on the Y address.

For K = 0 the entire 24 bit word located at the Y address is used as an operand.

For K=1 the right half (RH) of the word at Y is used as the operand. When the operand is acquired, bits 0 to 10 of Y become bits 0 to 10 of the operand, and bit 11 of Y is replicated as bits 11 to 23 of the operand. When a store is performed, bits 0 to 11 of the operand become bits 0 to 11 of Y. The left half of the word at Y is not changed.

For K = 2 the left half (LH) of the word at Y is used as the operand. When the operand is acquired, bits 12 to 22 of Y become bits 0 to 10 of the operand and bit 23 of Y is replicated as bits 11 to 23 of the operand. When a store is performed, bits 0 to 11 of the operand become bits 12 to 23 of Y. The right half of the word at Y is not changed.

For K=3 the 14 low order bits (Y) of the instruction word itself are used as the operand, i. e. the Y field is used as the operand. No operand acquisition from memory is required, since the bits of the Y field become bits 0 to 13 of the operand, and a zero is replicated as bits 14 to 23 of the operand. When a store is performed the Y-field is used as an address and bits 0 to 13 of the operand replace bits 0 to 13 of the word at the memory address indicated by the Y field leaving bits 14 to 23 of the word at Y unchanged.

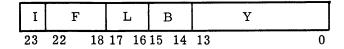

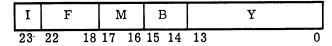

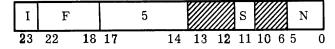

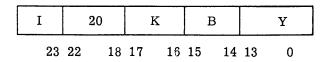

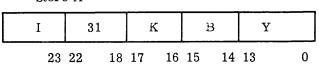

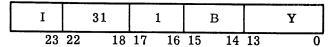

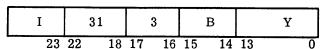

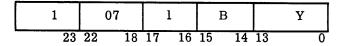

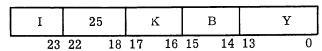

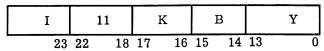

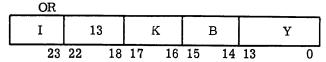

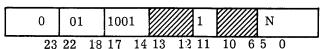

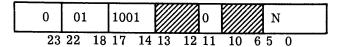

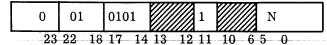

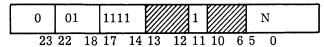

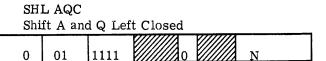

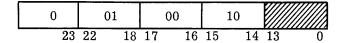

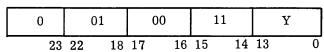

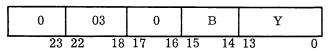

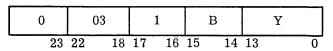

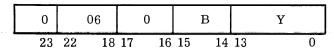

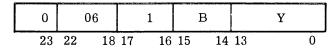

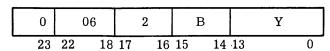

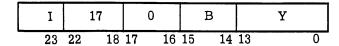

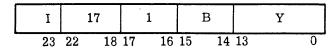

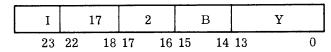

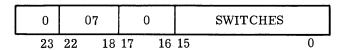

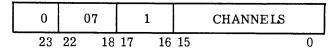

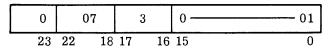

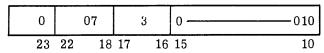

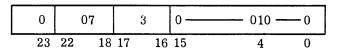

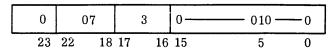

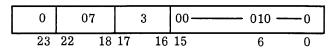

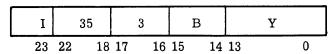

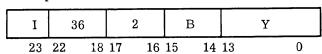

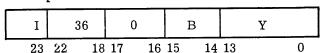

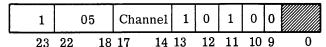

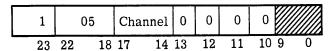

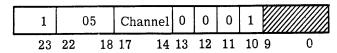

(6) Additional Instruction Formats. - The remaining instruction formats for the DPS-2402 are shown below.

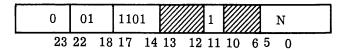

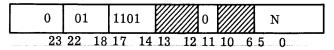

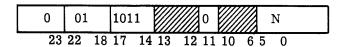

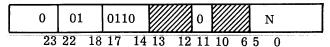

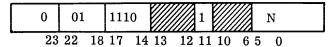

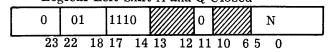

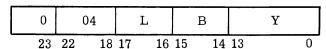

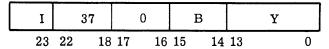

Conditional skip instruction format

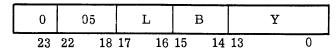

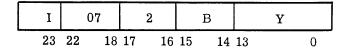

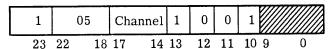

Input/Output instruction format

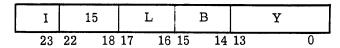

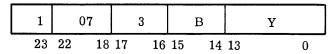

Jump instruction format

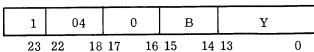

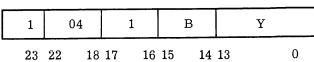

Shift instruction format

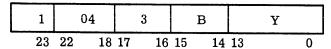

Sense switch instruction format

| I | $\mathbf{F}$ | GP | Bits |

|---|--------------|----|------|

(7) L Designator. - Some skip and jump instructions use an L designator in place of the K designator. In this case, the operand always refers to a full word. The F designator specifies what is to be tested, and the L designator specifies the case for the abnormal sequence.

For L = 0 the skip or jump occurs when the sign of the operand is plus, (or zero).

For L=1 the skip or jump occurs when the sign of the operand is minus.

For L=2 the skip or jump occurs when the operand is zero.

For L=3 the skip or jump occurs when the operand is non-zero.

Special word formats for shift and inputoutput are described concurrent with the instructions. Other instructions requiring the I and/or K field for special designations are described concurrent with the function described concurrent with the function description.

(8) M Designator. - The M designator interpretation of bits 16 and 17 depends on the particular instruction.

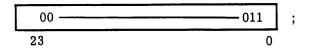

(9) Numeric. - Numeric data are stored in 2's complement form. This applies to both full and half words. Full-word positive numbers have a zero in bit position 23, while negative numbers have a 1 in this bit position (e.g., +3<sub>10</sub> appears in storage as

-3<sub>10</sub> appears in storage as

Half-word numbers similarly have the sign bit as the left most bit of the appropriate half. For example, with the left half-5 and the right half +2 the word in storage appears as

The range of full-word numbers as integer and fraction is given below. Note that with 2's complement notation, zero is unique as a positive number and a negative sign (1 in bit position 23) with 23 trailing zeros representing the largest negative number.

| Integer    |          | Binary | Fra               | actional               |

|------------|----------|--------|-------------------|------------------------|

| 8388607 2  | 3 -1     | 01111  | 1.0 -2            | <sup>23</sup> 99999988 |

|            | 2        | -      |                   |                        |

| 1          | 1        | 00 01  | $2^{-23}$         | .00000012              |

| 0          | 0        | 0000   | 0                 | .0                     |

| -1         | -1       | 1111   | -2 <sup>-23</sup> | 00000012               |

| -8388608 - | $2^{23}$ | 10 00  | -1.0              | -1.0                   |

f. Interrupt Definition and Sources. - The term interrupt refers to the process of causing the computer to execute an instruction out of the programmed sequence. In the interrupt mode, the instruction address is not specified by the P-Register but is instead obtained from a fixed location corresponding to the particular interrupt. The instruction at this fixed interrupt location in most cases would be a Jump and Set Return which stores the point of departure from the program when the interrupt occured and jumps to

the proper subroutine. The interrupt may be ignored by placing a No Operation instruction in the fixed location. It should be noted that when an instruction is acquired from a fixed location, the normal incrementing of the P-Register does not take place.

An interrupt is processed after the completion of the current instruction if it is the highest priority interrupt waiting to be processed. Interrupt priorities are briefly described below.

- (1) Fault Interrupt. If an instruction is executed which has bits 18 to 23 all zero (i. e., a FAULT instruction), and the FAULT REACTION switch is in the "no half" position, the instruction in location 00020 is executed in the interrupt mode.

- (2) Input/Output Parity Error Interrupt. If the computer detects a parity error while reading from memory during the input or output (buffered or express) process and the I/O PARITY REACTION switch is in the "no halt" position, the instruction in location 00021 is executed in the interrupt mode.

- (3) Program Parity Error Interrupt. If the computer detects a parity error while reading instructions or operands from memory and the PROGRAM PARITY ERROR REACTION switch is in the ''no halt'' position, the instruction in location 00022 is executed in the interrupt mode.

- (4) Manual Interrupt. If the computer is running and the MANUAL INTERRUPT switch on the OPERATION panel is depressed, the instruction in location 00023 is executed in the interrupt mode.

- (5) Power Failure Interrupt. Loss of power is sensed 100 microseconds before voltages drop below safe operating levels. Upon sensing imminent power failure, the instruction in location 00026 is executed in the interrupt mode.

- (6) Real Time Clock Interrupt. This interrupt is described under topic 8, "Real Time Clock".

- (7) Input/Output Channel Interrupts. The input/output control provides for both internal (buffer completed) interrupt and external interrupt processing on all channels. See section 4-5 for details and priorities.

- (8) Real Time Clock. When the computer is running and the REAL TIME CLOCK switch is in the ON position, the contents of location 00024 is automatically incremented every 5 milliseconds. The incrementing process does not interrupt the execution of a program, but does require two memory cycles for each update.

An interrupt will occur immediately after the clock has been updated from all 1's to all 0's. This interrupt forces the instruction in location 00025 to be executed in interrupt mode. Since a full 24-bit word is used for the clock location, its 0 to 0 period is slightly less than 24 hours.

The programmer may use this interrupt feature to generate any accurate real time interval by pre-setting the contents of location 00024.

g. Assigned Core Memory Special Locations and Sense Switches

### OCTAL

|    | 00000<br>00001<br>00002<br>00003                            | Master Clear - Start Location<br>Index Register #1<br>Index Register #2<br>Index Register #3                                                                                                       |

|----|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to | 00004<br>00017                                              | Reserved for Index Register Expansion                                                                                                                                                              |

|    | 00020<br>00021<br>00022<br>00023<br>00024<br>00025<br>00026 | Fault Interrupt Location Parity Interrupt Location, I/O Parity Interrupt Location, Program Manual Interrupt Location Real Time Clock Clock = 0 Interrupt Location Power Failure Interrupt Location |

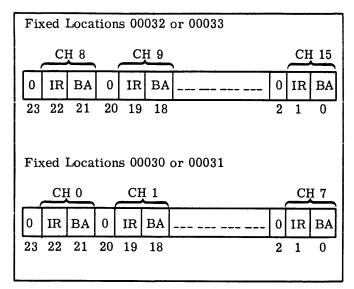

|    | 0030<br>0031<br>0032<br>0033                                | Input Buffer Status, Channels 0 - 7<br>Output Buffer Status, Channels 0 - 7<br>Input Buffer Status, Channels 8 - 15<br>Output Buffer Status, Channels 8-15                                         |

| to | 0040<br>0057                                                | Input Buffer Control Word<br>for Channels 0 through 15                                                                                                                                             |

| to | 0060<br>0077                                                | Output Buffer Control Word<br>for Channels 0 through 15                                                                                                                                            |

| to | 0100<br>0117                                                | Input Buffer Complete Interrupt<br>Locations for Channels 0 through 15                                                                                                                             |

| to | 0120<br>0137                                                | Output Buffer Complete Interrupt<br>Locations for Channels 0 through 15                                                                                                                            |

| to | 0140<br>157                                                 | External Interrupt Status Word<br>Address for Channels 0 through 15                                                                                                                                |

| to | 160<br>177                                                  | Input External Interrupt Locations for Channels 0 through 15                                                                                                                                       |

| to | 0200<br>0217                                                | Output External Interrupt Locations<br>for Channels 0 through 15                                                                                                                                   |

h. Detailed Description of Instructions. - Instructions are divided functionally into eight categories: data transfer, arithmetic, logical, shift, increment, conditional skip, jump, and input-output. The assembler, descriptive name, and field designation are presented for each instruction. Timing is given as the number of

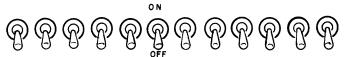

Sense Switch Assignments

| Bit | Manual Switch       | Input Data<br>Available | Output Data<br>Lines Available | Special                  |

|-----|---------------------|-------------------------|--------------------------------|--------------------------|

|     | GP = 0              | GP = 1                  | GP = 2                         | GP = 3                   |

| 0   | Switch 0            | Channel 0               | Channel 0                      | Arithmetic Overflow      |

| 1   | Switch 1 (S1)       | Channel 1               | Channel 1                      | Division Error           |

| 2   | Switch 2 (S2)       | Channel 2               | Channel 2                      | Shift Parity             |

| 3   | Switch 3            | Channel 3               | Channel 3                      | Sign A                   |

| 4   | Switch 4            | Channel 4               | Channel 4                      | Sign of Q                |

| 5   | Switch 5            | Channel 5               | Channel 5                      | Contents of $A = 0$      |

| 6   | Switch 6            | Channel 6               | Channel 6                      | Memory Range Overflow    |

| 7   | Switch 7            | Channel 7               | Channel 7                      | Master Lockout           |

| 8   | Switch 8            | Channel 8               | Channel 8                      | Program Flag Light (set) |

| 9   | Switch 9            | Channel 9               | Channel 9                      | )                        |

| 10  | Switch 10           | Channel 10              | Channel 10                     |                          |

| 11  | Switch 11           | Channel 11              | Channel 11                     |                          |

| 12  | Clock - ON, OFF     | Channel 12              | Channel 12                     | Not Assigned             |

| 13  | Parity Reaction     | Channel 13              | Channel 13                     |                          |

| 14  | Parity Reaction I/O | Channel 14              | Channel 14                     |                          |

| 15  | Fault Reaction      | Channel 15              | Channel 15                     | J                        |

memory accesses to acquire the instruction and operand and to perform the instruction without indexing or indirect addressing. One memory access is added for each indirect addressing operation and one memory access for each address modification by an index register. The first instruction in a category is described in more detail than its various options. A composite list of all instructions appears in Figure 1-1-C.

(1) Address Indexing. - For those instructions which allow indexing, the specification of a B modifier will cause the contents of the designated B-Index location to be added to the direct or indirect Y field. The resulting sum serves as the operand address or the new indirect address. Each indirect address level can indicate a different or no B modifier.

Timing: 1 cycle for direct addressing 1 cycle per level for indirect addressing

(2) Multiple-Level Indirect Addressing. - Execution of an indirect instruction is identical

to the execution of its direct equivalent once the effective address has been attained. The indirect cycle can run indefinitely and is stopped by the acquisition of any direct instruction code. The indirect address at every level is modified by the contents of B specified at that level.

(3) Enter Class Instructions (DATA TRANS-FER)

ENA Enter A

With K=0, the contents of location Y replace the contents of the A register. The contents of location Y remain unchanged. Indexing and indirect addressing apply in all combinations. No other registers are changed and the next instruction is taken in sequence. Timing: 2 cycles.

|                              |          |       | LGR QC LGR AQC<br>LGL QC LGL AQC          |                           |     | DD1 Y                               | SSK N    | STS                | 1                         | SUB1 N  |         | SOF, SDE, SOP, SAM, SQM, SAZ, SMO, SMS, HEY | NOP                | AND Y * | *             |                 | * *                      | EOR Y *     | * * * * |                            | SCP N                               | CMP Y *           | 14 52A |                       | ENQ Y *            | ENA Y *        | ENB Y *          |      | RAD Y         | * * * * * * * * * * * * * * * * * * * | SUB Y *       | * WUL Y       | * * X AIO         |           | STQ Y            | STA Y            | Y Y              | B=0 STZ Y  | RSB Y         | INOP         | ЈМР QР          | JMP CML          | Not Indexable | JSR SML<br>Not Indexable                 |                                               |                      |                              | t t                                                       |                    | d providing B = 0.                                                                                                                                                   | nd. The high                                                                                                                                            |                       | t addressing is tield of the                                                                                                                                                                                                                        |

|------------------------------|----------|-------|-------------------------------------------|---------------------------|-----|-------------------------------------|----------|--------------------|---------------------------|---------|---------|---------------------------------------------|--------------------|---------|---------------|-----------------|--------------------------|-------------|---------|----------------------------|-------------------------------------|-------------------|--------|-----------------------|--------------------|----------------|------------------|------|---------------|---------------------------------------|---------------|---------------|-------------------|-----------|------------------|------------------|------------------|------------|---------------|--------------|-----------------|------------------|---------------|------------------------------------------|-----------------------------------------------|----------------------|------------------------------|-----------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |          |       | LGR C L                                   |                           |     |                                     | 8        |                    |                           | 8<br>IS |         | 3 SOF,                                      | 8                  |         |               | 3               | e<br>2                   | 3 E         | en      |                            | e<br>S                              | 3                 |        |                       | S E                | 3 H            | e                |      | Б             | 8                                     | e2            | 8             | 8                 | ŀ         | ო                | e .              | 60               |            |               | 8            | 8               | 8                |               | es .                                     |                                               |                      | $^{b}_{11}$                  | U left<br>1 righ                                          |                    | the operan<br>s the opera                                                                                                                                            | the operar                                                                                                                                              | ss indirec            | ises the B                                                                                                                                                                                                                                          |

| e Mnemonics                  |          |       | LGR Q LGR AQ<br>LGL Q LGL AQ              |                           |     | ДОВ Z<br>АДОТ Т.Н                   | SSK Z    | ELS<br>SSH 7.      |                           | SUB1 Z  |         | ООР                                         | JHT                | AND LH  |               |                 | SCL LH                   | EOR LH      | SRT LH  |                            | SCP Z                               | CMP LH            | 240    | CYS Z                 | ENQ LH             | ENA LH         | ENB LH           |      | кар гн        | АББ Г.Н                               | SUB LH        | MUL LH        | DIV LH            |           | STQ LH           | STA LH           | STB LH           | B=0 STZ LH | RSB LH        | NOT ASSIGNED | JMP AZ          | JMP S2           |               | JSR AZ                                   | ssing in the assembly<br>field in parenthesis |                      | b <sub>14</sub>              | o logical<br>1 arithmetic                                 |                    | order 14 bits of the instruction with 10 leading zelos are used as the operand p,<br>the low order 14 bits of the designated index register are used as the operand, | The low order 14 bits of the location called out by the addr. sa are used as order 10 bits are zero after fetching and are not disturbed while storing. | function applies unle | The B field designates the index register to which the function applies unless indirect addressing specified. Indirect addressing uses the B field to designate indexing and uses the B field of the indirect address word as nart of the function. |

| Language                     |          |       | AQC LGR<br>AQC LGL                        |                           |     | 62 63                               | 62       | 2 2                | BIM                       | 2       |         | 67                                          | 22                 | 2       | -             | NI              | 2                        | 73          | 6       | 1                          | 8                                   | 2                 |        | eq.                   | 63                 | 22             | 8                |      | 62            | 2                                     | 2             | 2             | 63                | 1         | 81               | 8                | 2                |            |               | TED 2        | 2               | 7                |               | 61                                       | addressin                                     | essing               | L <sup>q</sup>               |                                                           | ount.              | 10 leadin                                                                                                                                                            | out by the<br>not distu                                                                                                                                 | which the             | which ure<br>eld to desi                                                                                                                                                                                                                            |

| Assembly 3, 17               |          |       | SHR QC SHR A<br>SHL QC SHL A              |                           |     | ADD1 RH                             | SSK M    | SAL<br>SSH M       | BOMTI, BIMT,              | SUB1 M  |         | IDA                                         | XAQ                | AND RH  |               | Юк кн           | SCL RH                   | EOR RH      | хвт вн  |                            | SCP M                               | CMP RH            |        | CYS M                 | ENQ RH             | ENA RH         | ENB RH           |      | RAD RH        | ADD RH                                | SUB RH        | MUL RH        | DIV RH            |           | STQ RH           | STA RH           | STB RH           | B=0 STZ RH |               | NOT ASSIGN   | JMP AM          | JMP S1           |               | JSR AM                                   | To specify indirect address                   | I indirect addr      |                              | 1 circular<br>0 linear                                    | N is 6 bit shift c | Instruction with<br>s of the design:                                                                                                                                 | ocation called e                                                                                                                                        | lex register to       | lex register to<br>ig uses the B fil<br>for the function                                                                                                                                                                                            |

| BITS 16,                     |          |       | TLY<br>SHR C S                            |                           |     |                                     | -        |                    | BOMT.                     | 1       |         |                                             | 1                  | 1       | ,             | -               | 1                        | 1           | -       | -                          | <del>-</del>                        | F                 |        | <del>-</del>          |                    | -              | 1                |      | -             | -                                     | -             |               | -                 | •         | П                | П                | -                |            | π             |              |                 | 1                |               | <del>-</del>                             | To g                                          | sing I = 1           |                              | KBAQ                                                      | 2                  | lts of the i<br>der 14 bit                                                                                                                                           | ts of the l<br>ero after f                                                                                                                              | tes the inc           | addressir                                                                                                                                                                                                                                           |

| DESIGNATOR FOR               | T        |       | SCAQ RBAQ<br>SHR Q SHR AQ<br>SHL Q SHL AQ |                           |     | ADD1                                | SSK P    | CIR SSH D          | BINI, BOT, BOTI,          | SUB1 P  |         | SSW                                         | NEG                | AND     |               | NOI             | SCL                      | EOR         | Free    | 3D 1                       | SCP P                               | CMP               |        | CYS P                 | ENQ                | ENA            | ENB              |      | RAD           | ADD                                   | SUB           | MUL           | DIV               |           | STQ              | STA              | STB              | B=0 STZ    | RSB           | XEQ          | JMP AP          | JMP              |               | JSR                                      | signator                                      | no direct addres     | esignator<br>b <sub>16</sub> | 0 use A and 1 use Q                                       | 1 use AQ           | The low order 14 b If $B \neq 0$ , the low or                                                                                                                        | he low order 14 bi                                                                                                                                      | he B fleld designa    | he b Held woslend<br>pecified, Indirect                                                                                                                                                                                                             |

| DESIG                        | FAULT    | EXI   |                                           | EXO                       |     |                                     | 0        |                    | BIN.                      | 0       | EXF     | 0                                           | 0                  |         |               | <b>-</b>        | 0                        | 0           | -       | <b>D</b>                   | 0                                   | 0                 | -      | 0                     | 0                  | 0              | 0                |      | 0             | 0                                     | 0             | 0             | -                 | >         | 0                | 0                | 0                |            | 0             | 0            | 0               | 0                |               | 0                                        | I do                                          | I = 0                | 8 d                          | 0 1 0                                                     |                    | *<br>                                                                                                                                                                | +                                                                                                                                                       | - 1                   | + +                                                                                                                                                                                                                                                 |

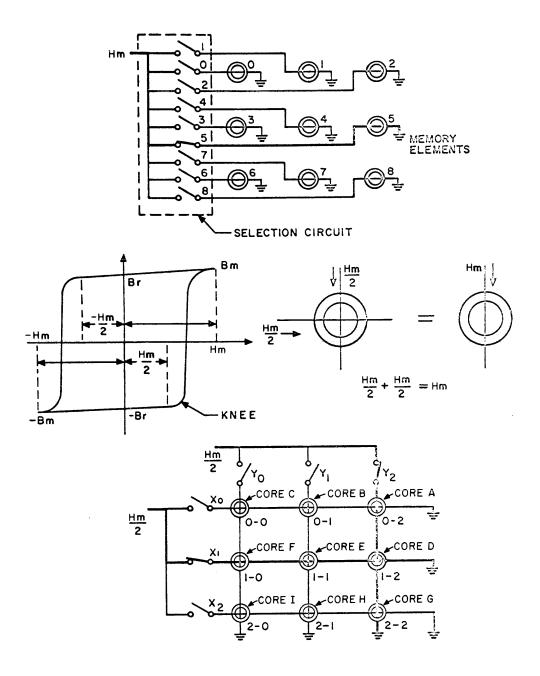

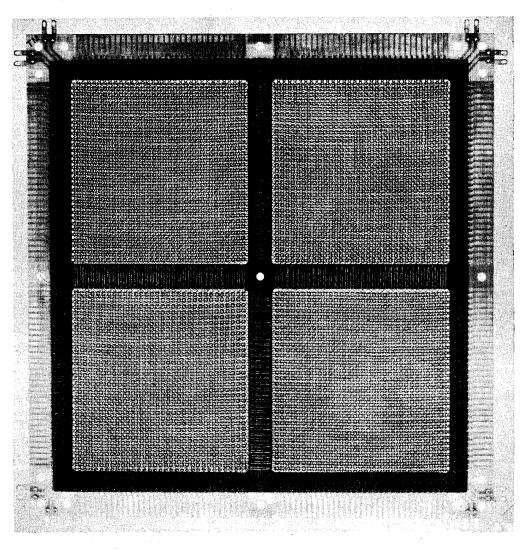

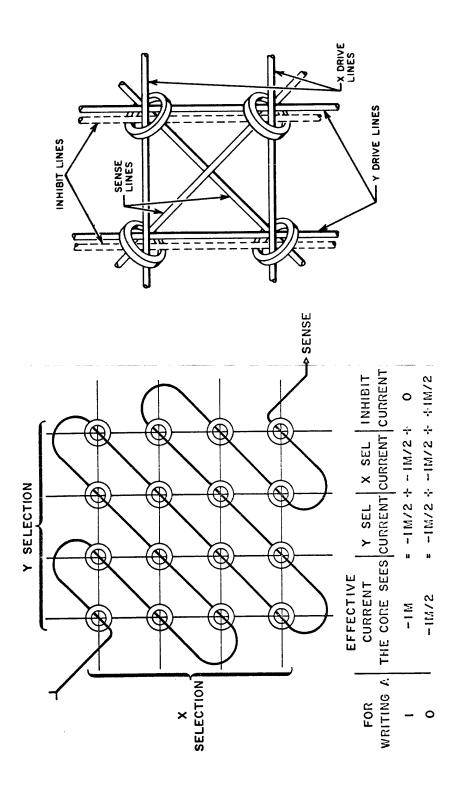

| Definition                   | []       | ) ]   |                                           | (Y)→CHANNEL & output ack. |     | (B) - 1 → B, cond, jump (Y) + 1 → Y | (Y), cor | Change interrupt a | (Y) shifted left 1, cond. |         | (X)     | Senseline Test                              |                    | 1       | (A) ^ (Y) + A | (A) \ (Y) \ \ A | Clear (A) for 1's of (Y) | (A) ⊕ (Y) A |         | Ħ                          | (A) - $[(Q) \land (Y)]$ , cond skip | if (A) < (Y) skip |        | (A) - (Y), cond. skip | Enter Q, (Y) → (Q) | Enter A, (Y) A | Enter B, (Y) → B |      | (A) + (Y) - Y | (A) + (Y) - A                         | (A) - (Y) - A | (Q) x (Y) AQ  | ▼ O ← (x) ÷ (O v) | (1)       | Store Q, (Q) → Y | Store A, (A) → Y | Store B, (B) → Y | †          | (A) - (Y) → Y | Execute (Y)  | (A), cond. jump | misc. cond. jump |               | (P) $\longrightarrow$ Y, jump to (Y) + 1 |                                               | 0 N: L = 3 ( ) ≠ 0   | NO INDEXING                  | $Y + (B1) \longrightarrow Y$ $Y + (B2) \longrightarrow Y$ |                    | SIGNATOR dependent on particular instruction.                                                                                                                        | 1                                                                                                                                                       |                       | storing                                                                                                                                                                                                                                             |