CUSTOMER ENGINEERING TRAINING AND DOCUMENTATION

741-9034

### **CUSTOMER ENGINEERING TRAINING CENTER**

# OIS 40/50/60 BOARD REPAIR WORKBOOK VOLUME 1

"This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary information, and its use is restricted soley to assisting you in servicing Wang products, neither this document nor its contents may be disclosed, copied, revealed or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang."

#### PREFACE

This document is intended to be used for TRAINING PURPOSES only. The material contained in this document, while accurate during the development of this workbook, may not reflect the latest developments or changes to the OIS 40/50/60 system.

### TECHNICAL SUPPORT DOCUMENTS

OIS 50 INTERNAL PRINTER CONTROLLER HARDWARE SPECIFICATIONS HM-60

OIS 40/50 RESOURCE MANAGEMENT UNIT THEORY OF OPERATION 751-0902

OIS 40/50 RESOURCE CONTROL UNIT THEORY OF OPERATION 751-0911

OIS 40/50 IWS FULL MATRIX CONTROLLER SPECIFICATION HM-67

WL-2630 OIS/VS COLLECTIVE GATE ARRAY SPECIFICATION HM-37

OIS-50 INTERNAL WISE SPECIFICATION REVISION 3 HM-85

OFFICE INFORMATION SYSTEMS OIS 40/50/60 741-1267

OIS SYSTEM ADMINISTRATION GUIDE 700-5562E

First Edition - December, 1985

C Copyright WANG Labs., Inc., 1985

# OUTLINE OF WORKBOOK

|          | SECTION # | TITLE                                 |

|----------|-----------|---------------------------------------|

| VOLUME 1 |           |                                       |

|          | 1.        | Introduction to System                |

|          | 2.        | Resource Management Unit (RMU)        |

|          | 3.        | Resource Control Unit (RCU)           |

|          | 4.        | Internal Workstation Controller (IWS) |

|          | 5.        | Appendices (A-E)                      |

| VOLUME 2 |           |                                       |

|          | 6.        | Internal Printer Controller (IPC)     |

|          | 7.        | Internal WISE Controller (IWISE)      |

|          | 8.        | Diagnostics                           |

|          | 9.        | Appendices (F-K)                      |

# TABLE OF CONTENTS VOL I

| CHAPTER                                                                                 |                                                                                                                                                                                                                        | Page                                                                         |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|                                                                                         | SECTION 1                                                                                                                                                                                                              |                                                                              |

|                                                                                         | 01S 40/50/60 WORKBOOK INTRODUCTION                                                                                                                                                                                     |                                                                              |

| 1.1 OIS                                                                                 | 5 40/50/60 SYSTEM INTRODUCTION                                                                                                                                                                                         | 1-2                                                                          |

| 1.2.1<br>1.2.2<br>1.2.3<br>1.2.4                                                        | Resource Management Unit (RMU) Resource Control Unit (RCU) The Internal Workstation Controller (IWS) The Internal Printer Controller (IPC) The Internal WISE Controller (IWISE)                                        | 1-3<br>1-5<br>1-5<br>1-7<br>1-8<br>1-8                                       |

|                                                                                         | SECTION 2                                                                                                                                                                                                              |                                                                              |

|                                                                                         | Resource Management Unit (RMU)                                                                                                                                                                                         |                                                                              |

| 2.1.1<br>2.1.2                                                                          | ource Management Unit (RMU) Controls and Indicators Clock Generation Memory Mapped Input/Output                                                                                                                        | 2-1<br>2-5<br>2-13<br>2-14                                                   |

| 2.2.1<br>2.2.2                                                                          | DA CENTRAL PROCESSOR UNIT Z80A CONTROL LINES ADDRESS BUS DATA BUS                                                                                                                                                      | 2-18<br>2-18<br>2-22<br>2-22                                                 |

| 2.3 COU                                                                                 | JNTER TIMER CHIP                                                                                                                                                                                                       | 2-24                                                                         |

| 2.4.2<br>2.4.3<br>2.4.4<br>2.4.5<br>2.4.6                                               | MORY Z80A and Direct Memory Access Paths Memory Parity Generator/Checker Memory Refresh RAS/CAS Signal Generator RAS/CAS Timing Read/Write Signal Generator Programmable Read Only Memory                              | 2-26<br>2-26<br>2-30<br>2-33<br>2-35<br>2-37<br>2-38                         |

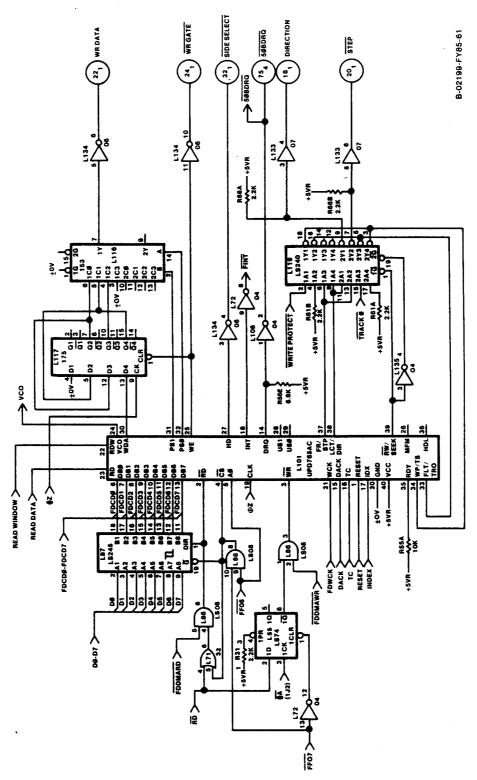

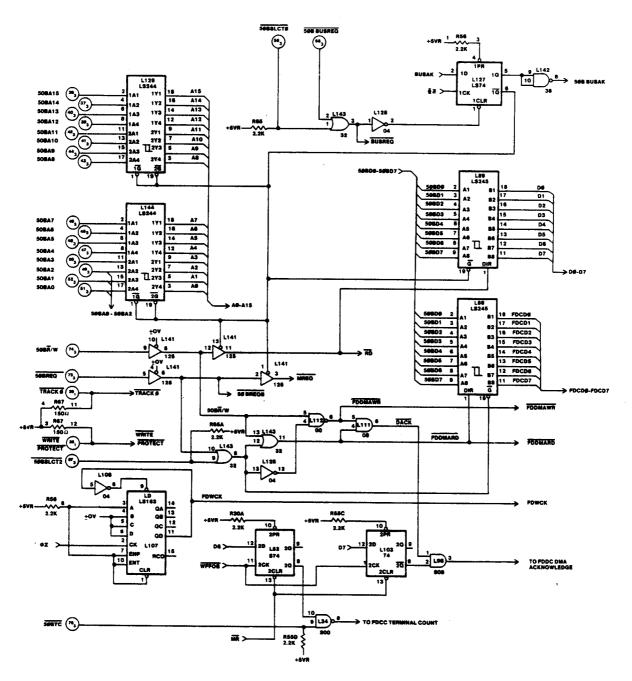

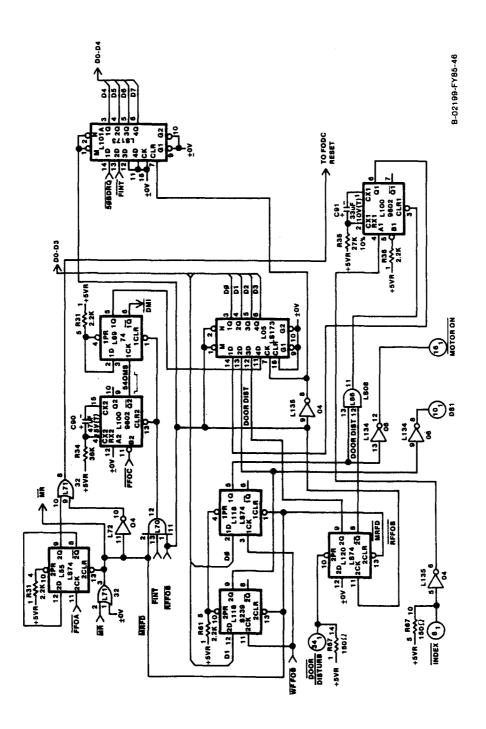

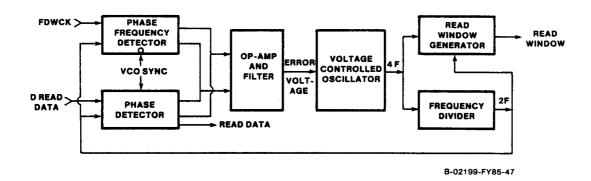

| 2.5.1<br>2.5.2<br>2.5.3<br>2.5.4<br>2.5.5<br>2.5.6<br>2.5.7<br>2.5.8<br>2.5.9<br>2.5.10 | PPY DISK CONTROLLER Read/Write Operation Read/Write Enabling Control Signal Generator Write Data Precompensation Motor Control Terminal Count DMA Acknowledge Deadman Timer Floppy Disk Controller Reset Data Recovery | 2-40<br>2-40<br>2-43<br>2-45<br>2-46<br>2-47<br>2-48<br>2-48<br>2-49<br>2-49 |

| CHAPTER  |                                           | Page |

|----------|-------------------------------------------|------|

| 2.6 SER  | IAL DATA LINK                             | 2-56 |

| 2.6.1    | Command Decoder                           | 2-56 |

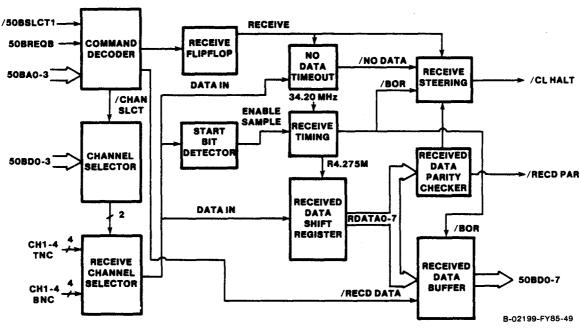

| 2.6.2    | Receive Operation                         | 2-59 |

| 2.6.3    | Transmit Operations                       | 2-62 |

| 2.6.4    | Status Register                           | 2-66 |

|          |                                           |      |

|          | SECTION 3                                 |      |

|          | Resource Control Unit (RCU)               |      |

| 3.1 Reso | urce Control Unit (RCU)                   | 3-1  |

| 3.1.1    | GENERAL INFORMATION                       | 3-1  |

|          | RMU-RCU Interaction                       | 3-3  |

| 3.1.3    | RMU-RCU Interface                         | 3-5  |

|          | 05 MICROCONTROLLER                        | 3-9  |

|          | Microcontroller Instruction Storage Area  | 3-13 |

|          | Left Bank Scratchpad Memory               | 3-13 |

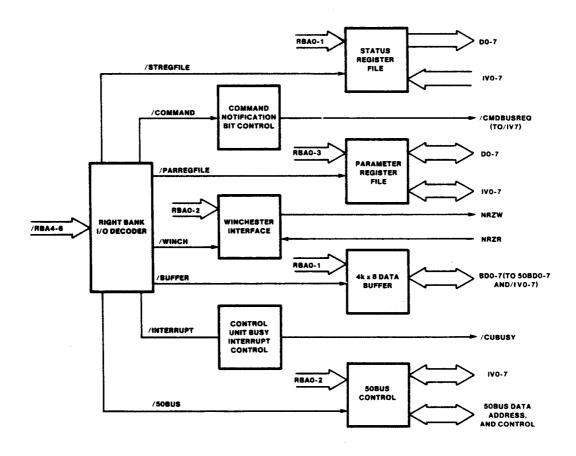

| 3.2.4    | Right Bank I/O Decoder Operations         | 3-19 |

| 3.3 RIG  | HT BANK OPERATIONS                        | 3-22 |

| 3.3.1    | Status Register File Control I/O Commands | 3-22 |

| 3.3.2    | Parameter Register File Control I/O Comma | 3-24 |

| 3.3.3    | Command Notification Bit Issuance I/O Com | 3-25 |

| 3.3.4    | 4K x 8 Data Buffer Control I/O Commands   | 3-26 |

|          | 50BUS Control I/O Commands                | 3-27 |

|          | Winchester Control I/O Commands           | 3-30 |

| 3.3.7    | Interrupt Issuance I/O Command            | 3-35 |

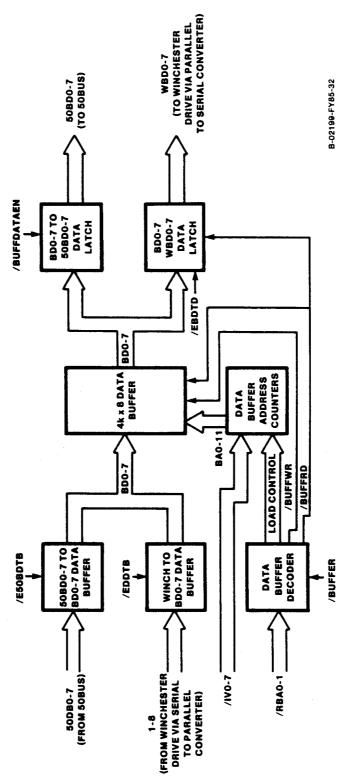

| 3.4 4K   | x 8 DATA BUFFER and 50BUS INTERFACE       | 3-36 |

|          | 4K x 8 Data Buffer                        | 3-36 |

|          | Data Buffer I/O Command Functions         | 3-39 |

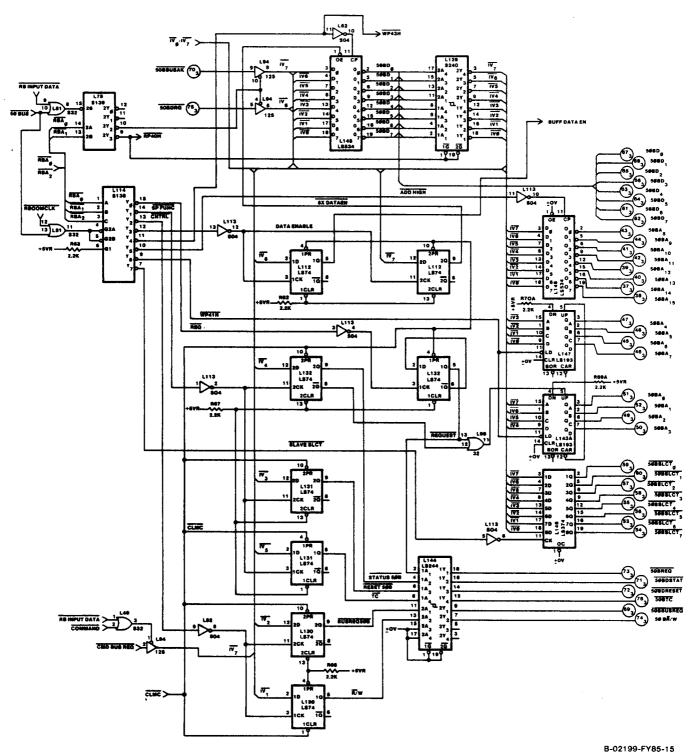

|          | 50BUS Interface                           | 3-40 |

| 3.4.4    | 50BUS I/O Command Functions               | 3-42 |

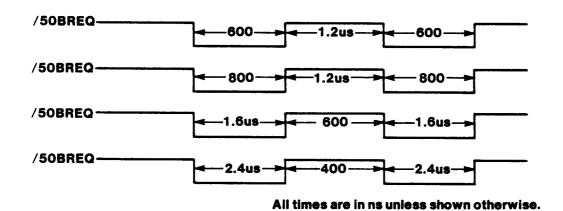

|          | Interfacing to a Parallel Device on the 5 | 3-46 |

| 3.4.6    | Microcontroller Halt Circuit              | 3-48 |

| 3.5 WIN  | CHESTER DISK DRIVE INTERFACE              | 3-51 |

| 3.5.1    | Winchester I/O Command Functions          | 3-51 |

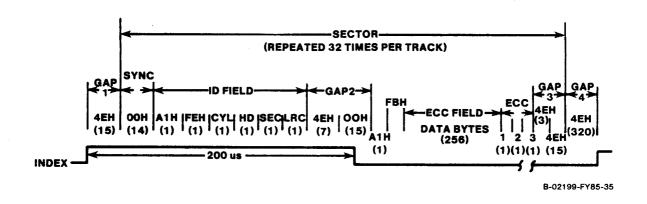

| 3.5.2    | Winchester Data Format                    | 3-59 |

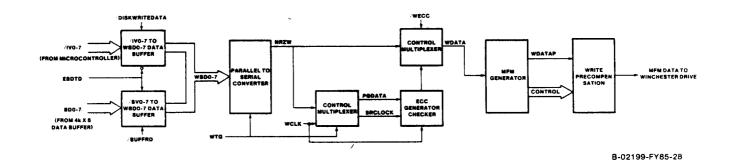

| 3.5.3    | Winchester Write Operation                | 3-61 |

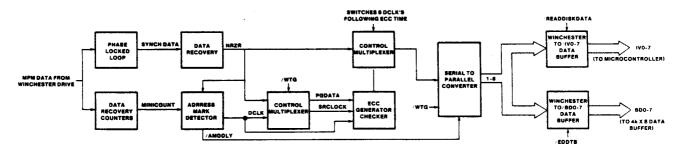

|          | Winchester Read Operation                 | 3-63 |

|          | ECC Generator/Checker                     | 3-65 |

| 3.5.6    | Winchester Step Logic                     | 3-69 |

| 3.5.7    | Dead Man Timer                            | 3-70 |

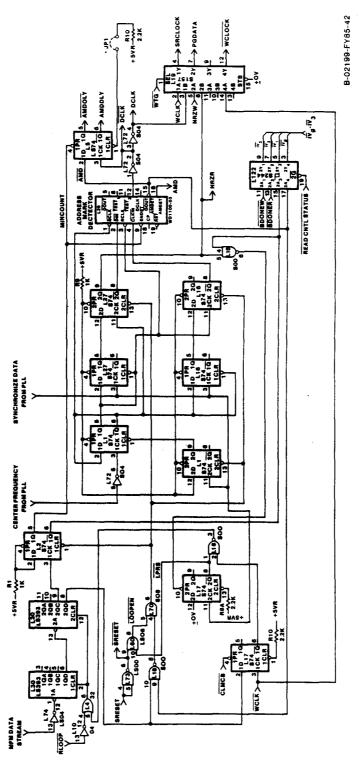

| 3.5.8    | Phase Locked Loop                         | 3-71 |

|          | Data Recovery                             | 3-73 |

| 3 5 10   | Data Recovery Logic Reset Control         | 2-76 |

| CHAPTER                                                                                                                                                                                                                                                       | Page                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| 3.6 STATUS AND PARAMETER REGISTER FILES 3.6.1 SRF-PRF Control 3.6.2 Status Register File 3.6.3 Microcontroller Writes to the SRF 3.6.4 RMU Reads from the SRF 3.6.5 Parameter Register File 3.6.6 Microcontroller Accesses the PRF 3.6.7 RMU Accesses the PRF | 3-78<br>3-78<br>3-79<br>3-80<br>3-82<br>3-82<br>3-83<br>3-86 |

| SECTION 4                                                                                                                                                                                                                                                     |                                                              |

| Internal Workstation Controller (IWS)                                                                                                                                                                                                                         |                                                              |

| 4.1 The CPU and Support Logic. 4.1.1 Clock Generation 4.1.2 Z80A Control Inputs 4.1.3 Control Outputs 4.1.4 Address Bus 4.1.5 Data Bus 4.1.6 MMI/O Decoders                                                                                                   | 4-4<br>4-4<br>4-9<br>4-9<br>4-10                             |

| 4.2 Main Memory and Control Logic 4.2.1 Addressing Main Memory 4.2.2 Data Transfers 4.2.3 Parity Circuits                                                                                                                                                     | 4-12<br>4-12<br>4-14<br>4-15                                 |

| 4.3 Display Memory and Control Logic 4.3.1 Character/Control Memory 4.3.2 Font Memory                                                                                                                                                                         | 4-17<br>4-19<br>4-22                                         |

| 4.4 Display Timing 4.4.1 Display Memory Access 4.4.2 Display Modification Logic                                                                                                                                                                               | 4-24<br>4-29<br>4-31                                         |

| 4.5 Keyboard Interface 4.5.1 The 8031 Microcontroller 4.5.2 Receive Operations 4.5.3 Transmit Operation 4.5.4 The 8031 Instruction Cycle                                                                                                                      | 4-37<br>4-37<br>4-39<br>4-39<br>4-40                         |

| 4.6 OIS 40/50/60 Bus Interface Logic 4.6.1 Read operation 4.6.2 Write Operation 4.6.3 Status Information 4.6.4 Block Transfers                                                                                                                                | 4-41<br>4-41<br>4-42<br>4-42                                 |

| СНАРТЕ | CR .                                                                                                                                            | Page                     |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|        | SECTION 5<br>APPENDICIES                                                                                                                        |                          |

| A      | RELATED DOCUMENTATION                                                                                                                           | A-1                      |

| В.     | OIS 40/50/60 MNEMONICS Part 1: Resource Management Unit (RMU) Part 2: Resource Control Unit (RCU) Part 3: Internal Workstation Controller (IWS) | B-1<br>B-11<br>B-26      |

| С      | CHIP LIST Part 1: Resource Management Unit (RMU) Part 2: Resource Control Unit (RCU) Part 3: Internal Workstation Controller (IWS)              | C-1<br>C-15<br>C-29      |

| D      | QUIZ ANSWERS Section 1 Section 2 Section 3 Section 4                                                                                            | D-1<br>D-2<br>D-3<br>D-4 |

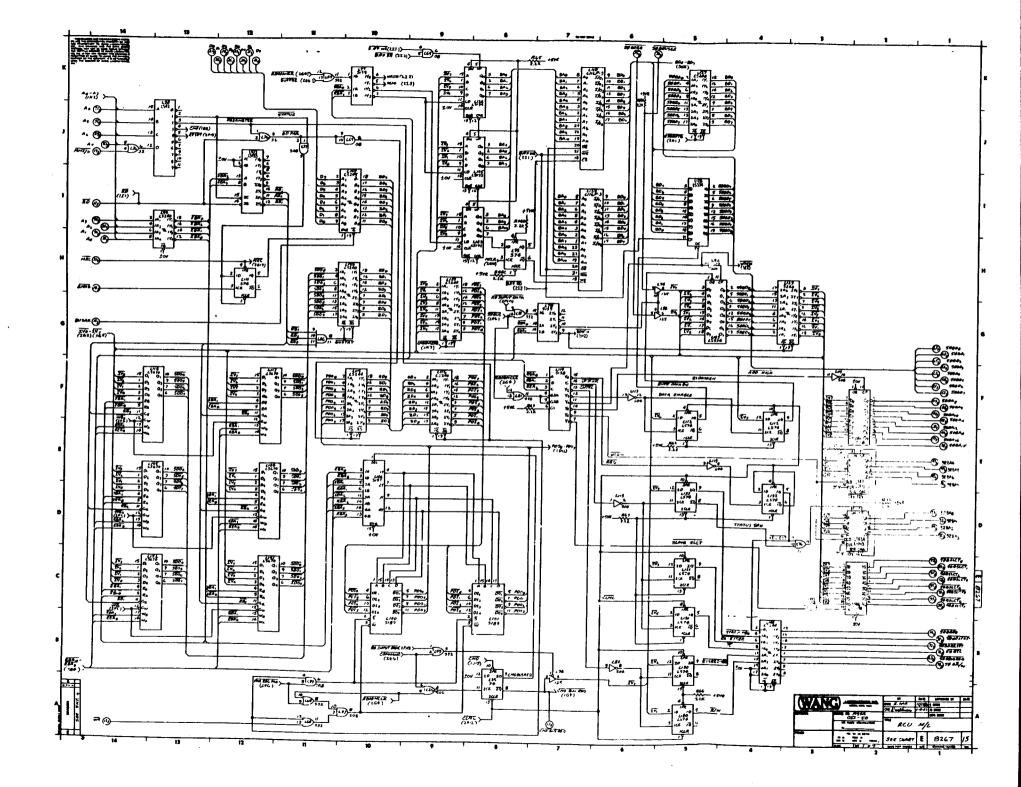

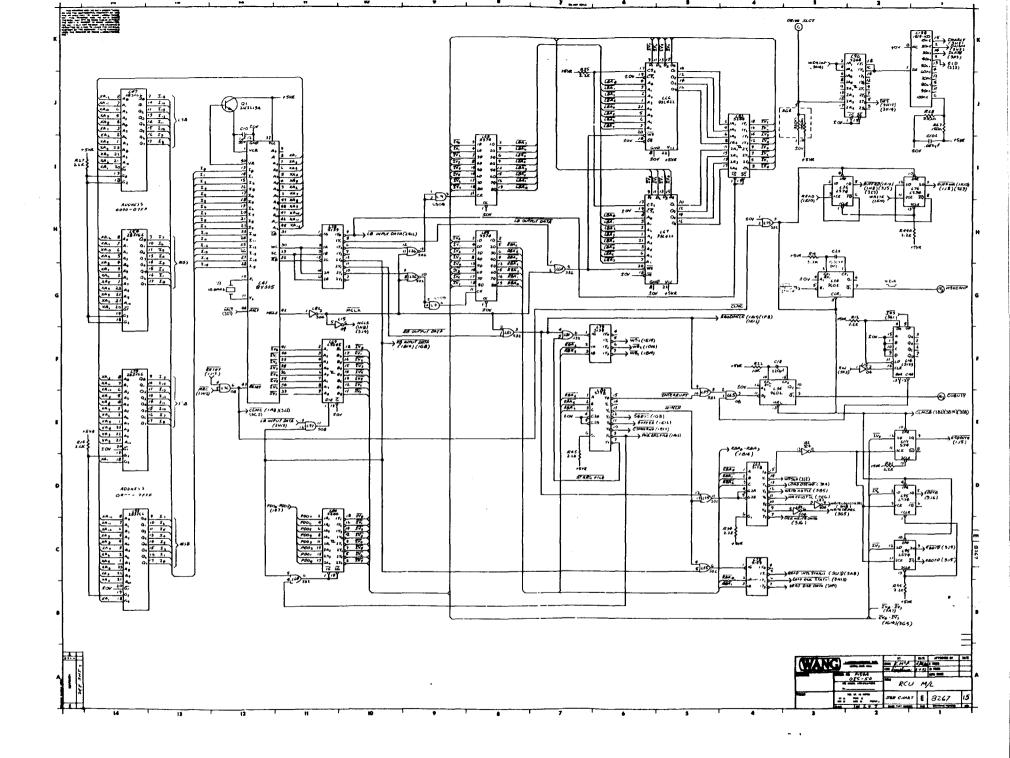

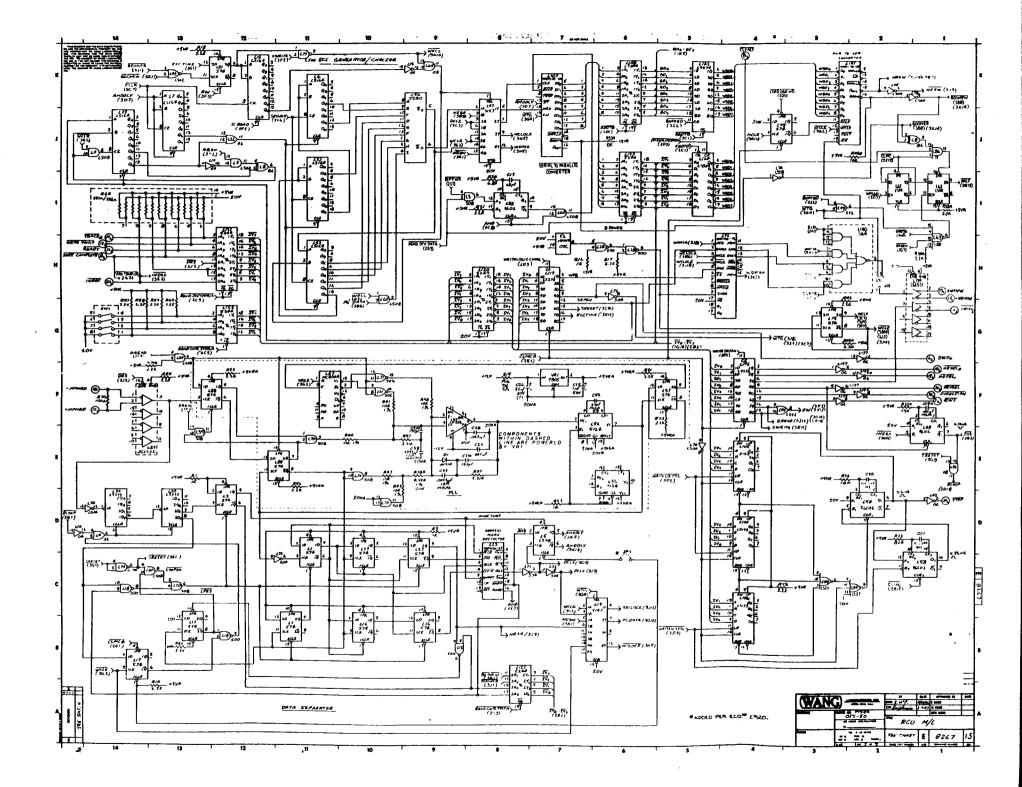

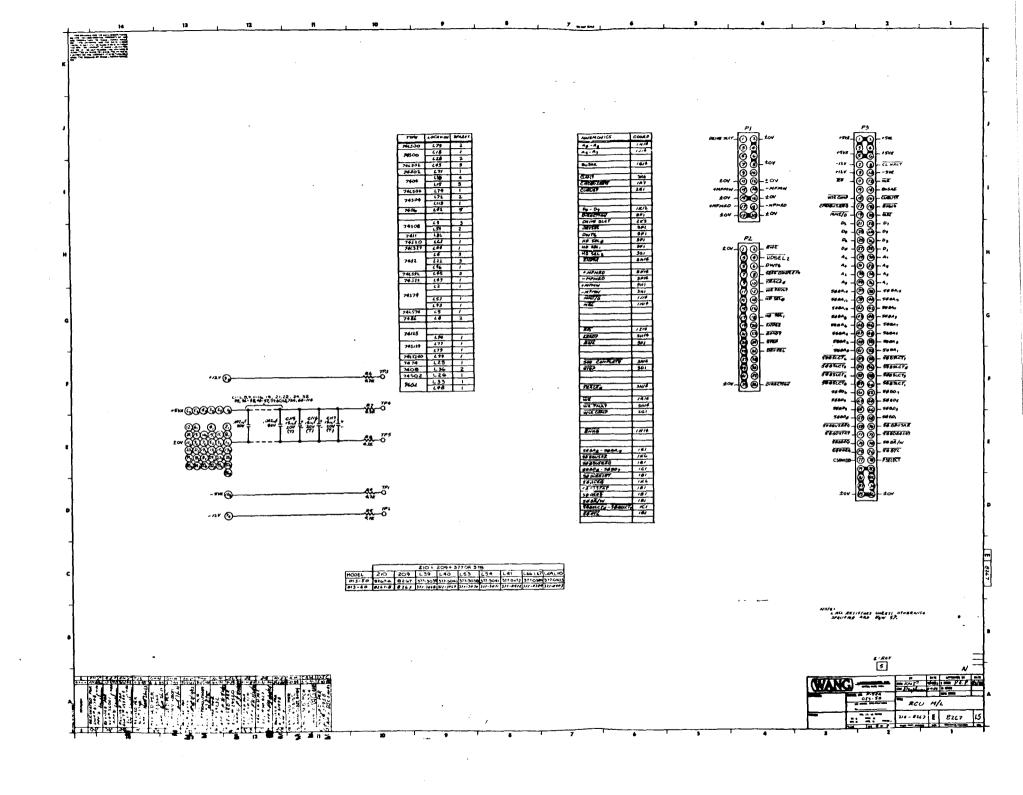

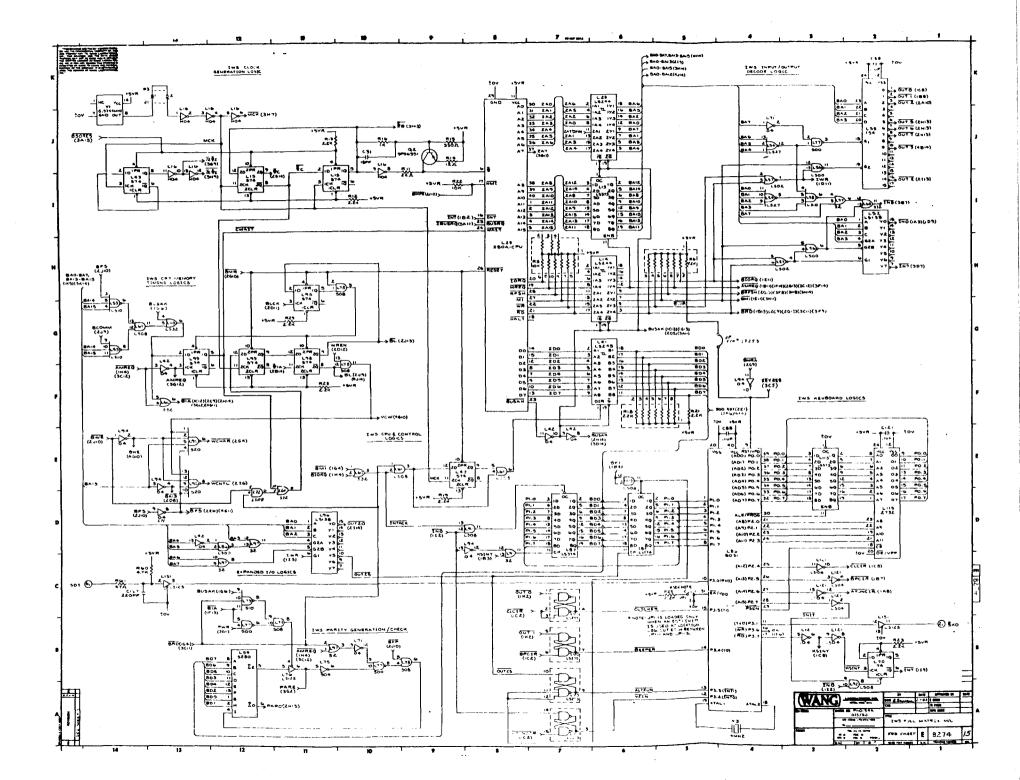

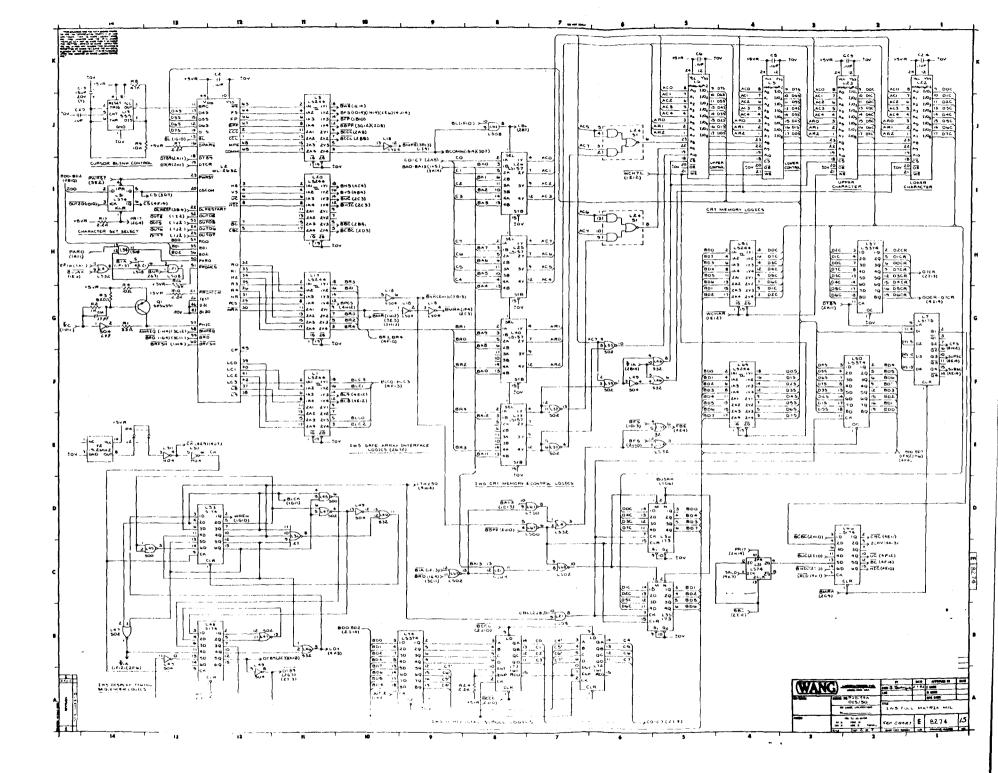

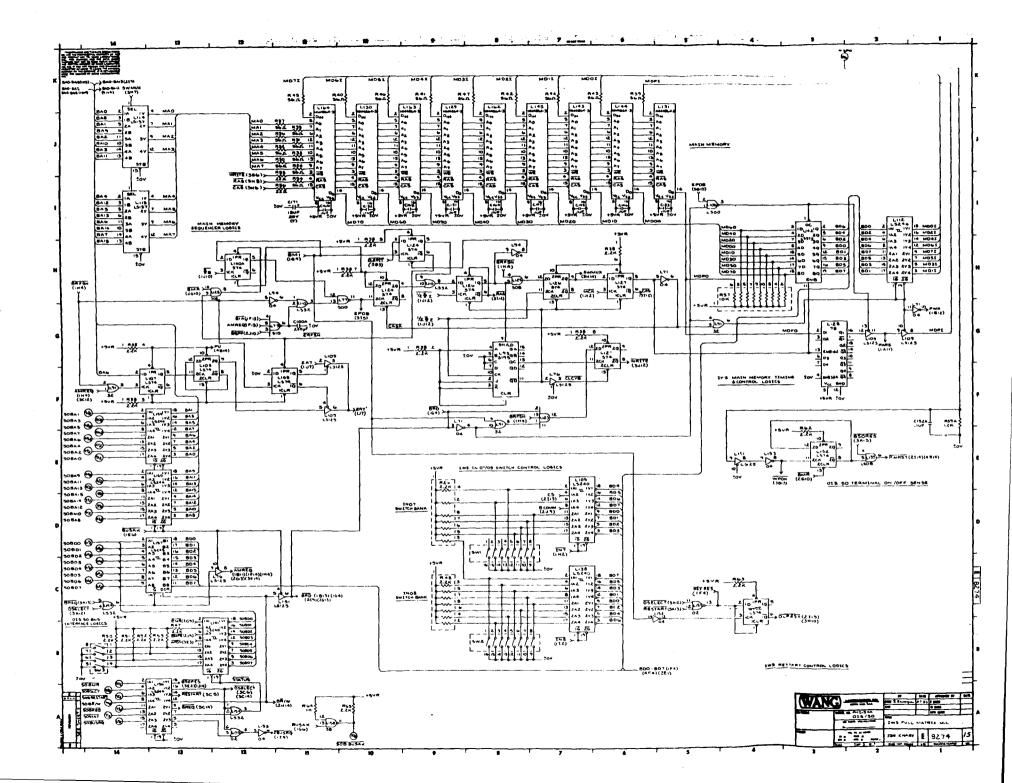

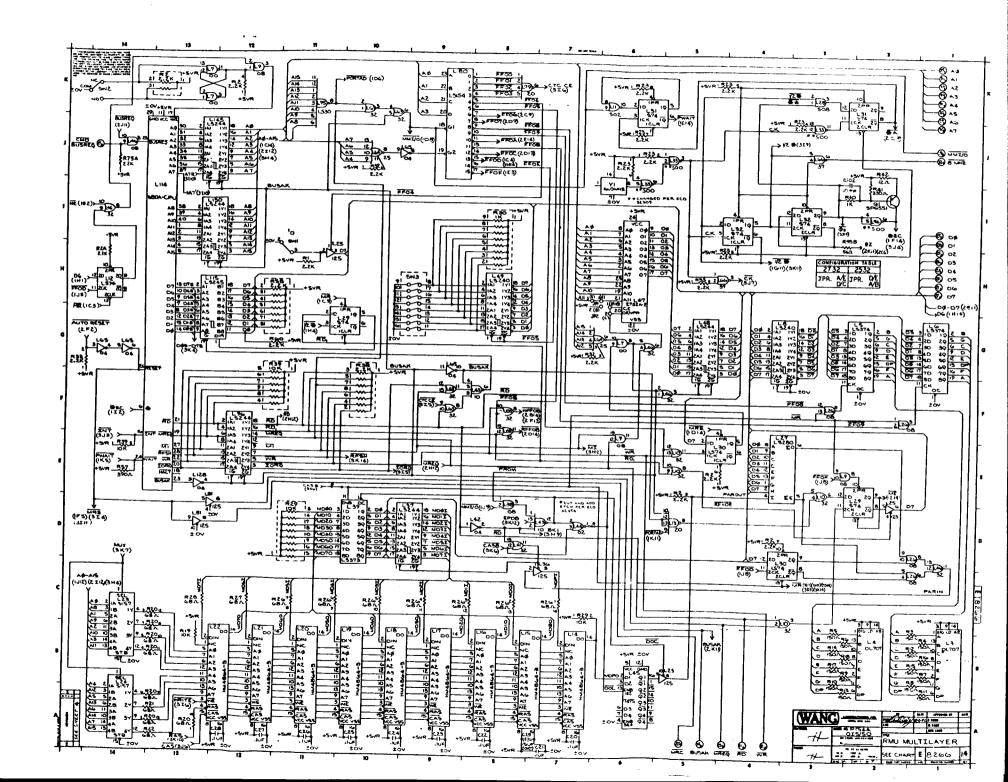

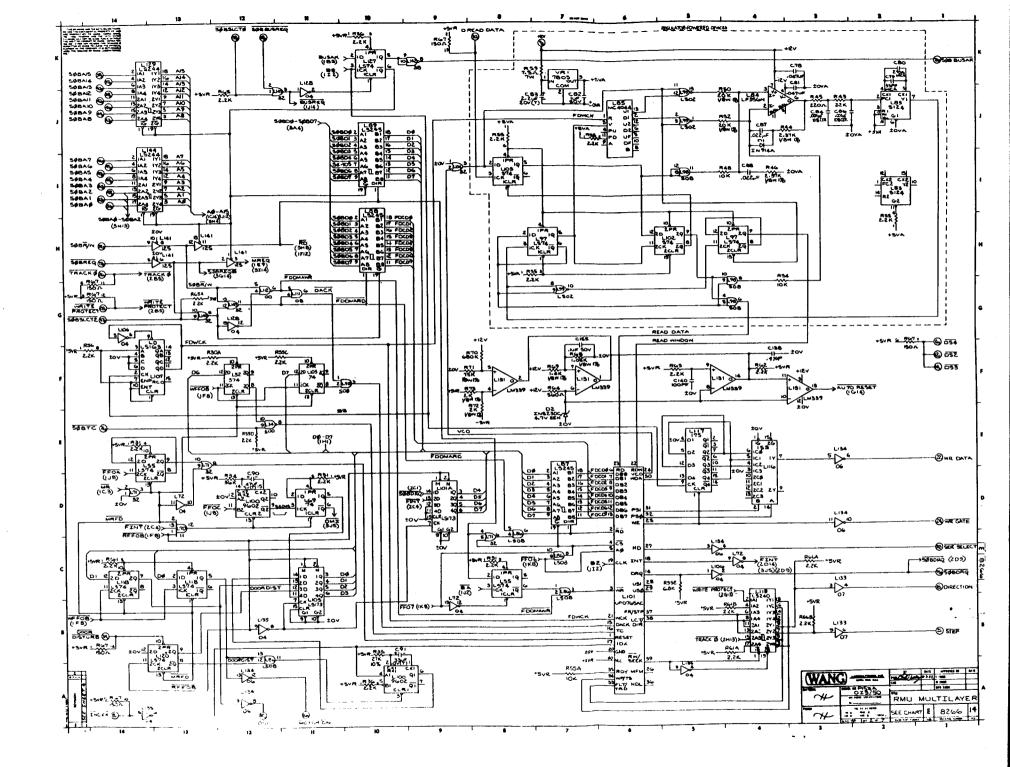

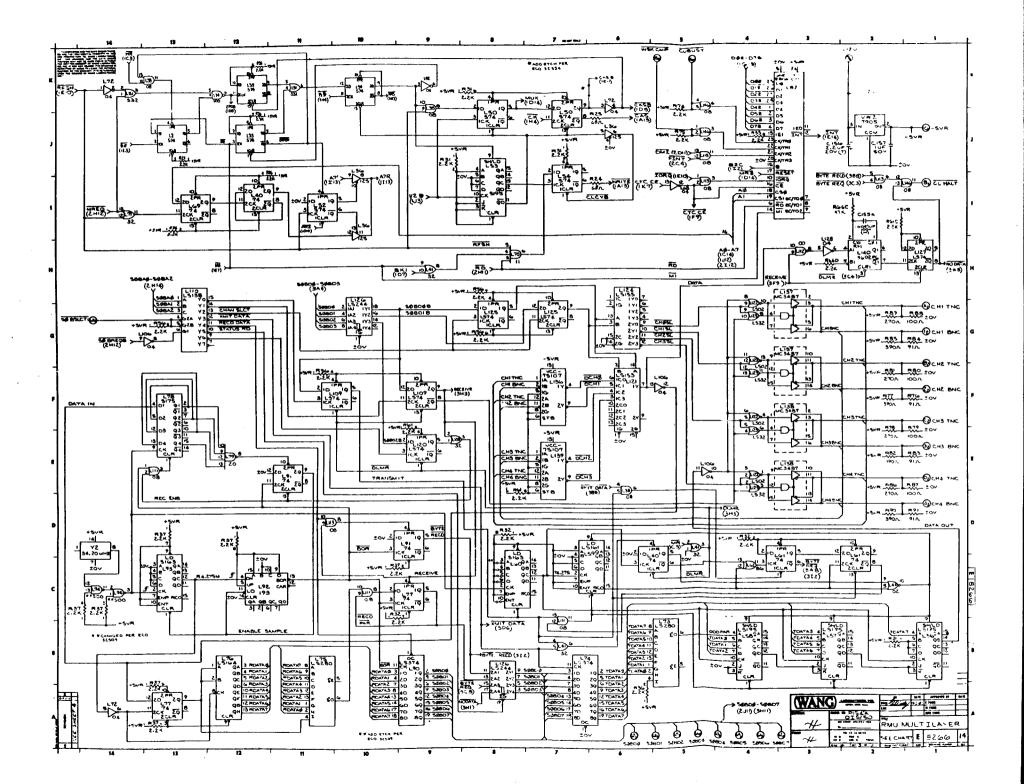

| E      | SCHEMATICS Resource Management Unit (RMU) Resource Control Unit (RCU) Internal Workstation Controller (IWS)                                     |                          |

# TABLE OF CONTENTS VOL 11

| CHAPTER                                                                                                                                                                            | Page                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

|                                                                                                                                                                                    | CTION 6<br>er Controller (IPC) |

| 6.1 INTRODUCTION                                                                                                                                                                   | 6-1                            |

| 6.2 60BUS Interface                                                                                                                                                                | 6-3                            |

| 6.3 Z80A Microprocessor<br>6.3.1 NOP Generation<br>6.3.2 I/O Operations                                                                                                            | 6-3<br>6-3<br>6-5              |

| 6.4 IPC Memory                                                                                                                                                                     | 6-9                            |

| 6.5 RS-232C Interface                                                                                                                                                              | 6-14                           |

| 6.6 Troublshooting the IPC bo                                                                                                                                                      | ard 6-20                       |

|                                                                                                                                                                                    | CTION 7<br>Controller (IWISE)  |

| 7.1 INTRODUCTION                                                                                                                                                                   | 7-1                            |

| 7.2 Overview                                                                                                                                                                       | 7-1                            |

| 7.3 IWISE Protocol                                                                                                                                                                 | 7-4                            |

| 7.4 Command Structure 7.4.1 Status Read 7.4.2 One Byte Read Sequenc 7.4.3 Block Read Sequence 7.4.4 One Byte Write Sequence 7.4.5 Block Write Sequence 7.4.6 Restart Command seque | 7-11<br>7-12<br>7-12           |

| 7.5 Detailed Theroy of Operat<br>7.5.1 Central Processing Un                                                                                                                       |                                |

| 7.6 Serial Data Link Protocol 7.6.1 SDL Receive 7.6.2 Command Decoder 7.6.3 Command Sequencer 7.6.4 Transmit Circuits 7.6.5 Termination of Transmi                                 | 7-21<br>7-23<br>7-25<br>7-27   |

| 7.7 50BUS Protocol Logic                                                                                                                                                           | 7-33                           |

| 7.8 Access Control                                                                                                                                                                 | 7-35                           |

| CHAPTER                                                                             |                                 |  |

|-------------------------------------------------------------------------------------|---------------------------------|--|

| SECTION 7 (cont.)                                                                   |                                 |  |

| 7.9 IWISE Memory<br>7.9.1 Zero Page Access                                          | 7-38<br>7-39                    |  |

| 7.10 Hardware Control Ports                                                         | 7-40                            |  |

| SECTION 8 DIAGNOSTICS                                                               |                                 |  |

| 8.1 INTRODUCTION                                                                    | 8-1                             |  |

| 8.2 System Diagnostics 8.2.1 MASTER DTOS 8.2.2 ONLINE DTOS 8.2.3 B.I.T. 8.2.4 SYSEX | 8-1<br>8-2<br>8-6<br>8-6<br>8-7 |  |

| 8.3 Individual Board Diagnostic                                                     | 8-9                             |  |

| CHAPTI | CHAPTER                                                                                                                                                          |                                           |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

|        | SECTION 9 APPENDICIES                                                                                                                                            |                                           |  |

| F      | Part 1: 8X305 COMMAND SEQUENCES FOR SDL OPERATIONS Part 2: 8X305 MICROCONTROLLER COMMAND SEQUENCES                                                               | F-1                                       |  |

| G.     | RMU - RCU COMMUNICATION PROTOCOL Introduction Master Unit Commands Floppy Unit Commands Winchester Unit Commands RCU Port Commands Status Register File Contents | G-1<br>G-2<br>G-9<br>G-11<br>G-20<br>G-22 |  |

| н      | MNEMONICS LIST Part 1: Internal Printer Controller (IPC) Part 2: Internal WISE Controller (IWISE)                                                                | H-1<br>H-3                                |  |

| I      | CHIP LIST Part 1: Internal Printer Controller (IPC) Part 2: Internal WISE Controller (IWISE)                                                                     | I-1<br>I-4                                |  |

| J      | QUIZ ANSWERS Section 6 Section 7                                                                                                                                 | J-1<br>J-2                                |  |

| K      | SCHEMATICS Internal Printer Controller (IPC)                                                                                                                     |                                           |  |

# LIST OF ILLISTRATIONS

| FIGURE NUMBER |       |                                               | Page |

|---------------|-------|-----------------------------------------------|------|

|               |       | SECTION 1 OIS 40/50/60 WORKBOOK INTRODUCTION  |      |

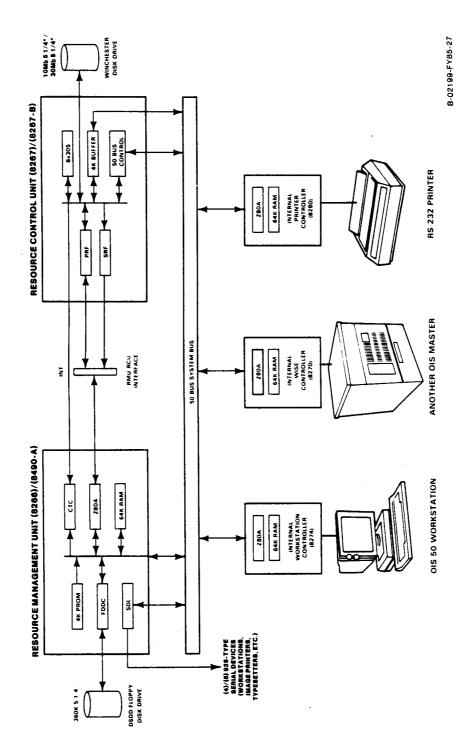

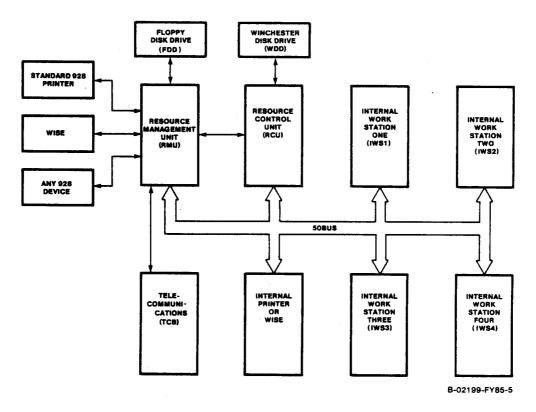

| FIGURE        | 1-1 0 | IS 40/50/60 Simplified Block Diagram          | 1-4  |

|               |       | SECTION 2 Resource Management Unit (RMU)      |      |

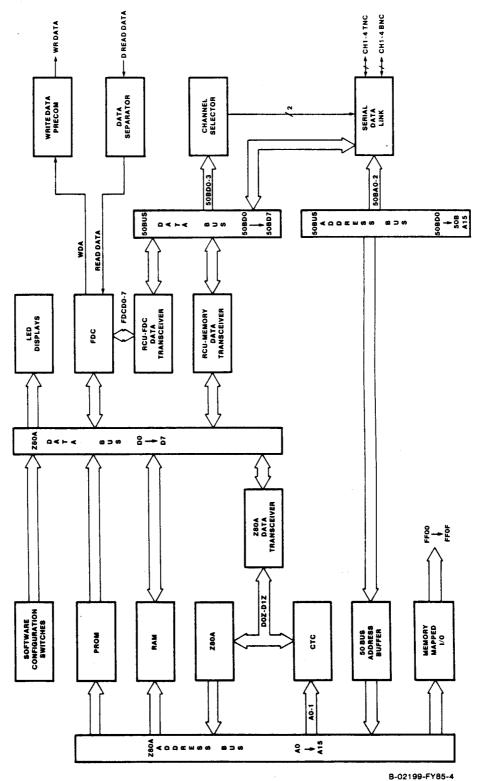

| FIGURE        | 2.1-1 | Block Diagram of the Resource Management Unit | 2-2  |

| FIGURE        | 2.1-2 | OIS 50 Block Diagram                          | 2-3  |

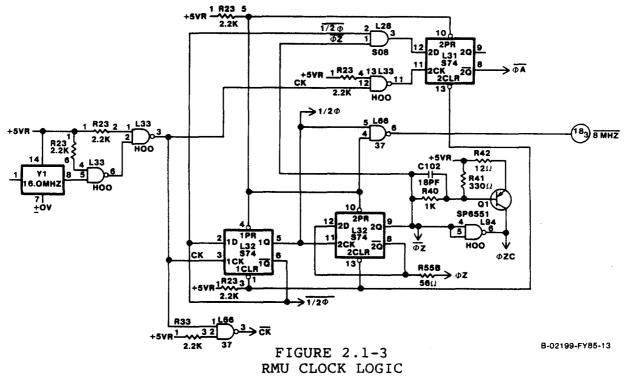

| FIGURE        | 2.1-3 | RMU CLOCK LOGIC                               | 2-13 |

| FIGURE        | 2.1-4 | RUM TIMING                                    | 2-13 |

| FIGURE        | 2.1-5 | MMI/O Logic                                   | 2-14 |

| FIGURE        | 2.2-1 | Z80A Access Logic                             | 2-21 |

| FIGURE        | 2.3-1 | Counter Timer Chip Access Logic               | 2-24 |

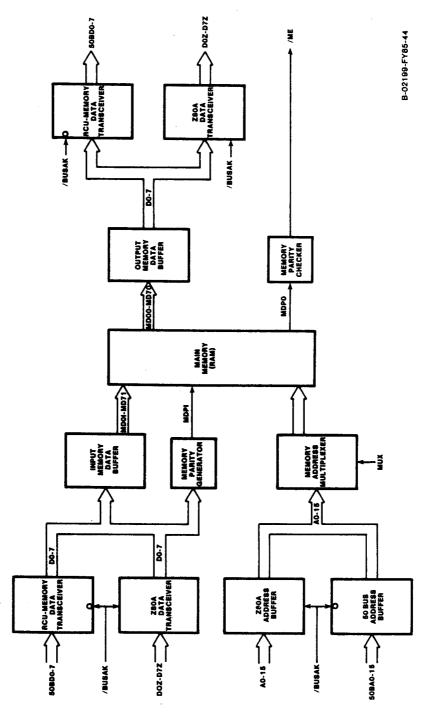

| FIGURE        | 2.4-1 | Address Bus and Data Bus Circuitry            | 2-27 |

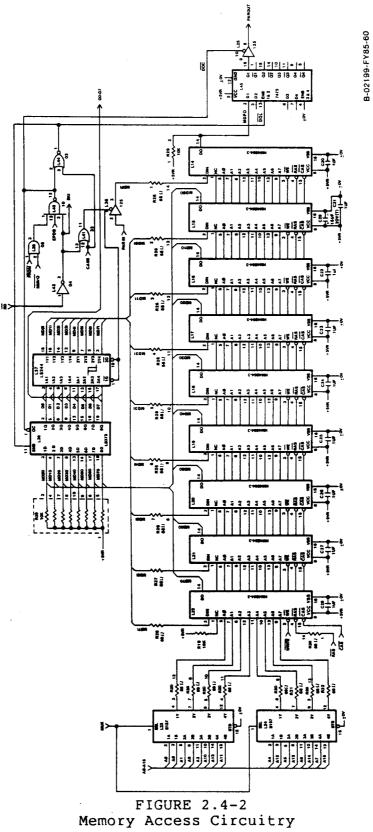

| FIGURE        | 2.4-2 | Memory Access Circuitry                       | 2-28 |

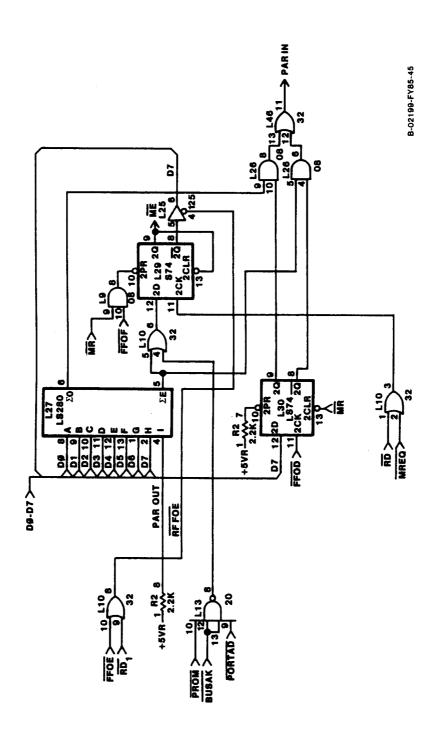

| FIGURE        | 2.4-3 | Parity Generator/Checker Logic                | 2-31 |

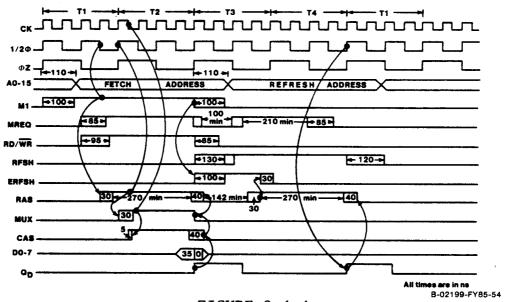

| FIGURE        | 2.4-4 | Op-Code Fetch / Memory Refresh Timing Diagram | 2-33 |

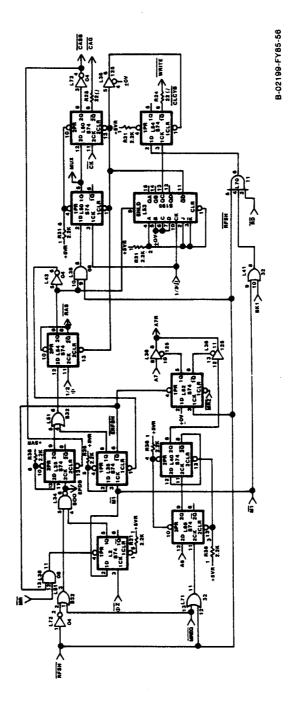

| FIGURE        | 2.4-5 | RAS/CAS and WRITE Generating Logic            | 2-36 |

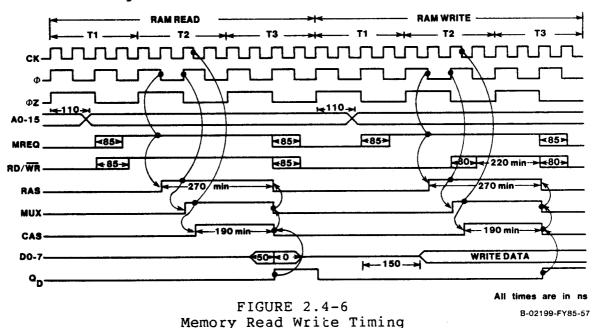

| FIGURE        | 2.4-6 | Memory Read/Write Timing Diagram              | 2-37 |

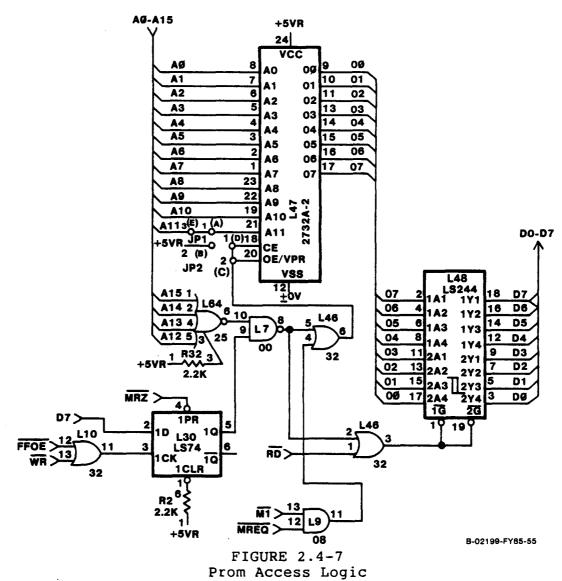

| FIGURE        | 2.4-7 | Prom Access Logic                             | 2-39 |

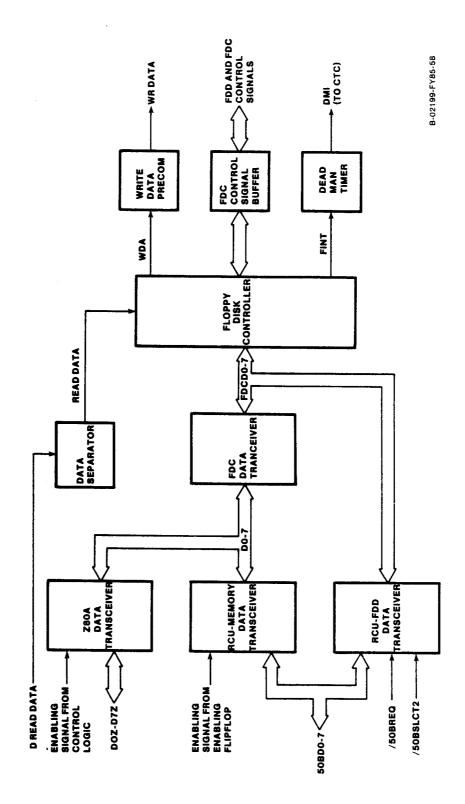

| FIGURE        | 2.5-1 | FDC Access Block Diagram                      | 2-41 |

| FIGURE        | 2.5-2 | FDC Access Logic                              | 2-42 |

| FIGURE        | 2.5-3 | FDC Data Path Logic                           | 2-44 |

| FIGURE        | 2.5-4 | FDC Status Logic                              | 2-51 |

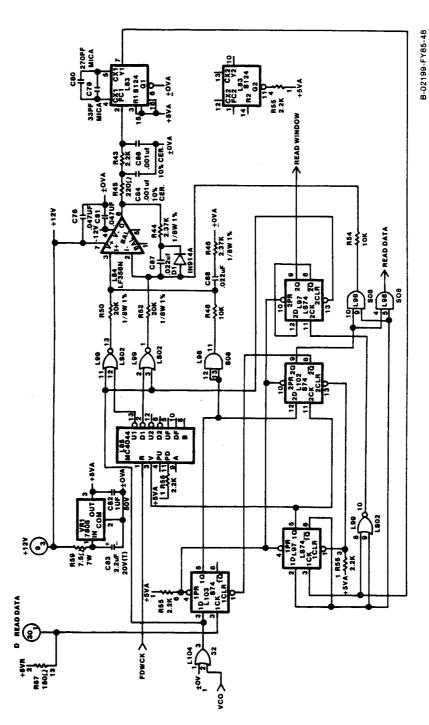

| FIGURE        | 2.5-5 | Data Recovery Block Diagram                   | 2-53 |

| FIGURE        | 2.5-6 | Data Recovery Logic                           | 2-54 |

| FIGURE        | 2.6-1 | SDL Operation Control Logic                   | 2-58 |

| FIGURE        | 2.6-2 | SDL Receive Block Diagram                     | 2-59 |

### LIST OF ILLISTRATIONS (cont.)

| FIGU | RE NUMBER  |       |                                                | Page |

|------|------------|-------|------------------------------------------------|------|

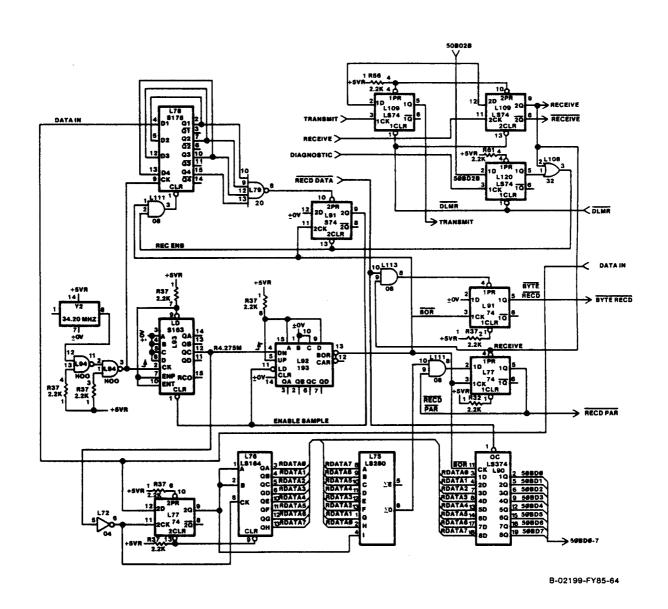

|      | FIGURE 2.6 | 5-3   | SDL Receive Logic                              | 2-60 |

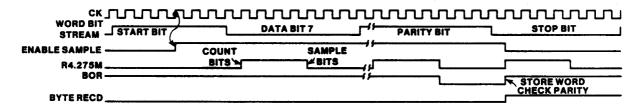

|      | FIGURE 2.6 | 6-4   | SDL Receive Timing                             | 2-61 |

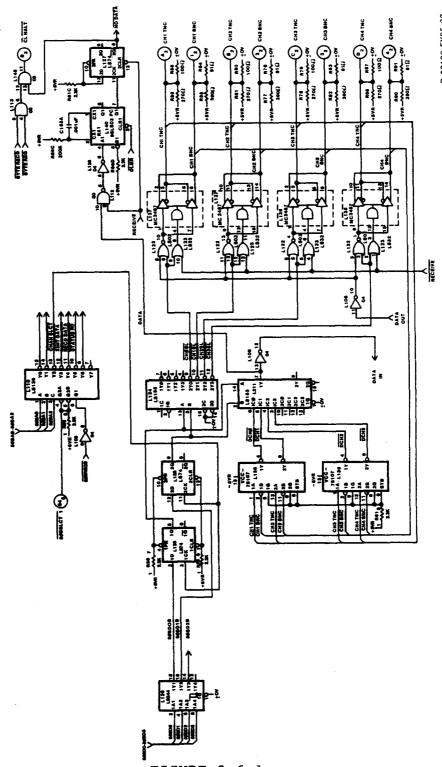

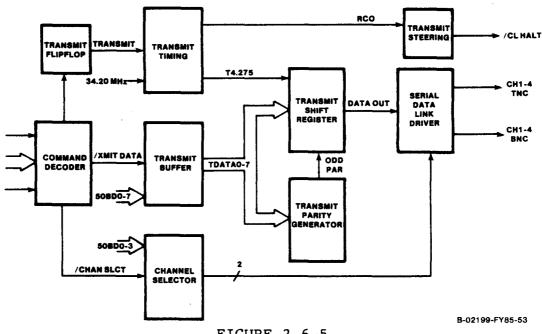

|      | FIGURE 2.6 | 5-5   | SDL Transmit Block Diagram                     | 2-62 |

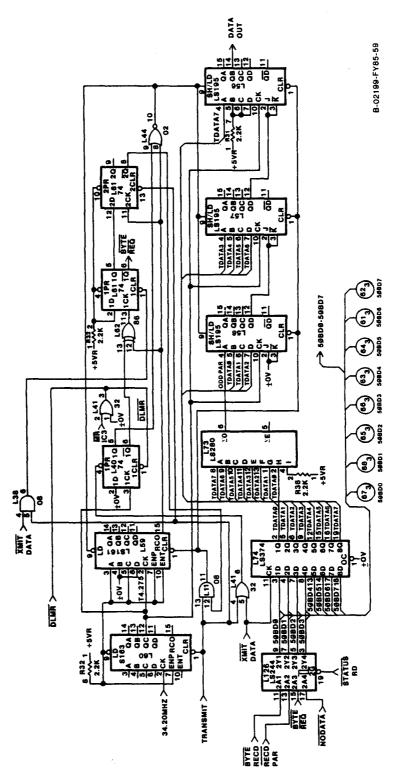

|      | FIGURE 2.6 | 5-6   | SDL Transmit Logic                             | 2-64 |

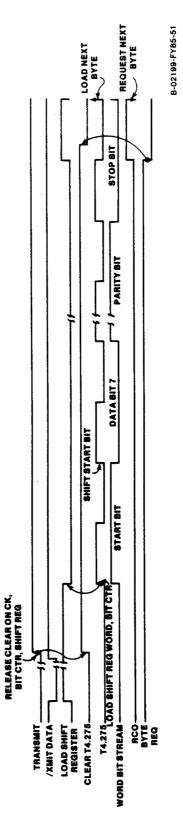

|      | FIGURE 2.6 | 5−7   | SDL Transmit Timing Diagram                    | 2-65 |

|      |            |       | SECTION 3 Resource Control Unit (RCU)          |      |

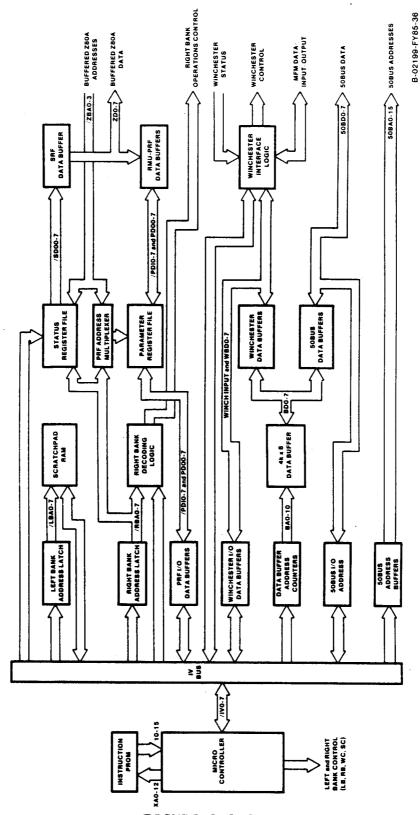

|      | FIGURE 3.1 | 1-1   | Block Diagram of the Resource Control Unit     | 3-2  |

|      | FIGURE 3.1 | 1-2   | RMU / RCU Interface Block Diagram              | 3-6  |

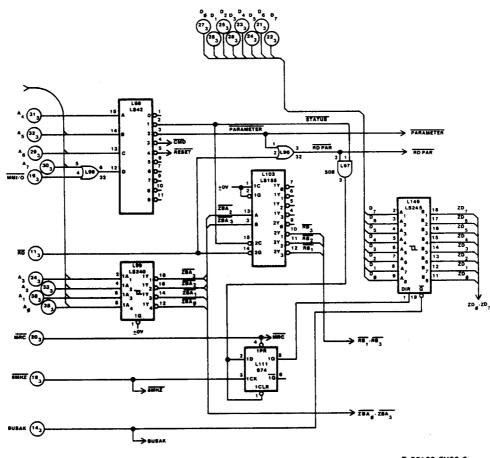

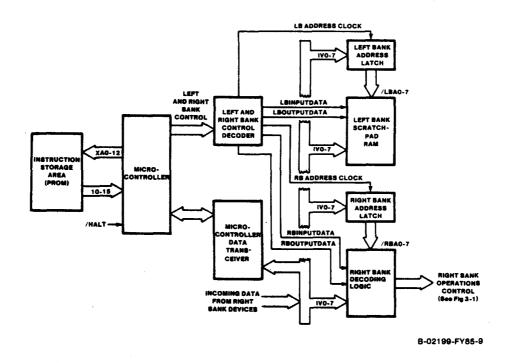

|      | FIGURE 3.2 | 2-1   | 8X305 Microcontroller Block Diagram.           | 3-10 |

|      | FIGURE 3.2 | 2-2   | 8X305 Microcontroller Access Logic             | 3-12 |

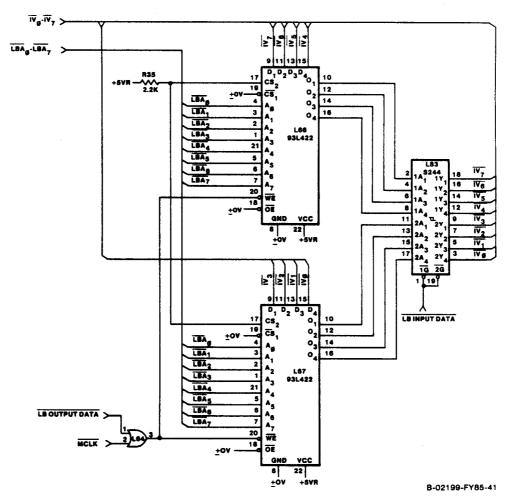

|      | FIGURE 3.2 | 2-3   | Scratchpad Memory Logic                        | 3-18 |

|      | FIGURE 3.3 | 3-1   | Right Bank Decoding Block Diagram              | 3-23 |

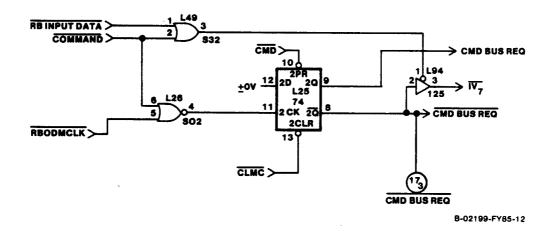

|      | FIGURE 3.3 | 3-2   | Command Bus Request Bit Control Logic.         | 3-25 |

|      | FIGURE 3.4 | 4-1   | 4K x 8 Data Buffer Block Diagram.              | 3-37 |

|      | FIGURE 3.4 | 4-2   | 4K x 8 Data Buffer Access Logic.               | 3-38 |

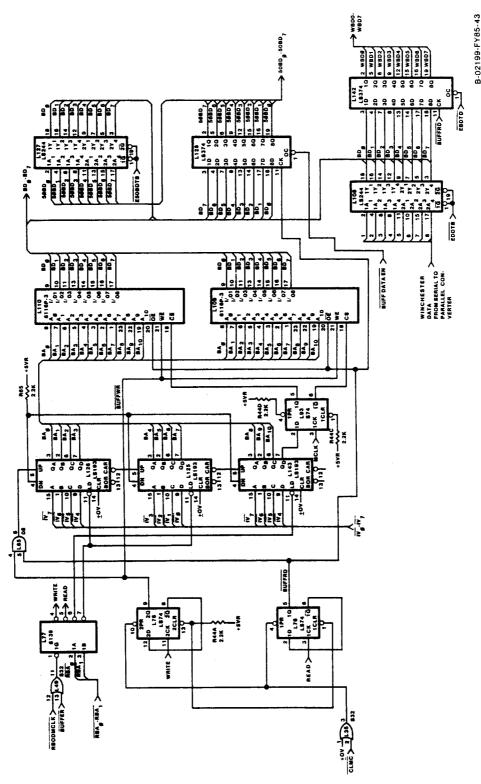

|      | FIGURE 3.4 | 4-3   | 50BUS Control Logic.                           | 3-41 |

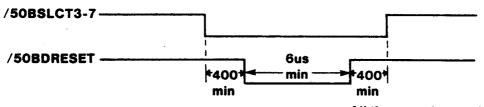

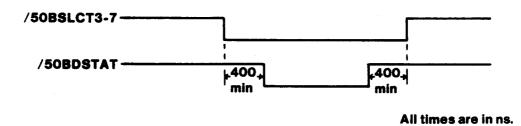

|      | FIGURE 3.4 | 4-4   | Parallel Device Restart Timing Diagram.        | 3-47 |

|      | FIGURE 3.4 | 4-5   | Parallel Device Status Timing Diagram.         | 3-47 |

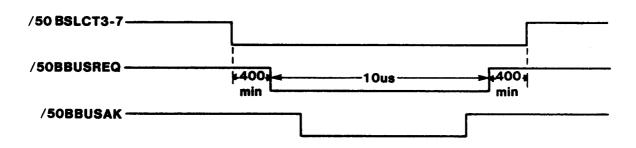

|      | FIGURE 3.4 | 4-6   | 50BUS Handshaking Timing Diagram.              | 3-47 |

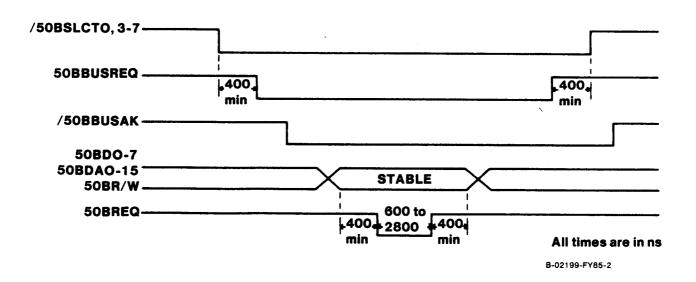

|      | FIGURE 3.4 | 1-7   | Parallel Device Memory Access Timing Diagram.  | 3-49 |

|      | FIGURE 3.4 | 1-8   | Block Read/Write 50BUS Request Timing Diagram. | 3-49 |

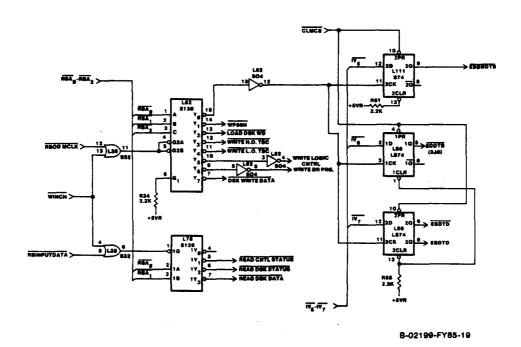

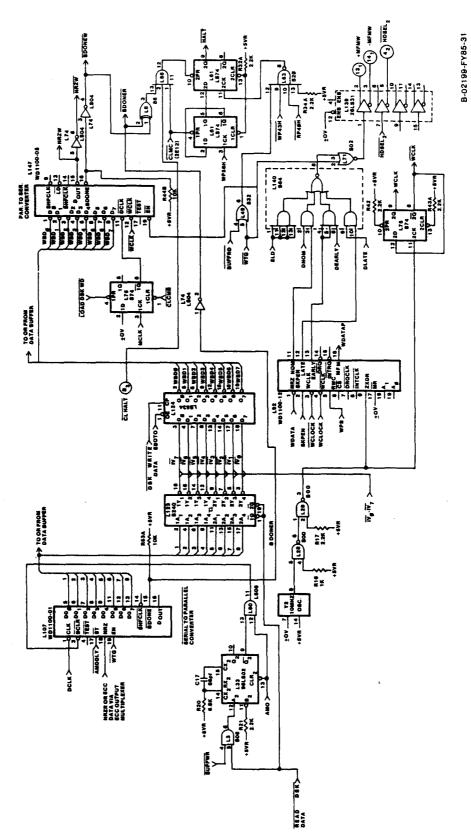

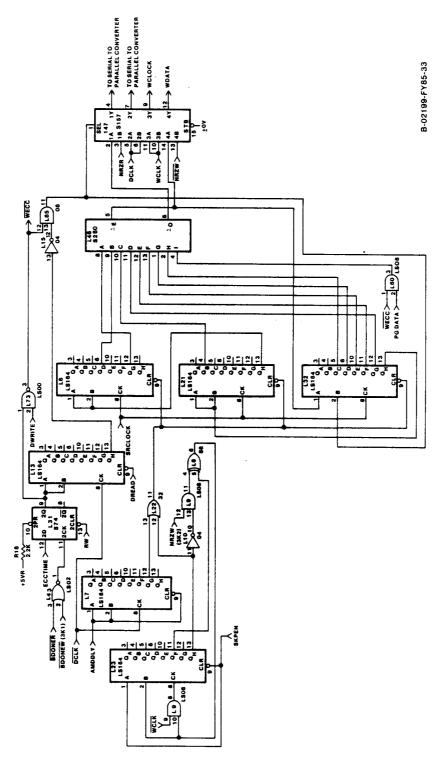

|      | FIGURE 3.5 | 5-1   | Winchester Interface Control Logic.            | 3-52 |

|      | FIGURE 3.5 | 5-2   | Winchester Interface Logic.                    | 3-53 |

|      | FIGURE 3.5 | 5-3 1 | Winchester Disk Data Format.                   | 3-59 |

# LIST OF ILLISTRATIONS (cont.)

| FIGURE NUMBER |                                                 | Page |

|---------------|-------------------------------------------------|------|

| FIGURE 3.5-4  | Winchester Write Block Diagram.                 | 3-64 |

| FIGURE 3.5-5  | Winchester Read Block Diagram.                  | 3-64 |

| FIGURE 3.5-6  | ECC Generator/Checker Logic.                    | 3-66 |

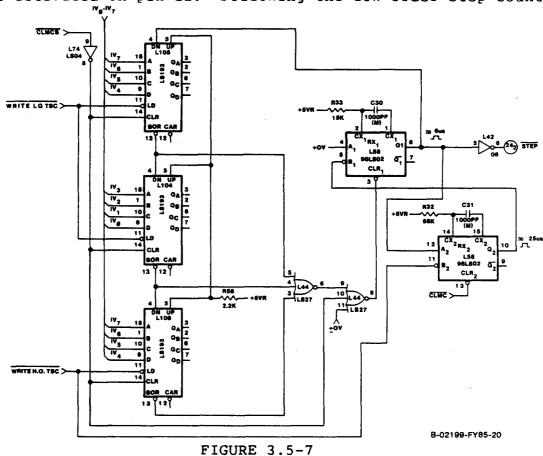

| FIGURE 3.5-7  | Winchester Step Generating Logic.               | 3-69 |

| FIGURE 3.5-8  | Phase Locked Loop Logic.                        | 3-72 |

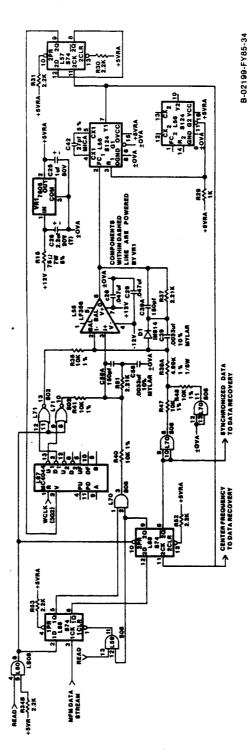

| FIGURE 3.5-9  | Data Recovery Logic.                            | 3-74 |

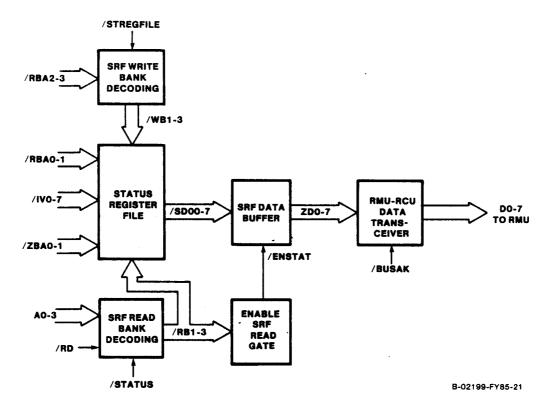

| FIGURE 3.6-1  | Status Register File Block Diagram.             | 3-80 |

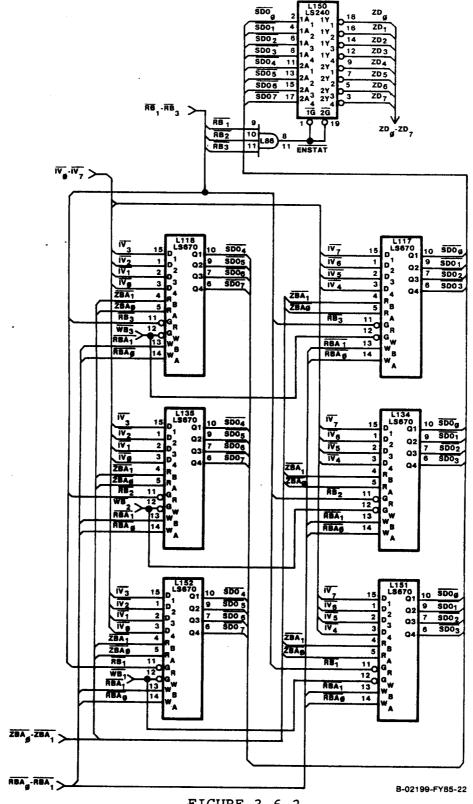

| FIGURE 3.6-2  | Status Register File Logic.                     | 3-81 |

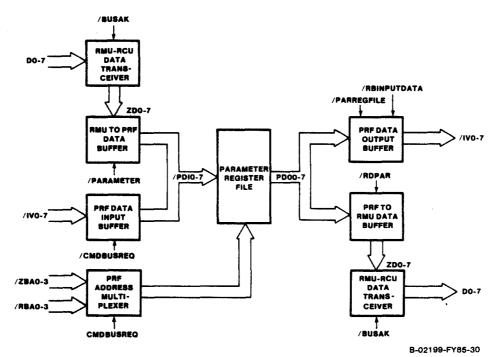

| FIGURE 3.6-3  | Parameter Register File Block Diagram.          | 3-83 |

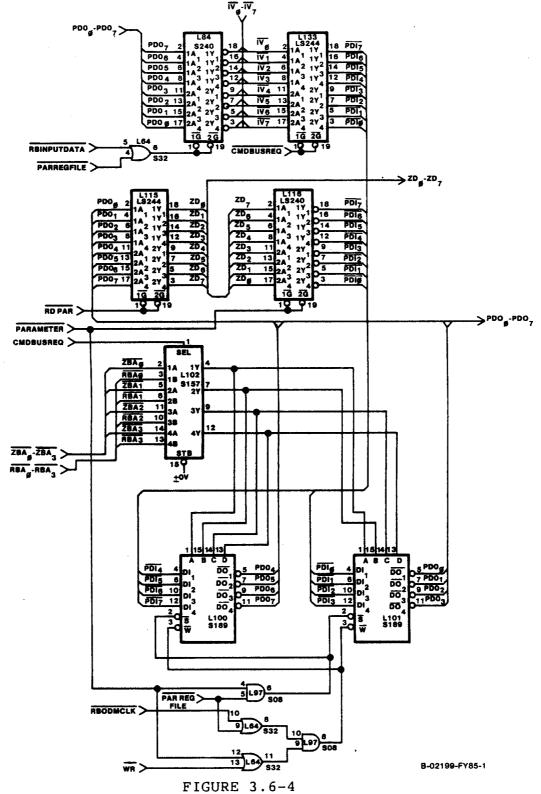

| FIGURE 3.6-4  | Parameter Register File Logic.                  | 3-84 |

|               | SECTION 4 Internal Workstation Controller (IWS) |      |

| FIGURE 4-1    | Internal Workstation Controller Block Diagram   | 4-2  |

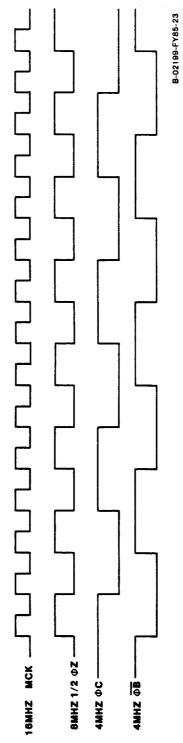

| FIGURE 4.1-1  | Clock Timing Diagram                            | 4-5  |

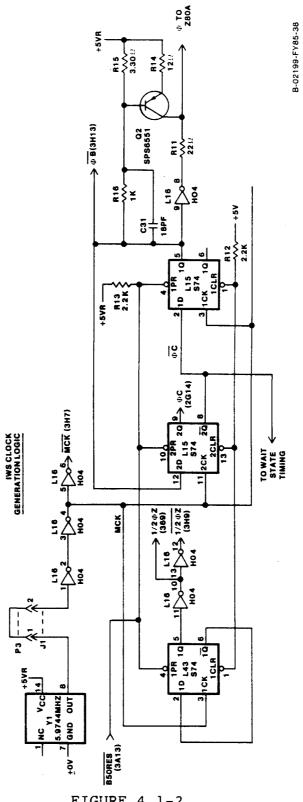

| FIGURE 4.1-2  | Clock Logic                                     | 4-6  |

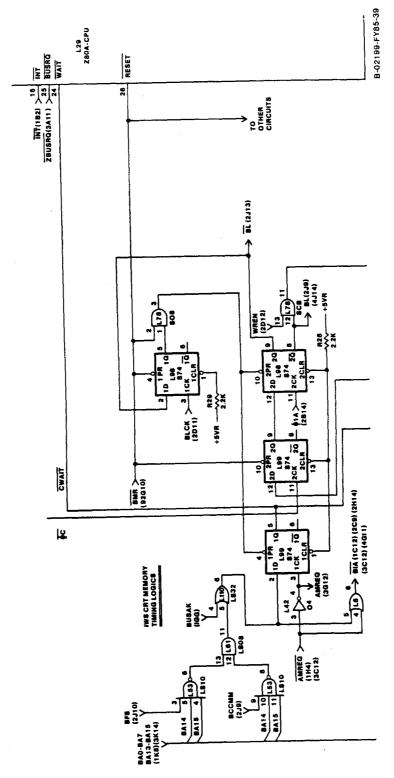

| FIGURE 4.1-3  | Wait State Timing Logic                         | 4-8  |

| FIGURE 4.2-1  | RAS/CAS Generating Logic                        | 4-13 |

| FIGURE 4.2-2  | Parity Generating/Checking Logic                | 4-16 |

| FIGURE 4.3-1  | FONT MATRIX                                     | 4-22 |

| FIGURE 4.4-1  | Display Timing                                  | 4-28 |

| FIGURE 4.4-2  | FONT MATRIX                                     | 4-35 |

| FIGURE 4.4-3  | Line Count to Address Relationship              | 4-35 |

| FIGURE 4.5-1  | 8031 Block Diagram                              | 4-38 |

# LIST OF ILLISTRATIONS (cont.)

| FIGURE NUN                                 | IBER      |                                             | Page |  |

|--------------------------------------------|-----------|---------------------------------------------|------|--|

|                                            |           | SECTION 6 Internal Printer Controller (IPC) |      |  |

| FIGUE                                      | RE 6.1-1  | Internal Printer Controller Block Diagram   | 6-2  |  |

| FIGUE                                      | RE 6.3-1  | I/O Decoders                                | 6-7  |  |

| FIGUE                                      | RE 6.4-1  | REFRESH LOGIC DIAGRAM                       | 6-10 |  |

| FIGUE                                      | RE 6.4-2  | Ml Timing Diagram                           | 6-10 |  |

| FIGU                                       | RE 6.4-3  | RAS/CAS LOGIC DIAGRAM                       | 6-12 |  |

| FIGU                                       | RE 6.5-1  | SC2661C Block Diagram                       | 6-15 |  |

| SECTION 7 Internal WISE Controller (IWISE) |           |                                             |      |  |

| FIGU                                       | RE 7.2-1  | IWISE Block Diagram                         | 7-2  |  |

| FIGUI                                      | RE 7.3-1  | Typicial Transmitted Word                   | 7-6  |  |

| FIGUI                                      | RE 7.10-1 | Jl Pin Assignments                          | 7-44 |  |

### LIST OF TABLES

| TABLE NUMBER |                                          | Page |

|--------------|------------------------------------------|------|

|              | SECTION 2 Resource Management Unit (RMU) |      |

| Table 2.1-1  | LED DISPLAY CODES                        | 2-6  |

| Table 2.1-2  | POWER-UP DIAGNOSTIC DISPLAY ERROR        | 2-7  |

| Table 2.1-3  | SYSTEM DISPLAY ERROR CODES               | 2-11 |

| Table 2.1-4  | SOFTWARE CONFIGURATION SWITCH            | 2-12 |

| Table 2.1-5  | RMU MEMORY MAPPED I/O COMMANDS           | 2-15 |

| Table 2.5-1  | WRITE DATA/PRECOMPENSATION SELECT        | 2-47 |

| Table 2.5-2  | FLOPPY DISK DRIVE STATUS BYTE            | 2-50 |

| Table 2.6-1  | SERIAL DATA LINK COMMANDS                | 2-57 |

| Table 2.6-2  | SERIAL DATA LINK STATUS BYTE             | 2-66 |

|              | SECTION 3 Resource Control Unit (RCU)    |      |

| Table 3.1-1  | Z80A-GENERATED I/O COMMANDS              | 3-8  |

| Table 3.2-1  | MICROCONTROLLER CONTROL SIGNAL           | 3-11 |

| Table 3.2-2  | SCRATCHPAD MEMORY MAP                    | 3-14 |

| Table 3.2-3  | RCU RIGHT BANK I/O DECODER               | 3-20 |

| Table 3.3-1  | STATUS REGISTER FILE I/O COMMANDS        | 3-24 |

| Table 3.3-2  | 4K x 8 DATA BUFFER I/O COMMANDS          | 3-26 |

| Table 3.3-3  | 50BUS I/O COMMANDS                       | 3-28 |

| Table 3.3-4  | WINCHESTER I/O COMMANDS                  | 3-31 |

# LIST OF TABLES (cont.)

| TABLE NUMBER |                                                 | Page |

|--------------|-------------------------------------------------|------|

| Table 3.5-1  | WINCHESTER STATUS BYTE                          | 3-54 |

| Table 3.5-2  | WINCHESTER PROGRAM BYTE                         | 3-55 |

| Table 3.5-3  | WINCHESTER CONTROL STATUS BYTE                  | 3-56 |

| Table 3.5-4  | WINCHESTER INTERFACE CONTROL BYTE               | 3-57 |

| Table 3.5-5  | WINCHESTER DATA MOTION CONTROL                  | 3-59 |

|              | SECTION 4 Internal Workstation Controller (IWS) |      |

| Table 4.1.1  | MMI/O COMMANDS                                  | 4-10 |

| Table 4.3.1  | Main Memory Overlay Assignents                  | 4-18 |

| Table 4.3.2  | Display Attribute Decoding                      | 4-20 |

| Table 4.3.3  | Attribute Control Bits                          | 4-21 |

| Table 4.4-1  | WL2632 Display Signals                          | 4-25 |

| Table 4.6-1  | Status Information                              | 4-42 |

# LIST OF TABLES (cont.)

| TABLE NUMBER |                                             | Page |

|--------------|---------------------------------------------|------|

|              | SECTION 6 Internal Printer Controller (IPC) |      |

| Table 6.3-   | l Device and Diagnostic I/O Operations      | 6-5  |

| Table 6.3-   | 2 SC2661C I/O Operations                    | 6-6  |

| Table 6.5-   | l 2661 Register Addressing                  | 6-18 |

|              |                                             |      |

|              | SECTION 7 Internal WISE Controller (IWISE)  |      |

| Table 7.4-   | 1 STATUS BYTE ASSIGNMENTS                   | 7-9  |

| Table 7.5-   | l I/O Port Allocations                      | 7-16 |

| Table 7.5-2  | 2 CTC I/O Allocations                       | 7-18 |

| Table 7.5-3  | 3 IWRESTART RESET TABLE                     | 7-20 |

| Table 7.6-1  | 1 BYTE AQUSISTION AND CHECK TIMING          | 7-22 |

| Table 7.6-2  | 2 Command Decoder Sub Command               | 7-24 |

| Table 7.6-3  | 3 L81 Action Table                          | 7-30 |

| Table 7.7-1  | l 50BUS Signals                             | 7-33 |

|              |                                             |      |

|              | SECTION 8<br>DIAGNOSTICS                    |      |

| Table 8.2-1  | l System Diagnostic                         | 8-2  |

# SECTION I

# SECTION 1

# OIS 40/50/60 WORKBOOK INTRODUCTION

This board repair workbook is comprized of two volumes. In the first volume the overall system will be covered in general. Then the reader will be presented with theory of operation for the three main circuit boards within the system, the Resource Management Unit (RMU), the Resource Control Unit (RCU), and the Internal Workstation Controller (IWS). Each of these sections will include a detailed description of the circuit board with limited bit chasing. The reader will be referred to Figures and Tables, along with references to the schematics to help him or her understand the operation of the unit. At the end of each section there is a quiz covering the information that was presented. After answering the questions in the quiz the reader can check his or her answers by referring to the answers in Appendix G.

In the second volume the reader will be presented with a detailed description of the theory of operation for the Internal Printer Controller (IPC), and the Internal WISE Controller (IWISE) circuit boards. The organization of the second volume is similar to that of the first as far as type of content and objectives.

Both volumes contain Appendices that provide relitive infromation about the circuit boards within that volume. Also located in the rear of the each volume is a master index that covers both volumes, this should provide the reader with a quick reference to just about any circuit operation.

If after you read this book you have any further questions or are interrested in learning more about the operation of the system, a list of reference books is provided in Appendix A of volume 1.

If while you are reading this workbook you come accross any errors that you feel need correcting, fill out the form provided at the back of the book and subbmit it to you supervisior. This feed back will help us improve the quality of the books that we produce and improve the quality of training that you receive.

### 1.1 OIS 40/50/60 SYSTEM INTRODUCTION

The OIS 40/50/60 system is a smaller version of the OIS 140 system that is contained in one package. The OIS 50 is capable of supporting up to four non-intelligent workstations and one or two non-intelligent printers. The logic providing the intelligence of these workstations and printers resides within the OIS 50 Master Processor. In addition the system will support up to four OIS 928 type serial devices, including intelligent workstations, image printers, phototypesetters, and telecommunication devices. The OIS 50 may be connected in a network configuration to more powerful Office Information Systems through the use of a Wang Inter-System Exchange Unit (WISE).

The OSI 40 is essentially a subset of the more versitile OIS 50. It was designed to be used as a stand alone system, capable of supporting one non-intelligent workstation along with one non-intelligent printer. As an option the OIS 40 may be configured to support one 928 type serial intelligent workstation or device. Like the OIS 50, it may be connected in an office system network via WISE, and has optional telecommunications capability.

The OIS 60 system represents the latest design in the OIS family of WANG Office Information Systems. In addition to the features of the OIS 40/50 configurations the OIS 60 provides four additional standard 928-type serial data link ports enabling the system to support a total of 12 peripheral devices, eight of these could be workstations. To support the additional ports the Resource Management Unit (RMU) and the Resource Control Unit (RCU) PCA's have been modified. The applicable theory and maintenance information (differences) for each will be covered as the RMU and RCU boards are discussed.

All three system contain an onboard 5 1/4 inch floppy archive drive, and either a 10 Meg or 30 Meg Winchester disk drive. The OIS 40 and 50 contain 10 Meg Winchester drives while the OIS 60 has a 30 Meg Winchester drive. In addition the OIS 60 has a hinged rear panel for easier access to the internal cabling for troubleshooting purposes.

The front panel of each of the units contains a rocker switch used for selecting which drive the unit will IPL from, (i.e. the Winchester or the Floppy). Directly above the IPL switch is located a LED status display. When the system is first powered on the unit will run an onboard BIT diagnostic. If an error is detected during the BIT test the status display will reflect the type of problem found. Refer to Appendix zzz for a complete list of error codes and their meaning.

### 1.2 SYSTEM OPERATION

In the OIS 40/50/60 system there are six printed circuit board that reside in the Master Processor, they are:

| BOARD #    | DESCRIPTION                           | SYSTEM           |

|------------|---------------------------------------|------------------|

| 210-8266-A | Resource Management Unit (RMU)        | ((OIS 40/50))    |

| 210-8490-A | Resource Management Unit (RMU)        | ((OIS 60))       |

| 210-8267-A | Resource Control Unit (RCU)           | ((OIS 40/50))    |

| 210-8267-B | Resource Control Unit (RCU)           | ((OIS 60))       |

| 210-8274-A | Internal Workstation Controller (IWS) | ((OIS 40/50/60)) |

| 210-8280-A | Internal Printer Controller (IPC)     | ((OIS 40/50/60)) |

| 210-8270-A | Internal WISE Controller (IWISE)      | ((OIS 40/50/60)) |

| 210-8269   | OIS 50 Motherboard                    | ((OIS 40/50/60)) |

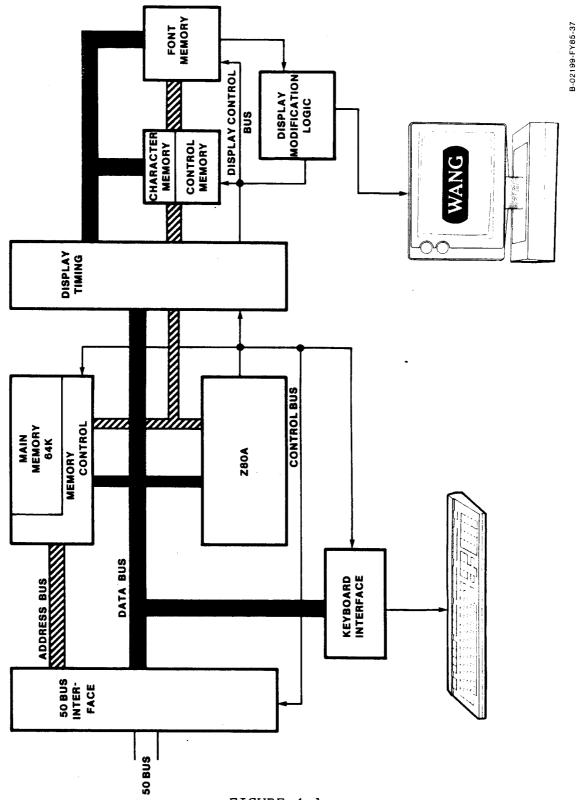

The OIS motherboard is designed to hold a total of seven printed circuits boards, two of these boards must be the RMU and RCU These two board contain all the Central Processing Logic for the Master unit. The five remaining slots accommodate the different peripheral controller boards in various combinations. Four of these slot may contain Internal Workstation Controllers (IWS), while the last slot may contain either an Internal WISE Controller (IWISE) or Internal Printer Controller (IPC). on the system configuration, an additional IPC board may be substituted for one of the IWS controllers. FIGURE 1-1 shows a simplified block diagram of the OIS 40/50/60 system depicting the RMU, RCU, IWS, IPC and IWISE controllers, floppy and Winchester storage, and various peripheral devices. The flow of information between the various devices and PC boards occurs on the 50BUS. This bus is comprised of 40 signals representing address, data, select, and control information.

All of the Central Processing Logic for the OIS 40/50/60 is contained on the Resource Management Unit (RMU) and the Resource Control Unit (RCU) circuits boards. The Resource Management Unit (RMU) as its name implies, is responsible for the overall management of system operations. It runs the Operating System code and contains the system's main memory. The Resource Control Unit (RCU) shares the processing burden by controlling some of the more cumbersome tasks. In this way the RCU relieves the RMU of certain time-consuming operations, thus freeing the RMU to concentrate on overall system management. The net result is a system that runs faster and more efficiently than single-processor systems.

### 1.2.1 Resource Management Unit (RMU)

The RMU contains a Z80 microprocessor that executes the system operating code, also on the RMU is located 64K of RAM overlayed by 4K of PROM memory. The RAM functions as main memory for the system, while the PROM contains the BIT power-up diagnostics and bootstrap loader code. The upper 256 bytes of memory is reserved Memory Mapped I/O. A Z80 Counter/Timer Chip (CTC) handles the various interrupts that the Z80 must respond to. The RMU is also responsible for controlling all operation involving the system's mini-floppy disk drive. An LSI Floppy Disk Controller chip (FDDC) resides on the RMU for this purpose. Finally, the RMU also contains all transmit and receive logic for all the external Serial Data Link (SDL) ports that connect the OIS 40/50/60 to 928-type serial peripherals. Although this SDL logic resides on the RMU board the RCU is actually responsible for its control.

### 1.2.2 Resource Control Unit (RCU)

The RCU board is designed around a Signetics 8X305 Microcontroller chip. It relieves the RMU's Z80 of a good deal of overhead by assuming the processing duties in four main areas:

- 1. Control and execution of all operations involving the 5 1/4" Winchester Disk Drive.

- Execution of all block data transfers.

- 3. Control and arbitration of the 50BUS System Bus.

- 4. Control and execution of the Serial Data Link (SDL).

The 8X305 Microcontroller is the heart of the RCU board, and operates from instructions stored in firmware. A 4K Data Buffer is located on the RCU, and is involved in any operation that requires the transfer of block data. Logic on the RCU board generates commands and control signals that governs the operation of the 50BUS. Finally, all Serial Data Link (SDL) operations are under direct control of the 8X305 Microcontroller and additional support logic, even though the actual SDL transmit and receive circuitry is on the RMU.

In a multi-processor system such as this, communication between the two microprocessors is an important aspect of the system The RMU's Z80A and the RCU's 8X305 Microcontroller communicate with one another through the use of shared memory and interrupt signals. Two special memory areas are present on the RCU Both the Z80A and the 8X305 Microcontroller can access these One area is called the Parameter Register File (PRF) while the other is labeled the Status Register File (SRF). Z80A of the RMU encounters and instruction that is the responsibility of the RCU, it will instruct the RCU to perform the To do this the RMU will write commands and parameter information into the Parameter Register File. The RCU then reads the (PRF) and interprets and executes the commands. When the RCU completes the task it writes status information into the Status Register File. The RMU reads the status information from the (SRF) to determine the outcome of the operation. For lengthy RCU operations such as block transfers the RMU will attend to other management duties while the RCU carries out the operation. When the RCU completes the task it will generate an interrupt to the Z80A indicating that the operation is complete.

As mentioned earlier, the 50BUS is the system's internal bus network comprised of 40 signals representing address, data, select, and control information. All information exchanged between the OIS 40/50/60 Central Processing Logic (RMU, RCU) and the various peripheral controllers (IWS, IPC, IWIS) travel on the 50BUS. The RCU initiates and governs all 50BUS transactions. Via the 50BUS the RCU is able to exchange information with a total of eight logical devices, called 50BUS Devices. Three of these logical devices reside on the RMU board:

- 1. Main Memory

- 2. The Floppy disk drive controller

- 3. The Serial Data Link transmit and receive logic

The remaining five logical devices correspond to the five Motherboard slots which house the various peripheral controller boards (IWS, IPC, IWISE).

A typical 50BUS transaction between the RCU and a 50BUS Device usually involves the transfer of block data. Consider the following While running the operating system, the RMU determine that it needs to read a portion of the workstations memory. the operation involves use of the 50BUS, and the RCU is responsible for operation of the 50BUS then the RMU instruct the RCU to perform the task and supplies the RCU with the particulars (which IWS, what portion of memory to read from, etc.) by writing to the (PRF). RMU then goes about doing other housekeeping duties while the RCU performs the task. Using the 50BUS, the RCU selects the desired slave and places the slaves Z80A into a Bus-Request state so a DMA operation can take place. Then the RCU reads the desired slaves memory and transfers it byte for byte into the 4K Data Buffer on the RCU board via the 50BUS. When the operation is complete the RCU notifies the RMU by an interrupt. The RMU will then read the (SRF) to determine the results of the operation.

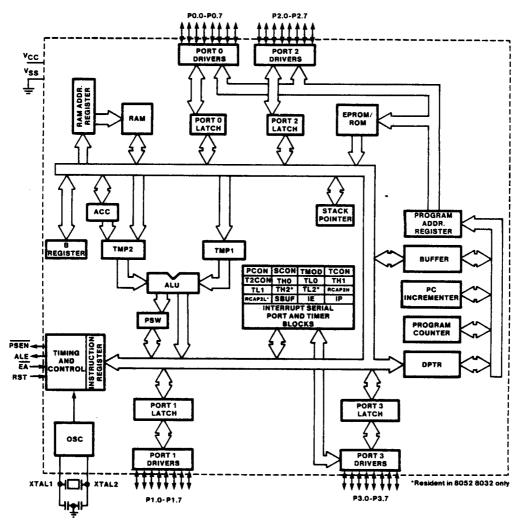

Three type of peripheral controller boards may be included in an OIS 40/50/60 system. They are; the Internal Workstation Controller (IWS), Internal Printer Controller (IPC), and the Internal WISE Controller (IWISE). Each of these controller boards contain a Z80A microprocessor along with 64K bytes of RAM used as slave memory. The following paragraphs contain a brief description of each board's responsibilities.

### 1.2.3 The Internal Workstation Controller (IWS)

The OIS 40/50/60 Master is capable of supporting up to four OIS 40/50/60 non-intelligent display terminals. The workstation is termed non-intelligent because the hardware and software that control the logical functions reside within the OIS 40/50/60 Master, on an (IWS) Controller board. The IWS Controller is responsible for providing:

- 1. The interface signals to the monitor electronics.

- The interface logic to the serial keyboard.

- The CRT, font, and main memory storage.

- 4. Interface logic required to communicate with the 50BUS.

### 1.2.4 The Internal Printer Controller (IPC)

The Internal Printer Controller (IPC) is designed to control a single RS-232C printer. The IPC receives commands and data from the RCU board via the 50BUS and communicates with the printer through an RS-232C serial interface. It is designed around a Z80A microprocessor running at 4 Mhz, and contains:

- 1. 50BUS interface logic.

- 2. RS-232C interface logic.

- 3. Printer control interface logic.

- 4. 64K of Dynamic RAM

### 1.2.5 The Internal WISE Controller (IWISE)

The internal WISE board provides a high speed communication path between the OIS 40/50/60 and any other WANG system that employs the standard 928-type Serial Data Link. The IWISE enables the OIS 40/50/60 to be used as clustered system, providing a communication link to a higher level Master Processor, such as the OIS 145 shown in FIGURE 1-1. Like the other controller devices attached to the 50BUS, the IWISE board depends on a Z80A running at 4 Mhz, and also contains:

- 1. Serial Data Link protocol logic.

- 2. 50BUS protocol logic.

- 3. 64K of Dynamic RAM and memory access arbitration logic.

- 4. DMA logic.

A complete theory of operation, and detailed circuit description for each of the circuit boards in the OIS 40/50/60 system is discussed in the following sections. Appendix A gives a complete list of all related documents for the OIS 40/50/60 system.

### SECTION 1 QUIZ

| 1) | What | are | the | major | differences | between | an | OIS | 50 | and | an | OIS |

|----|------|-----|-----|-------|-------------|---------|----|-----|----|-----|----|-----|

|    | 60?  |     |     |       |             |         |    |     |    |     |    |     |

- Name the five PCA assemblies that can reside in the main unit of either of the systems?

- What two controller circuits reside on the RMU but are primarily controlled by the RCU?

- 4) In what four main areas does the RCU assume processing duties for the RMU?

- 5) What two memory areas do the Z80A and the 8X305 use to communicate with each other?

- 6) Who initiates and governs all 50BUS transactions?

- 7) What four items is the Internal Workstation Controller (IWS) responsible for?

- 8) How many printers can be connected to an Internal Printer Controller (IPC)?

- 9) What type of interface does the Internal WISE Controller (IWISE) require to communicate with other units?

- 10) Which Appendix contains a listing of reference materials that may be read to provide a better understanding of the OIS 40/50/60 system.

# SECTION 2 RESOURCE MANAGEMENT UNIT (RMU)

# SECTION 2

# Resource Management Unit (RMU)

### 2.1 Resource Management Unit (RMU)

In this section we will discuss the theory of operation and circuit description for the Resource Management Unit (RMU). In lue of the fact that the RMU can not operate completely by itself, parts of the RCU circuits will also be discussed throughout this section.

While reading this section you should refer to the schematics in Appendix E so that you can follow along with the descriptions given. All circuit components will be referred to by their chip number and schematic location; Example L4 (1B2) indicates chip L4 located on sheet 1 row B column 2. If you are unfamiliar with a pectular type of chip that is being discussed you should refer to either the manufactures specification sheet or to the TTL Data Book by Texas Instruments. A quick reference of all the chips in the OIS 40/50/60 system is located in appendix C, each chip is listed by number and a brief description of its operation in the circuit is given. This Appendix is divided into parts representing each of the circuit boards located in the OIS 40/50/60. I recommend that you turn to Appendix C now and take a quick look at the listings.

Throughout the description of the circuits I will be using mnemonics to describe different signals that are generated. A complete listing of the meaning of these mnemonics are given in Appendix B. Any mnemonics that are active low and are indicated in the schematics by having a bar over the top will be prefixed in this document be an ampersand (&). Some signal have dual functions, such a R/W which when active low indicates a read operation and when active high indicates a write operation. To indicate which part of the mnemonic is active low I will place an additional ampersand next to the portion of the mnemonic that is active low, (i.e. &&R/W will represent the above description whereas R/W&& would indicate the reverse situation).

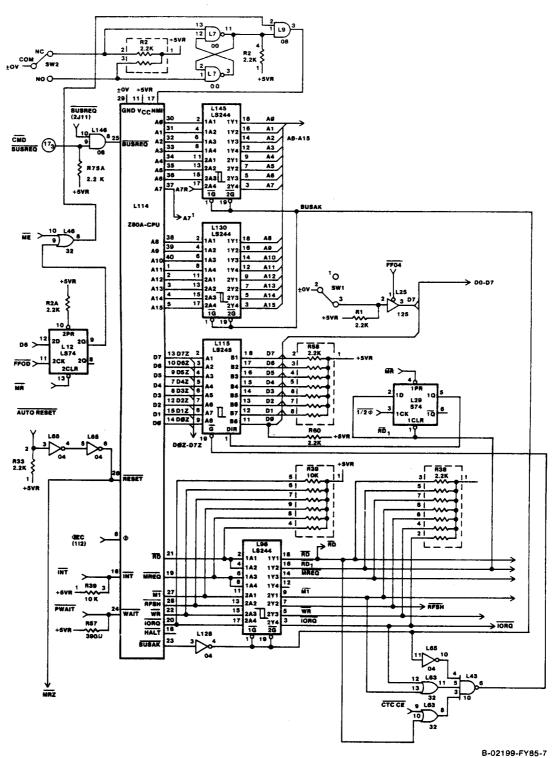

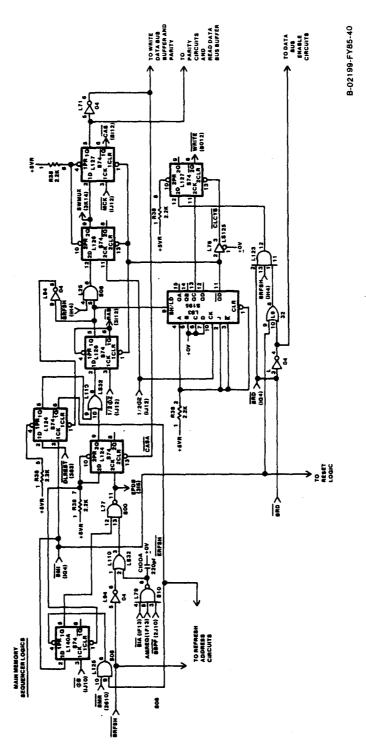

The 8266 Resource Management Unit used in the OIS 40/50/60 processor-based data processing system contains the 4-MHz Z80A Processor; the Counter Timer Chip, which generates interrupts and acts as a time-of-day clock; and the NEC765 Floppy Disk Controller (FDC), which manages operations involving the system's Floppy Disk Drive (FDD). (The 8X305 Microcontroller, the second processor of the OIS 50 multiprocessor system, is located on the 210-8267 Resource Control Unit board.) FIGURE 2.1-1 is a block diagram of the Resource Management Unit, and FIGURE 2.1-2 illustrates the Resource Management Unit's relation to the OIS 40/50/60 system.

FIGURE 2.1-1

Block Diagram of the Resource Management Unit

FIGURE 2.1-2 OIS 50 Block Diagram

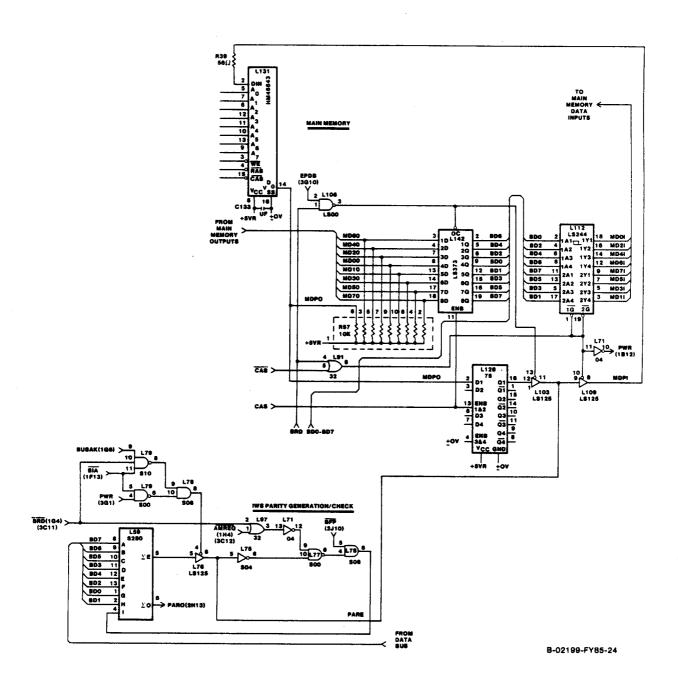

Memory support for the OIS 40/50/60 is located on the Resource Management Unit (RMU) and is divided among RAM, PROM, and Memory Mapped Input/Output (MMI/O). Sixty-four kilobytes of RAM and 4k bytes of PROM are available for power-up diagnostics and Initial Program Load (IPL). Memory addresses from 1000-FF00 are used as random access memory, with the lower 4k bytes (0000-0FFF) overlayed by PROM. Memory addresses from FF00-FFFF are reserved for MMI/O.

The RMU board also contains serial transmit and receive logic for external Data Link ports 1-4. However, the 8X305 Microcontroller on the Resource Control Unit (RCU) board maintains control of these ports.

### RMU-RCU Interaction

RMU-RCU communication involves shared memory, a Command Notification Bit (CNB), and the 8X305 Microcontroller interrupts that assert the Z80A. Two memory areas on the RCU board are shared between the Z80A and the 8X305: the 16-byte Parameter Register File (PRF) and the 12-byte Status Register File (SRF). Both the Z80A and the 8X305 can read from or write to the PRF; they cannot, however, access the PRF simultaneously. Only the Z80A can read the SRF, and only the 8X305 can write to it.

The RCU decodes RMU requests via the Parameter Register File. The Z80A microprocessor in the RMU loads the PRF with the command codes and data that the RCU needs to perform a specific operation. When the Z80A sets the Command Notification Bit, the 8X305 operates on the PRF as needed to complete the command. (Generally, the 8X305 moves the PRF data to its scratchpad RAM and then releases the PRF.) The PRF must be released quickly because the Z80A is suspended (ie, held in a bus request state) while the 8X305 uses the PRF.

PRF byte assignments depend upon the function requested (see Appendix G). Typically, the Z80A issues the FF20 (Command Request) byte and the FF22 (Specify Command) byte to the PRF. The RCU reads the bytes and defines the remaining bytes according to specific command requirements and then returns the FF21 (Command Acknowledge) byte to the PRF for the Z80A to read. To avoid invalid parameter errors, unused or undefined bytes should always be cleared to zero.

To perform a function that involves the RCU, the Z80A loads the command code and necessary data into the PRF. The Z80A then writes to address FF30 to issue the Command Notification Bit that initiates the command. Normally, the 8X305 is polling, waiting for the Command Notification Bit to be set. When the RMU issues a command, the 8X305 can perform one of two routines. If the command is an immediate command, the Z80A is awaiting command completion and the RCU must, therefore, execute the command immediately. If, however, the command is a non-immediate command, the RCU defers the command until it has completed any immediate operation in progress.

Upon receiving an immediate command, the RCU validates the command code, copies the PRF to its scratchpad RAM, completes the requested operation, and releases the RMU. Upon receipt of a non-immediate command, the RCU validates the command code, copies the PRF to its scratch RAM, sets RCU Busy status in the SRF, releases the RMU, completes the requested operation, and issues either an interrupt request or a Control Unit Busy (CUBUSY) signal to the RMU when the operation has been completed.

When the 8X305 Microcontroller performs a 1-byte operation, it does not immediately release the PRF. The Microcontroller holds the Z80A in a suspended state for a maximum of 1 ms (otherwise the lack of dynamic RAM refresh could cause a memory data loss). When the 8X305 releases the Z80A, the data and/or status from the 1-byte operation is immediately available to the Z80A via the SRF.

Status and error information returns to the RMU via the dual-ported SRF. When the 8X305 is busy, RCU Busy status information is set in byte FF10 of the SRF. Status information concerning Data Link block operations resides in SRF bytes FF11 and FF12. SRF bytes FF13-FF15 contain status information about the 1-byte Data Link operations, and bytes FF16-FF1B contain status information concerning the Winchester Disk Drive (WDD).

### 2.1.1 Controls and Indicators

Two 7-segment displays (L3 and L4, located on the top edge of the RMU board and visible through the front bezel of the OIS 40/50/60 cabinet) indicate various errors. Error codes are displayed to indicate errors detected during power-up diagnostics or system errors (such as operator errors) detected after the operating system has taken control. Inverted data bits /D0-7 drive the LEDs, the data bits are inverted through L8 (1G3) and then supplied to drivers L5 (1G2) (activated by /FF08 write command) and L6 (1G1) (activated by /FF09 write command). L5 drives the L4 (1B2) lower display, and L6 drives the L3 (1B1) upper display.

All seven display segments light up momentarily when power is applied to the OIS 40/50/60. The LEDs do not remain on long enough to be seen, however, and their lighted condition can be verified only with a Zebug (to establish that all LEDs are functioning correctly). Power-up LED illumination is created by the trailing edge of the /MR signal as it clocks the L4 and L5 drivers via L26 (1F3) while bits D0-7 are high.

Table 2.1-1 shows the codes used on bits D0-7 to create each hexadecimal symbol on the display. Table 2.1-2 lists the display error codes for power-up diagnostics and the error condition indicated by each symbol. Table 2.1-3 lists the display error codes for system errors and the error condition indicated by each code.

Switch SW2 is a pushbutton Restart Control Switch located on the interior of the OIS 40/50/60 cabinet on the front edge of the RMU board. If the operating system has control, activating SW2 generates a Non-Maskable Interrupt (NMI) to the Z80A. The NMI traps the Z80A to the Master Debugger routine (if the system is configured with the Master Debugger). The Master Debugger routine is used exclusively as a development tool.

Activating the Restart Control Switch during Test 1 (the LED Test) of the power-up diagnostics causes the tests following Test 1 to be skipped and initiates the bootstrap routine. To prevent error message generation, bit 7 of the Software Configuration Switches should be open prior to activating SW2 during Test 1. Activating SW2 with bit 7 open normally allows a smooth transition into the bootstrap routine.

In Table 2.1-2, "fatal\*" next to an error indicates that the program cannot "continue on error" (not even when using the special DIP switch settings described in Table 2.1-4). "Fatal\*\*" indicates that the encountered error halts the power-up sequence; however, tests can continue with the use of the DIP switch settings shown in Table 2.1-4. The test number is shown on the upper display, and the error number is shown on the lower display.

| (D6) | (D7)<br>(D4)<br>(D1) | (D5)<br>(D2) |

|------|----------------------|--------------|

|------|----------------------|--------------|

(D0) = decimal point

| DISPLAY | CODE (HEX, without decimal point) | CODE (HEX, with decimal point |

|---------|-----------------------------------|-------------------------------|

| 0       | EE                                | EF                            |

| 1       | 48                                | 49                            |

| 2       | BA                                | ВВ                            |

| 3       | В6                                | В7                            |

| 4       | 74                                | 75                            |

| 5       | D6                                | D7                            |

| 6       | DE                                | DF                            |

| 7       | A4                                | A5                            |

| 8       | FE                                | FF                            |

| 9       | F4                                | F5                            |

| A       | FC                                | FD                            |

| В       | 4E                                | 4 F                           |

| С       | CA                                | СВ                            |

| D       | 3E                                | 3F                            |

| E       | DA                                | DB                            |

| F       | D8                                | D9                            |

Table 2.1-1: LED DISPLAY CODES

Table 2.1-2: POWER-UP DIAGNOSTIC DISPLAY ERROR CODES

| TEST<br>NUMBER | TEST NAME                                                                                                                                                                 | ERR<br>NUM                                            | OR<br>BER                  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|

| <u>o</u>       | LED SEGMENT DISPLAY TEST<br>Visual Feedback for Error Detection                                                                                                           |                                                       |                            |

| 1              | CTC TEST<br>Read/Write Miscompare<br>Down Count Failure                                                                                                                   | (fatal**)<br>(fatal**)                                | 1<br>2                     |

| <u>2</u>       | UPPER RAM TEST Data Error (fatal**) Parity Error (fatal**) Parity Status Register Error Non-Maskable Interrupt (NMI) Error                                                | 0-7<br>P<br>(fatal**)<br>(fatal**)                    | PS<br>P8                   |

| <u>3</u>       | PRF TEST  RCU Busy (loops until ready)  RCU Command Response to RMU  Command Not Accepted  Command Invalid  Incomplete Command Accepted  None of the Above  PRFs Affected | (fatal*) (fatal*) (fatal*) (fatal*) (fatal*) (fatal*) | .d<br>.0<br>.1<br>.2<br>.3 |

Table 2.1-2: POWER-UP DIAGNOSTIC DISPLAY ERROR CODES (cont.)

| Table 2.1-2: POWER-UP DIAGNOSTIC DISPLAY ERROR CODES (CONt.) |                                                                                                                                                                    |                                          |                            |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------------|

| <u>4</u>                                                     | CTC TEST<br>CTC Not Interrupting (Channels 0-3)<br>Incorrect Vector                                                                                                |                                          | 1<br>2                     |

| <u>. 4</u>                                                   | FDD DEADMAN TIMER TEST No Interrupt (fatal**) Incorrect Vector Interrupt Not Caused by Deadman Timer Floppy Disk Controller Has Interrupt Pending                  | l<br>(fatal**)<br>(fatal**)<br>(fatal**) | 2<br>3<br>4                |

| <u>5</u>                                                     | RCU INTERRUPT TEST  RCU Busy (loops until ready)  RCU Response Bad on Block Write Command  Vector Error (fatal**)  No Interrupt Created                            | (fatal**)<br>2                           | d<br>1<br>3                |

| <u>.5</u>                                                    | WINCHESTER DEADMAN TIMER TEST RCU Busy (loops until ready) No Interrupt Requested Vector Error Drive Not Selected Indexing Stuck Off Indexing Stuck On             | (fatal**)<br>(fatal**)<br>(fatal**)      | d<br>1<br>2<br>3<br>4<br>5 |

| <u>6</u>                                                     | SET SLAVE LIST RCU Busy (loops until ready) RCU Command Response to RMU Command Not Accepted Command Invalid Incomplete Command Accepted None of the Above         | (fatal*) .<br>(fatal*) .<br>(fatal*) .   | d<br>0<br>1<br>2           |

| <u>7</u>                                                     | MAP SLAVE STATUS  RCU Busy (loops until ready)  RCU Command Response to RMU  Command Not Accepted  Command Invalid  Incomplete Command Accepted  None of the Above | (fatal*) .<br>(fatal*) .<br>(fatal*) .   | d<br>0<br>1<br>2<br>3      |

Table 2.1-2: POWER-UP DIAGNOSTIC DISPLAY ERROR CODES (cont.)

|          | The following error numbers are displayed for second, but do not prevent continuation of                                                                                                                                                                                                                                 |                                                                         |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

|          | 1-Byte Data Link Status (DLS) 1-Byte Slave Status (SS)  CPE Detected by DLS and SS  CPE Detected Only by SS  MPE Detected by DLS and SS  MPE Detected Only by SS  Detected by Data Link Status  Received Parity Error  No Data Timeout  Check Power-Up State  If slaves are not available,  display error and loop on te |                                                                         |

| <u>8</u> | SLAVE CONTROL  WRITE SECTION  RCU Busy (loops until ready)  RCU Command Response to RMU  Command Not Accepted  Command Invalid  Incomplete Command Accepted  None of the Above                                                                                                                                           | (fatal*) .d<br>(fatal*) .0<br>(fatal*) .1<br>(fatal*) .2<br>(fatal*) .3 |

|          | The following error numbers are displayed for second, but do not prevent continuation of                                                                                                                                                                                                                                 |                                                                         |

|          | 1-Byte Data Link Status (DLS) 1-Byte Slave Status (SS)  CPE Detected by DLS and SS  CPE Detected Only by SS  MPE Detected by DLS and SS  MPE Detected Only by SS  Detected by Data Link Status  Received Parity Error  No Data Timeout  Check Power-Up State                                                             | .4<br>.5<br>.6<br>.7<br>.8<br>.9<br>.P                                  |

| .8       | READ SECTION RCU Busy (loops until ready) RCU Command Response to RMU Command Not Accepted Command Invalid Incomplete Command Accepted None of the Above                                                                                                                                                                 | (fatal*) .d<br>(fatal*) .0<br>(fatal*) .1<br>(fatal*) .2<br>(fatal*) .3 |

Table 2.1-2: POWER-UP DIAGNOSTIC DISPLAY ERROR CODES (cont.)

|          | The following error numbers are displayed for second, but do not prevent continuation of t                                                                                                                                                                                                 |                                              |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|          | 1-Byte Data Link Status (DLS) 1-Byte Slave Status (SS)  CPE Detected by DLS and SS  CPE Detected Only by SS  MPE Detected by DLS and SS  MPE Detected Only by SS  Detected by Data Link Status  Received Parity Error  No Data Timeout  Check Power-Up State  Compare Data to Correct Data | .4<br>.5<br>.6<br>.7<br>.8<br>.9<br>.P<br>.E |

|          | If slaves are not available, a loop back to performed until a slave passes the test.                                                                                                                                                                                                       | Test 7 is                                    |

|          | COMPARE DATA ERROR Register Contents:  H - Data Received  C - Data Expected  D - XOR Data  E - Slave Number  L - Low Address                                                                                                                                                               |                                              |

| <u>9</u> | IPL TEST FLOPPY DISK DRIVE I/O Error Addressed Drive Is Not Ready (loops on drive if not ready) WINCHESTER DISK DRIVE I/O Error Addressed Drive Is Not Ready (loops on drive if not ready)                                                                                                 | (fatal*) .1 .2                               |

|          | "UP" is displayed for approximately 1 s after completion of all power-up tests. Control to bootstrap program.                                                                                                                                                                              |                                              |

Table 2.1-3: SYSTEM DISPLAY ERROR CODES

| Display Error Code (Hex) | Error Condition                              |

|--------------------------|----------------------------------------------|

| FF                       | Parity                                       |

| FE                       | Restart                                      |

| FD                       | Software Debugger                            |

| FC                       | Hardware Debugger                            |

| FB                       | I/O Error Reading Master or Volume Label     |

| FA                       | Illegal PROM Address                         |

| F9                       | Parity and Illegal PROM Address              |

| DC                       | PROM Revision Levels Not Compatible          |

| DD                       | No RCU Response                              |

| DE                       | XMM Configured for 64k Master                |

| DF                       | Data Link Error During I/D Transfer (XMM)    |

| E0                       | Invalid Volume Label (Hash Code)             |

| El                       | Not System Disk                              |

| E2                       | Bad Configuration - Too Little Memory        |

| E3                       | Bad Configuration - System Disk Excluded     |

| E4                       | Insufficient Memory for Control Blocks       |

|                          | (TCB)                                        |

| <b>E</b> 5               | Insufficient Memory for Control Blocks (VCB) |

| <b>E</b> 6               | Insufficient Memory for Control Blocks (DCB) |

| E7                       | Insufficient Memory for Control Blocks (FCB) |

| E8                       | Unsupported Disk Type                        |

| E9                       | Insufficient Memory for Buffers (VAU Map)    |

| EA                       | Insufficient Memory for Buffers (Catalog)    |

| EB                       | Incorrect PROM Installed                     |

| EC                       | Unsupported Timer Interval                   |

| ED                       | Cannot Mount System Disk                     |

| EE                       | Invalid SMD/CMD Characteristic Switches      |

| EF                       | Invalid IPL Sector                           |

IPL Device Select Switch SWl is a rocker switch located on the OIS 40/50/60 control panel. When read by the /FF04 command, SWl selects either the Floppy Disk Drive or the Winchester Disk Drive as the system drive for initial program loading. When SWl is in position 3, D7 is cleared to 0 and the Floppy Disk Drive is selected to IPL the system; when SWl is in position 1, D7 is set to 1 and the Winchester Disk Drive is used to IPL the system.

SW3 is an 8-bit switch bank used to select various software configurations during the power-up sequence. SW3 switch settings define, via data bits D0-7, which software configurations run on the OIS 40/50/60. Switch settings are passed through the L49 Software Configuration Switch Buffer when the /FF05 command is activated. The SW3 Software Configuration Switches, used only during power-up diagnostics, are sensed in the order listed in Table 2.1-4.

Table 2.1-4: SOFTWARE CONFIGURATION SWITCH SETTINGS

| Switch Number | Function                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------|

| 7             | Software configuration switch settings are of no significance to the built-in test unless this bit is set (ie, D7 = 1). |

| 0             | When cleared (D0 = 0), causes program to loop on power-up diagnostics.                                                  |

| 1             | When cleared (D1 = 0), causes program to stop on error.                                                                 |

| 2             | When cleared (D2 = 0), causes program to loop on error.                                                                 |

| 3             | When cleared (D3 = 0), causes program to continue on error.                                                             |

| 4-6           | Ignored by diagnostics.                                                                                                 |

### Power-Up Protection

Power-Up protection circuitry (L131 (2F3-8), composed of four comparators) monitors the 5-V (pin 9), -5-V (pin 4), and 12-V (pin 7) power levels to ensure that the proper voltages are reached before the Z80A is released to place the OIS 40/50/60 into an operative mode. When the voltages are at their correct levels, the active &AUTO RESET signal from L131 pin 13 is deactivated, allowing the Z80A to begin operation. The &AUTO RESET signal is converted into the Master Reset (&MRC) signal and sent to the other boards of the OIS 40/50/60 system. &MRC holds each OIS 40/50/60 board reset until proper voltage levels are reached.

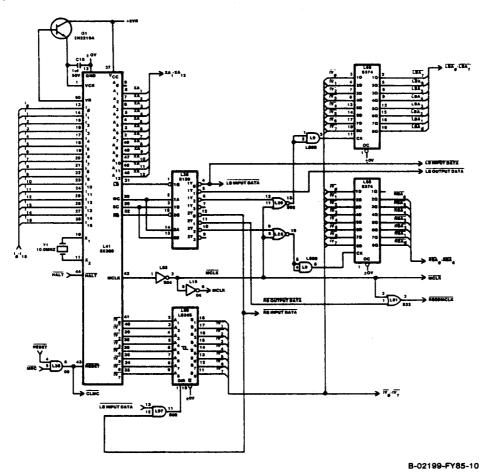

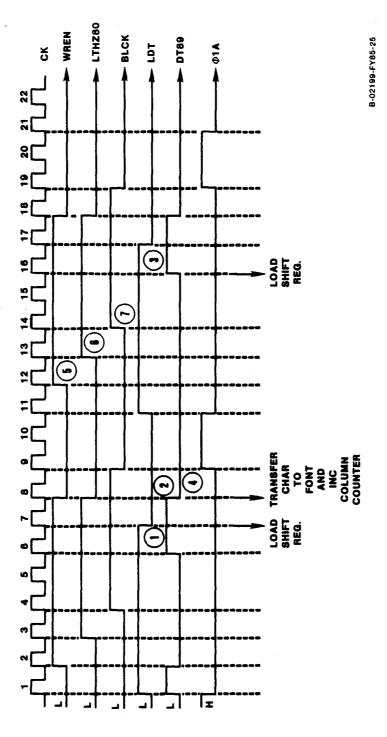

## 2.1.2 Clock Generation

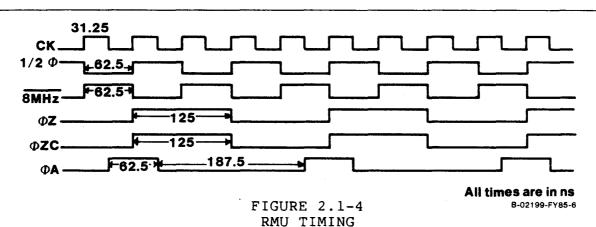

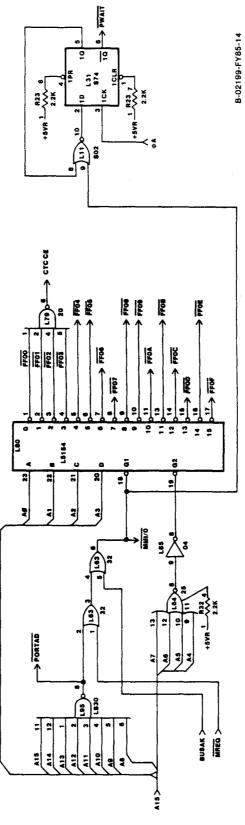

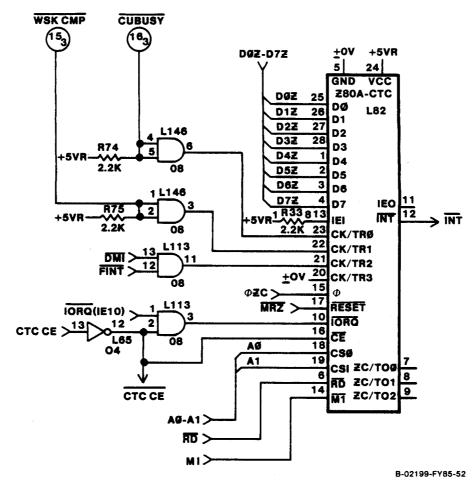

Yl generates the 16-MHz base timing signal (CK) from which the clock generation circuitry (L31 (1K2) and L32 (1I3/4), shown in FIGURE 2.1-3) creates all other clock signals used on the RMU board. L32 gate 1 divides the 16-MHz signal to create the 8-MHz 1/2Phi signal that synchronizes the generation of Z80A Data Bus direction control signals and the RAS signal. L32 gate 2 divides the 8-MHz signal to create the 4-MHz Phi-Z and Phi-ZC signals that drive the CTC and the Z80A processors. L31 gate 2 generates the /Phi-A signal used for FDC write timing and for the Z80A wait circuit. FIGURE 2.1-4 illustrates the relationship of the various clocking signals.

## 2.1.3 Memory Mapped Input/Output

Memory addresses FF00-FFFF are reserved for Memory Mapped I/O (MMI/O) operations. FF00-FF0F are decoded on the RMU board, and FF10-FF40 are decoded on the RCU board. MMI/O Decoder L80 on the RMU board decodes address bits A0-3 into I/O Port Commands /FF00-/FF0F (defined in Table 2.1-5). Address bits A4-15 are decoded through gates L64 (1J10) and L95 (1K11) to enable the MMI/O Decoder L80 (1J/K9). MMI/O Logic is shown in FIGURE 2.1-5.