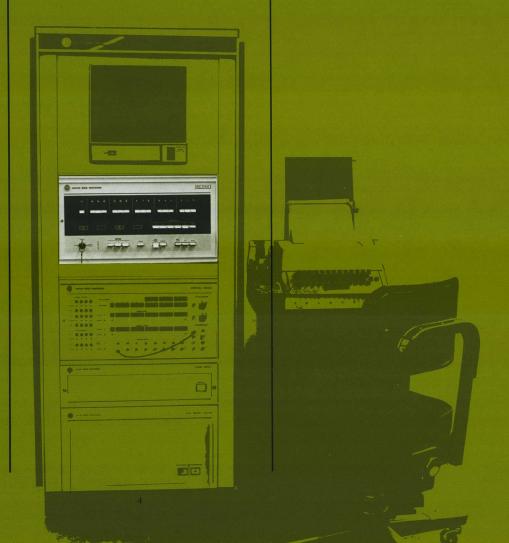

The new Varian 620/f-100 is the computer of choice for the large system user. No other minicomputer on the market offers such a combination of CPU power, software capabilities and variety of peripheral devices.

The Varian 620/f-100 has been designed from the inside out for large systems. Low priced memory expansion modules make it economically feasible to expand memory up to 32K to support sophisticated software operating systems such as Varian VORTEX (see page 8).

The computer's fast, 750-nanosecond cycle time is matched by special I/O options that allow data transfers of over a million 16-bit data words per second. The systems designer can now take full advantage of the newer high-speed drums, discs, and other mass storage devices.

the new varian 620/f-100

...new

low

price

for

top

performance

At the same time, the Varian 620/f-100 is a workhorse computer, equally compatible with all standard peripherals and I/O interfaces. The designer can choose from the industry's widest selection of field-tested data-processing devices, displays, communication controllers, and analog/digital interfaces.

A feature of all 620 computers of particular value in real-time applications is the hardware priority interrupt structure of up to 64 levels. Response time to an interrupt is less than 3 microseconds.

# fast efficient programming

I/O up to 1.33 million words/sec.

real-time operating systems

CPU and Power Supply

32K Memory

All I/O

16K Memory and I/O

#### **Fast, Efficient Programming**

The exceptional speed and efficiency of the Varian 620/f-100 is the product of both its fast cycle time and its memoryreference-oriented instruction set.

The versatile instruction list allows the programmer to write compact, highly efficient programs, saving on both memory storage and processing time. A single-word instruction can directly address any location in the first 2K of memory. Addressing modes include pre-and-post indexing, extended addressing, and index/indirect addressing. Other standard features include hardware multiply and divide, memory protect, real time clock and power failure/restart.

The Varian 620 instruction set provides an optimum balance between fast execution time, compact code and ease of coding. Three general purpose registers (two of them also serving as index registers) are more than enough for efficient programming and at the same time allow a single-word instruction to execute a complete range of logical and arithmetic register-memory operations. These operations (e.g., add memory to register) execute in just two memory cycles or 1.5 microseconds.

## Three Input/Output Techniques

The Varian 620/f-100 features three different types of I/O operations.

The basic I/O bus is a party line that can address up to 64 peripheral devices and transfer data under program control at rates up to 100,000 16-bit words per second. A Direct Memory Access (DMA) mode interlaces program steps with I/O transfers to produce a cycle-stealing data rate of up to 274,000 words per second. The Priority Memory Access (PMA) option provides a direct port to memory for high-speed transfer rates up to 1.33million 16-bit words per second with latency of less than a microsecond.

#### **Software Library**

Programs developed for any Varian 620 computer can be executed on the Varian 620/f-100.

The Varian 620 software library includes a full set of programming aids. such as FORTRAN IV, BASIC, a complete mathematical package, DAS assemblers, debugging programs, and a source program editor. RPG IV is a businessoriented language for stand alone cardbased systems or for other peripherals under MOS. ADAPTS provides an easy to use system for control of analog and digital I/O.

Varian software also includes diagnostic programs for the mainframe, memory and peripherals, plus a complete set of I/O subroutines for all standard peripherals and I/O interfaces.

Hardware/software operating systems are available for a range of special applications. MOS is for batch processing from tape, disc, or drum. VORTEX is for melding real-time applications with background programs and takes full advantage of the fast data transfer rates between the Varian 620/f-100 and high-capacity rotating memories.

The new Varian 620/L-100 has set a new price/performance standard for the industry. With a cycle time of only 950 nanoseconds, and standard hardware multiply/divide, power failure/restart, real-time clock, and 8 levels of hardware priority interrupt, it offers the industry's highest performance for the dollar.

At the same time, the Varian 620/L-100 is the direct descendant of the classic Varian 620/A, 620/i, and 620/L computers, with thousands of successful installations in the field. For the designer of small to medium sized systems, the new Varian 620/L-100 represents the optimum balance between innovation and proven capabilities.

Key to the design of the new computer is the imaginative use of high-speed TTL

the

new

varian

620/L-100

...new

top

performance

for

low price

MSI integrated circuits in the all-new central processor unit. These now match the inherent speed and reliability of the compact core memory modules that were the outstanding feature of the Varian 620/L.

The changes have only enhanced the efficiency and flexibility of the basic design. With over a hundred basic instructions and a versatile I/O structure, the Varian 620/L-100 is adaptable to an almost infinite range of applications.

### Off-the-Shelf Peripherals and Software

Varian 620/L-100 systems are supported by a complete line of off-the-shelf input/output devices, including teletypes, paper-tape equipment, magnetic tape transports, disc drives, drums, card readers and punches, communication controllers, analog/digital front ends, displays, plotters, line printers, and special computer-to-computer interfaces.

The computer is also supported by the full complement of Varian 620 software, including assemblers, compilers, utility packages, mathematical subroutines, and operating systems (except VORTEX). All programs written for the Varian 620/i and 620/L computers may be run on the new computer without any alteration. The only change is a 90% increase in the processing speed.

# 950 nanosecond cycle time

low cost memory expansion

compact packaging design

#### **Compact Packaging Design**

The Varian 620/L-100 features a rugged, simple, yet highly reliable and easy-to-service package design.

All circuit cards are of uniform size, including the central processor and memory modules, and load through the back of the chassis for easy access and installation. The mainframe enclosure, only 10-1/2 inches high, can contain a complete system including all mainframe options, up to 8K of memory, and interface controllers for up to 8 peripheral devices. Full expansion of the memory requires only one additional enclosure, the same size as the mainframe.

## **Dedicated or Multi-Purpose Applications**

The economy and versatility of the Varian 620/L-100 makes it adaptable to a wide range of applications, from the simplest to the most sophisticated.

The low cost of the basic unit makes it possible to dedicate the computer to a single chore, such as processing the output of a single analytical instrument or controlling a single manufacturing process. Yet the Varian 620/L-100 has the power to perform highly complex computations at high speeds and is a valuable tool for scientific research, engineering studies, and business accounting.

The flexibility of the computer's I/O structure makes it ideally suited for time-share networks, as a communication controller, and as a pre-processor for a larger computer system.

CPU, 8K Memory, I/O

24K Memory

All I/O

# varian 620 software

Both Varian 620-100 computers are totally compatible with all programs written for the corresponding earlier models in the Varian 620 line. Numerous application programs are available for immediate use with the extensive list of Varian 620 peripherals and controllers.

The Varian 620-100 user also has the benefit of the industry's most refined set of software packages for creating new programs. Varian 620 assemblers, language processors and utility programs have been field tested for over half a decade by thousands of Varian users, ranging from professional programmers to individuals with little or no computer training.

Clearly written and complete instructions for using these software packages are contained in a single, comprehensive 450-page Varian Software Handbook, available on request from any Varian representative. Regular classes are conducted on programming, and the VOICE Varian Users Group maintains a constant flow of information on new additions and modifications in the Varian 620 software library. VOICE also promotes the interchange of helpful information and application programs between the users themselves.

As an added service, the Varian Computer Programming Department is staffed to provide close support to Varian users, either as consultants and advisors or as contract suppliers of complete turn-key systems.

# software selection

The selection of a particular software package is a function of several factors, including the hardware configuration, the job to be done, and the sophistication of the user.

The fastest, most efficient programs can be written, of course, in the Varian 620 symbolic language (see instruction list on page 10) and translated into machine language by one of the Varian DAS Assemblers. However, highly effective programs can also be written without any knowledge of the Varian 620 architecture and instruction set by using one of the three language processors: FORTRAN IV, BASIC, or RPG IV. A language processor translates functional

statements into complete sets of machine instructions for carrying out specified tasks.

The simplest language processor to use is BASIC, which can be self-taught with a few hours of study. This is followed by the more powerful and versatile FORTRAN IV, of special value in scientific and instrumentation applications. RPG IV is a special businessman's language for the preparation of reports and statistical data. The remaining elements in the Varian software library are the utility programs, which go far to simplify the task of loading the programs into the computer, debugging any errors that may have been entered, and assuring that the computer is in smooth running order.

# DAS assemblers

Varian 620 DAS Assemblers are invaluable programming aids. Their function is to translate a source program, written in symbolic instructions, pseudo ops, and data statements, into a machinelanguage object program that can be directly executed by a Varian 620 computer.

Three versions of the DAS Assembler are available. DAS 4A is designed for a minimum system consisting of a computer with 4K memory and a teletype. DAS 8A provides expanded capabilities for systems with at least 8K of memory, and utilizes additional peripheral devices, such as a rotating memory, magnetic tape transport, card equipment, paper tape system, or line printer.

The third and most comprehensive assembler is DAS MR, an integral part of the VORTEX, and MOS operating systems (see page 8). DAS MR is a macro assembler which produces relocatable object modules that may be loaded into any sector of the computer memory.

## FORTRAN IV

Varian FORTRAN IV is an integrated software package that consists of a single-pass compiler for interpreting FORTRAN statements, converting them to machine-language instructions, a relocating loader for assembling object modules, and a run-time package that includes I/O drivers and a full set of arithmetic and data-conversion subroutines.

The FORTRAN IV language is especially useful in writing programs for scientific and engineering applications that involve mathematical computations. Problems can be stated in simple English words and mathematical terms that are fully compatible with the American National Standards Institute (ANSI) FORTRAN.

The FORTRAN compiler transforms the statements into a Varian 620 object program in a single pass through the computer and simultaneously detects any errors made by the programmer in his source program.

The package is available either as a stand-alone version requiring only 8K of memory, or as an integral part of the VORTEX and MOS operating systems.

## BASIC

Two versions of the popular BASIC programming system are available for use with Varian 620 computers.

**BASIC** is an advanced version of the self-teaching system developed at Dartmouth College. It is applicable to a variety of business and scientific applications.

The programming language is simple and easy to use. Source statements are typed directly on a system console; if any errors are entered, the computer immediately responds and a correction can be made. Since BASIC requires only an 8K computer and a teletype, even a small dedicated system can be used for program preparation and general computation during periods when the system is not performing its primary function.

**Extended BASIC** expands the BASIC language to make it a more powerful tool for researchers. Special statements have been developed to facilitate the interaction between the computer and an external data-acquisition or processcontrol system. Other statements are designed to establish and control data files stored on a rotating memory device, and to facilitate changing of program overlay segments. Extended BASIC has been developed to operate with the ADAPTS hardware/software system.

## RPG IV

Varian RPG IV (Report Program Generator) is a business-oriented language for preparing statistical data and tabular reports such as inventory records, sales analyses, and personnel summaries.

The Varian RPG IV compiler is an advanced version of RPG systems now widely used throughout industry for commercial applications. It is available either as a free-standing software package, or under control of the MOS batch operating system.

## **BEST**

BEST (Basic Executive Scheduler and Timekeeper) is a real-time monitor that automatically schedules core-resident programs according to the time of day, at fixed time intervals, or at the earliest opportunity.

BEST can operate with any Varian 620series computer equipped with 4K of memory, making it a valuable addition to dedicated real-time computer systems. With it, the real-time programmer has a framework for his programs, complete with automatic mechanisms for handling timekeeping, power failure/restart, and relative program scheduling.

# utility programs

Varian 620 utility programs are standard software elements supplied (along with an Assembler) with every Varian computer. Their function is to simplify the programming and operation of the computer, making it easy for the operator to load programs, detect errors, make editing changes, and check out the hardware.

**BLD II** (Binary Load/Dump) is a program that can be readily entered by the bootstrap loader. BLD II is used, in turn, to load object programs from a paper tape or TTY reader. It can also be used to output the binary contents of memory on paper tape in a reloadable format.

**AID II** is an on-line debugging program for correcting programming errors. By entering AID commands on the TTY, the operator can display and alter the contents of any memory address or block. Areas of memory can also be searched for specified conditions.

**EDIT** permits the programmer to add, delete, and correct any portion of a symbolic program. When the program is correct and ready to be assembled or compiled, EDIT is used to generate a tape of the symbolic program stored in memory.

MAINTAIN II is a diagnostic program that checks that all hardware elements in the system are operating correctly. Individual tests are run on the central processor, memory, options, and peripherals. If a fault is found, more comprehensive tests are made to isolate the malfunction.

**MATH LIBRARY** is a comprehensive set of mathematical function subroutines (e.g. floating point arithmetic) written in assembly language. Subroutine calls may be made from DAS or FORTRAN programs.

# varian operating systems

Two comprehensive software operating systems are available for use with Varian 620-100 computers: VORTEX and MOS. Both systems incorporate a full repertoire of utility programs, as well as DAS MR and FORTRAN IV language processors. MOS also includes RPG IV.

VORTEX is a real-time executive program for the Varian 620/f-100. MOS is a batch-processing system for both the Varian 620/f-100 and the 620/L-100.

VORTEX (Varian Omnitask Real-Time Executive) is a multi-programming system with special features designed for real-time applications. A number of different tasks may be stored in the main memory or on a rotating memory device. These tasks are scheduled by a resident executive program that gives highest priority to real-time "foreground" programs. Lower priority "background" programs are executed during the idletime intervals embedded in most real-time operations. The effect is to give the system the utility of two computers for the price of one.

VORTEX also increases the efficiency of any installation in which the computer is required to operate on a number of different programs in sequence. The user simply establishes the priority of the jobs to be executed; the system automatically schedules and runs the programs without further operator intervention.

Varian **MOS** (Master Operating System) is an integrated batch-process software system designed to boost performance and simplify operation for the medium-to-large-scale system user.

MOS is available in disc, drum, and magnetic-tape resident versions, and includes a complete I/O Control System and System Executive.

Features offered by MOS are automatic identification of both printed listings and binary object output with the job title and date to provide for program control and job accountability; a system preparation program, system maintenance program, source program editor, object program debug package, and a program library.

MOS conserves main memory space for the user by allowing all software elements, except for a small Resident Monitor, to be stored on the rotating memory or magnetic tape and loaded into the computer only when needed. This applies even to the System Executive, which serves as the central control element.

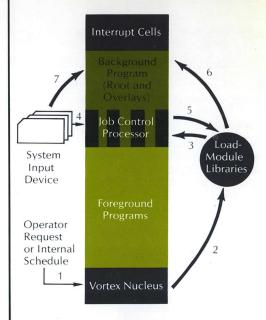

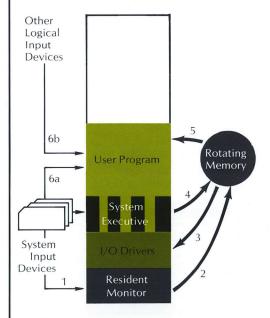

### **Example of VORTEX Operation**

When Real-Time Executive senses (1) that time is available for the scheduling of a background task (following an initial operator request), the Job Control Processor is read into the background area of the main memory (2 and 3). The JCP responds to a directive from the System Input Device (4) and loads a background task from either the rotating memory (5 and 6) or the System Input Device (7).

#### **Example of MOS Operation**

A directive from the System Input Device (1) instructs the Resident Monitor to load the System Executive, I/O Control Module, and appropriate I/O drivers (2 and 3). The System Executive loads and executes a program from the rotating memory (4 and 5) or any logical input unit (6). Programs can overlay the System Executive, but not the I/O Control and Driver modules.

Peripheral devices and I/O interfaces for Varian 620 systems have been field tested in hundreds of installations and have been selected to provide an optimum combination of economy and high performance.

Each standard peripheral subsystem is an integrated unit, including the device itself, interconnecting cables, I/O controller, and software for its operation. The standard Varian peripherals are supplemented by a list of over 100 other peripheral models and types that may be supplied on special order.

FIXED HEAD DISCS — Low-cost storage, with capacity of 30K, 61K or 123K words; 17 ms average access time; 73.3K word transfer rate; 1 head per track.

MOVING HEAD DISCS — Capacities from 1.17 million words to 58 million words; 12.5 ms and 20 ms on-track access time, average access times to a track of 45 and 60 ms; transfer rates up to 156K words per second.

DRUM MEMORIES — Capacity of 30K, 61K, 123K, 246K, 491K, or 983K words; 8.7 ms average access time; 106K word transfer rate; 1 head per track.

MAGNETIC TAPE — 9-track or 7-track, with up to 4 transports per controller, densities of 200, 556, and 800 bpi and speed of 25 ips.

TELETYPES — Model ASR 33, ASR 35, or KSR 35 units.

HIGH-SPEED PAPER TAPE—Punch rates up to 75 characters per second and read rates up to 300 characters per second.

CARD READER — Reading speed of 300 cards per minute.

CARD PUNCH — Punching speed of 35 cards per minute.

LINE PRINTER — 245 to 1100 lines per minute, up to 132 characters per line,

# varian 620 peripherals

buffered, ASCII code, 64 alphanumeric characters and symbols.

DIGITAL PLOTTER — 300 steps per second, 0.01-inch step size, other sizes are available.

ELECTROSTATIC PLOTTER — Statos 21 Printer/Plotter; produces graphic displays, and alphanumeric information at rates up to 5,000 lines per minute.

ANALOG INPUT — Multiplexer/ Controllers expandable up to 256 single ended or differential channels. Analogto-digital converters for word lengths to 13 bits, conversion rates to 55K words per second.

ANALOG OUTPUT — Controllers expandable to 64 channels, word lengths to 14 bits per channel.

DIGITAL INPUT — Multiplexer/controllers expandable up to 2048 channels of 16 bits.

DIGITAL OUTPUT — Controllers expandable up to 64 output channels of 16 bits each.

CRT DIAPLAY — 11-inch storage scope.

RELAY INTERFACES — Contact inputs and mercury-wetted contact outputs; 0.5 to 3 A; up to 400 V.

GENERAL PURPOSE INTERFACES — Buffer Interface Controller; Buffered I/O Controller; Digital I/O Controller; Universal Serial Asynchronous Controller.

DATA SET COUPLERS — Interface with Type 103, 201, 202 and 301 modems, hardware or software sync character detection; transmission rates up to 50,000 baud; controller available for 801 Automatic Call Unit.

COMMUNICATIONS CONTROLLER — Multiplexes, controls and provides data interface for up to 64 data sets; synchronous and asynchronous lines may be intermixed; modular line controllers for RS 232B, CCITT, discrete, and relay communication systems.

# varian 620-100 instructions

|                | tore Instructions                                                    | 620/f-100  | 620/L-100    |

|----------------|----------------------------------------------------------------------|------------|--------------|

| LDA<br>LDAI    | Load A Register Immediate                                            | 2          | 2            |

| LDAE           | Load A Register Immediate<br>Load A Register Extended                | 2 3        | 2 3          |

| LDB            | Load B Register                                                      | 2          | 2            |

| LDBI           | Load B Register Immediate                                            | 2          | 2            |

| LDBE           | Load B Register Extended                                             | 3          | 3            |

| LDX            | Load X Register                                                      | 2          | 2            |

| LDXI           | Load X Register Immediate                                            | 2          | 2            |

| LDXE           | Load X Register Extended                                             | 3          | 3            |

| STA<br>STAI    | Store A Register Store A Register Immediate                          | 2 2        | 2 2          |

| STAE           | Store A Register Extended                                            | 3          | 3            |

| STB            | Store B Register                                                     | 2          | 2            |

| STBI           | Store B Register Immediate                                           | 2          | 2            |

| STBE           | Store B Register Extended                                            | 3          | 3            |

| STX            | Store X Register                                                     | 2          | 2            |

| STXI           | Store X Register Immediate                                           | 2          | 2            |

| STXE<br>*TSA   | Store X Register Extended                                            | 3          | 3            |

|                | Transfer Switches to A Register                                      | 1          | _            |

|                | ic Instructions                                                      | 2          | 2            |

| INR<br>INRI    | Increment Memory and Replace<br>Increment and Replace Immediate      | 3          | 3            |

| INRE           | Increment Memory and Replace Extended                                | 4          | 3 4          |

| ADD            | Add Memory to A Register                                             | 2          | 2            |

| ADDI           | Add Memory to A Register Immediate                                   | 2          | 2            |

| ADDE           | Add Memory to A Register Extended                                    | 2 3        | 3            |

| SUB            | Subtract Memory from A Register                                      | 2          | 2            |

| SUBI           | Subtract Memory from A Register Immediate                            | 2          | 2            |

| SUBE           | Subtract Memory from A Register Extended                             | 3          | 3            |

| MUL<br>MULI    | Multiply                                                             | 8.5        | 10           |

| MULE           | Multiply Immediate<br>Multiply Extended                              | 8.5<br>9.5 | 8.5<br>10-14 |

| DIV            | Divide                                                               | 8.5        | 8.5          |

| DIVI           | Divide Immediate                                                     | 8.5        | 8.5          |

| DIVE           | Divide Extended                                                      | 9.5        | 9.5          |

| Logic Inst     | tructions                                                            |            |              |

| ORA            | Inclusive-OR Memory and A Register                                   | 2          | 2            |

| ORAI           | Inclusive-OR to A Register Immediate                                 | 2          | 2            |

| ORAE           | Inclusive-OR Memory and A Register                                   |            |              |

| FD .           | Extended                                                             | 3          | 3            |

| ERA            | Exclusive-OR Memory and A Register                                   | 2          | 2            |

| ERAI<br>ERAE   | Exclusive-OR to A Register Immediate                                 | 2          | 2            |

| LKAL           | Exclusive-OR Memory and A Register<br>Extended                       | 3          | 3            |

| ANA            | AND Memory and A Register                                            | 2          | 2            |

| ANAI           | AND to A Register Immediate                                          | 2          | 2            |

| ANAE           | AND Memory and A Register Extended                                   | 3          | 3            |

| Jump Inst      | ructions                                                             |            |              |

| JMP            | Jump Unconditionally                                                 | 2          | 2            |

| JOF            | Jump if Overflow Indicator Set                                       | 1,2        | 2            |

| JAP            | Jump if A Register Positive                                          | 1,2        | 2            |

| JAN            | Jump if A Register Negative                                          | 1,2        | 2            |

| JAZ<br>JBZ     | Jump if A Register Zero                                              | 1,2        | 2            |

| JXZ            | Jump if B Register Zero Jump if X Register Zero                      | 1,2<br>1,2 | 2            |

| JSS1           | Jump if Sense Switch 1 Set                                           | 1,2        | 2            |

| JSS2           | Jump if Sense Switch 2 Set                                           | 1,2        | 2 2          |

| JSS3           | Jump if Sense Switch 3 Set                                           | 1,2        | 2 2          |

| JIF            | Jump if Combined Conditions Are Met                                  | 2          | 2            |

| *JANZ          | Jump if A Register Not Zero                                          | 1,2        | _            |

| *JBNZ          | Jump if B Register Not Zero                                          | 1,2        | _            |

| *JXNZ<br>*JS1N | Jump if X Register Not Zero                                          | 1,2        | _            |

| *JS2N          | Jump if Sense Switch 1 Not Set<br>Jump if Sense Switch 2 Not Set     | 1,2        | _            |

| *JS3N          | Jump if Sense Switch 3 Not Set                                       | 1,2<br>1,2 | _            |

| *IJMP          | Indexed Jump                                                         | 2          | =            |

| *JSR           | Jump Unconditionally and Set Return                                  | _          |              |

|                | in Index Register                                                    | 2          | _            |

| *JOFN          | Jump if Overflow Indicator Not Set                                   | 1,2        | _ ,          |

| *BT            | Bit Test                                                             | 1,2        | _            |

| *SRE           | Skip if Register Equal                                               | 1,2        |              |

|                | -Mark Instructions                                                   | 3,3.5      | _            |

| <b>JMPM</b>    | Jump and Mark Unconditionally                                        | 3          | 2,3          |

| JOFM           | Jump and Mark if Overflow Set                                        | 1,3        | 2,3          |

| JANM           | Jump and Mark if A Register Negative                                 | 1,3        | 2,3          |

| JAPM<br>JAZM   | Jump and Mark if A Register Positive                                 | 1,3        | 2,3          |

| JBZM           | Jump and Mark if A Register Zero<br>Jump and Mark if B Register Zero | 1,3<br>1,3 | 2,3<br>2,3   |

| JXZM           | Jump and Mark if X Register Zero                                     | 1,3        | 2,3          |

| JS1M           | Jump and Mark if Sense Switch 1 Set                                  | 1,3        | 2,3          |

| JS2M           | Jump and Mark if Sense Switch 2 Set                                  | 1,3        | 2,3          |

|                |                                                                      |            |              |

| JS3M                                                                                                                                                                                                                                                                                                                                                                                | Jump and Mark if Sense Switch 3 Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1,3                                                                                         | 2,3                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| JIFM                                                                                                                                                                                                                                                                                                                                                                                | Jump and Mark if Combined Conditions Are Met                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1,3                                                                                         | 2,3                                                                                         |

| *JOFNM                                                                                                                                                                                                                                                                                                                                                                              | Jump and Mark if Overflow Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1,3                                                                                         |                                                                                             |

| *JANZM                                                                                                                                                                                                                                                                                                                                                                              | Jump and Mark if A Register Not Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1,3                                                                                         | _                                                                                           |

| *JBNZM<br>*JXNZM                                                                                                                                                                                                                                                                                                                                                                    | Jump and Mark if B Register Not Zero Jump and Mark if X Register Not Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1,3<br>1,3                                                                                  | _                                                                                           |

| *JS1NM                                                                                                                                                                                                                                                                                                                                                                              | Jump and Mark if Sense Switch 1 Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1,3                                                                                         |                                                                                             |

| *JS2NM                                                                                                                                                                                                                                                                                                                                                                              | Jump and Mark if Sense Switch 2 Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1,3                                                                                         | _                                                                                           |

| *JS3NM                                                                                                                                                                                                                                                                                                                                                                              | Jump and Mark if Sense Switch 3 Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1,3                                                                                         | _                                                                                           |

| XEC                                                                                                                                                                                                                                                                                                                                                                                 | Instructions Execute Unconditionally                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                           | 2                                                                                           |

| XOF                                                                                                                                                                                                                                                                                                                                                                                 | Execute if Overflow Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1,2                                                                                         | 2                                                                                           |

| XAP                                                                                                                                                                                                                                                                                                                                                                                 | Execute if A Register Positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2                                                                                         | 2                                                                                           |

| XAN<br>XAZ                                                                                                                                                                                                                                                                                                                                                                          | Execute if A Register Negative Execute if A Register Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1,2                                                                                         | 2                                                                                           |

| XBZ                                                                                                                                                                                                                                                                                                                                                                                 | Execute if B Register Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1,2<br>1,2                                                                                  | 2 2                                                                                         |

| XXZ                                                                                                                                                                                                                                                                                                                                                                                 | Execute if X Register Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1,2                                                                                         | 2 2                                                                                         |

| XS1<br>XS2                                                                                                                                                                                                                                                                                                                                                                          | Execute if Sense Switch 1 Set Execute if Sense Switch 2 Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1,2<br>1,2                                                                                  | 2 2                                                                                         |

| XS3                                                                                                                                                                                                                                                                                                                                                                                 | Execute if Sense Switch 3 Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1,2                                                                                         | 2                                                                                           |

| XIF                                                                                                                                                                                                                                                                                                                                                                                 | Execute if Combined Conditions Are Met                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1,2                                                                                         | 2                                                                                           |

| *XOFN<br>*XANZ                                                                                                                                                                                                                                                                                                                                                                      | Execute if Overflow Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1,2                                                                                         | -                                                                                           |

| *XBNZ                                                                                                                                                                                                                                                                                                                                                                               | Execute if A Register Not Zero Execute if B Register Not Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1,2<br>1,2                                                                                  | = = = = = = = = = = = = = = = = = = = =                                                     |

| *XXNZ                                                                                                                                                                                                                                                                                                                                                                               | Execute if X Register Not Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1,2                                                                                         | _                                                                                           |

| *XS1N<br>*XS2N                                                                                                                                                                                                                                                                                                                                                                      | Execute if Sense Switch 1 Not Set<br>Execute if Sense Switch 2 Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1,2                                                                                         | _                                                                                           |

| *XS3N                                                                                                                                                                                                                                                                                                                                                                               | Execute if Sense Switch 3 Not Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1,2<br>1,2                                                                                  | _                                                                                           |

| Control In                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1/2                                                                                         |                                                                                             |

| HLT                                                                                                                                                                                                                                                                                                                                                                                 | Halt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                           |                                                                                             |

| NOP<br>SOF                                                                                                                                                                                                                                                                                                                                                                          | No Operation Set Overflow Indicator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1                                                                                           |                                                                                             |