#### INTRODUCTION

<u>A Programmer's Guide to the X-6 Assembly System</u> is concerned with the preparation of a data processing program for the X-6 assembly on a USS 80 or 90 Tape System. For the most part, this consists of the coding of the object program according to X-6 symbolic and relative coding conventions and the preparation of the punched card input deck to be processed by the X-6 Assembly System program. Such preassembly preparations are covered in detail. An understanding of the reasons for these preparations, however, is only possible through a general knowledge of the processing steps during the actual assembly by the X-6 system. For this purpose, a general description of the X-6 processing has been included. The details of the processing can be found in the flow charts of the X-6 Assembly System.

Most of the examples used are applicable to both the USS 80, 80 Tape, and 90 Tape computers. Some, however, are inimical to one computer (for example, three part alphabetics and interlaces).

Much of the description and terminology used in this manual presupposes that the reader has a general knowledge of machine coding and operation of the USS 90/80 computers.

# TABLE OF CONTENTS

| INTRODU | CTION                                      |

|---------|--------------------------------------------|

| GENERAL | DESCRIPTION                                |

| X-6 INS | TRUCTION CODES                             |

| ADDRESS | ING                                        |

| I. In   | struction Addressing                       |

| Α.      | Space Addressing                           |

| В.      | Tag Addressing                             |

|         | 1. Permanent Tags                          |

|         | 2. Temporary Tags                          |

| С.      | Overflow Addressing                        |

| D.      | Absolute Addressing                        |

| E.      | Register Addressing                        |

| II. Da  | ta Addressing                              |

| Α.      | Working Storage and Constant Addressing 19 |

| В.      | Table Entry Addressing    23               |

| С.      | Interlace Addressing                       |

| LATENCY | MINIMIZATION                               |

| CLOCK M | ODIFICATION                                |

| LIBRARY | ROUTINES                                   |

| ASSEMBL | Y INPUT CARDS                              |

| I. Syn  | nbolic Deck Organization                   |

| II. In  | put Card Format                            |

| Α.      | Label Card, Card Type 1                    |

| В.      | Restrict Card, Card Type 2                 |

| C.      | Tag Equals Card, Card Type 3               |

| D.      | Interlace Card, Card Type 4                |

| E.      | Tables Card, Card Type 5                   |

| F.      | Specifications Card, Card Type 6           |

|         | Operation Header Card, Card Type 7         |

|         | Detail Card, Card Type 8                   |

|         | Operation Sentinel Card, Card Type 9       |

|         | End-of-Run Sentinel Card, Card Type 10     |

3

| OUTPU | T CARD | FORMAT                | •      | • • | •    | •   | •   | •  | •   | ٠   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 57 |

|-------|--------|-----------------------|--------|-----|------|-----|-----|----|-----|-----|-----|----|------|----------|---|---|---|---|---|---|---|---|---|----|

| PROGR | AMMING | PROCED                | URES   | 5.  | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 58 |

| I.    | Flow-( | Chartin               | ng ,   | • • | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 58 |

| II.   | Coding | g • • •               | •      | • • | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 59 |

| PREPA | RATION | FOR TH                | E X-   | -6  | ASS  | SEM | BL  | Ϋ́ | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 60 |

| OPERA | TING I | NSTRUCI               | IONS   | 5 F | OR   | ΤH  | E   | X- | 6   | AS  | SE  | ME | 3L Y | <u>r</u> | • | • | • | • | • | • | • | • | • | 61 |

| I.    | Loadi  | ng and                | Asse   | emb | ly   | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | ٠ | • | 61 |

| II.   | Error  | Codes                 | •      | • • | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 62 |

| III.  | Stop ( | Codes .               | •      | • • | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 63 |

| IV.   | X-6 S  | torage                | Layo   | out | •    | •   | •   | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 64 |

| APPEN | лт хта | - OPERA               | יסדייע | 18  | A NT | 5   | SUF | RO | TTT | ידא | E.S | 5  |      |          |   |   | ` |   |   |   |   |   |   |    |

| WITH  | IN THE | X-6 AS                | SEMI   | ЗLY | S    | YSI | 'EM | P  | RO  | GR  | AM  | [  | •    | •        | • | • | • | • | • | • | • | • | • | 67 |

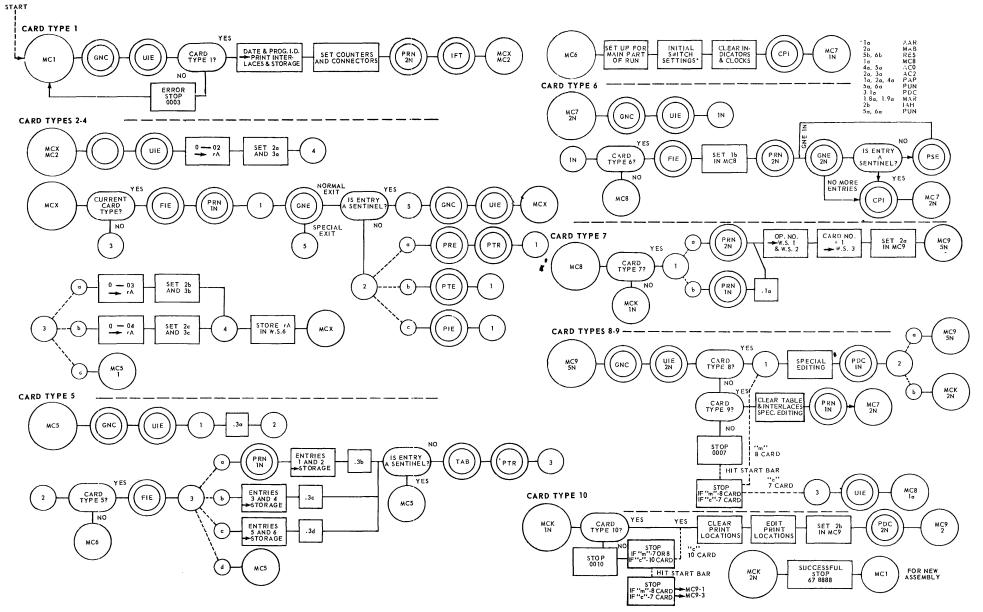

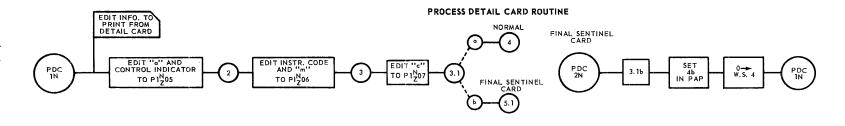

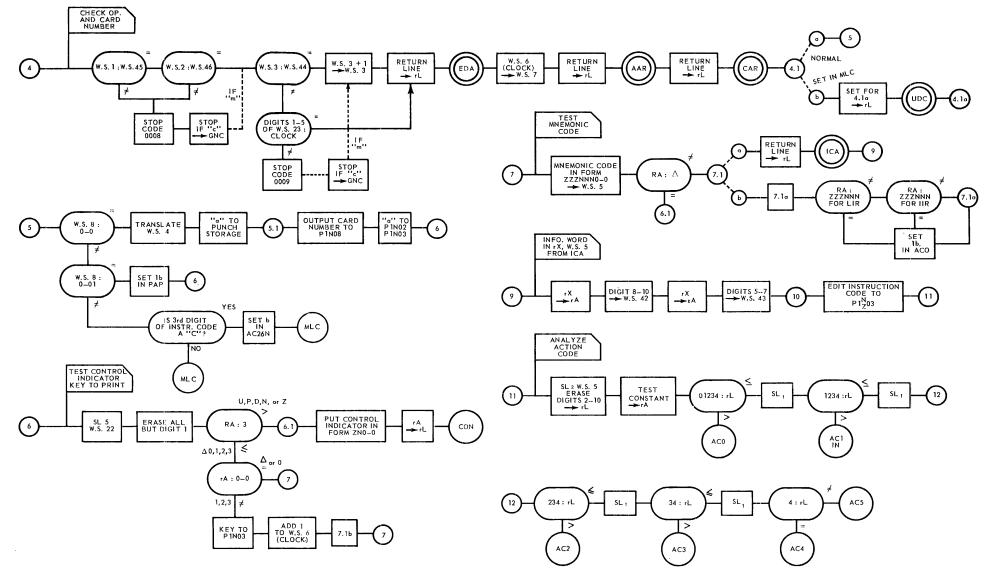

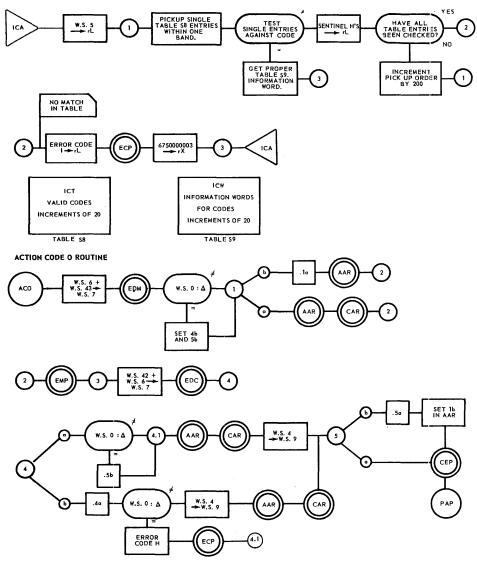

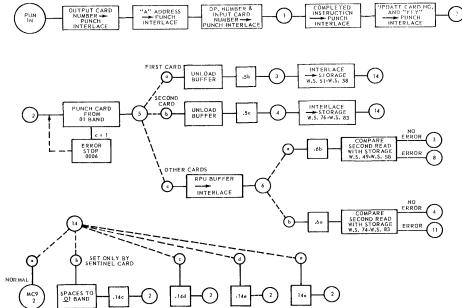

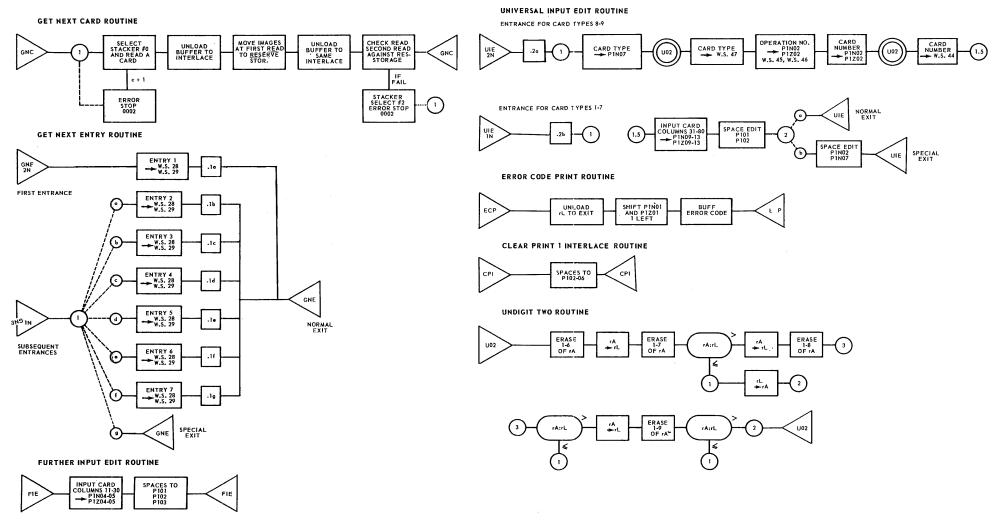

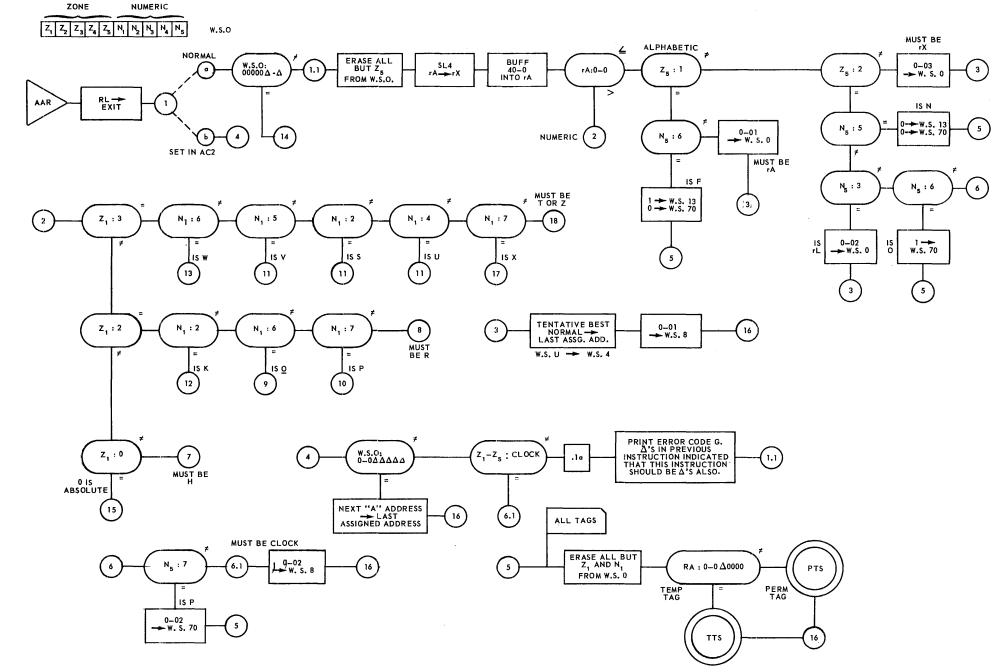

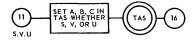

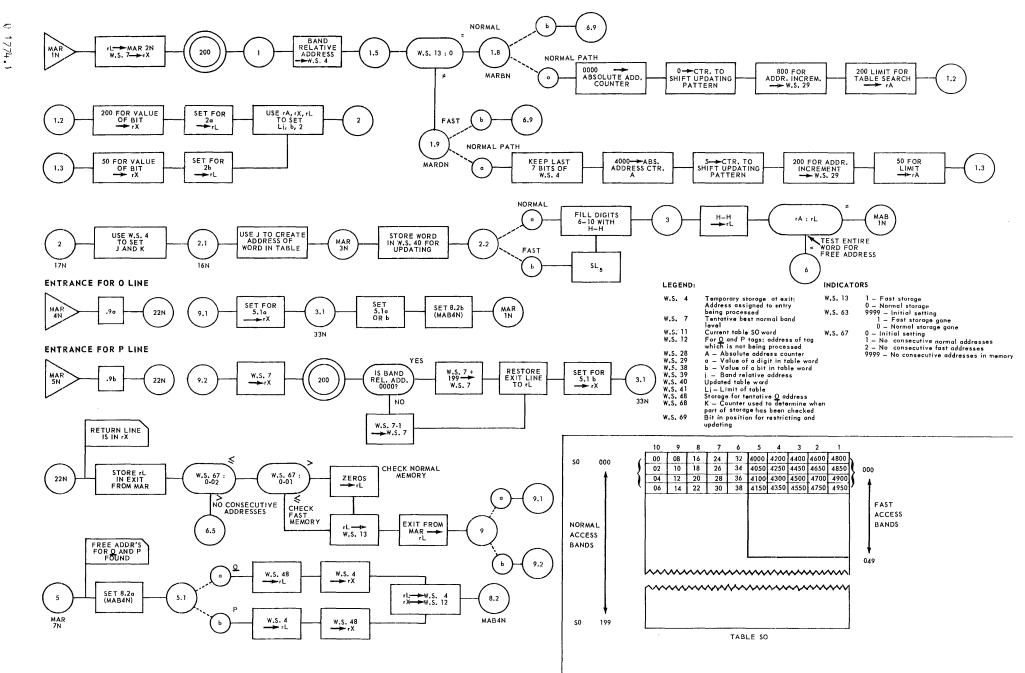

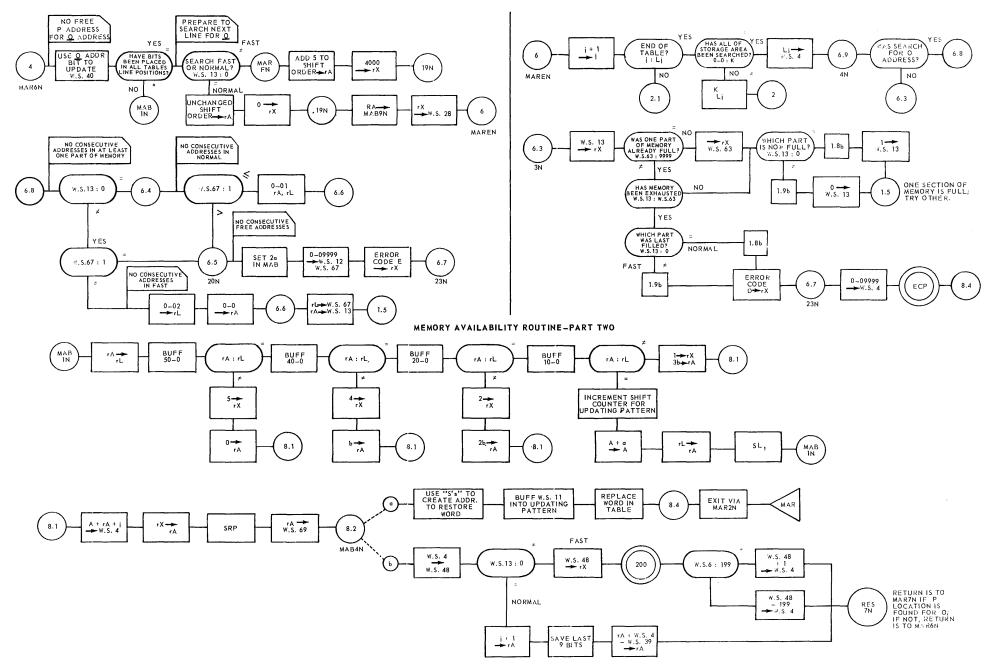

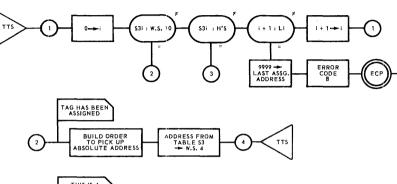

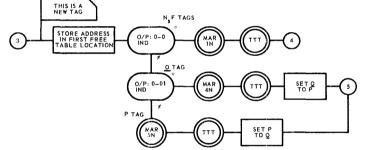

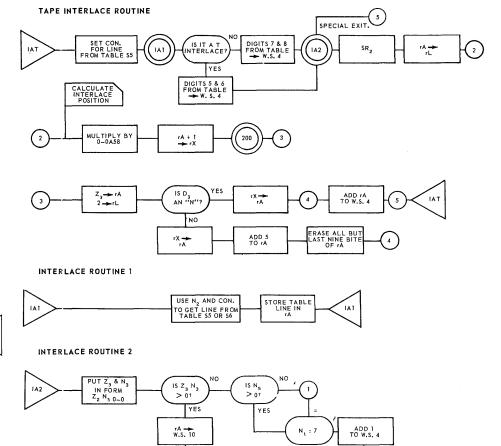

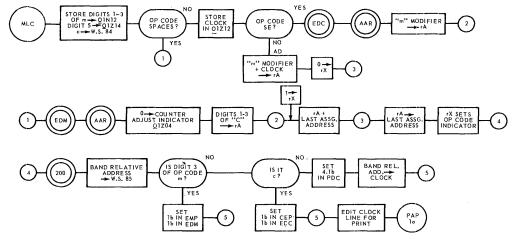

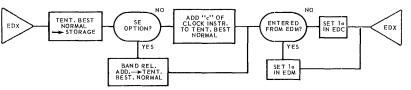

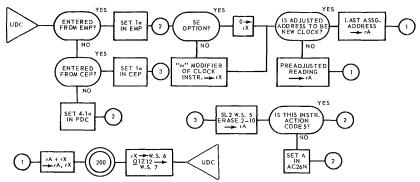

| APPEN | DIX II | <b>-</b> X <b>-</b> 6 | FLOU   | v-C | HAF  | RTS |     | •  | •   | •   | •   | •  | •    | •        | • | • | • | • | • | • | • | • | • | 71 |

|       |        |                       |        |     |      |     |     |    |     |     |     |    |      |          |   |   |   |   |   |   |   |   |   |    |

GENERAL DESCRIPTION

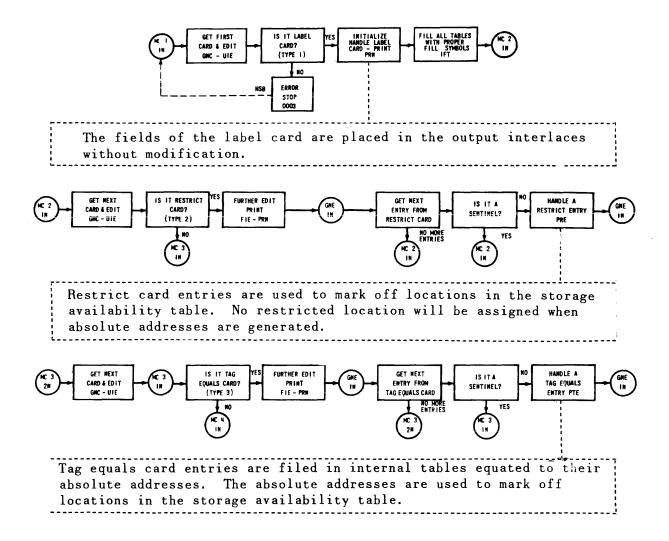

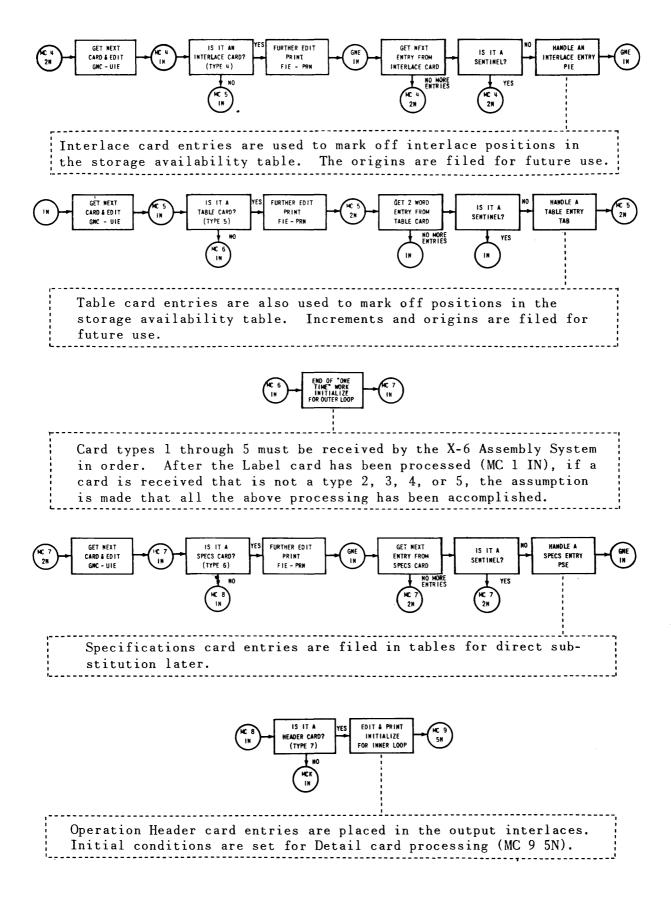

When the X-6 coding of a data processing program or operation has been completed, this coding, and any further information required by the X-6 Assembly System for the processing of the coding, is punched on appropriate input card types. These input cards are then placed in a specific order in the input deck and the actual assembly is begun.

Each card type will be processed in a specific way:

U 1774.1

1

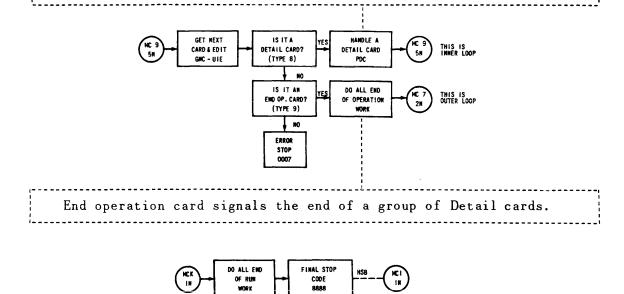

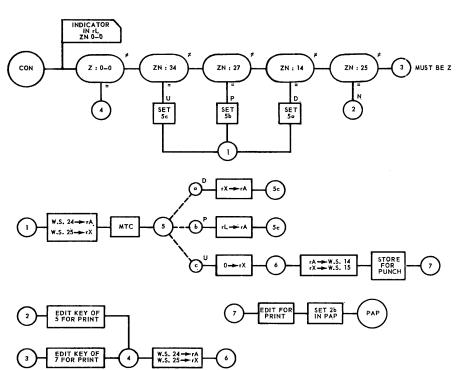

Detail cards contain the instruction lines and constants of a program. Only Detail card processing will produce output punching. The four basic steps in Detail card processing are:

- 1. Handle the a address.

- 2. Analyze the instruction code and separate instructions from constants. For instructions, obtain a code word to control further processing by the use of the necessary increment needed between the a, m, and c addresses and substitute the computer code equivalent of the mnemonic code. Determine if one or both of the m and c addresses are significant.

- 3. Handle the m address if necessary.

End input card signals the last card of the program being assembled. It contains the instruction to be used by the loading routine to start execution of the assembled program.

# X-6 INSTRUCTION CODES

| X<br>Mnem<br>Co |      |    | Computer<br>Code | Minimum<br>Word Times | Function                                                                                    |

|-----------------|------|----|------------------|-----------------------|---------------------------------------------------------------------------------------------|

| Arit            | hmet | ic |                  |                       |                                                                                             |

| ADD             | m    | с  | 70               | 5                     | Add (m) to (rA). If over-<br>flow, next instruction is<br>c+1.                              |

| SUB             | m    | с  | 75               | 5                     | Subtract (m) from (rA).<br>If overflow, next instruc-<br>tion is c+1.                       |

| MUL             | m    | с  | 85               | 105                   | Multiply (rL) by (m).                                                                       |

| DIV             | m    | с  | 55               | 115                   | Divide (m) by (rL). If<br>overflow, next instruction<br>is c+1.                             |

| Tran            | sfer |    |                  |                       | · · ·                                                                                       |

| LDA             | m    | С  | 25               | 24                    | Load rA: (m)——rA.                                                                           |

| LDX             | m    | с  | 05               | 4                     | Load rX: (m)——rX.                                                                           |

| LDL             | m    | с  | 30               | 4                     | Load rL: (m)rL.                                                                             |

| STA             | m    | с  | 60               | 4                     | Store rA: (rA) m] connet                                                                    |

| STX             | m    | с  | 65               | 24                    | Store rX: $(rX) \longrightarrow m$ m cannot<br>Store rX: $(rX) \longrightarrow m$ be regis- |

| STL             | m    | с  | 50               | չ <sub>+</sub>        | Store rL: $(rL) \longrightarrow m$ ter ad-<br>dress.                                        |

| ATL             | -    | с  | 77               | 3                     | $(rA) \longrightarrow rL.$                                                                  |

| CTA             | m    | -  | 23               | 3                     | $(rC) \longrightarrow rA.$                                                                  |

| CAA             | m    | -  | 36               | 3                     | Clear rA to zeros: Ø→→rA.<br>Original sign remains.                                         |

| CLA             | m    | -  | 26               | 3                     | Clear rA to zeros: ∅→rA.<br>Sign +.                                                         |

| CLX             | m    | -  | 06               | 3                     | Clear rX to zeros: ∅→→rX.<br>Sign +.                                                        |

| CLL             | m    | -  | 31               | 3                     | Clear rL to zeros: ∅→rL.<br>Sign +.                                                         |

| CAX             | m    | -  | 86               | 14                    | Clear rA and rX to zeroes.<br>Sign of rL goes to rA and<br>rX.                              |

U 1774.1

| Mner<br>Cc      | -6<br>Ionic<br>de |                 | Computer<br>Code              | Minimum<br>Word Times           | Function                                                                                                                                                            |  |  |

|-----------------|-------------------|-----------------|-------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Tran            | ıslat             | е               |                               |                                 |                                                                                                                                                                     |  |  |

| CTM             | -                 | с               | 12                            | 3                               | Translate card to machine<br>(computer) code: 80CC (rA,<br>rL, rX)> MC-6 (rA, rX);<br>Ø> rL.                                                                        |  |  |

| MTC             | -                 | С               | 17                            | 3                               | Translate machine (com-<br>puter) to card code: MC-6<br>(rA, rX)→80CC (rA, rL,<br>rX).                                                                              |  |  |

| TXM             | -                 | С               | C3                            | 3                               | Translate XS-3 code to<br>machine (computer) code:<br>XS-3 (rA)→→MC(rA).                                                                                            |  |  |

| TMX             | -                 | с               | C1                            | 3                               | Translate machine (com-<br>puter) code to XS-3 code:<br>MC(rA) ──→XS-3 (rA).                                                                                        |  |  |

| Index Registers |                   |                 |                               |                                 |                                                                                                                                                                     |  |  |

| LIR<br>Abs      | m<br>solut        | c<br>e          | 02                            | 3                               | Load index register: m<br>portion of instruction<br>word —>rBi.                                                                                                     |  |  |

| Add             | ress              |                 |                               |                                 | word — rBI.                                                                                                                                                         |  |  |

| IIR             | m                 | с               | 07                            | չ <sub>+</sub>                  | Increment Index Register:<br>m portion of instruction<br>word +(rBi) $\longrightarrow$ rBi and to<br>m portion of rA; $\emptyset \longrightarrow$<br>balance of rA. |  |  |

| Note<br>dres    | : Wł<br>s poj     | nen ei<br>stion | ther an L<br><u>must</u> be a | IR or IIR ins<br>n absolute add | truction is used, the m ad-<br>dress.                                                                                                                               |  |  |

| Comp            | ariso             | on              |                               |                                 |                                                                                                                                                                     |  |  |

| TEQ             | m                 | с               | 82                            | 3                               | Test (rA) and (rL) for<br>equality: If =, next in-<br>struction at m. If ≠,<br>next instruction at c.                                                               |  |  |

| TGR             | m                 | с               | 87                            | 3                               | Test (rA) and (rL) for<br>magnitude:<br>If (rA) > (rL), next in-<br>struction at m.<br>If (rA) $\leq$ (rL), next in-<br>struction at c.                             |  |  |

| Mneg | K-6<br>nonic<br>ode |      | Computer<br>Code | Minimum<br>Word Times | Function                                                                                                                                                                         |

|------|---------------------|------|------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Logi | ical                |      |                  |                       |                                                                                                                                                                                  |

| BUF  | m                   | с    | 20               | λ <del>ι</del>        | Superimpose (m) on<br>(rA) <del>→</del> rA.                                                                                                                                      |

| ERS  | m                   | с    | 35               | <u></u> γ+            | Extract (m) from<br>(rA)→rA.                                                                                                                                                     |

| SHR  | ∆∆∆nn               | с    | 32               | 3+nn                  | Shift right nn places:<br>$(rA) \longrightarrow (rX) \longrightarrow rA$ . nn<br>is number of places to<br>be shifted within range<br>OO through 10.                             |

| SHL  | ΔΔΔnn               | с    | 37               | 3+nn                  | Shift left nn places:<br>(rA) — Ø. nn is number<br>of places to be shifted<br>within range OO through<br>10.                                                                     |

| ZUP  | -                   | с    | 62               | դ                     | Zero suppress commas and zeros. MC-6 in rA, rX.                                                                                                                                  |

| JMP  | m                   | -    | 00               | 2                     | Jump to m.                                                                                                                                                                       |

| STP  | m                   | с    | 67               | -                     | Stop. m or c is alternative.<br>next instruction (re-<br>quires manual interven-<br>tion).                                                                                       |

| High | n-Speed             | i Pr | inter            |                       |                                                                                                                                                                                  |

| PBT  | m                   | с    | 27               | 3 if c.<br>4 if m.    | Printer test. If printer<br>free, next instruction<br>at m. If printer is not<br>free, next instruction<br>at c.                                                                 |

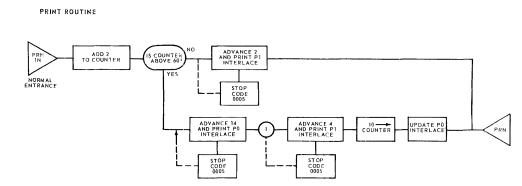

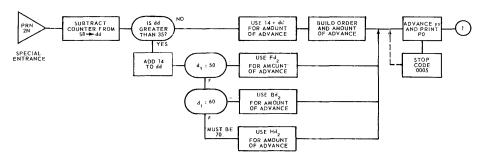

| PFD  | ∆∆∆nn               | с    | 16               | λ <del>ι</del>        | Advance nn lines.<br>nn is within the range OO<br>through 79.<br>If abnormal operation of<br>HSP, next instruction is<br>c+1.                                                    |

| PRN  | PyOnn               | С    | 11               | 592                   | Advance and print.<br>y=Print interlace (0<br>through 9).<br>nn=number of lines to ad-<br>vance (∆0 through 79).<br>If abnormal operation of<br>HSP, next instruction at<br>c+1. |

| X-6<br>Mnemonic<br>Code | Computer<br>Code | Minimum<br>Word Times      | Function                                                                                                                                                                              |

|-------------------------|------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High-Speed              | l Card Reader    | 2                          |                                                                                                                                                                                       |

| HBT m                   | c 42             | 3 if c.<br>4 if m.         | HSR buffer test: if<br>buffer loaded, next in-<br>struction at m; if buffer<br>not loaded, next instruc-<br>tion at c.                                                                |

| HBU HnOOd               | c 96             | 203 if d=0.<br>215 if d=1. |                                                                                                                                                                                       |

| HCC m                   | c 72             | 3 if c.<br>4 if m.         | HSR card cycle. If HSR<br>interlock, next instruc-<br>tion at m.<br>If HSR not interlocked,<br>next instruction at c.<br>If abnormal operation of<br>HSR, next instruction is<br>c+1. |

| HSS ∆∆n00               | c 47             | 3                          | HSR stacker selection.<br>n=stacker 0, 1, or 2.                                                                                                                                       |

| Read-Puncl              | n Unit           |                            |                                                                                                                                                                                       |

| RBT m                   | c 22             | 3 if c.<br>4 if m.         | RPU buffer test.<br>If buffer loaded, next<br>instruction at m.<br>If buffer not loaded,<br>next instruction at c.                                                                    |

| RBU RnOOd               | с 46             | 203 if d=0.<br>215 if d=1. | <pre>RPU buffer unload.<br/>n=RPU input interlace<br/>(0 through 9).<br/>d=0 if no automatic<br/>translation.<br/>1 if automatic transla-<br/>tion.</pre>                             |

| RCC OnOOd               | c 81             | 203 if d=0.<br>215 if d=1. |                                                                                                                                                                                       |

| Mnemonic<br>Code | Computer<br>Code | Minimum<br>Word Times | Function                                                                                                                                                  |

|------------------|------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  |                  |                       | If abnormal operation of RPU, next instruction is c+1.                                                                                                    |

| RSS – c          | 57               | 3                     | RPU select Stacker 1.                                                                                                                                     |

| Magnetic Tape    |                  |                       |                                                                                                                                                           |

| TST m c          | C2               | 3 if c.<br>4 if m.    | Test servo availability.<br>If servo free, next in-<br>struction at m. If servo<br>not free, next instruc-<br>tion at c.                                  |

| TBL xn000 c      | C6               | 205                   | Tape buffer load.<br>x=T or Z.<br>n=Tape interlace (O<br>through 9).                                                                                      |

| TBT m c          | C7               | 3 if c.<br>4 if m.    | Test tape buffer.<br>If buffer not <b>available,</b><br>next instruction at c.<br>If available, next<br>instruction at m.                                 |

| TRW ∆∆xyO c      | F2               | 600 ms.               | Rewind tape to first<br>block condition.<br>x=servo number (0 through<br>9).<br>y=0 if rewind without in-<br>terlock.<br>2 if rewind with inter-<br>lock. |

| TBU xn000 c      | F6               | 205                   | Tape buffer unload.<br>x=T or Z.<br>n=Tape interlace (O<br>through 9).<br>If abnormal operation of<br>tape, next instruction<br>is c+1.                   |

| TRD ∆∆xyz c      | G2               | 17                    | Read one block from servo x<br>into tape buffer band.<br>x=servo number (0 through<br>9).<br>y=0 if USS mode.<br>5 if UNIVAC mode.                        |

| X-6<br>Mnemonic<br>Code |   | Computer<br>Code | Minimum<br>Word Times | Function                                                                                                                                                                              |

|-------------------------|---|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         |   |                  |                       | z=direction and gain:                                                                                                                                                                 |

|                         |   |                  |                       | O=forward normal.<br>1=forward low.<br>2=forward high.<br>5=backward normal.<br>6=backward low.<br>7=backward high.                                                                   |

| TWR xyO                 | с | Η2               | 17                    | Write one block from the<br>tape buffer band onto the<br>tape.<br>x=servo number (0 through<br>9).<br>y=mode and density.<br>0=USS 250 cpi.<br>5=UNIVAC 250 cpi.<br>6=UNIVAC 125 cpi. |

# PRINTED EQUIVALENTS FOR ALPHA-NUMERIC COMPUTER CODES

| X-6 Mnemonic<br>Code    | Computer<br>Code | Printed<br>Equivalents |

|-------------------------|------------------|------------------------|

| TST                     | C2               | )2                     |

| $\mathbb{T}\mathrm{BL}$ | C6               | )6                     |

| $	extsf{TBT}$           | C7               | )7                     |

| TRW                     | F2               | (2                     |

| TBU                     | F6               | (6                     |

| TRD                     | G2               | ;2                     |

| TWR                     | H2               | '2                     |

| TXM                     | C3               | )3                     |

| TMX                     | C1               | )1                     |

9

#### ADDRESSING

The X-6 Assembly System will generate absolute a, m, and c addresses with optimal latency address development. In the assembly of a program, however, it may be necessary to establish certain relationships between data being assembled and data that has already been assembled or that will be assembled. The program is coded in small segments, termed "operations", with each of the operations coded by one or more programmers. To assemble these operations, X-6 instructions must be coded in such a way that the relation of each operation to any other is taken into account. It may also be that certain routines such as 90/80 HSR and RPU routines which already occupy fixed locations will be used with the program. Such routines must be referenced in absolute notation only and the assembly system must be restricted from assigning any of the fixed locations.

Various methods of addressing that relate lines and operations or that restrict the generation of addresses may be used. In a general sense, these methods come under the headings of Instruction Addressing and Data Addressing.

- I. INSTRUCTION ADDRESSING

- A. Space Addressing

Space addressing relates two successive lines of coding. It cannot relate one line of coding with another line separated from it by any intervening coded lines.

When the a, m, or c address of an X-6 instruction is filled with spaces, these spaces will have one of several meanings:

Following any instruction code that requires an m and c address, spaces in these portions will be interpreted:

Portion

#### Meaning

- c The next instruction to be executed is in the next line of coding. Therefore, the address generated for and assigned to this c will be identical to the a address assigned to the next line.

- M A computer operation is to be performed on the word in the next line of coding; or, the next instruction to be executed is in the next line of coding. Therefore, this m will be identical to the a address assigned to the next line.

2. When an instruction code requires only an m or only a c address, the portion not used may be filled with spaces or any other characters without affecting the program.

When using space addressing, certain restrictions must be observed:

- Spaces cannot be used in both the m and c addresses of an instruction unless the instruction requires only an m or c address. If spaces are used when the instruction requires both an m and c address, the spaces in the m portion will be assumed to be in error and an error code will appear when the X-6 listing is printed out during assembly.

- 2. When an m or c address necessary to the instruction is space filled, the next line must contain spaces in the a address. If the a address in such a case does not contain spaces, it will be processed correctly but the line with spaces in the m or c address will not. When the X-6 listing is printed during assembly, an error code will be printed with the line containing the a address to indicate that the previous line must be recoded.

Examples of Space Addressing:

| a Op                   | o m            | с     | Remarks                                                                                                                                                                  |

|------------------------|----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\Delta\Delta 553$ LDA | ∆4211          |       | This c and the next a ad-<br>dress will be the same.                                                                                                                     |

| ΔΔΔΔΔ LDY              | ∆4216          |       | This c and the next a ad-<br>dress will be the same.                                                                                                                     |

| AAAA CTN               | ΩΔΔΔΔ          |       | This m is ignored; this c<br>and the next a address will<br>be the same.                                                                                                 |

| ΔΔΛΛΔΔ LDA             |                | ∆4211 | This m and the next a ad-                                                                                                                                                |

|                        | 00000          | ∆0001 | dress will be the same;<br>the contents of the mext<br>coded line will be loaded<br>in rA. The next instruc-<br>tion is in the coded line<br>with 4211 in the a address. |

| ∆42 <b>11</b> STA      | ∆42 <b>1</b> 5 |       | The contents of rA will be<br>stored in 4215. This c and<br>the next a address will be<br>the same.                                                                      |

| а | Op  | m | с     | Remarks                                                                                                                                                                                                                                                                                               |

|---|-----|---|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | JMP |   |       | This c is ignored; this m<br>and the next a address will<br>be the same.                                                                                                                                                                                                                              |

|   | TEQ |   | ∆4630 | This m and the next a ad-<br>dress will be the same.<br>When the assembled program<br>is used, if the result of<br>the test is equality, the<br>next instruction will be<br>at the address generated<br>for the m address; if in-<br>equality, the next instruc-<br>tion will be at location<br>4630. |

## B. Tag Addressing

A tag is a symbolic address that relates one non-successive line of coding with another and may be either a temporary or permanent tag. It may be used for an entrance to or an exit from common subroutines, to transfer control to a common line at the end of a branching chain of instructions, to transfer from one operation to another, or to reference lines that may be modified.

A temporary tag refers only to lines within the same operation in which it occurs. When a tag is referenced by more than one operation (that is, when it is referenced by lines within other operations than the one in which it occurs) it is a permanent tag.

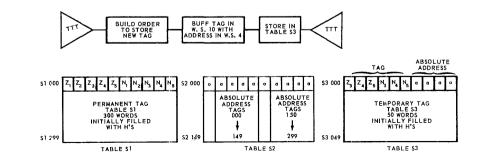

To conserve the memory space used during an X-6 assembly, a table is kept of each type of tag. The tag identifier and the address assigned to it are entered in the appropriate table. When an operation has been processed, the temporary tag table is erased so that the temporary tags of the next operation to be assembled may be stored in those same table locations. The permanent tag table is not erased (thus permitting communication between operations).

1. Permanent Tags

A permanent tag is coded by using all five digits of the X-6 symbolic address:

Digits

12345

Symbolic Address PPPPm

- PPPP (Digits 1-4) identifies a permanent tag and may be composed of alphabetic and/or numeric characters. Since identification depends on the use of these digits (plus m), the first digit cannot be  $\Delta$  or 0.

- m (Digit 5) specifies the memory area the tagged line is to be assigned, or it may refer to an overflow or c+1 condition (see Overflow Addressing, below).

In either case, m must be one of the follow-ing:

- N for Normal Access memory assignment.

- F for Fast Access memory assignment.

- <u>O</u> or 'P for overflow condition.

When assigning permanent tags, the following should be observed:

- a. No more than 300 permanent tags can be used in each program.

- b. Permanent tags may be assigned to a specific memory location by the use of a Tag Equals Card, Card Type 3 (see Input Card Section, below).

- c. The identifier of the tag (digits 1-4) is arbitrary. It is recommended that a meaningful tag coding scheme be developed for each program. This may be found useful after assembling the X-6 Instruction Deck in checking the X-6 listings.

- d. An overflow line should be given a permanent tag if the overflow subroutines referenced are used by more than one operation.

Examples of Permanent Tag Coding:

| Coding                | Remarks                                                                                                                    |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| AAAAA LDA ASINF AAAAA | Loal rA with the line whose<br>a address is ASINF.                                                                         |

| AAAAA ADD KOO15 STINF | The constant in KOO15 is<br>added to the contents of<br>ASINF. Control is sent to<br>the line whose a address<br>is STINF. |

## Remarks

STINF STA ASINF A124F Restor

Restore ASINF; transfer to line A124F.

2. Temporary Tags

A Temporary Tag is coded by using three of the five digits of the X-6 symbolic address:

| Digits   |         | 12345 |

|----------|---------|-------|

| Symbolic | Address | ∆∆ttm |

- tt (Digits 3-4) identifies a temporary tag and may be composed of alphabetic and/or numeric characters. Digit 2 may also be used as part of the tag identifier; however, only digits 3-4 will be processed.

- m (Digit 5) specifies the memory area the tagged line is to be assigned, or it may refer to an overflow condition (see Overflow Addressing, below). In either case, m must be one of the following:

- N for Normal Access memory assignment.

- F for Fast Access memory assignment.

- O or P for overflow conditions.

When assigning temporary tags, the following should be observed:

- a. No more than 50 temporary tags can be used in each operation.

- b. It is not possible to assign absolute locations to temporary tags.

- c. The identifier of the tag (digits 3-4) is arbitrary. However, to make certain that no more than 50 temporary tags are assigned in any operation, it is recommended that such tags be coded by numbers 01 through 50.

- d. Temporary tags cannot be referenced within any operation except the one in which they occur.

Example of Temporary Tag Coding:

CodingRemarksAA11N LDA WOOO5 AAAAPage/Line counter to rA.AAAAA LDL KOO12 AAAAAConstant: 00 0000 0030AAAAA TEQ AA12N AAA8NAre they equal?AA12N CLA AAA8N AAAAAZeros into rA.AAA8N STA WOOO5 AAA1NZeros into Page/line<br/>counter; transfer to<br/>the beginning of this<br/>operation.

# C. Overflow Addressing

Overflow, a c+1 condition, can result from either an arithmetic operation or an abnormal condition in an input or output unit. In an arithmetic operation, it is caused by the generation of a quantity beyond the capacity of the register which is to receive it. In an input or output unit, it may be due to any of a number of mechanical conditions (HSP out of paper, RPU card jam, for example). In either case, the instruction to be executed in the program is determined by the addition of 1 to the c portion of the instruction in which the overflow condition occurred.

There are eight X-6 instruction codes that can result in overflow conditions: ADD, SUB, DIV, RCC, HCC, PRN, PFD, TBU. Whenever one of these codes is used, a subroutine should be coded that will handle the possible overflow condition. In X-6 coding, this is accomplished by the use of temporary or permanent tags with an <u>O</u> or P in the fifth digit position. The tag with the <u>O</u> is placed in the c address of the instruction in which overflow may occur. If there is no overflow, control will be sent to the line with the <u>O</u> tag in the a address portion. If overflow does occur, control will be sent to the line with the P tag in the a address portion. Thus, when the following instruction is assembled:

#### Coding

Remarks

Digits 12345 12345 12345 a Op m c  $\Delta\Delta\Delta\Delta\Delta$  DIV K $\Delta$ 295  $\Delta\Delta$ 180 If overflow does not occur, control is to go to tag  $\Delta\Delta$ 180.

If overflow does occur, control is to go to tag  $\Delta\Delta 1.8P$ .

The address assigned to tag  $\Delta\Delta 1\,8P$  will be equal to the address assigned to tag  $\Delta\Delta 1\,8\underline{O}$  plus 1.

When coding for overflow conditions, it should be observed:

- 1. Neither the <u>O</u> nor the P line has to follow the line from which the overflow may result.

- 2. If the subroutine coded to handle the overflow condition is common to more than one operation, a permanent tag must be used. If the subroutine is only entered from one operation, a temporary tag may be used. In either case, the tag must follow the correct format for its type (see Tag Addressing, above).

- 3. Overflow lines must be counted as part of the tag limits.

The  $\underline{0}$  and the P lines must each be counted once.

| Coding                                                               | Remarks                                                                                                  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| AAAAA LDA WOOO2 AAAAA                                                | Counter (original setting<br>99 9999 9975) to rA.                                                        |

| ΔΔΔΔΔ ADD K0109 ΔΔ42 <u>0</u>                                        | Update counter; if overflow,<br>go to a address 42P; if no<br>overflow, go to a address<br>42 <u>0</u> . |

| $\triangle 19$ N LDA KOOO6 $\triangle 20$ N                          |                                                                                                          |

| $\triangle 20$ N STA $\triangle \Delta 2$ 7N $\triangle \Delta 2$ 8N |                                                                                                          |

| ∆∆42 <u>0</u> STA W0002 ∆∆19N                                        | No overflow, store updated counter in WOOO2; go to a address $\Delta\Delta$ 19N.                         |

| ΔΔ42P LDA KO212 ΔΛΔΔΔ                                                | Reset counter (99 9999 9975<br>to rA).                                                                   |

| $\Delta\Delta\Delta\Delta\Delta$ STA WOOO2 $\Delta\Delta$ 22N        | Store reset counter in WOOO2; go to a address $\Delta\Delta$ 22N.                                        |

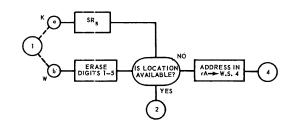

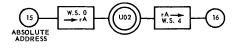

#### D. Absolute Addressing

When it is necessary in an operation to reference a fixed computer location or absolute address, it is coded by placing the specific numeric characters that designate that location in the X-6 symbolic address, digit positions 2-5. To refer to Fast Access memory location 4318, for example, the numbers 4318 would be placed in digit positions 2-5 of the appropriate X-6 symbolic address. Digit position 1 may be coded as a  $\Delta$  or 0. Thus, digit positions 2-5 when used for absolute

addressing must be in the range  $\Delta\Delta\Delta0$  (or 0000) through  $\Delta4999.^{1}$

An address coded in this manner will not be modified in any way. For example, if RPU04-8C01 is to be used with an X-6 coded program and it is necessary to enter the RPU04 Punch Section. The X-6 coded line that transfers control that section will contain the absolute address of the Punch Section entrance:

Coding Remarks 0p а m С 12345 12345 12345  $\triangle \triangle \triangle \triangle$  LDA  $\triangle \triangle 1$ N  $\triangle 3072$ Bring the contents of tagged line 1N to rA, and go to location 3072 for the next instruction to be executed. (3072 is the entrance to the Punch Section of RPU04-8C01. Control will be returned to the X-6 assembled program at the line placed in rA.) The c address could also have

been coded as 03072.

References to absolute addresses may be placed in the a, m, and c portions of an X-6 instruction.

To determine whether an address is absolute or not, during an X-6 assembly, a test is made to determine if the character in digit position 5 is alphabetic. If it is not, digit position 1 is checked. If this character is also not an alphabetic, the address is classed as an absolute address and is not modified in any way. If absolute addressing is to be used in a program, the specific locations must be restricted from assignment during the X-6 program assembly. This is done by specifying such locations, or even specific groups of locations (portions of the computer memory) on Restrict Cards, Card Type 2 (see Input Card Section, below).

E. Register Addressing

When it is necessary in an operation to address the contents of a register, the address is coded by using two of the five digits of the X-6 symbolic address:

<sup>&</sup>lt;sup>1</sup>If the absolute address OOOO is to be assigned, it should be noted that at least one digit must be a zero. The other digits positions may be coded as spaces.

Digit 12345 Symbolic Address △△ARi

R should be placed in digit position 4 though only digit 5 is processed.

i (Digit 5) must be:

A for register A. X for register X. L for register L.

The register contents should be added to the symbolic deck by use of a card with the register in the a address portion. This will allow the latency counter or Clock to be updated for correct address assignment of the next line to be assembled. For example:

Instruction Line

| а                                      | Оp  | m     | С                       | Remarks                                                                                                                         |

|----------------------------------------|-----|-------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| $\Delta\Delta\Delta\Delta\Delta\Delta$ | LDA | кооо5 |                         | Contains JMP ASINF                                                                                                              |

|                                        | ADD | K0012 | $\Delta\Delta\Delta RA$ | Add 00 0000 0010 to the con-<br>tents of rA and go to rA for<br>the next instruction. The next<br>instruction is in line ASINF. |

AAARA JMP ASINF AAA10

The card with rA in the a address portion will cause a print out on the listing. No corresponding output card will be produced.

## II. DATA ADDRESSING

X-6 coding provides four basic types of data addressing:

Working Storage Constants Table Entry Interlace

Working Storage and Constant addressing refer to data (or instructions treated as data). These are stored in locations related to the lines of the operations in which they are referenced but not to themselves. Table Entry and Interlace Addressing reference data stored in locations relative to themselves, the relation to their program references being of secondary importance.

.-5.+

#### A. Working Storage and Constant Addressing

Both constant and working storage data may be coded with spaces in the a symbolic addresses each time they are required by the program. Such coding would assure the best possible latency positions being assigned during an X-6 assembly. However, the data would have to be placed in a specific location for each reference and could not be referenced by any line of coding other than the line directly preceding it. When time alone is the prime consideration, this method can be used to advantage. The disadvantage, of course, is that more than one location is occupied by the same data word.

To conserve memory and assure at least minimal relative latency between a working storage or constant location and the lines of the operations that reference it, such data are assigned to pools. Working Storage data would be placed in the W-Storage pool and constant data in the K-Constant pool. When assigned to a pool, the addresses generated for a W-Storage or K-Constant by the X-6 Assembly System will depend upon the address assigned to the line in which it is first referenced. During the subsequent assembly process, the same address will be assigned whenever a particular W-Storage or K-Constant occurs.

To assure minimal relative latency to all the lines in which they are referenced, W-Storages and K-Constants will be assigned by the X-6 assembly system to the Fast Access memory until all such locations are exhausted. After that, they will be assigned to the normal access bands.

The most appropriate method of addressing W-Storages or K-Constants will depend upon the program to be assembled. Final determination will be made by considerations of program memory space and running time. Whatever the method, the decision must be made before the program is coded. For example, if the program flowchart indicates that the coding will take about a thousand lines, and computer running time is critical, space addressing would be the most logical method of coding. If the flowchart indicates that storage space may be critical, working storages and constants would be pooled, or a portion pooled (those most often referenced by various operations) and others space coded.

When data is placed in a pool, consideration should be given to when the first reference is to be made to it during the X-6 Assembly. For example, if an operation is to be executed repeatedly for each input item in a program, and working storage and/or constant data used in that operation is also referenced by other operations, the first references to the W-Storage and K-Constant data during the X-6 assembly should be made in the repeated operation. Thus, minimum latency would be obtained for the references in the repeated operation and minimal relative latency would be obtained for references in other operations by Fast Access memory assignment of the W-Storage and K-Constant data.

A maximum of 300 W-storages and 300 K-Constants are allowed in a program. Both W-Storage and K-Constant entries are addressed in X-6 coding by tags conforming to a particular format.

1. W-Storage and K-Constant Addressing

The W-Storage or K-Constant tag will most often occur in the m symbolic address portion of an X-6 instruction. When the contents of the W-Storage or K-Constant is given, the tag will occur in the a portion. If the contents should be an instruction to be performed, reference may be made in a c portion.

> Coding Digits 12345 Symbolic Address yOxxx

- y (Digit 1) Either W or K must be used in this location. W=W-Storage pool. K=K-Constant pool.

- O (Digit 2) This position is ignored during X-6 Assembly. It is usually coded with  $\triangle$  or O but may be any character.

- xxx (Digits 3-5) These must be a numeric in the range 000 to 299. Leading zeros may be coded as spaces (KAAA1=KAOO1). During X-6 assembly, these digits are extracted and used to form a table look up instruction when W and K tags are converted to absolute addresses.

When coding W-Storage or K-Constant addresses, the following should be observed:

- a. The order of addressing is not important. For example,  $\Delta 299$  may be referenced before  $\Delta 050$ .

- b. All 300 numbers for each type of tag do not have to be used in a program.

- c. An absolute address may be assigned to W-Storage or K-Constants by using a Tag Equals Card, Card Type 3 (see Input Card Section, below).

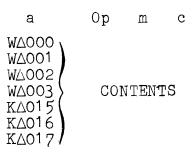

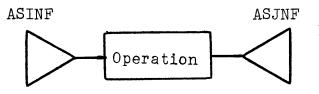

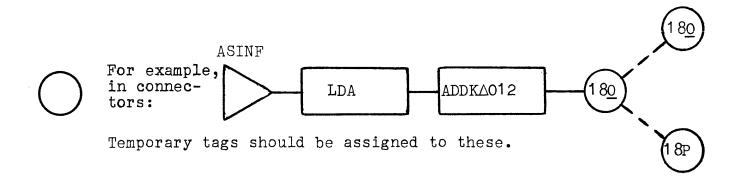

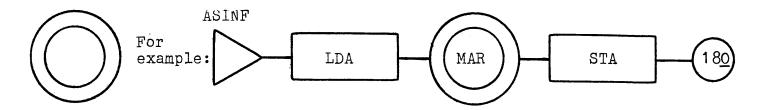

- 2. When the X-6 Symbolic deck is keypunched from the X-6 coding, for every W-Storage or K-Constant referenced in m or c addresses, there must be a card containing the W-Storage or K-Constant in the a address. For example, if in the coding there are m and/or c address references to W∆OOO through W∆OO3 and K∆O15 through K∆O17, the following cards must be part of the symbolic deck:

The contents of the constant addressed by the K-Constant tag will appear in the Op, m, and c address positions of the card. When W-Storage locations must be set to initial conditions, as with counters or limits, these initial conditions will be keypunched in the same manner as K-Constant contents. Whether the contents are for K-Constants or for W-Storages, they may be coded to be treated as absolutes, not to be modified in any way, or coded symbolically to be translated during the X-6 assembly.

3. If absolute coding is used, AAA must be placed in the Op portion. The ten digits that are placed in the m and c portions may be alphabetic, numeric, or any combination of the two. For example, the contents of the following would be treated as absolute:

a Op m c WAO74 AAA 99999 99975 KA284 AAA 00000 00000

In the case of data not to be translated into machine code, a Key of the card would also be punched. If, for example, the following K-Constants were to be used for punching and/or printing, the Key would be punched:

| а     | Key | Op                   | m     | с            |                                                              |

|-------|-----|----------------------|-------|--------------|--------------------------------------------------------------|

| K∆025 | U   | $\Delta\Delta\Delta$ | RUN01 | EDIT         | 2 part alphabetic, USS<br>90 Card code.<br>(U=Unprimed)      |

| к∆026 | Ρ   | $\Delta\Delta\Delta$ | RUNO1 | EDIT         | (P=Primed)                                                   |

| K0015 | U   | $\Delta\Delta\Delta$ | RUNO1 | EDIT         | 3 part alphabetic, USS<br>80 Card code.                      |

| к∆016 | Ρ   | ΔΔΔ                  | RUNO1 | EDITA        | (U=Unprimed)<br>(P=Primed)                                   |

| к∆017 | D   | $\Delta\Delta\Delta$ | RUNO1 | $EDIT\Delta$ | (D=Duoprimed)                                                |

| к∆050 | N   | $\Delta\Delta\Delta$ | RUNO1 | EDITA        | 2 part alphabetic, USS<br>80/90 machine code.<br>(N=Numeric) |

| K0051 | Z   | $\Delta\Delta\Delta$ | RUN01 | $EDIT\Delta$ | (Z=Zone)                                                     |

When X-6 symbolic coding is used, translation of the W-Storage or K-Constant data will be made during the X-6 assembly. The thirteen digit positions comprising the Op, m, c address portions must be used. For example, the contents of the following would be translated during assembly:

a Op m c KAOO8 LDA KAOO4 ASINF

The processing of W-Storage and K-Constant data is determine by the presence or absence of spaces ( $\Delta\Delta\Delta$ ) in the Op portion of the coding.

4. There are six non-numeric computer coded characters. The alphabetic designations for these are:

| 01 01 | Α |

|-------|---|

| 0110  | В |

| 0111  | С |

| 1101  | F |

| 1110  | G |

| 1111  | Н |

- 5. A  $\triangle$  or a 2 in the control column will indicate a positive or negative value (see INPUT CARD FORMAT, Card Type 8).

- 6. During the assembly of the symbolic deck, it is advantageous to group the cards containing W-Storage data together under the same operation name and the cards containing K-Constant data under another operation name (usually, WWW and KKK are the operation names used). By using such an assembly, desk checking and program testing of an X-6 assembled program is simplified: When it is necessary to check the contents of a referenced W-Storage or K-Constant, it is easier to find if the location in the deck is a known relative position.

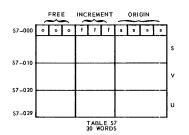

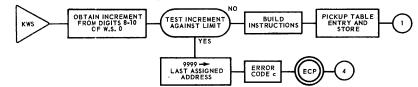

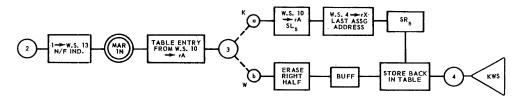

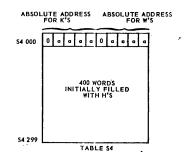

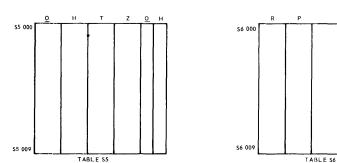

B. Table Entry Addressing

Digit

1. A table consists of data stored at regularly spaced intervals. The contents of any particular storage location in a table may be designated as an entry. Provision has been made in the X-6 Assembly System for as many as thirty tables of up to 1,000 words each in a program. A table entry reference will usually occur in the m symbolic address portion but may occur in the a or c portion. It is coded in the following manner:

#### Coding

12345

Symbolic Address tnxxx

- tn (Digits 1-2) is the identifier of the table referenced: t (Digit 1) must be either S, U, or V. Thus allowing 30 possible table names.

- n (Digit 2) must be a numeric in the range O through 9.

- xxx (Digits 3-5) is the identifier of the table entry and must be a numeric in the range OOO through 999.

Thus, S3000 would reference the first entry of table S3, V4898 would reference the 899th entry of table V4.

The order in which tables are referenced is not important (the first table might be V8, the second S1, the third U9, etc.).

2. When the number of tables that will be used in a program has been determined, each table must be described on a Type 5 Card (see Input Card Section, below). The coding on the Type 5 Card will define the location of the first table entry, the number of entries (000-999) in the table, and the desired interval between entries. When this card is processed by the X-6 Assembly System, all locations required by the table will be restricted from other assignment.

Care must be taken during the X-6 coding of a program not to reference an entry that is not in a particular table. That is, if the number of entries in a particular table was defined as 25 on the Type 5 Card, only 25 locations were restricted to that table. Should a reference be made to an entry greater than 25 for that table, it will not be detected as a logical error during the X-6 assembly.

U 1774.1

- C. Interlace Addressing

- Positions on the Input and Output Interlaces may be referenced as absolute addresses or in X-6 symbolic coding. When referenced symbolically, the coding, which may appear in the a, m, and c symbolic addresses, is:

Coding

| Digits   |         | 12345 |

|----------|---------|-------|

| Symbolic | address | inxyz |

- in (Digits 1-2) is the identifier of the interlace.

- i (Digit 1) specifies the I/O device and must be one of the following:

- H the read interlace of the HSR.

- R the read interlace of the RPU.

- $\underline{0}$  the punch interlace of the RPU.

- P the HSP interlace.

- $\frac{T}{Z}$  tape interlace.

- n (Digit 2) specifies the number of the interlace and must be a numeric in the range 0 through 9.

Thus, the combination of the alphabetic specifying and I/O device and the numeric of O through 9 allows ten possible identifiers for each I/O device. Since two alphabetics may be used to specify a tape interlace, 20 tape interlace identifiers are possible. A program requiring the use of alternate input bands could be coded throughout with symbolic addresses. Alternate Cards, Type 4 (see Input Card Section, below) would be used to redefine each band.

- xyz (Digits 3-5) depends upon the action desired by the reference.

- 2. To refer to an entire hand:

- a. xy (Digits 3-4) must be OO when reference is made to an entire band of the HSR or RPU.

- z (Digit 5) must be 0 if the contents of the band are not to be automatically translated; 1 if the contents of the band are to be automatically translated.

(For example, HBU H1000 would dump the HSR buffer into the first and second read interlace positions without automatic translation. For automatic translation, the instruction HBU H1001 would be used.) b. When a reference is made to a complete HSP interlace band:

x (Digit 3) must be 0.

yz (Digits 4-5) will specify a number of lines and must be a numeric in the range OO through 79.

(Thus, PRN POOOO would advance the paper zero lines before printing.

PRN PO030 would advance the paper thirty lines before printing.)

- c. When an entire tape interlace is referenced, as in read and write instructions:

- x (Digit 3) refers to the Uniservo number and must be a numeric in the range 0-9.

- y (Digit 4) refers to mode and density and must be:

- O for USS, 250 cpi.

- 5 for UNIVAC, 250 cpi.

- 6 for UNIVAC, 125 cpi (used only with write instructions).

- z (Digit 5), used only with read instructions, refers to direction and gain and must be:

- O forward normal.

- 1 forward low.

- 2 forward high.

- 5 backward normal.

- 6 backward low.

- 7 backward high.

When reference is to be made to a particular word of an interlace band, the above coding cannot be used.

- 3. To refer to a particular word of an interlace band:

- a.x (Digit 3) relates to the translation mode and must be one of the following:

- (1) For untranslated (Card Code) words of a band:

U=Unprimed. P=Primed. D=Duoprimed (applicable USS 80 only.) (2) For the HSP Interlace and for translated (Machine Code) words:

- b. yz (Digits 4-5) relate to the word in the interlace band. The coding varies for each I/O device:

- (1) HSR and RPU Read Stations:

- y (Digit 4) means the read station and must be 1 or 2.

- z (Digit 5) means one of the eight words and must be a numeric in the range 0 through 7.

- Thus, N11 specifies the numeric portion of the second word at the first read station.

- Z20 would specify the zone portion of the first word at the second read station.

- U25 would specify the unprimed portion of the sixth word at the second read station.

- (2) RPU Punch Interlace:

y (Digit 4) must be 1.

- z (Digit 5) indicates the word and must be a numeric in the range of 0 through 7.

- Thus, U13 specifies the unprimed portion of the fourth word of the punch interlace.

- Z10 would specify the zone portion of the first word of the punch interlace.

- (3) HSP Interlace:

- yz (Digits 4-5) must be a numeric in the range O1 through 13.

- Thus, N12 would specify the numeric portion of the twelfth word of the HSP interlace.

- (4) Tape Interlace:

$\mathbf{x} = \mathbf{N} \text{ or } \mathbf{Z}$

yz (Digits 4-5) when referring to a word of a tape interlace must be a numeric: in the range 00-71 of an interlace in XS-3 Code, in the range 00-99 of an interlace in USS Code.

N=Numeric Z=zone.

- 4. As examples of interlace addressing from the foregoing:

- H1Z10 HSR interlace #1, the zone portion of word zero at the first read station. H1Z20 would be the same word at the second read station.

- P1N13 Printer interlace #1, numeric portion of word 13. P1Z13 would be the same word, zone portion.

- T9Z11 The ninth tape interlace, zone portion of word 11. (TRD∆∆800 would be, read one block from tape buffer band using Servo 8, USS mode, forward normal).

# LATENCY MINIMIZATION

Latency minimization during a program or an operation assembly is achieved through use of a working storage location called a "Clock" in which the X-6 Assembly System stores the relative band level location. The value or setting of the clock is initially 00 0000 0000. At any subsequent time, the setting will always lie within the range 00 0000 0000 through 00 0000 0199. When an instruction line is analyzed by the X-6 Assembly System, the clock reading is used to obtain the tentative best address (TBA) for the next address to be assigned. The TBA is generated and assigned by using the value of the clock setting, incrementing the setting by the specific word increments associated with each instruction code, or by assigning a new setting to the clock and then incrementing the value of the new setting (these increments can be found in the Instruction Code Information Words Table, below). After the TBA is obtained, the available memory locations are searched. If a band location equivalent to the relative band level of the TBA is found, it is assigned. If no such band location is found, the TBA is incremented and another search is made. This process continues until an assignment is possible. When it is not possible to make an assignment because the memory is full, an arbitrary assignment to 9999 is made and the assembly continues. A printout indicating such an assignment is made in the listing. After an address assignment has been made, the absolute address is reduced to a relative band level value and is stored in the Clock.

# INSTRUCTION CODE INFORMATION WORDS TABLE

If control column indicates Index Register modification, add one more word time before m.

|                                                                                                | Digits<br>1-2                                            | Digit 3<br>Action<br>Code                 | Digits<br>5-7<br>Before m                                          | Digits<br>8-10<br>Before                                                                              | с                                                                           |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| ADD<br>BUF<br>DIV<br>ERS<br>LDA<br>LDL<br>LDX<br>MUL<br>STA<br>STL<br>STX<br>SUB<br>LIR<br>IIR | 700555055005527<br>208656700<br>005527                   | 000000000000000000000000000000000000000   | 002<br>002<br>002<br>002<br>002<br>002<br>002<br>002<br>002<br>002 | 003<br>002<br>113<br>002<br>002<br>002<br>103<br>002<br>002<br>002<br>002<br>002<br>003<br>003<br>004 |                                                                             |

| TRD<br>TWR<br>TRW<br>TMX<br>TXM<br>ATL<br>CTM<br>MTC<br>ZUP<br>HSS<br>RSS                      | G2<br>H2<br>C1<br>C3<br>77<br>12<br>17<br>627<br>57      | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>00  | 017<br>017<br>150<br>003<br>003<br>003<br>003<br>003<br>004<br>003<br>003                             |                                                                             |

| CLA<br>CLL<br>JMP<br>CAA<br>CAX<br>CTA<br>PFD<br>SHL<br>SHR                                    | 26<br>31<br>06<br>00<br>36<br>86<br>23<br>16<br>37<br>32 | 222222                                    | 003<br>003<br>002<br>003<br>014<br>002<br>003<br>222<br>111<br>111 | 000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>00                                     | 222 is a code not affect-<br>ting timing; 111 means use<br>amount of shift. |

|                                                                                                | Digits<br>1-2                                                                                            | Digit 3<br>Action<br>Code | Digits<br>5-7<br>Before m                                                                                    | Digits<br>8-10<br>Before c                                                                                 |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| HBU<br>PRN<br>RBU<br>TBU<br>TBL<br>HBT<br>HCC<br>PBT<br>RBT<br>STP<br>TEQ<br>TGR<br>TBT<br>TST | 96<br>11<br>46<br>F6<br>42<br>727<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>27<br>2 | <u> </u>                  | 198<br>197<br>098<br>098<br>048<br>198<br>004<br>004<br>004<br>004<br>003<br>003<br>003<br>003<br>005<br>004 | 203<br>592<br>203<br>203<br>103<br>205<br>003<br>003<br>003<br>003<br>003<br>003<br>003<br>003<br>003<br>0 |

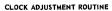

# CLOCK MODIFICATION

The purpose of the clock modification instructions is to allow relationships to be established between addresses when these relationships cannot be detected by the X-6 Assembly System. This is necessary because the X-6 Assembly System is a one pass program. Once an address has been assigned, therefore, it cannot be changed at any subsequent assembly point. Certain conditions may arise when the process by which the X-6 system assigns addresses will not result in the best latency from an overall program point of view. One example of this would be:

X-6 Coded Lines

X-6 Assembled Coding

Remarks

| a | Op  | m                        | с     |                                                                                                                      |

|---|-----|--------------------------|-------|----------------------------------------------------------------------------------------------------------------------|

|   | ΤEQ | $\Delta\Delta\Delta$ 1 N | ΔΔΔΔΔ | The address for temporary tag 1N                                                                                     |

|   | TGR | ∆∆∆1 N                   |       | would be assigned during the assem-<br>bly of the TEQ line. This address<br>would then be placed in the TGR<br>line. |

| 2145 82 2148 2348<br>2348 87 2148 2351 | Thus, if control is sent to 2348<br>by the equality test and then sent<br>to 2148 by the magnitude test, a<br>drum revolution would be lost. |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

In this case, it would be desirable to have the address assigned to 1N increased by the increment between the first reference to it in the TEQ line and the second reference to it in the TGR line so that the coding generated would be:

| X-6 Assembled                | Coding | Remarks                                                                                                                              |

|------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| 2145 82 2151<br>2348 87 2151 |        | The process by which this is accom-<br>plished will be found in the Examples<br>of Clock Modification at the end of<br>this section. |

The clock setting may be modified by any arbitrary increment, or the clock may be set to any arbitrary band relative reading. Such modification is programmed by the use of any of seven clock modification instructions. Each such instruction used is keypunched on a detail Card, Card Type 8 (see Input Card Section, below), and filed in the symbolic deck immediately preceding the instruction the new clock reading is to affect.<sup>1</sup> Each of the seven

<sup>&</sup>lt;sup>1</sup>Clock modification cards do not require a card number in columns 6-8. Thus, they may be inserted at any time without breaking the detail card sequence and causing an entire operation to be renumbered.

clock modification instructions must have CLOCK in the a symbolic address portion of the coding.

The clock modifications may be divided into two basic types:

- SE (Set) in which a new setting of the Clock is made before incrementation by a specified number of word times. An SE in-struction may only directly modify one address in the suceeding instruction.

- AD (Add) in which a specified increment is added to the normal band relative address which the X-6 Assembly System would normally assign. An AD instruction may directly modify two addresses in the succeeding instruction.

The clock modifications and their format are as follows:

A.  $\Delta \Delta \Delta$  Instruction:

Remarks

| а     | qO | m     | с     | remarks                       |    |

|-------|----|-------|-------|-------------------------------|----|

| CLOCK |    | SSSSS | 00xxx | The succeeding a address will | be |

|       |    |       |       | modified:                     |    |

- sssss must be a legitimate X-6 symbolic address or an absolute memory location. This address will be converted to a band relative reading and placed in the clock.2

- xxx must be a numeric increment to be added to the new clock setting in addition to the normal incrementation. The result of this addition will be the TBA for the assignment of the succeeding a address.<sup>3</sup>

<sup>2</sup>If sssss is an X-6 symbolic address that has not already been processed, it will be assigned a permanent address when the clock modification instruction line is processed. Thus, it would be assigned in minimal latency to the line just preceding the clock modification in the assembly process. If this happens, it could result in a loss of word times when the object program instruction line that first references sssss is assembled.

<sup>3</sup>The word time increment of the clock modification instructions is always added to the clock setting. Since the clock setting will always lie within the range 000-199, the setting may, in effect, be decremented by subtracting the desired decrement from 200 and using the result as the specified increment.

This is the only clock modification that does not contain a mnemonic code in the Op portion of the instruction. The same modification may be accomplished by use of the SEA instruction (see below). It is also the only clock modification instruction that does not allow the clock to be reset to its premodification setting after the succeeding desired address portion has been assigned according to the modified clock setting.

B. SE Instructions:

For each of the succeeding SE instructions, the format of the a, m, and c address is the same:

1. The a address portion must always be:

a CLOCK

2. The m address must always contain:

m

xxx0z

- xxx = The numeric increment to be added to the new clock reading that will be specified in the c portion of this instruction in addition to the normal incrementation. The new clock reading plus the increment will result in the TBA for the address to be assigned. (Spaces, Δ, cannot be used in place of zeros.)

- z = 0 if the clock setting is <u>not</u> to be restored to its premodification setting before obtaining the TBA for the address succeeding the address to be modified.

- z = 1 if the clock setting is to be reset to the premodification setting before obtaining the TBA for the address succeeding the address specified to be modified.

| 4. | The mnemonic SE inst | tructions and their format are:                                                                                                                                                                                                                                                                                                                                                                               |

|----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | CLOCK SEA xxxOz sss  | The succeeding a address TBA<br>will be arrived at by using the<br>band relative equivalent of<br>sssss plus the increment xxx.<br>The presence of O or 1 in the z<br>digit position will determine<br>whether the clock will be re-<br>stored to its original setting<br>when this modification has been<br>accomplished or if the clock<br>setting that results from this<br>modification will be retained. |

|    | CLOCK SEM xxxOz sss  | ss The succeeding m address TBA<br>will be arrived at by the above<br>process.                                                                                                                                                                                                                                                                                                                                |

|    | CLOCK SEC xxxOz sss  | The succeeding c address TBA will be arrived at by the above process.                                                                                                                                                                                                                                                                                                                                         |

- C. AD Instructions:

- 1. The a address portion must always be:

a CLOCK

- 2. The m and c address portions must always contain: m c

- xxx0 00yyy yy = The numeric increment to be added to the present clock reading, in addition to the normal incrementation, to arrive at the TBA to be assigned to the next address specified in the operation code of the AD instruction.

- xxx = The numeric increment to be added to the clock reading according to the numeral in the z digit. This addition is used to obtain the TBA for the address to be assigned after the address called for in the operation code of the AD instruction. If xxx=000, the address generated will be derived normally from the clock reading determined by the z digit.

(Space,  $\Delta$ , cannot be used in place of zeros in the xxx and yyy portions.)

- z = 0 if the clock setting is not to be restored to its pre yyy reading before incrementing by xxx.

- z = 1 if the clock setting is to be restored to its pre yyy mo- dification before incrementing by xxx.

- 3. The AD instruction Codes, and their format, are: CLOCK ADA xxxOz OOyyy address will be arrived at by adding yyy to the clock reading. The succeeding m address will be arrived at by incrementing the new clock reading, if z=0; or, if z=1, by restoring the pre yyy incrementation clock reading before incrementing by xxx. The succeeding a address will be assigned normally.

- CLOCK ADM xxxOz OOyyy The succeeding m and c addresses will be arrived at by the above process.

- CLOCK ADC xxxOz OOyyy The succeeding a and m addresses will be assigned normally. The succeeding c and the a address following it will be arrived at by the above process.

- 4. When an absolute address on the Fast Access bands is specified in a clock modification instruction, the Fast Access address is reduced to a number in the range OO through 49. This is placed in the clock in the form OOO through 049. Thus, if no further incrementation is specified, the absolute address derived from this reading will have to be on an even band level on the Normal Access bands. An odd numbered band assignment on the Normal Access bands is only possible when the clock seting, plus increment if called for, is in the range 100 through 199.

- D. Examples of Clock Modification

The following examples of the use of the clock modification instruction are not intended to illustrate every possible condition that may arise. The application of these instructions will depend entirely on the nature of the object program to be assembled.

U 1774.1

1. In the beginning of this section, the following example was given:

| <b>X-</b> 6 | Symbol           | ic C           | oding | X-6 Assembled Coding                                      |

|-------------|------------------|----------------|-------|-----------------------------------------------------------|

| a           | Op<br>TEQ<br>TGR | $1 \mathrm{N}$ | C     | a Op <b>m c</b><br>2145 82 2148 2348<br>2348 87 2148 2351 |