# UNISYS

# BT 3200 Series 324X/326X/328X Magnetic Tape Unit

Theory of Operation Manual

**Class B Document** Customer Services Engineering Restricted/Proprietary Data

September 1988 CE Dist. Code DQ Library Binder Number 17/4 5024599

### Customer Services Engineering Restricted and Proprietary Data

The information contained in this document is restricted and proprietary to Unisys Corporation. Neither the information nor this document is to be reproduced, shown, or disclosed outside Unisys Corporation without prior written permission of the Law department, Unisys Corporation.

The information or this document is furnished solely for use by Unisys Customer Services Engineering personnel in servicing customer's equipment and is left at the customer's site for their convenience.

# This document is the property of and shall be returned to Unisys Corporation, One Unisys Place, Detroit, Michigan, 48232, US America

Correspondence regarding this publication should be forwarded to Unisys Corporation either by using the Business Reply Mail form at the back of this manual or by addressing remarks directly to Commercial Product Information, P.O. Box 500, Blue Bell, PA 19424 U.S.A.

Reproduced with the permission of FUJITSU LIMITED Copyright<sup>©</sup> 1982, 1984, 1986, 1988 All Rights Reserved.

Fujitsu Document Code No.: 44FH3019E-04

| EDITION RECORD                |            |                       |  |  |  |  |

|-------------------------------|------------|-----------------------|--|--|--|--|

| Edition Date Revised Contents |            |                       |  |  |  |  |

| 04                            | Mar., 1987 | All pages are revised |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

|                               |            |                       |  |  |  |  |

Model Number Cross Reference Table

UNISYS Model No.

(

$\bigcirc$

Description Model No.

| 3241 | F617A1  |

|------|---------|

| 3242 | F617A2  |

| 3244 | F617B   |

| 3243 | F617E   |

|      |         |

| 3261 | F618A1  |

| 3262 | F618A2  |

| 3266 | F618B   |

| 3265 | F618E   |

|      |         |

| 3281 | M2436-1 |

| 3282 | M2436-2 |

| 3288 | M2436-8 |

|      |         |

#### CONTENTS

|         |             | р                                                               | age   |

|---------|-------------|-----------------------------------------------------------------|-------|

| CHAPTER | 1           | GENERAL DESCRIPTION OF THE MAGNETIC TAPE UNIT                   | -     |

| ond Lak | 1.1         | Introduction                                                    |       |

|         | 1.2         | Operational Performance                                         |       |

|         | 1.3         | External Features                                               |       |

|         | 1.4         | Service Clearances                                              |       |

|         | 1.5         | Interconnectors                                                 | 1-7   |

|         | 1.6         | MTU Shorting Pluges                                             | 1-8   |

|         |             |                                                                 |       |

| CHAPTER | 2           | MECHANICAL OPERATION                                            |       |

|         | 2.1         | Mechanical Features                                             |       |

|         | 2.1.1       | Tape path                                                       |       |

|         | 2.1.2       | Autoload mechanism                                              |       |

|         | 2.1.3       | Auto hub                                                        |       |

|         | 2.1.4       | Head assembly                                                   |       |

|         | 2.1.5       | Capstan                                                         |       |

|         | 2.1.6       | File protection mechanism                                       |       |

|         | 2.1.7       | Photo sense block                                               |       |

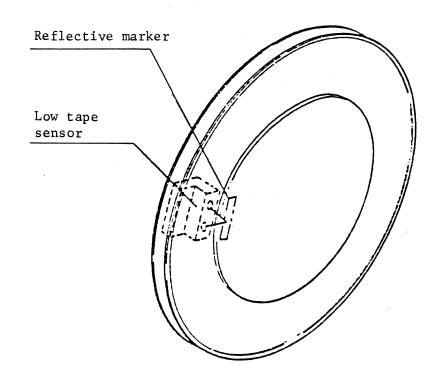

|         | 2.1.8       | Low-tape sensor                                                 |       |

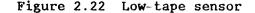

|         | 2.1.9       | Autocleaner                                                     |       |

|         |             | Error marker                                                    |       |

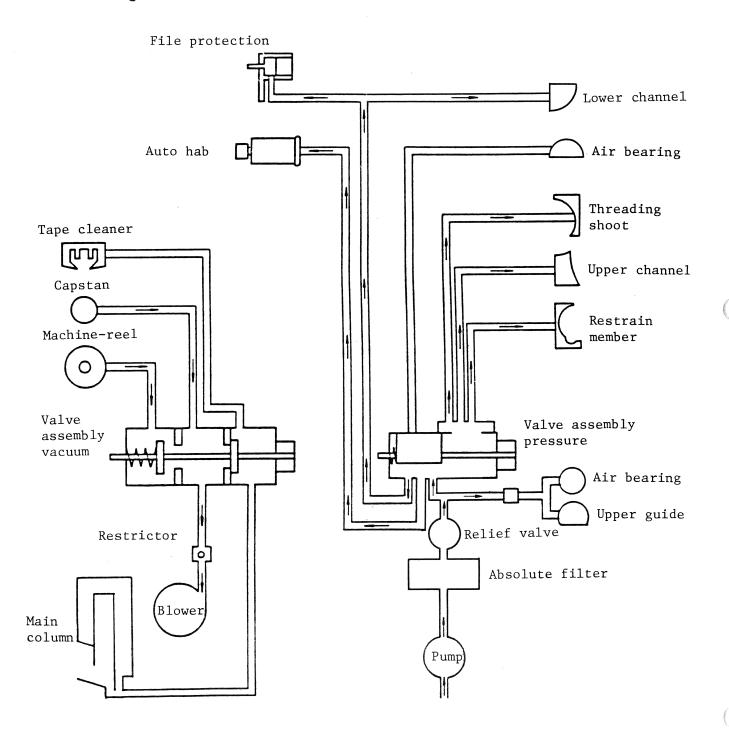

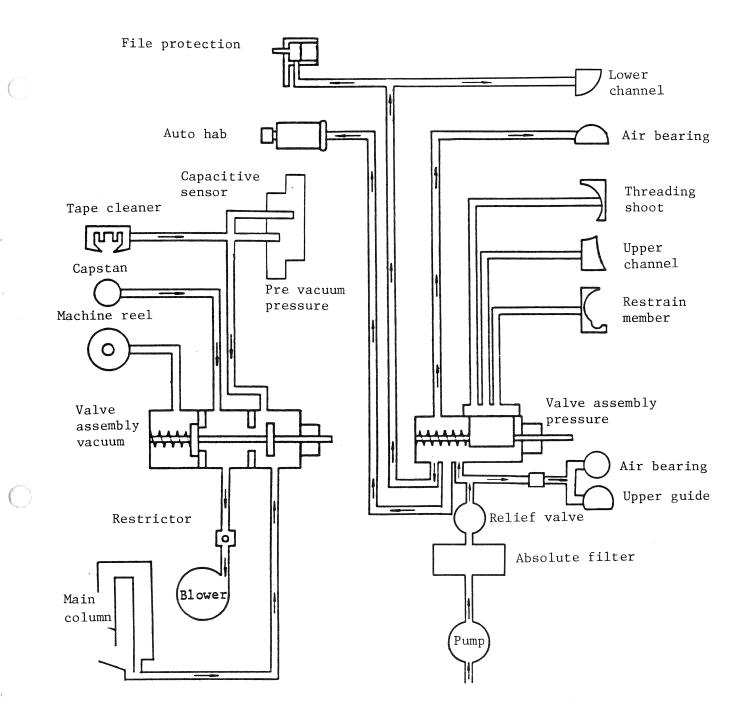

|         | 2.2         | Air Supply System                                               | 2-24  |

| CHAPTER | 2           | CIRCUIT OPERATION                                               | 2 1   |

| CHAPIER | 3.1         | Overall Circuit Configuration                                   |       |

|         | 3.2         | Operator Panel                                                  |       |

|         | 3.3         | MTC Interface                                                   |       |

|         | 3.3.1       | Connecting cable                                                |       |

|         | 3.3.2       | Interface signal lines                                          |       |

|         | 3.3.3       | Tag line control                                                |       |

|         | 3.4         | Control Circuit of the MTU                                      |       |

|         | 3.4.1       | Introduction                                                    |       |

|         | 3.4.2       | Logical Operation of the Control Circuit                        |       |

|         | 3.4.3       | Microcommands                                                   |       |

|         | 3.4.4       | Register files and test signals                                 | 3-53  |

|         | 3.4.5       | The executing microprogram                                      |       |

|         | 3.5         | Maintenance Functions                                           | 3-83  |

|         | 3.5.1       | The maintenance panel structure                                 |       |

|         | 3.5.2       | Device maintenance function                                     |       |

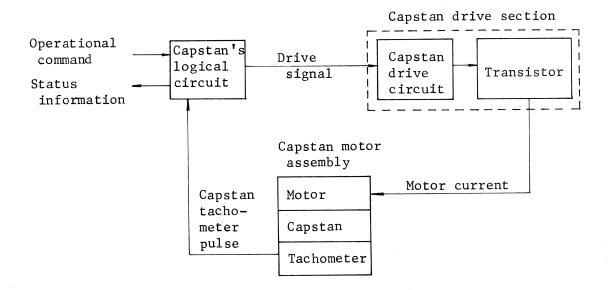

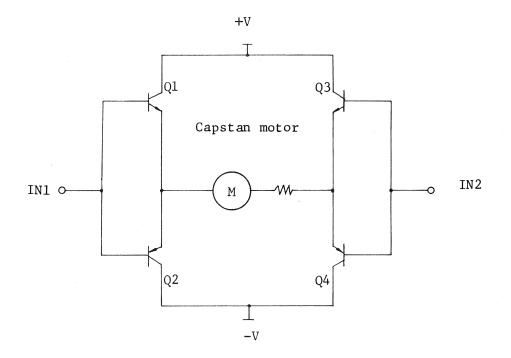

|         | 3.6         | Capstan Control Circuit                                         |       |

|         | 3.6.1       | Introduction                                                    |       |

|         | 3.6.2       | Capstan motor assembly                                          |       |

|         | 3.6.3       | Logical circuit                                                 |       |

|         | 3.6.4       | Operation of the servo system                                   | 3-105 |

|         | 3.6.5       | Capstan drive circuit                                           | 3-115 |

|         | 3.7         | Reel Control Circuit                                            |       |

|         | 3.7.1 3.7.2 | Reel motor and tape-loop detection                              |       |

|         | 3.7.2       | Operation of the reel motor drive circuit<br>Write/Read circuit |       |

|         | 3.8.1       | Write/Read operation                                            |       |

|         | 3.8.2       | Interface circuit                                               |       |

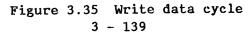

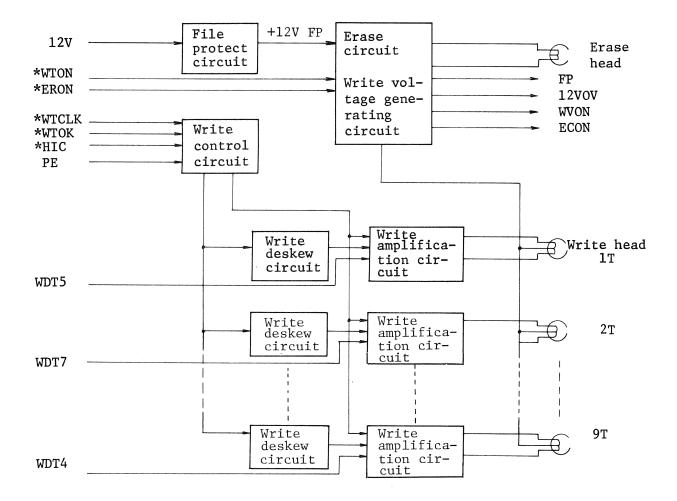

|         | 3.8.3       | Write circuit for the 6250/1600 BPI MTU                         |       |

|         | 3.8.4       | Write circuit for the 1600/800 BPI MTU                          |       |

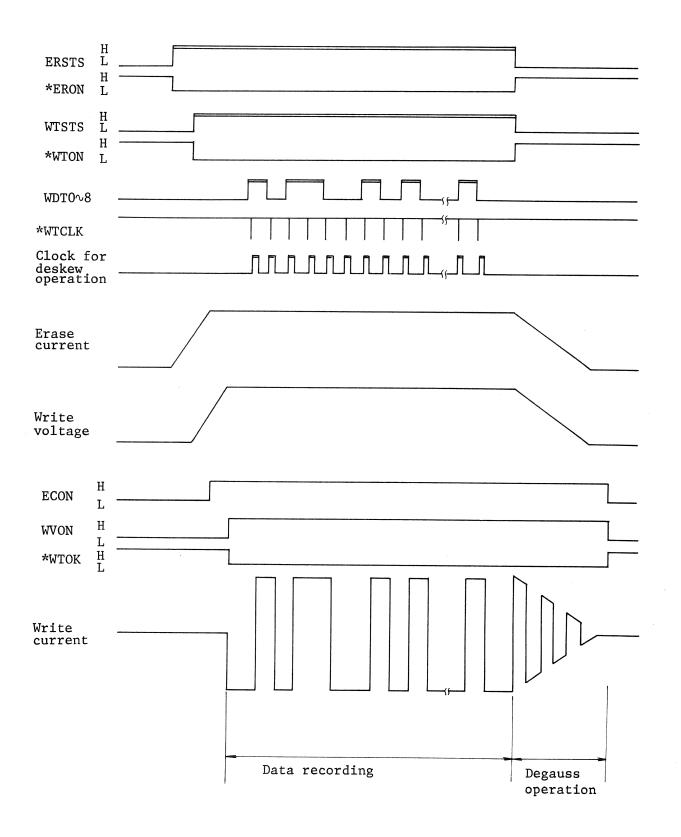

|         | 3.8.5       | Read circuit for the 6250/1600 BPI MTU                          |       |

|         | 3.8.6       | Read circuit for the 1600/800 BPI MTU                           |       |

|         |             |                                                                 |       |

|         | 3.9<br>3.01 | Circuits for Mechanical Parts and Stabilizing<br>Introduction | 3-156 |

|---------|-------------|---------------------------------------------------------------|-------|

|         | 2.2.1       |                                                               | 3-156 |

|         | 3.9.2       | Components                                                    | 3-156 |

|         | 3.9.3       | Circuit operation                                             | 3–158 |

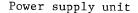

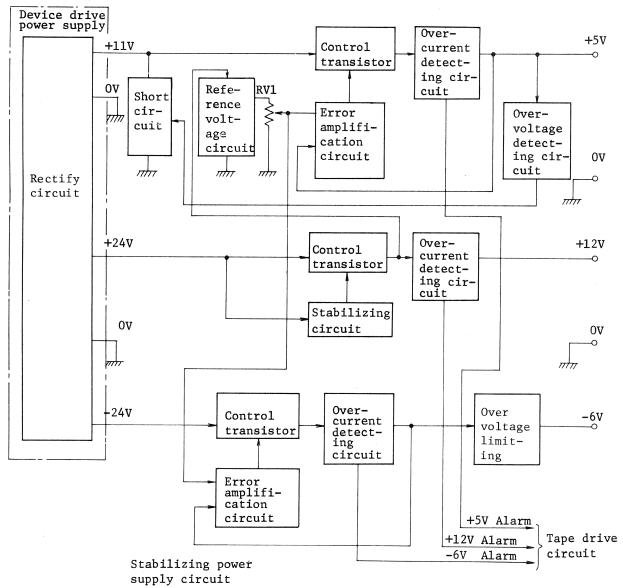

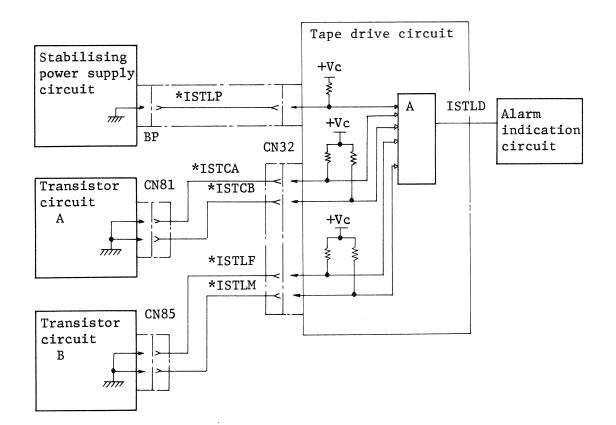

| CHAPTER | •           | POWER SUPPLY                                                  | 4-1   |

|         | 4.1         | Introduction                                                  | 4-1   |

|         | 4.2         | Functions                                                     | 4-1   |

|         | 4.3         | Power Supply Front Panel                                      | 4-4   |

APPENDIX A LIST OF SIGNALS USED IN LOGICAL CIRCUITS

#### 1.1 Introduction

The 324X/326X/328T magnetic tape unit (MTU) is connected to the host controller via the magnetic tape controller (MTC). Data is recorded and read back using magnetic tape as the storage medium.

The MTU consists of the magnetic tape feeding mechanism, autoload mechanism, record/read-back mechanism, and control circuits. Because the tape-drive mechanism uses a single capstan system driven by a DC motor, the oxide coating surface of the magnetic tape loaded in the tape feeding mechanism touches only the read/write head, the cleaning ribbon, and the tape cleaner blades, thereby achieving high reliability. The auto-hub mechanism makes it easy to mount and remove tape reels; the power window automates the window opening and closing, and the autocleaner reduces operator tasks.

The magnetic head uses a two-gap head to perform instantaneous read-in of written data and to check data. The system uses 9 tracks. Available recording densities are 6250 BPI, 1600 BPI, and 800 BPI, in recording modes of group coded recording (GCR), phase encoded recording (PE), and nonreturn to zero change at "1" (NRZI).

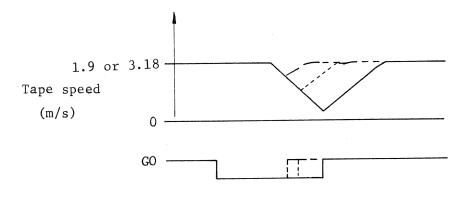

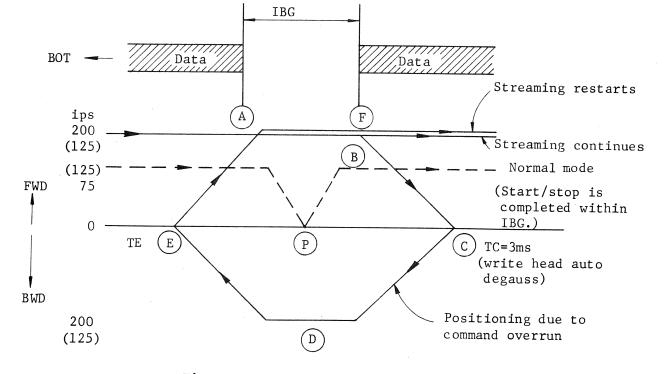

The normal tape speed of the equipment is 75 ips for 324X, and is 125 ips for 326X. These speeds can be increased to 125 ips and 200 ips, respectively, by a streaming function command. The tape speed of 328T is 200 ips.

### 1.2 Operational Performance

# Table 1.1 lists the operational performance of each model.

|                                                          |                        |                |                      |          | -                    |                      |                      |  |

|----------------------------------------------------------|------------------------|----------------|----------------------|----------|----------------------|----------------------|----------------------|--|

| Model<br>Items                                           |                        |                | 3241<br>3242<br>3244 | 3243     | 3261<br>3262<br>3266 | 3265                 | 3281<br>3282<br>3288 |  |

| Density (BP)                                             | I)                     |                | 6250/1600            | 1600/800 | 6250/1600            | 1600/800             | 6250/1600            |  |

| Recording method                                         |                        |                | GCR/PE               | PE/NRZI  | GCR/PE               | PE/NRZI              | GCR/PE               |  |

| Data<br>transfer<br>rate                                 | Normal<br>(start/stop) |                | 469/120              | 120/60   | 781/200              | 200/100              | 1250/320             |  |

| (Kb/sec)                                                 | Streaming              |                | 781/200              | 2001 –   | 1250/320             | 320/ -               | _                    |  |

| Access<br>time (ms)                                      | Read                   | Normal         | 2.6/4.0              | 4.0/4.0  | 1.6/2.6              | 2.6/2.6              | 1.7/2.3              |  |

|                                                          |                        | Stream-<br>ing | 6.9/6.9              | 6.9/ -   | 4.5/4.5              | 4.5/ -               |                      |  |

|                                                          | Write                  | Normal         | 2.3/3.0              | 3.0/3.0  | 1.5/2.0              | 2.0/2.0              | 1.6/1.9              |  |

|                                                          |                        | Stream-<br>ing | 5.7/5.7              | 5.7/     | 3.7/3.7              | 3.7/ -               | _                    |  |

| Positioning<br>time (ms)                                 | Read                   |                | 12.3                 |          | 9.5                  |                      | -                    |  |

|                                                          | Write                  |                | 22.9                 |          | 17.3                 |                      |                      |  |

| Inter-block gap (IBG)<br>length (inches)                 |                        | 0.3/0.6        | 0.6/0.6              | 03./0.6  | 0.6/0.6              | 0.4(W)<br>0.3(R)/0.6 |                      |  |

| Tape speed                                               | Normal                 |                | 75                   |          | 125                  |                      | 200                  |  |

| (IPS)                                                    | Streaming              |                | 125                  |          | 200                  |                      | -                    |  |

| Number of tracks                                         |                        |                | 9                    |          |                      |                      |                      |  |

| Rewind time<br>reel nomina                               |                        |                | 55                   |          |                      |                      | 69                   |  |

| Rewind/unload time<br>(2400 feet reel, nominal)<br>(sec) |                        |                | 65                   |          |                      |                      | 79                   |  |

| Autoloading time (sec)                                   |                        |                | 12 12                |          |                      |                      | 12                   |  |

# Table 1.1 MTU specifications

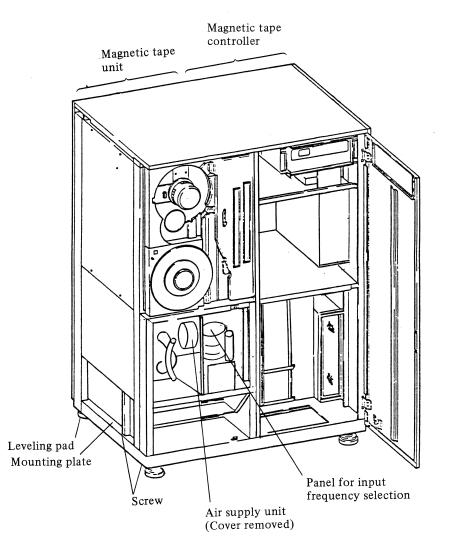

#### 1.3 External Features

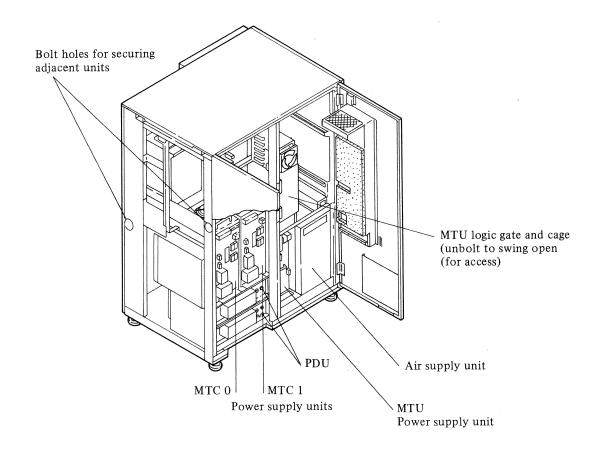

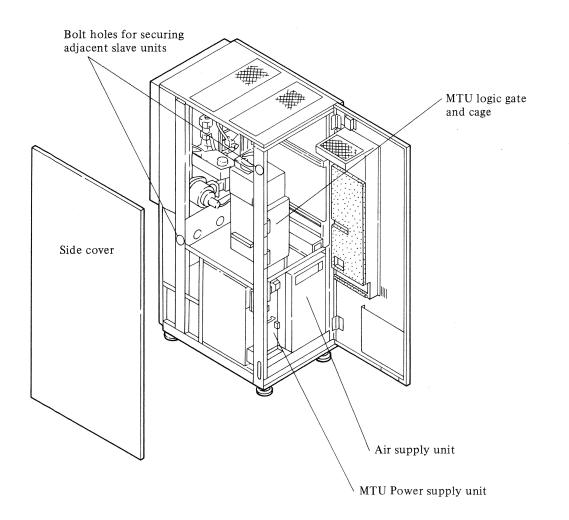

This magnetic tape subsystem (MTS) master unit consists of an MTU and either one or two MTCs housed in a single cabinet. Figure 1.1 is a front view of the master unit, showing the MTU on the left and the MTC on the right. Figure 1.2 is a rear view of the master unit, showing the location of the MTU and MTC power supply units and the MTU logic gate. Figure 1.3 shows the rear view of the MTU slave unit. A slave unit contains no MTC.

Figure 1.1 Master unit (front view)

Figure 1.2 Master unit (rear view)

$\bigcirc$

( )

Ŷ

Figure 1.3 Slave unit (rear view)

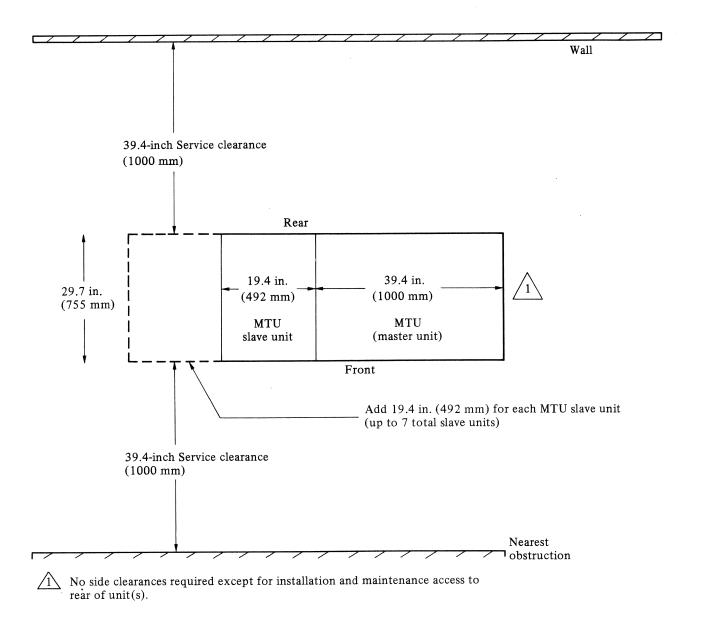

#### 1.4 Service Clearances

Clearances required for servicing the magnetic tape unit are shown in Figure 1.4.

Figure 1.4 Service clearances

#### 1.5 Interconnectors

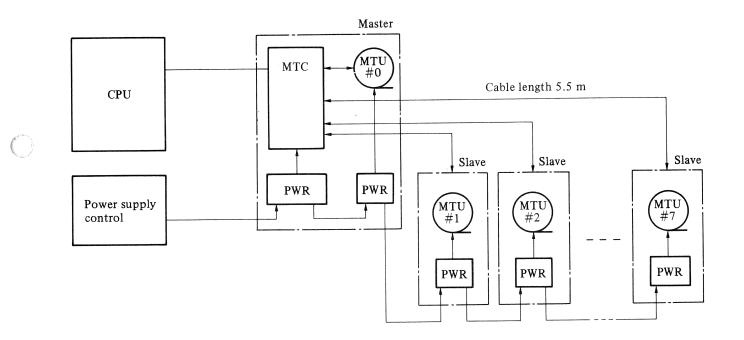

The MTUs are connected to the host/controller via the MTC, as shown in Figure 1.5. The interface between the MTC and the MTU is the distribution PCA. One MTC can control up to 8 MTUs.

The master unit is available in two models, one MTC model (3241, 3242, and 3261) and two MTC model (3242, 3242, and 3262). Two MTC model is applicable for device crosscall.

Figure 1.5 MTU interconnections

#### 1.6 MTU Shorting Plugs

Shorting plug settings for the MTU are shown below. Refer to the Maintenance Manual when checking or setting the short circuits.

| PCA<br>package                                                                                                          | Specification           | Strap<br>mounting<br>position | Pins to be<br>strapped           |                                  | Remarks                                                        |                                                                 |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------------|----------------------------------|----------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|

|                                                                                                                         |                         | postcion                      | "0"                              | "1"                              |                                                                |                                                                 |

| C16B-5121-<br>0820#U                                                                                                    | Tape unit<br>unique ID  | AG4                           | 12-13                            | 13-14                            | TID12                                                          | (2 <sup>12</sup> )                                              |

| (512182U)<br>or<br>C16B-5126-<br>0490#U<br>(512649U)                                                                    | (manufacture<br>number) | AG6                           | 02-03<br>05-06<br>09-10<br>12-13 | 03-04<br>06-07<br>10-11<br>13-14 | TID11<br>TID10<br>TID9<br>TID8                                 | $(2^{11})$<br>$(2^{10})$<br>$(2^{9})$<br>$(2^{8})$<br>$(2^{8})$ |

| (3120490)                                                                                                               |                         | AG5                           | 02-03<br>05-06<br>09-10<br>12-13 | 03-04<br>06-07<br>10-11<br>13-14 | TID7<br>TID6<br>TID5<br>TID4                                   | $(2^{7})$<br>$(2^{5})$<br>$(2^{4})$<br>$(2^{4})$                |

|                                                                                                                         |                         | AG7                           | 02-03<br>05-06<br>09-10<br>12-13 | 03-04<br>06-07<br>10-11<br>13-14 | TID3<br>TID2<br>TID1<br>TID0                                   | $(2^3)$<br>$(2^1)$<br>$(2^1)$<br>$(2^0)$<br>$(2^0)$             |

|                                                                                                                         | EC level                | AF4                           | 02-03<br>05-06<br>09-10<br>12-13 |                                  | EC3<br>EC2<br>EC1<br>EC0                                       |                                                                 |

|                                                                                                                         | Function                | AG4                           | 09-10                            | 0304<br>0607                     | NEWF<br>SKIPF<br>ENITR                                         |                                                                 |

| C16B-5121-<br>0810#U<br>(512181U)<br>or<br>C16B-5126-<br>0480#U<br>(512648U)<br>or<br>C16B-5325-<br>0210#U<br>(532521U) | Options                 | BG7                           | 02-03<br>05-06<br>09-10<br>12-13 |                                  | OPTNO<br>OPTN1<br>OPTN2<br>OPTN3                               |                                                                 |

| C16B-5126-<br>0490#U<br>(512649U)                                                                                       | Function                | AJ6                           | 02-03<br>05-06<br>09-10*         | 10-11<br>13-14                   | Not Use<br>AGC Step<br>Streamin<br>Function<br>Dual<br>Density | g                                                               |

#### Table 1.2 MTU shorting plugs

\*Note This pin must be set "0" (09-10) in the case of 200 ips MTU.

1 - 8

#### 2.1 Mechanical Features

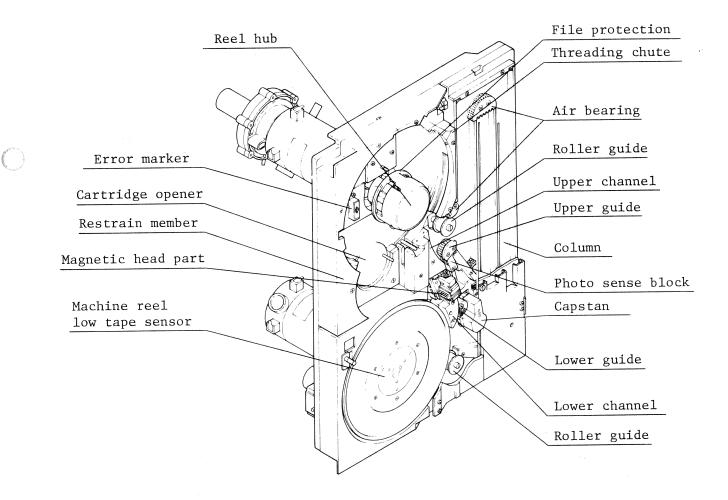

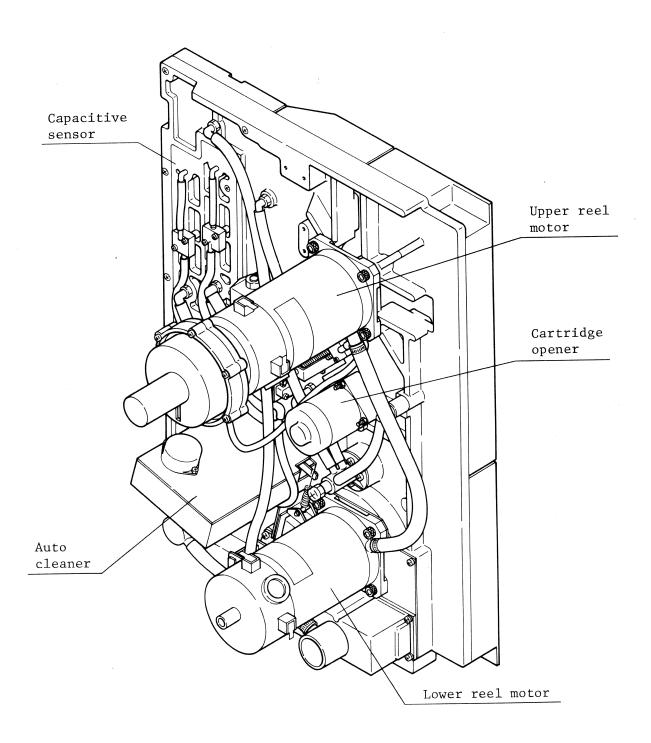

Front and rear views of the MTU mechanism are shown in Figures 2.1 and 2.2, respectively.

Figure 2.1 MTU front view

Figure 2.2 MTU rear view

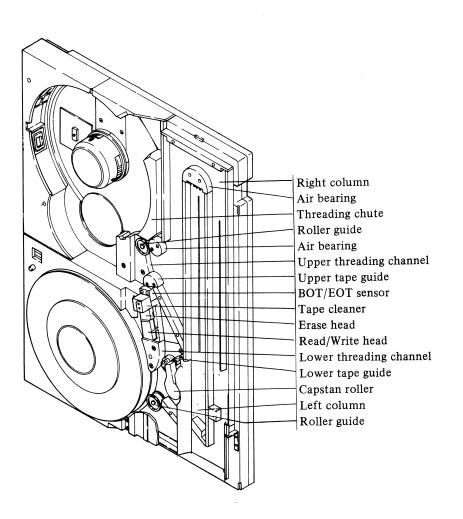

#### 2.1.1 Tape path

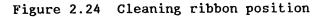

The MTU tape path, shown in Figure 2.3, is designed to minimize scratches on the coated surface of the tape and to increase system reliability. The tape coating surface touches only the magnetic head, tape cleaner, and cleaning ribbon. The base surface of the tape is guided by roller guides, shown in Figure 2.4, which reduce friction.

Figure 2.3 Tape path

2 - 3

Figure 2.4 MTU components related to the tape path

#### (1) Tape guide

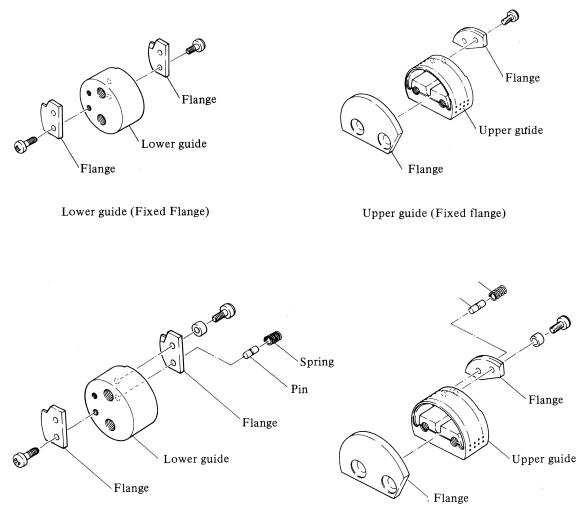

The upper and lower guides are located above and below the magnetic head. As shown in Figure 2.5, the fixed flanges are attached to both the front and rear sides of the upper guide, respectively. Both the fixed flanges are precisely positioned, and the tape runs between the flanges. The flange on the rear side of the lower guide is movable. The tape runs while being pressed by the movable flange in the front direction such that the standard edge of the tape always touches the fixed flange on the front side. Thus, the information track is protected from movement relative to the magnetic head.

Lower guide (Movable flange)

Upper guide (Movable flange)

#### (2) Roller guide

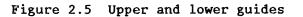

Two kinds of large and small roller tape guides are used. The large roller tape guide, shown in Figure 2.6, is designed to reduce the friction of tape passing the file reel, the machine reel, and the entry to the column, and to reduce uneven winding.

Figure 2.6 Roller guide

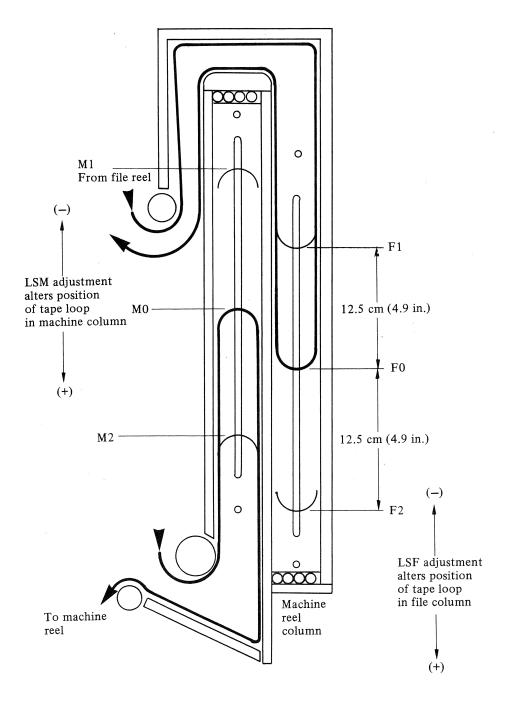

(3) Tape column

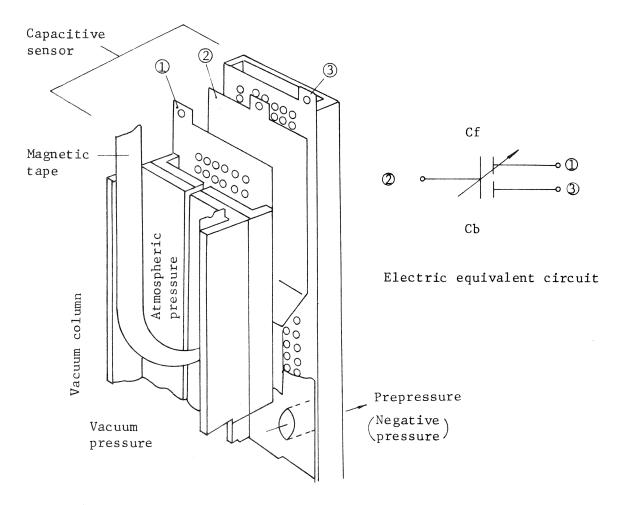

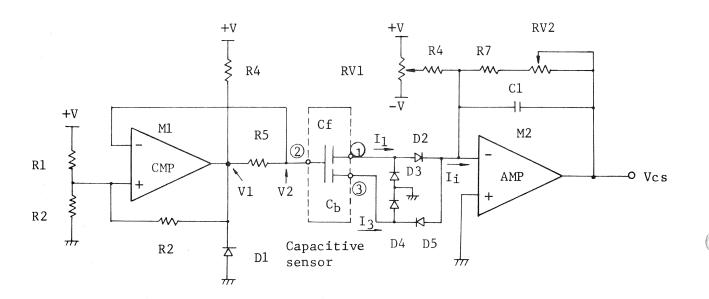

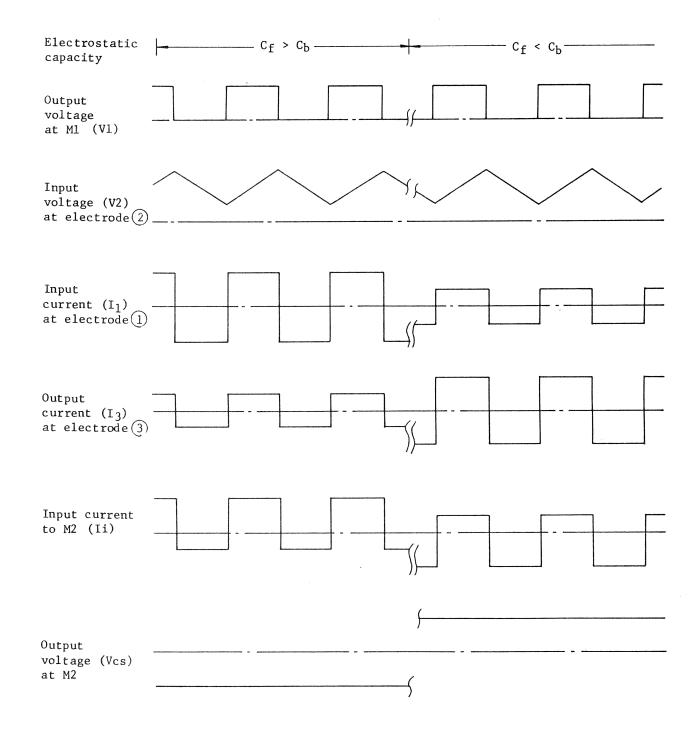

This is a buffer mechanism installed between the capstan and the machine and file reels. The capstan activates abrupt starts and stops repeatedly. The reel drive cannot follow the capstans action due to their large inertia. An electrostatic capacitive sensor and air pressure are used to maintain and detect the position of the tape loop in the tape column.

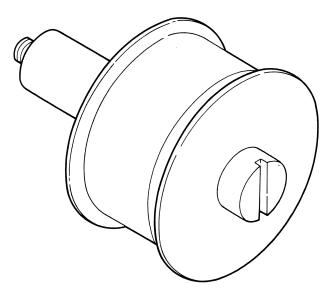

#### 2.1.2 Autoload mechanism

The autoload mechanism, shown in Figure 2.7, feeds the tape on the manually locked file reel to the machine reel via the upper and lower channels. The tape is wound five to six times on the machine reel and is then loaded into the tape columns.

The autoload mechanism consists of four main elements:

- o Restraint member

- o Cartridge opener

- o Cartridge sensor

- o Threading shute.

Figure 2.7 Autoload mechanism

#### (1) Restraint member

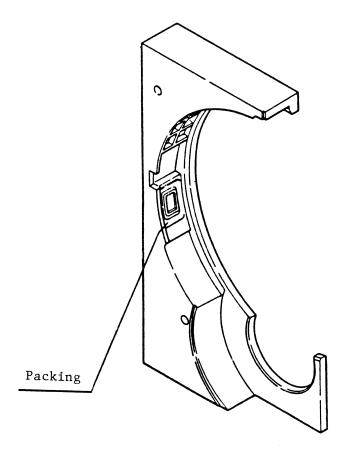

The restraint member, shown in Figure 2.8, is used during the autoload operation with a cartridge. It supports the cartridge and blows air inside the cartridge to cause the tape to more easily exit.

Figure 2.8 Restraint member

#### (2) Cartridge opener

$\bigcirc$

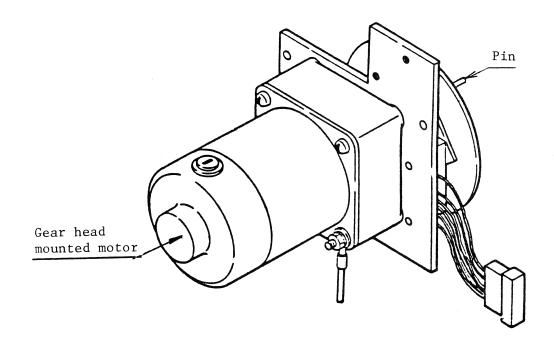

The cartridge opener, shown in Figure 2.9, causes the tape cartridge to open and close. When a cartridge mounted tape is loaded, a pin is inserted into a hole in the cartridge open and close mechanism. The pin rotates causing the cartridge to open or close. The angle of opening and closing the cartridge is detected and determined by a cam and microswitch.

Figure 2.9 Cartridge opener

#### (3) Cartridge sensor

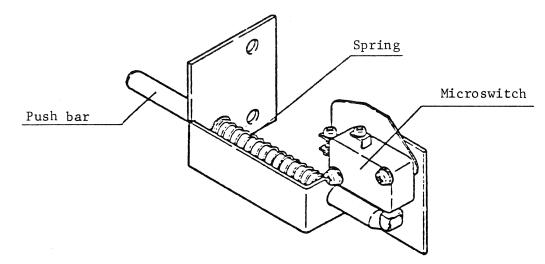

Because the autoload sequence depends on the presence or absence of a cartridge, a cartridge sensor, shown in Figure 2.10, is used. When a cartridge mounted reel is loaded, a push bar is depressed, and the microswitch is activated.

Figure 2.10 Cartridge sensor

#### (4) Threading chute

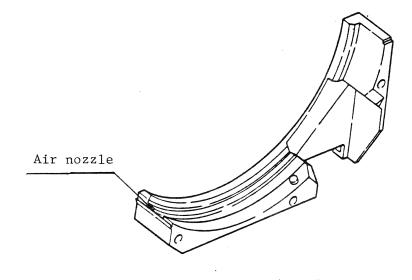

In the autoload mode using a reel installed in a cartridge, the threading chute in conjunction with the restraint member supports the cartridge. When no cartridge is used, the tape entry must be inserted in a grooved pad for threading to start autoloading. The air blown from the opening between the two plates of the threading chute and air blown from a channel (for peeling off the tape) make it possible to thread the tape smoothly.

Figure 2.11 Threading chute

#### (5) Upper channel

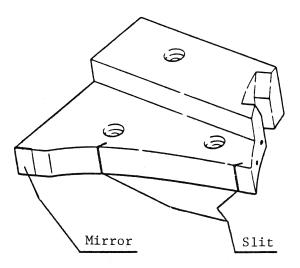

The upper channel, shown in Figure 2.12, has three inclined slits to produce a stable air stream along the channel and to feed the tape. A mirror is attached to the bottom end of the upper channel through which the photosense block detects whether or not tape is present by the presence or absence of the light reflected from the mirror.

Figure 2.12 Upper channel

(6) Lower channel

Similar to the upper channel, the lower channel shown in Figure 2.13 blows air to feed the tape to the machine reel.

Figure 2.13 Lower channel

#### (7) Machine reel

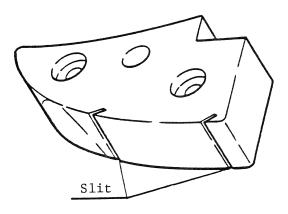

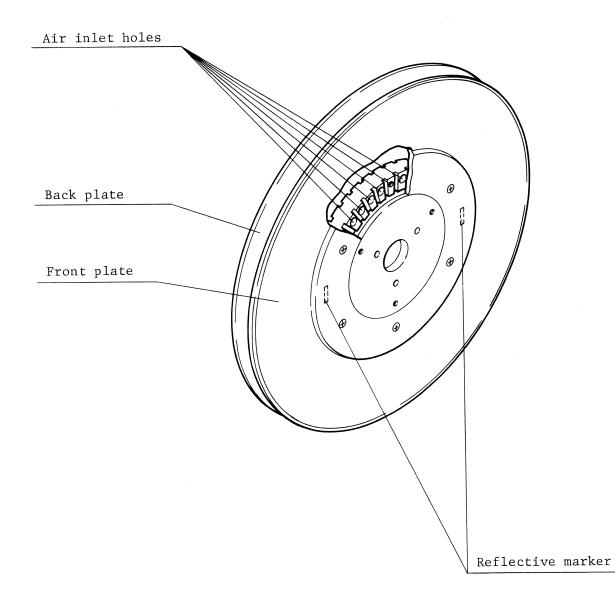

The machine reel air inlets, shown in Figure 2.14, provides suction to assist in winding the tape onto the machine reel during autoloading. The air inlets are most effective from the bottom right position so that the inlet can effectively apply suction to the tape. A reflective marker is attached to the front plate of the machine reel. The low-tape sensor detects the rotation speed of the machine reel and the amount of tape remaining on the reel.

#### 2.1.3 Auto hub

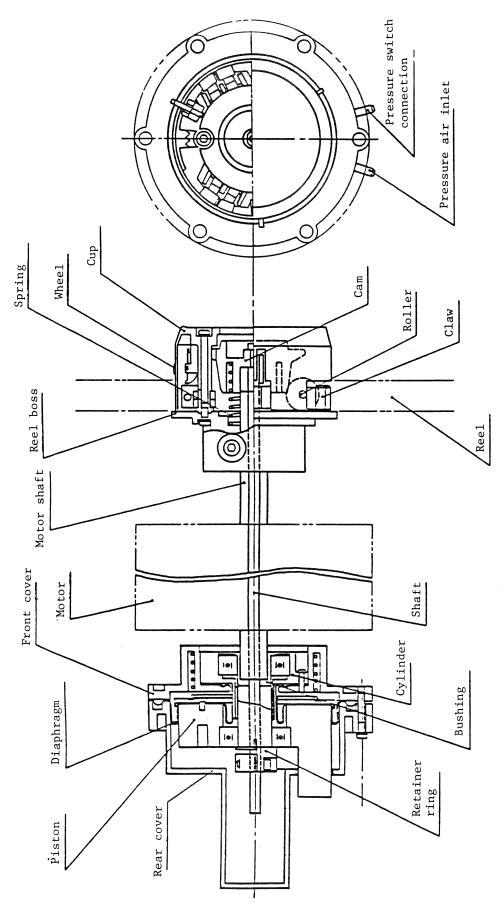

The auto hub, shown in Figures 2.15 and 2.16, consists of three main sections:

- (1) A section to convert pneumatic pressure into mechanical power. This section contains the diaphragm, piston, and front cover.

- (2) A section to retain the reel that contains the reel boss, cam, roller, claw, and rubber tip.

- (3) A wheel that holds the reel in its position and provides safety in case of a malfunction.

The diaphragm has a double-wall configuration. When air pressure is applied between the diaphragm and the front cover, the retainer ring moves, and the roller rises. As the roller rises, the claw enlarges; the reel is held in place by the friction of the rubber tip.

If the wheel is mounted, the reel is positioned properly when the reel is pressed inside. The wheel prevents the reel from being pushed out accidentally.

Figure 2.15 Auto hub

$\bigcirc$

C

$\bigcirc$

#### 2.1.4 Head assembly

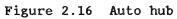

The head assembly, shown in Figure 2.17, consists of a magnetic read/write head, erase head, tape cleaner, and azimuth adjusting mechanism.

Figure 2.17 Head assembly

#### (1) Magnetic head

The magnetic head contacts the coating surface of the tape to perform data recording and regeneration.

(2) Erase head

The erase head is located close to the coating surface of the tape (but does not touch the tape surface) to perform erase operations.

#### (3) Tape cleaner

The tape cleaner is provided with a sharp edge to remove dust, foreign substances, and purple oxide adhering to the coating surface of the tape. All such materials are likely to cause the tape to drop data. The removed substances are blown off by the air stream from the cleaner edge.

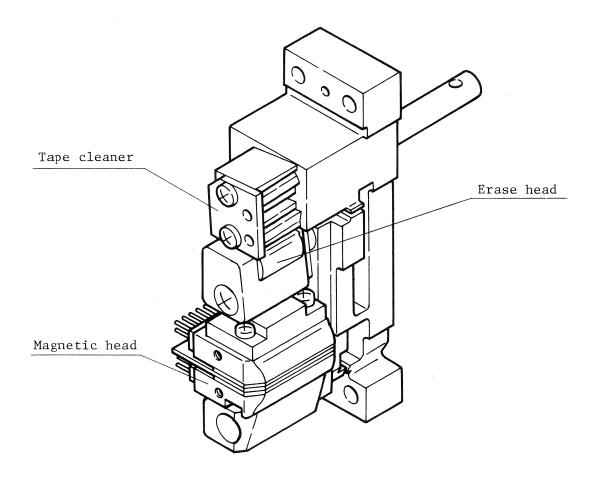

#### (4) Azimuth adjusting mechanism

The azimuth adjusting mechanism is shown in Figure 2.18. When rotating the azimuth adjusting screw, the deformation part shown in the figure deforms, and the magnetic head is inclined. This mechanism is used to adjust azimuth while observing tape skew.

Figure 2.18 Azimuth adjusting mechanism

#### 2.1.5 Capstan

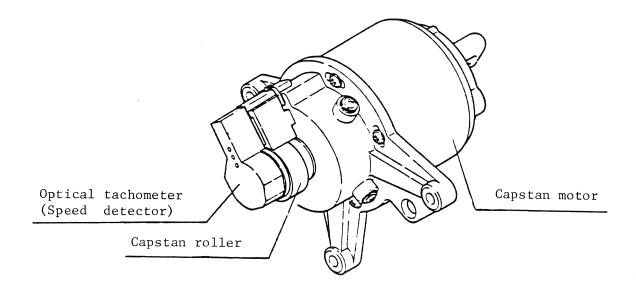

#### (1) Capstan motor

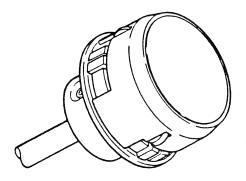

Tape is fed by rotation of the capstan roller, shown in Figure 2.19. The roller is connected directly to the capstan motor and operates in forward or backward direction.

The capstan motor starts and stops abruptly since it uses a DC servo motor with low inertia. The surface of the capstan roller is lined with material having a high coefficient of friction to protect against tape slippage. The lining is extremely thin. Exercise care when servicing the capstan to avoid scratching or deforming the surface of the capstan roller.

Figure 2.19 Capstan motor

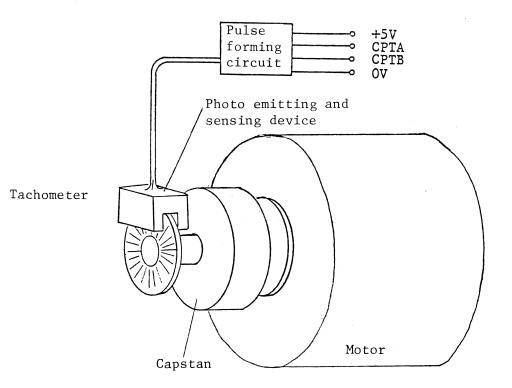

#### (2) Detection of capstan rotation speed

An optical tachometer detects the capstan motor's speed of rotation. The 500 optical tachometer is provided with the code plate on which 500 slits are printed between an LED and a phototransistor, which has a mask for detection. The code plate is mounted on the capstan motor shaft.

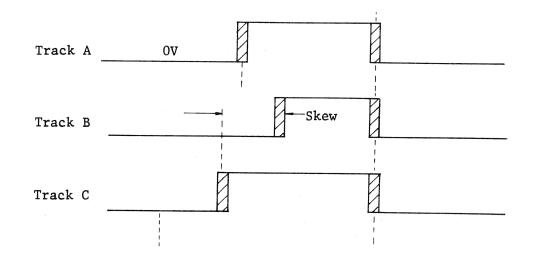

The mask is concentric with the code plate and is mounted on the capstan motor. The rotating direction of the capstan motor is detected by the slits with a phase shift of  $90^{\circ}$ .

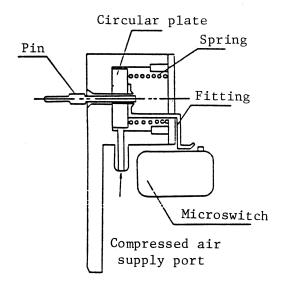

#### 2.1.6 File protection mechanism

A tape file is protected such that when the file reel has a write enable ring installed, the ring pin is inserted and pulled in by the air cylinder. The ring pin is separated from the enable ring. When the microswitch shown in Figure 2.20 detects the separation of the pin from the ring, a write-enable signal is issued.

Figure 2.20 File-protection mechanism

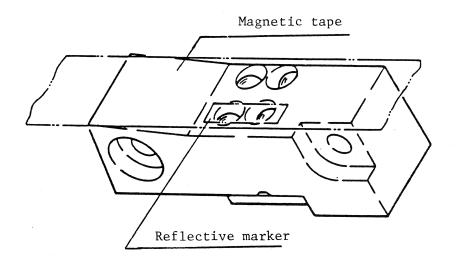

#### 2.1.7 Photo sense block

The photo sense block shown in Figure 2.21 detects the beginning-of-tape (BOT) marker, the end-of-tape (EOT) marker, and the presence or absence of the reflection from the mirror mounted on the upper channel. The presence or absence of tape, the current tape position, the sequence of events, and the BOT and EOT are all detected by the photo sense block.

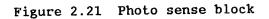

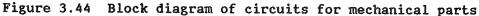

#### 2.1.8 Low-tape sensor

Abrupt stoppage of tape being rewound at high speed is difficult even when the BOT is detected. Thus, the low-tape sensor shown in Figure 2.22 detects the amount of tape wound on the machine reel in advance. The tape speed is reduced when low tape is detected. The amount of tape wound on the machine reel is detected by reflected light from the reflective marker attached to the front plate of the machine reel. During autoloading, the detected frequency of reflected light from the reflective marker makes up the number of machine reel rotations. This allows timing for the column in action.

### 2.1.9 Autocleaner

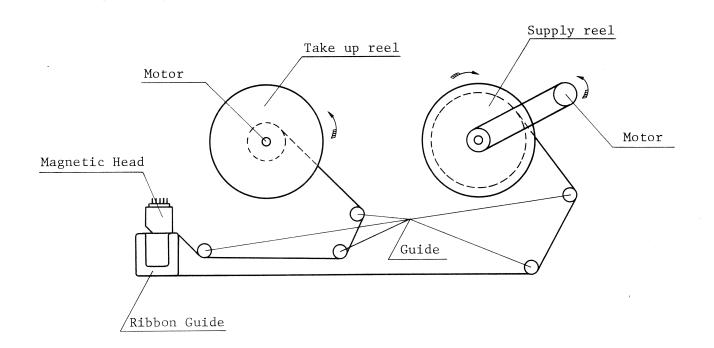

The autocleaner shown in Figure 2.23 cleans dust adhering to the tape and protects the magnetic head from wear. The autocleaner cleans the tape coating surface by inserting a cleaning ribbon between the magnetic head and the magnetic tape during rewinding in normal speed. In addition, manual cleaning of the magnetic head, erase head, and tape cleaner can be performed by manually inserting the autocleaner.

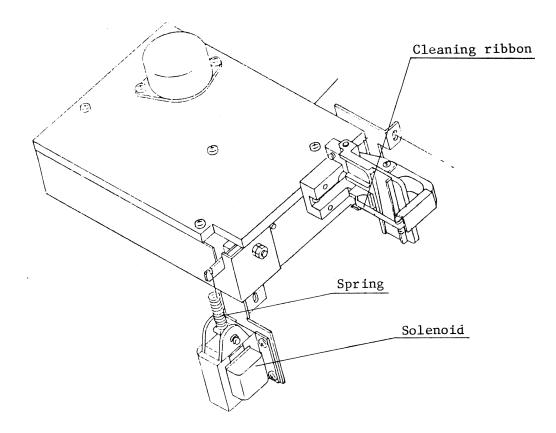

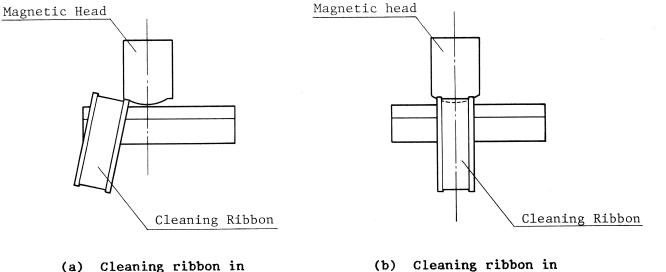

(1) Slide assembly

The slide assembly that guides the cleaning ribbon is located below the right side of the magnetic head. It is activated by the solenoid and causes the cleaning ribbon to move under the write/read gap as shown in Figure 2.24. This cleaning ribbon cleans the magnetic head while preventing the magnetic tape from touching the magnetic head. When the solenoid is turned off, it is returned to its original position by releasing the spring.

### (2) Cleaning ribbon

The cleaning ribbon is activated when the slide assembly is in operation. Delivery rate is 2 to 5 mm/min. The cleaning ribbon is 50 m long.

Figure 2.23 Autocleaner

(a) Cleaning ribbon in the state when the solenoid is not in operation

Figure 2.25 Autocleaner structure

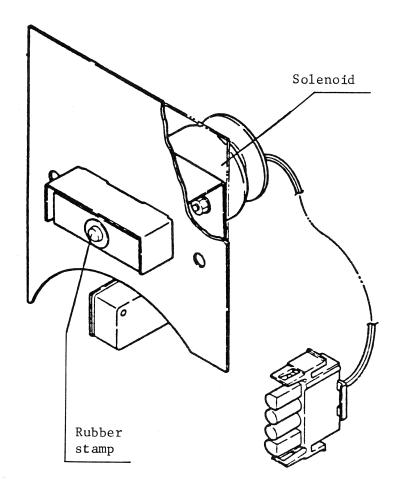

### 2.1.10 Error marker

The error marker shown in Figure 2.26 places a mark on tape reels that produce frequent errors. The magnetic channel counts errors occurring during the write operation. If many errors occur, an appropriate signal is issued to the MTU. When receiving the signal, the MTU stamps a mark on the reel during unloading. The mark is made by a rubber stamp embedded in the solenoid axle when the solenoid operates.

Figure 2.26 Error marker

#### 2.2 Air Supply System

The air supply system, shown in Figures 2.27 and 2.28, performs air pressure and vacuum operations for each section. Air pressure and vacuum are generated by suction and blowing of air by the motor driven blower. The locations to which air pressure and vacuum are supplied vary as a function of conditions of operation. Switching is executed by an electromagnetic valve.

Figure 2.27 Air supply system during autoload operation

Figure 2.28 Air supply system during normal tape run

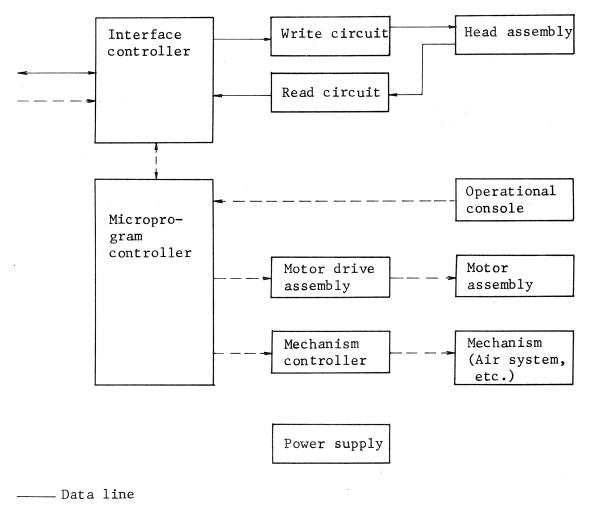

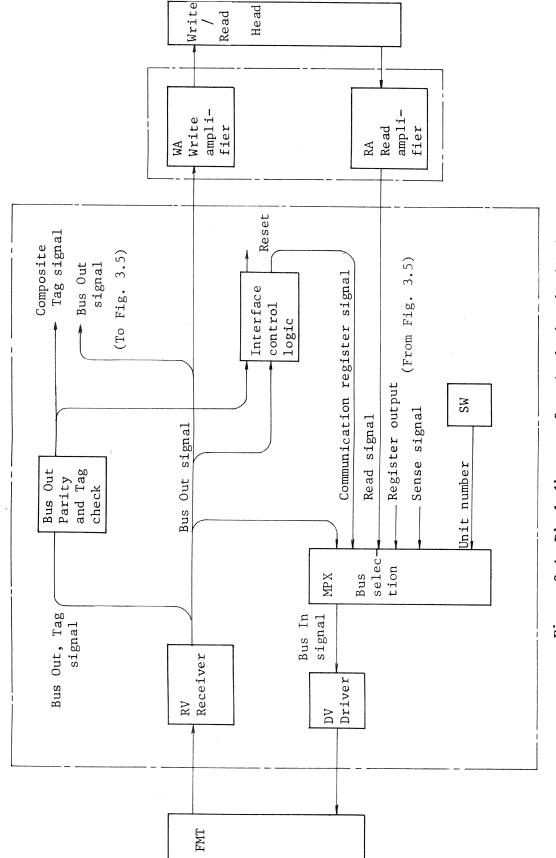

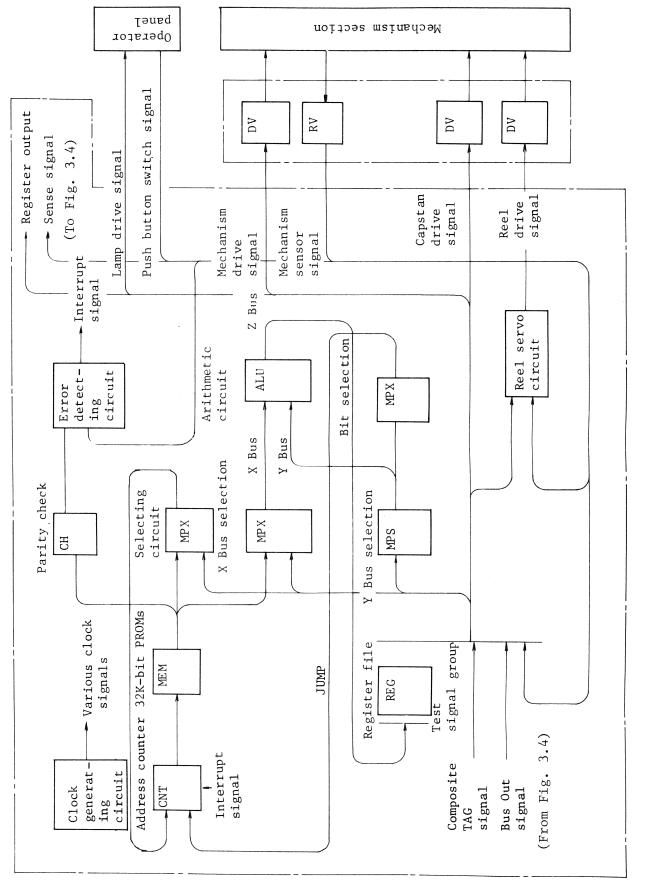

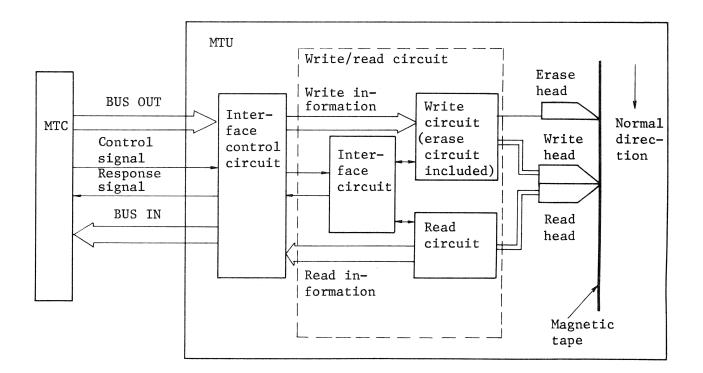

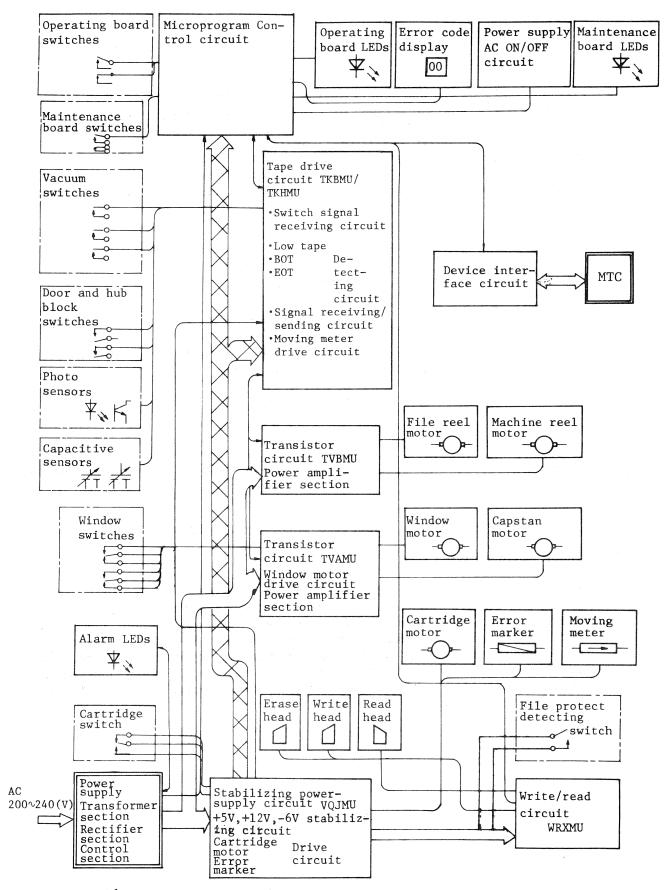

## 3.1 Overall Circuit Configuration

Figure 3.1 shows the overall circuit configuration of the MTU. Power supply lines are omitted in this illustration because power is supplied to every section of the MTU.

---- Control line

Figure 3.1 Circuit configuration of the MTU

The overall system circuit consists of 11 main elements.

- (1) The microprogram controller consists of the read-only memory (ROM), arithmetic logic unit (ALU), resistors, and bus control circuit.

- (2) The interface controller is the interface circuit to the MTC that receives instructions from the MTC and sends and receives control signals to and from the microprogram controller.

- (3) The write circuit is the circuit for writing data from the MTC on the tape with the write head. This circuit also supplies current to the erase head and to the automatic degauss of the write head.

- (4) The read circuit amplifies the read signal from the read head, digitizes, and transmits the signal to the MTC. In the 6250 BPI mode, the circuit that automatically adjusts the gain of the read amplifiers is included in the read circuit.

- (5) The motor driving circuit consists of a current amplifying circuit to drive the capstan motor, the servo system circuit for the reel motor, a drive circuit for the window motor, and the cartridge motor.

- (6) The mechanism controller consists of a driving circuit network for air supply, solenoid, and valve operations.

- (7) The head assembly consists of the write head, read head, and erase head.

- (8) The operator panel contains pushbutton switches and indication lamps (LED). This panel is described in more detail in Section 3.2.

- (9) The motor section consists of the capstan motor, reel motor, window motor, and cartridge motor.

- (10) The mechanism section consists of air supply units, a sensor mechanism, and the autoload mechanism.

- (11) The power supply section includes the power supply for PCA operation, the power supply for mechanisms, and all remaining units requiring power.

3 – 2

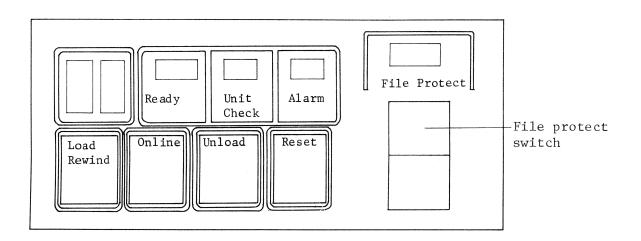

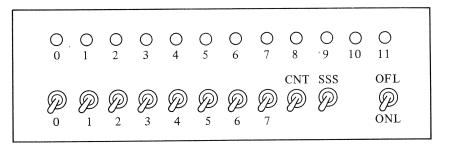

#### 3.2 Operator Panel

The operator panel consists of various switches necessary for MTU operation. Indication lamps (LED) show the condition of each operation. Figure 3.2 is an exterior view of the operator panel.

Figure 3.2 Exterior view of the operator panel

#### (1) READY (LED)

When the MTU is in the ready state under control of the MTC, the green light of the Ready lamp goes on. During the rewind operation, data security erase (DSE) operation, space file and back space file operations, or tape load operation, this lamp will not be ON until the operation is completed.

(2) UNIT CHECK (LED)

When tape loading fails, the red Unit Check lamp flashes. If an abnormal state occurs at other times, this red lamp remains ON. When the RESET switch is depressed, this lamp turns off.

(3) ALARM (LED)

The Alarm lamp lights (red) when a fuse blows, when a circuit breaker shuts off, a power supply fails, or when an abnormal temperature rise is detected.

#### (4) LOAD/REWIND switch

This switch is effective only in the offline state. To use the LOAD/REWIND switch, place the reel on the hub and install the tape on the file reel. Place the point of tape on the threading chute and depress this LOAD/REWIND switch. The tape reel is automatically locked, auto threading and tape loading are executed, and the tape runs until the BOT marker is detected (the window also automatically closes). When this switch is depressed while tape is in the loaded state, the tape is rewound at high speed until the BOT marker is detected.

To reload (also referred to as mid-load) tape that is only partly in the column due to some problem, such as electric stoppage, gently rotate the file reel to extract the stacked part of the tape until the tape becomes tense between the machine reel and the file reel. Press the LOAD/REWIND switch. The tape is automatically fed into the column and rewound until the BOT marker is detected.

(5) ONLINE switch

Use the ONLINE switch to turn the MTU to the online state. Press the ONLINE switch to make the MTU available with the MTC.

(6) UNLOAD switch

This switch is effective only when the MTU is in the offline state. Use the UNLOAD switch to rewind loaded tape at high speed to BOT, to unlock the auto hub, and to open the window. when this switch is depressed and tape is completely rewound on the file reel, the window opens.

(7) RESET switch

Depress the RESET switch to turn the MTU to the offline state and to reset the control line. The window is also closed by this switch. When the MTU fails in tape loading (the UNIT CHECK lamp flashes), depressing this switch releases the reel brake, thereby enabling the tape to be rewound manually. If the MTU fails during tape loading, the window opens automatically. If an abnormal state (with the UNIT CHECK lamp continuing to light), depressing this switch opens the window.

(8) FILE PROTECT LED and switch

This lamp lights (amber) when the write-enable ring is removed from the file reel. When the switch is depressed, the file is protected from writing.

(9) Two-digit indicator LED

This lamp indicates a two-digit code representing the condition of the power supply and an abnormal (error) condition of the MTU.

- 00 Represents no MTU errors (if the Unit Check lamp is off).

- 01 Indicates that an erroneous operation is occurring in the relevant unit, or displays the contents of an error. When either of these codes is indicated, the UNIT CHECK lamp flashes or remains ON.

## 3.3 MTC Interface

### 3.3.1 Connecting cable

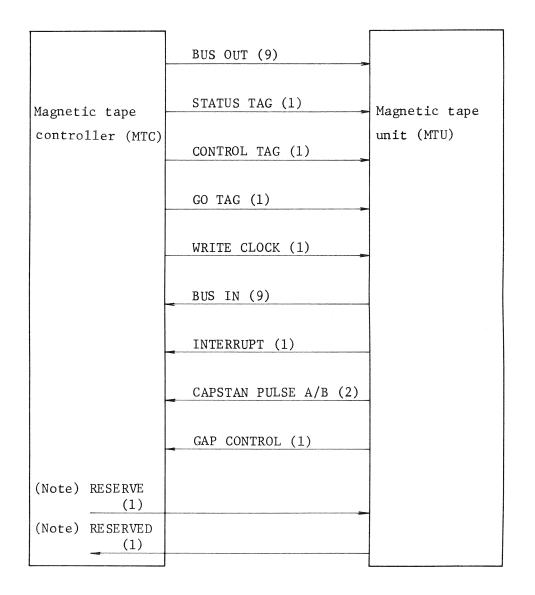

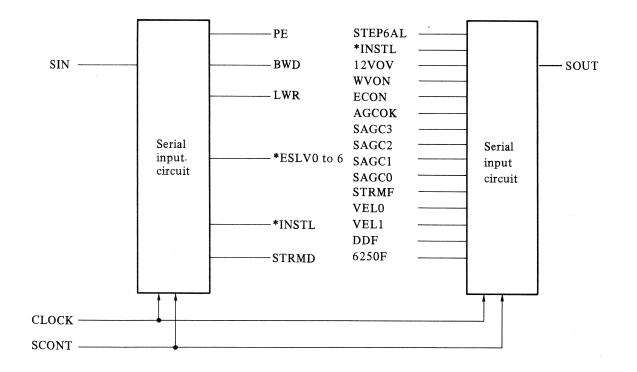

Each MTU is connected to the MTC through a single, flat cable. The address of each MTU is determined by the connection on the MTC distribution PCA. All 28 pairs of signals between the MTC and the MTU are digital. The signals between the MTC and the MTU are shown in Figure 3.3.

Note: The Reserved signals are not used in the MTU. However, the MTU should be provided with a terminal resistance.

Figure 3.3 Signals between MTC and MTU

#### 3.3.2 Interface signal lines

### (1) Data lines

These lines are used to transmit data from the MTC to the MTU. Data represents the status control command, encoded write data, and sense data. Data is discriminated by the tag signal.

## Bus In through 8

These lines transmit data from the MTU to the MTC. The data represents status byte data, control byte data, command byte data, read data from the tape, loop write-to-read return data, and the sense data. Data is discriminated by the tag line.

#### (2) Tag line

Tag control is shown in Tables 3.1 and 3.2.

Table 3.1 Contents of tag control

$\bigcirc$

()

|         |                                       |              |                               | ~                    | <u>س</u>            | 4                   | <u>ل</u>                       |            | ~          | m        |

|---------|---------------------------------------|--------------|-------------------------------|----------------------|---------------------|---------------------|--------------------------------|------------|------------|----------|

|         | GO                                    | RDO          | RD1                           | RD2                  | RD3                 | RD4                 | RD5                            | RD6        | RD7        | RD8      |

|         | COMMAND<br>(Status<br>Control<br>"1") |              | See the<br>following<br>table |                      |                     |                     |                                |            |            | TAG IN   |

| BUS IN  | CONTROL                               | Level Test 0 | -1<br>:                       | :                    | Test Mode           | EMK                 | DSE                            | REW        | UNI.       | TAG IN   |

|         | STATUS                                | ERS          | FWD                           | BWD                  | Write<br>Status     | TU Check            | SAGC ON                        | 1600       | LWR TUIF   | TAG IN   |

| r .     | CO                                    | WD0/RDL0     | WD1/RDL1                      | WD2/RDL2             | WD3/RDL3            | WD4/RD4             | WD5/RDL5                       | WD6/RDL6   | WD7/RDL7   | WD8/RDL8 |

|         | COMMAND<br>(Status<br>Control<br>"1") |              | See the<br>following<br>table |                      |                     |                     |                                |            |            | Parity   |

| BUS OUT | CONTROL                               | Level Test 0 | L :                           | :                    | Set Test<br>Mode    | Set Error<br>Marker | Set Data<br>Security<br>Erase  | Set Rewind | Set Unload | Parity   |

|         | STATUS                                | Set Erase    | Set Read<br>Forward           | Set Read<br>Backward | Set Write<br>Status | Reset               | Set 6250 & SAGC<br>or Set NRZI | Set 1600   | Set LWR    | Parity   |

|         | TAG<br>BUS OUT/IN<br>BIT              | 0            | 7                             | 2                    | ຕ                   | 4                   | Ś                              | 9          | 7          | 8        |

| Bus  | 0ut  | Command              |             | Content of BUS IN                   |

|------|------|----------------------|-------------|-------------------------------------|

| 0123 | 4567 | Command              | BUS OUT     | 0 Character "X"<br>may be any digit |

| 0    | 0    |                      | BUS IN      | 0 1 2 3 4 5 6 7                     |

| 0    | 1    |                      |             |                                     |

| 0    | 2    | Set Streaming Mode   | 0           | STRMF (Streaming Feature)           |

| 0    | 3    | Reset Streaming Mode | · · · · · · |                                     |

| 0    | 4    | Space File           | 1           | SKIPF (Skip File Feature)           |

| 0    | 5    | Back Space File      |             |                                     |

| 0    | 6    | -                    | 2           |                                     |

| 0    | 7    |                      |             |                                     |

| 0    | 8    | Set LWR RW           | 3           | LWSL (Low Slice)                    |

| 0    | 9    | Reset LWR RW         |             |                                     |

| 0    | A    | Set Low Slice        | 4           | STRMD (Streaming Mode)              |

| 0    | В    | Reset Low Slice      |             |                                     |

| 0    | C    |                      | 5           | LWR RW                              |

| 0    | D    |                      |             |                                     |

| 0    | E    |                      | 6           | HACT (Action)                       |

| 0    | F    |                      |             |                                     |

| L    |      | <u></u>              | 7           | RDY (Ready)                         |

|      |      |                      | 8           | TAG IN                              |

|      |      |                      | Ŭ,          |                                     |

| Table 3.2 Contents of the command tag | Table | 3.2 | Contents | of | the | command | tag |

|---------------------------------------|-------|-----|----------|----|-----|---------|-----|

|---------------------------------------|-------|-----|----------|----|-----|---------|-----|

| Bus                | Out                    |                         |

|--------------------|------------------------|-------------------------|

| Address<br>0 1 2 3 | Contents of<br>4 5 6 7 | Communication Registers |

| 1000               | 0 through F            | Reg. 0 Upper 4 bits     |

| 1001               | 0 through F            | Reg. 0 Lower 4 bits     |

| 1010               | 0 through F            | Reg. 1 Upper 4 bits     |

| 1011               | 0 through F            | Reg. 1 Lower 4 bits     |

| 1100               | 0 through F            | Reg. 2 Upper 4 bits     |

| 1101               | 0 through F            | Reg. 2 Lower 4 bits     |

| 1110               | 0 through F            | Reg. 3 Upper 4 bits     |

| 1111               | 0 through F            | Reg. 3 Lower 4 bits     |

| BUS OUT<br>BUS IN                    | 0 to 3 4 to 7<br>8 or 9 "X" | 0 to 3 4 to 7 0 to 3 4 to 7<br>A or B "X" C or D "X" | 0 to 3 4 to 7<br>E or F "X" |  |  |

|--------------------------------------|-----------------------------|------------------------------------------------------|-----------------------------|--|--|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | Reg. O                      | Reg. 1 Reg. 2                                        | Reg. 3                      |  |  |

| 8                                    | TAG IN                      |                                                      |                             |  |  |

#### Status Tag

- a. This signal causes the MTC to call the status information from the MTU or sets the status operation.

- b. To implement status call, set Status Tag to "1". The Write Clock must not be set to "1".

- c. To implement status set to the MTU, the MTC sets a predetermined control item to "1" on the Bus Out line and sets both the Status Tag and the Write Clock to "1".

- d. When GO Tag is "1", the Tape Unit (TU) Sense Byte 8 is issued to Bus In when Status Tag is set to "1".

- e. When Status Tag, in conjunction with Control Tag, is set to "1", it acts as a Command Tag.

#### Control Tag

- a. This signal causes the MTC to call the control information from the MTU or to set control operation.

- b. To call the control information, set Control Tag to "1", but do not set Write Clock to "1".

- c. To set Control to the MTU, the MTC sets a predetermined control item to "1" on the Bus Out line and sets both the Control Tag and the Write Clock to "1".

- d. When the Control Tag, in conjunction with the Status Tag, is set to "1", it acts as a Command Tag.

#### Command Tag

- a. When both the Status Tag and the Command Tag are "1", the MTU regards them as a Command Tag.

- b. This signal causes the MTC to call the command information from the MTU or to set command operation.

- c. To call the command information, set the Command Tag to "1". The Write Clock must not be set to "1".

- d. To issue a command to the MTU, the MTC sets a predetermined control item to "1" on the Bus Out line and sets both the Command Tag and the Write Clock to "1".

- a. This signal causes the MTC to direct the MTU to set the tape drive for the read or write operation.

- b. If the MTU is already in the Write Status when this signal is "1", the Bus Out line provides the write information to the tape, and the "Write Clock" is used together.

- c. If the MTU is already in the Read Status when this signal is "1", this signal becomes control information to switch the threshold level of the read circuit in the MTU to zero.

- d. If the MTU is already in the Read Status when the Go Tag signal is "1", the Bus In line becomes data from the tape.

- (3) Write Clock

- a. When the Status Tag, the Control Tag, or the Command Tag, in conjunction with the Write Clock, is set to "1", the contents of the Bus Out are stored.

- b. To call the Status information, the command information, the Sense information, and the Write Clock are not needed.

- c. When the MTU is in the Write Status and the Go Tag is "1" the MTU implements sampling of the data on the Bus Out line at the rise of Write Clock.

- (4) Interrupt

This signal is set to "1" when the MTU causes the following conditions in offline operation:

- a. When file protect occurs during the forward action in the write or erase operation.

- b. When the condition that causes the Unit Check to be "1" occurs within the MTU.

- c. When the Ready or the Online is set to "O" during the write or read operation (Go Tag "1").

- d. When ONLINE is set to "O" during Rewind or DSE operation.

- e. When the BOT is detected during the Read backward operation (when the Go Tag is issued from the MTU).

- f. When the Test Mode FF in the MTU is "1" and the EOT is detected during Write or Read operation.

- g. When the Self-Adjust Gain Control (SAGC) Check occurs during the SAGC operation.

- h. When BOT is detected in the back-space file.

- i. When the 20-m check is detected in the space file.

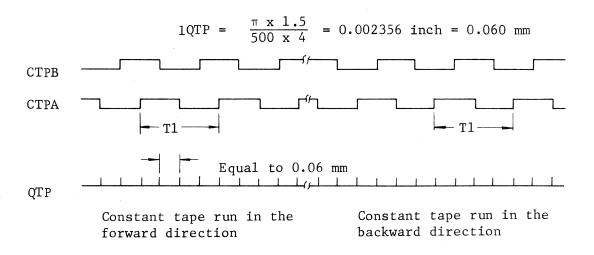

- (5) Capstan pulse A/B

- a. This signal provides information about tape-drive speed detected optically from the code disk connected directly to the capstan.

- b. When the capstan rotates in the forward direction, pulse A is in a phase delay relative to pulse B. When rotating in the backward direction, the phase relation between pulse A and pulse B is reversed.

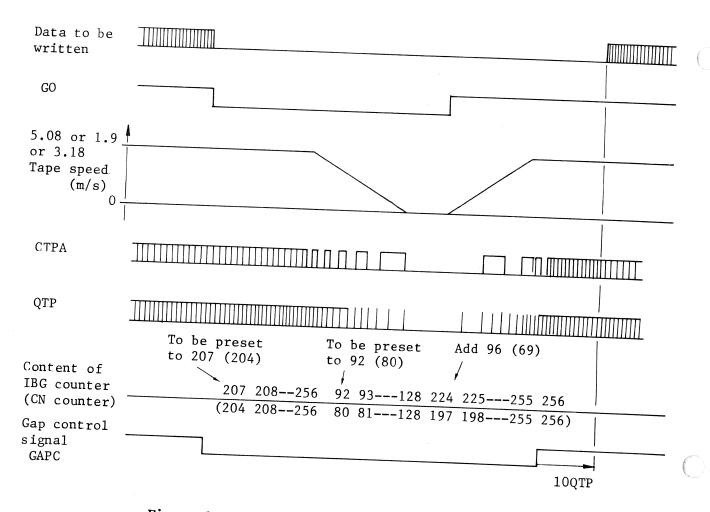

- (6) Gap Control

- a. This is the block-access start signal that the MTC receives from the MTU after the MTC sets the Go Tag to "1" during the read/write operation.

- b. The MTU starts counting capstan pulses when the Go Tag is set to "O" in the immediately preceding read/write operation. The number of capstan pulses are counted since the beginning of the present operation when the Go Tag was set to "1". The MTU sets the Gap Control signal to "1" at the time that the amount of tape length fed by capstan rotation reaches a predetermined length of Inter-Block Gap (IBG).

#### 3.3.3 Tag line control

( )

- (1) The meaning of the Bus Out bit in the Status Tag is as follows:

- a. Bit 0 Set Erase

When this bit is "1", the MTU is set to the erase status.

b. Bit 1 Set Read Forward

When this bit is "1" and both bits 2 and 3 are "0", the MTU sets the write status to "0" (Read Status) and changes to the FWD status.

c. Bit 2 Set Read Backward

When this bit is "1" and both bits 2 and 3 are "0", the MTU sets the write status to "0" (Read Status) and changes to the BWD status.

d. Bit 3 Set Write Status

When this bit is "1" and both bits 2 and 3 are "0", the MTU is set to the write status.

e. Bit 4 Reset

When this bit is "1", the following signal in the MTU is set to "0".

- TU check (Status Tag bit 4)

Interrupt

Ready hold (TU Sense Byte 3 bit 2)

Overrun (TU Sense Byte 8 bit 5)

Tape Mark (TU Sense Byte 8 bit 7)

Test Mode (Control Tag bit 3)

LWR (Status Tag bit 7)

LWR2 (Command Tag bit 5)

- TU Sense Byte 2

- f. Bit 5 Set 6250 and SAGC or Set NRZI

- . For the MTU in the GCR/PE mode. This means that the MTU is set in the 6250 BPI and SAGC mode.

- . For the MTU in the PE/NRZI mode. This means that the MTU is set in the 800 BPI NRZI mode.

- g. Bit 6 Set 1600

When this bit is "1" and bit 5 is "0", the MTU is operated in the 1600 BPI mode.

h. Bit 7 Set LWR TUIF (Loop-Write-to-Read TU interface)

This bit sets the MTU in the LWR TUIF mode. The MTU is set in the loop mode, and the output on the BO line is input to the BI line without changing the wave shape, where the MTU is set in the loop mode when the GO Tag signal is "1".

- (2) The meaning of the Bus Out bits in the Control Tag is as follows:

- a. Bits 0 through 2 Level Test 0 through 2

The combination of bits 0 through 2 determines the slice level as shown in Table 3.3.

b. Bit 3 Set Test Mode

When this bit is "1", the MTU is set in the Test Mode.

c. Bit 4 Set Error Marker (EMK)

This bit specifies the action to print character E on the back of a file reel.

| Table 3.3 Slice level of each mode | Table | 3.3 | Slice | level | of | each | mode |

|------------------------------------|-------|-----|-------|-------|----|------|------|

|------------------------------------|-------|-----|-------|-------|----|------|------|

| Application | Lev | el | Test |       | READ                 | WRITE                |        |

|-------------|-----|----|------|-------|----------------------|----------------------|--------|

| Application | 0   | 1  | 2    | FWD   | BWD                  | FWD                  | Mođe   |

| (           | 1   | 1  | 1    |       | 125 ± 12%            | ·                    |        |

|             | 1   | 1  | 0    |       | 100 ± 12%            |                      |        |

| Diagnosis { | 1   | 0  | 1    |       | 80 ± 8%              |                      | GCR/PE |

|             | 1   | 0  | 0    |       | 64 ± 8%              |                      |        |

|             | 0   | 1  | 1    |       | 51 ± 5%              |                      |        |

|             | 0   | 1  | 0    |       | 41 ± 5%              |                      |        |

| Marginal    | 0   | 0  | 1    | 15±2% | 10±1%<br>15±2%       | 37±4%                |        |

|             |     |    |      |       | (AGC step is         | (AGC step is         |        |

|             |     |    |      |       | greater<br>than C)   | greater<br>than C)   |        |

| Normal      | 0   | 0  | 0    | 10±1% | 7±1%                 | 20±2%                |        |

|             |     |    |      |       | 10±1%                | 25±2%                |        |

|             |     |    |      |       | (AGC step is greater | (AGC step is greater |        |

|             |     |    |      |       | than C)              | than C)              |        |

| Marginal    | x   | x  | 1    | 26    | 5±4%                 | 50±5%                |        |

| Normal      | x   | x  | 0    | 17    | ±2%                  | 40±5%                | NRZI   |

## d. Bit 5 Set Data Security Erase (DSE)

When the MTU is in the write status, this bit initiates the data security erase action of the MTU. The MTU carries out the erase action until the EOT marker is detected. During the erase action, READY (Sense byte 0 bit 7) is in the "O" state. When the EOT marker is detected and the erase action is completed, the DSE status is set to OFF and READY returns to "1".

e. Bit 6 Set Rewind (REW)

This bit specifies high-speed rewinding until the BOT marker is detected. After the rewind action starts, the MTC need not intervene until the rewind action is completed. During the rewind action, the Ready state is "0", the Online status is kept as "1", and the MTU is in the busy condition. At the completion of the rewind action, the Ready state is recovered. f. Bit 7 Set Unload (UNL)

This bit specifies the unload action. When the unload action starts, both the Online status and the READY are set to "O". These are not automatically returned to "1" even when the unload action is completed. When the unload action is completed, the tape is wound entirely on the file reel, resulting in servo-off, reel lock release, and window open.

- (3) The meaning of Bus Out in the Command Tag (both the Status Tag and the Control Tag are "1") is as follows:

- a. Code 02 Set Streaming Mode

This command sets the MTU in the streaming mode.

b. Code 03 Reset Streaming Mode

This command resets the streaming mode.

c. Code 04 Space File

This command makes the MTU set the READY signal to "O" and moves the loaded tape in the forward direction until the Tape Mark (TM) block is detected.

d. Code 05 Backspace File

This command makes the MTU set the READY signal to "0" and moves the loaded tape in the backward direction until the TM block is detected.

e. Code 08 Set Loop-Write-to Read RW

This command causes the MTU to loop the write data onto the read data lines. The LWR RW is made to return. The write data is returned via the analog circuit following the pre-amplifier circuit. The LWR is the same shape as the write data, while the wave shape of the LWR RW is similar to that of the data read by the read head.

f. Code 09 Reset Loop-Write-to Read RW

This command resets the LWR RW mode.

g. Code OA Set Low Slice

This command sets the slice level to the MTU to the low level (7%). This command is effective only for the erase instruction.

h. Code OB Reset Low Slice

This command returns the slice level to the normal level.

i. Set Communication Registers

This command sets or resets the registers by using 4 lower bits of the Bus Out and specifying greater than 8 for its upper bits. A 4-byte register can be set or reset in units of 4 bits.

- (4) The definition of the Bus in bit in the Status Tag is as follows:

- a. Bit O ERS

When the MTU is in the erase status, this bit is "1".

b. Bit 1 FWD

When the forward status is determined, this bit is set to "1".

c. Bit 2 BWD

When the backward status is determined, this bit is set to "1".

d. Bit 3 Write Status

When the MTU is in the write status, this bit is set to "1".

e. Bit 4 Tape Unit (TU) Check

When this bit is "1", it indicates that an abnormal condition is occurring in the MTU.

f. Bit 5 Self-Adjust Gain Control (SAGC)

This bit is set to "1" when Set 6250 and SAGC or Set NRZI is specified while the MTU in the 6250/1600 BPI mode does not detect the BOT.

g. Bit 6 1600

When the MTU is operated in the 1600 BPI mode this bit is "1".

h. Bit 7 LWR TUIF

When this bit is "1", the MTU is set in the Loop-to-Read Through the TU Interface mode.

i. Bit 8 TAG IN

When the contents of the Bus Out bits 0 through 8 represent an odd number, this bit is set to "1".

- (5) The meaning of the Bus In bit in the Control Tag is as follows:

- a. Bit 0 through 2 Level Test 0 through 2

These bits indicate that the MTU is set to the slice level.

b. Bit 3 Test mode

The MTU is in the Test mode when this bit is "1".

c. Bit 4 EMK

This signal is set to "1" by the Set EMK signal from the MTU.

d. Bit 5 Data Security Erase (DSE)

When the MTU operates in the forward direction and in the write status, it executes the data security erase using the Set DSE from the MTC. The MTU carries out the erase action until the EOT marker is detected. When the erase action is completed, the DSE status is set to "0", and the ready signal is returned to "1". During the erase operation, the MTU is busy.

e. Bit 6 REW

This bit is set to "1" by the Set REW from the MTC when the ready signal is set to "0". During the rewind operation, the ready signal is "0" and the MTU is busy.

f. Bit 7 UNL

This bit is set to "1" by Set UNL; Online and Ready are set to "0". This bit is reset when the unload operation is completed or suspended.

g. Bit 8 TAG IN

This bit is set to "1" when the contents of Bus Out 0 through 8 represent an odd number.

- (6) The meaning of the Bus Out in the Command Tag (both the Status Tag and the Control Tag are "1") is as follows:

- a. Bit 0 (when the upper digit of the Bus Out is "0".) STRMF (Streaming Feature)

If the relevant MTU has the streaming function, this bit is "1".

b. Bit 1 (when the upper bit of Bus Out is "0".) SKIPF (Skip File Feature)

If the relevant MTU has the space file and backspace file functions, this bit is "1".

c. Bit 2 (when the upper bit of Bus Out is "O".)

This bit is always "0".

d. Bit 3 (when the upper bit of Bus Out is "O".) LWSL (Low Slice)

When the Low Slice is specified for the relevant MTU, this bit is "1".

e. Bit 4 (when the upper bit of Bus Out is "O".) STRMD (Streaming mode)

When the MTU is set in the streaming mode, this bit is "1".

f. Bit 5 (when the upper bit of Bus Out is "0".) LWR RW (Loop-Write-to-Read Through Read/Write Circuit)

When the LWR RW is specified for the relevant MTU, this bit is "1".

g. Bit 6 (when the upper bit of Bus Out is "O".) HACT (Action)

This bit is "1" during actual functioning of the MTU.

h. Bit 7 (when the upper bit of Bus Out is "0".) RDY (Ready)

This bit indicates that the MTU is ready to execute the instruction from the MTC for carrying out tape action.

i. Register 0 through 3 (when the upper digits of the Bus Out are 8 through F.)

This bit represents the contents of the communication register set by the MTC.

j. Bit 8 TAG IN

This bit is "1" when contents of the Bus Out O through 8 is an odd number.

(7) The Bus Out/ Bus In line in the Go Tag

When the Go Tag is set to "1", the Bus Out line has the following meanings:

- a. If the MTU is in the READ status and is to carry out the read action in a recording mode other than the NRZI mode, the read threshold level is specified without the presence of the write clock. The MTU if effective for both the FWD and the BWD operations.

- b. If the MTU is in the Write status and neither LWR TUIF nor LWR RW is set, the MTU outputs the write data on magnetic tape with the presence of the write clock.

- c. When the MTU is set in the LWR (Loop Write-to-Read) TUIF or LWR RW, the MTU outputs the turnaround data to the Bus In line.

- d. When the Go Tag is "1", the TU Sense Byte 8 is output to the Bus In line if the status is set to "1".

- e. In case of items (a) and (b) above, the data output on to the Bus In line is the read data from the loaded magnetic tape. In case of item (c) above, the Bus Out loop data of LWR TUIF or LWR RW, and the content of the TU Sense Byte 8 is output.

- (8) Sense Byte

When all Tag lines are "O" or both Go Tag and the Status Tag are "1", the Bus In line indicates the particular sense information. Table 3.4 shows the contents of the sense information.

| œ                | *3&5 or GO & STS<br>TAG   | UERS (Unit Erase<br>(Current ON)         | UACT (Unit<br>Action)   | UBWD (Unit<br>Backward)  | UWCON (Unit Write<br>Current<br>ON)       | u64S (Unit 64%<br>Slice)  | UOVRN (Unit Over<br>Run 20 m<br>Check) | UPE (Unit PE<br>Mode) | TM (Tape Mark)  | TAG IN |

|------------------|---------------------------|------------------------------------------|-------------------------|--------------------------|-------------------------------------------|---------------------------|----------------------------------------|-----------------------|-----------------|--------|

| 7                | 0                         | Error<br>Code O                          |                         | " 2                      | ຕ<br>ະ                                    | 4                         | ÷                                      | . 6                   |                 | TAG IN |

| 9                | -                         | Read<br>Data O                           | 1                       | " 2                      | ۍ<br>۴                                    | 4                         | <b>1</b><br>2                          |                       |                 |        |

| S                | 2                         | sAGC<br>Count 0                          | :                       | :                        | :                                         | EC<br>Level 2             | :                                      | 7<br>:                | :               | TAG IN |

| 4                | æ                         | Tape Unit<br>Unique ID<br>Low Order<br>2 | . 2                     | 7<br>:                   | :                                         | . 2                       | :                                      | 2<br>1                | 5<br>÷          | TAG IN |

| e                | 4                         | MTU Model                                | MTU Model               | Ready<br>Holđ            | Tape Unit<br>Unique ID<br>High Order<br>2 | : 2                       | : 2                                    | :                     | 2               | TAG IN |

| 2                | Ś                         | MISC Error                               | Tape Loop<br>Alarm Left | Tape Loop<br>Alarm Right | ROM parity<br>Error                       | Write<br>Circuit<br>Alarm | Not Use                                | Air<br>Alarm          | Load<br>Failure | TAG IN |

| -1               | ور                        | EXT IF                                   | Reset Key               | DSE                      | 7 Track                                   | Test Mode                 | Dual<br>Density                        | High<br>Density       | 6250            | TAG IN |

| 0                | 7, 8<br>all "0"           | BWD                                      | Not FP                  | TWA                      | BOT                                       | Write<br>Status           | Online                                 | TU Check              | Ready           | TAG IN |

| TU Sense<br>Byte | Bus Out Bit<br>Bus In Bit | 0                                        | 7                       | 2                        | ę                                         | 4                         | Ś                                      | ę                     | 7               | ø      |

Table 3.4 Contents of the MTU Sense Byte Bus In

$\bigcirc$

$\bigcirc$

O

- a. Sense Byte 0

- Bit 0 Backward (BWD) This bit is "1" when the MTU is in the backward status.

- Bit 1 No File Protect (FP) This bit is "1" when the MTU is not file protected.

- 3) Bit 2 Tape Warning Area (TWA) When the current tape position is in the Tape Warning Area (that is, when the EOT is detected in the forward direction), this bit is set to "1". When EOT is detected in the backward direction, this bit is set to "0".

- 4) Bit 3 Beginning of Tape (BOT) This bit is "1" when the BOT marker has been detected.

- 5) Bit 4 Write Status This bit is "1" when the MTU is in the Write Status.

- 6) Bit 5 Online This bit is set to "1" when the MTU meets online requirements and the Online switch is depressed.

- 7) Bit 6 Tape Unit Check This bit is "1" when a malfunction of the MTU occurs.

- 8) Bit 7 Ready This bit indicates that the MTU is ready to execute the instruction for tape operation.

- 9) Bit 8 TAG IN Of the Bus Out bits 0 through 8, only bits 7 or 8 indicate "1".

- b. Sense Byte 1

- 1) Bit 0 Extended Interface (EXTIF) This bit indicates "1" if the MTU is provided with the streaming function or the skip-file function.

- 2) Bit 1 Reset Key This bit is "O" when the reset key on the operator panel is depressed or the door is manually opened.

- 3) Bit 2 Data Security Erase (DSE) This bit is "1" while the MTU is executing the data security erase.

- Bit 3 Not Used. This bit is always "0".

- 5) Bit 4 Test Mode This bit is "1" when the MTC specifies the Online and Set Test mode for the MTU.

- 6) Bit 5 Dual Density Feature This bit is "1" if the MTU is of two different recording density types: either 6250/1600 BPI or 1600/800 BPI.

- 7) Bit 6 High Density Mode This bit is "1" when the MTU is set in the high recording density mode.

- 8) Bit 7 6250 Feature This bit is "1" when the MTU is set in the 6250/1600 BPI mode.

- 9) Bit 8 TAG IN Of the Bus Out bits 0 through 8, only bit 6 is "1".

- c. Sense Byte 2

- Bit 0 MISC Error (miscellaneous Error) This bit is set to "1" when the MTU detects an error occurring somewhere other than the bits in Sense Byte 2.

- 2) Bit 1 Tape Loop Alarm Left This bit is set to "1" when the running tape enters the warning area in the left column.

- 3) Bit 2 Tape Loops Alarm Right This bit is set to "1" when the running tape enters the warning area in the right column.

- 4) Bit 3 ROM Parity Error This bit is set to "1" when a parity error takes place in the PROM of the MTU.

- 5) Bit 4 Write Circuit Alarm This bit is set to "1" when an abnormal condition occurs in the write circuit system.

- 6) Bit 5 Not Used This bit is always "0".

- 7) Bit 6 Air Bearing Alarm This bit is set to "1" when abnormal pressure is detected.

- Bit 7 Load Failure This bit is set to "1" when the MTU fails in autoloading.

- 9) Bit 8 TAG IN Of the Bus Out bits 0 through 8, bit 5 indicates "1".

- d. Sense Byte 3

- Bits 0, 1 MTU Models 0, 1 The bits 0 and 1 specify the following models:

| Bit O | Bit 1 | Model   |

|-------|-------|---------|

| 0     | 0     | 125 ips |

| 0     | 1     | 50 ips  |

| 1     | 0     | 200 ips |

| 1     | 1     | 75 ips  |

| 1     | 1     |         |

- 2) Bit 2 Ready Hold This bit is set to "1" when the MTU changes its status from Not Ready to Ready.

- Bit 3 (2<sup>1</sup><sup>2</sup>) through bit 7 (2<sup>8</sup>) This bit indicates the Tape Unit Unique ID High Order.

- 4) Bit 8 TAG IN Of the Bus Out bits 0 through 8, only bit 4 indicates "1".

- e. Sense Byte 4

- 1) Bits 0 (2<sup>7</sup>) through 7 (2<sup>o</sup>) indicate the Tape Unit Unique ID Low Order.

- 2) Bit 8 TAG IN Of the Bus Out bits 0 through 8, only bit 3 indicates "1".

- f. Sense Byte 5

- 1) The bits 0 through 3 indicate the maximum value of the SAGC count.

- 2) The bits 4 (2 <sup>3</sup>) through 7 (2 <sup>9</sup>) indicate an EC level.

- Bit 8 TAG IN

Of the Bus Out bit 0 through 8, only bit 2 indicates "1".

- g. Sense Byte 6

When the Bus Out bit 1 is set to "1" after the Go Tag is reset, the MTU sends out the Read data to the Bus In. bits 0 through 8 of the Bus In represent the Read data.

- h. Sense Byte 7

- Bits 0 through 7 indicate an error code Error code 00 indicates that the power supply condition and the MTU condition are normal. Error codes 01 through 99 indicate the contents of an erroneous operation and a unit failure.

- 2) Bit 8 TAG IN Of the Bus Out bits 0 through 8, only bit 0 indicates "1".

- i. Sense Byte 8

This byte is effective when all bits of the Go, Control, and the Status Tag, are zeros and both BO3 and BO5 are "1"s. This byte is also effective when both the Go Tag and the Status Tag are "1".

- Bit 0 UERS (Unit Erase Current ON) This bit indicates the state of the current flow in the erase head of the MTU.

- 2) Bit 1 UACT (Unit Action) This bit is "1" while the MTU is in a range of operation from the actual start of the MTU operation to the end of its operation. (The turn-around time is not included. However, it is included during positioning of the MTU.)

- 3) Bit 2 UBWD (Unit Backward Status) This bit indicates that the MTU is in the Backward status. The signal varies with the advancement of the MTU operation during the Forward operation or stop position.

- 4) Bit 3 UWCON (Unit Write Current ON) This bit indicates that the current is flowing in the write head of the MTU.

- 5) Bit 4 U64S (Unit 64% Slice) This bit indicates that in the 6250 BPI read/write operation, the slice level is cut down to 64% after counting up the Self-Adjust Gain Control.

- 6) Bit 5 UOVRN (Unit Overrun) This bit indicates that the length of data block (TMBOB) did not exceed 20 m while the MTU executed the Space file operation.

- 7) Bit 6 UPE (Unit PE Mode) This bit indicates that the operation mode in which the MTU is actually carrying out the processing is the Phase Encoded (PE) mode.

- 8) Bit 7 TM (Tape Mark) This bit is set to "1" when the MTU normally detects a TM block using the SPF or BSPF command.

- 9) Bit 8 TAG IN If the Bus Out bits 0 through 8 are an odd number, this bit is "1".

## Table 3.5 Error codes list

| Item                                     | Error<br>code | Content                                                                                                | Cause             |

|------------------------------------------|---------------|--------------------------------------------------------------------------------------------------------|-------------------|

| Abnormal<br>states of<br>arithmetic      | 00            | Parity error of the ROM occurring<br>before executing the microprogram<br>(when unit check lamp light) | Hardware<br>error |

| circuits,<br>registers,<br>timers,       | 01            | Faculty arithmetic operation of the ALU                                                                | **                |

| counter, and<br>sense signals            | 02            | Faculty arithmetic operation of the microprogram                                                       | 11                |

|                                          | 03            | Malfunction of the register<br>LSI for file address \$00 ~ \$03.                                       | **                |

|                                          | 04            | Malfunctioning of the register<br>LSI for file address \$04 ~ \$07.                                    | ••                |

| an a | 05            | Malfunctioning of the register<br>LSI for file address \$08 ~ \$0B                                     |                   |

|                                          | 06            | Malfuncitoning of the general<br>register for file address \$0C ~ \$0F                                 | ••                |

|                                          | 07            | Malfunctioning of timer 0 for file<br>address \$10                                                     | "                 |

|                                          | 08            | Malfuncitoning of timer 1 for file<br>address \$11                                                     | 11                |

|                                          | 09            |                                                                                                        |                   |

|                                          | 10            | Malfuncitoning of the counter for file address \$12                                                    | Hardware<br>error |

|                                          | 11            | Malfuncitoning of the register for file address \$13                                                   | **                |

|                                          | 12            | One to more faulty bits from bits 0, 4, and 5 for file address \$14                                    | **                |

|                                          | 13            | One or more faulty bits from bits 0, 1, and 4 for file address \$15                                    | **                |

|                                          | 14            |                                                                                                        |                   |

|                                          | 15            | One or more faulty bits from bits<br>6 and 7 for file address \$17                                     | Hardware<br>error |

|                                          | 16            | Malfunctioning of the register for file address \$18                                                   | **                |

$\bigcirc$

$\bigcirc$

$\bigcirc$

| Item                                                   | Error<br>code | Content                                                                                                                               | Cause             |

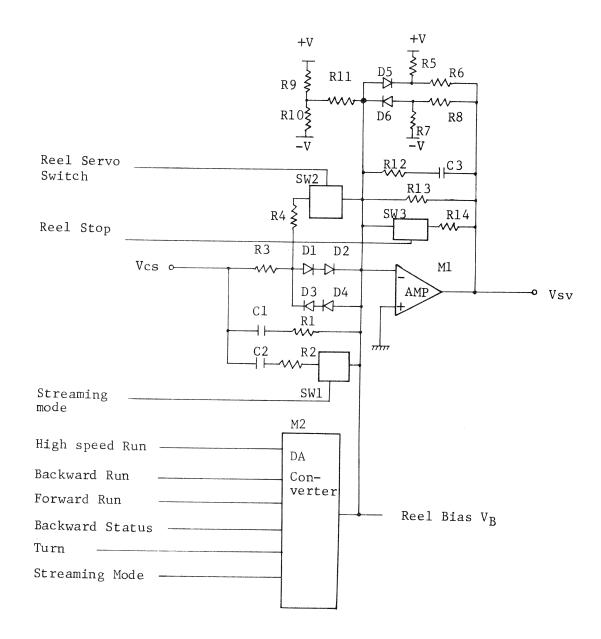

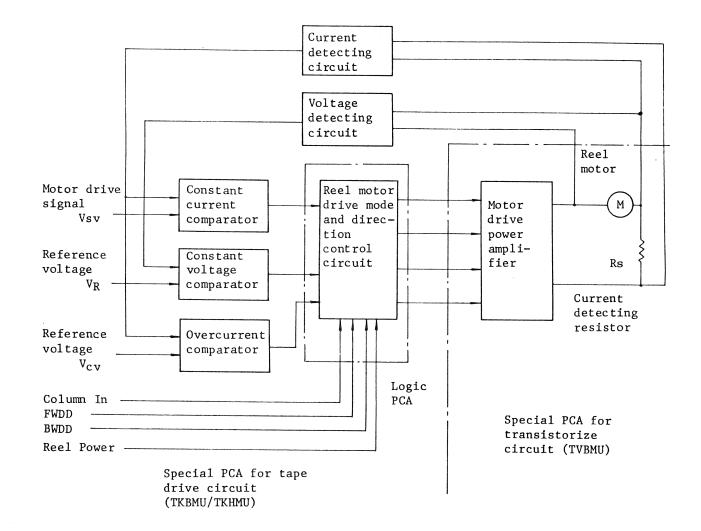

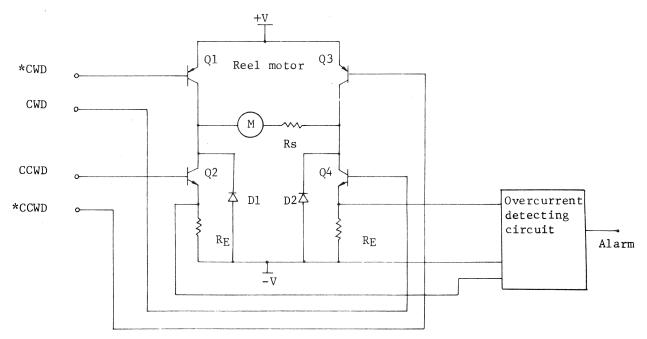

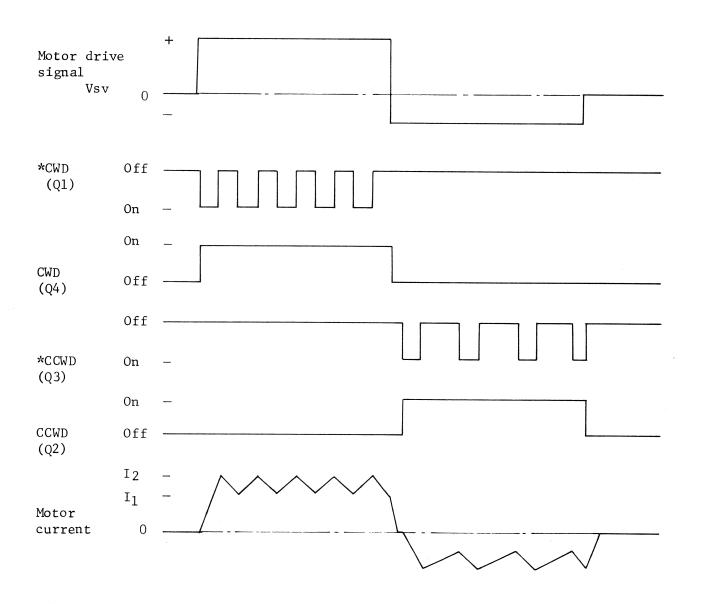

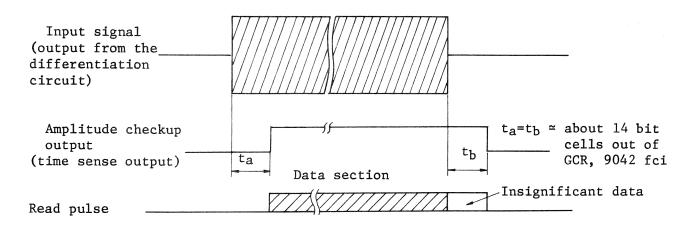

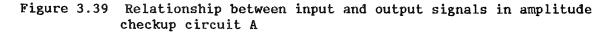

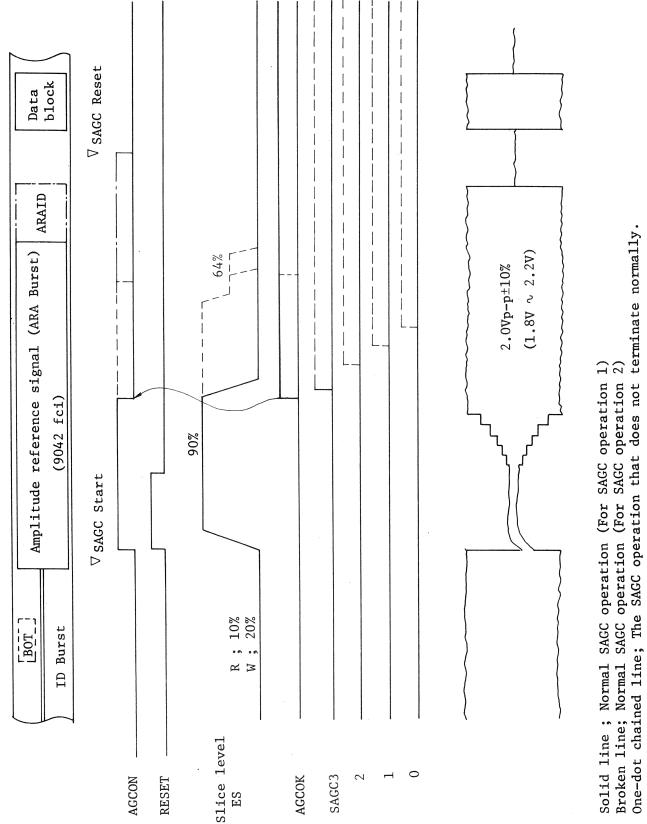

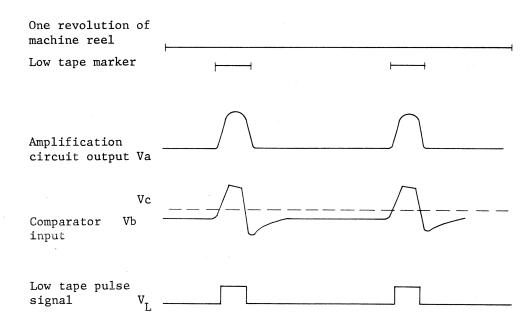

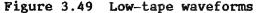

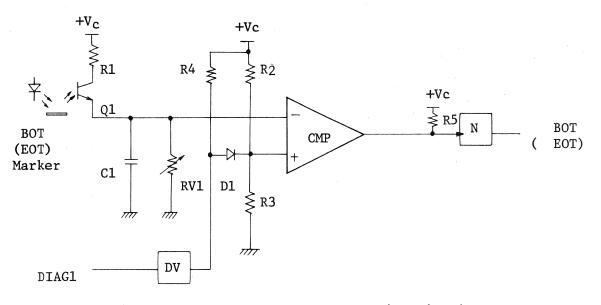

|--------------------------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------|