# COPY # 10

# UNIVAC R CALCULATING TABULATOR

PROCESSOR MANUAL

SECTIONS: 4 & 5 APPENDIX: C

#### <u>COMPANY CONFIDENTIAL</u>

### **REGISTERED CIRCULATION**

The information contained in this manual is the property of the Sperry Rand Corporation and is Company Confidential. It is submitted in confidence and should not be disclosed to others unless so disclosed in confidence with the permission of Remington Rand Univac, Division of Sperry Rand Corporation, being first obtained. This copy is numbered and is so registered in your name in our records. The document is not to be reproduced or duplicated without express permission in writing from a duly authorized representative of the Sperry Rand Corporation. This manual is subject to recall.

> REMINGTON RAND UNIVAC DIVISION OF SPERRY RAND CORP. Philadelphia, Pa. March 1958

|              | SECTION IV                                                              |                       |

|--------------|-------------------------------------------------------------------------|-----------------------|

|              | <b>我</b> 你来你不知道你,你不知道你们的你。"                                             | $f_{i}(t) = f_{i}(t)$ |

| · · ·        | TABLE OF CONTENTS                                                       |                       |

| n water (19  |                                                                         |                       |

| Paragraph    | Title                                                                   | Pag                   |

| <i>A</i> 0   |                                                                         |                       |

| 4-2<br>4-5   | Basic Operation Cycle                                                   | 4-                    |

|              | Search-for-Instruction Step.                                            | 4-                    |

| 4-9<br>4-20  | Locating the Memory Address                                             | 4-                    |

| 4-20         | Comparison and Head Selection                                           | 4-1                   |

| 4-40         | Band Selection                                                          | 4-1                   |

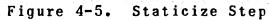

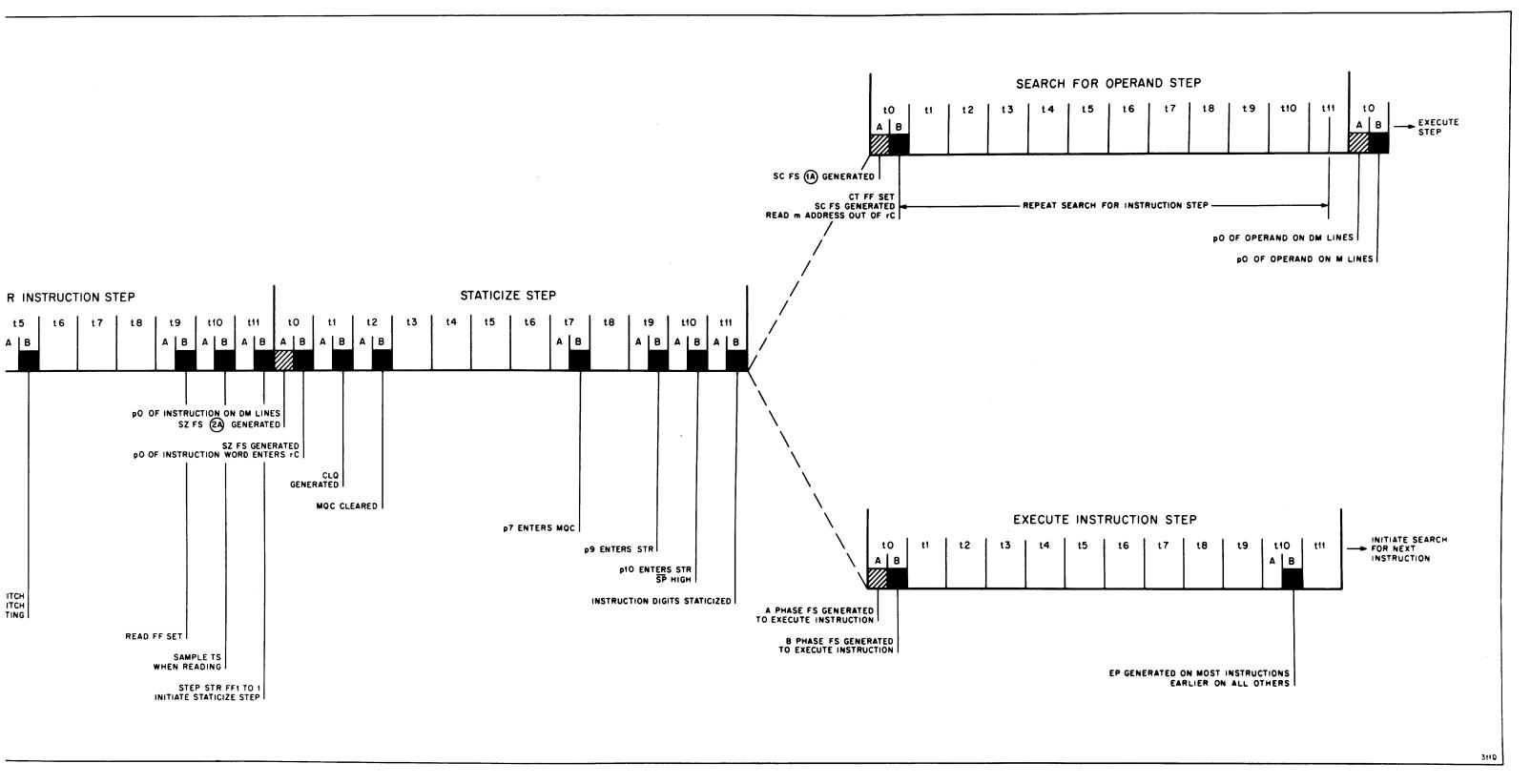

| 4-47         | Staticize-Instruction Step                                              | 4-1                   |

| 4-52<br>4-54 | Storing the p7 Digit                                                    | 4-2                   |

| 4-55         | Storing the Instruction Word                                            | 4-2                   |

| 4-58         | Staticizing the Instruction                                             | 4-2                   |

| 4-50         | Search-for-Operand Step<br>Instruction Code Characteristics             | 4-2                   |

| 4-62         |                                                                         | 4-2<br>4-2            |

| 4-67         | Locating the Operand                                                    | 4-2                   |

| 4-70         | Execute-Instruction Step                                                | 4-2                   |

| 4-72         | Two-Execution-Step Instructions                                         | 4-2                   |

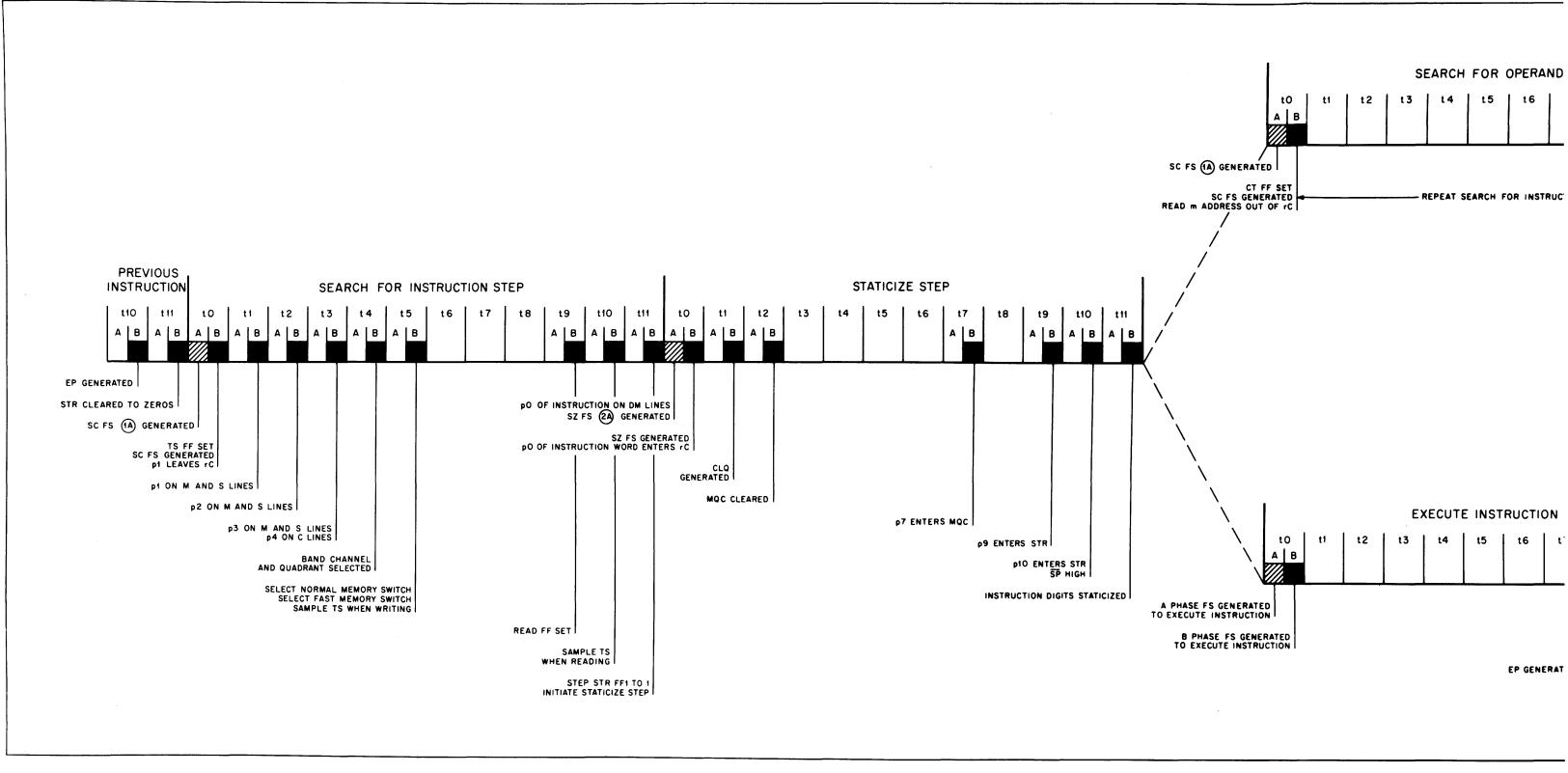

| 4-72         | Timing of the Basic Operation Cycle<br>Processing a Typical Instruction | 4-2                   |

| 4-74         | Search for Operand                                                      | 4-2                   |

| 4-83         | Execute the H(60) Instruction                                           | 4-3                   |

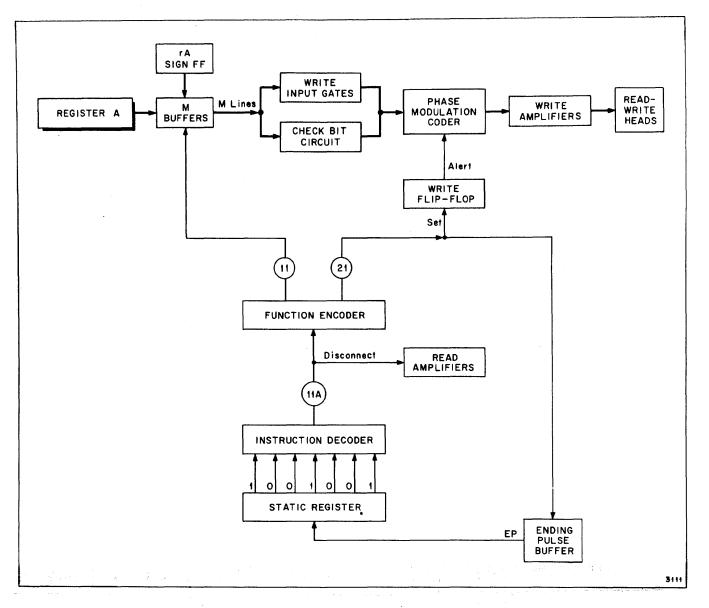

| 4-88         | Memory Write Operation                                                  | 4-3                   |

| 4-92         | Arithmetic Operations                                                   | 4-3                   |

| 4-93         | Addition and Subtraction                                                | 4-3                   |

| 4-94         | Add Instruction                                                         | 4-3                   |

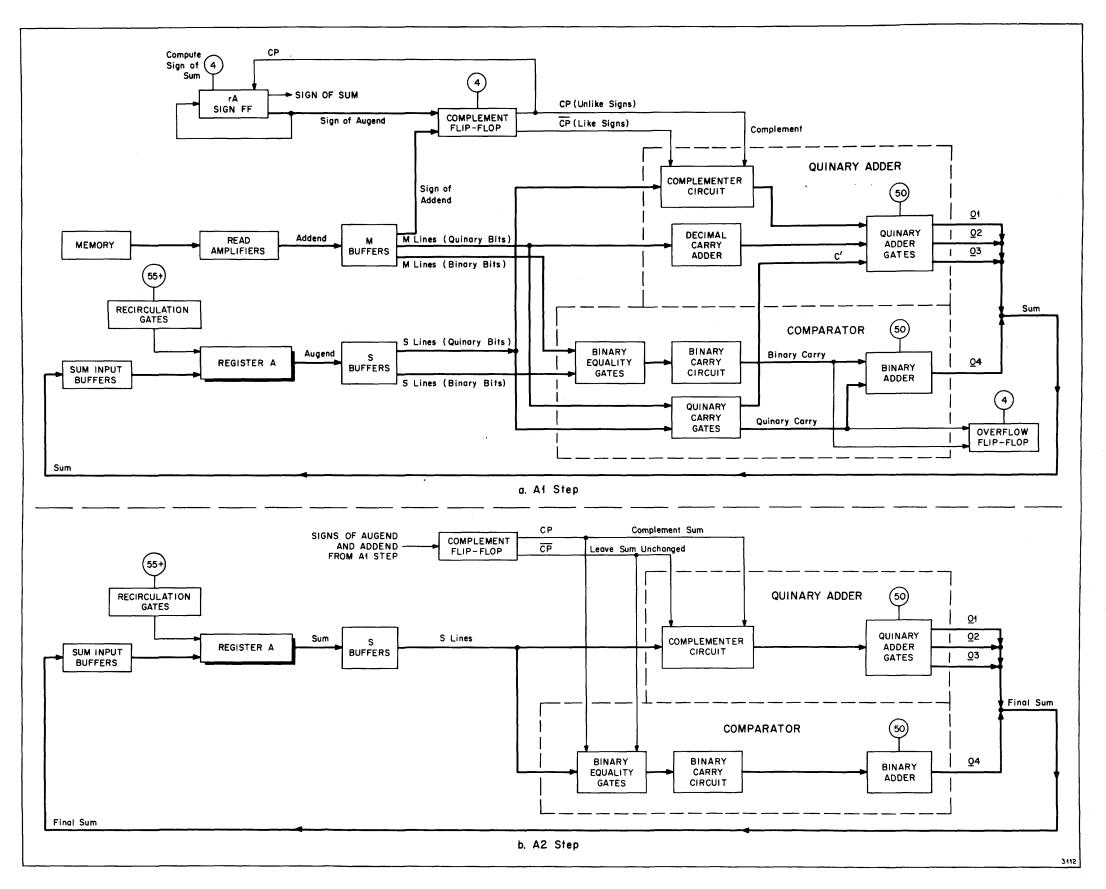

| 4-96         | Al Step                                                                 | 4-3                   |

| 4-109        | A2 Step                                                                 | 4-4                   |

| 4-112        | Subtraction                                                             | 4-4                   |

| 4-116        | Sample Problems                                                         | 4-4                   |

| 4-118        | Addition                                                                | 4-4                   |

| 4-120        | Subtraction                                                             | 4-4                   |

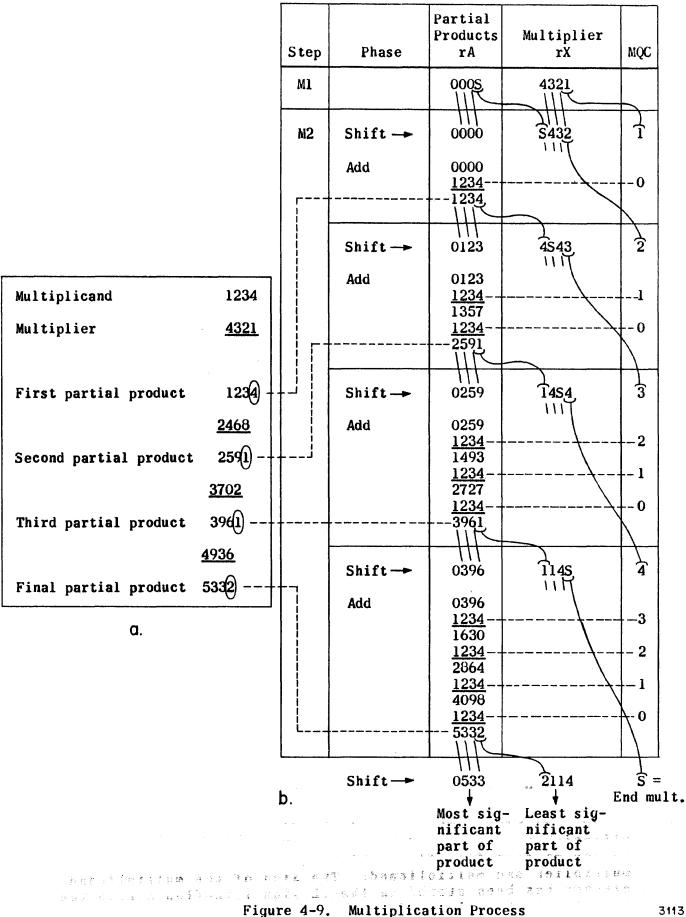

| 4-127        | Multiplication                                                          | 4-4                   |

| 4-135        | General Description                                                     | 4-4                   |

| 4-138        | Detailed Description                                                    | 4-4                   |

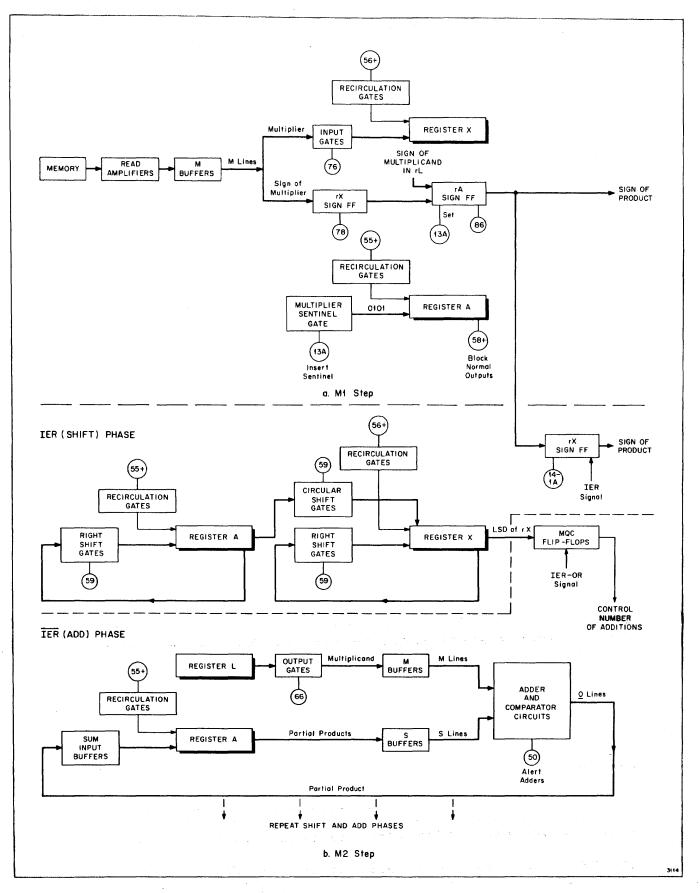

| 4-139        | M1 Step                                                                 | 4-4                   |

| 4-144        | M2 Step                                                                 | 4-5                   |

| 4-145        | IER Phase                                                               | 4-5                   |

| 4-150        | IER Phase                                                               | 4-5                   |

| 4-153        | Division                                                                | 4-5                   |

| 4-156        | General Description                                                     | 4-5                   |

| 4-175        | Detailed Description                                                    | 4-5                   |

| 4-176        | D1 Step                                                                 | 4-5                   |

| 4-183        | D2 Step                                                                 | 4-5                   |

| 4-184        | OR Phase                                                                | 4-5                   |

| 4-186        | Complementing and Left Shift of rA                                      | 4-5                   |

| 4-187        | Complementing and Left Shift of rX                                      | 4-5                   |

| 4-188        | Complementing the LSD of rA                                             | 4-5                   |

| 4-190        | Jam MQC                                                                 | 4-6                   |

| 4-191        | Initiate OR Phase                                                       | 4-6                   |

| 4-192        | OR Phase                                                                | 4-6                   |

i

|                                                                                                                                                                                                                                      | and the state of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 4-193                                                                                                                                                                                                                                | Addition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-62                                     |

| 4-194                                                                                                                                                                                                                                | End of D2 Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-63                                     |

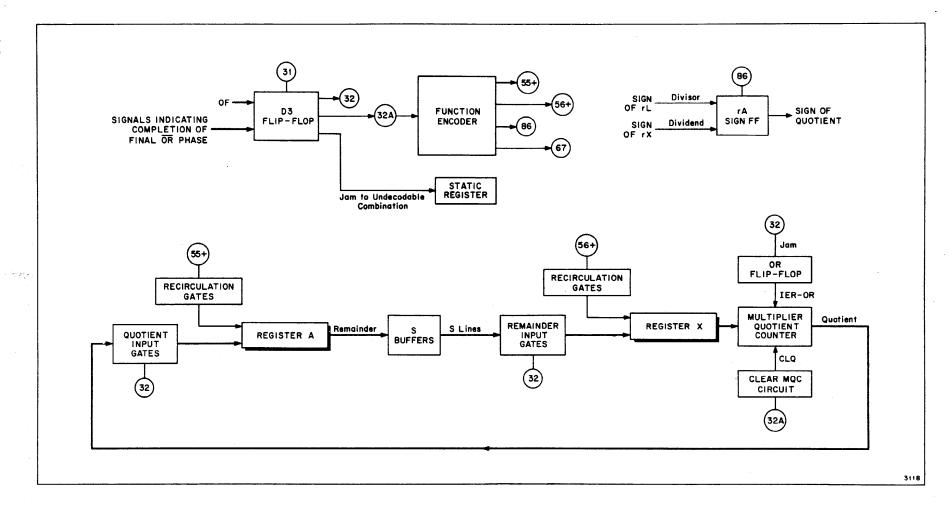

| 4-195                                                                                                                                                                                                                                | D3 Step                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-63                                     |

| 4-196                                                                                                                                                                                                                                | Interchanging rA and rX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-63                                     |

| 4-199                                                                                                                                                                                                                                | Sign of the Quotient                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-65                                     |

| 4-200                                                                                                                                                                                                                                | Error Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-65                                     |

| 4-202                                                                                                                                                                                                                                | Memory-Check Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-66                                     |

| 4-206                                                                                                                                                                                                                                | Timing-Error Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-67                                     |

| 4-210                                                                                                                                                                                                                                | Cycling-Unit Error Flip-Flop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-68                                     |

| 4-213                                                                                                                                                                                                                                | Input-Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-68                                     |

| 4-217                                                                                                                                                                                                                                | Manually-Controlled Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-69                                     |

| 4-220                                                                                                                                                                                                                                | One-Line Print                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-69                                     |

| 4-226                                                                                                                                                                                                                                | One-Card RPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-71                                     |

| 4-228                                                                                                                                                                                                                                | One-Card HSR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-71                                     |

| 4-230                                                                                                                                                                                                                                | One Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-71                                     |

| 4-232                                                                                                                                                                                                                                | Comparison Stop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-71                                     |

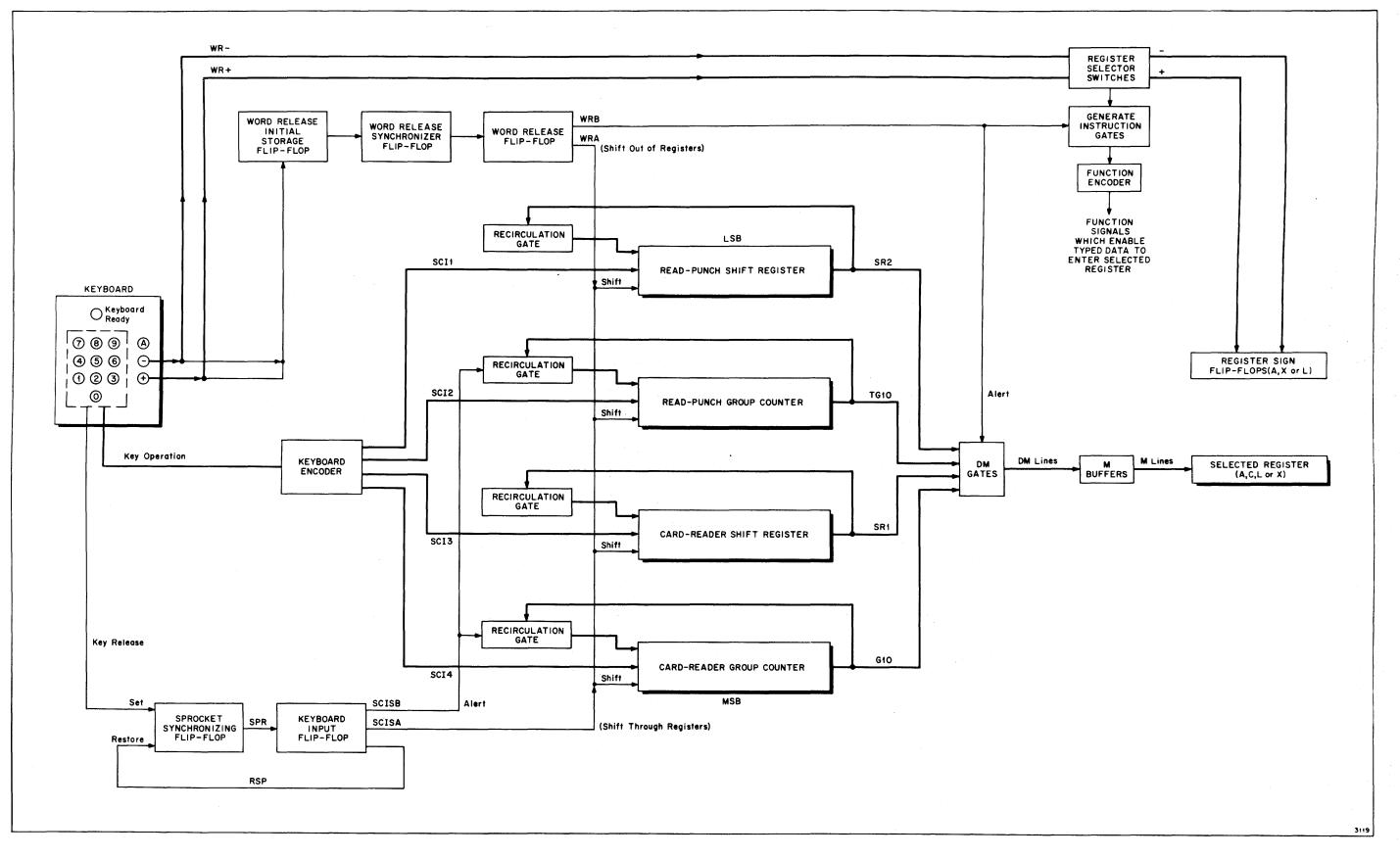

| 4-235                                                                                                                                                                                                                                | Keyboard Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-72                                     |

| 4-237                                                                                                                                                                                                                                | Manual Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-72                                     |

| 4-243                                                                                                                                                                                                                                | Depressing a Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-74                                     |

| 4-246                                                                                                                                                                                                                                | Releasing a Key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4-75                                     |

| 4-249                                                                                                                                                                                                                                | Signing and Releasing the Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-76                                     |

|                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                          |

|                                                                                                                                                                                                                                      | になっていたが、「たちに」ですが、そう。<br>「読が好い」が、「「「「」」「読」」がない。「読書」の意味である。                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |

|                                                                                                                                                                                                                                      | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                          |

| i i i i i i i i i i i i i i i i i i i                                                                                                                                                                                                | and the second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n na se                                  |

| Number                                                                                                                                                                                                                               | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page                                     |

| anna an taona an taona<br>Taona an taona an taon | - 1975年 - 19756 - 19758年 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197584 - 197  |                                          |

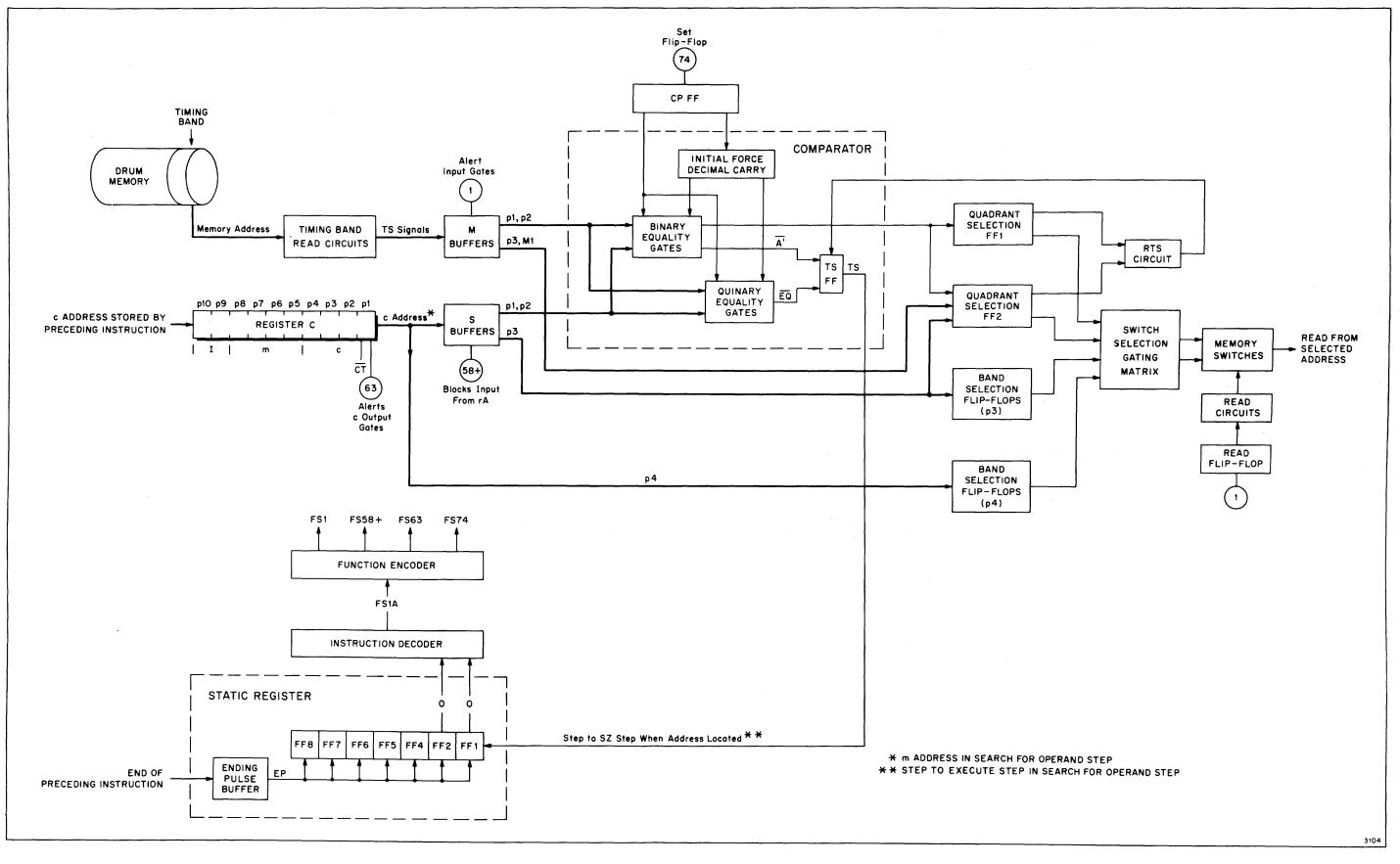

| 4-1                                                                                                                                                                                                                                  | Search Step of Basic Operation Cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4-3                                      |

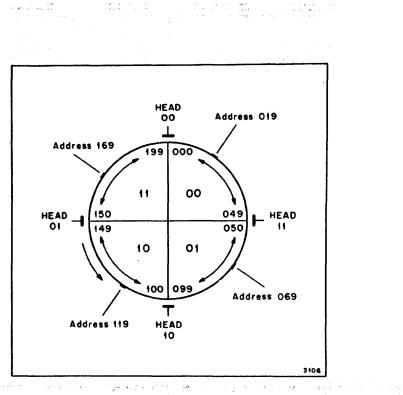

| 4-2                                                                                                                                                                                                                                  | Drum Quadrants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-5                                      |

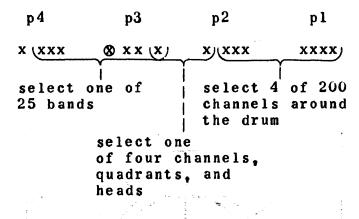

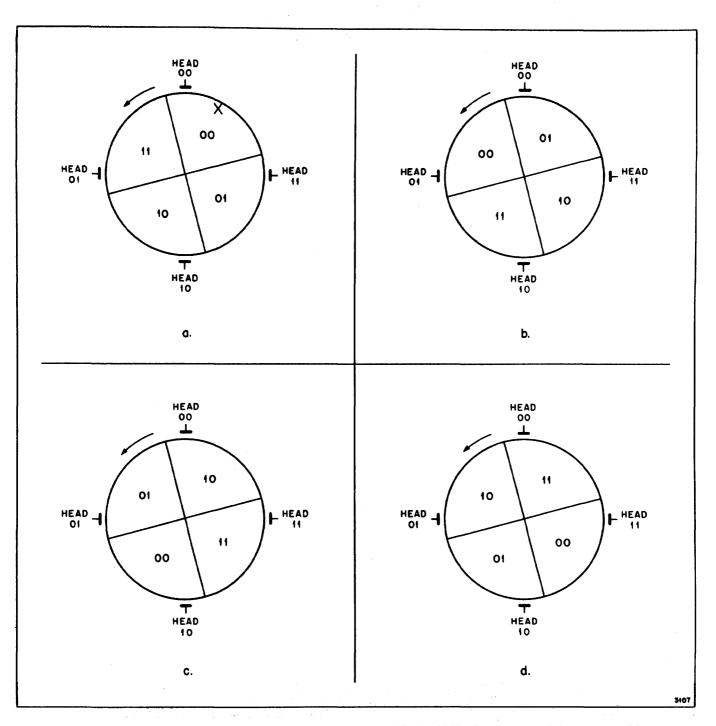

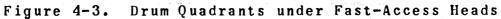

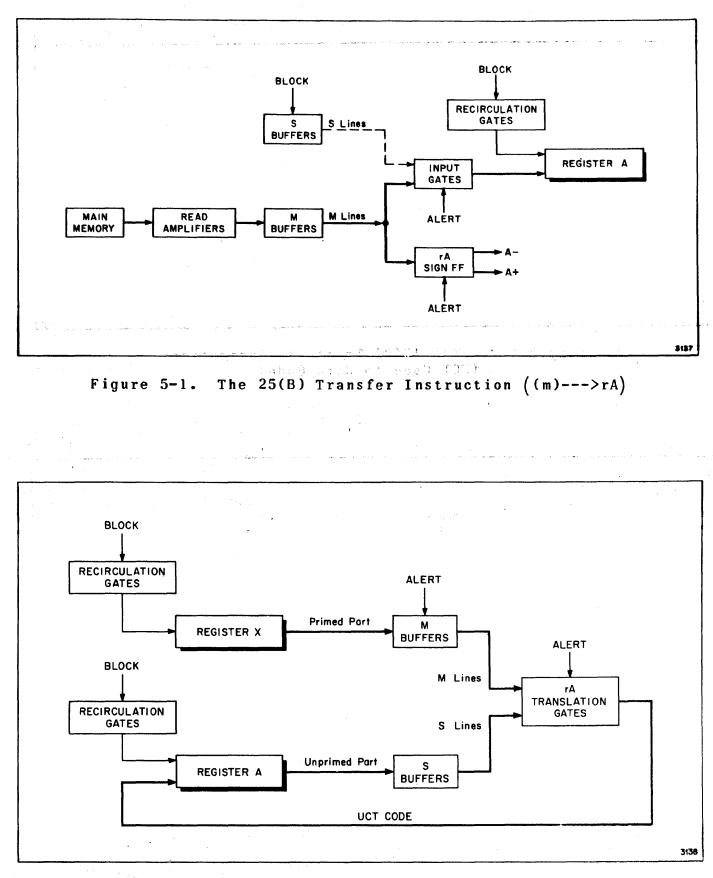

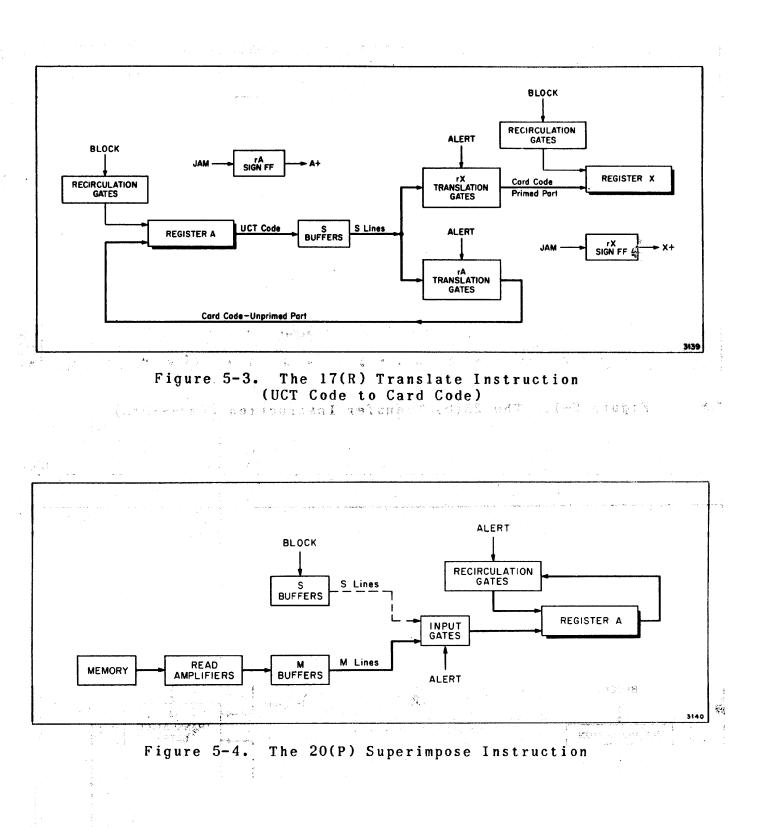

| 4-3                                                                                                                                                                                                                                  | Drum Quadrants under Fast-Access Heads                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-8                                      |