## HARDWARE TECHNICAL REFERENCE

# BUSINESS-PRO™ Professional Computer

2241092-000 April 1986

# TEXAS INSTRUMENTS

© 1986, Texas Instruments Incorporated. All Rights Reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Texas Instruments Incorporated.

#### MANUAL REVISION HISTORY

The total number of pages in this publication is 532.

The computers offered in this agreement, as well as the programs that TI has created to use with them, are tools that can help people better manage the information used in their business; but tools—including TI computers—cannot replace sound judgment nor make the manager's business decisions.

Consequently, TI cannot warrant that its systems are suitable for any specific customer application. The manager must rely on personal judgment of what is best for his or her business.

#### Contents

| Paragrap:                                                                                                                                                                              | h Title                                                                                                                                                                                                                                                                 | Page                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                        | Preface                                                                                                                                                                                                                                                                 | xiii                                                                                                  |

|                                                                                                                                                                                        | l Introduction                                                                                                                                                                                                                                                          |                                                                                                       |

| 1.1.1<br>1.1.2<br>1.1.3<br>1.2<br>1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3<br>1.2.1.4<br>1.2.1.5<br>1.2.2<br>1.2.3<br>1.2.4<br>1.2.5<br>1.2.6<br>1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.3 | Workstation Applications Local Area Networks Multiuser Environments  BUSINESS-PRO Hardware System Unit Central Processing Unit System Memory Serial and Parallel Ports Mass Storage System Expansion Slots Keyboard Display Units Optical Mouse Communications Graphics | 1-2<br>1-2<br>1-2<br>1-2<br>1-3<br>1-3<br>1-3<br>1-3<br>1-4<br>1-4<br>1-5<br>1-5<br>1-5<br>1-6<br>1-6 |

| 2.1                                                                                                                                                                                    | 2 Main Logic Board  General                                                                                                                                                                                                                                             | 2-1<br>2-8                                                                                            |

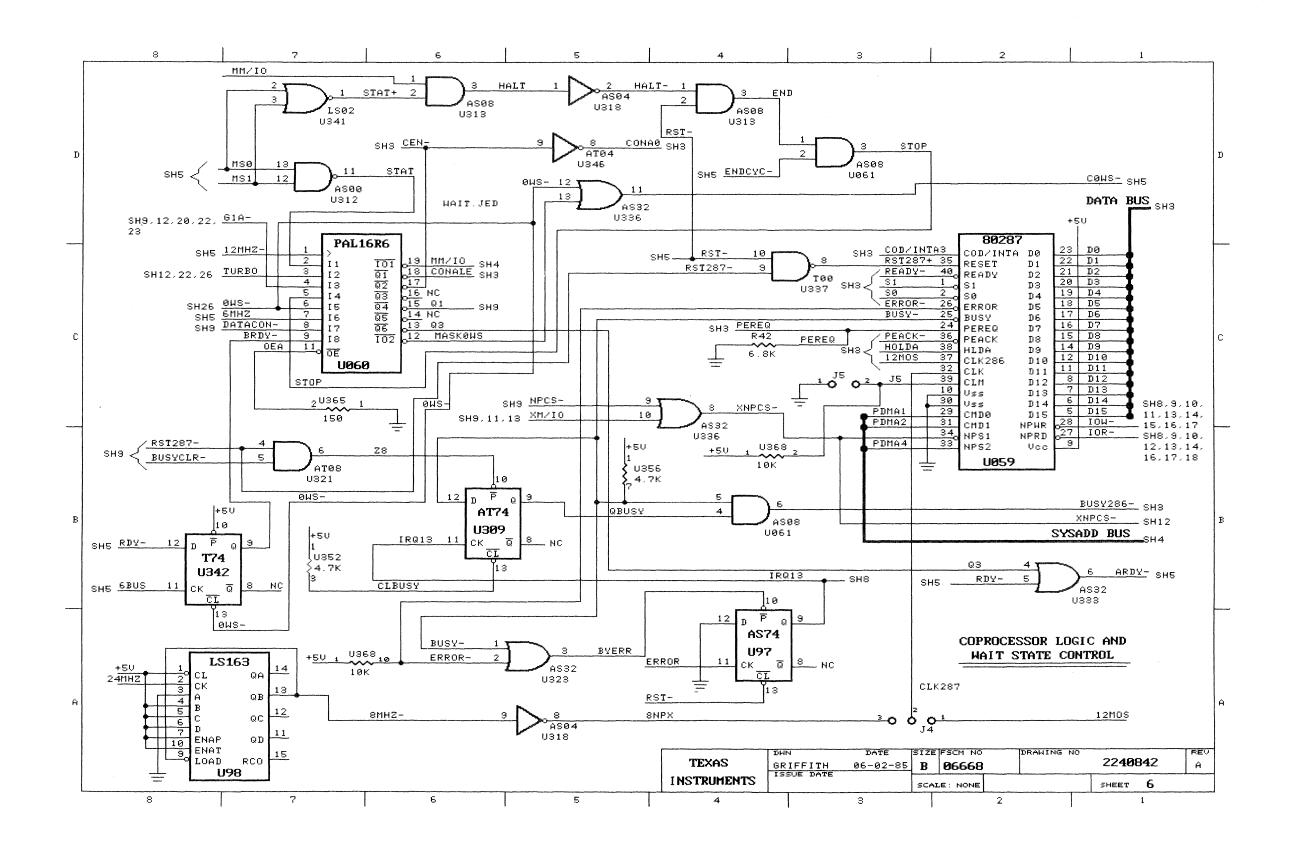

| 2.2.1<br>2.2.2<br>2.2.3<br>2.2.3.1<br>2.2.3.2<br>2.2.4<br>2.2.5<br>2.2.5.1<br>2.2.5.2<br>2.2.6                                                                                         | Microprocessor Unit Optional Numeric Coprocessor CPU Bus Buffering Address and Control Bus Buffering Data Bus Buffering CPU Clock Generation and Bus Control Reset Circuit Software Reset and Shutdown Cycles System Reset Control Signals                              | 2-8<br>2-8<br>2-8<br>2-9<br>2-11<br>2-11<br>2-11                                                      |

| Paragrap | oh Title                                   | Page  |

|----------|--------------------------------------------|-------|

|          |                                            | 0.75  |

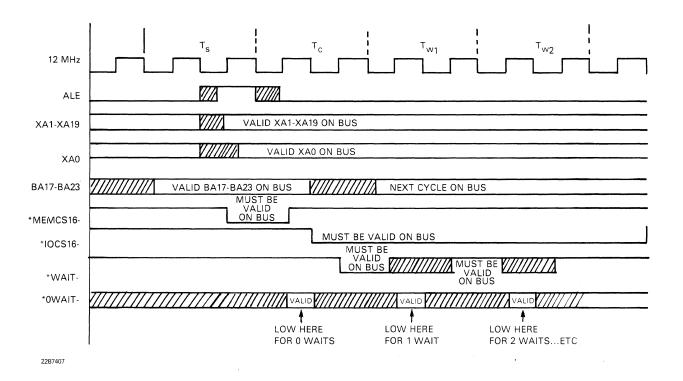

| 2.3      | Wait-State Control Logic                   | 2-12  |

| 2.3.1    | Zero-Wait-State Memory Cycles              |       |

| 2.3.2    | One-Wait-State Memory Cycles               | 2-14  |

| 2.3.3    | One-Wait-State I/O Cycles                  | 2-15  |

| 2.3.4    | Four-Wait-State Cycles                     | 2-15  |

| 2.3.5    | Ten-Wait-State Cycles                      | 2-16  |

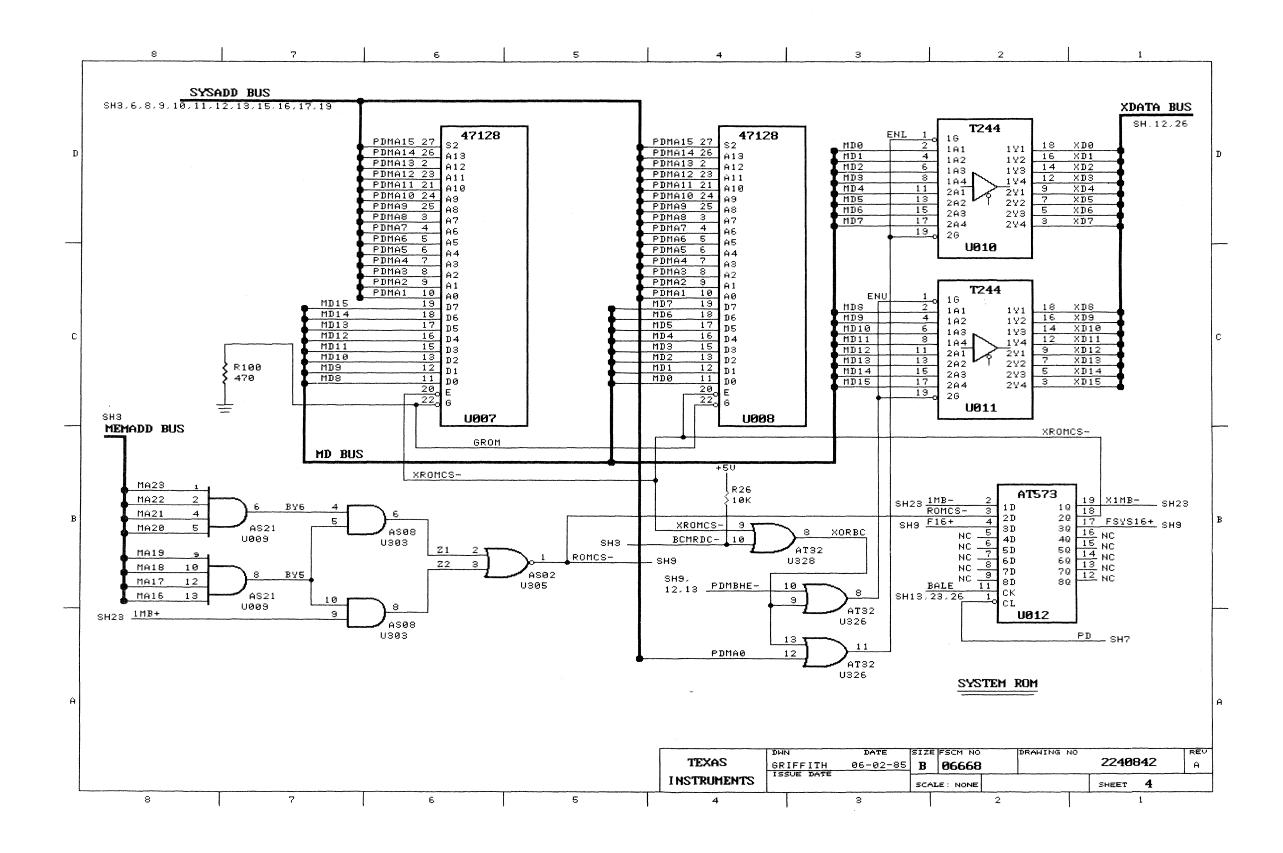

| 2.4      | System Memory                              | 2-18  |

| 2.4.1    | Main Memory                                | 2-18  |

| 2.4.2    | System ROMs                                | 2-19  |

| 2.5      | Memory Control Logic                       | 2-20  |

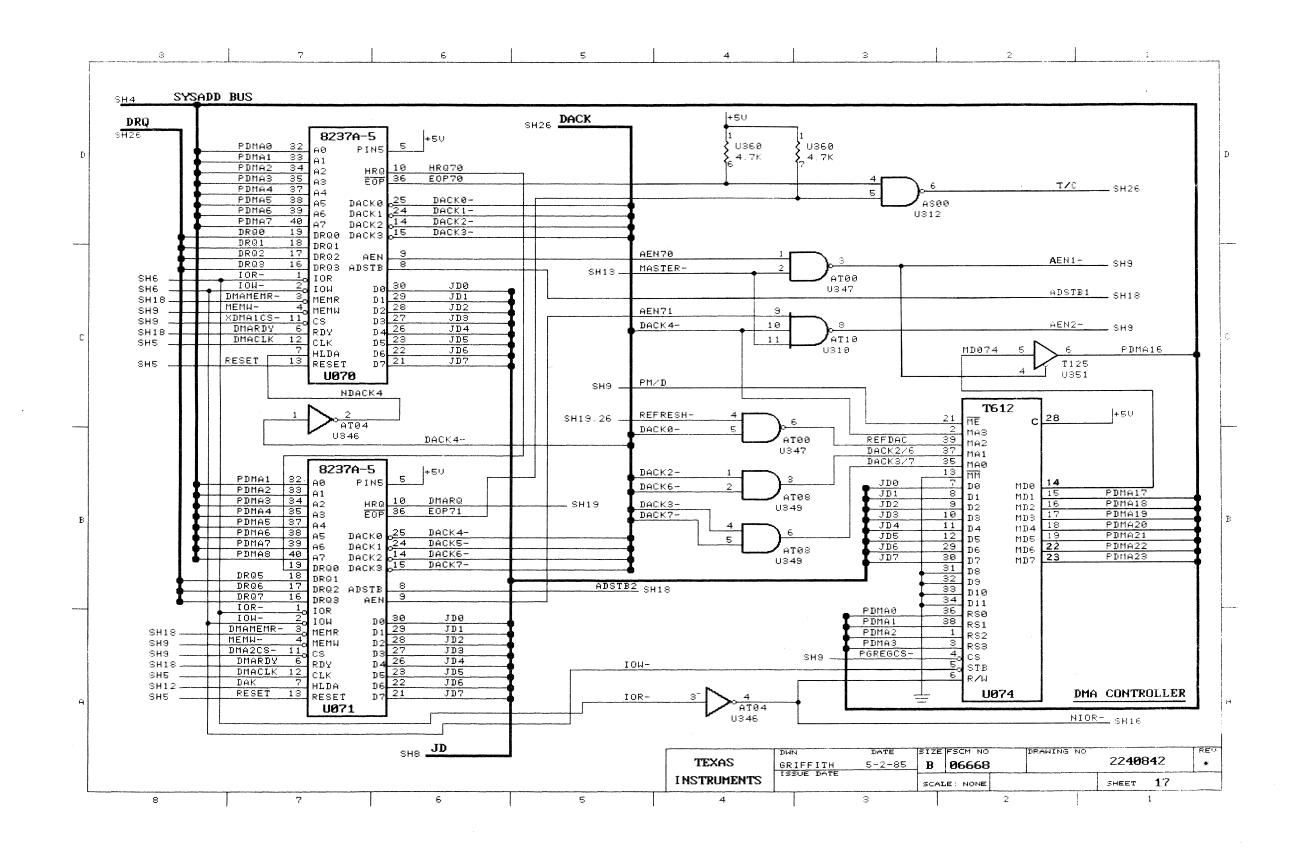

| 2.5.1    | DMA Controller and Memory Page Register    |       |

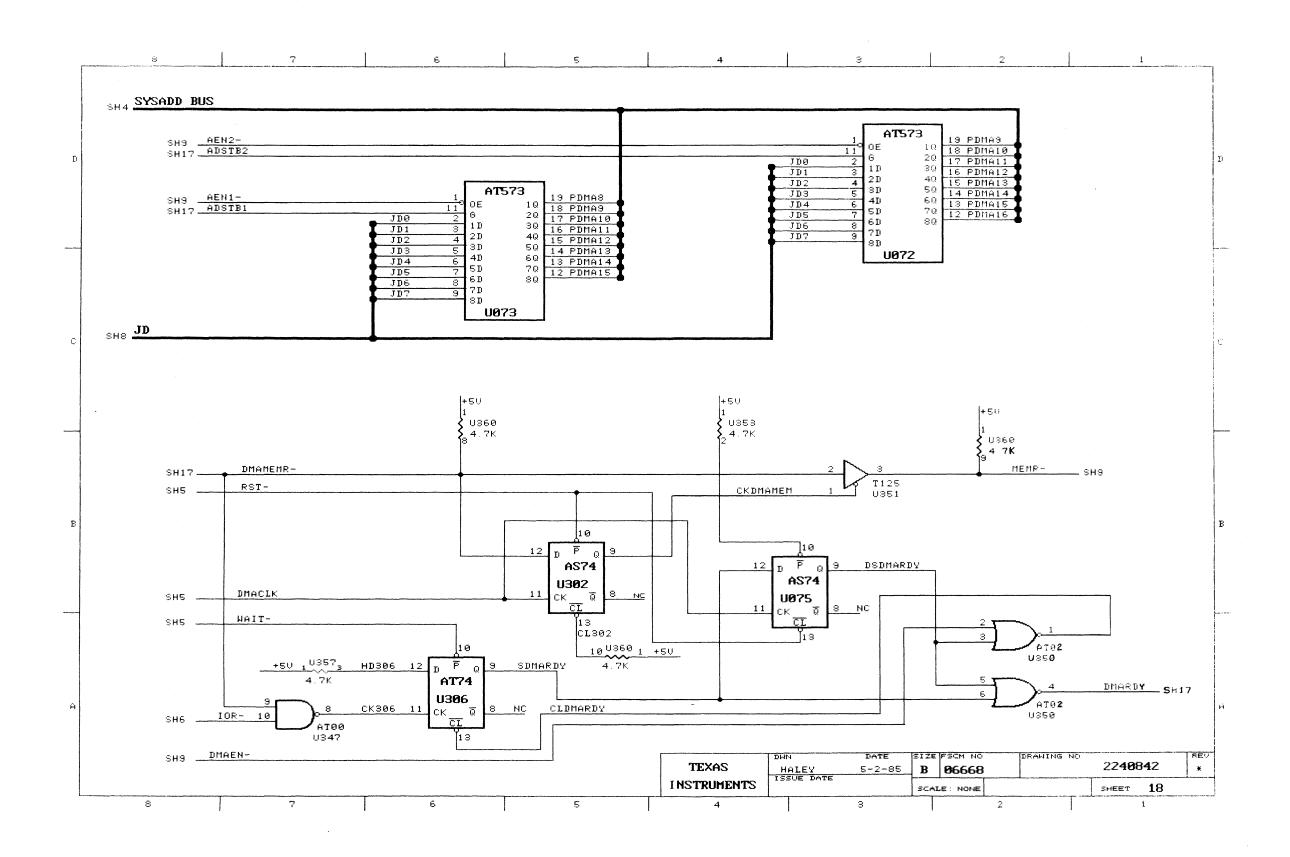

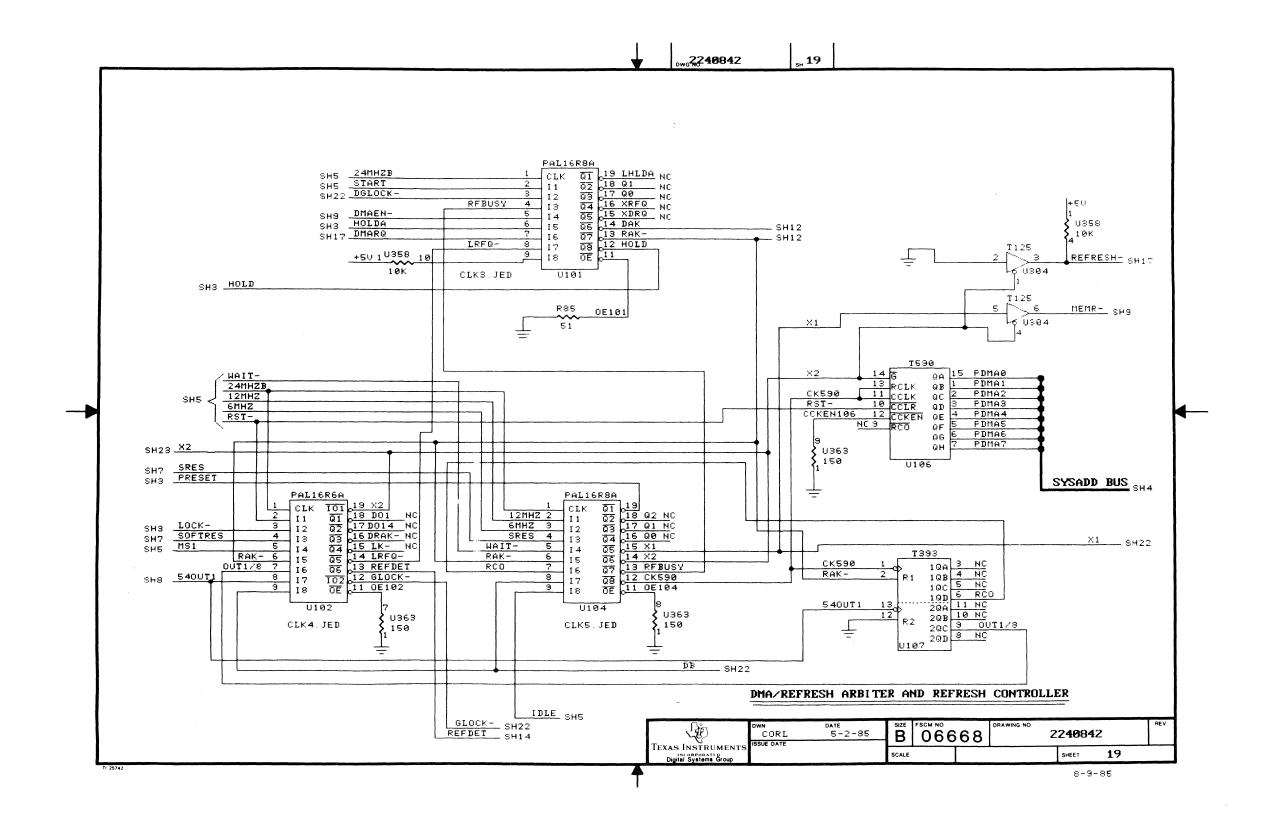

| 2.5.1.1  | DMA/Refresh Arbiter and Refresh Controller |       |

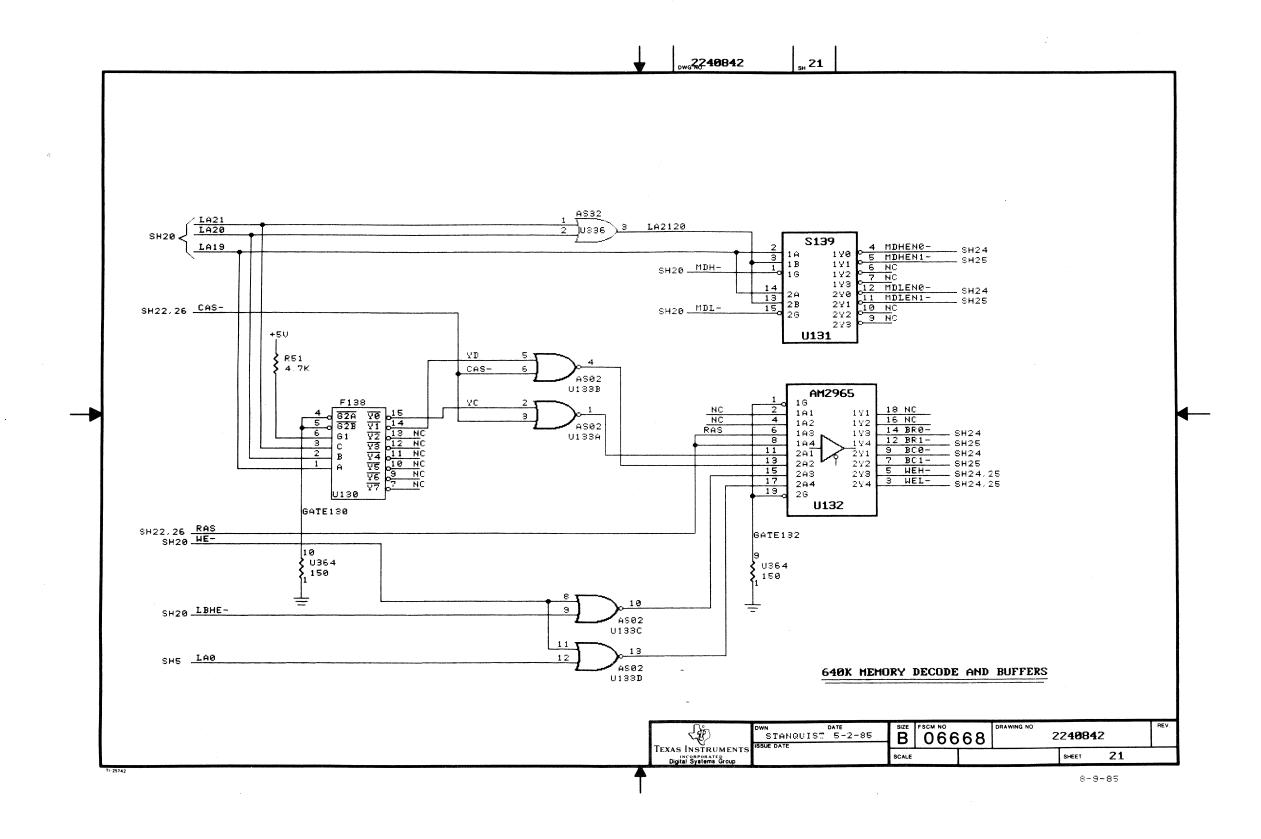

| 2.5.1.2  | Memory Degode Logic                        | 2-22  |

| 2.5.1.3  | Memory Decode Logic                        | 2-22  |

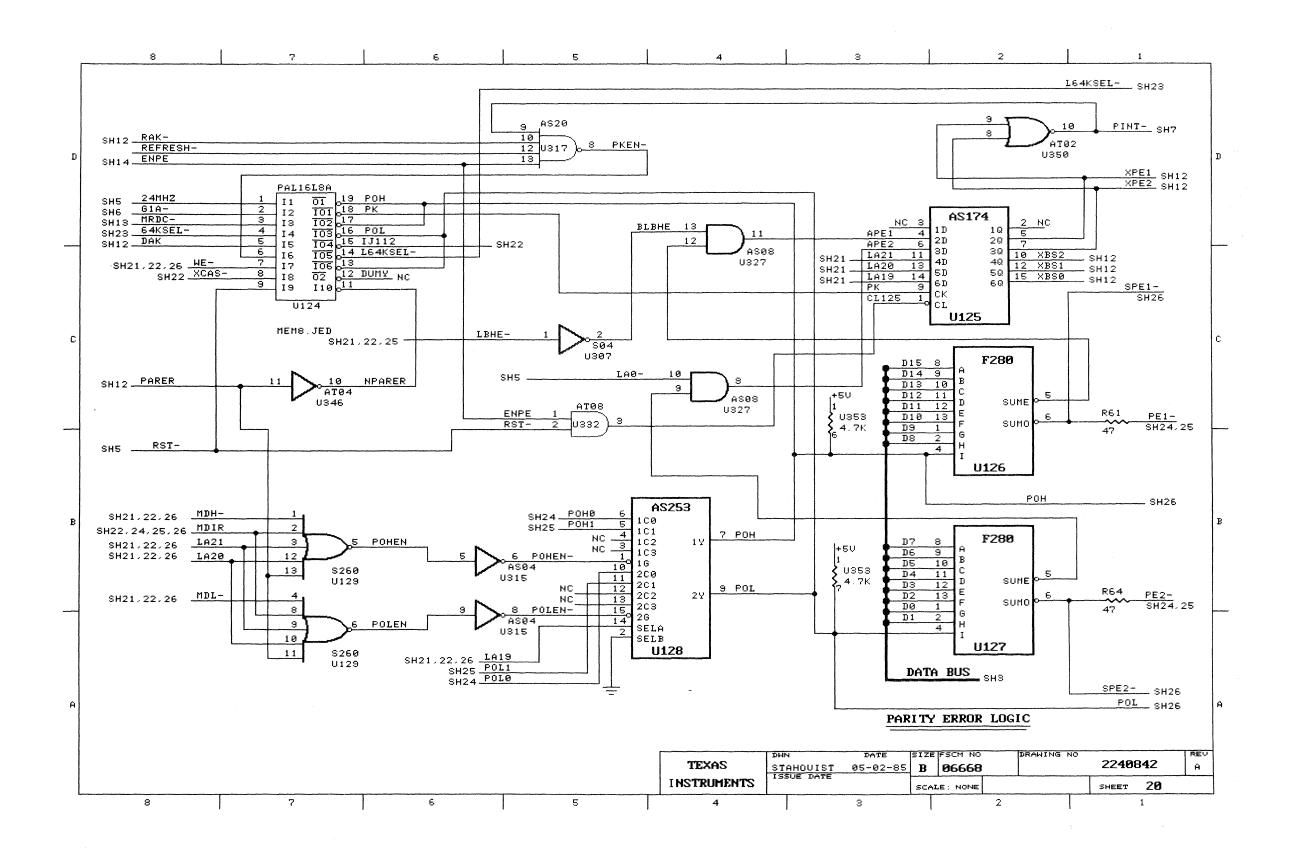

| 2.5.1.4  | Danity Ennon Logic                         | 2 44  |

|          | Parity Error Logic                         | 2 23  |

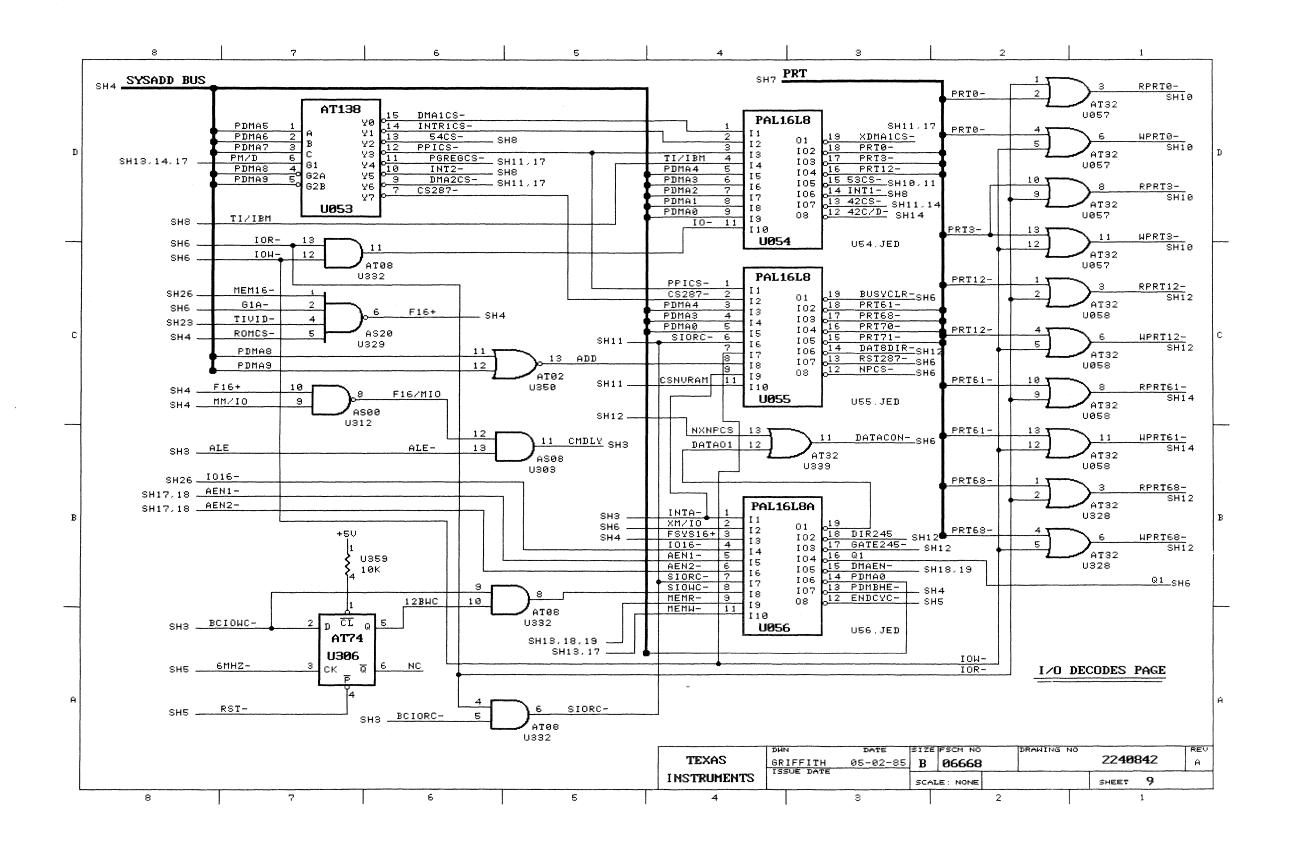

| 2.6      | I/O Subsystem                              | 2-23  |

| 2.6.1    | I/O Decode Logic                           |       |

| 2.6.2    | Real-Time Clock (RTC) and Nonvolatile RAM  |       |

| 2.6.2.1  | Battery Circuit                            |       |

| 2.6.2.2  |                                            |       |

| 2.6.2.3  | Real-Time Clock                            | 2-25  |

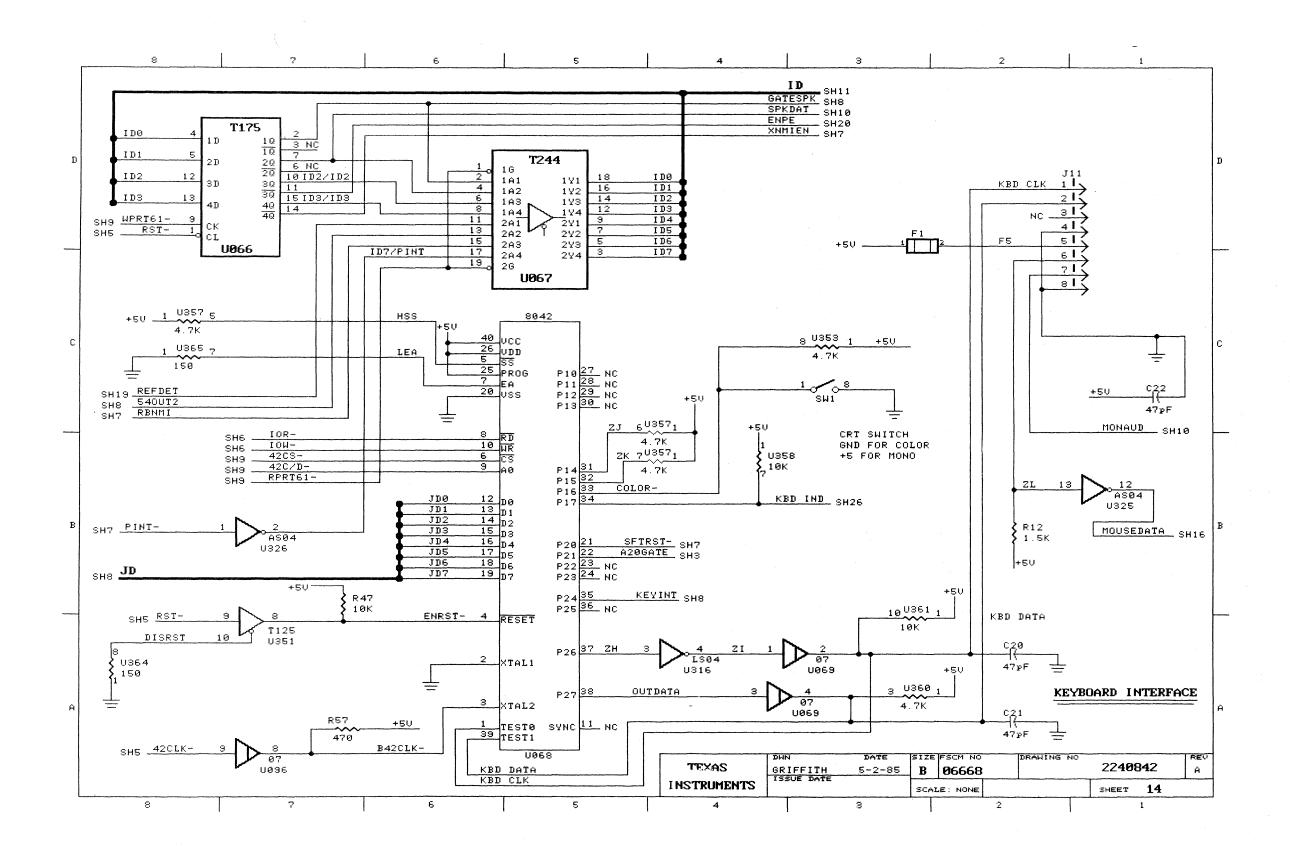

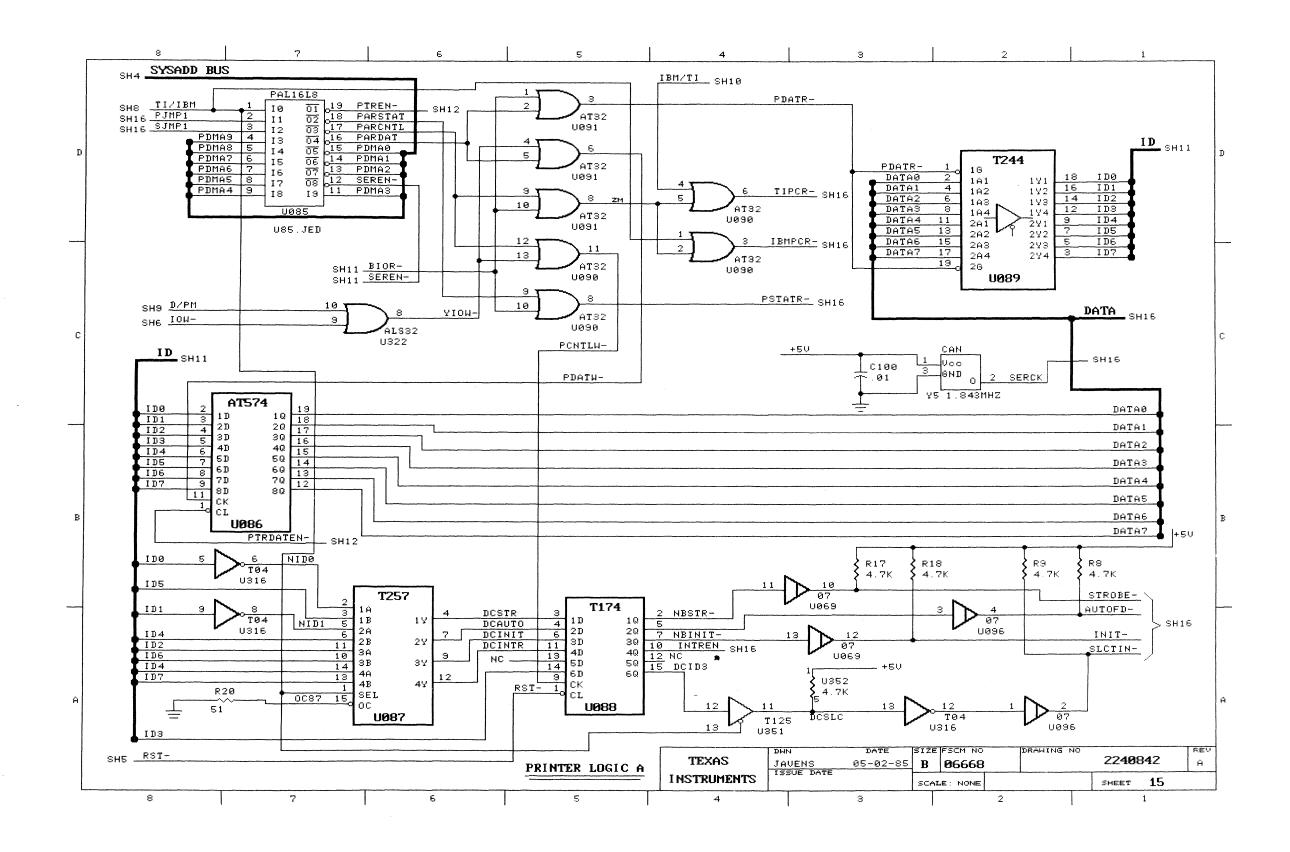

| 2.6.3    | Keyboard Interface                         | 2-34  |

| 2.6.3.1  | Receiving Data From the Keyboard           |       |

| 2.6.3.2  | Sending Data to the Keyboard               |       |

| 2.6.3.3  | Keyboard Commands                          |       |

| 2.6.3.4  | Keyboard Interface I/O Ports               |       |

| 2.6.4    | Darallel Drinter Dort                      | 2-30  |

| 2.6.5    | Parallel Printer Port                      | 2 22  |

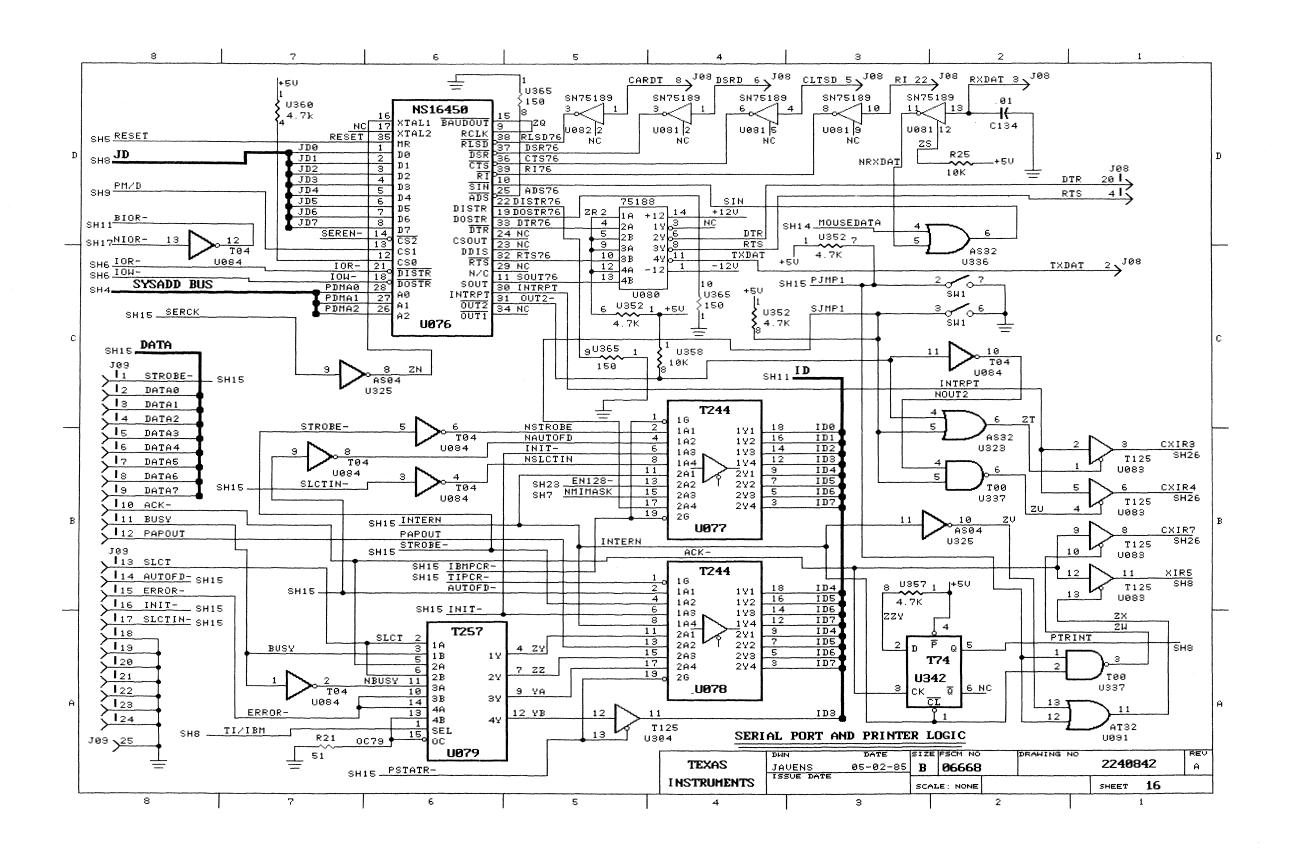

| 2.6.5.1  | Clear to Cond Cianal                       | 2 4 4 |

|          | Clear-to-Send Signal                       |       |

| 2.6.5.2  | Data-Set Ready Signal                      | 2-44  |

| 2.6.5.3  | Data-Carrier Detect Signal                 | 2-44  |

| 2.6.5.4  | Ring Indicator Signal                      | 2-45  |

| 2.6.5.5  | Data Terminal Ready Signal                 | 2-45  |

| 2.6.5.6  | Request-to-Send Signal                     | 2-45  |

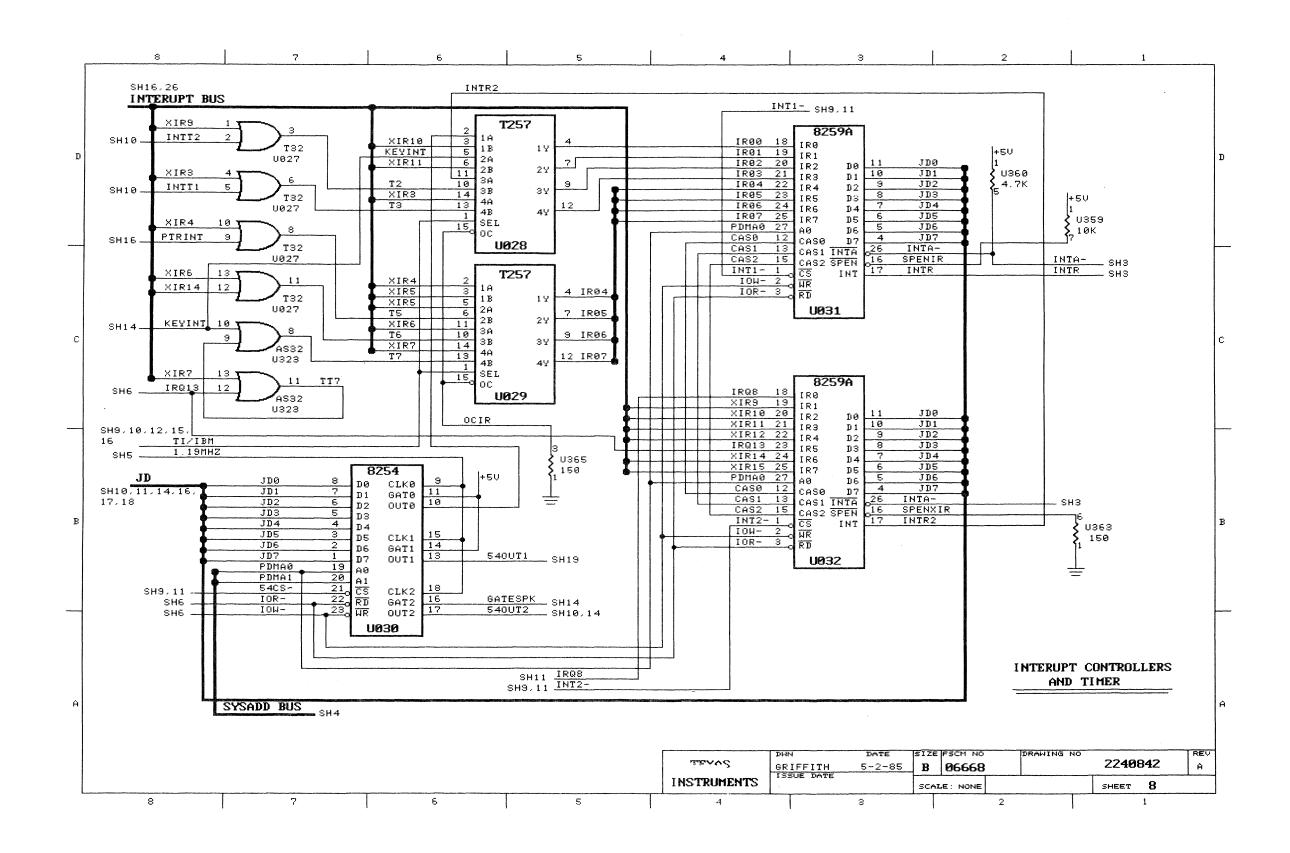

| 2.6.6    | Timing Services                            | 2-45  |

| 2.6.6.1  | TI Compatible Timer                        | 2-45  |

| 2.6.6.2  | PC-AT Compatible Timer                     |       |

| 2.6.6.3  | -                                          |       |

| 2.6.7    | Interrupt System                           |       |

| 2.6.7.1  | Interrupt Levels 0 Through 15              |       |

| 2.6.7.1  |                                            | 2-49  |

|          |                                            |       |

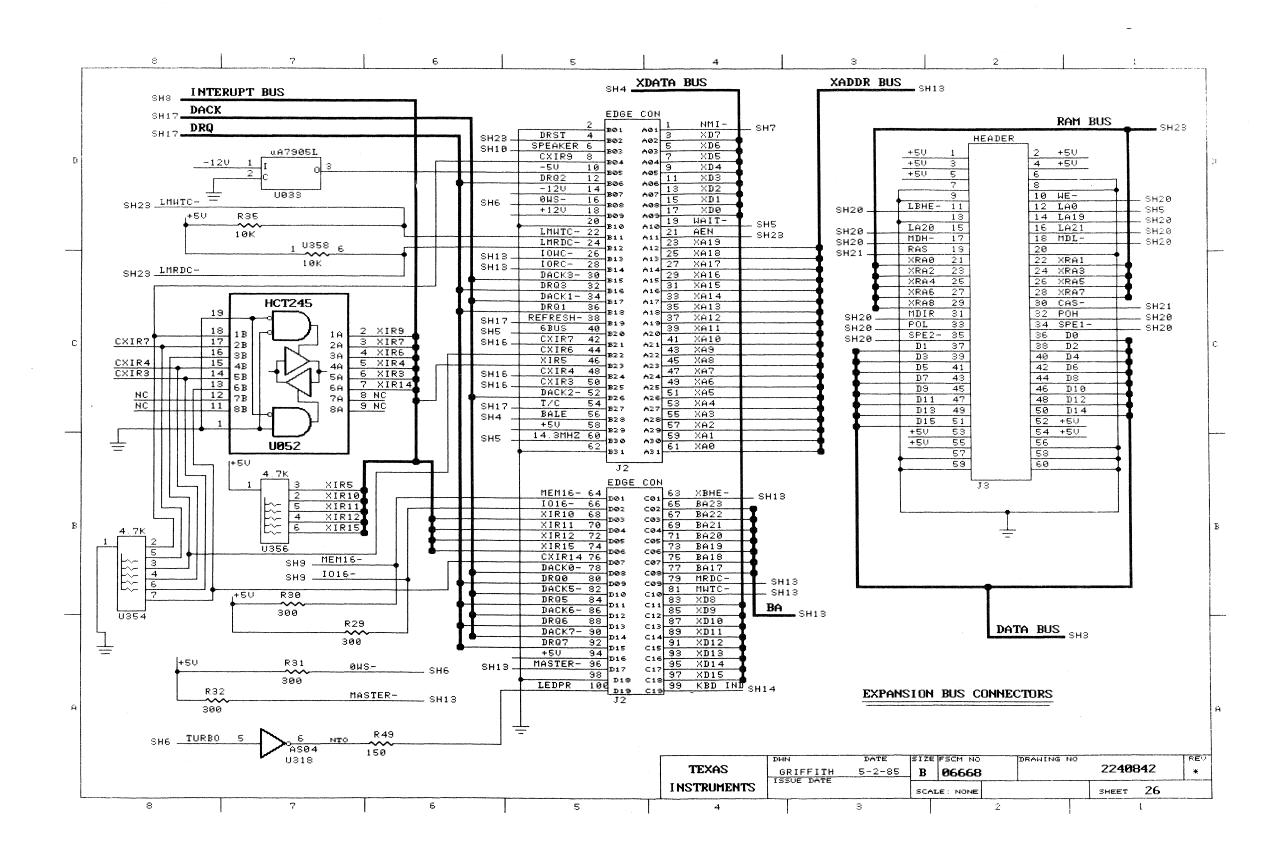

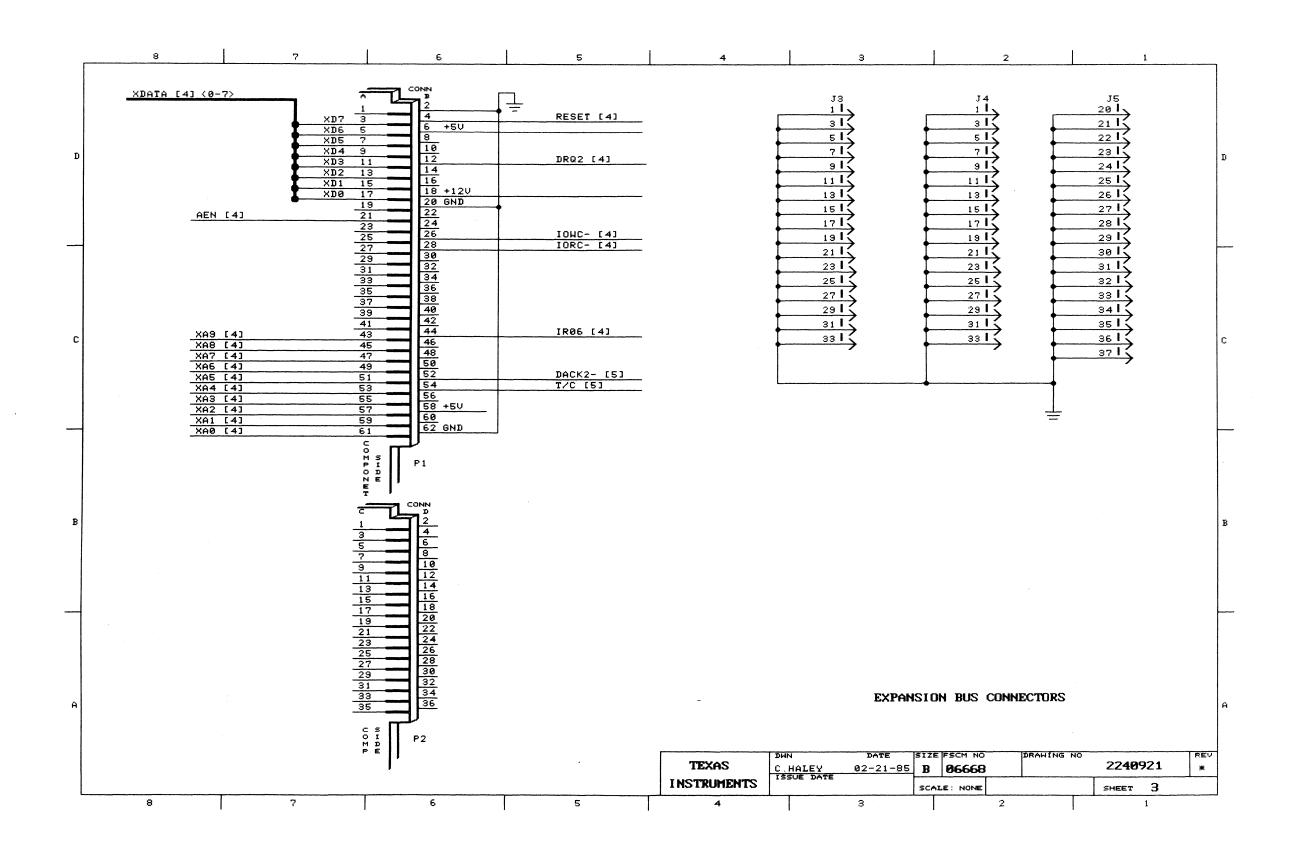

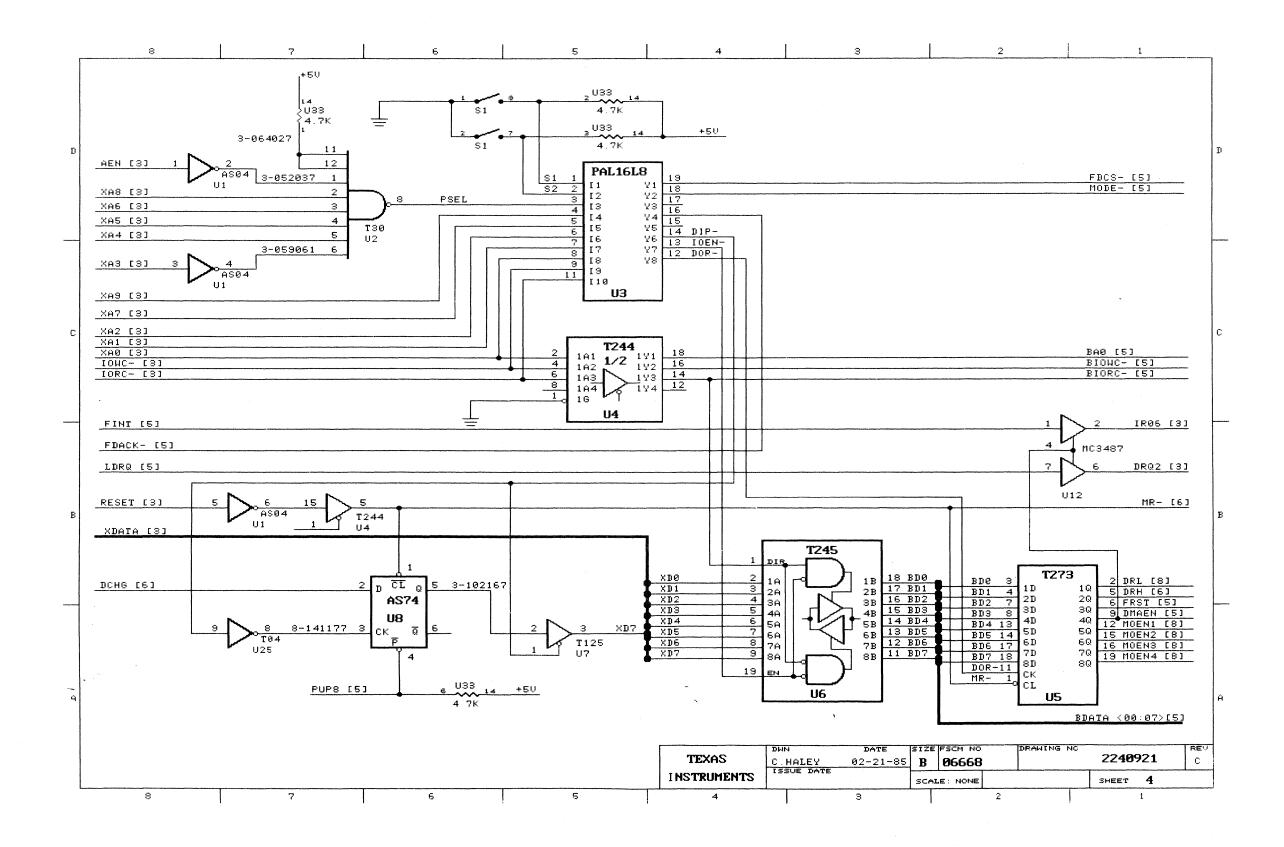

| 2.7      | Expansion Bus Interface                    | 2-49  |

|          |                                            |       |

|          | 3 Power Supply                             |       |

|          | o louci puppin                             |       |

| 3.1      | Power Supply Output Voltages               | . 3-1 |

| 3.2      | BUSINESS-PRO Power Consumption             | . 3-1 |

| Paragrap                                  | h Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Page                                                                                                                |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

|                                           | 4 Keyboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                     |

| 4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.5 | General Typamatic Transmission N-Key Rollover Key Click Mode Indicators Keyboard Buffer Keyboard Operations Keyboard Self-Tests Basic Assurance Self-Test Periodic Self-Test Periodic Self-Test Power-Up Sequence Keyboard Connector Specifications Clock Line Data Line Hardware Handshaking Protocols Keyboard Transmission Transmission Process Aborted Keyboard Transmission Inhibited Keyboard Transmission System Unit Transmission System Unit Transmission System-to-Keyboard Commands Set Key Click Volume Command Turn Mode Indicator LEDS On/Off Command Enable Command No Operation Command Set Typamatic Rate and Delay Command Enable Command Besend Command Resend Command Reset Command Reset Command Reset Command Self-Test OK Command Break Code Prefix Command Break Code Prefix Command Resend Command Resend Command Resend Command Failure Command Resend Command Break Code Prefix Command Resend Command Resend Command Resend Command Resend Command Resend Command | 4-12<br>4-22<br>4-23<br>4-33<br>4-34<br>4-34<br>4-34<br>4-16<br>4-16<br>4-11<br>4-11<br>4-11<br>4-11<br>4-11<br>4-1 |

| 4.7                                       | Keyboard Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-19                                                                                                                |

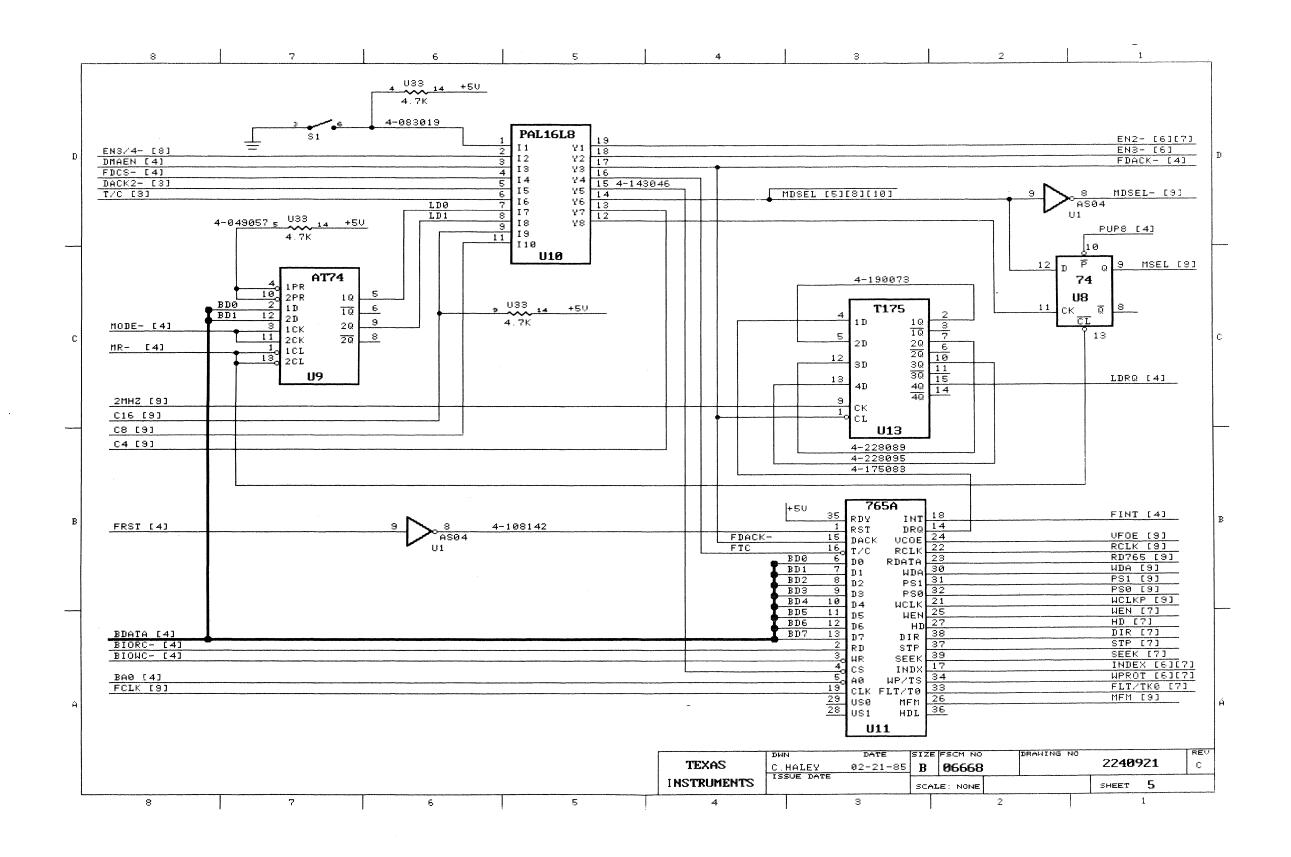

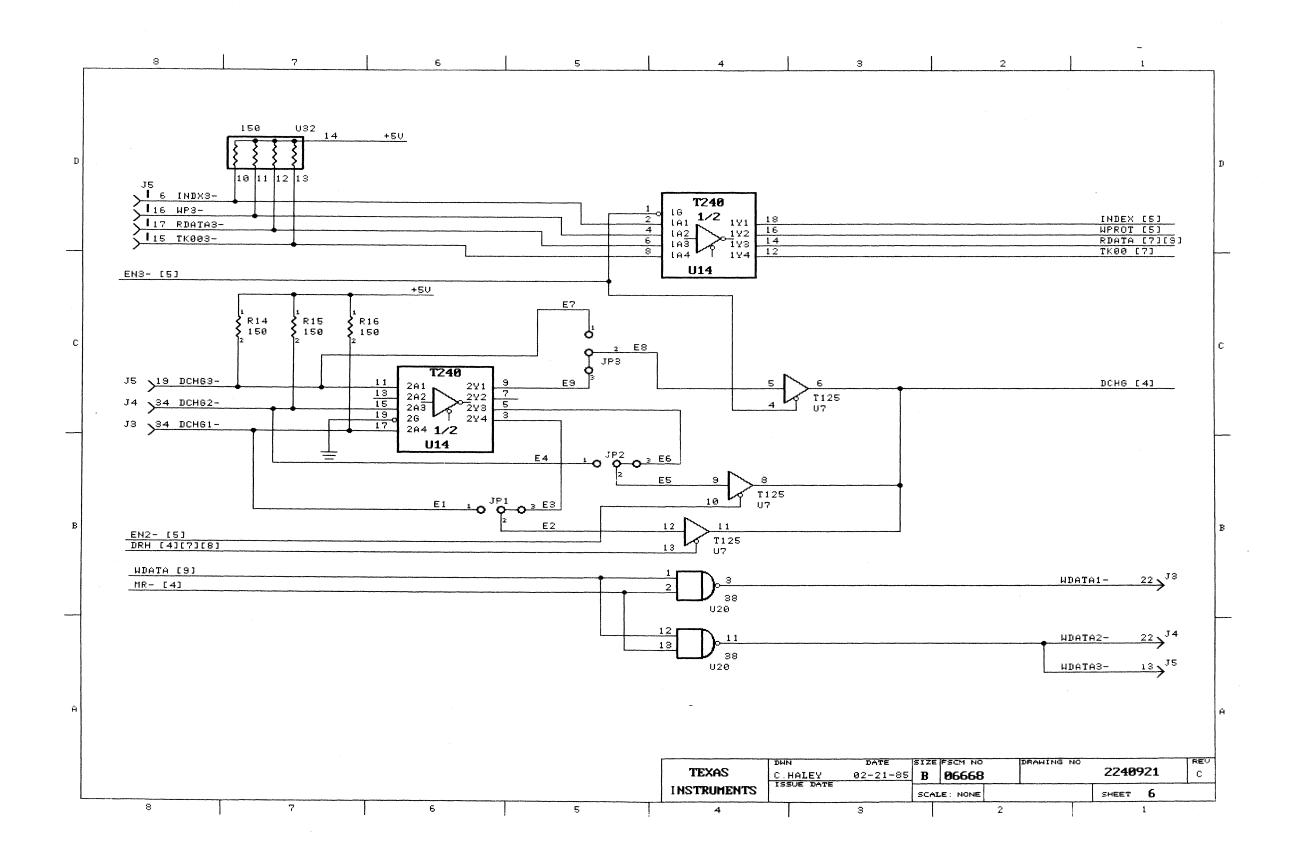

| 5.1                                       | 5 Floppy Disk Drive Controller  General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-1                                                                                                                 |

| 5.1.1                                     | Floppy Disk Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-1                                                                                                                 |

| Paragrap                                          | h Title                                                                                                                                              | Page                 |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                                   |                                                                                                                                                      |                      |

| 5.1.1.2<br>5.1.2<br>5.1.2.1<br>5.1.2.2<br>5.1.2.3 | Host I/O Interface and Control Logic Floppy Disk Controller Programming Information Floppy Disk Controller IC Internal Registers Controller Commands | 5-15<br>5-15<br>5-19 |

|                                                   | 6 Hardware Options                                                                                                                                   |                      |

| 6.1                                               | General                                                                                                                                              | 6-1                  |

|                                                   | RAM Expansion                                                                                                                                        | 6-3                  |

| 6.2.1                                             |                                                                                                                                                      | 6-3                  |

| 6.2.1.1                                           |                                                                                                                                                      | 6-3                  |

| 6.2.1.2                                           | 128-Kilobyte RAM Expansion Kit Specifications .                                                                                                      |                      |

| 6.2.2                                             | 512-Kilobyte RAM Expansion Kit                                                                                                                       |                      |

| 6.2.2.1                                           | 512-Kilobyte RAM Expansion Kit Interface Signals                                                                                                     |                      |

| 6.2.2.2                                           | 512 Kilobyte RAM Expansion Kit Intellace Signals 512-Kilobyte RAM Expansion Kit Specifications .                                                     |                      |

| 6.3                                               | BUSINESS-PRO Mass Storage Options                                                                                                                    |                      |

| 6.3.1                                             | 1.2-Megabyte Floppy Disk Drive                                                                                                                       |                      |

| 6.3.1.1                                           | 1.2 Megabyte Floppy Disk Drive                                                                                                                       |                      |

| 6.3.1.2                                           |                                                                                                                                                      |                      |

|                                                   |                                                                                                                                                      | 0 10                 |

| 6.3.1.3                                           | 1.2-Megabyte Floppy Disk Drive Tabulated                                                                                                             | 6-10                 |

| 6.3.2                                             | Information                                                                                                                                          | 6-16                 |

|                                                   | 360-Kilobyte Floppy Disk Drive                                                                                                                       | 0_T2                 |

| 6.3.2.1                                           | 360-Kilobyte Floppy Disk Drive Kit                                                                                                                   | 0-13                 |

| 6.3.2.2                                           | 360-Kilobyte Floppy Disk Drive Tabulated                                                                                                             | c 10                 |

| 6.3.3                                             | Information                                                                                                                                          |                      |

| 6.3.3.1                                           | Winchester Disk Controller                                                                                                                           |                      |

| 6.3.3.2                                           | Winchester Disk Controller Kit                                                                                                                       | 6-10                 |

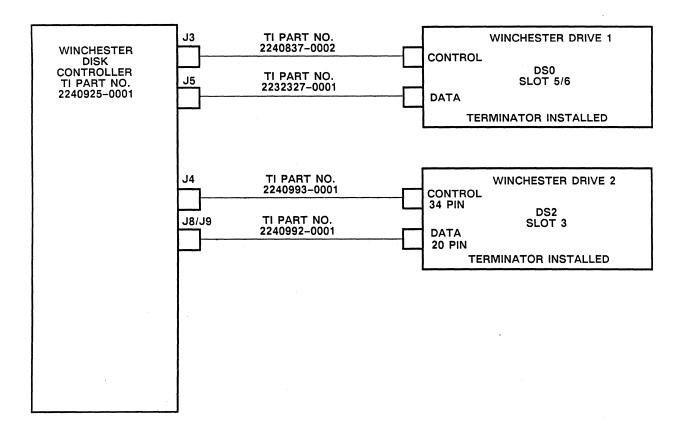

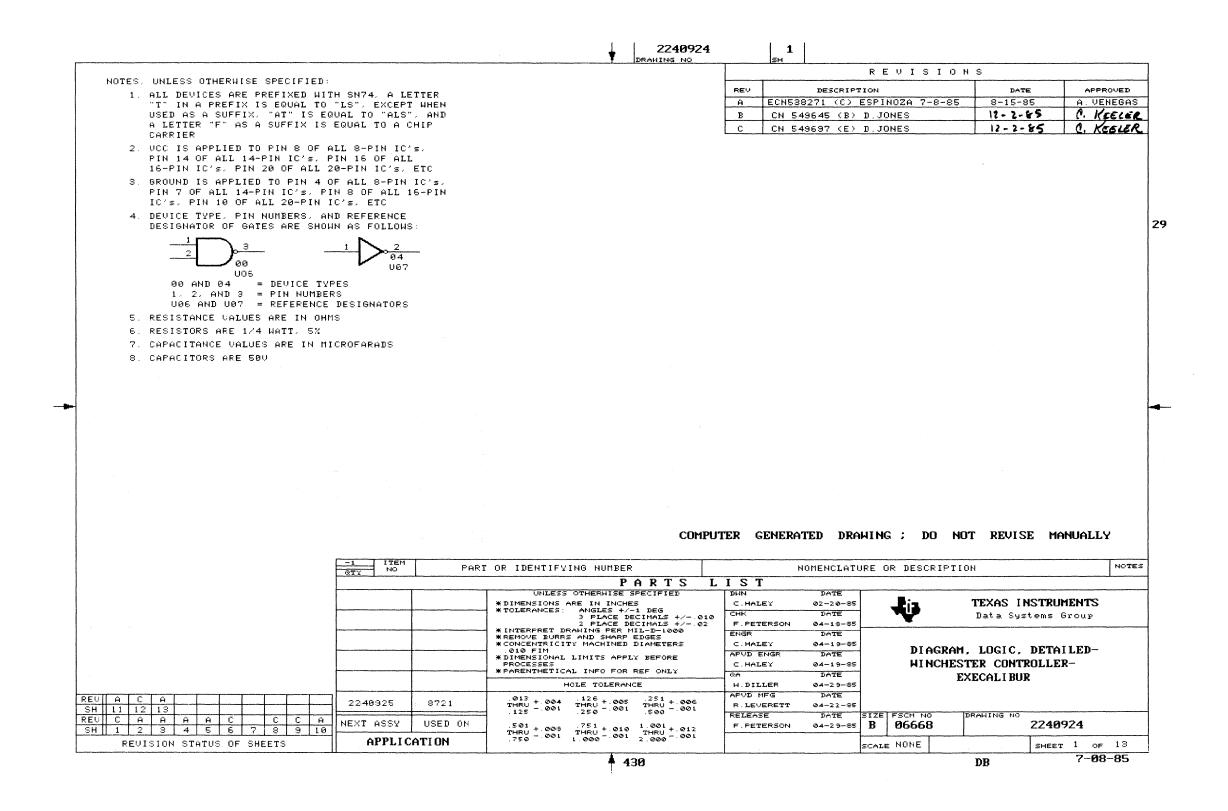

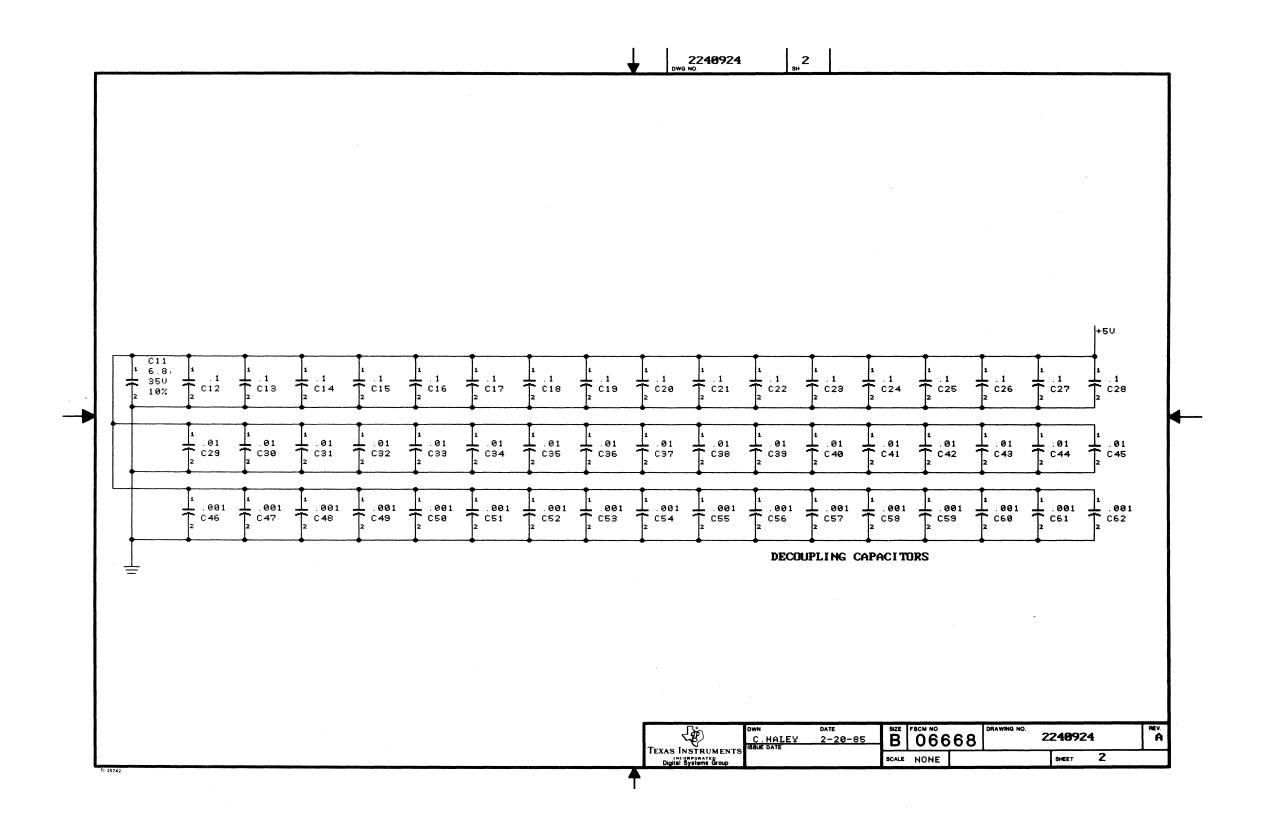

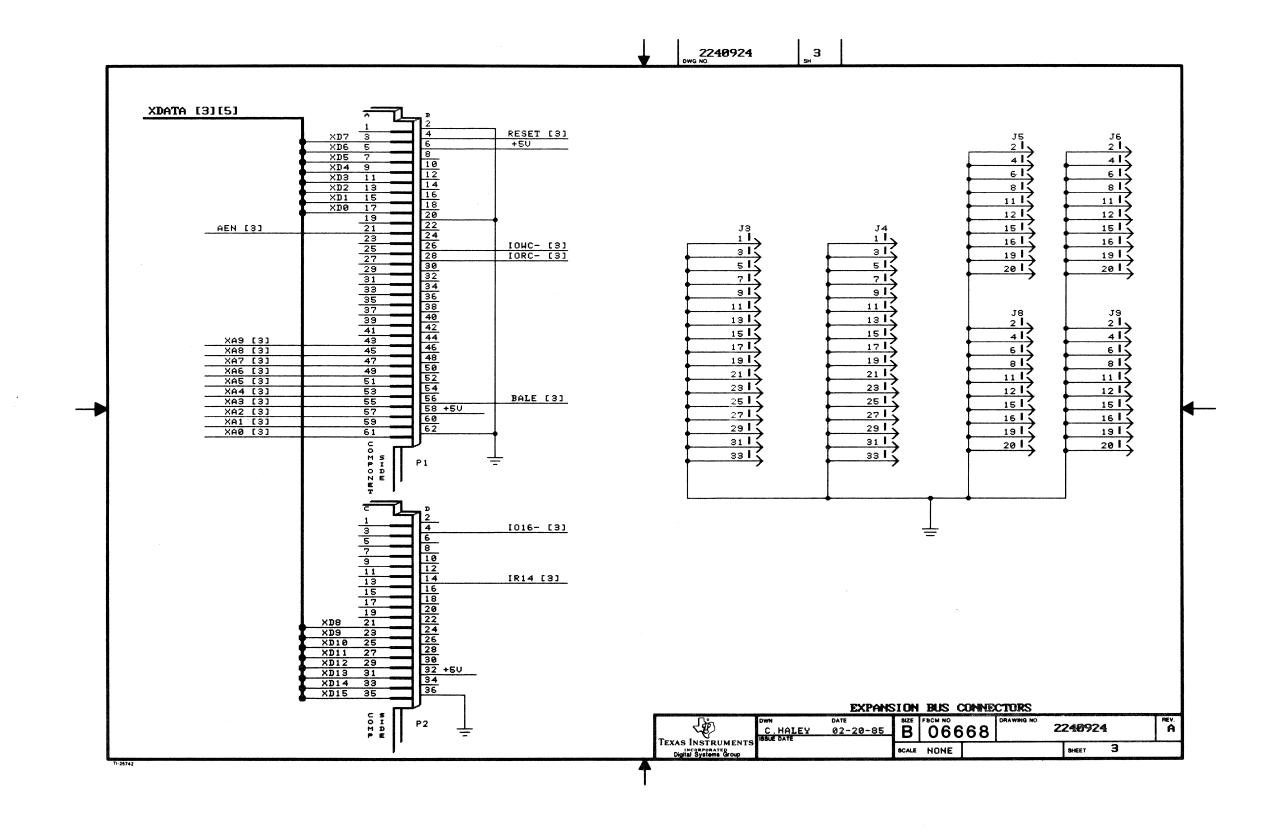

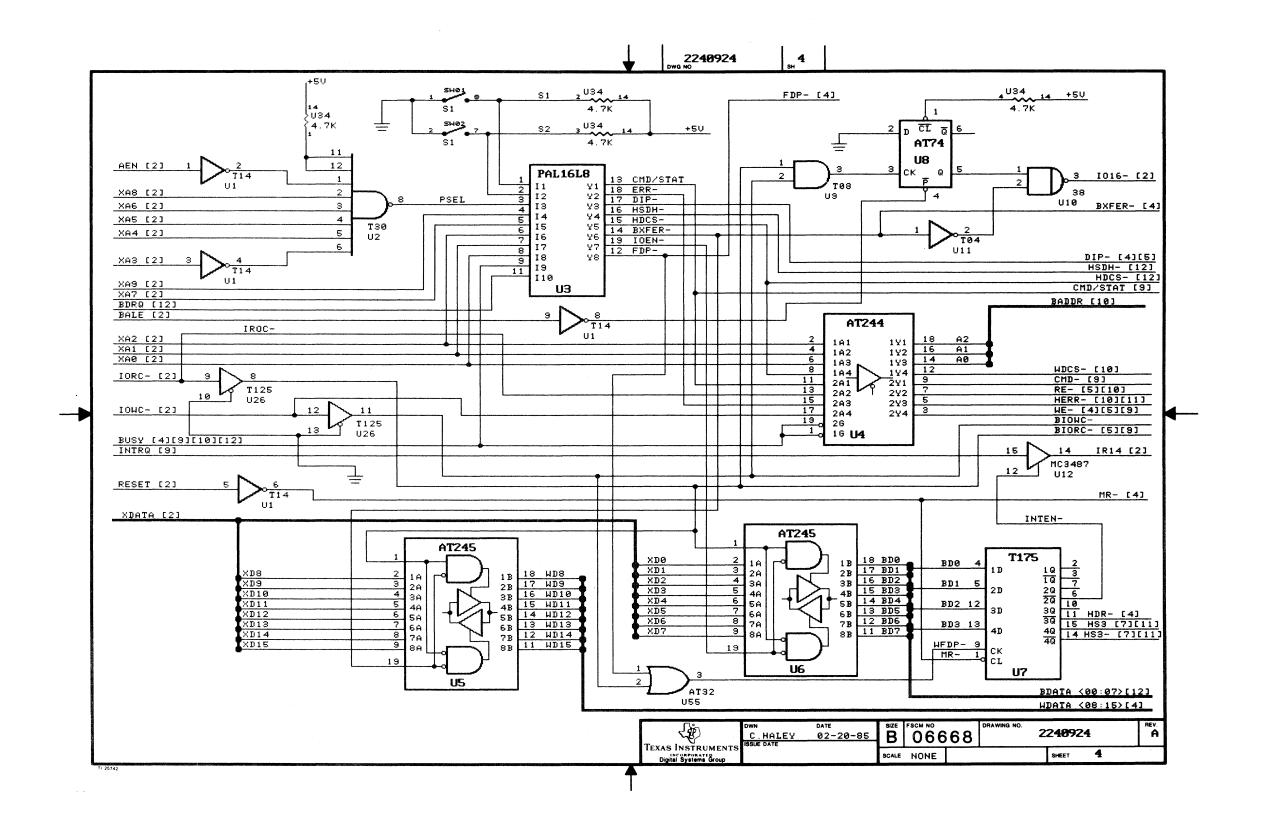

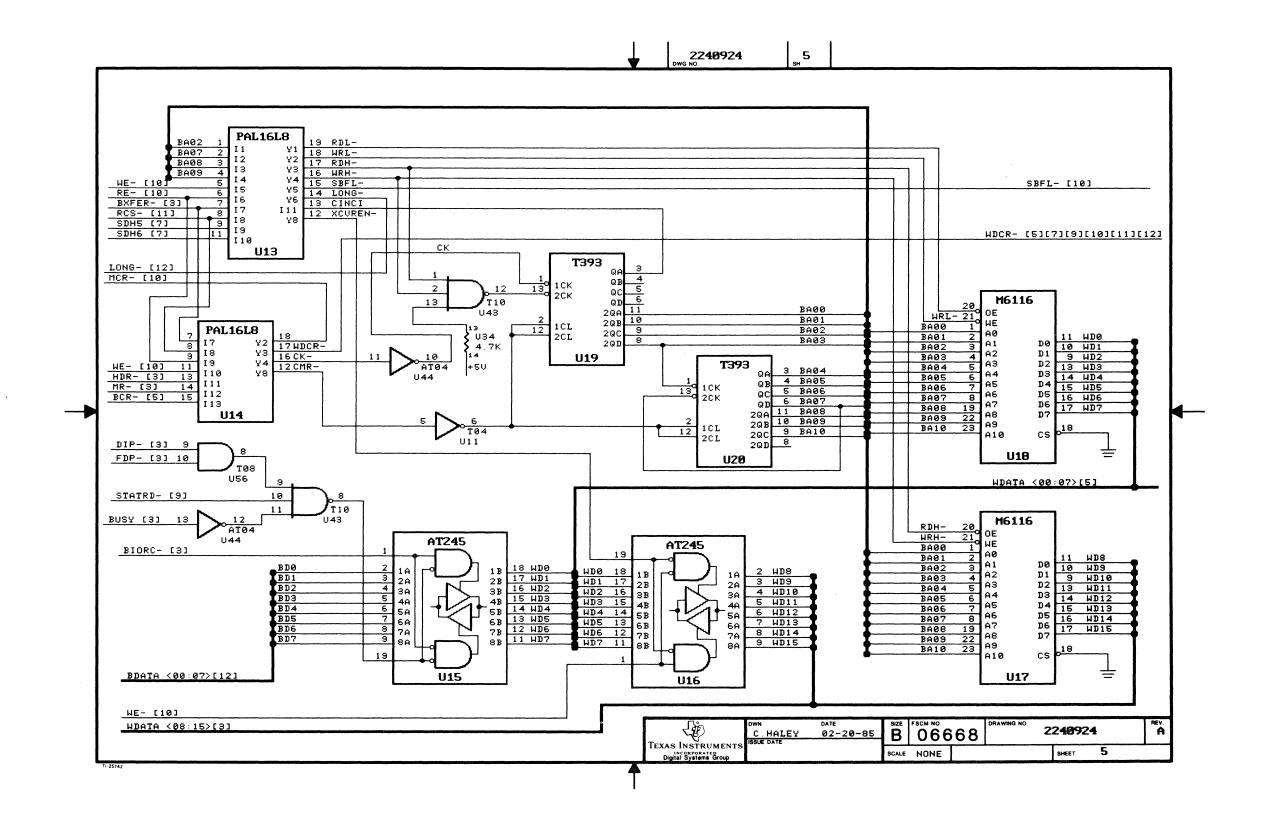

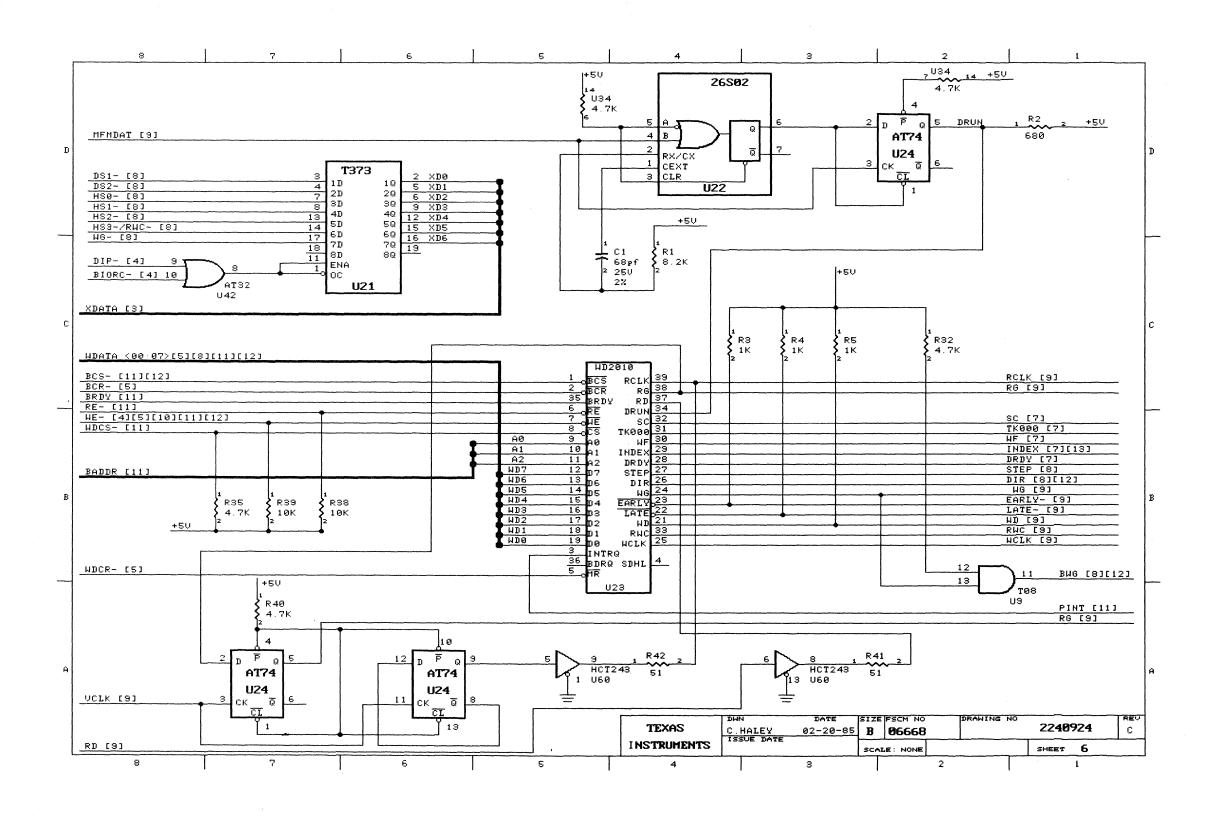

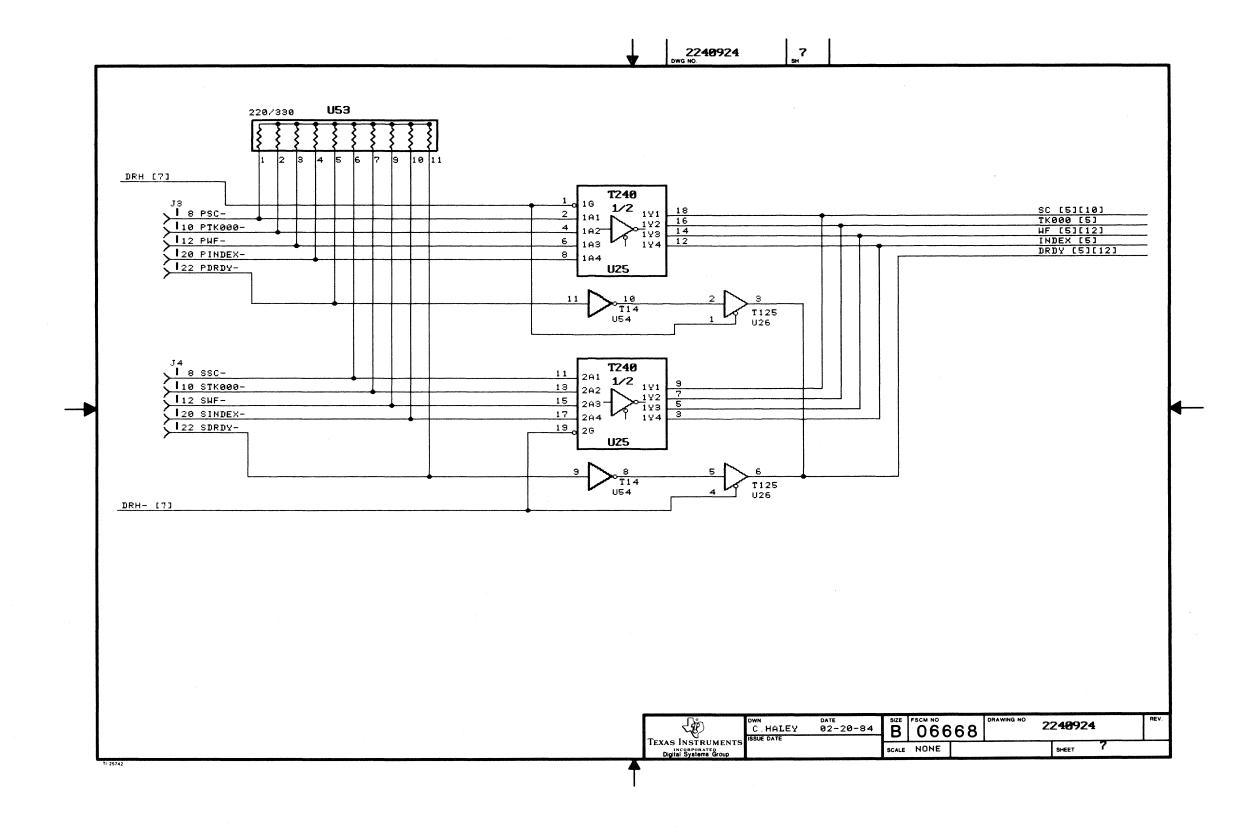

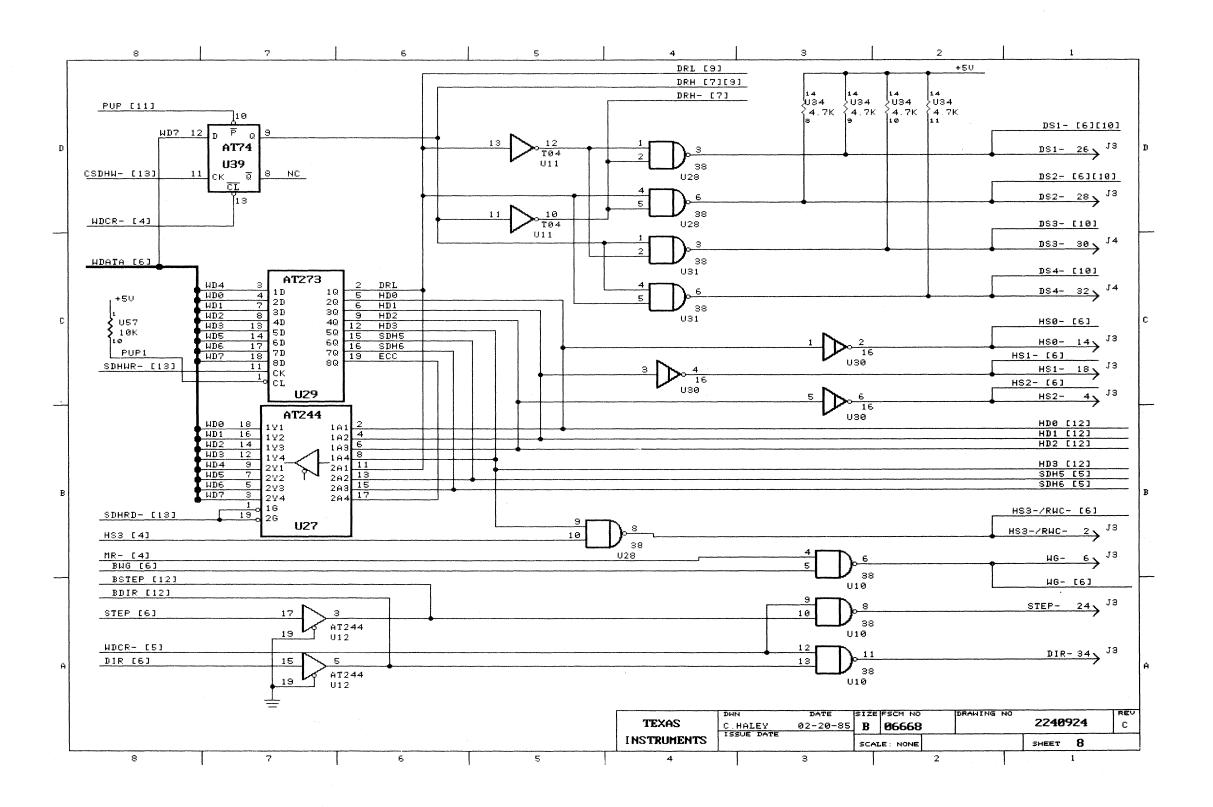

| 6.3.3.3                                           | Winchester Disk Controller Diagrams                                                                                                                  |                      |

| 6.3.3.4                                           | Winchester Disk Controller Tabulated Information                                                                                                     |                      |

| 6.3.4                                             | External Activity Indicator                                                                                                                          |                      |

|                                                   | Winchester Disk Controller System Addresses                                                                                                          |                      |

| 6.3.4.1                                           | I/O Port Descriptions                                                                                                                                | 6-32                 |

| 6.3.4.2                                           | Controller Command Functions                                                                                                                         |                      |

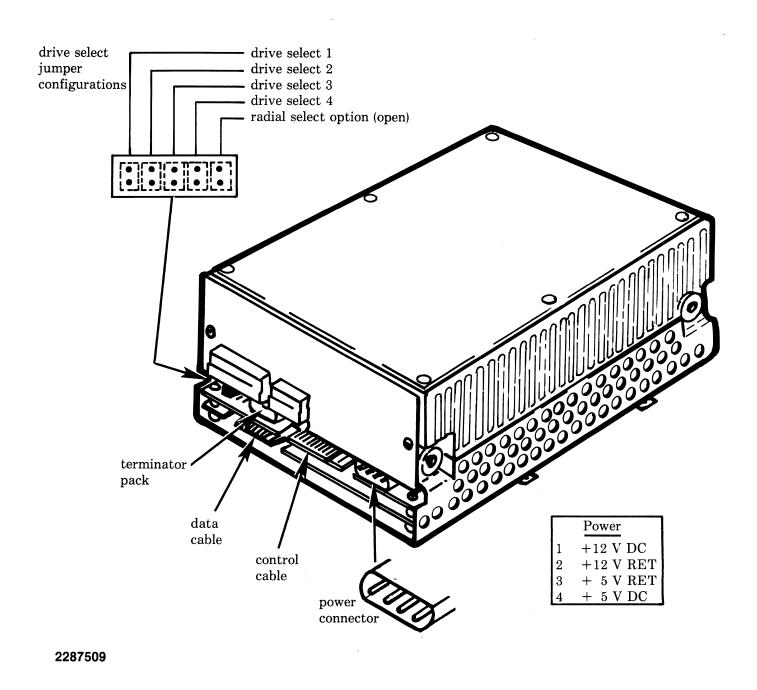

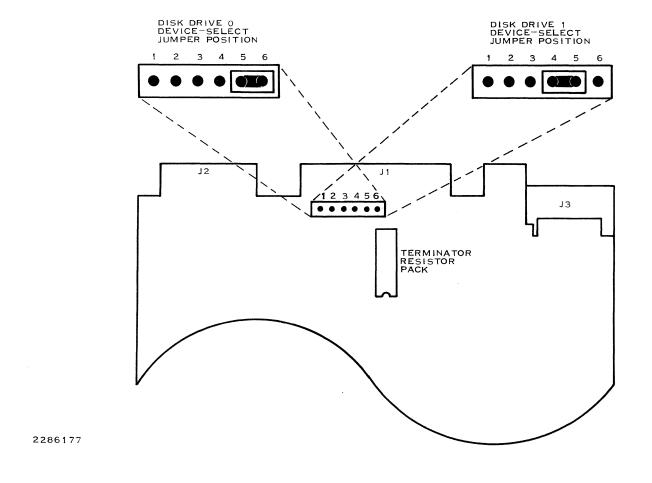

| 6.3.5                                             | Winchester Disk Drives                                                                                                                               | 6-43                 |

| 6.3.5.1                                           | Types of Winchester Disk Drives                                                                                                                      |                      |

| 6.3.6                                             | 21-Megabyte Winchester Disk Drive                                                                                                                    | 6-45                 |

| 6.3.6.1                                           | 21-Megabyte Winchester Drive Kit                                                                                                                     |                      |

| 6.3.6.2                                           | 21-Megabyte Disk Drive Tabulated Information                                                                                                         |                      |

| 6.3.6.3                                           | Configuring a 21-Megabyte Disk Drive                                                                                                                 |                      |

| 6.3.7.1                                           | 40-Megabyte Winchester Disk Drive                                                                                                                    | 0-53                 |

| 6.3.7.1                                           | 40-Megabyte Winchester Disk Drive Kit                                                                                                                | 6-53                 |

| 6.3.7.3                                           | 40-Megabyte Disk Drive Tabulated Information                                                                                                         |                      |

| 6.3.8                                             | Configuring a 40-Megabyte Disk Drive                                                                                                                 |                      |

| 6.3.8.1                                           | 72-Megabyte Winchester Disk Drive                                                                                                                    | 662                  |

| 6.3.8.2                                           | 72-Megabyte Winchester Disk Drive Kit                                                                                                                |                      |

| 6.3.8.3                                           | 72-Megabyte Disk Drive Tabulated Information                                                                                                         |                      |

| 6.3.9                                             | Configuring a 72-Megabyte Disk Drive                                                                                                                 |                      |

| $\cup$ . $\cup$ . $\supset$                       | TAU MEGADY LE WINCHESTEL DISK DITVE                                                                                                                  | 0-09                 |

| Paragraph                                                                                                                                                                                                                       | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

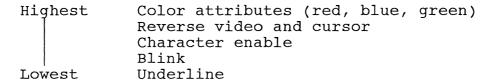

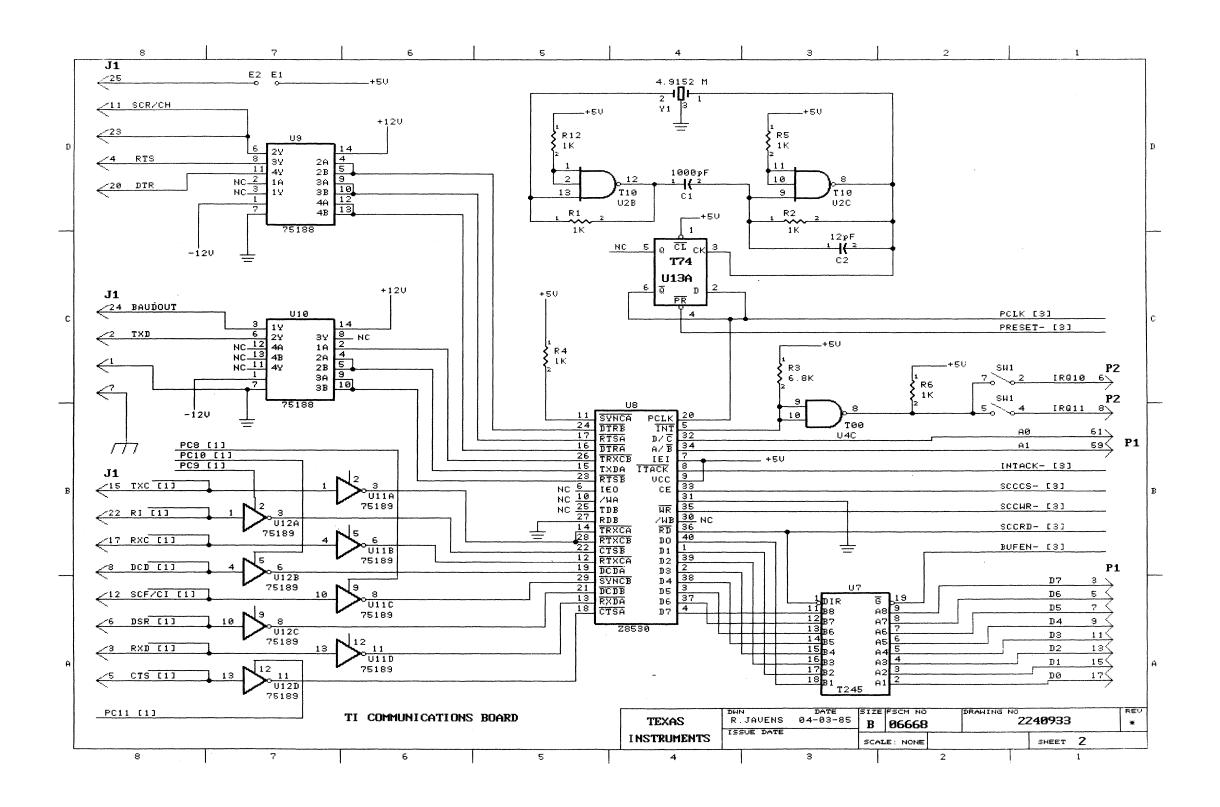

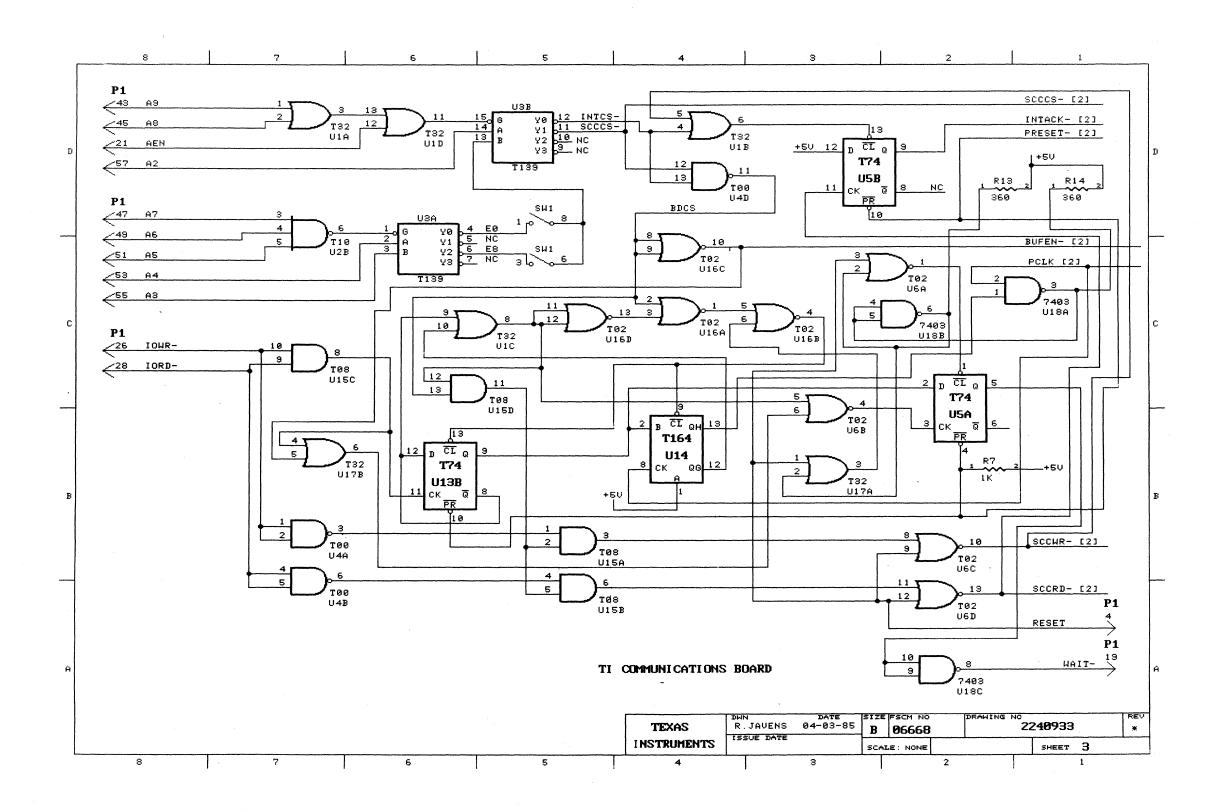

| 6.4.1<br>6.4.1.2<br>6.4.1.3<br>6.4.1.4<br>6.4.1.5<br>6.4.1.6<br>6.4.1.7<br>6.4.1.8<br>6.4.2.1<br>6.4.2.2<br>6.4.2.3<br>6.4.2.3<br>6.4.2.4<br>6.4.3.3<br>6.4.3.1<br>6.4.3.2<br>6.4.3.3<br>6.4.3.3<br>6.4.3.4<br>6.5.5.1<br>6.5.2 | 120-Megabyte Winchester Disk Drive Kit 120-Megabyte Disk Drive Tabulated Information Configuring a 120-Megabyte Disk Drive Tape System Tape Drive Kit Tape Drive Kit Tape Drive Tideo Options Video Controllers TI Mode CRT Controller Board Diagnostic Loopback Graphics Controller Board TIPC Compatibility PC-AT Mode CRT Controller PC-AT CRT Controller Operational Modes CRT Timing Parameters Color Display Unit Color Display Unit Kit Color Display Unit Tabulated Information Displayed Colors Keyboard/Mouse Cable Connector J4 Monochrome Display Unit Kit Monochrome Display Unit Tabulated Information Displayed Intensities Keyboard/Mouse Cable Connector J4 Timode RS-232 Serial Interface TI Mode RS-232 Serial Interface TI Mode RS-232 Serial Interface Kit TI Mode RS-232 Serial Interface Tabulated Information Baud Rate Generation Optical Mouse Optical Mouse Tabulated Information Books Numeric Coprocessor | . 6-70<br>. 6-75<br>. 6-79<br>. 6-79<br>. 6-95<br>. 6-95<br>. 6-109<br>. 6-109<br>. 6-117<br>. 6-124<br>. 6-135<br>. 6-135<br>. 6-143<br>. 6-143<br>. 6-145<br>. 6-155<br>. 6-155 |

|                                                                                                                                                                                                                                 | Appendixes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                 |

| Appendix                                                                                                                                                                                                                        | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page                                                                                                                                                                              |

| B C F C F C C                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | . A-1<br>. B-1<br>. C-1<br>. D-1<br>. E-1<br>. F-1                                                                                                                                |

Index

### Illustrations

| Figure | Title                                                      | Рa | .ge  |

|--------|------------------------------------------------------------|----|------|

| 2-1    | Main Logic Board Block Diagram                             | •  | 2-3  |

| 2-2    | Main Logic Board, TI Part No. 2240843-0001, Key Components |    | 2-6  |

| 2-3    | Main Logic Board, TI Part No. 2240843-0001, Key Components |    | 2-7  |

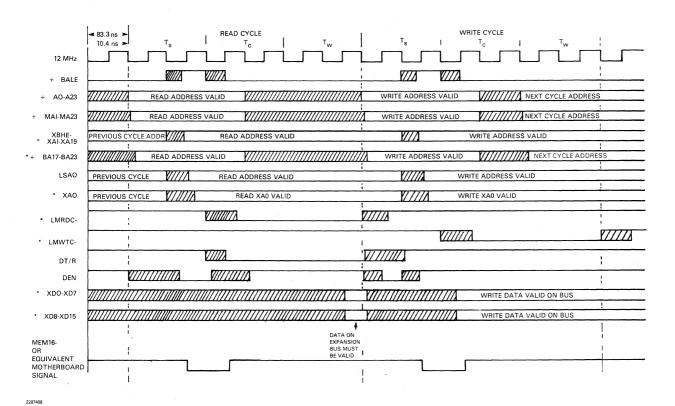

| 2-4    | Required Input Timing for a Processor-Driven Cycle         | •  | 2-13 |

| 2-5    | One-Wait-State MPU-Driven Memory Cycles                    | •  | 2-14 |

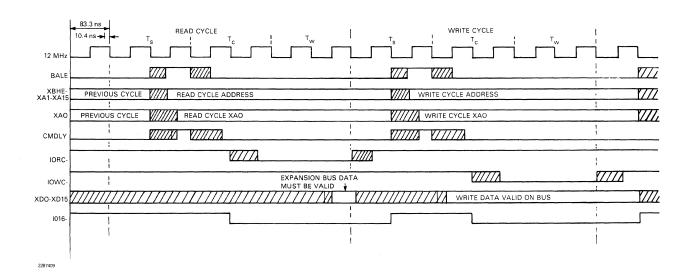

| 2-6    | One-Wait-State MPU-Driven I/O Cycles                       |    |      |

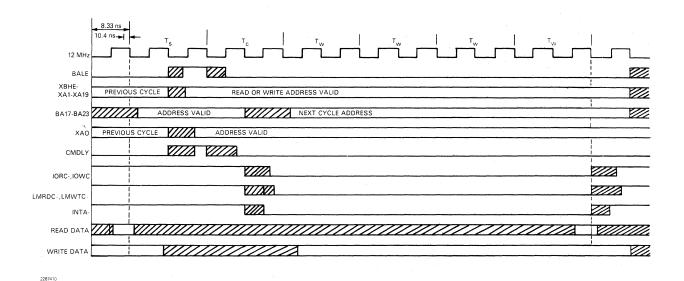

| 2-7    | Four-Wait-State MPU-Driven Memory or I/O Cycle             | •  | 2-16 |

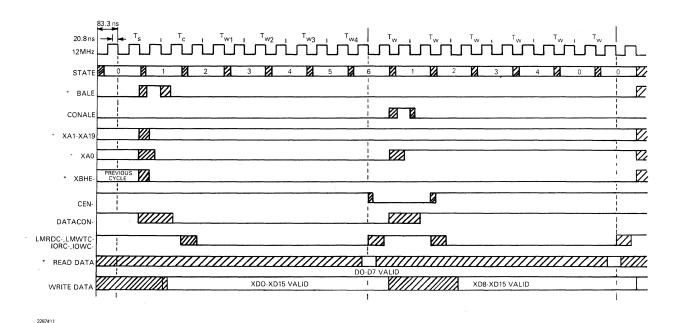

| 2-8    | Ten-Wait-State MPU-Driven Memory or I/O Cycle              | •  | 2-17 |

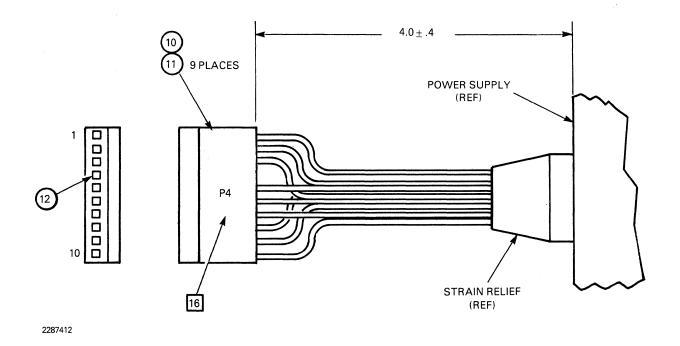

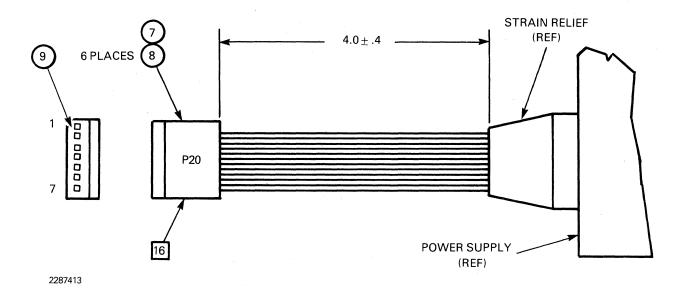

| 3-1    | Main Logic Board Power Connector                           |    |      |

| 3-2    | Expansion Bus Board Power Connector                        |    |      |

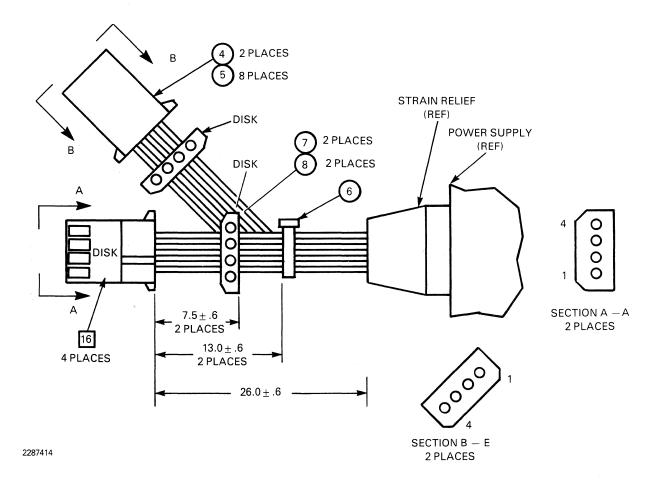

| 3-3    | Disk Drives 1 Through 4 Power Connector                    |    |      |

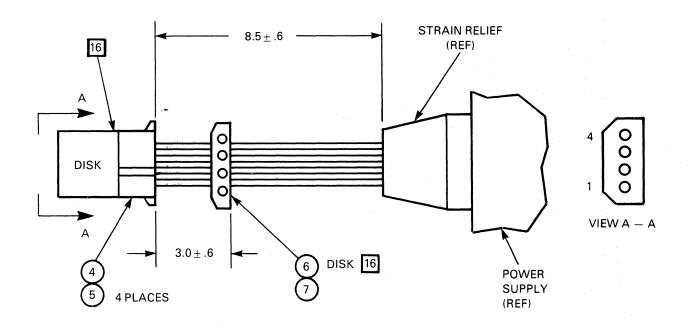

| 3-4    | Disk Drives 5 and 6 Power Connector                        | •  | 3-6  |

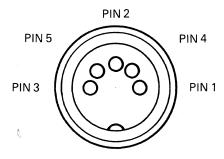

| 4-1    | Keyboard Connector Pin Arrangement                         |    | 4-4  |

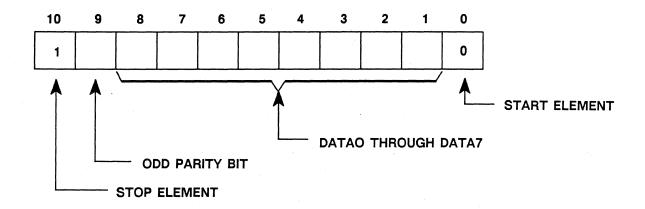

| 4-2    | Keyboard Data Frame Format                                 |    | 4-6  |

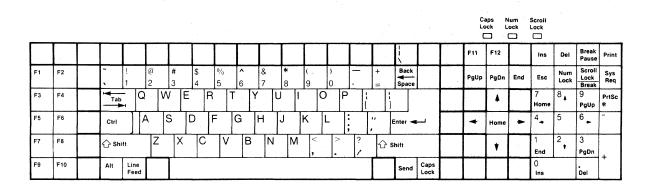

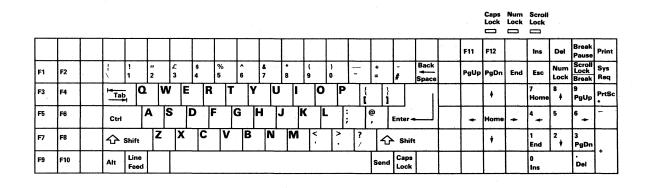

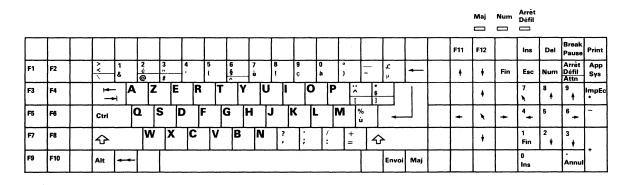

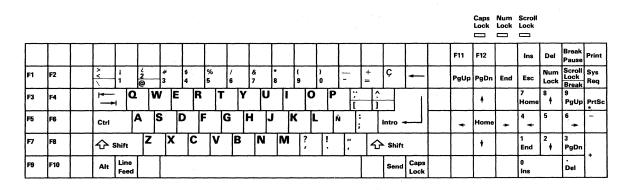

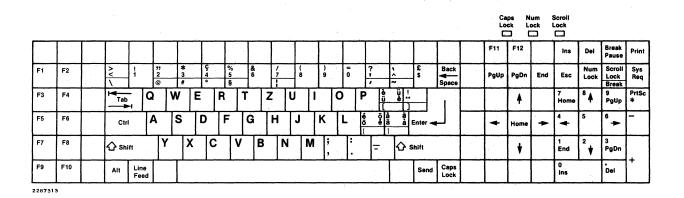

| 4-3    | <pre>Key Station/Code Map</pre>                            |    | 4-7  |

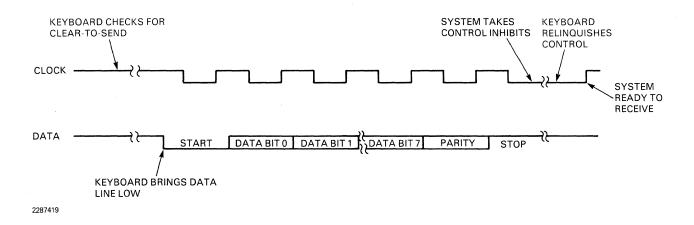

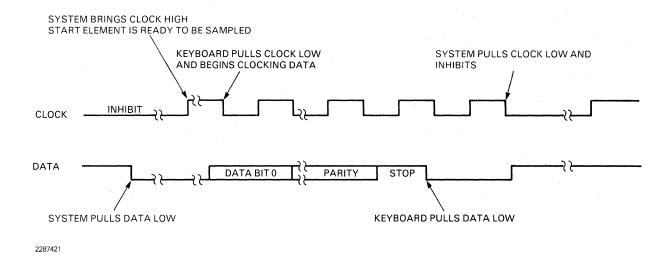

| 4-4    | Keyboard Transmission Timing Completed                     |    |      |

| 4-5    | Transmission                                               | •  | 4-10 |

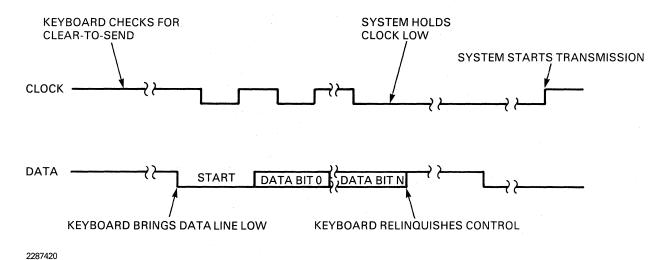

| 4-6    | System Unit Transmission Timing                            | 1  | 4-12 |

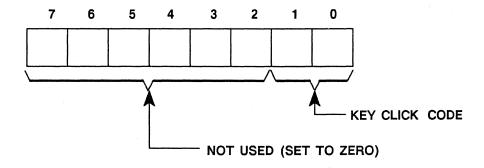

| 4-7    | Set Key Click Volume Command Data Byte                     | •  | 4-14 |

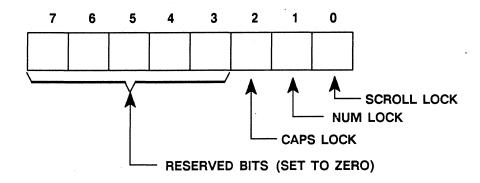

| 4-8    | Second Byte of the Indicator LED Command                   |    |      |

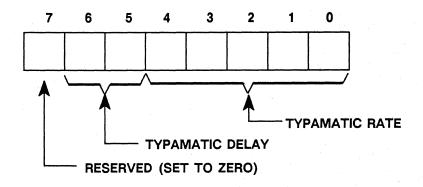

| 4-9    | Second Byte of the Set Typamatic Rate Command              |    | 4-16 |

| 4-10   | Keycap Configuration Domestic                              |    |      |

| 4-11   | Keycap Configuration Germany                               | •  | 4-20 |

| 4-12   | Keycap Configuration France                                | •  | 4-21 |

| 4-13   | Keycap Configuration Italy                                 |    |      |

| 4-14   | Keycap Configuration Norway                                | •  | 4-22 |

| 4-15   | Keycap Configuration Spain                                 | •  | 4-22 |

| 4-16   | Keycap Configuration Sweden                                |    |      |

| 4-17   | Keycap Configuration Switzerland                           |    | 4-23 |

| 4-18   | Keycap Configuration United Kingdom                        | •  | 4-24 |

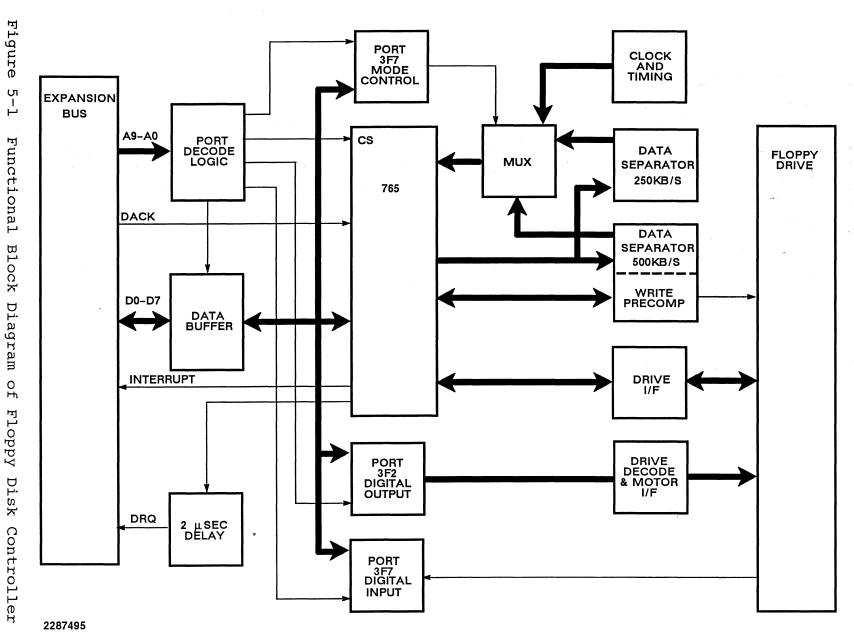

| 5-1    | Functional Block Diagram of Floppy Disk Controller         |    | 5-3  |

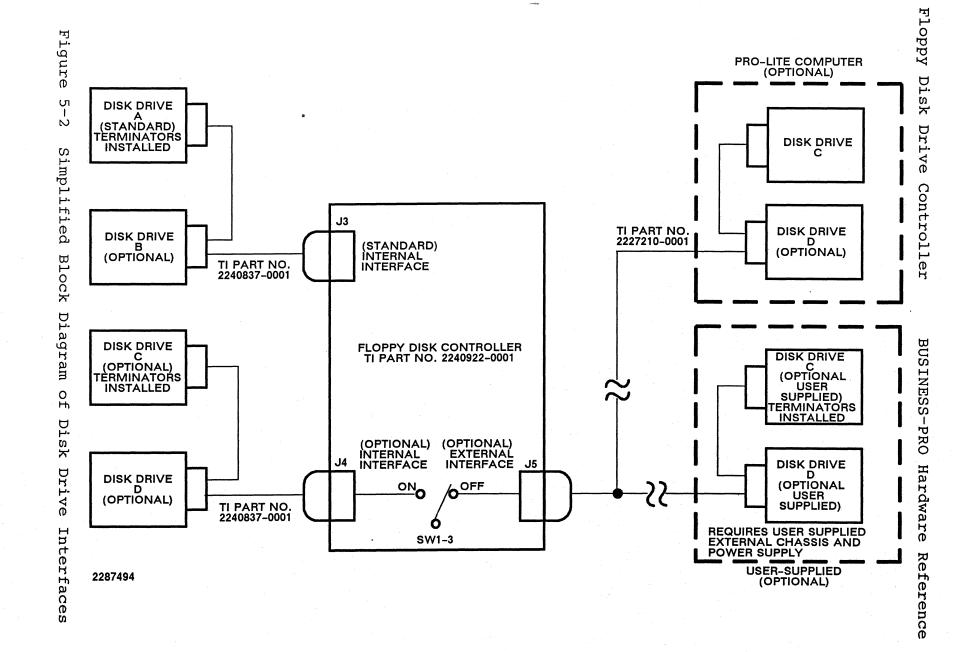

| 5-2    | Simplified Block Diagram of Disk Drive Interfaces .        | •  | 5-4  |

| 6-1    | Winchester Controller Functional Block Diagram             |    | 6-20 |

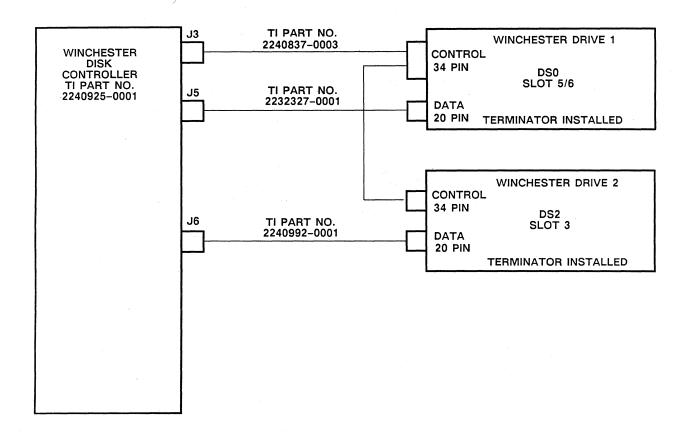

| 6-2    | Controller Connected in a Two-Drive Configuration .        |    | 6-21 |

| 6-3    | Controller Connected in a Two-Drive XENIX System .         |    | 6-22 |

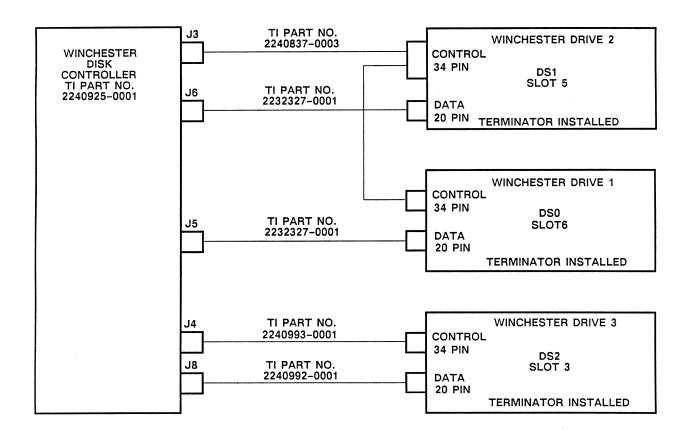

| 6-4    | Controller Connected in a Three-Drive Configuration        | •  |      |

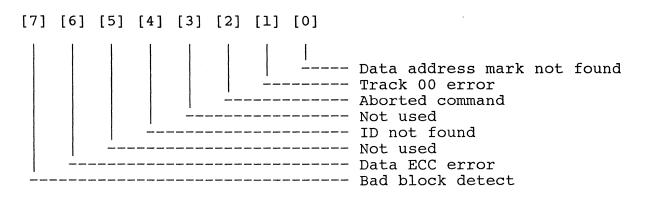

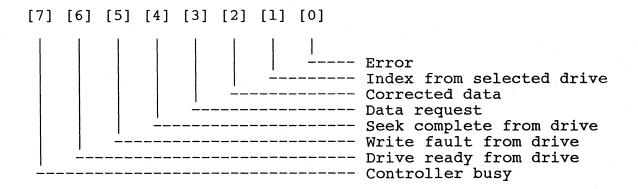

| 6-5    | Error Register Bit Definitions                             | •  | 6-33 |

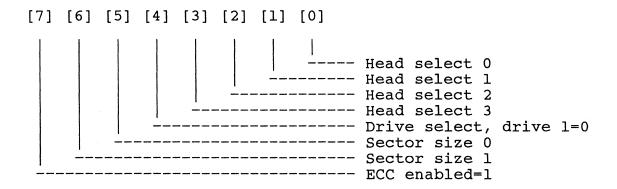

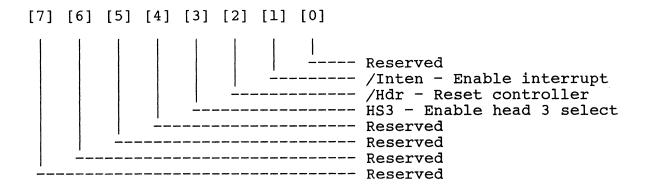

| 6-6    | , , ,                                                      |    | 6-35 |

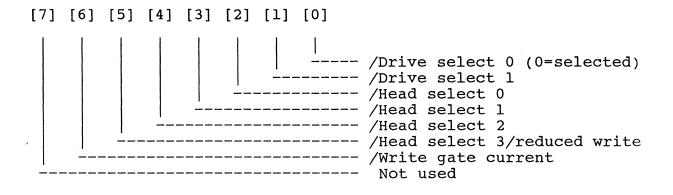

| 6-7    |                                                            |    | 6-36 |

| 6-8    | Fixed Disk Control Register                                | •  | 6-39 |

| Figure                                                                           | Title                                                           | Page                                                 |                                     |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------|-------------------------------------|

| 6-9<br>6-10<br>6-11                                                              | Diagnostic Register Bit Definitions                             |                                                      |                                     |

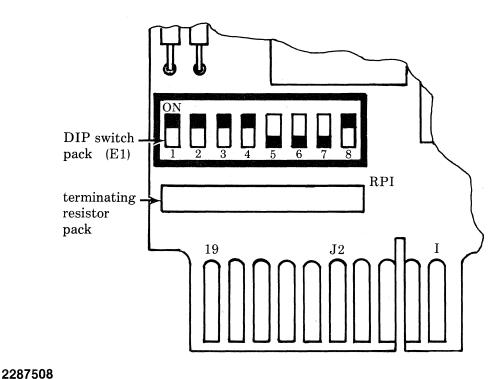

| 6-12                                                                             | and Terminator                                                  | . 6-<br>. 6-                                         | 59<br>75                            |

|                                                                                  | Tables                                                          |                                                      |                                     |

| Table                                                                            | Title                                                           | Рa                                                   | ge                                  |

| 1-1                                                                              | BUSINESS-PRO System Specifications                              | . 1-                                                 | 7                                   |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6                                           | Address and Control Bus Buffering Buffer States of the Data Bus | . 2-<br>. 2-<br>. 2-<br>. 2-                         | 10<br>19<br>25<br>41                |

| 2-7<br>2-8<br>2-9                                                                | Serial Port Pin Assignments                                     | . 2-                                                 | 44                                  |

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5<br>3-6                                           | Power Supply Nominal Output Voltages                            | . 3-<br>. 3-<br>. 3-                                 | 2 3 4 5                             |

| 4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9 | Initial Keyboard Default Conditions                             | . 4-<br>. 4-<br>. 5-<br>. 5-<br>. 5-<br>. 5-<br>. 5- | -5<br>-17<br>-6<br>-7<br>-15<br>-17 |

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5                                                  | 128-Kilobyte RAM Interface Signals                              | . 6-<br>. 6-                                         | -5<br>-11<br>-13                    |

| Table  |                      | Title                              | Page |

|--------|----------------------|------------------------------------|------|

| 6-6    | 1.2-Megabyte Floppy  | Disk Drive Performance             |      |

|        | Specifications       | Disk Drive Power Requirements      | 6-14 |

| 6-7    | 1.2-Megabyte Floppy  | Disk Drive Power Requirements      | 6-15 |

| 6-8    | 360-Kilobyte Floppy  | Disk Drive Power Connector P2      | 0-T0 |

| 6-9    | 360-Kilobyte Floppy  | Disk Drive Jumper Settings         | 6-17 |

| 6-10   | 360-Kilobyte Floppy  | Disk Drive Specifications          | 6-17 |

| 6-11   |                      | Disk Drive Power Requirements      |      |

| 6-12   |                      | croller Control Connector J3       |      |

| 6-13   |                      | troller Control Connector J4       |      |

| 6-14   | Winchester Disk Cont | troller Data Connector J5          |      |

| 6-15   | Winchester Disk Cont | troller Data Connector J6          | 6-29 |

| 6-16   | Winchester Disk Cont | troller Data Connector J8          | 6-30 |

| 6-17   | Winchester Disk Cont | troller Data Connector J9          | 6-30 |

| 6-18   | Winchester Disk Cont | troller Switches SWl Through SW4 . | 6-31 |

| 6-19   |                      | troller Performance Specifications |      |

| 6-20   |                      | er I/O Port Addresses              |      |

| 6-21   |                      | initions                           |      |

| 6-22   | Winchester Controlle | er Commands                        | 6-37 |

| 6-23   | Controller-Supported | d Stepping Rates                   | 6-38 |

| 6-24   | BUSINESS-PRO Drive   | Types                              | 6-43 |

| 6-25   | Comparison of Winche | ester Disk Drive Types             | 6-44 |

| 6-26   |                      | ive Control Connector Jl           |      |

| 6-27   |                      | ive Data Connector J2              |      |

| 6-28   |                      | ive Power Connector J3             |      |

| 6-29   |                      | ive Performance Specifications     |      |

| 6-30   | 21-Megabyte Disk Dr: | ive Power Requirements             | 6-52 |

| 6-31   | 40-Megabyte Disk Dr: | ive Control Connector J3           | 6-54 |

| 6-32   | 40-Megabyte Disk Dr: | ive Data Connector J3              | 6-57 |

| 6-33   |                      | ive Power Connector J2             |      |

| 6-34   |                      | ive Performance Specifications     |      |

| 6-35   |                      | ive DC Power Requirements          |      |

| 6-36   |                      | ive Control Connector J3           |      |

| 6-37   |                      | ive Data Connector J3              |      |

| 6-38   |                      | ive Power Connector J2             |      |

| 6-39   |                      | ive Performance Specifications     |      |

| 6-40   |                      | ive DC Power Requirements          |      |

| 6-41   |                      | rive Control Connector Jl          |      |

| 6-42   |                      | rive Data Connector J2             |      |

| 6-43   |                      | rive Power Connector J3            |      |

| 6 - 44 |                      | rive Performance Specifications .  |      |

| 6-45   |                      | rive DC Power Requirements         |      |

| 6-46   | Tape Drive Interfac  | e Signals Connector Jl             | 6-80 |

| 6-47   | Tape Position Codes  | nnector J2                         | 6-83 |

| 6-48   | Tape Drive Power Co  | nnector J2                         | 6-83 |

| 6-49   | Tape Drive Performa  | nce Specifications                 | 6-84 |

| 6-50   | Tape Drive Power Re  | quirements                         | 6-85 |

| 6-51   |                      | ansion Bus Interface Signals       |      |

| 6-52   | Tape Controller Jum  | per Settings                       | 6-89 |

| 6-53   |                      | gnostic Indicators                 |      |

| 6-54   | Tape Controller Reg  | isters                             | 6-90 |

| Table        | Title                                                 | Page  |

|--------------|-------------------------------------------------------|-------|

| C ==         | Mana Cantuallan Danfarmanaa Chasifiastiona            | 6 02  |

| 6-55         | Tape Controller Performance Specifications            |       |

| 6-56         | Tape Controller Power Requirements                    |       |

| 6-57         | TI Mode CRT Controller/Monitor Interface Connector J3 |       |

| 6-58         | TI Mode/PC-AT Mode Controller Interface Connector J4  |       |

| 6-59         | TI Mode CRT Controller Expansion Interface Signals .  |       |

| 6-60         | TI Mode CRT Controller Performance Specifications     |       |

| 6-61         | Video AC Parameters                                   |       |

| 6-62         | CRT System Memory Map                                 |       |

| 6-63         | CRTC Programming Values                               | 6-107 |

| 6-64         | Color Map                                             |       |

| 6-65         | Organization of Graphics Screen Memory Into Pixels .  |       |

| 6-66         | Color Combinations                                    |       |

| 6-67         | Bit Correlations                                      |       |

| 6-68         | Color Latch Byte                                      | 6-113 |

| 6-69         | Default Values of Color Latches                       |       |

| 6-70         | TIPC vs BUSINESS-PRO Monochrome Compatibility         | 6-116 |

| 6-71         | PC-AT Mode CRT Controller/Monitor Interface           |       |

| 6 70         | Connector J3                                          |       |

| 6-72         | Interface Connector J4                                |       |

| 6-73         | PC-AT Mode CRT Controller Expansion Interface Signals |       |

| 6-74         | Light Pen Enable Connector J5                         | 6-T22 |

| 6-75         | PC-AT CRT Controller Specifications                   |       |

| 6-76         | SWI Selectable Options                                | 6-125 |

| 6-77         | PC-AT Controller Monochrome I/O Addresses             |       |

| 6-78         | PC-AT CRTC Color Graphics I/O Addresses               |       |

| 6-79         | Bit Functions of Control Port 3D8H                    |       |

| 6-80         | Valid Color/Graphics Mode 3D8H                        | 0-T3( |

| 6-81<br>6-82 | PC-AT CRT Controller Color Select Register            | 6-13( |

| 6-83         | Bit Functions of Status Port 3DAH                     |       |

| 6-84         | CRT Timing Parameters                                 |       |

| 6-85         |                                                       |       |

| 6-86         | Color Display Unit Color Map                          | 6-130 |

| 6-87         | Color Display Unit Video AC Parameters                |       |

| 6-88         | Color Display Unit Performance Specifications         | 6-141 |

| 6-89         | Color Display Unit AC Power Requirements              |       |

| 6-90         | Monochrome Display Unit/Controller Interface          | 0 11. |

| 0 00         | Connector II                                          | 6-144 |

| 6-91         | Connector J2                                          | 6-146 |

| 6-92         | Monochrome Display Unit Video AC Parameters           | 6-14  |

| 6-93         | Keyboard/Mouse Connector J4                           |       |

| 6-94         | Monochrome Display Unit Performance Specifications .  | 6-149 |

| 6-95         | Monochrome Display Unit AC Power Requirements         |       |

| 6-96         | TI Mode RS-232 Serial Interface Connector J1          | 6-153 |

| 6-97         | Port-Selection Switches SWI-1 Through SWI-4           | 6-15  |

| 6-98         | TI Mode RS-232 Serial Interface Port Addresses        | 6-15  |

| 6-99         | TI Mode RS-232 Interface Programmable Baud Rate       | 0 10. |

|              | Values                                                | 6-154 |

| 6-100        | Optical Mouse Interface Signals                       | 6-15  |

| 6-101        | Mouse Data Format                                     | 6-156 |

| 6-102        | Ontigal Mouga Porformance Charling                    | 6-154 |

#### Preface

This document provides technical information about the standard and optional hardware devices of the Texas Instruments (TI) BUSINESS-PRO(TM) Computer, TI Part No. 2240803-0001. The information in this document is intended to be used by system designers, value added retailers (VARs), maintenance personnel, and system users. This manual is divided into the following six sections and seven appendixes:

#### Section

- Introduction -- Provides general information about the BUSINESS-PRO computer, a general system overview, and system specifications.

- Main Logic Board -- Provides detailed information about the operation and the capabilities of the BUSINESS-PRO main logic board. This section includes information about the system central processing unit, the system memory and memory control logic, the direct-memory access logic, the input/output (I/O) control logic, and various system interfaces.

- Power Supply -- Provides tabulated information about the BUSINESS-PRO system power supply.

- Keyboard -- Provides descriptive information about BUSINESS-PRO keyboard, its interface to the system, and the commands used for communication and data transfer between the system and the keyboard.

- Floppy Disk Drive Controller -- Provides information about the controller and the floppy disk drive interface.

- 6 Hardware Options -- Provides information about the various optional hardware devices and subsystems that are available for the BUSINESS-PRO computer.

#### Appendixes

G

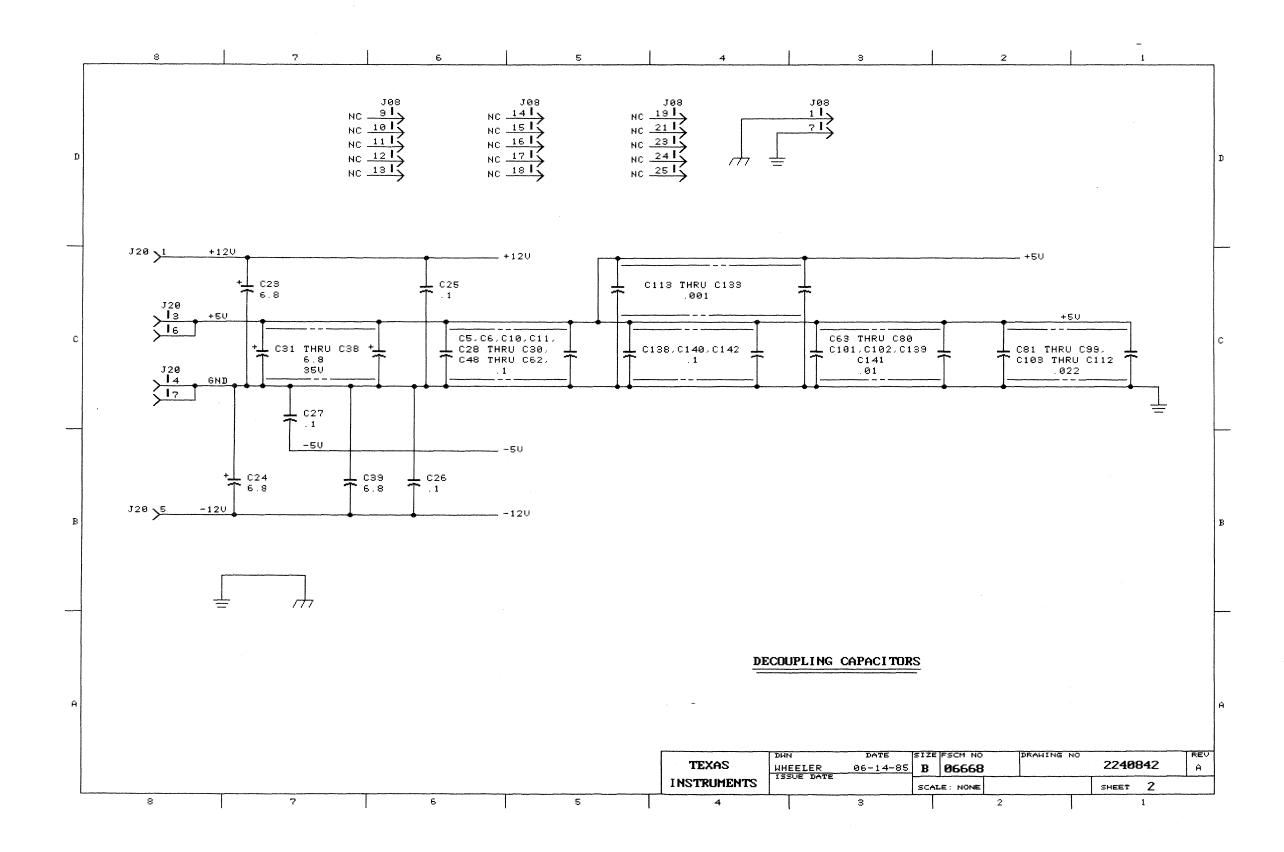

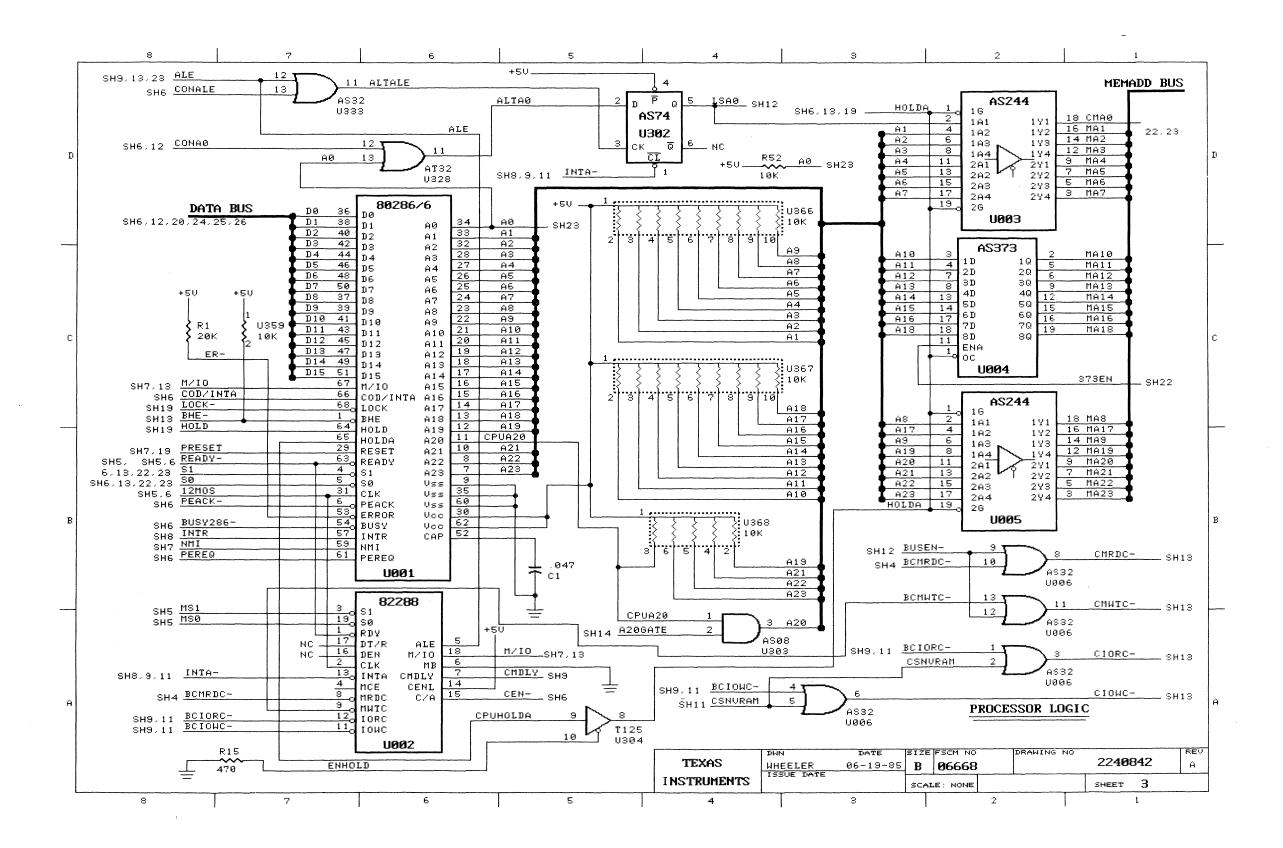

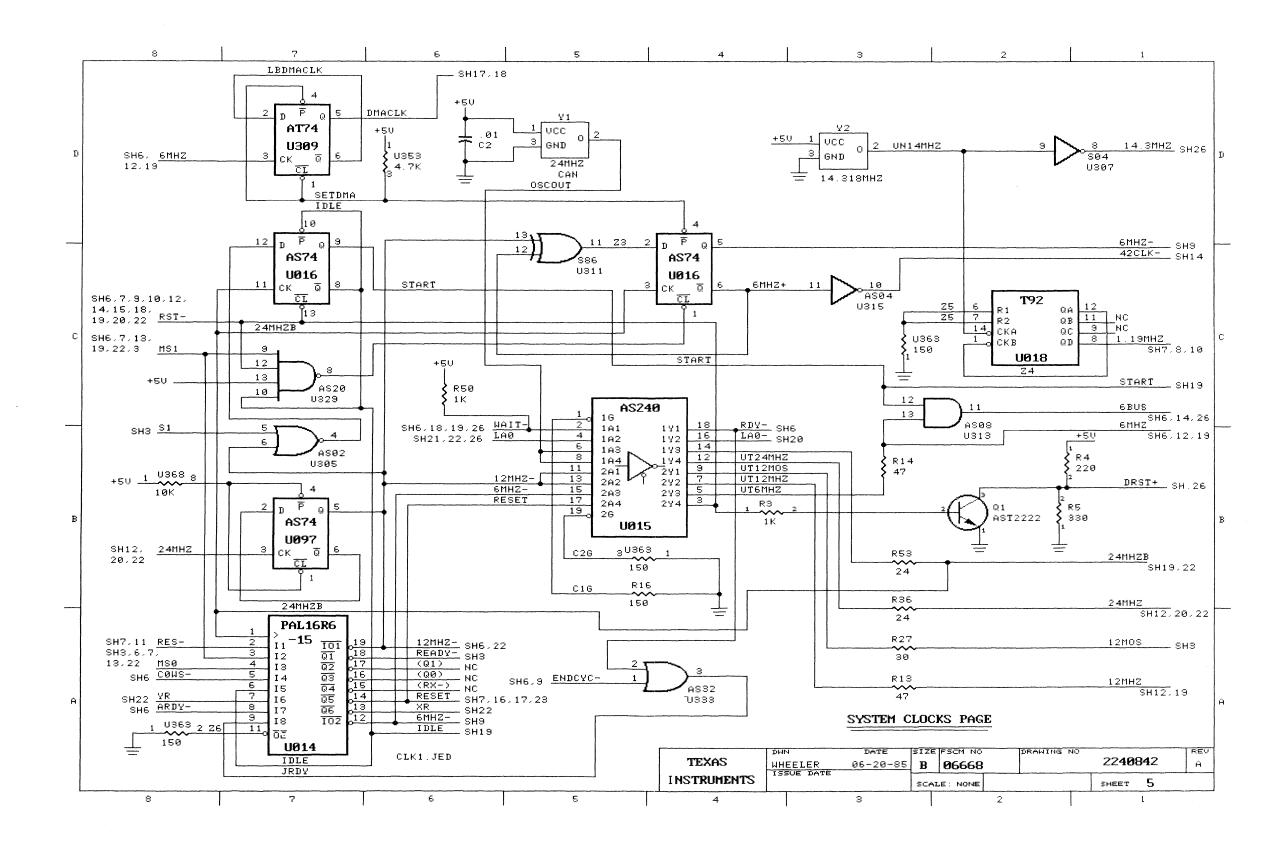

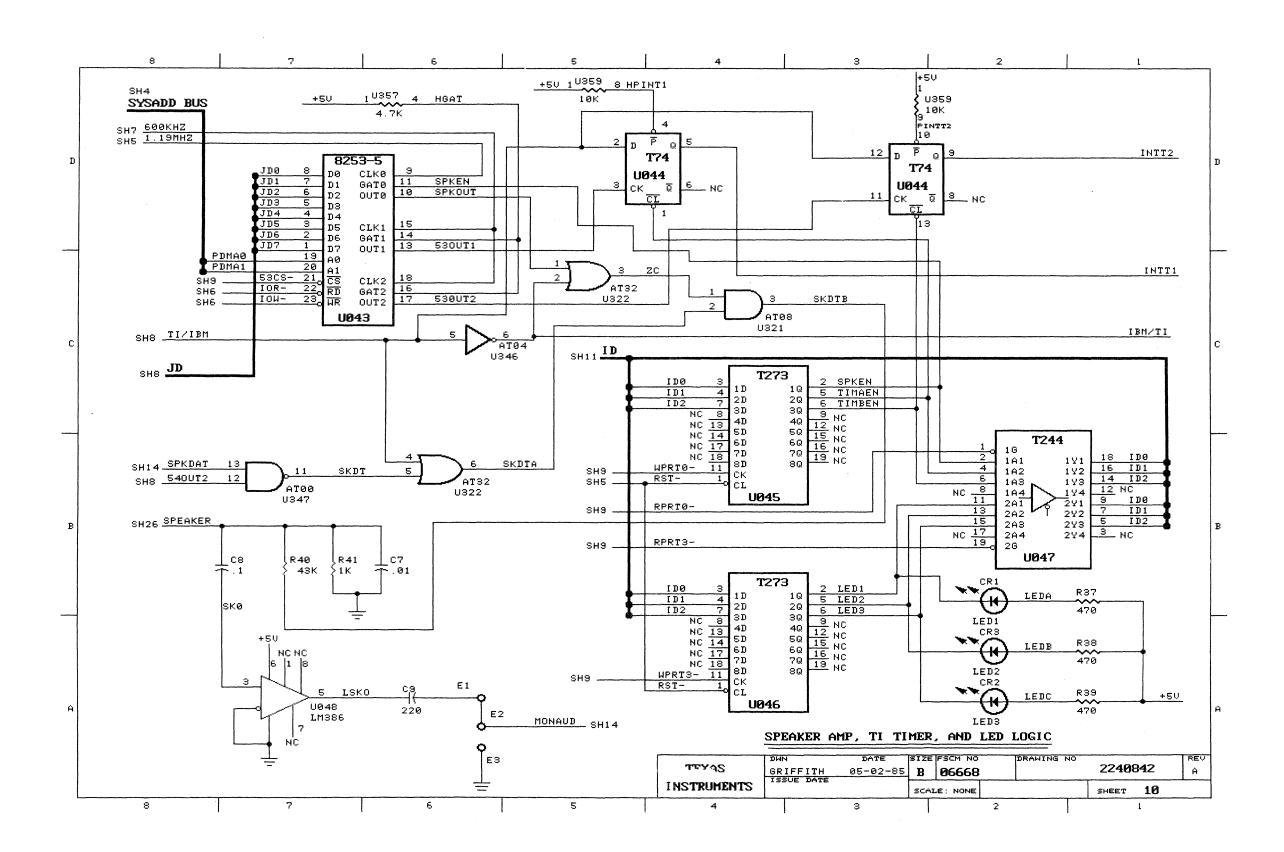

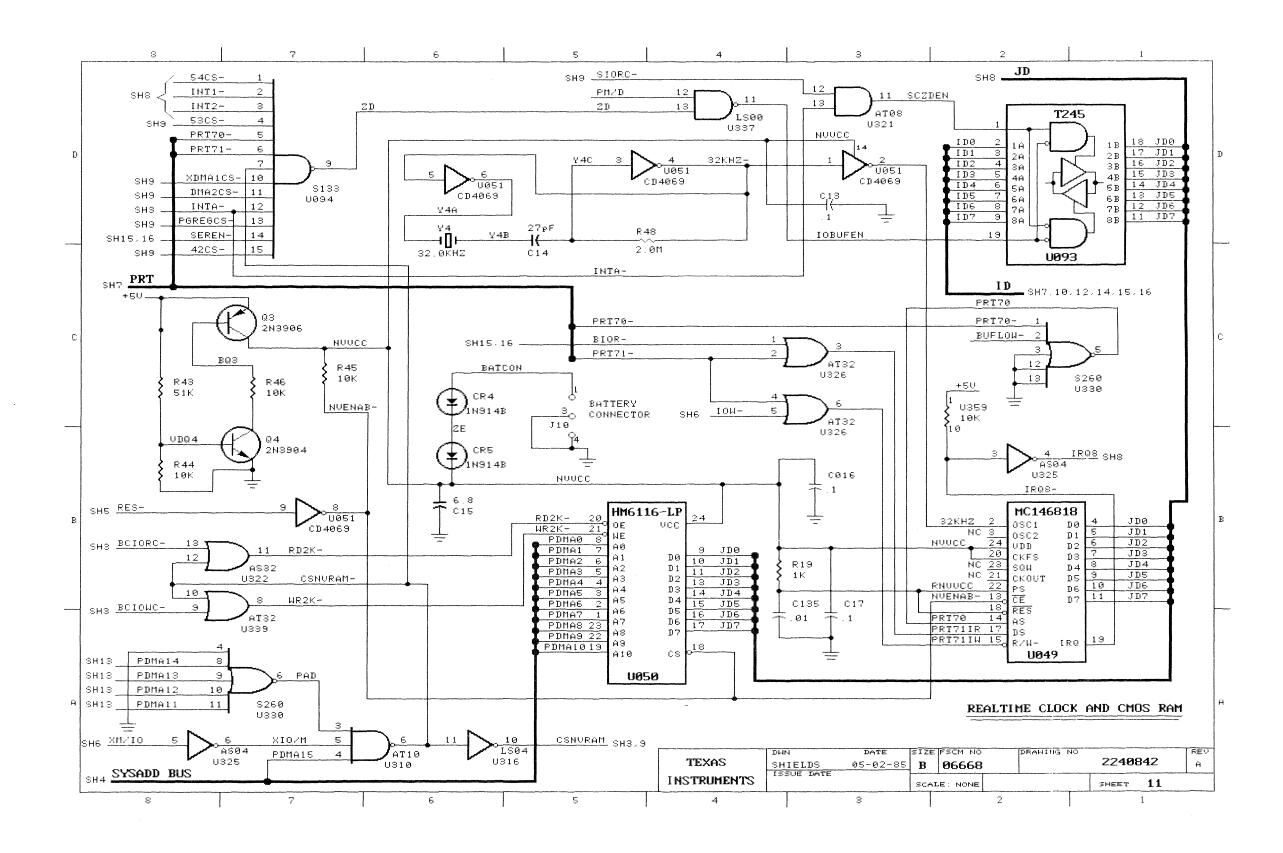

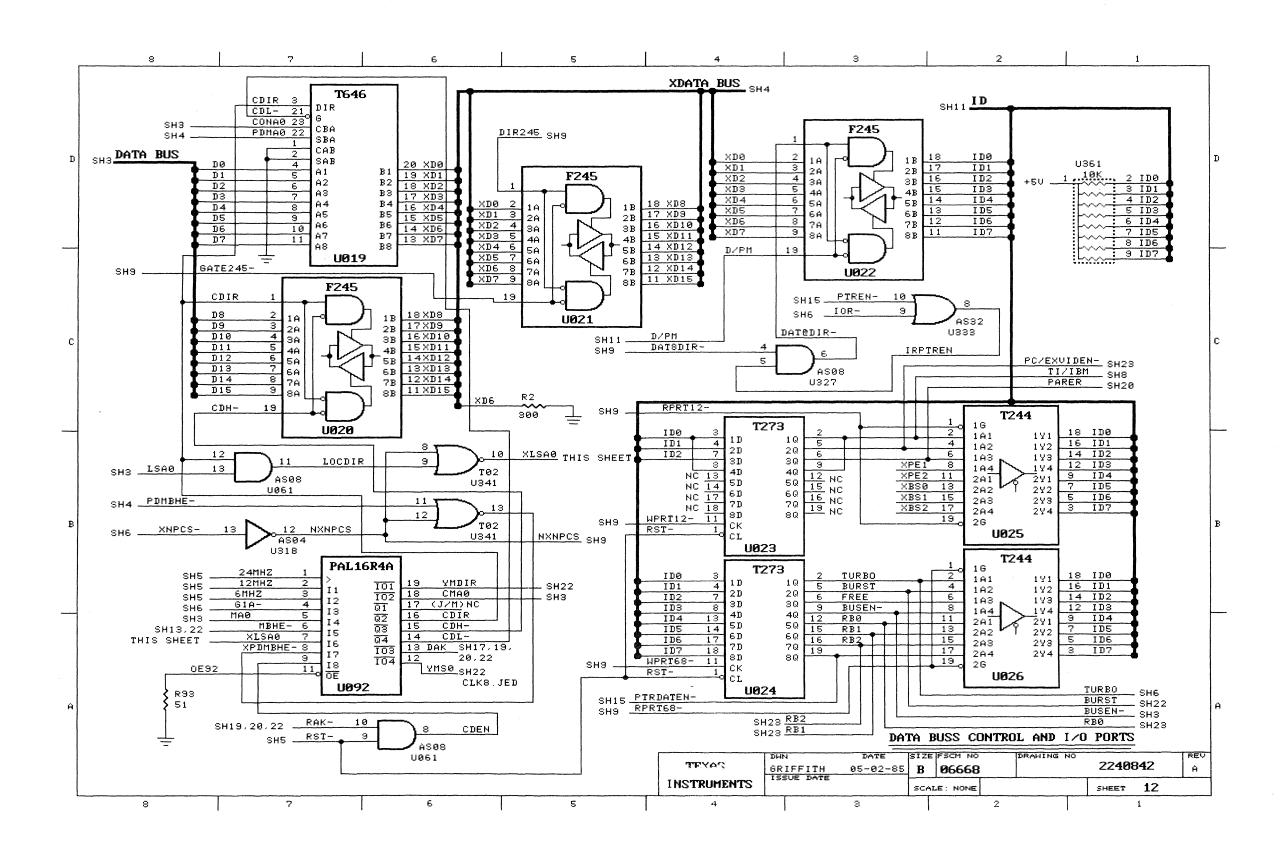

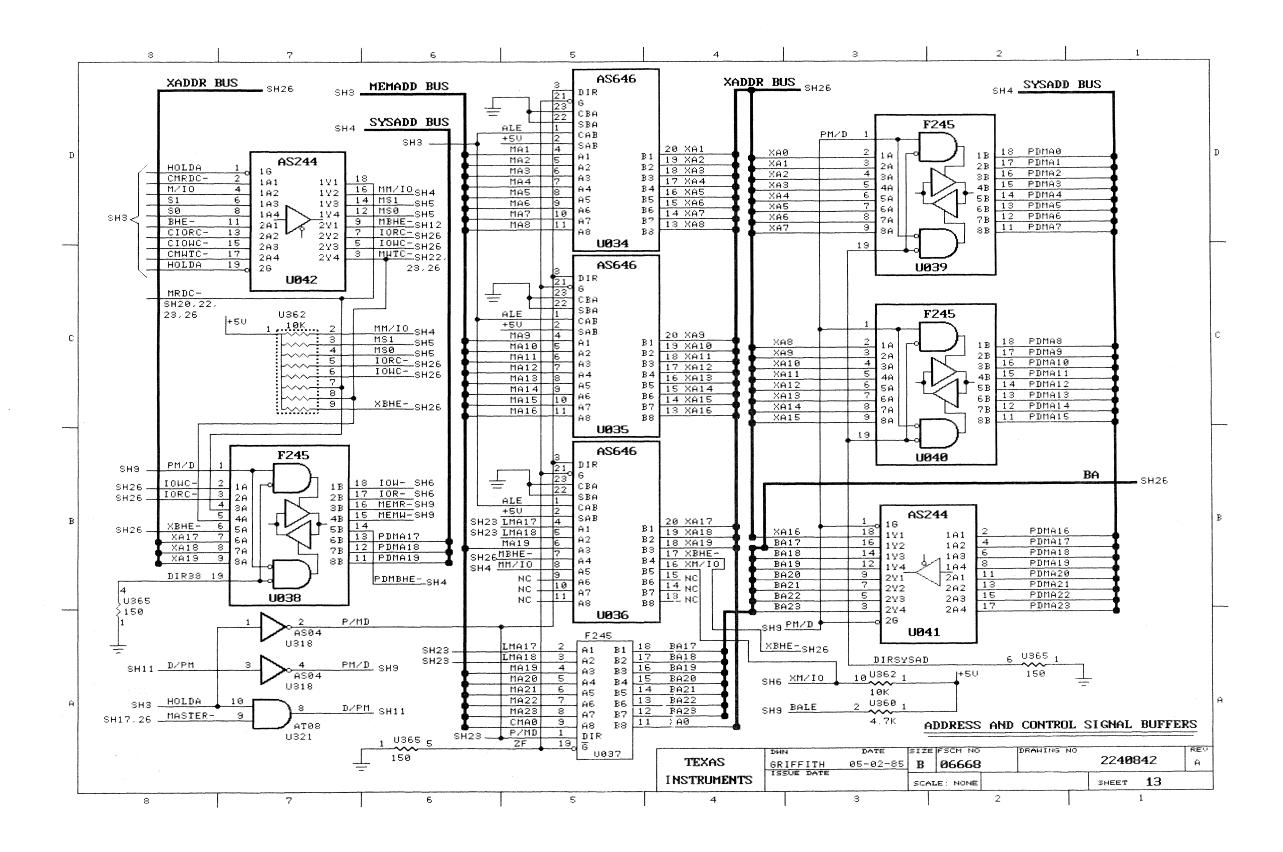

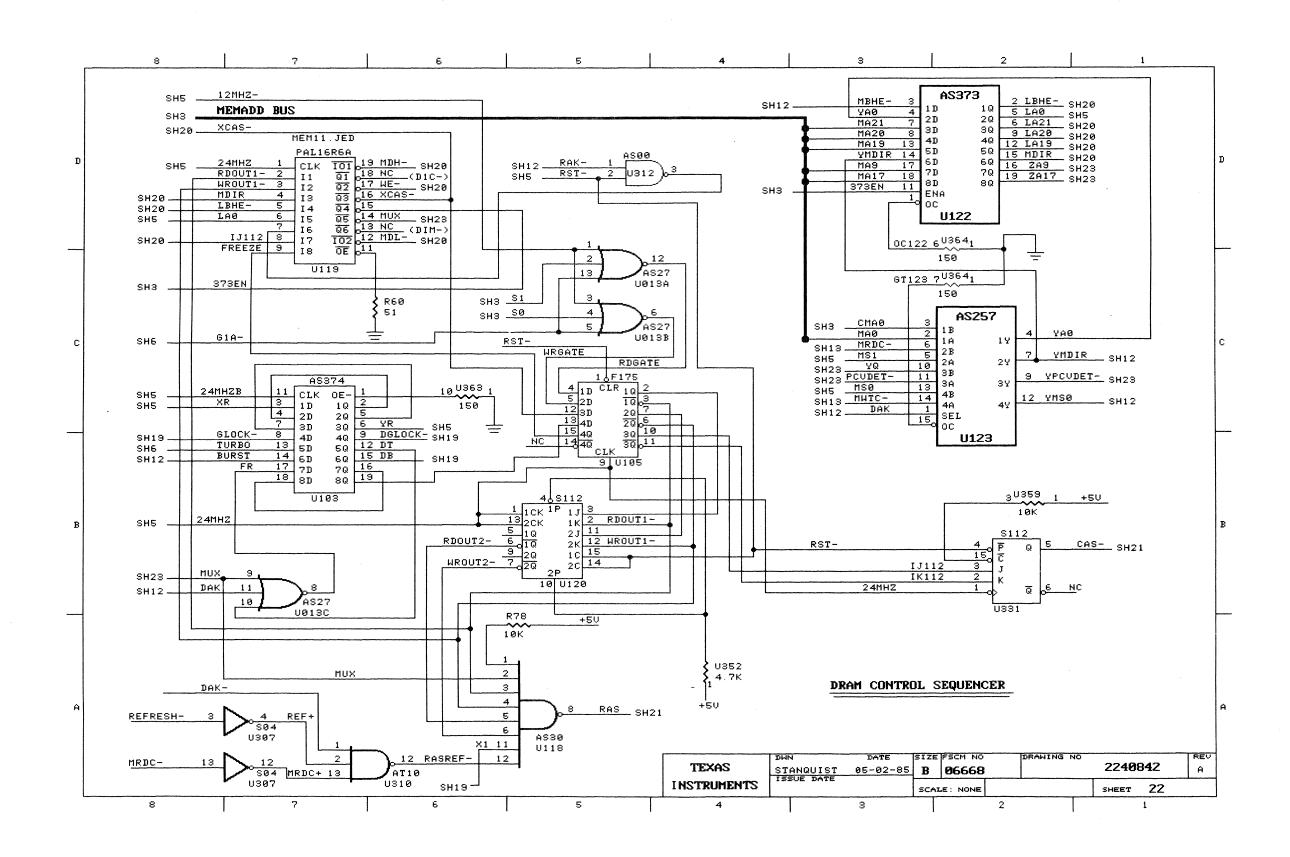

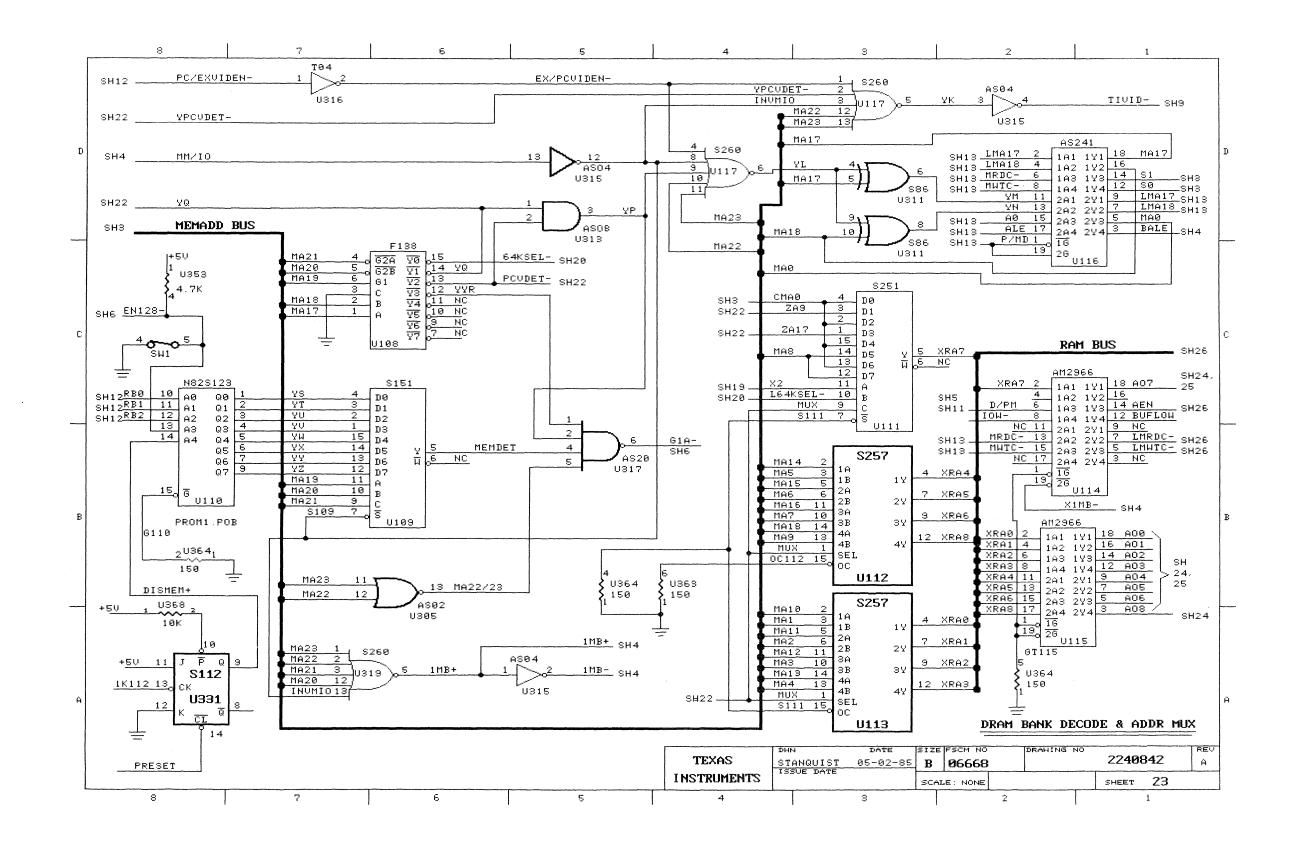

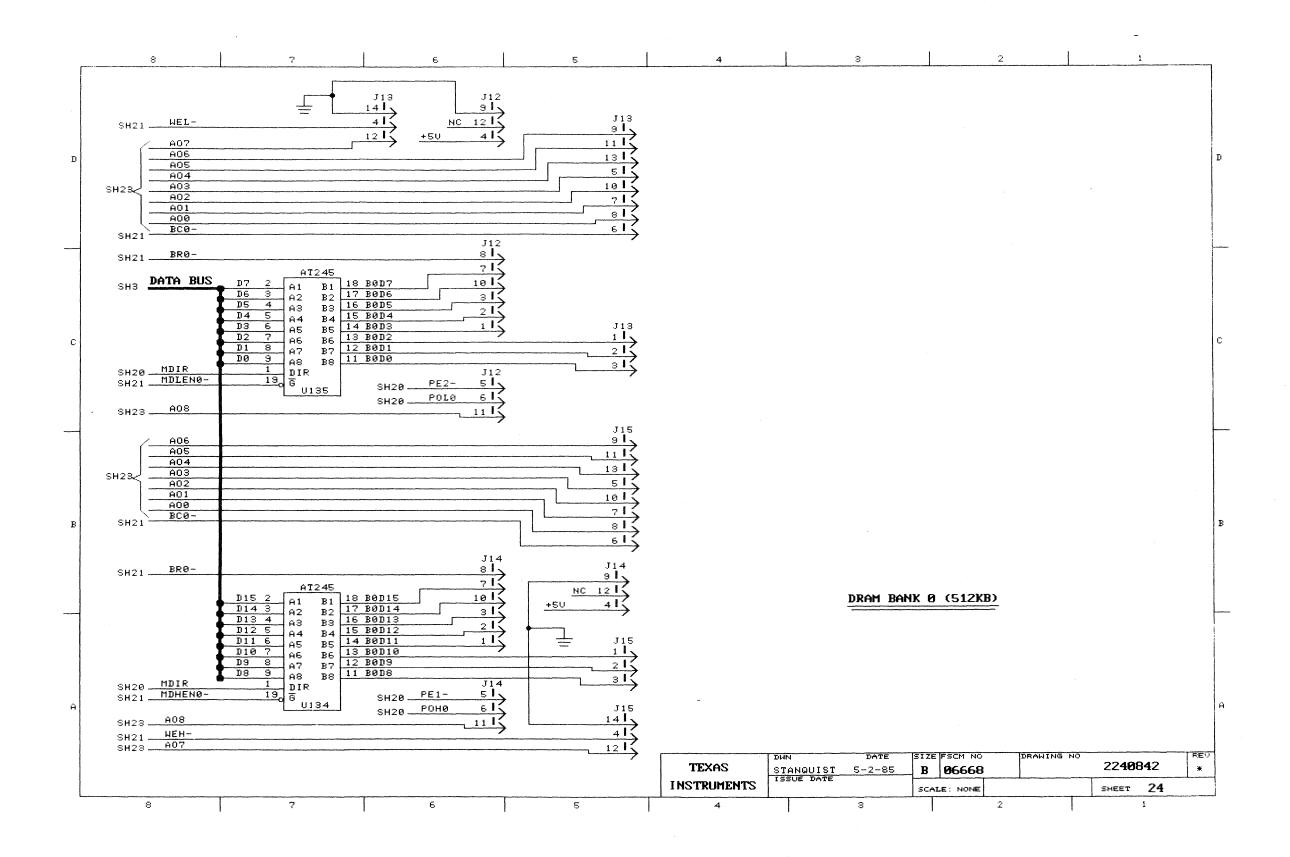

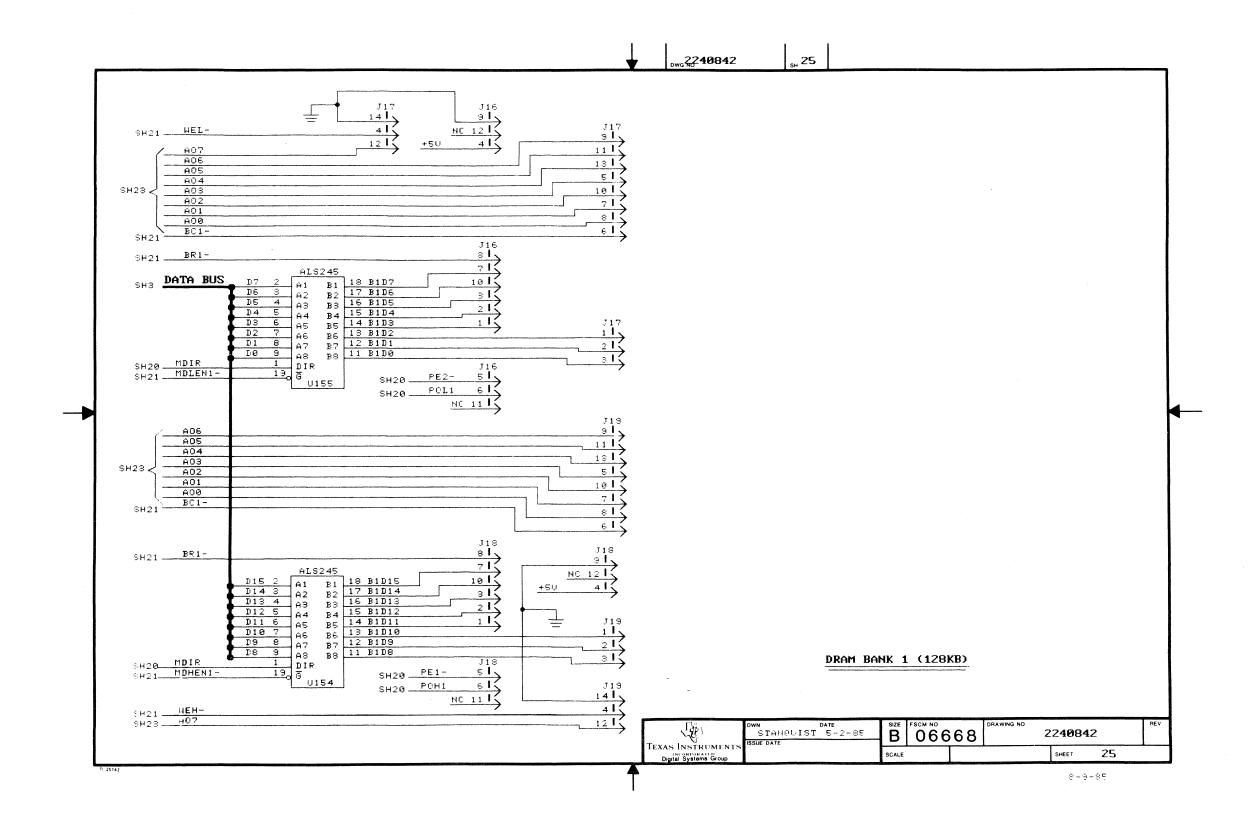

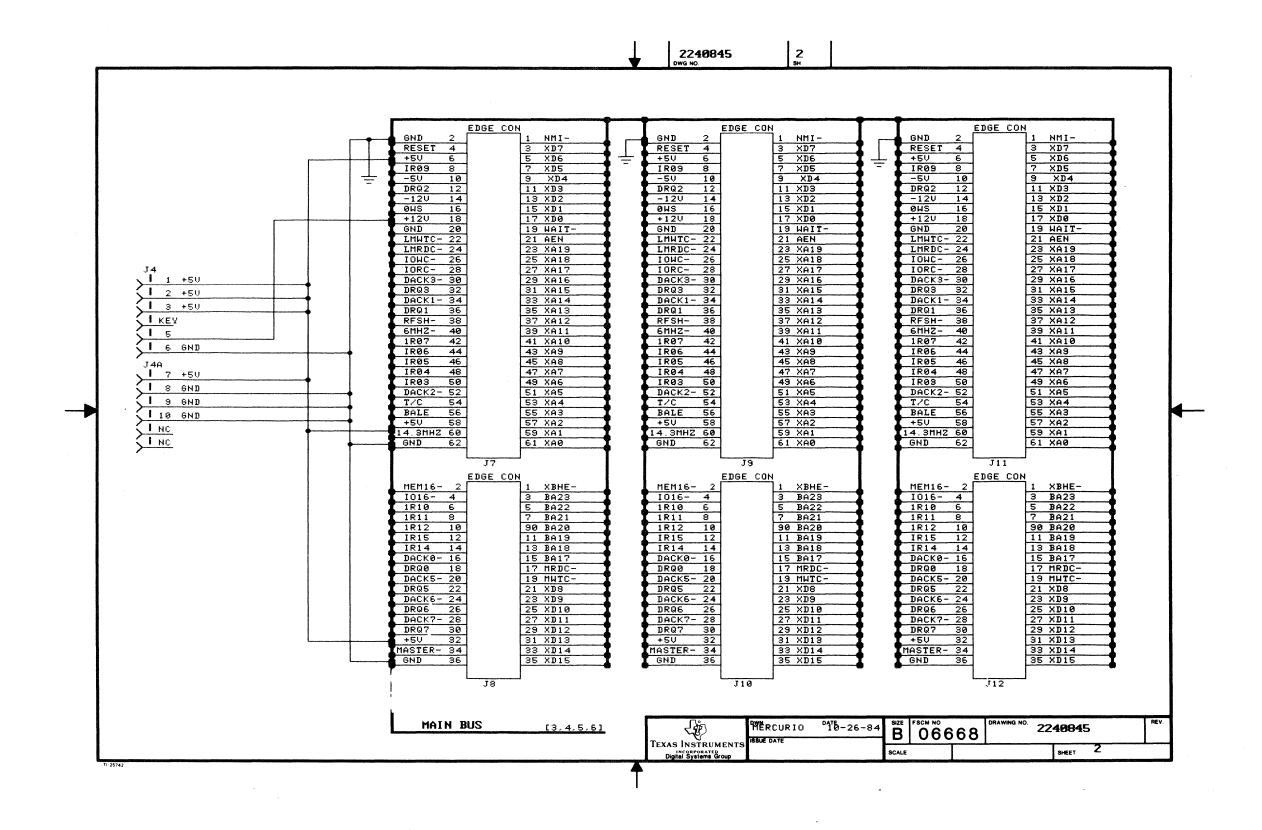

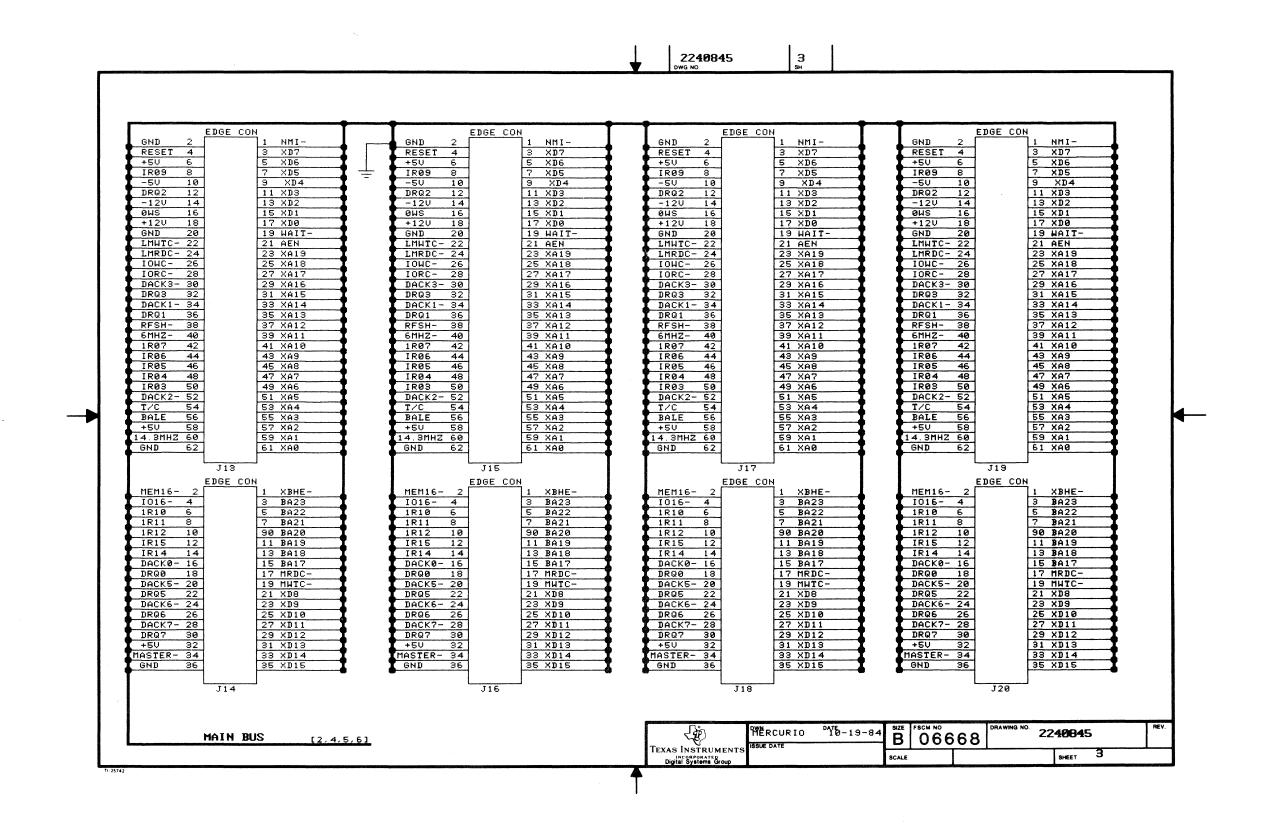

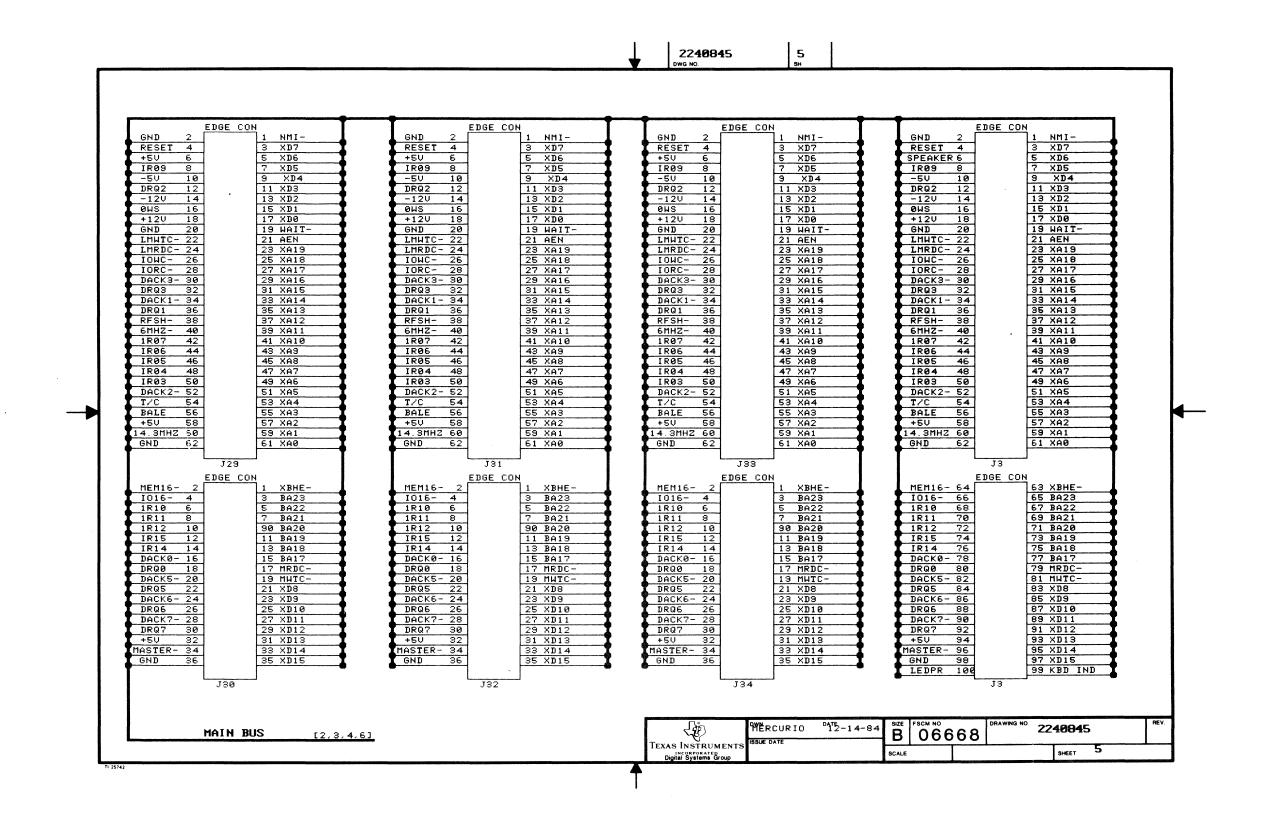

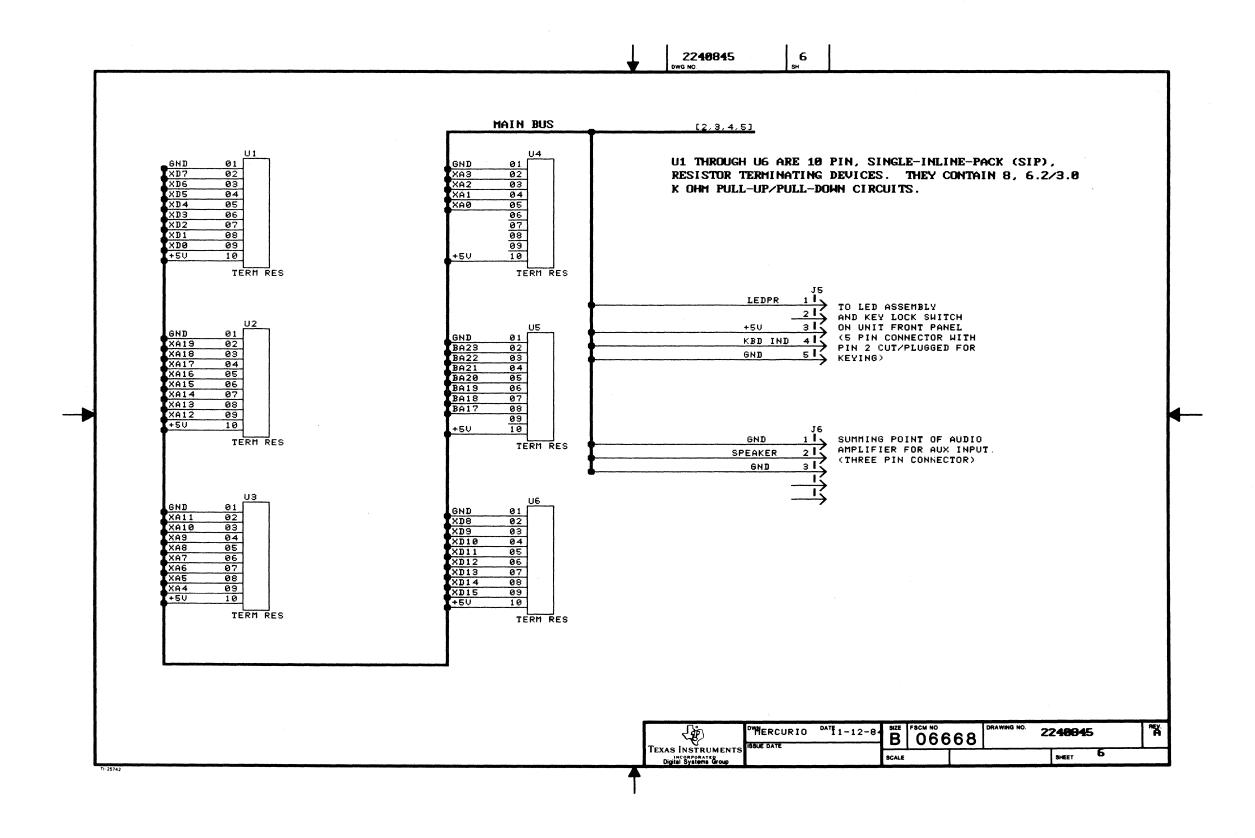

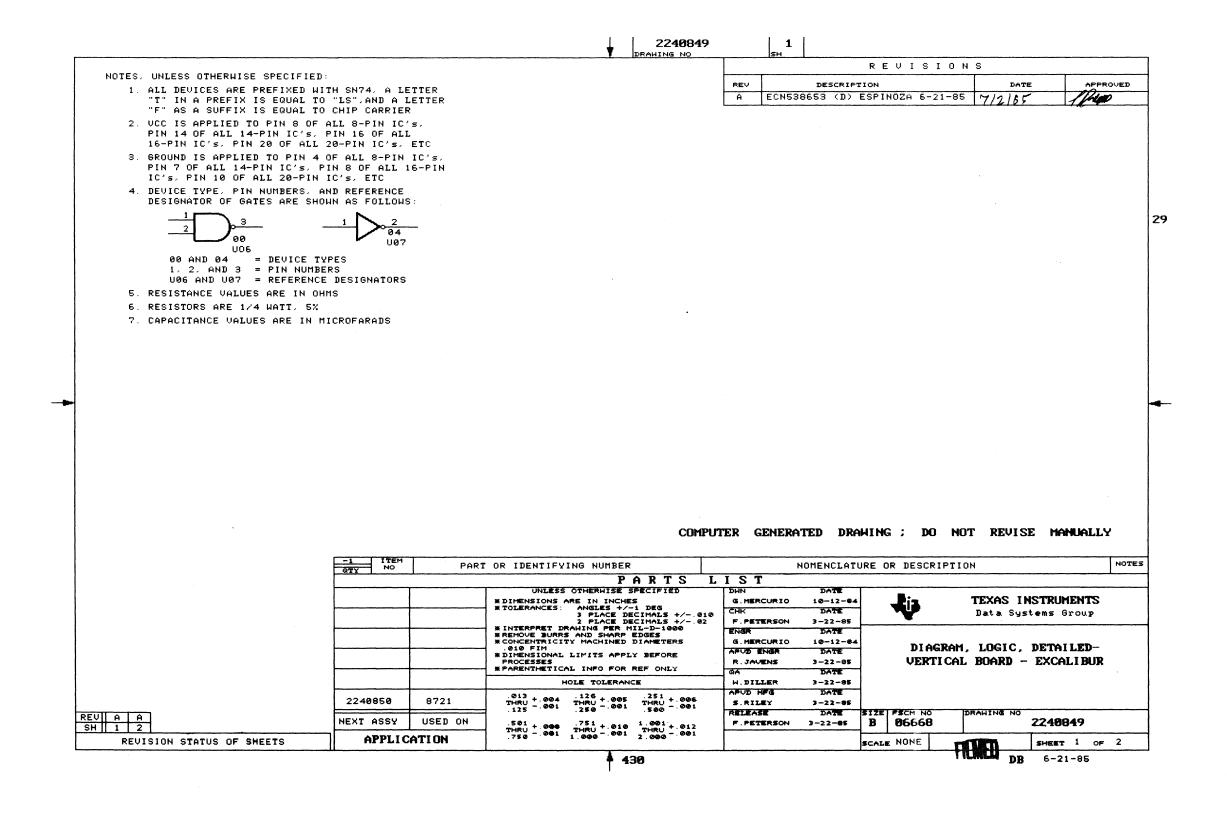

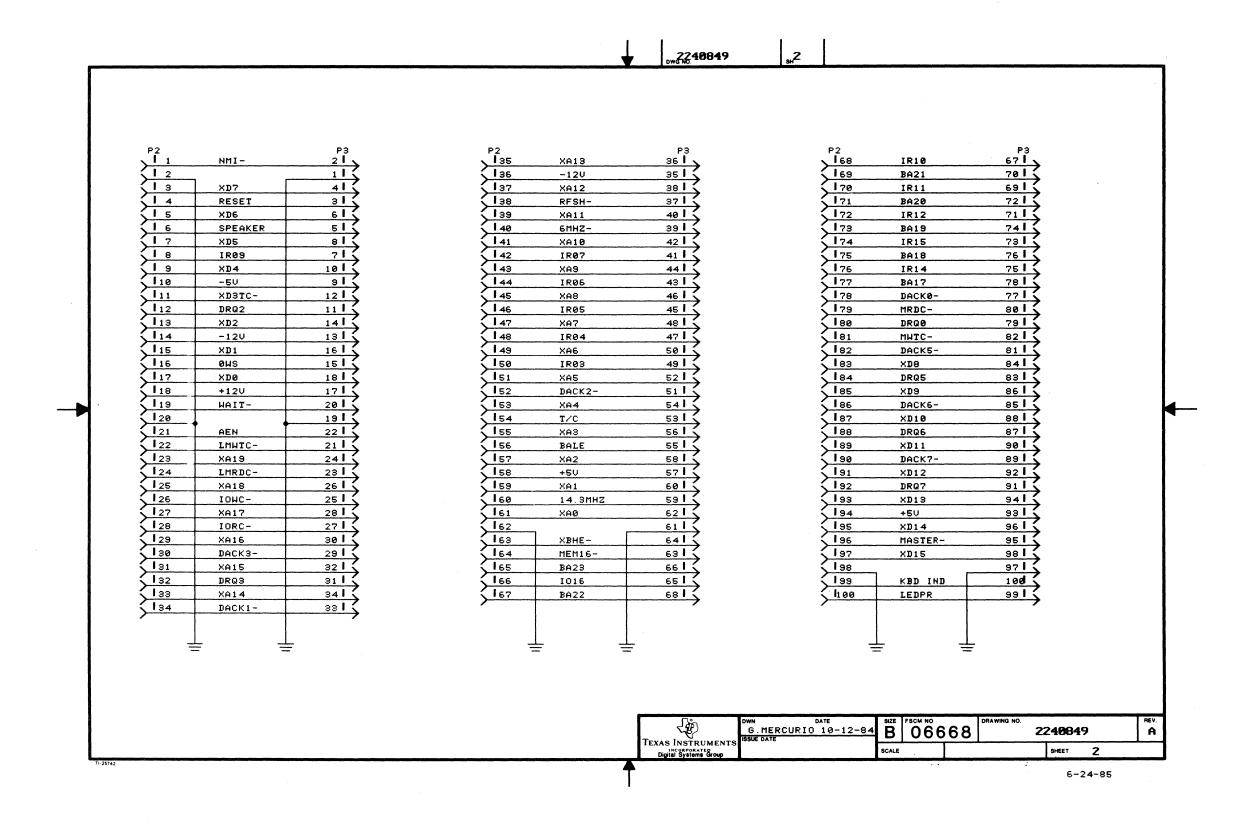

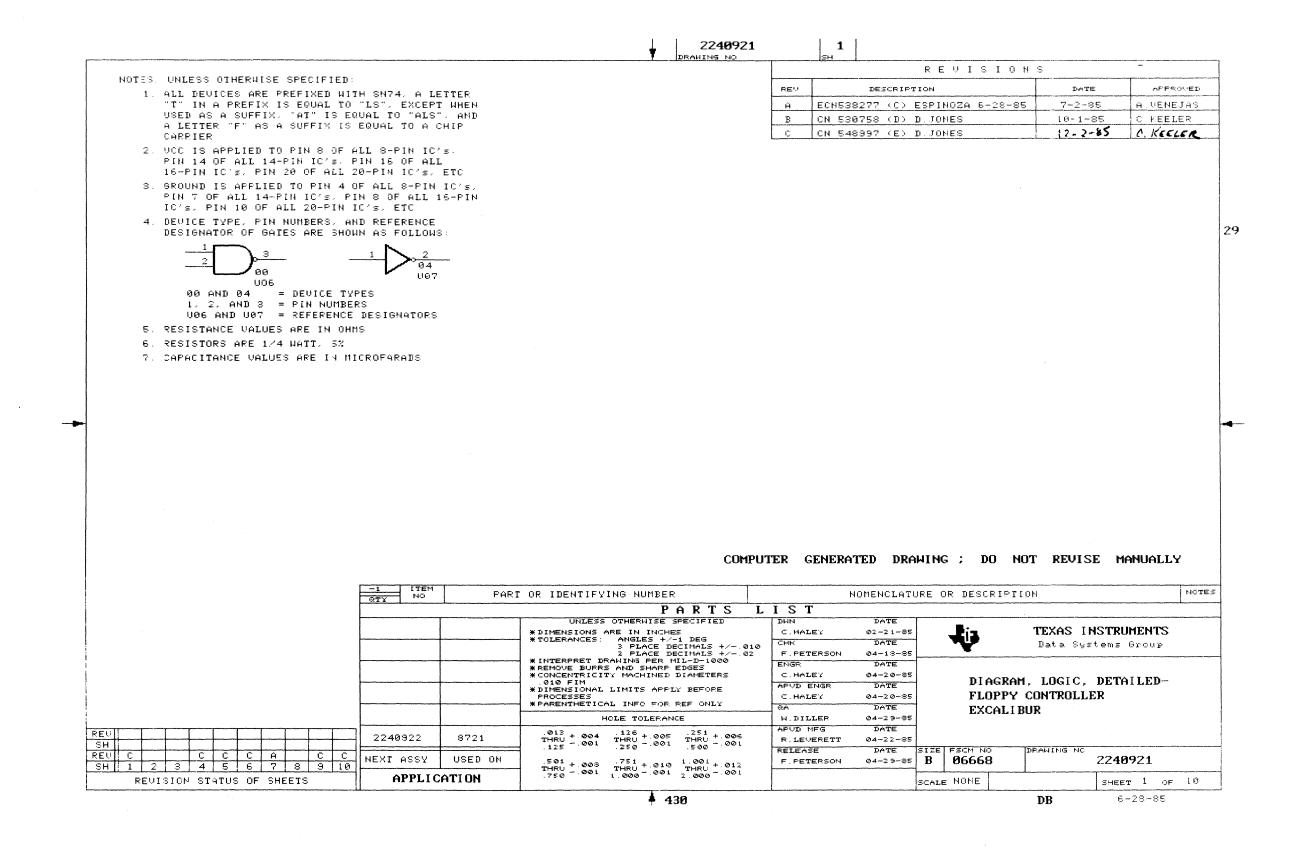

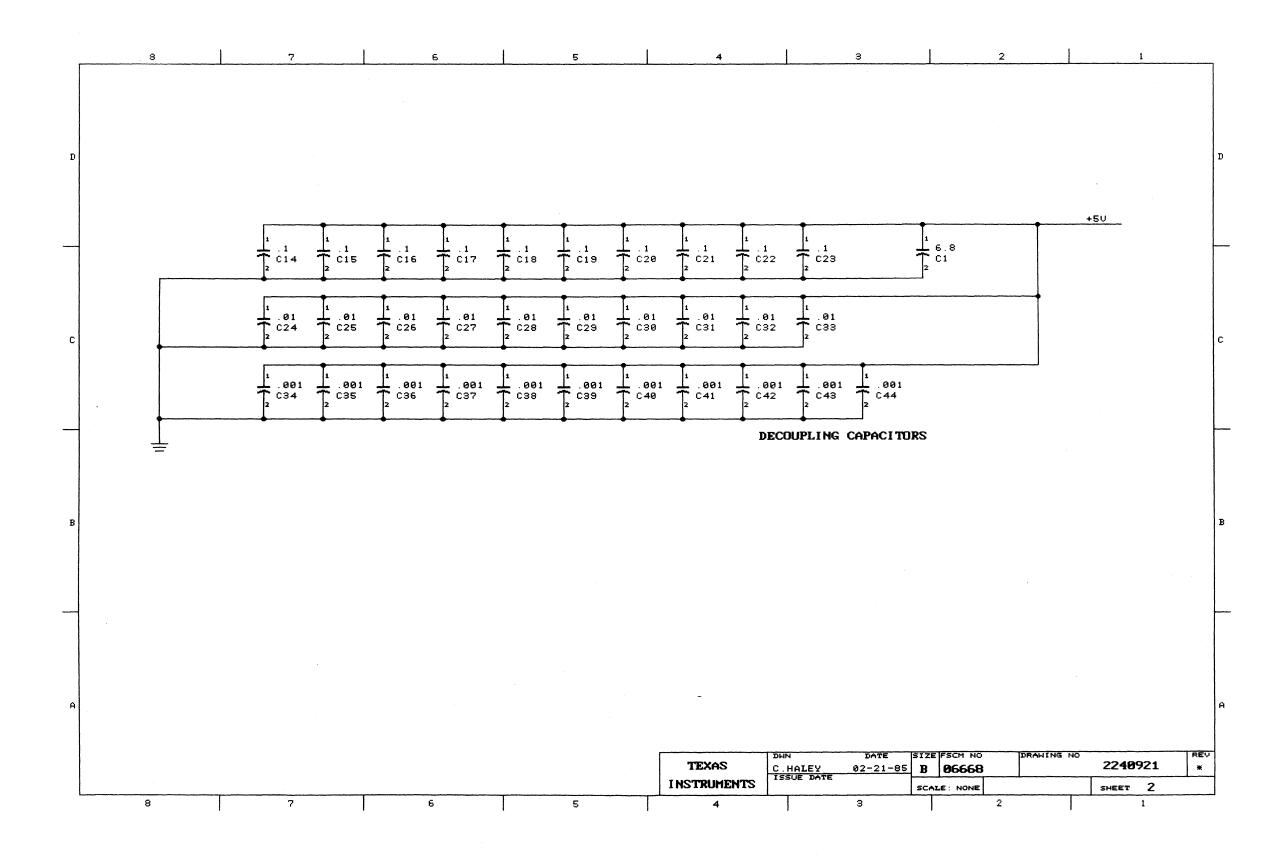

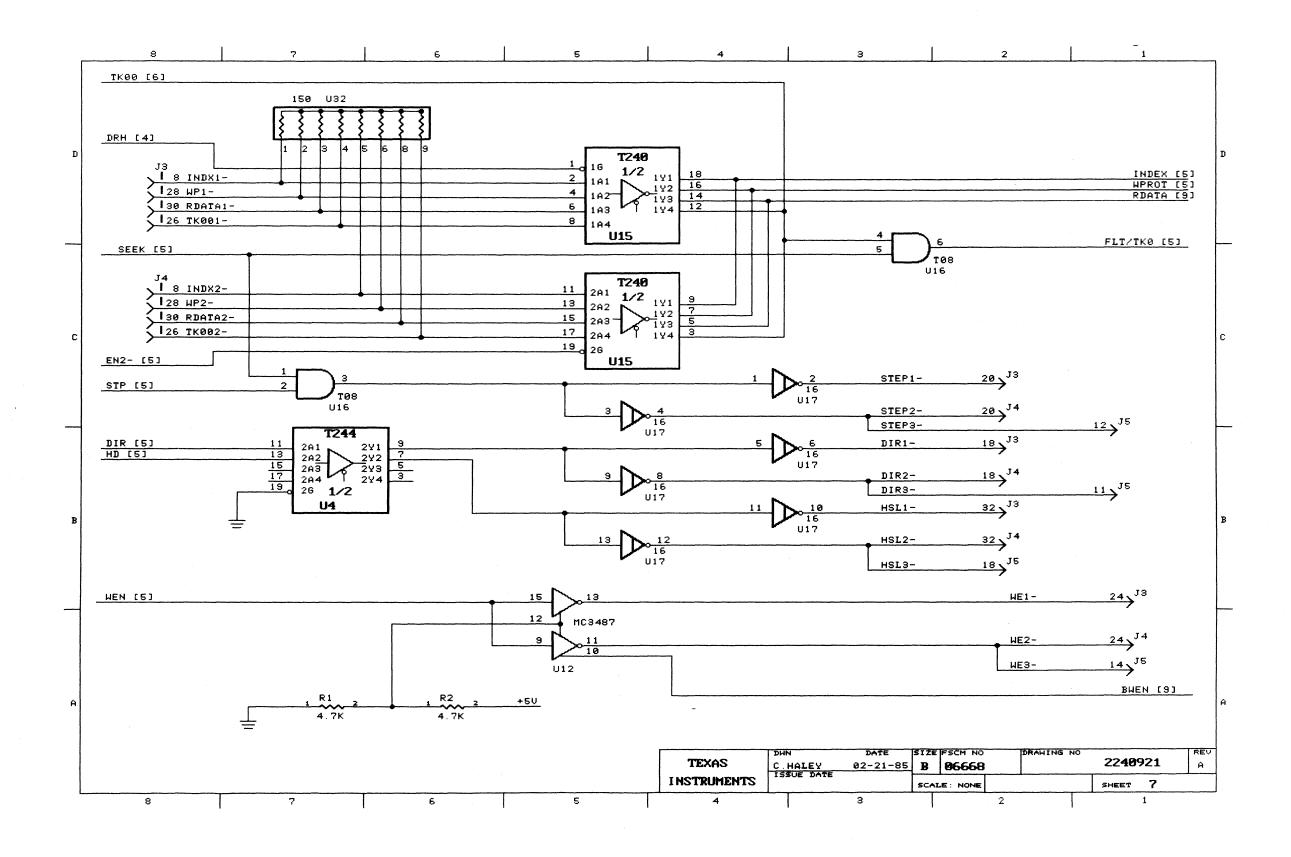

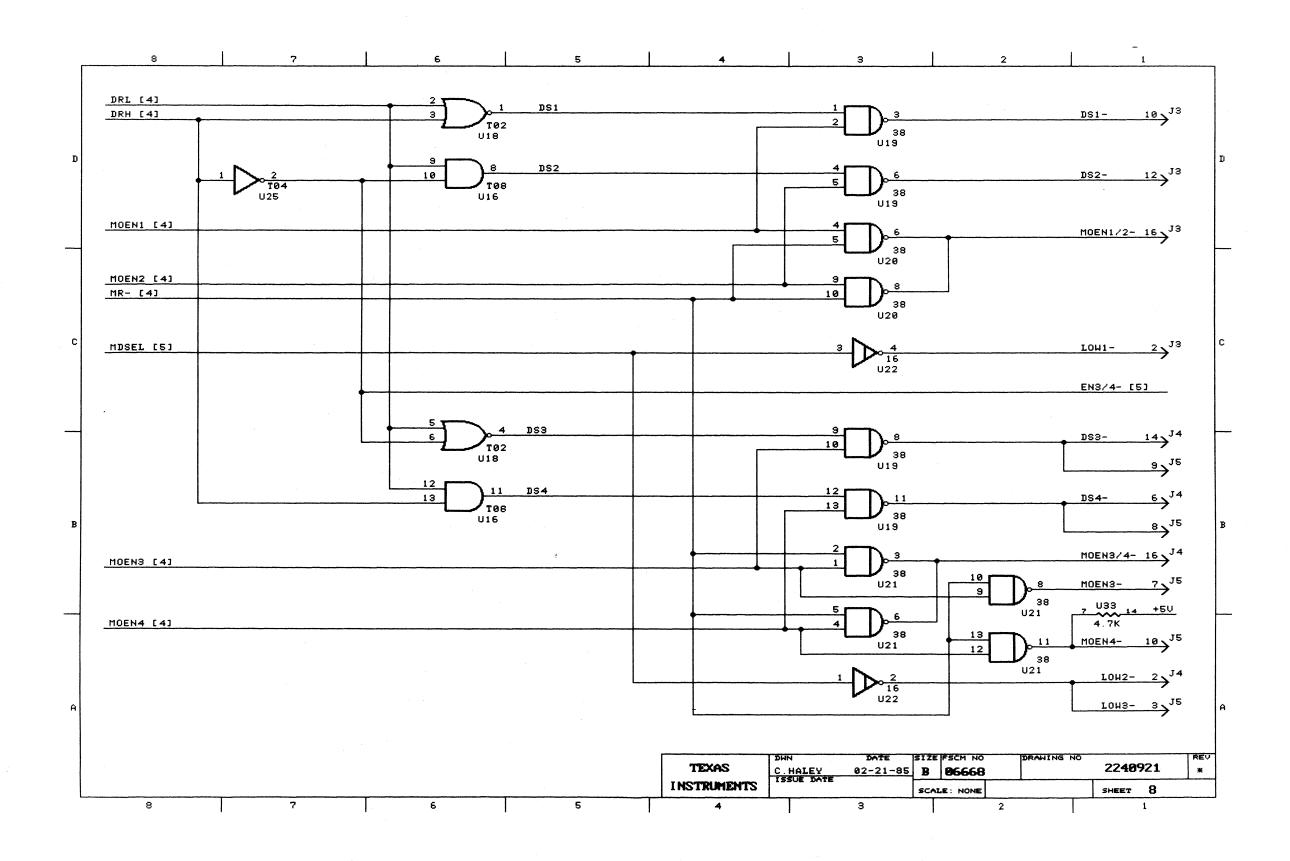

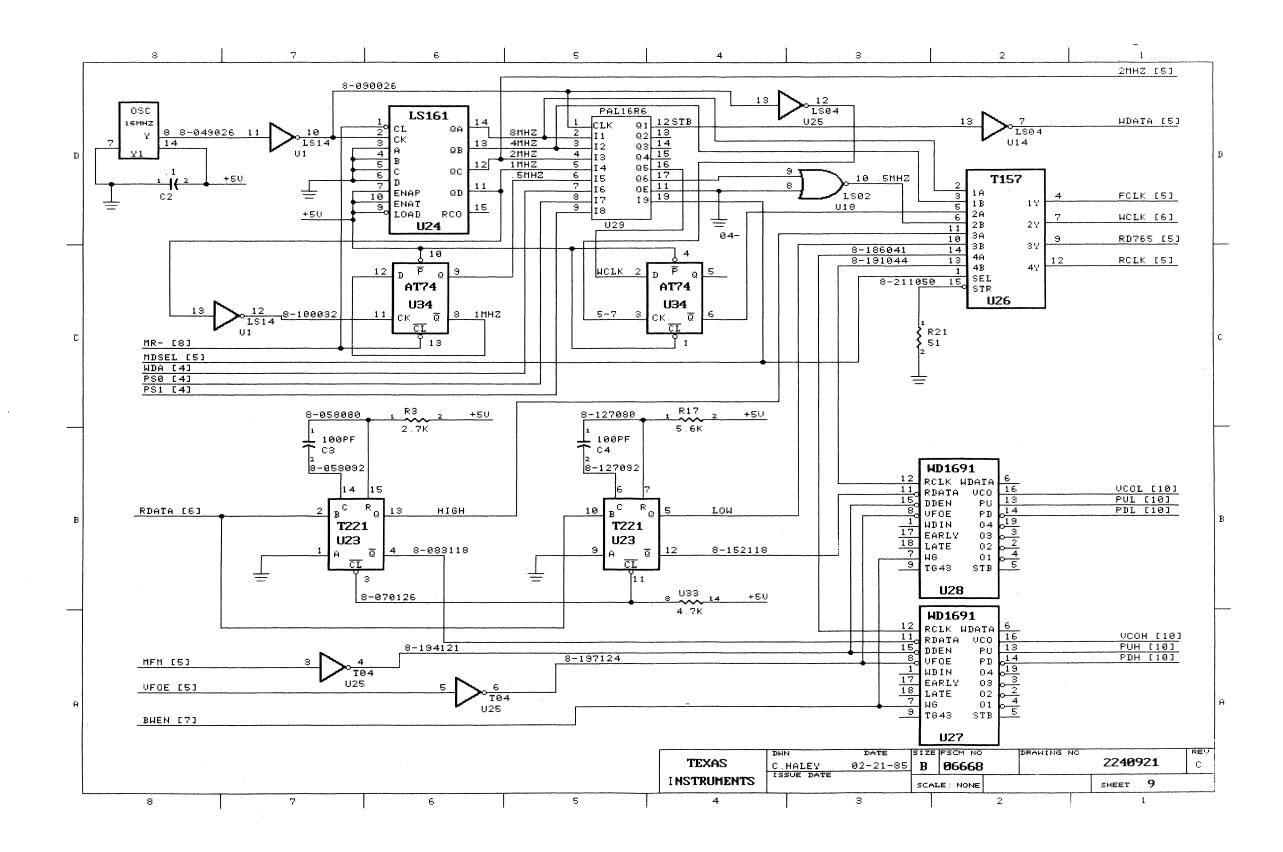

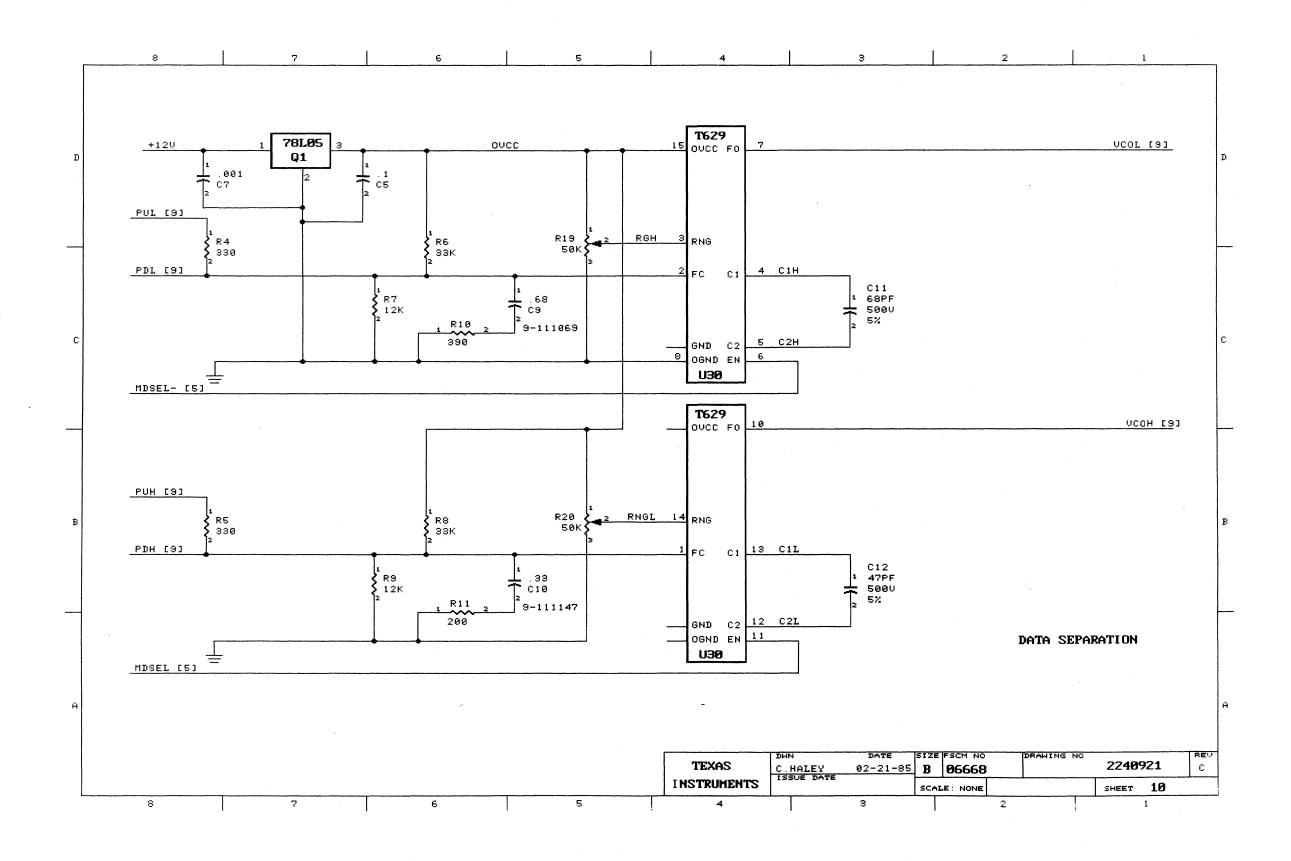

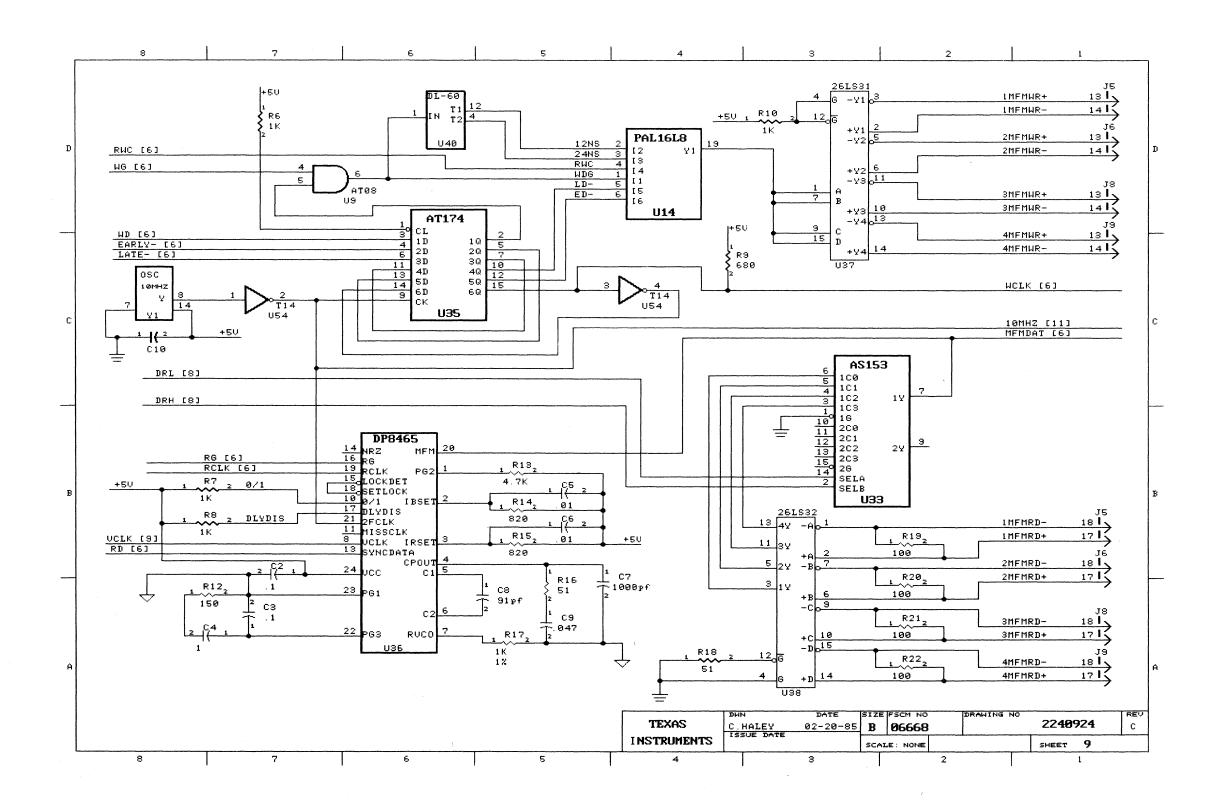

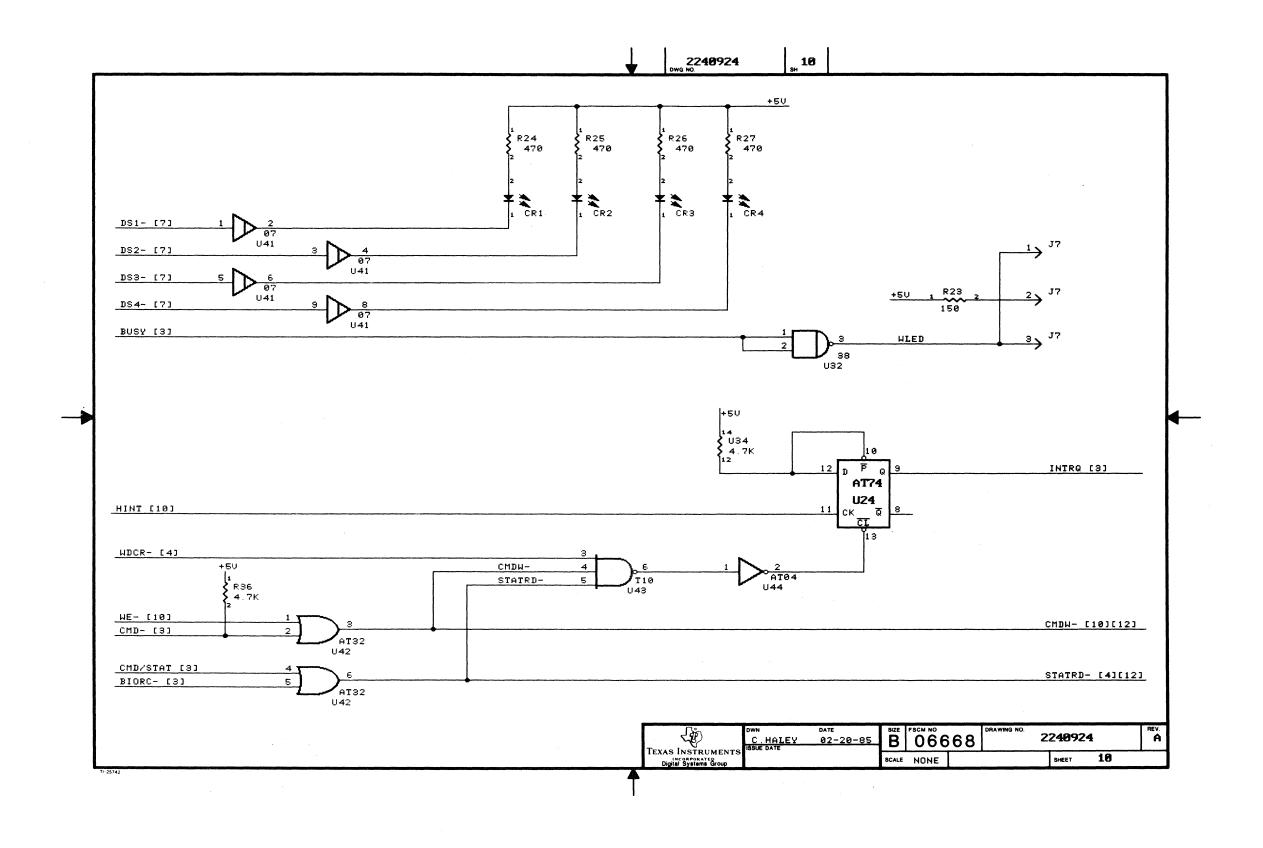

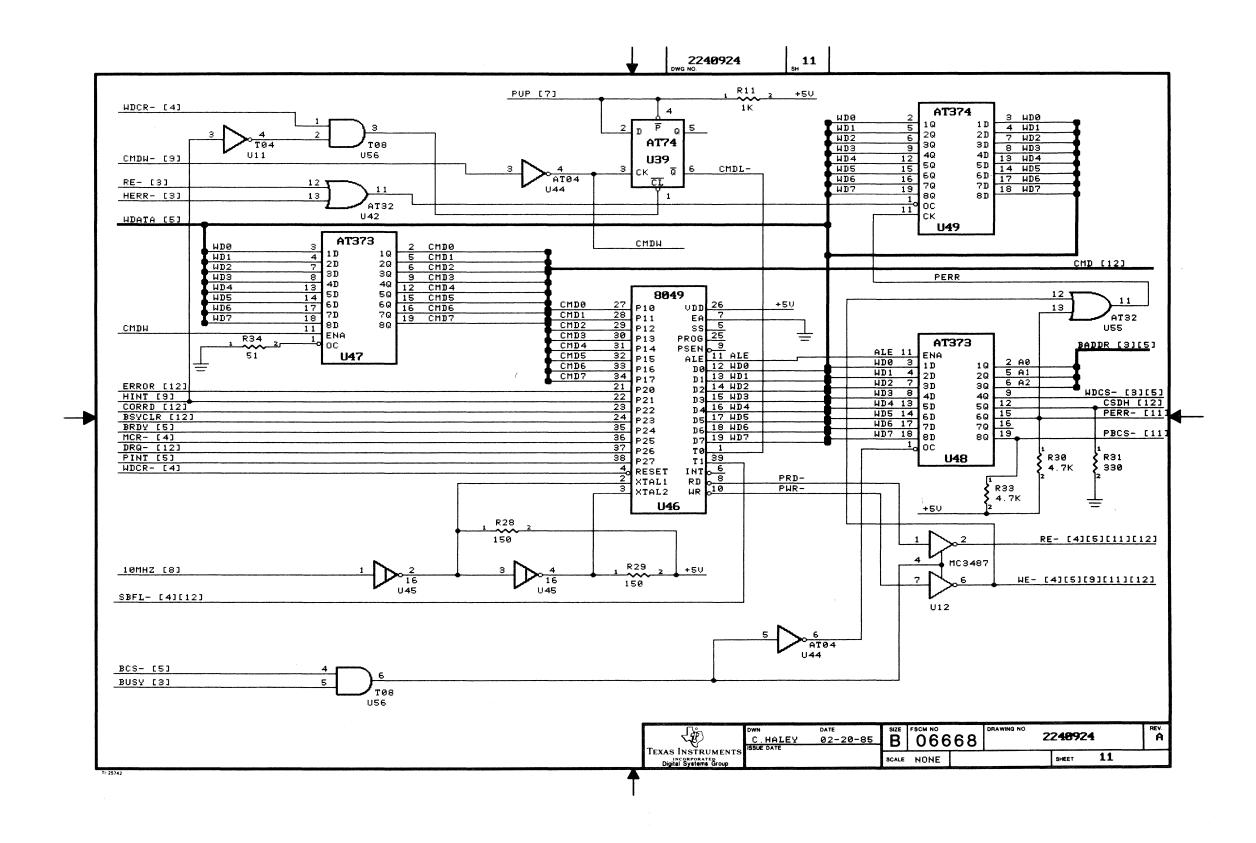

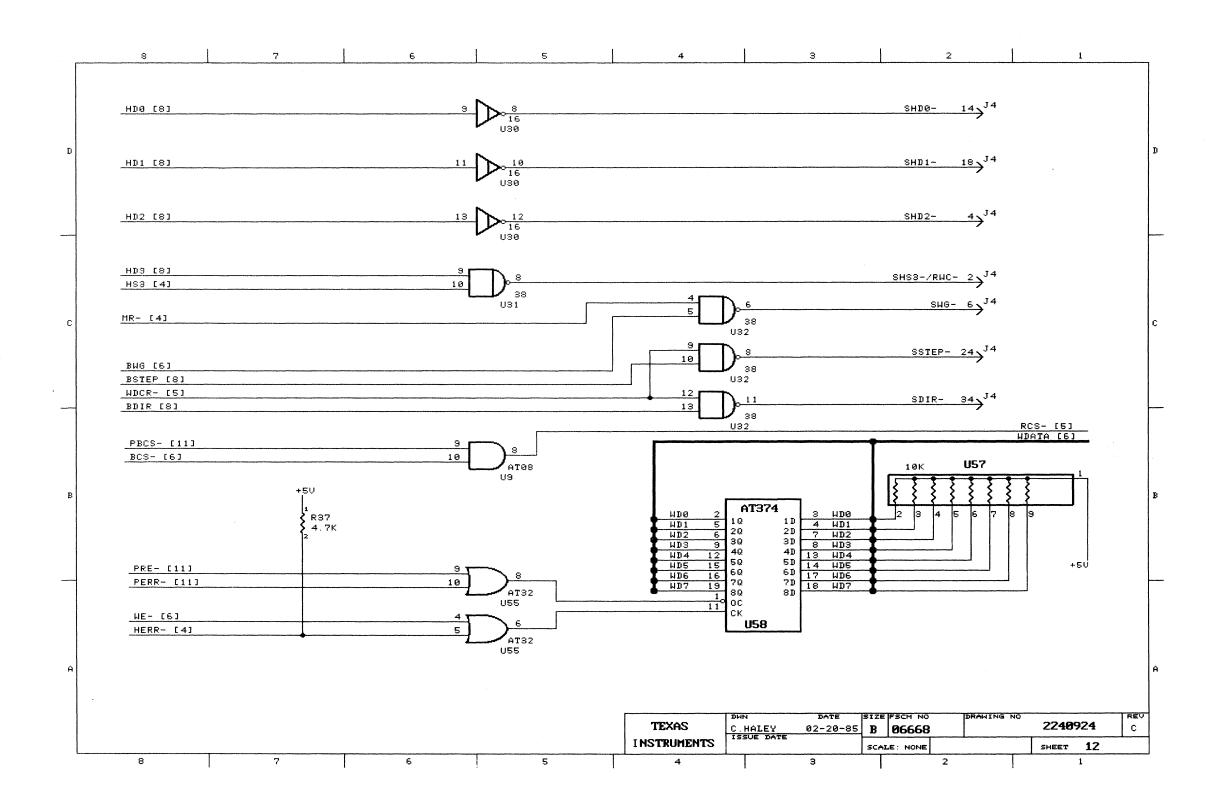

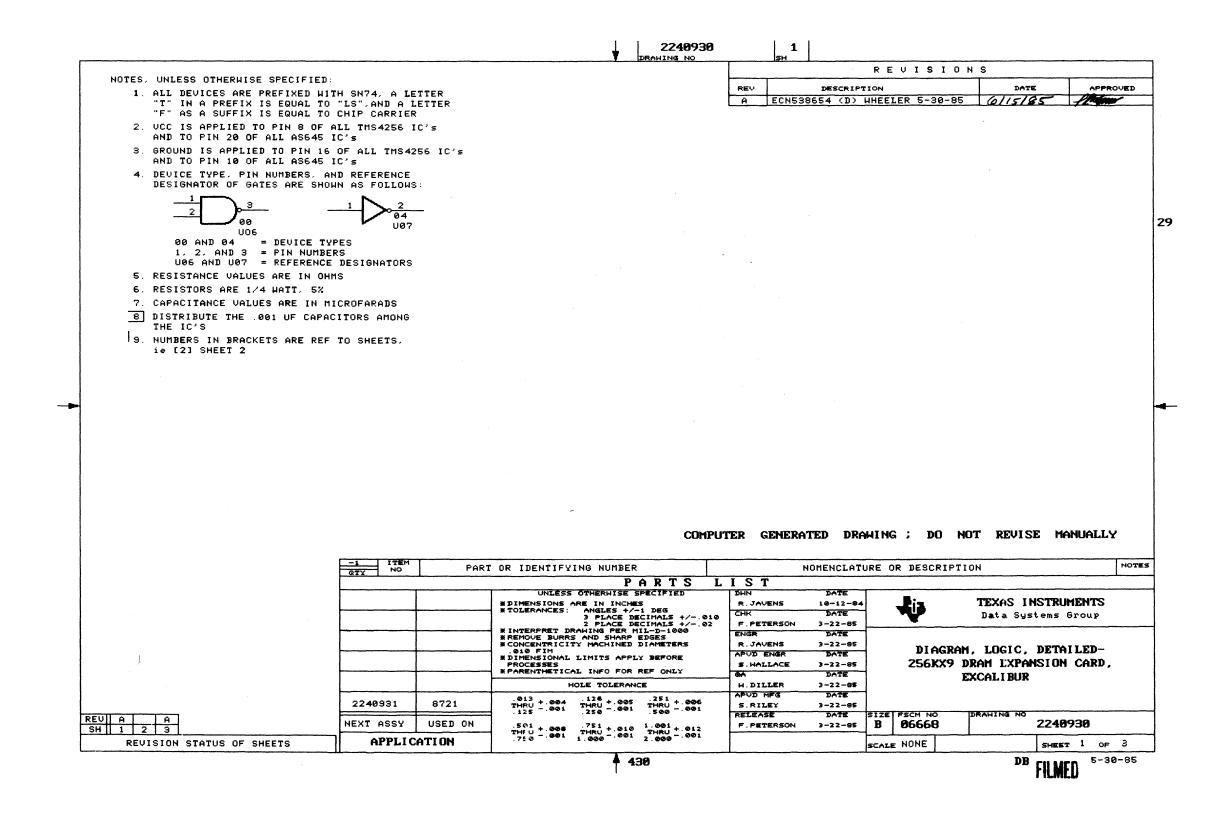

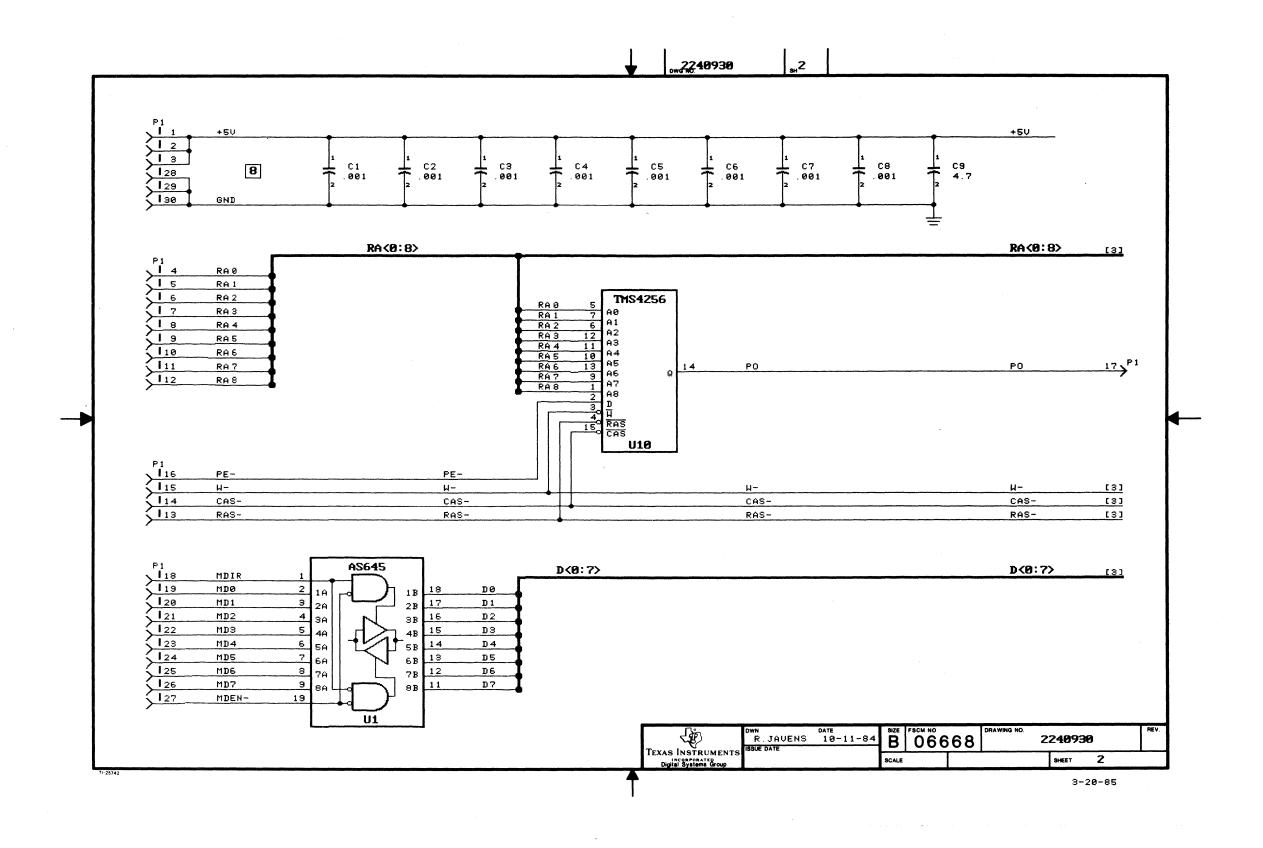

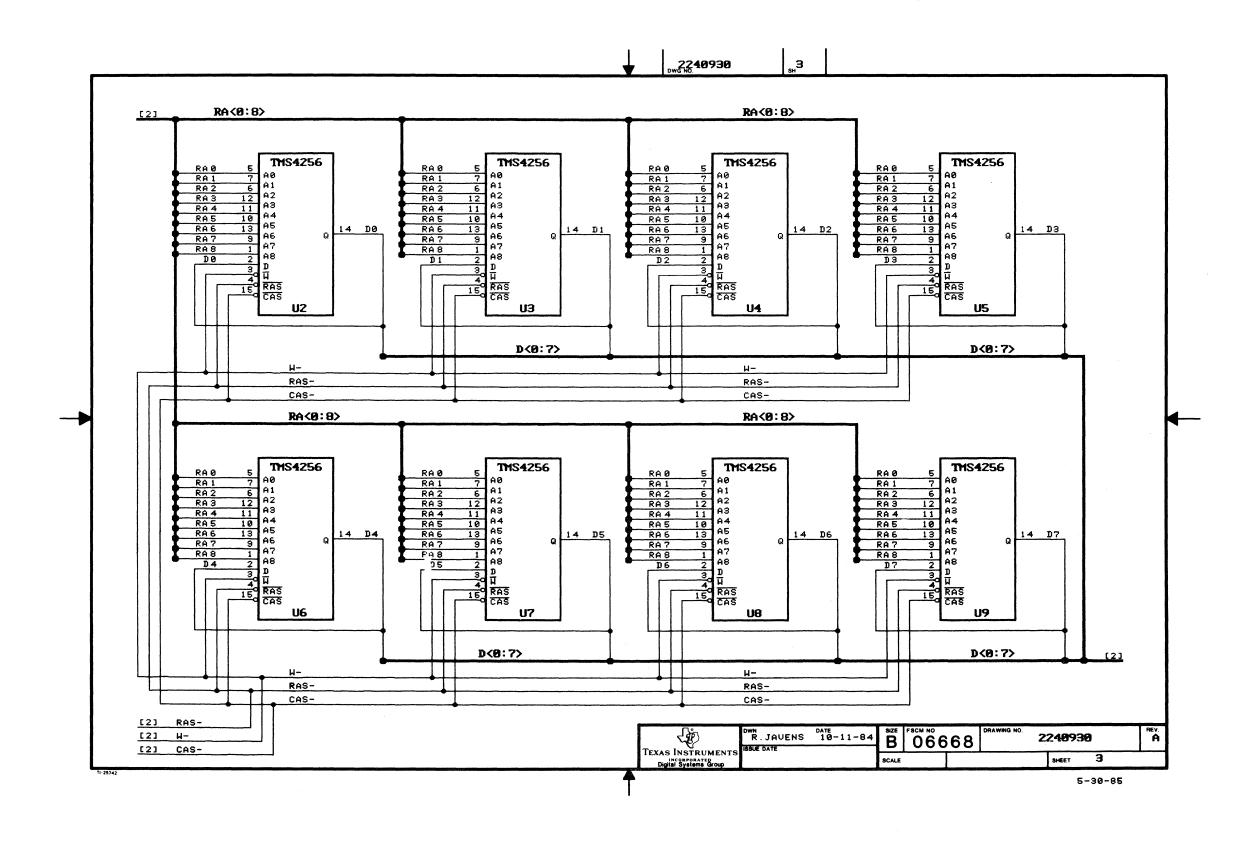

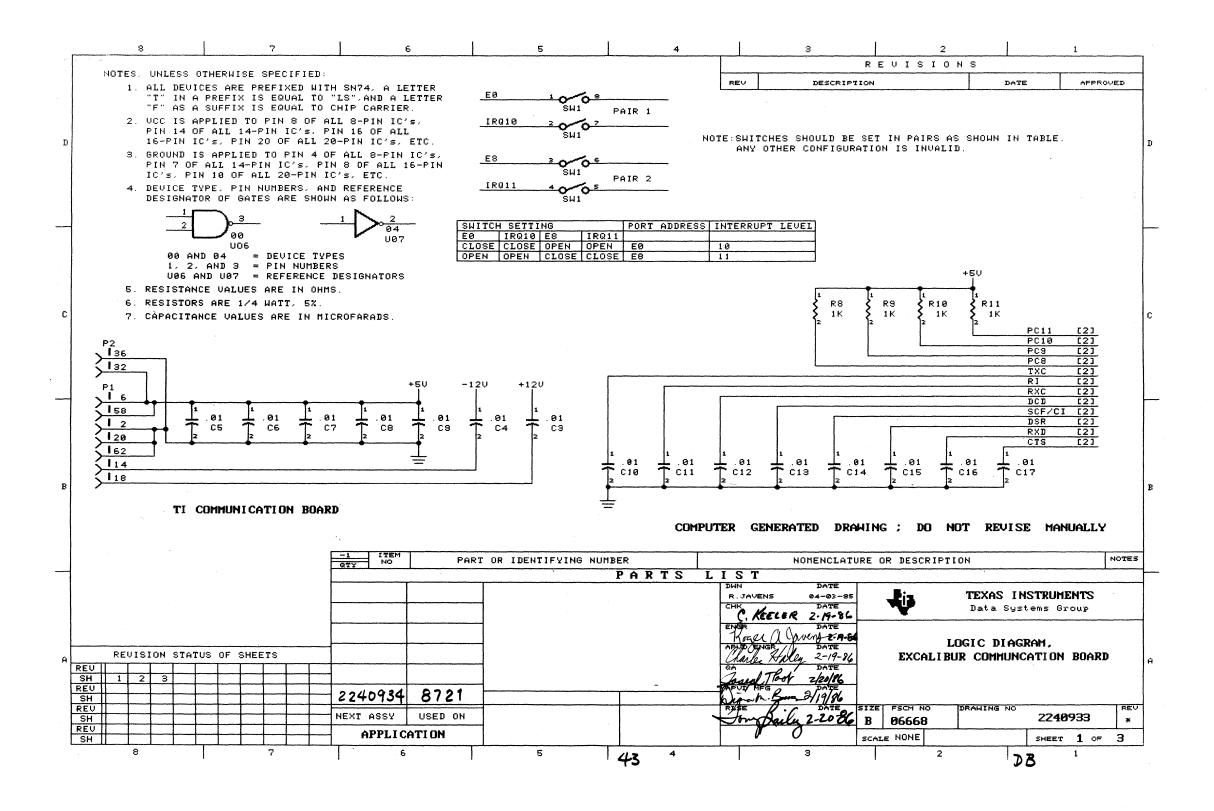

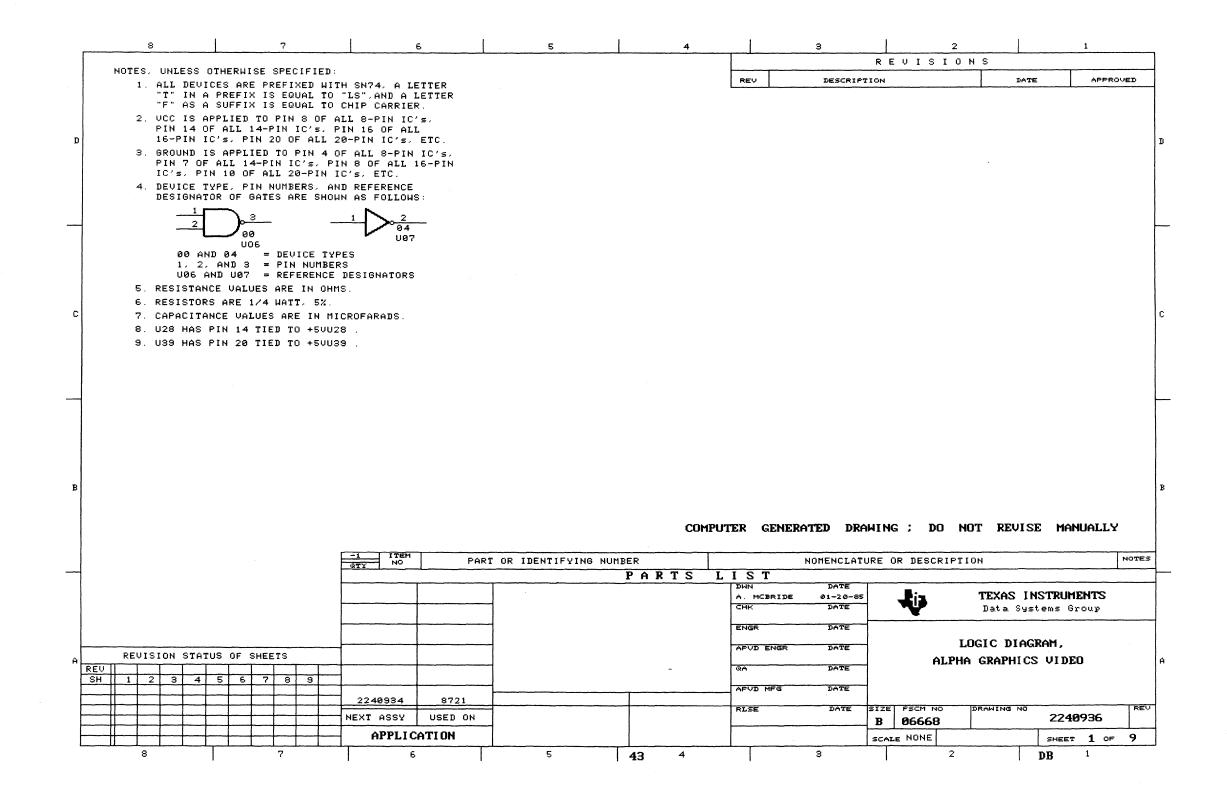

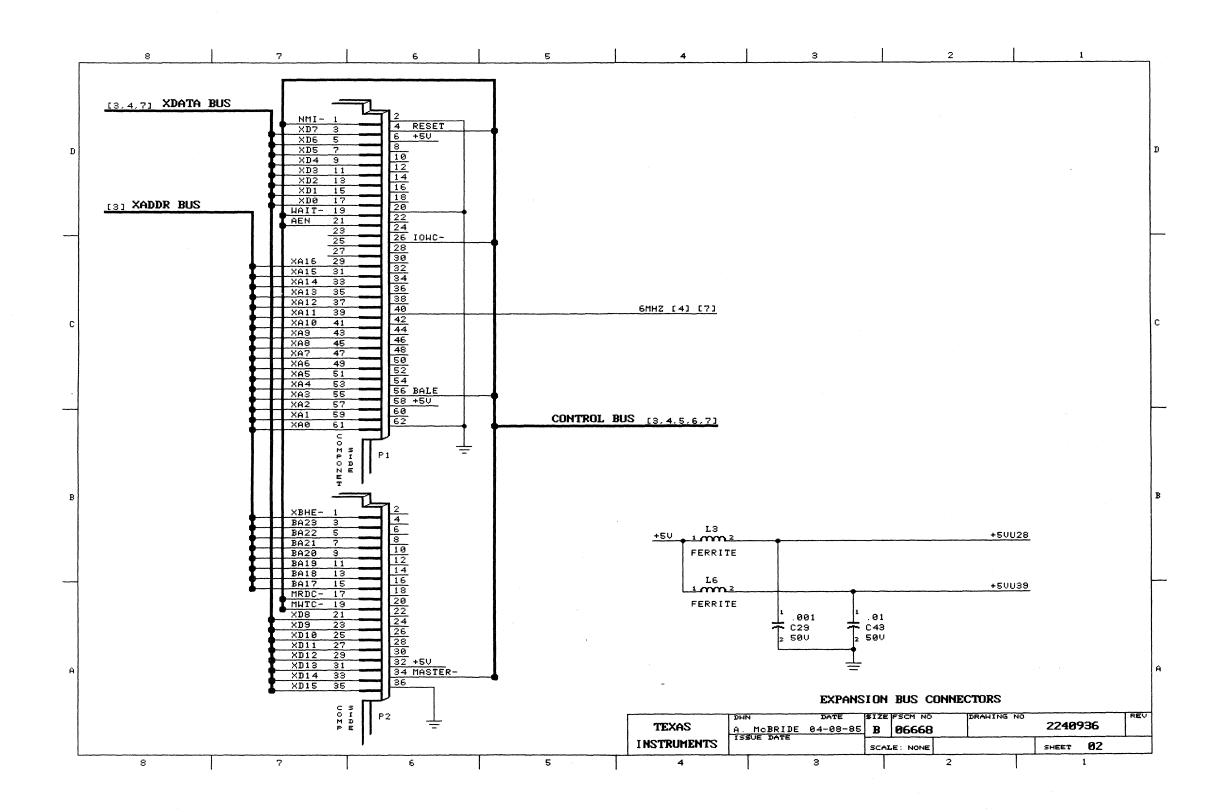

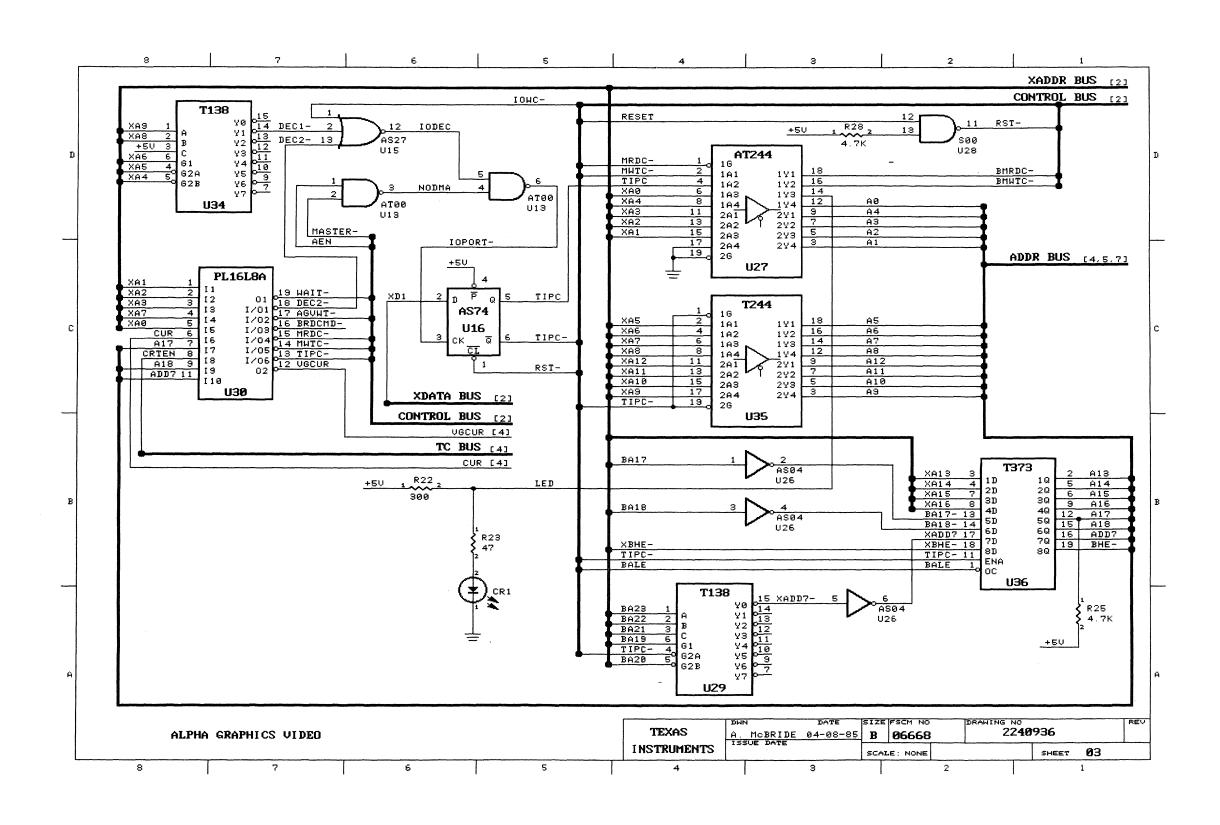

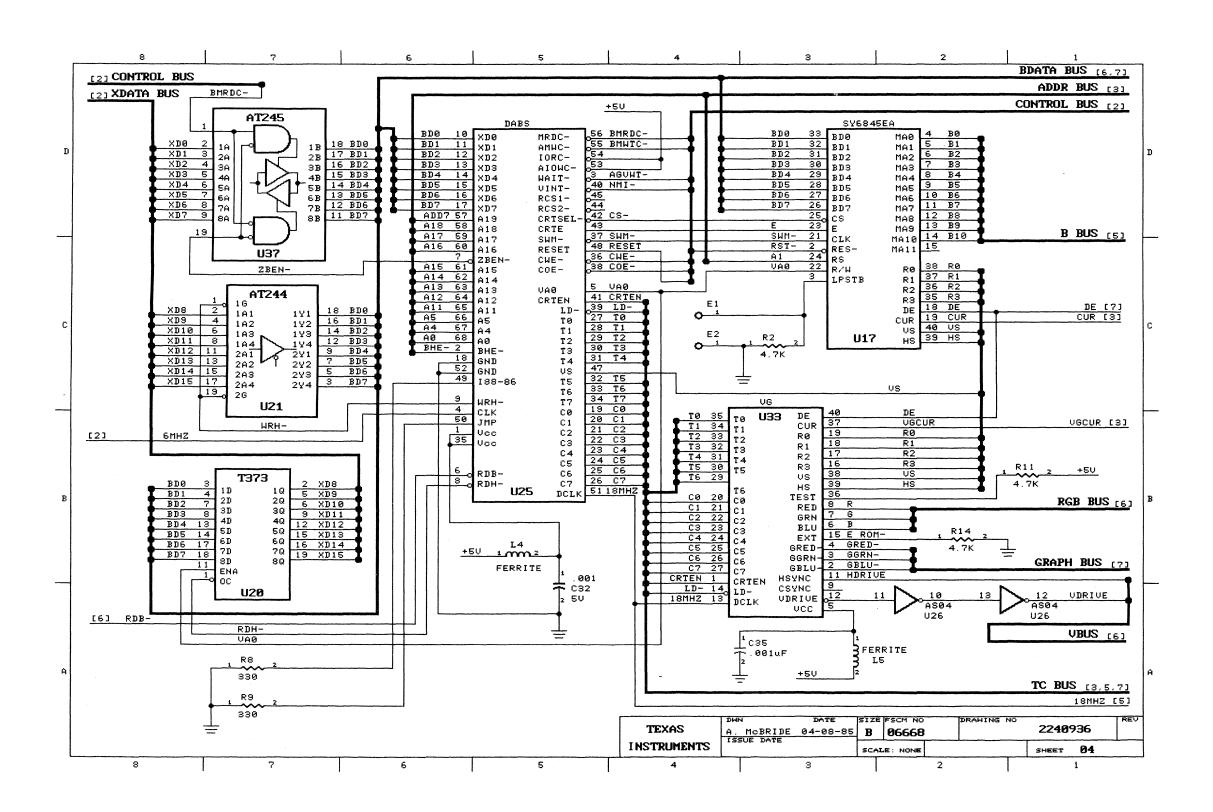

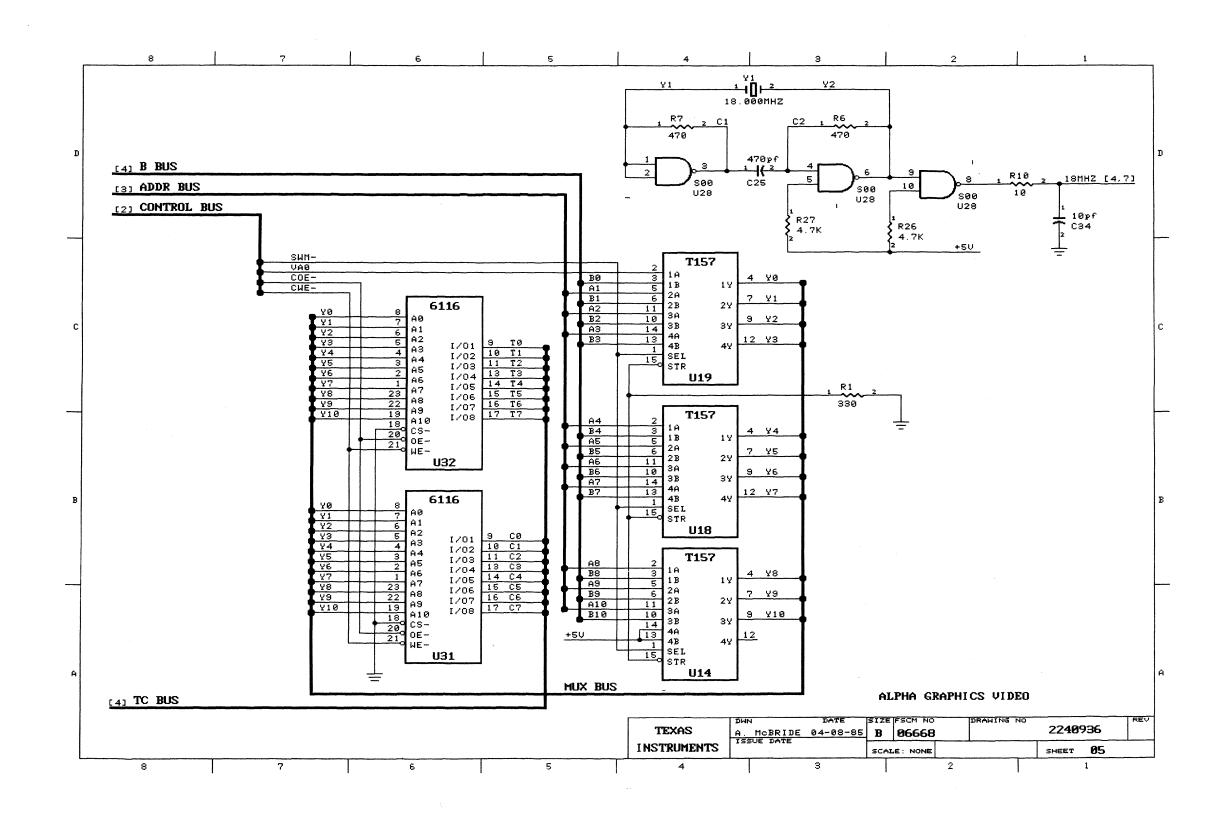

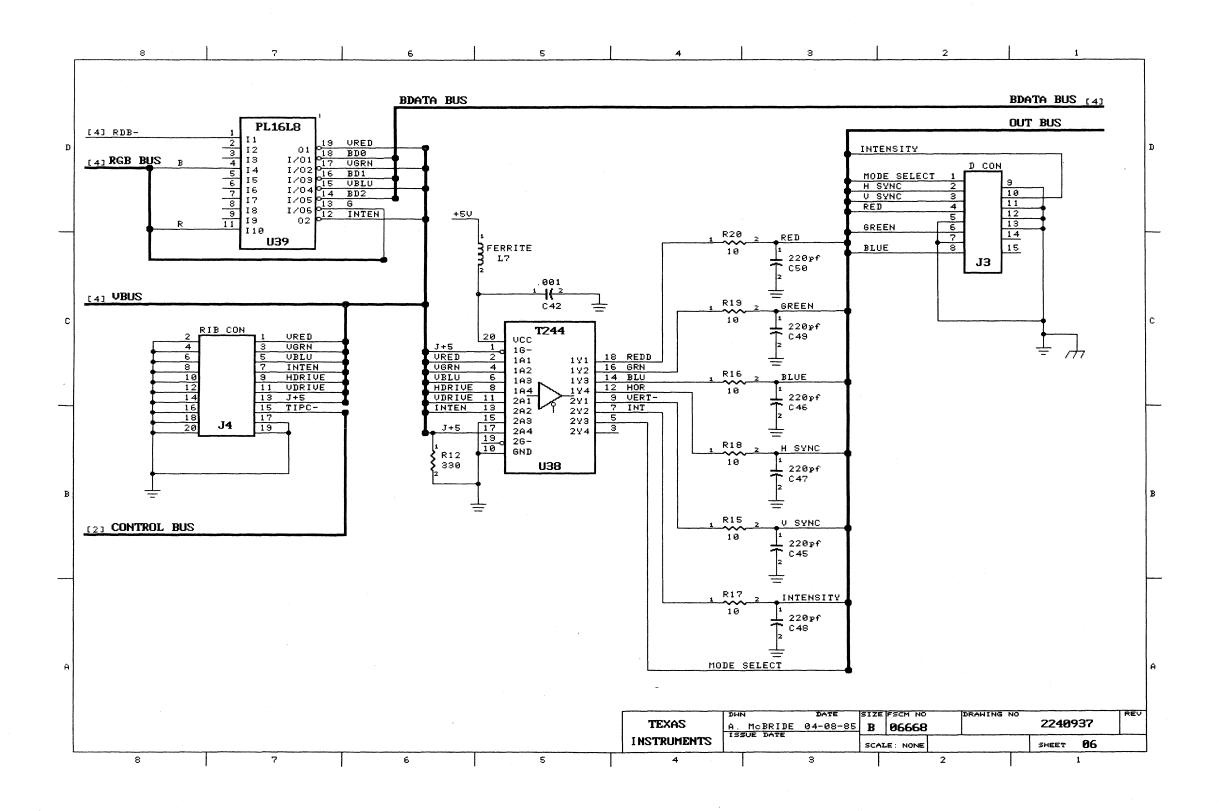

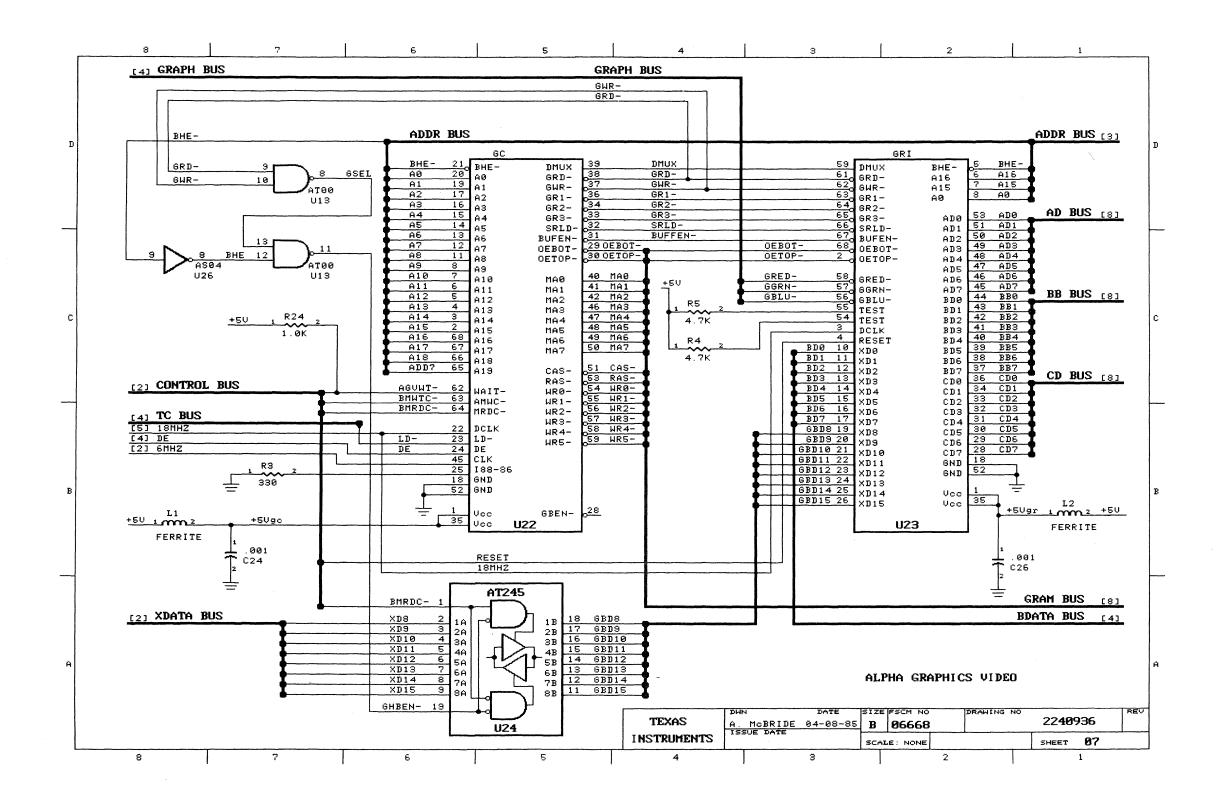

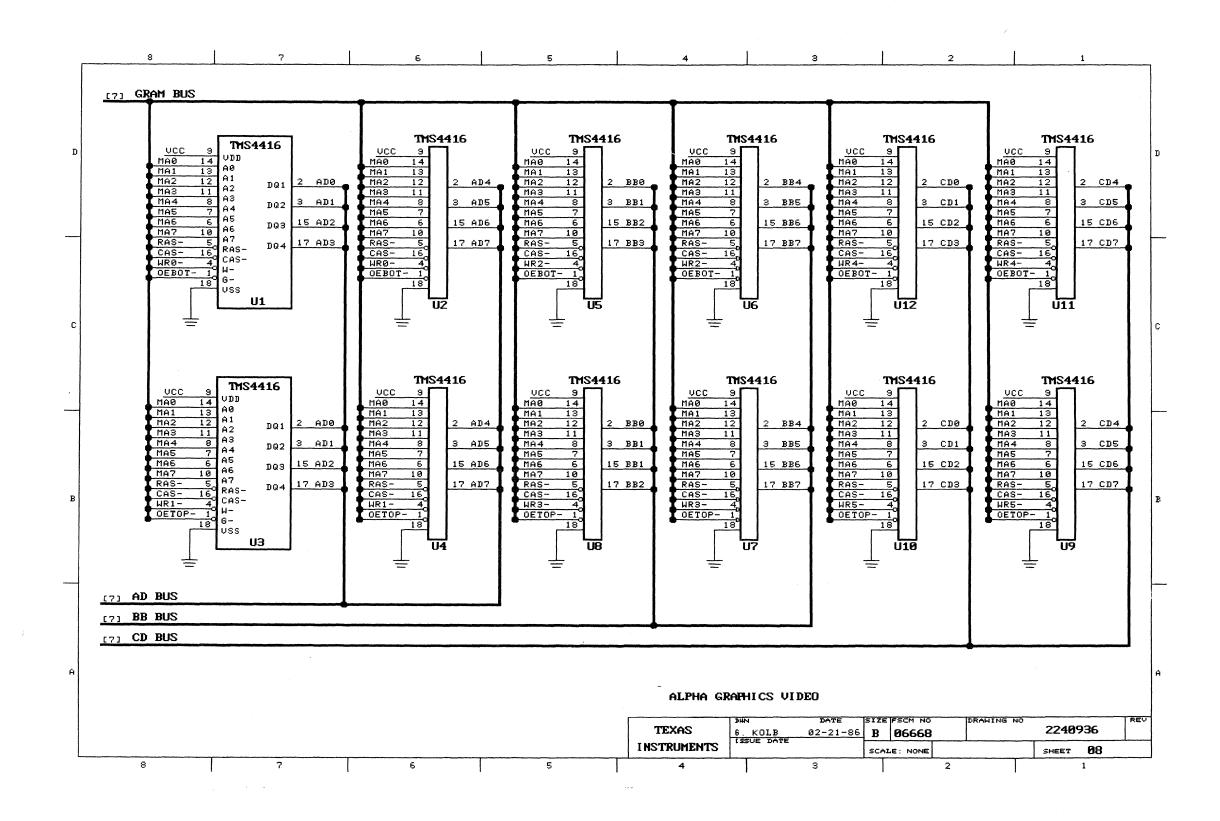

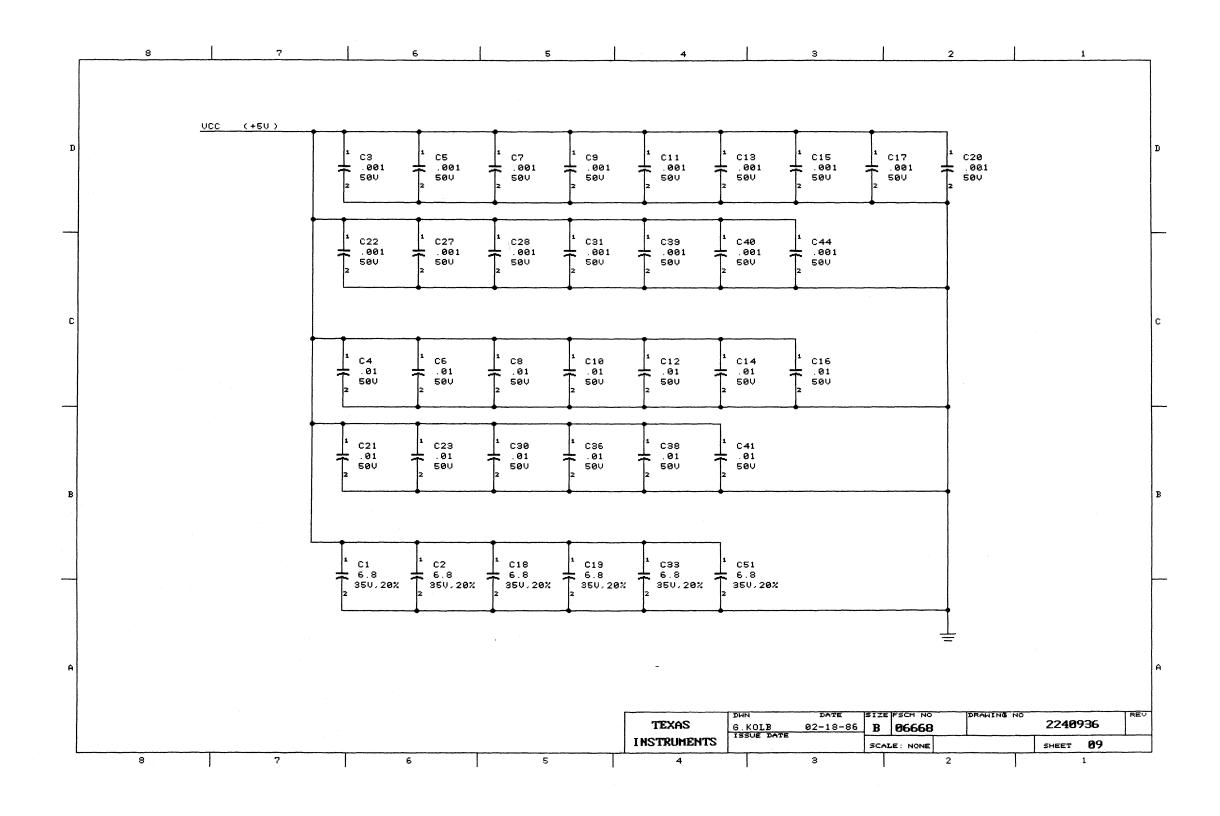

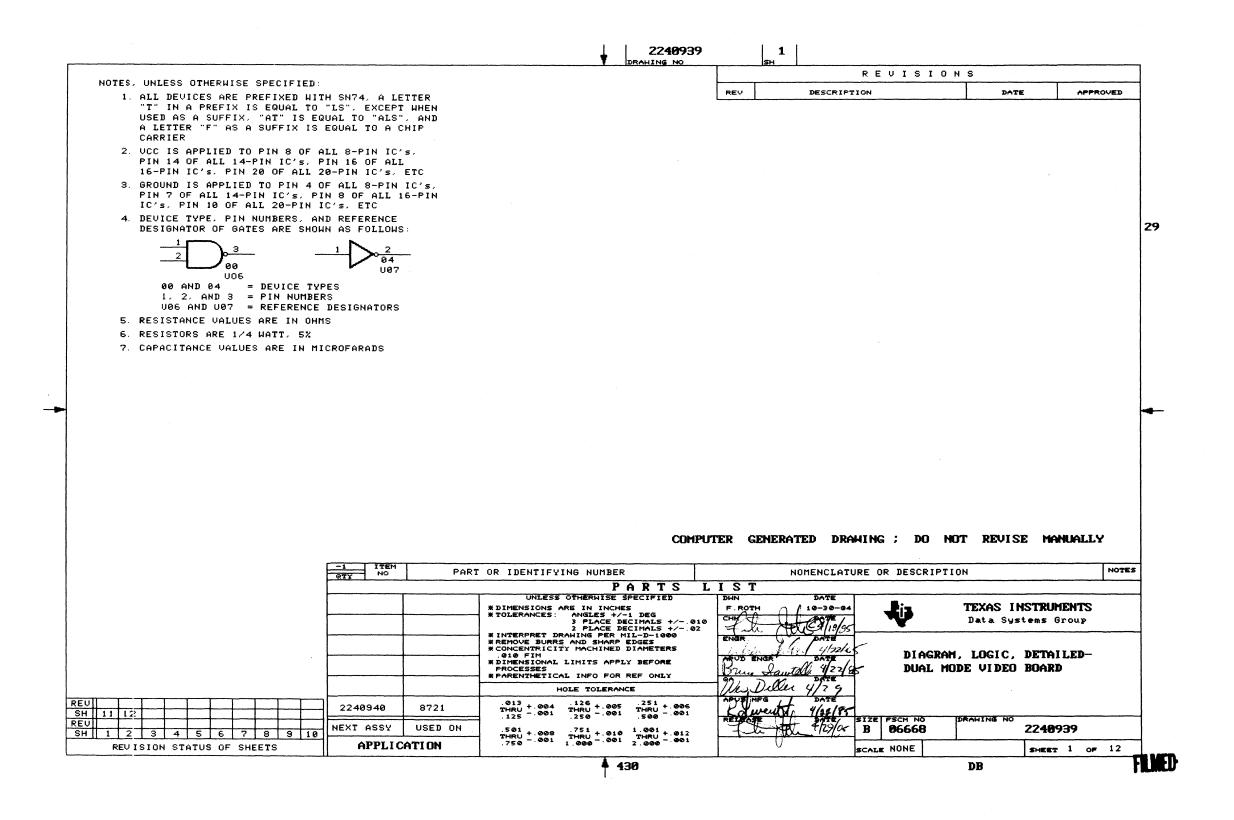

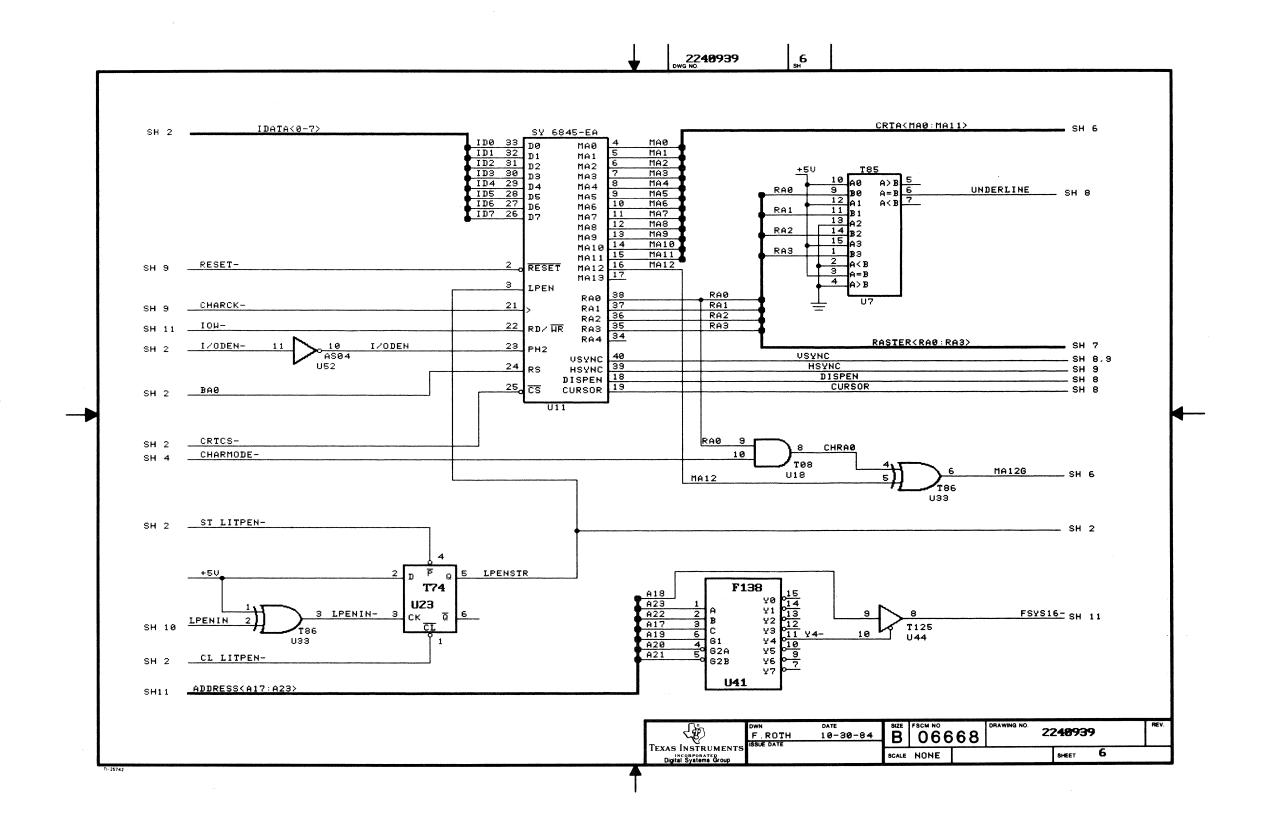

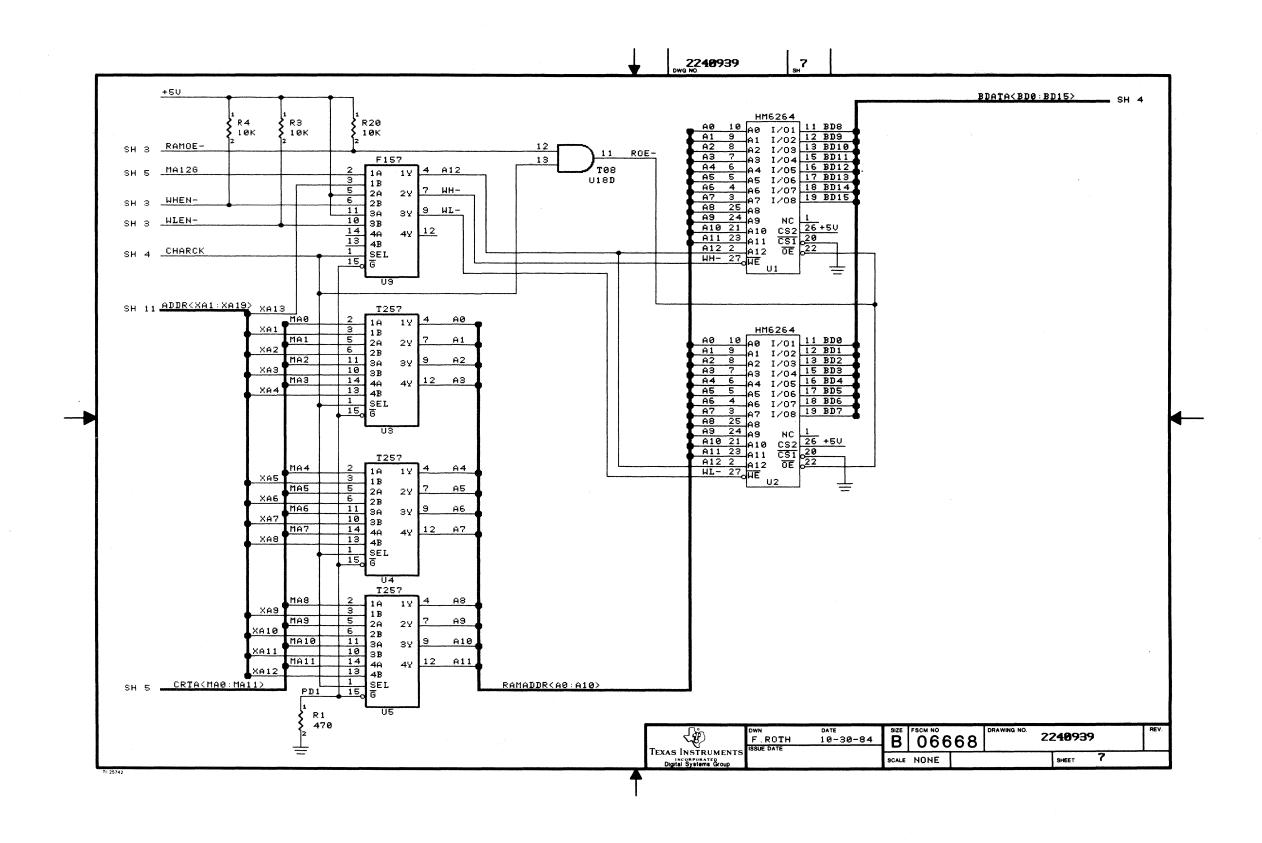

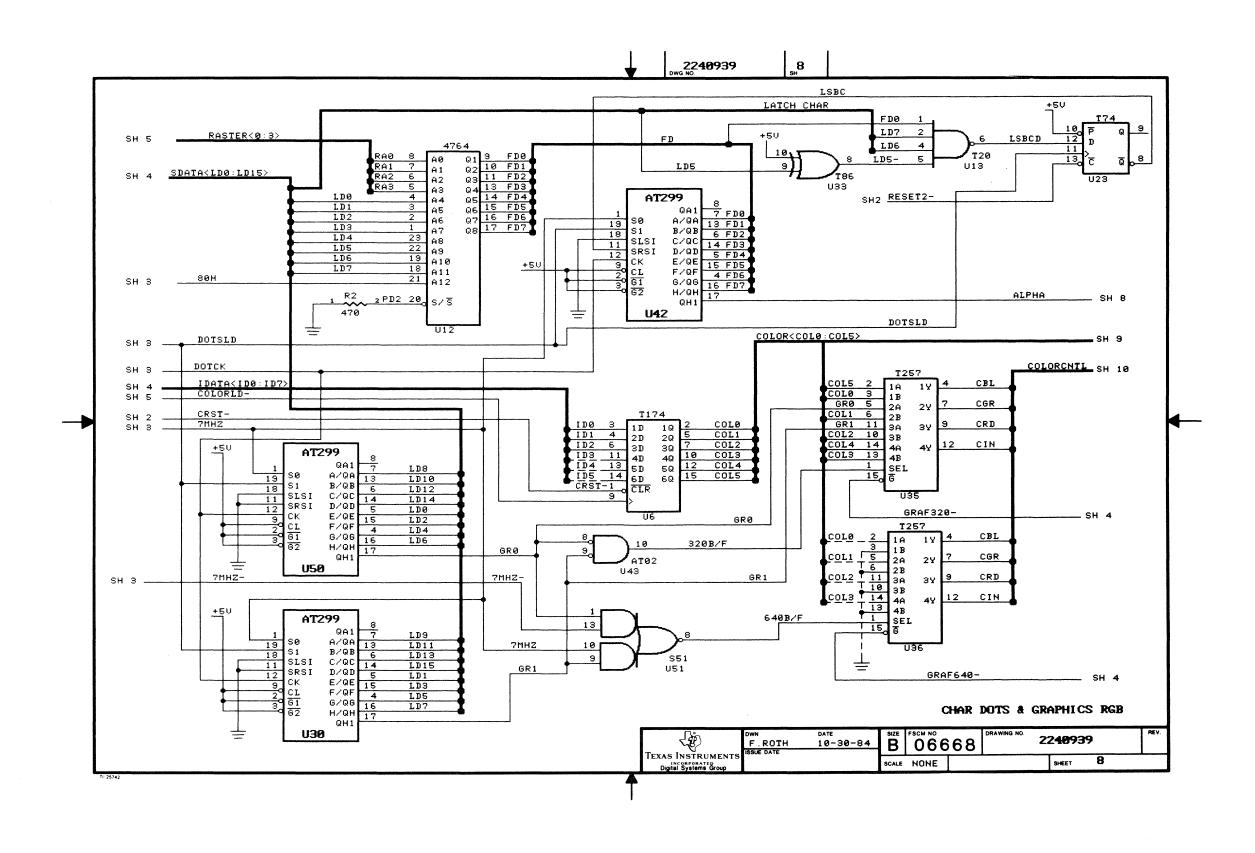

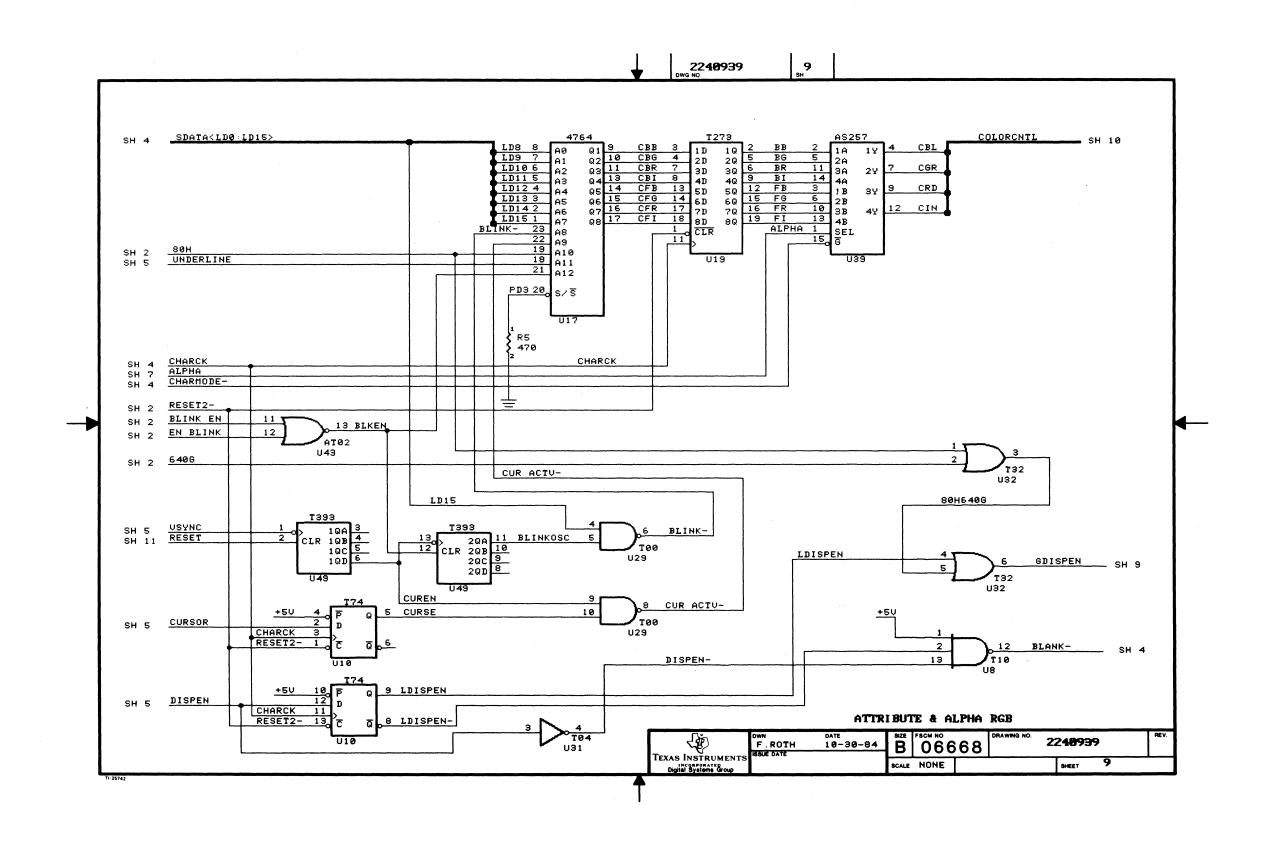

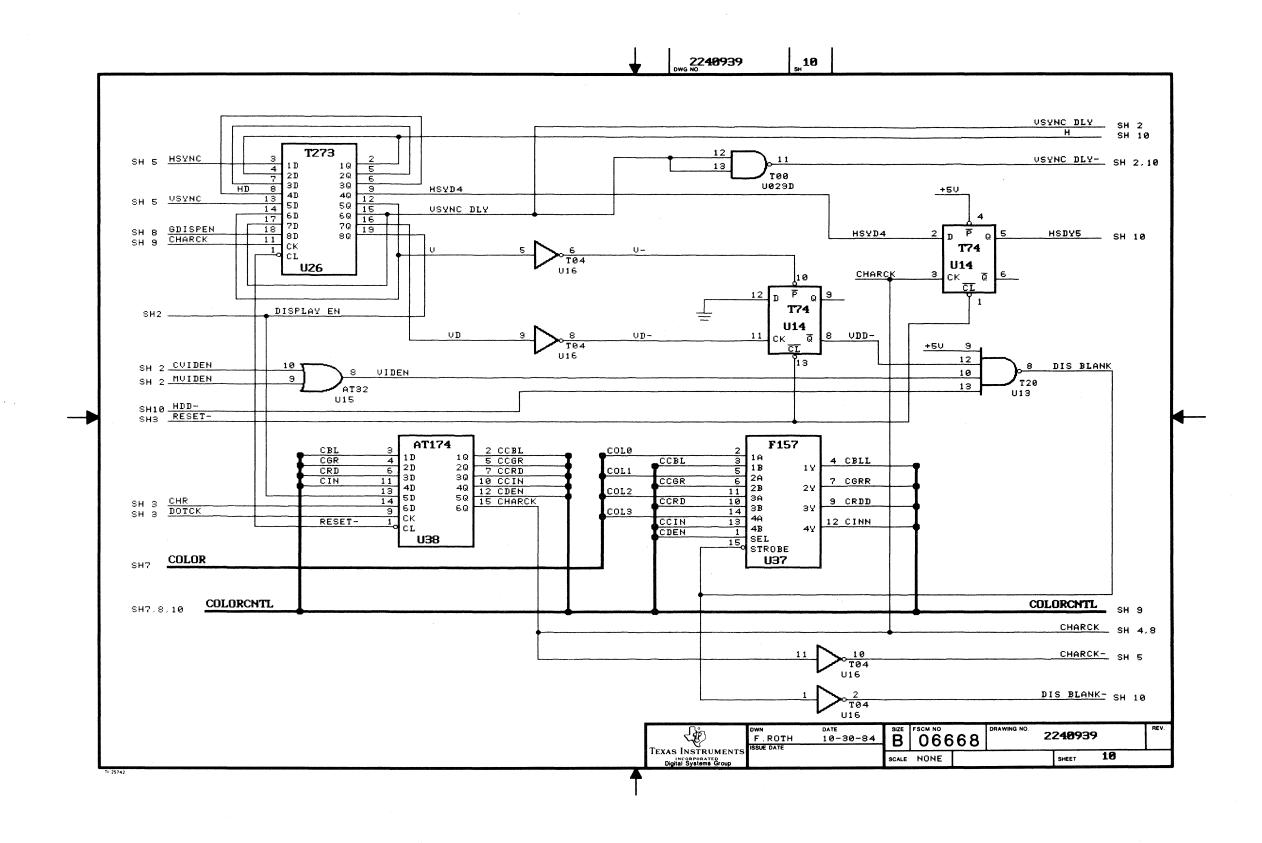

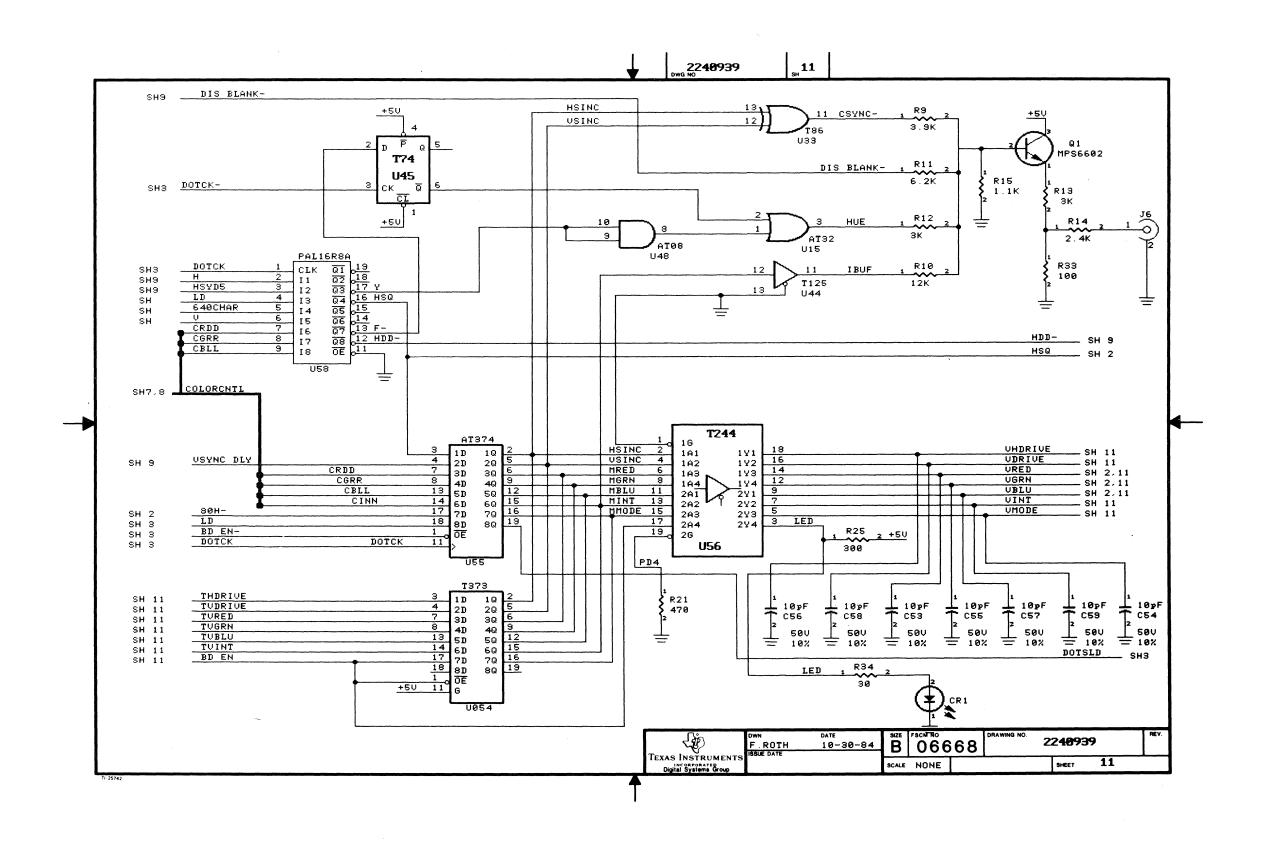

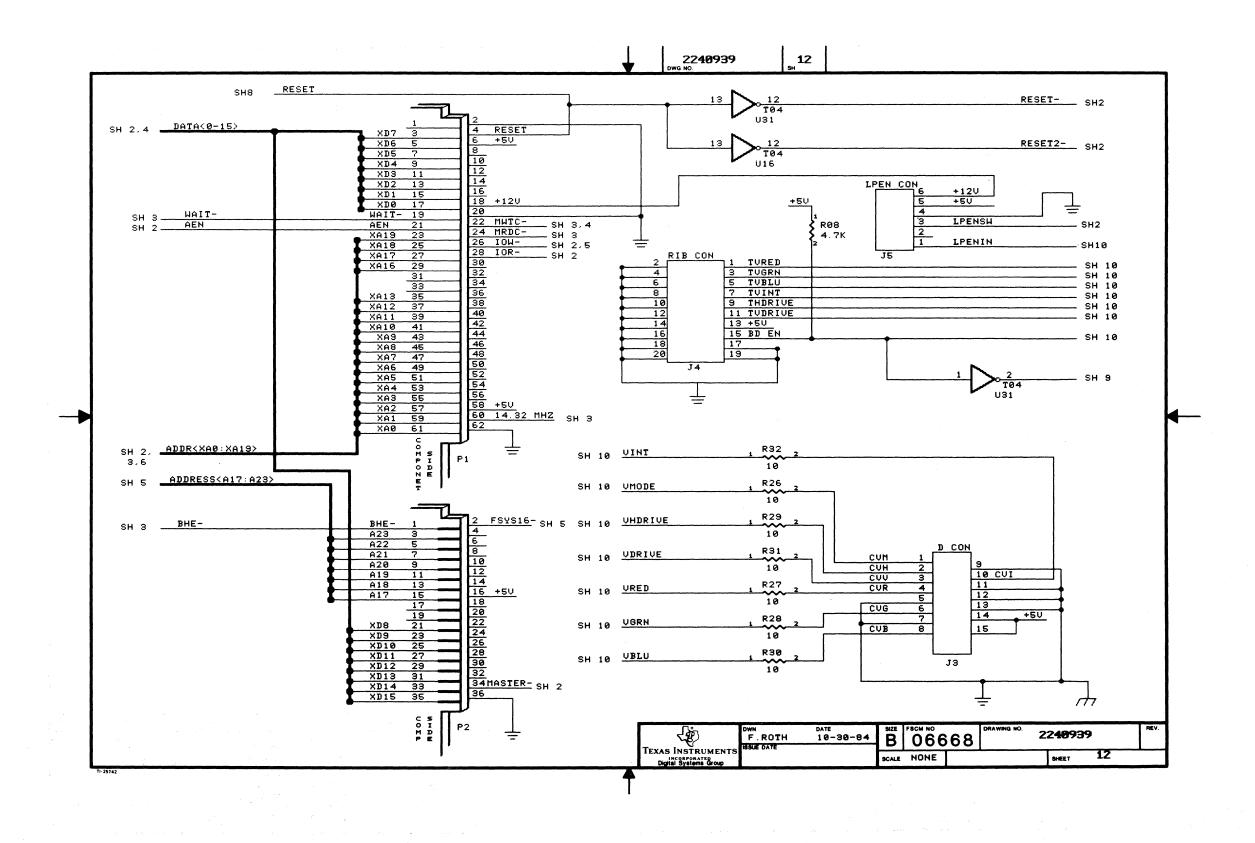

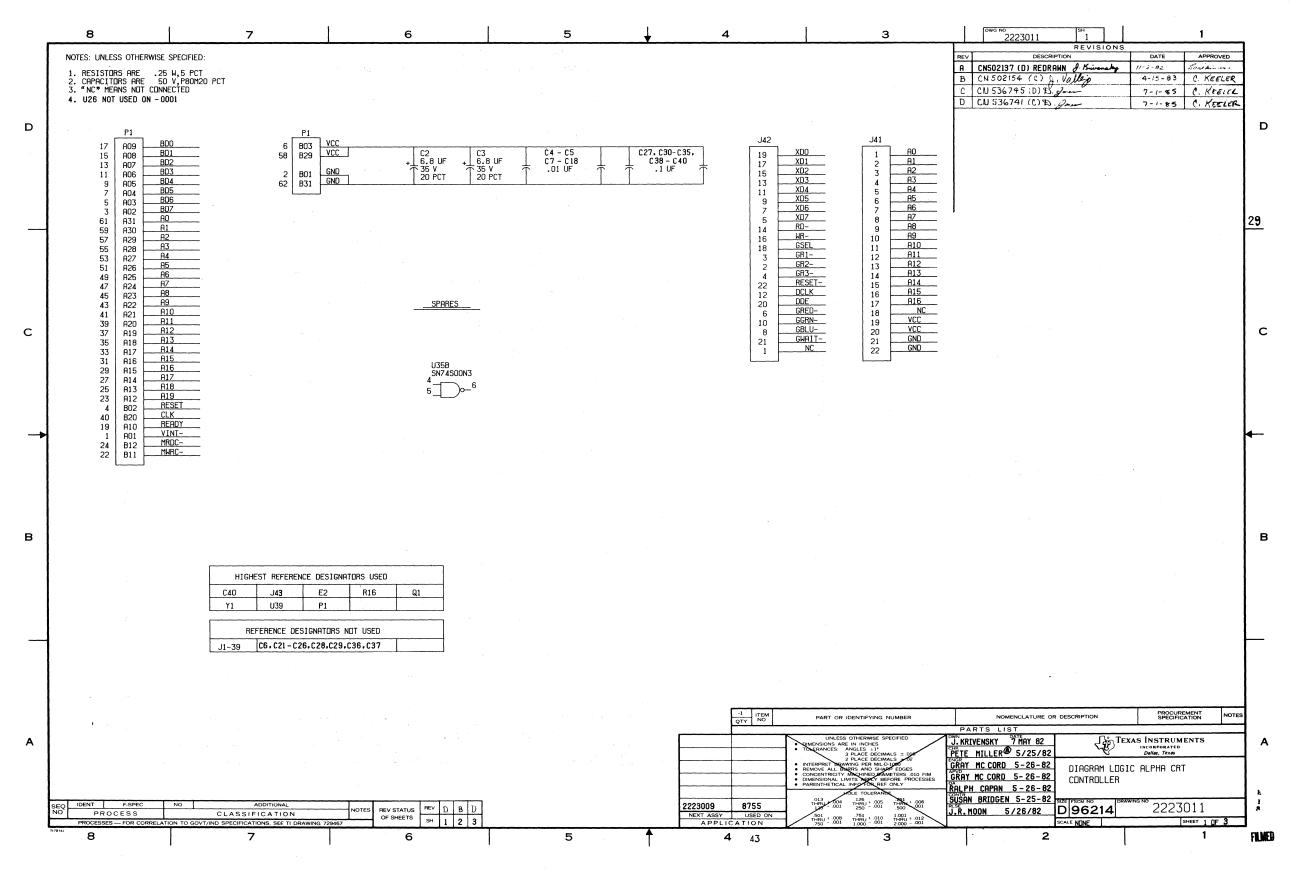

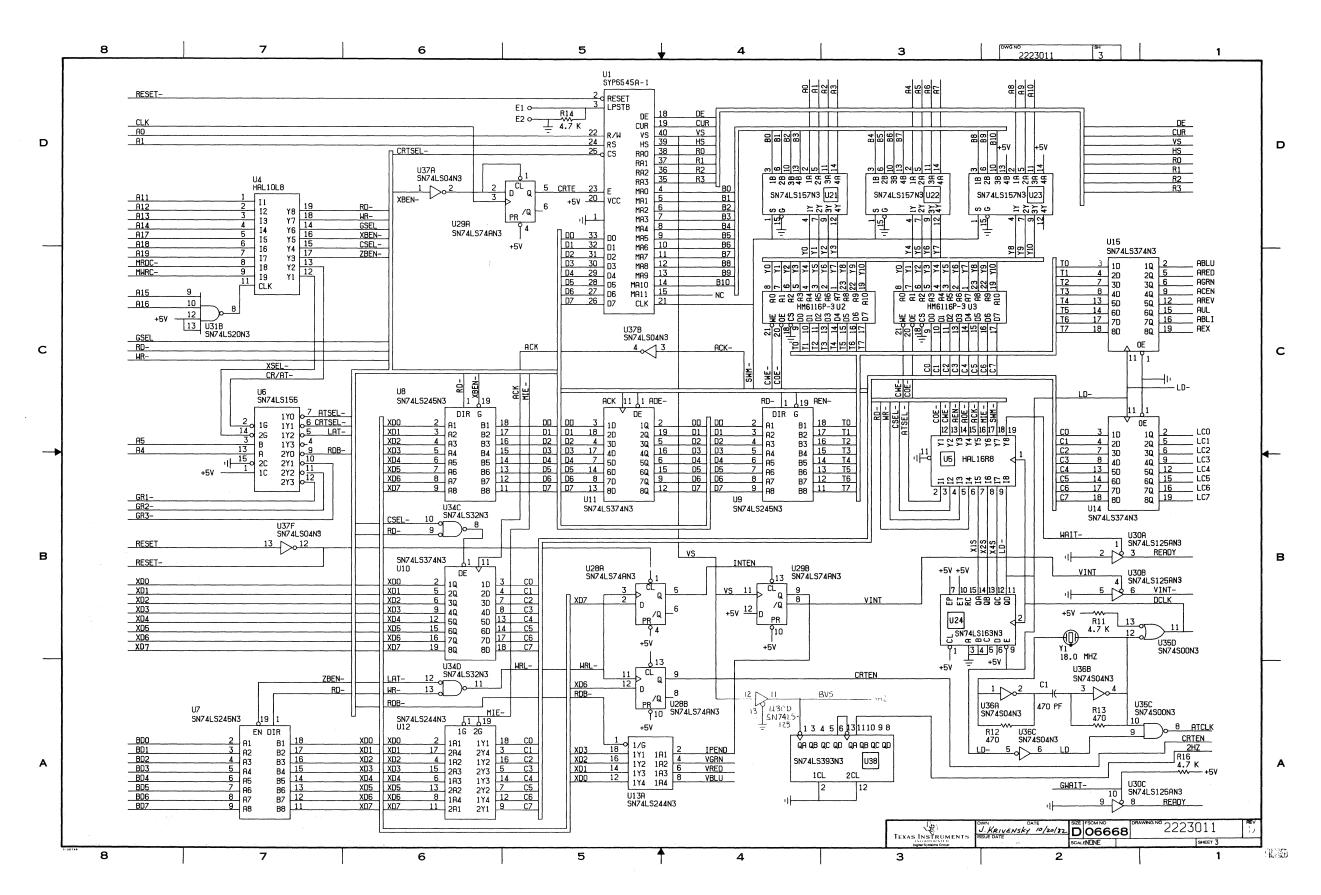

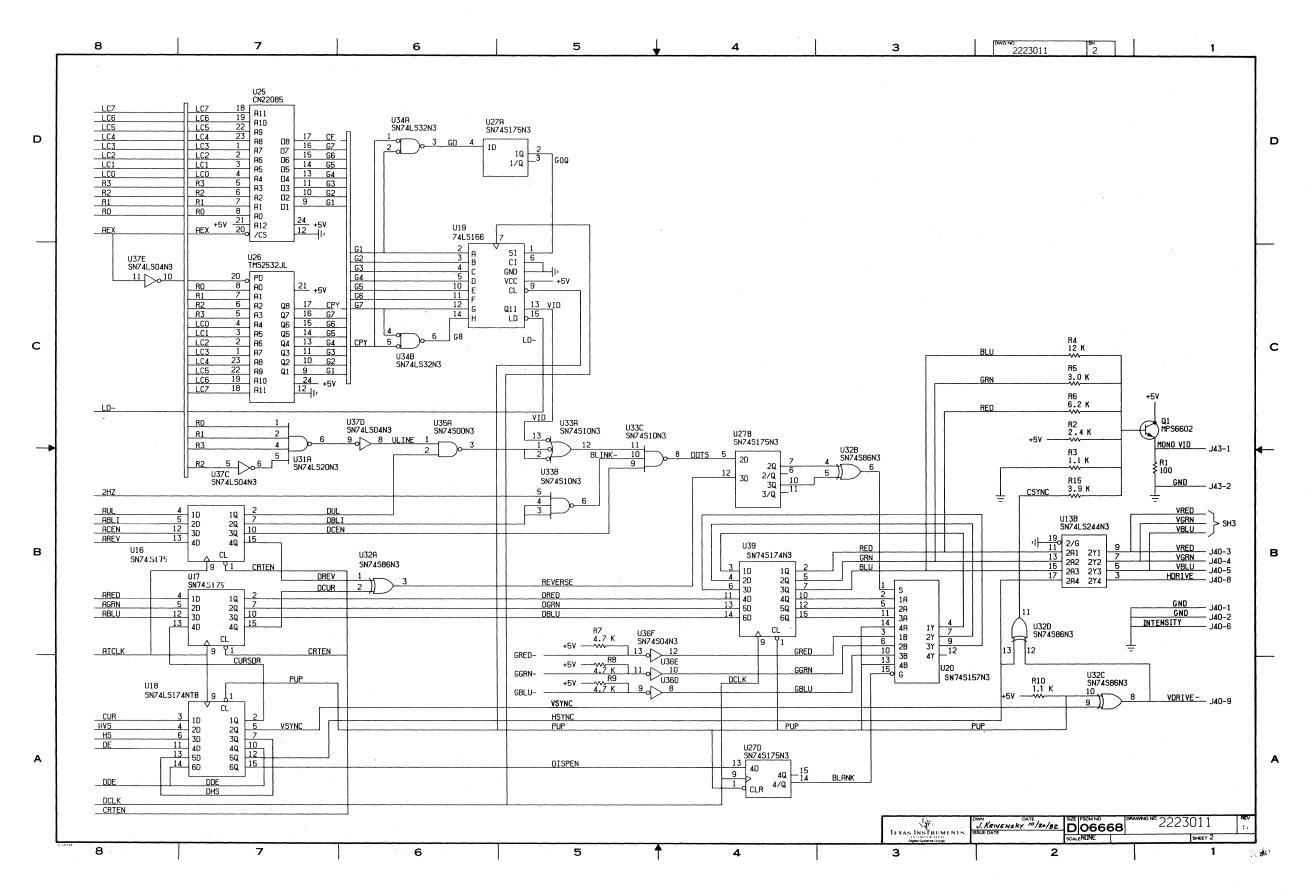

Α Memory and I/O Maps -- Provides a list of the system memory addresses and their allocations, and a general list of the system I/O address allocations. TI Mode I/O Maps -- Provides categorized lists of В the TI mode I/O address allocations. PC-AT Mode I/O Maps -- Provides categorized lists C of the PC-AT mode I/O address allocations. D PAL(R) Programming Information -- Provides tables of the main logic board programmable array logic (PAL) functions, based on the PAL programming equations.  $\mathbf{E}$ Logic Diagrams -- Provides system logic diagrams. F Option Board Outline -- Gives outline dimensions for full- and half-size boards.

Switch and Jumper Settings -- Gives a summary of

the switch and jumper option settings.

PAL is a registered trademark of Monolithic Memories, Incorporated.

#### Section 1

#### Introduction

#### 1.1 GENERAL

The Texas Instruments (TI) BUSINESS-PRO(TM) Computer, a member of the TI Professional Computer line, can be configured for a variety of computer applications. The BUSINESS-PRO offers most of the features of the Texas Instruments Professional Computer (TIPC) plus greater memory and mass storage capacity, greater expandability, and greater speed.

The BUSINESS-PRO can be configured to be compatible with most of the software designed for the TIPC as well as that designed for the IBM(R) Personal Computer AT(TM) (PC-AT). The computer supports a wide variety of operating systems, including MS(R)-DOS and XENIX(R). While using MS-DOS, the user can switch back and forth between the TI mode and the PC-AT mode with the appropriate hardware.

The BUSINESS-PRO computer's unique turbo operating mode increases the speed of the computer by deleting memory wait states. This enhancement allows both 16-bit and 8-bit memory transfer operations with minimum delay.

The BUSINESS-PRO system consists of a high-resolution, bit-mapped display (either color or monochrome), a combined TIPC and PC-AT keyboard, and a system unit that includes a floor stand. The computer and its floor stand fit easily under a desk top. A variety of mass storage devices can be installed in the system unit. The system can be used as a high-performance, single-user workstation; a local area network (LAN) server; an artificial intelligence (AI) workstation; or as a clustered, multiuser system running in the XENIX software environment.

BUSINESS-PRO is a trademark of Texas Instruments Incorporated.

IBM is a registered trademark and Personal Computer AT is a trademark of International Business Machines Corporation.

MS and XENIX are registered trademarks of Microsoft Corporation.

#### 1.1.1 Workstation Applications

The single-user capability is ideal for users who require a faster computer for processing large quantities of data. Also, it is appropriate for running memory intensive, AI-based software that includes integrated window environments and large expert systems. The BUSINESS-PRO is also well-suited for users who require access to large databases with natural language interfaces or for engineering applications.

#### 1.1.2 Local Area Networks

The LAN server capability of the BUSINESS-PRO provides high-performance and security capabilities to work groups who require resource sharing and teamwork among different workstations. A LAN allows users to share databases and peripheral devices, and to distribute their processing needs.

#### 1.1.3 Multiuser Environments

The multiuser cabability of the BUSINESS-PRO allows multiple users to share a single processor. A typical multiuser configuration consists of the BUSINESS-PRO system unit with TI Model 931 or TI Model 924 Video Terminals connected to it. The system unit can provide the mass storage and a printer.

#### 1.2 BUSINESS-PRO Hardware

The BUSINESS-PRO computer hardware is characterized by its high-performance capabilities and configuration flexibility. The following paragraphs provide an overview of the BUSINESS-PRO hardware.

#### 1.2.1 System Unit

The system unit houses the main logic board, the system power supply, the mass storage devices, and various controllers and interface boards. The main logic board contains the central processing unit (CPU), direct memory access (DMA) logic, input/output (I/O) logic, and various supporting circuits.

1.2.1.1 Central Processing Unit. The CPU is based on the Intel(R) 80286, 16-bit microprocessor. An optional 80287 numeric coprocessor can be added to the CPU to provide enhanced operations for those applications involving a large number of floating point mathematic operations.

Intel is a registered trademark of Intel Corporation.

- 1.2.1.2 System Memory. The main logic board contains 512K bytes of 150-nanosecond RAM that can be expanded to 3.64 megabytes without using any of the systems 14 expansion slots. The expansion slots can be used to expand the main memory up to a total of 14.64 megabytes.

- 1.2.1.3 Serial and Parallel Ports. The main logic board provides a parallel port and a serial port. The parallel port can support a printer or other options requiring parallel data. The serial port is a programmable, PC-AT compatible port that provides asynchronous communication between the system and various options that require serial data transfers.

- 1.2.1.4 Mass Storage System. The system unit provides mounting rails that can accommodate up to six half-height mass storage devices. For maximum flexibility, the user can choose a combination of half-height and full-height peripherals (with appropriate controller required). The following mass storage devices are available from Texas Instruments:

- \* Half-height, 21-megabyte Winchester disk drive

- \* Full-height, 40-megabyte Winchester disk drive

- \* Full-height, 72-megabyte Winchester disk drive

- \* Full-height, 120-megabyte Winchester disk drive

- \* Half-height, 1.2-megabyte floppy disk drive

- \* Half-height, 360-kilobyte floppy disk drive

- \* Half-height, tape backup drive

- 1.2.1.5 Expansion Slots. The BUSINESS-PRO system unit contains 8 full-size, and 6 half-size expansion slots. Three of these slots are 8-bit slots that allow the installation of PC-XT compatible options. As an example of the degree of flexibility the slots can provide, a system with a 3.64-megabyte main memory, a floppy controller, a Winchester disk controller with one or more Winchester disk drives, a video controller, and a tape backup system still has 10 slots available for other options.

- 1.2.2 Keyboard

The BUSINESS-PRO keyboard provides both TI and PC-AT operations with a standard typewriter layout, plus some special keys and keypads. These include dedicated function keys, cursor control keys, and a numeric keypad. The keyboard also features tactile typing response and a variable tilt adjustment. The standard configuration provides 100 keys, many of which can be relocated using special software. Also, spaces are provided for additional keys, which can increase the total key count to 144.

#### 1.2.3 Display Units

The BUSINESS-PRO provides optional dual-resolution display units in either a color version or a monochrome version. Both versions support software designed for the TIPC as well as software designed for the IBM color/graphics monitor adapter. The display units feature tilt/swivel bases that provide two identical connectors to accommodate a keyboard and/or an optical mouse. The use of identical connectors permits the keyboard and the mouse to connect to either side of the monitor base. The units also provide an internal speaker with volume control.

#### 1.2.4 Optical Mouse

The optical mouse and its associated pad provide fast and easy cursor control on the display screen. The mouse features three buttons whose functions depend upon the software. The mouse is especially useful for graphics applications.

#### 1.2.5 Communications

The communications hardware options include the TI mode RS-232 serial interface and the EtherLink(TM) hardware kit.

The RS-232 provides a serial port for communicating with external devices such as modems, serial printers, and other computers. Although the RS-232 is provided for TI mode applications, specially designed hardware allows its use in the PC-AT mode to provide a third or fourth communications port.

The EtherLink hardware kit provides a means of connecting the BUSINESS-PRO to a local area network.

#### 1.2.6 Graphics

The TI mode CRT controller provides high-resolution, bit-mapped, three-plane graphics in eight colors with the color display unit or in eight levels of intensity with the monochrome display. The PC-AT mode CRT controller provides IBM CGA-compatible graphics and IBM monochrome/printer adapter compatible text (excluding the printer functions). Both controllers are specially-designed for use with an 80286-based computer system. They can be installed simultaneously to allow dual-mode operation.

EtherLink is a trademark of 3Com Corporation.

#### 1.3 BUSINESS-PRO COMPUTER STANDARD CONFIGURATIONS

The BUSINESS-PRO computer system is available in two standard hardware configurations: the single-drive floppy system and the Winchester system. To allow the user maximum flexibility when configuring the system, neither of these basic configurations contains the video controllers or the display units.

- 1.3.1 Single-Drive Floppy System

The single-drive floppy system includes the following components:

- \* System unit with a main logic board

- \* Bus interface board that provides 14 expansion slots

- \* Keyboard

- \* 1.2-megabyte floppy disk drive and controller

- \* Keylock

- 1.3.2 Winchester System

The Winchester system includes the following components:

- \* System unit with a main logic board

- \* Bus interface board that provides 14 expansion slots

- \* Keyboard

- \* 1.2-megabyte floppy disk drive and controller

- \* 21-megabyte, half-height Winchester disk drive and controller

- \* Keylock

- 1.3.3 System Unit Enclosure

The system unit enclosure is 19.8 centimeters (7.75 inches) wide 47.7 centimeters (18.8 inches) high, and 47.0 centimeters (18.5 inches) deep. The system enclosure houses the bus interface board, the main logic board, and a system power supply with an integral ventilation fan. An optional RAM expansion board can be attached to an edge connector on the main logic board to provide up to 3 megabytes of additional RAM without using an expansion slot. Appendix E contains the system interconnect diagram.

- 1.3.3.1 Main Logic Board. The main logic board contains the CPU, the memory-control logic, and I/O control devices. The board provides connectors for the 25-pin parallel printer port, the 25-pin asynchronous serial port, and an 8-conductor keyboard cable. It also provides a 100-pin interface connector to the bus interface board.

- 1.3.3.2 Bus Interface Board. The bus interface board provides the system bus connections between the main logic board and the option boards. The board provides eight full-size and six half-size option slots. Each option board contains a bulkhead mounting plate to secure the board in the chassis and to provide a mount for any required external-access connectors. The bus interface board mounts above the main logic board. A small interface board connects the two boards together.

- 1.3.3.3 System Power Supply. The system power supply is self-contained within a box, which mounts inside the system enclosure. The power supply contains a dc fan that obtains its operating voltage from the 12-volt secondary of the power transformer. The power supply provides 225 watts ouput power to operate a fully configured system.

The power switch is located on the front panel of the computer. A cable connects the switch to the rear of the power supply. The switch also controls power to a switched power-access connector to which a display unit can be connected. This arrangement allows the user to control power to both the system unit and the display unit with a single switch.

1.3.3.4 Mass Storage Device Mounting. The system enclosure accepts mounting slides for the mass storage devices. The slides allow the devices to be installed or removed from the front of the system unit. A typical configuration includes one or two 1.2-megabyte floppy disk drives and one or two full-size Winchester disk drives. A wiring harness from the system power supply provides power for the devices.

A 34-pin ribbon cable connects between the floppy disk controller and the floppy drive compartment; it handles data and control signal transfers between the controller and the first two floppy drives. The Winchester disk drives also use a 34-pin ribbon cable for control of multiple drives, however, each drive requires a separate data interface to the controller.

#### NOTE

The addresses in this manual are in hexadecimal notation, as stated in column headings and by a trailing H after the hexadecimal number.

#### 1.4 BUSINESS-PRO SPECIFICATIONS

Table 1-1 lists the environmental, electrical, and physical specifications for the BUSINESS-PRO computer system.

Table 1-1 BUSINESS-PRO System Specifications

Characteristic Specification

naracteristic Specification

Environmental requirements:

Temperature:

Operating +10 to +35 degrees C (+50 to +95

degrees F) with a temperature

gradient of less than 10 degrees

C (50 degrees F) per hour

Nonoperating -40 to +65 degrees C (-40 to +149

degrees F)

Relative humidity (noncondensing):

Operating 15 to 80 percent

Nonoperating 5 to 95 percent

Altitude -300 to 12 000 meters (-984.24 to

39 369.50 feet)

Power Requirements:

Voltage:

Domestic 90 to 140 volts ac

International 180 to 264 volts ac

Frequency:

Domestic 57 to 63 Hertz

International 47 to 53 Hertz

| Table 1-1 BUSINESS-PRO Sys         | stem Specifications (Continued) |

|------------------------------------|---------------------------------|

| Characteristic                     | Specification                   |

| Physical dimensions:  System Unit: |                                 |

| Width                              | 19.8 cm (7.8 in)                |

| Depth                              | 47.0 cm (18.5 in)               |

| Height                             | 47.2 cm (18.6 in)               |

| Weight                             | 26.1 kg (58.0 lbs)              |

| Color monitor:                     |                                 |

| Width                              | 38.1 cm (15.0 in)               |

| Depth                              | 38.9 cm (15.3 in)               |

| Height                             | 41.9 cm (16.5 in)               |

| Weight                             | 11.7 kg (26.0 lbs)              |

| Monochrome monitor:                |                                 |

| Width                              | 33.8 cm (13.3 in)               |

| Depth                              | 32.3 cm (12.7 in)               |

| Height                             | 36.6 cm (14.4 in)               |

| Weight                             | 6.8 kg (15.0 lbs)               |

| Keyboard:                          |                                 |

| Width                              | 54.1 cm (21.3 in)               |

| Depth                              | 19.3 cm (7.6 in)                |

| Height                             | 4.5 cm (1.8 in)                 |

| Weight                             | 2.1 kg (4.8 lbs)                |

#### Section 2

#### Main Logic Board

#### 2.1 GENERAL

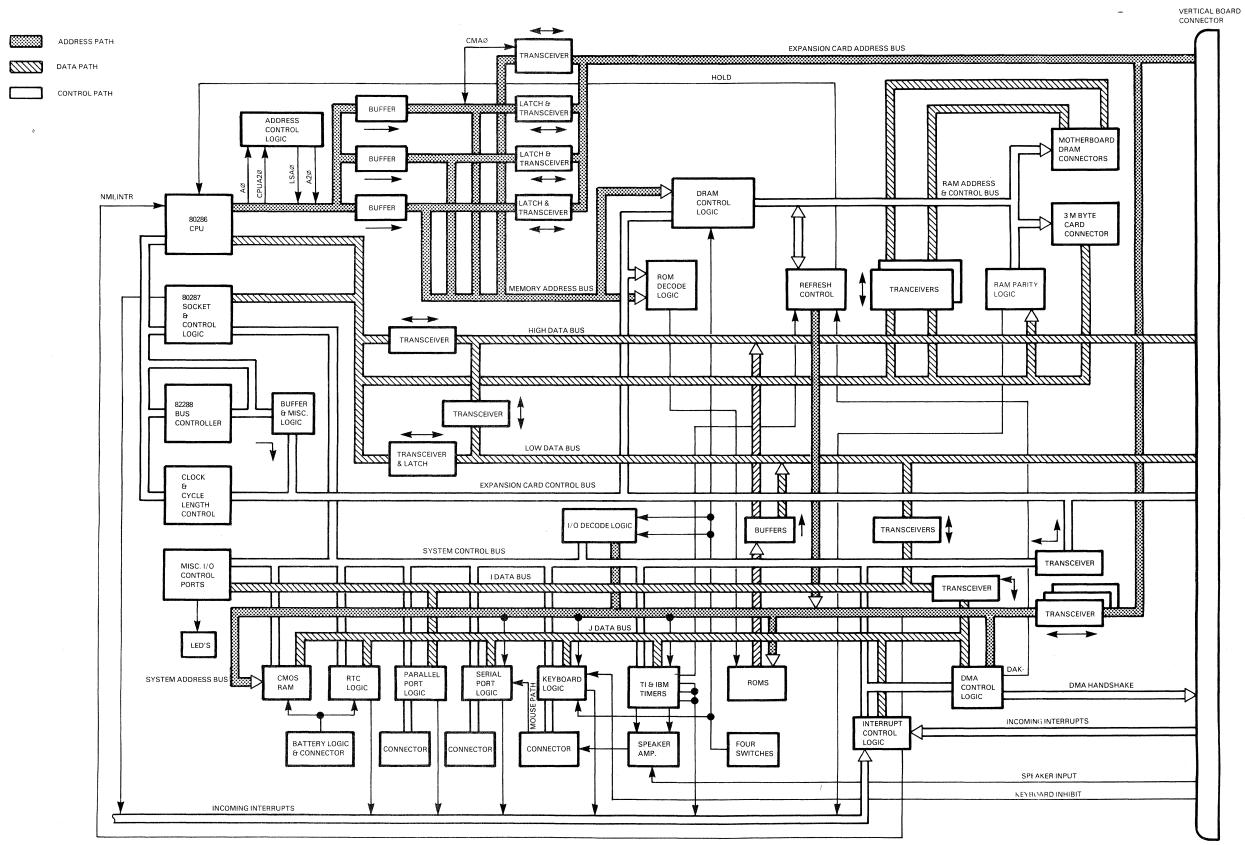

Figure 2-1 shows a block diagram of the BUSINESS-PRO computer's main logic board. This board contains the system's central processing unit (CPU) and its supporting logic, the system memory and memory control logic, direct-memory access (DMA) logic, and various other devices and circuits that generate and control system operations.

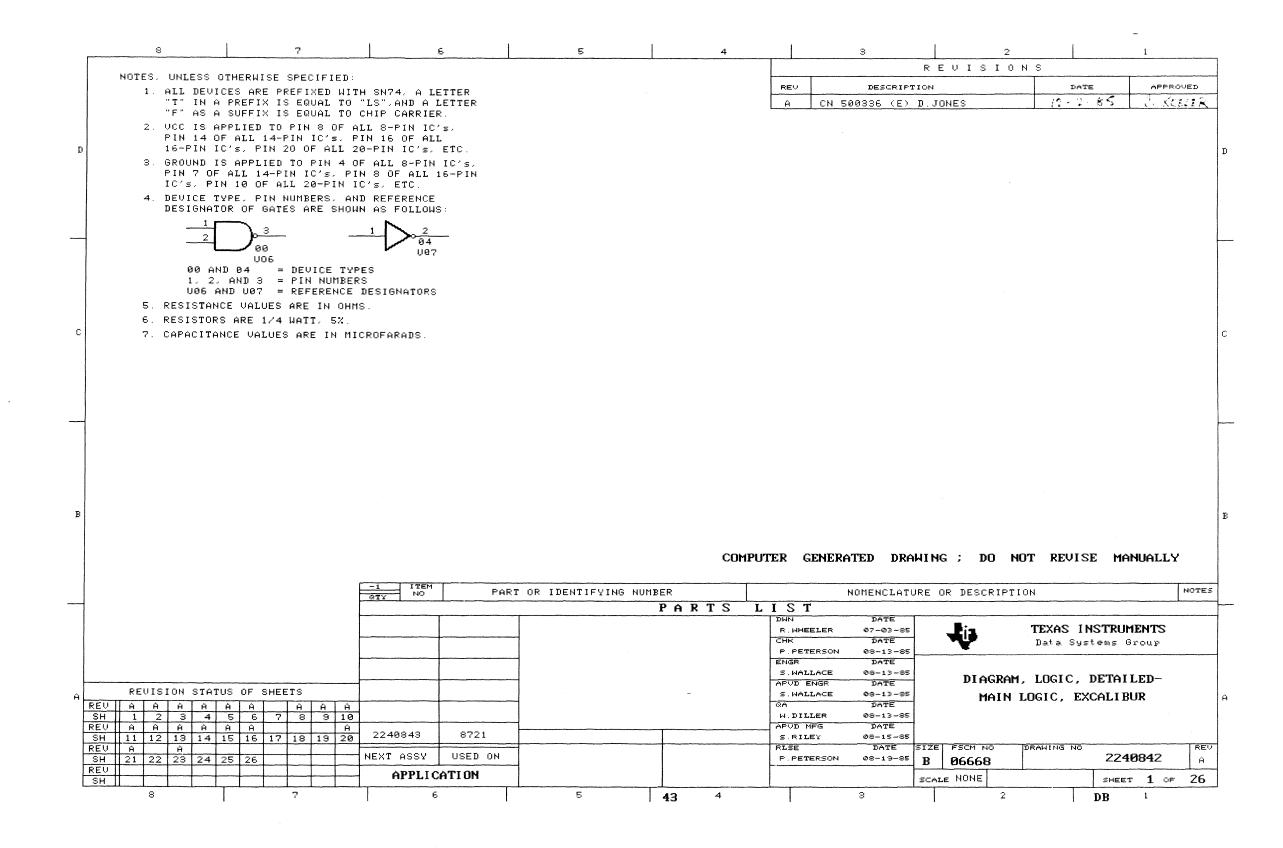

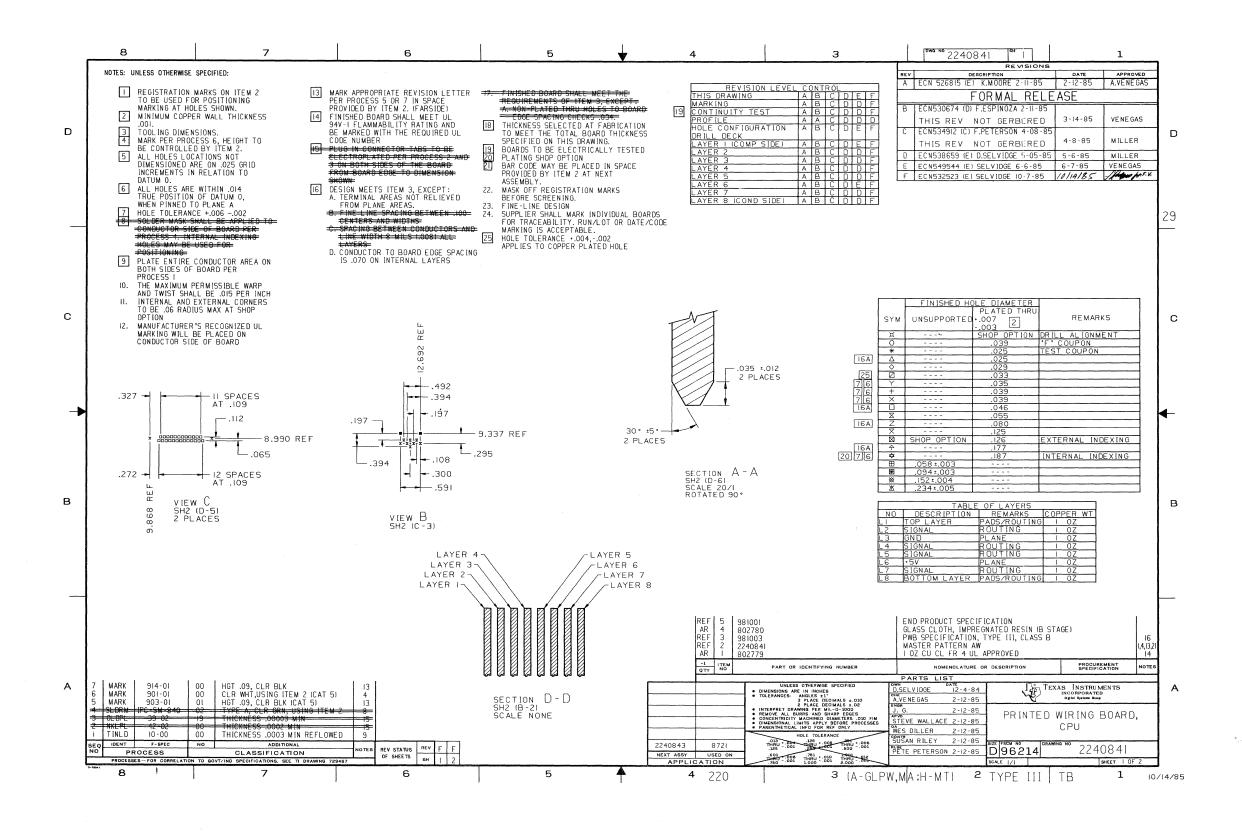

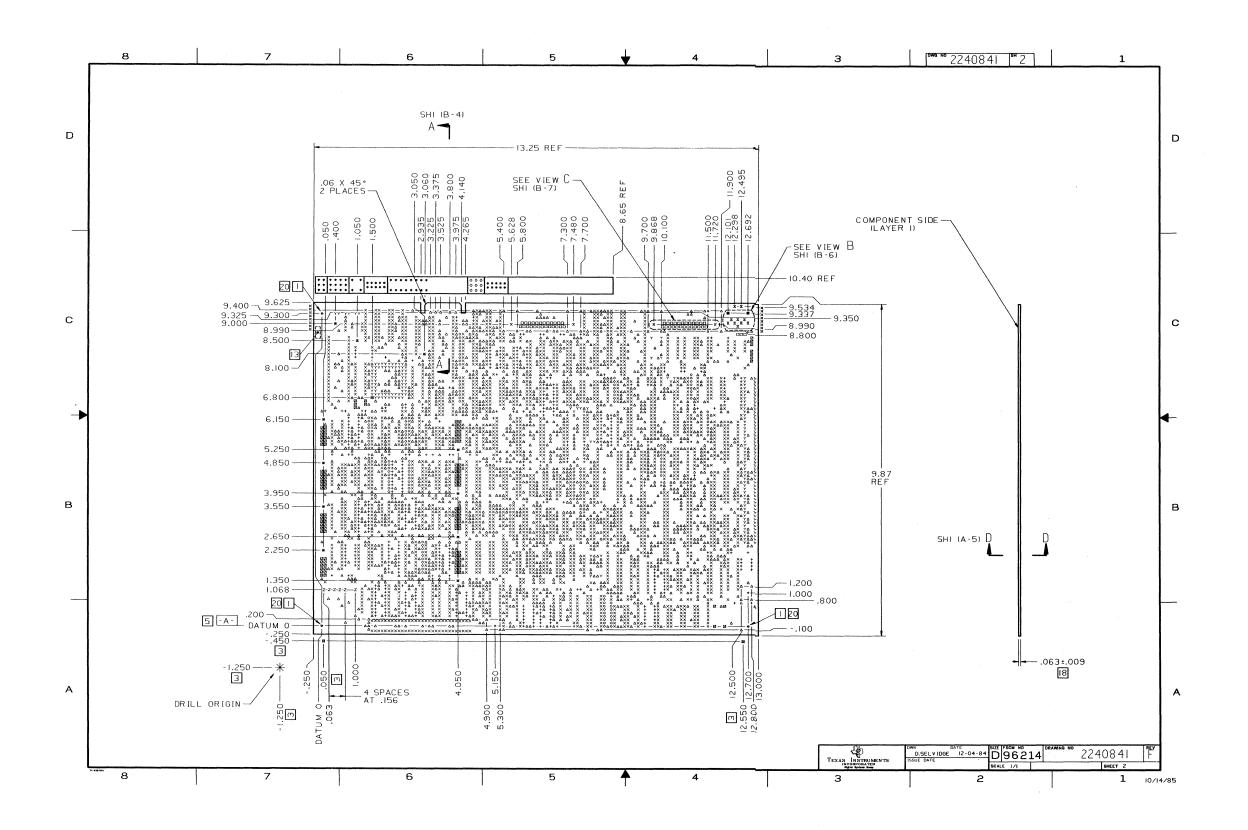

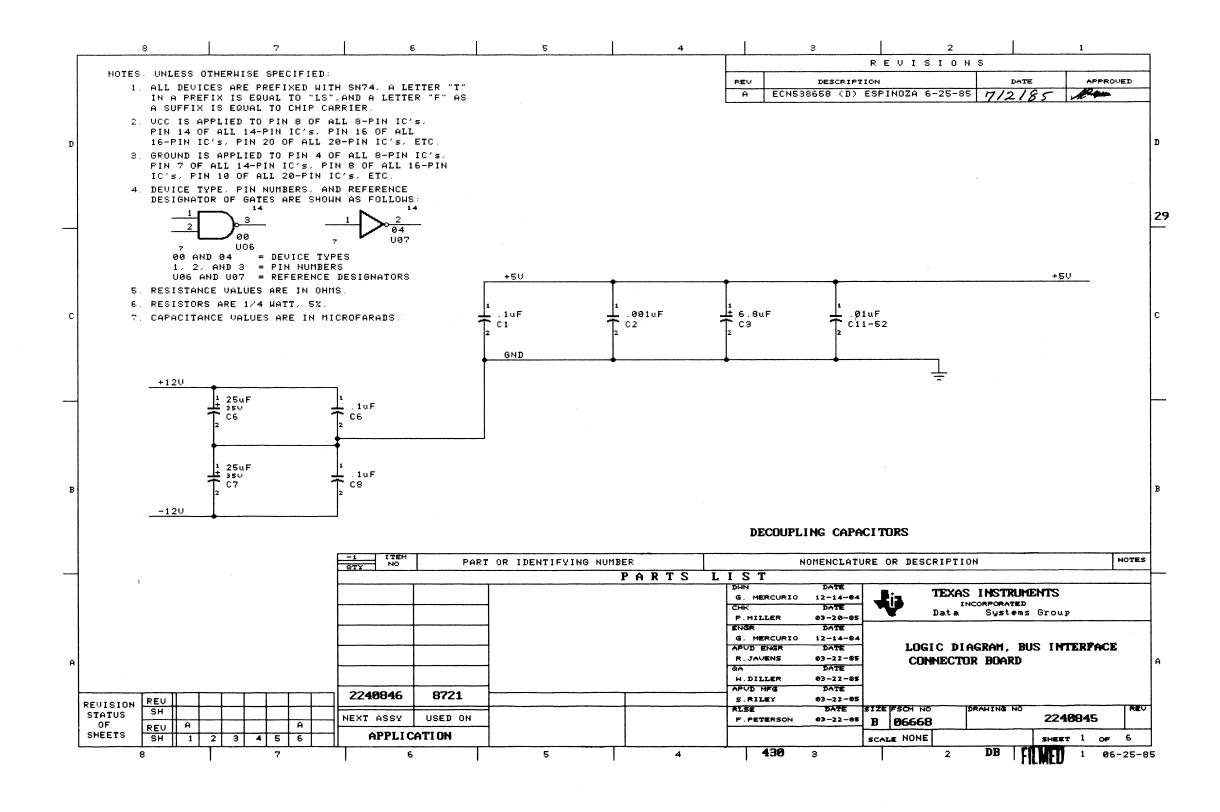

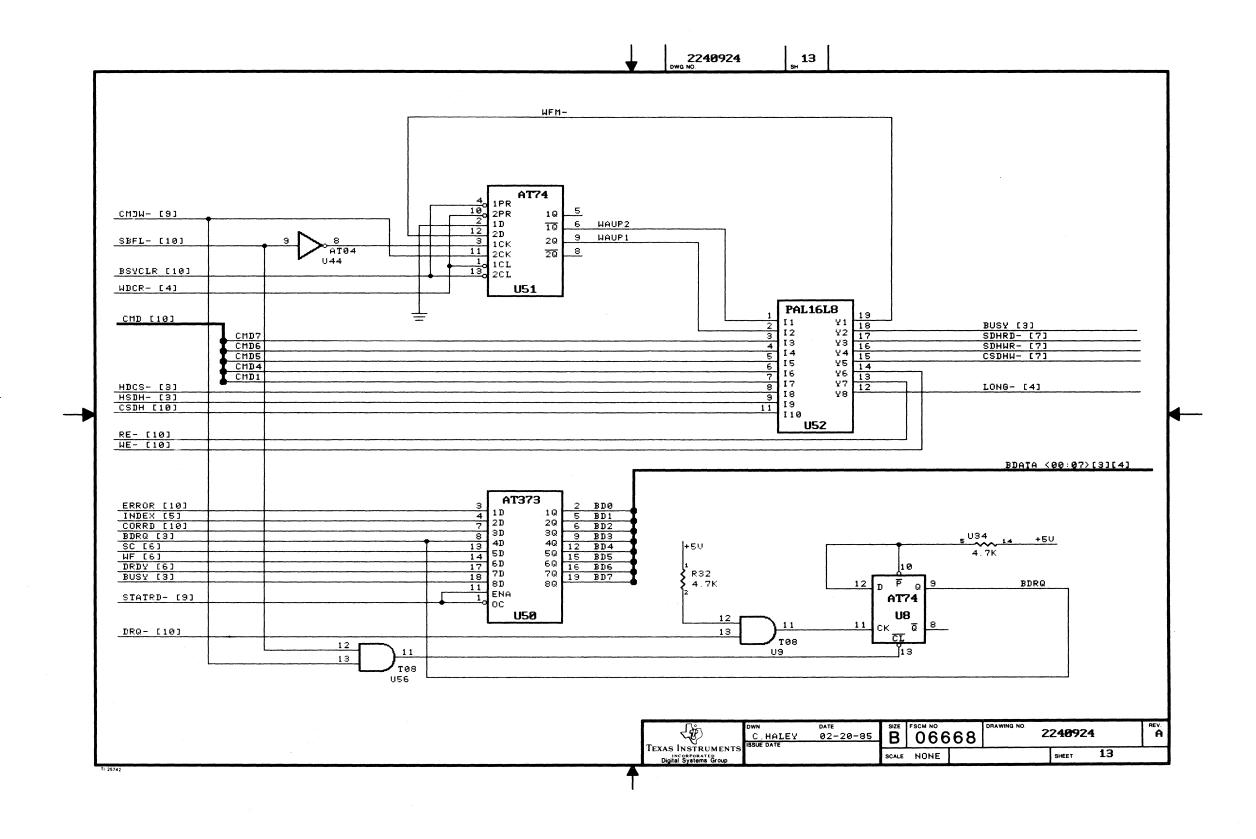

Appendix E contains the main logic board's logic diagrams and an index to its various circuits.

Figure 2-1 Main Logic Board Block Diagram

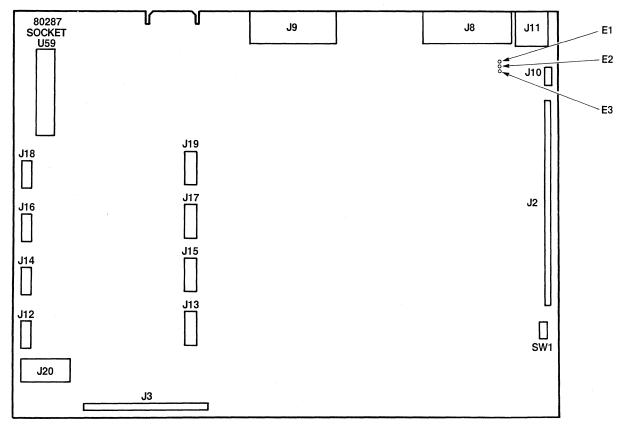

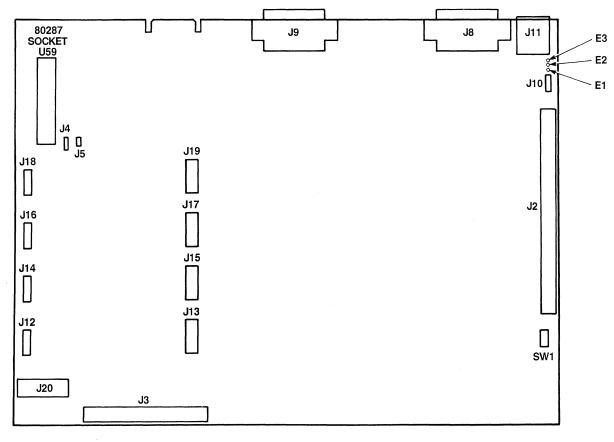

Figures 2-2 and 2-3 show the locations of the connectors, jumpers, switches, and the coprocessor on the two versions of the main logic board. The two boards, TI Part No. 2240843-0001 and 2535670-0001, can be distinguished by the presence or absence of the coprocessor option jumpers. The original board, TI Part No. 2240843-0001 does not have these jumpers; the later version does. The following is a list of the reference designators and their functions:

- \* J2 -- Expansion bus connector.

- \* J3 -- Expansion RAM interface connector.

- \* J4 and J5 -- Coprocessor option jumpers.

- \* J8 -- Serial port interface connector.

- \* J9 -- Parallel port connector.

- \* J10 -- Connector for the 6-volt battery.

- \* Jll -- Keyboard/mouse interface connector.

- \* J12 and J13 -- Interface connectors for on-board expansion RAM board 1.

- \* J14 and J15 -- Interface connectors for on-board expansion RAM board 2.

- \* J16 and J17 -- Interface connectors for on-board expansion RAM board 3.

- \* J18 and J19 -- Interface connectors for on-board expansion RAM board 4.

- \* J20 -- Power connector for the main logic board.

- \* E1, E2, and E3 -- Speaker terminals for systems that do not have a speaker in the monitor.

- \* SWl -- Five-section, dual-inline-package (DIP) switch that provides all required manual switching for the main logic board. The following table shows the use and setting for each section of the switch.

| Section  | Use                                                           | Setting        |               |

|----------|---------------------------------------------------------------|----------------|---------------|

| Switch 1 | CRT switch Parallel port Serial port 128K-byte DRAM Base DRAM | Off=mono       | On=color      |

| Switch 2 |                                                               | Off=port 1     | On=port 2     |

| Switch 3 |                                                               | Off=port 1     | On=port 2     |

| Switch 4 |                                                               | Off=disable    | On=enable     |

| Switch 5 |                                                               | Off=512K bytes | On=256K bytes |

2287490

Figure 2-2 Main Logic Board, TI Part No. 2240843-0001, Key Components

2287491

Figure 2-3 Main Logic Board, TI Part No. 2535670-0001, Key Components

The following paragraphs describe the circuits of the main logic board.

#### 2.2 SYSTEM CENTRAL PROCESSING UNIT

The system central processing unit (CPU) consists of an 80286 microprocessor unit and an optional 80287 numeric coprocessor. The microprocessor unit (MPU) and the coprocessor operate in parallel so that they appear to associated components as a single chip. If both devices are installed, the term CPU refers to both the 80286 and the 80287. The system CPU also includes the system clocks, the CPU bus buffers and latches, and the CPU status decoding and control line generation logic. The following paragraphs describe the circuits.

#### 2.2.1 Microprocessor Unit

The MPU can operate in either the real address mode or the protected virtual address mode. A reset operation places the MPU in the real address mode, which provides up to 1 megabyte of real address space. The MPU can then be placed in the protected virtual address mode, in which 1 gigabyte of virtual addresses can be mapped into a 16-megabyte real address space. This mode also provides memory protection to isolate the operating system and to ensure privacy for the programs and data of each task. The only way to return to the real address mode from the protected virtual address mode is to reset the MPU.

- 2.2.2 Optional Numeric Coprocessor An additional socket is available for the installation of an 80287 IC optional numeric coprocessor. For additional information, refer to the paragraphs entitled Numeric Coprocessor in Section 6.

- 2.2.3 CPU Bus Buffering

A set of address and control latches and various bus buffers

(data, address, and control) are provided as part of the CPU.

The following paragraphs describe these circuits.

- 2.2.3.1 Address and Control Bus Buffering. The CPU controls the address and control bus buffers, transceivers, and latches via the address latch enable (ALE) and hold acknowledge (HOLDA) signal, and a set of control lines labeled P/MD, D/PM, and PM/D, where P, D, and M represent processor-driven cycles, DMA-driven cycles, and master-driven cycles, respectively.

These control lines assume the following levels for the indicated type of cycle:

- \* P/DM -- High for a processor-driven cycle and low for a master- or DMA-driven cycle.

- \* D/PM -- High for a DMA-driven cycle and low for a processor- or master-driven cycle.

- \* PM/D -- High for a processor- or master-driven cycle and low for a DMA-driven cycle.

Table 2-1 lists the various devices and their states for the various types of cycles.

MPU Driven Cycles DMA orRefresh On-Board Master Devices Cycle Memory Other Cycle U3 and U5 | On On Off Off114 | Fall Thru | Off Off Latched U34, U35 Fall Thru Fall Thru Latched Latched A --> B B --> A and U36 A --> B B --> A | A --> B | A --> B | B --> A U38, U39 A --> B A --> B A --> B  $B \longrightarrow A$ and U40 U41 Off Off Off On U42 l On On Off Off

Table 2-1 Address and Control Bus Buffering

2.2.3.2 Data Bus Buffering. The data bus buffers, transceivers, and latches are, for the most part, under PAL(R) control. To provide for correct data transfer during 8-bit operations, the active byte of data is written or read on the low byte of the system data bus during byte wide cycles. Data bus transceiver U21 creates this byte switch. Table 2-2 shows the different buffer states for various operations. Refer to the device programming tables in Appendix D for more information.

Table 2-2 Buffer States of the Data Bus

| ODII Dadies                              |                                     |                           |                  |                        |                        |

|------------------------------------------|-------------------------------------|---------------------------|------------------|------------------------|------------------------|

| CPU Driven<br>Cycles                     | U19                                 | U20                       | U21              | U22                    | U93                    |

| R/W<br>80287                             | Off                                 | Off                       | Off<br>*1        | a->b                   | Off                    |

| R/W<br>on-board<br>memory                | a->b                                | a->b                      | Off              | a->b                   | Off                    |

| 8-bit<br>device<br>low-byte<br>transfer  | b->a R<br>a->b W                    | Off                       | Off              | b->a R<br>a->b W<br>*2 | b->a R<br>a->b W<br>*2 |

| 8-bit<br>device<br>high-byte<br>transfer | Off                                 | b->a R<br>a->b W          | a->b R<br>b->a W | b->a R<br>a->b W<br>*2 | b->a R<br>a->b W<br>*2 |

|                                          | lo-byte lst<br>latch b R<br>a->b W  | b->a R<br>a->b W          | Off              | b->a R<br>a->b W       | b->a R<br>a->b W       |

|                                          | hi-byte 2nd<br>stored->a R<br>Off W | a >D W                    | a->b R<br>b->a W | *2                     | *2                     |

| l6-bit<br>device<br>transfer             | b->a R<br>a->b W<br>*1              | b->a R<br>a->b W<br>*3    | Off              | b->a R<br>a->b W<br>*2 | b->a R<br>a->b W<br>*2 |

| MASTER<br>CYCLE                          | a->b R<br>b->a W<br>*1,*4           | a->b R<br>b->a W<br>*3,*4 | Off<br>*1        | b->a R<br>a->b W<br>*2 | b->a R<br>a->b W<br>*2 |

| DMA<br>CYCLE                             | a->b R<br>b->a W<br>*1              | a->b R<br>b->a W<br>*3    | Off<br>*1        | Off                    | Off                    |

| ++<br>  REFRESH                          | Off                                 | Off                       | Off              | Off                    | Off                    |

<sup>\*</sup>l - Condition true for word or low-byte transfers.

<sup>\*2 -</sup> Condition true if the device accessed is on the specified bus. If not, U93 is off, and U22 is driven a->b.\*3 - Condition true for word or high-byte transfers.

<sup>\*4 -</sup> Condition true for transfers involving on-board memory.

2.2.4 CPU Clock Generation and Bus Control

The CPU clock generator consists of a 24-megahertz can

oscillator, a divide-by-two flip-flop, and a divide-by-four flipflop. These flip-flops provide the 12-megahertz and 6-megahertz

system clocks, each of which has a duty cycle of 50 percent.

These clocks are buffered by an inverting buffer.

A programmable array logic (PAL) device contains synchronizing logic for the ARDY-, JRDY-, and OWS- lines from the wait-state control logic and the RES- line from the power-good circuit. Refer to the device programming tables in Appendix D for more information.

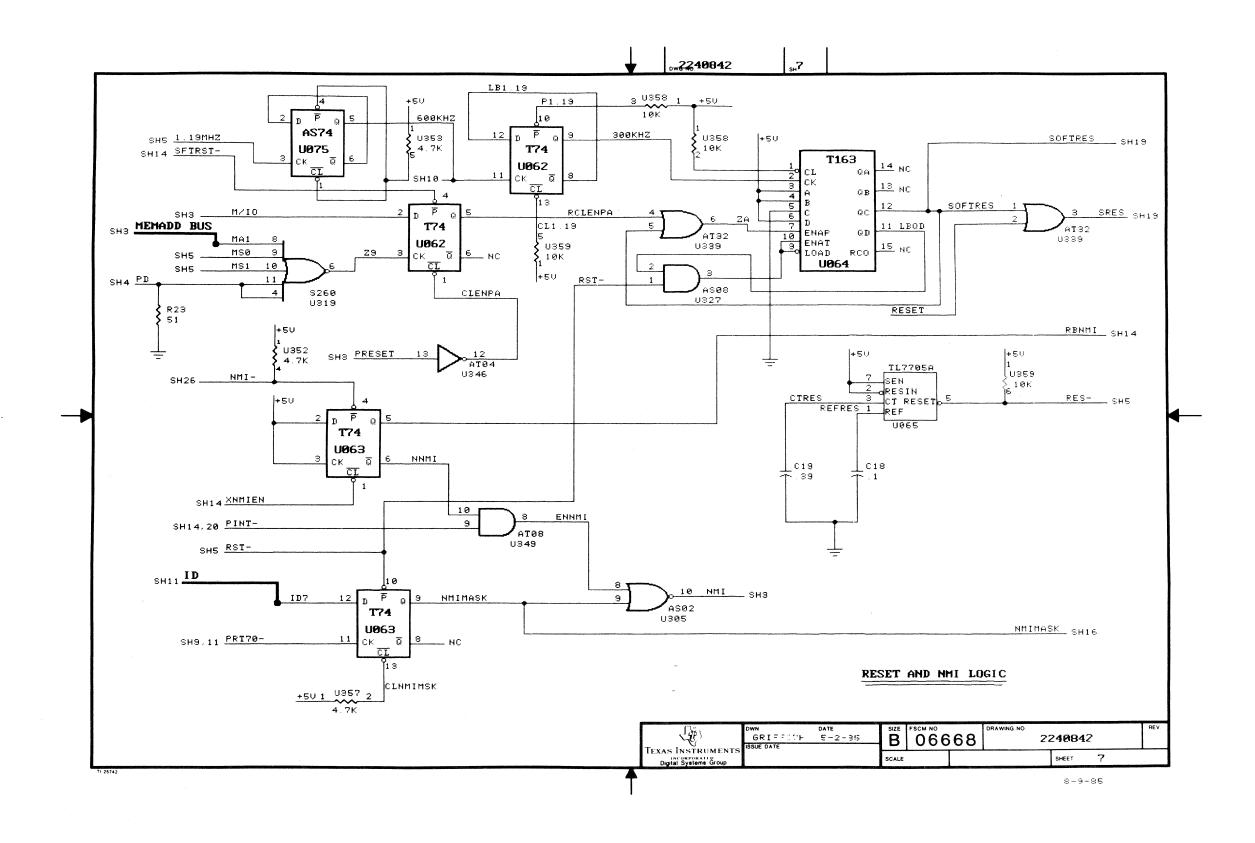

- 2.2.5 Reset Circuit

The main logic board provides the following reset conditions:

- \* System reset -- Power-up and dropout conditions initiate this reset.

- \* MPU software reset -- A software instruction initiates this reset to return the MPU to the real address mode from the protected virtual address mode.

- \* Coprocessor software reset -- A software instruction initiates this reset to return the coprocessor to the real address mode from the protected virtual address mode.

- \* Shutdown reset -- A shutdown cycle initiates this reset.

The following paragraphs describe the reset conditions.