KASTNERŚ MEMOS 4X TI-ASC

#### MEMORANDUM

4 April 1972

TO

Hardware Design (15) System Engineering Wayne Winkelman (4)

FROM

Bill Kastner

SUBJECT

NEW INSTRUCTIONS FOR THE TIMES-FOUR CENTRAL PROCESSOR

A description of all new times-four CP instructions is attached. These instructions are listed following:

- 1. FORK, Fork.

- 2. JOIN, Join.

- 3. PB, Prepare to Branch.

- 4. LEM, Load Arithmetic Exception Mask and Condition.

- 5. LRL, Load Arithmetic Register Right Half from Alpha Left Half.

- 6. STRL, Store Arithmetic Register Right Half to Alpha Left Half.

- 7. SCLK, Store 32-bit Fixed Point Clock.

- 8. Select on Equal, Select on Not Equal (Vector).

- 9. Replace on Equal, Replace on Not Equal (Vector).

BILL KASTNER

Bill Kastner

WDK:jc

Attachment

#### **ATTACHMENT**

Fork Indicator FORK Mnemonic code  $1 \rightarrow Fork$  Indicator 9A Op code

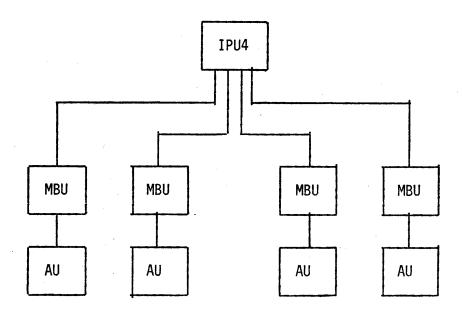

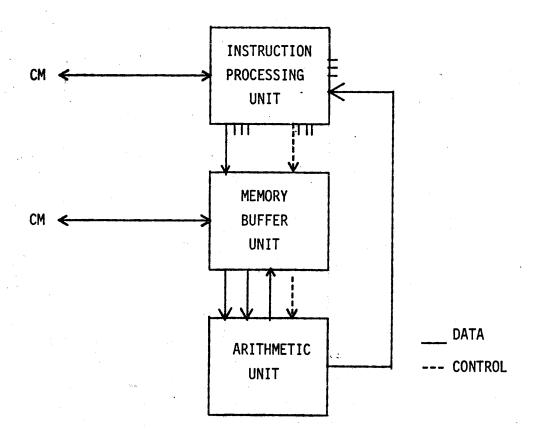

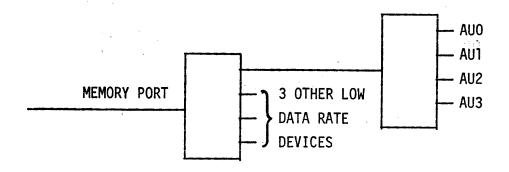

The FORK instruction is an advisory type instruction to the IPU control: Execution of the FORK instruction sets the fork indicator bit-within the IPU control and allows subsequent vector or scalar instructions to proceed to execution independently. In the times-four CP, this means that any combination of vector or scalar instructions can be in execution simultaneously in each of the four MBU-AU pairs. Refer to the write-up describing FORK and JOIN control for further details on the effect of this instruction.

| <u>Join</u>                   | JOIN       | Mnemonic code |

|-------------------------------|------------|---------------|

| <pre>0 → Fork Indicator</pre> | <b>9</b> B | Op code       |

The JOIN instruction is an advisory type instruction to the IPU control. Execution of the JOIN instruction resets a control bit which then disallows parallel pipeline processing of subsequent mixtures of vector and scalar instructions. In the times-four CP, this means that only scalars can be in execution at a time or only a singular vector at a time. Combinations of vectors and scalars cannot be in execution simultaneously. Refer to the write-up describing FORK and JOIN control for further details on the effect of this instruction.

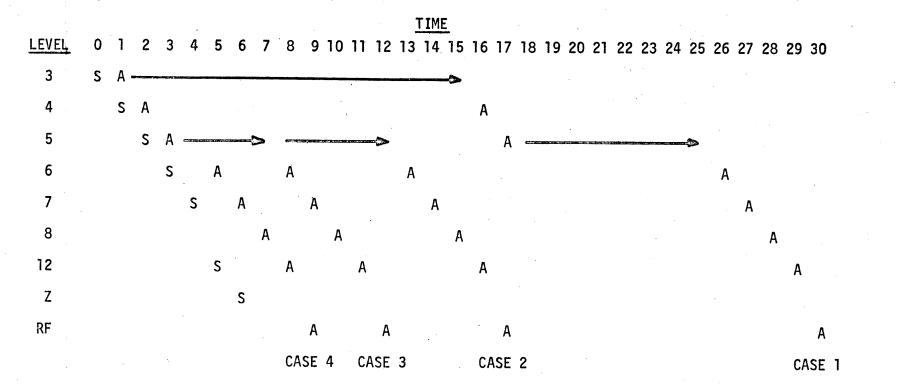

#### FORK and JOIN Control

#### Purpose

Scalar instructions, operating disjoint from vectors, normally use the four pipes in a parallel fashion. For scalar code of this type, operand and instruction hazard checking hardware is built into the IPU. This hardware prevents the IPU from using scalar operands or instructions that have been modified by prior scalar instructions but which have not yet reached their register or memory destination. However, when vectors and scalars are mixed, the hardware for checking operand or instruction hazards is not effective if these two types are in execution simultaneously. Therefore, the scalar FORK and JOIN instructions have been provided to allow the user to have control over operand and instruction hazard checking between vectors and scalars by either allowing or disallowing their simultaneous execution. In addition to these two scalar instructions, there also exists a means by which the fork indicator can be turned on or off with a VECT or VECTL instruction.

# Setting or Resetting FORK/JOIN Mode

Two methods may be used to set the Fork indicator. One of these is by means of the scalar FORK instruction. The other is by placing a "one" in the ALLOW FOLLOWING (AF) bit of a vector instruction. Resetting of the Fork indicator is done by the JOIN instruction or by a "zero" in the AF bit of a vector instruction.

When the Fork indicator is set, parallel execution of vectors and scalars is allowed by the hardware. When the Fork indicator

is reset, only a singular vector may be in execution in one of the four pipes; or only pure scalar instructions (not mixed with vectors) may be in execution in any of the four pipes.

#### Uses of the ALLOW CURRENT Bit

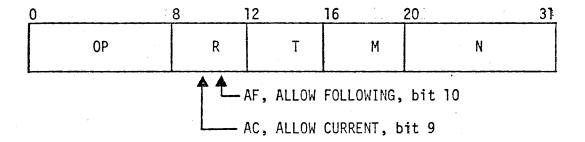

The ALLOW CURRENT (AC) bit is contained in the R-field of a vector instruction adjacent to the ALLOW FOLLOWING bit as shown following:

This bit is used in combination with the existing mode of the Fork indicator. The combinations are best described by using some examples.

#### Example A:

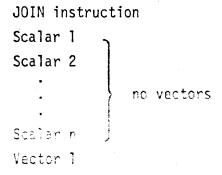

In example A, all scalar instructions are processed in parallel up to Vector 1. Vector 1 will begin processing when all scalar

writes to Central Memory are complete, and no instructions will modify the Vector Parameter File (VPF). This is true no matter what the value of the AC bit is for Vector 1. If the program is to continue in the JOIN mode, the "Allow Following" bit of Vector 1 must be zero.

#### Example B

JOIN instruction

Scalar 1

Scalar 2

no vectors

Scalar n

FORK instruction

Scalar n+1

Scalar n+2

Vector 1

In example B, all scalar instructions are processed in parallel up to Vector 1. Vector 1 must wait at level 3 of the IPU pipeline until all scalars through "n" have completed their writes to memory, and none of these instructions are of the type that will modify the Vector Parameter File. Any other scalar instruction, either before or after the FORK, can be processed in parallel with Vector 1 if Vector 1 has its "Allow Current" bit set to "one." If the AC bit is "zero," processing of Vector 1 is held up until the preceding conditions are true through Scalar n+2. If this is the case, the FORK instruction had no effect.

#### Uses of the ALLOW FOLLOWING Bit

In certain applications it may be desirable for a program to operate in a JOIN mode through Vector 1 but to allow parallel execution of Vectors 1 and 2. This is accomplished with the following program:

#### Example C

```

JOIN instruction

Scalar 1

Scalar 2

no vectors

Scalar n

Vector 1 (AC = Ø, AF = 1)

Vector 2 (AC = 1, AF = Ø)

where "Ø" is a "Don't Care"

```

This program is the same as example A with the exception of the inclusion of Vector 2. The "Allow Following" bit of Vector 1 and the "Allow Current" bit of Vector 2, both being a "one," are the keys that unlock the pipelines for parallel processing.

If either the AF bit of Vector 1 or the AC bit of Vector 2 is "zero" in example C, Vector 2 will proceed to the point of selecting a pipe and initializing that MBU but will not access memory until Vector 1 is complete.

#### Example D

JOIN instruction

Scalar 1

Scalar 2

no vectors

Scalar n

Vector 1

FORK instruction

Scalar n+1

Example D is a case where the JOIN mode is desired through Vector 1, and then the FORK instruction is encountered. For this code to be reasonable, the "Allow Following" bit of Vector 1 is "zero." Vector 1 will proceed as described in example A. Vector 1 must complete before any other instruction is processed in the IPU. This includes the FORK, so Scalar n+1 will not be executed until Vector 1 completes.

# AC and AF Summary

The four cases of the AC and AF bits of a vector instruction are summarized as follows:

$$(AC, AF) = (0, 0)$$

Finish all the preceding instructions, and then complete this vector before proceeding.

$$(AC, AF) = (0, 1)$$

Finish all the preceding instructions, but allow succeeding instructions to proceed while executing this vector.

$$(AC, AF) = (1, 0)$$

Begin this vector as soon as all instructions preceding the FORK have been completed, and then finish this vector before proceeding.

$$(AC, AF) = (1, 1)$$

Begin this vector as soon as all instructions preceding the FORK have been completed, but allow succeeding instructions to proceed while executing this vector.

The following table relates the AC and AF bits of the R-field to how the instruction string would look without the bits:

|        | · · · · · · · · · · · · · · · · · · · |                |                        |

|--------|---------------------------------------|----------------|------------------------|

| WITH   | BITS                                  |                | WITHOUT BITS           |

| VECTOR | <u>AC</u><br>0                        | <u>AF</u><br>0 | JOIN<br>VECTOR<br>JOIN |

| VECTOR | 0                                     | 1              | JOIN<br>VECTOR<br>FORK |

| VECTOR | 1                                     | 0              | VECTOR<br>JOIN         |

| VECTOR | 1                                     | 1              | VECTOR<br>FORK         |

PB

Mnemonic code

9E

Op code

The Prepare-to-Branch instruction is an advisory type instruction to the IPU instruction look-ahead hardware. Execution of a PB instruction does not affect the results of a program in any way; its purpose is to decrease the time taken at a branch instruction in fetching the octet of instructions to which the branch is directed.

The PB instruction develops a ß address from its T-, M-, and N-fields in the same way that a standard branch instruction (BCC or BRC) would do if it were placed at the instruction address of the PB instruction. The R-field of the PB instruction should be set to the difference between the instruction address of the PB instruction and the intended branch instruction. This count may not exceed 15 since the R-field is only four bits. Counts of "O" and "1" have special uses.

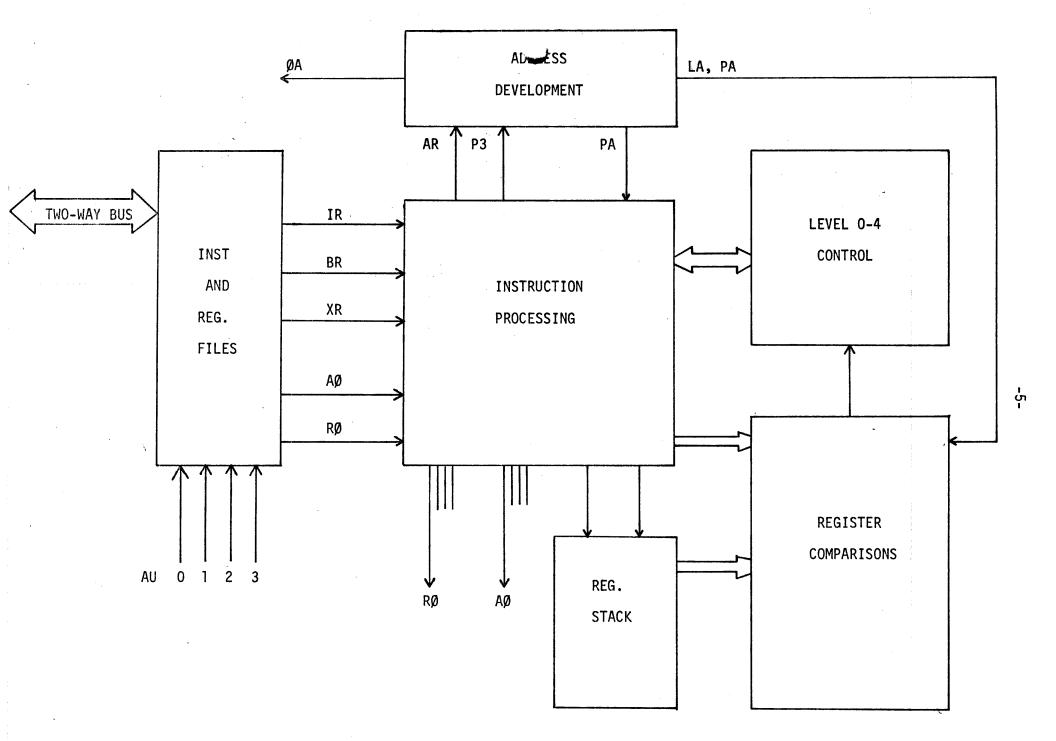

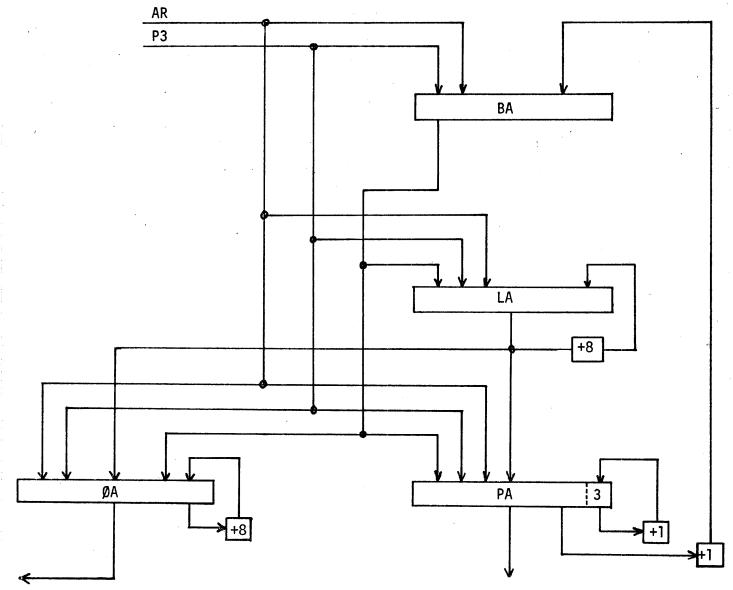

The internal IPU hardware saves both the  $\beta$  address developed by the PB instruction and the length count specified by the R-field. The length count is decremented by one as each new instruction is entered into the instruction register (IR). At the octet boundary where the look-ahead would normally request the next octet past the octet containing the branch, it recalls the  $\beta$  address saved by the PB instruction and requests it instead of the normal look-ahead octet. In this manner the instruction at the branch address of the target branch instruction will be available for immediate processing following the execution of the target branch instruction.

Should the target branch fail to take the branch, the hardware will realign itself to take the downstream instructions. This is done by

rerequesting the branch instruction's octet if necessary, plus the next octet of look-ahead instructions beyond the branch octet.

Here is an example of PB instruction usage. In this example the R-field is "7," designating seven instruction locations from the PB to the BLB instruction. The branch address developed by the PB is indirect to the PB instruction address, plus eight (Program counter + 8). At this indirect address we find the address of the COSINE routine. The BLB instruction also uses this same indirect address but refers to it via an indirect program counter address plus one. By using the PB instruction in this manner, the first instruction of the COSINE routine will be directly behind the BLB instruction in the IPU pipeline at the completion of BLB execution.

## Special Extension to PB Instruction

R-field counts of 1 and 0 of the PB instruction have a special use of enabling or disabling the dual branch hardware. If a PB of R-field 1 is executed, the dual branch mechanism is enabled. When enabled, a conditional branch instruction of the type BRC, BCC, or BAE will make a memory request for the octet containing the branch address while waiting at level 3 for the determination of the branch condition.

The octet containing the branch address replaces the look-ahead octet on the assumption that the branch will be taken. If the branch fails, then the octet containing the branch address is discarded; and the normal look-ahead octet is refetched. Dual branch hardware works only if a BRC, BCC, or BAE is positioned in the first four words of an octet.

If a PB of R-field O is executed, the dual branch mechanism is disabled. When disabled, nothing is done to fetch an octet along the branch path. The normal look-ahead along the downstream path will continue to function.

#### Load Arithmetic Exception Mask and Condition Registers

LEM Mnemonic code

11 Op code

$(\alpha)_{0-7} \rightarrow AC$ , AM

Loads bits 0 through 3 of the contents of location  $\alpha$  into the fourbit arithmetic exception condition code register, and loads bits 4 through 7 of the contents of location  $\alpha$  into the four-bit arithmetic exception mask register.

Bits 0 through 3 load the arithmetic exception condition code register as follows:

Bit

- O Divide check

- 1 Fixed point overflow

- 2 Floating point overflow

- 3 Floating point underflow

Bits 4 through 7 load the arithmetic exception mask as follows:

Bit

- 4 Divide check

- 5 Fixed point overflow

- 6 Floating point overflow

- 7 Floating point underflow

Result Code

Not set.

#### Programming Notes

An interrupt signal from the CP to the PPU is activated if an arithmetic exception is detected and the mask bit corresponding to that arithmetic exception has been set to a "one." An interrupt is not possible for that arithmetic exception if the mask bit is set to "zero."

Alteration of the AE condition register and AE mask register by a LEM instruction will cause an arithmetic exception program interruption if the corresponding bits of the AE condition register and AE mask register are both "one" after the LEM instruction has passed through the CP pipeline. Also, a program interruption will occur after completion of a LEM instruction if any of the following pairs of bits from the contents of location  $\alpha$  are both "one":

- (0, 4)

- (1, 5)

- (2, 6)

- (3, 7)

This instruction is paired with the BLB and BLX instructions in that the bit positions (bits O through 7) agree with the position of the AE condition and AE mask bits stored as a result of a previous BLB or BLX instruction.

| Load Arithmetic Register Right    | LRL Mnemonic code        |

|-----------------------------------|--------------------------|

| Halfword From Alpha Left Halfword | 10 Op code               |

| $(\alpha_h) \rightarrow AR_{rh}$  | Arithmetic register file |

A halfword operand from memory is entered into the right half of arithmetic register AR. The left half of register AR remains unchanged. The operand selected is from the left half of a central memory or register whole word when not indexed. If indexed, an even index value selects words from the left half of a central memory or register whole word. An odd index value addresses the right halfword.

Result Code: Set arithmetically.

Store Arithmetic Register Right STRL Mnemonic code

Halfword into Alpha Left Halfword 26 Op code

$$(AR_{rh}) \rightarrow \alpha_h$$

The right half of arithmetic register AR is stored into the left half of a singleword location when not indexed. If indexed, an even

index value selects the left half of a singleword location for storage.

An odd index value addresses the right halfword.

Result Code: Set arithmetically.

## Store Clock

SCLK Mnemonic code

CLOCK → a

AE 'Op code

The current value of the 32-bit fixed point CP clock is stored into singleword location  $\alpha$ .

Result Code: Set arithmetically.

## Vector Select on Not Equal

$(SV_{msb} = 1)$

A vector select on not equal instruction generates an output vector  $\vec{C}$  composed of elements from vector  $\vec{B}$ . The index values given by the elements of vector  $\vec{A}$  correspond to the index location of elements that are not selected from vector  $\vec{B}$ . All other elements of vector  $\vec{B}$  are selected. These selected elements are the ones for which the index values given by vector  $\vec{A}$  do not correspond to the index location of elements from vector  $\vec{B}$ .

# Programming Notes:

- (1) Same as (1) under Select on Equal.

- (2A) Same as (2A) under Select on Equal. Also, if the last index value plus one is less than the number of elements of vector  $\vec{B}$ , then

the self loop length should be set equal to the number of elements of vector  $\vec{B}$ .

- (2B) If the last index value plus one is equal to the number of elements of vector  $\vec{B}$ , then the index list of vector  $\vec{A}$  can be examined further to determine if the index values looking backward from this last index value decrease by unity for each step backward. Using this procedure, the value of the last index value found prior to a nonunity decrease of index values can be used for the self loop length specification of the vector select on not equal instruction and still obtain the same result vector  $\vec{C}$ . If an index value of zero is reached using this procedure, then no elements of vector  $\vec{B}$  will be used by this instruction. The self loop length can be set equal to zero in this case, and no operation will be performed.

- (3A) Same as (3A) under Select on Equal.

- (3B) Same as (3B) under Select on Equal.

- (4) Same as (4) under Select on Equal.

- (5) An index list beginning with a value of one, selects the first element of vector  $\vec{B}(b_0)$  but not the second element  $(b_1)$ .

- (6) Same as (6) under Select on Equal.

Example: A singleword select on not equal instruction using one self loop of length 8.

| Halfword<br>Index Vector Ā | Singleword<br>Vector B | Singleword<br>Vector C |

|----------------------------|------------------------|------------------------|

| 2, 3                       | +16,+72,-54,-75        | +16,+72,+71,+14        |

| 5, 6                       | +71,-64,-15,+14        |                        |

| 7FFF, -                    |                        |                        |

## Vector Replace on Not Equal

$(SV_{msb} = 1)$

A vector replace on not equal instruction accepts as inputs a contiguous list of replacement elements from vector  $\vec{B}$  and a contiguous list of indices from vector  $\vec{A}$ . Elements from vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output array. The index values given by the elements of vector  $\vec{A}$  correspond to the index location of elements in the  $\vec{C}$  output array that are not replaced. All other elements of vector  $\vec{C}$  are replaced. These replaced elements are the ones for which the index values given by vector  $\vec{A}$  do not correspond to the index location of elements in vector  $\vec{C}$ .

#### Programming Notes:

- (1) The length specification of the self loop (L-field) for a vector replace on not equal instruction should be set equal to the difference between the number of elements in the  $\vec{C}$  vector and the number of indices in the  $\vec{A}$  vector for a shortened vector operation. Otherwise, the length specification can be set equal to the number of elements in the  $\vec{C}$  vector providing that an index boundary limit equal to the largest positive number (7FFF $_{hex}$ ) is placed in the data location following the last index value of vector  $\vec{A}$ .

- (2) Same as (2) under Replace on Equal.

- (3) An index list beginning with a value of "one" replaces the first element of vector  $\vec{C}$  ( $C_0$ ) but not the second element ( $C_1$ ).

- (4) Inner or outer loops with vector replace on not equal require a considerable amount of preparessing on index vector  $\vec{A}$  before they can be used.

#### MEMORANDUM

24 April 1972

TO

Dennis Best Gary Boswell John Gifford Frank Little

Bill Beebe Gary Cobb Bill Cohagan

Al Riccomi Tom Treptow

COPY TO

Buddy Dean

Charles Stephenson

Joe Watson

FROM

Bill Kastner V

SUBJECT

DECISIONS MADE ON 4X CP CONTEXT SWITCHING

Several decisions were made in a meeting on April 14 relative to context switching on the times four CP. This memo is a confirmation of these decisions.

1. Load, Store, and Exchange Status CCR commands will exist on the 4X CP. The CCR command codes for these operations will not change from those of the 1X CP. They are as follows:

4108 Store Status 4109 Load Status 410A Exchange Status

The data stored in the Status Map consists of six octets of the Register File, the Program Status Doubleword (PSDW), and the 32-bit CP clock. New information stored in the PSDW for the 4X CP is the fork indicator in bit position 2l of the first word of the doubleword. Refer to page 3-26 of the Central Processor Hardware Specification for the PSDW format. Four bits for disabling any one or more of the four pipes during diagnostic tests will be provided in bit positions 12 through 15 of the first word of the Program Status Doubleword.

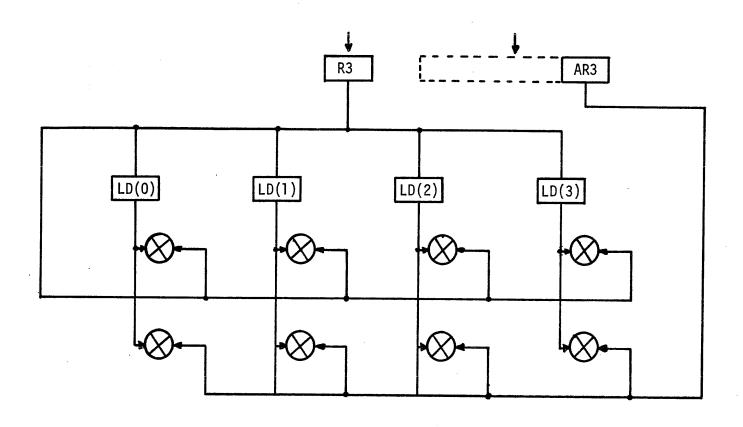

2. Load, Store, and Exchange Intermediate CCR commands will be changed to Load, Store, and Exchange CP Details CCR commands on the 4% CP. The difference between the old Store intermediate and the new Store CP Details operation will be in the amount of data stored. Store CP Details is essentially the same as the Store Maintenance Details operation on the 4% machine with the difference being the point at which vectors are stopped. With a Store CP Details command the circular address file of the MBU is drained to its empty state; whereas in the case of a Store Maintenance

Details command, the circular address file (CAF) is not emptied since this command is primarily for maintenance use. It is necessary during certain maintenance operations to see the CAF in operation, so the Store Details command is being kept for this purpose.

- 3. A recent decision, with regard to CCR commands for the CP, is the removal of the Lock and Unlock PC maintenance commands. No satisfactory use has been found for these commands during hardware checkout, so they are being eliminated. Therefore, strike the CCR commands 4102 and 4103 for Unlock PC and Lock PC, respectively, on page 35 of Section G of the ASC System Hardware Description.

- 4. A CR-bit will be assigned to indicate when a "vector bad guy" is in progress. The CR-bit will continuously monitor the "vector bad guy" state of the CP. A final software check of the CP details map in memory will be made to cover the case in which a bad guy vector was just starting at the time the CR-bit was tested and found to be "zero" or the case in which a bad guy vector had just finished at the time the CR-bit was tested and found to be "one." Appropriate job output messages will be printed by the operating system in the event either of the two cases are detected during operation.

- 5. Addressability restrictions will be placed on the user when executing a "vector bad guy." In the times four CP the "vector bad guys" are the Vector Select, Replace, and Order instructions. These vectors should not write over their input arrays. This constraint, however, will be the responsibility of the user and will not be protected by hardware.

- Efforts to reduce the context switching time have dealt with the possibility of using the status map for exchanging CP jobs. The proposed plan is to Store Status when an MCW instruction is encountered or when a stacked MCP occurs. A CP details map will be stored if the CP job is interrupted during execution or if an arithmetic exception, illegal op, spec. error, or protection violation occurs. Interrupting a job during execution is done by issuing a Store CP Details CCR command.

The map stored into memory will contain a bit that indicates whether it was stored as a CP Details map or as a Status map. Hen a job is returned to CP execution, this bit is transferred to a newly defined CR-bit in the PPU CR-file. This CR-bit is used by the automatic context switch mechanism to determine whether to load a CP Details map or a Status map into the CP when resuming job execution.

Bill Kastner

BILL KASTNER

#### **MEMORANDUM**

19 June 1972

| TO      | SE Group Wayne Winkelman (4)                                       |

|---------|--------------------------------------------------------------------|

| * .     | Gary Cobb                                                          |

|         | Bill Cohagan .                                                     |

|         | Sterling Mathis                                                    |

|         | Gary Miley                                                         |

|         | Dave Paterson                                                      |

|         | Charles Stephenson (4)                                             |

| FROM    | Bill Kastner                                                       |

| SUBJECT | INSTRUCTION MNEMONIC CODE CHANGES FOR TIMES FOUR CENTRAL PROCESSOR |

The mnemonics for the halfword Load and Store instructions are being changed in the times four Central Processor to a more consistent set. The new halfword Load and Store instructions in the 4X CP are LRL and STRL. The letter sequence used in these mnemonics has been arranged according to the order in which the register operand, then the memory operand is specified in assembler source code. For LRL, the RL sequence indicates the right half register word is loaded from the left half of a central memory word. Similarily for STRL, the RL sequence is an aid in remembering that the right half register word is stored into the left half of a central memory word.

The halfword Load and Store instructions that were available in the times one CP used mnemonics that are not easily associated with their register - memory usage. The following set of mnemonic codes are being used for the 4XCP.

| OP CODE | MNEMONIC CODE | DESCRIPTION                                                     |

|---------|---------------|-----------------------------------------------------------------|

| 15      | LLL           | Load register left halfword from central memory left halfword   |

| 19      | LLR           | Load register left halfword from central memory right halfword  |

| 10      | LRL           | Load register right halfword from central memory left halfword  |

| 1D      | LRR           | Load register right halfword from central memory right halfword |

| 25      | STLL          | Store register left halfword into central memory left halfword  |

19 June 1972

| OP CODE | MNEMONIC CODE | DESCRIPTION                                                                   |

|---------|---------------|-------------------------------------------------------------------------------|

| 29      | STLR          | Store register left halfword into central memory right halfword               |

| 26      | STRL          | Store register right halfword into central memory left halfword               |

| 2D      | STRR          | Store register right halfword into central into central memory right halfword |

BILL KASTNER

BKfo

ask y

TO:

CP Checkout

Hardware Development Software Development

SDD

System Engineering

System Test

FROM: •

Bill Kastner

CATEGORY:

CT

SUBJECT:

Retrofit of ASC #1, #2, and #3 With CP Instructions LRL and STRL

The CP currently has three halfword load and three halfword store instructions. The old and new mnemonic codes for these instructions are:

| OP CODE | OLD MNEMONIC | NEW MNEMONIC |

|---------|--------------|--------------|

| 15      | LH           | LLL          |

| 19      | LL           | LLR          |

| 10      | LR           | LRR          |

| 25      | STH          | STLL         |

| 29      | STL          | STLR         |

| 2D      | STR          | STRR         |

|         |              |              |

Four halfword load paths exist from the left or right half memory word to the left or right half register word. A set of four similar paths exist for stores. The remaining halfword load and store path is being included in the times four CP instruction set and will be retrofit on ASC serial numbers 1, 2, and 3. These instructions are:

| OP CODE | MNEMONIC CODE | DESCRIPTION                                                       |

|---------|---------------|-------------------------------------------------------------------|

| 10      | LRL           | Load Arithmetic Register<br>Right Half from Memory Left<br>Half.  |

| 26      | STRL          | Store Arithmetic Register<br>Right Half into Memory Left<br>Half. |

The new instructions provide the following paths from and to the arithmetic register:

| •                                     | 16 - Bits | 16 - Bits |

|---------------------------------------|-----------|-----------|

| Arithmetic<br>Register                |           | _         |

|                                       |           | // .      |

| ·                                     | STRL      | L/        |

| Central Memory<br>or<br>Register File |           |           |

A significant feature of this change is the ability to modify the DAI, DCI, DAO, and DCO fields of the vector parameter file with data from the right half an arithmetic register using the STRL instruction.

Bell Kastner ems

#### **MEMORANDUM**

4 August 1972

TO

Hardware Development System Engineering

System Planning and Applications

COPY TO

Bill Cohagan Gary Cobb

Dave Paterson Charles Stephenson

Sterling Mathis

Joe Watson

Sid Nolte

Wayne Winkelman (4)

FROM

Bill Kastner

SUBJECT

NEW INSTRUCTIONS AND NEW FEATURES OF THE TIMES-FOUR CENTRAL PROCESSOR

New vector instructions for generating and using Boolean vectors have been added to the times-four Central Processor (4XCP), creating the need to re-issue the list of new instructions. This list supersedes the old list of new instructions issued 4 April 1972. In addition to this list of new instructions, all the previous instructions of the times-one CP are implemented on the 4XCP.

Several new features have been added to the 4XCP and are described following the new instructions.

**BILL KASTNER**

Bill Kastner

WDK:jc

Attachment

# Contents

| Page | New Scalar Instructions                                          |

|------|------------------------------------------------------------------|

| 1    | FORK                                                             |

| 1    | JOIN                                                             |

| 2    | PB, Prepare to Branch                                            |

| 4    | LEM, Load Arithmetic Exception Mask and Condition                |

| 6    | LRL, Load Arithmetic Register Right Half from Alpha<br>Left Half |

| 7    | STRL, Store Arithmetic Register Right Half into Alpha Left Half  |

| 8    | SCLK, Store 32-bit Fixed Point Clock                             |

|      | New Vector Instructions                                          |

| 9    | VMAP, Vector Map Singleword                                      |

| 9    | VMAPH, Vector Map Halfword                                       |

| 9    | VMAPD, Vector Map Doubleword                                     |

| 14   | VSELB, Vector Select Singleword Boolean                          |

| 14   | VSELHB, Vector Select Halfword Boolean                           |

| 14   | VSELDB, Vector Select Doubleword Boolean                         |

| 16   | VREPB, Vector Replace Singleword Boolean                         |

| 16   | VREPHB, Vector Replace Halfword, Boolean                         |

| 16   | VREPDB, Vector Replace Doubleword Boolean                        |

| 19   | VMAPB, Vector Map Singleword Boolean                             |

| 19   | VMAPHB, Vector Map Halfword Boolean                              |

| 19   | VMAPDB, Vector Map Doubleword Boolean                            |

| Page | New Vector Instructions                                 |

|------|---------------------------------------------------------|

| 22   | VMAX, Vector Max/Min Fixed Point Singleword             |

| 22   | VMAXH, Vector Max/Min Fixed Point Halfword              |

| 22   | VMAXF, Vector Max/Min Floating Point Singleword         |

| 22   | VMAXFD, Vector Max/Min Floating Point Doubleword        |

| 24   | VCB, Vector Compare Fixed Point Singleword Boolean      |

| 24   | VCHB, Vector Compare Fixed Point Halfword Boolean       |

| 24   | VCFB, Vector Compare Floating Point Singleword Boolean  |

| 24   | VCFDB, Vector Compare Floating Point Doubleword Boolean |

| 26   | VCAB, Vector Compare AND Singleword Boolean             |

| 26   | VCADB, Vector Compare AND Doubleword Boolean            |

| 26   | VCORB, Vector Compare OR Singleword Boolean             |

| 26   | VCORDB, Vector Compare OR Doubleword Boolean            |

|      | New Features                                            |

| 27   | Pipe Disable Bits                                       |

| 27   | Vector Length Field Specification                       |

| 30   | Dual Look-Ahead                                         |

Fork

FORK Mnemonic Code

1 → Fork Indicator

9A Op code

The FORK instruction is an advisory type instruction to the IPU control. Execution of the FORK instruction sets the fork indicator bit within the IPU control and allows subsequent vector or scalar instructions to proceed to execution independently. In the times-four CP, this means that any combination of vector or scalar instructions can be in execution simultaneously in each of the four MBU-AU pairs. Refer to the write-up describing FORK and JOIN control for further details on the effect of this instruction.

A FORK instruction with the fork indicator already "on" results in the equivalent of a JOIN followed by a FORK.

Join

JOIN Mnemonic code

0 → Fork Indicator

9B Op code

The JOIN instruction is an advisory type instruction to the IPU control. Execution of the JOIN instruction resets a control bit which then disallows parallel pipeline processing of subsequent mixtures of vector and scalar instructions. In the times-four CP, this means that only scalars can be in execution at a time or only a singular vector at a time. Combinations of vectors and scalars cannot be in execution simultaneously. Refer to the write-up describing FORK and JOIN control for further details on the effect of this instruction.

PB

Mnemonic code

9E

Op code

The Prepare-to-Branch instruction is an advisory type instruction to the IPU instruction look-ahead hardware. Execution of a PB instruction does not affect the results of a program in any way; its purpose is to decrease the time taken at a branch instruction in fetching the octet of instructions to which the branch is directed.

The PB instruction develops a ß address from its T-, M-, and N-fields in the same way that a standard branch instruction (BCC or BRC) would do if it were placed at the instruction address of the PB instruction. The R-field of the PB instruction should be set to the difference between the instruction address of the PB instruction and the intended branch instruction. This count may not exceed 15 since the R-field is only four bits. Counts of "O" and "1" are not used.

The internal IPU hardware saves both the  $\beta$  address developed by the PB instruction and the length count specified by the R-field. The length count is decremented by one as each new instruction is entered into the instruction register (IR). At the octet boundary where the look-ahead would normally request the next octet past the octet containing the branch, it recalls the  $\beta$  address saved by the PB instruction and requests it instead of the normal look-ahead octet. In this manner the instruction at the branch address of the target branch instruction will be available for immediate processing following the execution of the target branch instruction.

Should the target branch fail to take the branch, the hardware will realign itself to take the downstream instructions. This is done by

rerequesting the branch instruction's octet if necessary, plus the next octet of look-ahead instructions beyond the branch octet.

Here is an example of PB instruction usage. In this example the R-field is "7," designating seven instruction locations from the PB to the BLB instruction. The branch address developed by the PB is indirect to the PB instruction address, plus eight (Program counter + 8). At this indirect address we find the address of the COSINE routine. The BLB instruction also uses this same indirect address but refers to it via an indirect program counter address plus one. By using the PB instruction in this manner, the first instruction of the COSINE routine will be directly behind the BLB instruction in the IPU pipeline at the completion of BLB execution.

| PB       | 7, 0 \$ + 8  |

|----------|--------------|

| <u>.</u> |              |

| -        | ٠            |

| -        |              |

| -        |              |

| BLB      | B1, @ \$ + 1 |

| IND      | cos          |

## Load Arithmetic Exception Mask and Condition Registers

LEM

Mnemonic code

$(\alpha)_{0-7} \rightarrow AC$ , AM

11

Op code

Loads bits 0 through 3 of the contents of location  $\alpha$  into the fourbit arithmetic exception condition code register and loads bits 4 through 7 of the contents of location  $\alpha$  into the four-bit arithmetic exception mask register.

Bits 0 through 3 load the arithmetic exception condition code register as follows:

Bit

- O Divide check

- 1 Fixed point overflow

- 2 Floating point overflow

- 3 Floating point underflow

Bits 4 through 7 load the arithmetic exception mask as follows:

Bit

- 4 Divide check

- 5 Fixed point overflow

- 6 Floating point overflow

- 7 Floating point underflow

Result Code

Not set.

Programming Notes

An interrupt signal from the CP to the PPU is activated if an arithmetic exception is detected and if the mask bit corresponding to that arithmetic exception has been set to a "one." An interrupt is not possible for that arithmetic exception if the mask bit is set to "zero."

Alteration of the AE condition register and AE mask register by a LEM instruction will cause an arithmetic exception program interruption if the corresponding bits of the AE condition register and the AE mask register are both "one" after the LEM instruction has passed through the CP pipeline. This implies that a program interruption will occur after completion of a LEM instruction if any of the following pairs of bits from the contents of location  $\alpha$  are both "one":

- (0, 4)

- (1, 5)

- (2, 6)

- (3, 7)

This instruction is paired with the BLB and BLX instructions in that the bit positions (bits 0 through 7) agree with the position of the AE condition and AE mask bits stored as a result of a previous BLB or BLX instruction.

| Load Arithmetic Register Right    | LRL | Mnemonic code |

|-----------------------------------|-----|---------------|

| Halfword From Alpha Left Halfword | 10  | Op code       |

| $(\alpha_h) \rightarrow AR_{rh}$  |     |               |

A halfword operand from memory is entered into the right half of arithmetic register AR. The left half or register AR remains unchanged. The operand selected is from the left half of a central memory or register whole word when not indexed. If indexed, an even index value selects words from the left half of a central memory or register whole word. An odd index value addresses the right halfword.

Result Code

Set arithmetically.

| Store Arithmetic Register Right    | STRL | Mnemonic code |

|------------------------------------|------|---------------|

| Halfword Into Alpha Left Halfword  | 26   | Op code       |

| $(AR_{nh}) \rightarrow \alpha_{h}$ |      |               |

The right half of arithmetic register AR is stored into the left half of a singleword location when not indexed. If indexed, an even index value selects the left half of a singleword location for storage. An odd index value addresses the right halfword.

Result Code

Set arithmetically.

Store Clock

SCLK

Mnemonic code

CLOCK  $\rightarrow \alpha$

ΑE

Op code

The current value of the 32-bit, fixed-point CP clock is stored into singleword location  $\alpha$ . This clock is incremented by "one" every CP clock pulse. It cycles modulo  $2^{32}$  approximately once every four minutes (based on a 60 ns clock rate).

Result Code

Set arithmetically.

#### New Vector Instructions

| Mnemonic<br>Code | Instruction            | Operation<br><u>Code</u> |

|------------------|------------------------|--------------------------|

| VMAP ,           | Vector Map Singlewords | F8                       |

| VMAPH            | Vector Map Halfwords   | F9                       |

| <b>VM</b> APD    | Vector Map Doublewords | FB                       |

Vector-Map-on-Equal,  $SV_{msb}$  option bit = 0.

A Vector-Map-on-Equal instruction accepts as inputs a contiguous list of indices from vector  $\vec{A}$  and a set of source mapping elements from vector  $\vec{B}$ . The elements of vector  $\vec{B}$  that are mapped are those elements for which the index location in  $\vec{B}$  corresponds to the index value given by the elements of vector  $\vec{A}$ . Elements from source mapping vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector. Elements of the  $\vec{C}$  output vector that are replaced are those elements for which the index location in  $\vec{C}$  corresponds to the index value given by the elements of vector  $\vec{A}$ . Elements of vector  $\vec{B}$  do not replace elements of vector  $\vec{C}$  for those index locations in  $\vec{C}$  that are not represented in the index list given by vector  $\vec{A}$ .

This instruction differs from the Vector Replace instruction in the manner in which elements of vector  $\vec{B}$  are used. Vector Replace uses consecutive elements of vector  $\vec{B}$ , whereas Vector Map uses only those elements of Vector  $\vec{B}$  that are mapped by the specification of vector  $\vec{A}$ .

#### **Programming Notes**

For self-loops:

1A) The length specification of the self-loop (L-field) for a Vector-Map-on-Equal instruction should be set equal to the number of elements of a self-loop of the  $\vec{C}$  vector. Or, if the  $\vec{B}$  vector is the greater in length, then set the L-field equal to the number of elements of vector  $\vec{B}$ .

- IB) It is possible to shorten the vector operation and still obtain the same result vector  $\vec{C}$  by setting the self-loop length equal to one plus the value of the last index in vector  $\vec{A}$ .

- 2A) If the vector length is specified according to 1A above, then an index boundary limit equal to the largest positive number (7FFF hex) must be placed in the data location following the last index value of vector  $\vec{A}$ .

- 2B) If the vector length is specified according to 1B above, then the index boundary limit is not necessary.

- 3) Each index value given by vector  $\vec{A}$  is a positive, fixed-point halfword. Vector  $\vec{A}$  should be a contiguous list of monotone increasing halfwords.

- 4) An index value of zero maps the first element of vector  $\vec{B}$  into the first element of vector  $\vec{C}$ .

Example 1: A singleword Vector-Map-on-Equal ( $SV_{msb}$ =0) instruction using a self-loop of length 8.

|                                 |                        |                                              | en e    |

|---------------------------------|------------------------|----------------------------------------------|---------------------------------------------|

|                                 |                        | -11-                                         |                                             |

| Singleword<br>Index<br>Vector A | Singleword<br>Vector B | Singleword<br>Vector C Before<br>Replacement | Singleword<br>Vector C After<br>Replacement |

| 2, 3                            | -14                    | 16                                           | 16                                          |

| <b>5,</b> 6                     | -70                    | . 82                                         | 82                                          |

| 7FFF, -                         | -25                    | 27                                           | <b>-25</b> .                                |

|                                 | -34                    | 36                                           | -34                                         |

|                                 | -69                    | <b>71</b>                                    | 71                                          |

|                                 | -30                    | 32                                           | -30                                         |

|                                 | - 6                    | 8                                            | <b>-</b> 6                                  |

|                                 | -12                    | 14                                           | 14                                          |

Vector-Map-on-Not-Equal,  $SV_{msb}$  option bit = 1

A Vector-Map-on-Not-Equal instruction accepts as inputs a contiguous list of indices from vector  $\vec{A}$  and a set of source mapping elements from vector  $\vec{B}$ . The elements of vector  $\vec{B}$  that are mapped are those elements for which the index location in  $\vec{B}$  is not represented in the index list given by vector  $\vec{A}$ . Elements from source mapping vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector. Elements of the  $\vec{C}$  output vector that are replaced are those elements for which the index location in  $\vec{C}$  is not represented in the index list given by vector  $\vec{A}$ . Elements of vector  $\vec{B}$  do not replace elements of vector  $\vec{C}$  for those index locations that correspond to the index value given by the elements of vector  $\vec{A}$ .

# Programming Notes

# For self-loops:

- (1) The length specification of the self-loop (L-field) for a Vector-Map-on-Not-Equal instruction should be set equal to the number of elements of a self-loop of the  $\vec{C}$  vector. Or, if the  $\vec{B}$  vector is the greater in length, then set the L-field equal to the number of elements of vector  $\vec{B}$ .

- (2) An index boundary limit equal to the largest positive number (7FFF hex) must be placed in the data location following the last index value of vector  $\vec{A}$ .

- (3) Each index value given by vector A is a positive, fixed-point halfword. Vector A should be a contiguous list of monotone increasing halfwords.

(4) An index list beginning with a value of "one" maps the first elements of vector  $\vec{B}$  into  $\vec{C}$  but not the second element (element  $C_0$  is replaced with  $B_0$  but not  $C_1$  by  $B_1$ ).

Example 2: A singleword Vector-Map-on-Not-Equal ( $SV_{msb}$ =1) instruction using a self-loop of length 8.

| Singleword<br>Index<br>Vector Ā | Singlewo <u>r</u> d<br>Vector B | Singl <u>ew</u> ord<br>Vector C Before<br>Replacement | Singleword<br>Vector C After<br>Replacement |

|---------------------------------|---------------------------------|-------------------------------------------------------|---------------------------------------------|

| 2, 3                            | -14                             | 16                                                    | -14                                         |

| 5, 6                            | -70                             | 82                                                    | <b>-70</b>                                  |

| 7FFF, -                         | -25                             | 27                                                    | 27                                          |

|                                 | -34                             | 36                                                    | 36                                          |

|                                 | -69                             | 71                                                    | -69                                         |

|                                 | -30                             | 32                                                    | 32                                          |

|                                 | - 6                             | 8                                                     | 8                                           |

|                                 | -12                             | 14                                                    | -12                                         |

| Mnemonic<br>Code | Instruction                      | Operation<br><u>Code</u> |

|------------------|----------------------------------|--------------------------|

| VSELB            | Vector Select Singleword Boolean | B4                       |

| VSELHB           | Vector Select Halfword Boolean   | B5                       |

| VSELDB           | Vector Select Doubleword Boolean | B7                       |

Vector-Select-on-One,  $SV_{msb}$  option bit = 0

A Vector-Select-on-One instruction generates an output vector  $\vec{C}$  composed of elements from vector  $\vec{B}$ . The elements selected from vector  $\vec{B}$  are those for which the location in vector  $\vec{B}$  corresponds to the location of nonzero elements of vector  $\vec{A}$ . Selected elements are stored into contiguous locations of vector  $\vec{C}$ .

$\mbox{Vector-Select-on-Zero, SV}_{\mbox{msb}} \mbox{ option bit = 1}$

A Vector-Select-on-Zero instruction generates an output vector  $\vec{C}$  composed of elements from vector  $\vec{B}$ . The elements selected from vector  $\vec{B}$  are those for which the location in vector  $\vec{B}$  corresponds to the location of zero elements of vector  $\vec{A}$ . Selected elements are stored into contiguous locations of vector  $\vec{C}$ .

# Programming Notes

# For self-loops:

- (1) The length specification of the self-loop (L-field) for a Vector-Select-Boolean instruction is set equal to the number of elements of vector  $\vec{A}$  or  $\vec{B}$ .

- (2) Each element of vector  $\overrightarrow{A}$  is a halfword that assumes one of two Boolean values. "Zero" is assumed if the value is zero, and "one" is assumed if the value is nonzero.

Example 1: A singleword Vector-Select-on-One (SV $_{\rm msb}$ =0) instruction using a self-loop of length 8.

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B | Singleword<br>Selected<br>Vector C |

|---------------------------------|------------------------|------------------------------------|

| 0, 0                            | +16                    | -54                                |

| 1, 1                            | +82                    | <b>-</b> 75                        |

| 0, 1                            | <b>-</b> 54            | -64                                |

| 1, 0                            | <b>-</b> 75            | -15 '                              |

|                                 | +71                    |                                    |

|                                 | -64                    |                                    |

|                                 | -15                    | •                                  |

|                                 | +14                    |                                    |

Example 2: A singleword Vector-Select-on-Zero (SV $_{\rm msb}$ =1) instruction using a self-loop of length 8.

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B | Singleword<br>Selected<br>Vector C |

|---------------------------------|------------------------|------------------------------------|

| 0, 0                            | +16                    | +16                                |

| 1, 1                            | +82                    | +82                                |

| 0, 1                            | -54                    | <sub>#</sub> +71                   |

| 1, 0                            | <b>-7</b> 5            | · +14                              |

|                                 | +71                    |                                    |

|                                 | -64                    |                                    |

|                                 | -15                    |                                    |

|                                 | +14                    |                                    |

| Mnemonic<br>Code | Instruction                       | Operation<br><u>Code</u> |

|------------------|-----------------------------------|--------------------------|

| VREPB            | Vector Replace Singleword Boolean | ВС                       |

| VREPHB           | Vector Replace Halfword Boolean   | BD                       |

| VREPDB           | Vector Replace Doubleword Boolean | BF                       |

Vector-Replace-on-One, SV<sub>msb</sub> option bit = 0

A Vector-Replace-on-One instruction accepts as inputs a continuous list of replacement elements from vector  $\vec{B}$  and a continuous list of Boolean elements from vector  $\vec{A}$ . Elements from vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector. Elements of the  $\vec{C}$  output vector that are replaced with elements of vector  $\vec{B}$  are those elements for which the location in the  $\vec{C}$  output vector corresponds to the location of nonzero elements of vector  $\vec{A}$ . Elements of the  $\vec{C}$  output vector remain unchanged in those locations for which the corresponding location in vector  $\vec{A}$  is zero.

Vector-Replace-on-Zero,  $SV_{msb}$  option bit = 1

A Vector-Replace-on-Zero instruction accepts as inputs a continuous list of replacement elements from vector  $\vec{B}$  and a continuous list of Boolean elements from vector  $\vec{A}$ . Elements from vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector. Elements of the  $\vec{C}$  output vector that are replaced with elements of vector  $\vec{B}$  are those elements for which the location in the  $\vec{C}$  output vector corresponds to the location of zero elements of vector  $\vec{A}$ . Elements of the  $\vec{C}$  output vector remain unchanged in those locations for which the corresponding location in vector  $\vec{A}$  is nonzero.

## Programming Notes

# For self-loops:

- (1) The length specification of the self-loop (L-field) for a Vector-Replace-Boolean instruction is set equal to the number of elements of vector  $\vec{A}$  or  $\vec{C}$ .

- (2) Each element of vector  $\overrightarrow{A}$  is a halfword that assumes one of two Boolean values. "Zero" is assumed if the value is zero, and "one" is assumed if the value is nonzero.

Example 1: A singleword Vector-Replace-on-One ( $SV_{msb}=0$ ) instruction using a self-loop of length 8.

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B                | Singleword<br>Vector C Before<br>Replacement | Singleword<br>Vector C After<br>Replacement |

|---------------------------------|---------------------------------------|----------------------------------------------|---------------------------------------------|

| 0, 0                            | -54                                   | 16                                           | 16                                          |

| 1, 1.                           | -72                                   | 82                                           | 82                                          |

| 0, 1                            | 64                                    | 27                                           | -54                                         |

| 1, 0                            | -15                                   | 36                                           | <b>-72</b>                                  |

|                                 | e e e e e e e e e e e e e e e e e e e | 71                                           | 71                                          |

|                                 |                                       | 32                                           | -64                                         |

|                                 |                                       | 8                                            | <b>-</b> 15                                 |

|                                 | •                                     | 14                                           | 14                                          |

Example 2: A singleword Vector Replace on Zero ( $SV_{msb}=1$ ) instruction using a self-loop length of 8. (Following page.)

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B | Singleword<br>Vector C Before<br>Replacement | Singleword<br>Vector C After<br>Replacement |

|---------------------------------|------------------------|----------------------------------------------|---------------------------------------------|

| 0, 0                            | -54                    | 16                                           | -54                                         |

| 1, 1                            | -72                    | <b>. 82</b> ,                                | -72                                         |

| 0, 1                            | -64                    | 27                                           | 27                                          |

| 1, 0                            | -15                    | 36                                           | . 36                                        |

|                                 | •                      | 71                                           | -64                                         |

|                                 |                        | 32                                           | 32                                          |

|                                 |                        | 8                                            | 8 .                                         |

| •                               |                        | 14                                           | -15                                         |

| Mnemonic<br>Code | Instruction                   | Operation<br><u>Code</u> |

|------------------|-------------------------------|--------------------------|

| VMAPB            | Vector Map Singleword Boolean | FC                       |

| VMAPHB           | Vector Map Halfword Boolean   | FD                       |

| VMAPDB           | Vector Map Doubleword Boolean | FF                       |

Vector-Map-on-One,  $SV_{msb}$  option bit = 0

A Vector-Map-on-One instruction accepts as inputs a continuous list of Boolean elements from vector  $\vec{A}$  and a set of source mapping elements from vector  $\vec{B}$ . The elements of vector  $\vec{B}$  that are mapped are those elements for which the location in  $\vec{B}$  corresponds to the location of nonzero elements of vector  $\vec{A}$ . Elements from source mapping vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector.

Elements of the  $\vec{C}$  output vector that are replaced are those elements for which the location in  $\vec{C}$  corresponds to the location of nonzero elements of vector  $\vec{A}$ . Elements of the  $\vec{C}$  output vector remain unchanged in those locations for which the corresponding location in vector  $\vec{A}$  is zero.

Vector-Map-on-Zero, SV<sub>msb</sub> option bit = 1

A Vector-Map-on-Zero instruction accepts as inputs a continuous list of Boolean elements from vector  $\vec{A}$  and a set of source mapping elements from vector  $\vec{B}$ . The elements of vector  $\vec{B}$  that are mapped are those elements for which the location in  $\vec{B}$  corresponds to the location of zero elements of vector  $\vec{A}$ . Elements from source mapping vector  $\vec{B}$  replace previously existing elements in a central memory region defined as the  $\vec{C}$  output vector.

Elements of the  $\vec{C}$  output vector that are replaced are those elements for which the location in  $\vec{C}$  corresponds to the location of zero elements of vector  $\vec{A}$ . Elements of the  $\vec{C}$  output vector remain unchanged in those locations for which the corresponding location in vector  $\vec{A}$  is nonzero.

# Programming Notes

# For self-loops:

- (1) The length specification of the self-loop (L-field) for a Vector-Map-Boolean instruction is set equal to the number of elements of vector  $\vec{A}$ . Vectors  $\vec{B}$  and  $\vec{C}$  should be of this same length.

- (2) Each element of vector  $\vec{A}$  is a halfword that assumes one of two Boolean values. "Zero" is assumed if the value is zero, and "one" is assumed if the value is nonzero.

Example 1: A singleword Vector-Map-on-One ( $SV_{msb}$ =0) instruction using a self-loop of length 8.

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B | Singleword<br>Vector C Before<br>Mapping | Singleword<br>Vector C After<br>Mapping |

|---------------------------------|------------------------|------------------------------------------|-----------------------------------------|

| 0, 0                            | -54                    | 16                                       | 16                                      |

| 1, 1                            | -72                    | 82                                       | 82                                      |

| 0, 1                            | -64                    | 27                                       | -64                                     |

| 1, 0                            | -15                    | 36                                       | -15                                     |

|                                 | · -29                  | 71                                       | 71                                      |

|                                 | - 5                    | 32                                       | - 5                                     |

|                                 |                        |                                          | 47                                      |

|                                 | - 2                    | 14                                       | 14                                      |

Example 2: A singleword Vector-Map-on-Zero ( $SV_{msb}$ =1) instruction using a self-loop of length 8.

| Halfword<br>Boolean<br>Vector A | Singleword<br>Vector B | Singleword<br>Vector C Before<br>Mapping | Singleword<br>Vector C After<br>Mapping |

|---------------------------------|------------------------|------------------------------------------|-----------------------------------------|

| 0, 0                            | -54                    | 16                                       | -54                                     |

| . 1, 1                          | <b>-72</b>             | 82                                       | <b>-72</b>                              |

| . 0, 1                          | -64                    | <b>27</b> <sub>5</sub>                   | 27                                      |

| 1, 0                            | -15                    | 36                                       | 36 ,                                    |

|                                 | -29                    | <b>71</b> ·                              | -29                                     |

|                                 | - 5                    | 32                                       | 32                                      |

|                                 | -47                    | 8                                        | 8                                       |

|                                 | - 2                    | 14                                       | - 2                                     |

| Mnemonic<br>Code | Instruction                              | Operation<br>Code |

|------------------|------------------------------------------|-------------------|

| VMAX             | Vector Max/Min Fixed-Point Singleword    | F4                |

| VMAXH            | Vector Max/Min Fixed-Point Halfword      | F5                |

| VMAXF            | Vector Max/Min Floating-Point Singleword | F6 <sup>°</sup>   |

| VMAXD            | Vector Max/Min Floating-Point Doubleword | F7                |

Vector Maximum,  $SV_{msb}$  option bit = 0

A Vector-Maximum instruction forms an output vector  $\vec{C}$  composed of the larger of the elements from either vector  $\vec{A}$  or vector  $\vec{B}$ . That is, element  $c_i$  assumes the larger arithmetic value of the elements  $a_i$  or  $b_i$ .

$$c_i = MAX(a_i, b_i)$$

Vector Minimum,  $SV_{msb}$  option bit = 1

A Vector-Minimum instruction forms an output vector  $\vec{c}$  composed of the smaller of the elements from either vector  $\vec{A}$  or vector  $\vec{B}$ . That is, element  $c_i$  assumes the smaller arithmetic value of the elements  $a_i$  or  $b_i$ .

$$c_i = MIN(a_i, b_i)$$

Example 1: A Fixed-Point, Singleword-Vector-Maximum instruction with a self-loop of length 8.

| Vector $\vec{A}$ Vector $\vec{B}$ |    | <u>V</u> | ector C |

|-----------------------------------|----|----------|---------|

| 40                                | 72 |          | 72      |

| 75                                |    | •        | 75      |

| -11                               | 45 |          | 45      |

| <u>Vector À</u> | Vector B | Vector C        |

|-----------------|----------|-----------------|

| 56              | 56       | 56              |

| 32              | - 9      | 32              |

| 16              | , 64     | 64 <sub>.</sub> |

| 97              | 28       | 97 <sup>-</sup> |

| 21              | 20       | 21              |

Example 2: A Fixed-Point, Singleword-Vector-Minimum instruction with a self-loop length of 8.

| <u>Vector À</u> | Vector B    | Vector C |

|-----------------|-------------|----------|

| 40              | 72          | 40       |

| 75              | 20          | 20       |

| -11             | 45 ·        | -11      |

| 56              | 56          | 56       |

| 32              | - 9         | - 9      |

| 16              | 64          | 16       |

| 97              | <b>.</b> 28 | 28       |

| 21              | 20          | 20       |

| Mnemonic<br><u>Code</u> | Instruction                                      | Operation<br>Code |

|-------------------------|--------------------------------------------------|-------------------|

| VCB                     | Vector Compare Fixed-Point Singleword Boolean    | F0                |

| VCHB                    | Vector Compare Fixed-Point Halfword Boolean      | F1                |

| VCFB                    | Vector Compare Floating-Point Singleword Boolean | F2                |

| VCFDB                   | Vector Compare Floating-Point Doubleword Boolean | F3                |

All ALCT options of the arithmetic compare instructions on page 3-200 can be used to generate Boolean vector outputs. A Boolean vector is a vector containing elements having a value of either "zero" or "one." For the arithmetic compare instructions, a "one" is placed in the  $\vec{C}$  output vector in each halfword location corresponding to the location of true comparisons of elements in the input vectors  $\vec{A}$  and  $\vec{B}$ . A "zero" is placed in the halfword location corresponding to the location of false comparisons of the  $\vec{A}$  and  $\vec{B}$  input vectors.

No item count is stored for any of the Boolean vector compare instructions.

Example 1: A Vector Compare Fixed-Point Singleword Boolean instruction with ALCT comparison option set to search for "greater than or equal to."

| Singleword<br>Vector A | Singleword<br>Vector B | Halfword<br>Vector C |

|------------------------|------------------------|----------------------|

| 40                     | 72                     | 0                    |

| 75                     | 20                     | 1                    |

| -11                    | 45                     | 0                    |

| 56                     | 56                     | 1                    |

| 32                     | . <b>- 9</b>           |                      |

| 16                     | 64                     | 0                    |

| Singleword<br>Vector A | Singlewo <u>r</u> d<br><u>Vector B</u> | Halfword<br>Vector C |

|------------------------|----------------------------------------|----------------------|

| 97                     | 28                                     | 1                    |

| 21                     | 20                                     | 1                    |

| Mnemonic<br>Code | Instruction                            | Operation<br><u>Code</u> |

|------------------|----------------------------------------|--------------------------|

| VCAB             | Vector Compare AND, Singleword Boolean | EA                       |

| VCADB            | Vector Compare AND, Doubleword Boolean | EB                       |

| VCORB            | Vector Compare OR, Singleword Boolean  | EE ·                     |

| VCORDB           | Vector Compare OR, Doubleword Boolean  | EF                       |

All ALCT options of the logical compare instructions on page 3-203 can be used to generate Boolean vector outputs. A Boolean vector is a vector containing elements having a value of either "zero" or "one." For the logical compare instructions, a "one" is placed in the  $\vec{C}$  output vector in each halfword location corresponding to the location of true comparisons of elements in the input vectors  $\vec{A}$  and  $\vec{B}$ . A "zero" is placed in the halfword location corresponding to the location of false comparisons of the  $\vec{A}$  and  $\vec{B}$  input vectors.

No item count is stored for any of the Boolean vector compare instructions.

Example 1: A Vector Compare OR Singleword Boolean instruction with ALCT comparison option set to search for "mixed zeros and ones."

| Singleword<br>Vector A | Singleword<br>Vector B | Halfword<br><u>Vector C</u> |

|------------------------|------------------------|-----------------------------|

| 005A                   | 0000                   | 01                          |

| 0000                   | 0000                   | 00                          |

| 0048                   | . 0024                 | 01                          |

| 5A5A                   | A5A5                   | 00                          |

#### New Features

### Pipe Disable Bits

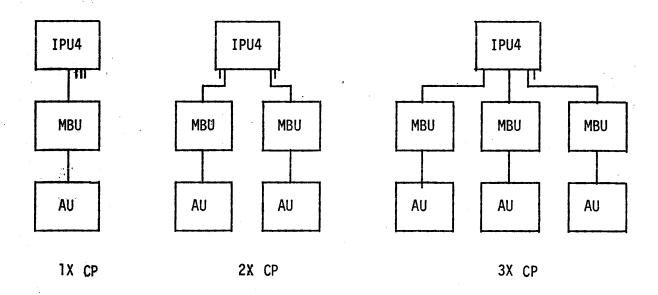

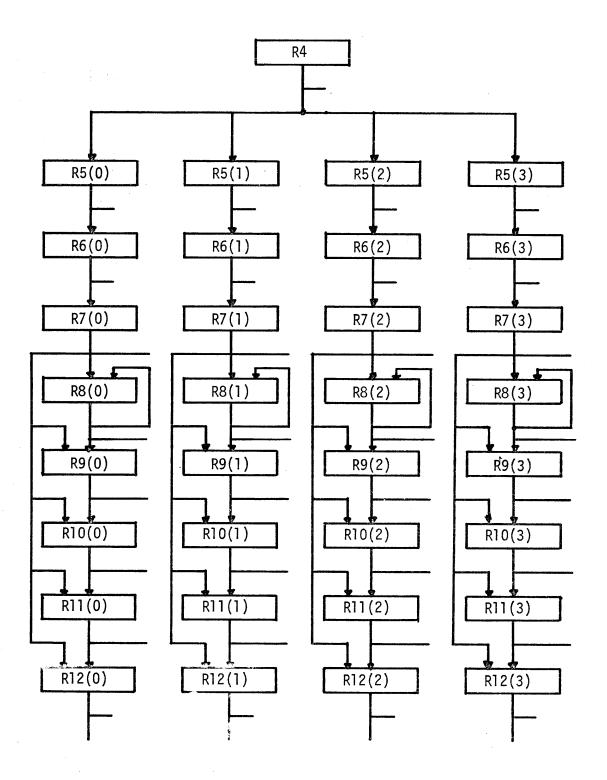

The times-four CP is provided with four bits in the Program Status Doubleword (PSDW) for individually disabling any combination of the four parallel pipelines. Bit positions 12, 13, 14, and 15 of the first word of the PSDW disables pipes 0, 1, 2, and 3, respectively, when the bits are "one." A "zero" in these bit positions enables the pipes if they exist in the system. The Program Status Doubleword information is formatted as shown following. A description of the various fields is given in the 1X CP Hardware Specifications on pages 3-19 through 3-27.

|                  | 0          |            | 1,2             | 16 | 2   | 0 2 | 4 2 | 28 |    |

|------------------|------------|------------|-----------------|----|-----|-----|-----|----|----|

| α                | N          | OT USED    | PIPE<br>DISABLE |    | СМИ | BSR | СС  | RC |    |

|                  | 0 4        | 8          |                 |    |     | •   |     | 3  | 1. |

| α+1 <sub>.</sub> | AE<br>COND | AE<br>MASK |                 |    | Р   | C . |     |    |    |

The pipe disable bits are primarily intended for use by maintenance and diagnostic testing. As an example of a diagnostic application, it is possible to disable all pipes, except pipe 0, and run an AU or MBU diagnostics program. Then, pipes 0, 2, and 3 can be disabled and pipe 1 enabled and the AU or MBU tests repeated. In this manner, all four pipes can be tested, one at a time. If a particular pipe fails the test, then the operating system can be informed of the malfunctioning pipe. The operating system can be instructed to turn off the pipe in which the failure was found by setting the proper disable bit in the PSDW of subsequent jobs as they are assigned to the CP. The CP can continue processing

jobs in this degraded mode until the failure can be corrected. Also, if the complete system files and status could be saved at periodic check-points following successful diagnostic tests, then it would be possible to rerun all jobs executed since the last good checkpoint prior to the detection of a failure by the diagnostic test program.

Vector Length Field Specification

This variation in hardware design existing between the times-one IPU and the times-four IPU has to do with a value of zero in the NI- or NØ-fields of the vector parameter file. In the times-one IPU, if NI is zero, the self-loop routine is executed once, there is no inner loop, and the outer loop count (NØ) is not examined. Also, if NØ is zero, the specified vector operation is executed NI times; and, then, the operation is terminated. This is no longer true in the 4X CP.

In the 4X CP, the vector operation becomes a NO OPERATION if <u>any</u> of the L-, NI-, or NØ-fields are zero. In fact, the MBU will not even be initialized with data from the vector parameter file. The IPU4 detects the zero field condition and terminates the vector before it has had a chance to start initialization.

#### Dual Look-Ahead

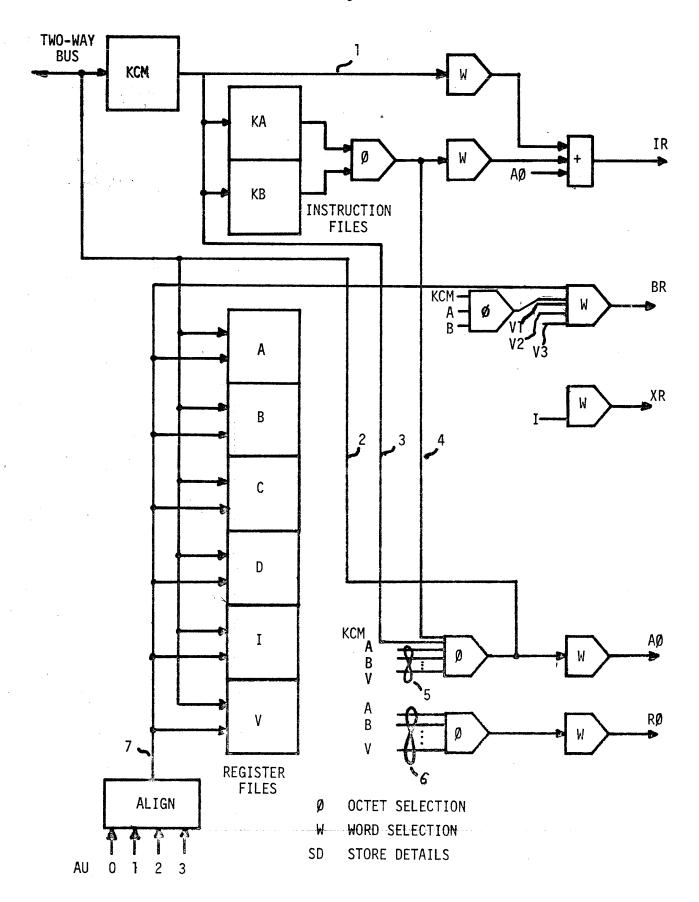

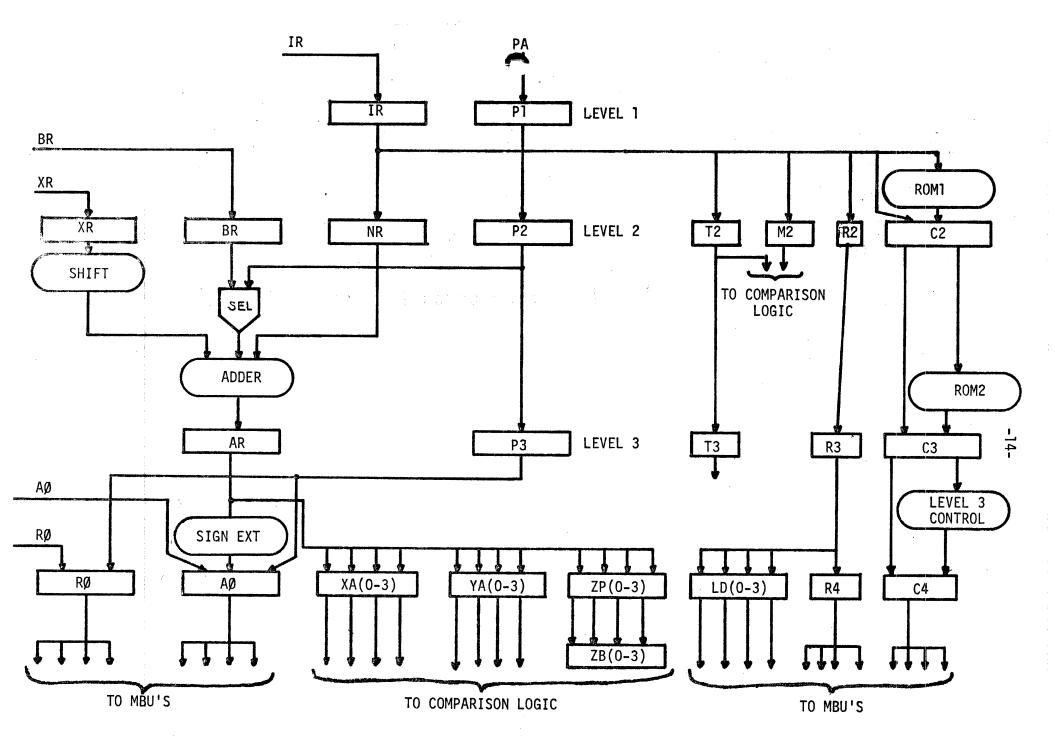

A dual look-ahead procedure is implemented in the 4X CP hardware for decreasing the wait time for acquiring instructions at the branch address of a conditional branch instruction. In this method, two instruction buffers (KA and KB) hold instructions to be executed. Each buffer contains eight instructions. These buffers operate in a toggling fashion such that one contains the octet of instructions from which the current instruction is being read, while the other octet contains the look-ahead octet (eight words) of instructions. These roles are reversed when the address of the current instruction moves across the octet boundary into the octet of instructions that were fetched by the look-ahead hardware.

A branch instruction breaks the normal flow of instructions through the instruction processing pipeline when the branch is taken. A delay in addition to the wait time for acquiring instructions along the branch path is due to the time taken in waiting for the branch condition to be determined. For example, a Branch-on-Result-Code instruction must wait for the result code to be set by the last result code modifying instruction prior to the branch.

The dual look-ahead hardware prefetches the address of the branch instruction before it is known whether the branch will be taken. However, the request for the branch address is made only if the conditional branch instruction is located in one of the first four words of an octet.

Imposing this restriction on the location of the branch instruction is for the purpose of instruction recovery in cases where the branch is not taken. In cases where the branch fails, there will be four instruc-

tions remaining in the current instruction buffer which provide work for the instruction preprocessor that can be overlapped with the request to recover instructions along the nonbranch path.

In cases where the branch is taken, the instructions along the branch path will be available for execution earlier than if the dual look-ahead hardware were not used. This is because the time required to fetch the instructions at the branch address can be overlapped with the determination of the branch condition.

Bill Kastner

T0:

CP Checkout

Hardware Development Software Development

SDD

System Engineering

System Test

FROM:

₩Bill Kastner

CATEGORY:

CT

SUBJECT:

CP Instruction Clarifications and Instruction Timing Changes

The clarifications and changes of this bulletin are to be made in the Volume titled "The ASC System Central Processor - May 1971". The clarifications involve (1) the limits that must be observed when using large numbers in the BCLE and BCG instructions and (2) the scale factor size when using the conversion instructions. The changes are the latest figures for divide times in the Arithmetic Unit.

- A. The BCG and BCLE instructions (operation codes 84, 85, 86, and 87) require clarification concerning the range of numbers over which these instructions are effective. Programming Notes are being added to these four instructions as follows:

- 1) BCLE, Op. code 84 and BCG, Op code 85

Programming Notes: This instruction is effective for numbers within the range  $|(AR) + (AT) - (AT+1)| \le 2^{31}-1$ .

Also, neither indexed nor indirect branch addressing is possible for BCLE or BCG instructions.

2) BCLE, Op. code 86 and BCG, Op code 87

Programming Notes: This instruction is effective for numbers within the range  $|(XR) + (AT) - (AT+1)| \le 2^{31}-1$ .