## **Data Transmission Circuits** Communications Controllers

**Mixed-Signal Products**

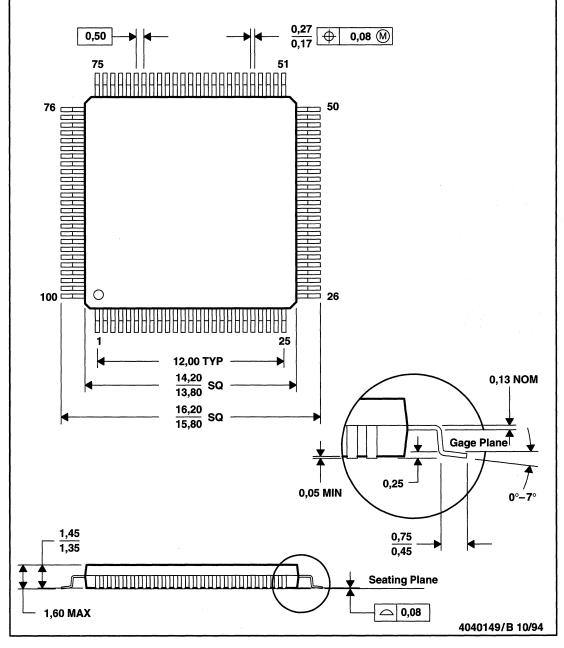

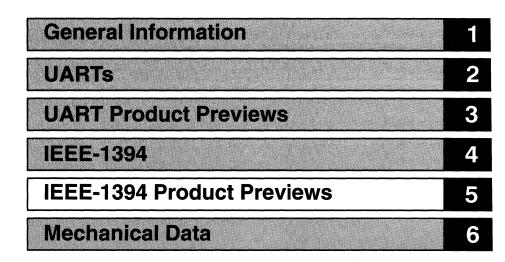

| General Information        | 1 |

|----------------------------|---|

| UARTs                      | 2 |

| UART Product Previews      | 3 |

| IEEE-1394                  | 4 |

| IEEE-1394 Product Previews | 5 |

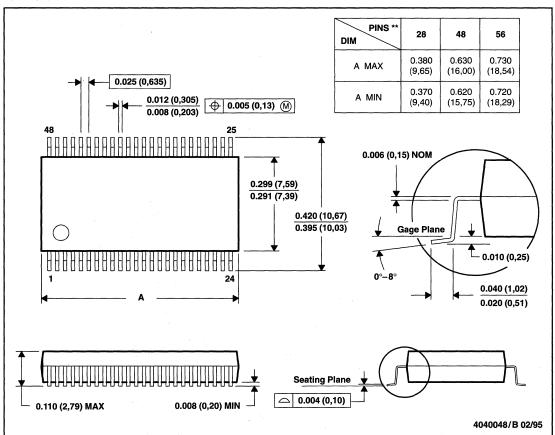

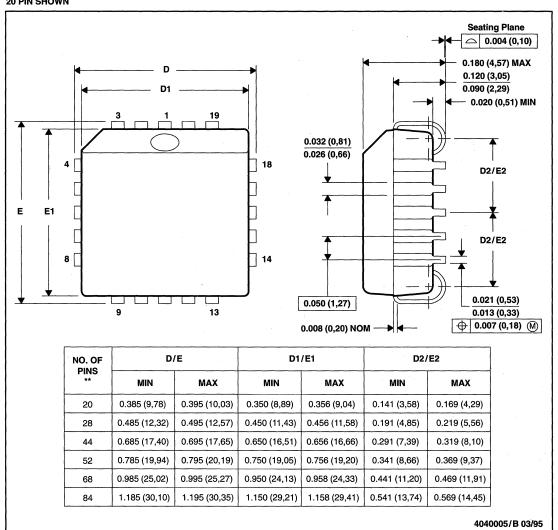

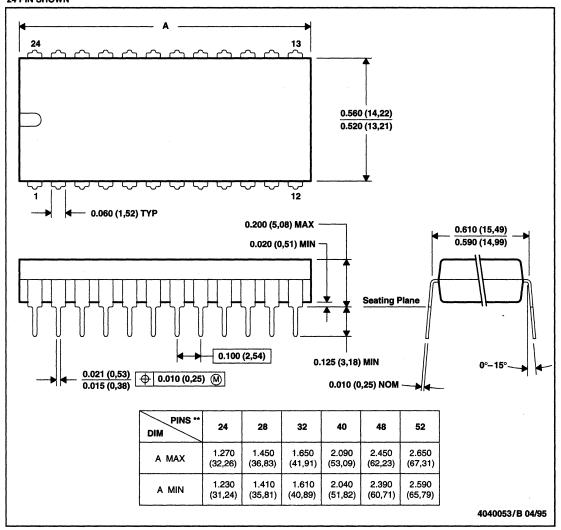

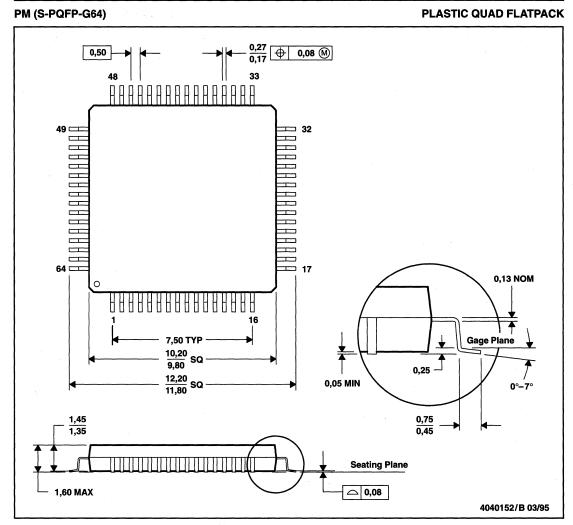

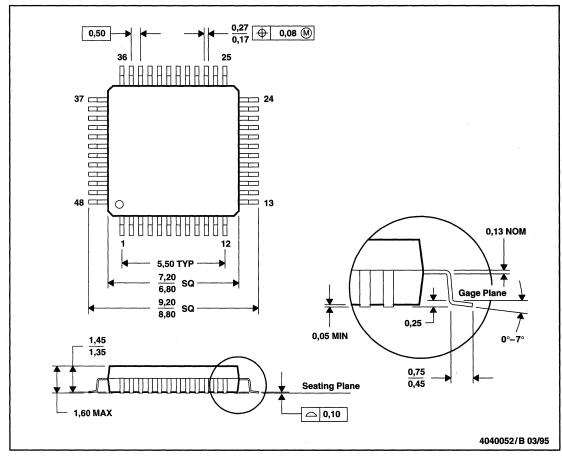

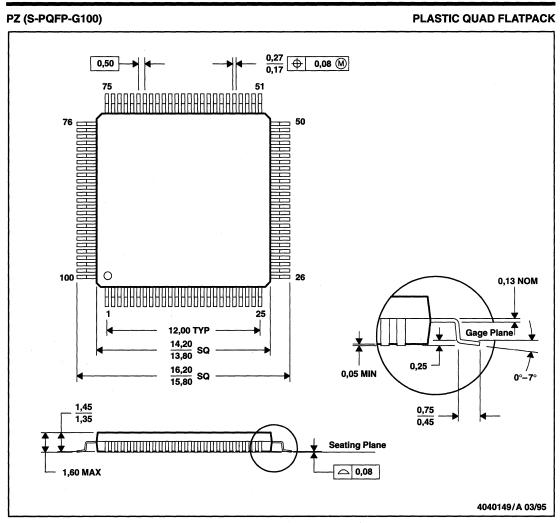

| Mechanical Data            | 6 |

# Data Transmission Circuits Data Book

Volume 2

## **Communications Controllers**

#### **IMPORTANT NOTICE**

Texas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Certain applications using semiconductor products may involve potential risks of death, personal injury, or severe property or environmental damage ("Critical Applications").

TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TI products in such applications requires the written approval of an appropriate TI officer. Questions concerning potential risk applications should be directed to TI through a local SC sales office.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1996, Texas Instruments Incorporated

Printed in U.S.A. by Custom Printing Company Owensville, Missouri

## INTRODUCTION

In the 1996 *Data Transmission Circuits Data Book, Volume 2*, the Mixed-Signal Products Division of Texas Instruments (TI) presents technical information on various products for electronic media and electronic devices.

The TI data transmission circuits represent technologies from classic bipolar through Advanced Low-Power Schottky (ALS), IMPACT<sup>™</sup>, LinBiCMOS<sup>™</sup>, CMOS, and BiMOS processes. The ALS and IMPACT oxide-isolated technologies provide the data transmission family with improved speed-power characteristics.

This data book provides information on the following types of products:

- UARTs

- Plug-and-play compatible devices

- Infrared serial data inputs and outputs

- IEEE 1394-1995

Among the new products offered by TI within the 1996 Data Transmission Circuits Data Book, Volume 2 are:

- TL16PNP100A a standalone plug-and-play controller.

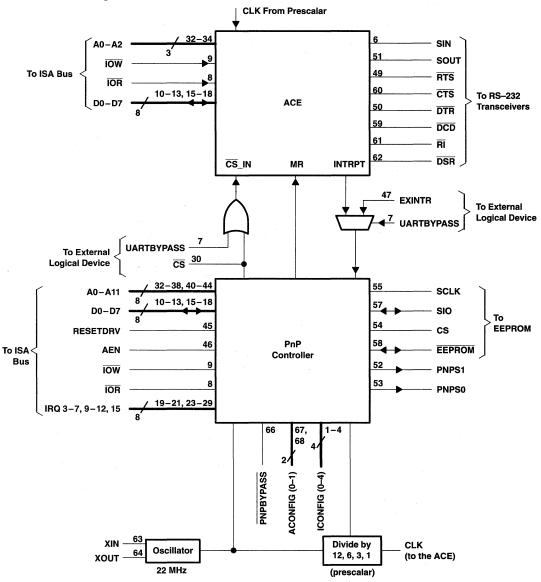

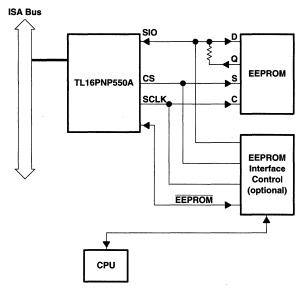

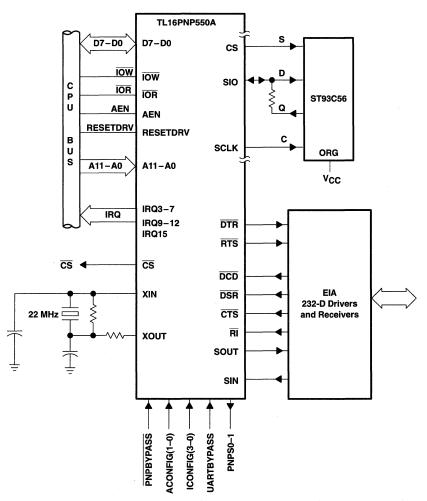

- TL16PNP550A the industry's first UART with plug-and-play capability.

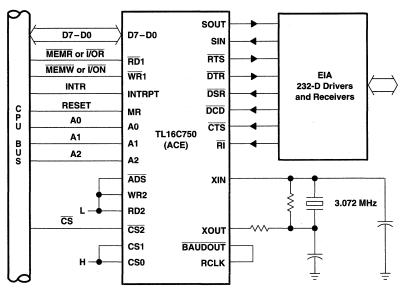

- TL16C750 a UART with a 64-byte FIFO buffer that reduces the number of interrupt requests.

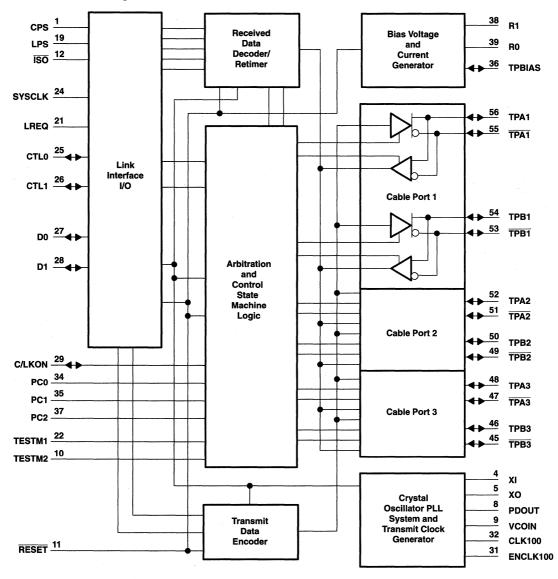

- TSB21LV03 a 1394 triple cable transceiver/arbiter that provides three fully compliant cable ports at 100/200 Mbits/s

- TSB11LV01 a 1-port 1394 cable transceiver/arbiter for 3-V supply operation at 100 Mbits/s

- TSB14C01 a 1-port 1394 backplane transceiver/arbiter that provides the transceiver functions needed to implement a single port node at 50/100 Mbits/s in a backplane-based 1394 network.

The data book is organized for quick location of a specific data sheet. The sequence is in base part number order (i.e., TL16C450 is located next to the TL16C451). The alphanumeric index provides a quick method of locating the data sheet for a known part number and indicates new products in this edition. A preview of new products that are near release to production are included for the first time in this data book.

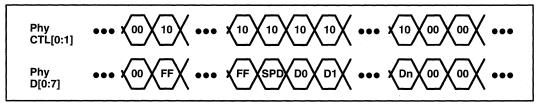

The selection guide is grouped by industry standard and includes key features and the standard device footprint of the products in each category. The cross-reference guide lists other manufacturers' devices with the suggested TI replacement. Package mechanical information is in the last section of the data book.

v

While this data book offers design and specification data only for data transmission products, complete technical data for any TI semiconductor product is available from your nearest TI Field Sales Office, local authorized TI distributor, or by writing directly to:

Texas Instruments Incorporated LITERATURE RESPONSE CENTER P.O. Box 809066 DALLAS, TEXAS 75380-9066

or telephone the TI Literature Response number: 1-800-477-8924.

We sincerely believe the new 1996 *Data Transmission Circuits Data Book, Volume 2* will be a valuable addition to your collection of technical literature.

| General Information        |   |

|----------------------------|---|

| UARTs                      | 2 |

| UART Product Previews      | 3 |

| IEEE-1394                  | 4 |

| IEEE-1394 Product Previews | 5 |

| Mechanical Data            | 6 |

| TIR1000                            | Standalone IrDA Encoder and Decoder 2–3                                           |

|------------------------------------|-----------------------------------------------------------------------------------|

| TL16C450                           | Asynchronous Communications Element 2–9                                           |

| TL16C451                           | Asynchronous Communications Element                                               |

| TL16C452                           | Asynchronous Communications Element                                               |

| TL16C550A                          | Asynchronous Communications Element                                               |

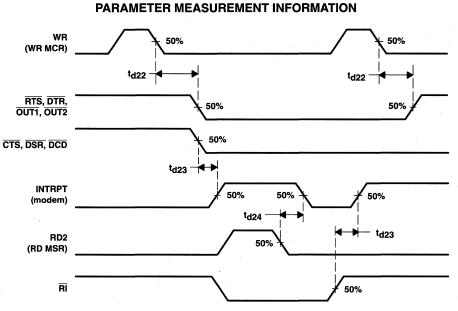

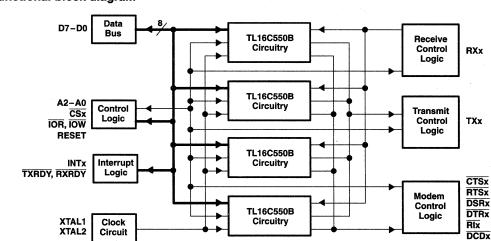

| TL16C550B                          | Asynchronous Communications Element 2-87                                          |

| TL16C550C                          | Asynchronous Communications Element with Autoflow Control                         |

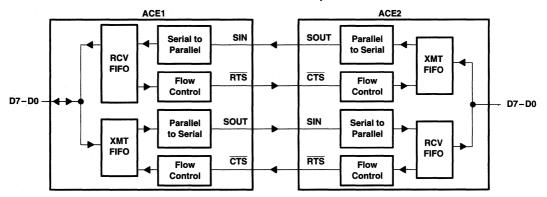

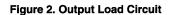

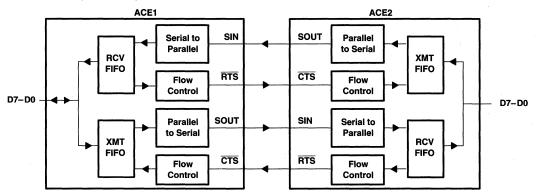

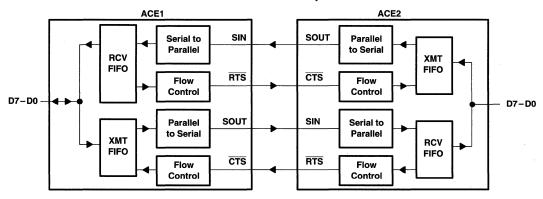

| TL16C552                           | Dual Asynchronous Communications Element with FIFO                                |

| TL16C552A                          | Dual Asynchronous Communications Element with FIFO                                |

| TL16C552AI                         | Dual Asynchronous Communications Element with FIFO                                |

| TL16C554                           | Asynchronous Communications Element                                               |

| TL16C750                           | Asynchronous Communications Element with 64-Byte FIFOs and Autoflow Control 2-281 |

| TL16PC564A                         | PCMCIA Universal Asynchronous Receiver Transmitter                                |

| TL16PIR552                         | Dual UART with Dual IrDA and 1284 Parallel Port                                   |

| TL16PNP100A                        | Standalone Plug-and-Play (PnP) Controller                                         |

| TL16PNP200 <sup>†</sup>            | Standalone Plug-and-Play (PnP) Controller                                         |

| TL16PNP550A                        | Asynchronous Communications Element with Plug-and-Play and Autoflow Control 2-365 |

| TSB11C01                           | IEEE 1394-1995 Triple-Cable Transceiver/Arbiter 4–3                               |

| TSB11LV01 <sup>†</sup>             | 1-Port P1394 Cable Transceiver/Arbiter For 3-Volt Supply Operation                |

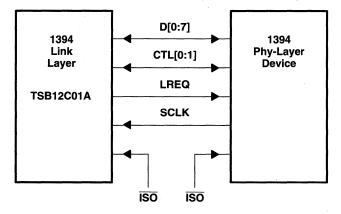

| TSB12C01A                          | 1394 High-Speed Serial-Bus Link-Layer Controller                                  |

| TSB12C01AM <sup>†</sup>            | P1394 High-Speed Serial-Bus Link-Layer Controller                                 |

| TSB14C01 <sup>†</sup>              | P1394 Backplane Transceiver/Arbiter For 5-Volt Supply Operation                   |

| TSB14C01M <sup>†</sup>             | IEEE 1394-1995 Backplane Transceiver/Arbiter For 5-Volt Supply Operation          |

| TSB21LV03 <sup>†</sup>             | P1394 Triple-Cable Transceiver/Arbiter                                            |

| TSB21LV03M <sup>†</sup>            | IEEE 1394-1995 Triple-Cable Transceiver/Arbiter                                   |

| <sup>†</sup> This is a product pre | eview data sheet.                                                                 |

## UARTs

| DEVICE      | DEVICE TYPE <sup>†</sup> | DESCRIPTION <sup>‡</sup>                                                                         | PACKAGES  | PAGE  |

|-------------|--------------------------|--------------------------------------------------------------------------------------------------|-----------|-------|

| TIR1000     | IR                       | Standalone IrDA encoder and decoder                                                              | PS        | 2–3   |

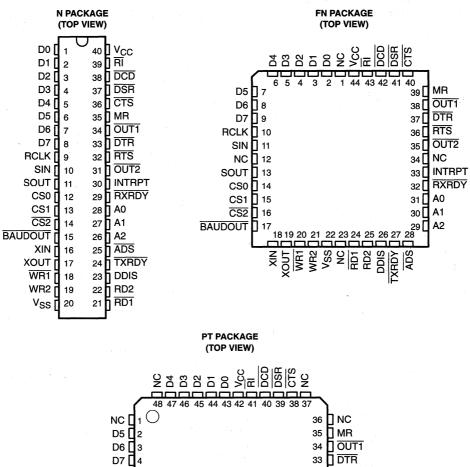

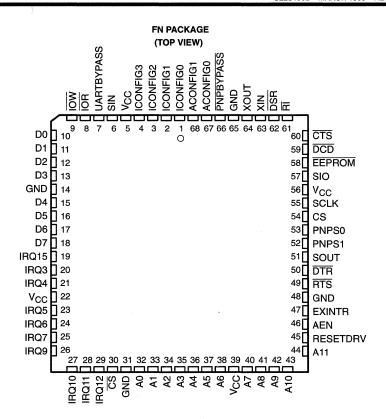

| TL16C450    | UART                     | Single ACE without FIFO                                                                          | FN, N     | 2–9   |

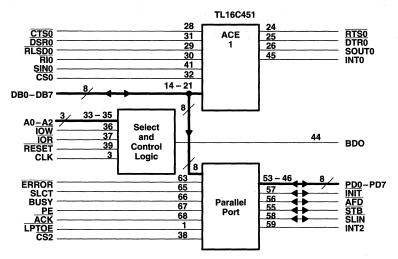

| TL16C451    | UART                     | Single ACE with parallel port and without FIFO                                                   | FN        | 2–33  |

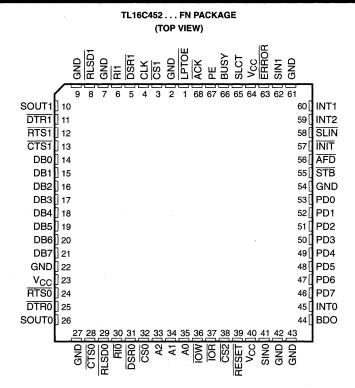

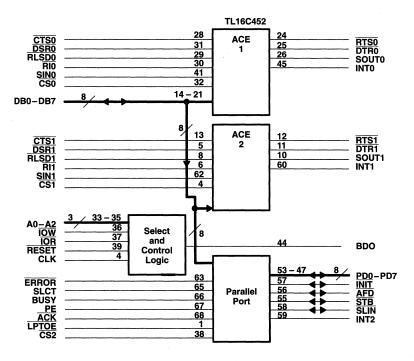

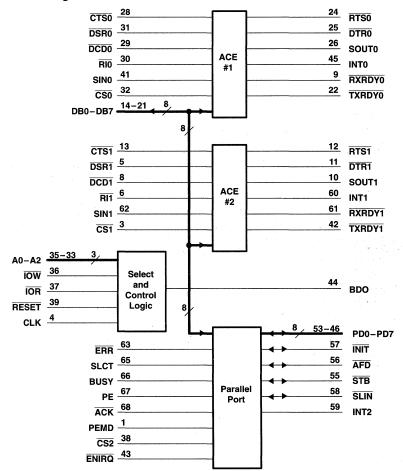

| TL16C452    | UART                     | Dual ACE with parallel port and without FIFO                                                     | FN        | 2–33  |

| TL16C550A   | UART                     | Single ACE with FIFO                                                                             | FN, N     | 2–57  |

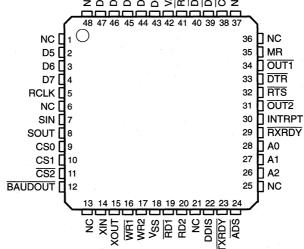

| TL16C550B   | UART                     | Single ACE with 16-byte FIFOs                                                                    | FN, N, PT | 287   |

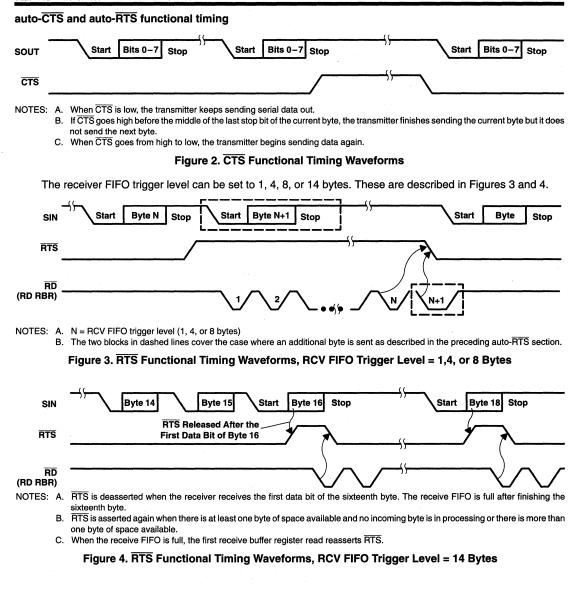

| TL16C550C   | UART                     | Single ACE with 16-byte FIFOs and auto flow control                                              | FN, N, PT | 2-117 |

| TL16C552    | UART                     | Dual ACE with 16-byte FIFOs and parallel port                                                    | FN        | 2–151 |

| TL16C552A   | UART                     | Dual ACE with 16-byte FIFOs and parallel port                                                    | FN        | 2–183 |

| TL16C552AI  | UART                     | Dual ACE with 16-byte FIFOs and parallel port characterized over<br>industrial temperature range | FN        | 2–217 |

| TL16C554    | UART                     | Quadruple ACE with 16-byte FIFOs                                                                 | FN        | 2-251 |

| TL16C750    | UART                     | Single ACE with 64-byte FIFOs, autoflow control, and low-power modes                             | FN, PM    | 2-281 |

| TL16PC564A  | UART, PCMCIA             | Single ACE with 64-byte FIFOs and PCMCIA interface                                               | PZ        | 2–315 |

| TL16PIR552§ | UART, IR                 | Dual ACE with 16-byte FIFOs and has selectable IR and 1284 modes                                 | n/a       | 33    |

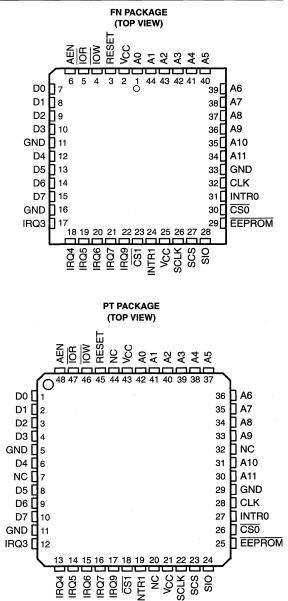

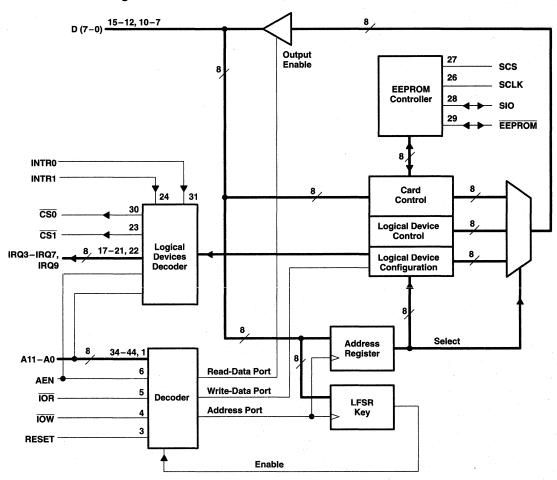

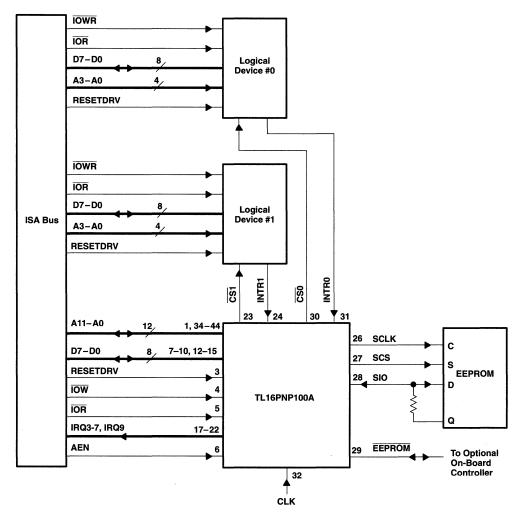

| TL16PNP100A | PnP                      | Standalone PnP controller that supports two logical devices                                      | FN, PT    | 2-347 |

| TL16PNP200§ | PnP                      | Standalone PnP controller that supports five logical devices                                     | n/a       | 3-5   |

| TL16PNP550A | UART, PnP                | Single ACE with 64-byte FIFOs, autoflow control, and PnP controller                              | FN        | 2-365 |

<sup>†</sup> UART = universal asynchronous receivers/transmitters, PCMCIA = Personal Computer Memory Card International Association, PnP = plug and play, IR = ifrared.

<sup>‡</sup> ACE = asynchronous communications element, FIFO = first in/first out, IrDA = Infrared Data Association

§ The data sheet for this device is product preview.

## IEEE 1394-1995

| DEVICE                  | DESCRIPTION                                                                 | PACKAGE | PAGE |

|-------------------------|-----------------------------------------------------------------------------|---------|------|

| TSB11C01                | Triple-cable transceiver/arbiter                                            | DL      | 43   |

| TSB11LV01               | Triple-cable transceiver/arbiter                                            |         | 53   |

| TSB12C01A               | High-speed serial-bus link-layer controller                                 | PZ      | 4-21 |

| TSB12C01AM <sup>†</sup> | High-speed serial-bus link-layer controller                                 | WN      | 5-7  |

| TSB14C01 <b>†</b>       | P1394 Single-Port Backplane Transceiver/Arbiter For 5-Volt Supply Operation | -       | 5-21 |

| TSB14C01M <sup>†</sup>  | P1394 Single-Port Backplane Transceiver/Arbiter For 5-Volt Supply Operation | WD      | 5-23 |

| TSB21LV03†              | Triple-cable transceiver/arbiter                                            |         | 5-25 |

| TSB21LV03MT             | Triple-cable transceiver/arbiter                                            | HV      | 529  |

<sup>†</sup> The data sheet for this device is product preview.

1-6

SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

- Adds Infrared (IR) Port to Universal Asynchronous Receiver Transmitter (UART)

- Compatible with Infrared Data Association (IrDA) & Hewlett Packard Serial Infrared (HPSIR)

- Provides 1200 bps to 115 kbps Data Rate

- Uses 2.7-V to 5.5-V Supply

- Provides Simple Interface With UART

- Decodes Negative or Positive Pulses

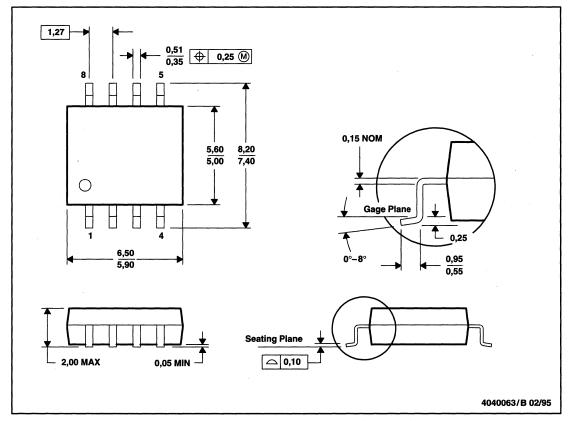

- Available in 8-Pin Small Outline Package (SOP)

#### description

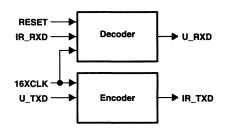

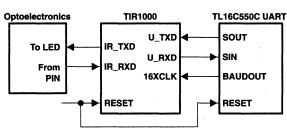

The TIR1000 serial infrared (SIR) encoder/ decoder is a CMOS device which encodes and decodes bit data in conformance with the IrDA specification.

A transceiver device is needed to interface to the photo-sensitive diode (PIN) and the light emitting diode (LED). A UART is needed to interface to the serial data lines.

#### **PS PACKAGE** (TOP VIEW) ⊐ v<sub>cc</sub> 10 16XCLK 8 7 2 IR\_TXD 6 3 IR\_RXD GND 🗖 4 5 RESET

functional block diagram

### **Terminal Functions**

| TERMI  | ERMINAL I/O |    | TERMINAL I/O DESCRIPTION                                                                                                                                                                                        |  | DESCRIPTION |

|--------|-------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------|

| NAME   | NO.         | 10 | DESCRIPTION                                                                                                                                                                                                     |  |             |

| 16XCLK | 1           | 1  | Clock signal. 16XCLK should be set to 16 times the baud rate. The highest baud rate for IrDA is 115.2 kbps, for which the clock frequency equals to 1.843 MHz (this terminal is tied to the BAUDOUT of a UART). |  |             |

| GND    | 4           |    | Ground                                                                                                                                                                                                          |  |             |

| IR_RXD | 6           | 1  | Infrared receiver data. IR_RXD is IRDA-SIR modulated input from an optoelectronics transceiver whose input<br>pulses should be 3/16 of the baud rate period.                                                    |  |             |

| IR_TXD | 7           | 0  | Infrared transmitter data. IR_TXD is IRDA-SIR modulated output to an optoelectronics transceiver.                                                                                                               |  |             |

| RESET  | 5           | 1  | Active high reset. RESET initializes a IRDA-SIR decode/encode state machine (this terminal is tied to a UART reset line).                                                                                       |  |             |

| U_RXD  | 3           | 0  | Receiver data. U_RXD is decoded (demodulated) data from IR_RXD per the IRDA specification (this terminal is tied to SIN of a UART).                                                                             |  |             |

| U_TXD  | 2           | 1  | Transmitter data. U_TXD is encoded (modulated) data and output data as IR_TXD (this terminal is tied to SOUT from a UART).                                                                                      |  |             |

| Vcc    | 8           |    | Power supply. The V <sub>CC</sub> requirement is 2.7 V to 5.5 V                                                                                                                                                 |  |             |

## TIR1000 STAND-ALONE IrDA ENCODER AND DECODER

#### SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1) |                                   |

|----------------------------------------------------|-----------------------------------|

| Input voltage range at any input, V <sub>1</sub>   |                                   |

| Output voltage range, VO                           | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Operating free-air temperature range, TA           |                                   |

| Storage temperature range, T <sub>stg</sub>        | –65°C to 150°C                    |

| Case temperature for 10 seconds: SOP package       | 260°C                             |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: All voltage levels are with respect to GND.

NOTE 1. All voltage levels are with respect to GND.

## recommended operating conditions over recommended operating free-air temperature range

#### low voltage (3 V nominal)

|                                    | MIN                 | NOM | MAX                 | UNIT |

|------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>CC</sub>    | 2.7                 | 3   | 3.3                 | v    |

| High-level input voltage, VIH      | 0.7 V <sub>CC</sub> |     |                     | V    |

| Low-level input voltage, VIL       |                     |     | 0.2 V <sub>CC</sub> | V    |

| Operating free-air temperature, TA | 0                   |     | 70                  | °C   |

#### standard voltage (5 V nominal)

|                                    | MIN                 | NOM | MAX                 | UNIT |

|------------------------------------|---------------------|-----|---------------------|------|

| Supply voltage, V <sub>CC</sub>    | 4.75                | 5   | 5.25                | V    |

| High-level input voltage, VIH      | 0.7 V <sub>CC</sub> |     |                     | v    |

| Low-level input voltage, VIL       |                     |     | 0.2 V <sub>CC</sub> | v    |

| Operating free-air temperature, TA | 0                   |     | 70                  | °C   |

## electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER  |                           | TEST CO                                                                 | TEST CONDITIONS                            |                        |   | MAX | UNIT |

|------------|---------------------------|-------------------------------------------------------------------------|--------------------------------------------|------------------------|---|-----|------|

|            |                           | I <sub>OH</sub> = -4 mA                                                 | V <sub>CC</sub> = 5 V                      | V <sub>CC</sub> - 0.8  |   |     | v    |

| VOH        | High-level output voltage | $I_{OH} = -1.8 \text{ mA}$                                              | V <sub>CC</sub> = 3 V                      | V <sub>CC</sub> – 0.55 |   |     | v    |

|            | Low level output valtage  | I <sub>OL</sub> = +4 mA                                                 | V <sub>CC</sub> = 5 V                      |                        |   | 0.5 | v    |

| VOL        | Low-level output voltage  | I <sub>OL</sub> = +1.8 mA                                               | V <sub>CC</sub> = 3 V                      |                        |   | 0.5 | v    |

| l          | Input current             | $V_{I} = 0$ to $V_{CC}$ ,                                               | All other pins floating                    | -                      |   | ±1  | μA   |

| lcc        | Supply current            | V <sub>CC</sub> = 5.25 V,<br>All inputs at 0.2 V,<br>No load on outputs | T <sub>A</sub> = 25°C,<br>16XCLK at 2 Mhz, |                        |   | 1   | mA   |

| Ci(16XCLK) | Clock input capacitance   |                                                                         |                                            |                        | 5 |     | pF   |

| f(16XCLK)  | Clock frequency           |                                                                         | -                                          |                        |   | 2   | MHz  |

SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

#### switching characteristics

|    | PARAMETER        | TEST CONDITIONS                          | MIN TYPT MAX |    |

|----|------------------|------------------------------------------|--------------|----|

| tr | Output rise time | C <sub>(LOAD)</sub> = 15 pF (10% to 90%) | 1.3          | ns |

| tf | Output fall time | C <sub>(LOAD)</sub> = 15 pF (90% to 10%) | 1.8          | ns |

<sup>†</sup>Typical values are at T<sub>A</sub> = 25°C.

#### Figure 1. Typical application of the TIR1000

## **PRINCIPLES OF OPERATION**

#### IrDA overview

The Infrared Data Association (IrDA) defines several protocols for sending and receiving serial infrared data, including rates of 115.2 kbps, 0.576 Mbps, 1.152 Mbps, and 4 Mbps. The low rate of 115.2 kbps was specified first and the others must maintain downward compatibility with it. At the 115.2 kbps rate, the protocol implemented in the hardware is fairly simple. It primarily defines a serial infrared data "word" to be surrounded by a start bit equal to 0 and a stop bit equal to 1. Individual bits are encoded or decoded the same whether they are start, data, or stop bits. The TIR1000 evaluates only single bits and only follows the 115.2 kbps protocol. The 115.2 kbps rate is a maximum rate. When both ends of the transfer are set up to a lower but matching speed, the protocol (with the TIR1000) still works. The clock used to code or sample the data is 16 times the baud rate, or 1.843 Mhz maximum. To code a 1, no pulse is sent or received for 1-bit time period, or 16 clock cycles. To code a 0, one pulse is sent or received within a 1-bit time period, or 16 clock cycles. The pulse must be at least 1.6 µs wide and 3 clock cycles long at 1.843 Mhz. At lower baud rates the pulse can be 1.6 µs wide or as long as 3 clock cycles. The transmitter output, IR\_TXD, is intended to drive a LED circuit to generate an infrared pulse. The LED circuits have inversion and generate negative pulses from the detected infrared light. Their output is normally high. The TIR1000 can decode either negative or positive pulses on IR\_RXD.

## TIR1000 STAND-ALONE IrDA ENCODER AND DECODER

SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

### **PRINCIPLES OF OPERATION**

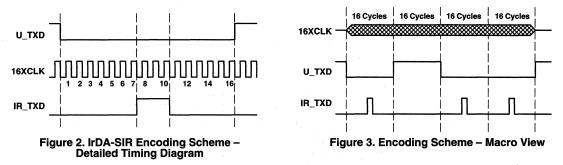

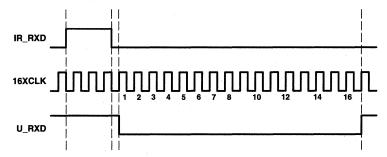

#### IrDA encoder function

Serial data from a UART is encoded to transmit data to the optoelectronics. While the serial data input to this block (U\_TXD) is high, the output (IR\_TXD) is always low, and the counter used to form a pulse on IR\_TXD is continuously cleared. After U\_TXD resets to 0, IR\_TXD rises on the falling edge of the seventh 16XCLK. On the falling edge of the tenth 16XCLK pulse, IR\_TXD falls, creating a 3-clock-wide pulse. While U\_TXD stays low, a pulse is transmitted during the seventh to tenth clocks of each 16-clock bit cycle.

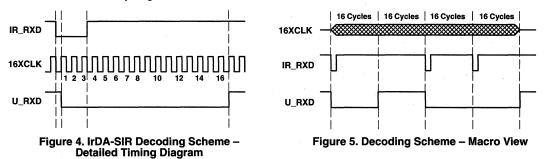

#### IrDA decoder function

After reset, U\_RXD is high and the 4-bit counter is cleared. When a falling edge is detected on IR\_RXD, U\_RXD falls on the next rising edge of 16XCLK with sufficient setup time. U\_RXD stays low for 16 (16XCLK) cycles and then returns to high as required by the IrDA specification. As long as no pulses (falling edges) are detected on IR\_TXD, U\_RXD stays high.

SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

## **PRINCIPLES OF OPERATION**

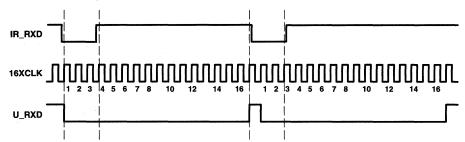

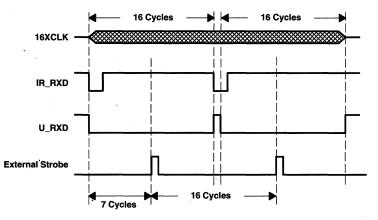

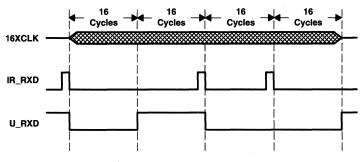

It is possible for jitter or slight frequency differences to cause the next falling edge on IR\_RXD to be missed for one 16XCLK cycle. In that case, a 1-clock wide pulse appears on U\_RXD between consecutive zeroes. It is important for the UART to strobe U\_RXD in the middle of the bit time to avoid latching this temporary value. The TL16C550C UART already strobes incoming serial data at the proper time. Otherwise, note that data is required to be framed by a leading zero and a trailing one. The falling edge of that first zero on U\_RXD synchronizes the read strobe. The strobe is on the eighth 16XCLK pulse after the U\_RXD falling edge and once every 16 cycles thereafter until the stop bit occurs.

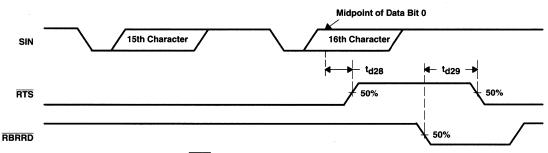

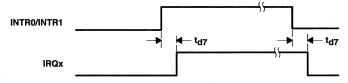

Figure 6. Timing Causing 1-clock Wide Pulse Between Consecutive Ones

Figure 7. Recommended Strobing For Decoded Data

## TIR1000 STAND-ALONE IrDA ENCODER AND DECODER

SLLS228A - DECEMBER 1995 - REVISED FEBRUARY 1996

#### **PRINCIPLES OF OPERATION**

The TIR1000 can also decode positive pulses on IR\_RXD. The timing is different, but the variation is invisible to the UART. Because the decoder works from the falling edge, it now recognizes a zero on the trailing edge of the pulse rather than on the leading edge. As long as the pulse width is fairly constant, as defined by the specification, the trailing edges should also be 16 clock cycles apart and data can readily be decoded. The zero appears on U\_RXD after the pulse rather than at the start of it.

Figure 9. Positive IR\_RXD Pulse Decode - Macro View

SLLS037B - MARCH 1988 - REVISED MARCH 1996

INSTRUMENTS POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SLLS037B - MARCH 1988 - REVISED MARCH 1996

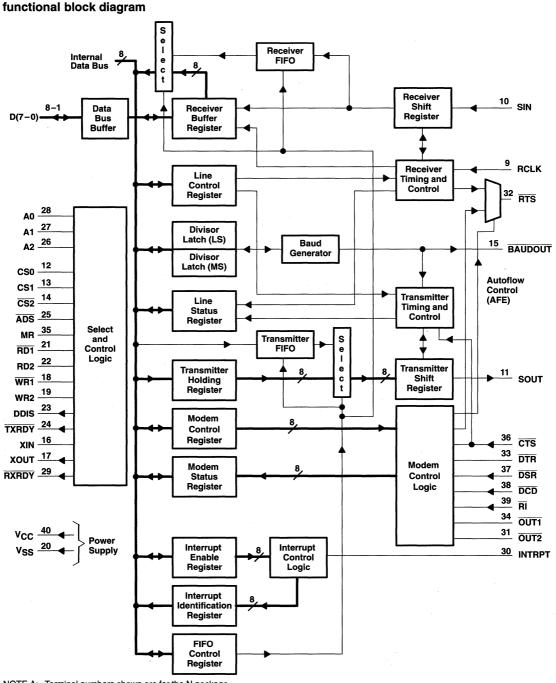

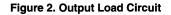

#### description (continued)

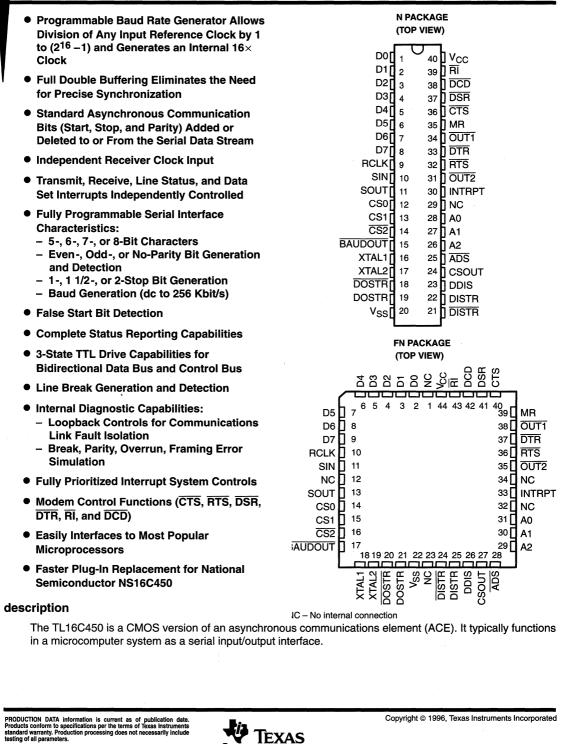

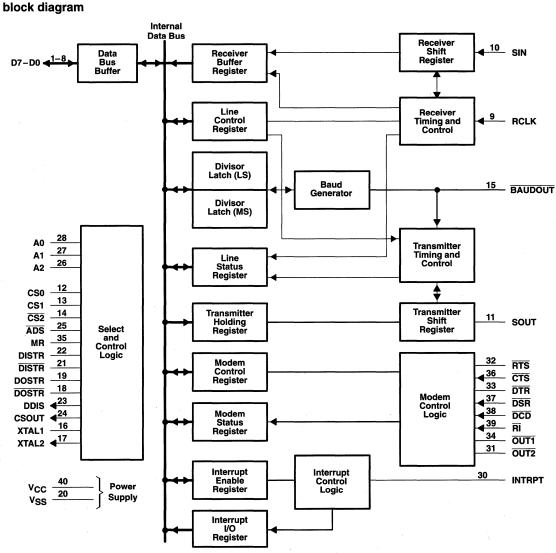

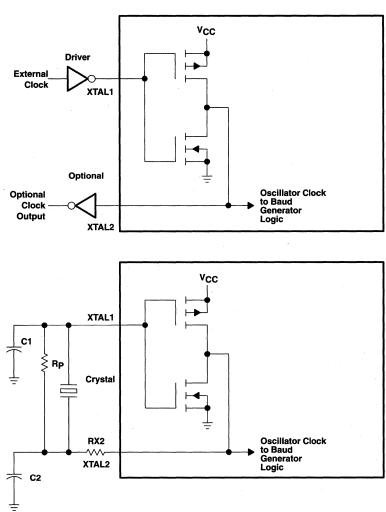

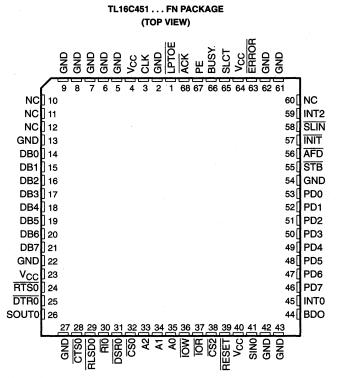

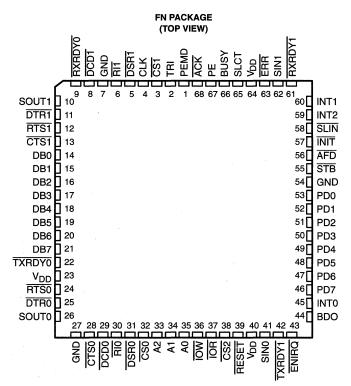

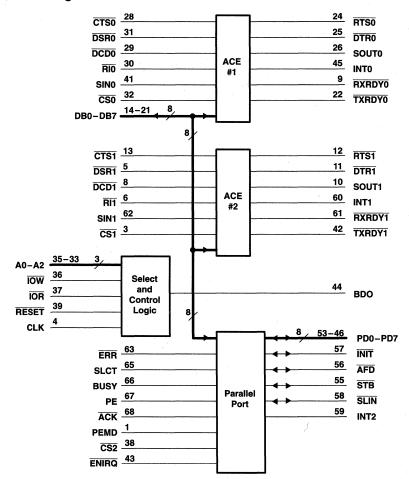

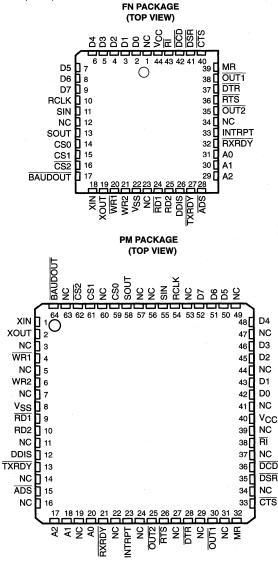

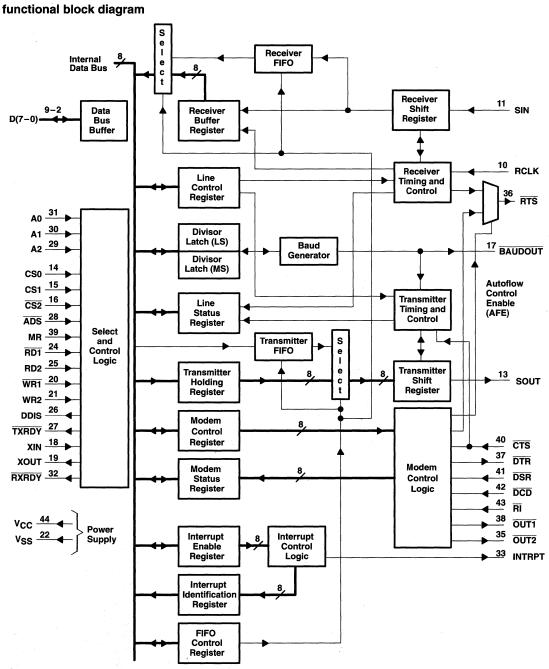

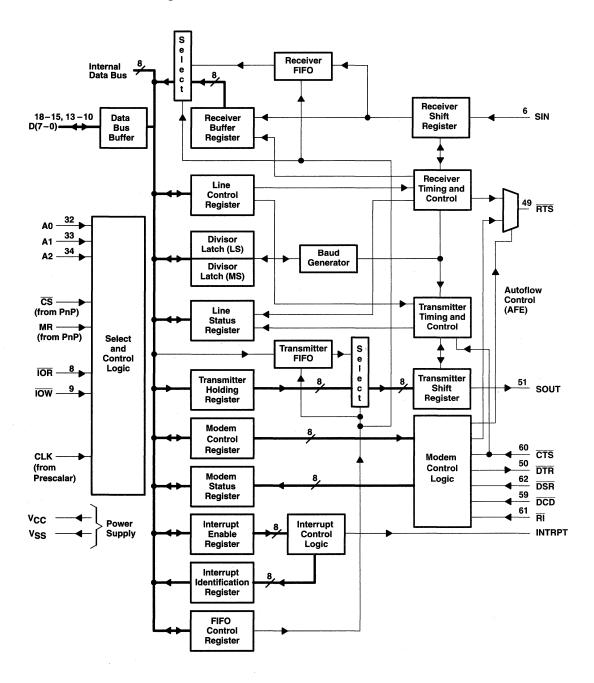

The TL16C450 performs serial-to-parallel conversion on data received from a peripheral device or modem and parallel-to-serial conversion on data received from its CPU. The CPU can read and report on the status of the ACE at any point in the ACE's operation. Reported status information includes the type of transfer operation in progress, the status of the operation, and any error conditions encountered.

The TL16C450 ACE includes a programmable, on-board, baud rate generator. This generator is capable of dividing a reference clock input by divisors from 1 to  $(2^{16} - 1)$  and producing a  $16 \times$  clock for driving the internal transmitter logic. Provisions are included to use this  $16 \times$  clock to drive the receiver logic. Also included in the ACE is a complete modem control capability and a processor interrupt system that may be software tailored to the user's requirements to minimize the computing required to handle the communications link.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

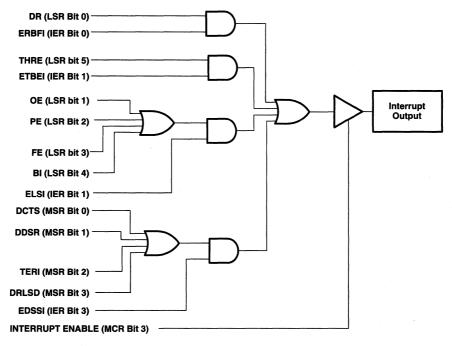

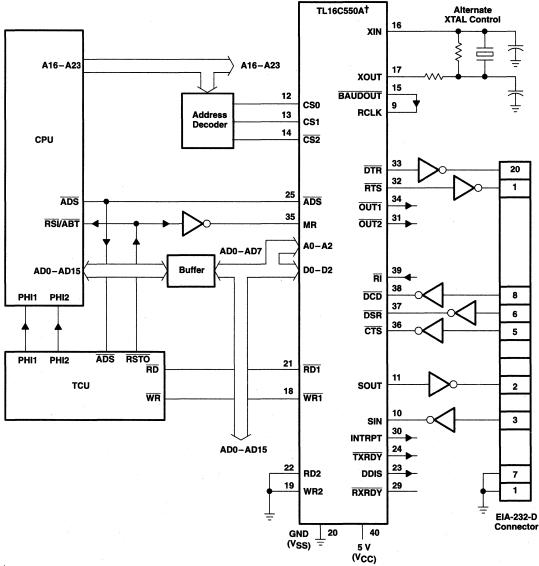

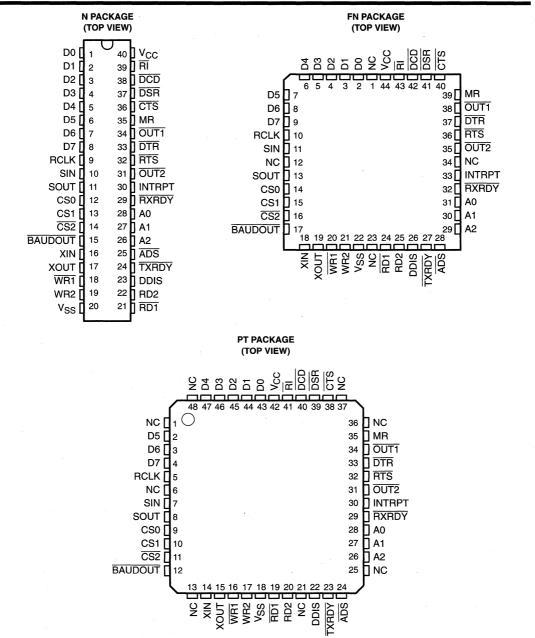

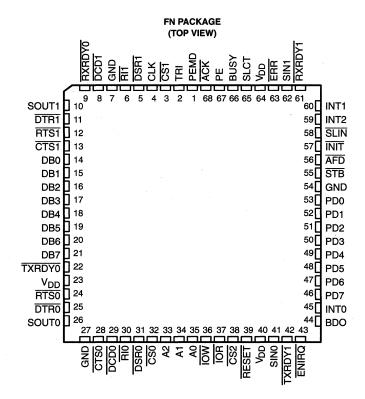

Terminal numbers shown are for the N package.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

| TERMI             | VAL            | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME              | NO.†           | 10  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

| A0<br>A1<br>A2    | 28<br>27<br>26 | I   | Register select. A0, A1, and A2 are three inputs used during read and write operations to select the ACE registe to read from or write to. Refer to Table 1 for register addresses, also refer to the address strobe (ADS) signates description.                                                                                                                                                           |

| ADS               | 25             | 1   | Address strobe. When ADS is active (low), the register select signals (A0, A1, and A2) and chip select signals (CS0, CS1, CS2) drive the internal select logic directly; when high, the register select and chip select signals are held in the state they were in when the low-to-high transition of ADS occurred.                                                                                        |

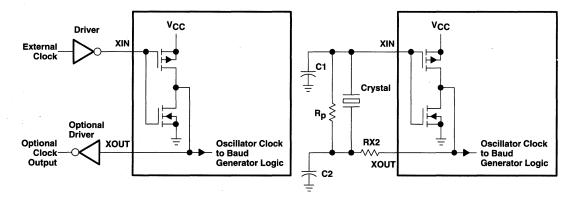

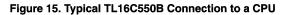

| BAUDOUT           | 15             | 0   | Baud out. BAUDOUT is a16× clock signal for the transmitter section of the ACE. The clock rate is established by the reference oscillator frequency divided by a divisor specified by the baud generator divisor latches BAUDOUT may also be used for the receiver section by tying this output to the RCLK input.                                                                                          |

| CS0<br>CS1<br>CS2 | 12<br>13<br>14 | 1   | Chip select. When CSx is active (high, high, and low respectively), the ACE is selected. Refer to the ADS signa description.                                                                                                                                                                                                                                                                               |

| CSOUT             | 24             | 0   | Chip select out. When CSOUT is high, it indicates that the ACE has been selected by the chip select inputs (CS0 CS1, and $\overline{CS2}$ ). CSOUT is low when the chip is deselected.                                                                                                                                                                                                                     |

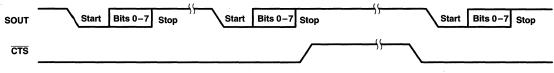

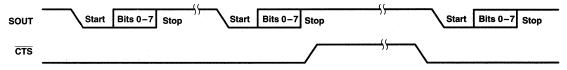

| CTS               | 36             | I   | Clear to send. CTS is a modem status signal. Its condition can be checked by reading bit 4 (CTS) of the modern status register. Bit 0 (DCTS) of the modern status register indicates that this signal has changed states since the last read from the modern status register. If the modern status interrupt is enabled when CTS changes state, ar interrupt is generated.                                 |

| D0 – D7           | 1 – 8          | I/O | Data bus. D0 – D7 are 3-state data lines that provide a bidirectional path for data, control, and status information between the ACE and the CPU.                                                                                                                                                                                                                                                          |

| DCD               | 38             | 1   | Data carrier detect. DCD is a modern status signal. Its condition can be checked by reading bit 7 (DCD) of the modern status register. Bit 3 (DDCD) of the modern status register indicates that this signal has changed states since the last read from the modern status register. If the modern status interrupt is enabled when the DCE changes state, an interrupt is generated.                      |

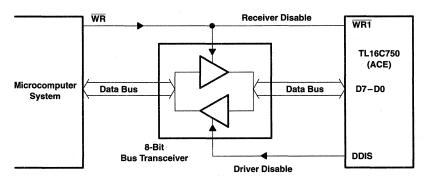

| DDIS              | 23             | 0   | Driver disable. DDIS is active (high) when the CPU is not reading data. When active, this output can disable ar external transceiver.                                                                                                                                                                                                                                                                      |

| DISTR<br>DISTR    | 22<br>21       |     | Data input strobes. When either DISTR or DISTR is active (high or low respectively) while the ACE is selected the CPU is allowed to read status information or data from a selected ACE register. Only one of these inputs is required for the transfer of data during a read operation. The other input should be tied in its inactive state (i.e. DISTR tied low or DISTR tied high).                    |

| DOSTR<br>DOSTR    | 19<br>18       | 1   | Data output strobes. When either DOSTR or DOSTR is active (high or low respectively), while the ACE is selected, the CPU is allowed to write control words or data into a selected ACE register. Only one of these inputs is required to transfer data during a write operation. The other input should be tied in its inactive state (i.e., DOSTF tied low or DOSTR tied high).                           |

| DSR               | 37             | I   | Data set ready. DSR is a modem status signal. Its condition can be checked by reading bit 5 (DSR) of the modem status register. Bit 1 (DDSR) of the modem status register indicates that this signal has changed state since the last read from the modem status register. If the modem status interrupt is enabled when the DSR changes state an interrupt is generated.                                  |

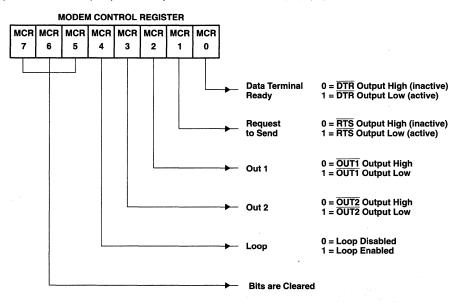

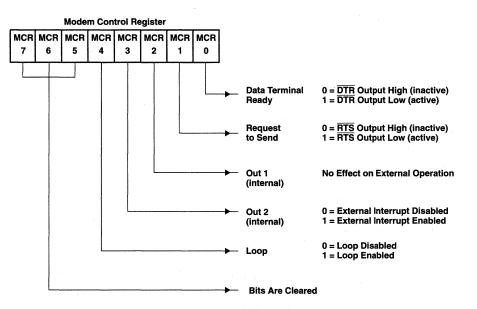

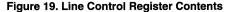

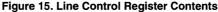

| DTR               | 33             | 0   | Data terminal ready. When active (low), DTR informs a modem or data set that the ACE is ready to establish communication. DTR is placed in the active state by setting the DTR bit of the modem control register to a high level. DTR is placed in the inactive state either as a result of a master reset or during loop mode operation o clearing bit 0 (DTR) of the modem control register.             |

| INTRPT            | 30             | 0   | Interrupt. When active (high), INTRPT informs the CPU that the ACE has an interrupt to be serviced. The fou<br>conditions that cause an interrupt are: a receiver error, received data is available, the transmitter holding registe<br>is empty, or an enabled modem status interrupt. The INTRPT output is reset (inactivated) either when the interrup<br>is serviced or as a result of a master reset. |

| MR                | 35             |     | Master reset. When active (high), MR clears most ACE registers and sets the state of various output signals<br>Refer to Table 2 for ACE reset functions.                                                                                                                                                                                                                                                   |

**Terminal Functions**

<sup>†</sup> Terminal numbers shown are for the N package.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

| TERM            | INAL     |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.†     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

| OUT1<br>OUT2    | 34<br>31 | 0   | Outputs 1 and 2. OUT1 and OUT2 are user-designated output terminals that are set to their active states by setting their respective modem control register bits (OUT1 and OUT2) high. OUT1 and OUT2 are set to their inactive (high) states as a result of master reset or during loop mode operations or by clearing bit 2 (OUT1) or bit 3 (OUT2) of the MCR.                                                                 |

| RCLK            | 9        | 1   | Receiver clock. RCLK is the 16× baud rate clock for the receiver section of the ACE.                                                                                                                                                                                                                                                                                                                                           |

| RI              | 39       | 1   | Ring indicator. $\overline{RI}$ is a modem status signal. Its condition can be checked by reading bit 6 (RI) of the modem status register. Bit 2 (TERI) of the modem status register indicates that the $\overline{RI}$ input has transitioned from a low to a high state since the last read from the modem status register. If the modem status interrupt is enabled when this transition occurs, an interrupt is generated. |

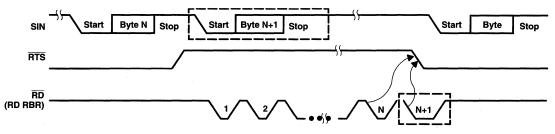

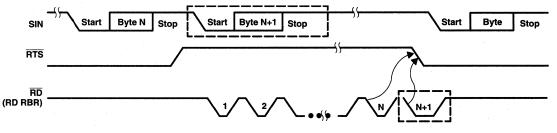

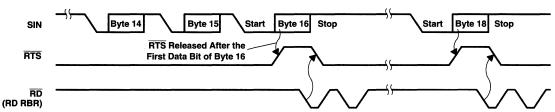

| RTS             | 32       | 0   | Request to send. When active, RTS informs the modem or data set that the ACE is ready to transmit data. RTS is set to its active state by setting the RTS modem control register bit and is set to its inactive (high) state either as a result of a master reset or during loop mode operations or by clearing bit 1 (RTS) of the MCR.                                                                                        |

| SIN             | 10       | 1   | Serial input. SIN is the serial data input from a connected communications device.                                                                                                                                                                                                                                                                                                                                             |

| SOUT            | 11       | 0   | Serial output. SOUT is the composite serial data output to a connected communication device. SOUT is set to<br>the marking (set) state as a result of MR.                                                                                                                                                                                                                                                                      |

| Vcc             | 40       |     | 5-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>SS</sub> | 20       |     | Supply common                                                                                                                                                                                                                                                                                                                                                                                                                  |

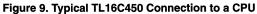

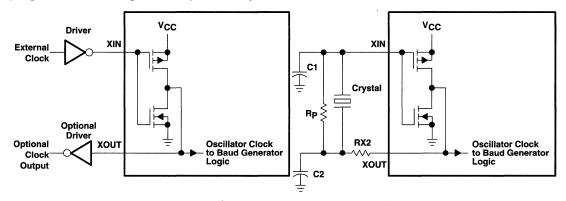

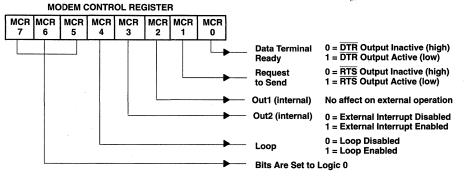

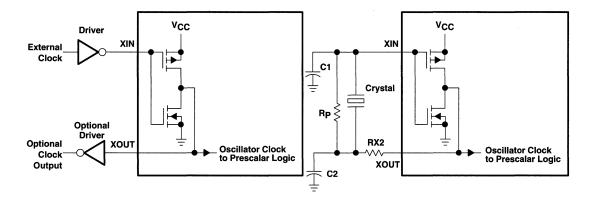

| XTAL1<br>XTAL2  | 16<br>17 | 1/0 | External clock. XTAL1 and XTAL2 connect the ACE to the main timing reference (clock or crystal).                                                                                                                                                                                                                                                                                                                               |

**Terminal Functions (continued)**

<sup>†</sup> Terminal numbers shown are for the N package.

### absolute maximum ratings over free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                             |

|------------------------------------------------------------------------------------------------|

| Input voltage range at any input, V <sub>1</sub> 0.5 V to 7 V                                  |

| Output voltage range, V <sub>O</sub> 0.5 V to 7 V                                              |

| Continuous total power dissipation at (or below) 70°C free-air temperature: FN package 1100 mW |

| N package 800 mW                                                                               |

| Operating free-air temperature range, T <sub>A</sub>                                           |

| Storage temperature range, T <sub>sta</sub>                                                    |

| Case temperature for 10 seconds, T <sub>C</sub> : FN package                                   |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N package                        |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to  $\ensuremath{\mathsf{V}_{\textsc{SS}}}$  .

### recommended operating conditions

|                                                | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                | 4.75 | 5   | 5.25 | V    |

| High-level input voltage, VIH                  | 2    |     | VCC  | V    |

| Low-level input voltage, VIL                   | -0.5 |     | 0.8  | V    |

| Operating free-air temperature, T <sub>A</sub> | 0    |     | 70   | °C   |

SLLS037B - MARCH 1988 - REVISED MARCH 1996

### electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                    | PARAMETER                     | TEST C                                                                                                | ONDITIONS                                      | MIN | TYP <sup>†</sup> | MAX | UNIT |

|--------------------|-------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------|-----|------------------|-----|------|

| v <sub>он</sub> ‡  | High-level output voltage     | IOH = -1 mA                                                                                           |                                                | 2.4 |                  |     | V    |

| V <sub>OL</sub> ‡  | Low-level output voltage      | I <sub>OL</sub> = 1.6 mA                                                                              |                                                |     |                  | 0.4 | v    |

| likg               | Input leakage current         | $V_{CC} = 5.25 V,$<br>V <sub>I</sub> = 0 to 5.25 V,                                                   | $V_{SS} = 0$ ,<br>All other terminals floating |     | ,                | ±10 | μA   |

| loz                | High-impedance output current | $V_{CC} = 5.25 V,$<br>$V_O = 0 V to 5.25 V,$<br>Chip selected, write mode                             | V <sub>SS</sub> = 0,<br>,or chip deselected    |     |                  | ±20 | μA   |

| lcc                | Supply current                | V <sub>CC</sub> = 5.25 V,<br>SIN, DSR, DCD, CTS, and<br>All other inputs at 0.8 V,<br>XTAL1 at 4 MHz, | d RI at 2 V,                                   |     |                  | 10  | mA   |

| C <sub>XTAL1</sub> | Clock input capacitance       |                                                                                                       | · .                                            |     | 15               | 20  | pF   |

| CXTAL2             | Clock output capacitance      | $V_{CC} = 0,$<br>f = 1 MHz,                                                                           | V <sub>SS</sub> = 0,<br>T <sub>A</sub> = 25°C, |     | 20               | 30  | pF   |

| Ci                 | Input capacitance             | All other terminals ground                                                                            |                                                |     | 6                | 10  | pF   |

| Co                 | Output capacitance            | 1                                                                                                     |                                                |     | 10               | 20  | pF   |

<sup>†</sup> All typical values are at  $V_{CC}$  = 5 V,  $T_A$  = 25°C. <sup>‡</sup> These parameters apply for all outputs except XTAL2.

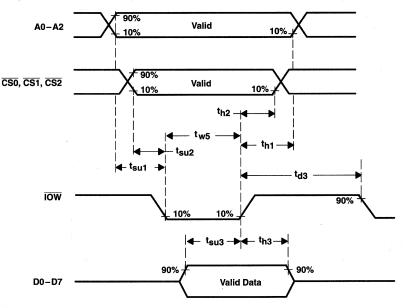

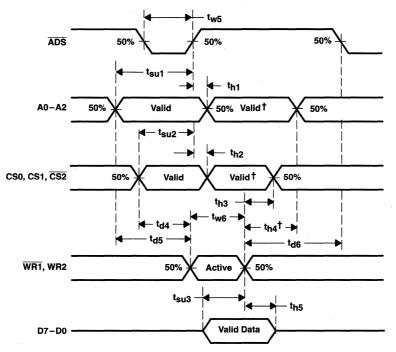

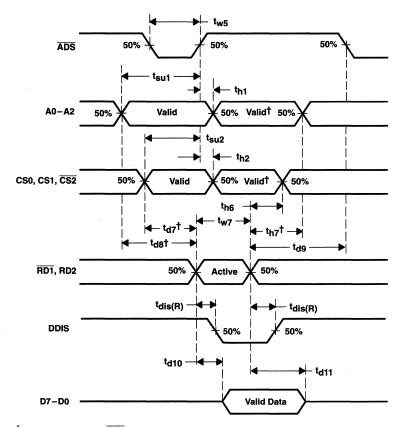

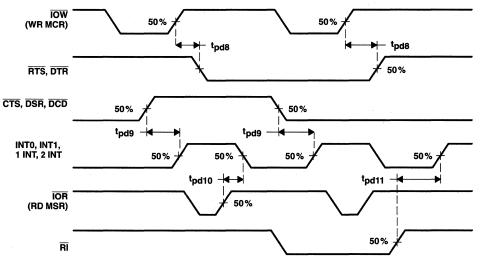

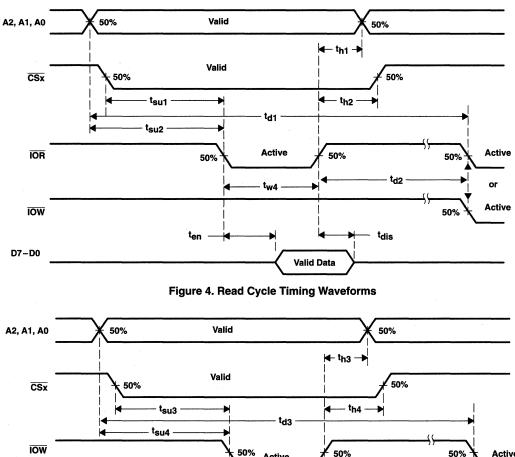

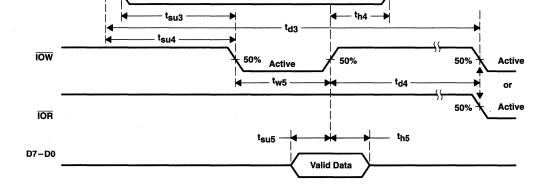

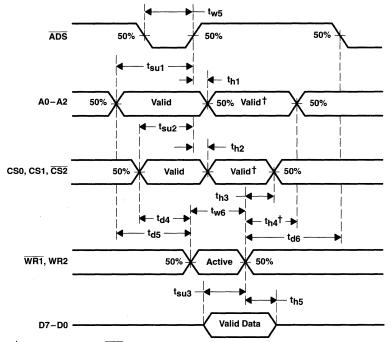

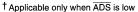

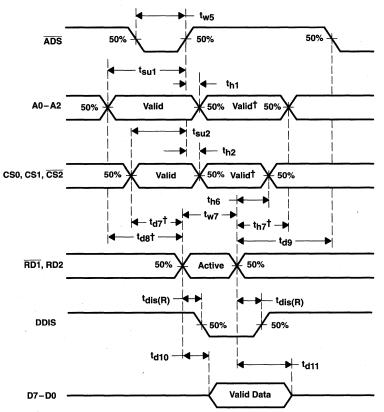

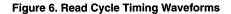

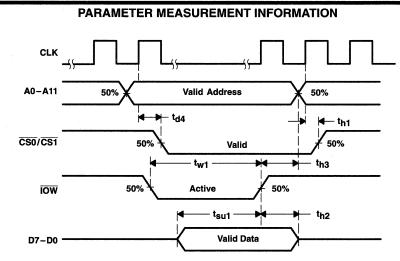

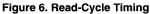

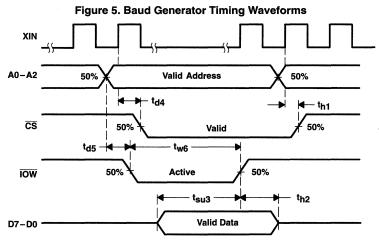

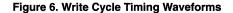

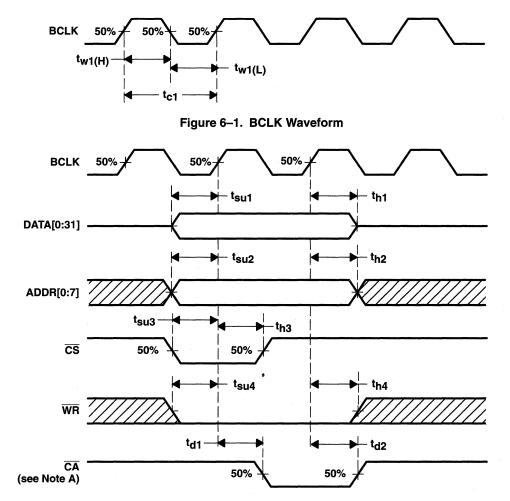

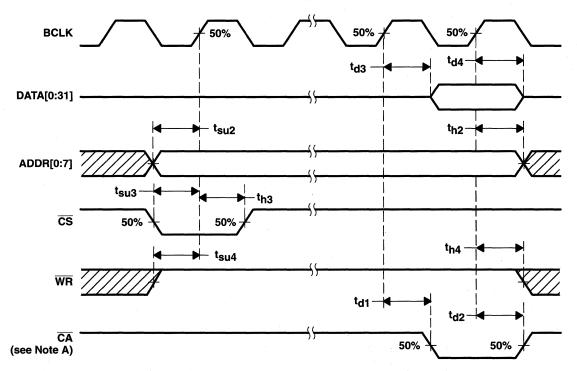

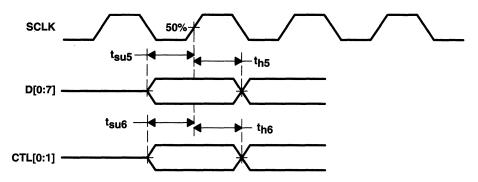

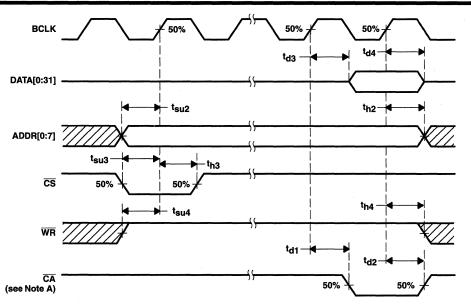

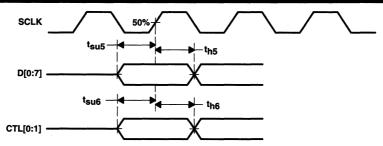

### system timing requirements over recommended ranges of supply voltage and operating free-air temperature

|                   | PARAMETER                                                                                          | FIGURE | MIN MAX | UNIT |

|-------------------|----------------------------------------------------------------------------------------------------|--------|---------|------|

| <sup>t</sup> cR   | Cycle time, read (t <sub>w7</sub> + t <sub>d8</sub> + t <sub>d9</sub> )                            |        | 175     | ns   |

| <sup>t</sup> cW   | Cycle time, write (t <sub>w6</sub> + t <sub>d5</sub> + t <sub>d6</sub> )                           |        | 175     | ns   |

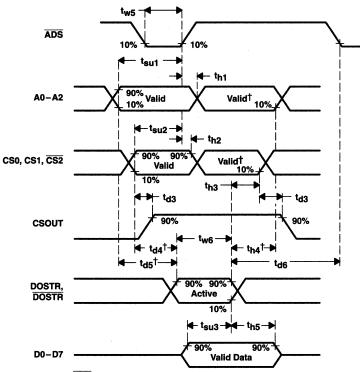

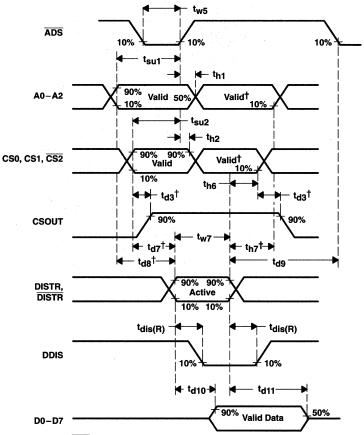

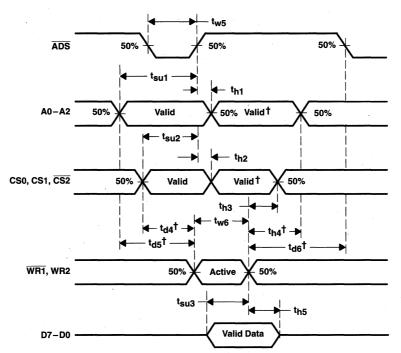

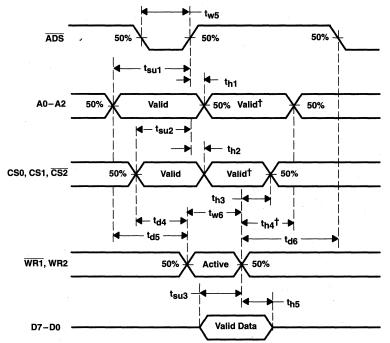

| tw5               | Pulse duration, ADS low                                                                            | 2,3    | 15      | ns   |

| tw6               | Pulse duration, write strobe                                                                       | 2      | 80      | ns   |

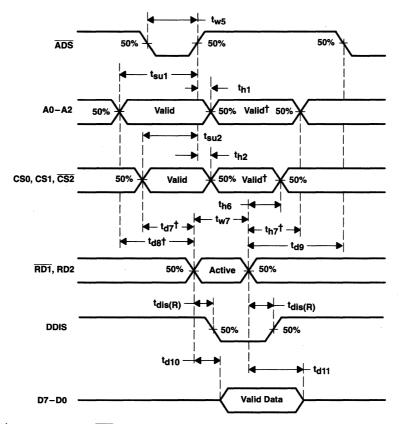

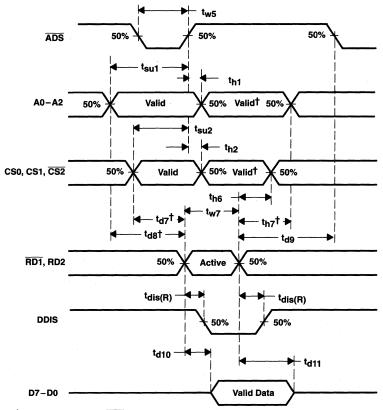

| t <sub>w7</sub>   | Pulse duration, read strobe                                                                        | 3      | 80      | ns   |

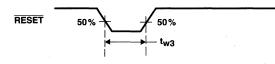

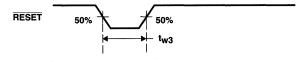

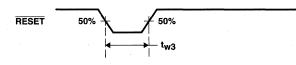

| twMR              | Pulse duration, master reset                                                                       |        | 1000    | ns   |

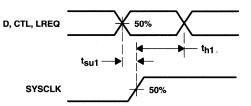

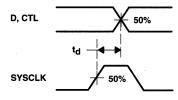

| tsu1              | Setup time, address valid before ADS↑                                                              | 2,3    | 15      | ns   |

| t <sub>su2</sub>  | Setup time, CS valid before ADS1                                                                   | 2,3    | 15      | ns   |

| t <sub>su3</sub>  | Setup time, data valid before $\overline{WR1}\downarrow$ or $WR2\uparrow$                          | 2      | 15      | ns   |

| <sup>t</sup> h1   | Hold time, address low after ADS↑                                                                  | 2,3    | 0       | ns   |

| th2               | Hold time, CS valid after ADS↑                                                                     | 2,3    | 0       | ns   |

| t <sub>h3</sub>   | Hold time, CS valid after WR1↑ or WR2↓                                                             | 2      | 20      | ns   |

| t <sub>h4</sub> § | Hold time, address valid after $\overline{WR1}\uparrow$ or $WR2\downarrow$                         | 2      | 20      | ns   |

| t <sub>h5</sub>   | Hold time, data valid after $\overline{WR1}$ or $WR2\downarrow$                                    | 2      | 15      | ns   |

| t <sub>h6</sub>   | Hold time, CS valid after $\overline{RD1}$ or $RD2\downarrow$                                      | 3      | 20      | ns   |

| t <sub>h7</sub> § | Hold time, address valid after $\overline{\text{RD1}}$ or $\text{RD2}\downarrow$                   | 3      | 20      | ns   |

| t <sub>d4</sub> § | Delay time, CS valid before $\overline{WR1}\downarrow$ or $WR2\uparrow$                            | 2      | 15      | ns   |

| t <sub>d5</sub> § | Delay time, address valid before $\overline{WR1}\downarrow$ or $WR2\uparrow$                       | 2      | 15      | ns   |

| td6               | Delay time, write cycle, $\overline{WR1}\uparrow$ or $WR2\downarrow$ to $\overline{ADS}\downarrow$ | 2      | 80      | ns   |

| td7§              | Delay time, CS valid to $\overline{\text{RD1}}\downarrow$ or RD2 $\uparrow$                        | 3      | 15      | ns   |

| t <sub>d8</sub> § | Delay time, address valid to $\overline{RD1}\downarrow$ or $RD2\uparrow$                           | 3      | 15      | ns   |

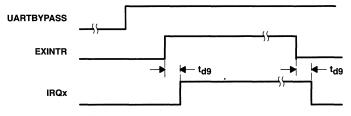

| t <sub>d9</sub>   | Delay time, read cycle, $\overline{RD1}\uparrow$ or $RD2\downarrow$ to $\overline{ADS}\downarrow$  | 3      | 80      | ns   |

§ Only applies when ADS is low.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

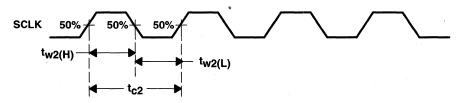

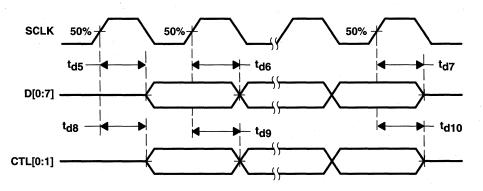

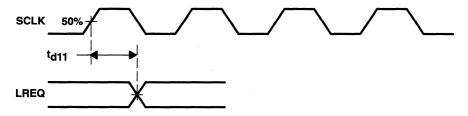

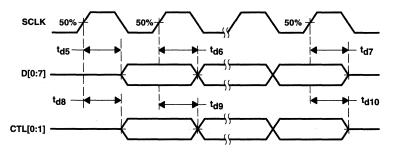

## system switching characteristics over recommended ranges of supply voltage and operating free-air temperature

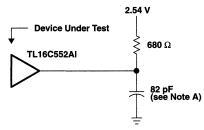

|                     | PARAMETER                                                                                                | FIGURE | TEST CONDITIONS         | MIN | MAX | UNIT |

|---------------------|----------------------------------------------------------------------------------------------------------|--------|-------------------------|-----|-----|------|

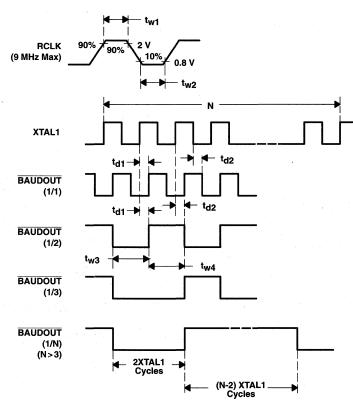

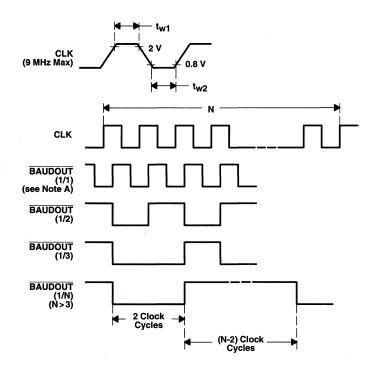

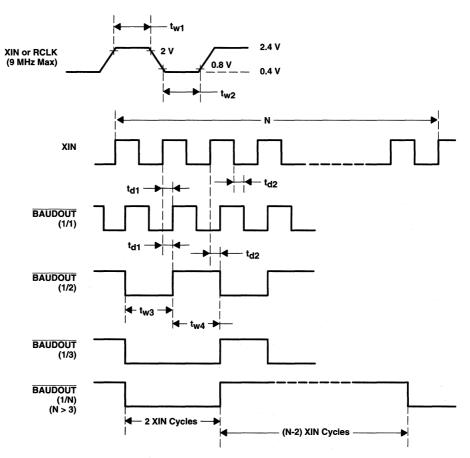

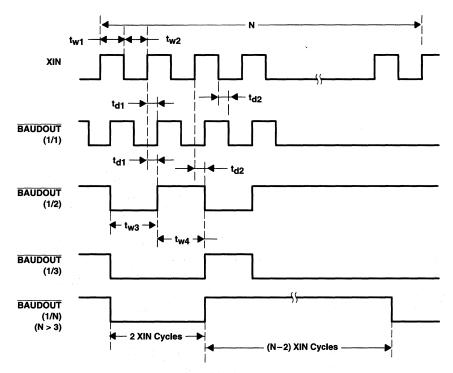

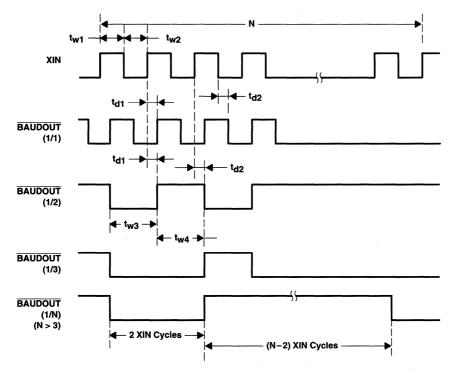

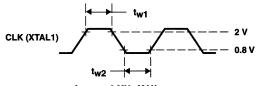

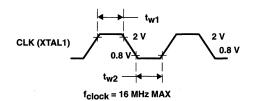

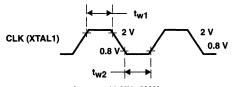

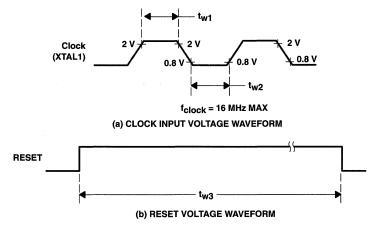

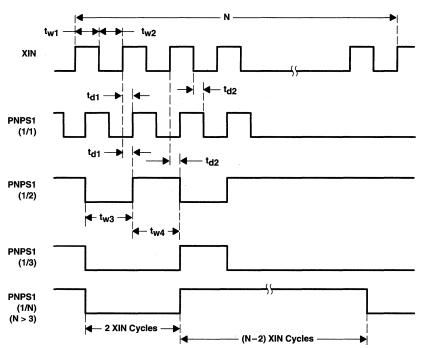

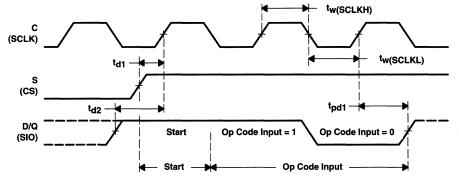

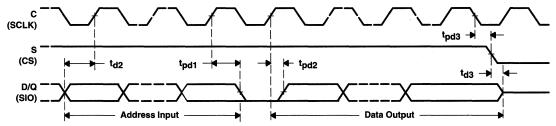

| <sup>t</sup> w1     | Pulse duration, clock high                                                                               | 1      | f = 9 MHz maximum       | 50  |     | ns   |

| tw2                 | Pulse duration, clock low                                                                                | 1      | f = 9 MHz maximum       | 50  |     | ns   |

| <sup>t</sup> d3     | Delay time, select to CS output                                                                          | 2,3†   | C <sub>L</sub> = 100 pF |     | 70  | ns   |

| <sup>t</sup> d10    | Delay time, $\overline{\text{RD1}}\downarrow$ or RD2 $\uparrow$ to data valid                            | 3      | C <sub>L</sub> = 100 pF |     | 60  | ns   |

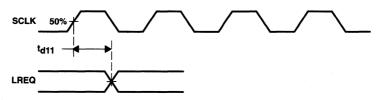

| <sup>t</sup> d11    | Delay time, $\overline{\text{RD1}}$ or $\text{RD2}\downarrow$ to floating data                           | 3      | C <sub>L</sub> = 100 pF | 0   | 60  | ns   |

| <sup>t</sup> dis(R) | Disable time, $\overline{RD1}\downarrow\uparrow$ or $RD2\uparrow\downarrow$ to DDIS $\uparrow\downarrow$ | 3      | C <sub>L</sub> = 100 pF |     | 60  | ns   |

<sup>†</sup>Only applies when ADS is low.

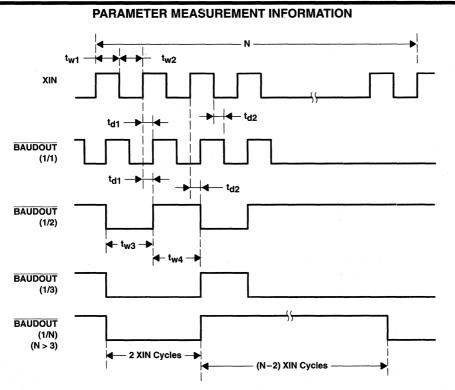

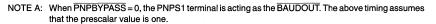

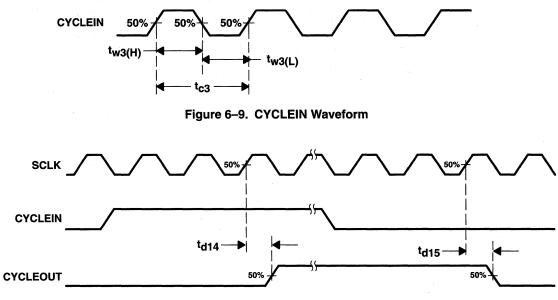

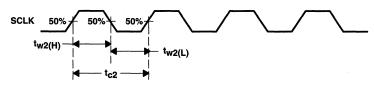

## baud generator switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                 | PARAMETER                     | FIGURE | TEST CONDITIONS                                   | MIN | MAX | UNIT |

|-----------------|-------------------------------|--------|---------------------------------------------------|-----|-----|------|

| <sup>t</sup> w3 | Pulse duration, BAUDOUT low   | 1      | f = 6.25 MHz, CLK ÷ 1,<br>C <sub>L</sub> = 100 pF | 80  |     | ns   |

| t <sub>w4</sub> | Pulse duration, BAUDOUT high  | .1     | f = 6.25 MHz, CLK ÷ 1,<br>C <sub>L</sub> = 100 pF | 80  |     | ns   |

| <sup>t</sup> d1 | Delay time, XIN↑ to BAUDOUT↑  | 1      | C <sub>L</sub> = 100 pF                           |     | 125 | ns   |

| t <sub>d2</sub> | Delay time, XIN↑↓ to BAUDOUT↓ | 1      | CL = 100 pF                                       |     | 125 | ns   |

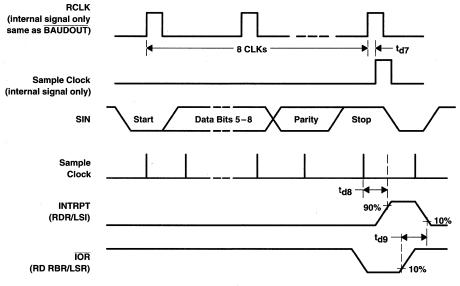

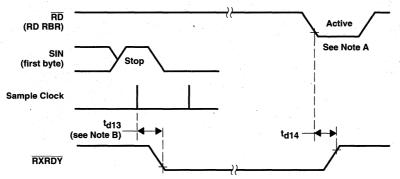

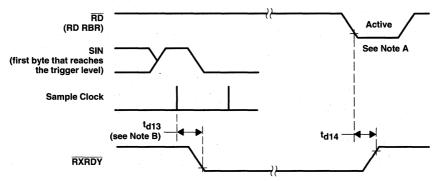

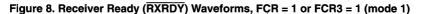

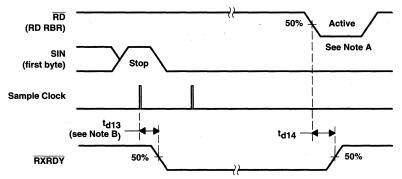

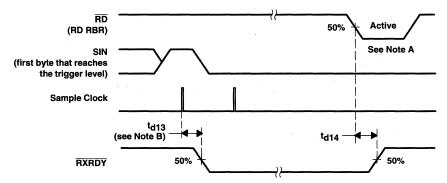

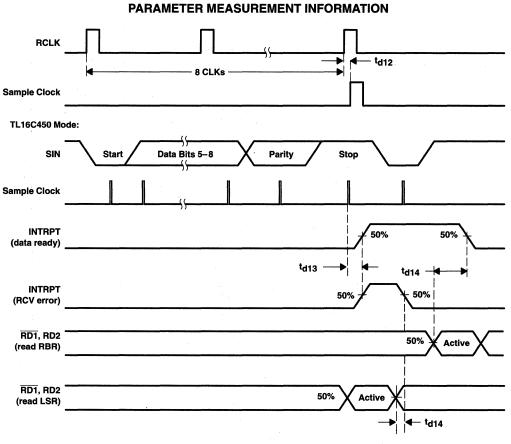

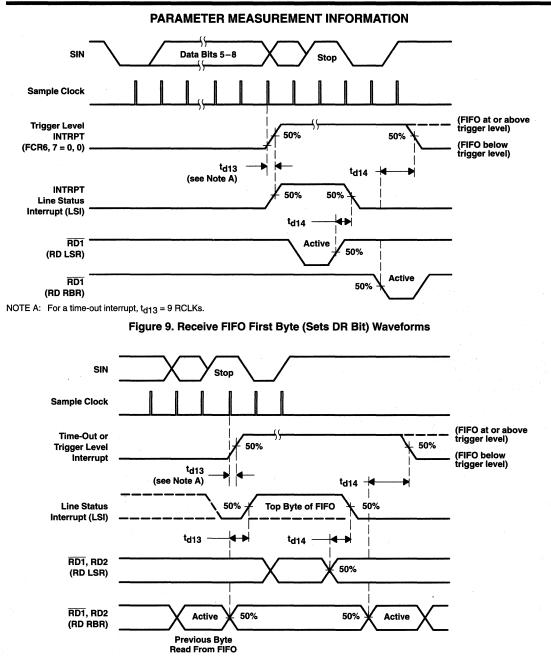

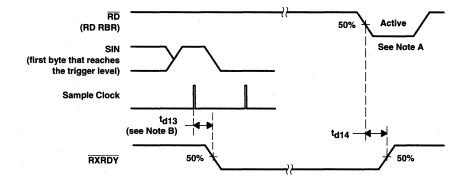

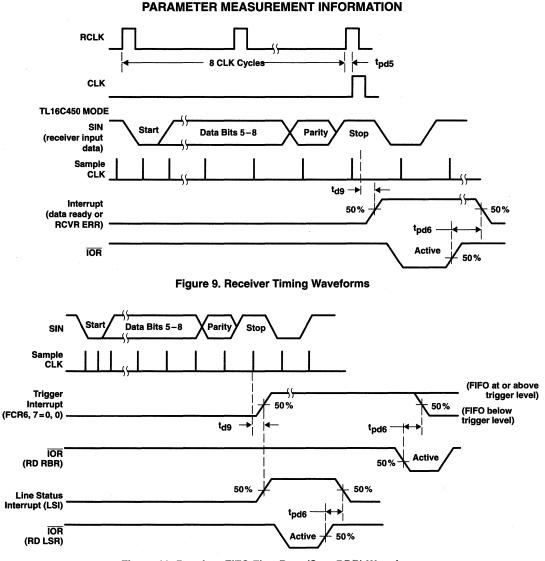

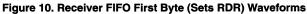

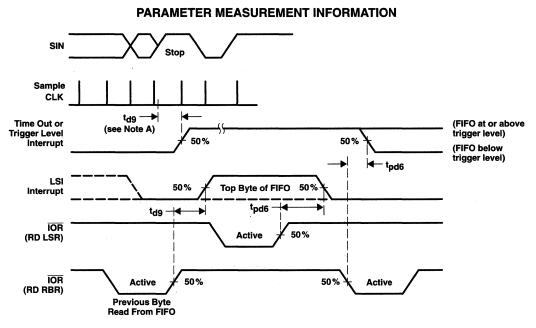

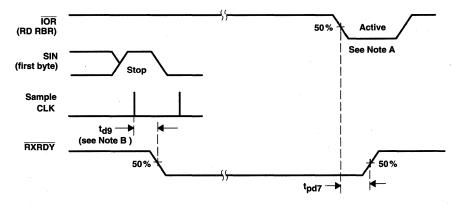

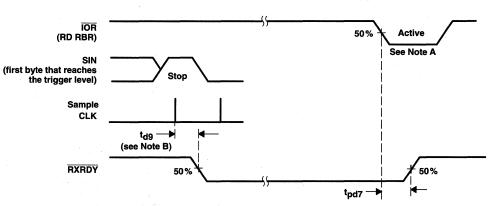

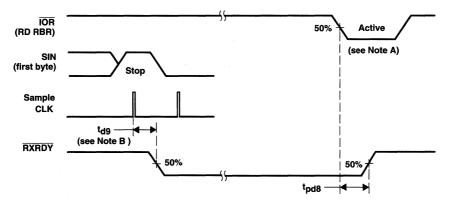

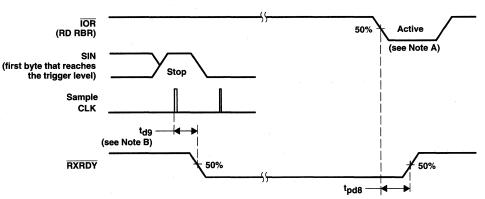

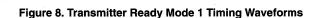

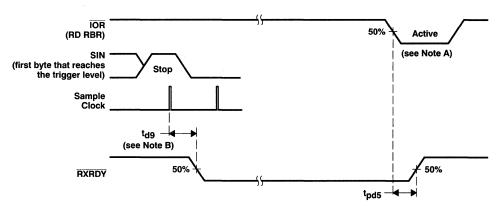

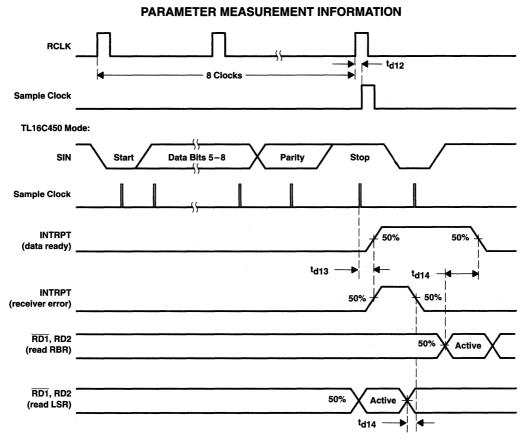

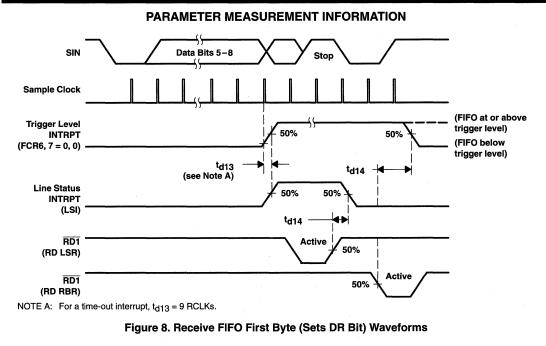

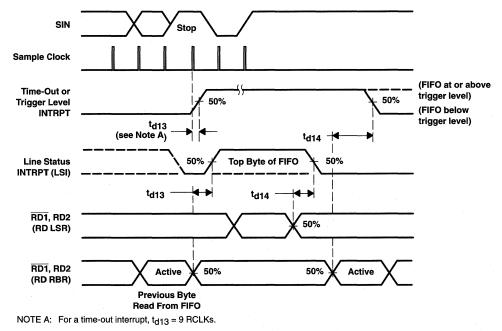

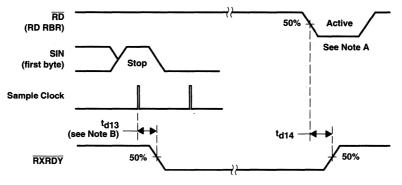

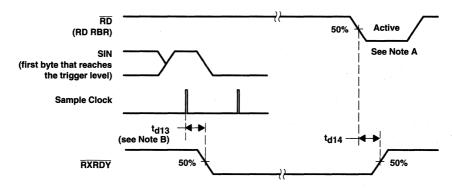

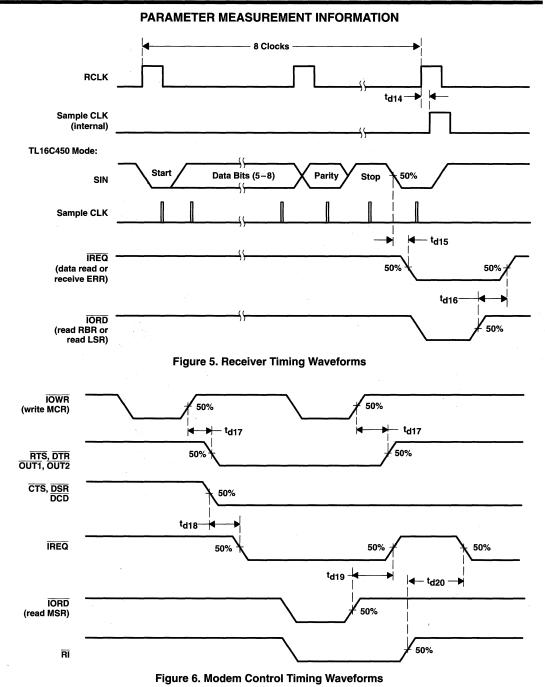

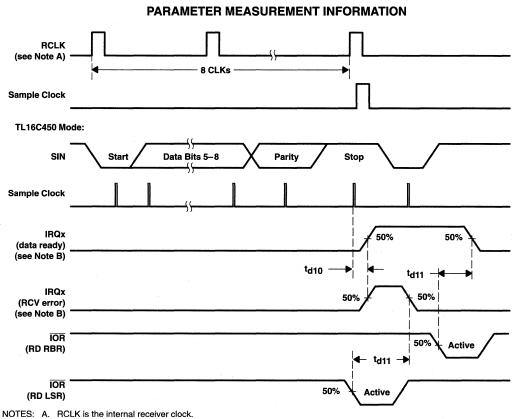

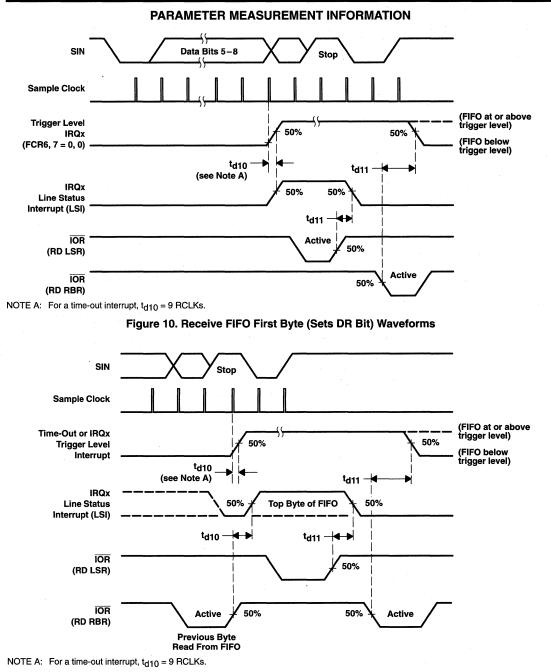

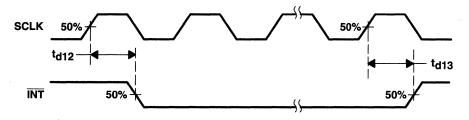

## receiver switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                                                                                           | FIGURE | TEST CONDITIONS         | MIN | MAX | UNIT           |

|------------------|---------------------------------------------------------------------------------------------------------------------|--------|-------------------------|-----|-----|----------------|

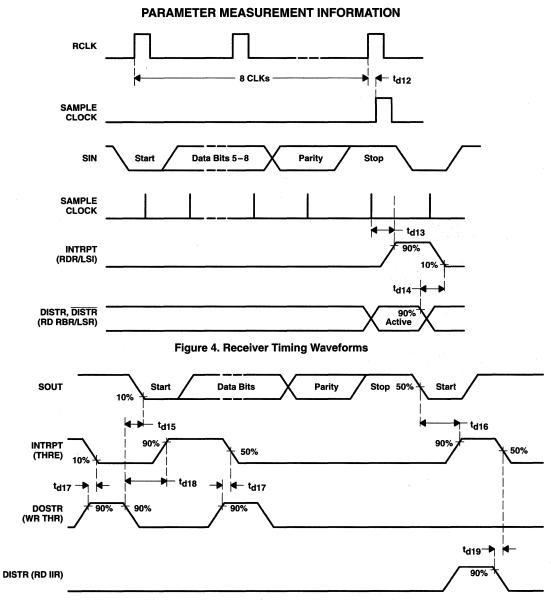

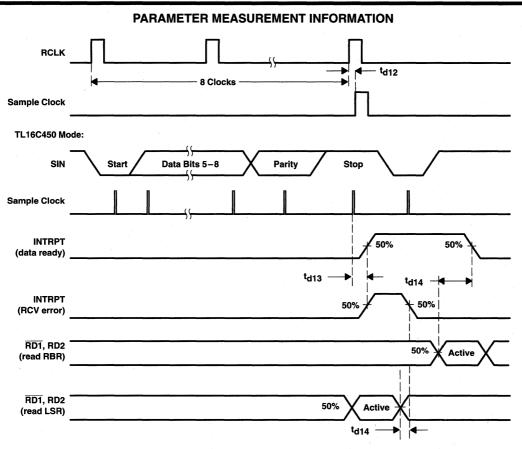

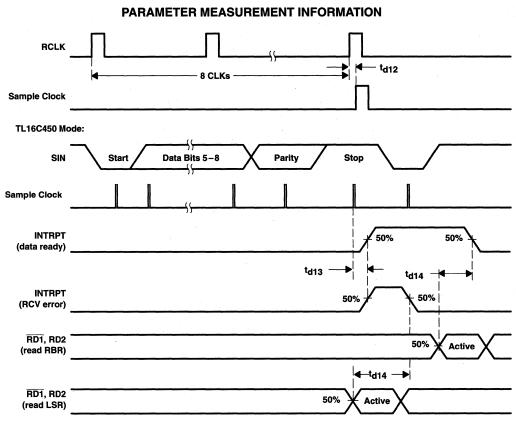

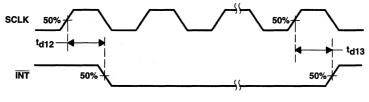

| <sup>t</sup> d12 | Delay time, RCLK to sample clock                                                                                    | 4      |                         |     | 100 | ns             |

| <sup>t</sup> d13 | Delay time, stop to set RCV error interrupt or read RDR to LSI interrupt or stop to $\overrightarrow{\text{RXRDY}}$ | 4      |                         | 1   | 1   | RCLK<br>cycles |

| td14             | Delay time, read RBR/LSR to reset interrupt                                                                         | 4      | C <sub>L</sub> = 100 pF |     | 140 | ns             |

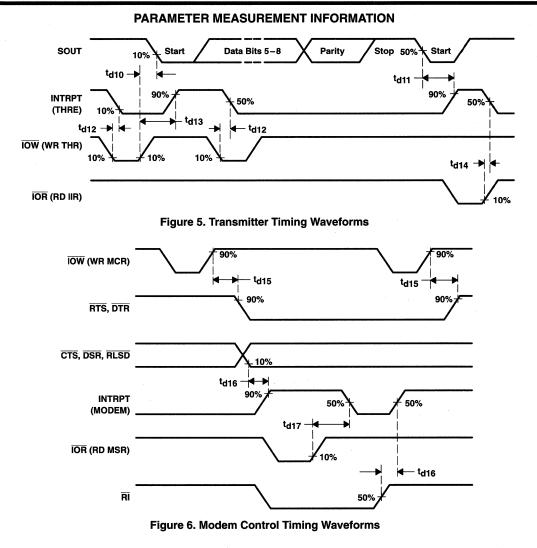

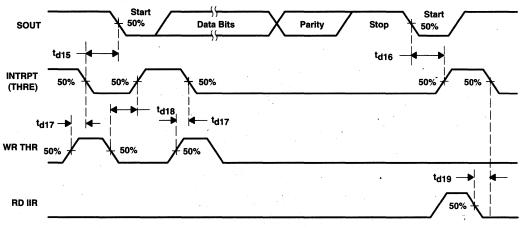

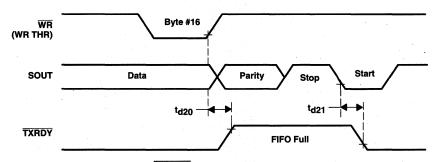

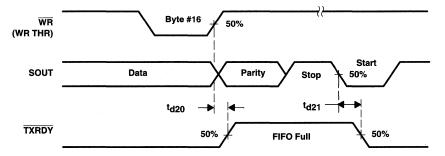

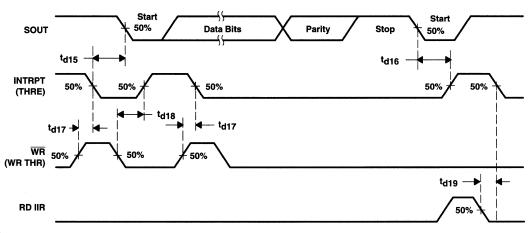

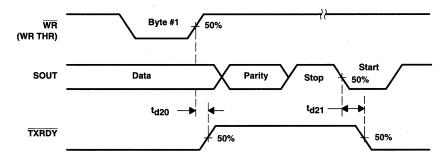

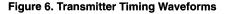

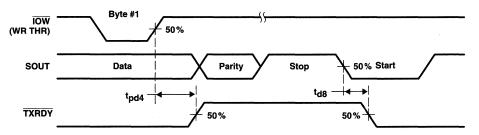

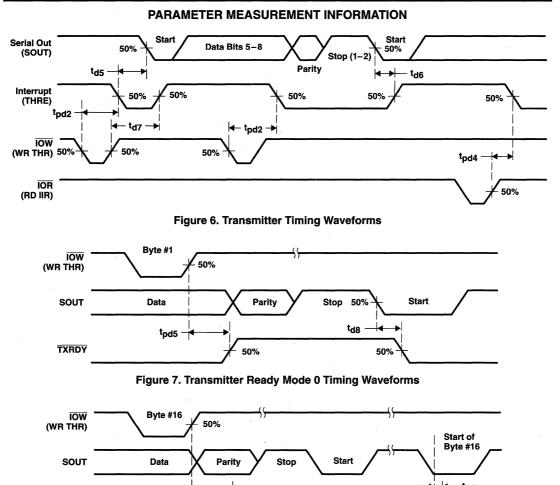

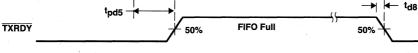

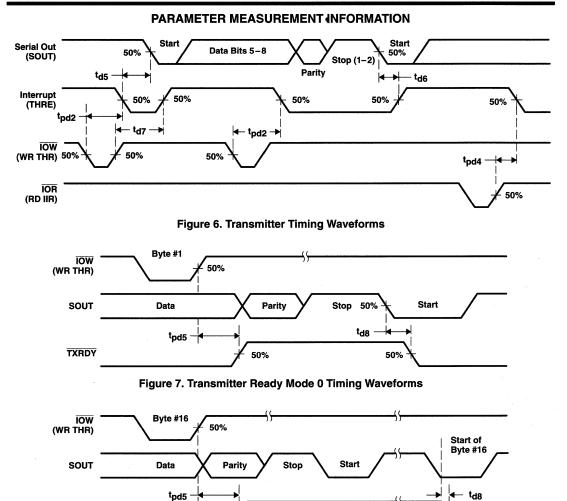

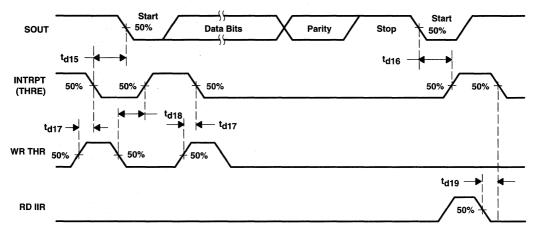

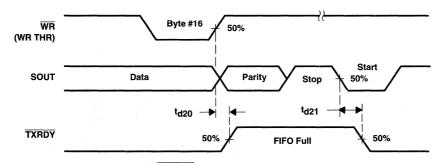

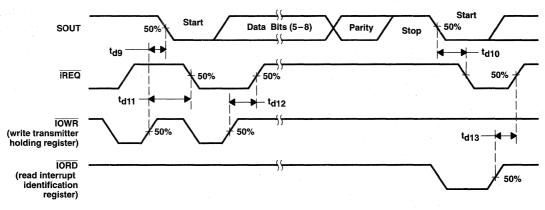

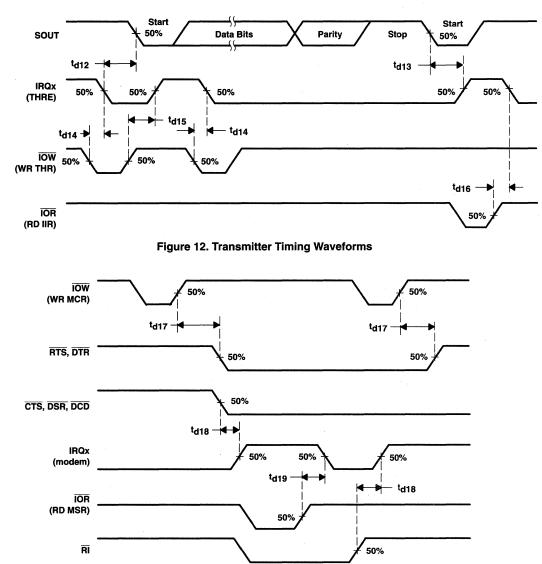

## transmitter switching characteristics over recommended ranges of supply voltage and operating free-air temperature

|                  | PARAMETER                                      | AMETER FIGURE TEST CONDITIONS |                         |    | MAX | UNIT              |

|------------------|------------------------------------------------|-------------------------------|-------------------------|----|-----|-------------------|

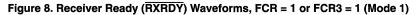

| <sup>t</sup> d15 | Delay time, INTRPT to transmit start           | 5                             |                         | 8  | 24  | baudout<br>cycles |

| <sup>t</sup> d16 | Delay time, start to interrupt                 | 5                             |                         | 8  | 8   | baudout<br>cycles |

| <sup>t</sup> d17 | Delay time, WR THR to reset interrupt          | 5                             | C <sub>L</sub> = 100 pF |    | 140 | ns                |

| <sup>t</sup> d18 | Delay time, initial write to interrupt (THRE)  | 5                             |                         | 16 | 32  | baudout<br>cycles |

| td19             | Delay time, read IIR to reset interrupt (THRE) | 5                             | C <sub>L</sub> = 100 pF |    | 140 | ns                |

SLLS037B - MARCH 1988 - REVISED MARCH 1996

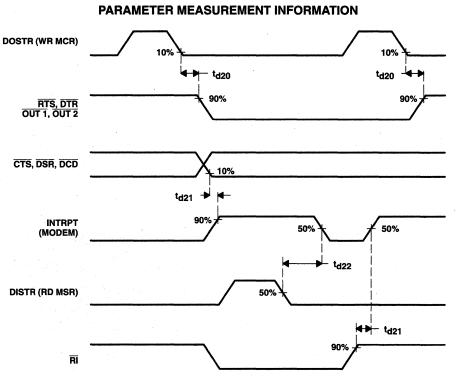

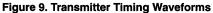

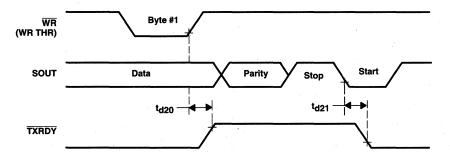

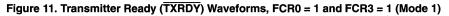

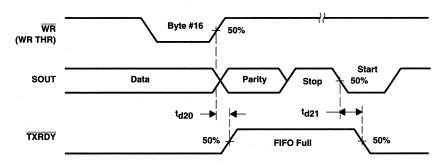

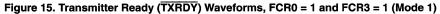

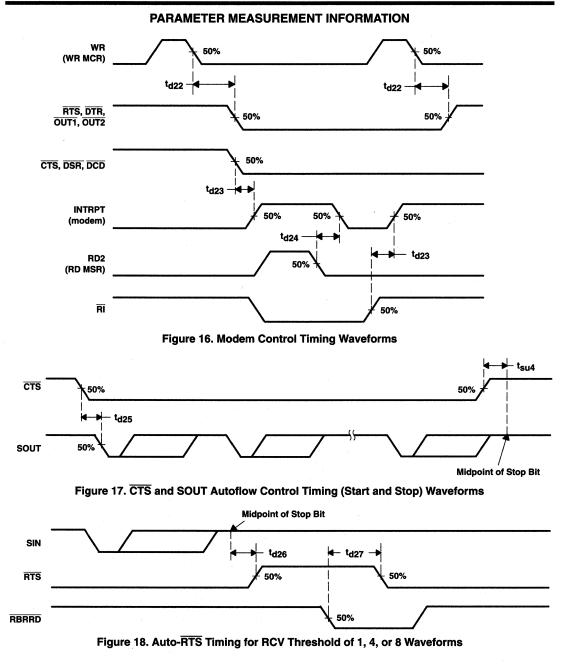

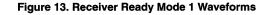

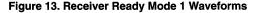

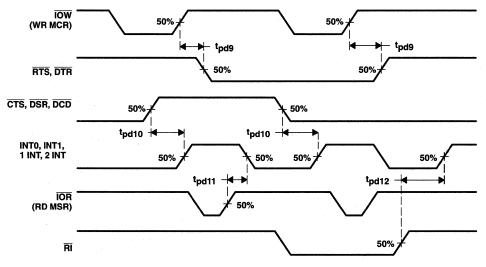

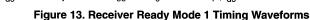

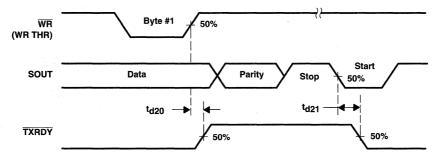

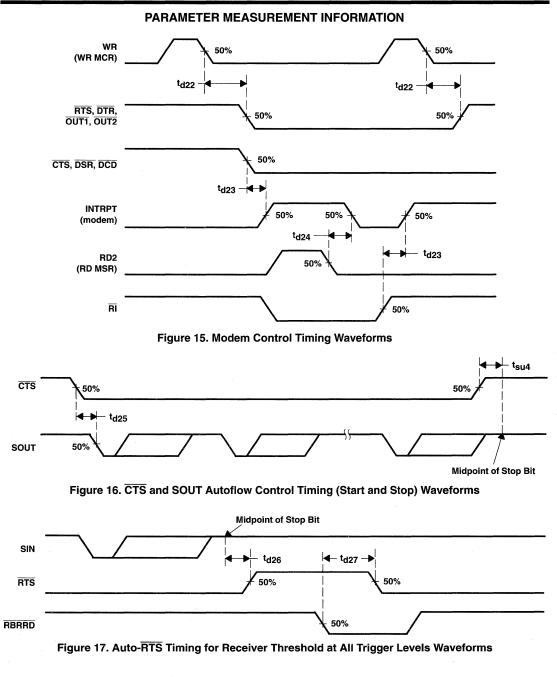

## modem control switching characteristics over recommended ranges of supply voltage and operating free-air temperature

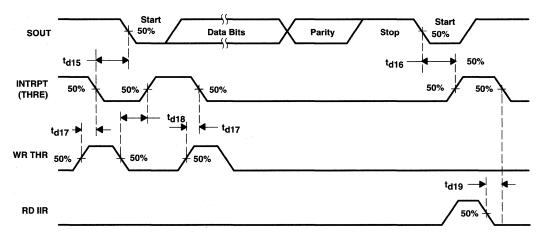

|      | PARAMETER                                    | FIGURE | TEST CONDITIONS         | MIN MAX | UNIT |

|------|----------------------------------------------|--------|-------------------------|---------|------|

| td20 | Delay time, WR MCR to output                 | 6      | C <sub>L</sub> = 100 pF | 100     | ns   |

| td21 | Delay time, modem interrupt to set interrupt | 6      | C <sub>L</sub> = 100 pF | 170     | ns   |

| td22 | Delay time, RD MSR to reset interrupt        | 6      | C <sub>L</sub> = 100 pF | 140     | ns   |

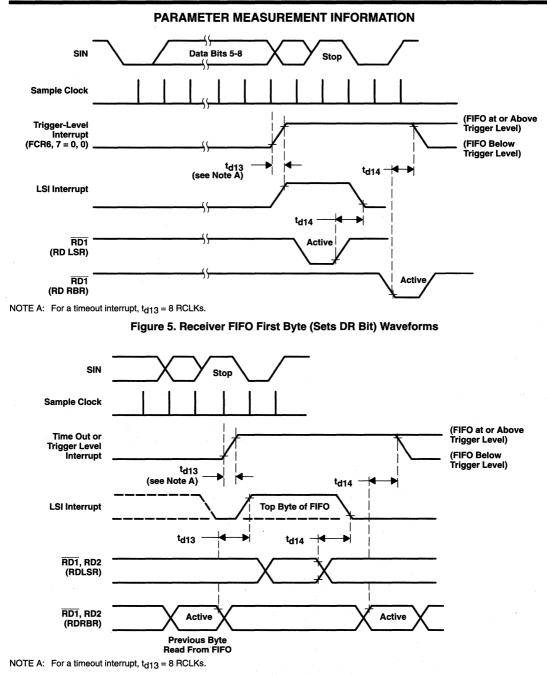

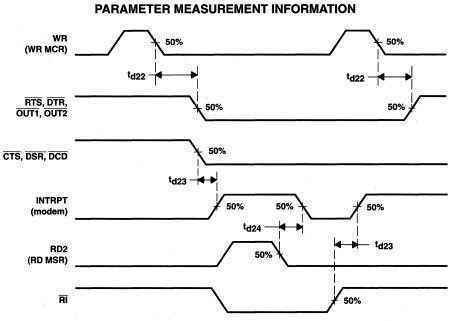

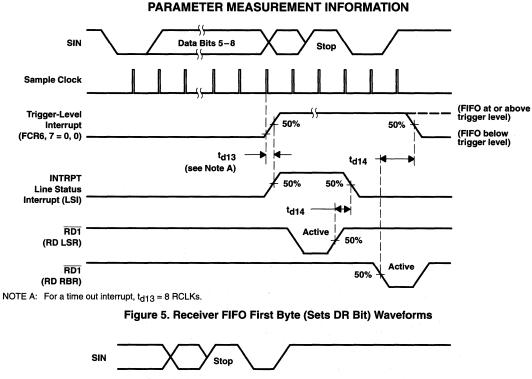

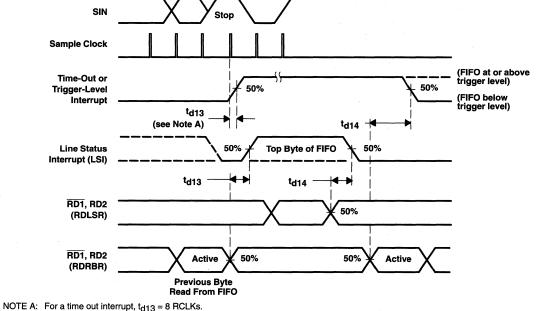

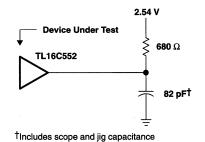

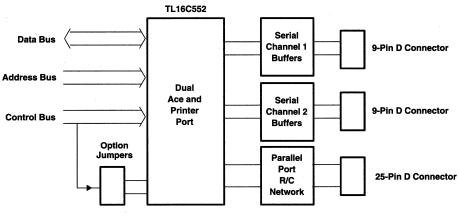

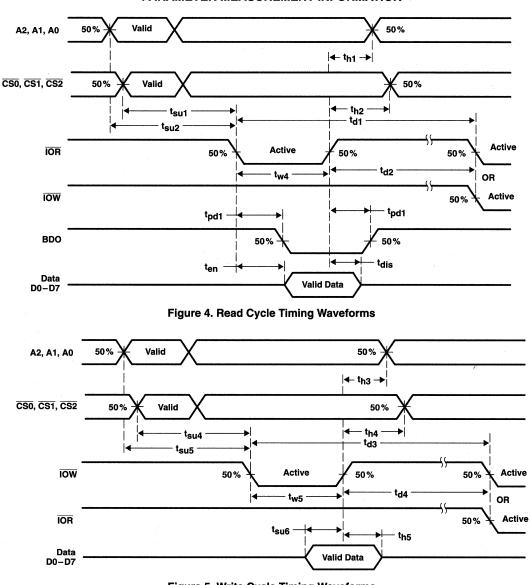

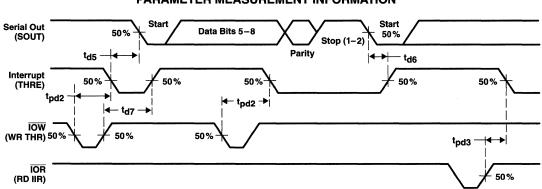

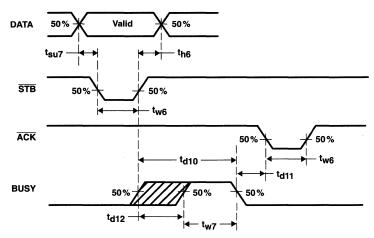

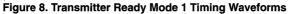

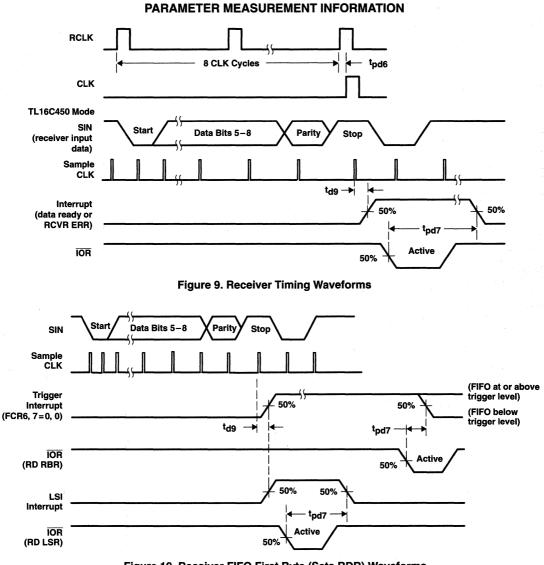

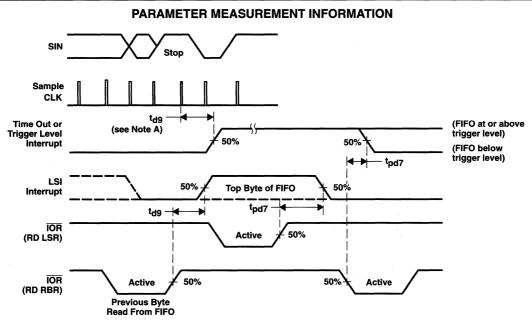

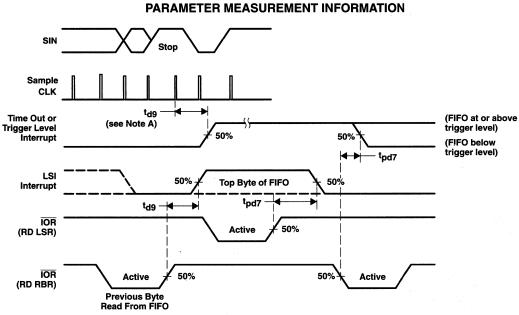

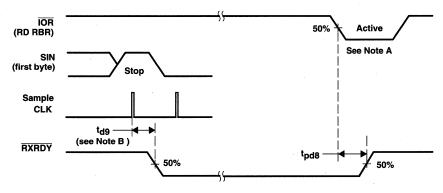

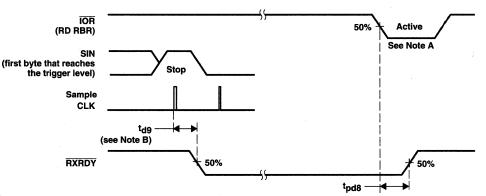

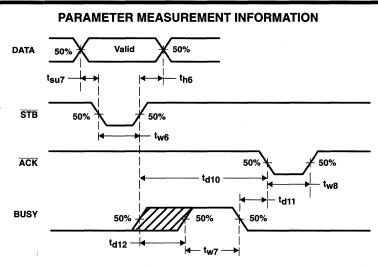

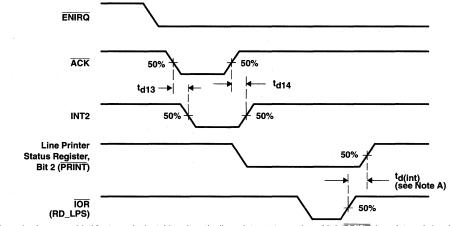

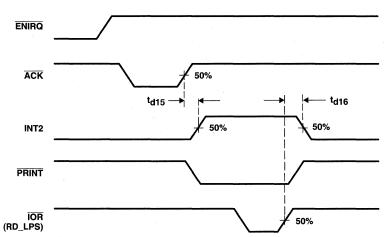

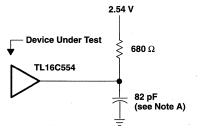

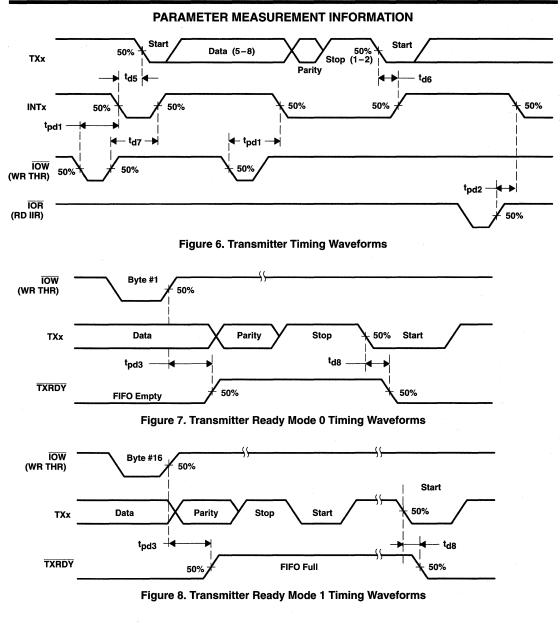

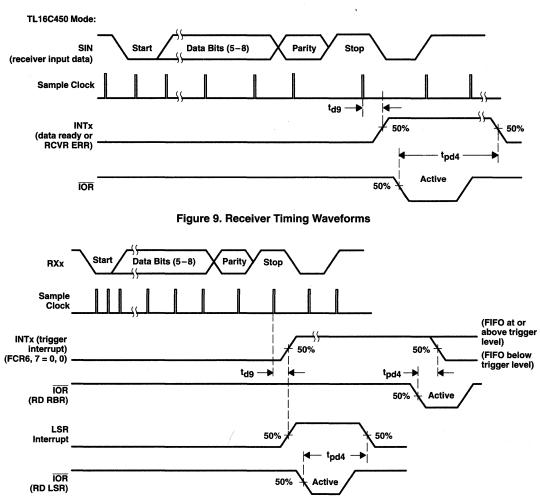

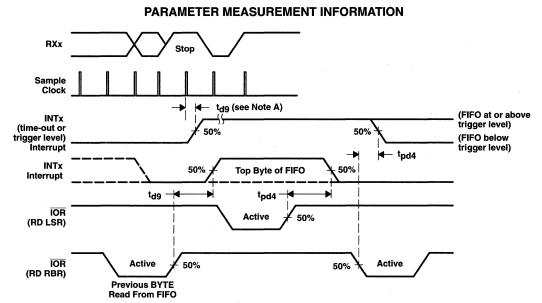

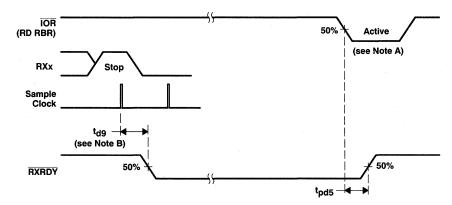

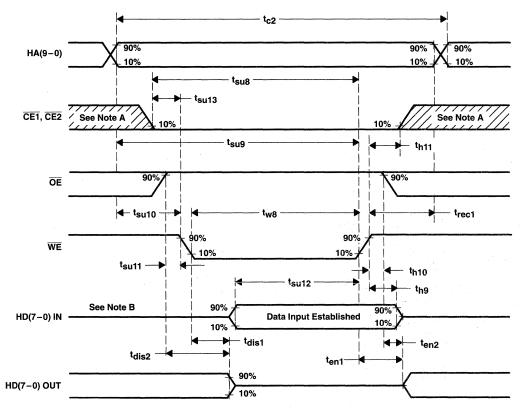

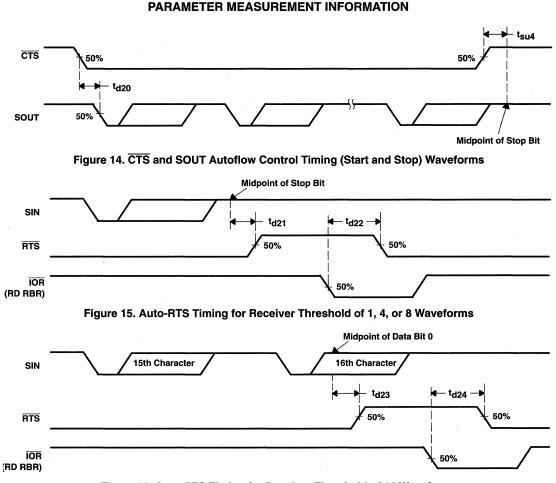

## PARAMETER MEASUREMENT INFORMATION

SLLS037B - MARCH 1988 - REVISED MARCH 1996

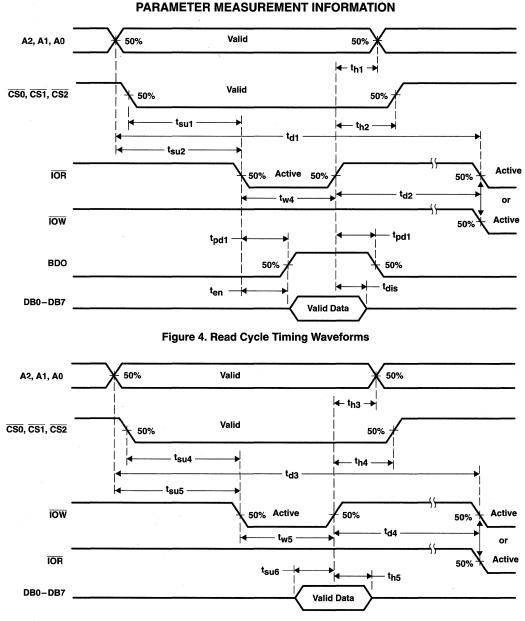

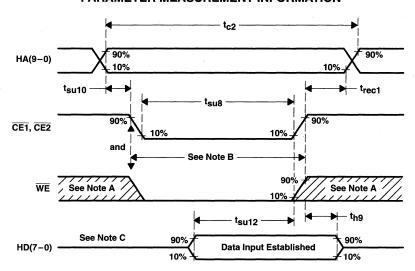

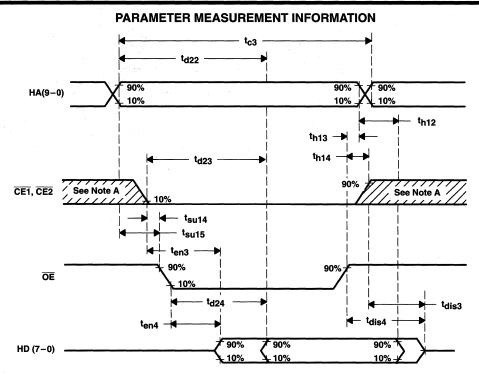

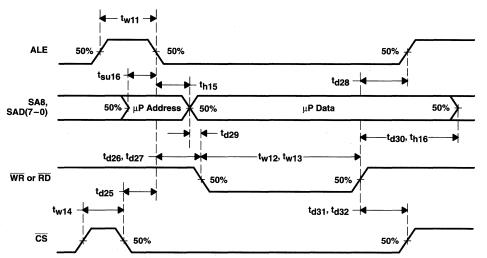

### PARAMETER MEASUREMENT INFORMATION

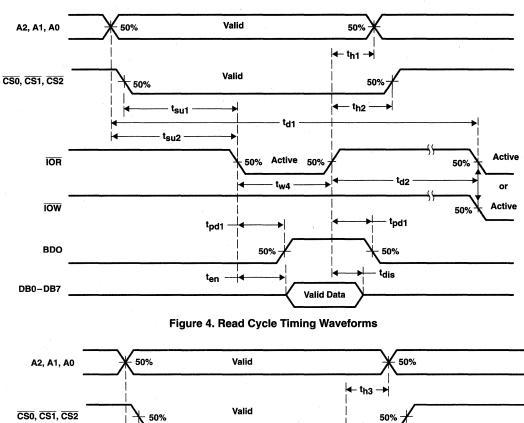

<sup>†</sup> Applicable only when ADS is tied low.

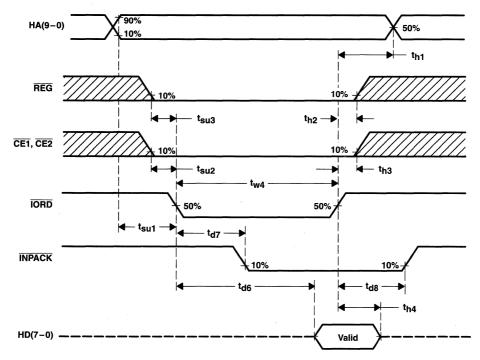

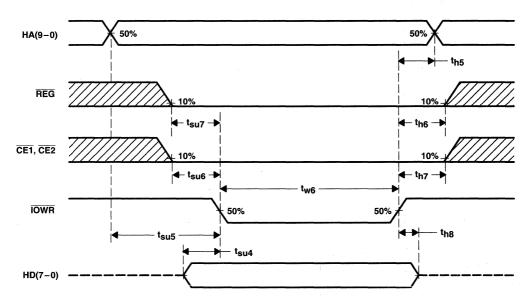

Figure 2. Write Cycle Timing Waveforms

SLLS037B - MARCH 1988 - REVISED MARCH 1996

### **PARAMETER MEASUREMENT INFORMATION**

$^\dagger\,\text{Applicable}$  only when  $\overline{\text{ADS}}$  is tied low.

Figure 3. Read Cycle Timing Waveforms

SLLS037B - MARCH 1988 - REVISED MARCH 1996

SLLS037B - MARCH 1988 - REVISED MARCH 1996

SLLS037B - MARCH 1988 - REVISED MARCH 1996

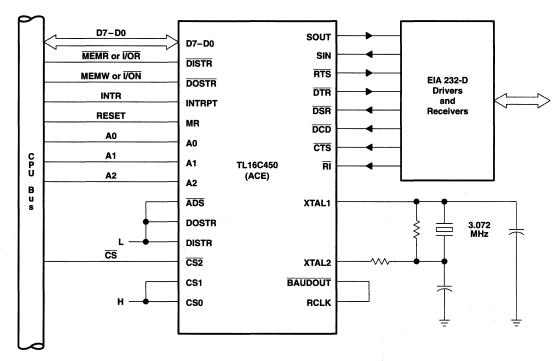

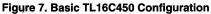

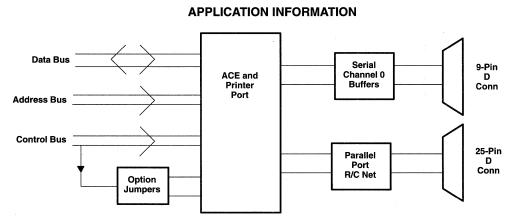

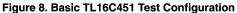

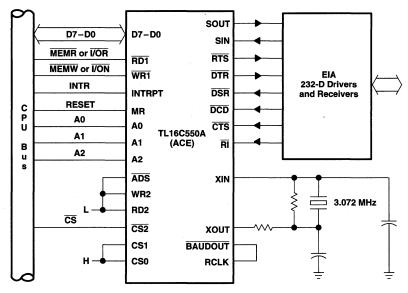

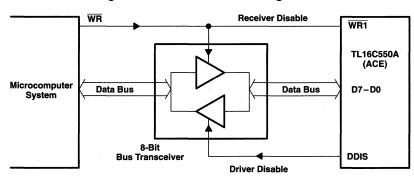

### **APPLICATION INFORMATION**

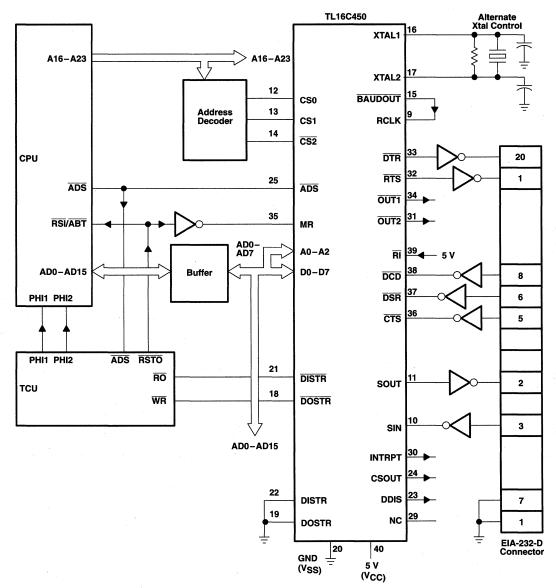

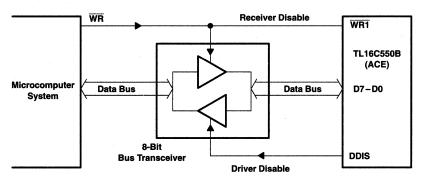

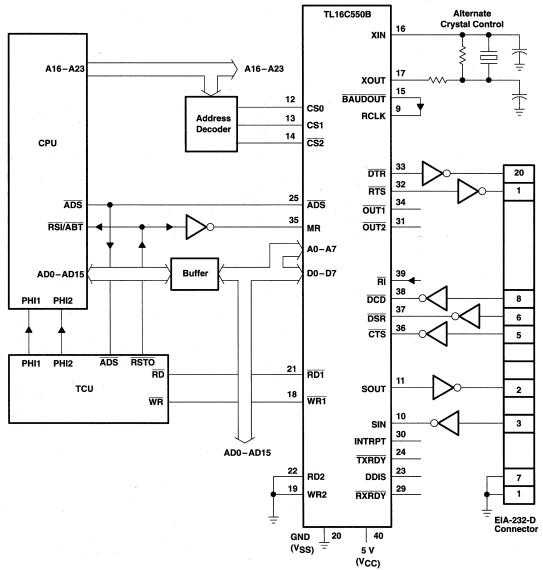

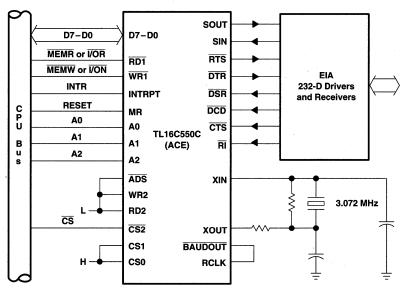

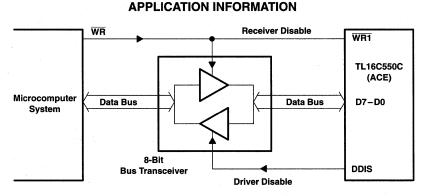

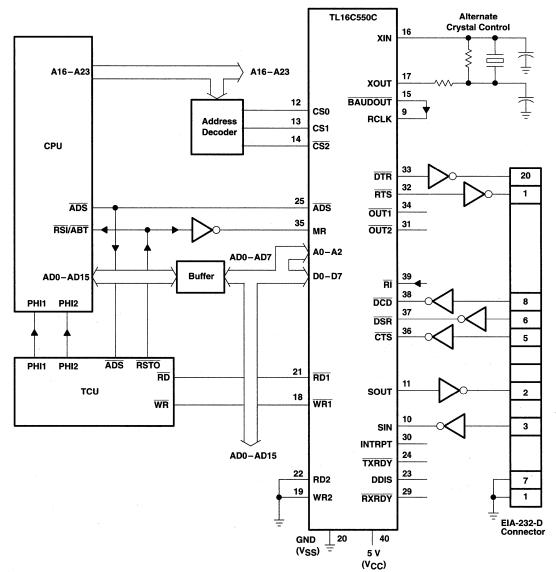

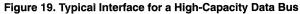

Figure 8. Typical Interface for a High-Capacity Data Bus

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## **APPLICATION INFORMATION**

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## **PRINCIPLES OF OPERATION**

#### **Table 1. Register Selection**

| DLABT | A2 | A1 | A0 | REGISTER                                                     |  |

|-------|----|----|----|--------------------------------------------------------------|--|

| 0     | L  | L  | L  | Receiver buffer (read), transmitter holding register (write) |  |

| 0     | L  | Ļ  | Н  | Interrupt enable                                             |  |

| х     | L  | н  | L  | Interrupt identification (read only)                         |  |

| х     | L  | Н  | Н  | Line control                                                 |  |

| х     | Н  | L  | L  | Modem control                                                |  |

| х     | Н  | L  | н  | Line status                                                  |  |

| х     | Н  | н  | L  | Modem status                                                 |  |

| х     | Н  | н  | н  | Scratch                                                      |  |

| 1     | L  | L  | L  | Divisor latch (LSB)                                          |  |

| 1     | L  | L  | Н  | Divisor latch (MSB)                                          |  |

<sup>†</sup> The divisor latch access bit (DLAB) is the most significant bit of the line control register. The DLAB signal is controlled by writing to this bit location (see Table 3).

## Table 2. ACE Reset Functions

| REGISTER/SIGNAL                             | RESET<br>CONTROL         | RESET STATE                                                            |

|---------------------------------------------|--------------------------|------------------------------------------------------------------------|

| Interrupt enable register                   | Master reset             | All bits low (0-3 forced and 4-7 permanent)                            |

| Interrupt identification register           | Master reset             | Bit 0 is high, bits 1 and 2 are low, and bits 3 –7 are permanently low |

| Line control register                       |                          | All bits low                                                           |

| Modem control register                      | Master reset             | All bits low                                                           |

| Line status register                        | Master reset             | Bits 5 and 6 are high, all other bits are low                          |

| Modem status register                       | Master reset             | Bits 0-3 are low, bits 4-7 are input signals                           |

| SOUT                                        | Master reset             | High                                                                   |

| INTRPT (receiver error flag)                | Read LSR/MR              | Low                                                                    |

| INTRPT (received data available)            | Read RBR/MR              | Low                                                                    |

| INTRPT (transmitter holding register empty) | Read IIR/Write<br>THR/MR | Low                                                                    |

| INTRPT (modem status changes)               | Read MSR/MR              | Low                                                                    |

| OUT2                                        | Master reset             | High                                                                   |

| RTS                                         | Master reset             | High                                                                   |

| DTR                                         | Master reset             | High                                                                   |

| OUT1                                        | Master reset             | High                                                                   |

| Scratch register                            | Master reset             | No effect                                                              |

| Divisor latch (LSB and MSB) register        | Master reset             | No effect                                                              |

| Receiver buffer register                    | Master reset             | No effect                                                              |

| Transmitter holding register                | Master reset             | No effect                                                              |

## TL16C450 ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## PRINCIPLES OF OPERATION

## accessible registers

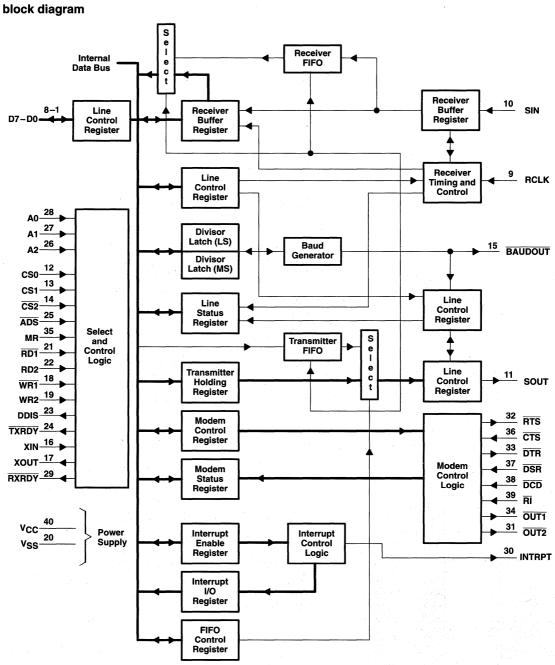

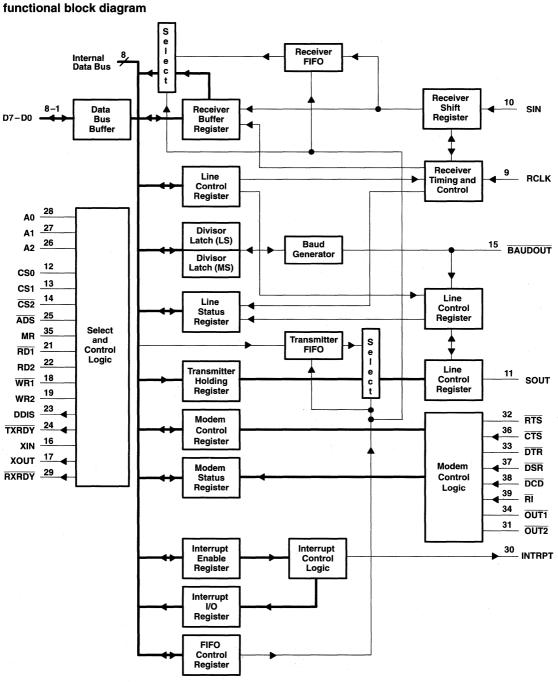

The system programmer, using the CPU, has access to and control over any of the ACE registers that are summarized in Table 3. These registers control ACE operations, receive data, and transmit data. Descriptions of these registers follow Table 3.

|     | REGISTER ADDRESS                                 |                                                       |                                                                              |                                                   |                                             |                                    |                                              |                                              |                     |                           |                  |  |  |

|-----|--------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------|------------------------------------|----------------------------------------------|----------------------------------------------|---------------------|---------------------------|------------------|--|--|

| Bit | O DLAB = 0                                       | O DLAB = 0                                            | 1 DLAB = 0                                                                   | 2                                                 | 3                                           | 4                                  | 5                                            | 6                                            | 7                   | O DLAB = 1                | 1<br>DLAB<br>= 0 |  |  |

| No. | Receiver<br>Buffer<br>Register<br>(Read<br>Only) | Transmitter<br>Holding<br>Register<br>(Write<br>Only) | Interrupt<br>Enable<br>Register<br>IER                                       | Interrupt<br>Ident.<br>Register<br>(Read<br>Only) | Line<br>Control<br>Register<br>LCR          | Modem<br>Control<br>Register       | Line<br>Status<br>Register                   | Modem<br>Status<br>Register                  | Scratch<br>Register | Divisor<br>Latch<br>(LSB) | Latch<br>(MSB)   |  |  |

|     | RBR                                              | THR                                                   | IER                                                                          | IIR                                               | LCR                                         | MCR                                | LSR                                          | MSR                                          | SCR                 | DLL                       | DLM              |  |  |

| 0   | Data Bit 0*                                      | Data Bit 0                                            | Enable<br>Received<br>Data<br>Available<br>Interrupt<br>(ERBF)               | "0" If<br>Interrupt<br>Pending                    | Word<br>Length<br>Select<br>Bit 0<br>(WLSO) | Data<br>Terminal<br>Ready<br>(DTR) | Data<br>Ready<br>(DR)                        | Delta<br>Clear<br>to Send<br>(DCTS)          | Bit 0               | Bit 0                     | Bit 8            |  |  |

| 1   | Data Bit 1                                       | Data Bit 1                                            | Enable<br>Transmitter<br>Holding<br>Register<br>Empty<br>Interrupt<br>(ETBE) | Interrupt<br>ID<br>Bit (0)                        | Word<br>Length<br>Select<br>Bit 1<br>(WLS1) | Request<br>to Send<br>(RTS)        | Overrun<br>Error<br>(OE)                     | Delta<br>Data<br>Set<br>Ready<br>(DDSR)      | Bit 1               | Bit 1                     | Bit 9            |  |  |

| 2   | Data Bit 2                                       | Data Bit 2                                            | Enable<br>Receiver<br>Line Status<br>Interrupt<br>(ELSI)                     | Interrupt<br>ID<br>Bit (1)                        | Number of<br>Stop Bits<br>(STB)             | Out 1                              | Parity<br>Error<br>(PE)                      | Trailing<br>Edge Ring<br>Indicator<br>(TERI) | Bit 2               | Bit 2                     | Bit 10           |  |  |

| 3   | Data Bit 3                                       | Data Bit 3                                            | Enable<br>Modem<br>Status<br>Interrupt<br>(EDSSI)                            | 0                                                 | Parity<br>Enable<br>(PEN)                   | Out 2                              | Framing<br>Error<br>(FE)                     | Delta<br>Data<br>Carrier<br>Detect<br>(DDCD) | Bit 3               | Bit 3                     | Bit 11           |  |  |

| 4   | Data Bit 4                                       | Data Bit 4                                            | 0                                                                            | 0                                                 | Even<br>Parity<br>Select<br>(EPS)           | Loop                               | Break<br>Interrupt<br>(BI)                   | Clear<br>to Send<br>(CTS)                    | Bit 4               | Bit 4                     | Bit 12           |  |  |

| 5   | Data Bit 5                                       | Data Bit 5                                            | 0                                                                            | 0                                                 | Stick<br>Parity                             | 0                                  | Transmitter<br>Holding<br>Register<br>(THRE) | Data<br>Set<br>Ready<br>(DSR)                | Bit 5               | Bit 5                     | Bit 13           |  |  |

| 6   | Data Bit 6                                       | Data Bit 6                                            | 0                                                                            | 0                                                 | Set<br>Break                                | 0                                  | Transmitter<br>Empty<br>(TEMT)               | Ring<br>Indicator<br>(RI)                    | Bit 6               | Bit 6                     | Bit 14           |  |  |

| 7   | Data Bit 7                                       | Data Bit 7                                            | 0                                                                            | 0                                                 | Divisor<br>Latch<br>Access<br>Bit<br>(DLAB) | 0                                  | . 0                                          | Data<br>Carrier<br>Detect<br>(DCD)           | Bit 7               | Bit 7                     | Bit 15           |  |  |

| Table 3. Summa | y of Accessible Registe | rs |

|----------------|-------------------------|----|

|----------------|-------------------------|----|

\*Bit 0 is the least significant bit. It is the first bit serially transmitted or received.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## PRINCIPLES OF OPERATION

#### interrupt enable register (IER)

The IER enables each of the four types of interrupts (refer to Table 4) and the INTRPT output signal in response to an interrupt generation. By clearing bits 0 - 3, the IER can also disable the interrupt system. The contents of this register are summarized in Table 3 and are described in the following bulleted list.

- Bit 0: This bit, when set, enables the received data available interrupt.

- Bit 1: This bit, when set, enables the THRE interrupt.

- Bit 2: This bit, when set, enables the receiver line status interrupt.

- Bit 3: This bit, when set, enables the modem status interrupt.

- Bits 4 7: These bits in the IER are not used and are always cleared.

#### interrupt identification register (IIR)

The ACE has an on-chip interrupt generation and prioritization capability that permits a flexible interface with most microprocessors.

The ACE provides four prioritized levels of interrupts:

- Priority 1 Receiver line status (highest priority)

- Priority 2 Receiver data ready or receiver character time out

- Priority 3 Transmitter holding register empty

- Priority 4–Modem status (lowest priority)

When an interrupt is generated, the IIR indicates that an interrupt is pending and the type of interrupt in its three least significant bits (bits 0, 1, and 2). The contents of this register are summarized in Table 3 and described in Table 4.

- Bit 0: This bit can be used either in a hardwire prioritized or polled interrupt system. When bit 0 is cleared, an interrupt is pending. When bit 0 is set, no interrupt is pending.

- Bits 1 and 2: These two bits identify the highest priority interrupt pending as indicated in Table 4.

- Bits 3 7: These bits in the IIR are not used and are always clear.

## TL16C450 ASYNCHRONOUS COMMUNICATIONS ELEMENT

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## **PRINCIPLES OF OPERATION**

## interrupt identification register (IIR) (continued)

| IDE   | NTERRUPT<br>NTIFICATI<br>REGISTER | ON    | PRIORITY<br>LEVEL | INTERRUPT TYPE                                  | INTERRUPT SOURCE                                                            | INTERRUPT RESET<br>METHOD                                                                                                           |

|-------|-----------------------------------|-------|-------------------|-------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| BIT 2 | BIT 1                             | BIT 0 |                   |                                                 |                                                                             |                                                                                                                                     |

| 0     | 0                                 | 1     | None              | None                                            | None                                                                        | <u> </u>                                                                                                                            |

| 1     | 1                                 | 0     | 1                 | Receiver line status                            | Overrun error, parity error,<br>framing error or break<br>interrupt         | Reading the line status register                                                                                                    |

| 1     | 0                                 | 0     | 2                 | Received data available Receiver data available |                                                                             | Reading the receiver buffer<br>Buffer register                                                                                      |

| 0     | 1                                 | 0     | 3                 | Transmitter holding register<br>empty           | Transmitter holding register<br>empty                                       | Reading the interrupt<br>identification register (if<br>source of interrupt) or writing<br>into the transmitter holding<br>register |

| 0     | 0                                 | 0     | 4                 | Modem status                                    | Clear to send, data set<br>ready, ring indicator, or data<br>carrier detect | Reading the modem status register                                                                                                   |

#### **Table 4. Interrupt Control Functions**

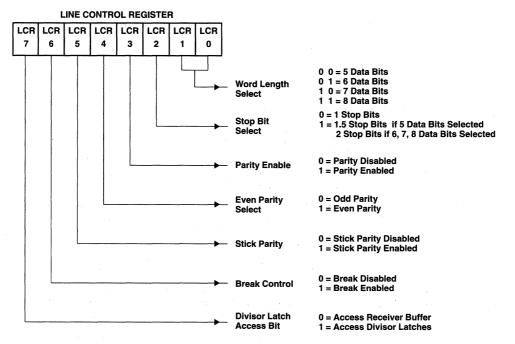

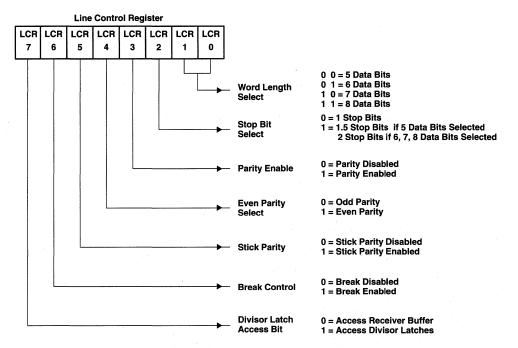

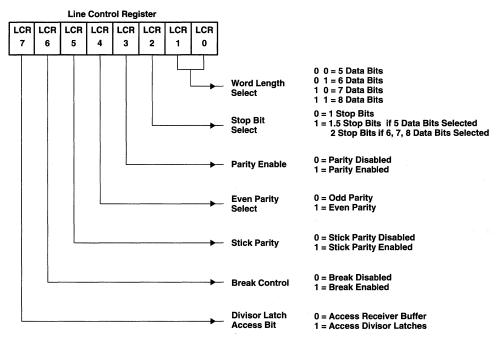

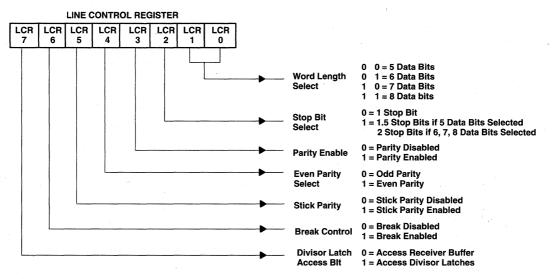

#### line control register (LCR)

The system programmer controls the format of the asynchronous data communication exchange through the LCR. In addition, the programmer is able to retrieve, inspect, and modify the contents of the LCR; this eliminates the need for separate storage of the line characteristics in system memory. The contents of this register are summarized in Table 3 and are described in the following bulleted list.

• Bits 0 and 1: These two bits specify the number of bits in each transmitted or received serial character. These bits are encoded as shown in Table 5.

| Bit 1 | Bit 0 | Word Length |  |

|-------|-------|-------------|--|

| 0     | 0     | 5 Bits      |  |

| 0     | 1     | 6 Bits      |  |

| 1     | 0     | 7 Bits      |  |

| 1     | 1     | 8 Bits      |  |

## Table 5. Serial Character Word Length

• Bit 2: This bit specifies either one, one and one-half, or two stop bits in each transmitted character. When bit 2 is cleared, one stop bit is generated in the data. When bit 2 is set, the number of stop bits generated is dependent on the word length selected with bits 0 and 1. The receiver checks the first stop bit only, regardless of the number of stop bits selected. The number of stop bits generated, in relation to word length and bit 2, is shown in Table 6.

SLLS037B - MARCH 1988 - REVISED MARCH 1996

## PRINCIPLES OF OPERATION

## line control register (LCR) (continued)

| Bit 2 | Word Length Selected<br>by Bits 1 and 2 | Number of Stop<br>Bits Generated |

|-------|-----------------------------------------|----------------------------------|

| 0     | Any word length                         | 1                                |

| 1     | 5 bits                                  | 1 1/2                            |

| 1     | 6 bits                                  | 2                                |

| 1     | 7 bits                                  | 2                                |

| 1     | 8 bits                                  | 2                                |

#### Table 6. Number of Stop Bits Generated

- Bit 3: This bit is the parity enable bit. When bit 3 is set, a parity bit is generated in transmitted data between the last data word bit and the first stop bit. In received data, if bit 3 is set, parity is checked. When bit 3 is cleared, no parity is generated or checked.

- Bit 4: This bit is the even parity select bit. When parity is enabled (bit 3 is set) and bit 4 is set, even parity (an even number of logic 1s is in the data and parity bits) is selected. When parity is enabled (bit 3 is set) and bit 4 is clear, odd parity (an odd number of logic 1s) is selected.

- Bit 5: This is the stick parity bit. When bits 3, 4, and 5 are set, the parity bit is transmitted and checked as cleared. When bits 3 and 5 are set and bit 4 is cleared, the parity bit is transmitted and checked as set.

- Bit 6: This bit is the break control bit. Bit 6 is set to force a break condition, i.e, a condition where the serial

output terminal (SOUT) is forced to the spacing (cleared) state. When bit 6 is cleared, the break condition

is disabled. The break condition has no affect on the transmitter logic, it only affects the serial output.

- Bit 7: This bit is the divisor latch access bit (DLAB). Bit 7 must be set to access the divisor latches of the baud generator during a read or write. Bit 7 must be cleared during a read or write to access the receiver buffer, the THR, or the IER.

## line status register (LSR)<sup>†</sup>

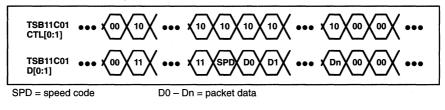

The LSR provides information to the CPU concerning the status of data transfers. The contents of this register are summarized in Table 3 and are described in the following bulleted list.