## SunDiagnostic Executive User's Guide For MC68020, MC68030, and SF9010IU (SPARC) Based Sytems

| fica y constant and an |                                        |  |

|------------------------------------------------------------|----------------------------------------|--|

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

| <b>NR_221</b> 2111111111111111111111111111111111           | 50000000000000000000000000000000000000 |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

|                                                            |                                        |  |

Part Number: 800-3273-10 Revision: A of 30 June 1989

## SunDiagnostic Executive User's Guide For MC68020, MC68030, and SF9010IU (SPARC) Based Systems

Sun Microsystems, Inc. • 2550 Garcia Avenue • Mountain View, CA 94043 • 415-960-1300

The Sun logo, Sun Microsystems, and Sun Workstation are registered trademarks of Sun Microsystems, Inc.

Sun, Sun-2, Sun-3, Sun-4, Sun386*i*, SunInstall, SunOS, SunView, NFS, NeWS, and SPARC are trademarks of Sun Microsystems, Inc.

UNIX is a registered trademark of AT&T.

All other products or services mentioned in this document are identified by the trademarks or service marks of their respective companies or organizations.

ALM and ALM2 are trademarks of Sun Microsystems, Inc.

SunIPC is a trademark of Sun Microsystems, Incorporated.

Multibus is a trademark of Intel Corporation.

Tapemaster is a trademark of Ciprico, Inc.

Copyright © 1989 Sun Microsystems, Inc. - Printed in U.S.A.

All rights reserved. No part of this work covered by copyright hereon may be reproduced in any form or by any means – graphic, electronic, or mechanical – including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owner.

Restricted rights legend: use, duplication, or disclosure by the U.S. government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and in similar clauses in the FAR and NASA FAR Supplement.

The Sun Graphical User Interface was developed by Sun Microsystems Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees.

## Contents

| Chap                                                               | ter 1 Introduction                                                               | 3                                    |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------|

| 1.1.                                                               | Audience                                                                         | 3                                    |

| 1.2.                                                               | Common Terms                                                                     | 3                                    |

| 1.3.                                                               | Conventions                                                                      | 3                                    |

|                                                                    | Fonts                                                                            | 3                                    |

|                                                                    | Hexadecimal Values                                                               | 4                                    |

| 1.4.                                                               | References                                                                       | 4                                    |

| 1.5.                                                               | The Exec Tape                                                                    | 4                                    |

| 1.6.                                                               | Organization of This Manual                                                      | 4                                    |

| 1.7.                                                               | Required Equipment                                                               | 5                                    |

| 1.8.                                                               | Software Requirements                                                            | 5                                    |

|                                                                    | Configuring a Terminal                                                           | 5                                    |

|                                                                    |                                                                                  | 5                                    |

| Chap                                                               | ter 2 Using the SunDiagnostic Executive                                          | 9                                    |

|                                                                    |                                                                                  | _                                    |

| 2.1.                                                               | ter 2 Using the SunDiagnostic Executive                                          | 9                                    |

| 2.1.<br>2.2.                                                       | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9                        |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> </ol>               | ter 2 Using the SunDiagnostic Executive<br>What This Chapter Contains<br>History | <b>9</b><br>9<br>9                   |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> </ol> | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9<br>9<br>9              |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> </ol> | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9<br>9<br>10<br>14       |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> </ol> | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9<br>9<br>10<br>14       |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> </ol> | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9<br>9<br>10<br>14<br>14 |

| <ol> <li>2.1.</li> <li>2.2.</li> <li>2.3.</li> <li>2.4.</li> </ol> | ter 2 Using the SunDiagnostic Executive                                          | <b>9</b><br>9<br>9<br>10<br>14<br>14 |

| 2.6. The Exec Environment                           | 22 |

|-----------------------------------------------------|----|

| The Menu Perspective                                | 22 |

| The Operating System Perspective                    | 23 |

| 2.7. User Interface                                 | 25 |

| Menu Structure                                      | 25 |

| Global Options                                      | 26 |

| Command Line Syntax                                 | 27 |

| Command Parameters                                  | 27 |

| Special Characters                                  | 28 |

| 2.8. Exec Menus                                     | 29 |

| The Main Menu                                       | 29 |

| The Environment Menu                                | 30 |

| The Options Menu                                    | 35 |

| Diagnostics Menu                                    | 36 |

| Starting A Diagnostic                               | 39 |

| Status Menu                                         | 39 |

| Log Menu                                            | 40 |

| 2.9. Writing Script Files                           | 41 |

| 2.10. Remote Execution and the Network Console      | 42 |

|                                                     |    |

| Chapter 3 Sun-3/400 Series Central Cache Diagnostic | 47 |

| 3.1. General Description                            | 47 |

| 3.2. What This Chapter Contains                     | 47 |

| 3.3. Overview of the Diagnostic                     | 47 |

| 3.4. Hardware Requirements                          | 47 |

| 3.5. Firmware Requirements                          | 48 |

| 3.6. Additional Requirements                        | 48 |

| 3.7. User Interface                                 | 48 |

| 3.8. Starting the Diagnostic                        | 48 |

| 3.9. The Diagnostic Menus                           | 48 |

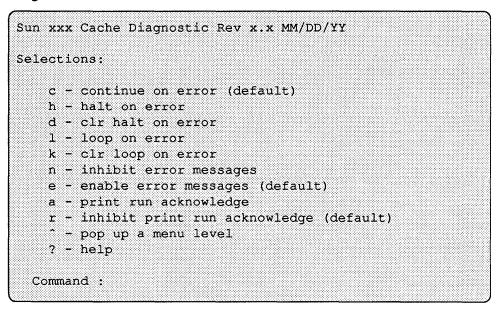

| Main Menu                                           | 49 |

| Command Parameters                                  | 49 |

| Environmental Parameters                            | 51 |

|        | All Tests in Sequence                 |

|--------|---------------------------------------|

|        | Default Test Sequence                 |

|        | Quick Test Sequence                   |

|        | Level 1 Menu                          |

|        | Level 2 Menu                          |

|        | Cross Boundary Menu                   |

|        | Blockcopy Menu                        |

|        | Options Menu                          |

|        | Display Error Log                     |

| 3.10.  | Messages                              |

| 3.11.  | Glossary                              |

| Chapte | er 4 SPARCsystem 330 Cache Diagnostic |

| -      | General Description                   |

|        | What This Chapter Contains            |

|        | Overview of the Diagnostic            |

|        | Hardware Requirements                 |

|        | User Interface                        |

|        | Starting the Diagnostic               |

|        | The Diagnostic Menus                  |

|        | Main Menu                             |

|        | Parameters                            |

|        | Data RAM Test Menu                    |

|        | Tag RAM Test Menu                     |

|        | Read Menu                             |

|        | Write Menu                            |

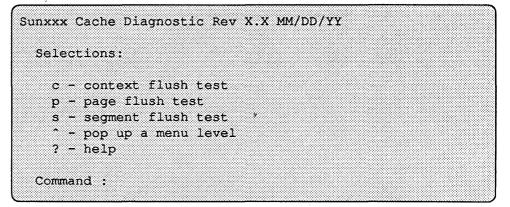

|        | Flush Menu                            |

|        | Debug Menu                            |

|        | Execute Quick Test Sequence           |

|        | Execute Default Test Sequence         |

|        | Execute All Tests                     |

|        | Set Environmental Variables           |

|        | Display Error Log                     |

|        |                                       |

| Clear Error Log                             | . <b>'</b> |

|---------------------------------------------|------------|

| Data RAM Test Menu                          |            |

| Data RAM Write/Write Next Pattern Test      | ·          |

| Data RAM Address Test                       | . <i>'</i> |

| Data RAM 3-Pattern Test                     | . ,        |

| Data RAM Walking Ones Test                  | . <i>'</i> |

| Data RAM March Test                         | . <i>'</i> |

| Execute All Cache Data Tests                | . <i>'</i> |

| Tag RAM Test Menu                           | . <i>'</i> |

| Read Menu                                   | , <i>י</i> |

| Read Hit Test                               | . <i>'</i> |

| Read Hit Context Test                       | . ,        |

| Read Hit Supervisor Access Violation Test   | . ,        |

| Read Hit/Write Hit (Load Store) Test        | . ,        |

| Read Miss Test                              | • •        |

| Read Miss Alignment Test                    | •          |

| Read Miss Valid Bit Set Test                | •          |

| Read Miss/Write Hit (Load Store) Test       |            |

| Read Miss Tag Update Test                   | •          |

| Execute All Cache Read Tests                | •          |

| Write Menu                                  |            |

| Write Hit Test                              | •          |

| Write Hit, Write Protection Violation Test  | •          |

| Write Hit, Alignment Test                   | •          |

| Write Hit, Modified Bit Test                | •          |

| Write Miss Test                             |            |

| Write Miss, Valid Bit Test                  |            |

| Load Store, Write Protection Violation Test |            |

| Write Exerciser Test                        |            |

| Execute All Cache Write Tests               |            |

| Flush Menu                                  | ••         |

| Cache Context Flush Test                    |            |

| Cache Segment Flush Test                    |            |

|      | Cache Page Flush Test             | 86   |

|------|-----------------------------------|------|

|      | Execute All Cache Flush Tests     | 87   |

|      | Debug Menu                        | 87   |

|      | Tag RAM Write                     | 88   |

|      | Data RAM Write                    | 88   |

|      | Tag RAM Read                      | 88   |

|      | Data RAM Read                     | 89   |

|      | Tag RAM Write/Read                | 89   |

|      | Data RAM Write/Read               | 89   |

| 4.8. | Error Messages                    | 90   |

|      | Main Menu Error Messages          | 90   |

|      | Data RAM Test Menu Error Messages | 90   |

|      | Tag RAM Test Menu Error Messages  | 90   |

|      | Read Menu Error Messages          | 9    |

|      | Write Menu Error Messages         | 9.   |

|      | Flush Menu Error Messages         | . 9. |

| 4.9. | Glossary                          | . 90 |

| ~    |                                   |      |

|      | ter 5 I/O Cache Diagnostic        |      |

|      | General Description               |      |

|      | What This Chapter Contains        |      |

|      | Overview of the Diagnostic        |      |

|      | Hardware Requirements             |      |

|      | Firmware Requirements             |      |

|      | User Interface                    |      |

|      | Starting the Diagnostic           |      |

| 5.8. | The Diagnostic Menus              | . 10 |

|      | Main Menu                         | . 10 |

|      | Optional Parameters               | . 10 |

|      | Tag RAM Memory Tests Menu         | . 10 |

|      | Data RAM Memory Tests Menu        | . 10 |

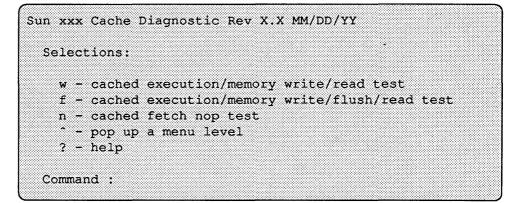

|      | Noncached Hits/Misses Tests Menu  | . 10 |

|      | Cached Hits/Misses Tests Menu     | . 10 |

.

| Flush Tests Menu                       | 110               |

|----------------------------------------|-------------------|

| Options Menu                           | 112               |

| All Test                               | 114               |

| Quick Test                             | 114               |

| Default Test                           | 114               |

| 5.9. Error                             | 114               |

| 5.10. Glossary                         | 115               |

| Chapter 6 Sun CPU Diagnostic           | 119               |

| 6.1. General Description               | 119               |

| 6.2. Hardware Requirements             | 119               |

| 6.3. Command-line Parameters           | 119               |

| 6.4. Looping on Read and Write         | 120               |

| 6.5. Main Menu                         | 121               |

| 6.6. Clock Tests Menu                  | 122               |

| 6.7. System Enable Tests Menu          | 125               |

| 6.8. Sun-3/80 LED Test                 | 127               |

| 6.9. Interrupt Tests Menu              | 129               |

| 6.10. PROM Tests Menu                  | 131               |

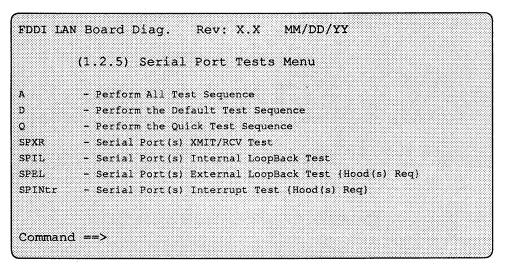

| 6.11. Serial Port Tests Menu           | 134               |

| Asynchronous Tests Sub-menu            | 136               |

| Keyboard/Mouse Port Sub-Menu           | 139               |

| Requirements                           | 139               |

| The Serial Port                        | 139               |

| All, Default or Quick commands         | 140               |

| Modem Tests Sub-menu                   | 140               |

| Register Tests Sub-menu                | 144               |

| 6.12. Parallel Port Menu—Sun-3/80 Only | 146               |

| 6.13. Glossary                         | 147               |

| Chapter 7 The EEPROM Editing Tool      | <b>151</b><br>151 |

| 7.2. Hardware Requirements             | 151               |

| 7.3. Loading And Starting The EEPTOOL          | 151 |

|------------------------------------------------|-----|

| 7.4. The Main Menu                             | 152 |

| 7.5. Primary Terminal Type                     | 152 |

| 7.6. Monitor Resolution                        | 153 |

| High Resolution Monitor Columns And Rows       | 153 |

| 7.7. Board Slot Data                           | 153 |

| Board Slot Sub-Menus                           | 157 |

| Board Type Defaults                            | 158 |

| 7.8. Boot Paths And Devices                    | 158 |

| 7.9. Diagnostic Boot Device and Path           | 160 |

| 7.10. Initialization                           | 161 |

| 7.11. EEPROM Reset                             | 162 |

| 7.12. Show EEPROM Fields                       | 162 |

| 7.13. Show All Write Counts                    | 162 |

| 7.14. Write Data to EEPROM                     | 162 |

|                                                |     |

| Chapter 8 Sun-3 FPA Diagnostic                 | 165 |

| 8.1. Required Hardware                         | 165 |

| 8.2. Tests                                     | 165 |

| Test Syntax                                    | 166 |

| Default Parameters                             | 166 |

| Batching Commands                              | 166 |

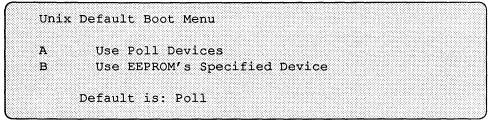

| Test Menus                                     | 167 |

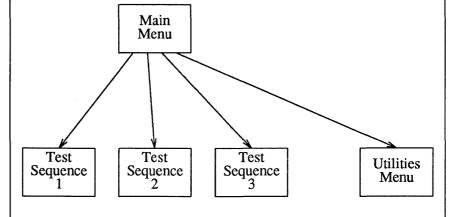

| 8.3. Main Menu                                 | 168 |

| Test Sequence 1 Menu                           | 169 |

| Test Sequence 2 Menu                           | 173 |

| Test Sequence 3 Menu                           | 176 |

| 8.4. Utilities Menu                            | 179 |

|                                                |     |

| Chapter 9 Sun-3/400 Series FPA-Plus Diagnostic | 183 |

| 9.1. General Description                       | 183 |

| 9.2. What This Chapter Contains                | 183 |

| 9.3. Overview of the Diagnostic                | 183 |

| 9.4. Hardware Requirements           | 183 |

|--------------------------------------|-----|

| 9.5. User Interface                  | 184 |

| 9.6. Starting the Diagnostic         | 184 |

| 9.7. The Diagnostic Menus            | 184 |

| Main Menu                            | 184 |

| Command Parameters                   | 185 |

| Perform All Test Sequence            | 186 |

| Perform the Default Test Sequence    | 186 |

| Perform the Quick Test Sequence      | 186 |

| Basic Hardware Tests Menu            | 187 |

| Functional Tests Menu                | 187 |

| Tools and Utilities Menu             | 187 |

| Display Current Environment Settings | 187 |

| Basic Hardware Tests Menu            | 188 |

| Register Tests Menu                  | 189 |

| Control and Path Tests Menu          | 191 |

| RAM Tests Menu                       | 195 |

| Functional Tests Menu                | 202 |

| Functional Tests Menu 1              | 203 |

| Functional Tests Menu 2              | 206 |

| Tools and Utilities Menu             | 210 |

| Display Current Environment Settings | 210 |

| DUT Examine Utility                  | 210 |

| Download to RAM                      | 211 |

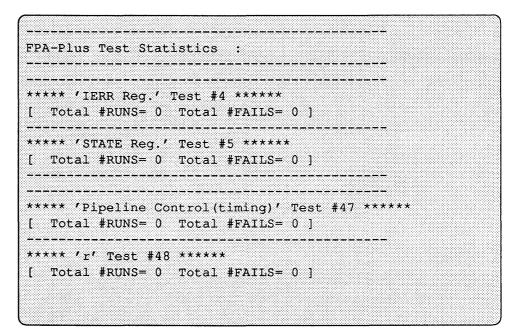

| Display/Save Test Statistics         | 212 |

| Clear Test Statistics                | 212 |

| Display RAM Error Log                | 212 |

| Clear RAM Error Log                  | 213 |

| 9.8. Error Messages                  | 213 |

| IERR Register Test                   | 213 |

| STATE Register Test                  | 213 |

| IMASK Register Test                  | 213 |

| LOAD_PTR Register Test               | 213 |

|                                      |     |

| MODE Register Test                     | 213 |

|----------------------------------------|-----|

| WSTATUS Register Test                  | 213 |

| Nack Test                              | 213 |

| Loop Counter Test                      | 214 |

| Pipeline Status Test                   | 214 |

| Pipeline Data Test                     | 214 |

| Pipeline Instruction Test              | 215 |

| Operand Data Path Test                 | 215 |

| TI Data Path Test                      | 215 |

| µstore RAM Quick Test                  | 215 |

| μstore RAM Data Pattern Test           | 215 |

| μstore RAM Data March Test             | 215 |

| μstore RAM Address Unique Test         | 216 |

| μstore RAM Address Alternate Test      | 216 |

| μstore RAM Address Disturbance Test    | 216 |

| μstore RAM Address March Test          | 216 |

| Register File Quick Test               | 216 |

| Register File Data Pattern Test        | 216 |

| Register File Data March Test          | 216 |

| Register File Address Unique Test      | 216 |

| Register File Address Alternate Test   | 216 |

| Register File Address Disturbance Test | 217 |

| Register File Address March Test       | 217 |

| Shadow RAM Test                        | 217 |

| Micro Store Address Test               | 217 |

| NEXT Address Test                      | 217 |

| JMP Address Test                       | 217 |

| CALL and RETURN Test                   | 217 |

| Simple Instruction Test                | 217 |

| Timeout And Retry Test                 | 218 |

| Load Pointer Test                      | 218 |

| Pointers (1 - 4) Test                  | 218 |

| Immed23 Test                           | 218 |

|                                        |     |

|        | Pointer Increment/Decrement Test          | 218 |

|--------|-------------------------------------------|-----|

|        | Pointer Five Test                         | 219 |

|        | Lock Test                                 | 219 |

|        | TI Operation Test                         | 219 |

|        | TI Status Test                            | 220 |

|        | Jump Conditions Test                      | 220 |

|        | Pipeline Control (timing) Test            | 220 |

|        | Pipeline State Machine Test               | 220 |

| 9.9. ( | Glossary                                  | 221 |

| Chapte | er 10 Floating Point Unit Diagnostic      | 225 |

| 10.1.  | Overview                                  | 225 |

| 10.2.  | Hardware Requirements                     | 225 |

| 10.3.  | Diagnostic Functional Description         | 226 |

| 10.4.  | Modular Description Of The Diagnostic     | 226 |

|        | Main Menu                                 | 226 |

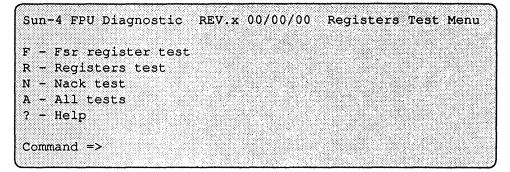

|        | Registers Test Menu                       | 228 |

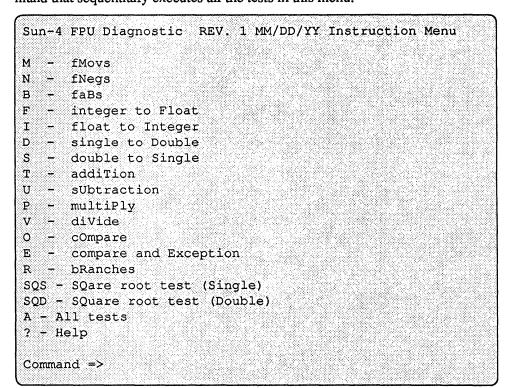

|        | Instructions Test Menu                    | 229 |

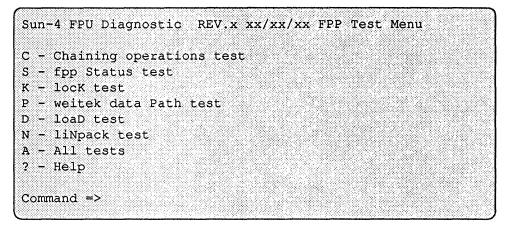

|        | FPP Test Menu                             | 232 |

| 10.5.  | Glossary                                  | 234 |

| Chapte | er 11 Color Graphics Diagnostic           | 237 |

| 11.1.  | Introduction to the Color Graphics Boards | 237 |

| 11.2.  | What's In This Chapter                    | 237 |

| 11.3.  | Objectives                                | 237 |

| 11.4.  | Required Equipment                        | 237 |

|        | User Interface                            | 238 |

| 11.6.  | Set-Up                                    | 238 |

| 11.7.  | Modular Description Of The Diagnostic     | 238 |

|        | The Main Menu                             | 238 |

|        | Manual Test Menu                          | 239 |

|        | Sub-Menus                                 | 242 |

|        | Register Test Menu                        | 242 |

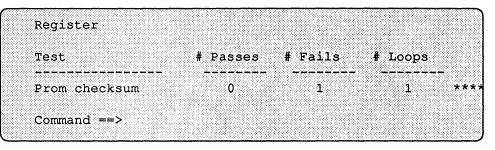

| Register Test Sub-Menu                              | 244 |

|-----------------------------------------------------|-----|

| Interrupt Test Menu                                 | 249 |

| Color Map Test Menu                                 | 249 |

| Frame Buffer Test Menu                              | 252 |

| ROPC Test Menu                                      | 254 |

| Zoom and Pan Test Menu                              | 255 |

| DAC Test Menu                                       | 256 |

| 11.8. Auto Test                                     | 257 |

| DAC Tests                                           | 257 |

| Green Ramp Monotonicity                             | 259 |

| Blue Ramp Monotonicity                              | 259 |

| White Ramp Monotonicity                             | 259 |

| Stable Gray Pattern                                 | 259 |

| Draw Borders                                        | 259 |

| 11.9. Interrupt Tests                               | 260 |

| 11.10. Auto Register Test Details                   | 260 |

| Color-5 Auto Register Test                          | 261 |

| Color-3 Auto Register Test                          | 261 |

| Color-2 Auto Register Test                          | 262 |

| 11.11. Auto Color Map Test                          | 262 |

| 11.12. Load Colors                                  | 263 |

| 11.13. Frame Buffer Tests: Word Mode and Pixel Mode | 264 |

| Constant Pattern Test                               | 265 |

| Address Uniqueness Test                             | 265 |

| Random data test                                    | 265 |

| Address Test (Modified Galpat)                      | 266 |

| Address test (Modified Surround Disturb)            | 266 |

| Refresh Logic Test                                  | 267 |

| Checker Test (32-bit Word Patterns)                 | 268 |

| Checker Test (Byte Patterns)                        | 268 |

| DMA Window Test                                     | 268 |

| DMA Width Register Test                             | 269 |

| DMA Window Visual Demo                              | 269 |

|                                                     |     |

| 11.14. Second DAC Auto Test                                       |   |

|-------------------------------------------------------------------|---|

| 11.15. Auto Zoom and Pan Test                                     | 2 |

| 11.16. ROPC Tests                                                 |   |

| 11.17. Random Data Function Test                                  | 2 |

| 11.18. Implicit word mode Tests                                   | 2 |

| 11.19. Pixel Mode Per-Plane Masking Test                          |   |

| 11.20. Word Mode Per-Plane Masking Test                           |   |

| 11.21. Error messages                                             |   |

| Register Test Error Messages                                      |   |

| Interrupt Test Error Messages                                     |   |

| Color Map Test Error Messages                                     |   |

| 11.22. Glossary                                                   |   |

| Chapter 12 CG6 Graphics Accelerator Board Diagnostic              |   |

| 12.1. Introduction                                                |   |

| 12.2. The Main Menu                                               |   |

| 12.3. CG6 Probe Menu                                              |   |

| 12.4. TEC Menu                                                    |   |

| 12.5. RDAC Menu                                                   |   |

| 12.6. FB Memory Menu                                              |   |

| 12.7. FBC Menu                                                    |   |

| 12.8. THC and Autoload Menu                                       |   |

| 12.9. System and Monitor Menu                                     |   |

| 12.10. Utilities Menu           12.11. Option Menu                |   |

| -                                                                 |   |

| 12.12. Error Messages                                             |   |

| PROBE Error Messages                                              |   |

| TEC Error Messages                                                |   |

| DAC Error Messages                                                |   |

| MEM Error Messages                                                |   |

|                                                                   |   |

|                                                                   |   |

| FBC Error Messages<br>CURSOR Error Messages<br>SYS Error Messages |   |

|        | UTILITIES Menu Error Messages       | 303 |

|--------|-------------------------------------|-----|

| Chapte | er 13 CG8 Diagnostics               | 307 |

| 13.1.  | Introduction                        | 307 |

| 13.2.  | Parameter Definitions               | 307 |

| 13.3.  | The Main Menu                       | 309 |

| 13.4.  | Memory Menu                         | 310 |

| 13.5.  | Register Menu                       | 315 |

| 13.6.  | Function Menu                       | 316 |

| 13.7.  | Pattern Menu                        | 317 |

| 13.8.  | Debug Menu                          | 319 |

| 13.9.  | Memory Map for Debugging            | 320 |

| Chapte | er 14 CG9 Color Graphics Diagnostic | 323 |

| 14.1.  | Introduction to the CG9             | 323 |

| 14.2.  | What This Chapter Contains          | 323 |

| 14.3.  | Overview of the Diagnostic          | 323 |

| 14.4.  | Hardware Requirements               | 323 |

| 14.5.  | User Interface                      | 324 |

| 14.6.  | Starting the Diagnostic             | 324 |

| 14.7.  | The Diagnostic Menus                | 324 |

|        | Main Menu                           | 324 |

|        | All Test Sequence                   | 325 |

|        | Quick Test Sequence                 | 325 |

|        | Memory Menu                         | 325 |

|        | Functional Menu                     | 326 |

|        | Pattern Menu                        | 326 |

|        | Debug Menu                          | 326 |

|        | Print Pass-fail Stats               | 326 |

|        | Initialize Frame Buffer             | 326 |

|        | Memory Menu                         | 327 |

|        | All Test Sequence                   | 328 |

|        | Quick Test Sequence                 | 328 |

| Control Space Test                  | . 328 |

|-------------------------------------|-------|

| Constant Data Test                  | . 328 |

| Walking One Data Test               | . 328 |

| Incrementing Data Test              | . 329 |

| Random Address and Data Test        | . 329 |

| 8- and 16-bit Data Size Access      | . 329 |

| RAMDAC Address Register Test        | . 329 |

| RAMDAC Command Register Test        | . 329 |

| RAMDAC Look-up Tables Test          | . 329 |

| Initialize Frame Buffer             | . 329 |

| Function Menu                       | . 329 |

| All Test Sequence                   | . 330 |

| Quick Test Sequence                 | . 330 |

| Buffer Enable Test                  | . 331 |

| Double Buffering Test               | . 331 |

| RGB Mask Control Test               | . 331 |

| Line Blit Test (Same Buffer)        | . 331 |

| Screen Blit Test (Mixed Buffer)     | . 331 |

| RAMDAC Color Look-up Test           | . 331 |

| RAMDAC Overlay Look-up Test         | . 332 |

| RAMDAC Read Mask Test               | . 332 |

| Retrace Interrupt Test              | . 332 |

| Initialize Frame Buffer             | . 332 |

| Pattern Menu                        | . 332 |

| All Test Sequence                   | . 332 |

| Rotate Through 16 Burst Patterns    | . 333 |

| Display One Overlay Color           | . 333 |

| 16 Gray Level Boxes                 |       |

| Alternating Stripes With Boxes      |       |

| Cross Hatch Pattern                 | 333   |

| TV Color Bar                        | 334   |

| Cycle Through Colors                | 334   |

| Crosstalk Color Memory With Overlay | 334   |

|                                     |       |

| FCC Dither Pattern (Gray Stripes)                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| One Pixel Wide Border                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Initialize Frame Buffer                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Debug Menu                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fill Frame Buffer Location(s)                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Edit Frame Buffer Location(s)                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Dump Block of Frame Buffer Data                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Display RAMDAC Overlay or Color Palette                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Scope Frame Buffer Location                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Write-Quick-Read Scope Test                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bit-blt Horizontal Line                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bit-blt Line Scope                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Bit-blt Rectangle                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Initialize Frame Buffer                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14.8. Glossary                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                     |

| Chapter 15 Graphics Processor1 Diagnostic                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.1. Introduction                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                              | 0.40                                                                                                                                                                                                                                                                                                                                                                                                |

| 15.2. What This Chapter Contains                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3. Overview of the Diagnostic                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     |

| 15.3. Overview of the Diagnostic                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li> <li>15.4. User Interface</li></ul>                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li> <li>15.4. User Interface</li> <li>15.5. Starting the Diagnostic</li> <li>15.6. The Main Menu</li> <li>Run the Slave Tests</li> <li>Run the Viewing Processor Tests</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          | 343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         344         345         346         347         347         349         349                                                                         |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          | 343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         344         345         346         347         347         347         347         349         349         349         349                         |

| <ul> <li>15.3. Overview of the Diagnostic</li></ul>                                                                                                                                                                          | 343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         343         345         346         347         347         347         349         349         349         349         349         350 |

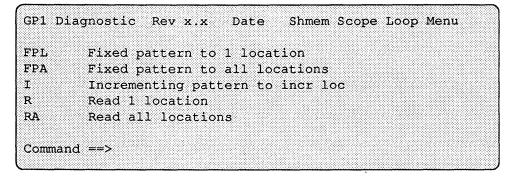

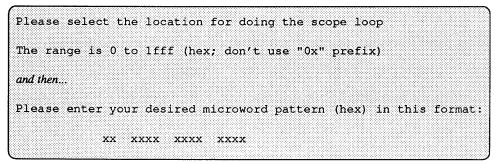

| A — Microstore Address Register       351         V — VP Scope Loop Menu       352         P — PP Scope Loop Menu       356         D — DRAM Scope Loop Menu       360 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P — PP Scope Loop Menu         356           D — DRAM Scope Loop Menu         360                                                                                      |

| D — DRAM Scope Loop Menu                                                                                                                                               |

|                                                                                                                                                                        |

|                                                                                                                                                                        |

| 15.8. Error Messages                                                                                                                                                   |

| 15.9. Abortion Message Interpretation 382                                                                                                                              |

|                                                                                                                                                                        |

| Chapter 16 Graphics Processor2 Diagnostic                                                                                                                              |

| 16.1. Introduction to the GP2                                                                                                                                          |

| 16.2. What This Chapter Contains 387                                                                                                                                   |

| 16.3. Diagnostic Objectives 387                                                                                                                                        |

| 16.4. Hardware Requirements 388                                                                                                                                        |

| 16.5. Diagnostic Overview                                                                                                                                              |

| 16.6. The Main Menu                                                                                                                                                    |

| Shared Memory Tests Menu 390                                                                                                                                           |

| WCS Memory Tests Menu 392                                                                                                                                              |

| XP, RP Processor Tests Menu                                                                                                                                            |

| XP, RP Shared Memory Tests Menu                                                                                                                                        |

| Test Syntax                                                                                                                                                            |

| Test Options                                                                                                                                                           |

| XP, RP Local RAM Menu                                                                                                                                                  |

| FIFO Tests Menu 402                                                                                                                                                    |

| FIFO Function Tests Menu 402                                                                                                                                           |

| FIFO RAM Tests Menu 40'                                                                                                                                                |

| PP Core Test Menu 409                                                                                                                                                  |

| PP Hardware Control Test Menu 412                                                                                                                                      |

| Z (depth) Buffer Test Menu 41:                                                                                                                                         |

| CG5 Frame Buffer Interface Tests                                                                                                                                       |

| P2 Bus Interface Test Menu 420                                                                                                                                         |

| CG9 Frame Buffer Test Menu 424                                                                                                                                         |

| Memory Utilities Menu 42                                                                                                                                               |

| Option Menu 428                                                                                                                                                        |

| 16.7. | Memory Test Descriptions   | 429 |

|-------|----------------------------|-----|

|       | Addressing Test            | 429 |

|       | Constant Pattern Test      | 430 |

|       | Checker Pattern Test       | 431 |

|       | Uniqueness Addressing Test | 433 |

|       | Mats (Modulo 3's) Test     | 433 |

|       | Walking 1's/0's Test       | 434 |

|       | NTA Pattern Test           | 435 |

|       | Random Pattern Test        | 436 |

|       | Triangle Pattern Test      | 437 |

|       | LRAM, SRAM Bus test        | 437 |

|       | XP Port 2, Port 3 Tests    | 438 |

|       | XP Port3 VME Test          | 439 |

|       | XP, RP Arbiter Test        | 440 |

| 16.8. | XP, RP Processor Tests     | 441 |

|       | Hshake Test                | 441 |

|       | CHshake Test               | 442 |

|       | XP Branch Tests            | 442 |

|       | WCS Addressing Test        | 443 |

|       | XP Logical Test            | 444 |

|       | XP Register Tests          | 444 |

|       | XP Push Pop Tests          | 444 |

|       | XP SOB Test                | 444 |

|       | XP SOB Neutralize Test     | 444 |

|       | XP SHOB Test               | 444 |

|       | XP Add, Sub Tests          | 444 |

|       | XP Call Tests              | 444 |

|       | XP Condition Code Tests    | 445 |

|       | XP Merge, Deposit Tests    | 445 |

|       | XP Extract Tests           | 445 |

|       | XP Multiply Test           | 445 |

|       | XP Divide Test             | 445 |

|       | XP Byte Alignment Test     | 445 |

|       |                            |     |

|        | XP Byte Store Test                              |

|--------|-------------------------------------------------|

|        | XP Addrd Test                                   |

| 16.9.  | XP Floating Point Tests                         |

|        | XP Fload Tests                                  |

|        | XP Fabs Tests                                   |

|        | XP Float Tests                                  |

|        | XP Fadd Tests                                   |

|        | XP Faddt Tests                                  |

|        | XP Fadd2 Tests                                  |

|        | XP Fmac Tests                                   |

|        | XP Fmul Tests                                   |

|        | XP Flut Tests                                   |

|        | XP F_cc Tests                                   |

|        | XP Fndloop Tests                                |

| 16.10. | Shared RAM Comm                                 |

|        | Handshake Communications                        |

| 16.11. | Error Messages                                  |

|        | Error Message No. 1.                            |

|        | Error Message No. 2                             |

|        | Shared RAM Error Messages                       |

|        | Arbiter Error Messages                          |

|        | FIFO Error Messages                             |

|        | PP Error Messages                               |

|        | PP Hardware Menu Error Messages                 |

|        | CG5 Frame Buffer Menu Error Messages            |

|        | CG9 Frame Buffer Menu Error Messages            |

|        | Z Buffer Menu Error Messages                    |

| 16.12  | Default Test Sequence                           |

| 16.13  | . Glossary                                      |

|        |                                                 |

| -      | r 17 TAAC-1 Applications Accelerator Diagnostic |

|        | Introduction to the TAAC-1                      |

| 17.2.  | What This Chapter Contains                      |

| 17.3. | TAAC-1 Functional Overview     | 465 |

|-------|--------------------------------|-----|

|       | VME Interface                  | 465 |

|       | Buses and Data Paths           | 466 |

|       | Registers                      | 467 |

|       | Vector Ports                   | 467 |

|       | Access Processor               | 467 |

|       | Video Output                   | 467 |

| 17.4. | Hardware Requirements          | 468 |

| 17.5. | Set-Up                         | 468 |

| 17.6. | Description Of The Diagnostic  | 469 |

|       | Main Menu                      | 469 |

|       | Options Menu                   | 471 |

|       | Tests Routine Menu             | 476 |

|       | Interactive Operations         | 476 |

| 17.7. | TAAC-1 Test Descriptions       | 478 |

|       | Microcode RAM Test             | 478 |

|       | Scratchpad RAM Test            | 478 |

|       | Video RAM Test                 | 479 |

|       | Video Registers Test           | 480 |

|       | Sequencer Functionality Test   | 482 |

|       | ALU Registers Test             | 482 |

|       | ALU Operations Test            | 483 |

|       | Barrel Shifter Test            | 484 |

|       | Floating Point Operations Test | 485 |

|       | Look-up Table RAM and ROM Test | 486 |

|       | Multiplier Accumulator Test    | 487 |

|       | RDRC Test                      | 487 |

|       | Sequencer Stack Test           | 487 |

|       | Access Processor Test          | 488 |

|       | Vector Port Test               | 490 |

|       | Vector Port Test (Write Only)  | 490 |

|       | Brooktree RAMDAC Test          | 491 |

|       | Interrupts Test                | 494 |

|       |                                |     |

|        | Frame Buffer Checksum Test                   | 495 |

|--------|----------------------------------------------|-----|

| Chapte | er 18 High Speed Serial Interface Diagnostic | 499 |

| -      | General Description                          | 499 |

|        | What This Chapter Contains                   | 499 |

|        | Overview of the Diagnostic                   | 499 |

|        | Hardware Requirements                        | 499 |

|        | User Interface                               | 500 |

|        | Starting the Diagnostic                      | 500 |

|        | The Diagnostic Menus                         | 500 |

|        | Main Menu                                    | 500 |

|        | All Sequential Test                          | 501 |

|        | Quick Sequential Test                        | 501 |

|        | CIO Menu                                     | 501 |

|        | Optional Parameters                          | 502 |

|        | All Sequential Test                          | 502 |

|        | Quick Sequential Test                        | 502 |

|        | CIO A Scope Menu                             | 502 |

|        | CIO B Scope Menu                             | 504 |

|        | CIO Access Test                              | 504 |

|        | CIO Port Read                                | 504 |

|        | CIO Port Write                               | 504 |

|        | CIO Control Register Read                    | 505 |

|        | CIO Control Register Write                   | 505 |

|        | V.35 Modem Control Test Menu                 | 505 |

|        | RS-449 Modem Control Test Menu               | 507 |

|        | Interrupt Verification                       | 508 |

|        | Parity Interrupt Verification                | 508 |

|        | Modem Control Interrupt Verification Menu    | 509 |

|        | Dynamic RAM Menu                             | 512 |

|        | Optional Parameters                          | 513 |

|        | All Sequential Test                          | 513 |

|        | Quick Sequential Test                        | 513 |

|       | Set Parity Menu                                    | 513 |

|-------|----------------------------------------------------|-----|

|       | Force Parity Error Test                            | 514 |

|       | Address Test                                       | 514 |

|       | Pattern Test                                       | 514 |

|       | Checker Pattern Test                               | 514 |

|       | Unique Pattern Test                                | 514 |

|       | MATS+ Pattern Test                                 | 514 |

|       | Random Pattern Test                                | 515 |

|       | NTA Test                                           | 515 |

|       | Triangle Pattern Test                              | 515 |

|       | Diagonal Pattern Test                              | 515 |

|       | DRAM Access Menu                                   | 516 |

|       | Serial Controller Menu                             | 519 |

|       | All Sequential Test                                | 519 |

|       | Quick Sequential Test                              | 519 |

|       | Serial Controller A Scope Menu                     | 520 |

|       | Serial Controller B Scope Menu                     | 522 |

|       | Internal Loopback Menu                             | 522 |

|       | External Loopback Menu                             | 523 |

|       | Port To Port Menu                                  | 524 |

|       | Programmable Divider Menu                          | 526 |

|       | Exit                                               | 527 |

| 18.9. | Messages                                           | 527 |

|       | CIO Ports A, B, and C and Control Registers Access |     |

|       | Verification                                       | 527 |

|       | Successful Completion Messages                     | 527 |

|       | Error Messages                                     | 528 |

|       | V.35 Modem Control Test Menu                       | 528 |

|       | Successful Completion Messages                     | 528 |

|       | Error Messages                                     | 528 |

|       | RS-449 Modem Control Test Menu                     | 529 |

|       | Successful Completion Messages                     | 529 |

|       | Error Messages                                     | 529 |

|       |                                                    |     |

| Interrupt Verification                       | 529 |

|----------------------------------------------|-----|

| Successful Completion Messages               | 529 |

| Error Messages                               | 529 |

| Parity Interrupt Verification                | 529 |

| Successful Completion Messages               | 529 |

| Error Messages                               | 529 |

| Modem Control Interrupt Verification Menu    | 530 |

| Successful Completion Messages               | 530 |

| Error Messages                               | 530 |

| Dynamic RAM Address, Pattern, and NTA Tests  | 531 |

| Error Messages                               | 531 |

| MK5025 Register Access Verification          | 531 |

| Successful Completion Messages               | 531 |

| Error Messages                               | 531 |

| MK5025 A/B Selftest                          | 531 |

| Successful Completion Messages               | 531 |

| Error Messages                               | 531 |

| MK5025 A/B FCS Check                         | 531 |

| Successful Completion Messages               | 531 |

| Error Messages                               | 531 |

| Serial Controller A/B Interrupt Verification | 532 |

| Successful Completion Messages               | 532 |

| Error Messages                               | 532 |

| 18.10. Glossary                              | 532 |

| Chapter 19 IPI Disk Subsystem Diagnostic     | 535 |

| 19.1. General Description                    | 535 |

| 19.2. What This Chapter Contains             | 535 |

| 19.3. Overview of the Diagnostic             | 535 |

| 19.4. Hardware Requirements                  | 535 |

| 19.5. User Interface                         | 535 |

| 19.6. Starting the Diagnostic                | 536 |

| 19.7. The Diagnostic Menus                   | 536 |

|        | Main Test Menu                | 536 |

|--------|-------------------------------|-----|

|        | Command Variables             | 537 |

|        | Local Environmental Variables | 538 |

|        | Controller Test Menu          | 539 |

|        | Drive Test Menu               | 543 |

|        | Utility Menu                  | 548 |

|        | Quick Test Sequence           | 554 |

|        | Default Test Sequence         | 554 |

|        | All Test Sequence             | 554 |

|        | Command Default Variables     | 555 |

|        | Display Error Log             | 555 |

|        | Clear Error Log               | 555 |

|        | Exit                          | 555 |

| 19.8.  | Error Messages                | 556 |

| 19.9.  | Glossary                      | 559 |

|        |                               |     |

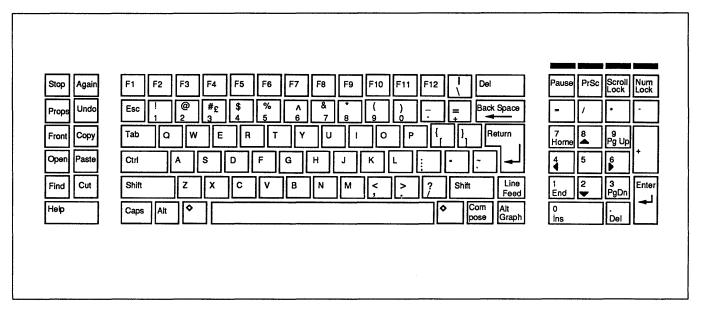

| Chapte | er 20 Keyboard Diagnostic     | 563 |

| 20.1.  | Requirements                  | 563 |

| 20.2.  | Description                   | 563 |

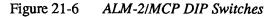

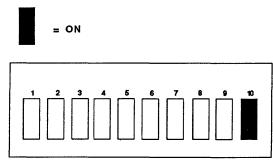

| Chante | er 21 MCP/ALM2 Diagnostic     | 569 |

|        | Introduction                  | 569 |

|        | Hardware Requirements         | 569 |

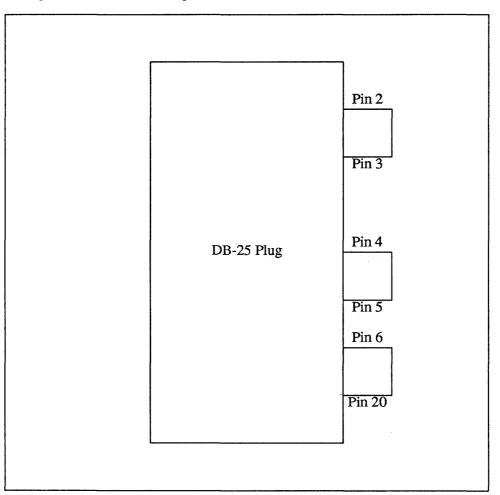

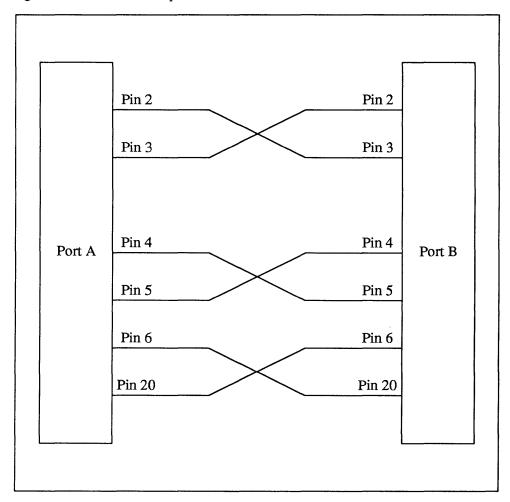

| 21.2.  | Loopback Connectors           | 569 |

| 213    | Limitations                   | 572 |

|        | Operating Instructions        | 572 |

| 21     | Loading And Starting          | 572 |

| 21.5   | The User Interface            | 572 |

| 21.5.  | Recommended Test Procedure    | 572 |

|        | The Main Menu                 | 573 |

|        | The Basic Test Menu           | 574 |

|        | DLF Option Menu               | 577 |

|        | The Middle Test Menu          | 577 |

|        |                               | 511 |

| 21.6. The Advanced Test Menu                       | 580 |

|----------------------------------------------------|-----|

| 21.7. Error Handling                               | 582 |

| 21.8. Message Interpretation And Failure Analysis. | 583 |

| 21.9. Status In DEVVEC Patterns                    | 597 |

| 21.10. Glossary                                    | 599 |

| Chapter 22 MTI/ALM Board Diagnostic                | 603 |

| 22.1. Introduction                                 | 603 |

| 22.2. Hardware Requirements                        | 603 |

| 22.3. Operating Instructions                       | 603 |

| Recommended Test Procedure                         | 603 |

| The Main Menu                                      | 604 |

| Configuration Selection Sub-Menu                   | 605 |

| 22.4. Test Descriptions                            | 606 |

| Character Data Test                                | 606 |

| Block Data Test                                    | 606 |

| Baud Rate Test                                     | 606 |

| Stop Bit Test                                      | 607 |

| Word Length Test                                   | 607 |

| Parity Test                                        | 607 |

| Modem Lines Test                                   | 607 |

| 22.5. Error Handling                               | 607 |

| 22.6. Glossary                                     | 608 |

| 22.7. References                                   | 609 |

| Chapter 23 Sun Memory Diagnostic                   | 613 |