$\mathbb{DEC}$ system-10/20  $\mathbb{H}$ ardware  $\mathbb{M}$ anual

# DECsystem-10/20 Hardware Manual

by

Digital Equipment Corporation

Staff of the Artificial Intelligence Laboratory

Staff of the LOTS Computer Facility

### **Abstract**

The Hardware Reference Manual explains the PDP-10 instruction set as it exists in the KL10 processor. Appendices explain the differences between the various processors in the PDP-10 family.

This manual is also published as part of LOTS Operating Note 2. This manual supersedes SAILON-26 and SAILON-71.

This manual was supported, in part, by the Advanced Research Projects Agency of the Department of Defense under Contract No. MDA903-76-C-0206. The views and conclusions contained in this document are those of the authors and should not be interpreted as necessarily representing the official policies, either expressed or implied, of Stanford University, the Advanced Research Projects Agency, the U.S. Government, or, for that matter, anyone else.

# HARDWARE REFERENCE MANUAL

Direct comments concerning this manual to Software Quality Control, Maynard, Massachusetts.

digital equipment corporation · maynard. massachusetts

Instruction times, operating speeds and the like are included here for reference only; they are not to be taken as specifications.

Copyright © 1968, 1969, 1971, 1974, 1976 by Digital Equipment Corporation

Fourth edition, March 1976

Changes are indicated by a triangle ( $\triangle$ ) in the outside margin.

### **Preface**

This manual explains the machine language programming and operation of the DECsystem-10, for both instructional and reference purposes. Basically the manual defines in detail how the central processor and the peripherals function, exactly what their instructions do, how they handle data, what their control and status information means, and what programming techniques and procedures must be employed to utilize them effectively. The programming is given in machine language, in that it uses only the basic instruction and device mnemonics and symbolic addressing defined by the assembler. The treatment relies on neither any other Digital software nor any of the more sophisticated features of the assembler; moreover the manual is completely self-contained — no prior knowledge of the assembler is required.

The text of the manual is devoted almost entirely to functional description and programming. Chapter 1 discusses the general characteristics of the system, defines the formats of the words used for numbers and instructions, and also explains the conventions needed to program the system and understand the examples given in the text. Chapter 2 covers all phases of the central processor, including the general principles of in-out programming and handling the interrupt system. The remaining chapters are devoted to the various categories of peripheral equipment. Chapters 3 and 4 cover the simple character-oriented devices that use form paper, paper tape and cards. Chapter 5 treats the data interfaces that are employed in the tape, disk and data communication systems covered in the three chapters following. Finally Chapter 9 describes the various terminals that can be used either at the console or in communication systems; this chapter includes both programming and operating information.

The first three appendices contain the basic reference tables for the programmer — word formats, instruction and device mnemonics. IO codes, IO bit assignments showing conditions and status, and a shorthand presentation of instruction actions in symbolic form. The next two appendices provide additional programming information of less general use: Appendix D gives the instruction times and Appendix E documents the differences among the several central processor models. The final three appendices provide a complete guide to the operation of the central processors, memories and peripheral devices (except terminals). This treatment is entirely in hardware terms, describing all lights and switches, how to load the devices, and so forth, but not how to run the system in terms of interacting with any Digital software — that information is given in the DECsystem—10 Operator's Guide.

# **Contents**

| 1.  | INTRODUCTION                                                                                                                                                              | 1-1  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|     | Time Sharing 1-4                                                                                                                                                          |      |

| 1.1 | Number System Floating point arithmetic 1-8                                                                                                                               | 1-7  |

| 1.2 | Instruction Format Effective address calculation 1-11                                                                                                                     | 1-10 |

| 1.3 | Memory KI10 memory allocation 1-14 KA10 memory allocation 1-14                                                                                                            | 1-12 |

| 1.4 | Programming Conventions                                                                                                                                                   | 1-15 |

| 2.  | CENTRAL PROCESSOR                                                                                                                                                         | 2-1  |

| 2.1 | Half Word Data Transmission                                                                                                                                               | 2-2  |

| 2.2 | Full Word Data Transmission  Move instructions 2-10  Pushdown list 2-12                                                                                                   | 2-9  |

| 2.3 | Byte Manipulation Special Considerations 2-17                                                                                                                             | 2-15 |

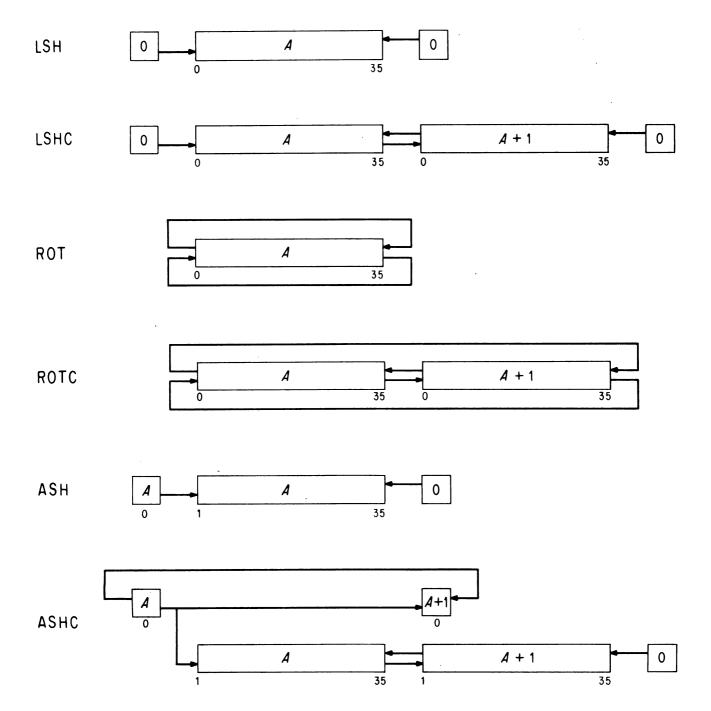

| 2.4 | Logic Shift and rotate 2-24                                                                                                                                               | 2-17 |

| 2.5 | Fixed Point Arithmetic  Double precision integer instructions 2-30  Arithmetic shifting 2-30b                                                                             | 2-26 |

| 2.6 | Floating Point Arithmetic Scaling 2-33 Number conversion 2-34 Single precision with rounding 2-36 Single precision without rounding 2-38 Double precision operations 2-42 | 2-31 |

| 2.7 | Arithmetic Testing                                                                                                                                                        | 2-45 |

| 2.8 | Logical Testing and Modification                                                                                                                                          | 2-51 |

| 2.9 | Program Control Overflow trapping 2-69                                                                                                                                    | 2-58 |

| 2.10 | Unimplemented Operations KL10 and KI10 2-71 KA10 2-72                                                                                                                                                                                                                                                                                                                                                                     | 2-70   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.11 | Programming Examples Processor identification 2-72 Parity 2-72 Counting ones 2-75 Number conversion 2-77 Table searching 2-78 Double precision floating point 2-79                                                                                                                                                                                                                                                        | 2-72   |

| 2.12 | Input-Output A typical IO device 2-84 Readin mode 2-85 Console-program communication 2-86                                                                                                                                                                                                                                                                                                                                 | 2-81   |

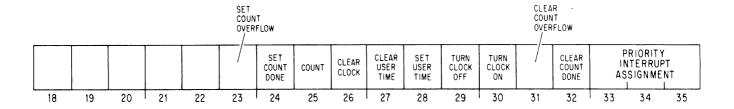

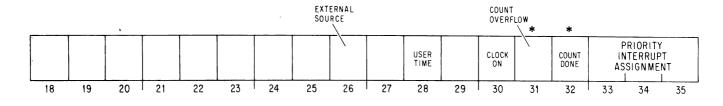

| 2.13 | Priority Interrupt KL10 interrupt 2-88 Processor conditions 2-88e KI10 interrupt 2-88e Interrupt instructions 2-89 Dismissing an interrupt 2-90 Priority interrupt conditions 2-91 Timing 2-93 Special considerations 2-93 Programming suggestions 2-93 KA10 interrupt 2-94 Interrupt instructions 2-94 Dismissing an interrupt 2-95 Interrupt conditions 2-96 Timing 2-97 Special considerations, programming suggestion | 2-87   |

| 2.14 | Processor Conditions KL10 processor conditions 2-98 Organization 2-98c KI10 processor conditions 2-98e KA10 processor conditions 2-101                                                                                                                                                                                                                                                                                    | 2-98   |

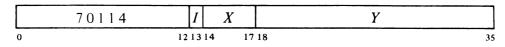

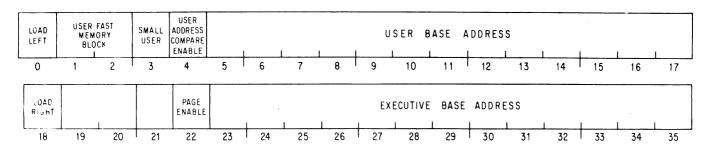

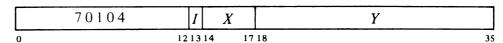

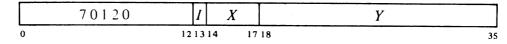

| 2.15 | KL10 Program and Memory Management User programming 2-103a Paging 2-103b Page map partitioning 2-103b Page failure 2-103f Monitor programming 2-103g Cache memory 2-103h Organization 2-103i Processor requests 2-103i Processor writes 2-103i                                                                                                                                                                            | 2-103a |

| 2.15 (0 | Cont)                                                                                                                                                                                                                  |       |                                                                      |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------------------------------------------------------------------|

|         | Channel reads 2-103i Channel writes 2-103i Programming 2-103j Cache sweep and validate main memory 2-103j User base 2-103m                                                                                             |       |                                                                      |

| 2.16    | KI10 Program and Memory Management User programming 2-104 Paging 2-105 Associative memory 2-108 Page failure 2-109 Monitor programming 2-111 Executive XCT 2-114 Individual instruction effects 2-115 Philosophy 2-116 | 2-104 |                                                                      |

| 2.17    | KA10 Program and Memory Management User programming 2-119 Monitor programming 2-119                                                                                                                                    | 2-117 |                                                                      |

| 2.18    | Real Time Clock DK10 Instructions 2-120                                                                                                                                                                                | 2-120 |                                                                      |

| 3.      | CONSOLE IN-OUT EQUIPMENT                                                                                                                                                                                               | 3-1   | Note: in the present                                                 |

| 3.1     | Paper Tape Reader<br>Readin mode 3-3                                                                                                                                                                                   | 3-1   | publication chapters<br>3 through 8 have been<br>omitted. Also,parts |

| 3.2     | Paper Tape Punch                                                                                                                                                                                                       | 3-4   | of the appendicies                                                   |

| 3.3     | Console Terminal                                                                                                                                                                                                       | 3-6   | are omitted.                                                         |

| 4.      | HARDCOPY EQUIPMENT                                                                                                                                                                                                     | 4-1   |                                                                      |

| 4.1     | Line Printer LP10                                                                                                                                                                                                      | 4-1   |                                                                      |

| 4.2     | Plotter XY10                                                                                                                                                                                                           | 4-8   |                                                                      |

| 4.3     | Card Reader CR10                                                                                                                                                                                                       | 4-11  |                                                                      |

| 4.4     | Card Punch CP10                                                                                                                                                                                                        | 4-15  |                                                                      |

| 5.      | DATA INTERFACES                                                                                                                                                                                                        | 5-1   |                                                                      |

| 5.1     | Data Channel DF10                                                                                                                                                                                                      | 5-1   |                                                                      |

| 5.2     | Twelve- and Eighteen-Bit Computer Interface DA10 PDP-10 instructions 5-7 Twelve-bit computer instructions 5-8 Eighteen-bit computer instructions 5-10 Programming considerations 5-11                                  | 5-7   |                                                                      |

| 6       | MAGNETIC TAPE                                                                                                                                                                                                                                                                                                              | 6-1  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| Part I  | DECtape                                                                                                                                                                                                                                                                                                                    | 6-1  |  |  |

| 6.1     | Tape Format Standard format DECtape 6-3 Compatibility 6-3                                                                                                                                                                                                                                                                  | 6-2  |  |  |

| 6.2     | Tape Handling Characteristics                                                                                                                                                                                                                                                                                              | 6-4  |  |  |

| 6.3     | Instructions                                                                                                                                                                                                                                                                                                               | 6-5  |  |  |

| 6.4     | Normal Programming Timing 6-12 Readin mode 6-14                                                                                                                                                                                                                                                                            |      |  |  |

| 6.5     | Formatting a Tape                                                                                                                                                                                                                                                                                                          | 6-14 |  |  |

| Part II | Standard Magnetic Tape                                                                                                                                                                                                                                                                                                     | 6-16 |  |  |

| 6.6     | Tape Format                                                                                                                                                                                                                                                                                                                | 6-16 |  |  |

| 6.7     | Instructions                                                                                                                                                                                                                                                                                                               | 6-19 |  |  |

| 6.8     | Tape Functions Interrupt when unit ready 6-27 Write 6-27 Mark end of file 6-28 Erase 6-28 Erase and write 6-28 Read record 6-28 Read multirecord 6-29 Read-compare record 6-29 Read-compare multirecord 6-30 Space records forward 6-30 Space file forward 6-30 Space file reverse 6-31 Rewind 6-31 Rewind and unload 6-31 | 6-27 |  |  |

| 6.9     | Programming Considerations Readin mode 6-32                                                                                                                                                                                                                                                                                | 6-31 |  |  |

| 6.10    | Timing Tape transport TU10 6-33 Tape transport TU20 6-34 Tape transport TU30 6-35 Tape transport TU40 6-35                                                                                                                                                                                                                 | 6-33 |  |  |

7-1

| Part I  | RC10 Disk/Drum System                                                                                                                                                       | 7-2  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|--|

| 7.1     | Data Format                                                                                                                                                                 | 7-3  |  |  |

| 7.2     | Instructions                                                                                                                                                                | 7-4  |  |  |

| 7.3     | 7.3 Programming Considerations Timing 7-11                                                                                                                                  |      |  |  |

| 7.4     | Operation                                                                                                                                                                   | 7-14 |  |  |

| Part II | RP10 Disk Pack System                                                                                                                                                       | 7-18 |  |  |

| 7.5     | Data Format                                                                                                                                                                 | 7-18 |  |  |

| 7.6     | Instructions                                                                                                                                                                | 7-20 |  |  |

| 7.7     | Disk Pack Functions                                                                                                                                                         | 7-27 |  |  |

| 7.8     | Programming Considerations Timing 7-29                                                                                                                                      | 7-28 |  |  |

| 7.9     | Operation                                                                                                                                                                   | 7-30 |  |  |

| 8       | DATA COMMUNICATIONS                                                                                                                                                         | 8-1  |  |  |

| 8.1     | Communication Signals and Procedures Bell System data sets 8-6                                                                                                              | 8-3  |  |  |

| 8.2     | Data Communication System DC68A Data multiplexing 8-11 Modem control DC08F 8-17 Call control DC08H 8-19 689AG: Part I, modem control 8-21 689AG: Part II, call control 8-24 | 8-7  |  |  |

| 8.3     | Data Line Scanner DC10 Instructions 8-29 Data line programming 8-33 Modem control programming 8-35                                                                          | 8-26 |  |  |

| 8.4     | Single Synchronous Line Unit DS10 Instructions 8-37 Programming considerations 8-40                                                                                         | 8-36 |  |  |

| APPEND  | ICES                                                                                                                                                                        |      |  |  |

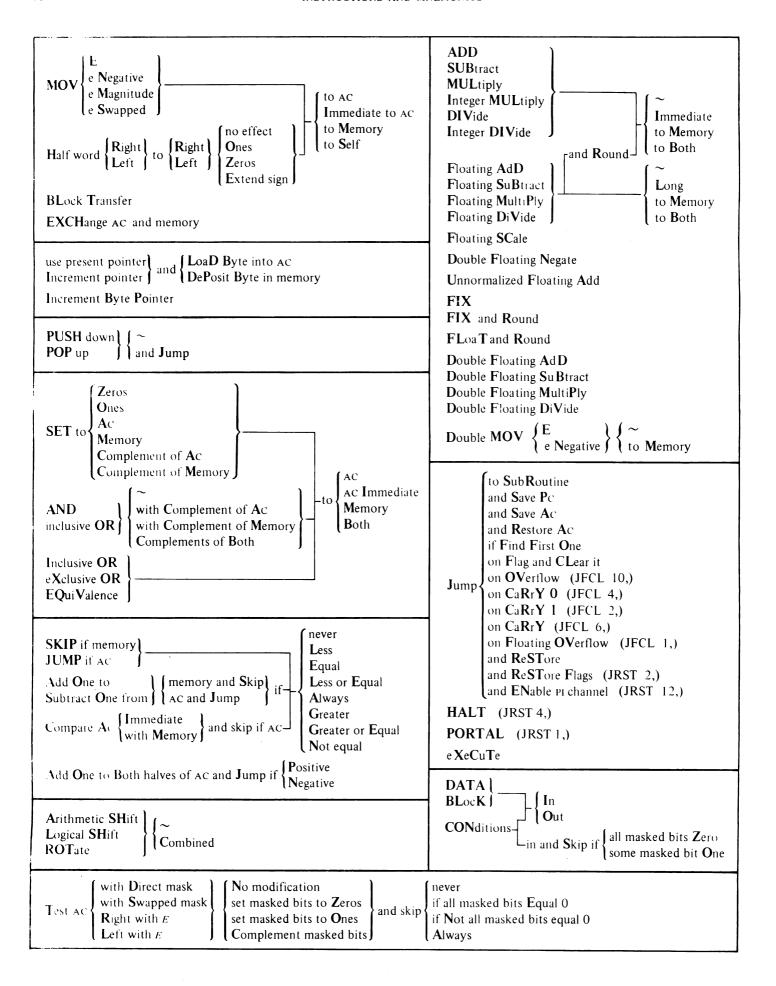

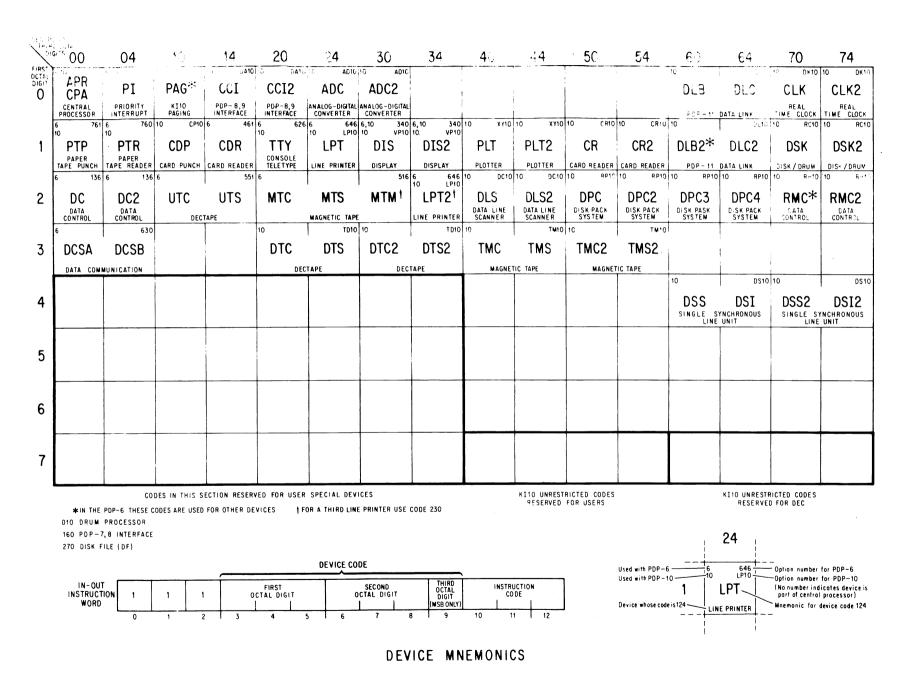

| A       | INSTRUCTIONS AND MNEMONICS  Word Formats A-2  Mnemonic Derivation A-4  Numeric Listing A-5  Alphabetic Listing A-8  Device Mnemonics A-12  Algebraic Representation A-13    | A-1  |  |  |

DISKS AND DRUMS

| В    | IN-OUT CODES  ASCII Code B-2 Line Printer Codes B-4 Card Codes B-8                                                                                    | B-1  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|

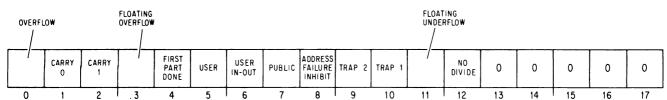

| C    | IO BIT ASSIGNMENTS  KI10 Processor C-2  KA10 Processor C-6  Console IO C-8  Peripheral devices follow in alphabetical order                           | C-1  |

| D    | TIMING  KI10 Instruction Times D-3  KA10 Instruction Times D-9                                                                                        | D-1  |

| E    | PROCESSOR COMPATIBILITY                                                                                                                               | E-1  |

| F    | PROCESSOR OPERATION                                                                                                                                   | F-1  |

| F1   | KI10 Operation Indicators F1-2 Operating keys F1-6 Operating switches F1-8 Real time clock DK10 F1-13                                                 | F1-1 |

| F2   | KA10 Operation Indicators F2-1 Operating keys F2-3 Operating switches F2-7 Real time clock DK10 F2-9                                                  | F2-1 |

| G .  | MEMORY OPERATION  Address Structure G-3  MA10 Core Memory G-4  MB10 Core Memory G-5  MD10 Core Memory G-6  ME10 Core Memory G-8  MF10 Core Memory G-9 | G-1  |

| Н    | OPERATION OF PERIPHERAL EQUIPMENT                                                                                                                     | H-1  |

| H1   | Console Equipment Paper tape reader H1-1 Paper tape punch H1-1 Console terminal H1-2                                                                  | H1-1 |

| H2   | Hardcopy Equipment                                                                                                                                    | H2-1 |

| H2.1 | Line Printer LP10  Models LP10F, H H2-1                                                                                                               | H2-1 |

|       | Models LP10B, C, D, E H2-4<br>Model LP10A H2-6                                                                                  |      |

|-------|---------------------------------------------------------------------------------------------------------------------------------|------|

| H2.2  | Plotter XY10                                                                                                                    | H2-6 |

| H2.3  | Card Reader CR10<br>Models CR10D, E, F H2-7<br>Model CR10A/B H2-9                                                               | H2-7 |

| H2.4  | Card Punch CP10                                                                                                                 | H2-9 |

| Н3    | Data Interfaces (to be added)                                                                                                   | H3-1 |

| H4    | Magnetic Tape                                                                                                                   | H4-1 |

| H4.1  | DECtape TD10                                                                                                                    | H4-1 |

| H4.2  | Standard Magnetic Tape TM10 Tape transport TU10 H4-4 Tape transport TU20 H4-6 Tape transport TU30 H4-7 Tape transport TU40 H4-8 | H4-3 |

| H5    | Disks and Drums (to be added)                                                                                                   | H5-1 |

| Н6    | Data Communications Data line scanner DC10 H6-1 Single synchronous line unit DS10 H6-2                                          | H6-1 |

| H7    | Cleaning Procedures                                                                                                             | H7-1 |

| H7.1  | Tape Equipment DECtape H7-1 Standard magnetic tape H7-2 Tapes H7-3                                                              | H7-1 |

| H7.2  | Disk Packs                                                                                                                      | H7-3 |

| H7.3  | Other Equipment Paper tape reader and punch H7-4 Line printer, H7-4 Card reader and punch H7-4                                  | Н7-4 |

| INDEX |                                                                                                                                 | I-1  |

| J     | Modifications to the A.I. Lab PDP-6 and KA10                                                                                    | J-1  |

| К     | KL10, KA10, and 166 I/O Status Bits                                                                                             | K-1  |

| L     | KL10 Information                                                                                                                | L-1  |

|       |                                                                                                                                 |      |

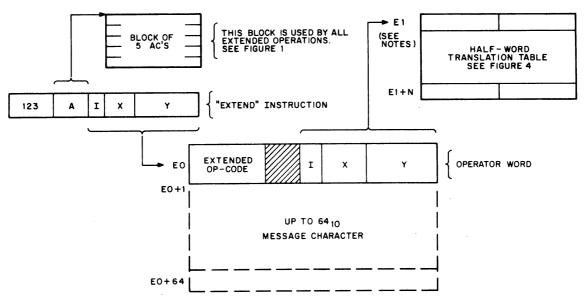

Extended Instruction Set Supplement

### 1

## Introduction

The DECsystem-10 is a general purpose, stored program computing system that includes at least one PDP-10 central processor, a memory, and a variety of peripheral equipment such as paper tape reader and punch, teletypewriter, card reader and punch, line printer, DECtape, magnetic tape, disk, drum, display and data communications equipment. Each central processor is the control unit for an entire large-scale subsystem, in which it is connected by an in-out bus to its own peripheral equipment and by a memory bus to one or more memory units in a main memory, some of whose units may be shared by several processors. Within the subsystem the central processor governs all peripheral equipment, sequences the program, and performs all arithmetic, logical and data handling operations. Besides central processors, there are also direct-access processors, which have much more limited program capability and serve to connect large, fast peripheral devices to memory bypassing the central processor. Every direct-access processor is connected to the in-out bus of some central processor, to which it appears as an in-out device; the direct-access processor is also connected to memory by its own memory bus, and to its peripheral equipment by a device bus. The DECsystem-10 may also contain peripheral subsystems, such as for data communications, which are themselves based on small computers; such a subsystem in toto is connected to a PDP-10 in-out bus and is treated by the PDP-10 as a peripheral device. Unless otherwise specified, the words "processor" and "central processor" refer to the large-scale PDP-10 central processor, and "in-out bus" refers to the bus from the central processor to its peripheral equipment. A direct-access processor and the bus to its peripheral equipment are all always referred to by their names, eg the DF10 data channel and its channel bus (often a direct-access processor and device control are a single unit).

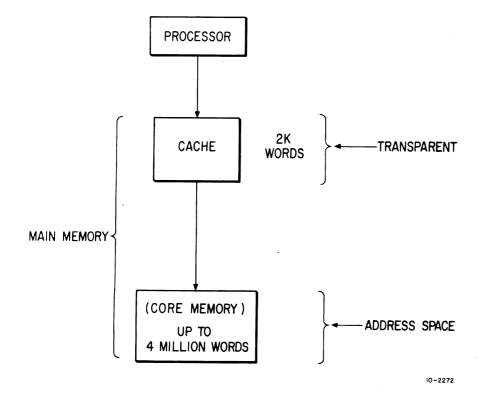

At present, there are three types of PDP-10 central processors, the KA10, the KI10, and the KL10. The three processors handle words of thirty-six bits, which are stored in a memory whose maximum capacity depends upon the addressing capability of the processor. Internally, the processors use 18-bit addresses and can thus reference 262,144 word locations in memory. This is the total addressing capability of the KA10. However, in the KI10 and KL10, it is only the virtual address space available to a single program. Paging hardware supplies four additional address bits to map pages in the program virtual address space into pages anywhere in a physical memory that is sixteen times as large. Thus for a number of different programs, the processor actually has access to a physical memory with a capacity of 4,194,304 words. Storage in memory is usually in the form of 37-bit words,

Confusion could result only in a chapter dealing with a small-computer subsystem. Here the small processor is usually referred to by its name (PDP-8, PDP-11) and the words "computer" and "memory" refer to the small computer. To differentiate, the PDP-10 is referred to by its name or as the "DECsystem-10 central processor", and the large scale memory connected to the PDP-10 memory bus is referred to as "DECsystem-10 main memory".

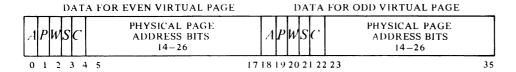

the extra bit producing odd parity for the word. The bits of a word are numbered 0-35, left to right (most significant to least significant), as are the bits in the registers that handle the words. The processor can handle half words, wherein the left half comprises bits 0-17, the right half, bits 18-35. There is also hardware for byte manipulation – a byte is any contiguous set of bits within a word. KA10 registers that hold addresses have eighteen bits, numbered 18-35 according to the position of an address in a word. The KI10 and KL10 internal address registers have eighteen bits, but a register that must supply a complete address to physical memory has twenty two bits (numbered 14-35). Words are used either as computer instructions in the program, as addresses, or as operands (data for the program).

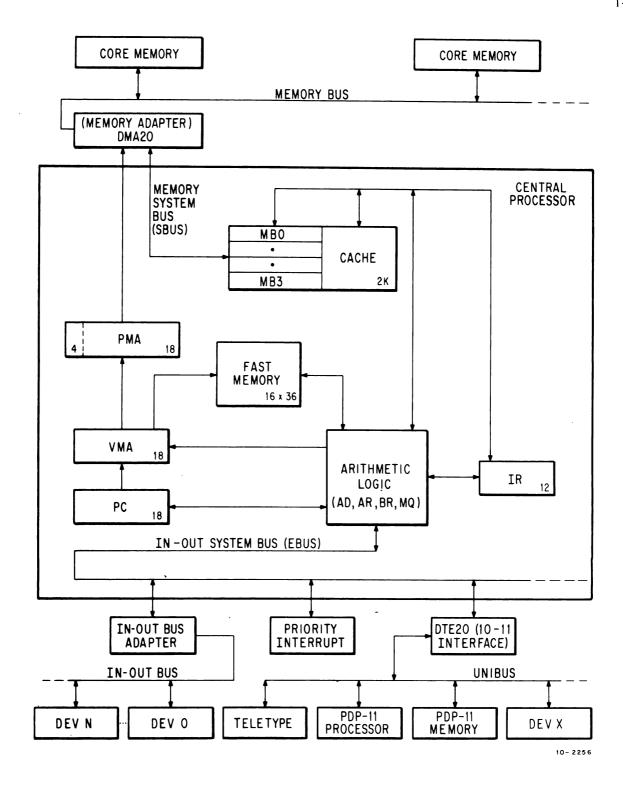

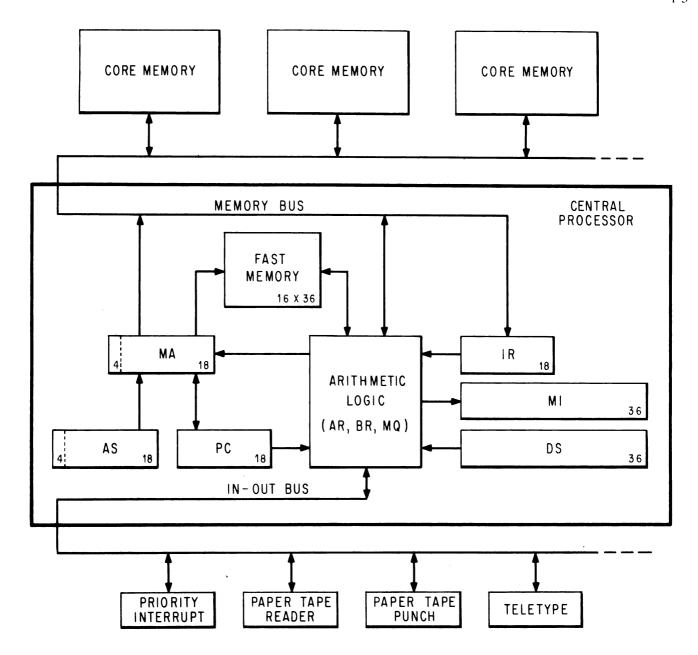

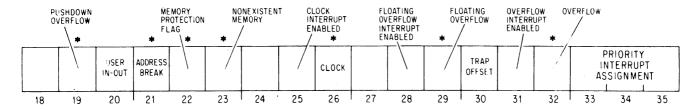

Of the internal registers shown in the illustration on the next page, only PC, the 18-bit program counter, is directly relevant to the programmer. The processor performs a program by executing instructions retrieved from the locations addressed by PC. At the beginning of each instruction PC is incremented by one so that it normally contains an address one greater than the location of the current instruction. Sequential program flow is altered by changing the contents of PC, either by incrementing it an extra time in a skip instruction or by replacing its contents with the value specified by a jump instruction. Also of importance to the KA10 and KI10 programmer are the sense switches and the 36-bit data switch register DS on the processor console; through these switches the program can read information supplied by the operator. The processor also contains flags that detect various types of errors, including several types of overflow in arithmetic and pushdown operations, and provide other information of interest to the programmer.

The processor has other registers, but the programmer is not usually concerned with them except when manually stepping through a program to debug it. On the KA10 and KI10, the operator can use the address switch register AS, to examine the contents of, or deposit information into, any memory location; stop or interrupt the program whenever a particular location is referenced; and through AS, the operator can supply a starting address for the program. Through the memory indicators MI the program can display data for the operator. In the KL10, these functions are provided by the PDP-11 console, which is connected to the KL10 by a hardware interface. The instruction register IR contains the left half of the current instruction word, ie, all but the address part. The memory address register MA (PMA in the KL10) supplies the address for every memory access. The heart of the processor is the arithmetic logic, principally the 36-bit arithmetic register AR. This register takes part in all arithmetic, logical and data handling operations; all data transfers to and from memory, peripheral equipment and console are made via AR. Associated with AR are an extremely fast full adder, a buffer register that holds a second operand in many arithmetic and logical instructions, a multiplier-quotient register MQ that serves primarily as an extension of AR for handling double length operands, and smaller registers that handle floating point exponents and control shift operations and byte manipulation.

From the point of view of the programmer however the arithmetic logic can be regarded as a black box. It performs almost all of the operations

DECSYSTEM-10 SIMPLIFIED, KL10

DECSYSTEM-10 SIMPLIFIED, KA10 AND KI10

necessary for the execution of a program, but it never retains any information from one instruction to the next. Computations performed in the black box either affect control elements such as PC and the flags, or produce results that are always sent to memory and must be retrieved by the processor if they are to be used as operands in other instructions.

An instruction word has only one 18-bit address field for addressing any location throughout all of the virtual address space. But most instructions have two 4-bit fields for addressing the first sixteen memory locations. Any instruction that requires a second operand has an accumulator address field,

The KI10 actually has four fast memory blocks (eight in the KL10), but only one of these is available to a program at any given time.

subroutine.

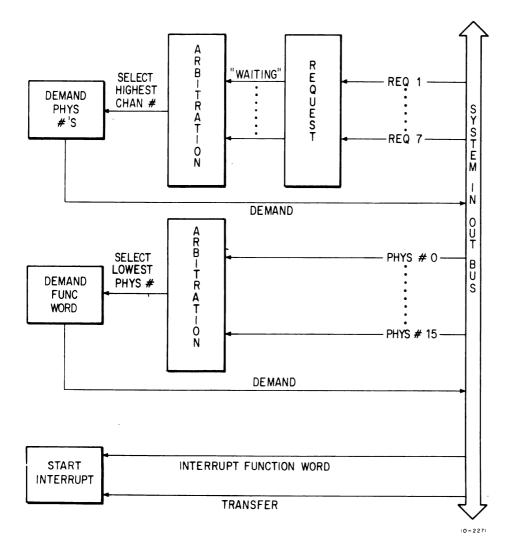

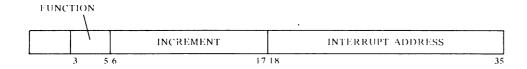

equipment to facilitate time sharing. The interrupt system facilitates processor control of the peripheral equipment by means of a number of priority-ordered channels over which external signals may interrupt the normal program flow. The processor acknowledges an interrupt request by executing the instruction contained in a particular location for the channel or doing some special operation specified by the device (such as incrementing the contents of a memory location). Assignment of channels to devices is entirely under program control. One of the devices to which the program can assign a channel is the processor itself, allowing internal conditions such as overflow or a parity error to signal the program.

Time Sharing. Inherent in the basic machine hardware are restrictions that

these locations whether they are addressed as accumulators, index registers

or ordinary memory locations. They can even be addressed from the

program counter, gaining faster execution for a short but oft-repeated

Besides the registers that enter into the regular execution of the program and its instructions, the processor has a priority interrupt system and

which can address one of these sixteen locations as an accumulator; in other words as though it were a result held over in the processor from some previous instruction (the programmer usually has a choice of whether the result of the instruction will go to the location addressed as an accumulator or to that addressed by the 18-bit address field, or to both). Every instruction has a 4-bit index register address field, which can address fifteen of these locations for use as index registers in modifying the 18-bit memory address (a zero index register address specifies no indexing). Although all computations on both operands and addresses are performed in the single arithmetic register AR, the computer actually has sixteen accumulators, fifteen of which can double as index registers. The factor that determines whether one of the first sixteen locations in memory is an accumulator or an index register is not the information it contains nor how its contents are used, but rather how the location is addressed. These first sixteen memory locations are not actually in core memory, but are rather in a fast solid state memory contained in the processor. This allows much quicker access to

The KI10 and KL10 allow unrestricted in-out with a limited number of devices for special real time applications.

apply universally: only certain instructions can be used to respond to a priority interrupt, and certain memory locations have predefined uses. But above this fundamental level, the time share hardware provides for different modes of processor operation and establishes certain instruction restrictions and memory restrictions so that the processor can handle a number of user programs (programs run in user mode) without their interfering with one another. The memory restrictions are dependent to a great extent on the processor, but the instruction restrictions are not, and these are relatively obvious: a program that is sharing the system with others cannot usually be allowed to halt the processor or to operate the in-out equipment arbitrarily. A program that runs in executive mode — the Monitor — is responsible for scheduling user programs, servicing interrupts, handling input-output needs, and taking action when control is returned to it from a user program. Any violation of an instruction or memory restriction by a user transfers control back to the Monitor. Dedication of the entire facility to a single purpose, in other words with only one user, is equivalent to

operation in executive mode (specifically kernel mode in the KI10 and KL10).

The KA10 has the two modes discussed above, user and executive. It also has protection and relocation hardware to confine the user virtual address space within a particular range, and to relocate user memory references to the appropriate area in physical core. A user ordinarily has access to two separate core areas, one of which may be write-protected, ie the user cannot alter its contents.

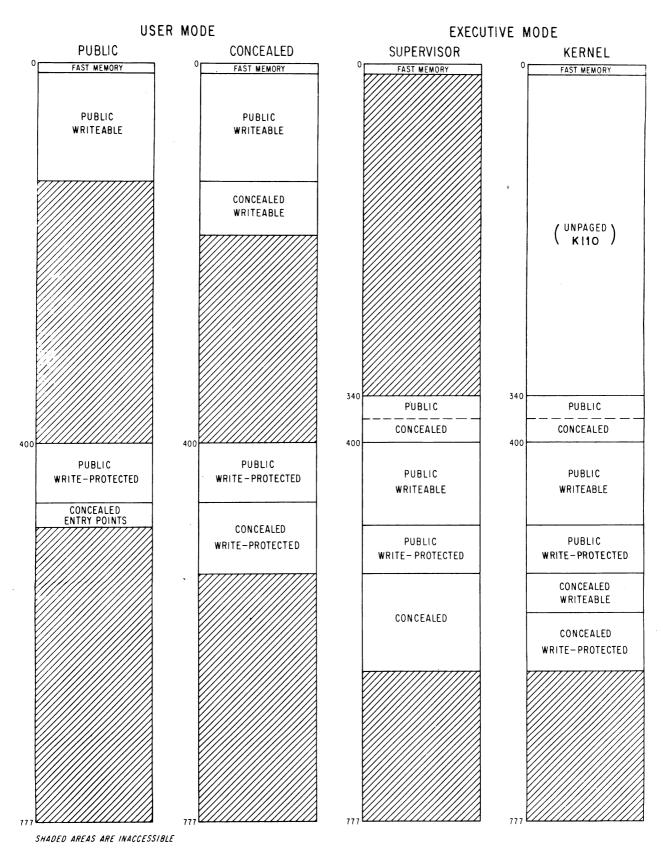

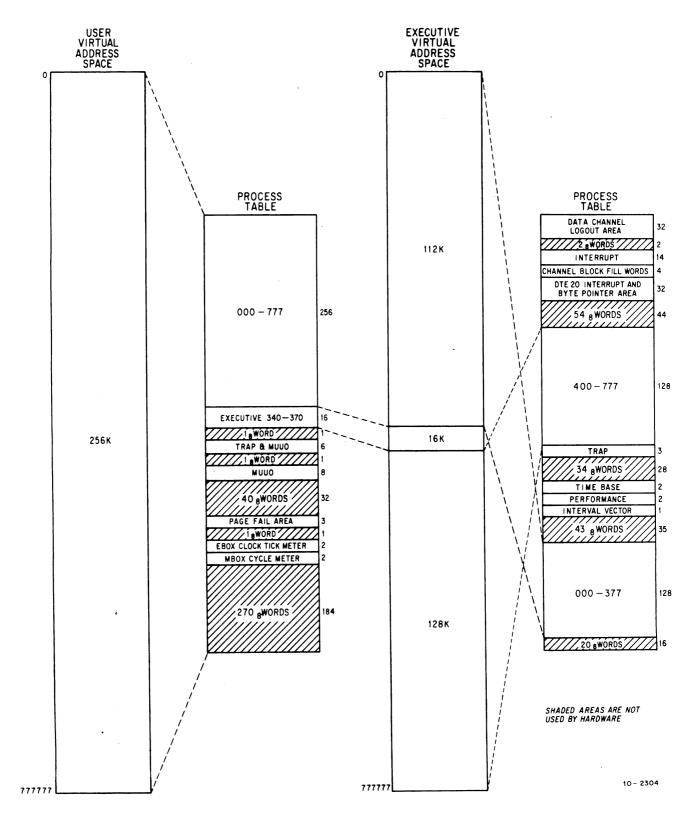

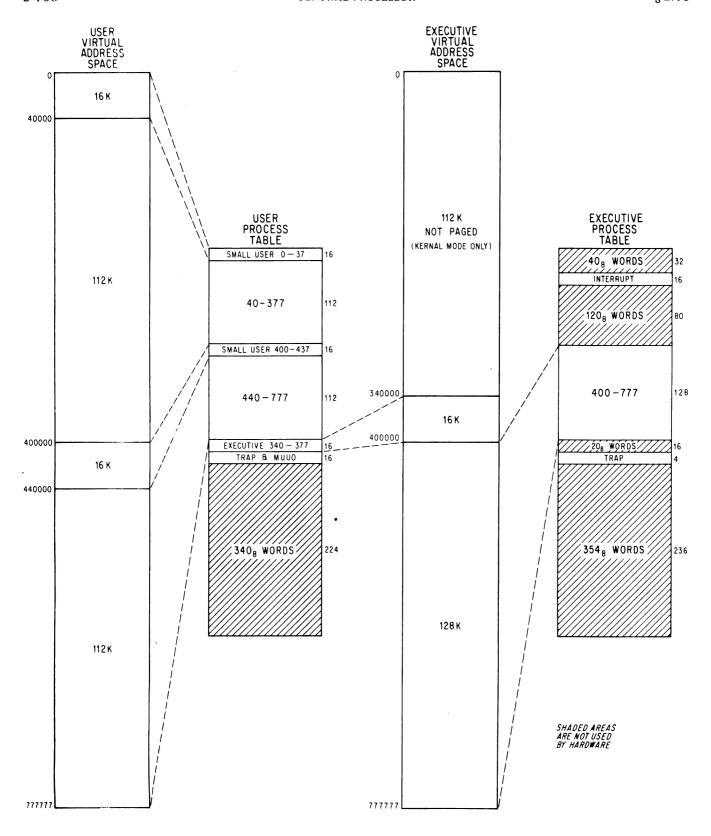

The KI10 and KL10 have paging hardware for the mapping of pages from the limited virtual address space into pages anywhere in physical memory. A page map for each program specifies not only the correspondence from virtual address to physical address, but also whether an individual page is accessible or not, alterable or not, and public or concealed. Both user and executive modes are subdivided according to whether the program is running in a public area or a concealed area. Within user mode these are the public and concealed modes; within executive mode, the supervisor and kernel modes. A program in concealed mode can reference all of accessible user memory, but the public program cannot reference the concealed area except to transfer control into it at certain legitimate entry points.

In kernel mode the Monitor handles the in-out for the system, handles priority interrupts, constructs page maps, and performs those functions that affect all users. This mode has no instruction restrictions and in the KI10 processor the program can even address some of memory directly (ie unpaged). In the KL10 processor, the entire executive address space is paged. In the paged address space, individual pages may be restricted as inaccessible or write-protected, but it is the kernel mode program that establishes these restrictions. In supervisor mode, the Monitor handles the general management of the system and those functions that affect only one user at a time. This mode has essentially the same instruction and memory restrictions as user mode, although the supervisor mode program can read, but not alter, the concealed areas; in this way the kernel mode Monitor supplies the supervisor program with information the latter cannot alter (even though the information is not write-protected from the kernel program). In either mode the Monitor automatically uses fast memory block 0 (the hardware requires this). The kernel program is responsible for assigning fast memory blocks to the various user programs: ordinarily blocks 2 and 3 are for special real time applications, and block 1 is assigned to all other users.

The illustration on the next page shows a typical layout of the virtual address space for the various modes. The space is 256K, made up of 512 pages numbered 0-777 octal. Any program can address locations 0-17 as these are in a fast memory block and are completely unrestricted (although the same addresses may be in different blocks for different programs). The public mode user program operates in the public area, part of which may be write-protected. The public program cannot access any locations in the concealed areas except to fetch instructions from prescribed entry points. The concealed mode user program has access to both public and concealed areas, but it cannot alter any write-protected location whether public or concealed, and fetching an instruction from the public area automatically returns the processor to public mode.

The concealed area would ordinarily be used for proprietary programs that the user can call but cannot read or alter.

TYPICAL VIRTUAL ADDRESS SPACE CONFIGURATION

In the KI10 only, the supervisor mode program is confined within the paged area of the address space, pages 340 and above. Part of the public area in this space may be write-protected, but the program can read information in the concealed areas — it cannot alter any location in a concealed area whether that area is write-protected or not. Pages 340—377 constitute the per-process area, which contains information specific to individual users and whose mapping accompanies the user page map. In other words the physical memory corresponding to these virtual pages can be changed simply by switching from one user to another, rather than the Monitor changing its own page map. The kernel mode program can access all of the unpaged area without restriction and can reference all of the accessible paged area, both public and concealed, with the usual restriction that it cannot alter a write-protected area. As in the case of concealed user mode, fetching an instruction from a public area returns control to supervisor mode.

### 1.1 NUMBER SYSTEM

The program can interpret a data word as a 36-digit, unsigned binary number, or the left and right halves of a word can be taken as separate 18-bit numbers. The PDP-10 repertoire includes instructions that effectively add or subtract one from both halves of a word, so the right half can be used for address modification when the word is addressed as an index register, while the left half is used to keep a control count.

The standard arithmetic instructions in the PDP-10 use twos complement, fixed point conventions to do binary arithmetic. In a word used as a number, bit 0 (the leftmost bit) represents the sign, 0 for positive, 1 for negative. In a positive number the remaining 35 bits are the magnitude in ordinary binary notation. The negative of a number is obtained by taking its twos complement. If x is an n-digit binary number, its twos complement is  $2^n - x$ , and its ones complement is  $(2^n - 1) - x$ , or equivalently  $(2^n - x) - 1$ . Subtracting a number from  $2^n - 1$  (ie, from all 1s) is equivalent to performing the logical complement, ie changing all 0s to 1s and all 1s to 0s. Therefore, to form the twos complement one takes the logical complement (usually referred to merely as the complement) of the entire word including the sign, and adds 1 to the result. In a negative number the sign bit is 1, and the remaining bits are the twos complement of the magnitude.

Zero is represented by a word containing all 0s. Complementing this number produces all 1s, and adding 1 to that produces all 0s again. Hence there is only one zero representation and its sign is positive. Since the numbers are symmetrical in magnitude about a single zero representation, all even numbers both positive and negative end in 0, all odd numbers in 1 (a

In the K110, the kernel address space (low 112K) is unpaged. In the KL10, the entire kernel address space is normally paged.

The adder actually acts as though the words represented 36-bit unsigned numbers, ie the signs are treated just like magnitude bits. In the absence of a carry into the sign stage, adding two numbers with the same sign produces a plus sign in the result. The presence of a carry gives a positive answer when the summands have different signs. The result has a minus sign when there is a carry into the sign bit and the summands have the same sign, or the summands have different signs and there is no carry.

Thus the program can interpret the numbers processed in fixed point addition and subtraction as signed numbers with 35 magnitude bits or as unsigned 36-bit numbers. A computation on signed numbers produces a result that

is correct as an unsigned 36bit number even if overflow occurs, but the hardware interprets the result as a signed number to detect overflow. Adding two positive numbers whose sum is greater than or equal to 235 gives a negative result, indicating overflow; but that result, which has a 1 in the sign bit, is the correct answer interpreted as a 36-bit unsigned number in positive form. Similarly adding two negatives gives a result which is always correct as an unsigned number in negative form.

Multiplication produces a double length product, and the programmer must remember that discarding the low order part of a double length negative leaves the high order part in correct twos complement form only if the low order part is null.

This convention for bit 0 of the low order word is inconsistent with that used for floating point arithmetic [see below]. This should cause no problem however, as fixed divide ignores bit 0 of the low order word in a double length dividend.

number all 1s represents -1). But since there are the same number of positive and negative numbers and zero is positive, there is one more negative number than there are nonzero positive numbers. This is the most negative number and it cannot be produced by negating any positive number (its octal representation is  $400000\,000000_8$  and its magnitude is one greater than the largest positive number).

If ones complements were used for negatives one could read a negative number by attaching significance to the 0s instead of the 1s. In twos complement notation each negative number is one greater than the complement of the positive number of the same magnitude, so one can read a negative number by attaching significance to the rightmost 1 and attaching significance to the 0s at the left of it (the negative number of largest magnitude has a 1 in only the sign position). In a negative integer, 1s may be discarded at the left, just as leading 0s may be dropped in a positive integer. In a negative fraction, 0s may be discarded at the right. So long as only 0s are discarded, the number remains in twos complement form because it still has a 1 that possesses significance; but if a portion including the rightmost 1 is discarded, the remaining part of the fraction is now a ones complement.

The computer does not keep track of a binary point – the programmer must adopt a point convention and shift the magnitude of the result to conform to the convention used. Two common conventions are to regard a number as an integer (binary point at the right) or as a proper fraction (binary point at the left); in these two cases the range of numbers represented by a single word is  $-2^{35}$  to  $2^{35} - 1$  or -1 to  $1 - 2^{-35}$ . Since multiplication and division make use of double length numbers, there are special instructions for performing these operations with integral operands.

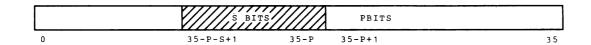

The format for double length fixed point numbers is just an extension of the single length format. The magnitude (or its twos complement) is the 70-bit string in bits 1-35 of the high and low order words. Bit 0 of the high order word is the sign, and bit 0 of the low order word is made equal to the sign. The range for double length integers and proper fractions is thus  $-2^{70}$  to  $2^{70} - 1$  and -1 to  $1 - 2^{-70}$ .

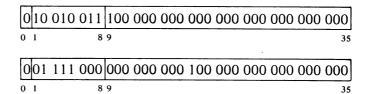

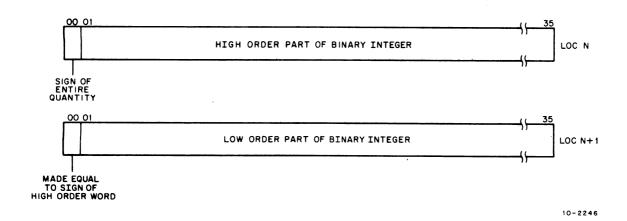

Floating Point Arithmetic. The KI10 and KL10 have hardware for processing single and double precision floating point numbers; the KA10 can generally process only single precision numbers, although the hardware does include features that facilitate double precision arithmetic by software routines. The same format is used for a single precision number and the high order word of a double precision number. A floating point instruction interprets bit 0 as the sign, but interprets the rest of the word as an 8-bit exponent and a 27-bit fraction. For a positive number the sign is 0, as before. But the contents of bits 9-35 are now interpreted only as a binary fraction, and the contents of bits 1-8 are interpreted as an integral exponent in excess  $128 (200_8)$  code. Exponents from -128 to +127 are therefore represented by the binary equivalents of 0 to 255  $(0-377_8)$ . Floating point zero and negatives are represented in exactly the same way as in fixed point: zero by a word containing all 0s, a negative by the twos complement. A negative number has a 1 for its sign and the two complement of the fraction, but since every fraction must ordinarily contain a 1 unless the entire number is zero (see below), it has the ones complement of the exponent code in bits 1-8. Since the exponent is in excess 128 code, an

actual exponent x is represented in a positive number by x + 128, in a negative number by 127-x. The programmer, however, need not be concerned with these representations as the hardware compensates automatically. Eg, for the instruction that scales the exponent, the hardware interprets the integral scale factor in standard twos complement form but produces the correct ones complement result for the exponent.

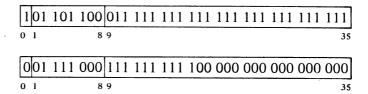

$$+153_{10} = +231_{8} = +.462_{8} \times 2^{8} =$$

$$\boxed{0 | 10 \ 001 \ 000 | 100 \ 110 \ 010 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 000 \ 00$$

Except in special cases the floating point instructions assume that all nonzero operands are normalized, and they normalize a nonzero result. A floating point number is considered normalized if the magnitude of the fraction is greater than or equal to ½ and less than 1. The hardware may not give the correct result if the program supplies an operand that is not normalized or that has a zero fraction with a nonzero exponent.

Single precision floating point numbers have a fractional range in magnitude of  $\frac{1}{2}$  to  $1-2^{-27}$ . Increasing the length of a number to two words does not significantly change the range but rather increases the precision; in any format the magnitude range of the fraction is  $\frac{1}{2}$  to 1 decreased by the value of the least significant bit. In all formats the exponent range is -128 to +127.

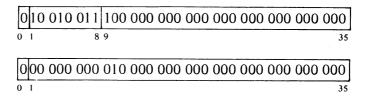

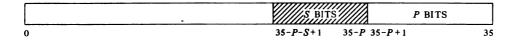

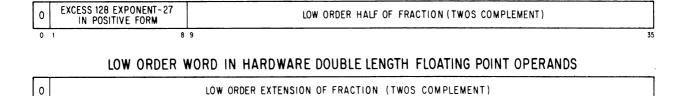

The precaution about truncation given for fixed point multiplication applies to most floating point operations as they produce extra length results; but here the programmer may request rounding, which automatically restores the high order part to twos complement form if it is negative. In single precision division the two words of the result are quotient and remainder, but in the other operations they form a double length number which is stored in two accumulators if the instruction is executed in "long" mode. (Long mode division uses a double length dividend.) A double length number used by the single precision instructions is in software double precision format. As such it contains a 54-bit fraction, half of which is in bits 9-35 of each word. The sign and exponent are in bits 0 and 1-8respectively of the word containing the more significant half, and the standard twos complement is used to form the negative of the entire 63-bit string. In the remaining part of the less significant word, bit 0 is 0, and bits 1-8 contain a number 27 less than the exponent, but this is expressed in positive form even though bits 9-35 may be part of a negative fraction. Eg the number  $2^{18} + 2^{-18}$  has this two-word representation in software

An instruction that generates a double length result sets the low word exponent part to zero whenever the low order fraction is zero, and sets the whole low order word to zero whenever the low order exponent overflows or underflows.

double precision format:

whereas its negative is

Essentially there are five number formats. Fixed point additive operations can be regarded as being performed on 36-bit unsigned numbers, which are equivalent to logical words. Otherwise fixed point arithmetic uses the fixed point format; numbers are single length with the exception that products and dividends can be double length, and there is provision for shifting a double length operand arithmetically. Double length format is an extension of single length format to two 36-bit words.

Single precision floating point instructions use two formats: single precision floating point format and software double precision floating point format. The latter appears only in the result of a long mode add, subtract or multiply, as the dividend in a long mode divide, and as the operand for an instruction that negates a number specifically in that format. Operands for double precision floating point instructions are exclusively in hardware double precision floating point format (and these instructions are not available on the KA10).

The double precision floating point instructions use a more straightforward double length format with greater precision than is allowed by the software format. For these instructions all operands and results are double length, and all instructions except division calculate a triple length answer, which is rounded to double length with the appropriate adjustment for a twos complement negative. In hardware double precision format the high order word is the same as a single precision number, and bits 1–35 of the low order word are simply an extension of the fraction, which is now sixty-two bits. Bit 0 is ignored. The number used above as an example of software double precision format has this representation in hardware format:

and its negative is

### 1.2 INSTRUCTION FORMAT

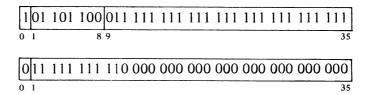

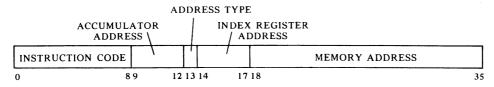

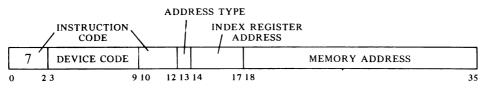

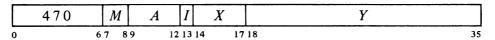

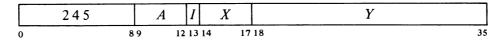

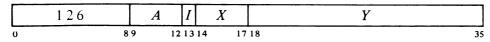

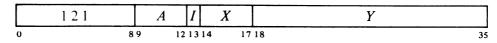

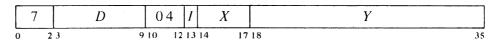

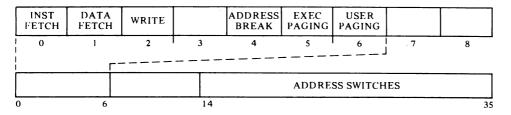

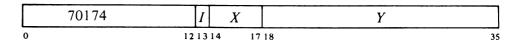

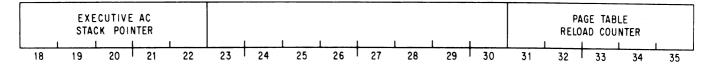

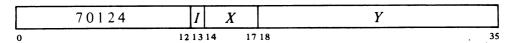

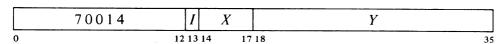

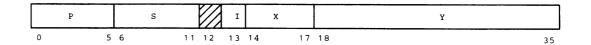

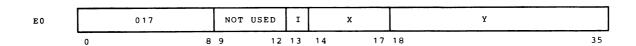

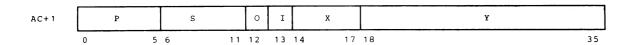

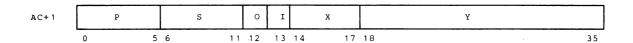

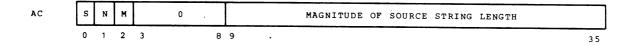

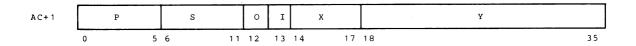

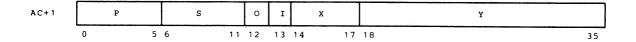

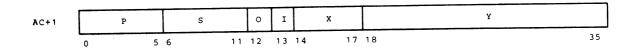

In all but the input-output instructions, the nine high order bits (0-8) specify the operation, and bits 9-12 usually address an accumulator but are sometimes used for special control purposes, such as addressing flags. The

rest of the instruction word usually supplies information for calculating the effective address, which is the actual address used to fetch the operand or alter program flow. Bit 13 specifies the type of addressing, bits 14–17 specify an index register for use in address modification, and the remaining eighteen bits (18–35) address a memory location. The instruction codes

BASIC INSTRUCTION FORMAT

that are not assigned as specific instructions are performed by the processor as so-called "unimplemented operations".

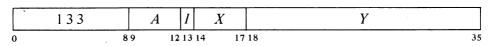

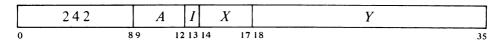

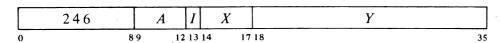

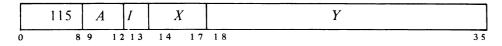

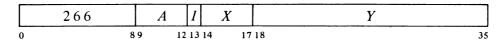

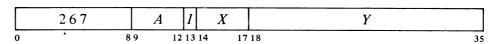

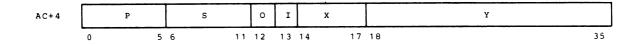

An input-output instruction is designated by three 1s in bits 0-2. Bits 3-9 address the in-out device to be used in executing the instruction, and bits 10-12 specify the operation. The rest of the word is the same as in other instructions.

IN-OUT INSTRUCTION FORMAT

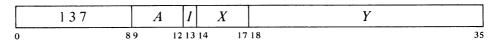

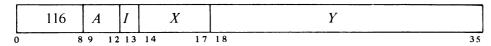

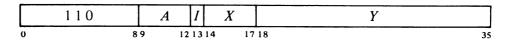

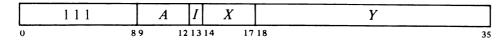

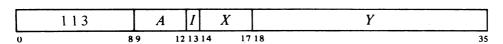

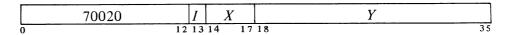

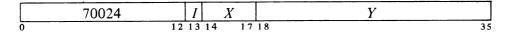

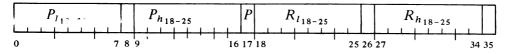

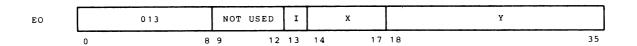

Effective Address Calculation. Bits 13-35 have the same format in *every* instruction whether it addresses a memory location or not. Bit 13 is the

| I  |    | X |    |    | Y |   |

|----|----|---|----|----|---|---|

| 13 | 14 |   | 17 | 18 | 3 | 5 |

indirect bit, bits 14-17 are the index register address, and if the instruction must reference memory, bits 18-35 are the memory address Y. The effective address E of the instruction depends on the values of I, X and Y. If X is nonzero, the contents of index register X are added to Y to produce a modified address. If I is 0, addressing is direct, and the modified address is the effective address used in the execution of the instruction; if I is 1, addressing is indirect, and the processor retrieves another address word from the location specified by the modified address already determined. This new word is processed in exactly the same manner: X and Y determine the effective address if I is 0, otherwise they are used for yet another level of address retrieval. This process continues until some referenced location is found with a 0 in bit 13; the 18-bit number calculated from the X and Y parts of this location is the effective address E.

The calculation outlined above is carried out for *every* instruction even if it need not address a memory location. If the indirect bit in the instruc-

Among the unimplemented operations are some that are specified as "unimplemented user operations" or UUOs (a mnemonic that means nothing to the assembler). Half of these are for the local use of a program (LUUOs) and the other half are for communication with the Monitor (MUUOs). In general, unassigned codes act like MUUOs.

On the other hand, please note that this calculation is carried

out only for words indicated in the text as having the format shown. Do not assume that the procedure is used for any miscellaneous pointer simply because it happens to contain an address [see page C-2].

### PLEASE READ THIS

The calculation of E is the first step in the execution of every instruction. No other action taken by any instruction, no matter what it is, can possibly precede that calculation. There is absolutely nothing whatsoever that any instruction can do to any accumulator or memory location that can in any way affect its own effective address calculation.

The KL10 contains a highspeed cache which holds some selection of words from the main memory system. This reduces access time and the percentage of main memory cycles required by the central processor. tion word is 0 and no memory reference is necessary, then Y is not an address. It may be a mask in some kind of test instruction, conditions to be sent to an in-out device, or part of it may be the number of places to shift in a shift or rotate instruction or the scale factor in a floating scale instruction. Even when modified by an index register, bits 18-35 do not contain an address when I is 0. But when I is 1, the number determined from bits 14-35 is an indirect address no matter what type of information the instruction requires, and the word retrieved in any step of the calculation contains an indirect address so long as I remains 1. When a location is found in which I is 0, bits 18-35 (perhaps modified by an index register) contain the desired effective mask, effective conditions, effective shift number, or effective scale factor. Many of the instructions that usually reference memory for an operand even have an "immediate" mode in which the result of the effective address calculation is itself used as a half word operand instead of a word taken from the memory location it addresses.

The important thing for the programmer to remember is that the same calculation is carried out for every instruction regardless of the type of information that must be specified for its execution, or even if the result is ignored. In the discussion of any instruction, E refers to the actual quantity derived from I, X and Y and used in the execution of the instruction, be it the entire half word as in the case of an address, immediate operand, mask or conditions, or only part of it as in a shift number or scale factor.

#### 1.3 MEMORY

The internal timing for each in-out device and each memory is entirely independent of the central processor. Because core memory readout is destructive, every word read must be written back in unless new information is to take its place. But the processor need never wait the entire cycle time. To read, it waits only until the information is available and then continues its operations while the memory performs the write portion of the cycle; to write, it waits only until the data is accepted, and the memory then performs an entire cycle to clear and write. To save time in an instruction that fetches an operand and then writes new data into the same location, the memory executes a read-modify-write cycle in which it performs only the read part initially and then completes the cycle when the processor supplies the new data. This procedure is not used however in a lengthy instruction (such as multiply or divide), which would tie up a memory that may be needed by some other processor. Such instructions instead request separate read and write access. The K110 further increases the speed of memory operation by overlapping memory cycles. Eg it can start one memory to read a word before receiving a word previously requested from a different memory.

Access times for the accumulator-index register locations are decreased considerably by substitution of a fast memory (contained in the processor) for the first sixteen core locations. Readout is nondestructive, so the fast memory has no basic cycle: the processor reads or writes a word directly (note: to write, the KA10 must first clear the location and then load it).

The following table gives the characteristics of the various memories. Modify completion is the time to finish a read-modify-write cycle after the processor supplies the new data. Times are in microseconds and include the delay introduced by ten feet (three meters) of cable. Fast memory times are for referencing as a memory location (18-bit address); when a fast memory location is addressed as an accumulator or index register, the access time is considerably shorter.

Read Write Modify Access Access Completion Cvcle Size 161 Core Memory 2.5 .49 4.7 2.69 16K 163 Core Memory .94 .49 1.8 1.33 16K 164 Core Memory .60\* .20\* 1.65\* .97 16K MB10 Core Memory MA10 Core Memory .61 .20 1.00 .57 16K MD10 Core Memory .83 .33 1.8 1.23 32-128K ME10 Core Memory .20 .61 1.00 .65 16K MF10 Core Memory .61 .20 1.00 32K,64K .63 MG10 Core Memory .67 .23 1.00 32-128K KA10 Fast Memory .21 .21 16K K110 Fast Memory 0. .28 16K KL10 Fast Memory .12 .08 16**K** 2K KL10 Cache Memory .16 .12

From the simple hardware addressing point of view, the entire memory is a set of contiguous locations whose addresses range from zero to a maximum dependent upon the capacity of the particular installation. In a system with the greatest possible capacity, the largest KA10 address is octal 777777, decimal 262,143; the largest KI10 or KL10 address is 17777777, decimal 4,194,303. (Addresses are always in octal notation unless otherwise specified.) But the whole memory would usually be made up of a number of core memories of different capacities as listed above. Hence a given address actually selects a particular memory and a specific location within it. For a 16K memory with 18-bit addressing, the high order four address bits select the memory, the remaining fourteen bits address a single location in it; selecting a 32K memory takes three bits, leaving fifteen for the location. The times given above assume the addressed memory is idle when access is requested. To avoid waiting for a previously requested memory cycle to end, the program can make consecutive requests to different memories by taking instructions from one memory and data from another. All memories can be interleaved in pairs i such a way that consecutive addresses actually alternate between the two memories in the pair (thus increasing the probability that consecutive references are to different memories). Appropriate switch settings at the memories interchange the least significant address bits in the memory selection and location parts, so that in any two memories numbered n and n+1 where n is even, all even addresses are locations in the first memory, all odd addresses are locations in the second. Hence memories 0 and 1 can be interleaved as can 6 and 7, but not 3 and 4 or 5 and 7. Some

\*Add .1 in a multiprocessor system.

MD10 can be increased in units of 32K up to 128K.

KI10 access to accumulators and index registers effectively takes no time - it is done in parallel with instruction operations that are required anyway. Retrieval of instructions or memory operands from fast memory is generally not worthwhile because of the extensive overlapping that speeds up core access. However, except in instructions that use two accumulators, storage of a memory operand in fast memory not only takes no time but actually decreases slightly the nonmemory time.

Information on memory setup is given in Appendix G. In the K110, the kernel mode program can always address locations 0-337777 as these are unpaged. Virtual pages 340 and above are mapped.

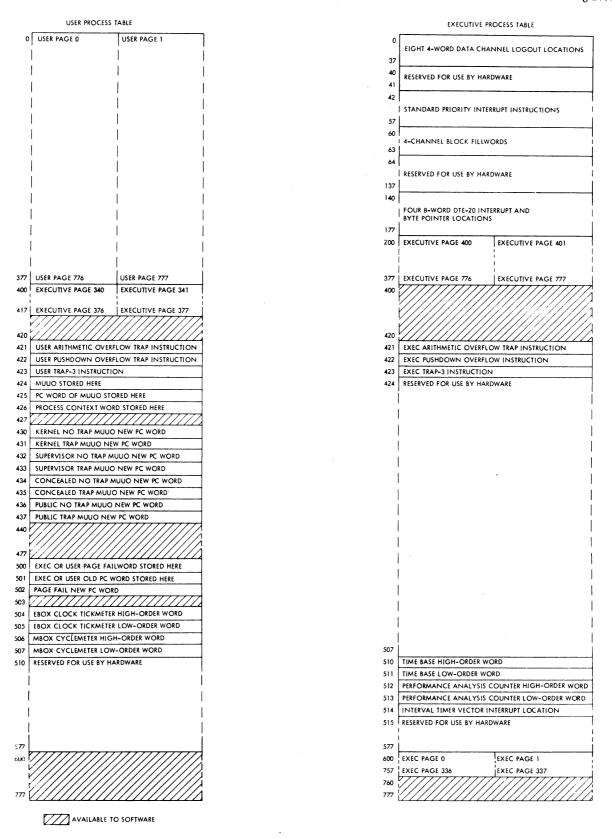

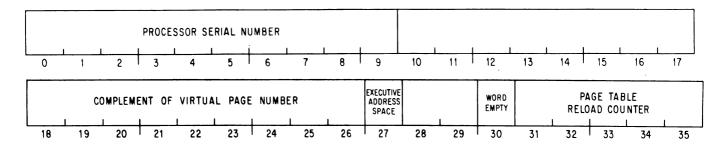

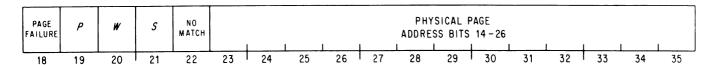

The Monitor keeps a user process table for each user program and one executive process table for itself for each K110 processor. In the text, the phrase "the user process table" refers to the process table currently specified by the Monitor as the one for the user, even if that user is not currently running. The Monitor must also specify the whereabouts of the executive process table for the processor under consideration.

The initial control word address for the DF10 Data Channel must be less than 1000.

memories can be interleaved in contiguous groups of four, where the number of the first memory in the group is divisible by four (eg memories 0-3 or 14-17). In this case all addresses ending in 0 or 4 reference the first memory in the group, all ending in 1 or 5 reference the second, and so forth.

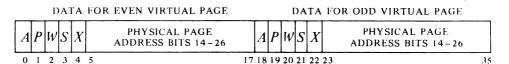

In terms of the virtual address space (the addresses that can be specified within the limits of the instruction format) or the subset of it that is accessible to a user, the situation may be quite different. In the KA10 the user program has a continuous address space beginning at 0, or two continuous spaces beginning at 0 and 400000. In the K110 the possible program address space is the set of all 18-bit addresses just as in the KA10, but which addresses a program can actually use depends entirely upon which of the 512 virtual pages (512 words per page) are accessible to it. For a so-called "small user", the accessible space must lie within the ranges 0-37777 and 400000-437777. In any event all programs have access to fast memory, whether as accumulators, index registers or ordinary memory references (*ie* addresses 0-17 are never restricted or relocated).

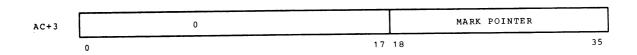

KI10 Memory Allocation. The KI10 hardware defines the use of certain memory locations, but most are relative to pages whose physical location is specified by the Monitor. The auto restart uses location 70. The only other physical locations uniquely defined by the hardware are those in fast memory, whose addresses are the same for all programs: location 0 holds a pointer word during a bootstrap readin, 0–17 can be addressed as accumulators, and 1–17 can be addressed as index registers. The only addresses uniquely specified in the user virtual space are for user local UUOs – locations 40 and 41.

All other addresses defined by the hardware, for use in page mapping, responding to priority interrupts, or other hardware-oriented situations, are to locations within a page specified by the Monitor for a particular user (including itself). For each user the Monitor keeps a process table, which must begin at location 0 of some page. The locations used by the hardware for the page map, traps, etc. of a given user are all in the first page of the table for that user. The parts of a user process table not used by the hardware may be used by the Monitor to keep accumulators (when the user is not running), a pushdown list that the Monitor uses for the job, and various user statistics such as running time, memory space, billing information, and job tables. The detailed configuration of the hardware-defined parts of the process tables (user and executive) is given in § 2.15.

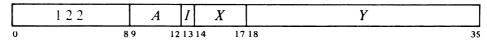

**KA10 Memory Allocation.** The use of certain memory locations is defined by the KA10 hardware.

| 0      | Holds a pointer word during a bootstrap readin |

|--------|------------------------------------------------|

| 0 - 17 | Can be addressed as accumulators               |

0-17 Can be addressed as accumulators

1-17 Can be addressed as index registers

Trap for unimplemented user operations (UUOs)

42–57 Priority interrupt locations

Trap for remaining unimplemented operations: these include the unassigned instruction codes that are reserved for future use, and also the byte manipulation and floating point instructions when the hardware for them is not installed

140-161 Allocated to second processor if connected (same use as 40-61 for first processor)

In a user program the trap for a local UUO is relocated to locations 40 and 41 of the user area; a Monitor UUO uses unrelocated locations. All other addresses listed are for physical (unrelocated) locations.

All information given in this manual about memory locations 40–61 for a KA10 applies instead to locations 140–161 for programming a second KA10 connected to the same memory.

#### 1.4 PROGRAMMING CONVENTIONS

The computer has five instruction classes: data transmission, logical, arithmetic, program control and in-out. The instructions in the in-out class control the peripheral equipment, and also control the priority interrupt and time sharing, control and read the processor flags, and communicate with the console. The next chapter describes all instructions mentioned above, presents a general description of input-output, and describes the effects of the in-out instructions on the processor, priority interrupt and time share hardware. Effects of in-out instructions on particular peripheral devices are discussed with the devices.

The Macro-10 assembly program recognizes a number of mnemonics and other initial symbols that facilitate constructing complete instruction words and organizing them into a program. In particular there are mnemonics for the instruction codes (Appendix A), which are six bits in in-out instructions, otherwise nine or thirteen bits. Eg the mnemonic

**MOVNS**

assembles as 213000 000000, and

MOVNS 2570

assembles as 213000 002570. This latter word, when executed as an instruction, produces the twos complement negative of the word in memory location 2570.

#### Note

Throughout this manual all numbers representing instruction words, register contents, codes and addresses are always octal, and any numbers appearing in program examples are octal unless otherwise indicated. On the other hand, the ordinary use of numbers in the text to count steps in an operation or to specify word or byte lengths, bit positions, exponents, etc employs standard decimal notation.

The initial symbol @ preceding a memory address places a 1 in bit 13 to produce indirect addressing. The example given above uses direct addressing, but

MOVNS @2570

assembles as 213020 002570, and produces indirect addressing. Placing the

The assembler translates every statement into a 36-bit word, placing 0s in all bits whose values are unspecified.

number of an index register (1-17) in parentheses following the memory address causes modification of the address by the contents of the specified register. Hence

which assembles as 213032 002570, produces indexing using index register 12, and the processor then uses the modified address to continue the effective address calculation.

An accumulator address (0-17) precedes the memory address part (if any) and is terminated by a comma. Thus

assembles as 213232 002570, which negates the word in location E and stores the result in both E and in accumulator 4. The same procedure may be used to place 1s in bits 9-12 when these are used for something other than addressing an accumulator, but mnemonics are available for this purpose.

The device code in an in-out instruction is given in the same manner as an accumulator address (terminated by a comma and preceding the address part), but the number given must correspond to the octal digits in the word (000-774). Mnemonics are however available for all standard device codes. To control the priority interrupt system whose code is 004, one may give

which assembles as 700600 001302, or equivalently

The programming examples in this manual use the following addressing conventions:

• A colon following a symbol indicates that it is a symbolic location name.

indicates that the location that contains ADD 6,5704 may be addressed symbolically as A.

♦ The period represents the current address, eg

is equivalent to

ullet Square brackets specify the contents of a location, leaving the address of the location implicit but unspecified. Eg

and

A: 7256004

are equivalent. The bracketed quantity can be given as the left and right halves separated by a double comma, not only eliminating the need to insert leading zeros for the right half, but allowing use of a minus sign for a negative half word as well. In other words

[-246, 135]

is equivalent to

[777532000135]

Anything written at the right of a semicolon is commentary that explains the program but is not part of it.

### 2

## Central Processor