DOCUMENT NO. Y240A201M0301 REV \_A

# ENGINEERING TECHNICAL REPORT

FOCAP SKC-2000 ASSEMBLER LANGUAGE REFERENCE MANUAL

DRR NO. 00807 (N/P)

THE SINGER COMPANY . KEARFOTT DIVISION . 1150 MCBRIDE AVENUE . LITTLE FALLS, N. J. 07424

F4200 4 2/72

eli Al

Y240A201M0301 REV A

FOCAP

SKC-2000

ASSEMBLER LANGUAGE

## **REFERENCE MANUAL**

Prepared by:

Engineering Programing and Computation

June 1974

Y240A201M0301 REV A

## FOCAP SKC 2000 ASSEMBLER LANGUAGE REFERENCE MANUAL

#### ABSTRACT

This document describes the syntax and function of the SKC 2000 (FOCUS) Assembly Language. An SKC 2000 computer program written in this language is automatically converted to machine language by Version 3 of the SKC 2000 (FOCUS) Assembly Program, FOCAP. The use of the 360/370 version of the FOCAP Assembler is described in the FOCAP Users' Manual (Y240A201M0302). These documents, with the SKC 2000 Principles of Operation Manual (Y240A200M0201), provide sufficient information for a programmer to prepare an SKC 2000 computer program.

This document was formerly published as Kearfott Engineering Technical Report, Document No. KD-71-60. The document number has been changed to Y240A201M0301 to be consistent with a new configuration control system. Similarly, the following KD numbers for the SKC 2000 programming manuals referenced herein have been changed to the indicated Y number.

KD-72-18 becomes KD-72-21 becomes KD-71-50 becomes Y240A201M0302 Y240A200M0201 Y240A204M0101

Users are invited to suggest improvements in this manual by using the form provided at the end.

## **REVISION RECORD**

| REV  | DESCRIPTION                                                    | APPROVAL<br>AND DATE |

|------|----------------------------------------------------------------|----------------------|

|      | RELEASE                                                        | MAY 1973             |

| A    | Substantial revisions to sections 3.2.6, 5.4.2, 3.1.2 and 3.3. | JUNE 1974            |

|      | Deleted sections 5.8.3 and 5.8.4 and Appendices C & D.         |                      |

|      | Less substantial changes to many other sections.               |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      | and an                     |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

|      |                                                                |                      |

| REV  |                                                                |                      |

| PAGE |                                                                | OTHER                |

## TABLE OF CONTENTS

|    |      |         |                            | PAGE |

|----|------|---------|----------------------------|------|

| 1. | INTR | ODUCTI  | ON                         | 1-1  |

| 2. | FOC  | AP LANG | JUAGE STRUCTURE            | 2-1  |

|    | 2.1  | SOUR    | CE LANGUAGE STATEMENT      | 2-2  |

|    |      | 2.1.1   | Label Entry                | 2-2  |

|    |      | 2.1.2   | Operation Entry            | 2-2  |

|    |      | 2.1.3   | Operand Entry              | 2-2  |

|    |      | 2.1.4   | Comment Entry              | 2-2  |

|    |      | 2.1.5   | Character Set              | 2-2  |

|    |      | 2.1.6   | Statement Format           | 2-2  |

|    | 2.2  | LANG    | UAGE ELEMENTS              | 2-4  |

|    |      | 2.2.1   | Symbols                    | 2-4  |

|    |      | 2.2.2   | Expressions                | 2-6  |

| 3. | ADD  | RESSING | G AND LOADING              | 3-1  |

|    | 3.1  | INTRA   | A-DECK ADDRESSING          | 3-2  |

|    |      | 3.1.1   | Short/Long Decision        | 3-2  |

|    |      | 3.1.2   | Location Counters          | 3-2  |

|    |      | 3.1.3   | Base Register Addressing   | 3-3  |

|    |      | 3.1.4   | Page Addressing            | 3-4  |

|    |      | 3.1.5   | Skip Addressing            | 3-4  |

|    | 3.2  | INTER   | -DECK ADDRESSING           | 3-6  |

|    |      | 3.2.1   | Entry Points               | 3-6  |

|    |      | 3.2.2   | External Symbols           | 3-6  |

|    |      | 3.2.3   | Common Areas               | 3-6  |

|    |      | 3.2.4   | TEMP (Stack) Areas         | 3-7  |

|    |      | 3.2.5   | Subroutine Call            | 3-7  |

|    |      | 3.2.6   | System Variables – COMPOOL | 3-8  |

|    | 3.3  | FOCAI   | P LOADER PROGRAM           | 3-9  |

|    |      | 3.3.1   | Memory Organization        | 3-9  |

|    |      | 3.3.2   | Loading Procedure          | 3-9  |

|    |      | 3.3.3   | Status                     | 3-13 |

## Y240A201M0301 REV A

## TABLE OF CONTENTS (Continued)

|    |     |          |                                                          | PAGE |

|----|-----|----------|----------------------------------------------------------|------|

| 4. | MAC | HINE LA  | NGUAGE INSTRUCTIONS                                      | 4-1  |

|    | 4.1 | ARITH    | IMETIC INSTRUCTIONS                                      | 4-3  |

|    |     | 4.1.1    | Operation Field                                          | 4-3  |

|    |     | 4.1.2    | Operand Field                                            | 4-5  |

|    | 4.2 | JUMP     | INSTRUCTIONS                                             | 4-7  |

|    |     | 4.2.1    | Operation Field                                          | 4-7  |

|    |     | 4.2.2    | Operand Field                                            | 4-7  |

|    | 4.3 | INDEX    | KREGISTER INSTRUCTIONS                                   | 4-9  |

|    |     | 4.3.1    | Operation Field                                          | 4-9  |

|    |     | 4.3.2    | Operand Field                                            | 4-9  |

|    | 4.4 | SHIFT    | INSTRUCTIONS                                             | 4-11 |

|    |     | 4.4.1    | Operation Field                                          | 4-11 |

|    |     | 4.4.2    | Operand Field                                            | 4-11 |

|    | 4.5 | NONM     | EMORY REFERENCE INSTRUCTIONS                             | 4-12 |

|    |     | 4.5.1    | Operation Field                                          | 4-12 |

|    |     | 4.5.2    | Operand Field                                            | 4-12 |

|    | 4.6 | INPUT    | OUTPUT INSTRUCTIONS                                      | 4-13 |

|    |     | 4.6.1    | Operation Field                                          | 4-13 |

|    |     | 4.6.2    | Operand Field                                            | 4-13 |

|    | 4.7 | BLOCK    | K TRANSFER INSTRUCTIONS                                  | 4-15 |

|    |     | 4.7.1    | Operation Field                                          | 4-15 |

| •  |     | 4.7.2    | Operand Field                                            | 4-15 |

| 5. | FOC | AP ASSEN | MBLER OPERATIONS                                         | 5-1  |

|    | 5.1 | LOCAT    | TION COUNTER OPERATIONS                                  | 5-4  |

|    |     | 5.1.1    | USE – Start Use of Location Counter                      | 5-4  |

|    |     | 5.1.2    | ORG – Specify An Absolute ORIGIN for the Program Segment | 5-5  |

|    |     | 5.1.3    | EVEN – Make Location Counter Even                        | 5-5  |

|    |     | 5.1.4    | COMMON – Allocate COMMON Data Area                       | 5-5  |

|    |     | 5.1.5    | TEMP – Temporary Data Area                               | 5-6  |

## TABLE OF CONTENTS (Continued)

| 5.2 | MEMOR                 | RY ALLOCATION OPERATIONS                        |                                                                                                                                         |

|-----|-----------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

|     | 5.2.1                 | DEC – Decimal Data Definition                   |                                                                                                                                         |

|     | 5.2.2                 | DEC16 – Halfword Decimal Data Definition        |                                                                                                                                         |

|     | 5.2.3                 | DEC64 – Double Precision Data Definition        |                                                                                                                                         |

|     | 5.2.4                 | HEX – Hexadecimal Data Definition               |                                                                                                                                         |

|     | 5.2.5                 | HEX16 – Halfword Hexadecimal Data Definition    |                                                                                                                                         |

|     | 5.2.6                 | SCLB – Binary Scale Operation                   | 같은 가 물건한 것 같은                                                                                                                           |

|     | 5.2.7                 | SCLB16 – Halfword Binary Scale Operation        |                                                                                                                                         |

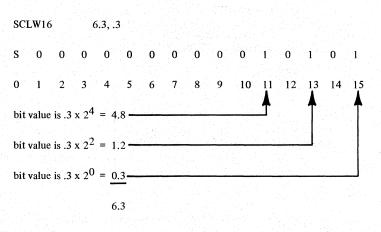

|     | 5.2.8                 | SCLW – Weighted Scale Operation                 |                                                                                                                                         |

|     | 5.2.9                 | SCLW16 – Halfword Weighted Scale Operation      |                                                                                                                                         |

|     | 5.2.10                | BSS – Block Started by Symbol                   |                                                                                                                                         |

|     | 5.2.11                | BES – Block Ended by Symbol                     |                                                                                                                                         |

|     | 5.2.12                | PTR – Pointer to Address                        |                                                                                                                                         |

| 5.3 | SYMBO                 | DL DEFINITION OPERATIONS                        |                                                                                                                                         |

|     | 5.3.1                 | EQU – Equate Symbol To Expression               | 가 있었는 가격 가지가 가지.<br>2017년 - 가구와 가지가 가지<br>2017년 - 1917년 |

|     | 5.3.2                 | SETD – Set Temporary Symbol to Decimal Number   | 영영 가슴 가슴 성격이 있                                                                                                                          |

|     | 5.3.3                 | SETX – Set Temporary Symbol To Hex Value        |                                                                                                                                         |

|     | 5.3.4                 | BIT – Assign a Symbol To a Bit                  |                                                                                                                                         |

| 5.4 | BASE R                | REGISTER OPERATIONS                             |                                                                                                                                         |

|     | 5.4.1                 | BASE – Base Register Designation                |                                                                                                                                         |

|     | 5.4.2                 | UBASE – Unconditional Base Register Designation |                                                                                                                                         |

|     | 5.4.3                 | DBASE – Drop a Base Register                    |                                                                                                                                         |

| 5.5 | SUBROUTINE OPERATIONS |                                                 |                                                                                                                                         |

|     | 5.5.1                 | ENTRY – Entry Point Designation                 |                                                                                                                                         |

|     | 5.5.2                 | CALL – Call Subroutine                          |                                                                                                                                         |

|     | 5.5.3                 | PROL – Subroutine Prologue                      |                                                                                                                                         |

|     | 5.5.4                 | SPROL – Short Subroutine Prologue               | 그는 말 모두 집에 가장 것을 물                                                                                                                      |

|     | 5.5.5                 | RETURN – Return From Subroutine                 |                                                                                                                                         |

| 5.6 | MODE (                | CONTROL OPERATIONS                              |                                                                                                                                         |

|     | 5.6.1                 | HALF – Half Word Arithmetic Mode                |                                                                                                                                         |

|     | 5.6.2                 | FULL – Full Word Arithemtic Mode                |                                                                                                                                         |

|     | 5.6.3                 | RTMX – Return to Memory Indexing                | 에 있는 것이 이 가지 않는 것이다.<br>19월 2일 - 이 이 이 관계에 있는 것이다.                                                                                      |

|     | 5.6.4                 | PAGE                                            |                                                                                                                                         |

| 5.7 | BIT MA                | NIPULATION OPERATIONS                           |                                                                                                                                         |

|     | 5.7.1                 | PUT Put 1 in Designated Bit Position            |                                                                                                                                         |

|     | 5.7.2                 | ZPUT - Set 0 in the Designated Bit Position     |                                                                                                                                         |

|     | 5.7.3                 | JMP – Jump If Bit is Set                        |                                                                                                                                         |

|     | 5.7.4                 | ZJMP – Jump If Bit is Zero                      |                                                                                                                                         |

PAGE

## TABLE OF CONTENTS (Continued)

| 5.8   | DOUBL   | E PRECISION FLOATING POINT MACROS          | 5-3 |

|-------|---------|--------------------------------------------|-----|

|       | 5.8.1   | LDAB – Double Precision Load Accumulator   | 5-3 |

|       | 5.8.2   | STAB – Double Precision Store Accumulator  | 5-3 |

| 5.9   | ARITH   | METIC STATEMENT (CMPL)                     | 5-3 |

| 5.10  | PROGR   | AM CONTROL OPERATIONS                      | 5-4 |

|       | 5.10.1  | END                                        | 5-4 |

|       | 5.10.2  | INT                                        | 5-4 |

| 5.11  | LIST CO | ONTROL OPERATIONS                          | 5-2 |

|       | 5.11.1  | LIST – Resume Listing                      | 5-4 |

|       | 5.11.2  | UNLIST – Suspend Listing                   | 5-4 |

|       | 5.11.3  | TTL – Define Page Title                    | 5-4 |

|       | 5.11.4  | EJECT – Start New Page                     | 5-4 |

|       | 5.11.5  | SPACE – Skip Blank Lines                   | 5-4 |

| ENDIX | A – SKO | C 2000 (FOCUS) MACHINE INSTRUCTION SUMMARY | A-  |

#### 1. INTRODUCTION

The SKC 2000 (FOCUS) airborne computer architecture was chosen particularly to facilitate programming in high level languages (e.g., PL/I, JOVIAL, CMS2) without loss of hardware efficiency. Toward that end, built-in floating point arithmetic is provided as well as powerful set of short (16 bit) instructions. The FOCAP Assembler Language was also developed as the next natural step toward programming in high level languages. FOCAP was designed to include many high level language features to both facilitate assembler language programming and to serve as an ideal target language for a compiler. It includes a set of powerful system macros for reentrant subroutine linkage, 25 location counters, automatic selection between short or long instructions, automatic sharing of scratchpad memory, COMMON data areas, system variables (COMPOOL-like) capability, and both relocatable and absolute addressing. The assembler program is complemented by a powerful loader program for allocating memory and linking external labels for a mixture of relocatable and absolute program segments. The assember/loader generates a load module which includes symbolic information. Hence, the simulator is designed to permit symbolic referencing of program information.

This manual describes the input language processed by the SKC 2000 (FOCUS) assembler program, FOCAP. It should be used in conjunction with the following manuals in developing an SKC 2000 computer program:

- SKC 2000 Principles of Operation (Document No. Y240A200M0201)

- SKC 2000 Subroutine Library Reference Manual (Document No. Y240A204M0101)

- SKC 2000 FOCAP Assembler Users Manual (Document No. Y240A201M0302).

It is presumed here that the reader is familiar with the content of the Principles of Operation manual, especially the sections on machine instruction format.

Y240A201M0301 REV A

THIS PAGE INTENTIONALLY LEFT BLANK

#### 2. FOCAP LANGUAGE STRUCTURE

An SKC 2000 (FOCUS) Computer Assembler Program (FOCAP) was developed to run on an IBM 360 or 370 computer. The Assembler was written almost exclusively in Fortran. Hence, it can be converted to run on similar host computers using a similar Fortran compiler. The source language processed by this Assembler is described in this document. Some basic language features are described in this section.

The FOCAP language provides a mnemonic (literally, memory aiding) machine instruction operation code for each machine instruction in the SKC 2000 airborne computer. The assembler language also contains mnemonic codes for assembler directive operations. These are used to provide the direction necessary for the assembler to perform its wide variety of auxiliary functions.

Assembler processing involves the translation of source statements into machine language, the assignment of memory words to instructions and data, and the development of all information required by the loader program for final memory allocation. The output of the assembler program is a relocatable or absolute object program module, a machine language translation of the input source program module. The assembler generates a printed listing of the source statements, side by side with their machine language translation, relocatable or absolute addresses, and additional information useful to the programmer in analyzing his program, such as error indications.

#### 2.1 SOURCE LANGUAGE STATEMENT

A FOCAP program consists of a sequence of source language statements or symbolic instructions. Each statement consists of one to four entries, which are from left to right: a label entry, an operation entry, an operand entry, and a comments entry. These entries must be separated by one or more blanks and must be written in the order stated. A brief description of each entry follows:

#### 2.1.1 Label Entry

The label entry is a symbol created by the programmer to identify a statement. The label symbol is used to reference the statement in the operand entry of other statements. A label entry is usually optional. Like all symbols, the label entry may consist of up to sixteen alphanumeric (or alphameric) characters, the first of which must be alphabetic.

#### 2.1.2 Operation Entry

The operation entry is the mnemonic operation code specifying the SKC 2000 machine operation, assembler operation or macro operation desired. An operation entry is mandatory (except for a full comment statement). Valid mnemonic operation codes for each machine operation are listed in Appendix A. All basic and macro FOCAP mnemonic operation codes are listed in Section 5 (Table 5-1). One of these valid mnemonic operation codes must appear in each FOCAP statement.

#### 2.1.3 Operand Entry

Operand entries identify and describe data to be acted upon by the machine or assembler operation. The operand entry has a variety of formats described in Sections 4 and 5. Depending on the requirements of the operation, one or more or no operands can be specified. Multiple operand entries must be separated by commas, and they cannot include embedded blanks.

#### 2.1.4 Comment Entry

Comments are descriptive items of information about the statement or the program that are included to clarify the program listing. Any printable character may be included in a comment, including blanks. An entire statement field can be used for a comment if an asterisk or period is punched in the first column.

#### 2.1.5 Character Set

The standard Fortran character set forms the basis for the FOCAP character set (except that any printable character may be used for comments). The character set for the label field is the alphabetic A-Z and the numbers 0-9 (hereinafter referred to as the alphanumeric or alphameric character set). The character set for the operation field is also the alphameric character set (A-Z, 0-9) combined to form a legal assembler mnemonic operation code. The character set of the operand field is the alphameric characters and the special characters shown below:

#### /\*.,+-() blank

For comments, any printable character is acceptable. For the IBM 360/370 version of the assembler, the EBCDIC character set is used.

#### 2.1.6 Statement Format

The primary input medium to the FOCAP assembler is 80 column card images. Source statements are usually punched one per card in the following format.

| LABEL FIELD                             | <b>OPERATION FIELD</b>                                                  | OPERAND FIELD                                                                 |

|-----------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| • Must start in column 1;               | • May not start in column 1.                                            | • Format depends on instruction used.                                         |

| • May be up to 16 characters in length; | • Must be a legal mnemonic operation code.                              | • One or more blanks must separate the operation field and the operand field. |

| • Must be a sumbol (see Section 2.4).   | • One or more blanks must separate the label field and operation field. |                                                                               |

| • Usually optional.                     |                                                                         |                                                                               |

Comments may be placed on a card in one of two ways: after at least one blank following the operand field, or after an asterisk (\*) or period (.) in column 1. If column 1 is left blank, the next field is assumed to be the operation field.

The fields are free format, with the exception that a label field or comment statement or operand must start in column 1; however, standard card columns for starting FOCAP fields are recommended for the sake of legibility. Figure 2-1 shows the standard FOCAP coding form, in which the operation field starts in column 8 and the operand field begins in column 15. In general, blanks delimit fields and commas delimit subfields. The operand field varies with the type of the operation (see Sections 4 and 5).

#### **KEARFOTT CODING FORM**

#### NAME ROGRAN LABEL OPERATIO OPERAND 10 40 70 20 illi 1.1.1.1.1 1.1.1.1.1 1111 I LI LI بتبتب i I i i TERESTATE FILTER FOR THE PERSON AND A DESCRIPTION OF THE PERSON AND A DESCRIPTION A and the state of the state of the second state 1.1 11 T CLI L 111111 IIII 11111 a 11 i i 11111 11 1.1.1 عنليد <u>i i i i i</u> Lilii 1111 Lilii 1111 11111 iili. citterentis (buschas) departmenter . . . . . . . 11111 **LILL** نبلب 51111 11111 <u>ulu</u> 1111 an an that t 1.54 e 5. 1 m コード そううりつつ <u>i din</u> i i i i i ..... int in i i i i i 11111 <u>inii</u>. i d i i i di na a baa maa maa maadaa ahaa ka maa ahaa ahaa ahaa maa maa maa ahaa a C P I I I I <u>iiiii</u> <u>iilii</u> 1 it it. 11111 11111 LILL i i i <u>riil</u>l 1111 cristin, 111 1.1

#### FIGURE 2-1. KEARFOTT CODING FORM

## SINGER

#### 2.2 LANGUAGE ELEMENTS

Before describing the various assembler operations in detail, let us discuss the basic language elements of FOCAP. Principal among these are expressions, symbols<sup>\*</sup>, and their attributes. Of course, the principal use of symbols and expressions is the mnemonic representation of a memory address or other numeric value. These language elements have their prime utility as constituents of the operand entry in FOCAP statements.

#### 2.2.1 Symbols

A symbol is represented by a string of one to sixteen alphameric characters (A-Z, 0-9), the first of which must be alphabetic. A FOCAP symbol is defined by its appearance as the label field of a statement. A symbol is usually defined only once in an assembly, unless it is a set-symbol. That is, each symbol used as the label of a statement must be unique within that assembly. A numeric value is associated with each symbol. Generally, a symbol in the label field of an instruction is assigned the value of the current location counter. The only exceptions are the SETD, SETX, BIT, and EQU operations whose label symbol is assigned the value specified by the operand field. When the assembler assigns values to symbols in the label field of statements defining instructions, constant data words, or variable data words, it chooses the address of the designated memory word. If the designated item occupies more than one (16 bit) memory word, the address of the leftmost or most significant (16 bit) word is assigned to the symbol.

Although the value of a symbol is its principal attribute, several other attributes are worthy of mention. A symbol value may be either absolute or relocatable based on the type of location counter it was allocated under. The symbol is then said to be either absolute or relocatable, accordingly. The value of a relocatable symbol is its displacement, in 16-bit words, from the origin of the location counter. A symbol value may be any integer from zero to  $2^{18}$  -1 (i.e., 262,143). This is the maximum addressing range of the SKC 2000 (FOCUS) computer. Since symbols are used to designate addresses, they may be used to form address fields for the short (16 bit) instructions. For jump instructions, the feasibility of using a short instruction is automatically established by the assembler based upon the difference between the current value of the location counter and the value of the symbol representing the destination (or target) address. For the short arithmetic instructions, the feasibility of using a short instruction is based primarily upon the difference between the current contents of each of the seven first level index (base) registers and the value of the symbol representing the operand address. In addition, if the symbol is absolute and within a specific range, the contents of Status Register Bits 2-5 can dictate a short instruction. With these definitions in mind, it is then sensible to talk about the short addressing attributes of a symbol in the operand field of a statement.

Symbols can also be distinguished by the nature of the information contained in the address they are referencing. For example, a symbol value may represent the address of an instruction, a constant data word, a variable data word, or an address pointer. In the latter case, the symbol may be said to have indirect addressing capability.

#### 2.2.1.1 Set-Symbols

Symbols normally assume a specific (absolute or relocatable) value which is retained throughout the assembly of the deck. However, the operations SETD and SETX can be used to define temporary symbols or set-symbols whose value can be changed during the assembly of a single deck. Once a symbol value has been specified by one of the SET operations, a subsequent definition of the same symbol by a SET operation is considered an assembly-time redefinition of the symbol value. A set-symbol may be redefined any number of times. However, regular permanent symbols (defined by any operation other than SETD or SETX) cannot be redefined via the two SET operations. Similarly, a set-symbol cannot be subsequently given a permanent value by appearing in another statement. By virtue of the variable nature of a set-symbol, it must be defined in a SET statement prior to any use of the symbol.

#### 2.2.1.2 External Symbols

Symbols which are used in the operand field of an instruction in a program but do not appear in the label field of another statement in the same program are assumed to be defined as entry points in another program, and, hence, are called external symbols. A table

\*Two popular alternate designations for symbol are "tag" and "label".

of external symbols is provided at the end of each assembly listing. When the loader encounters an external symbol, it expects to find, in the same loading operation, another program containing an entry point with the same symbol enabling resolution of the reference. If no entry point is found for an external symbol, the loader will print an appropriate error message.

#### 2.2.1.3 Asterisk Symbol

The asterisk charactet (\*) is used to specify a special symbol. When used in the operand field of an operation, it represents the current value of the location counter (either absolute or relocatable). Consequently, the asterisk (\*) need not be defined (assigned a value) like other symbols and, therefore, should never appear in the label field of a FOCAP statement. By its nature, the asterisk assumes a different value each time it is used. In this respect, it is similar to a temporary symbol or set-symbol, although it is not explicitly defined or redefined via the SET operations.

#### 2.2.1.4 Symbol Reference

A symbol is said to be defined by its appearance in the label field of a statement. A symbol is said to be referenced by its appearance in the operand field of a statement. There is, in general, no sequence restriction on the definition and reference of a permanent symbol; both forward referencing (reference preceding definition) and backward referencing (definition preceding reference) is permitted, except where otherwise noted (e.g., EQU operation). The following two examples illustrate the definition and use of symbols:

| • Forward I | Reference: |       |

|-------------|------------|-------|

|             | LDA        | SMBL1 |

|             | o          |       |

|             | 0          |       |

|             | 0          |       |

| SMBL1       | DEC        | 1.235 |

| • Backward  | Reference  |       |

| SMBL2       | LDA        | 0,4   |

|             | 0          |       |

|             | 0          |       |

|             | 0          |       |

|             | JN         | SMBL2 |

#### 2.2.1.5 Relative Addressing

As described above, the FOCAP assembler permits one statement to be referenced in another's operand field if the first statement defines a symbol in its label field. However, it also permits more complex forms of symbolic referencing including relative addressing. Once a statement has been named by the presence of a symbol in its label field, it is possible to refer to a second statement preceding or following the statement named by indicating the second statement's position relative to the named statement. This procedure is called relative addressing, and the operand entry would take the form:

s + n

where s represents the symbol in the label field of the named instruction and n represents a decimal integer (positive or negative) which represents the difference between the current values of the location counter at each statement. A more specific example would be

#### SYMBOL+6

#### 3. ADDRESSING AND LOADING

The SKC 2000 computer architecture provides a variety of techniques for addressing and intra-program communication. These capabilities are augmented and expanded by the FOCAP assembler and loader programs. This section is intended to provide the programmer with sufficient information about these techniques for him to use them effectively.

Y240A201M0301 REV A

#### 3.1 INTRA-DECK ADDRESSING

A program deck is a sequence of source program statements terminated by an END statement. As you will see later, a deck may contain several subroutines. The techniques available to permit one statement to reference another (within a deck) are discussed here.

#### 3.1.1 Short/Long Decision

The FOCAP assembler always attempts to construct short format instructions (16 bits long). The minimum criteria which must be met for the short form are:

- a. The programmer has not forced the long format in his coding (by appending L at the end of his statement).

- b. The instruction type does not dictate the long format (due to the amount of information it must contain).

- c. The operand or target address can be reached by a short instruction.

- d. The programmer has not specified an immediate or indirect operand.

- e. No conflict exists between the mnemonic and the arithmetic mode (fullword or halfword).

For jump operations, criterion c is satisfied, if the target address is within plus or minus 127 address locations of the address of the jump instruction. The assembler will perform this test only if both addresses are absolute or if both are relocatable under the same location counter. Otherwise, it constructs a long instruction automatically.

For arithmetic operations criterion c is satisfied if any one of the following conditions obtains:

- a. The operand address is absolute and a base register contains an absolute address less than 128 locations prior to the desired operand address.

- b. The operand address is relocatable and a base register contains a relocatable address under the same location counter which is less than 128 locations prior to the desired operand address.

- c. The operand address is absolute and within a specified range, and Status Register Bits 2-5 are set properly as described in Section 3.1.4.

Otherwise, it assumes a long instruction is required. In cases a and b above, the assembler must be informed (via the BASE or UBASE operation) that certain index registers have been designated as base registers and that they will be loaded with a specific address (usually designated symbolically) during execution of the SKC 2000 program. It is important to realize that the assembler does not react to executable statements (e.g., LDX, LXA) in keeping track of base register contents, since this would create ambiguities under many conditions. The programmer, therefore, must use the BASE or UBASE operation to inform the assembler of changes in base register contents.

#### 3.1.2 Location Counters

A location counter is used to assign memory addresses to program statements within a deck. The use of several location counters within a deck permits the user programmer to make several different types of memory allocation in the same deck. Table 3-I lists the several types which should be distinguished by the programmer, as a minimum. Each of these types should be allocated under a different location counter in the source deck. The Linkage/Editor and Loader program is then free to allocate each type to a different area of memory for system optimization reasons. Since there is provision in FOCAP for up to 25 location counters, the programmer is free to further segregate the source code for his own purposes. The user activates a location counter via a USE, TEMP

or COMMON statement. Once activated, memory is allocated under that location counter for all subsequent source statements until another location counter is activated. The user may freely switch among location counters at any point in the program deck.

A program segment assembled under a location counter can be absolute or relocatable. Hence the location counter is said to be correspondingly absolute or relocatable for that assembly. It is absolute if the first statement after the first USE or COMMON statement for that location counter is an ORG statement. The first address under each relocatable location counter is constrained to be even. Since all relocatable addresses are assembled relative to the first location under the location counter, the first location has a relative address of zero with subsequent addresses assigned in ascending order. Since the initial address is constrained to be even, a relocatable symbol with an even relocatable address is assured of being loaded at an even location in the SKC-2000. Each program has at least one location counter. If none is specified, location counter 0 is assumed. All location counters are typed according to Table 3-1. The first instruction, data definition, or data reservation operation coded immediately following the first USE or COMMON statement (paragraph 5.1) for a location counter defines the type for the block of all subsequent statements under that location counter.

As each machine instruction or data word is assembled, the value of the location counter is first adjusted to an even boundary if necessary. This adjustment is only necessary if the current location counter value is odd and the item being assembled consists of one or more 32 bit words. Next the location counter value is incremented by the length of the assembled item. Thus, it always points to the next available address. If the statement is named by a symbol in its label field, the symbol value is set equal to the current value of the location counter. Similarly, if an asterisk symbol is used in the operand field of a statement, it is assigned the same value as the location counter for that statement. An asterisk symbol in the operand field of a machine instruction statement is equivalent to placing a symbol in the label field and using that symbol in the operand field. The assembler listing includes the location counter value for each statement, whether labeled or unlabeled.

Only those statements which generate object code cause the location counter to be incremented. Since the number of 16 bit half words needed for each statement coded can vary, the location counter may be incremented by various values. For instance, some assembler operations such as USE, BASE or SETD, do not cause computer memory allocation and therefore, the location counter is not incremented. Other operations such as short machine instructions or data half words occupy one location and therefore, the location counter is increased by one. Long instructions and 32 bit data full words occupy two locations and increase the location counter is correspondingly increased. The FOCAP assembler has 25 location counters numbered 0 through 24 which can be established and controlled by the user.

#### 3.1.3 Base Register Addressing

When an index register is loaded with the address of the first word in a data block, for the purpose of serving as a pointer to the data block for short instructions, the index register is said to be used as a Base Register. Any of the first level index registers may be used as a Base Register.

#### TABLE 3-I. LOCATION COUNTER TYPE TABLE

#### WORD TYPE

#### ALLOCATION CLASS

Variables Constants COMMON Variables COMMON Constants Temporary (Stack) Variables Instructions Absolute & Relocatable Absolute & Relocatable Absolute & Relocatable Absolute & Relocatable Relocatable Only Absolute & Relocatable

Short arithmetic instructions can only access a small portion of the SKC-2000 memory without the use of Base Registers. However, by using all seven of the first level registers as Base Registers, seven different data areas can be accessed with short instructions. Each of these data areas can be located anywhere in the full (131K word) memory of the SKC-2000 computer since the base register holds a full 18 bit address. Thus, a short arithmetic instruction can address seven areas of 128 fullwords each (or 128 halfwords in halfword mode) via base registers as well as the 128 words which are addressable without indexing. The total addressing capability is, therefore, 1024 data words.

If given the proper information, the FOCAP Assembler will automatically choose the appropriate Base Register to permit a short arithmetic instruction to be assembled. The user must first specify the contents of each active Base Register via the BASE operation. Then if he writes a FOCAP arithmetic instruction with a simple symbol in the operand field, the assembler will determine whether the specified symbol is within the range of one of the Base Registers. If so, a short instruction is generated and the appropriate Base Register is automatically invoked.

For example, consider the program:

X Y Z

| DEC  | 321.2  |                         |

|------|--------|-------------------------|

| DEC  | 0.0    |                         |

| DEC  | 4096.3 |                         |

|      |        |                         |

| LDX  | 4,X,M  | Load XR4 with ADDR of X |

| BASE | 4,X    |                         |

| LDA  | Z      |                         |

|      |        |                         |

The LDA instruction will be assembled short. Base Register 4 will be invoked and the displacement between X and Z will be placed in the address field, M7, since the assembler is aware that XR4 is pointing at X and that Z is within its range (128 words). In this case, we say that the Base Register is invoked implicitly.

The UBASE operation permits any of the 15 index registers XR1,----, XR15 to be designated as an unconditional base register. Where the BASE operation causes invocation of a base register for short instructions, the UBASE operation causes the invocation of a base register for both long and short instructions. This is particularly useful when addressing data in a stack or data whose address is above 65535, the last data word which is directly addressable using the M16 address field.

#### 3.1.4 Page Addressing

Just as the BASE operation provides the assembler with the information needed to choose the appropriate Base Register when forming a short instruction, the PAGE operation provides the information needed to decide that the operand can be reached by a short instruction without indexing. Since Status Register bits 2 - 4 are used in the definition of the range of the short unindexed instruction (see Principles of Operation, Kearfott Document No. Y240A200M0201, for details) the PAGE operation is used to inform the assembler of the setting in SR2-SR4. Using this information, the assembler then automatically chooses a short unindexed instruction wherever the operand is within the region defined by SR2-4.

#### 3.1.5 Skip Addressing

Certain instructions cause the CPU to skip the next instruction in sequence and instead, execute the second instruction following the skip instruction. These instructions are: SAM, ICL, ICN and IMN. Since the instructions in the SKC-2000 can be both long (32 bits) and short (16 bits), and since long instructions must be located at an even address (i.e., they must occupy one memory word), some care is required in using the skip instructions.

For a short format skip instruction, the program counter is incremented by 1 when the skip is not taken and by 3 when it is taken. Incrementing the program counter by 3 causes the CPU to fetch the next instruction from the location whose address is 3 more than that of the skip instruction. To insure that only one instruction is skipped, the programmer should assure himself that each short format skip instruction is at an odd address. He should always construct a long instruction immediately following the skip instruction. If the short format skip instruction appeared at an even address, the resultant skip address would land on an odd address. This can create certain difficulties. For example, if a long instruction is to be skipped, it cannot be located in the two 16 bit words skipped by the instruction (since they are located at an odd address). Also, if it is desired to skip to a long instruction, it cannot begin at an odd address. These considerations are best illustrated by some examples.

If the short skip instruction is at an odd address (1001 in Example No. 1 in Figure 2-1), the next instruction will be at an even location (1002). If the skip is taken, program counter is incremented by 3, causing the CPU to take the next instruction from address 1004. In this case, either a long or short instruction can be placed in either location (1002 or 1004). However, two short instructions should not be placed in locations 1002 and 1003. Otherwise, they will both be skipped. The programmer, therefore, should force the instruction following a skip to be long or, if it must be short, to be followed by a NOP.

If the short skip instruction is at an even address (1000 in Example No. 2 in Figure 3-1), the next instruction will be at an odd location (1001). If the skip is taken, the program counter is incremented by 3, causing the CPU to take the next instruction from address 1003. In this case, a long instruction cannot be used in either of these odd locations (1001 or 1003). To alleviate this problem, the programmer should force the Skip instruction to be long if it is located at an even location, as in this example. The coding then becomes equivalent to Example No. 3 in Figure 2-1.

If a long skip instruction is employed, it must be at an even location (1000 in Example No. 3 in Figure 2-1). The next instruction will be at an even location (1002). If the skip is taken, the program counter is incremented by 4, causing the CPU to take the next instruction from address 1004. In this case, as in Example No. 1, either a long or short instruction can be placed in either location (1002 or 1004). Here, also, the programmer should force the instruction following a Skip to be long or, if it must be short, to be followed by a NOP. This assures that only one instruction will be skipped.

Note that Versions 5 and later of the FOCAP Assembler include provision for forcing these relationships. It will automatically make the appropriate long/short decisions on both the Skip Instruction and the following instruction (the one intended to be skipped).

| ADDRESS | EXAMPLE NO. 1    | EXAMPLE NO. 2    | EXAMPLE NO. 3         |

|---------|------------------|------------------|-----------------------|

| 1000    |                  | Skip Instruction | Long Skip Instruction |

| 1001    | Skip Instruction | Next Instruction |                       |

| 1002    | Next Instruction |                  | Next Instruction      |

| 1003    |                  | Skip Location    |                       |

| 1004    | Skip Location    |                  | Skip Location         |

| 1005    |                  |                  | [14] 관리 전 전 전 관리      |

#### FIGURE 3-1. SKIP INSTRUCTION EXAMPLES

#### 3.2 INTER-DECK ADDRESSING

This section is devoted to a description of the several alternatives available for transmitting information between FOCAP program decks. As before, a deck is defined as a sequence of source statements terminated by an END statement.

#### 3.2.1 Entry Points

Symbols may be defined in one deck and referred to by another, thus providing symbolic linkages between independently assembled programs. The linkages can be effected only if the assembler program is able to provide information about the symbol to the loader program, which resolves these linkage references at load time. In the program where the linkage symbol is defined, it must also be identified to the assembler by means of the ENTRY assembler operation. It is identified as a symbol that names an entry point, which means that another program may reference that location by using the same symbol in a jump instruction or a data reference instruction. The assembler places this information in the object deck for transmission to the loader.

#### 3.2.2 External Symbols

If a symbol is used in a program deck (i.e., appears in an operand field) but is not defined in the same program deck, the assembler assumes that it represents a symbol defined as an entry point in another program deck (see previous paragraph). It is identified then as an external or virtual symbol. The assembler places this information in the object code for transmission to the loader, which resolves these linkage references at load time. The assembler also prints a list of the external symbols at the end of each assembly for the programmer's reference.

If, at load time, no entry point can be found for an external symbol, an appropriate error message is printed.

#### 3.2.3 Common Areas

The COMMON operation can be employed to define labeled COMMON data blocks in several program decks. This permits each deck to reference the common data area in a manner precisely analogous to the use of labeled COMMON areas in FORTRAN.

Several COMMON areas can be defined which are distinguished by their labels. One unlabeled or blank COMMON can be used as well. Each subprogram that refers to one of the COMMON areas must include a definition of the memory allocation for the referenced COMMON in its source deck at assembly time. The loader program assigns a unique memory location to each labeled COMMON area despite the fact that it is defined in several program decks. Consequently, at execution time, each program that refers to data in a labeled COMMON will be referring to the same data. Furthermore, if a base register is loaded with the address of the first word in a labeled COMMON, the first 256 data words in that COMMON area can be accessed via short (16 bit) instructions. As a result, the careful use of COMMON blocks can be a significant factor in realizing a high density of short instructions in an SKC-2000 program.

The label of the COMMON area is the basis for inter-deck communication. The symbols associated with data words within a COMMON block are only for local reference (within the deck) and are not used for inter-deck communication. Two programs are referring to the same data word when it is the same distance from the beginning of each COMMON block definition. This same data word may be called X in the first program and Y in the second program and the COMMON blocks might be defined as follows:

| FIRST PROGRAM DECK |        |    | SECO | OND PROGRAM DECK |    |  |

|--------------------|--------|----|------|------------------|----|--|

| LABL               | COMMON | 10 | LABL | COMMON           | 9  |  |

| R1                 | BSS    | 10 | R    | BSS              | 14 |  |

| R2                 | BSS    | 4  | Y    | BSS              | 2  |  |

| X                  | BSS    | 2  |      |                  |    |  |

Note that both X and Y are located 14 locations from the top of the LABL COMMON area and they, therefore, refer to the same memory location.

The loader program automatically chooses the largest labeled COMMON block of the same name in allocating memory of that COMMON block.

Any COMMON block may be initialized to contain certain defined constants at absolute program load time (i.e., execution time). However, two rules must be observed:

- 1) At least the first statement under the COMMON declaration in question (labeled or unlabeled) must be a constant defining operation (e.g., DEC, HEX).

- 2) Two or more program decks referring to the same COMMON must not define conflicting constants for the same data positions.

Preferably, a particular COMMON which is to be initialized should have its constants declared by only one program deck (though any number of other decks may refer to these data as variables, or as identical constants, using arbitrary local symbolic locations).

#### 3.2.4 TEMP (Stack) Areas

The TEMP operation can be employed to define a variable data area (stack) to be shared between subroutines in separate decks. This permits the data area to be efficiently allocated in a manner precisely analogous to the use of the AUTOMATIC data type in PL/I. See the SKC-2000 Subroutine Library Reference Manual (Document No. Y240A204M0101) for a more detailed description of its implementation.

Briefly, the TEMP operation is used to denote the location counter under which all local (temporary) variables are normally allocated. For example, if a subroutine requires that four locations be used for intermediate computations, these should be allocated to the TEMP area. The standard FOCAP subroutine calling sequence (using the CALL, PROL, and RETURN operations) will allocate sufficient TEMP data area on entering a subroutine and will release this TEMP data area upon exiting. On release, of course, any data stored in the TEMP area is usually lost.

This automatic allocation/deallocation of the TEMP area is precisely analogous to the operation of a pushdown stack. As a result, a single memory cell may be used by several subroutines at different times. For many applications, this sharing of scratch data locations can result in substantial memory savings (see Document No. Y240A204M0101 for an example). In addition, in the SKC-2000 computer, some execution speed improvement can also be realized. This results from the fact that the LSI scratch memory in the SKC-2000 is faster than the main memory. If the TEMP area is assigned to the LSI fast scratch memory, these high speed cells will be shared by several routines with a resulting increase in speed over the unshared allocation of memory.

To accomplish reentrancy for all subroutines using the standard calling sequence, a different TEMP data area must be assigned to each major interrupt routine as well as the main program. This is accomplished by the FOCAP assembler via the INT operation. Once this is accomplished, there can be no interference when two interrupt programs call the same subroutine. Consequently, reentrancy has been accomplished.

#### 3.2.5 Subroutine Call

Information can also be transferred to a subroutine via the argument list in a CALL statement. This process is described in paragraph 5.5 and the SKC-2000 Subroutine Library Reference Manual. The arguments are transmitted in reentrant fashion via a stack of pointer information in the shared temporary data stack (TEMP) if the PROL statement is used in the subroutine for the prologue function.

#### 3.2.6 System Variables – COMPOOL

The short/long instruction decision is made at Assembly time as discussed in Section 3.1.1. The processing of ENTRY point references is done later since they are processed by the Loader. Consequently, a reference to an external ENTRY point will always result in a long instruction since the Assembler does not have the information necessary to decide that a short instruction is adequate. The use of COMMON solves this problem but at the cost of requiring that the definition of each labeled COMMON be included in any deck which references the labeled COMMON. This can create a substantial housekeeping problem for large or changeable COMMON regions. The System Variable capability was designed into the SKC-2000 FOCAP Assembler to alleviate this dilemma. It provides the Assembler with the ability to reference source code information derived from decks other than the deck being assembled. Hence, it is similar to the basic COMPOOL feature of the JOVIAL language. The principal value of the feature lies in that it permits short instructions to be generated without requiring the explicit inclusion of the source code for the referenced item.

More specifically, the system variable definition feature allows absolute symbols that are initially defined by the assembly of one or more program decks to be referenced in other program decks which are subsequently assembled. This is accomplished by saving the symbol tables from the initial assemblies and then, by means of a control card placed before a subsequently assembled program deck, causing the Assembler to consult one or more of the saved symbol tables to obtain the definitions of symbols which are referenced but undefined in the program deck being assembled. Optionally, the symbols whose definitions are to be sought from the saved symbol tables may be restricted to a specific list of symbols given at the beginning of a program deck, and then any other undefined symbols in the program will be treated as external references.

This list must be given if set symbol definitions are to be obtained from the saved symbol tables. When the definition of a one-bit symbol is extracted from a saved symbol table, its bit position is also extracted; thus, the initially assembled programs may define absolute BIT symbols for subsequent reference.

See the Assembler Users' Manual for details on the control cards used for Systems Variables.

#### 3.3 FOCAP LOADER PROGRAM

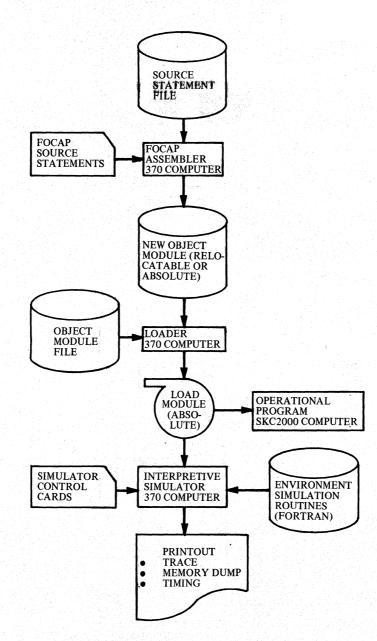

The SKC-2000 FOCAP Assembler Program converts a FOCAP source deck into an Object Module which contains object code (binary machine language) for each SKC-2000 instruction or data word designated in the source deck. However, the relocatable code will not yet be assigned a memory address and any instructions which directly reference relocatable or external operands will have an unresolved operand address field. The Object Module also contains information on the number and type of location counter under which each word was assembled. All the Object Modules comprising an SKC-2000 program are processed by the Loader Program which assigns an absolute memory address to each data and instruction word and resolves all operand address references to relocatable or external operands. The result is a Load Module which contains absolute machine code with its assigned memory address. The Load Module can be directly loaded into the SKC-2000 Computer. An outline of this process is shown in Figure 3-2.

#### 3.3.1 Memory Organization

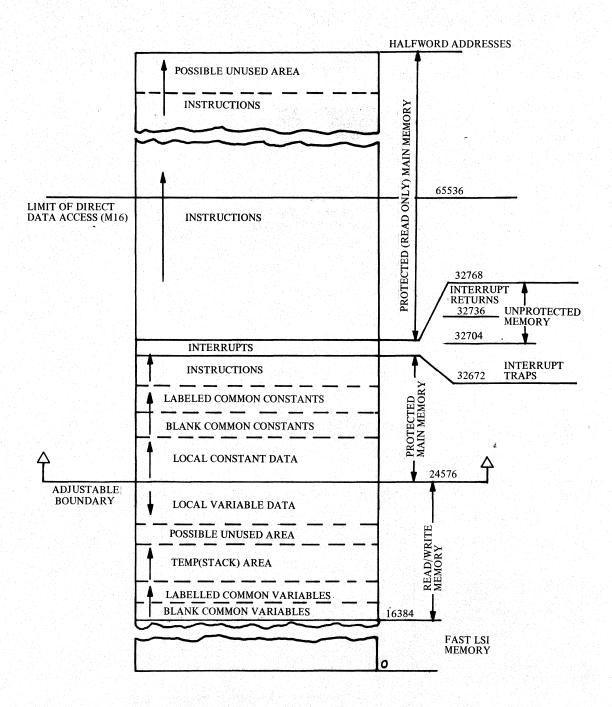

The main memory of the SKC-2000 computer is divided into two regions. One is available for variable data and may, therefore, undergo a Write operation. The other region (called the protected memory region) cannot be written into without the aid of test equipment. Hence during normal operation, inadvertent destruction of words in this area by a program is precluded by hardware. Data constants and instructions should reside in protected memory. Variable data must be allocated to unprotected memory.

The SKC-2000 main memory occupies contiguous addresses above 16384 and up to the main memory capacity of the machine. The maximum address can be as high as 262144 (or 131,074 fullwords). Addresses 0 to 16383 (or 8,192 fullwords) are reserved for fast LSI memory. If fast LSI ROM is supplied, it occupies contiguous addresses beginning at address 0 (the beginning of the LSI region). Fast writeable LSI memory occupies contiguous addresses ending at 16383 (the end of the LSI region). ROM memory can also be used as protected main memory which is accessed via the main bus. But then it will not result in increased execution speed.

For most SKC-2000 configurations, the unprotected (writeable) main memory is a contiguous region starting at address 16384 and ending at an adjustable boundary. The protected (read only) main memory is an essentially contiguous region starting at the boundary address and running to the maximum main memory address. One exception to this is a narrow band of unprotected locations for storing interrupt return addresses at the end of the first 8K main memory module (addresses just prior to 32768).

A minor hardware change (adding or deleting jumpers) will serve to change the boundary address between the protected and unprotected main memory regions. Consequently, the boundary address will tend to be different SKC-2000 applications. This boundary address plays a key role in the Loader's memory allocation algorithm, discussed below. Hence, it must be known by the Loader Program.

#### 3.3.2 Loading Procedure

Object code generated by the Assembler is processed by the Loader Program to resolve memory references, establish linkages and assign each instruction and dataword to the appropriate memory location.

The Assembler generates object code in the same sequence on tape as the source code it receives as input. The Loader also retains this sequence in its output code (load module). However, this tape sequence does not reflect the sequence of the code in memory, the allocation sequence. The memory allocation sequence is represented by the addressing information that accompanies the code in the object module and in the load module. The loader processes the partial memory allocation information inserted in the object module by the Assembler, and generates the final, complete memory allocation information which it includes in the load module. This section is devoted primarily to describing the procedure used by the Loader to determine the final memory allocation sequence.

First the Loader scans the object code for absolute segments whose memory location has been specified by the programmer using an ORG statement. Memory for these absolute segments is allocated first by the Loader. Any attempt to allocate a location twice will result in an error message. The relocatable segments are then allocated into the unused portion of memory. Allocation conflicts between absolute and relocatable segments are automatically avoided. To simplify subsequent discussion of allocation for relocatable segments we shall assume either that no absolute allocations have taken place or that their effect on the relocatable allocations is transparent.

#### FIGURE 3-2. SUPPORT SOFTWARE DATA FLOW

Relocatable data is assigned to the low main memory addresses while instructions are assigned the higher locations. This prevents overflow of the direct operand addressing region (up to address 65536) except in the most unusual circumstances. The program would have to include over 24,576 fullwords of constant or variable data in main memory for the boundary to be exceeded. If data is allocated beyond this boundary, it cannot be directly addressed by the M16 field in a basic arithmetic instruction. An index register would have to be employed to access it.

The Loader distinguishes between eight types of relocatable memory allocation and allocates each separately. These eight types and their order of allocation is given below:

- 1. Blank COMMON (Variables)

- 2. Labeled COMMON (Variable)

- 3. Temporary (Stack) Area

- 4. Local Variable Data

- 5. Local Constant Data

- 6. Blank COMMON (Constant)

- 7. Labeled COMMON (Constant)

- 8. Instructions

Different location counters are used to distinguish between the eight types. The first word allocated under a location counter determines whether the segment contains variable data, constant data, or instructions. Variable data must be specified by either the BSS or BES operations. Constant data is specified by any one of the following operations: DEC, DEC16, DEC64, HEX, HEX16, SCLB, SCLB16, SCLW, SCLW16 and PTR. Any machine instruction mnemonic will start an instruction segment. The operations COMMON and TEMP are used to invoke a location counter while further specifying the segment's allocation type.

All segments of the same type are allocated together as shown in Figure 3-3. In this figure, solid lines are used to designate physical boundaries and dotted lines indicate the separation between memory regions allocated to different types. Arrows indicate the direction of allocation for specific types.

More specifically, the Loader first scans all input decks to determine whether Blank COMMON has been used to allocate variable data. If so, it determines its length and then reserves the necessary area starting at location 16384 (the start of the relocatable allocation region). Next, the Loader scans all input decks to determine whether labeled COMMON has been used to allocate variable data. If so, it determines the length of each labeled COMMON and then reserves the necessary area just beyond the end of blank (variable) COMMON if it exists. If several labeled COMMON's are used, they are allocated in the order they are presented to the Loader.

Next the Loader scans all input decks to determine whether one or more TEMP (or STACK) areas are specified. A stack can only be used for variable data. If a stack is specified, the Loader analyzes the tree structure of the stack to determine its worst case memory requirement as described in the Subroutine Library Reference Manual. It then reserves the necessary area for each stack just beyond the end of the labeled (variable) COMMON area.

All remaining variable data is considered local to the defining routine and is allocated in the Local Variable Data area. Each deck is scanned for location counter segments used for this purpose. Their total memory requirement is determined and the necessary area allocated just before the boundary of the protected and unprotected main memory regions as shown in Figure 3-3. If this allocation is sufficiently large as to cause an overlap in allocation with the TEMP (Stack) Area, an error message indicating a memory allocation conflict will be issued. This concludes the allocation of variable data to unprotected memory.

Next the Loader must allocate constants and instructions to the protected memory region. As shown in Figure 3-3, this region runs from the boundary (address 24576 in the example shown) to the end of main memory, except for the narrow unprotected region for interrupts. The interrupt region is treated by the Loader as an absolute allocation. Hence, it is automatically excluded from the relocatable allocation region. The Loader scans all decks for segments which contain local constant data and allocates them to the first locations in protected memory, where they are certain to be directly addressable.

#### FIGURE 3-3 TYPICAL MEMORY LOAD

Y240A201M0301 REV A

The Loader then allocates blank COMMON, if used for constant data, followed by labeled COMMON for constant data and finally the instructions are assigned throughout the remainder of main memory if necessary. Usually, the instruction region is by far the largest single allocation region.

This completes the memory allocation procedure although a final note on use of multiple location counters is in order. If several location counters are used for a single memory allocation type within a single deck, the lower numbered location counter segments are allocated first.

#### 3.3.3 Status

Version 3 of the Loader Program performs precisely as described above. Singer-Kearfott has presently under development an improved Linkage Editor and Loader Program (Version 5) which is host computer portable and which provides more user controls over the memory allocation process. This new Loader is one component in a complete set of host machine portable support software for the SKC-2000 Computer.

Y240A201M0301 REV A

THE SINGER COMPANY KEARFOTT DIVISION

THIS PAGE INTENTIONALLY LEFT BLANK

Y240A201M0301 REV A

#### 4. MACHINE LANGUAGE INSTRUCTIONS

This section describes the rules for preparing source language statements which, when processed by the assembler program, produce SKC-2000 machine language instructions. The assembler uses the mnemonic in the operation field of a FOCAP statement to generate the operation code of the corresponding machine instruction. The operand field of a FOCAP statement contains any designator for other fields in the machine instruction.

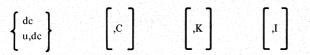

In describing the syntax of the operand field, it will be useful to employ some general notation. For example, lower case characters are employed in a symbol which represents a family of possible source code items. For example, u represents any valid FOCAP expression, such as: X, RANGE, Y2, X+Y, R-9, etc. In general, upper case characters are used to indicate source code in a literal sense.

Where options are available for fields in the source statement, brackets are used to denote a choice of any one or none of the enclosed language elements. For example,

$\left[\begin{array}{c} X\\ X+3\\ u,x1 \end{array}\right]$

is used to indicate a choice of any one of the three expressions

1. X 2. X+3 3. u,x1

or none of these expressions. Braces are used similarly except that one of the enclosed items must be chosen. For example,

$\left\{\begin{array}{c} x1\\ x1, x2\end{array}\right\}$

is used to indicate a choice of any one of the expressions

#### x1 or x1,x2.

Several other standard notations are employed in describing the source code syntax and the more general of these are defined below:

| Notation  | Definition                                                                                                                                                                                                       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| u         | Represents an absolute or relocatable expression (see Section 2.4) which is used to define the address field in an instruction.                                                                                  |

| X         | Represents a decimal integer from 0-15 or a set-symbol as defined in Section 5, which is used to designate one of the index registers (XRO-XR15).                                                                |

| <b>x1</b> | Represents a decimal integer from 1-7 or a set symbol which designates one of the seven first-level index registers (XR1-XR7). The x1 notation is commonly used to define the X1 field in a machine instruction. |

x2 Represents a decimal integer from 1-15 or a set-symbol which designates one of the fifteen index registers (XR1-XR15). The x2 notation is commonly used to define the X2 field in a machine instruction.

#### Notation

#### Definition

- I 🐘 Designates the indirect addressing option which causes bit 13 in the long machine instruction to be set to one.

- M Designates the immediate operand option which causes bit 14 in the long machine instruction to be set at one.

- L Designates the long option which causes the assembler to generate the long form of an otherwise short instruction.

- Bi Designates the ith index register XRi being used as a base register.

- () Designates the contents of the register or instruction subfield which is specified within the parentheses.

Some further notation used for specific statement descriptions is defined in the appropriate sections. The descriptions for SKC-2000 instructions are grouped according to the source statement syntax and each group is discussed separately below.

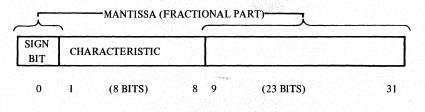

#### 4.1 ARITHMETIC INSTRUCTIONS

The majority of SKC-2000 machine instructions are in the Arithmetic Group and share the same basic instruction format, as described in the Principles of Operation Manual. Each of them has both a short (16 bit) format and a long (32 bit) format. The assembler attempts to generate the short form of an arithmetic instruction whenever possible. If a base register has been specified by a previous BASE or UBASE statement in the source program deck, and if the operand (denoted by u) is within its range, the assembler will generate a short instruction. The operand is within range of the base register if

u - (Bi) < 128 for halfword data

or

u - (Bi) < 256 for fullword data

When a short instruction is thus generated, the three bit X1 field is loaded with the value i which identifies (or specifies) the controlling base register, Bi. The seven bit M7 address field is then loaded with the appropriate displacement

M7 = u - (Bi) for halfword data

or

M77 = (u - (Bi)) for fullword data

Note that the effect is to cause the SKC-2000 (at execution time) to form the effective address E equal to the value of u, the desired operand address. A more detailed explanation of the BASE and UBASE operations is given in Section 5.

If u is an absolute expression, and if an appropriate absolute valued base register is not available, the assembler will attempt to construct a short instruction in conjunction with the contents of Status Register bits 2-5 as described in Section 3.1.4. Failing this, the assembler will construct a long instruction.

#### 4.1.1 Operation-Field

This section lists all the valid mnemonic code entries for the operation field of an arithmetic instruction.

| MNEMONIC | <b>OPERATION SUMMARY</b>                                   |

|----------|------------------------------------------------------------|

| ADF      | Add floating point                                         |

| ADL      | Add lower fix point                                        |

| ADU      | Add upper fix point                                        |

| AFD      | Add double precision floating point                        |

| AND      | Logical AND                                                |

| DVD      | Divide fix point                                           |

| DVF      | Divide floating point                                      |

| EXO      | Exclusive OR                                               |

| LAE      | Load A register with effective address                     |

| LDA      | Load A register                                            |

| LDB      | Load B register                                            |

| LDI      | Load interrupt mask register                               |

| LDS      | Load status register                                       |

| LOR      | Logical OR                                                 |

| MLF      | Multiply floating point                                    |

| MUL      | Multiply fix point                                         |

|          | 그는 사람은 모퉁 것이는 방법에서 물건을 가운데 가슴이 물건하다. 그 가슴은 눈 것 때마다 위험을 가지? |

Y240A201M0301 REV A

MNEMONIC

## **OPERATION SUMMARY**

| RTA   | Return Address                                            |

|-------|-----------------------------------------------------------|

| SAM   | Skip on A register masked                                 |

| SBF   | Subtract floating point                                   |

| SBL   | Subtract lower fix point                                  |

| SBU   | Subtract upper fix point                                  |

| SFD   | Subtract double precision floating point                  |

| STA   | Store A register                                          |

| STB   | Store B register                                          |

| STI   | Store interrupt mask register                             |

| STS   | Store status register                                     |

| ADFR  | Add floating point, return to memory                      |

| ADLH  | Add lower fix point, half word                            |