## Xerox Data Systems

# IC DIGITAL LOGIC MODULES T Series Description and Specifications

Revision 5 September 1969

# SDS T SERIES Integrated Circuit Logic Modules

#### CONTENTS

| I.   | INTRODUCTION AND GENERAL SPECI | FICATIONS 1       |

|------|--------------------------------|-------------------|

| II.  | DESCRIPTIONS OF MODULES        | 19                |

| III. | ACCESSORIES AND SERVICES       | 75                |

|      | PRODUCT INDEX AND PRICE LIST   | Inside Back Cover |

#### THE SDS APPROACH TO MODULES

Logic modules offered by Scientific Data Systems are designed by experienced circuit engineers for system applications. The T Series modules were originally designed for use in the successful SDS Sigma Series general purpose computers, peripherals, and related special-purpose systems.

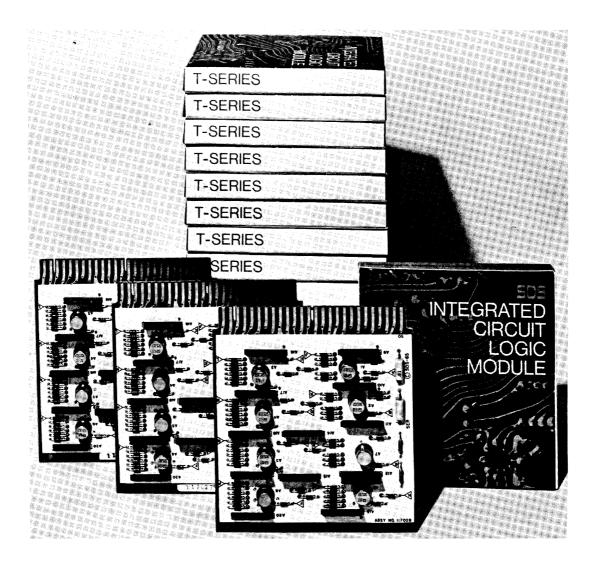

Since 1961, in the short span of eight years, SDS has produced more than three million modules for use in over 1200 computer based standard and special SDS systems. The first commercial computer with all silicon semiconductors ever delivered by any manufacturer was the SDS 910, shipped in 1962. The first computer with monolithic integrated circuits was the SDS 92, shipped in March 1965. SDS logic modules are in part responsible for the excellent reputation these computers have established for high reliability, flexibility, and low cost.

Now SDS offers its new T Series integrated circuits module family, as used in the Sigma 7, Sigma 5, and Sigma 2 Computers, to solve your system or special purpose logic problems.

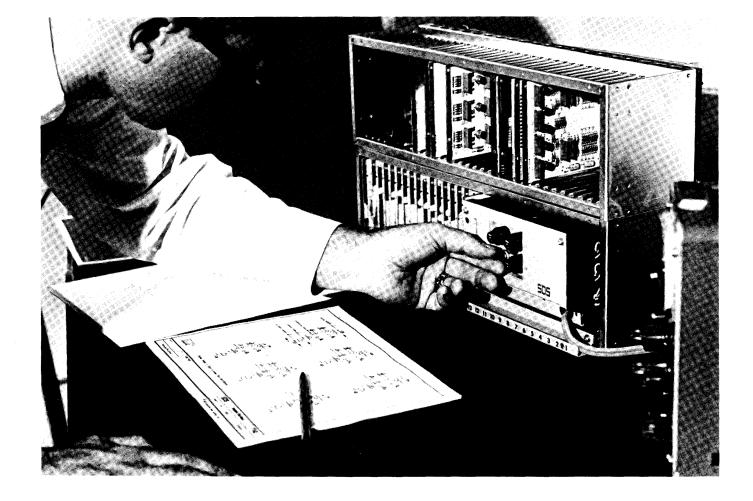

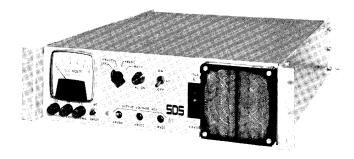

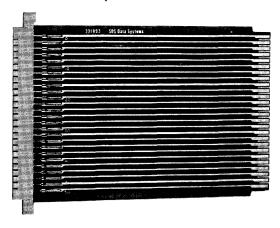

© 1966, 1967, 1968, 1969 Scientific Data Systems, Inc. All specifications subject to change without notice. Typical T Series Logic Module

# I. INTRODUCTION AND GENERAL SPECIFICATIONS

## THIS IS T SERIES:

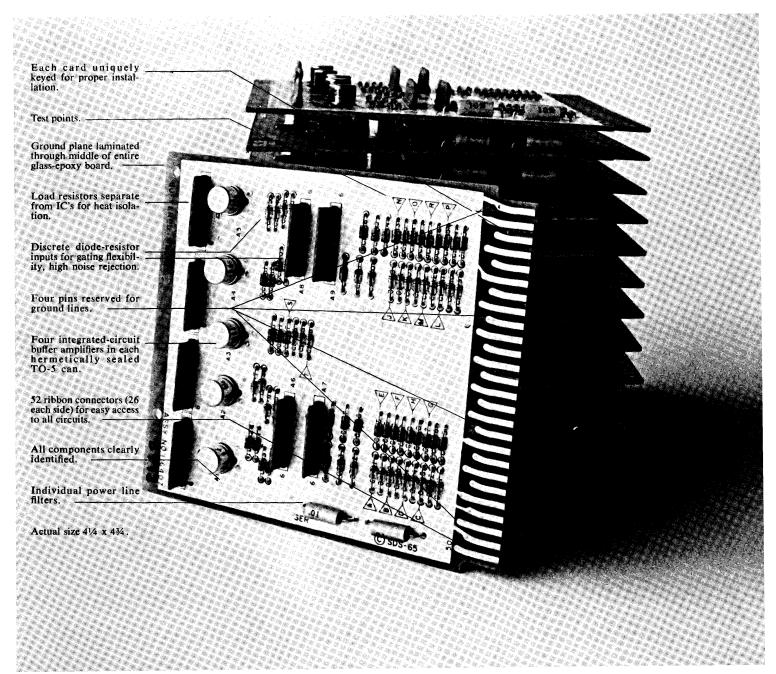

Experience with the successful SDS Sigma computers has shown that at the present state of component development the best performance, coupled with lower costs, is obtained when monolithic DTL integrated circuit flip-flops, inverters, and buffer amplifiers are combined with close tolerance, discrete diode-resistor gates and output pull-up resistors. Integrated circuits cut costs, save space, improve reliability, and improve performance, by replacing repetitive clusters of transistor circuitry. Diode gates retain flexibility where needed, in the gating structures, and help provide a very high noise rejection of 1.5 volts. Discrete pull-up resistors (load resistors between output collectors and Vcc) allow the use of high current drive by keeping most power dissipation outside the IC package. High current drive makes fan-out large, up to 14 gates per output, and easily permits use of clock frequency up to 10 Mhz because logic line capacitance can be charged rapidly.

Through the use of integrated circuits, 2-stage buffer amplifier cost has been reduced to that of 1-stage inverters. This permits the logic designer to discard the laborious design techniques needed to implement a system entirely with NAND or NOR logic. Logic may now be implemented in a natural way by direct substitution of logic circuits equivalent to the Boolean expressions that appear in the most simplified design equations. This saves both design time and hardware. In T Series these natural logic functions are provided by combining the integrated buffers, inverters, and flip-flops with various combinations of discrete diode-resistor gating. The circuits are grouped on modules in a wide variety of AND, OR, NAND, NOR, AND/OR, and AND/ NOR combinations, as described in Section II of this catalog.

A variety of flip-flop modules, with input gating included, are easily assembled into counters and registers. Some are general purpose while others are connected for specialized storage and counting functions. A unique, proprietary monolithic IC flip-flop is used as the storage element. It operates in any of the classic modes: R-S, J-K, T (Toggle), and D (Delay), using less external wiring than is required with the traditional flip-flop design. The clocked set input overrides the clocked reset input when both are simultaneously True, which simplifies input logic and wiring in most cases. Another significant improvement is trailing edge triggering, which reduces the input settling time required as compared to the traditional clocking techniques. The flip-flop also has unclocked inputs for clearing or presetting between clock times, and its outputs are fully buffered to prevent feedback from output lines to inputs.

An economical high-speed IC memory module stores 128 bits for bulk storage and input-output buffering.

Many supporting circuits are provided. Interface modules couple T Series logic into other logic systems with either positive or negative logic levels. An adjustable-threshold Schmitt-Trigger circuit accepts input of arbitrary waveshape and converts to logic levels. One-shots provide accurately adjustable delays. Several clock oscillator types provide timing references. Digital-to-analog converters (with reference voltage regulators) provide outputs that can drive recording and display devices or controllers. Cable receivers and drivers transmit logic signals over longer distances. A variety of lamp drivers and display lamps are available for building displays. Relay drivers and relays are also provided, as well as a manual toggle-switch module.

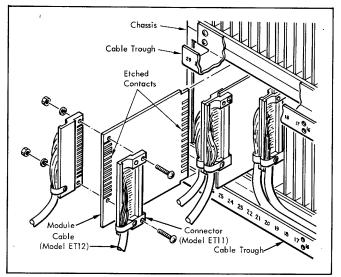

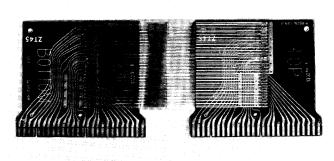

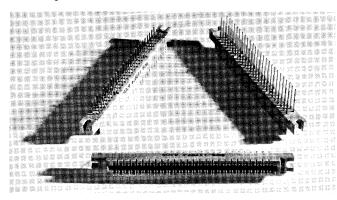

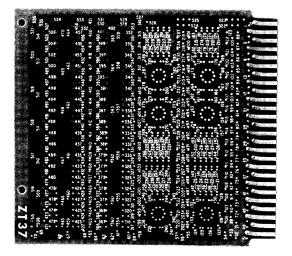

All of these circuits are placed on the same size epoxyglass etched circuit card, 4-1/4 inches high by 4-3/4 inches deep. The card has 52 gold plated connector contacts to maintain circuit accessibility and still provide dense packing.

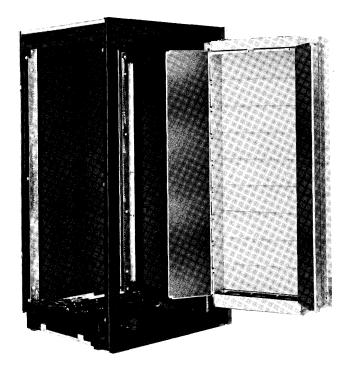

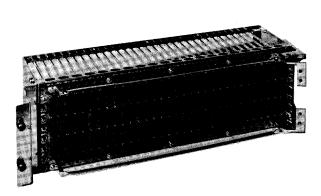

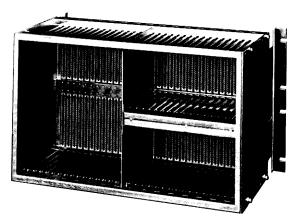

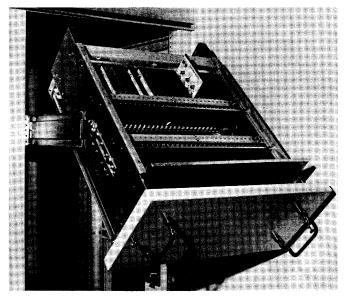

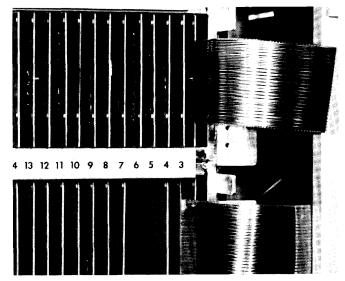

The cards plug into connectors which have reliable gold plated, spring loaded, bifurcated (2-pronged) contacts. Thirty-two modules can be placed side-by-side in 19-inch wide mounting cases, which are available in a variety of fixed-mount and hinged models having either wire wrap or solder tail back panel pins. Each mounting case incorporates a ground plane for noise immunity, and includes built-in power busses. Ninety-module tilting drawer cases are also offered. Any of the cases can be mounted in one of three types of cabinets which have 19-inch RETMA rails, doors, ac power wiring, swing-out frames, and optional side panels. A 300 cfm blower is available for cooling. An extender card is provided for troubleshooting.

Jumper wire kits, spooled wire, and wiring tools are available to further simplify mechanical assembly. Blank cards and drilled breadboard cards with circuit etch are available.

Two basic power supplies are offered: a compact supply which slides into a mounting case beside the modules, and a high-output supply which mounts on standard 19-inch rails. Both supplies can operate from a variety of input voltages and frequencies, have overvoltage and overload protection, and ±5% output regulation. Analog and large-system supplies are also available.

A complete range of services is available, from consulting engineering on application problems to a wiring service. Complete and accurate documentation is provided on all products. Application bulletins describe the various phases of building a system, from logic design through documentation and fabrication. Reproducible vellum logic sheets are provided for recording the interconnecting wiring and preparing wire lists.

Thus T Series provides all of the components, information, and services required to design and build a very high performance digital system quickly and at reasonable cost.

1

# **GENERAL SPECIFICATIONS**

#### ELECTRICAL AND ENVIRONMENTAL

#### Supply Voltages

| +4 volts |     |      |

|----------|-----|------|

| +8 volts | dc, | ±10% |

| -8 volts | x   |      |

#### Logic Levels

Logic 1: +4 volts nominal; +3.6 volts to +10 volts acceptable input range to interface with other module series; +3.6 volts to +4.4 volts maximum output variation.

Logic 0: 0 volts nominal; +1 volt to -3 volts acceptable input range to interface with other module series; 0 volt to +0.5 volts maximum output variation.

#### Noise Thresholds

At logic 0: +1.5 volts (greater may trigger True); At logic 1: +2.5 volts (lower may trigger False).

The above represents a noise rejection of 1.5 volts in either direction.

#### Loading

1 unit fan-out load is defined as 3.8 ma max., at the conducting logic level (0 volts).

Input Loading: Any logic input applies 1 unit load to the preceding signal source, unless otherwise noted.

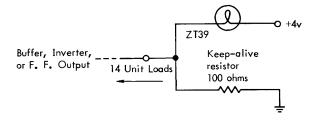

Output Loading: Buffer amplifier, inverter amplifier, or one flip-flop output can each drive 14 unit loads. (One flip-flop drives 28 loads, 14 with each output).

When buffer, inverter, or flip-flop outputs are wired together to form a wired logic function (see page 13), each output attached to the node absorbs 2 unit loads due to the additional pull-up resistor placed at the node.

#### Timing

Stage Delay (circuit delay):

|                | Typical | Worst-case |

|----------------|---------|------------|

| Buffered gate: | 18 nsec | 30 nsec    |

| Flip-flop:     | 40 nsec | 60 nsec    |

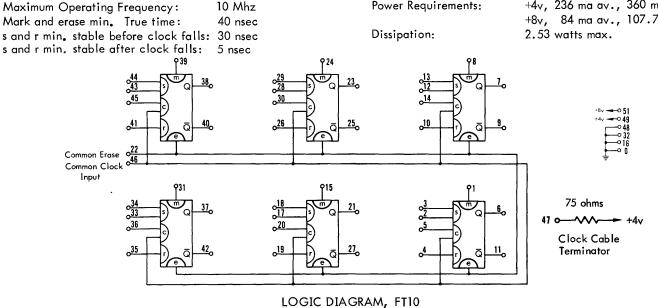

Frequency Range of Clock: dc to 10 Mhz.

Minimum Input Timing Requirements, Typical: Flipflop dc input (mark or erase) must be True for at least 40 nsec. Flip-flop clocked input (set or reset) must be True for 30 nsec. before clock changes from True to False, 5 nsec. thereafter.

Minimum Clock Duration: Clock must be True for 30 nsec., False for 60 nsec. Triggering takes place on falling edge when clock reaches the +2v (nominal) switching point. Fall time is not critical.

#### Temperature

Full-Performance Ambient Operating Temperature: 5°C to 71°C (41°F to 160°F)

Storage Temperature Range: -55°C to +150°C.

#### MECHANICAL

#### Card Size and Type

4-1/4 inches by 4-3/4 inches, epoxy-glass, gold plated etched copper wiring and connector contacts.

#### Connectors

52 gold-plated etched copper contacts mating with spring-loaded bifurcated (dual prong) connectors. Contacts are 0.15 inches apart; cards are spaced 0.50 inches center to center. Keys prevent wrong insertion.

#### Back Panel and Wiring

Terminations for wire-wrap, solderless push-on, or solder-tail connection feed through epoxy-glass back panel which is covered with solder plated etched copper ground plane for high frequency shielding. Four terminals from each card position are soldered to ground plane. Power connections are made to etched circuit busses on back panel, soldered to appropriate connector terminals at each card position. Recommended Wire: No. 28AWG copper with cut-through resistant insulation (see page 20).

#### **Mounting Cases**

19-inches wide by 5-1/4 inches high, fixed or hinged (32 cards); or 90 card tiltable pull-out drawer, 19 inches wide by 8-3/4 inches high. Welded all steel cases have ventilation slots, multiposition mounting hardware, and optional filtered blowers.

# MAKE OR BUY?

As always, there are cost and performance trade-offs in the decision to make or buy a family of logic modules. In some cases there is an advantage to making modules and buying cabinetry and other supporting components. Usually, however, the costs are greatly underestimated and unexpected performance difficulties arise during checkout, after most of the work has been done and the scheduled time has passed. Many system designers have decided that their time is better spent on system design, and that it pays to take advantage of the module maker's expertise.

SDS offers these benefits with its T Series module family:

- 1. Exclusive integrated circuits, identical to those used in the SDS Sigma computers, which perform better than commercially available integrated circuits.

- 2. The advantages of natural logic.

- Great savings in engineering time. Hundreds of computer systems have been built by SDS using T Series modules. The associated problems in mechanical design, interconnecting wiring design, and manufacturing techniques have been thoroughly worked out and solutions incorporated into the hardware.

- The components are properly matched in terms of logic mix, loading, frequency response, delay times, noise rejection, power requirements, reliability, environmental specifications, and mechanical compatibility.

- 5. Supporting circuits, which are particularly subject to unforseen problems, have been designed and refined to properly perform their functions, with adequate safety margins.

- 6. Special-configuration modules can be built to your specifications at moderate cost.

- 7. Quick delivery. The user receives finished hardware, usually within two weeks or less after receipt of order. Contrast this with the months of manufacturing lead time generally required.

- Full quality control, of assembled units as well as circuit components. One year warranty against defects. A complete module repair facility is available.

- Accessories are provided which might be considered too costly in a "make" situation, such as extender cards, jumper wire kits, relay and toggle switch modules, etc.

- Free application engineering is available, as well as design literature which gives detailed instructions to help avoid mistakes. The products themselves are thoroughly documented.

- 11. Reproducible logic design and wiring record forms are provided, with complete instructions on their use.

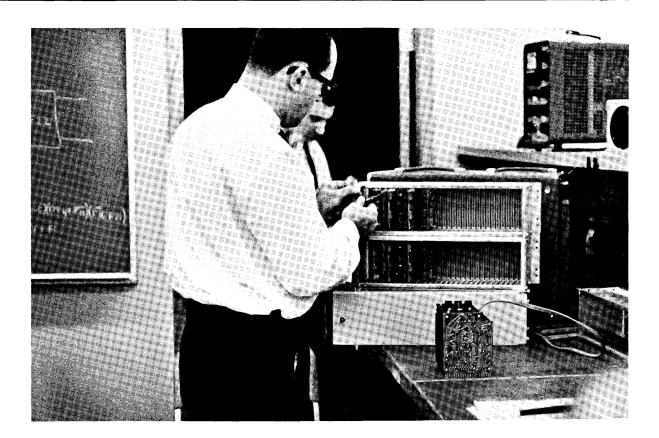

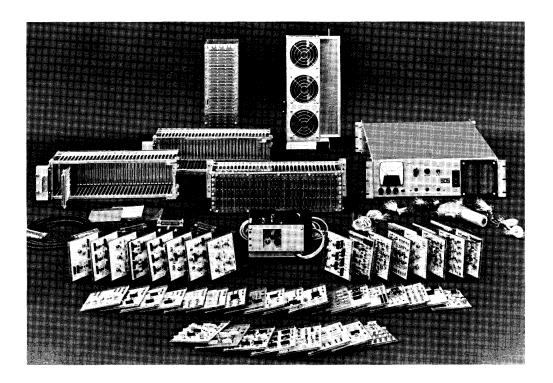

A Portion of The SDS T Series Production Line

Seventy incoming inspection tests can be performed on this T Series monolithic integrated circuit in less than four seconds. The integrated circuit tester is controlled by an SDS 92 computer that accepts or rejects circuits being tested and keeps a record from which engineers can evaluate the quality of circuits supplied by various vendors. Only a large volume module manufacturer can support testing on this scale.

## HOW T SERIES MEETS SYSTEM REQUIREMENTS

#### SYSTEM DESIGN GOALS

Good system design demands high performance at low cost.

In many digital applications, prime PERFORMANCE goals are:

- 1. Eliminate error (erroneous triggering)

- Minimize noise generation or pickup, and reject noise at logic inputs

- b. Maintain accurate timing

- c. Restore attenuated signals to retain signal integrity

- 2. Achieve fast system speed

- a. Achieve fast rise and fall times on logic levels changes

- b. Minimize propagation delays in logic circuits (stage delay) and interconnections (wiring delay)

- Minimize sum of delays in series in each logic chain by reducing the number of elements in series.

The corresponding ECONOMIC goals are:

- 1. Minimize engineering and related technical labor, particularly when building one-of-a-kind systems.

- a. Design logic simply and rapidly

- b. Plan and document interconnections quickly

- c. Avoid design of special circuits

- d. Assemble system quickly, conveniently, without expensive labor

- e. Debug system quickly

- f. Eliminate callbacks to correct failures

- 2. Minimize hardware cost

- a. Minimize number of logic elements required to perform a given logic function

- b. Minimize circuit and wiring cost per element

- c. Minimize cabinet hardware required (achieve dense packing)

- d. Minimize cost of other accessories (power supplies, etc.)

- e. Minimize replacement part quantities through standardization

- 3. Minimize equipment failure

- a. Avoid inconvenient or costly disruption of system operation

- b. Reduce troubleshooting and replacement costs

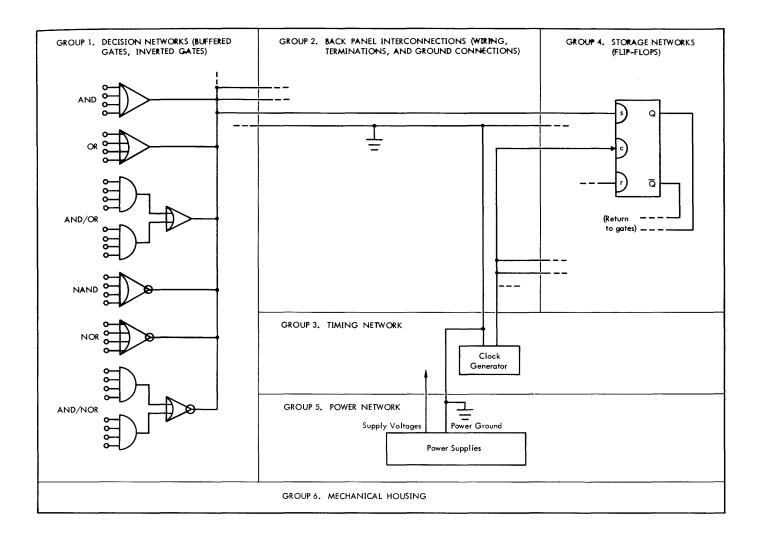

These goals can be translated into specific hardware design goals. Hardware can be lumped into six broad classes for this analysis (see diagram on page 5). Each group has its own effects on performance and economy. Each will be described in sequence.

#### GROUP 1. DECISION NETWORKS

Design of gate networks, usually with the aid of Boolean algebra, is often the most time-consuming task. In many cases gates and logic amplifiers also constitute the bulk of the system hardware. Thus, for economy, standard gateamplifier configurations should be designed to: 1) minimize implementation time, 2) minimize the total number of gates and amplifiers in the system, and 3) cost less per unit.

#### Minimize Implementation Time

The best way to minimize implementation time is to make all four logic functions, AND, OR, NAND, and NOR, available to the designer at the same low cost. T Series does just this. The technique is called natural logic. Once the Boolean expressions that define a logic function have been reduced to simplified form the task is almost finished. The designer then substitutes T Series gating structures directly for equation terms (see Example 1 on page 6).

Many other manufacturers urge the exclusive use of NAND or NOR functions. They standardize on one inverting gate type to solve their problems rather than the user's. But, implementation with only NAND or NOR functions requires additional equation manipulation. T Series eliminates the extra design work by economically providing all four functions. A unique combination of standardized IC logic amplifiers (both inverting and non-inverting) with flexible, discrete diode-resistor gates makes this possible.

SDS logic element modules contain a calculated mix of gate combinations, using gates with 2 to 5 inputs. This selection permits the designer to choose the right combinations of circuits from each card, reducing leftover circuits in the rack and avoiding many wiring problems. The 52 connectors per card permit full access to each circuit.

Load calculations are simple. All T Series logic elements are rated in unit fan-out loads of 3.8 ma. Each diode gate places 1 unit load on the previous amplifier output.

#### Minimize Hardware Quantity

The number of gates and amplifiers required to implement a given gating function must be the lowest possible.

Amplifiers in particular should be minimized, since they are the active (and therefore expensive) components. Primarily they furnish power to drive logic signals through the gating structure. They also can perform logical inversion, if required. Where adequate power is available, and amplifiers are used merely to perform logic inversions not required by the most simplified form of the equations, they create an inexcusable expense. Example 1 explains how they may be eliminated.

Example 1 also demonstrates another T Series feature that eliminates amplifiers. This is the ability to perform 3-stages of logic (AND-OR-AND) with 1 stage of amplification, without loss of signal quality. The combination of the AND/ OR gate with wired-AND functions formed at amplifier outputs makes this possible. The number of amplifiers is also cut by making output driving current high; this permits each amplifier to drive more gates. The fan-out from a T Series buffer or inverter amplifier is 14 unit loads, compared to 10 for many other types of integrated circuits.

These three T Series features, natural logic, three levels of logic, and high fan-out, typically yield hardware savings of at least 1/3 when compared to other module lines.

#### Minimize Unit Circuit Costs

SDS T Series achieves low unit circuit costs by integrating the repetitive clusters of components that occur mainly in amplifiers and flip-flops. The number of different integrated circuit types is kept small to simplify design and maintenance. By retaining the inexpensive gate structure outside the integrated circuit, T series retains the flexibility of natural logic. Logic modules (excluding supporting circuits) use only eight different components: 3 integrated circuit types, 3 resistor types, 1 diode type, and 1 decoupling capacitor type. Individual circuit costs are thereby held to a minimum.

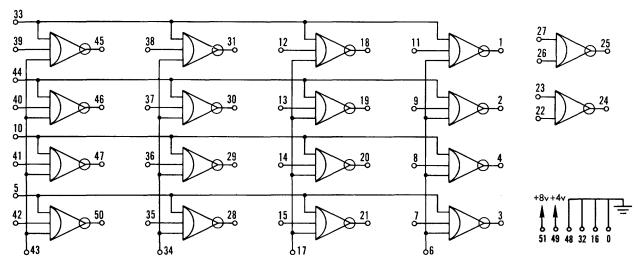

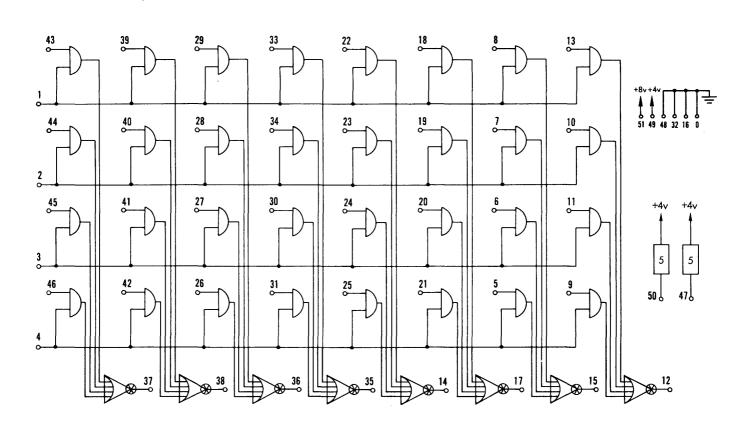

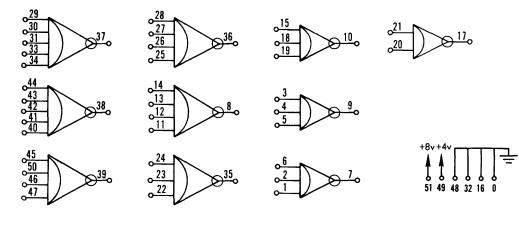

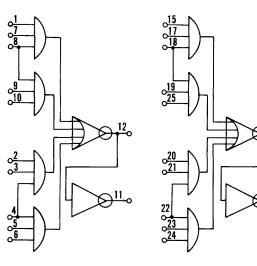

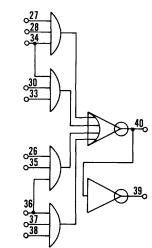

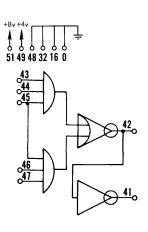

## **EXAMPLE 1 - NATURAL LOGIC IMPROVES PERFORMANCE AND COSTS LESS**

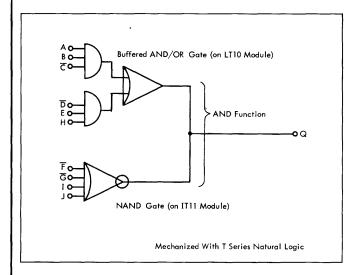

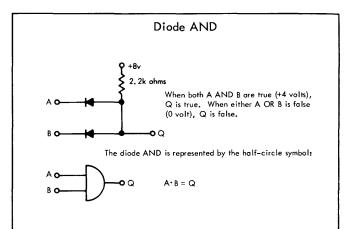

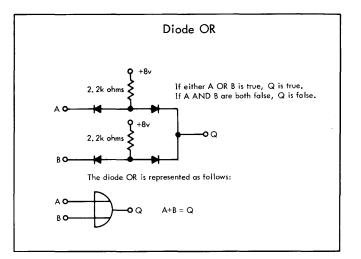

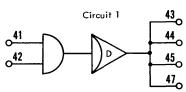

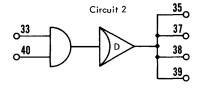

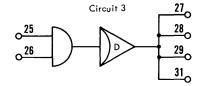

The monolithic integrated buffers, inverters, and flip-flops of T Series are designed to accept inputs from diode AND and OR structures. The unique SDS gating and logic amplifier designs permit three stages of logic to be performed with a single stage of amplification. Any active element such as a non-inverting amplifier may have AND/OR input gates (two stages) and also may have its outputs pararalleled with other active element outputs to implement a third stage of logic.

As an example, mechanize the following function:

$$Q = (AB\overline{C} + \overline{D}EH) (\overline{F}\overline{G}IJ)$$

T Series natural logic permits direct substitution of hardware for equation terms, as shown below. Note that only two amplifiers are required, one a buffer and one an inverter (NAND).

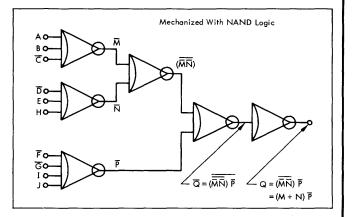

NAND functions are the most commonly available monolithic gate structures offered by other manufacturers. Implementation using NAND functions alone is more complex. First, the equation must be manipulated to represent a series of not-AND operations, of the form  $Q = \overline{Y \cdot Z}$ , where  $Y = \overline{V \cdot X}$ ,  $Z = \overline{T \cdot U}$ , etc. As an example let  $M = AB\overline{C}$ ,  $N = \overline{D}EH$ , and  $P = \overline{F}\overline{G}IJ$ . By DeMorgan's theorem, the original expression may be rewritten

$$Q = (M + N)\overline{P} = (\overline{\overline{M}}\overline{\overline{N}})\overline{P},$$

which puts it in the proper form for NAND implementation, providing one more inverter is added since the last NAND gate results in an inversion.

The structure that results using NAND gates is shown in the next column. Note that it uses 6 amplifiers as compared with 2 for the natural logic version.

Mechanizing the same function with NOR gates is similar, but requires 5 amplifiers if all complements are available, or 7 amplifiers if only the given signals are available.

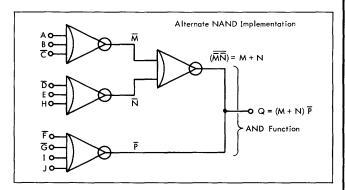

If ANDing at outputs is allowed the implementation is simpler, but still requires 4 logic amplifiers:

For a cost comparison, if we assume that each amplified logic function sells for roughly the same price, then the T Series approach costs 1/2 as much as the best NAND implementation, in this typical example.

To facilitate a comparison of relative delay times, assume that D is the average propagation delay of a diode AND gate or a diode OR gate. Then 5D is a realistic approximation of the delay of an inverting or a non-inverting amplifier. To favor NAND logic, further assume that 5D is also the delay of a monolithic NAND structure. The resulting total delay for the typical circuit illustrated above is 7D with SDS T Series, 20D with straight NAND logic, and 10D with NANDs ANDed at the output.

This example shows how one powerful feature of T Series becomes apparent in a system application. Comparison with other module lines on an individual circuit-for-circuit basis reveals only part of the full merit of T Series modules.

#### GROUP 2. INTERCONNECTIONS

#### Sources of Digital System Noise

Digital noise is defined as any unwanted voltage change on the two standard logic levels. Noise can take the form of an internally generated short-duration pulse or a long-duration d-c drift. In addition, there can be pickup of external signals, radiated from nearby devices outside the logic network. Noise introduces error into the data when gating circuits interpret noise as logic changes.

High speed digital systems are particularly subject to pulsetype noise because logic levels change rapidly. All integrated circuits have inherently fast switching speeds, typically in the 5 to 15 nsec range, due to the microscopic scale of the circuits. The ICs will switch at this speed regardless of the system clock frequency. These fast level changes produce high-frequency components which couple readily into the wrong circuits through interwiring capacitance. High speed systems are also sensitive to reflections of leading and trailing edges of pulses. The longer segments of interconnecting wiring act as transmission lines to the high-frequency transient components of logic signals. If these transmission lines are not properly terminated in their characteristic impedances, various reflections can interfere to cause erroneous switching.

The ground system can also create its share of problems at high frequencies. If inductive reactance is high, which often happens when large loops are created by using wires as ground returns, sharp noise pulses may occur at amplifier ground connections, proportional to the product of inductance and switching speed, Ldi/dt.

Another cause of signal degradation is poor contact mesh at the connectors which link the modules to the back panel wiring. Poor mesh or corrosion can lead to intermittent high resistance in logic signal lines.

#### Minimize Digital System Noise

These problems can be controlled through proper design of the interconnecting wiring and the ground system, and by establishing adequate noise thresholds at the gates. A number of specific objectives are:

- Prevent inductive or capacitive coupling among backpanel wires. Also prevent coupling between these wires and sources of noise signals external to the system. Design the ground system to have low inductance as well as low resistance.

- Design the back-panel interconnections to approximate transmission lines in order to achieve characteristics that are independent of frequency. Then terminate these lines (when long) with resistance close to their characteristic impedance, to reduce pulse reflections.

- 3. Reduce the possibility of poor contact mesh at connectors.

- 4. Design the gates to have high immunity to noise.

These design goals are all incorporated in T Series.

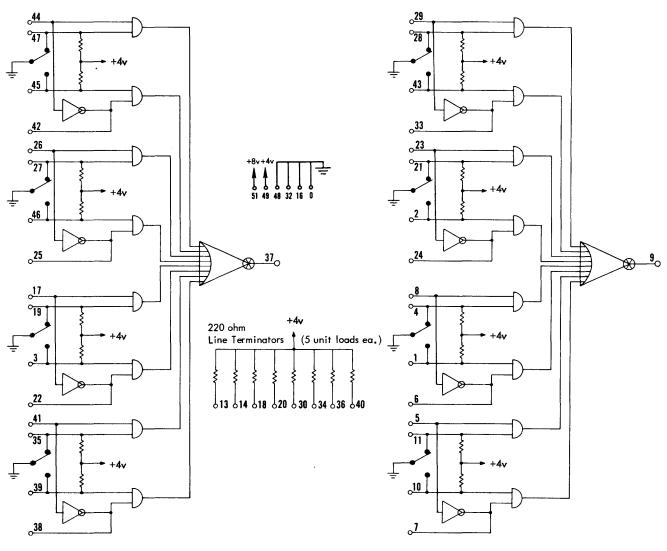

First, the ground for each module case is a plated flat copper sheet attached to an epoxy-glass board that runs the full width and height of the case. It has very low resistance, and the loops formed by the plane and each interconnecting wire have low inductance, four or five times less than would be the case without a ground plane.

The ground plane is used as a return path for currents in back panel wires. This has the effects of shielding each conductor from each other conductor and of turning each conductor into a transmission line. If the back panel wires are pushed down close to the shield plane the approximate characteristic impedance that results is about 150 ohms.

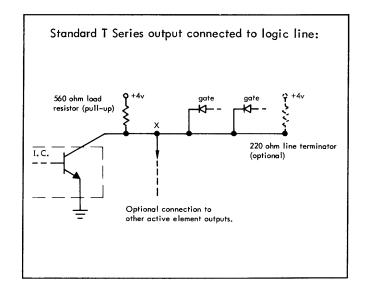

Second, the terminating impedance at the far end of a long back panel logic signal line may be made to approximate line impedance by connecting a standard 220 ohm terminating resistor, greatly reducing the amplitude of signal reflections. This is possible with T Series because of the high current drive. The discrete terminating resistors (and gate resistors) are outside the integrated circuit container, and power dissipation therefore is not a limiting factor. Signal reflection problems often arise in systems that rely exclusively on monolithic integrated circuits because the integrated load resistances must be considerably larger than line impedance in order to avoid excessive heating of the integrated circuit package.

Third, poor contact mesh is eliminated with the T Series connector design. The connector receptacles for module contacts have one pair of bifurcated (forked conductor), spring loaded, gold plated fingers for each contact. Gold plating reduces the probability of high resistance oxide formation. The fingers are so designed that they cannot distort or lose their spring pressure. Bifurcation provides redundant contacts, further reducing the already remote probability of contact resistance problems. These new connectors are manufactured to SDS specifications.

Wires may be attached to the connector pins (which protrude through openings in the ground plane) with reliable wire-wrap, solder tail, or the new solderless push-on terminals.

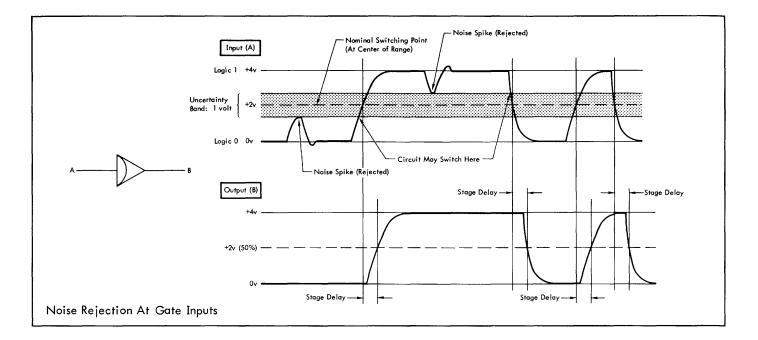

The preceding describes the various techniques used to reduce noise. However, since some noise is inevitable, the gates must be able to reject it. The gate switching point is therefore placed at +2 volts and the uncertainty band about this value is made as small as possible through tight component tolerance control.

#### Noise Rejection Specifications

With a signal at 0 volts (logic 0 level), noise on a gate input of up to +1.5 volts will not cause the associated amplifier output to change state. With a signal at +4 volts (logic 1 level), noise on a gate input of -1.5 volts, which brings logic 1 voltage down to +2.5 volts, will not cause the associated amplifier output to change state. This leaves an uncertainty band between +1.5 volts and +2.5 volts, within which the amplifier output will switch (see above).

These thresholds are determined by characteristics of the gate diodes, gate resistors, and the integrated amplifier input circuits. The superior noise rejection properties of T Series stem from close tolerance control, and the use of higher, symmetrical noise thresholds.

#### GROUP 3. SYSTEM TIMING (SPEED)

#### Propagation Delays and Clock Frequency

Stage delay is the time required for a signal to propagate through a logic circuit. In an idealized sense, it is defined as the time lag between arrival of a step function at a circuit input, and the appearance of a resultant step function at its output.

Operating Frequency Range is the repetition rate range of clock pulses over which the clocked system performs reliably in continuous operation while meeting all other specifications.

Since system speed is delay limited it makes no sense to emphasize high clock rate by itself as a desirable feature. A clock oscillator may easily be designed to operate at frequencies unheard of in digital work, but this is no guarantee that a system may be operated at that frequency. The clock must operate slowly enough to permit all logic signals to propagate through an appropriate chain of gates to the next level of flip-flops before the next clock pulse occurs. In other words, the logic circuits must have time to complete their decisions before the clock causes the flip-flops to store the results and commence the next series of logical decisions. Thus to achieve a high clock rate, series delays must be minimized.

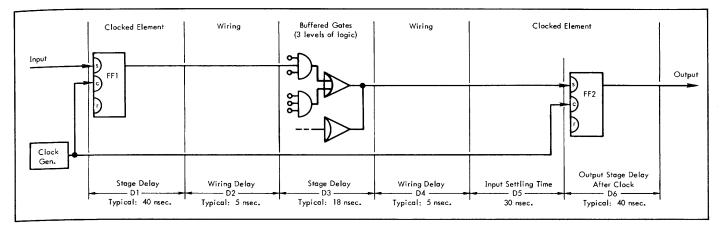

The diagram, page 9, illustrates these points. Assume the input is true. When a clock falling edge occurs flip-flop FF1 is set. Its output changes after internal (stage) delay D1. This signal is propagated through a series of wiring paths, gates, and amplifiers with a total delay D2 + D3 + D4, until it reaches another clocked element, FF2. Then FF2 may be triggered by a second clock falling edge after a stabilizing period, D5, and the output is available after an internal delay D6. The clock pulse falling edges, which trigger the flip-flops, cannot be allowed to occur at shorter intervals than the total series delay,  $D_t = D1 + D2 + D3 + D4 + D5$ . Thus the maximum permissible clock rate in this example is  $1/D_t$ . (This has no direct relation to the rate at which a single flip-flop can be toggled).

System design can be varied to some extent to minimize total system delay be performing whole functions in parallel rather than in series. However, the minimum delay in any single chain of elements as illustrated can only be reduced (and clock rate raised) if:

- 1. Stage delays of flip-flops and amplifiers are minimized

- 2. Wiring delays are minimized

- 3. Signal settling time is minimized.

Minimize Active Circuit Delays

The T Series active circuits have very short internal delays. Buffer and inverter amplifiers have stage delays (with input gates included) of 18 nsec. typical, 30 nsec. worst case.

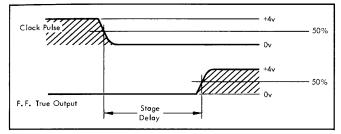

Flip-flop delay is 40 nsec. typical, 60 nsec. worst case, measured as follows:

Minimize Delay Due To Wiring

The stage delays of the active circuits, given above, are measured with the active circuits loaded to permit minimum rise time at the output. In actual practice, when the active circuit output is used to drive a load consisting of back panel wiring and gates, the rise time is extended. This difference in rise time is the delay due to wiring.

The factors which determine delay due to wiring are driver output characteristics, propagation velocity of the wire, length of line driven, and load characteristics. Length of line and load characteristics are the major contributors to wiring delays. Rise time is usually longer than fall time because the driver output presents a high impedance during the 0 to 1 transition, and a low impedance during the 1 to 0 transition.

On the 0 to 1 transition the wiring acts as a capacitance load on the driving circuit; wiring delay thus depends on how fast this capacitance charges. The capacitive characteristic is due not only to stray capacitance, but also to the fact that each wire, which approximates a 150 ohm transmission line, is always loaded with a resistance somewhat greater than its characteristic impedance of 150 ohms, and therefore behaves as a capacitive load. If terminating resistance is decreased to more closely match line impedance, the line behaves more like a resistive load, but fan-out is sacrificed. Example 2 (on the next page) shows the relations between these factors.

The logic designer has at his disposal the means to trade between fan-out and delay to meet higher speed requirements. He can reduce rise time (at the cost of fan-out) by adding a 5 unit load (220 ohm) terminating resistor to the end of a line, decreasing the RC time constant.

On the 1 to 0 transition the wiring acts generally as an inductive load because the internal impedance of the driving transistor in the conducting condition is very low. As mentioned, this delay is generally less than during the 0 to 1 transition, and is therefore not the limiting factor.

Typical back-panel wiring delays are 5 to 15 nanoseconds when wiring is properly designed.

#### Minimizing Flip-flop Input Settling Time

A T Series flip-flop set or reset input must be True for at least 30 nanoseconds before clock changes from True to False and stay True for 5 nanoseconds thereafter. This is a relatively short settling time.

#### Conclusion

The example shown at the top of the page is a typical configuration, having three levels of logic (AND/OR/AND) between clocked elements. The total delay that may be normally expected under these circumstances is obtained by adding the figures given:

$$D_{t} = D1 + D2 + D3 + D4 + D5$$

= 40 + 5 + 18 + 5 + 30 = 28 ngnoseconds.

This allows the use of a clock frequency of  $\frac{1}{98 \times 10^{-9}}$

= approximately 10 Mhz.

As can be seen by comparing T Series delay times with those of other module types, the stage delays, the wiring delays, and settling delays are at a minimum. When the design objective is maximum speed, T Series provides the capability to reach clock rates of 10Mhz using normal logic implementation.

## EXAMPLE 2 - HIGH CURRENT DRIVE AIDS SYSTEM SPEED

Very high current-handling capability of T Series integrated circuits (up to 60 ma) is directly responsible for two important advantages. One is the exceptionally high fanout of 14 (compared with about 10 offered by other integrated circuit modules). The other is faster system speed.

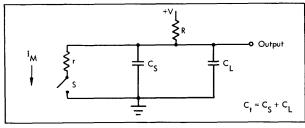

Shown below is a first approximation schematic of an integrated circuit driving an RC load.

Switch S and small resistance r roughly represent the output transistor of a monolithic gate or flip-flop. Symbol  $I_M$  denotes the maximum current handling ability of the output transistor at the 0 level, or fully "on" condition (S closed). Since r typically is small, load resistance R and supply voltage V must be chosen so that current through the transistor in the steady "on" condition does not exceed the limiting value,  $I_M$ . Thus with a given supply voltage, V, and a given maximum current handling capability,  $I_M$ ,  $R = V/I_M$ .

C<sub>S</sub> represents shunt and parasitic capacitance of the transistor. Load capacitance C<sub>L</sub> is wiring and pin capacitance to ground, and depends on the length of line driven and the number of connector pins. The total,  $C_t = C_S + C_L$ .

If the transistor initially is in the "on" condition, with maximum current I<sub>M</sub>, output voltage will be nearly zero.

If the switch is then opened (transistor cut off), output voltage rises exponentially toward V. The rate of output voltage buildup is controlled by the time constant:

$$RC_{\dagger} = \frac{V}{I_{M}} C_{\dagger}.$$

This equation shows that with a given capacitive loading, the rate of change of voltage on the interconnecting wiring in going from 0 level to 1 level is controlled by the load resistance, and therefore is limited by the ratio of supply voltage to transistor output current handling ability. The lower the supply voltage and the higher the current handling ability, the lower the load resistance(R) that can be used, and therefore the faster the rise times when current is turned off. SDS T Series integrated circuits operate with a relatively low supply voltage and have output transistors with very high output current handling ability, to quickly drive the system through logic level changes.

The real test of any circuit is its speed under load. T Series integrated circuits maintain their high operating speed under conditions of capacitive loading that significantly slow less powerful circuits.

This example is simplified to illustrate the principle involved. In practice, as many as 14 gating circuits are connected across the output. During a 0 to 1 level change each conducting gate supplies 1 unit load of charging current through a pull-up resistor connected to +8v. The supply voltages, load resistance, and pull-up resistances all are chosen so that steady-state current through transistor S does not exceed limiting value  $I_{M}$ . The conclusions of a more detailed analysis are the same: the higher the current handling ability, and the lower the voltages used, the faster the capacitive load can be charged.

#### GROUP 4. STORAGE NETWORKS

A flip-flop should be both versatile and economical. If possible, it should be designed to minimize interconnecting wiring in the majority of applications. It should have high current output to eliminate the need for amplifiers to drive the next stages of gating.

To enhance system performance the flip-flop should have minimum internal delay, for high speed applications. It should also have a short, precisely timed sampling period (time during which it is sensitive to inputs) in order to avoid erroneous triggering. It must also be insensitive to temperature variations and have excellent long term stability, to prevent erroneous switching due to change in circuit characteristics. Level changes at an output should not feed back through internal cross-coupling to an input, since noise may be present on the output lines.

#### T Series Flip-Flop Economy Features

The basic T Series flip-flop achieves these goals. In addition, its outputs can be tied directly to other flipflop or amplifier outputs to form an AND function without additional gates. This proprietary flip-flop is produced in quantity as a monolithic integrated circuit for low unit cost.

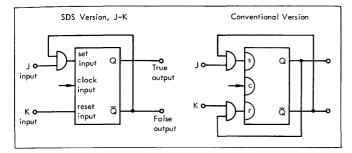

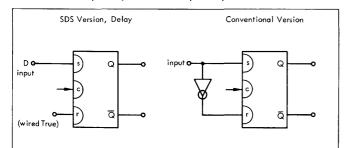

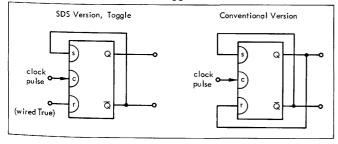

The "set-overrides-reset" feature makes it possible to use one flip-flop with little external wiring in four modes of operation (R-S, J-K, T, and D). A study of systems has revealed that, in the majority of cases, wiring is simpler if the set input always overrides the reset input when both are True simultaneously:

| Per       | n + 1       |           |

|-----------|-------------|-----------|

| set input | reset input | Q output  |

| 0         | 0           | Same as n |

| 0         | 1           | 0         |

| 1         | 0           | 1         |

| 1         | 1           | 1         |

Using this flip-flop, the reset output can be wired to an AND gate at the set input to create a J-K flip-flop. A conventional flip-flop requires a second gate to achieve the same result. The SDS model avoids this second connection because set always overrides reset.

The same feature saves an inverter and reduces wiring in the Delay mode of operation. When the reset input is left open (wired True) the set input operates the circuit as a delay flip-flop--that is, the Q output state follows the set input state, delayed by one clock pulse period.

This feature also saves wiring in the Toggle mode. In this mode the clock input operates the circuit, causing it to change state at each clock trigger.

The flip-flop may also be used as a straight clocked set-reset (R-S)flip-flop with the s and r inputs activated directly, or asynchronously with d-c inputs, mark (m) and erase (e), which override the s and r inputs. Note that in clocked R-S operation there is no ambiguity because set overrides reset.

#### T Series Flip-Flop Performance Features

The SDS flip-flop has the same fan-out as an amplifier. Each output can drive 14 unit loads.

Internal delay of the basic flip-flop is 40 nanoseconds typical, 60 nanoseconds worst case. Since the minimum clock True time is only 30 nanoseconds a simple toggle circuit such as used in a counter may be operated at a clock rate of 10 Mhz (100 nanoseconds) or faster.

Two features that prevent erroneous switching are a short sampling period and trailing edge clock triggering. Input signal conditions do not affect flip-flop operation, even when the clock input is True, until 30 nsec. prior to the clock's falling edge. The SDS circuit is not the conventional type in which the first rank is set on the 0 to 1 clock input transition, then the state is shifted to the second rank on the 1 to 0 transition. The SDS technique of pure trailing edge triggering provides timing security without undue restrictions on clock pulse shape, and also allows maximum input signal settling time between clocks.

Both flip-flop outputs are buffered within the integrated circuit to completely isolate output signals from inputs.

#### GROUP 5. POWER

D-c power for logic modules must have low drift. It must also be free from transients, which could cause false triggering. Transients normally enter the system via the a-c power line, particularly when high starting current devices such as motors are on the same line. A module power supply should also be designed to protect the delicate semiconductors from overvoltage or short circuits. Finally, the supply should be capable of being rack mounted and operating with various popular line frequencies and voltages.

#### T Series Power Supplies

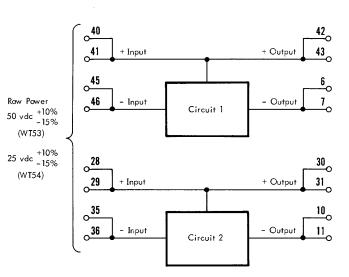

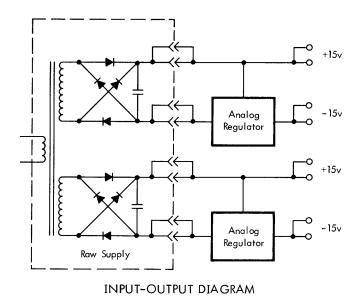

The PT10 (20-40 module supply) and PT12 (125-200 module supply) provide  $\pm 5\%$  output regulation, with inputs of either 110 or 230 volts. Both provide overvoltage and short circuit protection. The PT10 plugs into a module mounting case, requiring only 15 module spaces. The PT12 uses the 19-inch rack width.

Power busses for +4v and +8v are supplied on the back plane to minimize high frequency pickup.

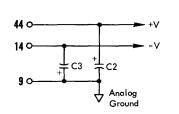

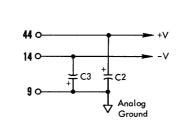

Additional transient filtering is provided by individual decoupling circuits on each module.

#### GROUP 6. MECHANICAL

Mounting hardware should be economical, lightweight, rugged, easy to assembly and disassemble, and compatible with industry standard hardware. It should be available in several options for convenience. Design must take into account electrical properties such as shielding and ground currents as well as heat dissipation.

T Series mounting hardware is based on a standard 19-inch rack width. A welded steel, ventilated 32-module mounting case is available with 2-position front or back bracket mounts, or right/left vertical hinges. A 90-module pullout drawer is available for high density applications.

Cabinets, blowers, and many other mechanical accessories are also available.

#### OTHER COST FACTORS

Equipment failure can be costly when it interrupts operation of another system. SDS modules have a proven reliability record. Natural logic results in fewer logic components per system. Integrated circuits reduce the number of wire connection points as much as 20 to 1. All modules are worst case designed and 100% tested. Parts standardization and fewer components per system means smaller, less expensive stocks of replacement parts.

Time consuming special circuit design is avoided because T Series offers many supporting circuit types that SDS engineers have found they need to build a variety of systems, and because special circuit engineering is available at reasonable cost.

#### SUMMARY

T Series modules are designed for low cost, error-free, high or low speed digital systems that may be assembled quickly, to operate reliably over long periods.

A number of important features such as natural logic, high current drive, back panel ground plane, and set-overridesreset flip-flop, are unique to the SDS product line. They are responsible for economy and performance benefits.

## ABOUT THE CIRCUITS . . .

#### GATES

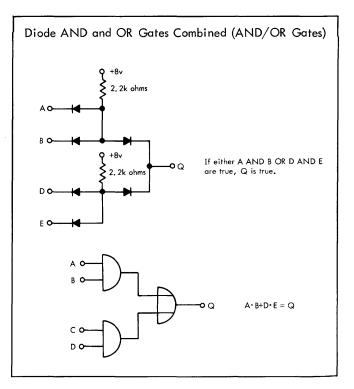

As mentioned previously, the T Series gating structures are composed of discrete diode-resistor combinations which are external to the integrated circuit buffers, inverters, flipflops, and other IC elements such as the 8-bit memory circuit used with the FT40 module. Thus the number of different ICs used is very small, but complete gating flexibility is retained, along with better noise rejection. The structure of the AND, OR, and AND/OR gates is shown at right.

#### LOGIC AMPLIFIERS

In order to preserve good signal characteristics, in T Series logic the output of a diode AND, OR, or an AND/OR combination never serves as input to another stage of diode gate circuits. It is always connected to an active element which restores the signal to the proper power level and filters out random noise. Active elements include inverting amplifiers, non-inverting (buffer) amplifiers, flip-flops and others, usually in IC form. The outputs of these active elements drive other gate inputs.

The most basic active elements are the non-inverting logic amplifiers (buffers) which standardize the signal waveshape and provide power gain (fan-out) for driving parallel loads.

The inverting logic amplifiers perform the same driving function plus the additional function of logical negation. The circle shown on the inverter symbol indicates this.

For convenience, buffered or inverted gates are symbolized with combined gate-amplifier symbols as shown on page 21.

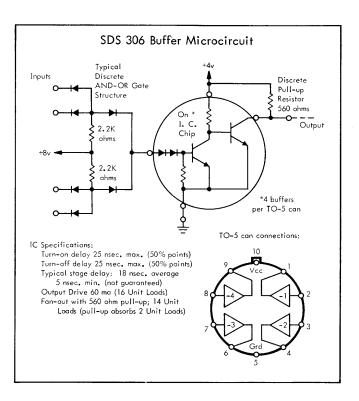

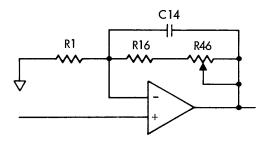

The illustrations below show the essentials of the buffer and inverter circuits, with inputs preceded by a typical discrete AND/OR gate. Note that the logic line pull-up resistors are also kept discrete, to obtain high current drive for fast rise time and high fan-out without reducing reliability by overheating the IC container. This also provides for the possibility of forming wired logic functions (or expanding gate functions) by tying several outputs together with only one pull-up resistor on the line, thereby preserving fan-out for useful loads. The model numbers SDS 305 and SDS 306 refer to the ICs, which contain four buffers or four inverters per one high-reliability TO-5 can.

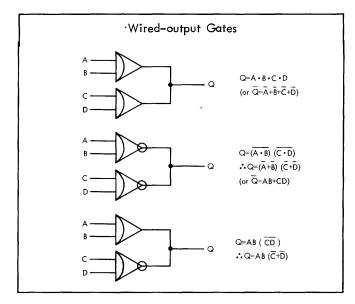

#### WIRED-OUTPUT GATES

With T Series it is possible to form gate functions by wiring buffer or inverter outputs together, thus creating a new gate function without additional hardware.

T Series logic outputs are normally constructed as shown below. When outputs are connected at point X an AND function is formed, as follows: when an integrated circuit output transistor conducts it shorts the logic line to ground, placing the line at logic 0. This is an AND function because all outputs must be at logic 1 for the line to be at logic 1.

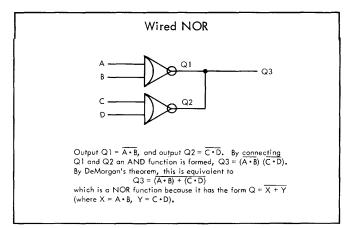

If all outputs are inverter outputs the wired gate can be considered a NOR as shown below.

The basic wired functions that can be formed with two outputs are given below. Up to seven outputs, each having a 560 ohm pull-up, may be wired together.

The trade-off for this additional logic capability is a reduction of fan-out. Each additional output absorbs 2 unit loads due to the additional 560 ohm pull-up resistor that is placed in parallel at the node. No more than seven outputs can be connected since seven pull-ups absorb 14 unit loads, leaving 2 unit loads for useful output.

However, if the additional pull-up resistors were not present there would be no fan-out reduction due to loading. Then the upper limit of fan-out is determined by the drop across the pull-up, which decreases noise margin in the True state. A 560 ohm pull-up can handle 6 common outputs; 220 ohms can handle 16. On some modules the pullup is omitted to permit this (see IT14 module description).

The wired-output technique also allows gate expansion (increase of fan-in). For instance, four 2-input NORs can be wired together at their outputs to form one 8-input NOR.

#### STORAGE ELEMENTS

The results of the decisions made by gates can be stored in one of several devices. All of them have two stable states, and when implemented with ICs or transistors are called flip-flops.

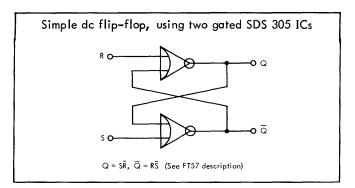

#### Dc Flip-Flop

A simple dc flip-flop made by cross-coupling two buffered NOR gates (inverted ORs) stores 1 bit. It has the disadvantage that inputs are sensitive to changes on the output logic lines because the outputs are directly fed back to the inputs without intervening buffers to isolate them. However, in a suitable application the dc flip-flop reduces storage cost. When the S input is made True (and R is False) the unit assumes one state (Q True,  $\overline{Q}$  False) and retains this state after S becomes False due to the feedback from Q. The opposite conditions flip the unit to the opposite stable state. When both inputs are made True simultaneously the state is indeterminate, and if the True level on both inputs is removed simultaneously the state is indeterminate. However, if one True level is removed before the other, and the one remaining is held True for the duration of the circuit delay of the logic amplifiers (30 nsec worst case) then the unit assumes the state determined by the last True input.

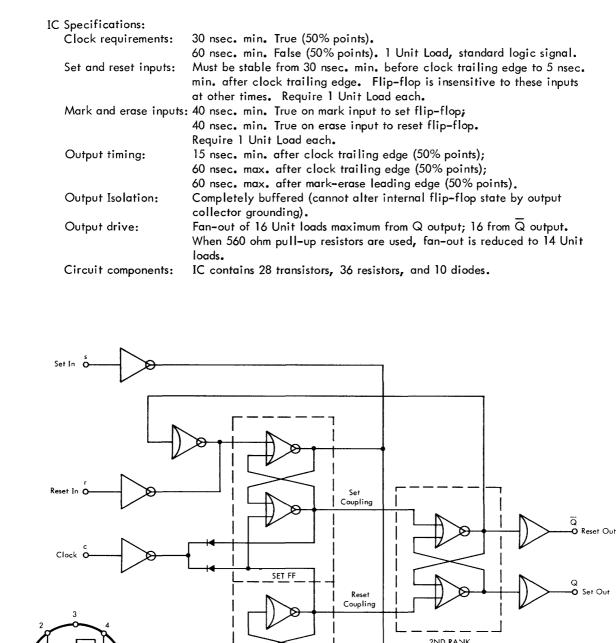

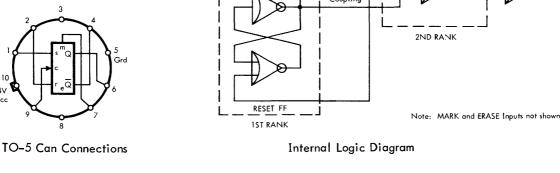

#### Clocked Flip-flop

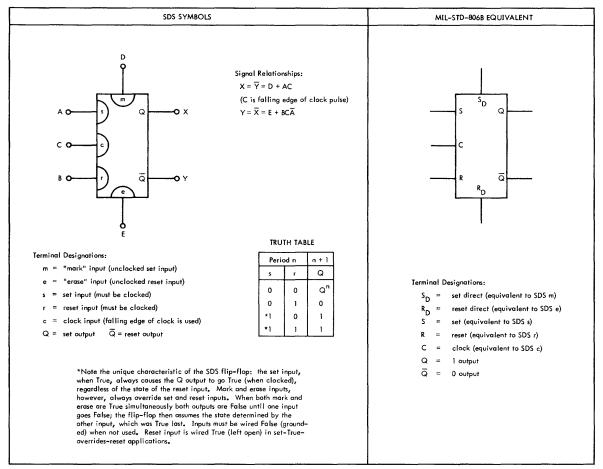

A more sophisticated flip-flop is used for most storage applications. Its cost is only slightly higher than that of the simple dc flip-flop because the entire circuit is placed on a single IC chip. This flip-flop IC is designated the SDS 307. Its characteristics are described in the diagram on page 15.

As can be seen from the logic diagram of the IC, the flipflop is essentially a structure of NOR elements, but much more complex than the simple dc flip-flop described previously.

The flip-flop has a pair of dc inputs (called mark for dc set and erase for dc reset) which can be used to make the flipflop behave like the simple dc flip-flop described before. Their primary use is to override the clocked set and reset (s and r) inputs, so that the flip-flop can be preset or cleared between clock trailing edges.

10 +4V Vcc

SDS 307 High Speed Flip-flop Microcircuit

When the mark input becomes True, the Q output becomes True and stays True regardless of the state of the mark input, and the Q output becomes False. When the erase input becomes True, the Q output becomes True and stays True and the Q output becomes False. If both dc inputs become True simultaneously, both outputs will become False as long as both inputs are held True. If one input then becomes False the flip-flop assumes the state determined by the other input, providing it remains True at least 40 nsec.

The gating to the flip-flop inputs is external to the IC, just as with buffers and inverters. The output pull-up resistor is also external to the chip. Gates are placed on the module; therefore, the IC inputs are not directly accessible at the module connector. On many modules the reset (r) inputs are wired True. That is, they are connected via circuit etch through a resistor to +8 volts. This eliminates external wiring to the r input in many applications. It is possible to wire the SDS flip-flop in this unique way because a True signal on the set (s) input always overrides a True on the reset (r) input.

The set-override mechanism and the other SDS 307 features can be understood in terms of the IC logic diagram above. The flip-flop is a dual rank configuration of NOR elements. The second rank is a simple NOR flip-flop, coupled to the output pins through buffers that each provide 60 ma (16 unit loads), normally connected to external pull-ups. The first rank consists of two flip-flops, one for set and one for reset. The two internal lines which couple the first rank to the second also connect to the clock inverter. When the clock goes True these two lines are clamped to ground, isolating the second rank so that it holds its original state. During this time, while clock is True, the set and reset flipflops are primed to the states of their inputs. When clock falls they assume the new states and regain control of the second rank flip-flop. Note that the outputs change to the new state on the clock trailing edge. Inputs must be steady for 30 nsec preceding and 5 nsec following the clock trailing edge to permit first rank flip-flops to stabilize.

The set inverter will always override inputs to the reset inverter when the set input is True because it is coupled to an output of the set flip-flop, forming a wired AND, while the reset inverter is coupled to an input. This is the basis for the set-override feature.

The second rank output is fed back to the first rank so that the outputs remain unchanged when clock pulses occur with both set and reset inputs False.

Note that the mark and erase inputs are not shown in the diagram. Essentially they bypass the first rank, activating the second rank directly, thus overriding the entire set-re-set-clock structure.

#### Advantages Of Clocked Flip-flop Operation

The use of a clock, or system time reference, was briefly

mentioned in the discussion of system requirements, and will be reviewed in more detail here.

A clock pulse, which is a logic signal that is sent simultaneously to all flip-flops in a synchronous system, serves to inhibit storage of logic signals during the periods when changes are taking place on the logic lines (the etched circuit and back-panel wiring that connects all inputs and outputs). The clock accomplishes this by limiting the time that new information can be stored in a clocked flip-flop via the set and reset inputs to the short duration (usually 5 to 10 nanoseconds) of the clock trailing edge. While the clock is high the second rank flip-flop of the SDS 307 retains its original state. It is only when the clock level falls that the state of the first rank flip-flops is transferred to the second. Then, while the clock level is False, the set and reset outputs remain as they are. The latter can be verified by assuming the several s and r input possibilities and working through the logic diagram.

The use of the clock avoids timing problems due to logic race conditions which can result when level changes arrive at flip-flop inputs at different times, because of different propagation delays in the electrical components in parallel paths leading to the same flip-flop. A logic race condition is present when one signal causes a flip-flop to change state before all signals have had time to settle to their final levels.

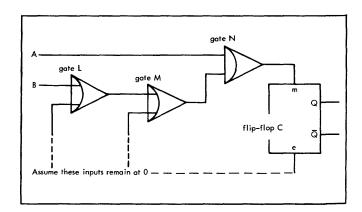

As an illustration, consider the simple network shown below, which uses the mark and erase inputs to illustrate the operation of a flip-flop without a clock. Assume that flipflop C is initially in the reset condition. Also assume that level A is initially False while level B is initially True. Now if A becomes True and simultaneously B becomes False, the new value of A arrives at gate N before the new value of B arrives, because the B change is delayed in going through gates L and M. Therefore, both inputs to gate N are True for the duration of the delay. Since the mark input of C is at all times sensitive to the output of gate N, flip-flop C will erroneously set if the delay is long enough. When the new value of B finally arrives at gate N, the desired input condition to flip-flop C is established, but an incorrect result has already been stored in C and cannot be reversed.

Obviously the problem is avoided if the output of gate N is not allowed to change flip-flop C state until after all signals have settled. The trailing edge trigger clo.:k technique provides the longest possible settling time.

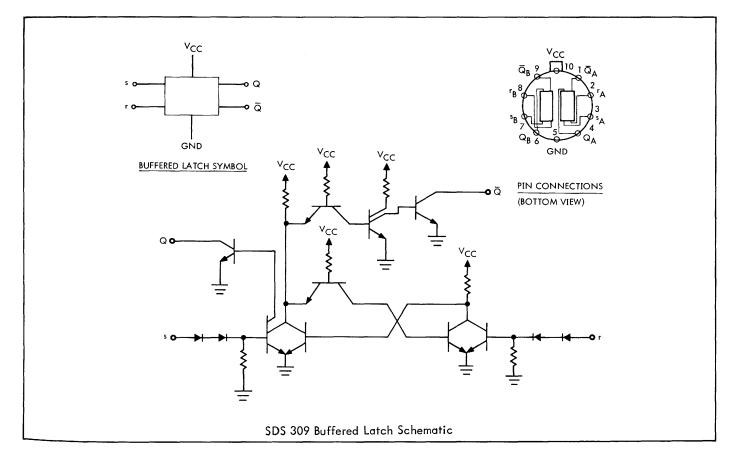

#### Buffered Latch

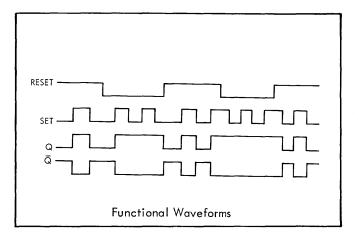

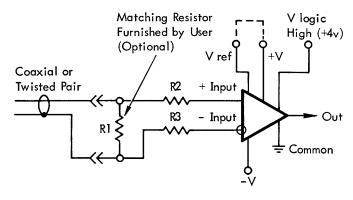

Another storage element used in T Series modules is the SDS 309 Buffered Latch microcircuit. This microcircuit provides the storage capabilities of a DC flip-flop and at the same time eliminates noise-induced delatching which sometimes affects other types of latch circuits.

One TO-96 case contains two buffered latch circuits. The logic symbol, pin connections, and schematic representation of a buffered latch are given in the figure below.

The buffered latch circuit has two modes of operation. One mode is defined by the reset input (r) being true (1), the other mode is defined by r being false (0). The functional waveforms in the figure shown at right support the following explanation of the two modes of operation.

If the reset input (r) is true (1), then the output (Q) follows the set input (s). If the reset input (r) is false (0), then the output (Q) will go true (1) with the first occurrence of a set pulse and remain true so long as the reset input (r) remains false.

This type of logic is commonly referred to as set-overridereset logic. If the set and reset inputs are true at the same time, the output will follow the set input.

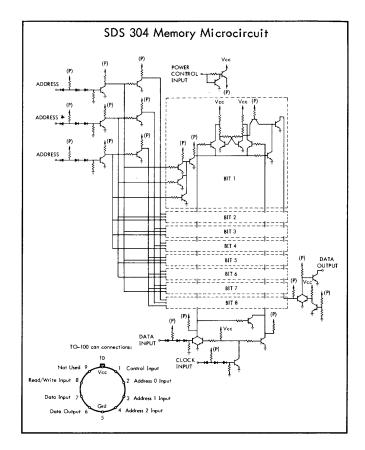

#### Fast-access Memory Element

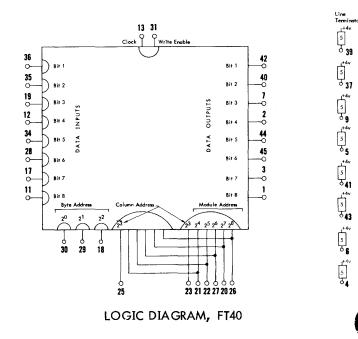

The FT40 module uses an integrated storage element which can store eight bits on one integrated circuit. This proprietary IC contains 178 components on a single IC chip. Sixteen ICs plus other logic circuits are mounted on one module to provide addressable, clocked flip-flop storage for 128 bits. The IC schematic is given in the diagram at right. Refer to the FT40 description and module data sheet for additional detail.

#### Other Circuits

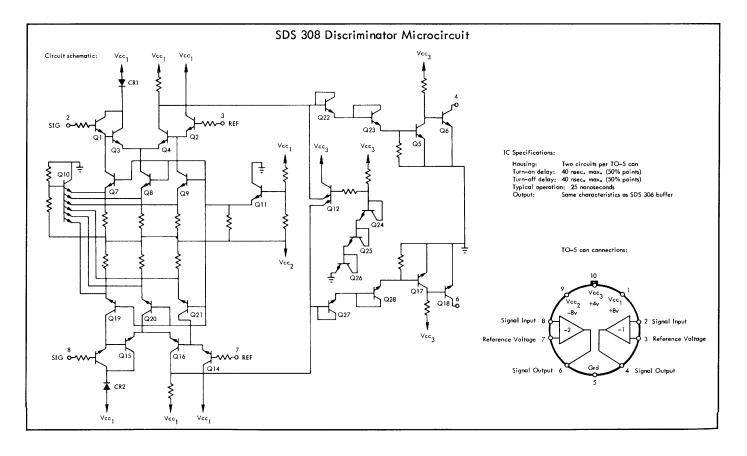

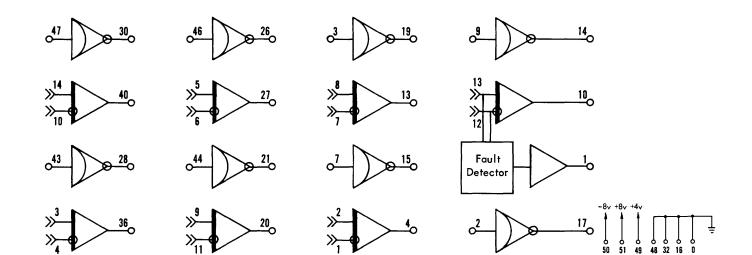

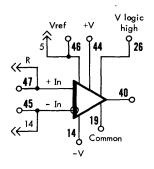

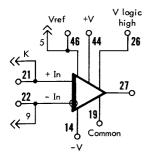

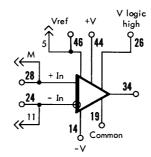

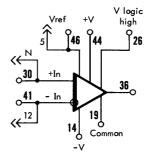

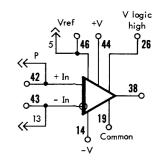

The supporting circuits such as clock oscillators, one-shots, cable drivers, etc. use a combination of integrated and discrete-component transistor circuits, as is generally the practice where volume of usage or the need for linear amplifiers makes an all-IC approach too costly at full performance. One function that does lend itself easily to integration, however, is the cable receiver circuit, (SDS 308 Discriminator) which is shown below. Circuit schematics of other circuits are given in the module data sheets.

# II. DESCRIPTIONS OF MODULES

# SUMMARY OF MODULE AND ACCESSORY TYPES

Modules are classified as logic element modules, storage element modules, and supporting circuit modules. The logic element modules contain AND, OR, NAND, and NOR gates with non-inverting or inverting amplifiers. The storage element modules contain flip-flops that are used for storage, counting, and shifting. These two broad classes of modules usually form the bulk of a system. Most supporting circuit modules are used to communicate with other equipments or with display devices. Supporting modules include cable driver and receiver modules; interface drivers and receivers to communicate with logic at levels other than 0v and +4v; Schmitt Trigger level detectors for accepting input of arbitrary waveshape; one-shots for precise control of delay; and lamp drivers, relay drivers, and D/A converters for driving display, recording, and mechanical control devices. Also included among supporting modules are the clock oscillators, which furnish the system time reference.

#### Table 1. LOGIC ELEMENTS PER MODULE

|              | OUTPUT NOT INVERTED     |                       | OUTPUT INVERTED      |                          |                         | D                            |                            |                                    |

|--------------|-------------------------|-----------------------|----------------------|--------------------------|-------------------------|------------------------------|----------------------------|------------------------------------|

| Model<br>No. | With<br>Single<br>Input | With<br>AND<br>Inputs | With<br>OR<br>Inputs | With<br>AND/OR<br>Inputs | With<br>Single<br>Input | With AND<br>Inputs<br>(NAND) | With OR<br>Inputs<br>(NOR) | With AND/OR<br>Inputs<br>(AND/NOR) |

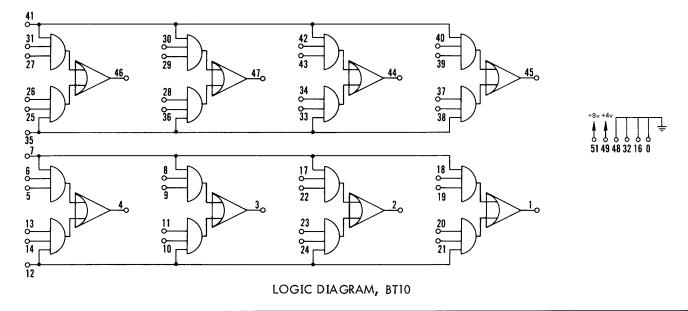

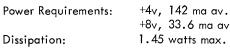

| BT10         | -                       | -                     | -                    | 8                        | -                       | -                            | -                          | -                                  |

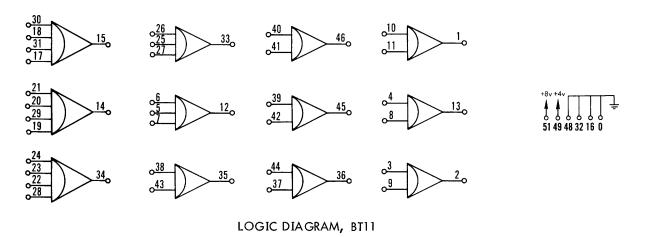

| BT11         | ~                       | 12                    | -                    | -                        | -                       | -                            | -                          | -                                  |

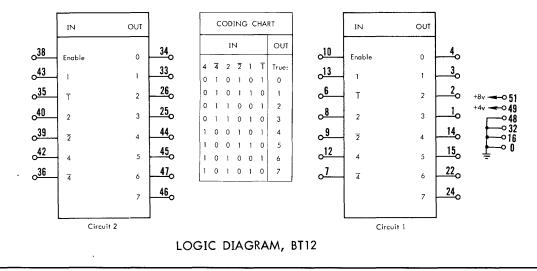

| BT12         | -                       | 2 <sup>a</sup>        | -                    | -                        | -                       | -                            | -                          | -                                  |

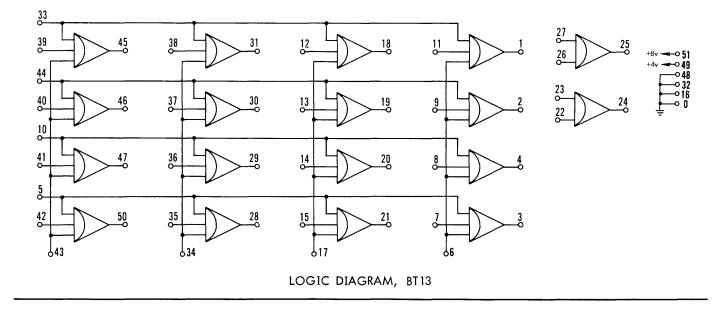

| BT13         | -                       | 18 <sup>b</sup>       | -                    | -                        | -                       | -                            | -                          | -                                  |

| BT18         | ~                       | 10                    | -                    | -                        | -                       | -                            | -                          | -                                  |

| BT27         | -                       | -                     | 12                   | -                        | -                       | -                            | -                          | -                                  |

| BT31         | 2                       | 14                    | -                    | -                        | -                       | -                            | -                          | -                                  |

| BT33         | -                       | -                     | -                    | 12 <sup>i</sup>          | -                       | -                            | -                          | -                                  |

| FT26         | -                       | -                     | 8c                   | -                        | -                       | -                            | -                          | -                                  |

| FT27         | -                       | -                     | 12°                  | -                        | -                       | -                            | -                          | -                                  |

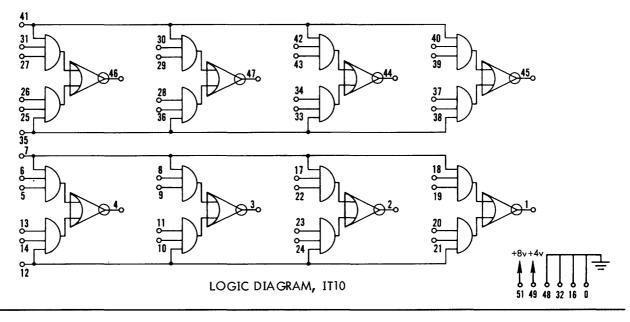

| IT 10        | -                       | -                     | -                    | -                        | -                       | -                            | -                          | 8                                  |

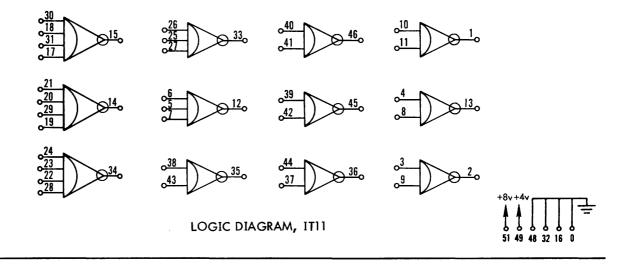

| IT11         | -                       | -                     | -                    | -                        | -                       | 12                           | -                          | -                                  |

| IT 13        | -                       | -                     | -                    | -                        | -                       | 18 <sup>b</sup>              | -                          | -                                  |

| IT14         | -                       | -                     | -                    | -                        | -                       | -                            | -                          | 8d                                 |

| IT18         | -                       | -                     | -                    | -                        | -                       | 10                           | -                          | -                                  |

| IT27         | -                       | -                     | -                    | -                        | -                       | -                            | 12                         | -                                  |

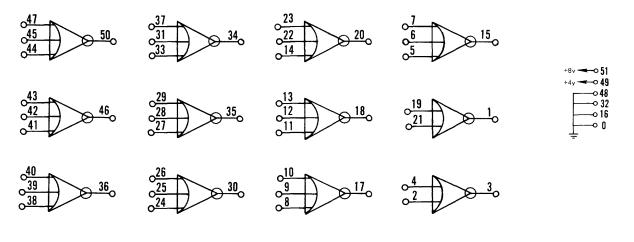

| IT31         | -                       | -                     | -                    | -                        | 2                       | 14                           | -                          | -                                  |

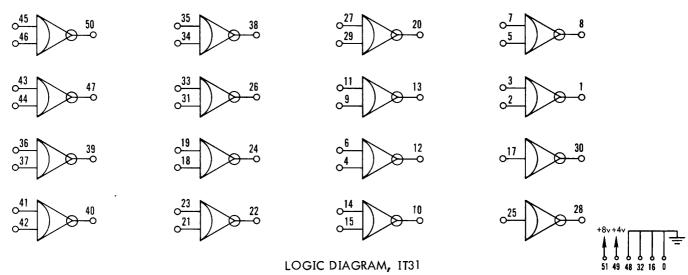

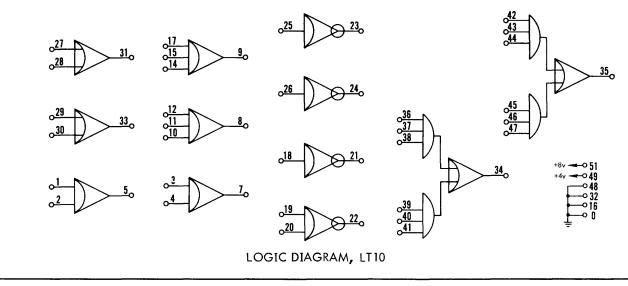

| LT10         | -                       | 4                     | 2                    | 2                        | 3                       | 1                            | -                          | -                                  |

| LT11         | -                       | -                     | -                    | 4                        | -                       | -                            | -                          | 4                                  |

| LT26         | -                       | -                     | -                    | -                        | -                       | -                            | -                          | 2 <sup>e</sup>                     |

| LT66         | -                       | 2 <sup>f</sup>        | -                    | 19                       | _                       | -                            | -                          | -                                  |

| LT67         | -                       | -                     | -                    | h                        | -                       | -                            | -                          | h                                  |

Arranged as 2 separate binary-to-octal decoders

b elements in matrix form, 2 independent

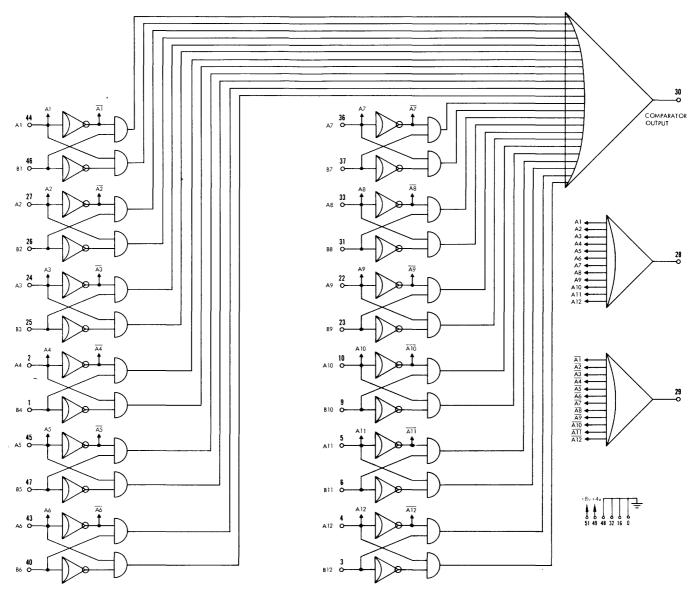

d With latch inputs grounded Eight 4-input AND/NORs in 4 x 8 matrix Two 4-bit switch comparators

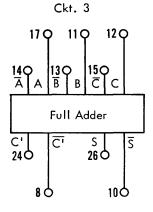

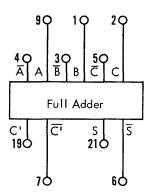

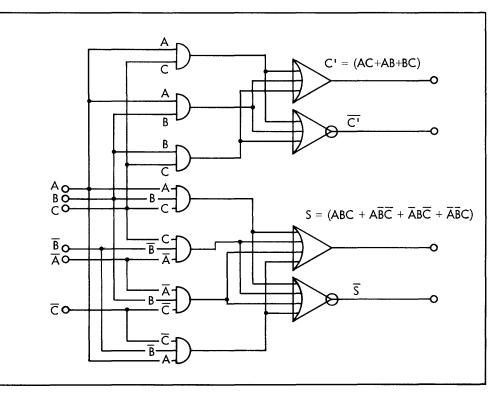

- Four full-adders; two bits and

- carry in, sum and carry out Arranged as dual-input 12-bit multiplexer

Accessory modules include cable plug modules, breadboard modules, and an extender module. Other accessories include power supplies, cabinets, mounting cases, cables and connectors, wire, and wiring tools. Accessories are described in Section III.

#### LOGIC ELEMENT MODULES

These modules carry the prefix B, I, or L. Some F prefix modules, the buffered latches, also operate as logic element modules when the latch control inputs are grounded. Table 1, below, lists the modules and shows the assignment of logic functions to modules.

The AND/OR structures may be very simply converted to pure ANDs or ORs by wiring AND inputs True (leaving open) or wiring OR inputs False (grounding). Thus the BT10, IT10, LT10, and LT11 modules can also furnish pure ORs or NORs, if the AND functions are bypassed.

#### STORAGE ELEMENT MODULES

T Series includes a number of dense and powerful modules which use the high speed, fully gated flip-flops. In addition four latch modules provide low cost storage. A high speed memory module, the FT40, can furnish storage for 128 bits.

#### SUPPORTING CIRCUIT MODULES

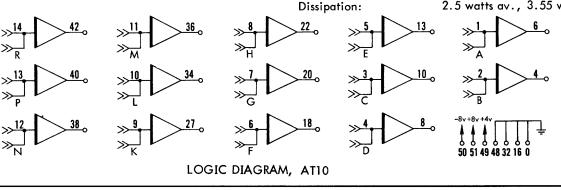

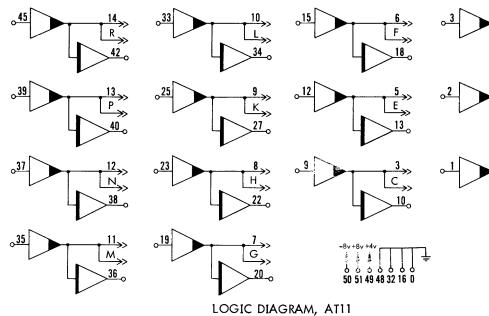

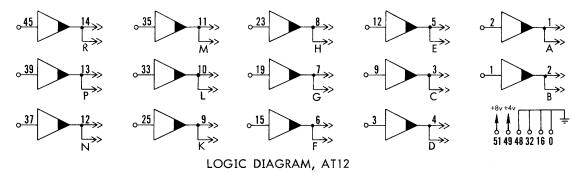

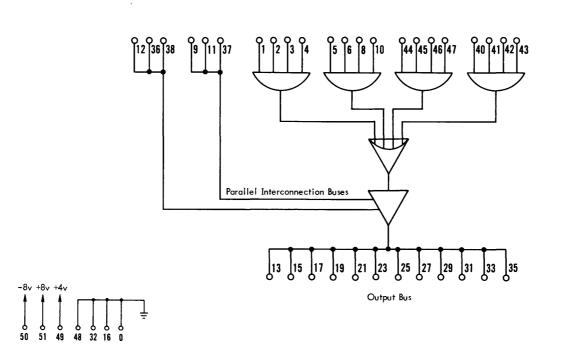

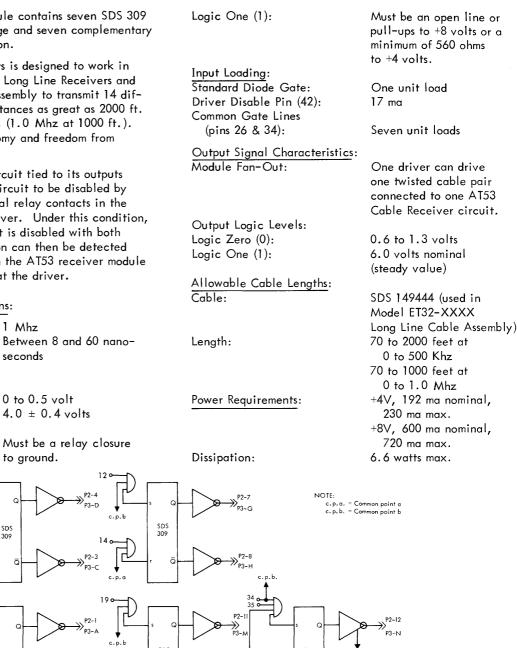

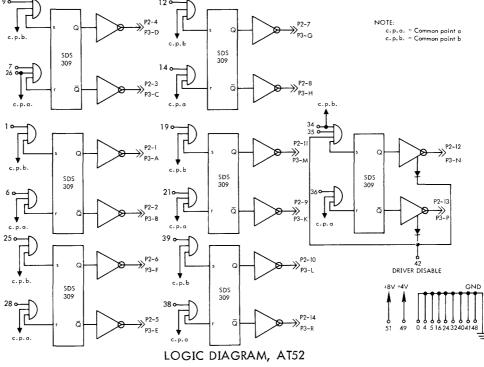

Two types of high density cable driver and receiver modules are offered. AT10, AT11, AT12, AT52 and AT53 are intended for equipment using T Series modules at both ends of the cable. AT47 and AT48 use 0v/+8v logic levels on outputs and inputs respectively, and are designed to interface through cables with other lines of modules such as the SDS discrete-component C, H, and L Series.

#### TABLE 2. STORAGE ELEMENTS PER MODULE

| Model No.                                                                   | Description                                                                | No. F. F.<br>or Latches |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------|

| FT10                                                                        | Basic flip-flops with gated set and gated clock inputs                     | 6                       |

| FT11                                                                        | Flip-flops with gating for counter modes                                   | 4                       |

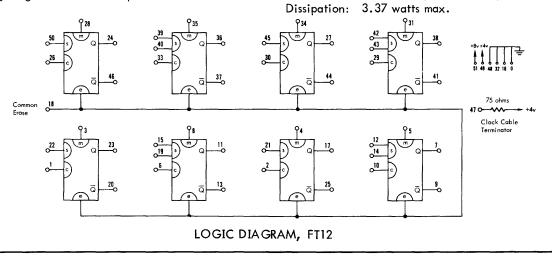

| FT12                                                                        | Basic flip-flops with some gated set inputs                                | 8                       |

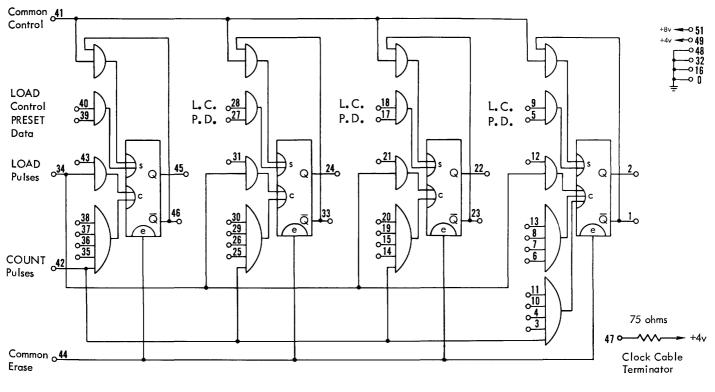

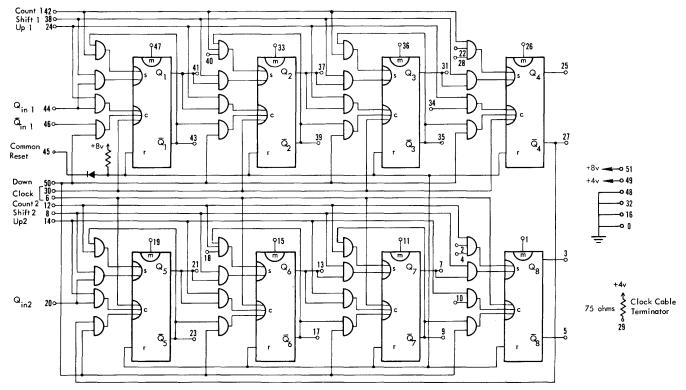

| FT19                                                                        | Multifunction counter-register                                             | 8                       |

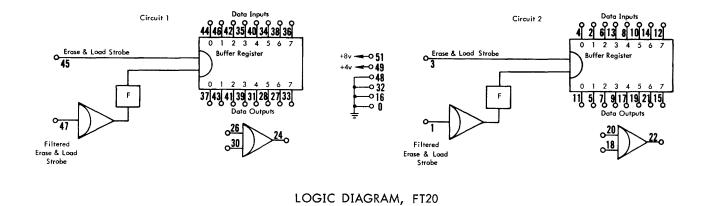

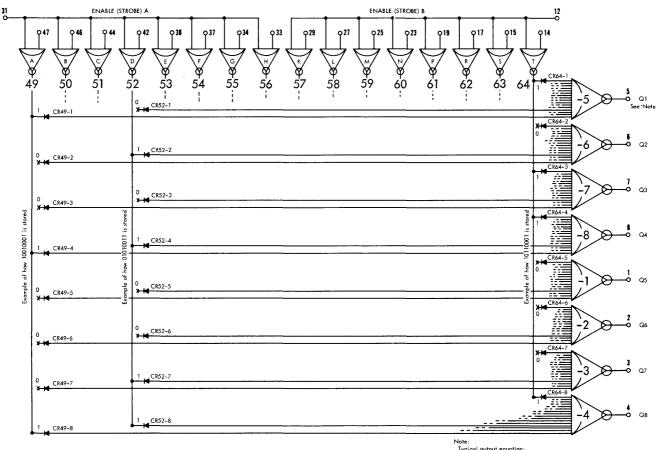

| FT20                                                                        | Two 8-bit buffered latch storage registers<br>with fast/slow strobe option | 16                      |

| FT26                                                                        | Buffered latch multiplexing matrix with 4-bit AND/OR inputs                | 8                       |

| FT27                                                                        | Buffered latch multiplexing matrix<br>with 2-bit AND/OR inputs             | 12                      |

| FT40                                                                        | 128-bit IC Memory                                                          | 128                     |

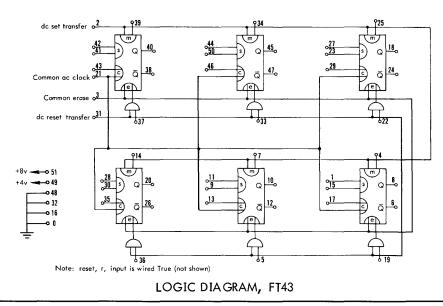

| FT43 Standard flip-flops with individual, strobed,<br>mark and erase inputs |                                                                            | 6                       |

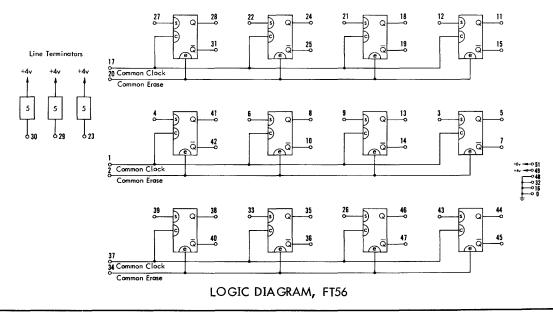

| FT56                                                                        | Clocked flip-flops, with common clock line                                 | 12                      |

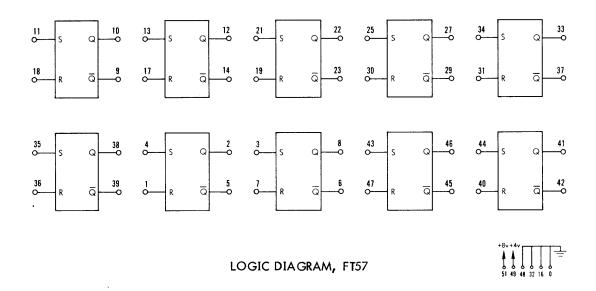

| FT57                                                                        | D-c flip-flops (cross-coupled NORs)                                        | 10                      |

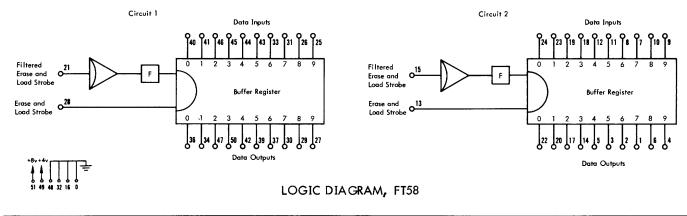

| FT58                                                                        | Two 10-bit buffered latch storage registers                                | 20                      |

<sup>&</sup>lt;sup>†</sup> Two 12–input AND Gates <sup>g</sup> One 12–bit comparator

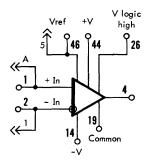

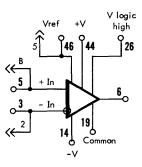

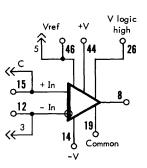

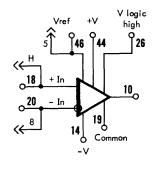

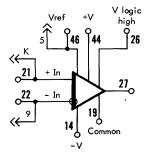

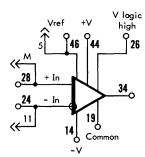

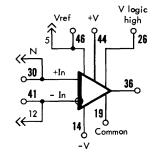

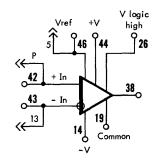

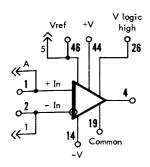

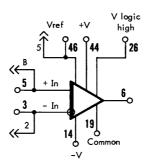

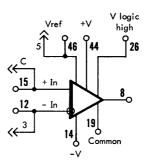

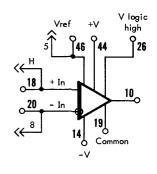

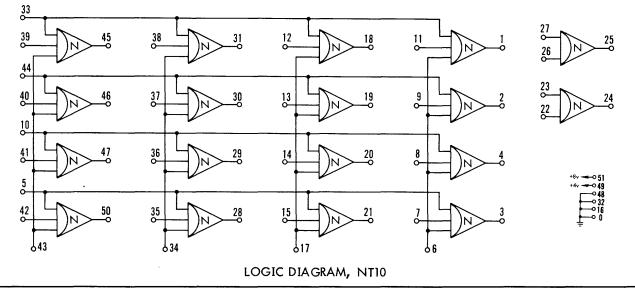

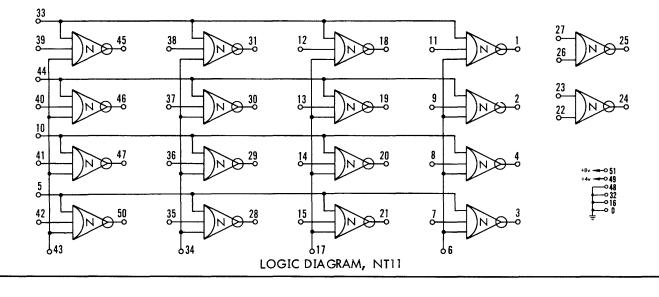

Two types of interface modules are offered. NT10 and NT11 will drive high level positive True logic (0v/+8v). Any T Series gate can receive high level logic up to +10v, thus no special interface receiver is required to work with NT10 or NT11. NT33 and NT18 interface with negative True logic systems having logic levels down to -12v.

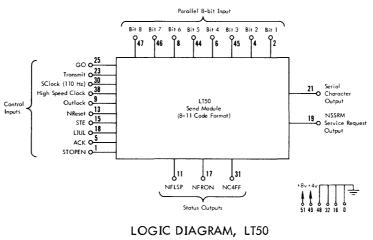

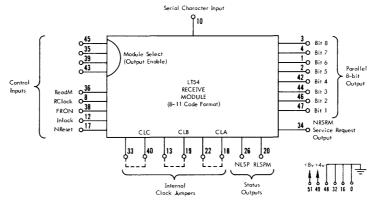

The LT50, LT54, and NT19 modules can be used to interface a digital system with a Teletypewriter or other keyboardprinter, as described in application bulletin 64–51–09.

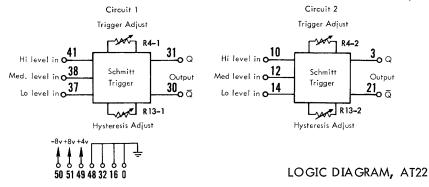

The adjustable AT22 Schmitt Trigger circuit converts any input waveshape to discrete logic level changes of 0v and +4v.

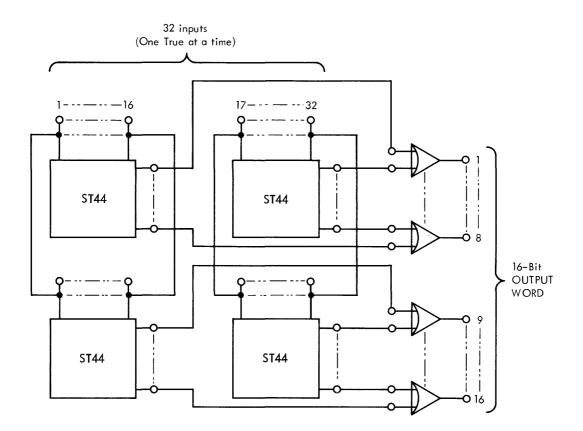

The ST44 Read-only Memory module recognizes one of eight 16-bit patterns and energizes one of eight lines upon recognition.

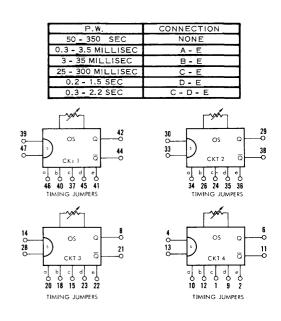

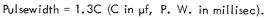

The OT18 One-shot provides outputs of adjustable pulsewidth from 100 nsec to 20  $\mu$ sec and has provision for adding external capacitance to permit pulsewidth up to 20 milliseconds. The OT14 One-shot provides outputs from 50  $\mu$ sec. to 2.2 seconds.

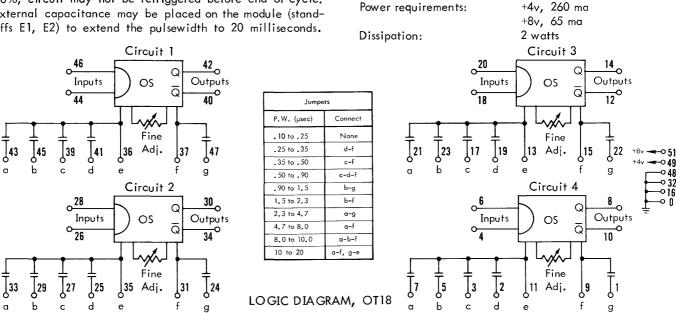

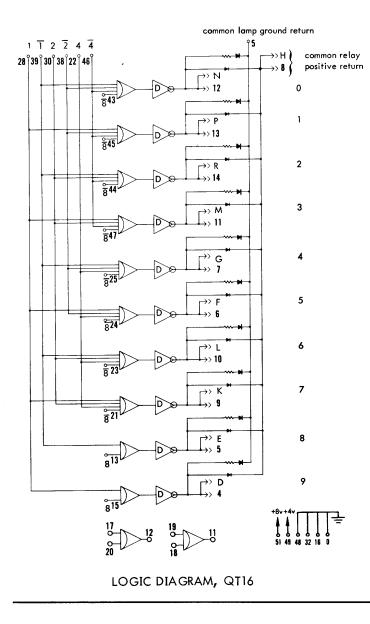

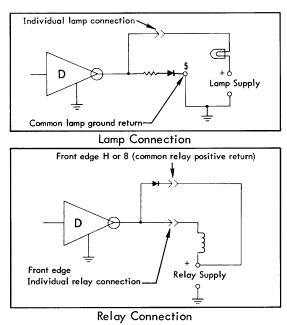

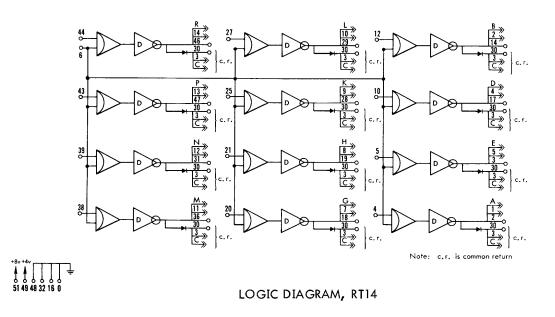

The QT14 Lamp Drivers and RT14 Relay Drivers handle up to 200 ma at 28 volts. QT16 decodes 1, 2, 4, 8 inputs and drives either ten lamps or ten relays.

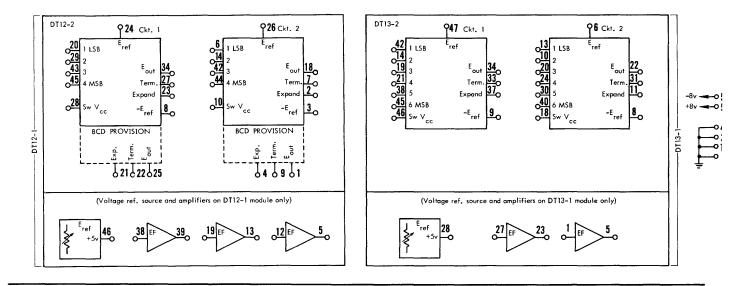

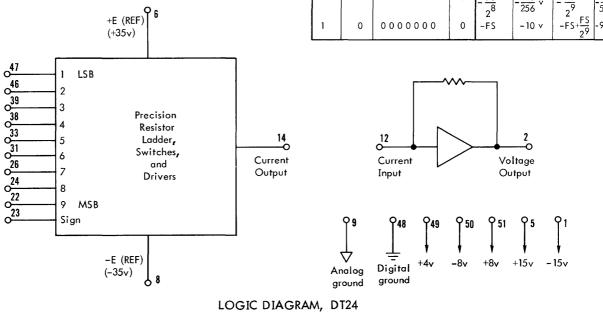

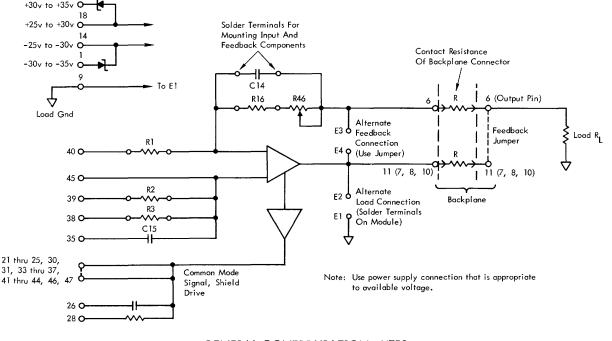

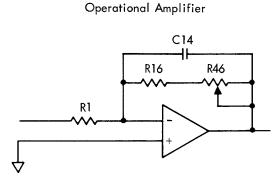

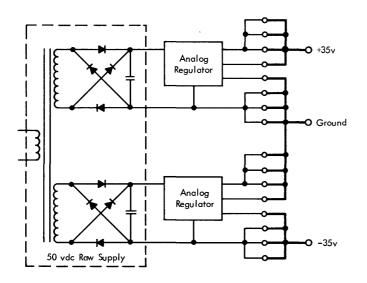

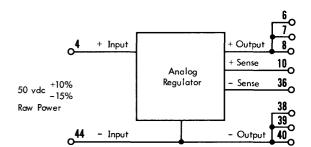

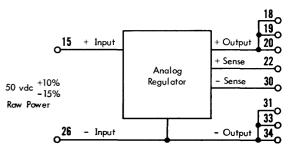

DT12 and DT13 modules drive analog devices having up to ±20 volt input requirements, in a variety of operating modes. The DT24 provides 9-bit and sign D-to-A conversion at 0.1% accuracy. The WT49 Analog Power Regulator supplies precision + or - 35 volts to sixteen DT24 modules.

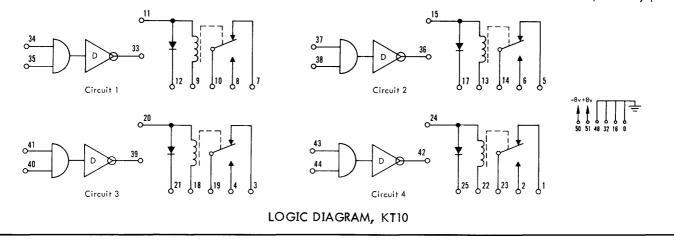

The KT10 module provides four SPDT mercury-wetted relays with individual 2-input NAND drivers. The ST14 module provides fifteen SPDT toggle switches on a card.

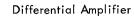

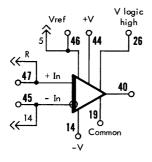

The HT58 and HT72 are versatile Operational Amplifier modules. The HT72 and AT69 provide sensitive differential receiving capability.

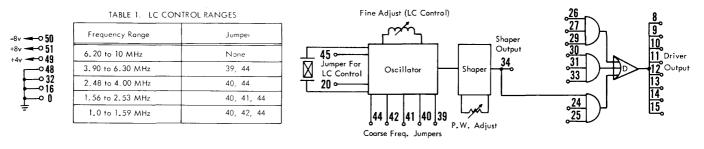

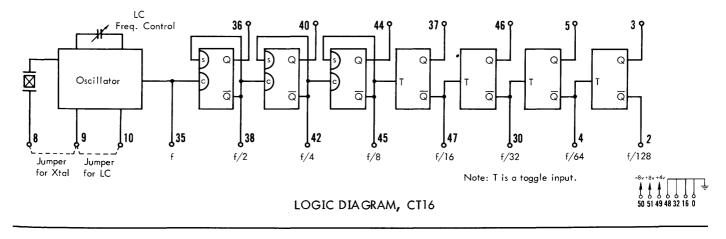

CT16 and CT10 crystal (or LC) controlled clock oscillators provide clock signals in two ranges: 1.8Kc to 2Mc, and 1Mc to 10 Mc, respectively. AT23 and AT24 clock drivers are used when large numbers of clock inputs are driven from the same source.

#### SPECIFICATIONS

Maximum operating frequency, circuit delays, fan-out, input loads, logic levels, and noise rejection are as described in General Specifications, p. 1, unless otherwise noted in the individual module descriptions.

#### Module Current Requirements

The maximum current and maximum dissipation listed for each module is for the case where all circuits are in the state which draws maximum current. The inverter and buffer circuits use maximum current when the output is logic 0. The average current specification given is the current used when the amplifier is on half the time and off half the time. In a system of any complexity the average current instead of the maximum current should be used to determine total power requirements. This gives a more accurate indication of the actual current required.

Only one current specification is given for IC flip-flops because one half of the flip-flop always conducts. Current requirements are therefore independent of output state.

#### Module Dissipation Ratings

The dissipation figure shown for a module is a worst-case calculation derived from the voltage-current product plus an allowance for IC or transistor dissipation due to load current supplied to other modules. This figure may be used to calculate maximum cooling requirements, but normally will not represent the power required by the module. If average current figures are used, dissipation will also be substantially lower than the dissipation values given.

# SUMMARY OF LOADING AND WIRING RULES

#### LOADING RULES

- Any 0v/+4v logic output may drive any 0v/+4v logic input.

- 2. Unless otherwise noted, every gate on a logic line places 1 unit load (3.8 ma) on the driver. Add all gates on a line for total load.

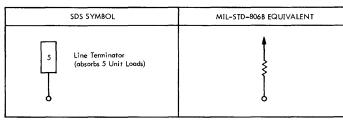

- 3. Each logic line terminator (220 ohms, on XT10) absorbs 5 unit loads. Maximum is 2 per line, 1 per branch.

- 4. Every T Series buffer, inverter, or flip-flop output drives 14 unit loads unless otherwise noted. Fan-outs of other circuits are as noted on individual specifications.

- 5. Buffer, inverter, and flip-flop outputs may be paralleled to form logic functions (see p. 13). Each one paralleled to the first decreases fan-out by 2 loads.

#### WIRING RULES

#### General

- Use No. 28 AWG copper/irradiated KEL-F wire, pointto-point. Push close to ground plane. Refer to Application Bulletin 64-51-07 for a description of wiring techniques.

- 2. Lay out connections for shortest total wire length. Two branches per line is maximum. Two connections per pin is maximum for both electrical and mechanical reasons.

- Ground unused flip-flop set inputs (wire False) to avoid set-1 permanently overriding reset. Ground unused flip-flop dc inputs. Ground unused OR inputs. Leave open (True) unused AND inputs.

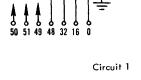

- Power pins are: +4v, pin 49; +8v, pin 51; -8v, pin 50. Ground pins are: 0, 16, 32, 48. The +4v, +8v, and ground wiring is built into back panel plane. The -8v must be wired separately to pin 50 when required.

#### Simplified Rules For Safe Operation Below 2Mhz

Because of relatively long settling time (>500 nsec) T Series logic wiring for use with clock rate under 2 Mhz is simple. Observe these rules:

- Maximum wire length is 60 inches per branch (max. 2 branches per line).

- 2. Three stages of series buffers/inverters between flipflops is maximum unless sum of delays is calculated to be under 500 nsec total.

3. With 3 stages use terminator on at least 1 line if total length of any line reaches 60 inches. With 1 or 2 stages no terminators are required.

#### Operation Above 2 Mhz Clock Rate

As clock rate is increased less delay can be tolerated in the wiring since active circuit delays are fixed. Line terminators decrease delay on the 0 to 1 transition by decreasing line capacitance charge time. At clock frequencies over 2 Mhz wiring rules are more stringent than those given above, and delays may have to be calculated. Refer to Application Bulletin 64–51–04 for a technical discussion of delay problems and for additional data on wiring delays.

In general, lines under 18 inches need not be terminated but lines over 60 inches must be terminated. Between these boundaries termination is optional and depends on both propagation speeds desired and the magnitude and timing of reflections.

# LOGIC SYMBOLS

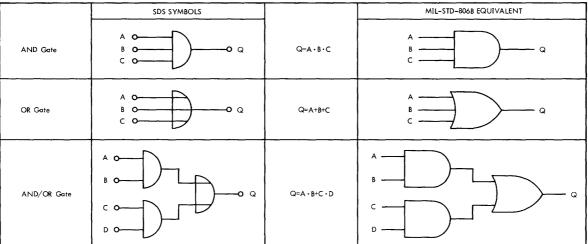

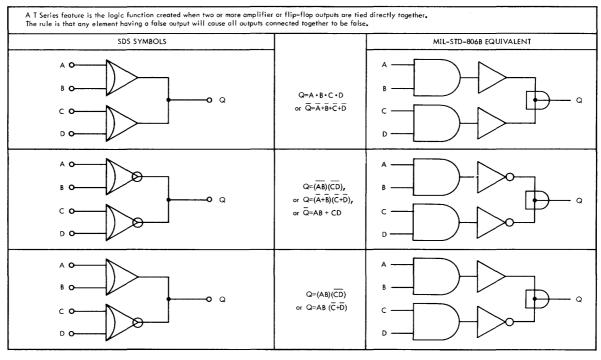

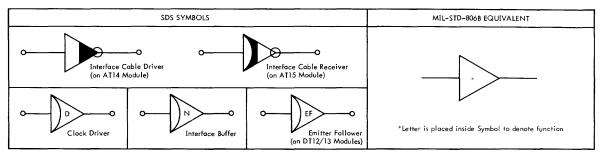

The SDS logic symbols shown below are used throughout this catalog. MIL-STD-806B logic symbols are shown beside the SDS symbols for comparison.

#### GATES WITHOUT LOGIC AMPLIFIERS

#### LOGIC AMPLIFIERS

|                                           | SDS SYMBOLS |                                             | MIL-STD-806B EQUIVALENT                                                       |

|-------------------------------------------|-------------|---------------------------------------------|-------------------------------------------------------------------------------|

| B∪ffer                                    |             | Q=A                                         |                                                                               |

| Inverter                                  |             | $\overline{Q} = A$<br>or $Q = \overline{A}$ |                                                                               |

| Without pull-up<br>resistor on the module |             | Inverter Q                                  | Pull-up resistor is connected externally.<br>Add note to symbols shown above. |

#### GATES COMBINED WITH LOGIC AMPLIFIERS

|                                      | SDS SYMBOLS |                                                                                                                                                           | MIL-STD-8068 EQUIVALENT |

|--------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Buffered AND<br>Gate (BAND)          |             | Q=A • B • C                                                                                                                                               |                         |