Price: \$7.75

## **Technical Manual**

## COMPUTER Model 930

SDS 900066C

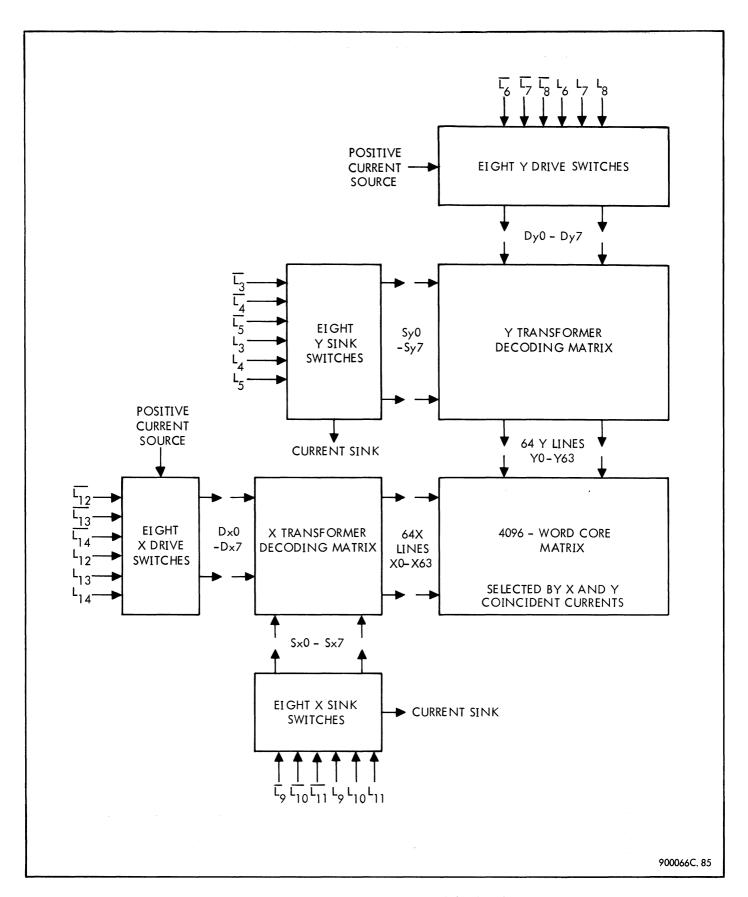

February 1966

This publication supersedes SDS 900066B dated June 1965

SCIENTIFIC DATA SYSTEMS ● 1649 Seventeenth Street ● Santa Monica, Calif. ● (213) 871-0960

## LIST OF EFFECTIVE PAGES

Total number of pages is 226, as follows:

| Page No.       | Issue    | Page No. | Issue |

|----------------|----------|----------|-------|

| Title          | Original |          |       |

| A              |          |          |       |

| i thru x       | . • .    |          |       |

| 1-1 thru 1-10  | Original |          |       |

| 2-1 thru 2-4   |          |          |       |

| 3-1 thru 3-160 | Original |          |       |

| 4-1 thru 4-18  | Original |          |       |

| 5-1 thru 5-12  | Original |          |       |

| 6-1 thru 6-2   | Original |          |       |

| 7-1 thru 7-2   | Original |          |       |

| 8-1 thru 8-2   | Original |          |       |

| I-1 thru I-4   | Original |          |       |

|                |          |          |       |

eg e segret i Liligia i

## TABLE OF CONTENTS

| Section |                                                                                                                                                                                                                           | Title Name of the Control of the Con | Page                                                 |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Ī       | GENER                                                                                                                                                                                                                     | AL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

|         | 1-1<br>1-5<br>1-14<br>1-17<br>1-22<br>1-24<br>1-26                                                                                                                                                                        | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 1-1<br>. 1-1<br>. 1-6<br>. 1-6                     |

| II      | OPERAT                                                                                                                                                                                                                    | TION AND PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                      |

|         | 2-1<br>2-3<br>2-5<br>2-6<br>2-8<br>2-10<br>2-14<br>2-16                                                                                                                                                                   | Introduction . Controls and Indicators . Operating Instructions . Turn-On Procedure . Displaying and Changing Contents of Memory . Changing Upper 16K of Memory . Turn-Off Procedure . Programming .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-1<br>2-1<br>2-1<br>2-1<br>2-1<br>2-1               |

| III     | THEOR                                                                                                                                                                                                                     | Y OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      |

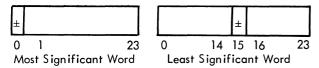

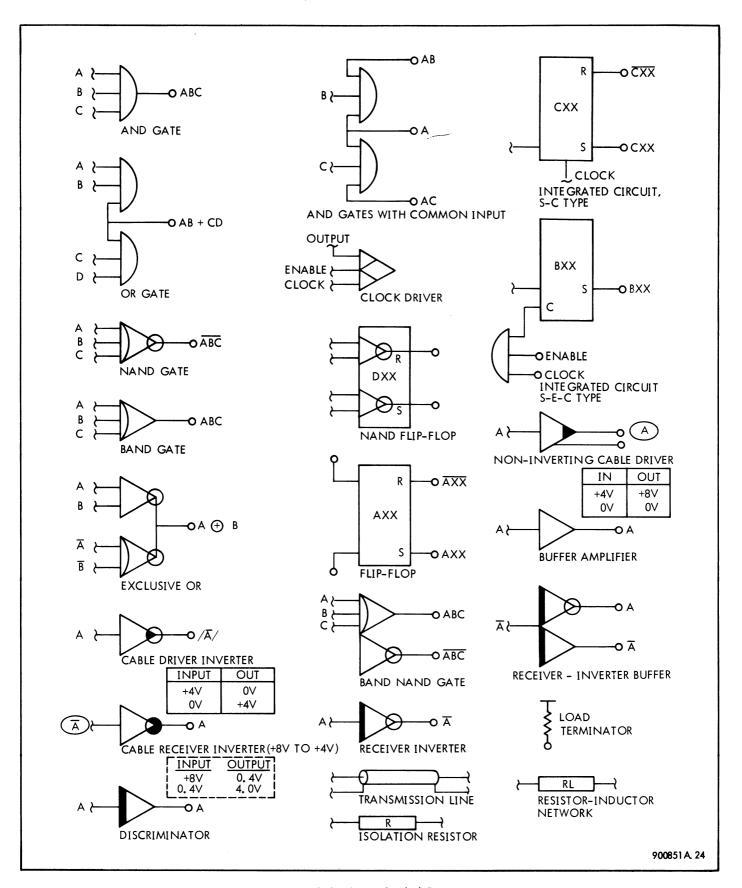

|         | 3-1<br>3-3<br>3-9<br>3-11<br>3-13<br>3-15<br>3-16<br>3-18<br>3-20<br>3-21<br>3-22<br>3-27<br>3-28<br>3-30<br>3-32<br>3-33<br>3-34<br>3-37<br>3-42<br>3-45<br>3-47<br>3-52<br>3-55<br>3-58<br>3-68<br>3-71<br>3-78<br>3-80 | General. Computer Interfaces Speed Instruction Codes. Signal Descriptions. Logical Elements Word Format  Data Word Format  Fixed-Point Format  Instruction Word Format  Instruction Word Format  Timing. Clock  Machine Cycle  Pulse Counter  Phase Control  Summary of Phase Functions  Phase Counter  Hardware Mechanization  Logic Mechanization  Registers  A- and B-Registers (A0 through A23, B0 through B23).  C-Register (C0 through C23).  Index Register (X)  Instruction Register (O1-O6)  Program Counter (P0 through P14)  Memory Data Register (M0 through M24).  Address Register (for Direct Access Buffer (Jz0 through Jz14)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3-1<br>3-1<br>3-1<br>3-1<br>3-1<br>3-3<br>3-3<br>3-3 |

|         | 3-82<br>3-84<br>3-90                                                                                                                                                                                                      | Input/Output Data Register (Rn1 through Rn3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 3–14                                               |

## TABLE OF CONTENTS (Cont.)

| Section        | Title                                                                | Page         |

|----------------|----------------------------------------------------------------------|--------------|

| 3-93           | Adders                                                               | 3-18         |

| 3-95           | P + 1 Adder (PO through P14)                                         | 3-18         |

| 3–100          | Half Adder (Hal through Ha3)                                         | 3-19         |

| 3-105          | Full Adder                                                           | 3-19         |

| 3–109          | Right Shift Adder                                                    | 3-20         |

| 3-117          | Shift Circuits                                                       | 3-23         |

| 3-118          | Right Shift One                                                      | 3-23         |

| 3-124          | Right Shift Three.                                                   | 3-24         |

| 3-128          | Left Shift Two                                                       | 3-24         |

| 3-131          | Sign Detector Circuit                                                | 3-25         |

| 3-134          | Memory Access                                                        | 3-25         |

| 3-140          | Parity                                                               | 3-26         |

| 3-148          | Time-Share                                                           | 3-27         |

| 3-150          | Interlace Time-Share                                                 | 3-27         |

| 3-153          | Simultaneous Ls and Lz Access                                        | 3-28         |

| 3-155          | Interrupts                                                           | 3-28         |

| 3-160          | Parity Interrupt Option.                                             | 3-28         |

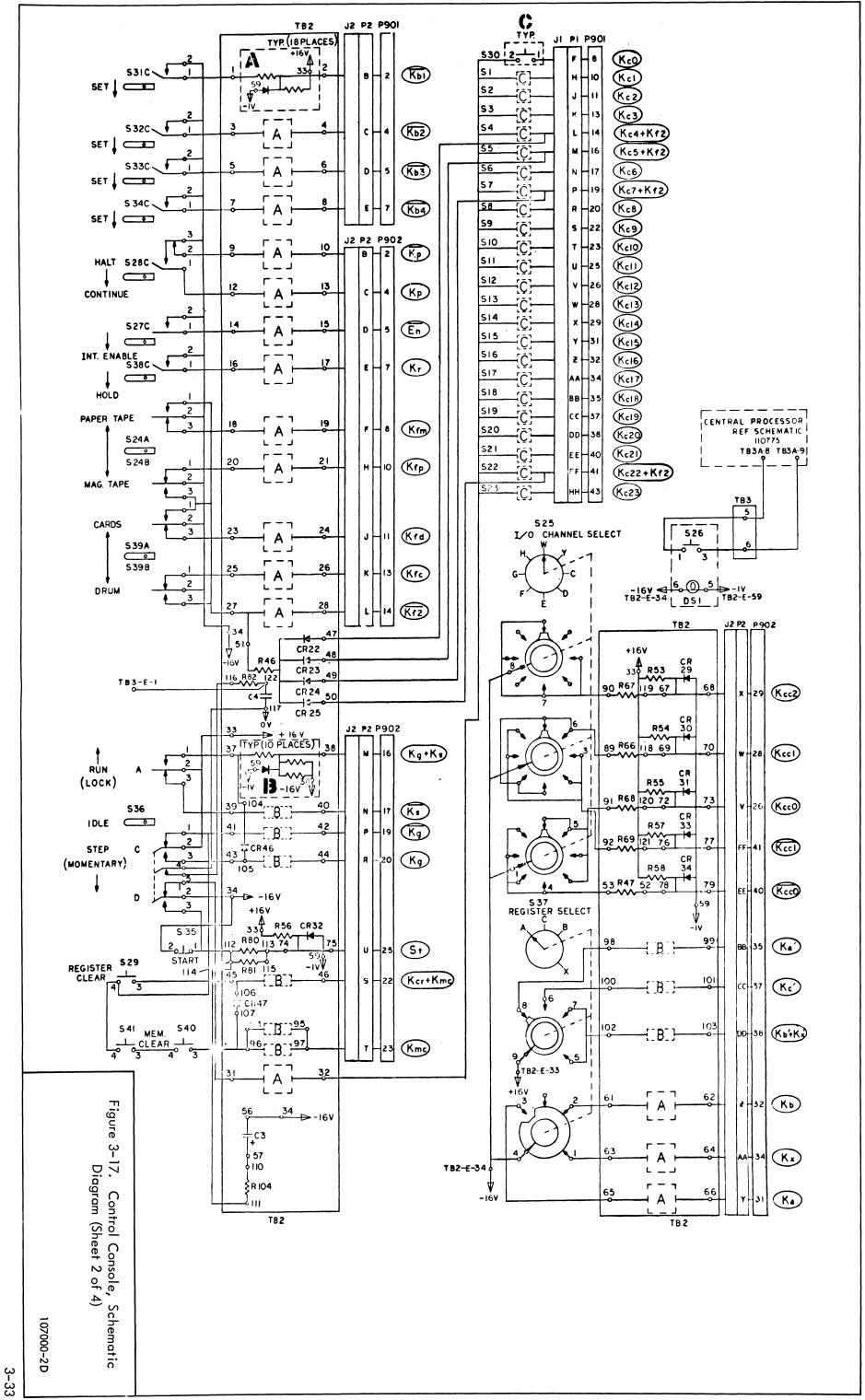

| 3-164          | Control Console Logic                                                | 3-30         |

| 3-166          | Controls                                                             | 3-30         |

| 3-167          | I/O Display Select Thumbwheel Switch                                 | 3-30         |

| 3-169          | Start Pushbutton                                                     | 3-30         |

| 3-107          | Hold Switch.                                                         | 3-30         |

| 3-172<br>3-174 |                                                                      | 3-30         |

| 3-174          | Fill Switches                                                        | 3-37         |

| 3-163          | Register Select Switch                                               | 3-37         |

| 3-195          |                                                                      | 3-39         |

| 3-173<br>3-198 | C-Register Set Pushbuttons                                           | 3-39         |

| 3-176          | Computer Enable Switch                                               | 3-39         |

| 3-200<br>3-203 | Halt Continue Switch                                                 | 3-39         |

| 3-208          | Memory Clear Pushbuttons                                             | 3-39<br>3-40 |

| 3-210          | Breakpoint Pushbuttons                                               | 3-40         |

| 3-210<br>3-215 | Run Idle Step Switch                                                 | 3-40         |

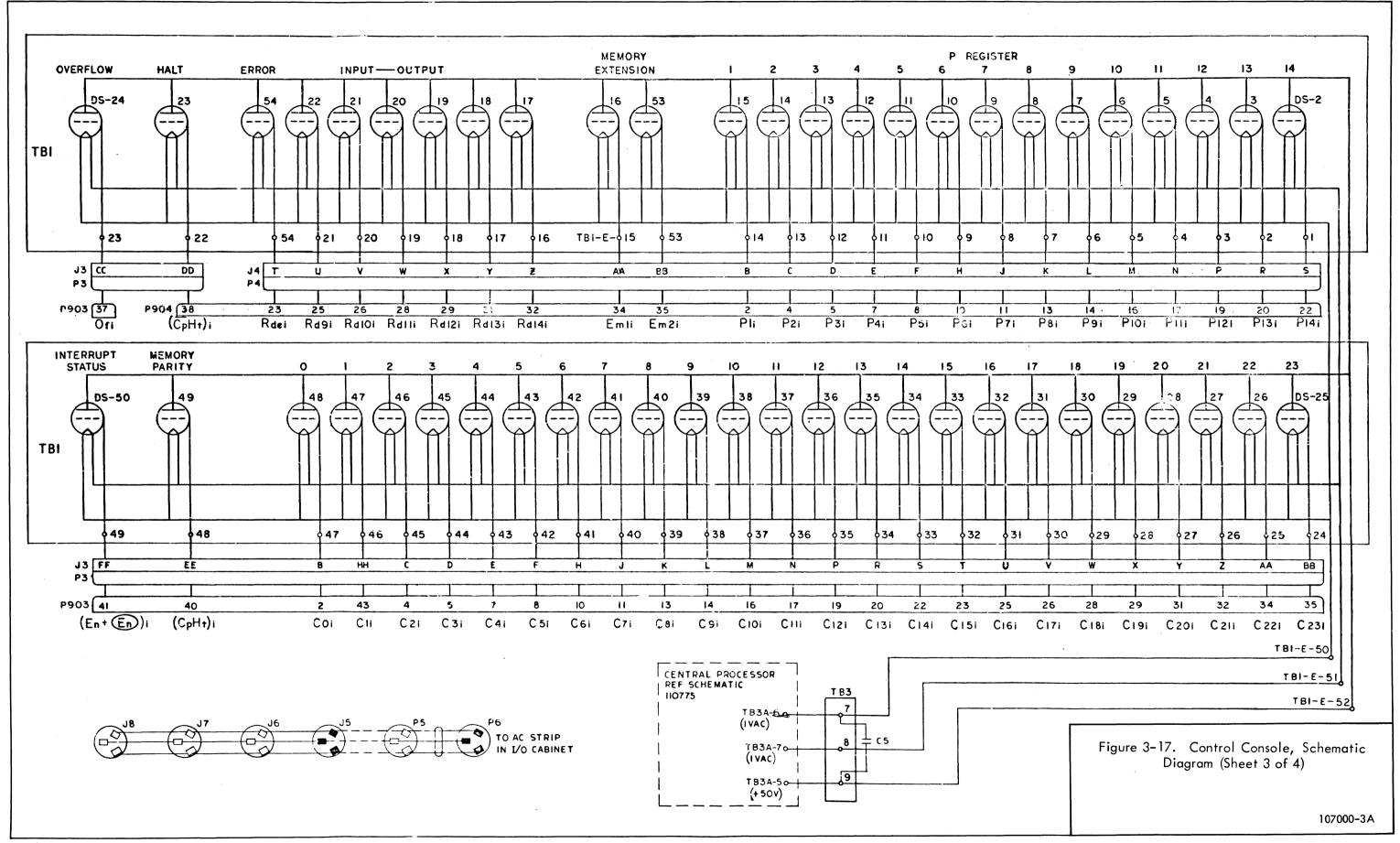

|                | Indicators                                                           |              |

| 3-216          | Overflow Indicators                                                  | 3-41         |

| 3–218          | Halt Indicator                                                       | 3-41         |

| 3-220          | Input-Output Indicators                                              | 3-41         |

| 3-222          | Memory Extension Indicators                                          | 3-41         |

| 3-224          | Program Location Indicators                                          | 3-41         |

| 3-226          | Interrupt Enabled Indicator                                          | 3-41         |

| 3-228          | Memory Parity Indicator                                              | 3-41         |

| 3-230          | Register Display Indicators                                          | 3-41         |

| 3-232          | Internal Operations                                                  | 3-41         |

| 3-233          | Instruction Set                                                      | 3-41         |

| 3-236          | Logic Description of Opcodes                                         | 3-44         |

| 3-240          | Indexing                                                             | 3-44         |

| 3-242          | Indirect Addressing                                                  | 3-45         |

| 3-244          | Programmed Operator                                                  | 3-45         |

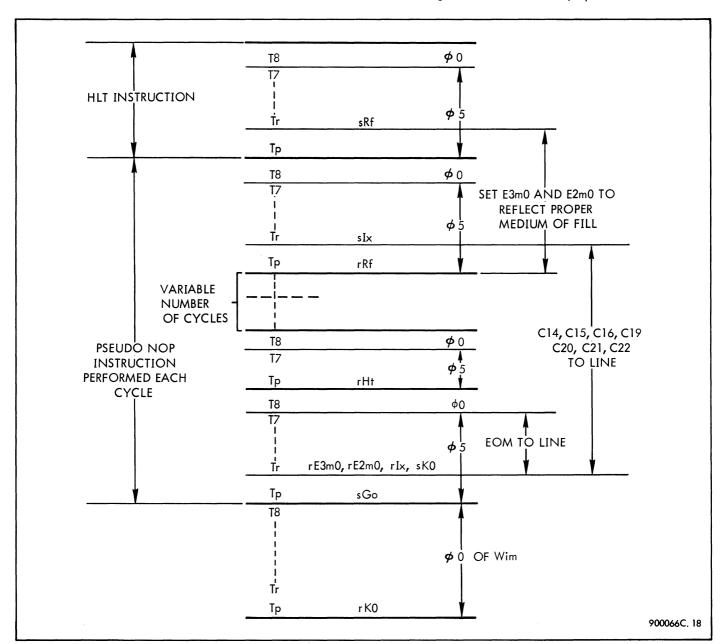

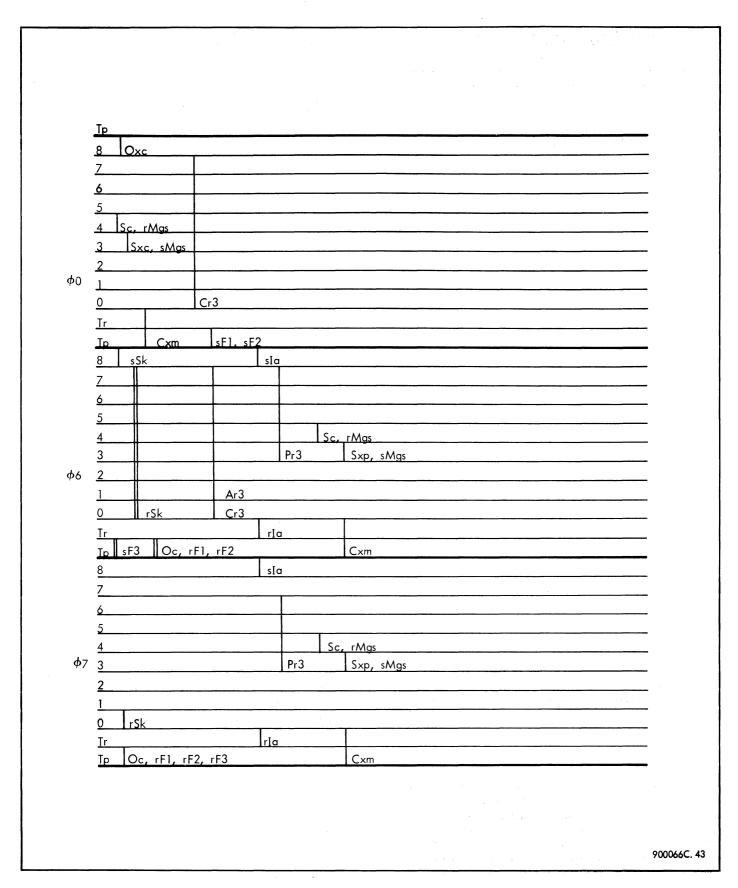

| 3-249          | Halt (HLT, Code 00) Ø0 – Ø5 – Ø0                                     | 3-47         |

| 3–253          | Branch Unconditionally (BRU, Code 01) Ø0 – Ø0                        | 3-47         |

| 3-256          | Branch Unconditionally and Clear Interrupt (BRU I, Code 01) Ø0 – Ø0  | 3-47         |

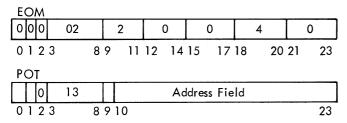

| 3-262          | Energize Output M (EOM, Code 02) Ø0 – Ø5 – Ø0                        | 3-49         |

| 3-264          | Energize Output to Direct Access Channel (EOD, Code 06) Ø0 – Ø5 – Ø0 | 3-49         |

| 3-268          | Memory Into Y Buffer When Empty (MIY, Code 10)                       | 3-50         |

| 3-270          | Memory Into W Buffer When Empty (MIW, Code 12)                       | 3-50         |

SDS 900066 Contents

## TABLE OF CONTENTS (Cont.)

Section

|       | Title                                                                       | Page         |

|-------|-----------------------------------------------------------------------------|--------------|

| 3-274 | Parallel Output (POT, Code 13) Ø0 Ø2 Ø0                                     | 3-50         |

| 3-277 | Extract (ETR, Code 14) Ø0 – Ø6 – Ø0                                         | 3-50         |

| 3-280 | Merge (MRG, Code 16) Ø0 – Ø6 – Ø0                                           | 3-50         |

| 3-282 | Exclusive OR (EOR, Code 17) Ø0 - Ø6 - Ø0                                    | 3-55         |

| 3-284 | No Operation (NOP, Code 20) Ø0 – Ø5 – Ø0                                    | 3-55         |

| 3-286 | Pseudo-NOP Instruction                                                      | 3-56         |

| 3-287 | Execute (EXU, Code 23) Ø0 – Ø0                                              | 3-56         |

| 3-289 | Y Buffer into M When Full (YIM, Code 30)                                    | 3-57         |

| 3-291 | W Buffer into M When Full (WIM, Code 32)                                    | 3–57         |

| 3-296 | Parallel Input (PIN, Code 33) Ø0 – Ø2 – Ø4 – Ø7 – Ø0                        | 3-57         |

| 3-301 | Store A (STA, Code 35) Ø0 – Ø4 – Ø7 – Ø0                                    | 3– <i>57</i> |

| 3-306 | Store B (STB, Code 36) Ø0 – Ø4 – Ø7 – Ø0                                    | 3-63         |

| 3-308 | Store Index (STX, Code 37) Ø0 – Ø4 – Ø7 – Ø0                                | 3-63         |

| 3-310 | Skip if Signal Not Set (SKS, Code 40)                                       | 3-63         |

| 3-319 | Increment Index and Branch (BRX, Code 41) Ø0 – Ø6 – Ø0                      | 3-67         |

| 3-325 | Mark Place and Branch (BRM, Code 43) Ø0 – Ø6 – Ø0                           | 3-67         |

| 3-332 | Register Change (RCH, Code X460XXXX) Ø0 – Ø5 – Ø0                           | 3-70         |

| 3-332 |                                                                             | 3-72         |

|       | Register Transfers                                                          |              |

| 3-340 | Register Clearing                                                           | 3-72         |

| 3-343 | Complementing Contents of the A-Register                                    | 3–72         |

| 3-344 | Processing Bits 15 Through 23 Only                                          | 3–73         |

| 3-345 | Skip if A Equals M (SKE, Code 50)                                           | 3–73         |

| 3-351 | Return Branch (BRR, Code 51) Ø0 – Ø6 – Ø0                                   | 3–73         |

| 3-355 | Skip if B and Memory Do Not Compare Ones                                    | 3–73         |

| 3-361 | Skip if Memory Negative (SKN, Code 53) Ø0 - Ø6 - Ø7 - Ø0                    | 3–77         |

| 3-367 | Subtract Memory From A (SUB, Code 54) Ø0 – Ø6 – Ø0                          | 3–77         |

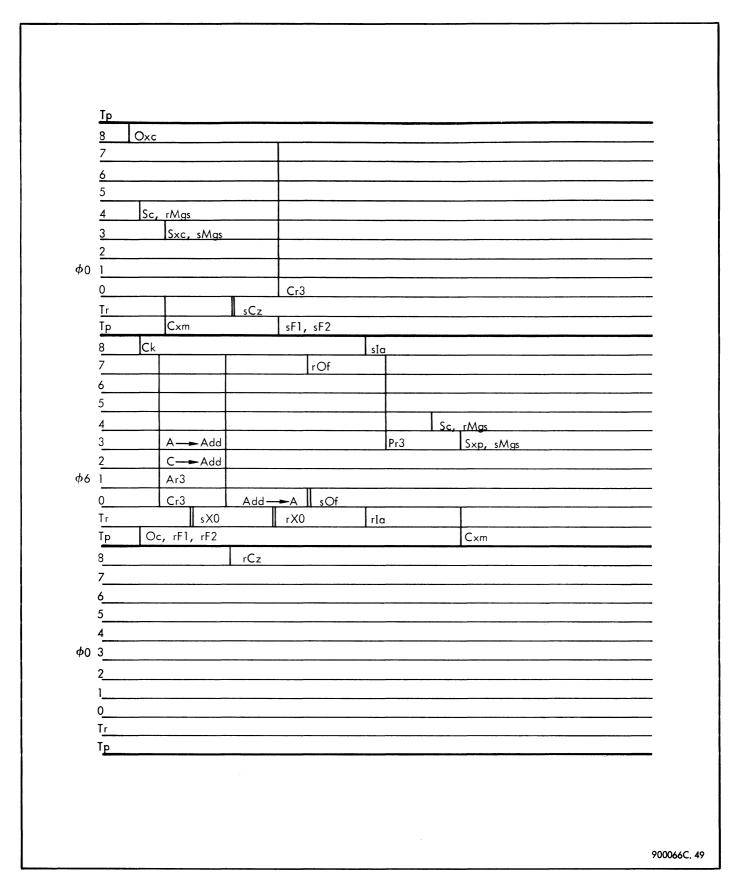

| 3-373 | Add Memory to A (ADD, Code 55) Ø0 – Ø6 – Ø0                                 | 3-80         |

| 3-379 | Subtract With Carry (SUC, Code 56) Ø0 – Ø6 – Ø0                             | 3-80         |

| 3-386 | Add With Carry (ADC, Code 57) Ø0 – Ø6 – Ø0                                  | 3–83         |

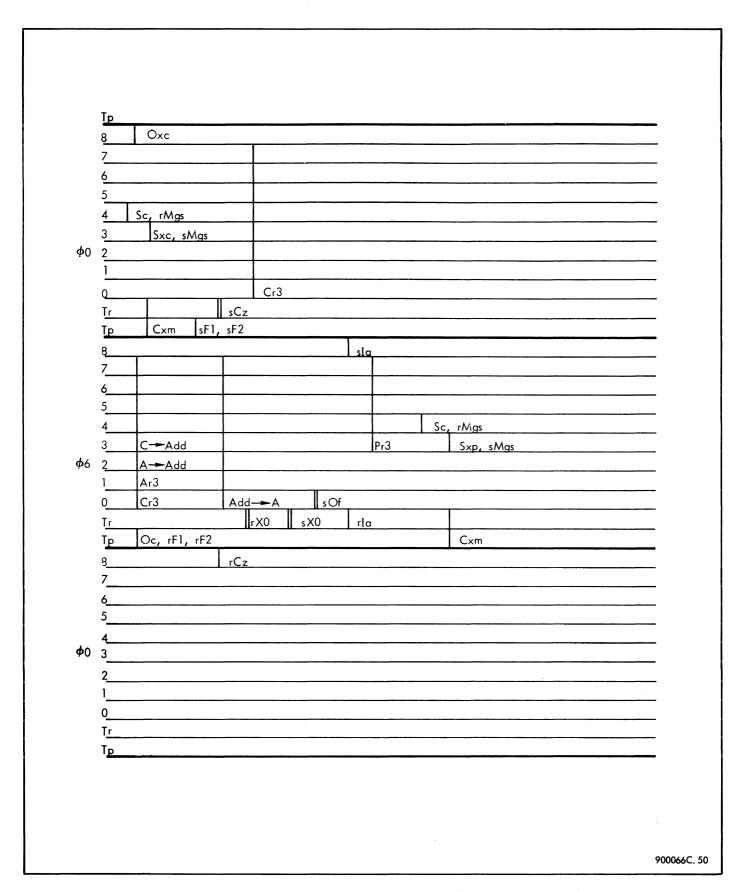

| 3-392 | Reduce Memory, Skip if Negative (SKR, Code 60) Ø0 – Ø4 – Ø7 – Ø0            | 3-83         |

| 3-399 | Memory Increment (MIN, Code 61) Ø0 – Ø4 – Ø7 – Ø0                           | 3-86         |

| 3-405 | Exchange Memory and A (XMA, Code 62) Ø0 – Ø4 – Ø7 – Ø0                      | 3–86         |

| 3-408 | Add A to Memory (ADM, Code 63) Ø0 – Ø4 – Ø7 – Ø0                            | 3-89         |

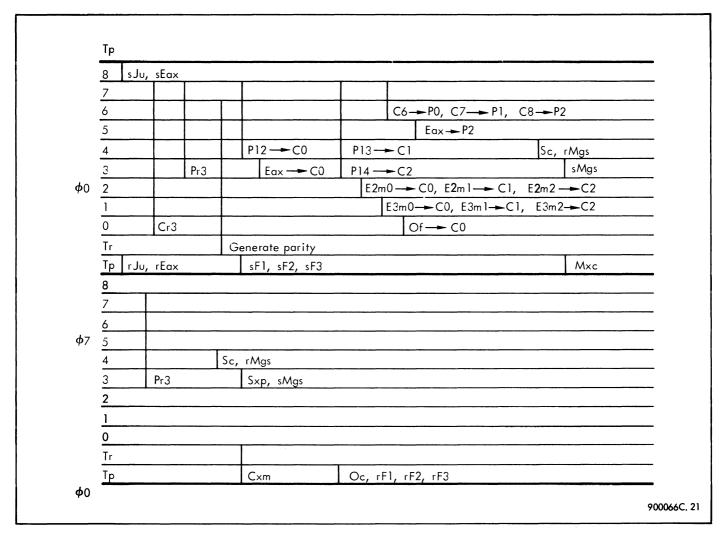

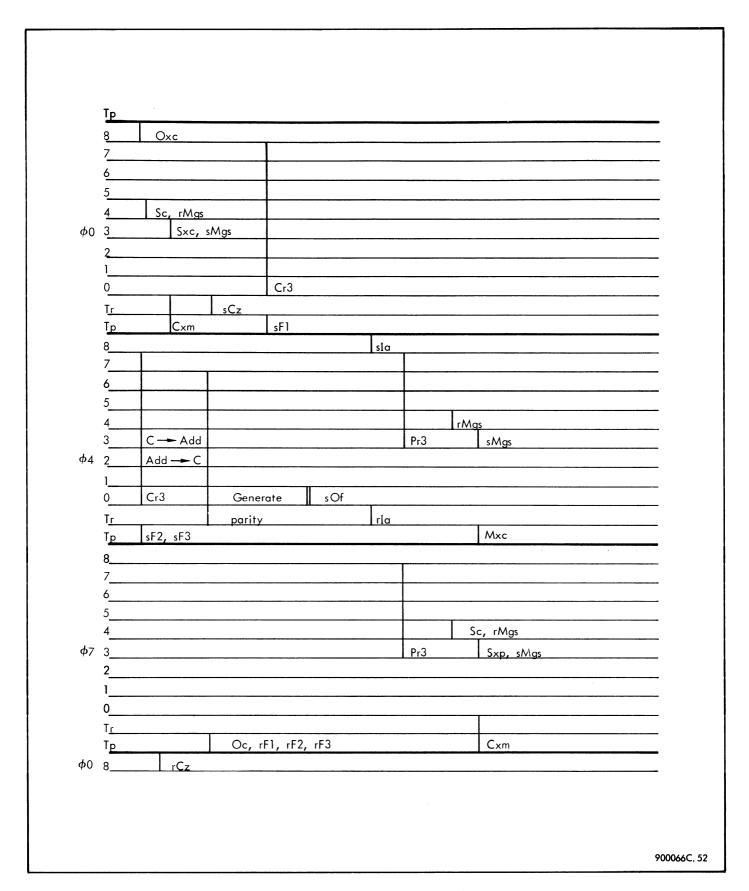

| 3-413 | Multiply (MUL, Code 64) Ø0 – Ø3 – Ø3 – Ø7 – Ø0                              | 3-89         |

| 3-427 | Divide (DIV, Code 65) Ø0 – Ø1 – Ø3 (7 Cycles) – Ø7 – Ø0                     | 3–93         |

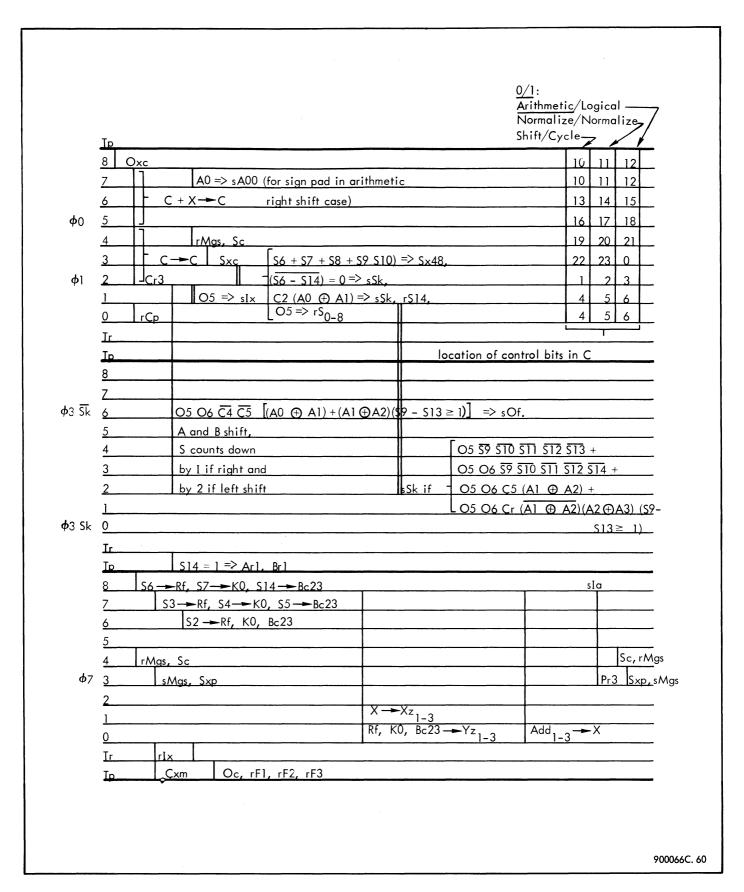

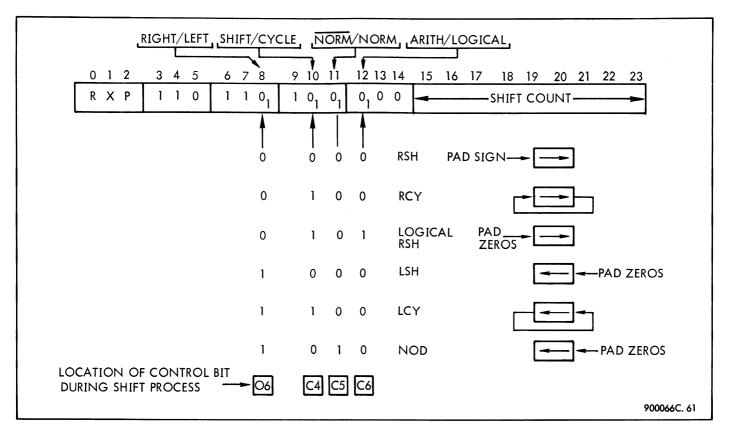

| 3-449 | Shift Series (RSH, RCY, LRSH, Code 66; LSH, NOD, DCY, Code 67)              | 0 100        |

| 0.450 | $\emptyset 0 - \emptyset 1 - \emptyset 3 - \emptyset 3 - \emptyset 7 \dots$ | 3-102        |

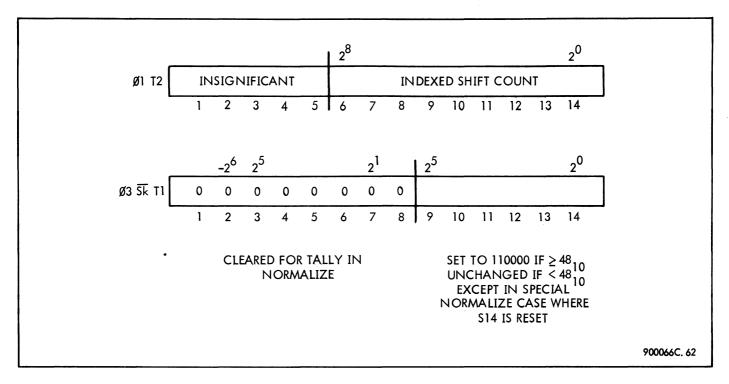

| 3-452 | General Logic for All Shift Operations                                      | 3-102        |

| 3-458 | Right Shift Logic                                                           | 3-105        |

| 3-462 | Left Shift, Not Normalize                                                   | 3-105        |

| 3-466 | Normalize                                                                   | 3-105        |

| 3-474 | Skip if A Equals Memory on B Mask (SKM, Code 70) Ø0 - Ø6 - Ø7 - Ø0          | 3-108        |

| 3-480 | Load Index (LDX, Code 71) Ø0 – Ø6 – Ø0                                      | 3-108        |

| 3-484 | Skip if A and Memory Do Not Compare Ones (SKS, Code 72) Ø0 – Ø6 – Ø7– Ø0    | 3-108        |

| 3-490 | Skip if A Greater Than Memory (SKG, Code 73) Ø0 – Ø6 – Ø7 – Ø0              | 3-112        |

| 3-498 | Difference Exponents and Skip (SKD, Code 74) Ø0 - Ø6 - Ø7 - Ø0              | 3-112        |

| 3-505 | Load B (LDB, Code 75) Ø0 – Ø6 – Ø0                                          | 3-115        |

| 3-508 | Load A (LDA, Code 76) Ø0 - Ø6 - Ø0                                          | 3-115        |

| 3-511 | Copy Effective Address into Index Register (EAX, Code 77) Ø0 - Ø6 - Ø0      | 3-115        |

| 3-516 | Memory Operation                                                            | 3-118        |

| 3-521 | Basic Operation                                                             | 3-118        |

| 3-526 | Memory Cycles                                                               | 3-121        |

| 3-529 | Read-Restore Cycle                                                          | 3-121        |

| 3-538 | Clear-Write Cycle                                                           | 3-125        |

| 3-541 | Addressing                                                                  | 3-125        |

## TABLE OF CONTENTS (Cont.)

| Section | Title                                                   | Page           |

|---------|---------------------------------------------------------|----------------|

|         | 3–543 Central Processor Addressing                      | 3-125          |

|         | 3-546 Direct Access                                     | 3-126          |

|         | 3–548 Priority Logic                                    |                |

|         | 3-552 Jumper Modules                                    |                |

|         | 3-557 Address Decoding                                  | 3-1 <i>2</i> 7 |

|         | 3-559 Drive Line Selection                              | 3-127          |

|         | 3–572 Stack Addressing                                  | 3-134          |

|         | 3–576 Inhibiting System                                 |                |

|         | 3–580 Inhibit (Z) Lines                                 | 3–136          |

|         | 3–588 Sensing System                                    |                |

|         | 3-594 Memory Write Lockout                              | 3-139          |

|         | 3-600 Programmed Write Lockout Model 92061              | 3-146          |

|         | 3-606 Manual Write Lockout Model 92060                  | 3-148          |

|         | 3-609 Lockout Interrupt                                 | 3-149          |

|         | 3-611 Memory Heating System                             |                |

| IV      | INSTALLATION AND MAINTENANCE                            |                |

|         | 4-1 Installation                                        | 4-1            |

|         | 4-2 Control Console                                     | 4-1            |

|         | 4-4 Forced-Air Cooling                                  | 4-1            |

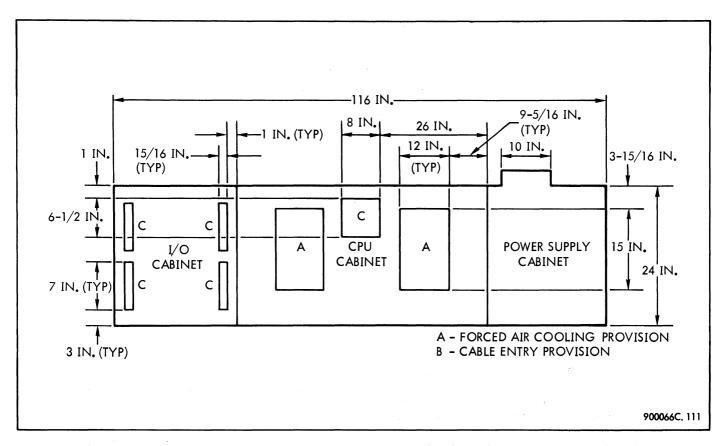

|         | 4-8 System Arrangement                                  | 4-1            |

|         | 4-10 Input Power Wiring                                 | 4–1            |

|         | 4-12 Pre-Installation Considerations                    | 4-1            |

|         | 4-14 Installation Procedure                             | 4-1            |

|         | 4-16 Parity Interrupt Installation                      | 4-1            |

|         | 4-18 Addressing Modification Installation               |                |

|         | 4-20 Memory Write Lockout Installation                  |                |

|         | 4-21 Manual Memory Write Lockout                        |                |

|         | 4–22 Programmed Memory Write Lockout                    |                |

|         | 4–23 Memory Expansion                                   |                |

|         | 4-25 Checkout                                           |                |

|         | 4–27 Preventive Maintenance                             |                |

|         | 4-29 Corrective Maintenance                             | 4-12           |

|         | 4-31 Special Test Equipment                             |                |

|         | 4-33 Adustments                                         |                |

|         | 4-35 Temperature Adjustment                             |                |

|         | 4-37 Memories With SDS Power Supplies                   | 4-12           |

|         | 4–38 Memories With Harrison Laboratories Power Supplies |                |

|         | 4-39 Adjustment of One-Shots                            |                |

|         | 4–41 Threshold Voltage Adjustment                       |                |

|         |                                                         |                |

|         | A =                                                     | 4-13           |

| V       | PERFORMANCE TESTING AND TROUBLE ANALYSIS                |                |

|         | 5–1 Test Programs                                       | 5-1            |

| VI      | 5-4 Memory Troubleshooting PARTS LIST                   | 5–1            |

|         | DRAWINGS                                                |                |

| VII     |                                                         |                |

|         | 7-1 Introduction                                        | 7-1            |

| VIII    | LOGIC EQUATIONS                                         |                |

|         | ALPHABETICAL INDEX                                      | I-1            |

## LIST OF ILLUSTRATIONS

| Figure | Title                                        | Page |

|--------|----------------------------------------------|------|

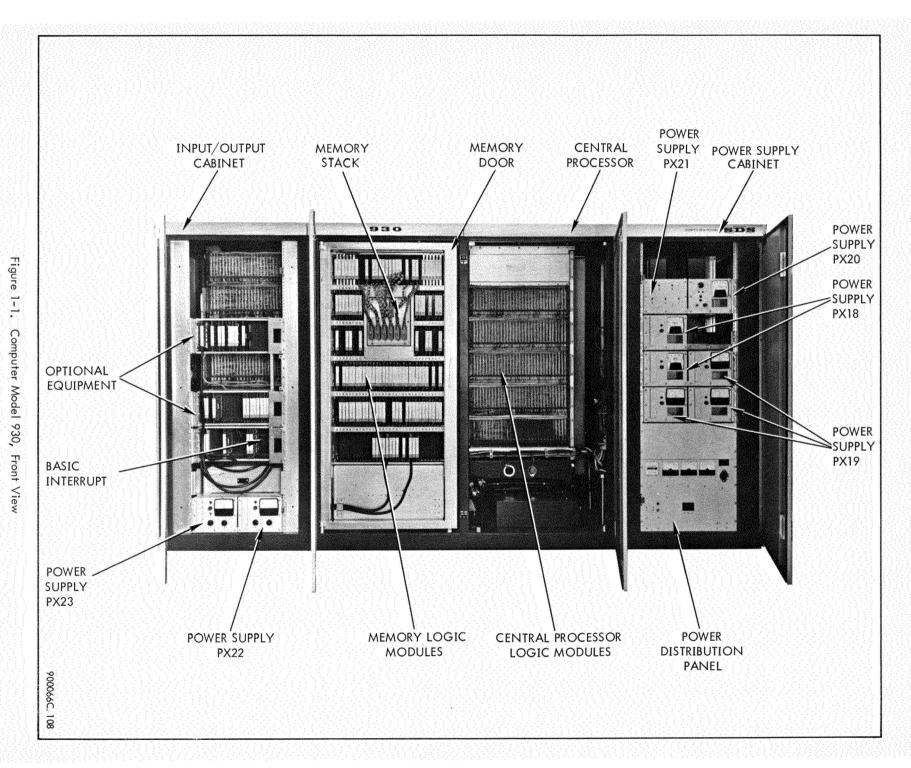

| 1-1    | Computer Model 930, Front View               | 1-2  |

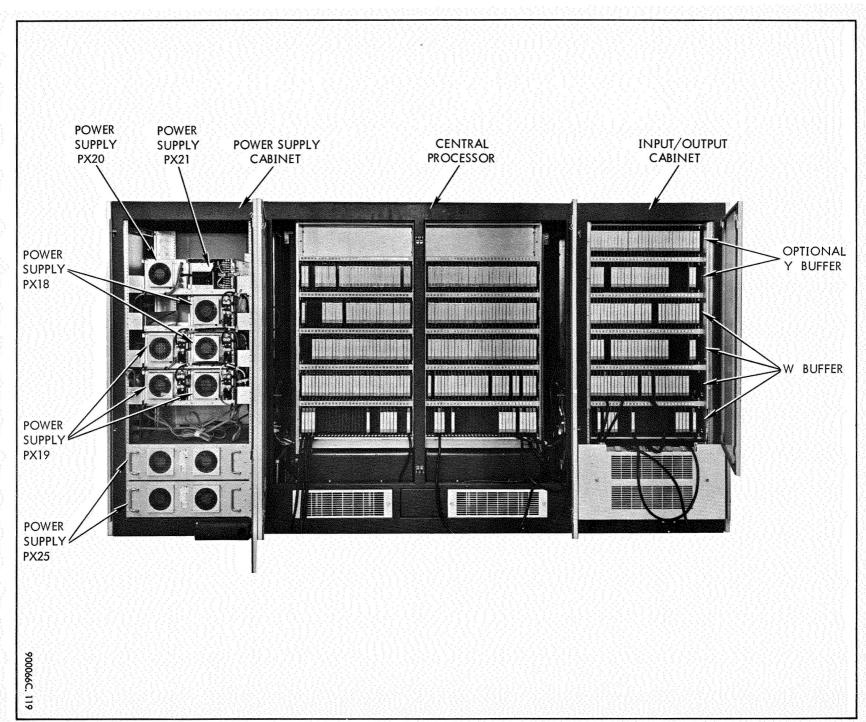

| 1-2    | Computer Model 930, Rear View                | 1-3  |

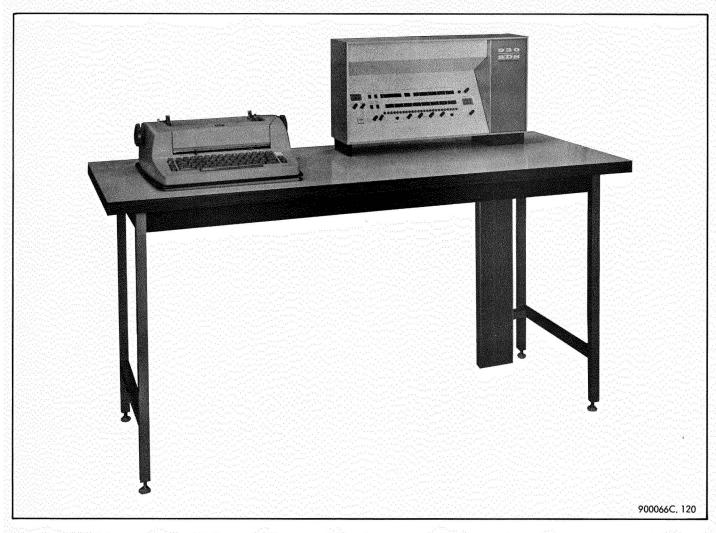

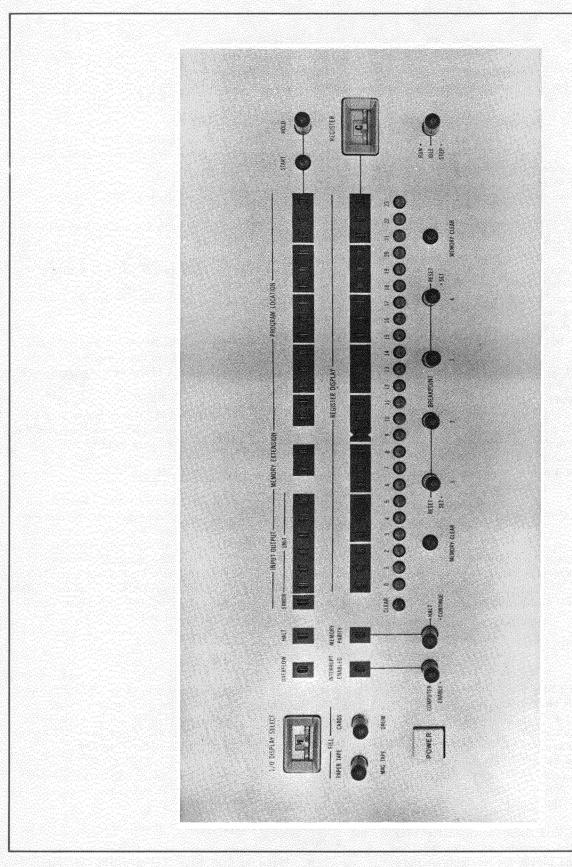

| 1-3    | Computer Model 930 Control Console           | 1-4  |

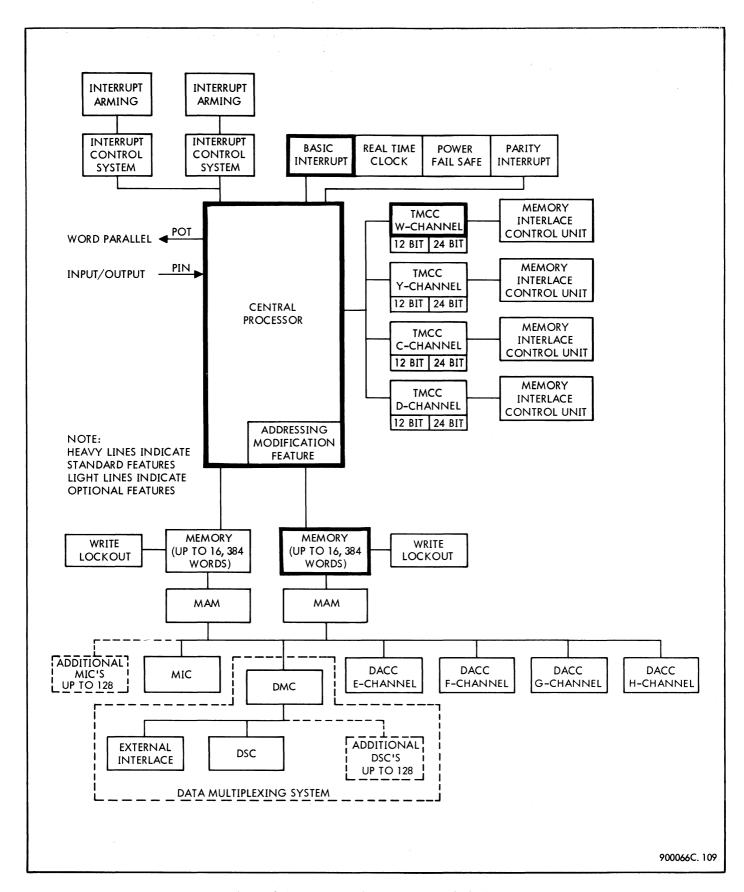

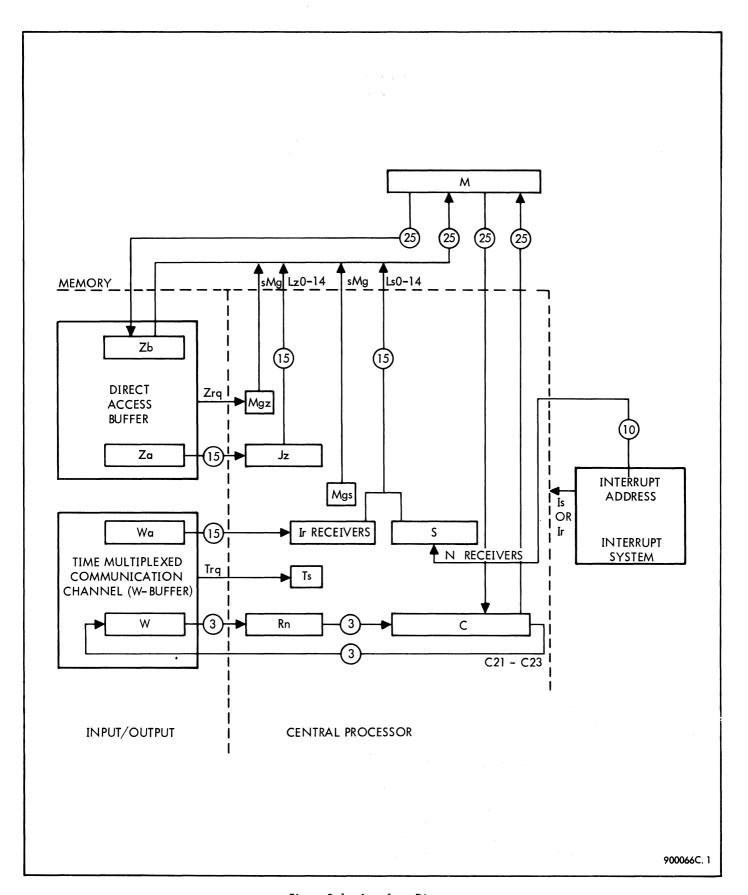

| 1-4    | Computer Model 930, Functional Block Diagram | 1-7  |

| 2-1    | Control Panel                                | 2-1  |

| 3-1    | Interface Diagram                            | 3-2  |

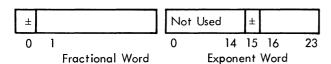

| 3-2    | Logic Symbol Diagram                         | 3–8  |

| 3-3    | Computer Registers, Block Diagram            | 3–9  |

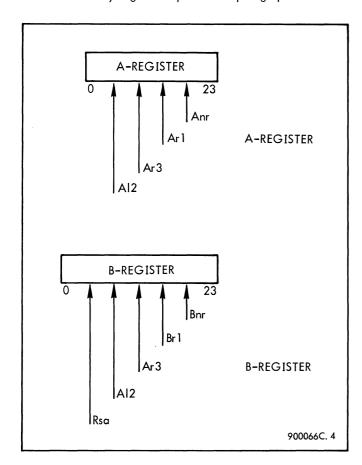

| 3-4    | A- and B-Register Enable Paths               | 3-11 |

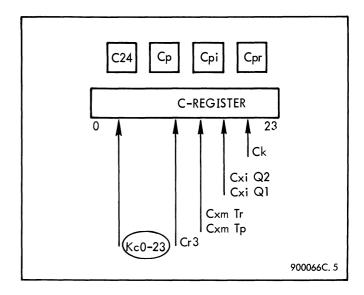

| 3-5    | C-Register Enable Paths                      | 3-11 |

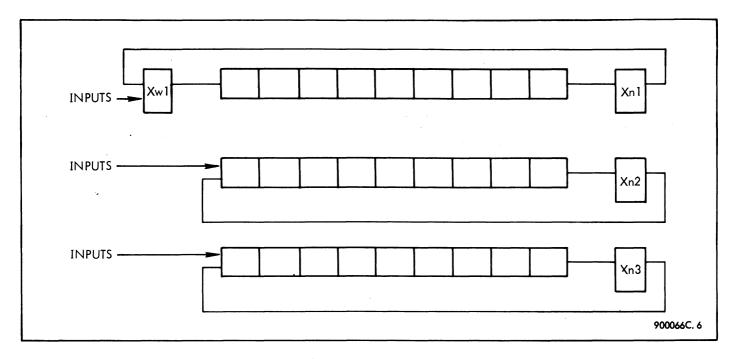

| 3-6    | Index Register                               | 3-12 |

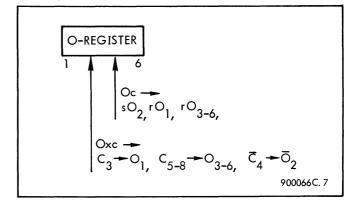

| 3-7    | O-Register Enable Paths                      | 3-12 |

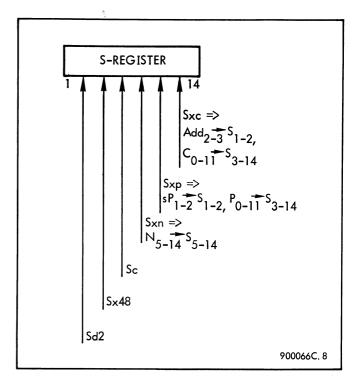

| 3-8    | S-Register Enable Paths                      | 3-12 |

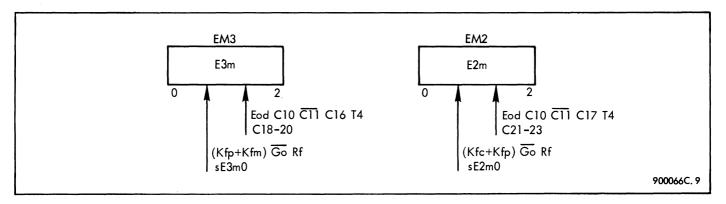

| 3-9    | Memory Extension Register Enable Paths       | 3-14 |

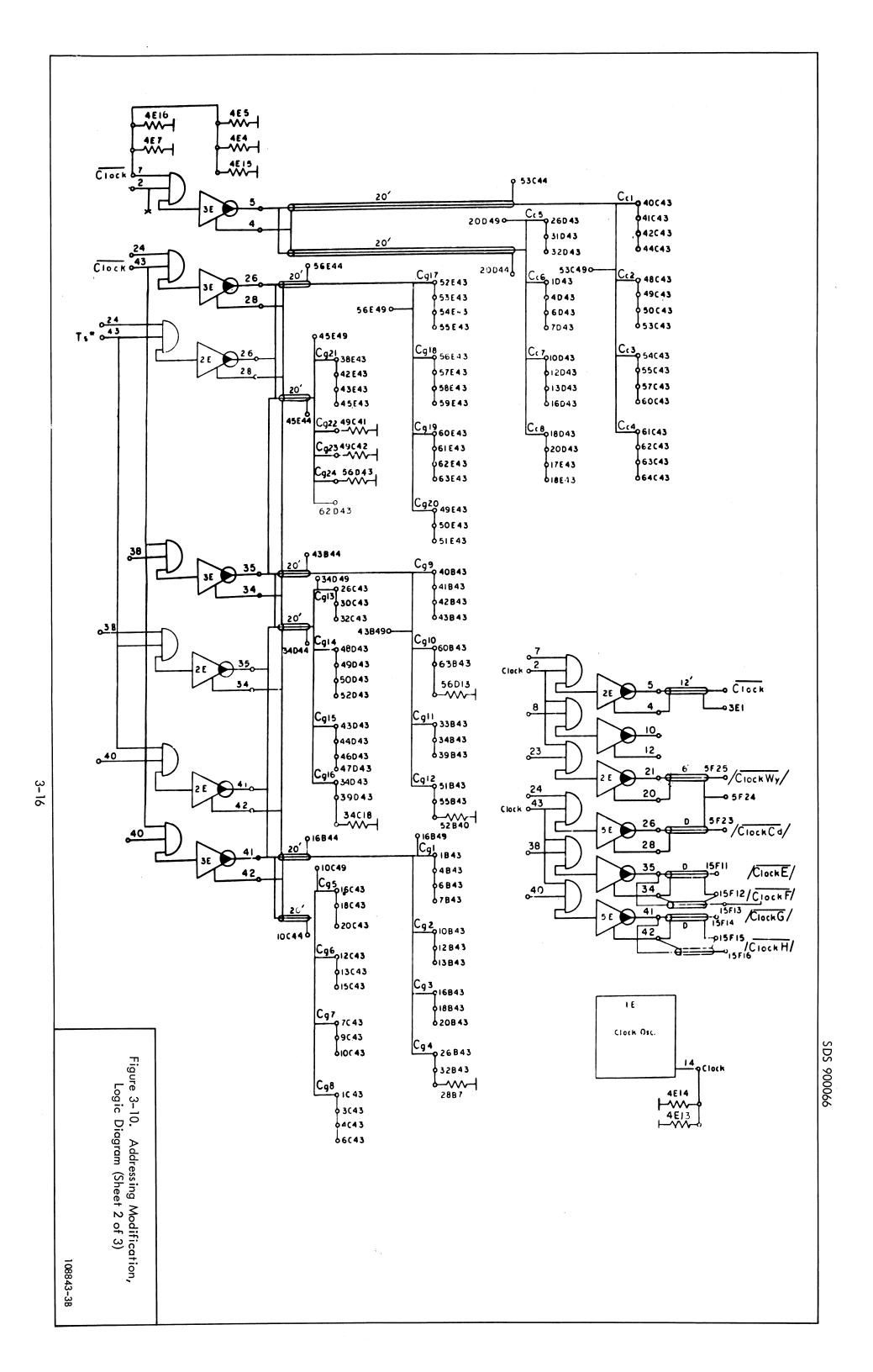

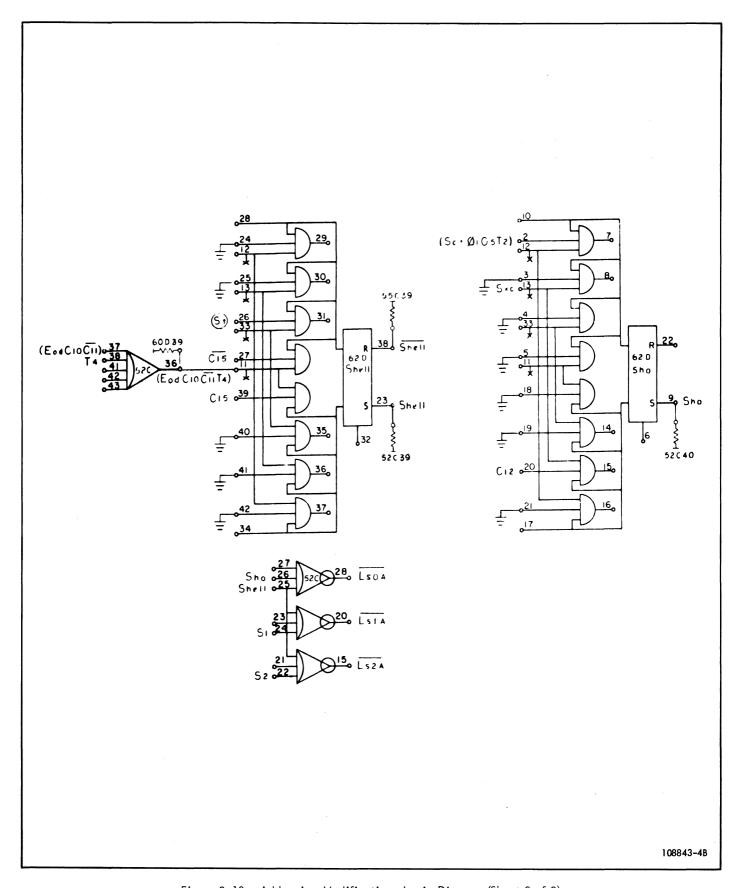

| 3-10   | Addressing Modification, Logic Diagram       | 3-15 |

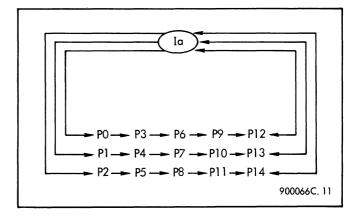

| 3-11   | P-Register Shift Operation                   | 3-18 |

| 3-11   |                                              | 3-10 |

| 3-12   | Right Shift Adder                            | 3-23 |

| 3-13   | Right Shift One, Simplified                  | 3-24 |

|        | Right Shift Three, Simplified Diagram        | 3-25 |

| 3-15   | Left Shift Two, Simplified Diagram           |      |

| 3-16   | Sign Detector, Functional Diagram            | 3-26 |

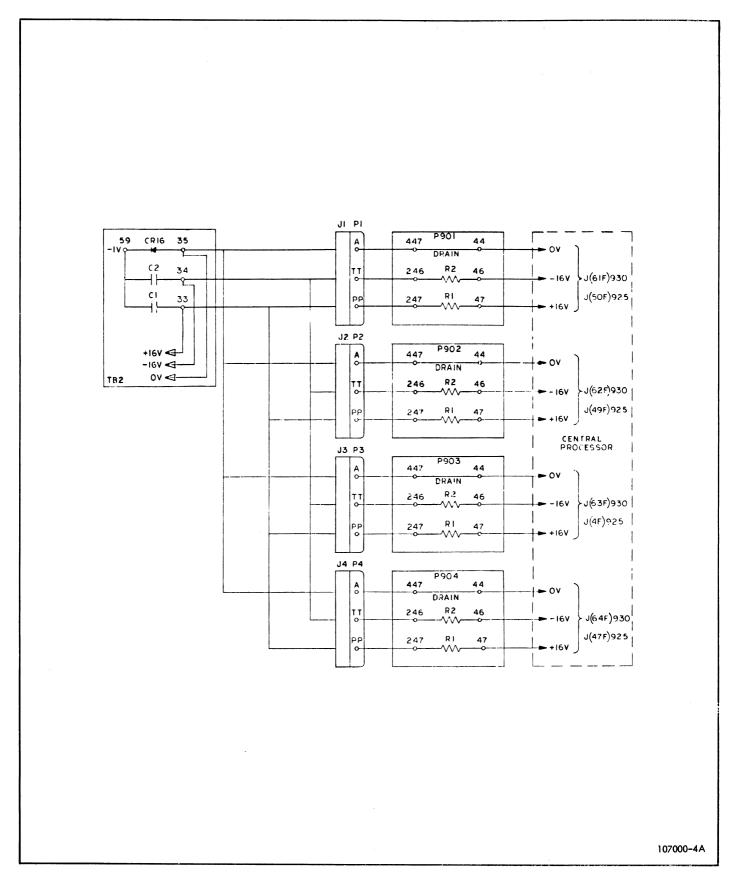

| 3-17   | Control Console, Schematic Diagram           | 3-31 |

| 3-18   | Fill Operation, Timing Diagram               | 3-37 |

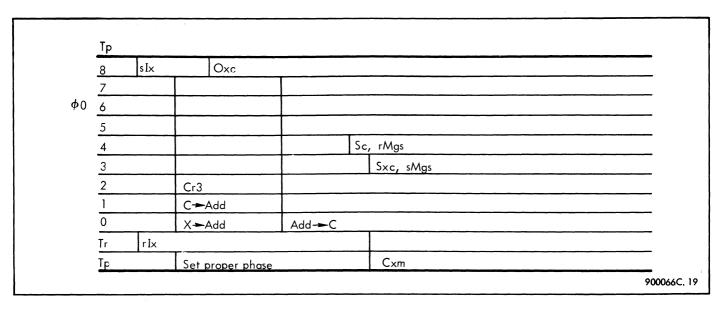

| 3-19   | Indexing, Timing Diagram                     | 3-45 |

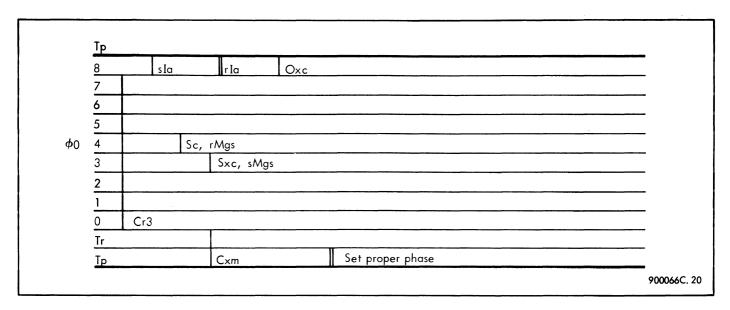

| 3-20   | Indirect Addressing, Timing Diagram          | 3-46 |

| 3-21   | Programmed Operator, Timing Diagram          | 3-46 |

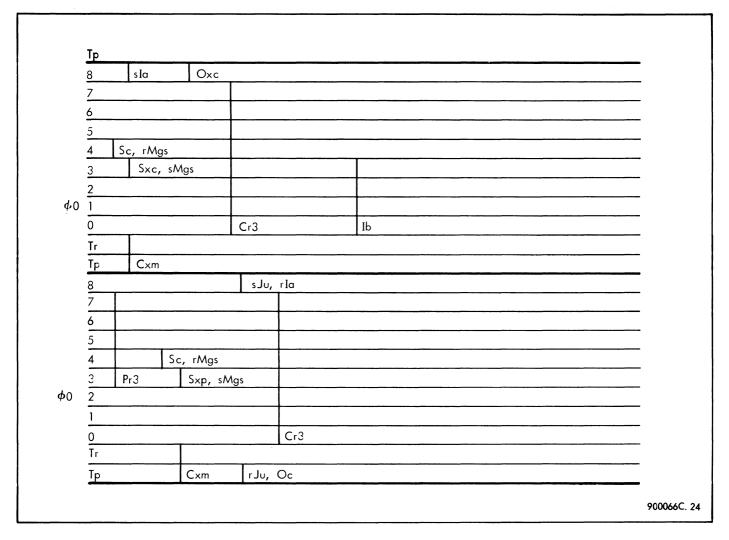

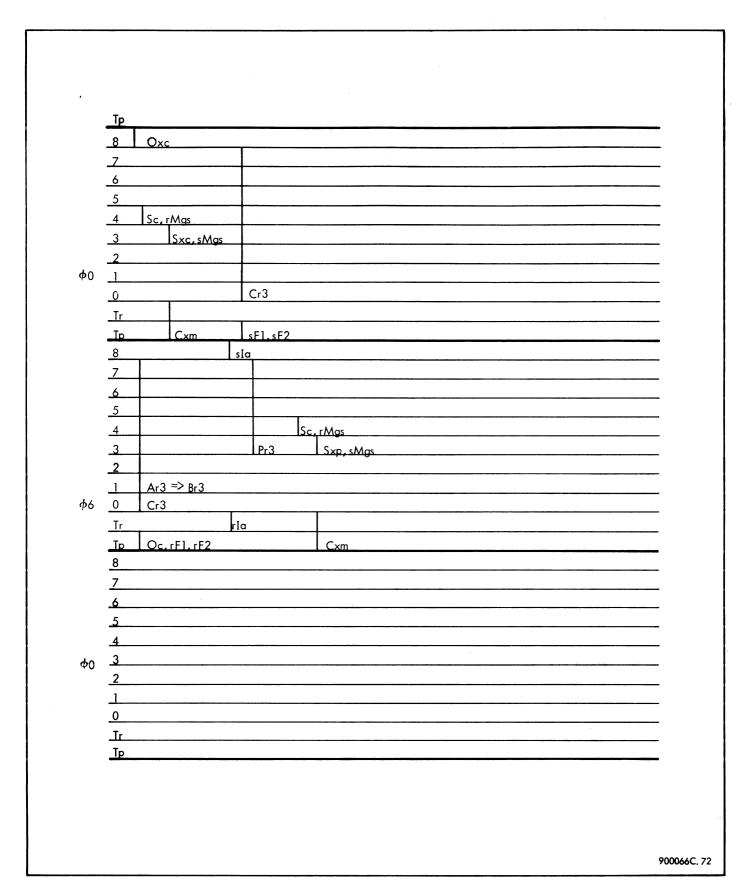

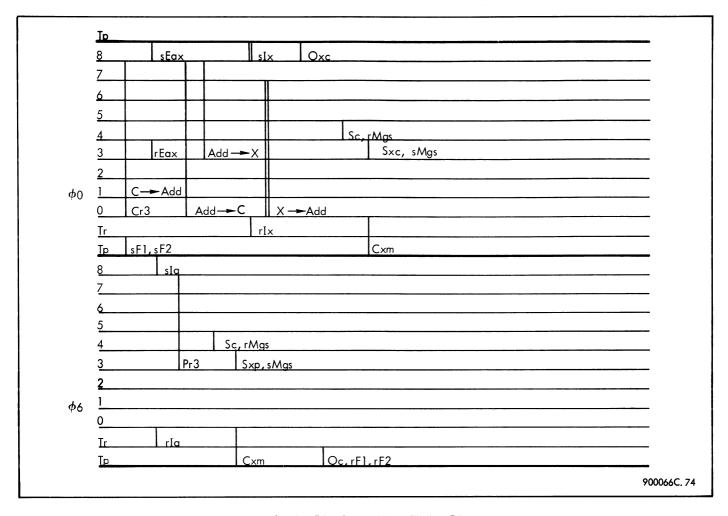

| 3-22   | HLT Instruction, Timing Diagram              | 3-47 |

| 3-23   | BRU Instruction, Timing Diagram              | 3-48 |

| 3-24   | BRU I Instruction, Timing Diagram            | 3-48 |

| 3-25   | EOM Instruction, Timing Diagram              | 3-49 |

| 3-26   | EOD Instruction, Timing Diagram              | 3-49 |

| 3-27   | MIW Instruction, Timing Diagram              | 3-51 |

| 3-28   | POT Instruction, Timing Diagram              | 3-52 |

| 3-29   | ETR Instruction, Timing Diagram              | 3-53 |

| 3-30   | MRG Instruction, Timing Diagram              | 3-54 |

| 3-31   | EOR Instruction, Timing Diagram              | 3-55 |

| 3-32   | NOP Instruction, Timing Diagram              | 3-56 |

| 3–33   | EXU Instruction, Timing Diagram              | 3-56 |

| 3-34   | WIM Instruction, Timing Diagram              | 3-58 |

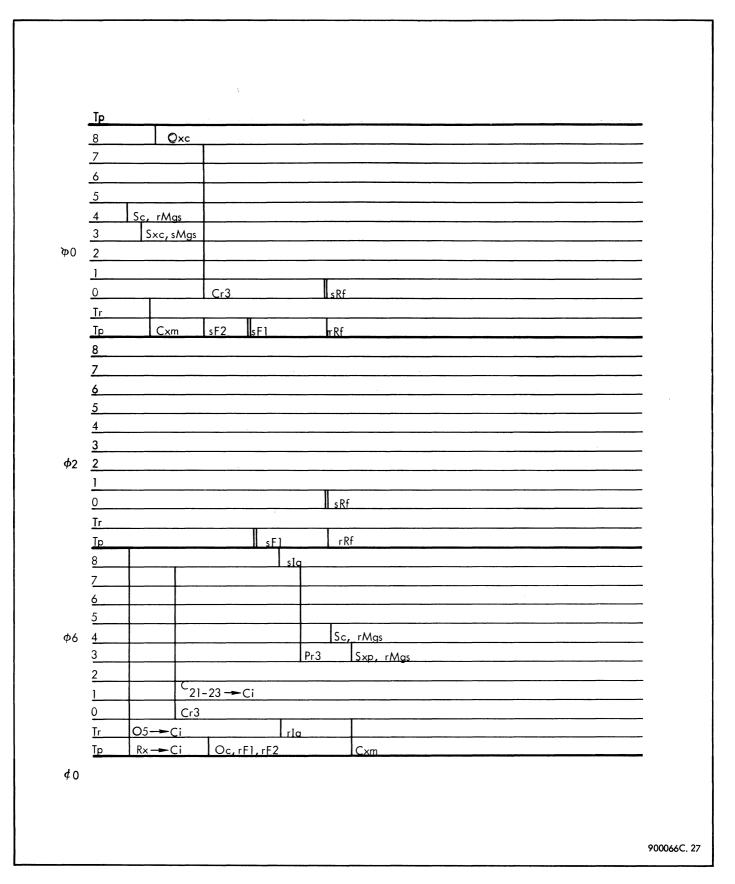

| 3–35   | PIN Instruction, Timing Diagram              | 3-60 |

| 3-36   | STA Instruction, Timing Diagram              | 3-62 |

| 3-37   | STB Instruction, Timing Diagram              | 3-64 |

| 3–38   | STX Instruction, Timing Diagram              | 3-65 |

| 3-39   | SKS Instruction, Timing Diagram              | 3-66 |

| 3-40   | BRX Instruction, Timing Diagram              | 3–68 |

| 3-41   | BRM Instruction, Timing Diagram              | 3-69 |

| 3-42   | RCH Instruction, Timing Diagram              | 3-70 |

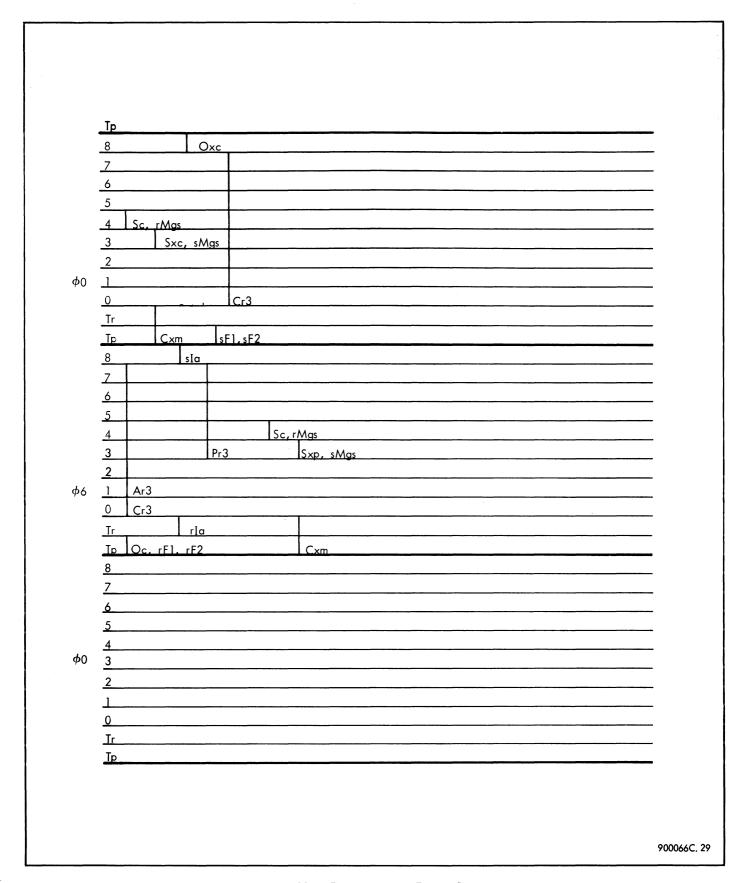

| 3-43   | SKE Instruction, Timing Diagram              | 3-74 |

| 3-44   | BRR Instruction, Timing Diagram              | 3-75 |

| 3-45   | SKB Instruction, Timing Diagram              | 3–76 |

| 3-46   | SKN Instruction, Timing Diagram              | 3-78 |

| 3-47   | SUB Instruction, Timing Diagram              | 3-79 |

| 3-48   | ADD Instruction, Timing Diagram              | 3-81 |

| 3-49   | SUC Instruction, Timing Diagram              | 3-82 |

| 3-50   | ADC Instruction, Timing Diagram              | 3-84 |

## LIST OF ILLUSTRATIONS (Cont.)

| igure        | Title                                                | Page                   |

|--------------|------------------------------------------------------|------------------------|

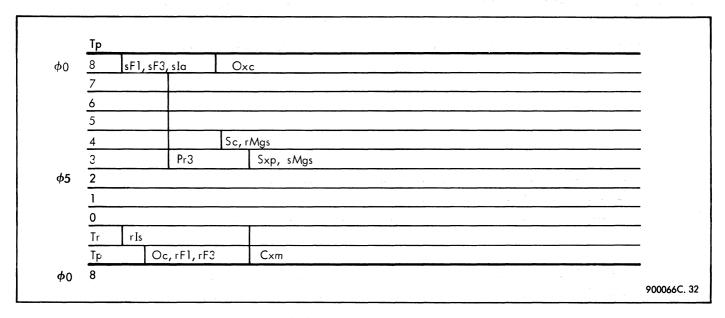

| 3-51         | SKR Instruction, Timing Diagram                      | 3-85                   |

| 3-52         | MIN Instruction, Timing Diagram                      | 3-87                   |

| 3-53         | XMA Instruction, Timing Diagram                      | 3-88                   |

| 3-54         | ADM Instruction, Timing Diagram                      | 3-90                   |

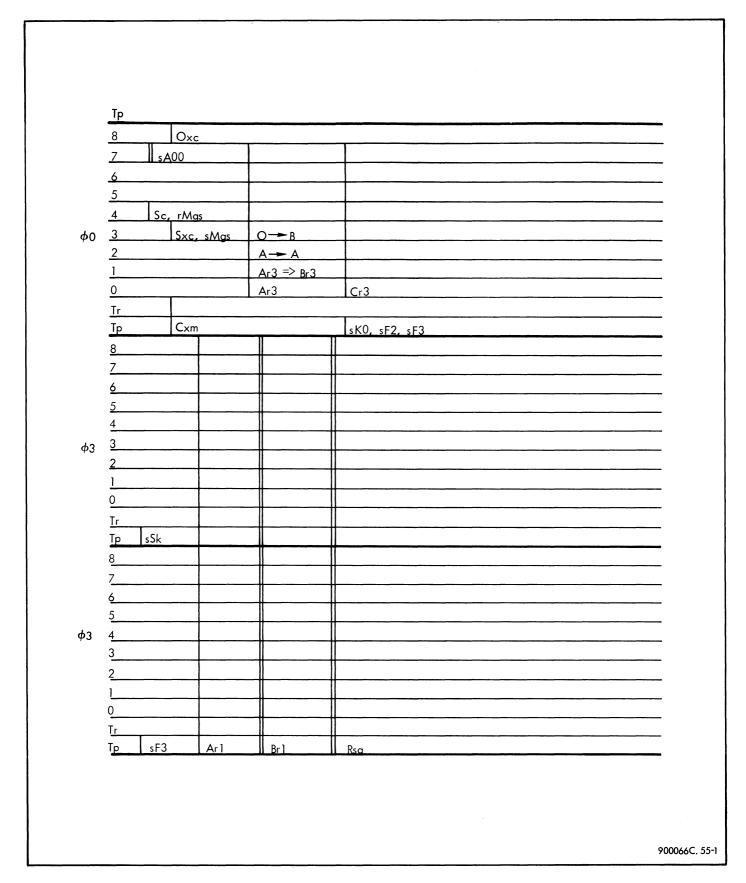

| 3-55         | MUL Instruction, Timing Diagram                      | 3-91                   |

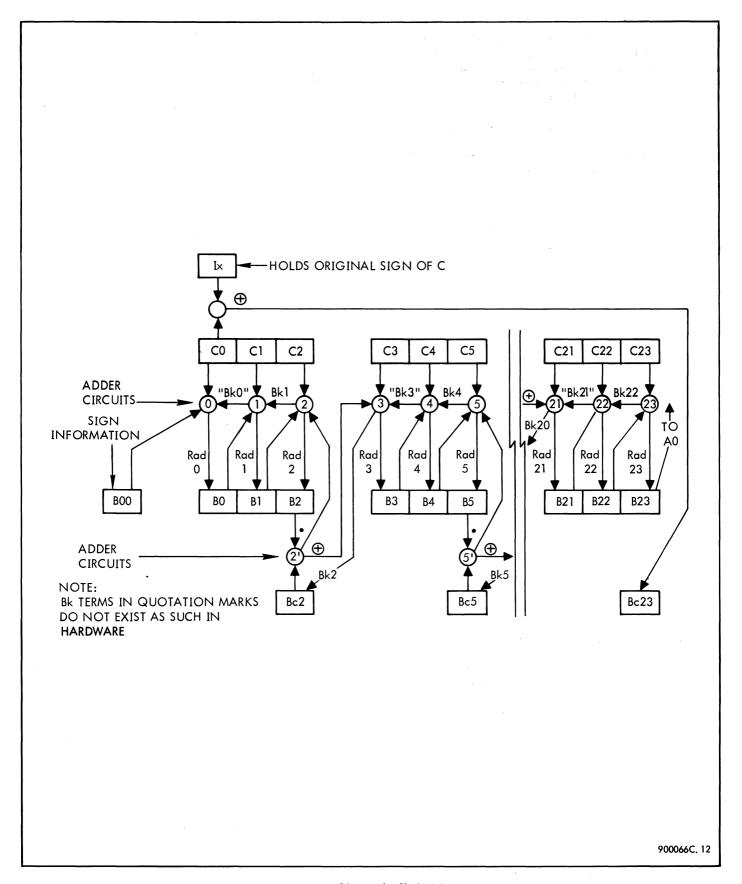

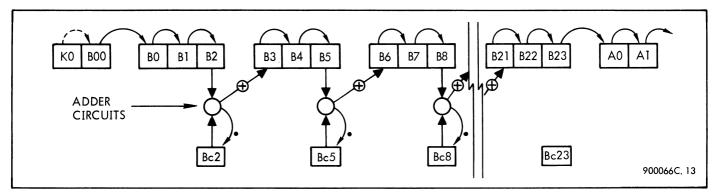

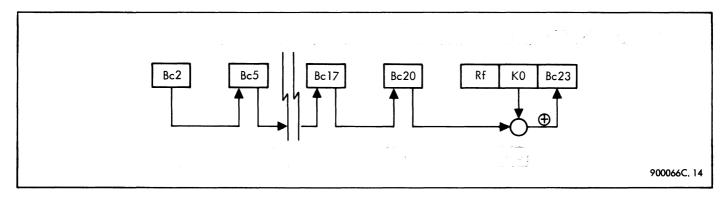

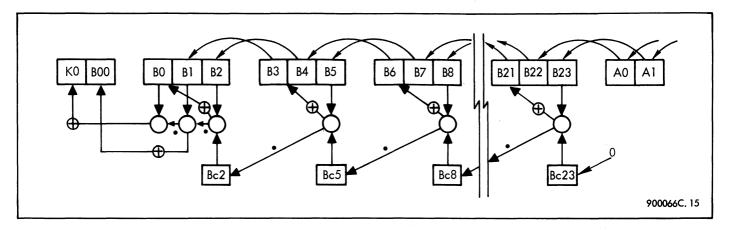

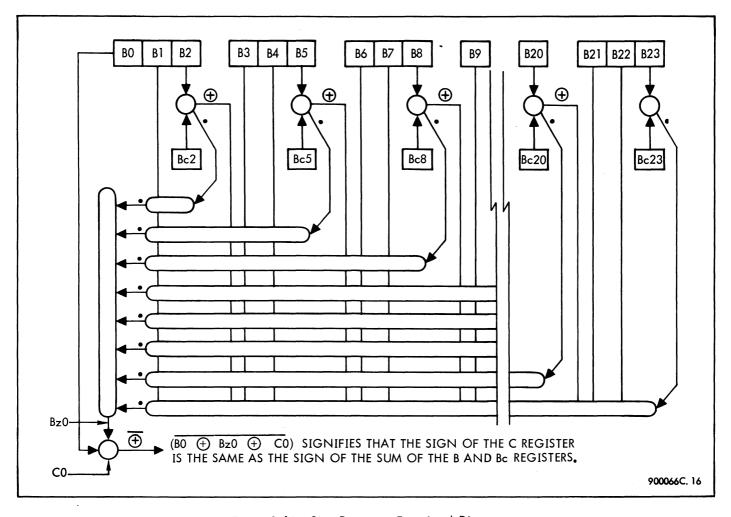

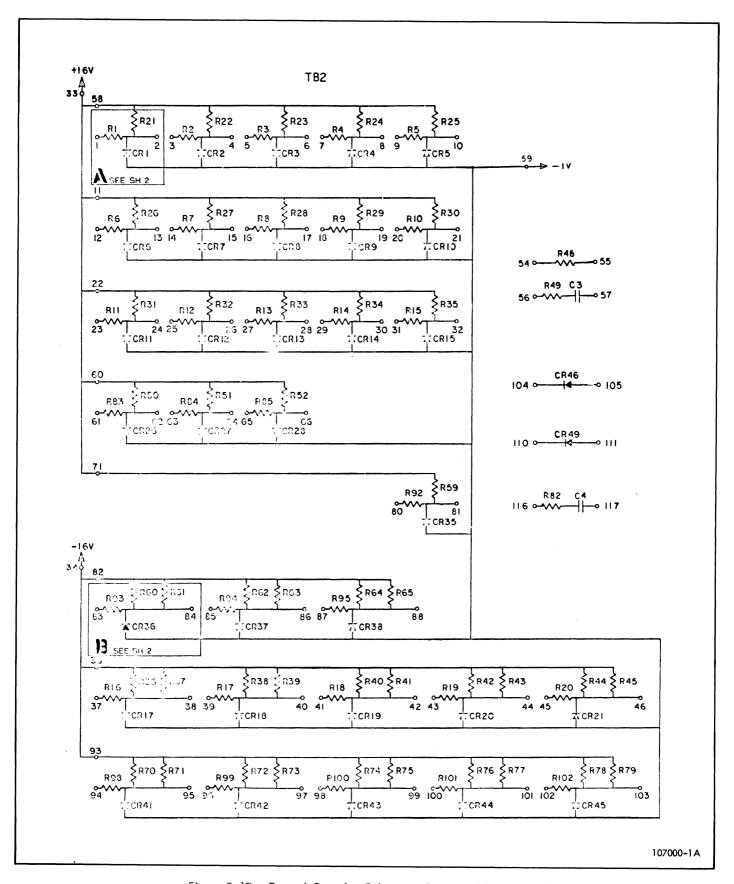

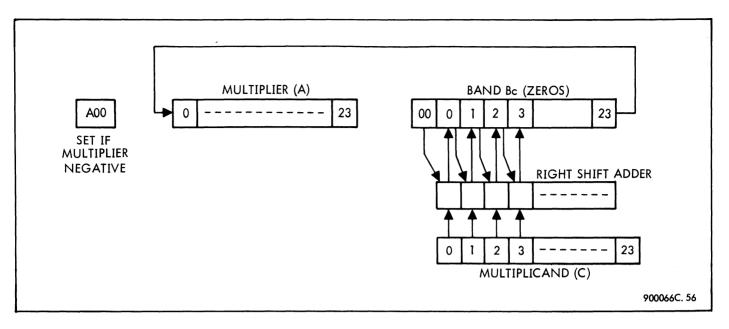

| 3-56         | Multiplication, Block Diagram                        | 3-93                   |

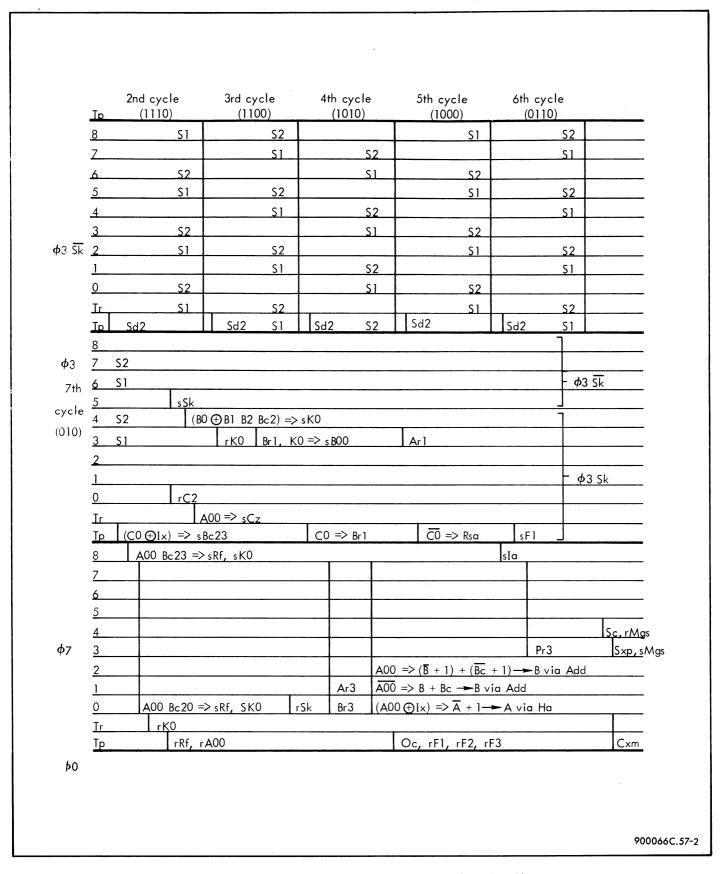

| 3-57         | DIV Instruction, Timing Diagram                      | 3-95                   |

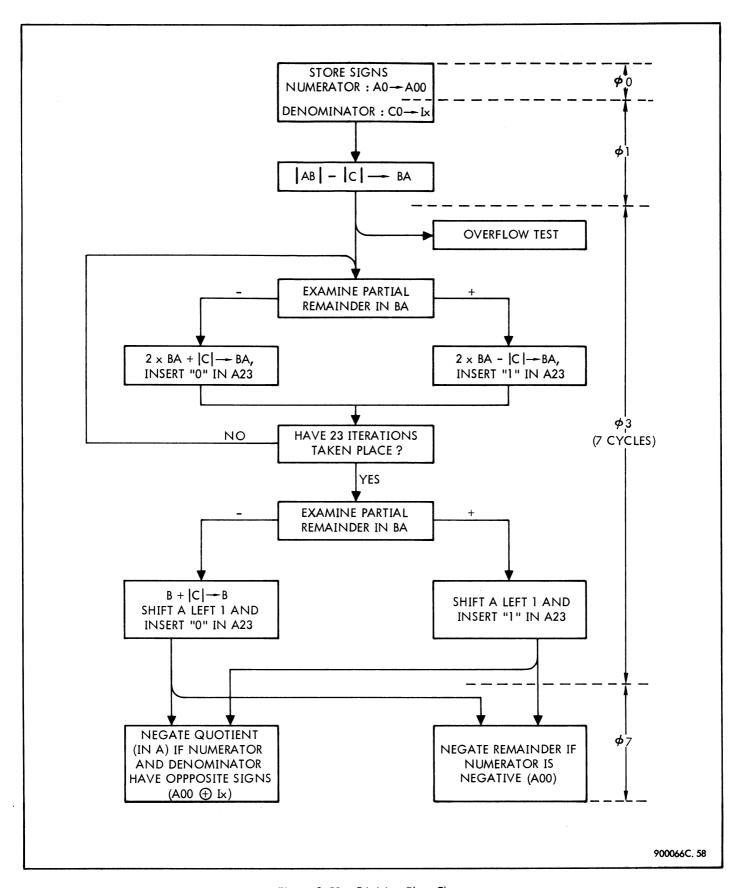

| 3-58         | Division Flow Chart                                  | 3-98                   |

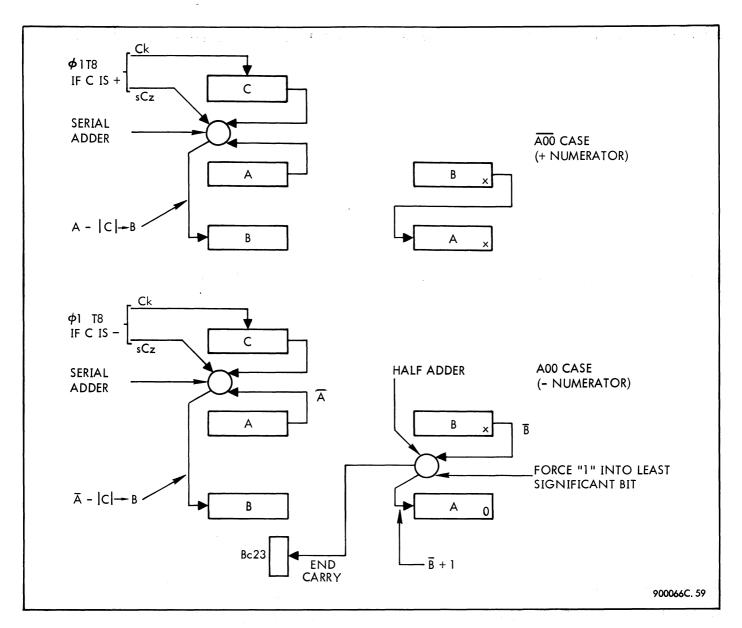

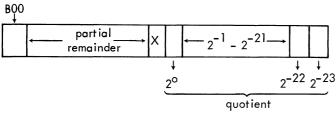

| 3-59         | First Subtract Operation in Divide, Block Diagram    | 3-99                   |

| 3-60         | Shift Series, Timing Diagram                         | 3-103                  |

| 3-61         | Shift Series Codes and Functions                     | 3-104                  |

| 3-62         | S-Register States                                    | 3-106                  |

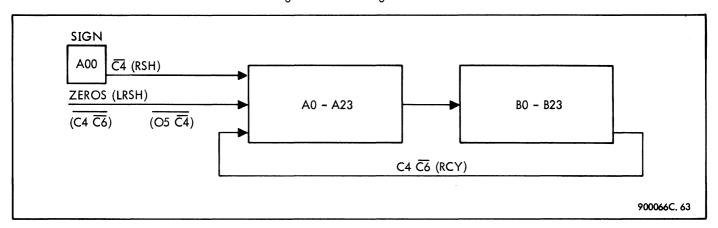

| 3-63         | Right Shift Options                                  | 3-106                  |

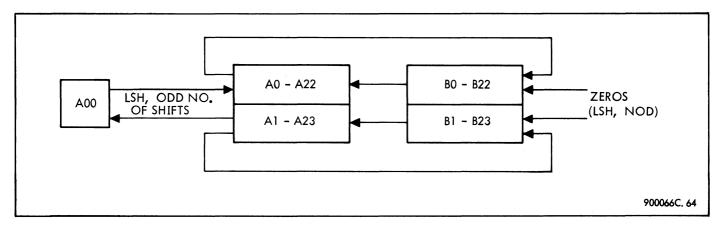

| 3-64         | Left Shift Options                                   | 3-106                  |

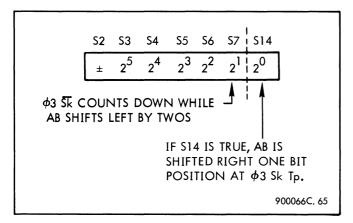

| 3-65         | Organization of S-Register for Normalize Shift Count | 3-100                  |

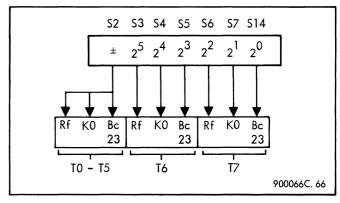

| 3-66         | Tally Transfer from S. Posister                      | 3-107                  |

| 3-67         | Tally Transfer from S-Register                       | 3-107                  |

| 3-68         | SKM Instruction, Timing Diagram                      | 3-107                  |

| 3-69         | LDX Instruction, Timing Diagram                      | 3-111                  |

| 3-70         | SKA Instruction, Timing Diagram                      |                        |

| 3-70         | SKG Instruction, Timing Diagram                      | 3-113<br>3-114         |

| 3-71         | SKD Instruction, Timing Diagram                      |                        |

| 3-72         | LDB Instruction, Timing Diagram                      | 3-11 <i>6</i><br>3-117 |

| 3-73<br>3-74 | LDA Instruction, Timing Diagram                      |                        |

| 3-74         | EAX Instruction, Timing Diagram                      | 3-118                  |

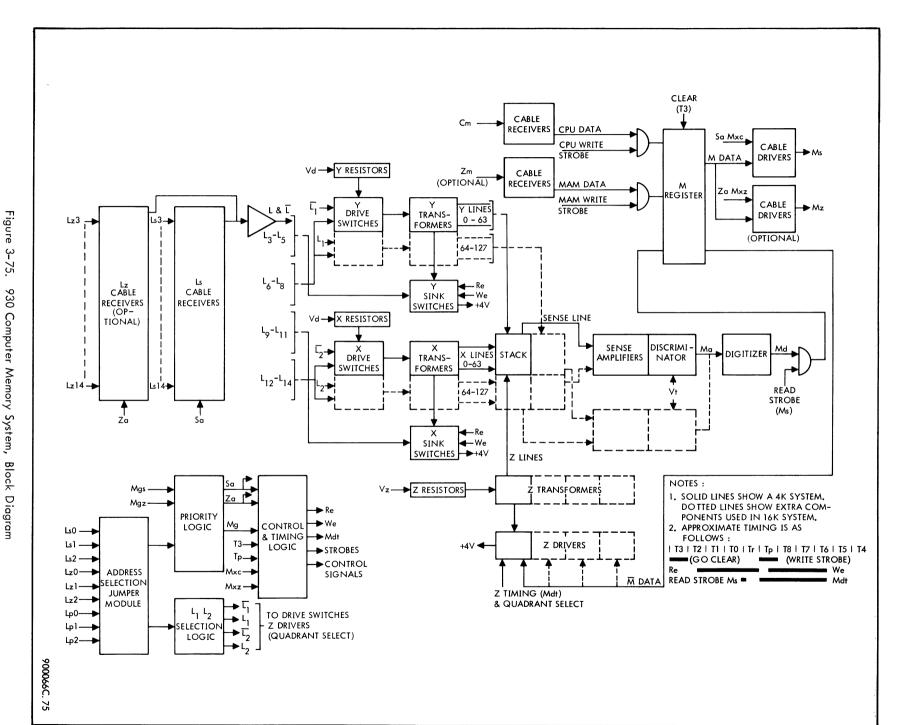

| 3-75<br>3-76 | 930 Computer Memory System, Block Diagram            | 3-119                  |

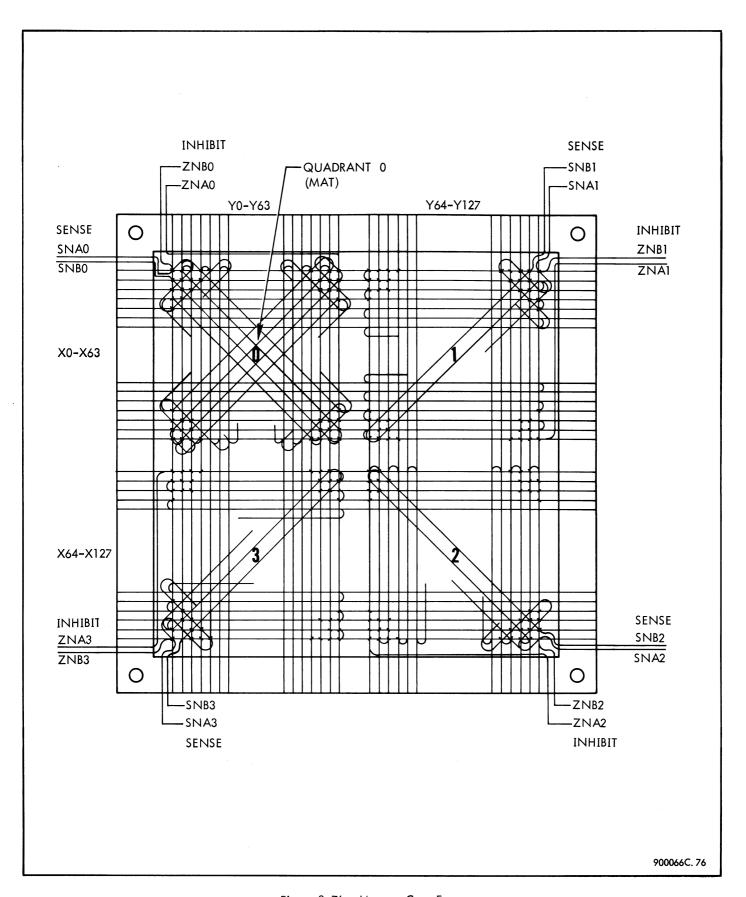

| 3-76<br>3-77 | Memory Core Frame                                    | 3-120                  |

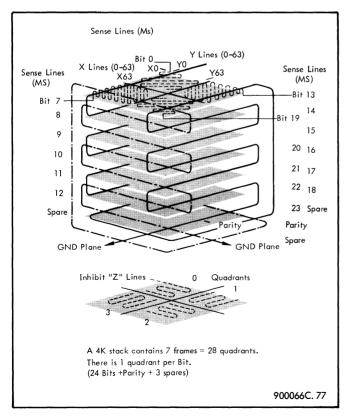

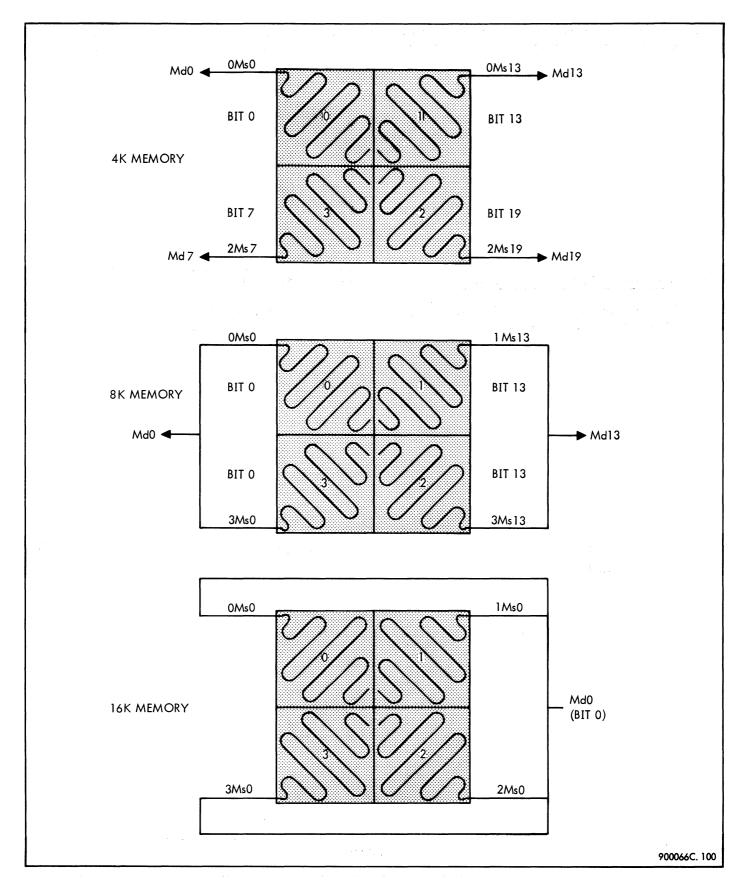

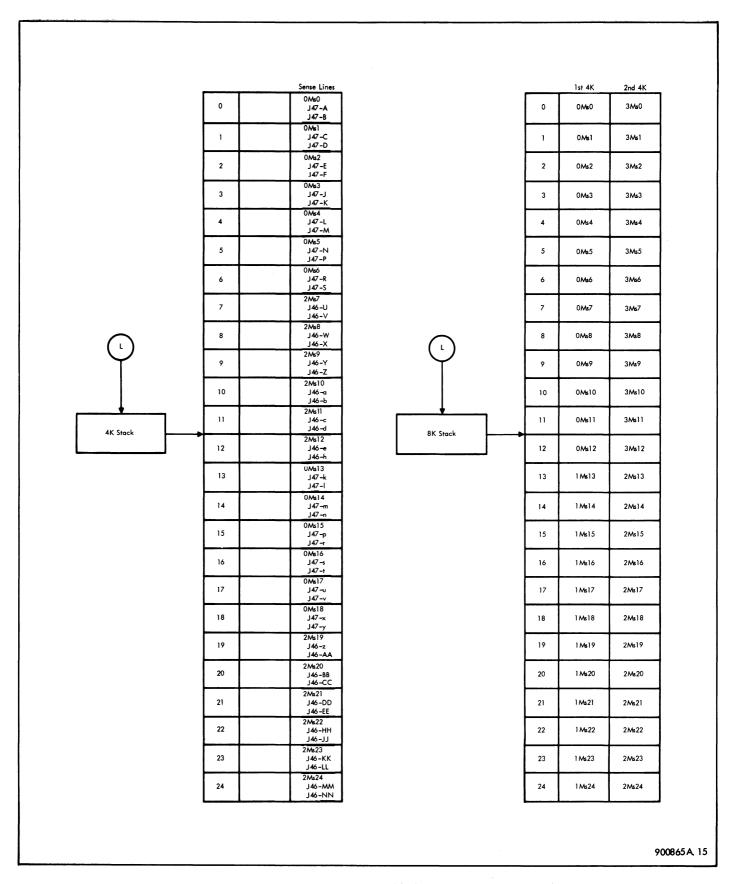

| 3-77<br>3-78 | 4K Stack Layout                                      | 3-121<br>3-122         |

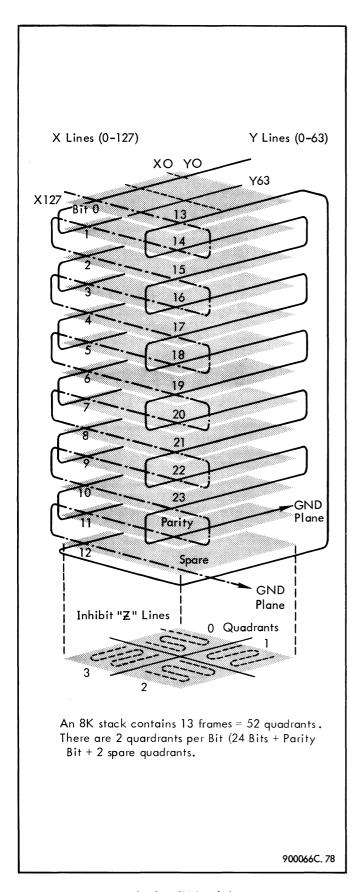

| 3-78         | 8K Stack Layout                                      |                        |

|              | 16K Stack Layout                                     | 3-122                  |

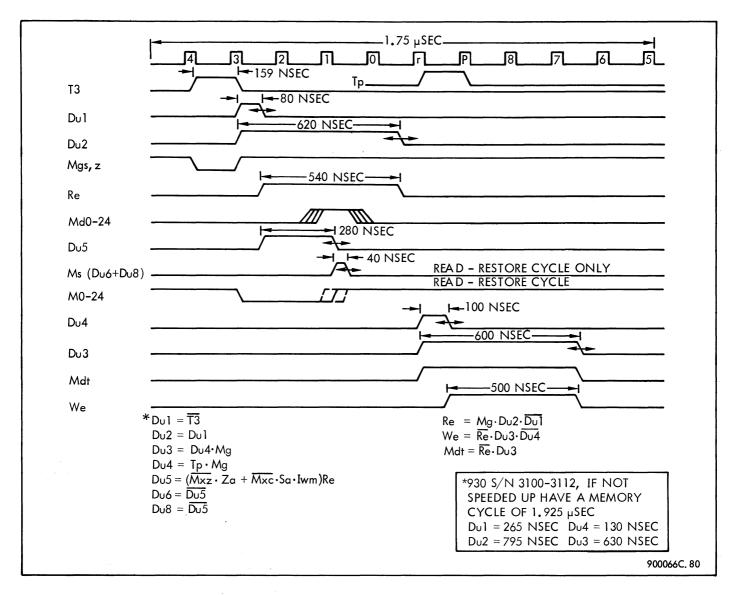

| 3-80         | Memory Cycle Timing                                  | 3-123                  |

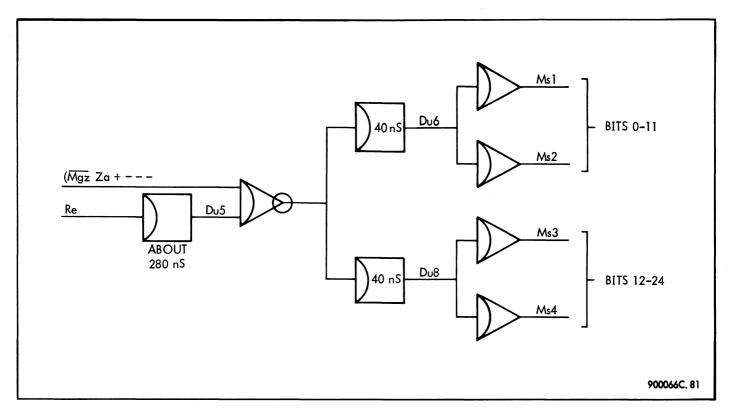

| 3-81         | Simultaneous Strobes                                 | 3-124                  |

| 3-82         | Staggered Strobes                                    | 3-124                  |

| 3-83         | X Transformer Decoding Matrix                        | 3-128                  |

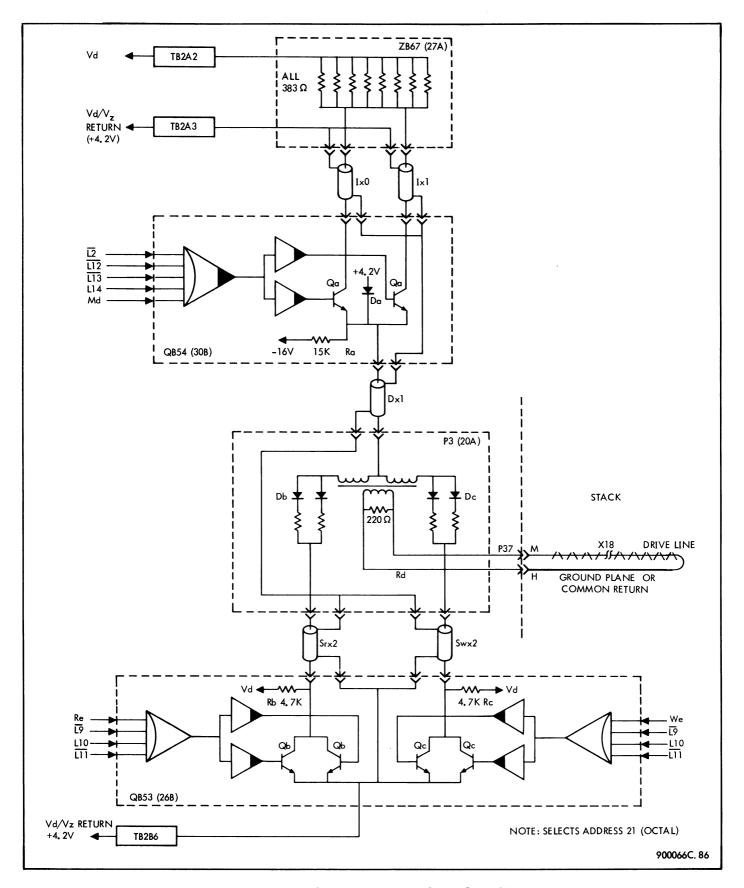

| 3-84         | Single-Core Drive Line Selection                     | 3-130                  |

| 3-85         | Address Decoding for 4,096 Words                     | 3-131                  |

| 3-86         | Selection Circuits for One X Drive Line              | 3-132                  |

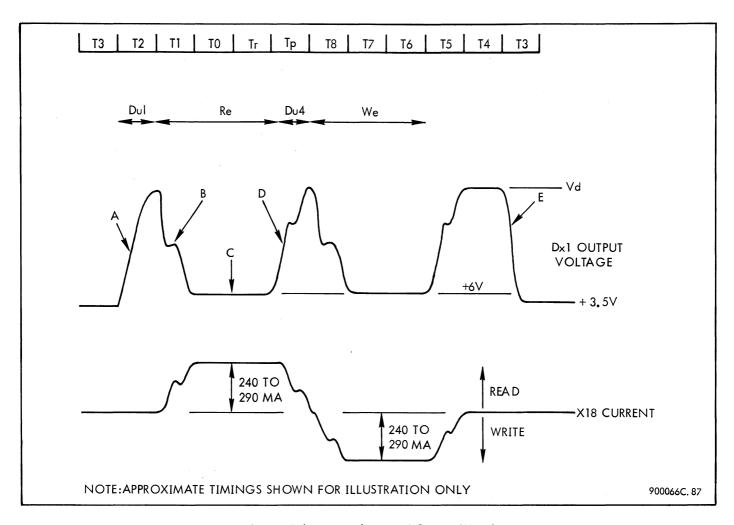

| 3-87         | Selection Voltage and Current Waveforms              | 3-133                  |

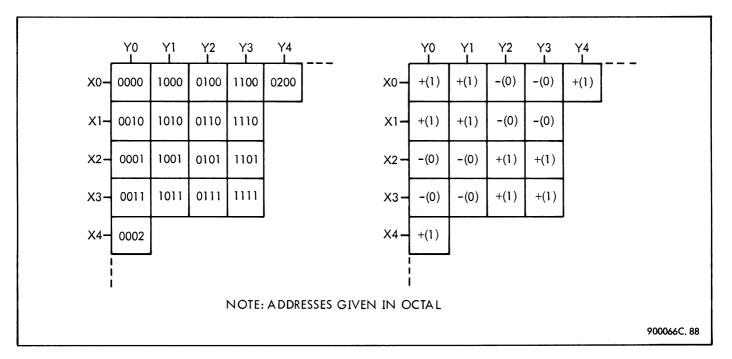

| 3-88         | Relationship of Address and Stack Location           | 3-134                  |

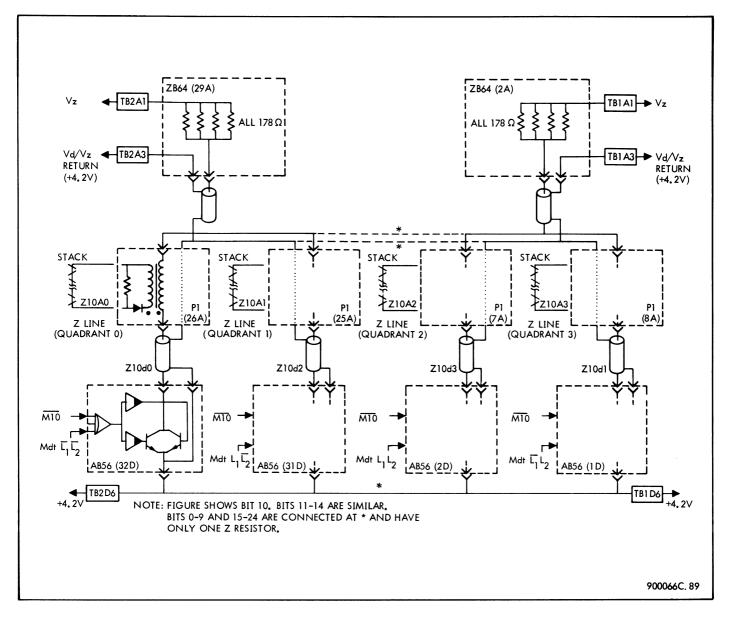

| 3-89         | Inhibiting System, 16K Memory                        | 3-136                  |

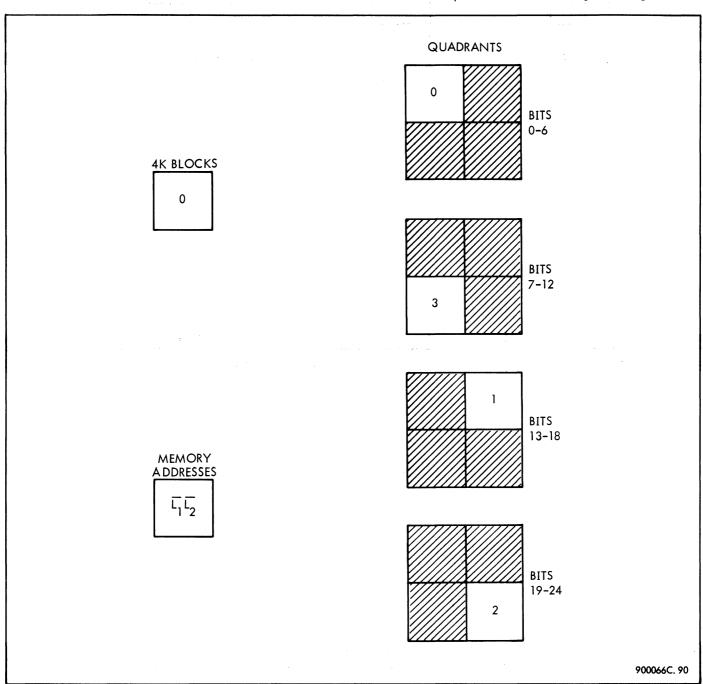

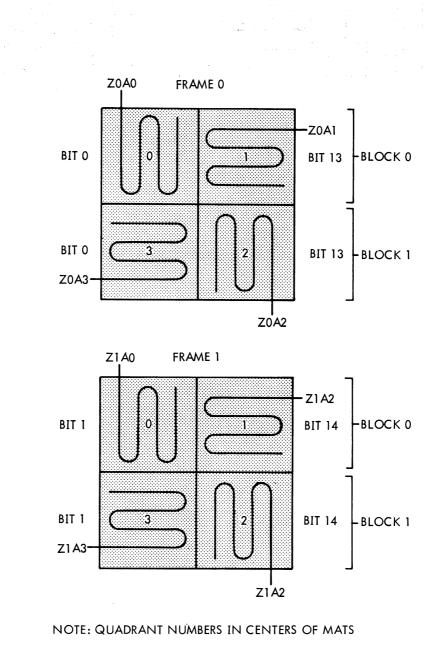

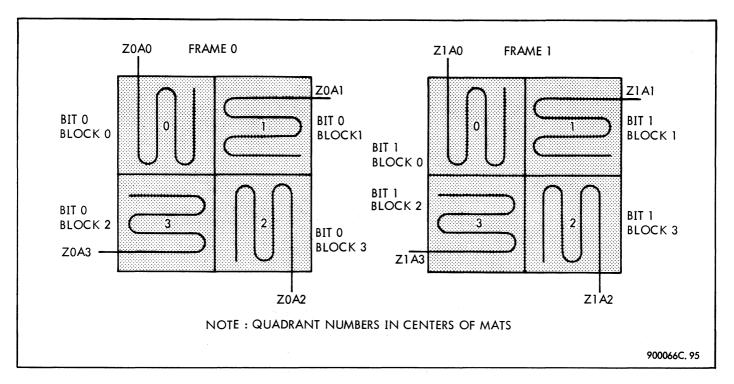

| 3-90         | Blocks and Quadrants, 4K Memory                      | 3-137                  |

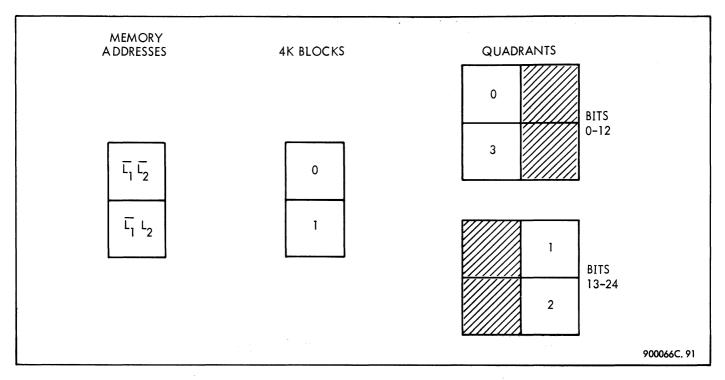

| 3-91         | Blocks and Quadrants, 8K Memory                      | 3-138                  |

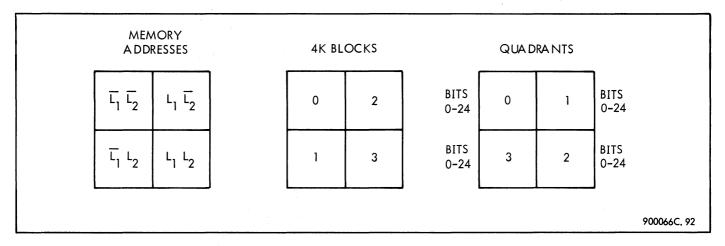

| 3-92         | Blocks and Quadrants, 16K Memory                     | 3-138                  |

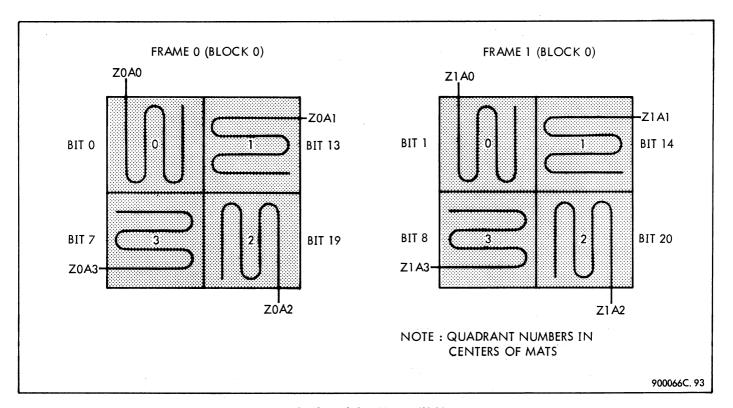

| 3-93         | Inhibit Lines, 4K Memory                             | 3-140                  |

| 3-94         | Inhibit Lines, 8K Memory                             | 3-141                  |

| 3-95         | Inhibit Lines, 16K Memory                            | 3-142                  |

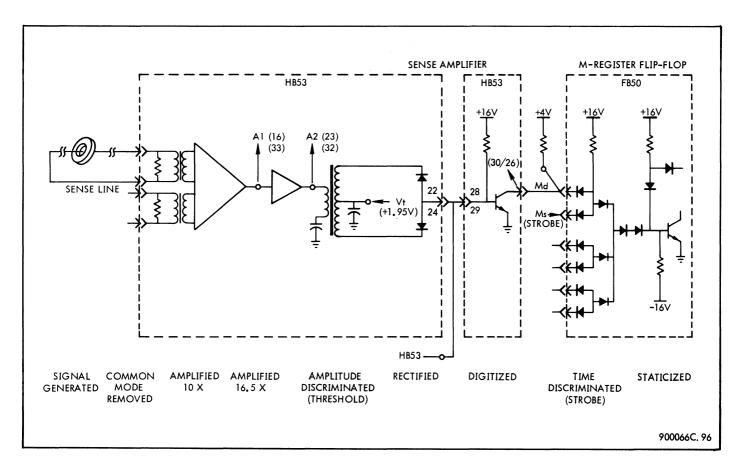

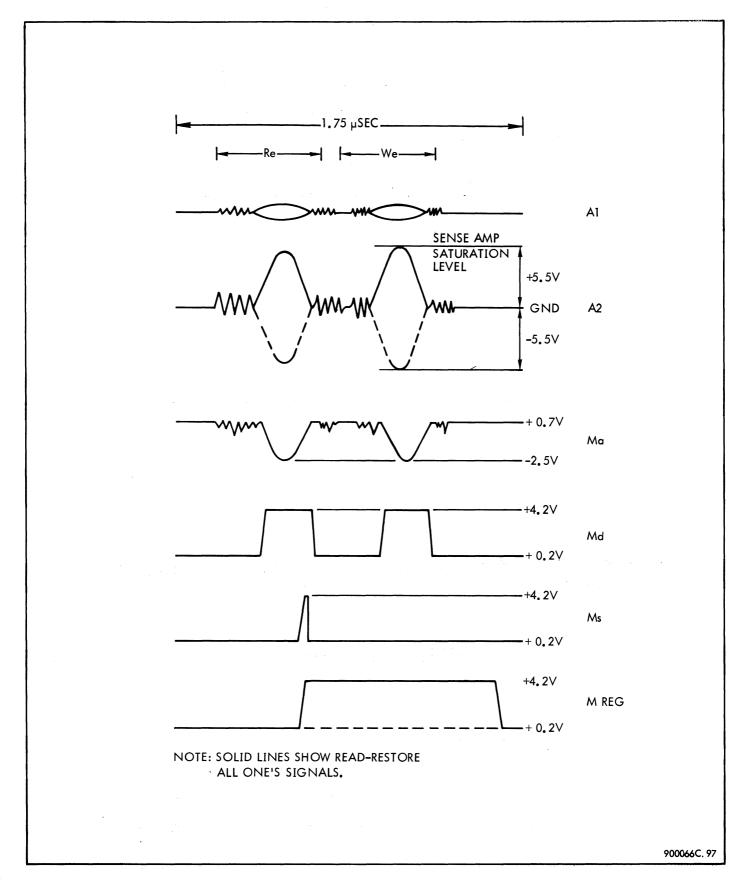

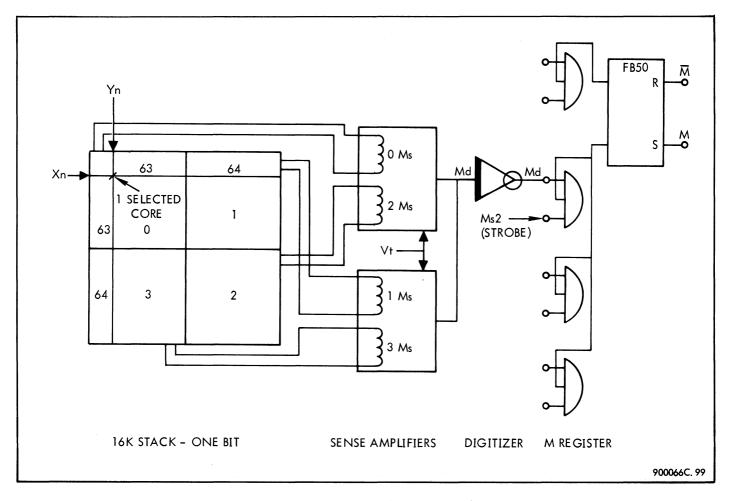

| 3-96         | Sensing System                                       | 3-142                  |

| 3-97         | Sensing System Waveforms                             | 3-143                  |

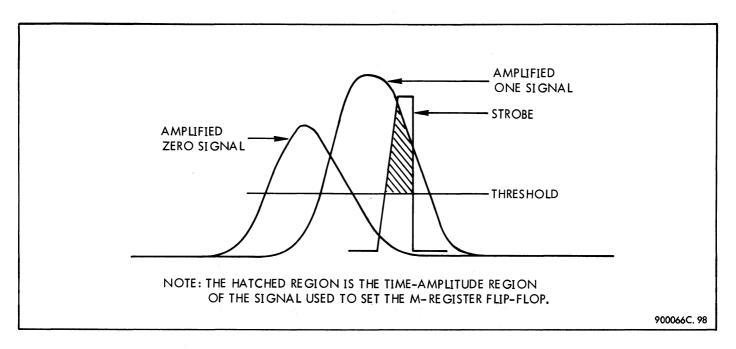

| 3-98         | Read Signal Discrimination                           | 3-144                  |

| 3-99         | 16K Sensing System                                   | 3-144                  |

| 3-100        | Sense Windings, Frame 0 for All Memories             | 3-145                  |

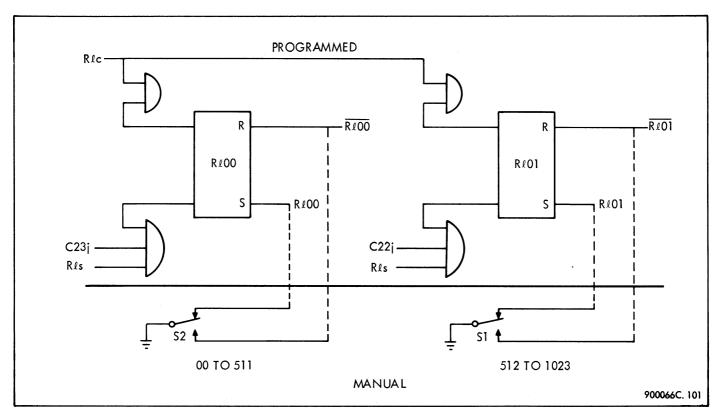

| 3-101        | Write Lockout Register (Two Bits)                    | 3-146                  |

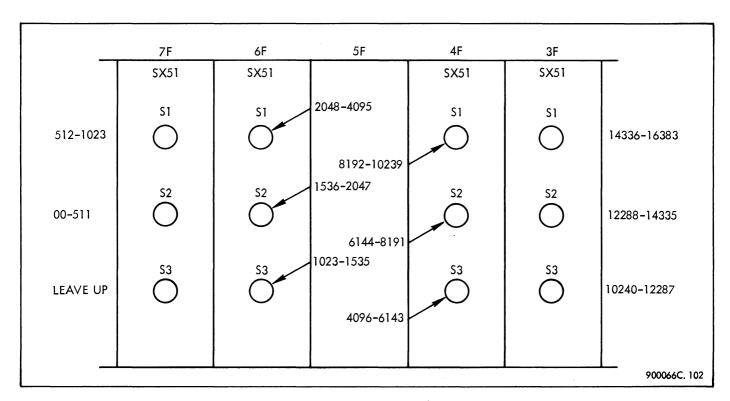

| 3-102        | Write Lockout Switches                               | 3-148                  |

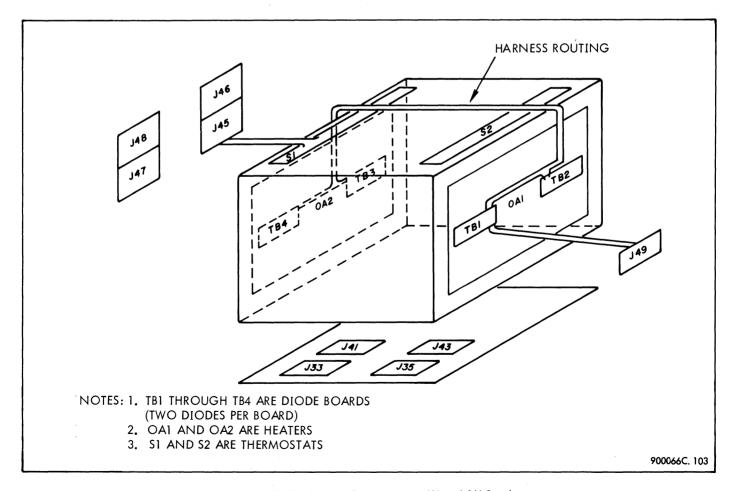

| 3–103        | Heater Components, 4K and 8K Stacks                  | 3-149                  |

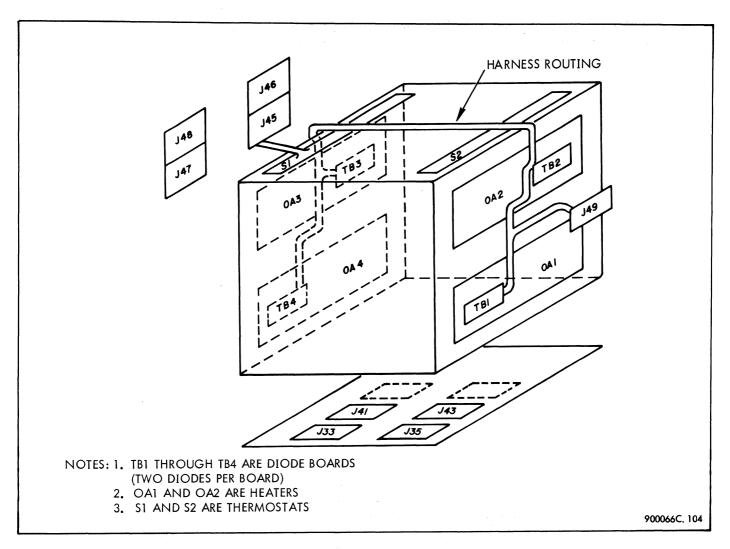

| 3-104        | Heater Components, 16K Stack                         | 3-150                  |

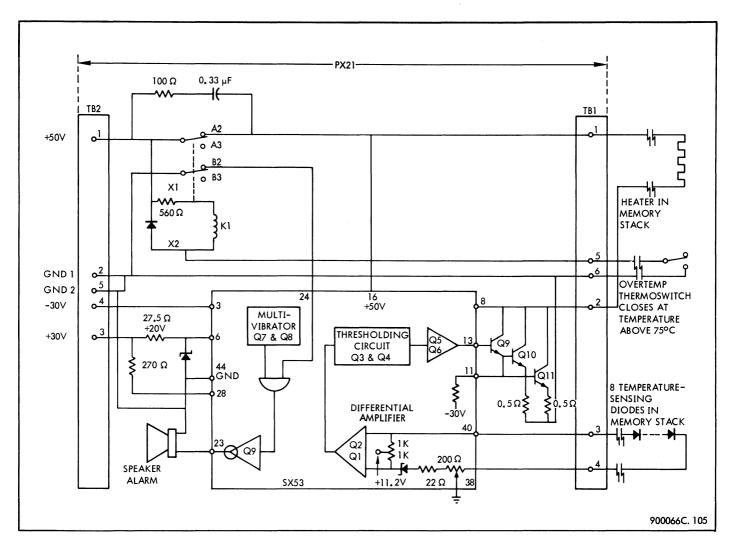

| 3-105        | Memory Heater Regulator                              | 3-151                  |

## LIST OF ILLUSTRATIONS (Cont.)

| Figure | Title                                               | Page  |

|--------|-----------------------------------------------------|-------|

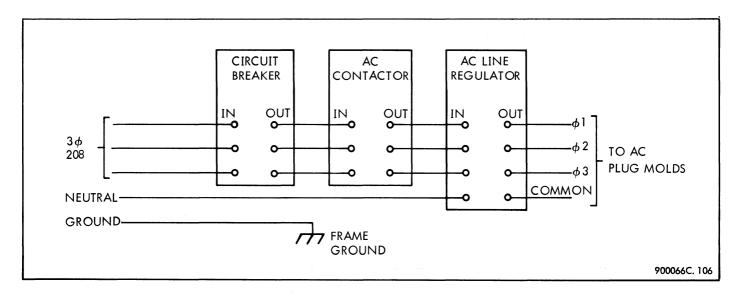

| 3-106  | AC Power Distribution                               | 3-151 |

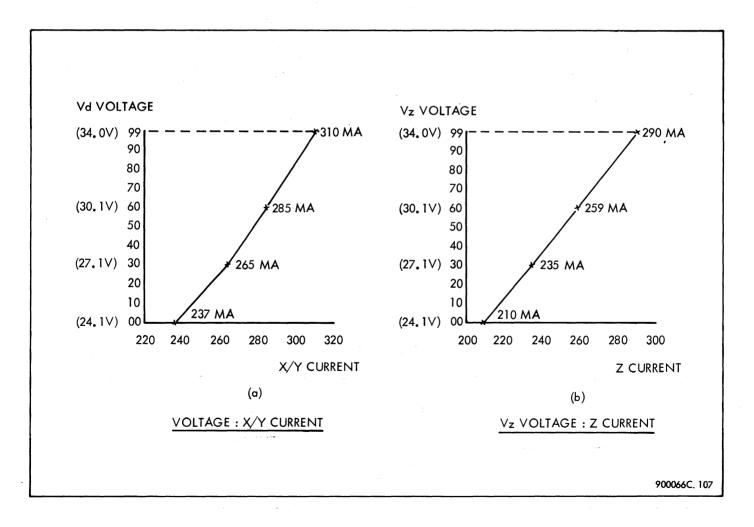

| 3-107  | Drive Voltage-Current Relationships                 | 3-152 |

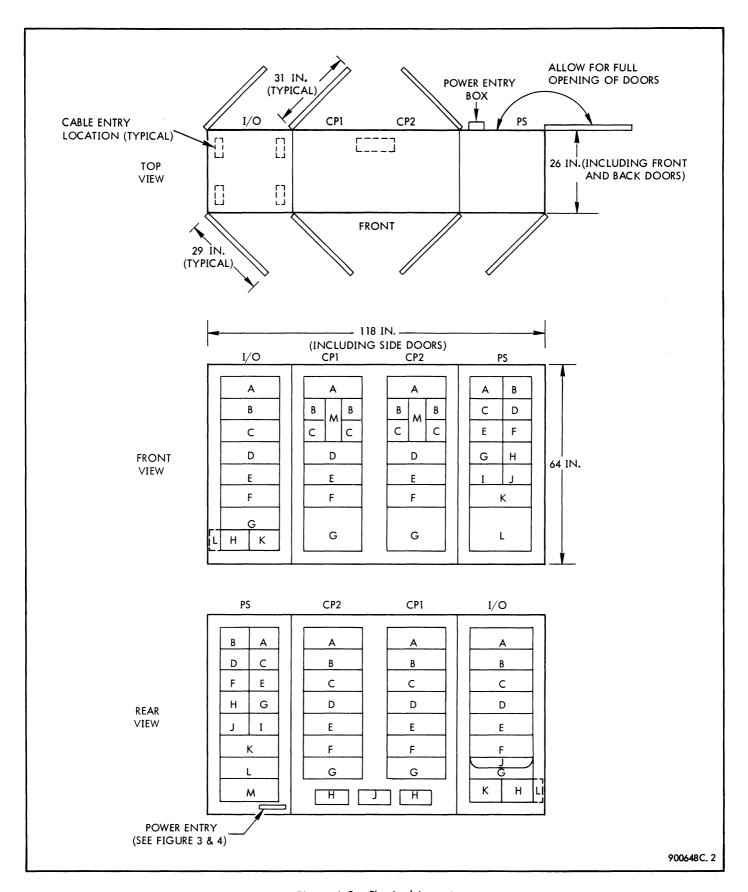

| 4-1    | Cabinet Base, Plan View                             | 4-2   |

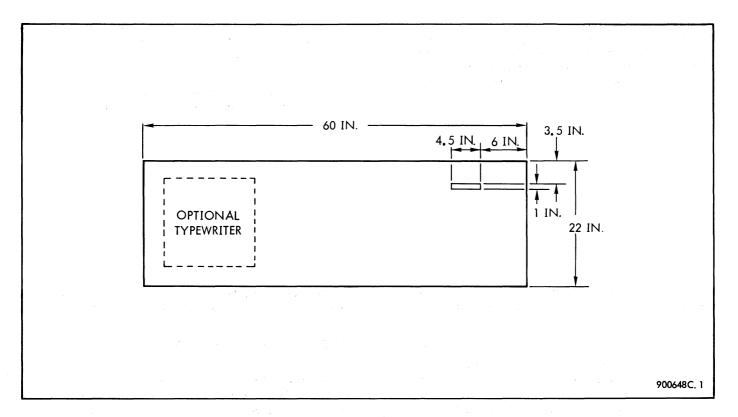

| 4-2    | Console, Plan View                                  | 4-2   |

| 4-3    | Physical Layout                                     | 4-3   |

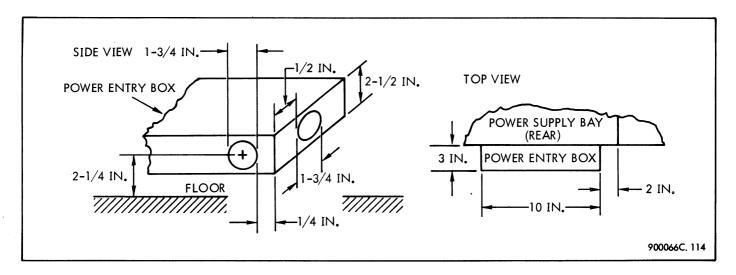

| 4-4    | Power Entry Box                                     | 4-5   |

| 4-5    | Service, Schematic Diagram                          | 4-6   |

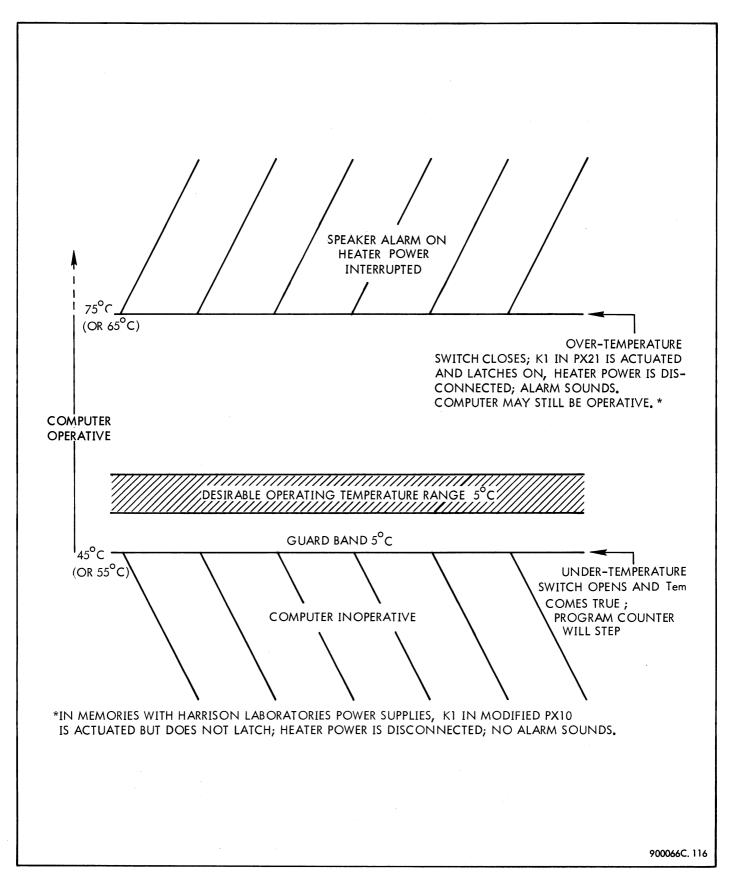

| 4-6    | Ideal Stack Operating Temperature                   | 4-13  |

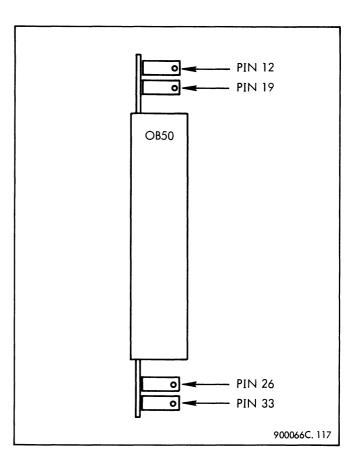

| 4-7    | Identification of OB50 Potentiometers by Output     | 4-14  |

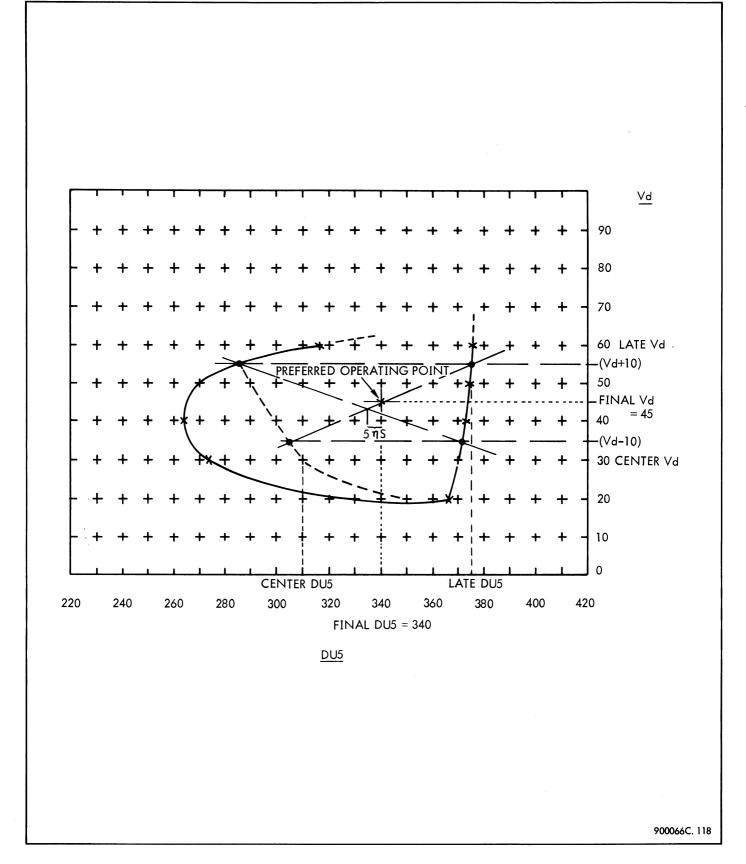

| 4-8    | Typical Schmoo Curve                                | 4-17  |

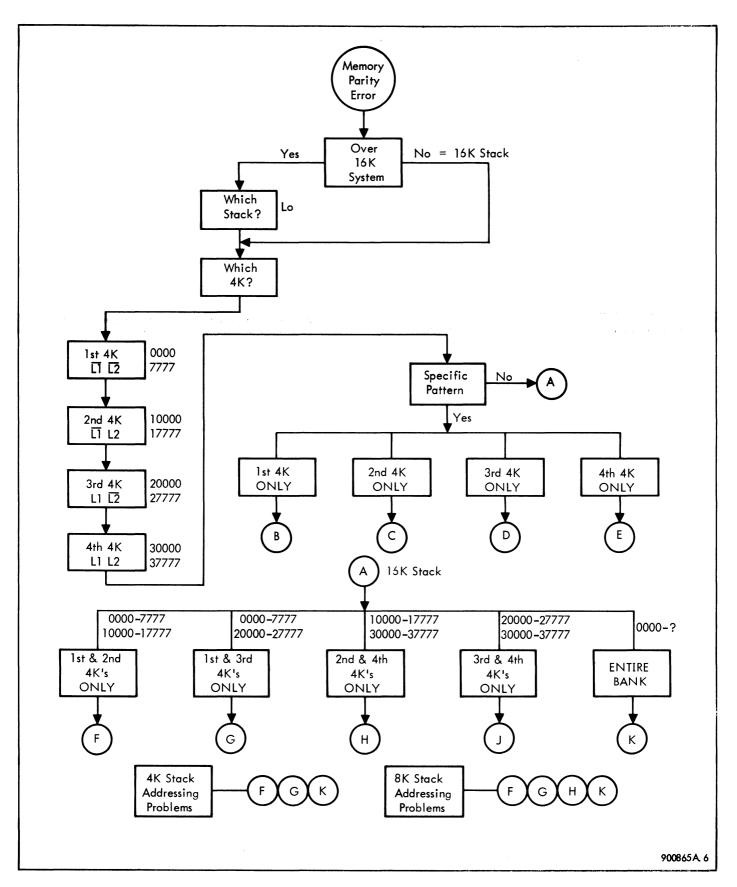

| 5-1    | Memory Troubleshooting, Flow Diagram                | 5-2   |

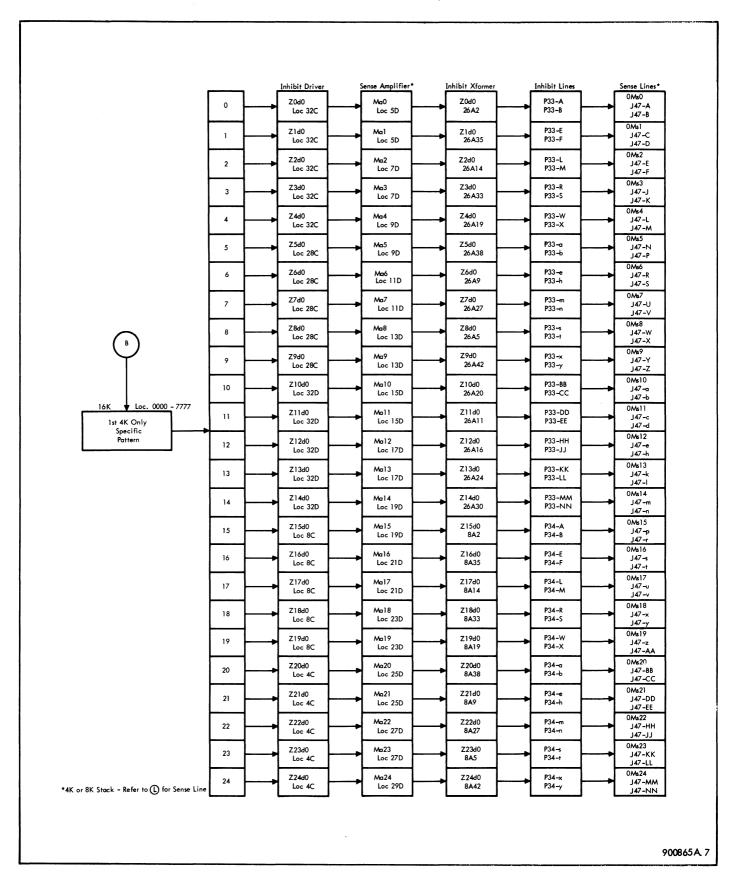

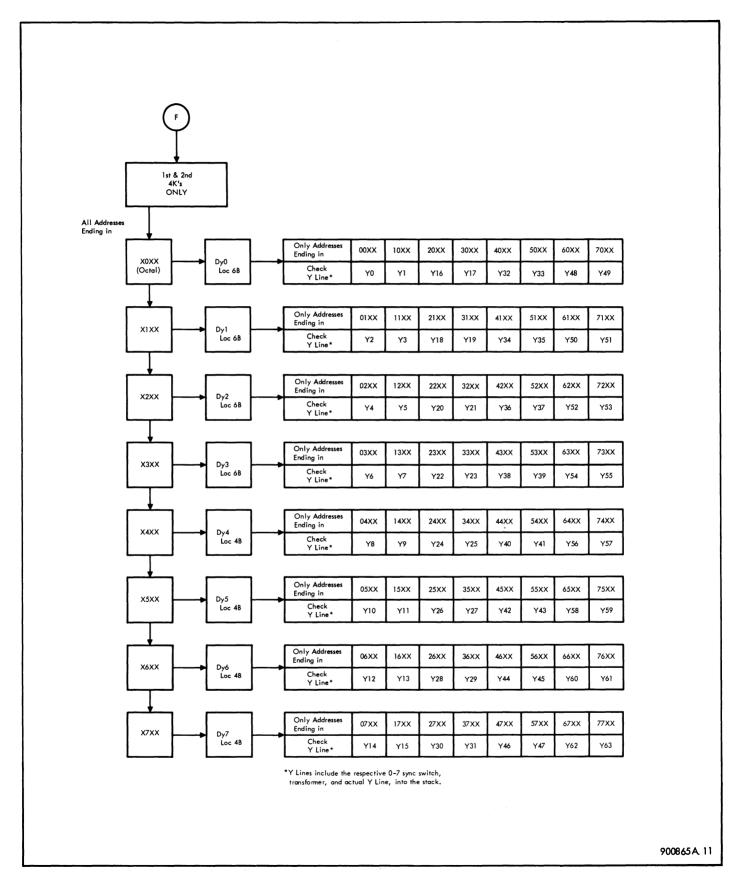

| 5-2    | Memory Troubleshooting, First 4K Stack              | 5-3   |

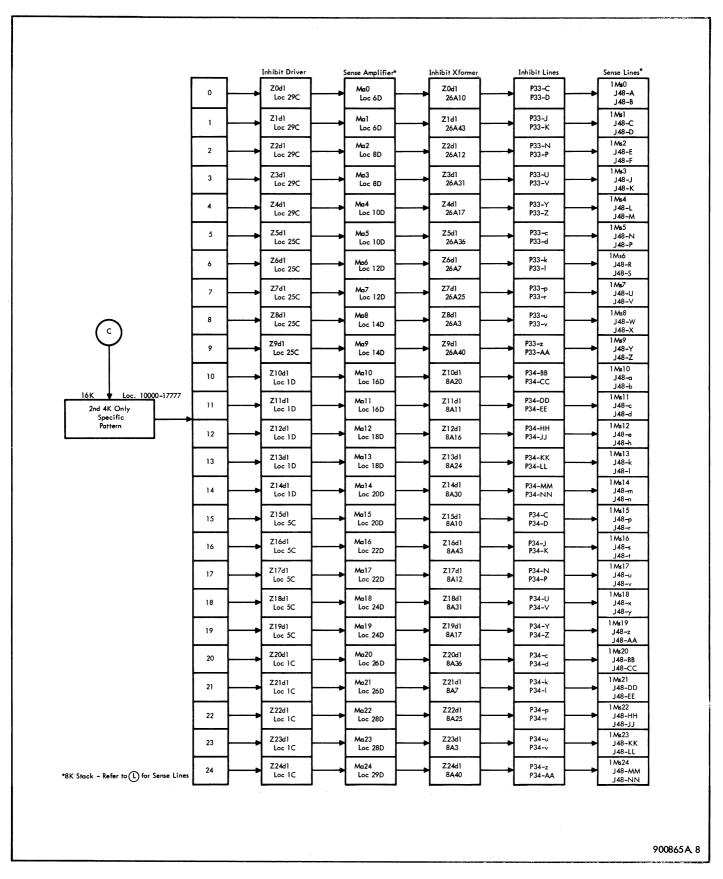

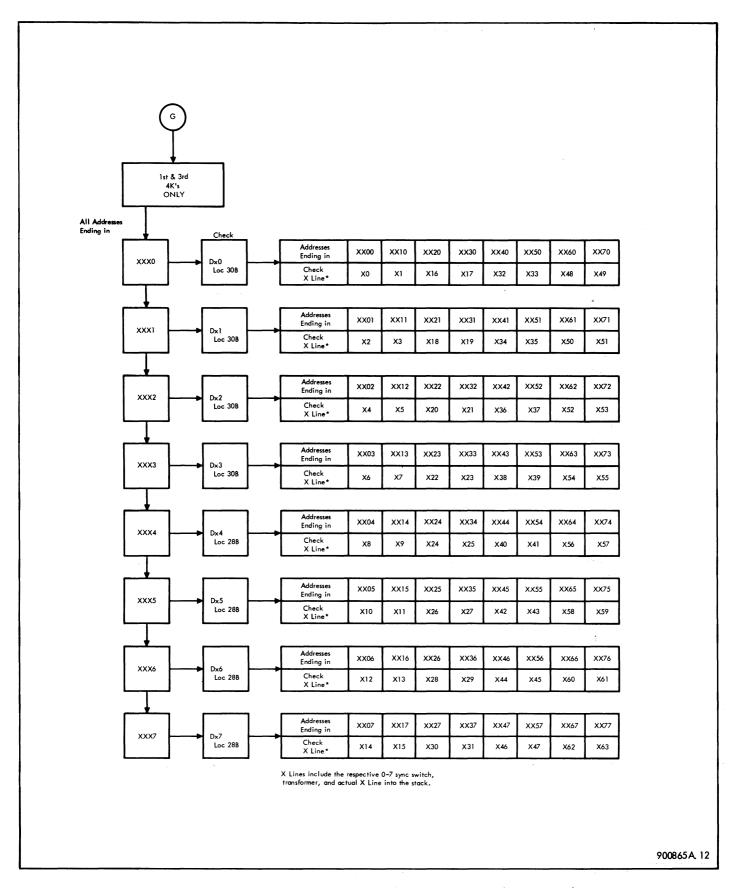

| 5-3    | Memory Troubleshooting, Second 4K Stack             | 5-4   |

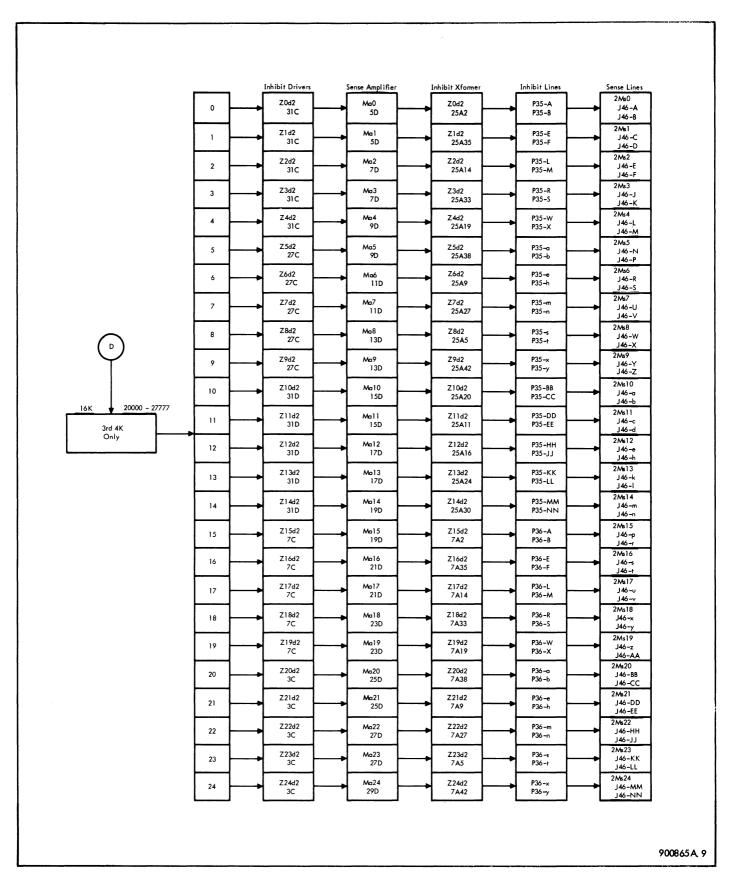

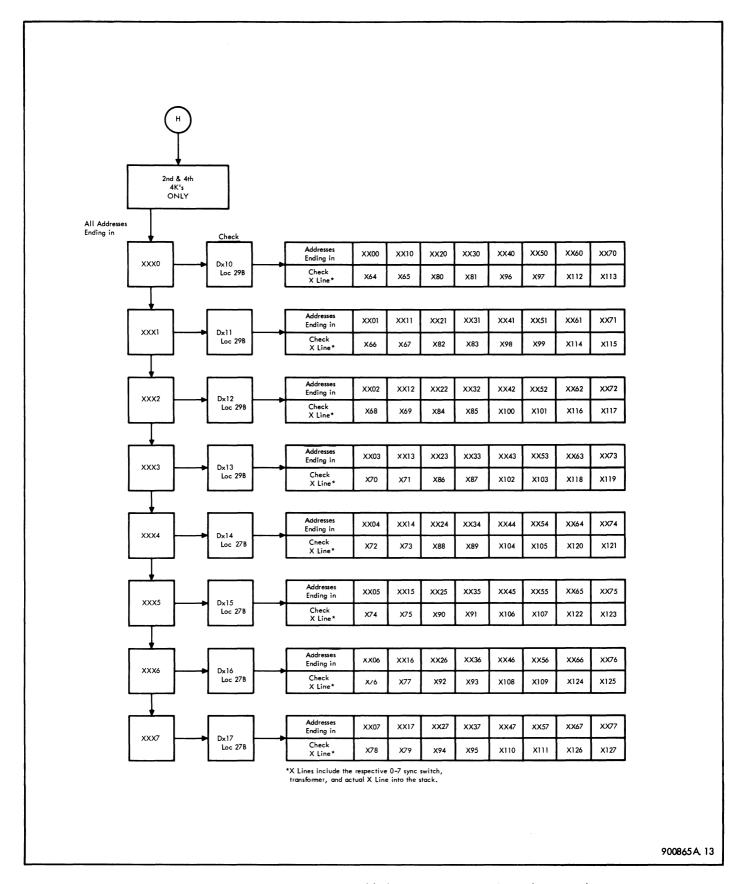

| 5-4    | Memory Troubleshooting, Third 4K Stack              | 5-5   |

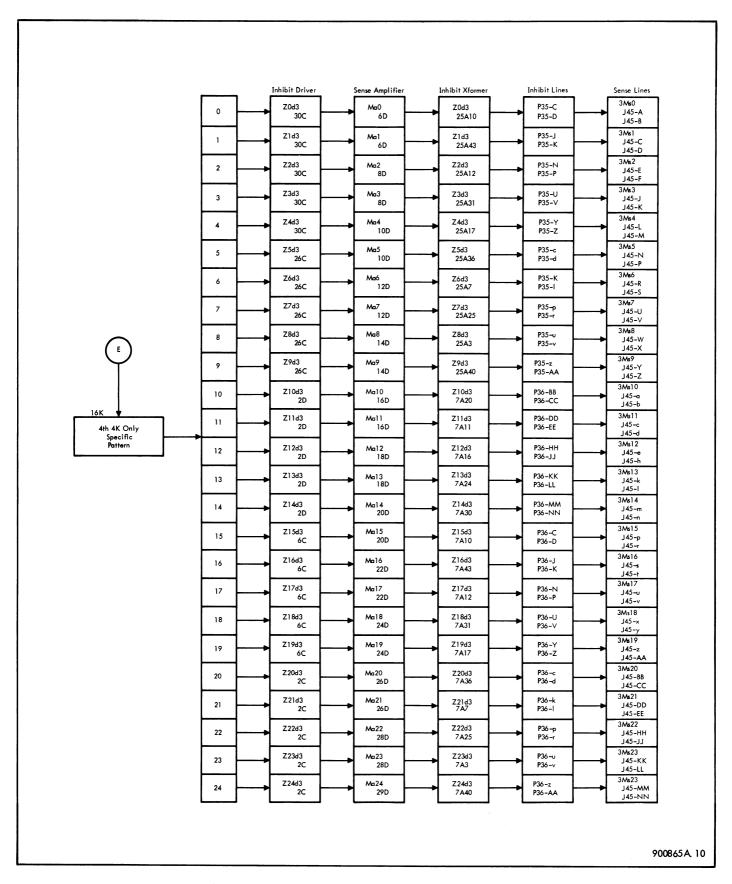

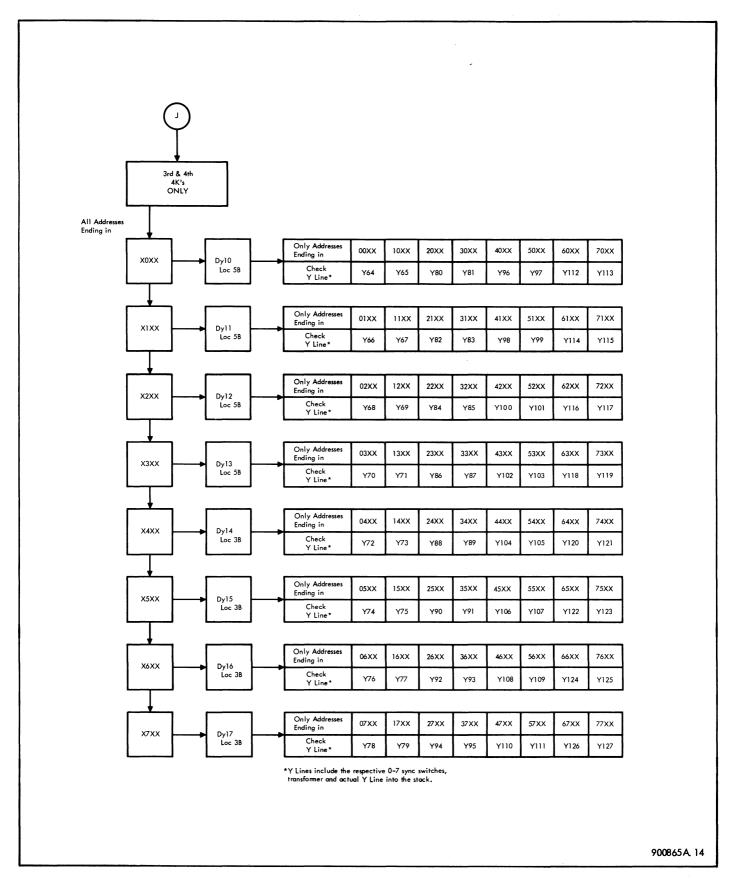

| 5-5    | Memory Troubleshooting, Fourth 4K Stack             | 5-6   |

| 5-6    | Memory Troubleshooting, First and Second 4K Stacks  | 5-7   |

| 5-7    | Memory Troubleshooting, First and Third 4K Stacks   | 5-8   |

| 5-8    | Memory Troubleshooting, Second and Fourth 4K Stacks | 5-9   |

| 5-9    | Memory Troubleshooting, Third and Fourth 4K Stacks  | 5-10  |

| 5-10   | Memory Troubleshooting, 4K and 8K Stacks            | 5-11  |

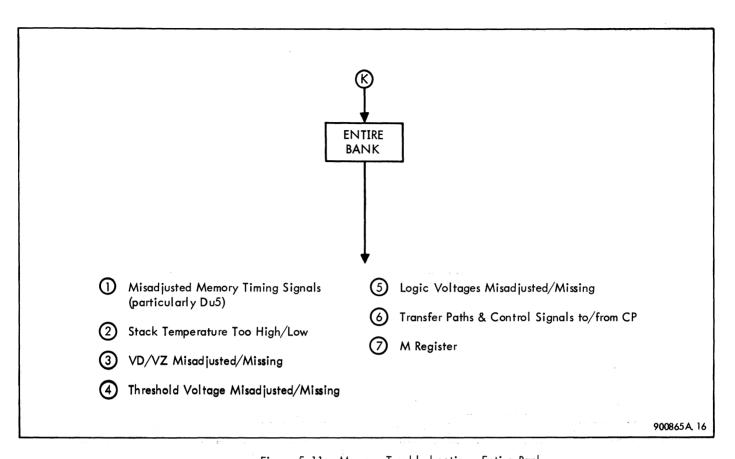

| 5-11   | Memory Troubleshooting, Entire Bank                 | 5-12  |

|        |                                                     |       |

|        | LIST OF TABLES                                      |       |

| Table  | Title                                               | Page  |

| 1-1    | 930 Computer Options                                | 1-4   |

| 1-2    | Specifications and Leading Particulars              | 1-6   |

| 1-3    | Fuses and Lamps                                     | 1-8   |

| 1-4    | Central Processor Chassis Modules                   | 1-9   |

| 1-5    | Memory Door Modules                                 | 1-9   |

| 1-6    | Memory ZB65 Jumper Module Variations                | 1-10  |

| 1-7    | Programmed Write Lockout ZB65 Variations            | 1-10  |

| 1-8    | Interrupt Chassis Modules                           | 1-10  |

| 2-1    | Controls                                            | 2-3   |

| 2-2    | Indicators                                          | 2-4   |

| 3-1    | Execution Times                                     | 3-1   |

| 3-2    | Instruction Set                                     | 3-3   |

| 3-3    | Machine Cycle Timing Pulse Decoding                 | 3-5   |

| 3-4    | Logic Symbols                                       | 3-7   |

| 3-5    | Central Processor Registers                         | 3-7   |

| 3-6    | Register Enable Paths                               | 3-10  |

| 3-7    | Basic Interrupt Levels                              | 3-29  |

| 3-8    | FILL Switch Control Signals                         | 3-36  |

| 3-9    | Decoding of A00 and B00                             | 3-38  |

| 3–10   | Instruction Timing                                  | 3-42  |

| 3-11   | Register Change Instructions                        | 3-71  |

| 3-12   | Functions of Register Change Instruction Bits       | 3–72  |

| 3-13   | Multiplication (A and C Positive)                   | 3-94  |

| 3–14   | Multiplication (A Negative, C Positive)             | 3-94  |

| 3-15   | Multiplication (A Positive, C Negative)             | 3-94  |

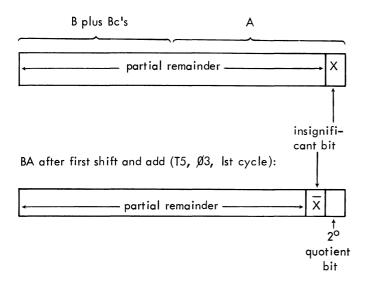

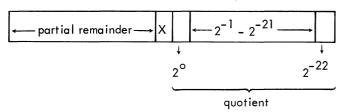

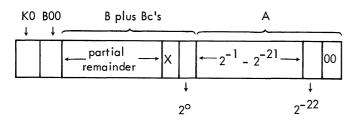

| 3-16   | Example of Nonrestoring Division                    | 3-97  |

| 3-17   | Register States in Division                         | 3-102 |

| 3-18   | Shift Instruction                                   | 3-104 |

## LIST OF TABLES (Cont.)

| Table | Title                                                                    | Page  |

|-------|--------------------------------------------------------------------------|-------|

| 3-19  | Address Selection Jumper Modules                                         | 3-127 |

| 3-20  | Octal Decoding for 4,096 Words                                           | 3-130 |

| 3-21  | Address-Drive Line Relationship                                          | 3-133 |

| 3-22  | Octal Decoding, 16,384 Words                                             | 3-135 |

| 3-23  | Inhibit (Z) Drivers                                                      | 3-138 |

| 3-24  | Inhibit Lines for Bit 19                                                 | 3-140 |

| 3-25  | Write Lockout Memory Blocks                                              | 3-147 |

| 3-26  | Z B65 Jumper Modules                                                     | 3-147 |

| 3-27  | Power Supplies                                                           | 3-152 |

| 3-28  | Central Processor Terms                                                  | 3-153 |

| 3-29  | Memory Terms                                                             | 3-157 |

| 4-1   | Equipment Location, Front View                                           | 4-4   |

| 4-2   | Equipment Location, Rear View                                            | 4-5   |

| 4-3   | Cable Installation                                                       | 4-6   |

| 4-4   | Control Console Connection                                               | 4-7   |

| 4-5   | Power Consumption and Heat Dissipation                                   | 4-8   |

| 4-6   | Addressing Modification Wiring Changes                                   | 4-9   |

| 4-7   | Module Installation for Manual Write Lockout                             | 4-10  |

| 4-8   | Installation of Direct Address Cable (P907) for Manual Write Lockout     | 4-10  |

| 4-9   | Module Installation for Programmed Write Lockout                         | 4-11  |

| 4-10  | Jumper Module ZB65 Installation                                          | 4-11  |

| 4-11  | Installation of Direct Address Cable (P907) for Programmed Write Lockout | 4-11  |

| 4-12  | Memory Expansion Kits                                                    | 4-11  |

| 4-13  | Special Test Equipment                                                   | 4-12  |

| 4-14  | OB50 One-Shot Adjustments                                                | 4-14  |

| 7-1   | Power Distribution and Control Console Schematics                        | 7-1   |

#### LIST OF RELATED PUBLICATIONS

The following publications contain information not included in this manual but necessary for a complete understanding of the Computer Model 930.

| Publication Title                                                                                           | Publication No. |

|-------------------------------------------------------------------------------------------------------------|-----------------|

| SDS 930 Computer, Reference Manual                                                                          | 900064          |

| SDS 930 Computer Examiner Diagnostic System, Technical Manual                                               | 900097          |

| 930/9300 Computer, Interface Manual                                                                         | 900561          |

| SDS 930 Computer Central Processor, Logic Diagrams                                                          | 900592          |

| 925/930 Computer, Basic Interrupt, Logic Layouts, Current and History                                       | 900608          |

| 925/930/9300 Computers, General Reference Drawings                                                          | 900619          |

| 930/9300 Memory, Logic Layouts, Current and History                                                         | 900620          |

| 925/930/9300 Computers, Module Reference Data                                                               | 900623          |

| SDS 930 Computer, Logic Equations, Main Frame and Memory                                                    | 900636          |

| Models 93280/90 Interrupt Control System, Technical Manual                                                  | 900667          |

| Models 9228, 9229, 92280, 92290 Interrupt Arming Option, Technical Manual                                   | 900668          |

| Models 92200/93200 Time-Multiplexed Communication Channels (TMCC), 925/930/9300 Computers, Technical Manual | 900685          |

| Models 925, 930, and 9300, Internal Memory Stack, Troubleshooting Guide                                     | 900689          |

| Models 92990/92992 Multiple Access to Memory (MAM), Technical Manual                                        | 900695          |

| Direct Access Communication Channel (DACC), Model 92220, Technical Manual                                   | 900696          |

| PX18 Power Supply, Technical Manual                                                                         | 900707          |

| PX19 Power Supply, Technical Manual                                                                         | 900708          |

| PX20 and PX21 Power Supplies, Technical Manual                                                              | 900709          |

| PX22 Power Supply, Service Manual                                                                           | 900710          |

| PX23 Power Supply, Service Manual                                                                           | 900711          |

| PX25 Power Supply, Technical Manual                                                                         | 900713          |

| Model 91500 Memory Interface Connection, Theory of Operation                                                | 900808          |

| Data Multiplex Channel (DMC), Model 91602, Technical Manual                                                 | 900850          |

| Data Subchannel I (DSC-I), Model 91711, Technical Manual                                                    | 900852          |

| Data Subchannel II (DSC-II), Model 91712, Technical Manual                                                  | 900853          |

| External Interlace, Model 91800, Technical Manual                                                           | 900854          |

| Power Fail-Safe, Model 92010, Technical Manual                                                              | 900858          |

| Model 91880 Real-Time Clock, Technical Manual                                                               | 900859          |

| Troubleshooting Manual Computer Memories for Computer Models 930/9300                                       | 900865          |

| Memory Diagnostic                                                                                           | 304001          |

| Instruction Diagnostic                                                                                      | 304002          |

| P & S Register Test                                                                                         | 304003          |

## SECTION I GENERAL DESCRIPTION

#### 1-1 INTRODUCTION

- 1-2 This manual contains information necessary to install, operate, and maintain the Computer Model 930, manufactured by Scientific Data Systems, Santa Monica, California. The material is presented in the form of a general description, a section on operation and programming, a complete theory of operation, a maintenance section, and troubleshooting instructions.

- 1-3 For a description of equipment associated with the 930 Computer and not described in this manual, refer to the documents in the List of Related Publications in the front of this manual. The list also contains the titles and publication numbers of logic diagrams, parts lists, and reference drawings for the 930 Computer.

- 1-4 The 930 Computer is a general-purpose, solid-state, digital computer designed for scientific and engineering computation and real-time applications. It is compatible with all SDS 900 series computers, peripheral units, and system components.

#### 1-5 PHYSICAL DESCRIPTION

- 1-6 The 930 Computer consists of a double-bay central processor cabinet, a single-bay power supply cabinet, a minimum of one single-bay input/output cabinet, and a control console. Additional input/output cabinets are included as necessary to contain the electronics and power supplies for input/output channels and peripheral equipment. The basic 930 Computer is shown in figures 1-1 through 1-3.

- 1-7 The central processor cabinet contains a computer chassis, two blower units, two distribution panels, and one or two memory doors. The computer chassis consists of five rows of plug-in printed circuit modules. The rows are designated B through F and contain 64 module locations numbered from right to left. A space at the top of the cabinet, which would normally contain row A, is empty. The distribution panels, one mounted on each end of the rack, are used for receiving the outputs from the power supplies and furnish distribution points for the power required by the central processor and memories. These panels are designated A, on the left, and B, on the right, as viewed from the front of the unit.

- 1-8 Amemory door is hinge-mounted on the front of the central processor cabinet. The memory chassis contains five rows of printed circuit modules, A through F, with 32 module locations in each row. The memory stack is located in the center of rows B and C. The first memory is usually mounted on the left-hand side of the central processor cabinet. A second memory may be mounted on the right-hand side of the cabinet. Each memory door contains blower units at the top and bottom.

- 1-9 If more than two memories are used, the third memory must be placed in a standard single-bay cabinet. In this case, the memory chassis is permanently mounted in the cabinet, and the additional power supplies are placed in the bottom of the cabinet.

- 1-10 The power supply cabinet contains a power distribution panel, a PX20 Power Supply, a PX21 Power Supply, two PX18's, three PX19's, and two PX25's. When a second memory is included, an additional PX20 and PX21 are installed. An optional PX19 and PX25 are included if necessary for further power demands.

- 1-11 An input/output cabinet is a standard SDS single-bay cabinet containing module chassis associated with input/output equipment. The basic interrupt chassis is generally mounted in the first input/output cabinet. Any number of input/output cabinets may be used, depending on the number necessary to contain the required input/output equipment.

- 1-12 The control console is a control panel mounted on a table. The control panel contains grid-controlled neon indicators, to display the states of flip-flops and registers, and pushbuttons, toggle switches, and thumbwheel switches for computer control and register display.

- 1-13 The optional features of the 930 are added as separate chassis in input/output cabinets or as additional modules in the central processor, the memory door, or the interrupt chassis. The options are listed in table 1-1 with their locations and the SDS publications in which they are described.

#### 1-14 FUNCTIONAL DESCRIPTION

1–15 The 930 Computer executes instructions, stores data and instructions, and processes interrupts. The instructions fall into the following categories:

Load and Store Shift

Arithmetic Control

Logical Breakpoint Tests

Register Change Overflow

Memory Extension Interrupt Enable and Disable

Branch Channel Control

Test and Skip Channel Tests

Input/Output

Figure 1-2. Computer Model 930, Rear View

Figure 1-3. Computer Model 930 Control Console

Table 1-1. 930 Computer Options

| Model<br>Number | Option                                         | Location    | Reference<br>Publication |

|-----------------|------------------------------------------------|-------------|--------------------------|

| 91210           | Memory Interlace Control Unit:<br>For Any TMCC | I/O cabinet | 900685                   |

| 91500           | Memory Interface Connection                    | I/O cabinet | 900808                   |

| 91602           | Data Multiplex Channel                         | I/O cabinet | 900850                   |

| 91711           | Data Subchannel I                              | I/O cabinet | 900852                   |

| 91712           | Data Subchannel II                             | I/O cabinet | 900853                   |

| 91800           | External Interlace                             | I/O cabinet | 900854                   |

Table 1-1. 930 Computer Options (Cont.)

| Model<br>Number | Option                                                    | Location                                      | Reference<br>Publication |

|-----------------|-----------------------------------------------------------|-----------------------------------------------|--------------------------|

| 91880           | Real-Time Clock                                           | Basic interrupt chassis<br>(I/O cabinet)      | 900859                   |

| 91903           | SDS 930 Addressing Modification<br>Feature                | Central processor                             | This manual, par. 3–90   |

| 92010           | Power Fail–Safe Option                                    | Basic interrupt chassis<br>(I/O chassis)      | 900858                   |

| 92040           | 4096 Words of Core Memory                                 | Memory door                                   | This manual, par. 3–516  |

| 92060           | Manual Memory Write Lockout<br>Feature                    | Memory door                                   | This manual, par. 3–606  |

| 92061           | Programmed Memory Write<br>Lockout Feature                | Memory door                                   | This manual, par. 3–600  |

| 92070           | Interrupts for Memory Parity and<br>Input/Output Parity   | Central processor and basic interrupt chassis | This manual, par. 3–160  |

| 92080           | 8192 Words of Core Memory                                 | Memory door                                   | This manual, par. 3-516  |

| 92160           | 16,384 Words of Core Memory                               | Memory door                                   | This manual, par. 3–516  |

| 92220           | Direct Access Communication<br>Channel                    | I/O cabinet                                   | 900696                   |

| 92280           | Arming for 16 Levels of Interrupt                         | I/O cabinet                                   | 900668                   |

| 92290           | Additional Arming for 16 Levels<br>of Interrupt           | I/O cabinet                                   | 900668                   |

| 92990           | Multiple Access to Memory (MAM)                           | Central processor and memory door             | 900695                   |

| 93201           | 12-Bit Option for Any TMCC                                | I/O cabinet                                   | 900685                   |

| 93202           | 24-Bit Option for Any TMCC                                | I/O cabinet                                   | 900685                   |

| 93220           | One Additional Time–Multiplexed<br>Communication Channel  | I/O cabinet                                   | 900685                   |

| 93221           | Two Additional Time–Multiplexed<br>Communication Channels | I/O cabinet                                   | 900685                   |

| 93280           | Interrupt Control System                                  | I/O cabinet                                   | 900667                   |

| 93290           | Priority Interrupt: Two Levels                            | Priority interrupt chassis<br>(I/O cabinet)   | 900667                   |

1-15 A block diagram of the functional units of the 930 Computer, including optional equipment, is given in figure 1-4.

1-16 The central processor performs all of the computer functions except storage, interrupt, and serial input/output. Parallel input and output of memory words is handled by the central processor. Word storage, memory control and addressing, and write lockout take place in the memory unit. The basic interrupt system receives interrupt signals from the power fail-safe, memory parity, memory lockout circuits, and the Time Multiplexed Communication Channel (TMCC) and Direct Access Communication Channel (DACC). These interrupts are handled on the basis of priority level, and an interrupt address is sent to the computer for each individual interrupt. The TMCC, W-buffer, communicates with the peripheral equipment using the first path to memory, through the C-register. The interlace control unit for the TMCC allows the program to designate to the TMCC how many words are to be transferred and the memory location of the first word.

#### 1-17 OPTIONAL FEATURES

1–18 The optional Y, C, and D channels of the TMCC provide additional buffered input/output. Direct access to the memory is obtained through the Data Multiplexing System, the Multiple Access to Memory, the Memory Interface Connection, and the Direct Access Communication Channel. The Interrupt Control System and the Interrupt Arming option supply interrupts not covered by the basic interrupt.

1-19 With the parity interrupt option installed, a sub-routine is entered when a memory parity error is detected. Blocks of memory may be locked out by the Write Lockout option so that data may not be written in the locked-out portions. The Power Fail-Safe option detects a drop in input power and stores in memory all data contained in the computer registers. A subroutine returns the data to the registers when power is resumed.

1–20 The Real-Time Clock option times the length of a program or subroutine or maintains the time of day for the computer.

1-21 The functions of the optional units are described in detail in the associated technical manuals indicated in table 1-1.

#### 1-22 SPECIFICATIONS AND LEADING PARTICULARS

1–23 The 930 Computer specifications and leading particulars are given in table 1–2.

Table 1-2. Specifications and Leading Particulars

| Table 1 21 Specifications and Leading Fartheolds           |                                                                                                                                                                                                                                 |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Characteristic                                             | Specification                                                                                                                                                                                                                   |  |  |  |

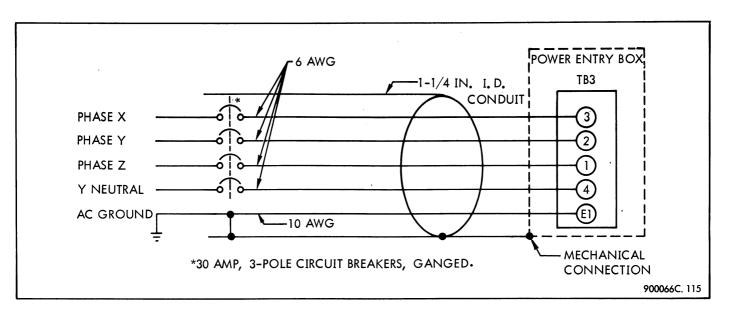

| Power requirements                                         | 208 (±20.8) vac, ±10%, 60 (±0.5) cps, 3 phase Y-connected                                                                                                                                                                       |  |  |  |

| Recommended<br>service                                     | 208 vac, 3 phase Y, 10 kva<br>minimum, with 30-amp circuit<br>breaker in each leg, ganged. 10<br>kva will permit system expansion.                                                                                              |  |  |  |

| Service entry                                              | No. 6 AWG wire for phase X, phase Y, phase Z, and Yneutral; No. 8 AWG wire for minimal system. The wires are run through a 1–1/4 inch I.D. conduit and enter at bottom rear of PS bay. Conduit is connected to the ground wire. |  |  |  |

| Operating temperature                                      | 10°C - 40°C (50°F - 104°F)                                                                                                                                                                                                      |  |  |  |

| Operating humidity                                         | 10% - 90%                                                                                                                                                                                                                       |  |  |  |

| Weights                                                    | Supported on four double casters                                                                                                                                                                                                |  |  |  |

| CPU<br>CPU<br>PS cabinet<br>I/O cabinet<br>Control console | 1150 lb with single memory bank<br>1350 lb with dual memory bank<br>1200 lb<br>700 lb<br>150 lb with I/O typewriter option                                                                                                      |  |  |  |

| Recommended<br>floor area                                  |                                                                                                                                                                                                                                 |  |  |  |

| Computer<br>Control console                                | 15 ft by 9 ft, 135 sq ft<br>9 ft by 6 ft, 54 sq ft                                                                                                                                                                              |  |  |  |

| Recommended access area                                    |                                                                                                                                                                                                                                 |  |  |  |

| Computer                                                   | 3–1/2 ft front and rear for maintenance                                                                                                                                                                                         |  |  |  |

| Control console                                            | 4 ft front for operation                                                                                                                                                                                                        |  |  |  |

| Memory cycle                                               | 1.75 µsec                                                                                                                                                                                                                       |  |  |  |

| Logic signal levels                                        | ONE, +4v; ZERO, 0v                                                                                                                                                                                                              |  |  |  |

| Word length                                                | 24 bits plus parity bit                                                                                                                                                                                                         |  |  |  |

| Data format                                                | Fixed point, floating point                                                                                                                                                                                                     |  |  |  |

| Coding                                                     | Binary                                                                                                                                                                                                                          |  |  |  |

Figure 1-4. Computer Model 930, Functional Block Diagram

#### 1-24 FUSES AND LAMPS

1-25 The fuses and lamps in the 930 Computer are described in table 1-3.

#### 1-26 MODULES

1-27 The modules listed below are located in the central processor, the memory door, or the interrupt chassis. The list automatically includes the following optional features, which are in these three basic 930 Computer chassis: Addressing Modification Feature Model 91903, Manual Memory Write Lockout Feature Model 92060, Programmed Memory Write Lockout Feature Model 92061, Multiple Access to Memory Model 92990, Interrupts for Memory Parity and Input/Output Parity Model 92070, Real-Time Clock Model 91880, and Power Fail-Safe Option Model

- 92010. The remainder of the optional features are contained in separate chassis in the input/output cabinets.

- 1-28 Table 1-4 is a list of modules in the central processor chassis.

- 1-29 Table 1-5 lists the modules in the memory door.

- 1–30 The variations of Jumpers ZB65 in memory and in the Programmed Write Lockout option are given in tables 1–6 and 1–7.

- 1-31 Table 1-8 lists the modules in the interrupt chassis.

- 1-32 For the Addressing Modification Feature Model 91903, BAND NAND IB57 is installed in location 52C of the central processor, and a Dual Flip-Flop FB51 is installed in location 62D of the central processor.

Table 1-3. Fuses and Lamps

|                                      |                                                                 | _                                                                                                               | Location                                                                                                                                                                             | Protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |