# RM 9460 GRAPHIC DISPLAY SYSTEM

# **Hardware Reference Manual**

Publication No. 8000080-02, Rev. B

January 1984

#### **PROPRIETARY STATEMENT**

This document contains Ramtek proprietary data and information. This data and information shall not be disclosed, used, disseminated, or reproduced in whole or in part without the express prior written authorization of Ramtek Corporation.

2211 Lawson Lane Santa Clara, California 95050

© 1983, RAMTEK CORPORATION

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Ramtek Corporation has prepared this manual for use by Ramtek personnel, licensees, and customers. The information herein is proprietary and shall not be reproduced in whole or in part without Ramtek's prior written approval.

Ramtek reserves the right to change, without notice, the specifications and materials herein. Moreover, Ramtek shall not be responsible for damages, including consequential damages, caused by erroneous information, including but not limited to erroneous typography, arithmetic, or listings.

Z80<sup>®</sup>-CPU and Z80A<sup>®</sup>-CPU are registered trademarks of Zilog, Inc.

VAX® / VMS® are registered trademarks of Digital Equipment Corporation.

### LIST OF EFFECTIVE PAGES

Changes, deletions, and additions to information in this manual are indicated by bars in the margins or by an asterisk near the page number if the entire page is affected.

| PAGE                                | REVISION | PAGE                      | REVISION |

|-------------------------------------|----------|---------------------------|----------|

| Title<br>iii*/iv                    | B        | 4-32 through 4-39<br>4-40 | A<br>B   |

| v                                   | Ă        | 4-41 through 4-146        | Ā        |

| vi through xii                      | В        | 4-147 through 4-147b      | В        |

| l-l through l-5                     | Α        | 4-148 through 4-170       | A        |

| 1-6                                 | В        | 4-170a* through 4-170f    | • В      |

| l-7 through l-ll                    | Α        | 4-171 through 4-175       | Α        |

| 1-12 through 1-13                   | В        | 4-176                     | В        |

| 1-14 through 1-23                   | Α        | 4-177 through 4-190       | Α        |

| 1-24 through 1-26*                  | В        | 4-191* through 4-194d*    | В        |

| 1-27 through 1-33                   | Α        | 4-195 through 4-298       | A        |

| 1-34                                | В        | 4-298a* through 4-298d*   | * В      |

| 1 <b>-</b> 35 through 1 <b>-</b> 36 | Α        | 4-299 through 4-306       | Α        |

| 2-1 through 2-17                    | Α        | 5-1 through 5-16          | A        |

| 2-18 through 2-20                   | В        | 6-1                       | В        |

| 2-21 through 2-30                   | Α        | 6-2                       | А        |

| 3-1 through 3-4                     | Α        | A-1 through A-10          | Α        |

| 4-1 through 4-31                    | Α        | B-1 through B-8           | Α        |

| 4-31a* through 4-31b*               | В        |                           |          |

Dates of issue for original and revision pages are:

| Reissued   | June 1983    |

|------------|--------------|

| Revision B | January 1984 |

# CONTENTS

Page

# Chapter 1. GENERAL INFORMATION

| 1.1<br>1.2 |                                         | -1<br>-1 |

|------------|-----------------------------------------|----------|

| T • C      |                                         | -1       |

|            |                                         | -1       |

|            |                                         | -1       |

|            |                                         | -1       |

|            |                                         | -2       |

|            |                                         | _        |

|            |                                         |          |

|            | • • • • • • • • • • • • • • • • • • • • | -2       |

| • •        |                                         | -2       |

| 1.3        |                                         | -2       |

|            |                                         | -2       |

|            |                                         | -2       |

|            |                                         | -2       |

|            | $\mathbf{v}$                            | -3       |

| 1.4        |                                         | -3       |

| 1.5        | SAFETY                                  | -3       |

|            | 1.5.1 Electrical Safety                 | -3       |

|            |                                         | -5       |

| 1.6        |                                         | -5       |

| 1.7        |                                         | -5       |

| 1.8        |                                         | -6       |

|            |                                         | -6       |

|            |                                         | -7       |

|            |                                         | 28       |

| 1.9        |                                         | 28       |

| 1.10       |                                         | 33       |

| T + T O    |                                         | 55       |

# Chapter 2. INSTALLATION

| 2.1 | INTRODUC | CTION .  |         | • •   |      | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | •  | • | • | • | 2-1 |

|-----|----------|----------|---------|-------|------|-----|-----|----|---|---|---|---|---|---|---|---|---|---|---|---|----|---|---|---|-----|

| 2.2 | RECEIVIN | NG AND F | RESHIP  | PING  |      | •   | •   | •  | • | • | • | • | • | • | • | • |   | • | • | • | •  | • | • | • | 2-1 |

|     | 2.2.1    |          |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-1 |

|     | 2.2.2    | Reshipp  | oing P  | roced | lure | s.  | •   | •  |   |   | • | • | • | • | • | • | • | ٠ | • | • | •  | • | • |   | 2-1 |

| 2.3 | FACILITI | IES REOL | JIRÊMEI | NTS.  |      | •   | •   | •  | • | • | • |   | • | • | • | • | • | • | • | • | •  | • | • | • | 2-2 |

|     |          | Space F  |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-2 |

|     | 2.3.2    | Floor (  | Consid  | erati | ions | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | •  | • | • | • | 2-3 |

|     |          | Surface  |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-3 |

|     | 2.3.4    | Earthqu  | Jake Co | onsid | lera | tic | ons | 5. | • | • | • | • | • | • | • | • | • | • | • | • | •. | • | • | • | 2-4 |

|     | 2.3.5    | AC Serv  | /ice .  | • •   | • •  | •   | •   | •  | • | • | • | • | • | • | • | • | • | • | • | • | •  | • | • | • | 2-5 |

|     | 2.3.6    | Groundi  | ing Co  | nside | erat | ior | าร  | •  | • | • | • | • | • | • | • | • | • | • | • | • | •  | • | • | • | 2-5 |

|     |          | Air Flo  |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-5 |

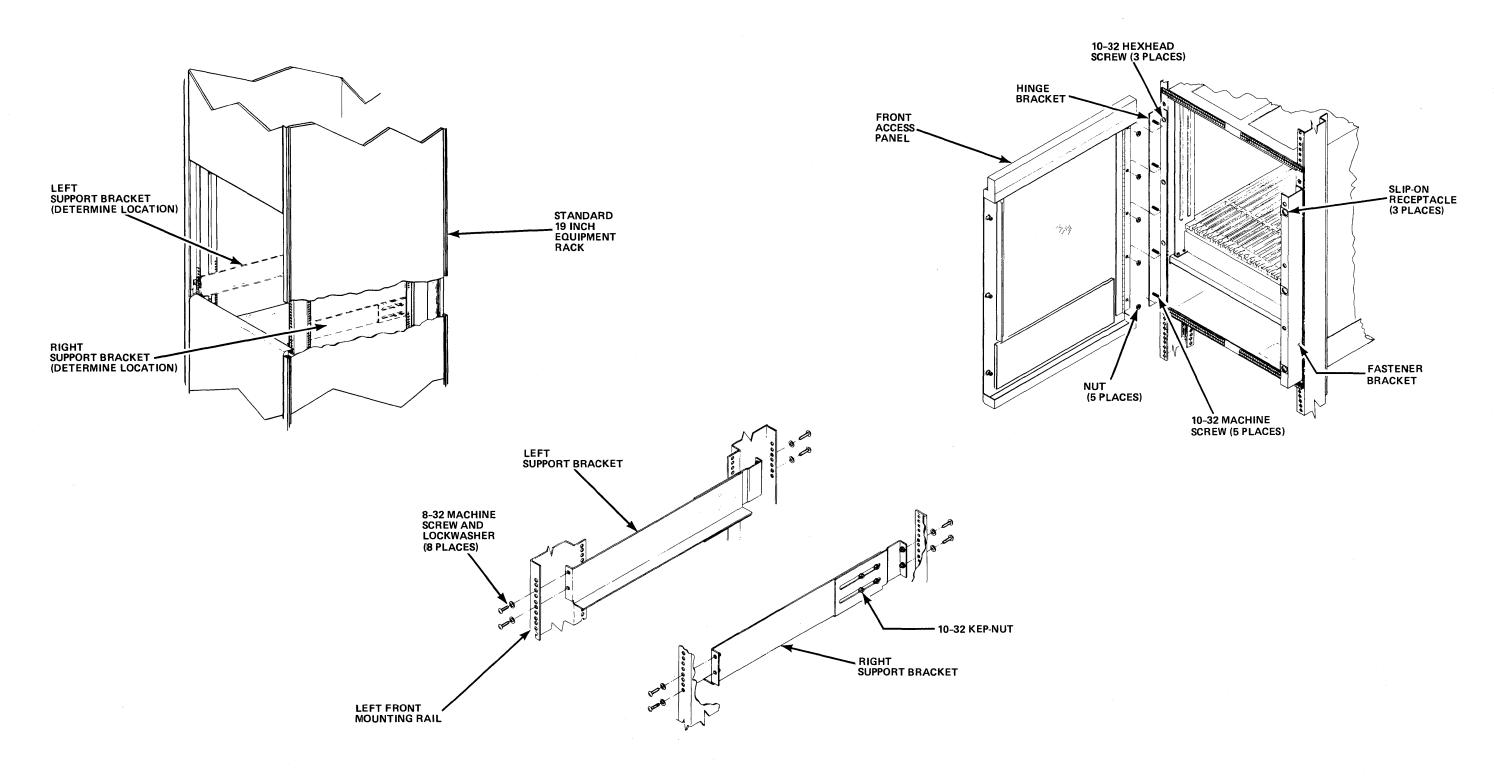

| 2.4 | INSTALLA |          |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-6 |

|     |          | Rack Mc  |         |       |      |     |     |    |   |   |   |   |   |   |   |   |   |   |   |   |    |   |   |   | 2-6 |

# 8000080-02B

# Paragraph

|     | 2.4.2    | PCB In<br>Signal | Connec  | cti | on  | 5.  | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | 2-8            |

|-----|----------|------------------|---------|-----|-----|-----|----|-----|----|----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------|

|     | 2.4.4    | Power            |         |     |     |     |    |     |    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                |

| 2.5 | CONFIGUE |                  |         |     |     |     |    |     |    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                |

|     | 2.5.1    | System           | Proces  | 550 | r I | PCB | () | Z80 | )) | •  | • | ٠ | • | • | • | • | • | • | • | • | • | • | • | • | ٠ | 2-10           |

|     | 2.5.2    | System           | Proces  | sso | r I | PCB | (6 | 580 | 00 | )) | • | • | • | • | • | • | • | • | • |   | • | • | • | • | • | 2-10           |

|     | 2.5.3    | Serial           |         |     |     |     |    |     |    |    |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |                |

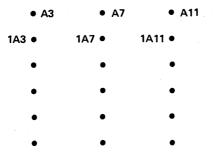

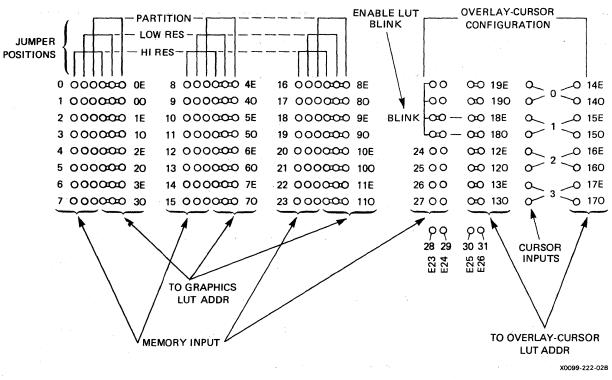

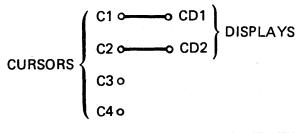

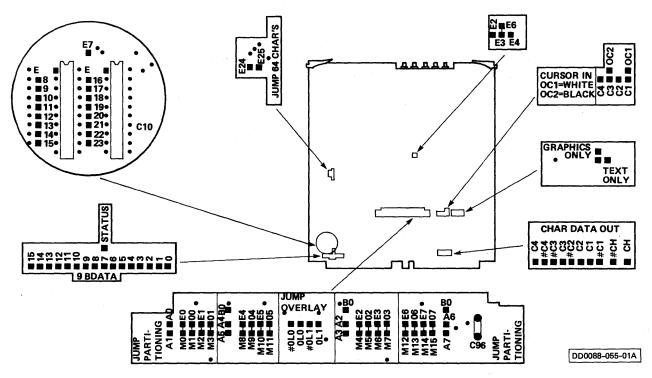

|     | 2.5.4    | Video            | 7 PCB.  | •   | •   |     | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 2-15           |

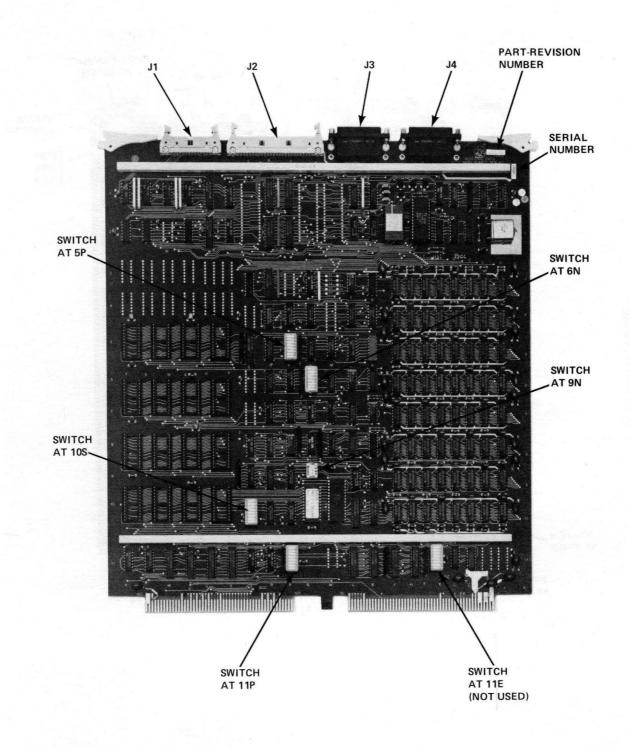

|     | 2.5.5    | Expans           | ion PCE | З.  | •   |     | •  | •   | •  | •  | • | • | • | • | • |   | • | • | • | • | • | • | • | • | • | 2-18           |

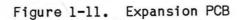

|     | 2.5.5A   | Video            | 6 PCB.  | •   | •   | • • | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | 2-18           |

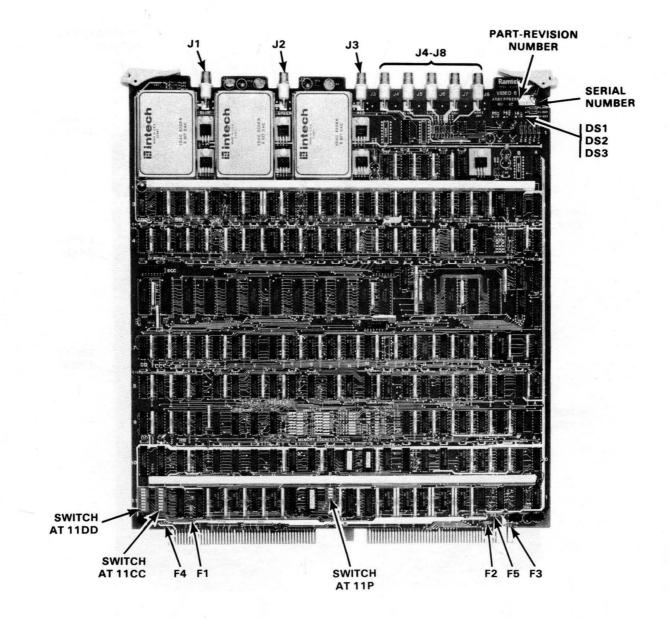

| 1   | 2.5.6    | Video            | 8 PCB.  | •   | •   | • • | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | ٠ | • | • | • | • | • | 2 <b>-</b> 18a |

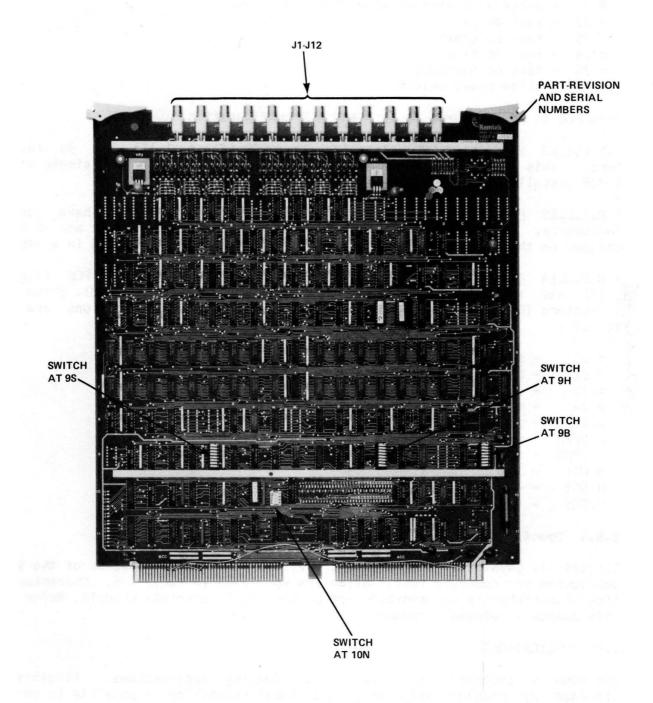

|     | 2.5.7    | Video            | 12 PCB  | •   | •   | • • | •  | •   | •  | •  | • | • | • | • | • | • | • | • | • | • | • |   | • | • | • | 2-22           |

| 2.6 | CHECKOU  | г                |         | •   | •   | • • | •  | •   | •  | •  | • | • | • | • | • | • | é | • | • | • | • | • | • | • | • | 2-26           |

# Chapter 3. OPERATION

| 3.1 | INTRODUCTION                           | 3-1 |

|-----|----------------------------------------|-----|

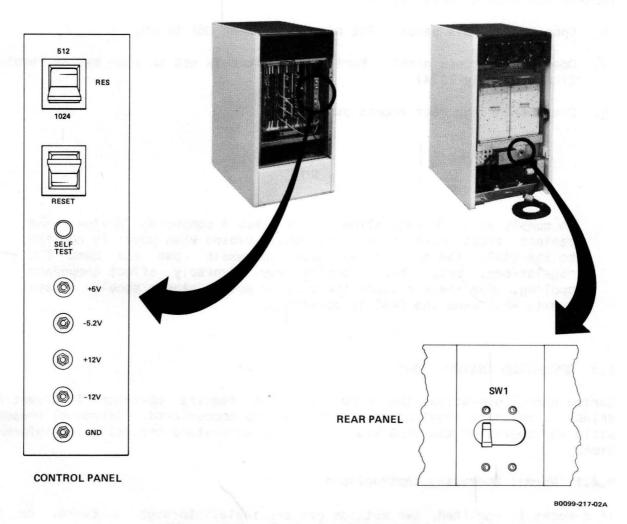

| 3.2 | CONTROLS AND INDICATORS                | 3-1 |

| 3.3 | 9460 TERMINAL TURN-ON                  | 3-2 |

| 3.4 | OPERATING INSTRUCTIONS                 | 3-2 |

|     | 3.4.1 Normal Operating Instructions    | 3-2 |

|     | 3.4.2 Emergency Operating Instructions | 3-3 |

| 3.5 | 9460 TERMINAL TURN-OFF                 | 3-3 |

# Chapter 4. FUNCTIONAL DESCRIPTION

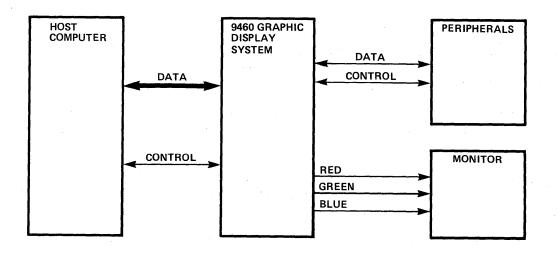

| 4.1 | SYSTEM  | CONCEPTS                            | 4-1  |

|-----|---------|-------------------------------------|------|

|     | 4.1.1   | Raster Scan                         | 4-1  |

|     | 4.1.2   | Refresh Memory                      |      |

|     | 4.1.3   | Video Lookup Table (VLT) Principles |      |

|     | 4.1.4   | Multi-Processing                    |      |

| 4.2 | SYSTEM  |                                     |      |

|     | 4.2.1   | Host Computer                       |      |

|     | 4.2.2   | 9460                                |      |

|     | 4.2.3   | Peripherals                         |      |

|     | 4.2.4   | Monitor                             |      |

| 4.3 | SIGNAL  |                                     |      |

|     | 4.3.1   | Signal Descriptions                 | 4-5  |

|     | 4.3.2   | Drawing Conventions                 | 4-5  |

| 4.4 | MINIMUM |                                     | 4-39 |

|     | 4.4.1   | Minimum Functional Elements         |      |

|     | 4.4.2   | Optional Functional Elements        |      |

| 4.5 | FUNCTIO | ONAL DESCRIPTIONS                   | 4-40 |

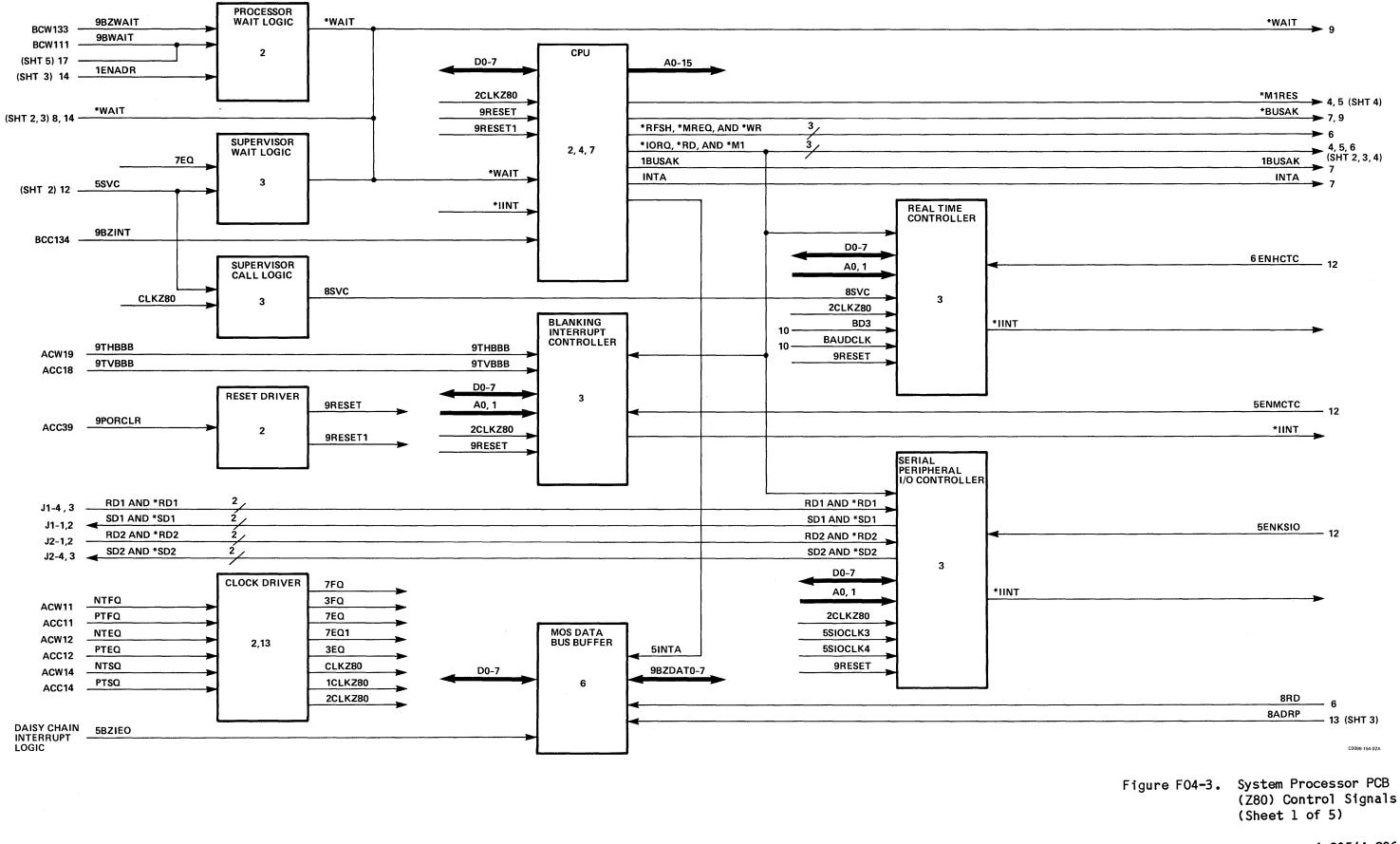

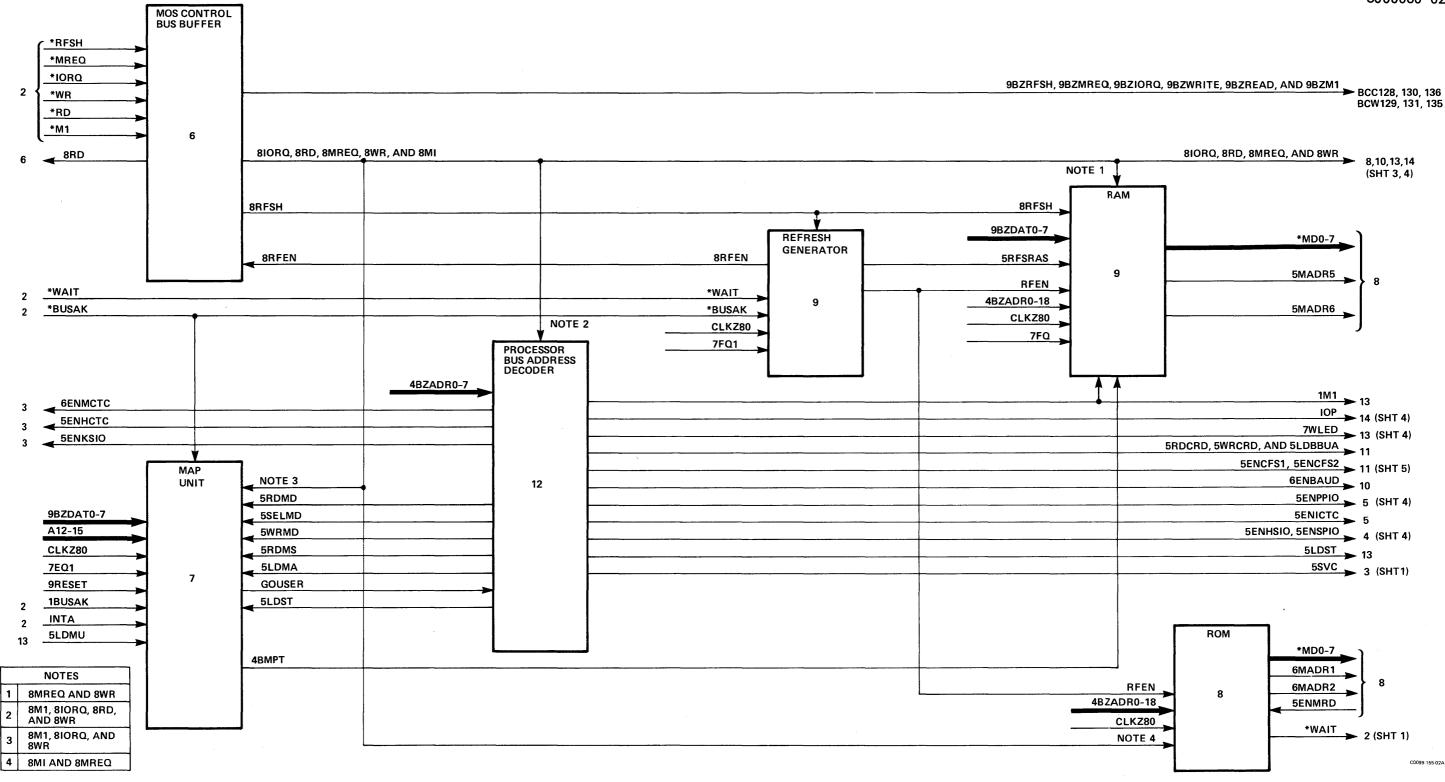

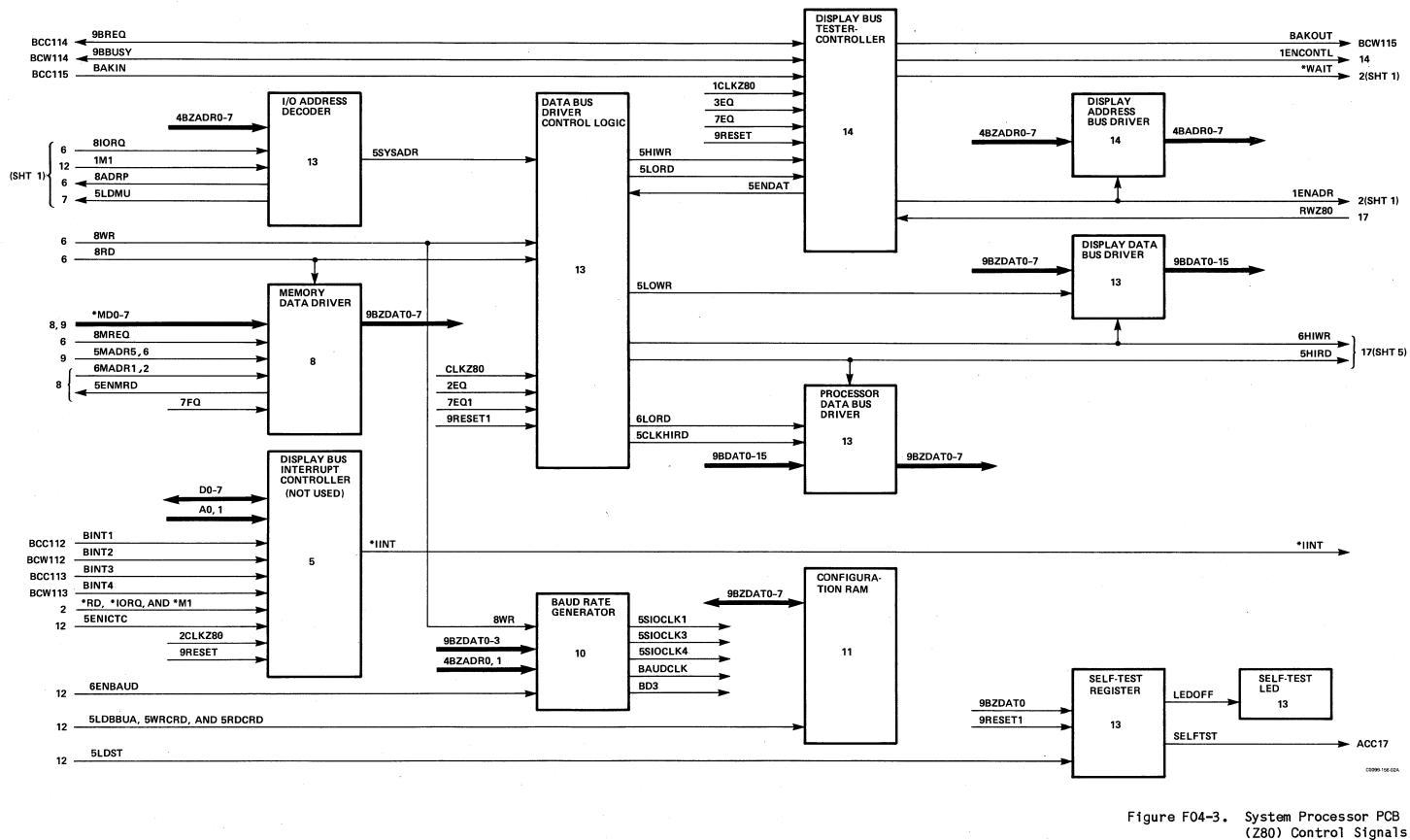

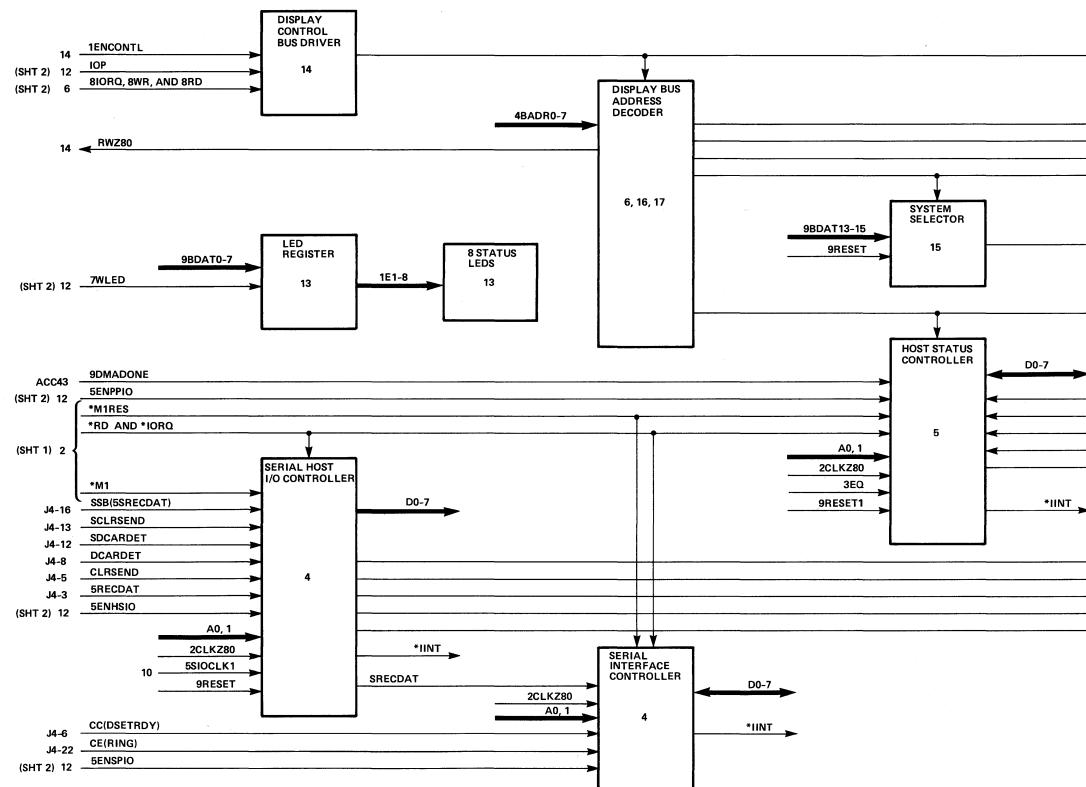

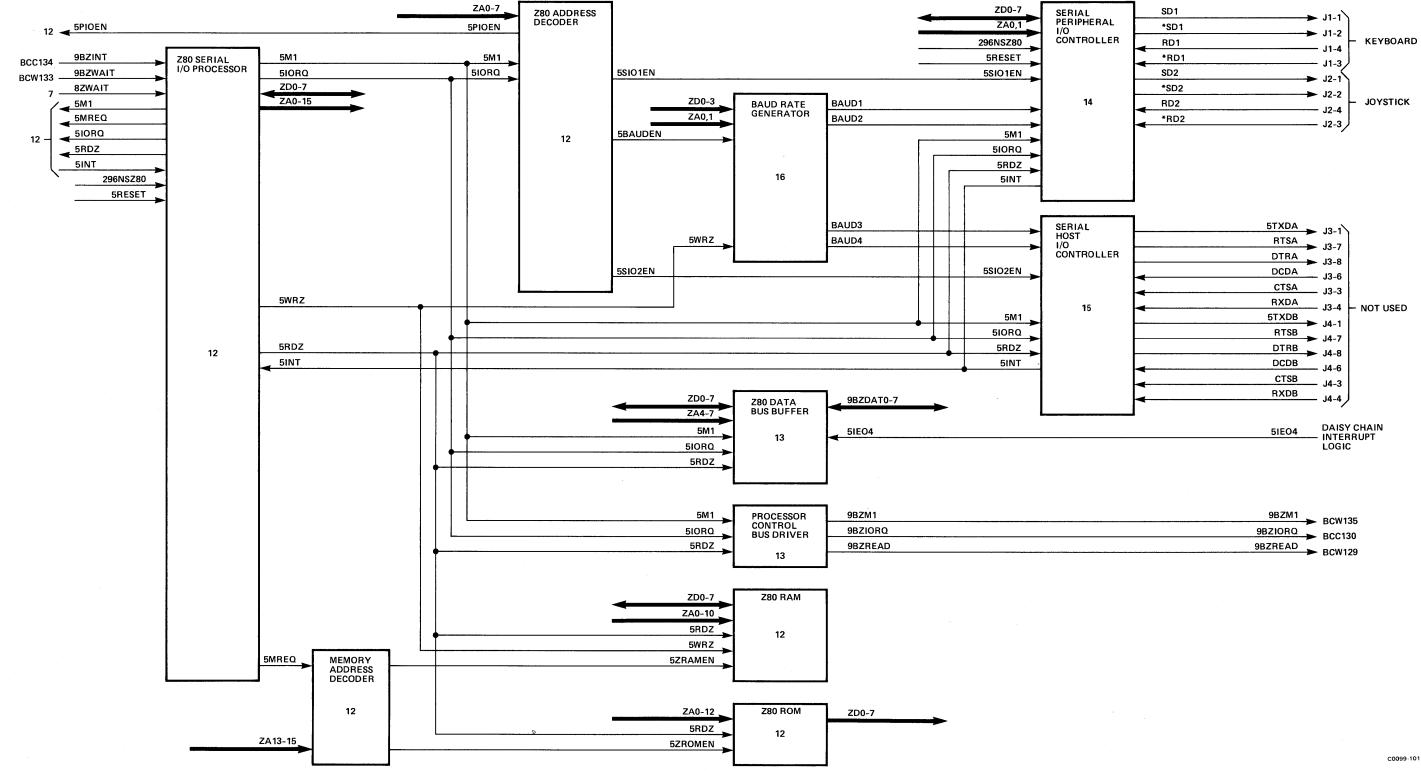

|     | 4.5.1   | System Processor PCB (Z80)          |      |

|     | 4.5.2   | System Processor PCB (68000)        |      |

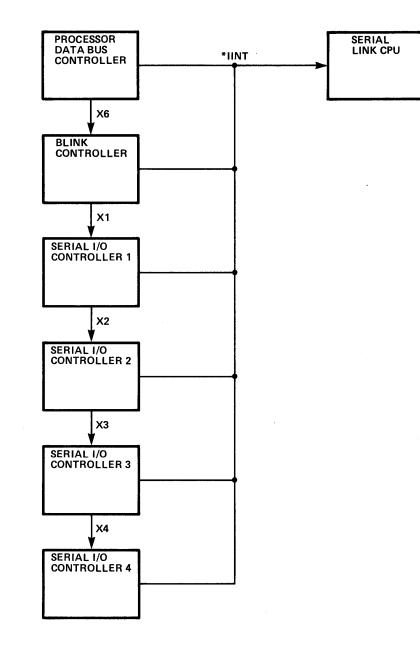

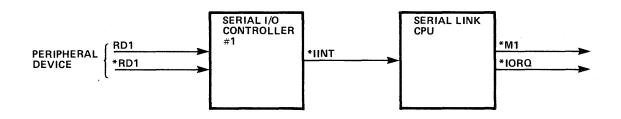

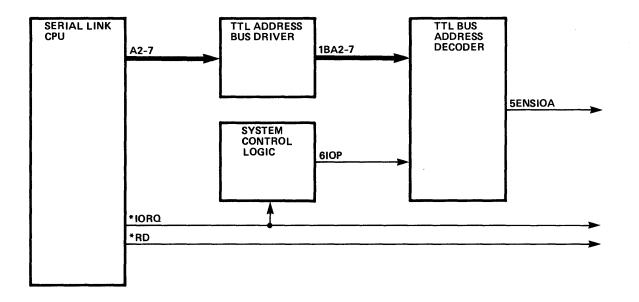

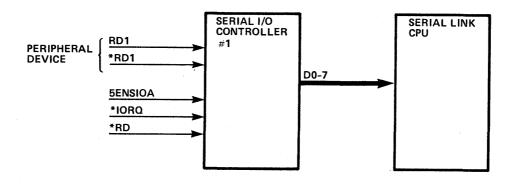

|     | 4.5.3   | Serial Link PCB                     |      |

|     | 4.5.4   | MCP2 PCB                            |      |

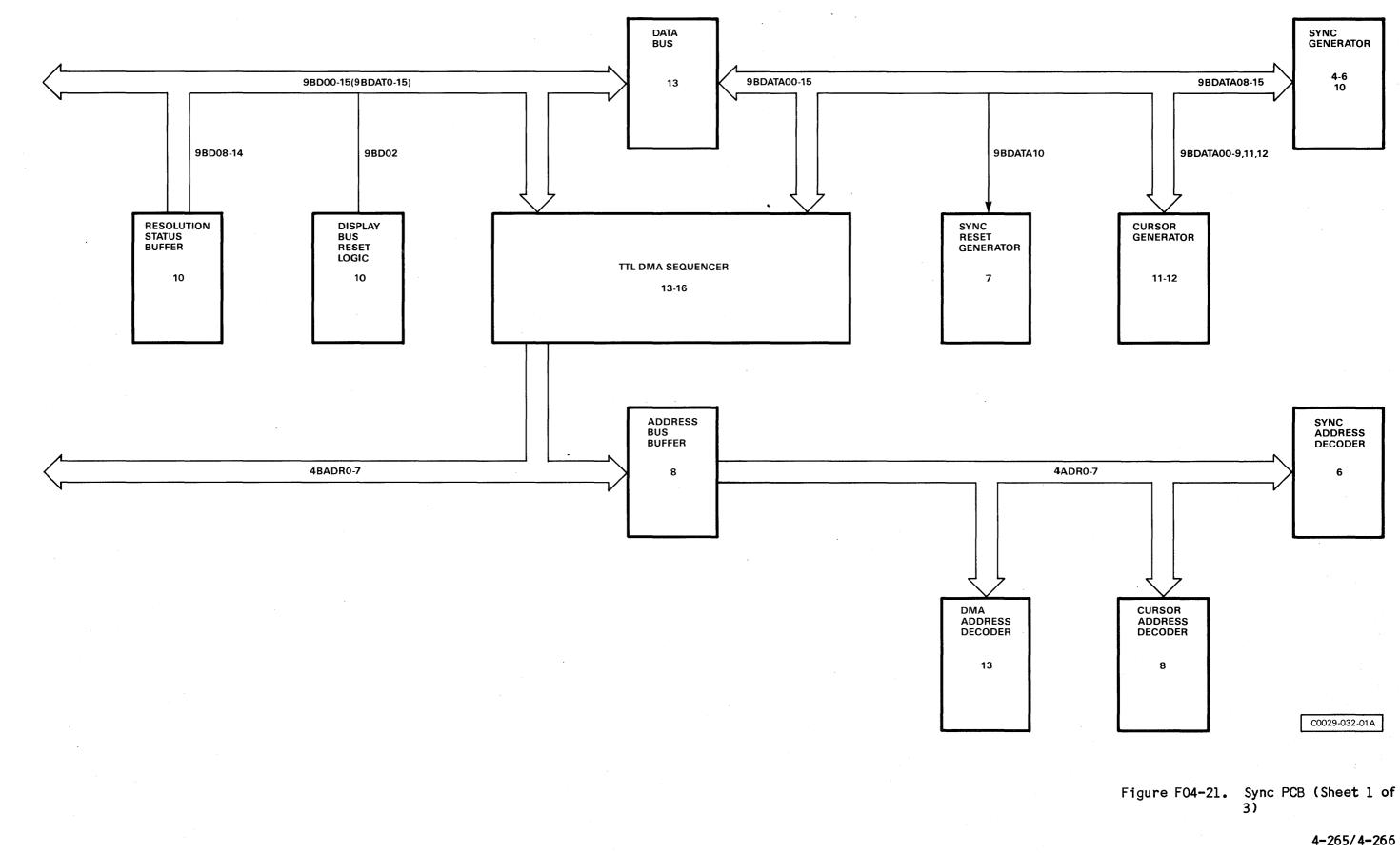

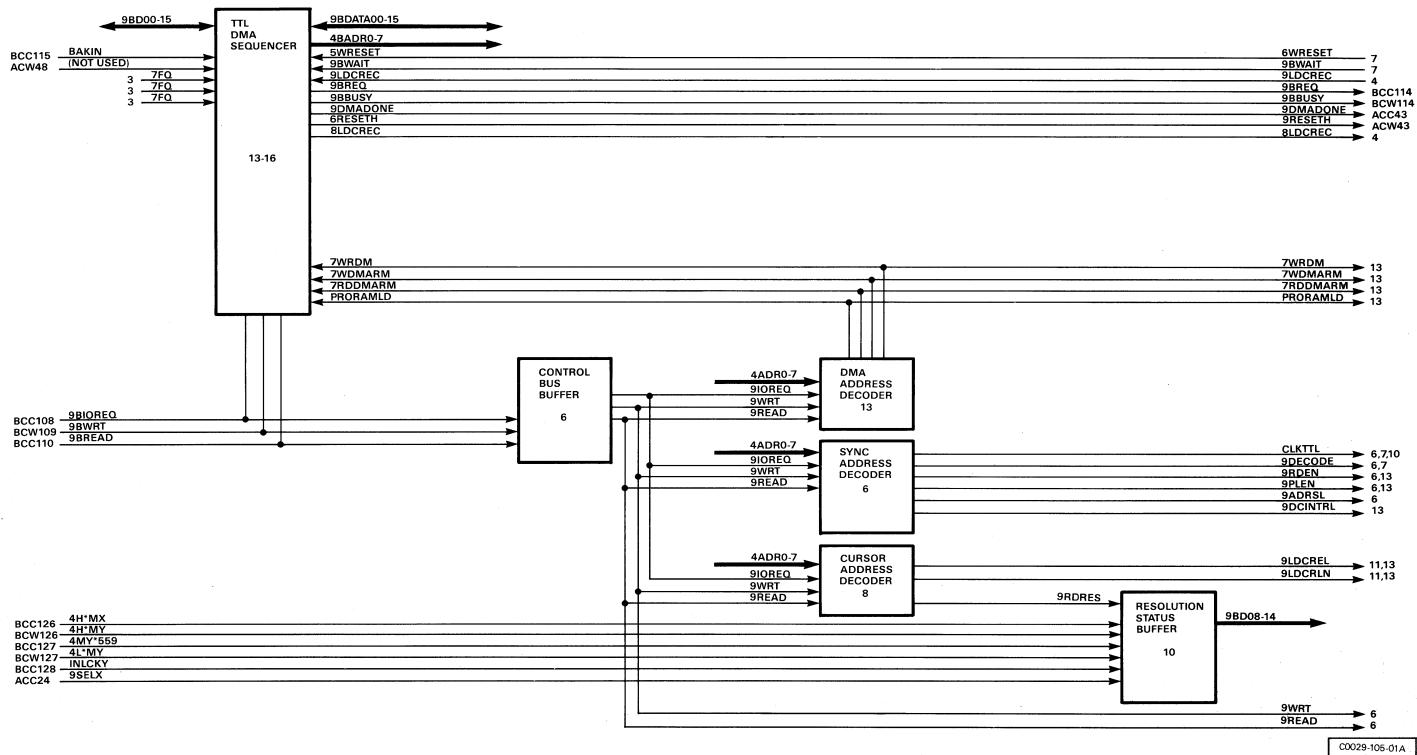

|     | 4.5.5   | Sync PCB                            |      |

| Paragraph |

|-----------|

|-----------|

| Page |

|------|

|------|

| 4.5.6   | Memory PCB            |   |

|---------|-----------------------|---|

| 4.5.7   | Video 7 PCB           |   |

| 4.5.8   | Backplane             |   |

| 4.5.9   | AC Power Distribution |   |

| 4.5.10  | Expansion PCB         |   |

|         | Video 1 PCB           |   |

| 4.5.11A | Video 6 PCB           | l |

| 4.5.12  | Video 8 PCB           |   |

| 4.5.13  | Video 12 PCB          |   |

| 4.5.14  | Video Load PCB        |   |

| 4.5.15  | Pixel Formatter PCB   |   |

| 4.5.16  | Transform PCB         | l |

# Chapter 5. MAINTENANCE

| 5.1 | INTRODUCTION                                     | 5-1 |

|-----|--------------------------------------------------|-----|

| 5.2 | TOOLS AND TEST EQUIPMENT                         | 5-1 |

| 5.3 | PREVENTIVE MAINTENANCE                           | 5-1 |

| 5.4 | CORRECTIVE MAINTENANCE                           | 5-1 |

|     | 5.4.1 Troubleshooting Hints                      | 5-2 |

|     | 5.4.2 Diagnostics                                |     |

| 5.5 | REMOVAL AND REPLACEMENT.                         | 5-2 |

|     | 5.5.1 Power Supply Removal and Replacement       | 5-2 |

|     | 5.5.2 PCB Removal and Replacement.               |     |

|     | 5.5.3 Fan Plate Assembly Removal and Replacement | 5-9 |

| 5.6 | PERFORMANCE VERIFICATION                         |     |

# Chapter 6. PARTS LIST

| 6.2 | INTRODUCTION<br>PARTS LIST<br>ORDERING INFORMATION | • | •   | •  | •  | • | •  | • | •  | •  |     | •   | • |   | • | • |   | • |   | • | • | • | • |   | 6-1   |

|-----|----------------------------------------------------|---|-----|----|----|---|----|---|----|----|-----|-----|---|---|---|---|---|---|---|---|---|---|---|---|-------|

|     |                                                    | A | ١pp | en | di | x | Α. | • | GL | _0 | SSI | ٩R١ | ( |   |   |   |   |   |   |   |   |   |   |   |       |

| A.1 | INTRODUCTION                                       | • | •   | •  | •  | • | •  | • | •  | •  | •   | ٠   | • | • | • | • | • | • | • | • | • | • | • | • | . A-1 |

# Appendix B. INDEX

| ~ . | THERACHART   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | -          | - |

|-----|--------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------------|---|

| 8•1 | INTRODUCTION | • | • | • | • | • | ٠ | ٠ | ٠ | • | ٠ | ٠ | • | • | ٠ | ٠ | ٠ | ٠ | • | ٠ | ٠ | ٠ | ٠ | ٠ | ٠ | • | ٠ | ٠ | <b>B</b> 3 | T |

TABLES

|   | Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                  | Page                                                                                                                                                                                                                                                                                          |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10<br>2-11<br>2-12<br>2-13<br>2-14<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-15<br>2-1 | Related Documents                | Page<br>1-4<br>1-6<br>1-8<br>1-9<br>1-13<br>1-34<br>2-3<br>2-11<br>2-12<br>2-12<br>2-13<br>2-14<br>2-14<br>2-15<br>2-15<br>2-17<br>2-18<br>2-18<br>2-19<br>2-20<br>2-21<br>2-22<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-26<br>3-2<br>4-6<br>4-11<br>4-15<br>4-15<br>4-21<br>4-24 |

|   | 4-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Memory PCB Signal Descriptions   | 4-24                                                                                                                                                                                                                                                                                          |

|   | 4-7<br>4-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Video 7 PCB Signal Descriptions  | 4-26<br>4-28                                                                                                                                                                                                                                                                                  |

|   | 4-0<br>4 <b>-</b> 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Video 1 PCB Signal Descriptions. | 4-20<br>4 <b>-</b> 31                                                                                                                                                                                                                                                                         |

| I | 4 <b>-</b> 9a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Video 6 PCB Signal Descriptions  | 4 <b>-</b> 31a                                                                                                                                                                                                                                                                                |

|   | 4-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Video 8 PCB Signal Descriptions  | 4-32                                                                                                                                                                                                                                                                                          |

|   | 4-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Video 12 PCB Signal Descriptions | 4-34                                                                                                                                                                                                                                                                                          |

### Page

Page

## Table

| 4-12 | Pixel Formatter PCB Signal Descriptions         |

|------|-------------------------------------------------|

| 4-13 | Transform Processor PCB Signal Descriptions     |

| 4-14 | Cursor Generator Equivalent Signals             |

| 4-15 | Serial I/O Controller Corresponding Signals     |

| 4-16 | Software - Internal Cable Conductor Assignments |

| 4-17 | Hardware - Internal Cable Conductor Assignments |

| 4-18 | Jack Jl Signals                                 |

| 5-1  | Fault Isolation Procedures                      |

| 6-1  | 9460 Standard Spares                            |

# FIGURES

| Figure           |                                                | Page  |

|------------------|------------------------------------------------|-------|

| 1-1              | 9460                                           | 1-10  |

| 1-2              | Chassis Assembly                               | 1-11  |

| 1-3              | Fan Plate Assembly                             | 1-14  |

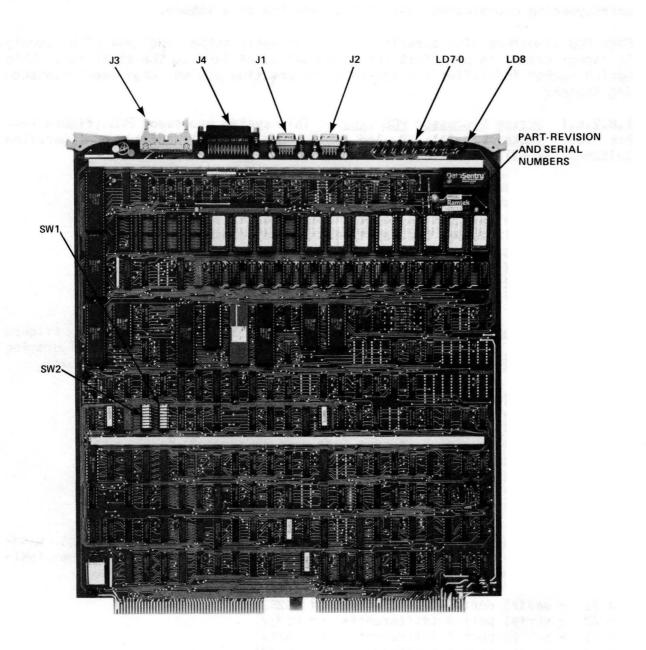

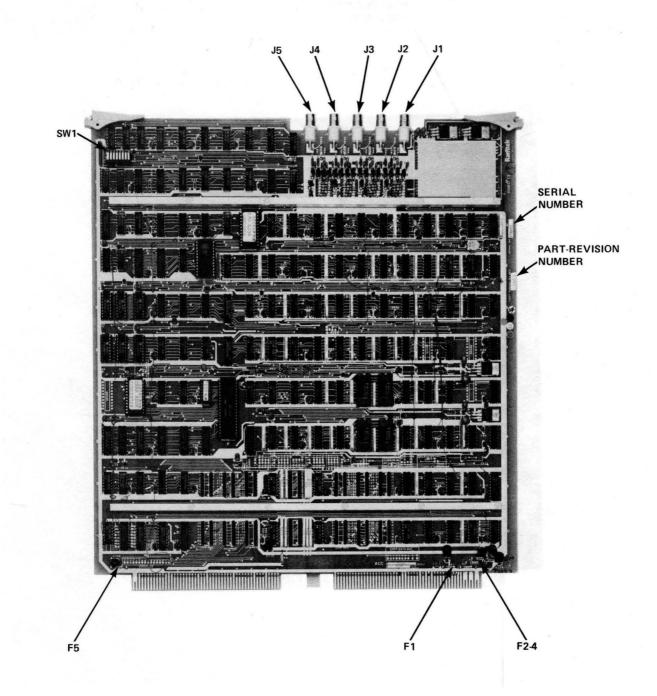

| 1-4              | System Processor PCB (Z80)                     | 1-16  |

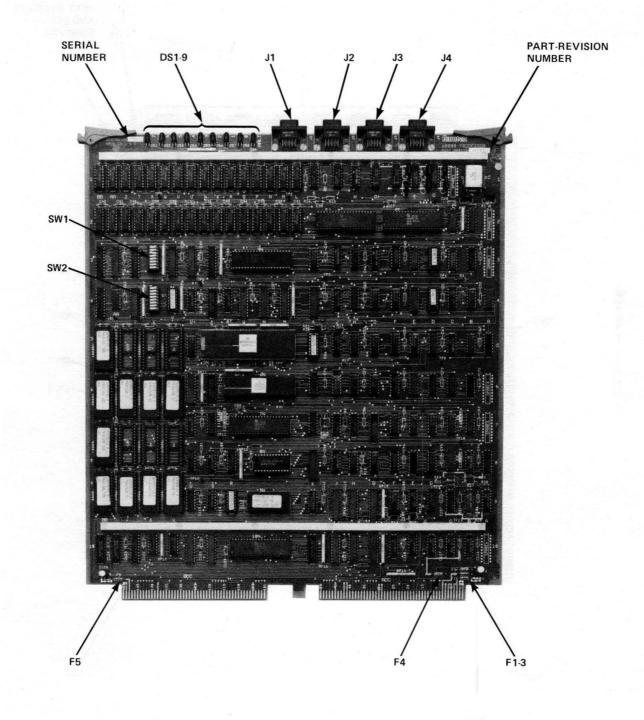

| 1-5              | System Processor PCB (MC68000)                 | 1-17  |

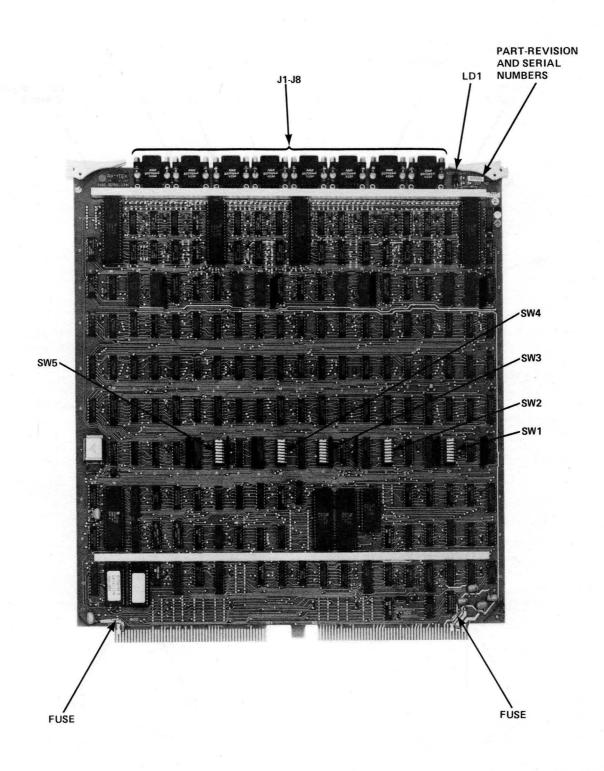

| 1-6              | Serial Link PCB                                | 1-18  |

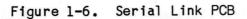

| 1-7              | MCP2 PCB                                       | 1-20  |

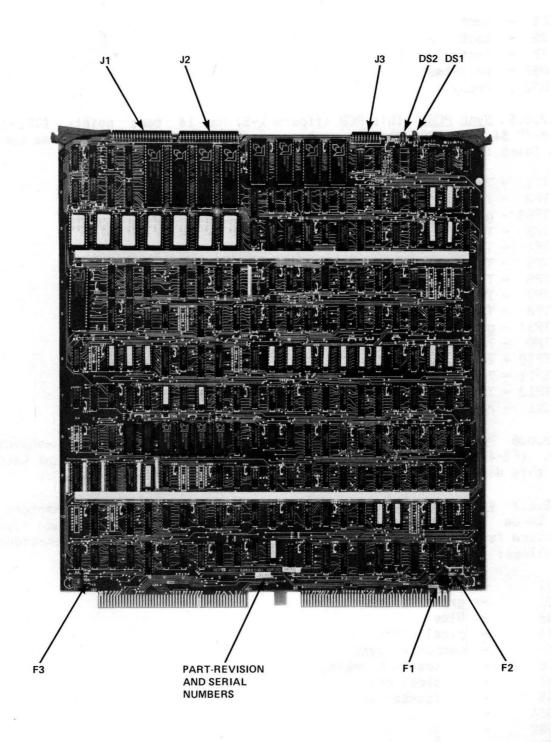

| 1-8              | Sync PCB                                       | 1-21  |

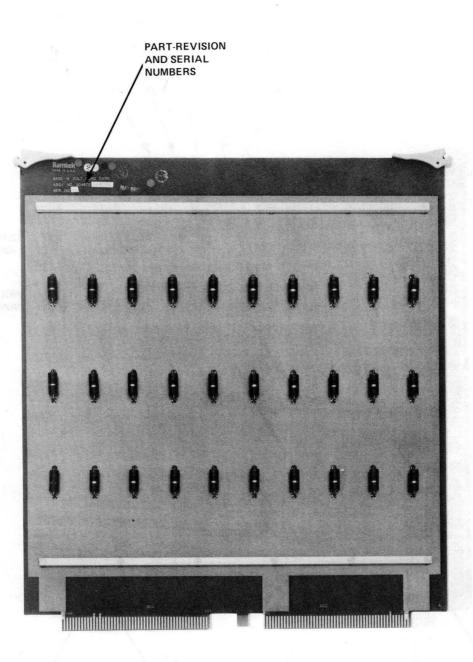

| 1-9              | Memory PCB                                     | 1-22  |

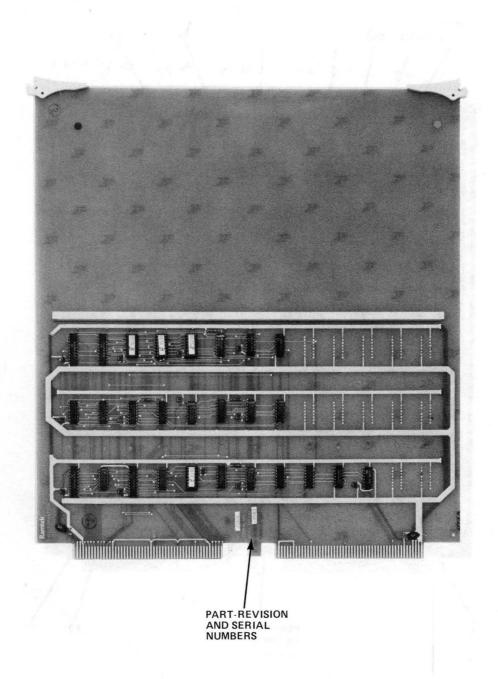

| 1-10             | Video 7 PCB                                    | 1-23  |

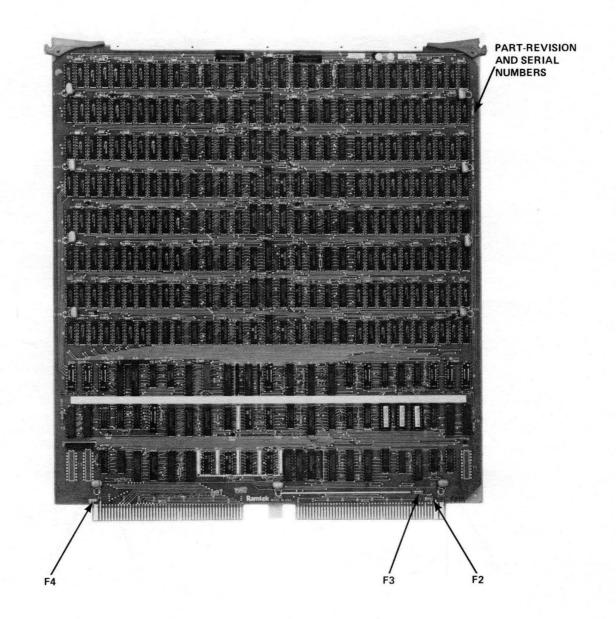

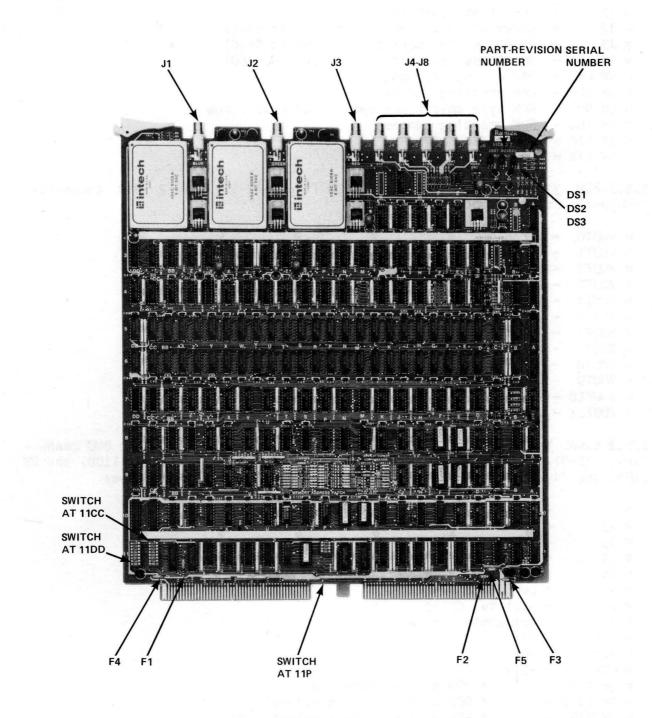

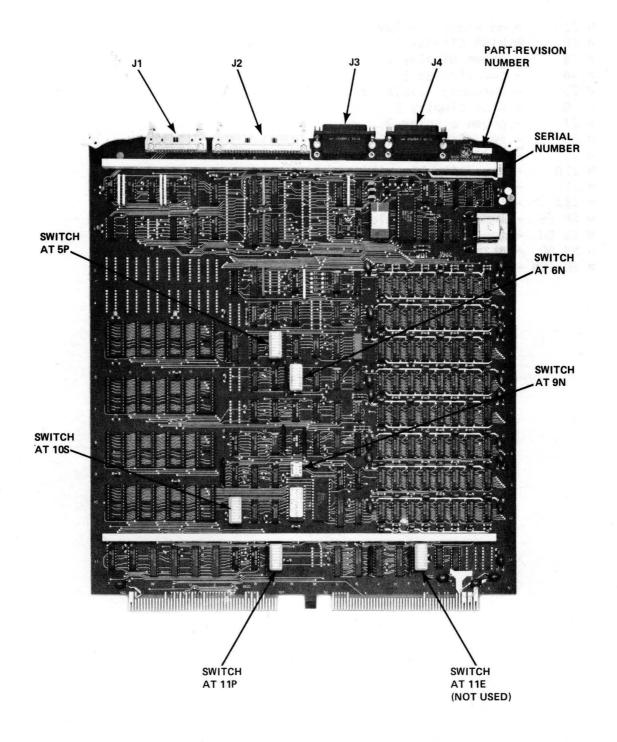

| 1-11             | Expansion PCB                                  | 1-24b |

| 1-12             | Video 1 PCB                                    | 1-25  |

| 1 <b>-</b> 12a   | Video 6 PCB                                    | 1-26  |

| 1-13             | Video 8 PCB                                    | 1-27  |

| 1-14             | Video 12 PCB                                   | 1-29  |

| 1-15             | Video Load PCB                                 | 1-30  |

| 1-16             | Pixel Formatter PCB                            | 1-31  |

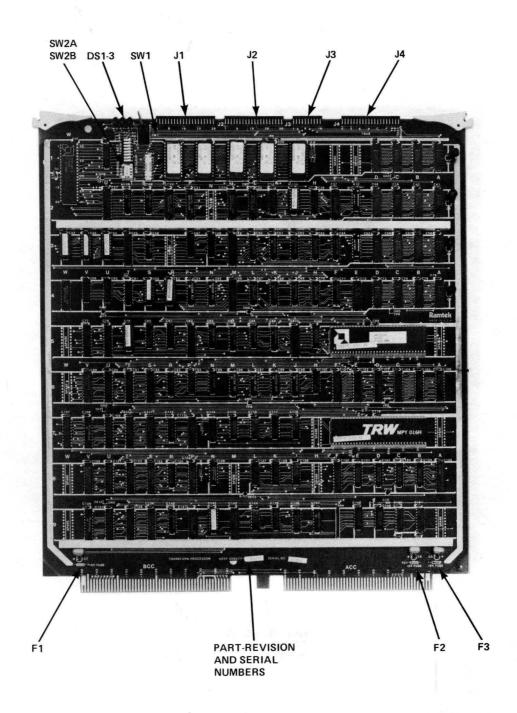

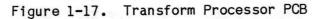

| 1-17             | Transform Processor PCB                        | 1-32  |

| 2-1              | Representative Installation Signal Connections | 2-9   |

| 2-2              | Video 7 PCB Resistor Pack Position             | 2-16  |

| 2-3              | Video 7 PCB Any-to-Any Patches                 | 2-16  |

| 2-3a             | Video 6 PCB Any-to-Any Patches                 | 2-18b |

| 2-4              | Video 8 PCB Jumper Status                      | 2-21  |

| 2-5              | Cursor To Display Assignments                  | 2-22  |

| 2-6              | Video 8 PCB Any-to-Any Patching                | 2-23  |

| 2 <del>-</del> 7 | Video 12 PCB Strapping Location Diagram        | 2-24  |

| F02-1            | Rack Mount Installation                        | 2-29  |

| 3-1              | Controls and Indicators                        | 3-1   |

| 4-1              | Generalized Computer Graphics System           | 4-3   |

| 4-2              | 9460 Status Readout                            | 4-52  |

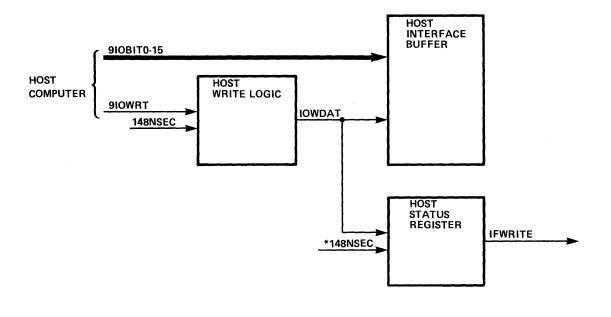

| 4-3              | Host Data Input.                               | 4-53  |

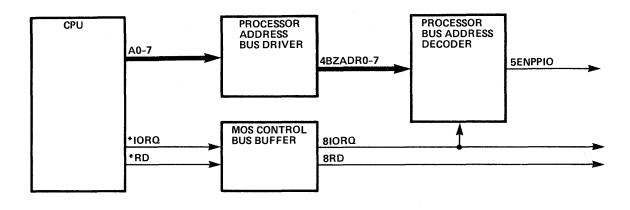

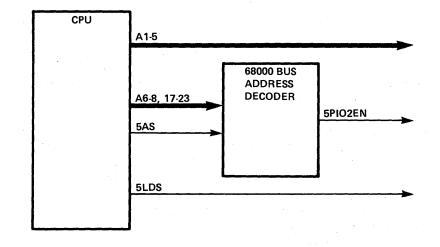

| 4-4              | Status Read Control.                           | 4-54  |

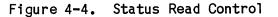

| 4-5              | Host Status Readout.                           | 4-54  |

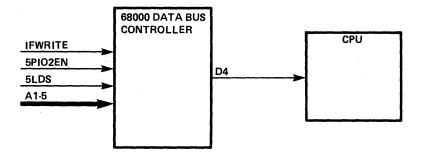

| 4-6              | Data Bus Control                               | 4-55  |

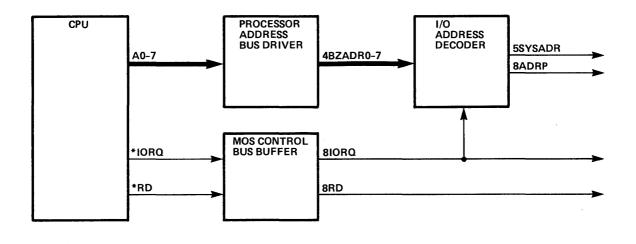

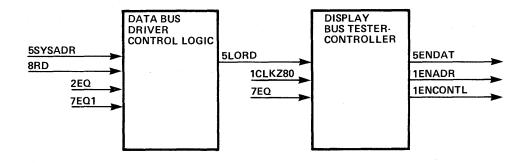

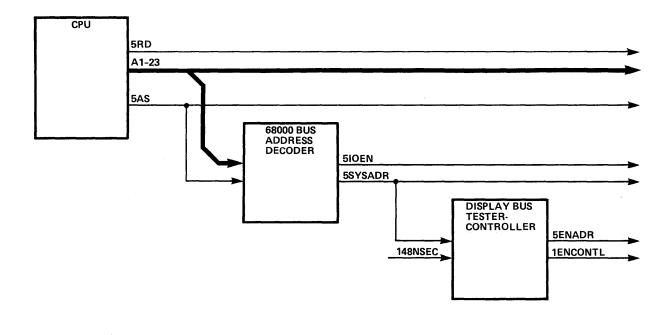

| 4-7              | Display Bus Test                               | 4-56  |

|                  |                                                |       |

Figure

| 4-8               | Data Read Control                                             |   |

|-------------------|---------------------------------------------------------------|---|

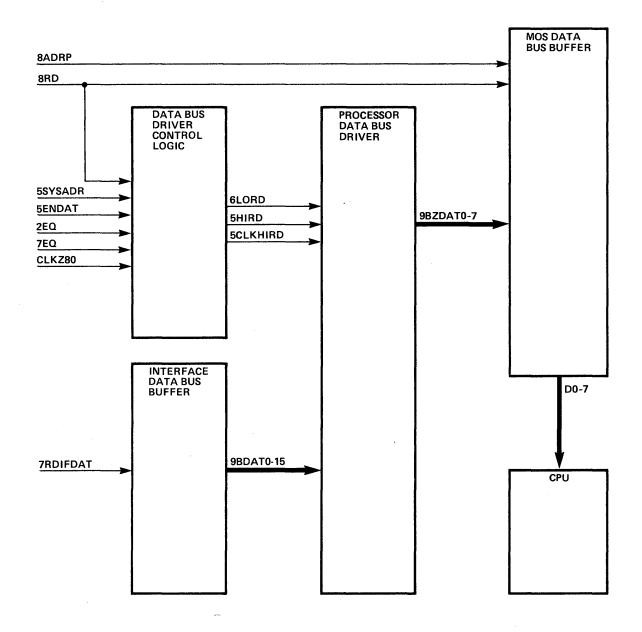

| 4-9               | Host Data Transfer                                            |   |

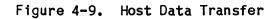

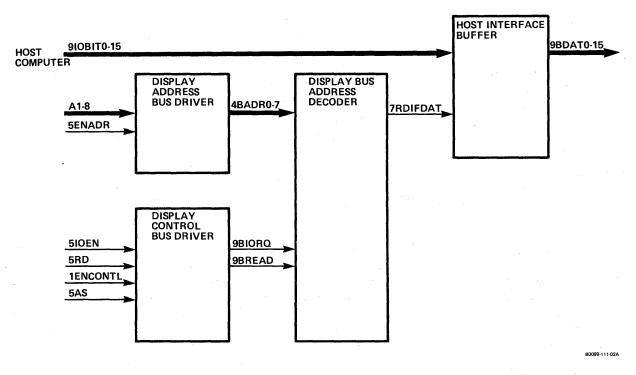

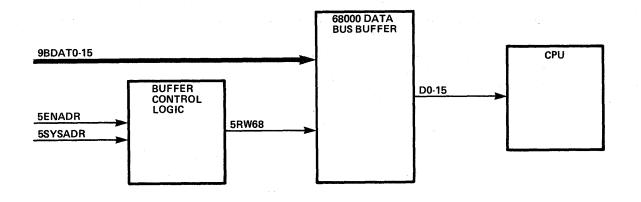

| 4-10              | Data Storage                                                  | - |

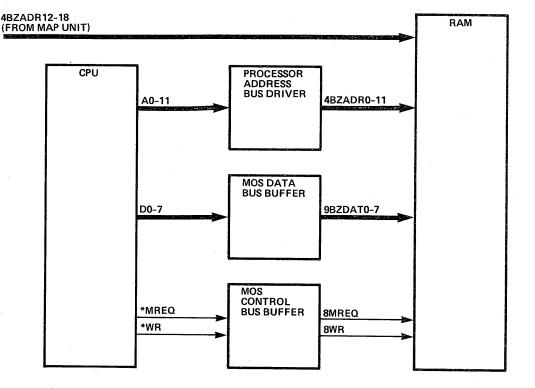

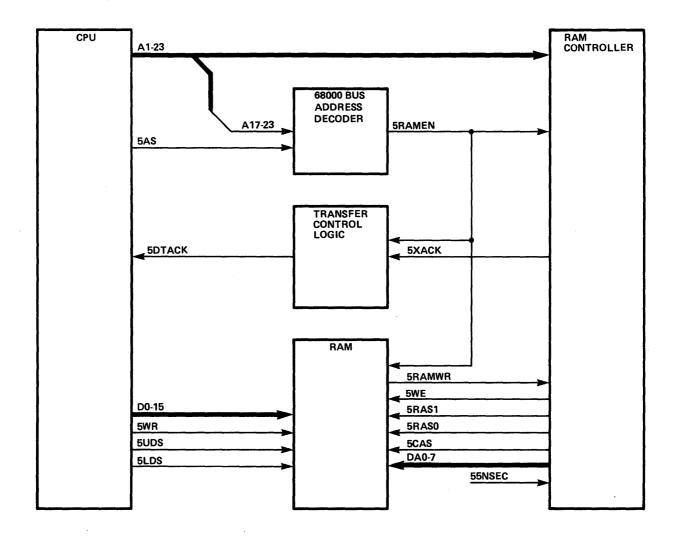

| 4-11              | RAM Access                                                    |   |

| 4-12              | RAM Output                                                    |   |

| 4-13              | Interrupt Request                                             | - |

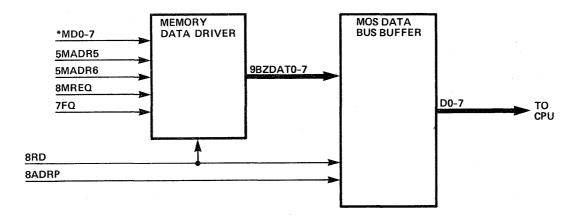

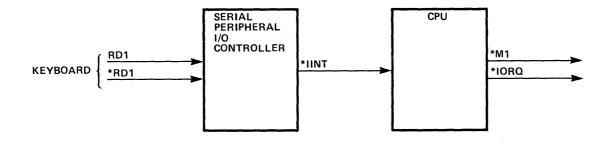

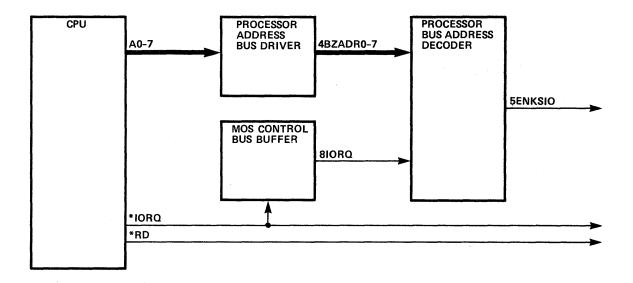

| 4-14              | Keyboard Read Control                                         |   |

| 4-15              | Keyboard Data Transfer                                        |   |

| 4-16              | Remote Interrupt Request                                      |   |

| 4-17              | Remote Read Control                                           | ŀ |

| 4-18              | 9460 Status Readout Block Diagram                             | ) |

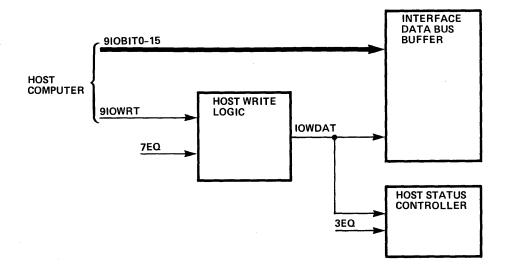

| 4-19              | Host Data Input Block Diagram                                 | 1 |

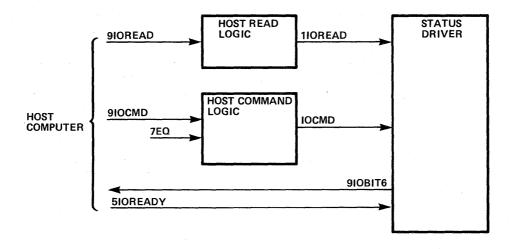

| 4-20              | Status Read Control Block Diagram                             | 1 |

| 4-21              | Host Status Readout Block Diagram                             | 3 |

| 4-22              | Data Transfer Control Block Diagram                           | ) |

| 4-23              | Data Read Control Block Diagram                               | ) |

| 4-24              | Host Data Transfer Block Diagram                              | ) |

| 4-25              | Data Storage                                                  |   |

| 4-26              | RAM Readout                                                   |   |

| 4-27              | ROM Readout Block Diagram                                     |   |

| 4-28              | Output Control Block Diagram                                  |   |

| 4-29              | Data Output Block Diagram                                     |   |

| 4-30              | Z80 Interrupt Request Block Diagram                           |   |

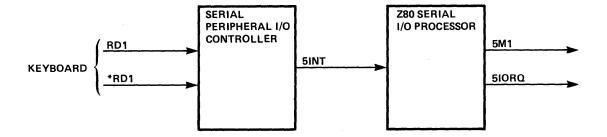

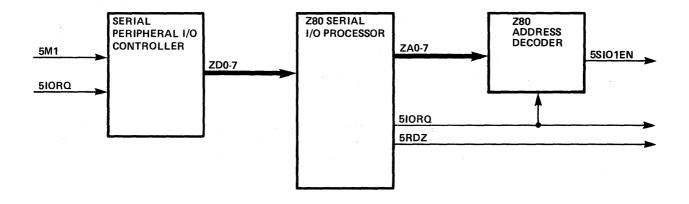

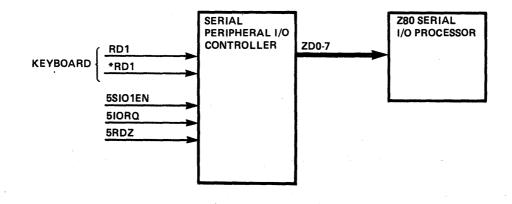

| 4-31              | Vector Transfer Block Diagram                                 |   |

| 4-32              | Keyboard Data Transfer Block Diagram                          |   |

| 4-33              | Data Transfer to Z80 Data Bus Controller                      |   |

| 4-34              | Data Transfer to 68000 Data Bus Controller Block Diagram 4-88 |   |

| 4-35              | Data Transfer to CPU Block Diagram                            |   |

| 4-36              | Remote Interrupt Request Block Diagram                        |   |

| 4-30<br>4-37      | Remote Vector Transfer Block Diagram                          |   |

| 4-37              |                                                               |   |

| 4-30<br>4-39      |                                                               |   |

| 4-39<br>4-40      | Remote Data Transfer Block Diagram                            |   |

| 4-40              | Cursor RAM Logic                                              | ) |

| 4-41              | Interrupt Priority Daisy Chain                                |   |

|                   | Internal Interrupt Request                                    |   |

| 4-43              | Data Input Control                                            |   |

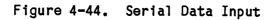

| 4-44              | Serial Data Input                                             |   |

| 4-45              | Serial Link RAM Control                                       |   |

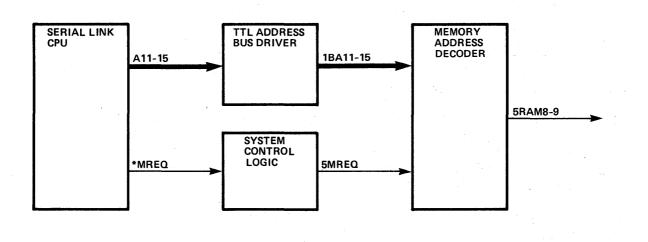

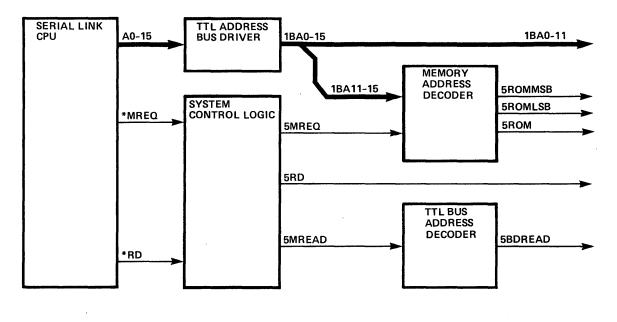

| 4-46              | Serial Link RAM Storage                                       |   |

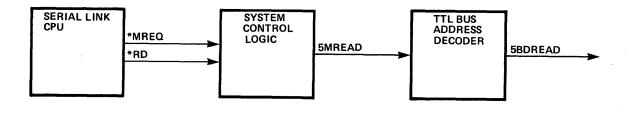

| 4-47              | Serial Link RAM Readout Control                               |   |

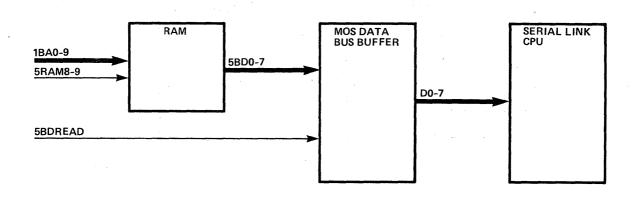

| 4-48              | Serial Link RAM Readout                                       |   |

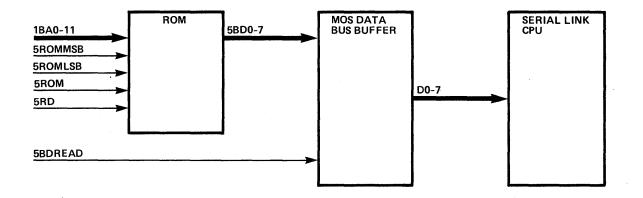

| 4-49              | ROM Readout Control                                           |   |

| 4-50              | Serial Link ROM Readout                                       |   |

| 4-51              | Data Transfer Control                                         |   |

| 4 <b>-</b> 52     | Controller Status Readout                                     |   |

| 4 <b>-</b> 53     | External Interrupt Request                                    |   |

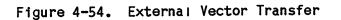

| 4-54              | External Vector Transfer                                      |   |

| 4-55              | Data Output Control                                           | ) |

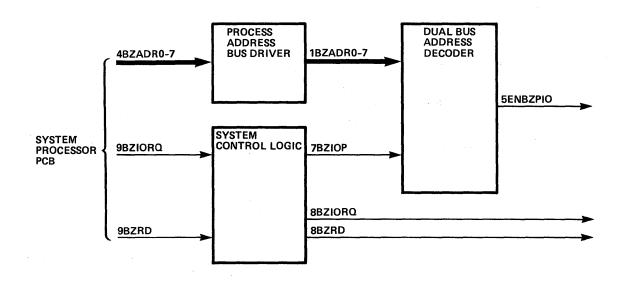

| 4-56              | Data Output                                                   |   |

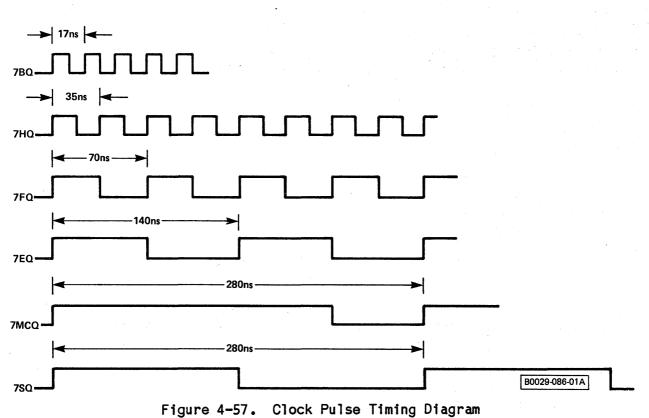

| 4 <del>-</del> 57 | Clock Pulse Timing Diagram                                    |   |

Figure

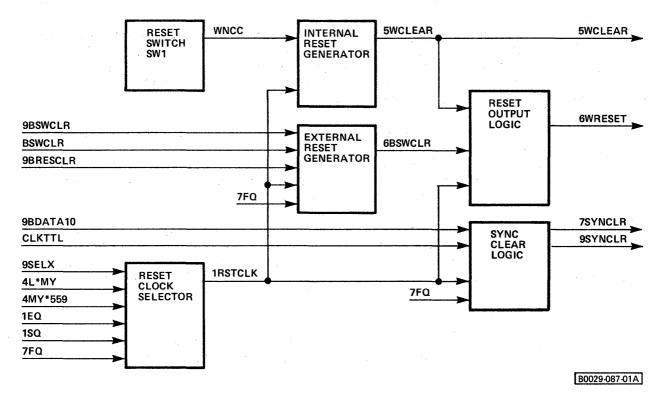

| 4-58                      | Sync Reset Circuit Block Diagram                                                                             |

|---------------------------|--------------------------------------------------------------------------------------------------------------|

| 4-59                      | Simplified Interface Logic Block Diagram                                                                     |

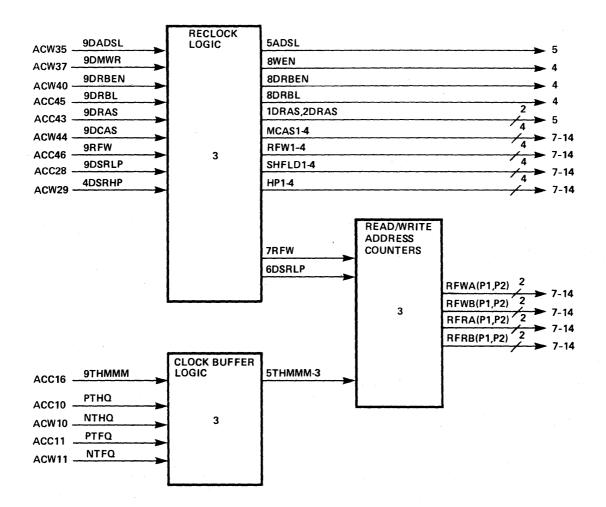

| 4-60                      | Simplified Data Control Logic Block Diagram                                                                  |

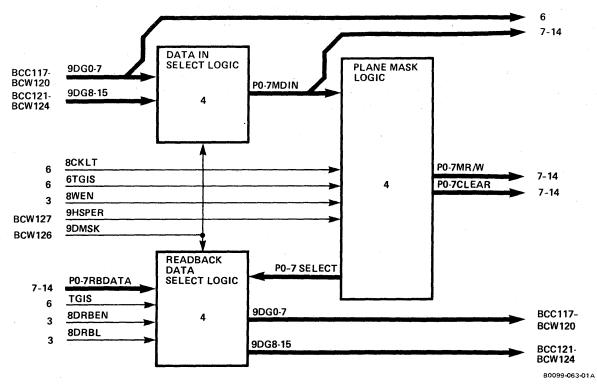

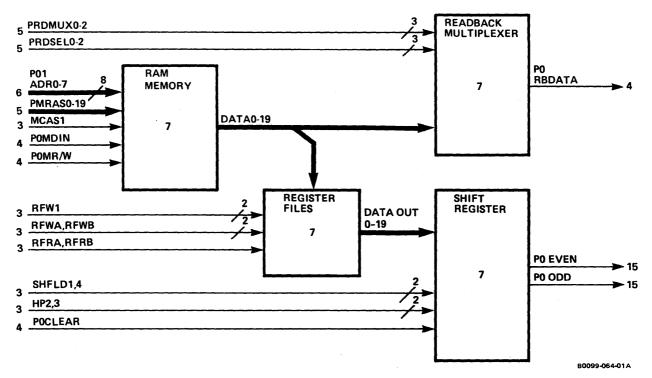

| 4-61                      | Simplified Memory Plane O Block Diagram                                                                      |

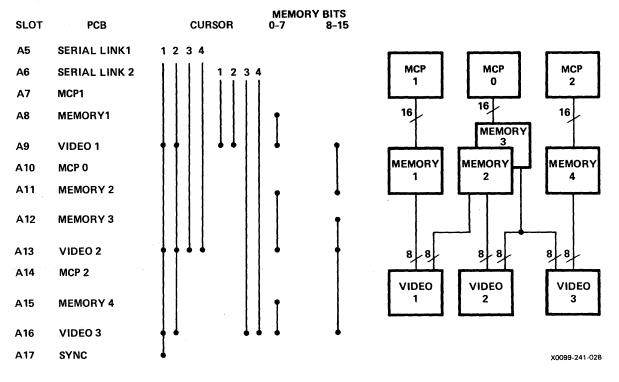

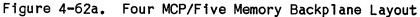

| 4-62                      | Three MCP/Four Memory Backplane Layout                                                                       |

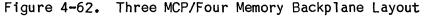

| 4-62a                     | Four MCP/Five Memory Backplane Layout                                                                        |

| 4-62b                     | Three MCP/Six Memory Backplane Layout                                                                        |

| 4-63                      | Backplane Connectors                                                                                         |

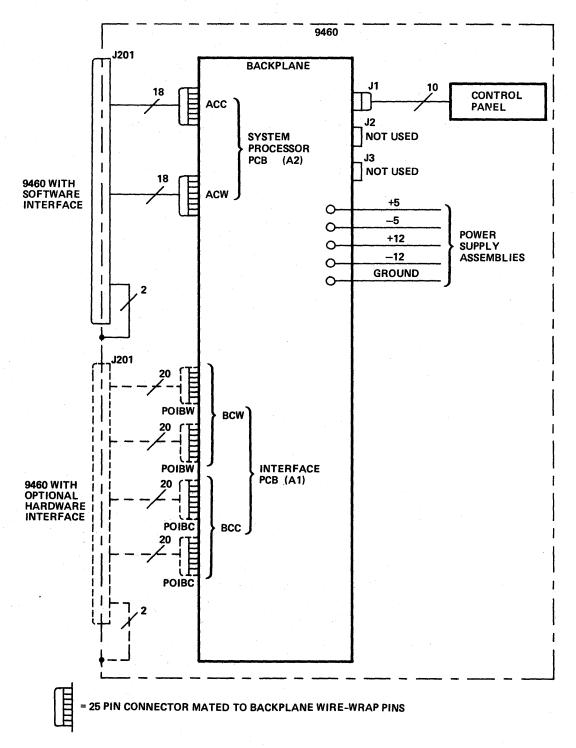

| 4-64                      | Bus Driver and Control Logic                                                                                 |

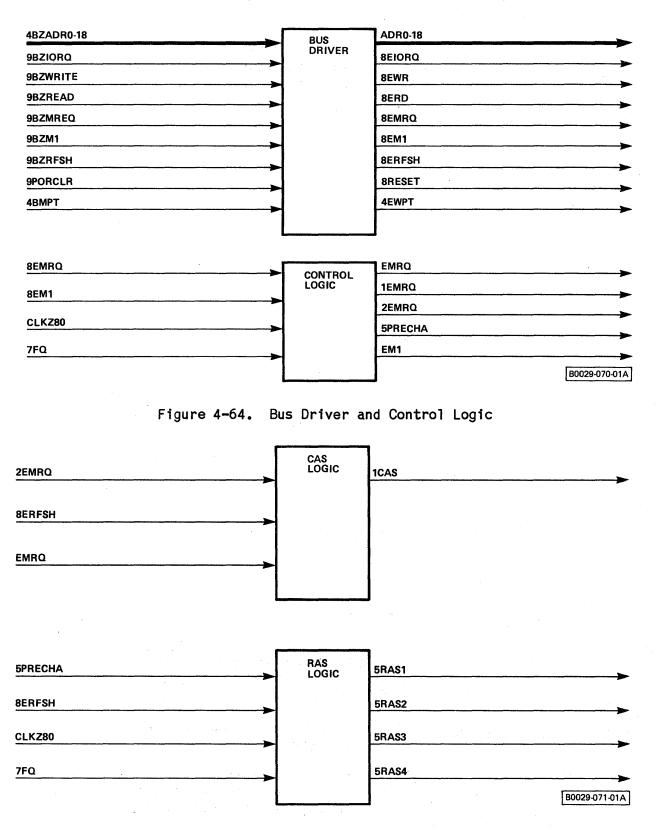

| 4-65                      | CAS and RAS Logic. $\ldots$ |

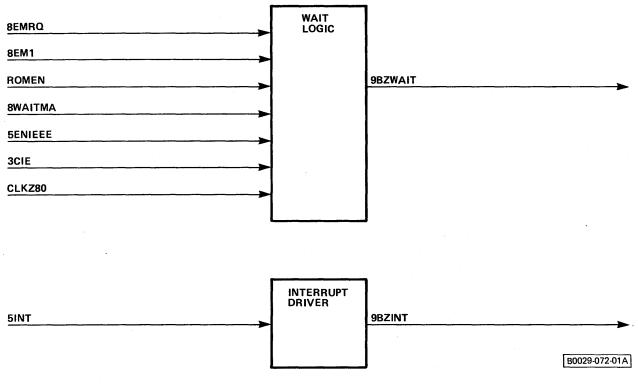

| 4-66                      | Wait and Interrupt Logic                                                                                     |

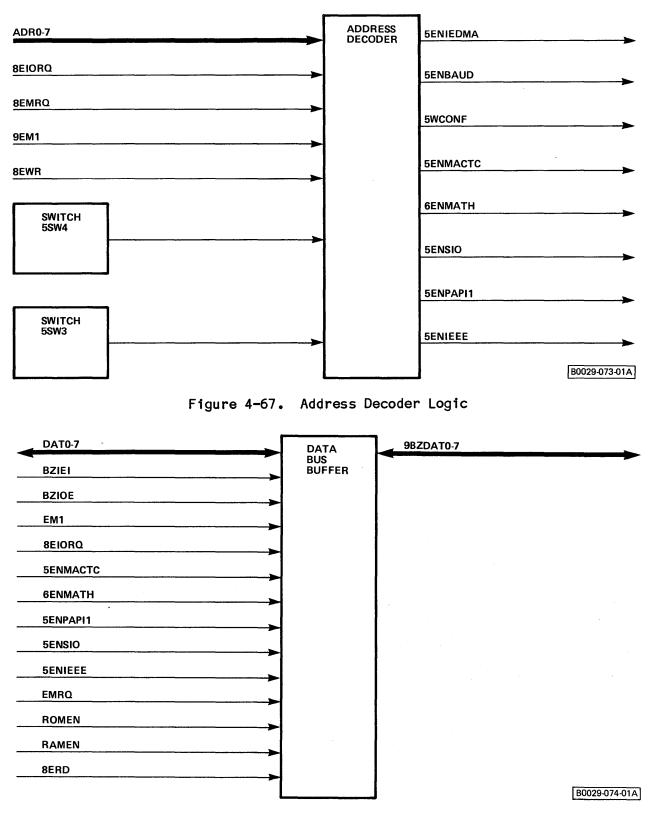

| 4 <b>-</b> 67             | Address Decoder Logic                                                                                        |

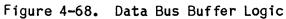

| 4-68                      | Data Bus Buffer Logic.                                                                                       |

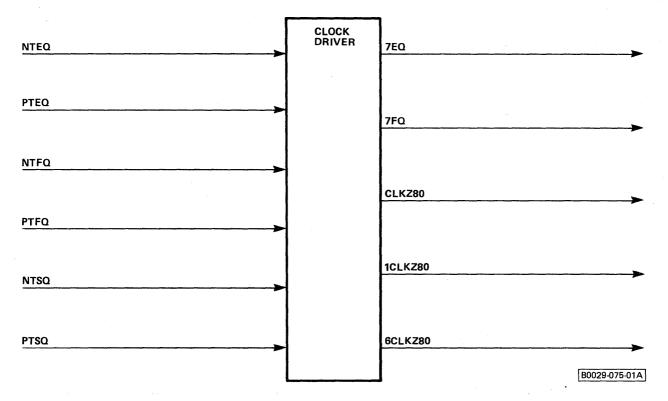

| 4-69                      | Clock Driver                                                                                                 |

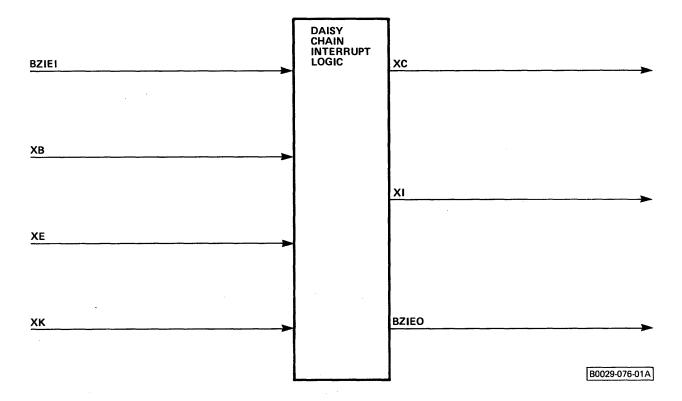

| 4-09<br>4-70              | Daisy Chain Interrupt Logic                                                                                  |

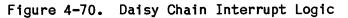

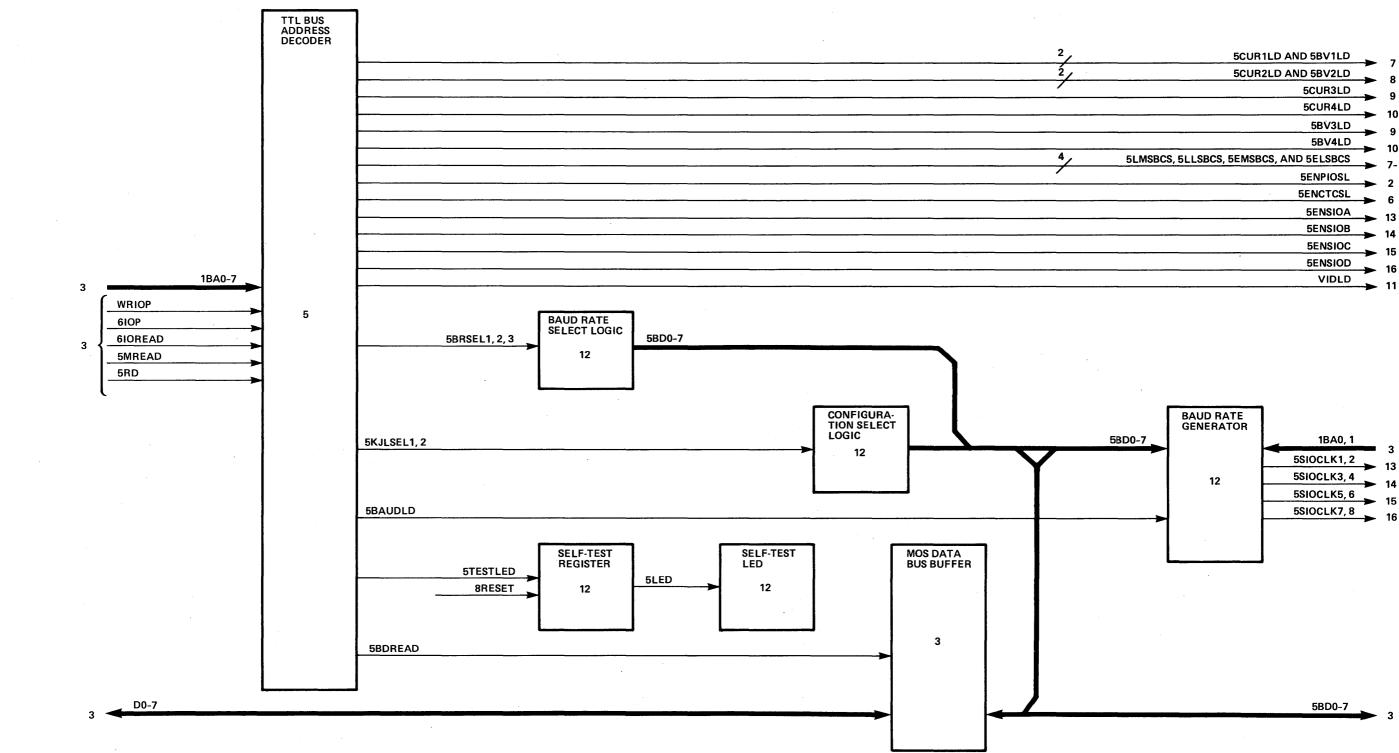

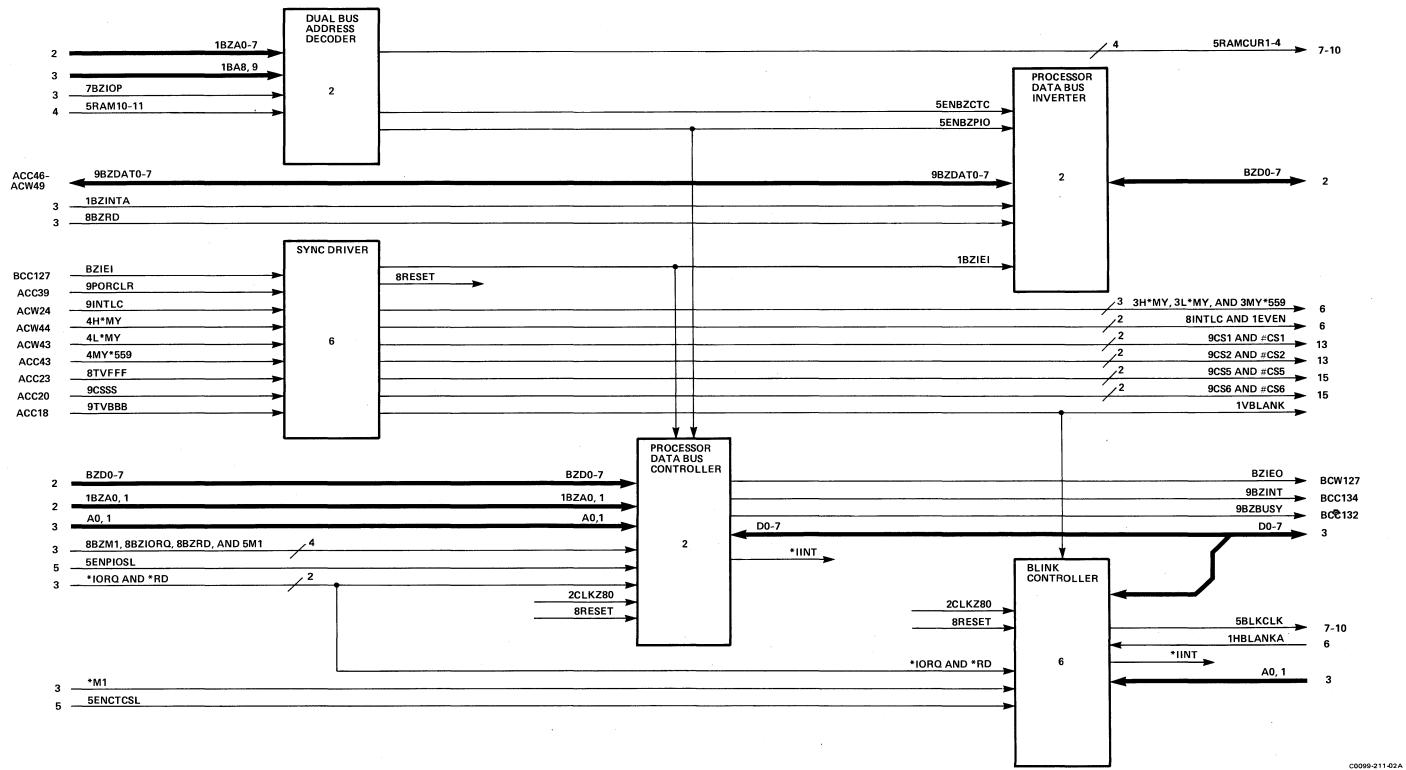

| 4-71                      | Baud Rate Generator and Busy Logic                                                                           |

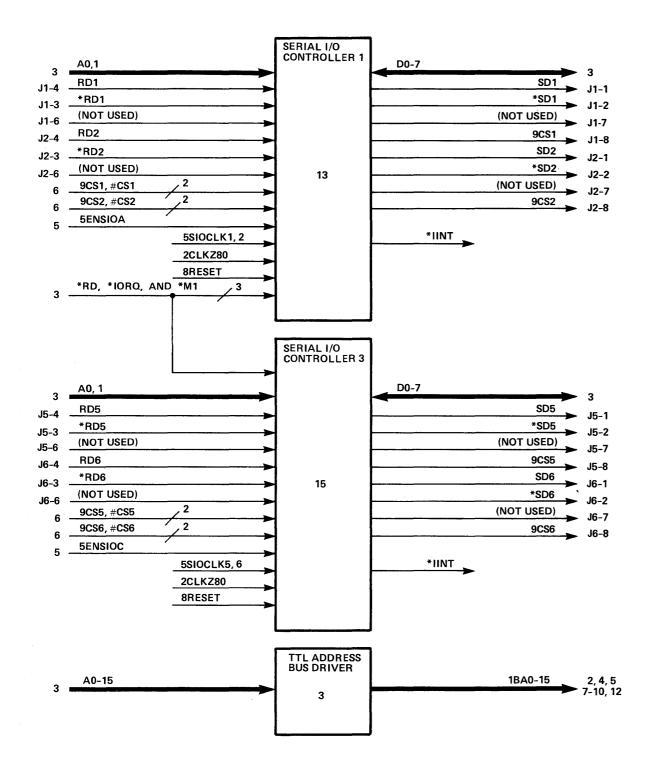

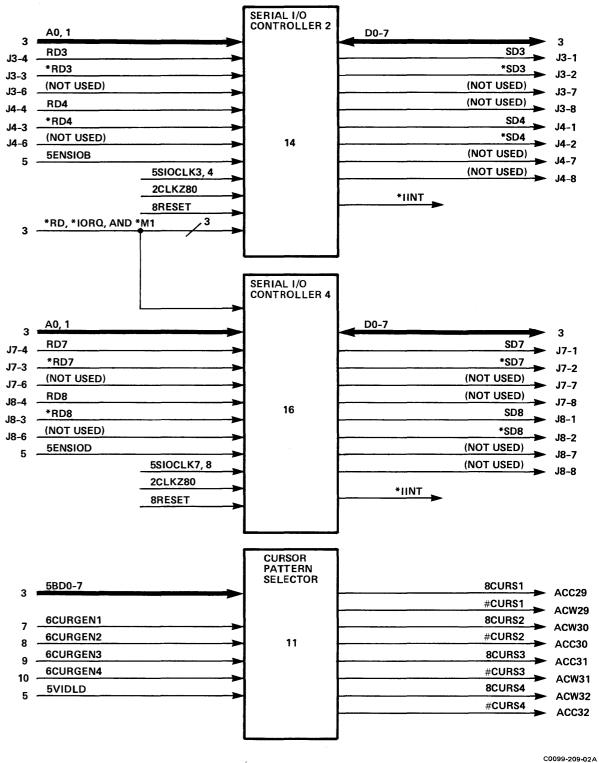

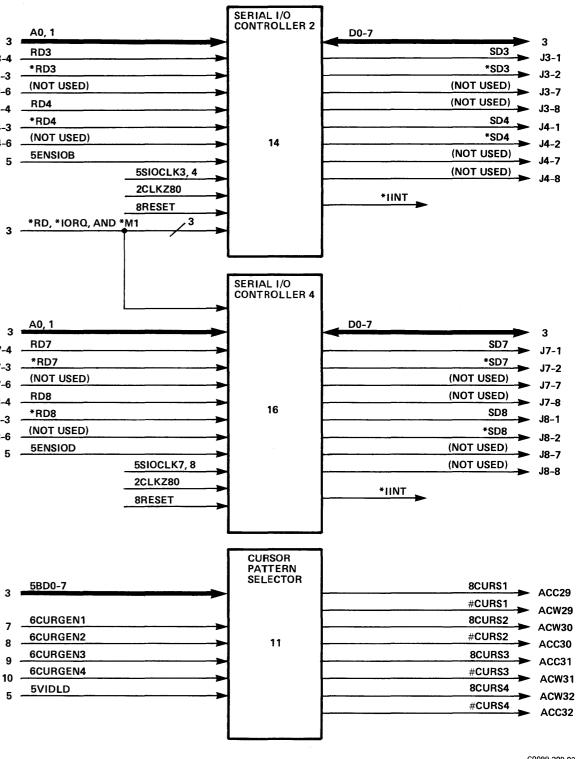

| 4-71                      | Serial I/O Controller                                                                                        |

| 4-72                      | Video 1 PCB Input Logic Block Diagram.                                                                       |

| 4-73<br>4-74              | Video 1 PCB Control Logic Block Diagram                                                                      |

| 4-74                      |                                                                                                              |

| 4 <del>-</del> 75<br>4-76 | Video 8 PCB Buffer Logic                                                                                     |

|                           | Video 8 PCB Graphics Logic                                                                                   |

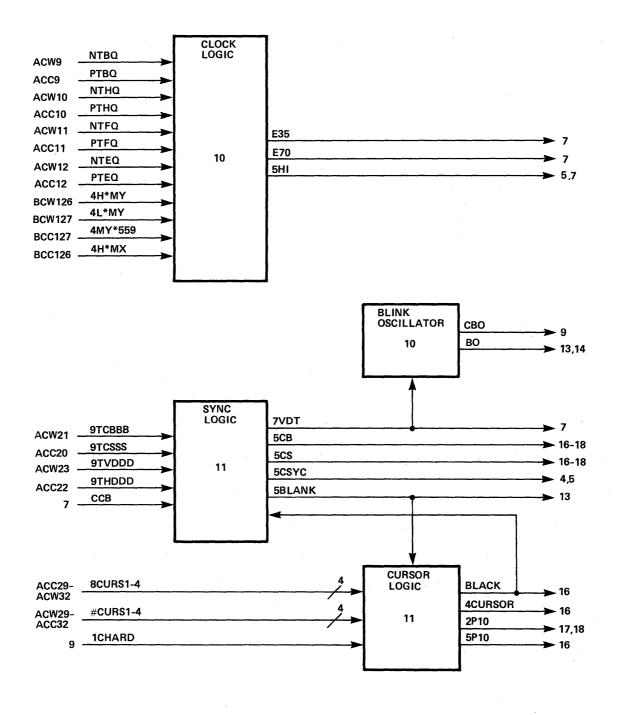

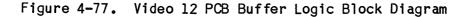

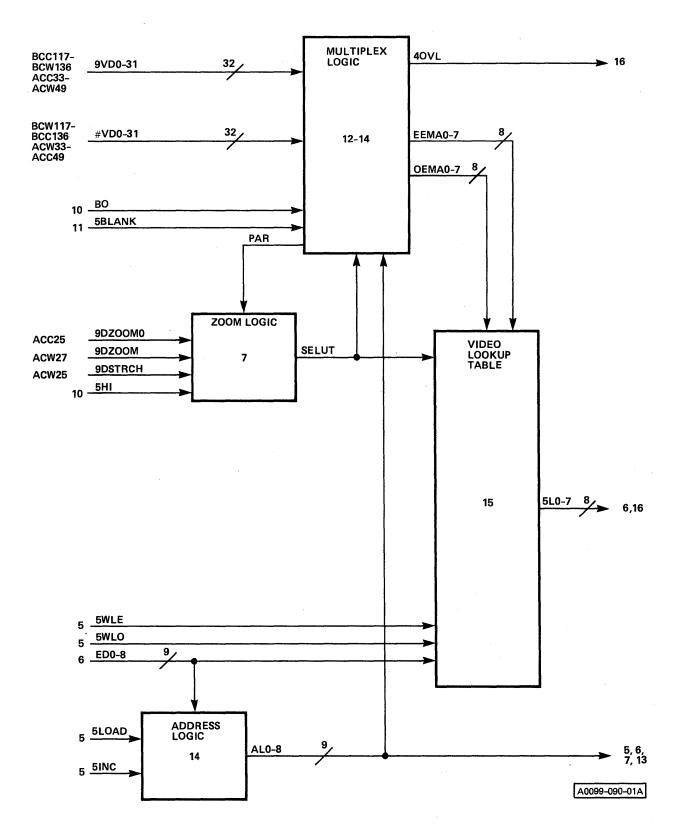

| 4-77                      | Video 12 PCB Buffer Logic Block Diagram                                                                      |

| 4-78                      | Text Logic Block Diagram                                                                                     |

| 4-79                      | Graphics Logic Block Diagram                                                                                 |

| 4-80                      | Video Load PCB Schematic Diagram                                                                             |

| 4-81                      | Pixel Formatter PCB Block Diagram                                                                            |

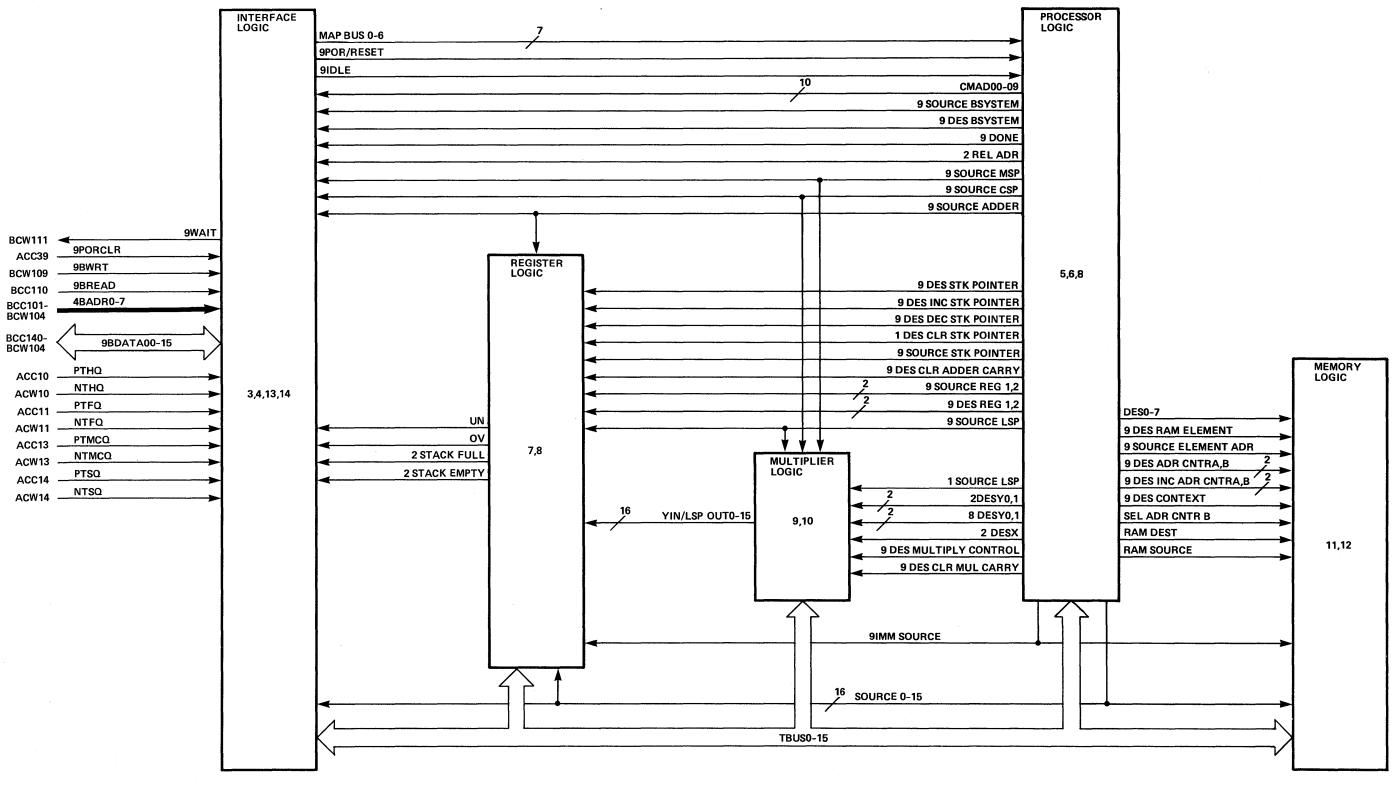

| 4-81a                     | Interface Logic Block Diagram                                                                                |

| 4-82                      | Memory Logic Block Diagram                                                                                   |

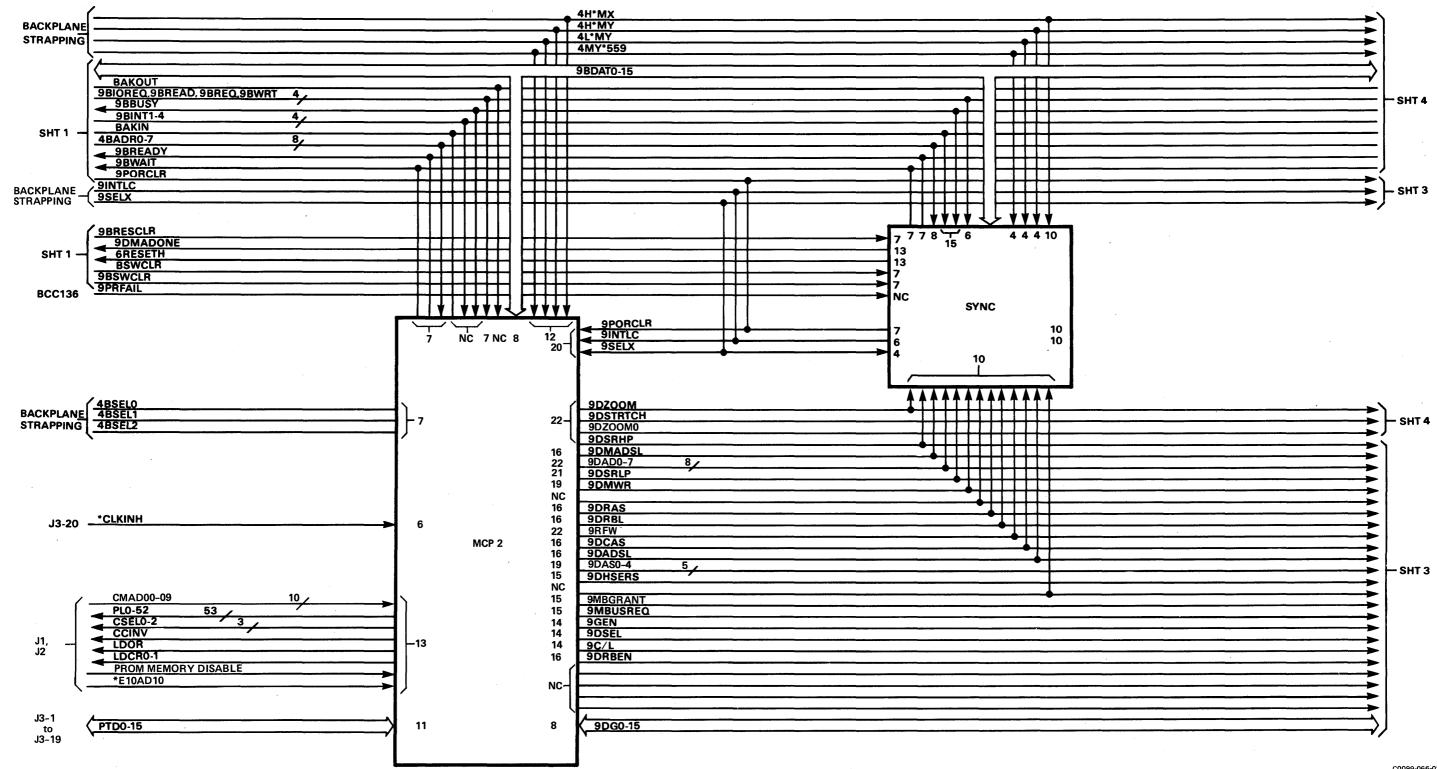

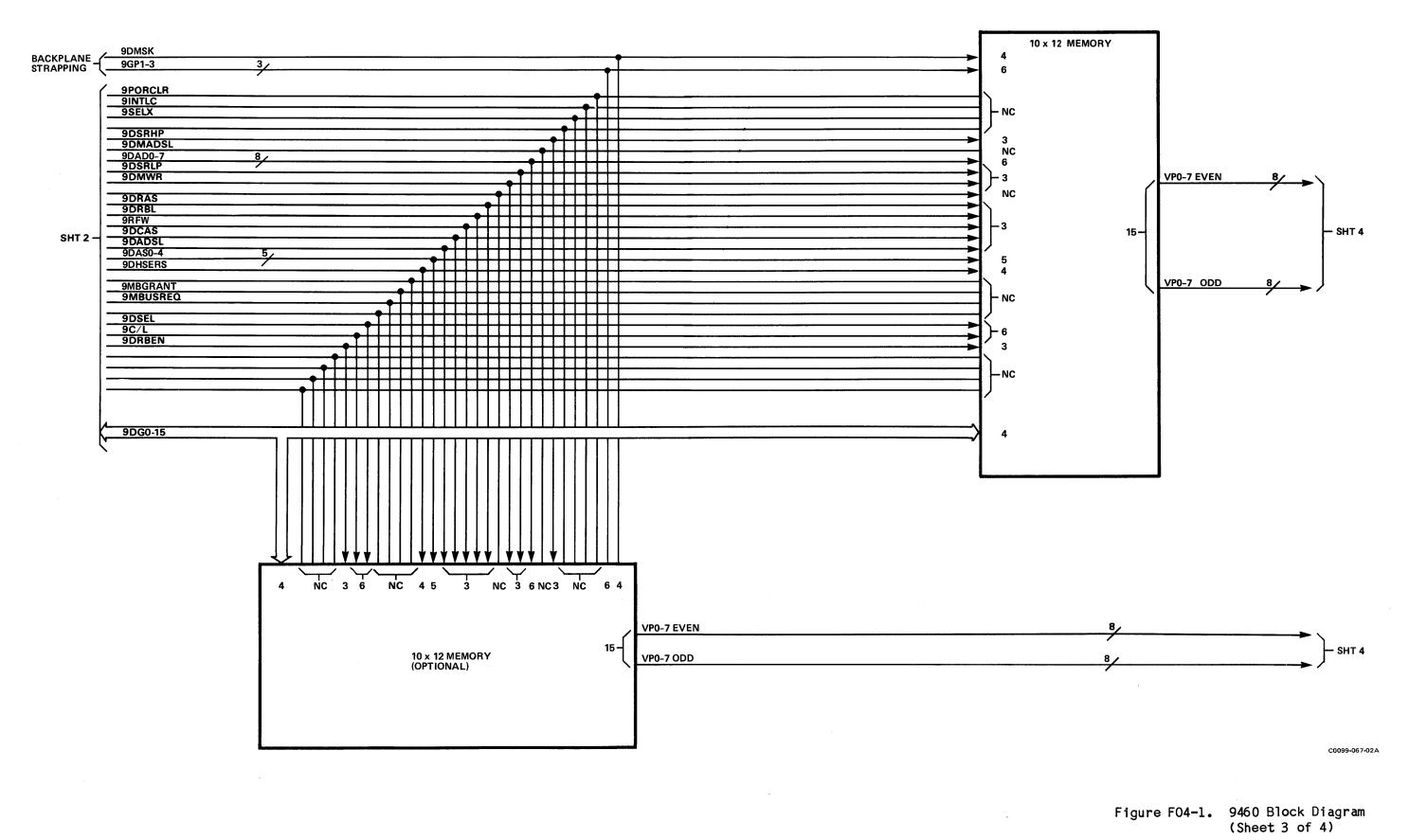

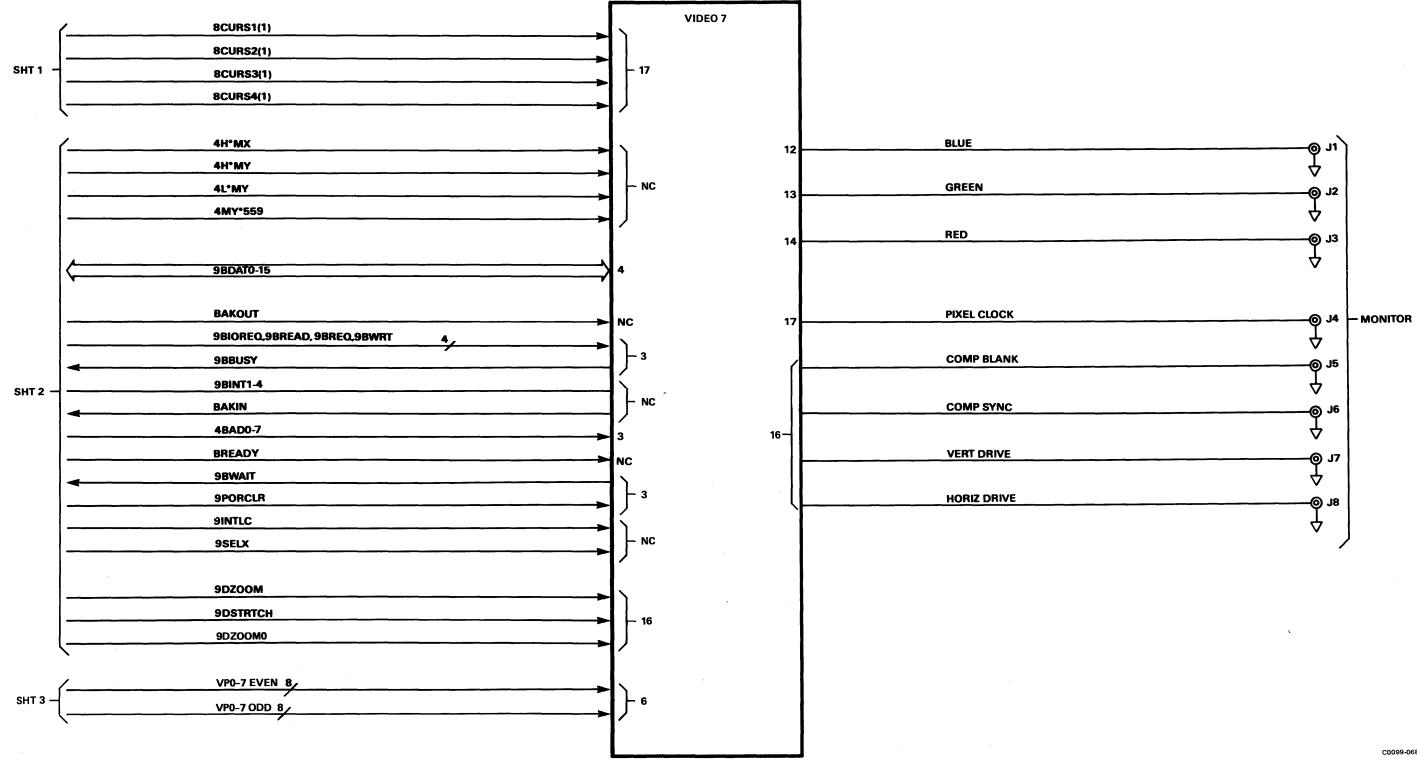

| F04-1                     | 9460 Block Diagram                                                                                           |

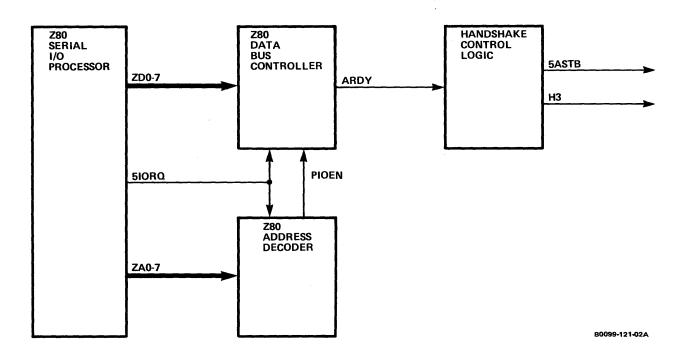

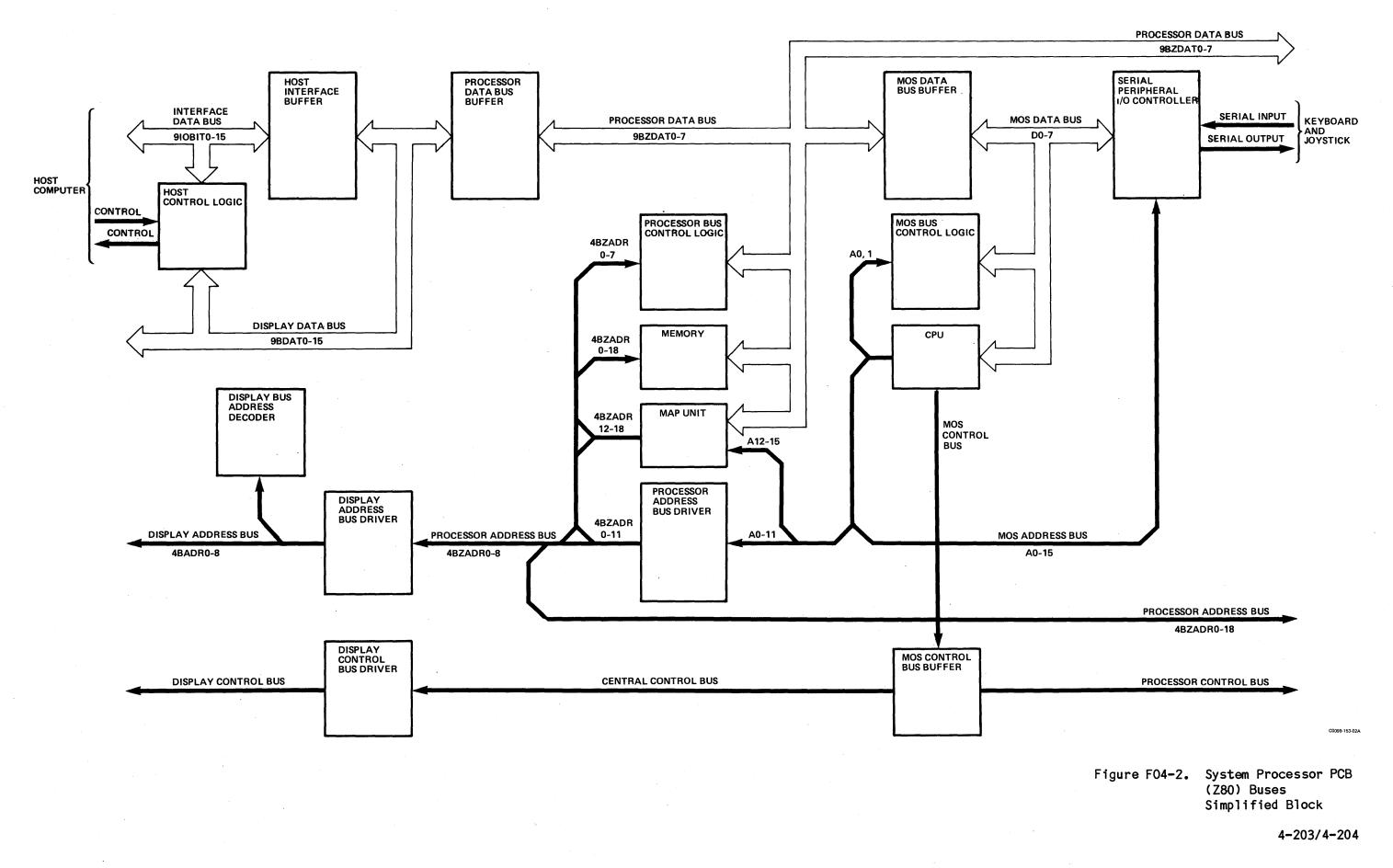

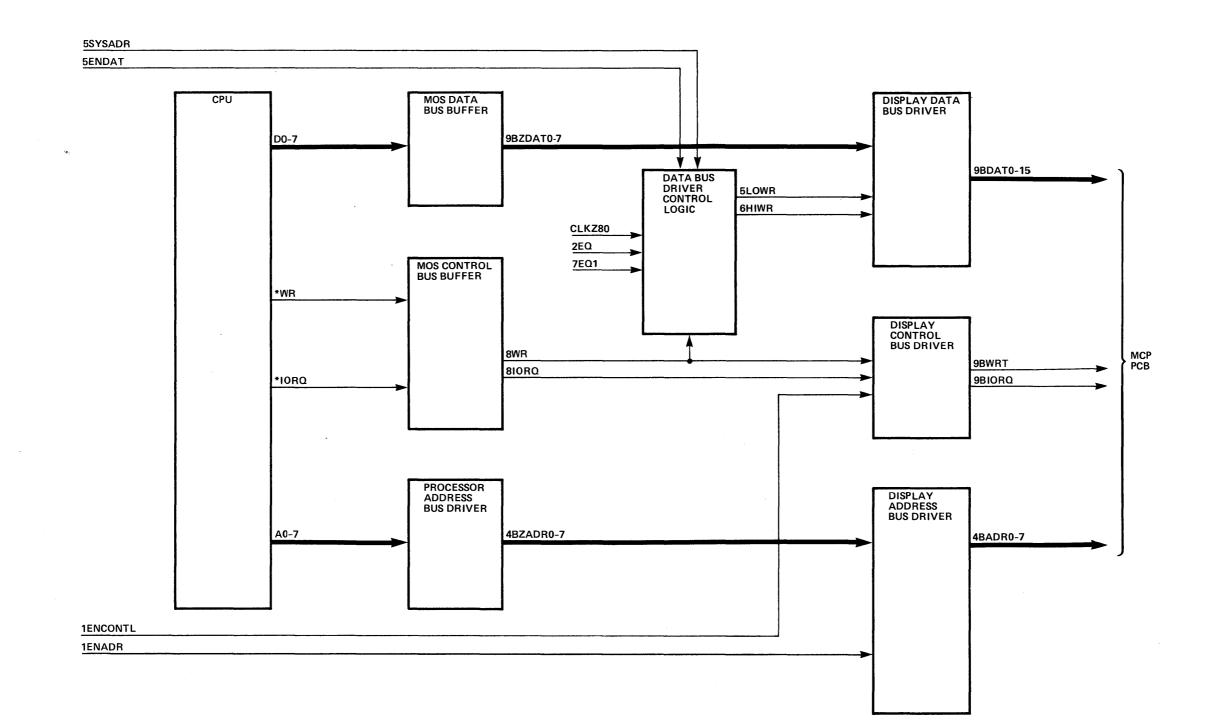

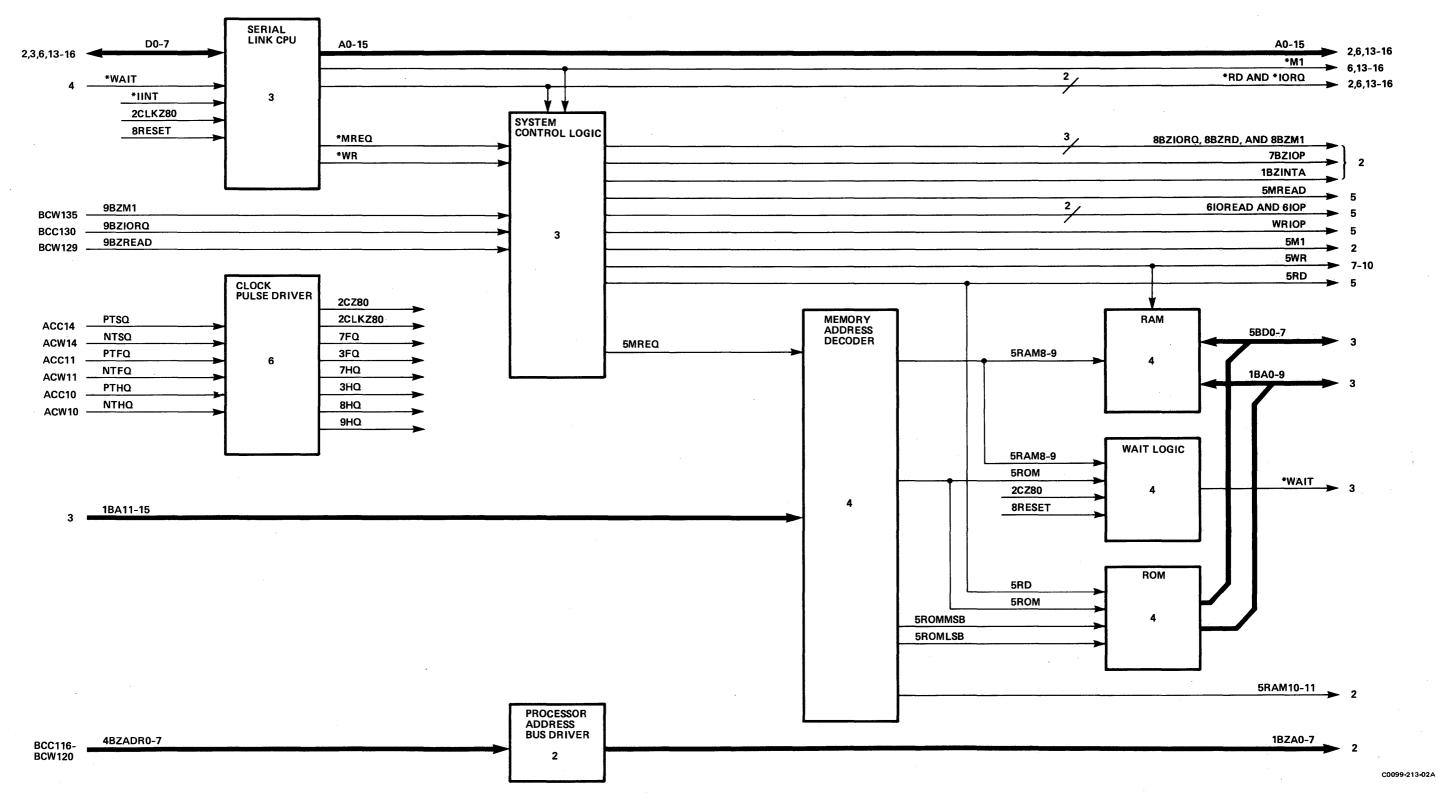

| F04-2                     | System Processor PCB (Z80) Buses Simplified Block                                                            |

| F04-3                     | System Processor PCB (Z80) Control Signals                                                                   |

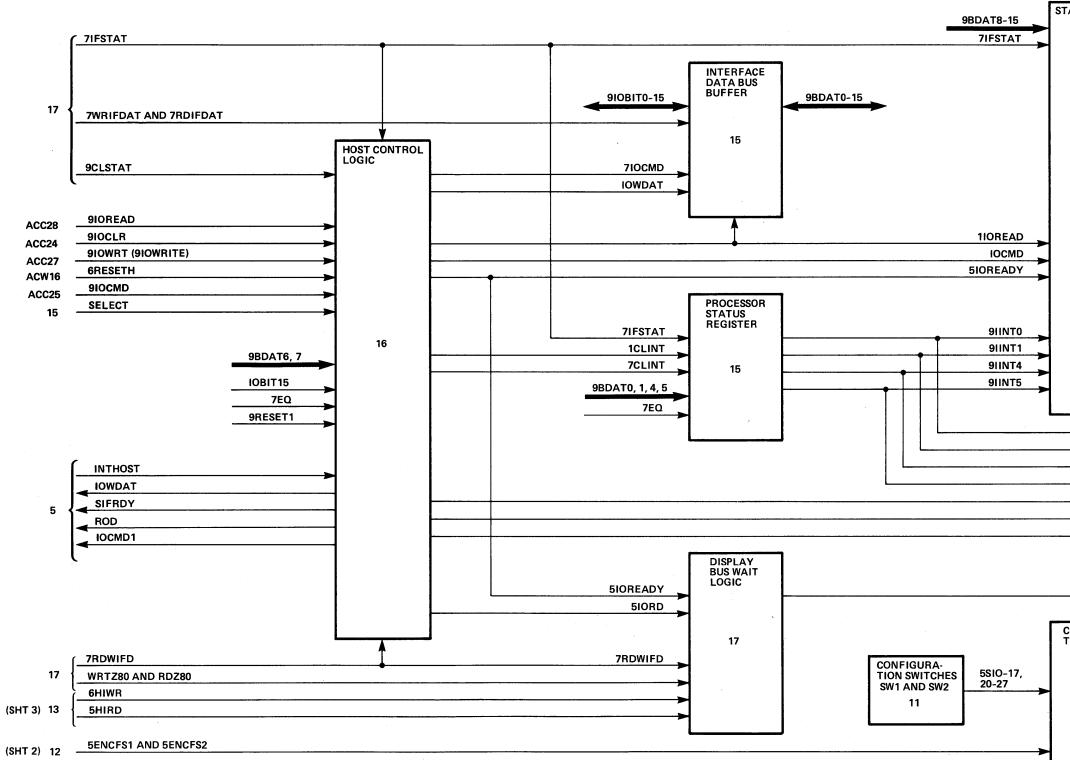

| F04-4                     | Host Control Logic                                                                                           |

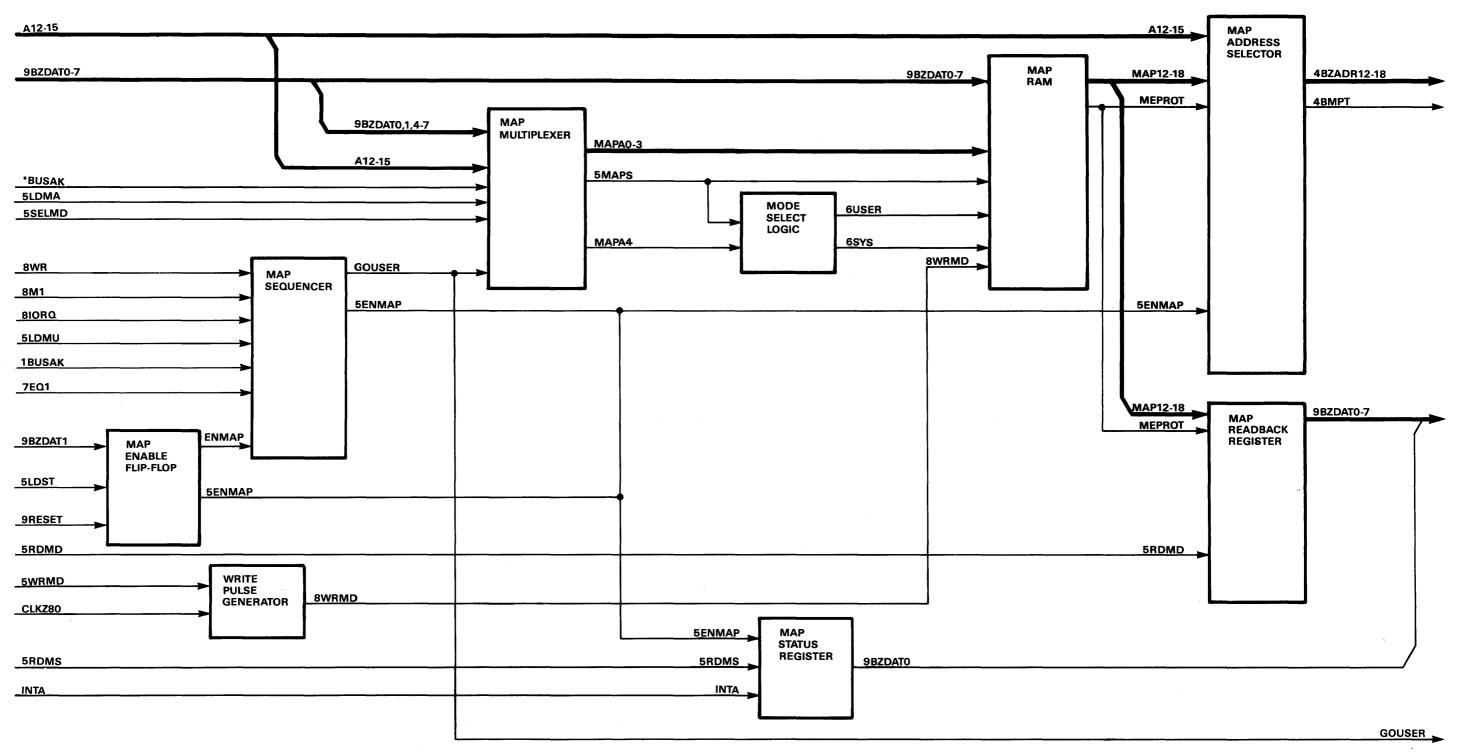

| F04-5                     | MAP Unit                                                                                                     |

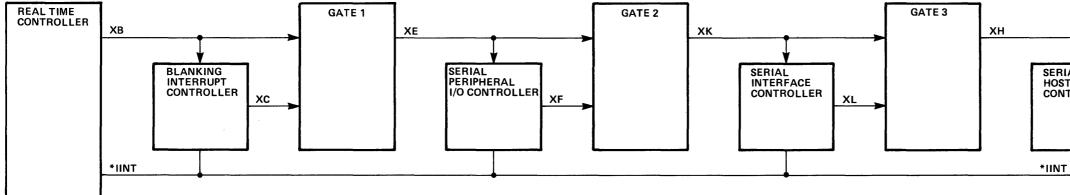

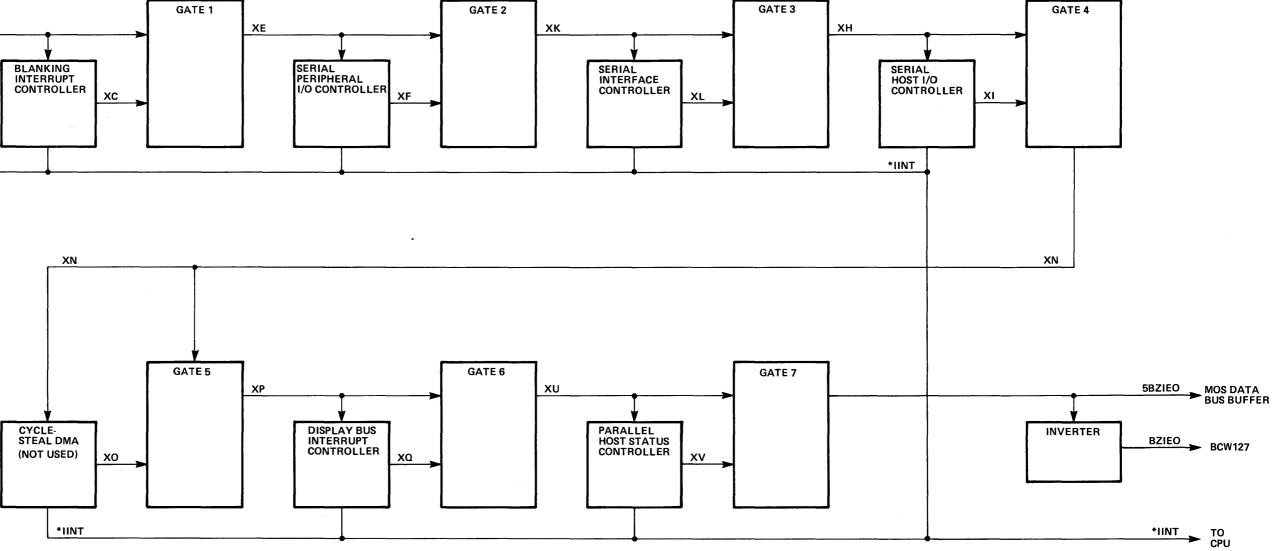

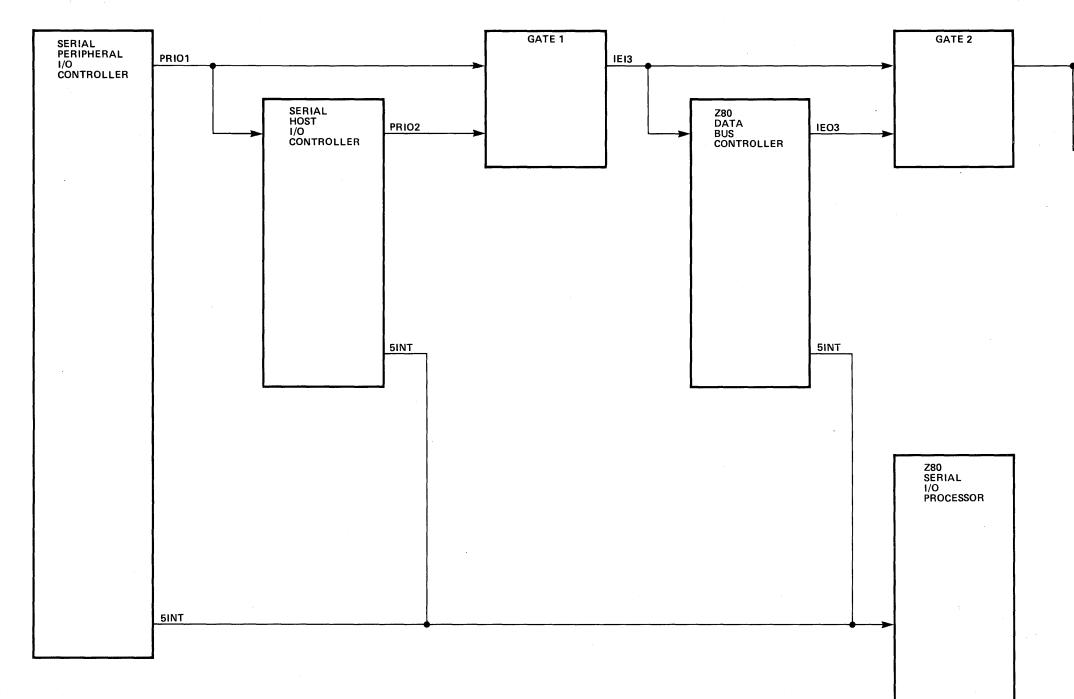

| F04-6                     | Daisy Chain Interrupt Logic                                                                                  |

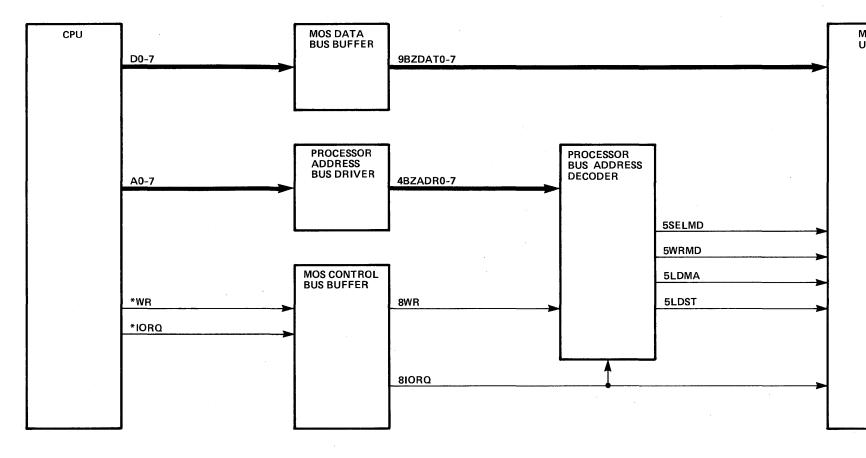

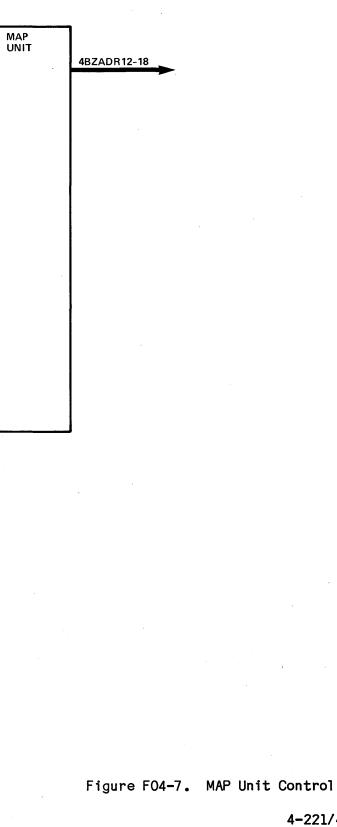

| F04-7                     | MAP Unit Control                                                                                             |

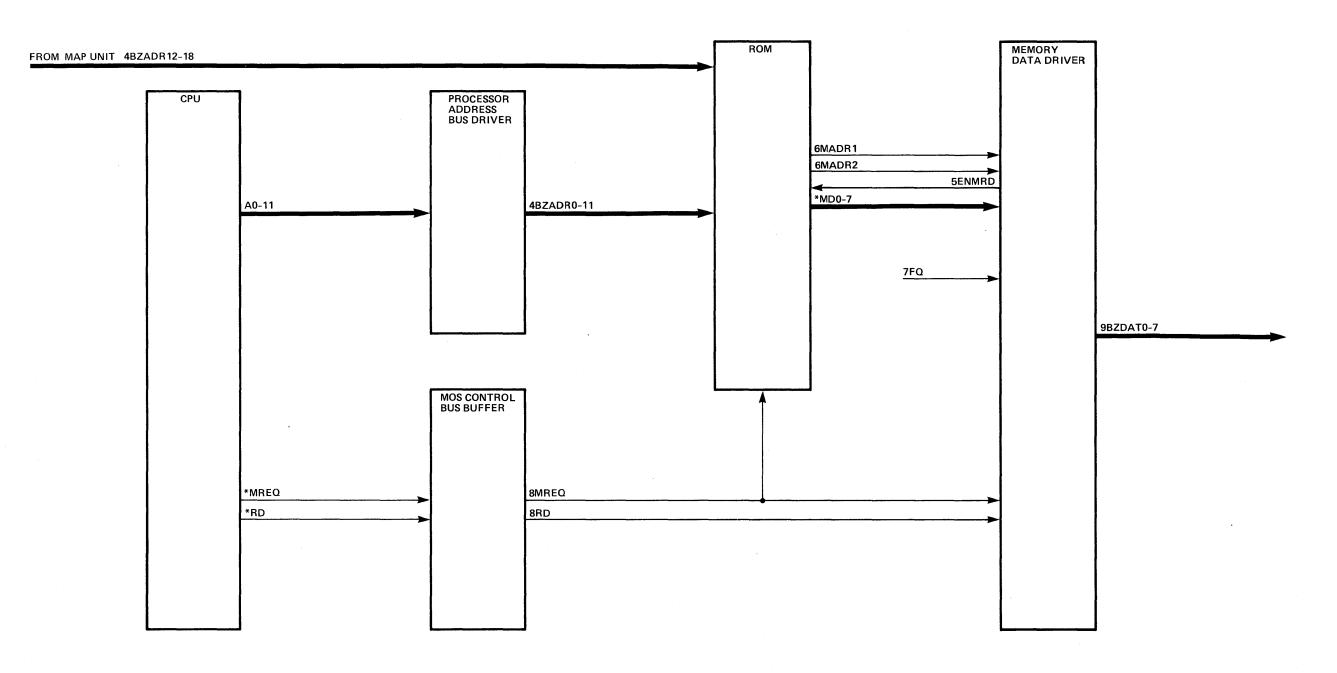

| F04-8                     | ROM Access                                                                                                   |

| F04-9                     |                                                                                                              |

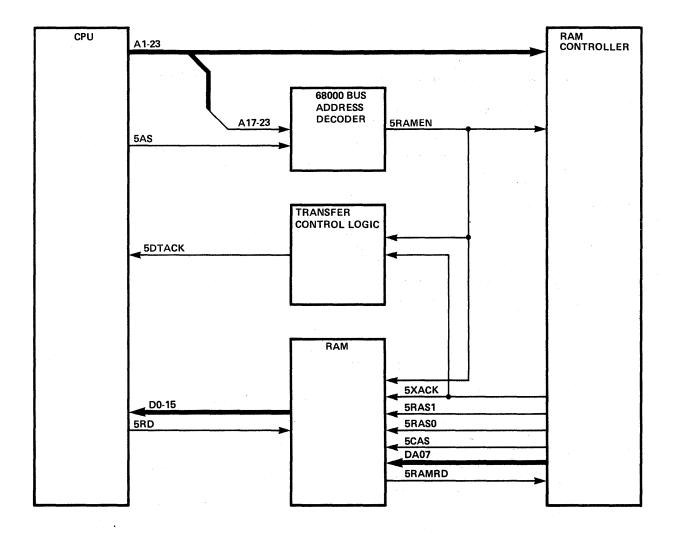

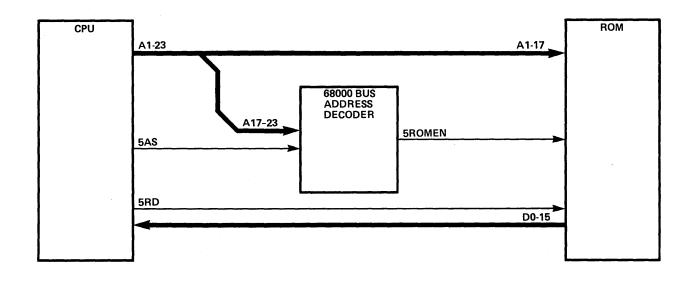

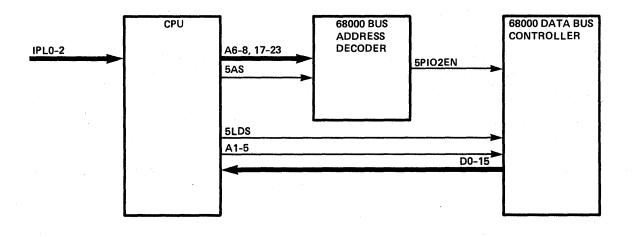

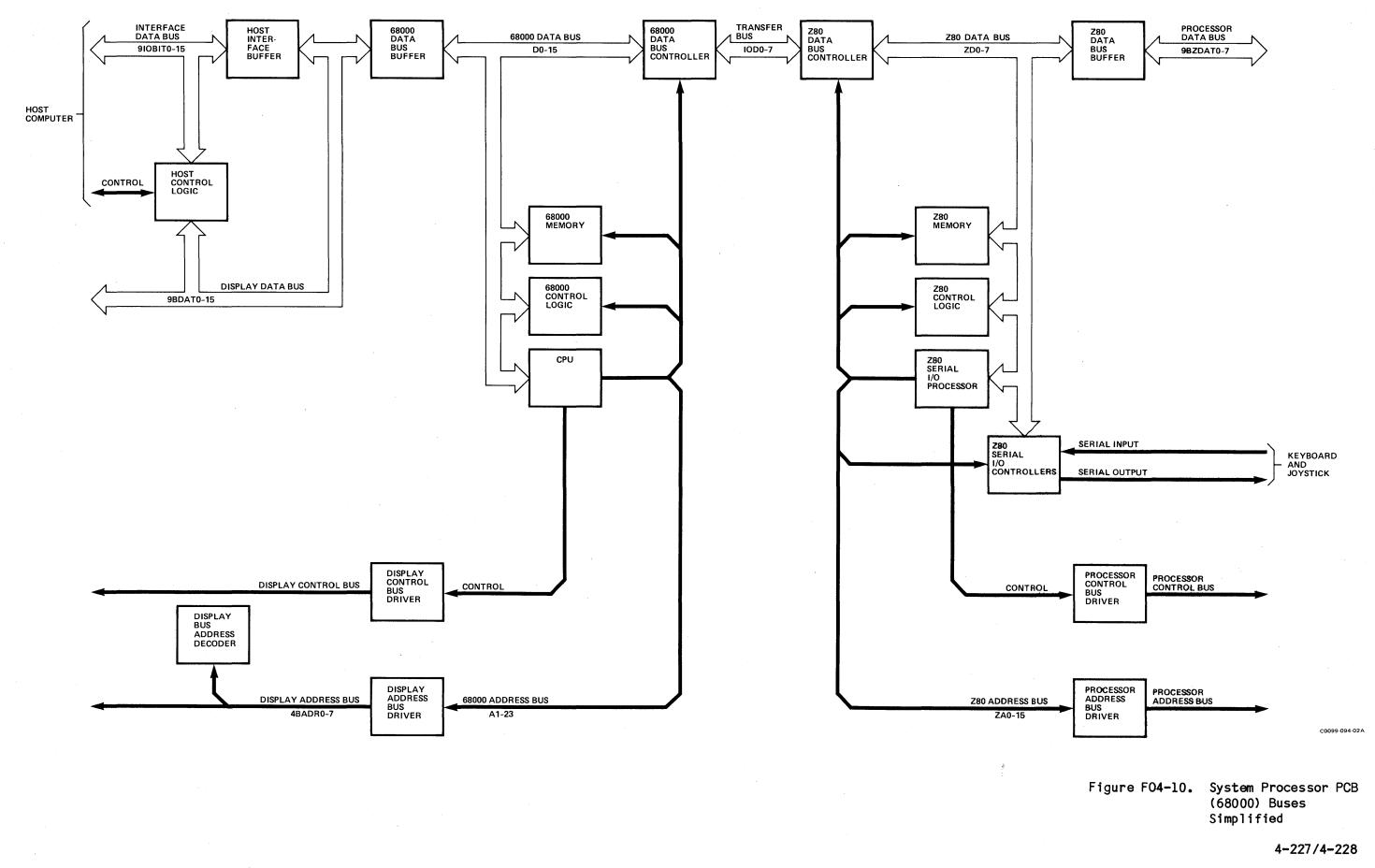

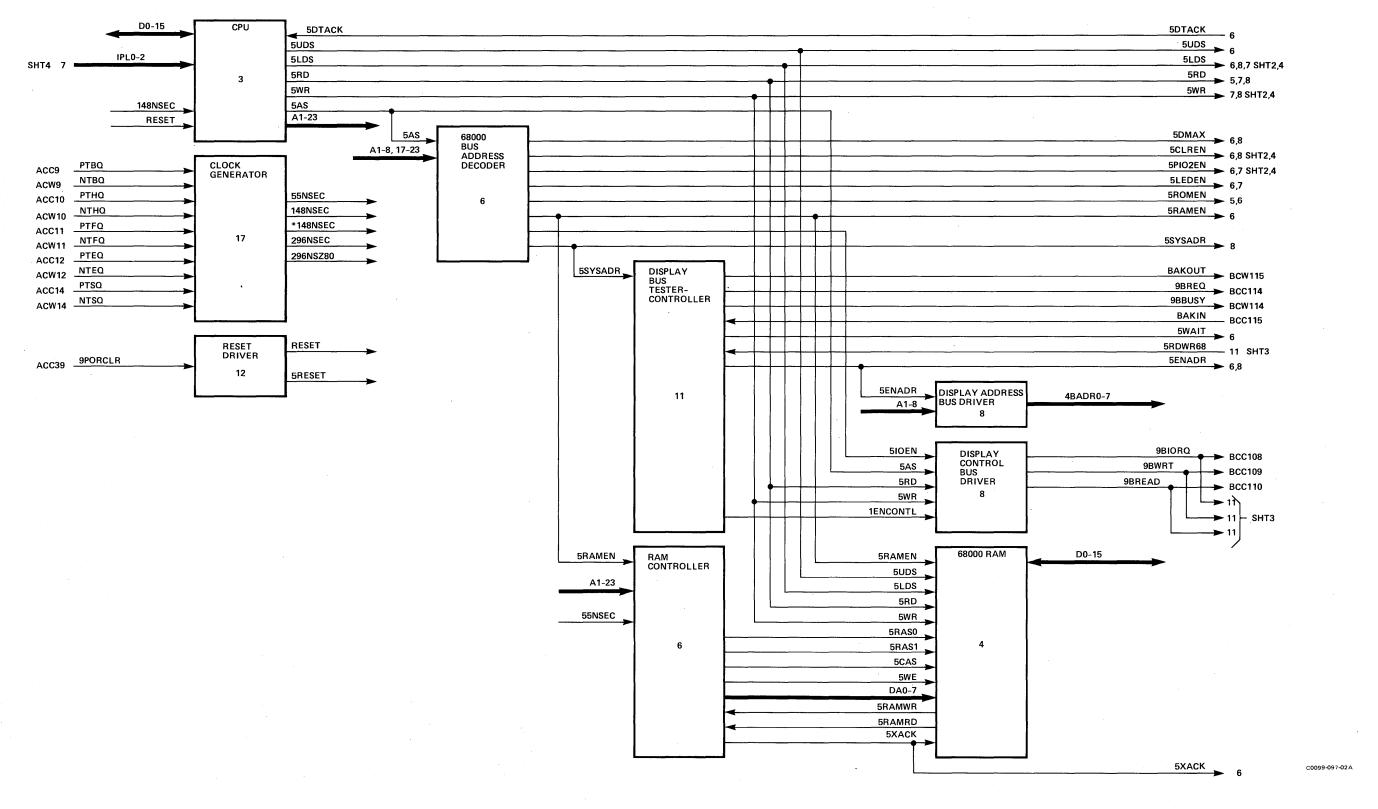

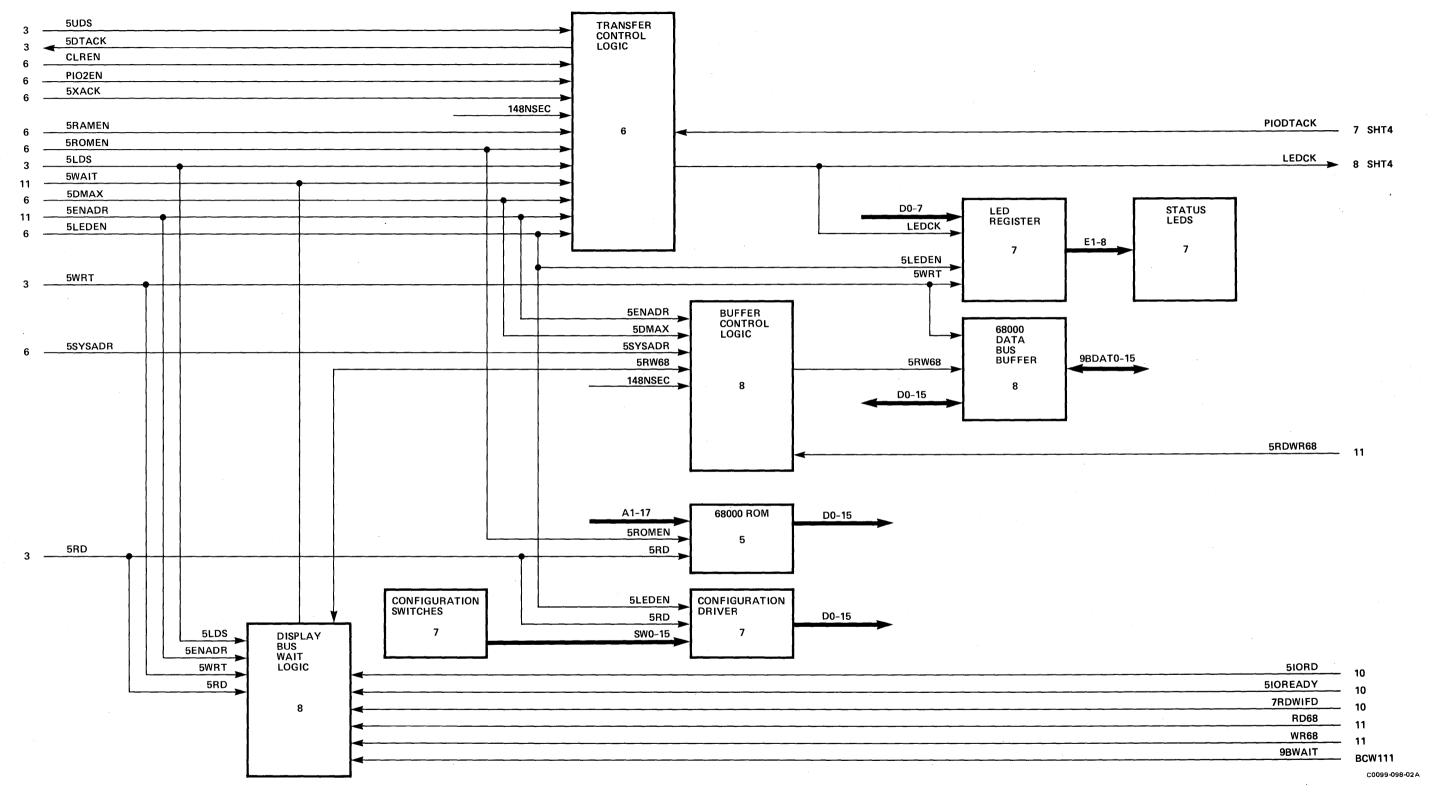

| F04-10                    | System Processor PCB (68000) Buses Simplified 4-227                                                          |

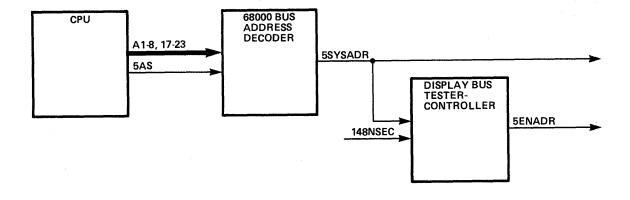

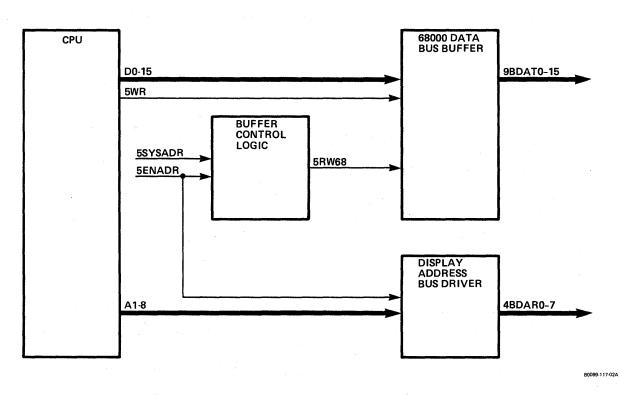

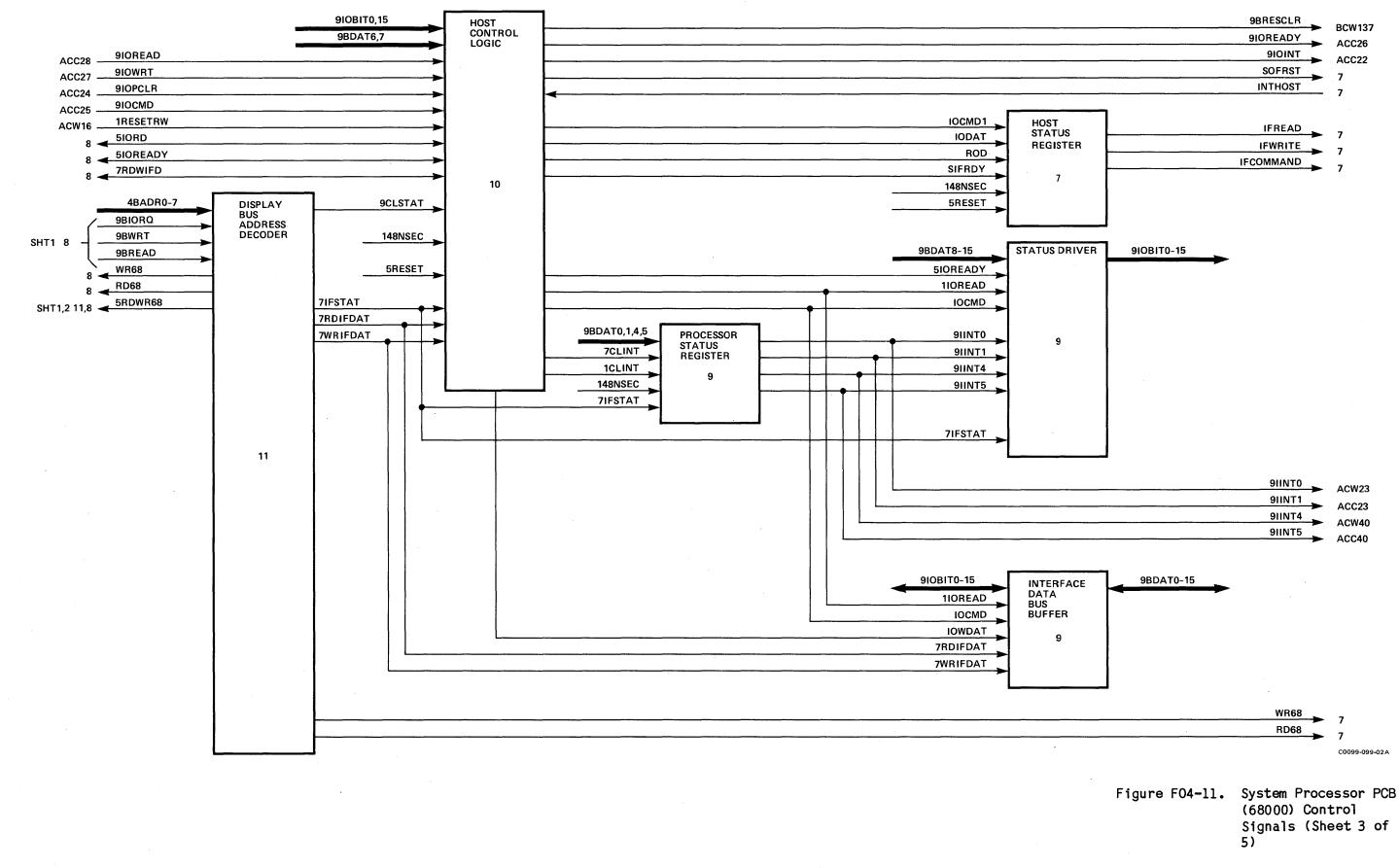

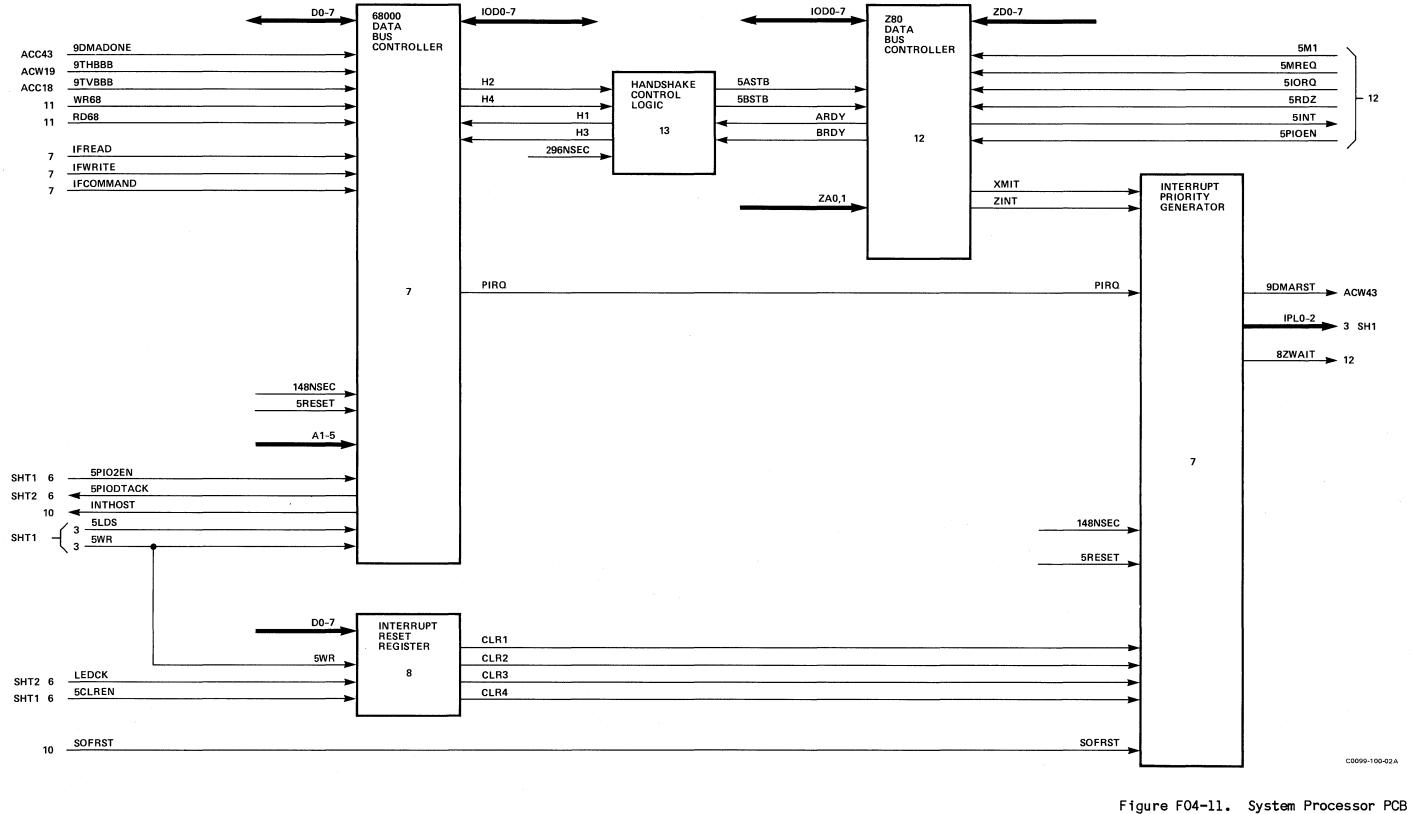

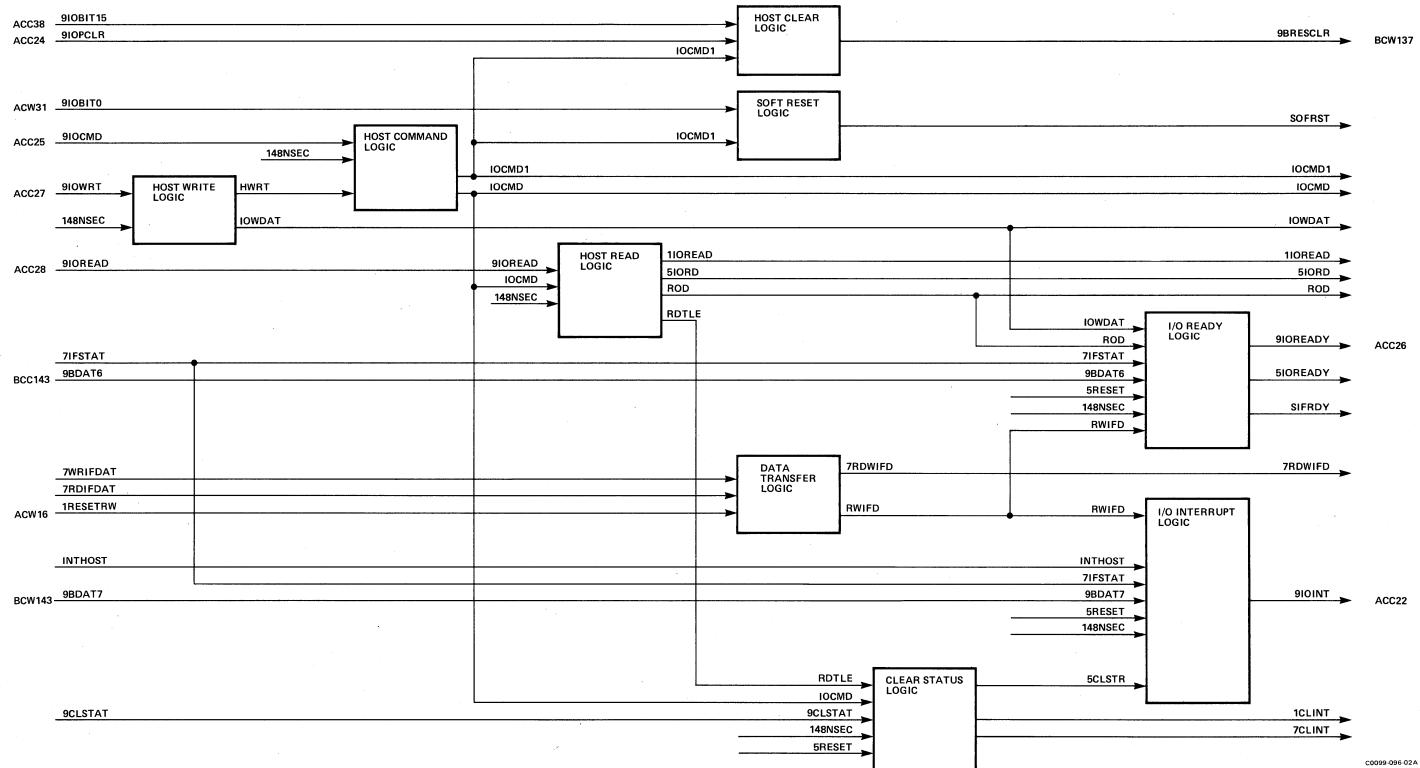

| F04 <b>-</b> 11           | System Processor PCB (68000) Control Signals 4-229                                                           |

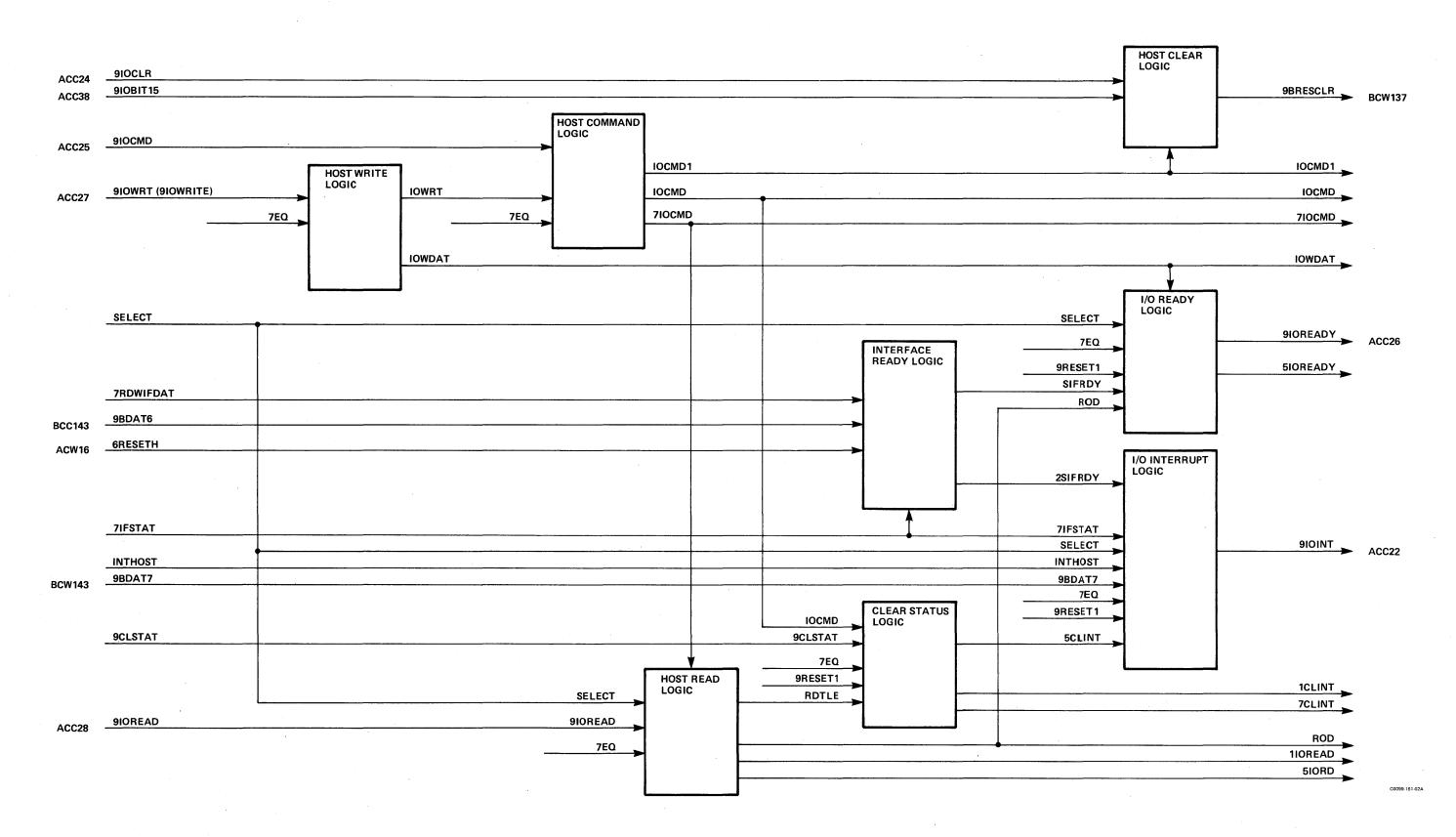

| F04-12                    | Host Control Logic                                                                                           |

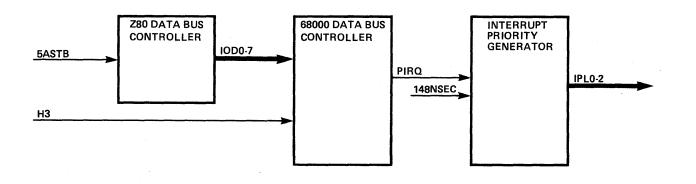

| F04-13                    | Daisy Chain Interrupt Logic                                                                                  |

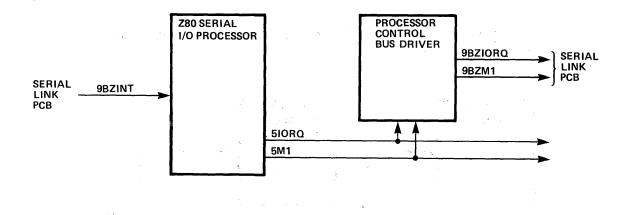

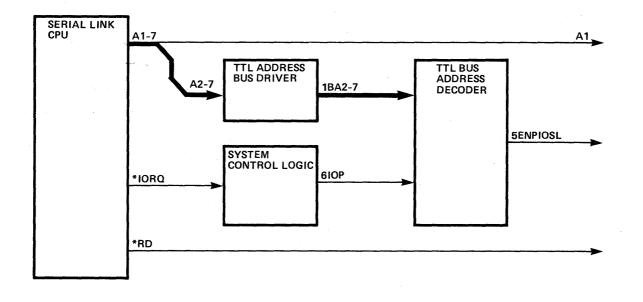

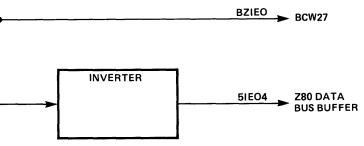

| F04-14                    | Serial Link PCB Data and Address Buses                                                                       |

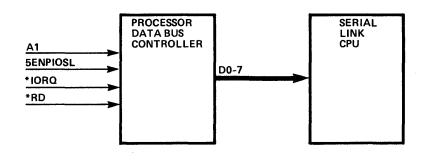

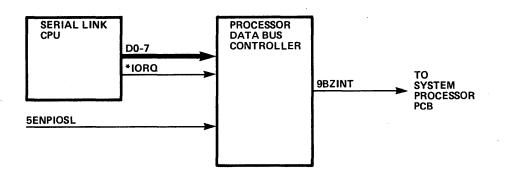

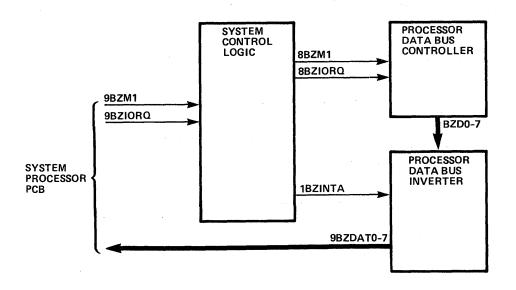

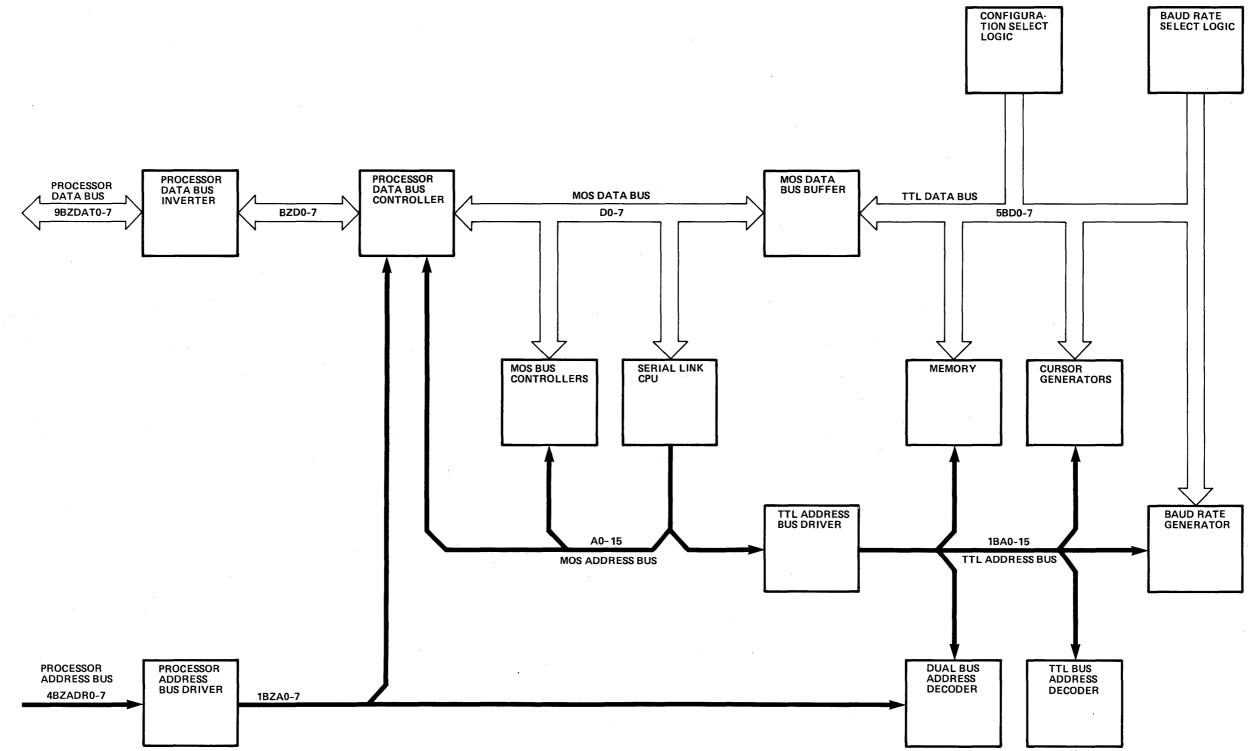

| F04 <b>-</b> 15           | Serial Link PCB Control Signals                                                                              |

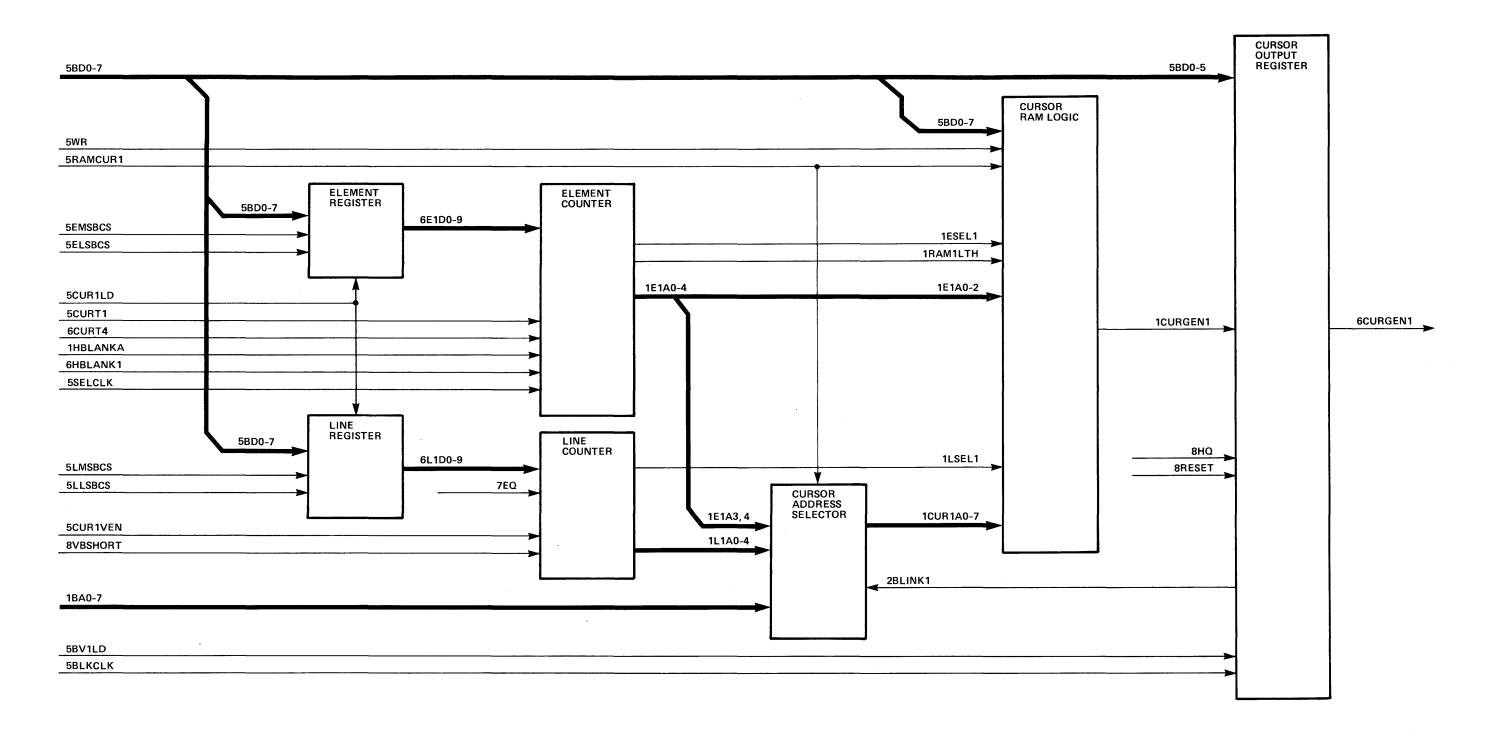

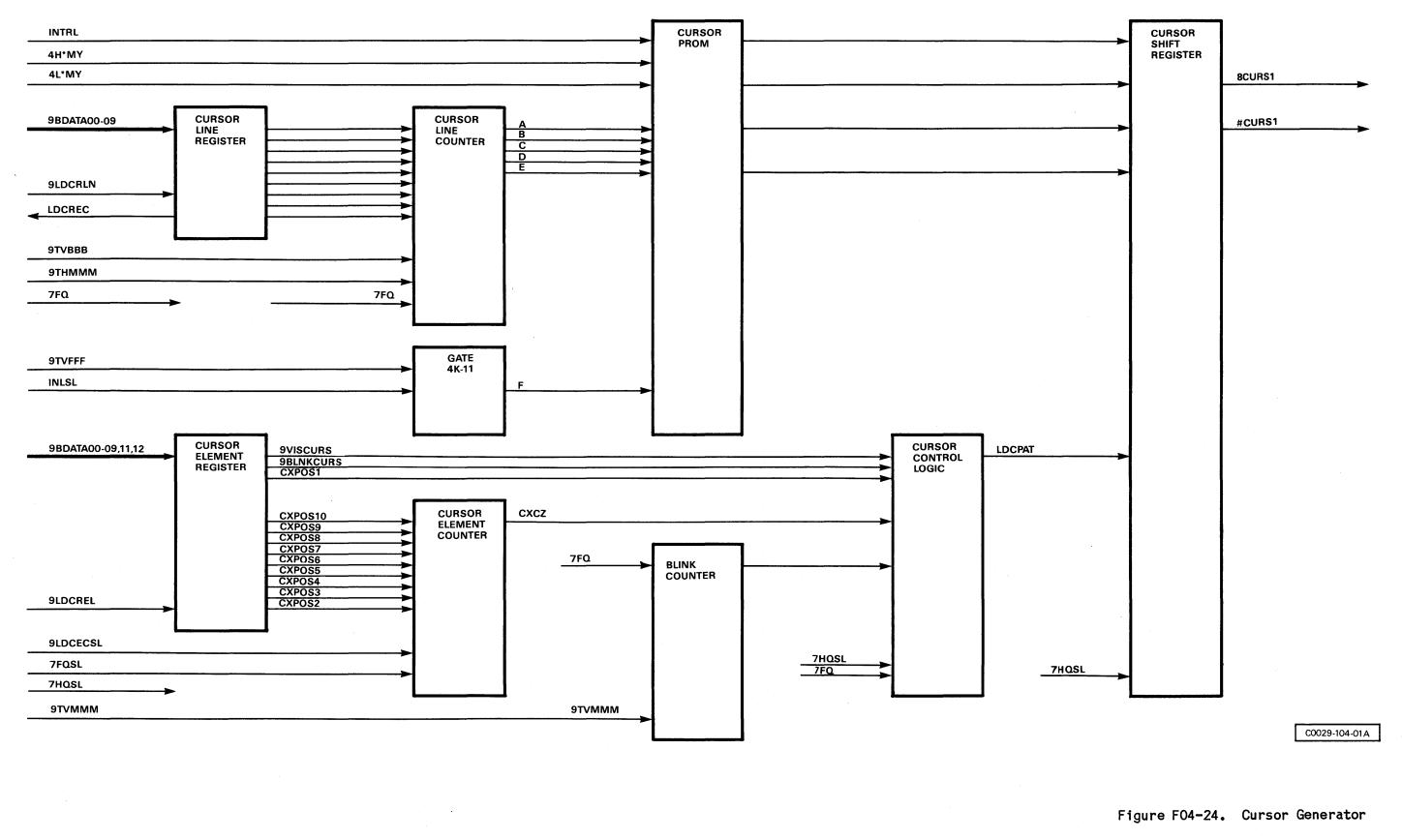

| F04-16                    | Cursor Generator                                                                                             |

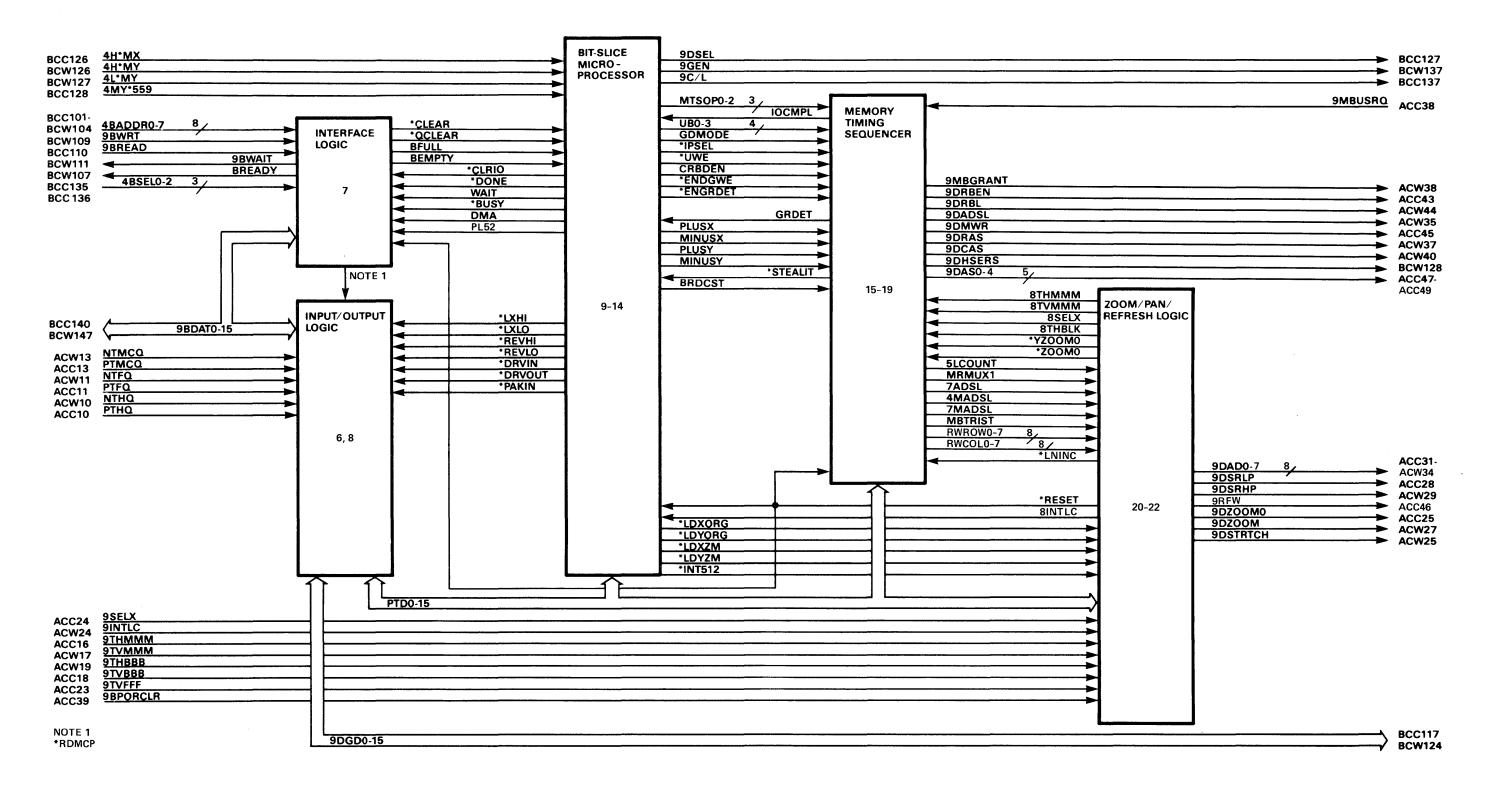

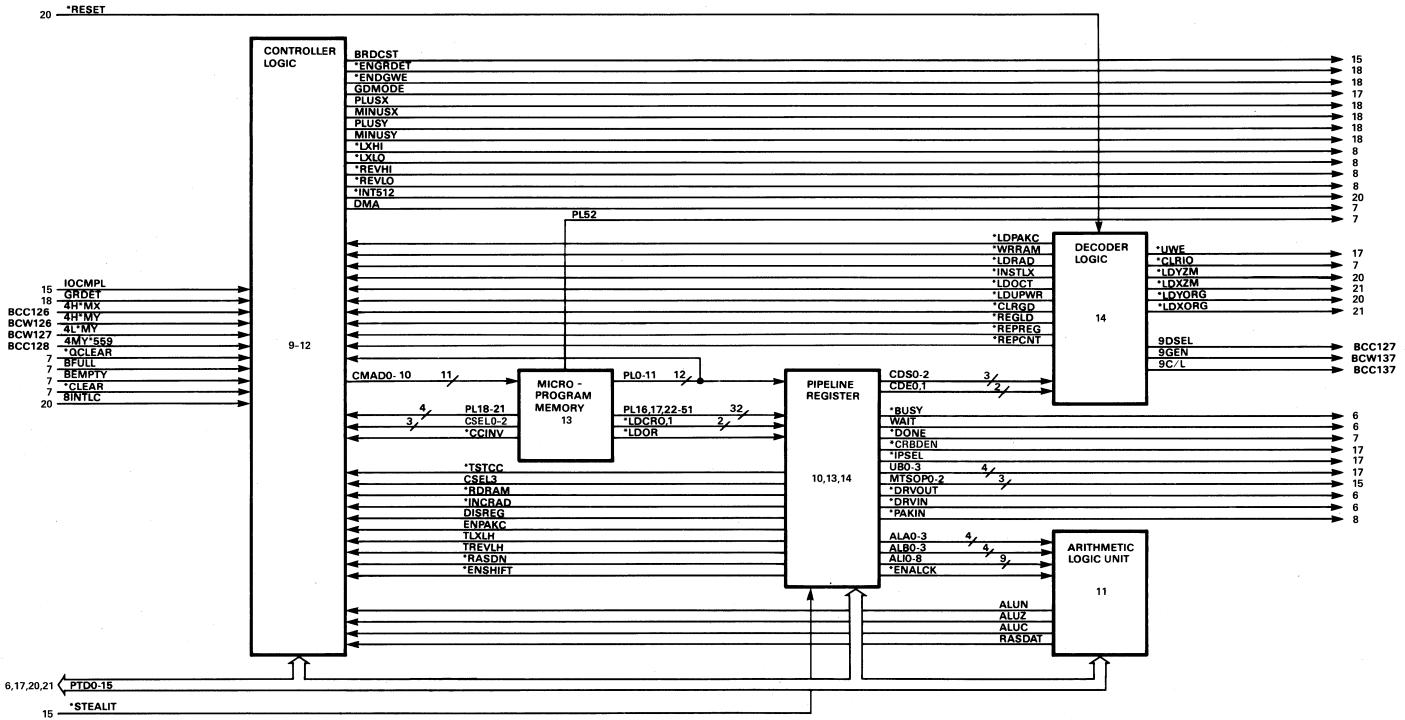

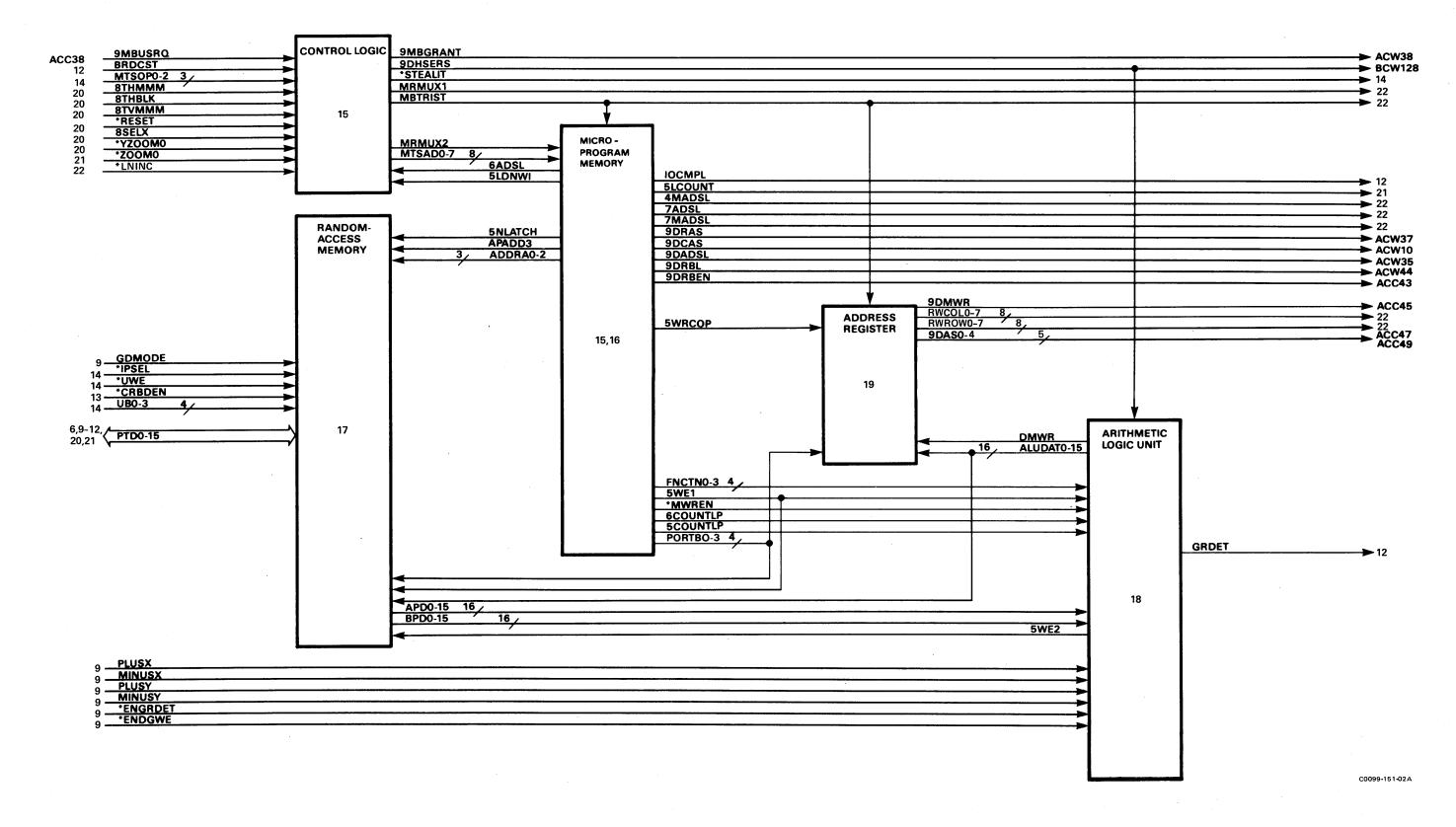

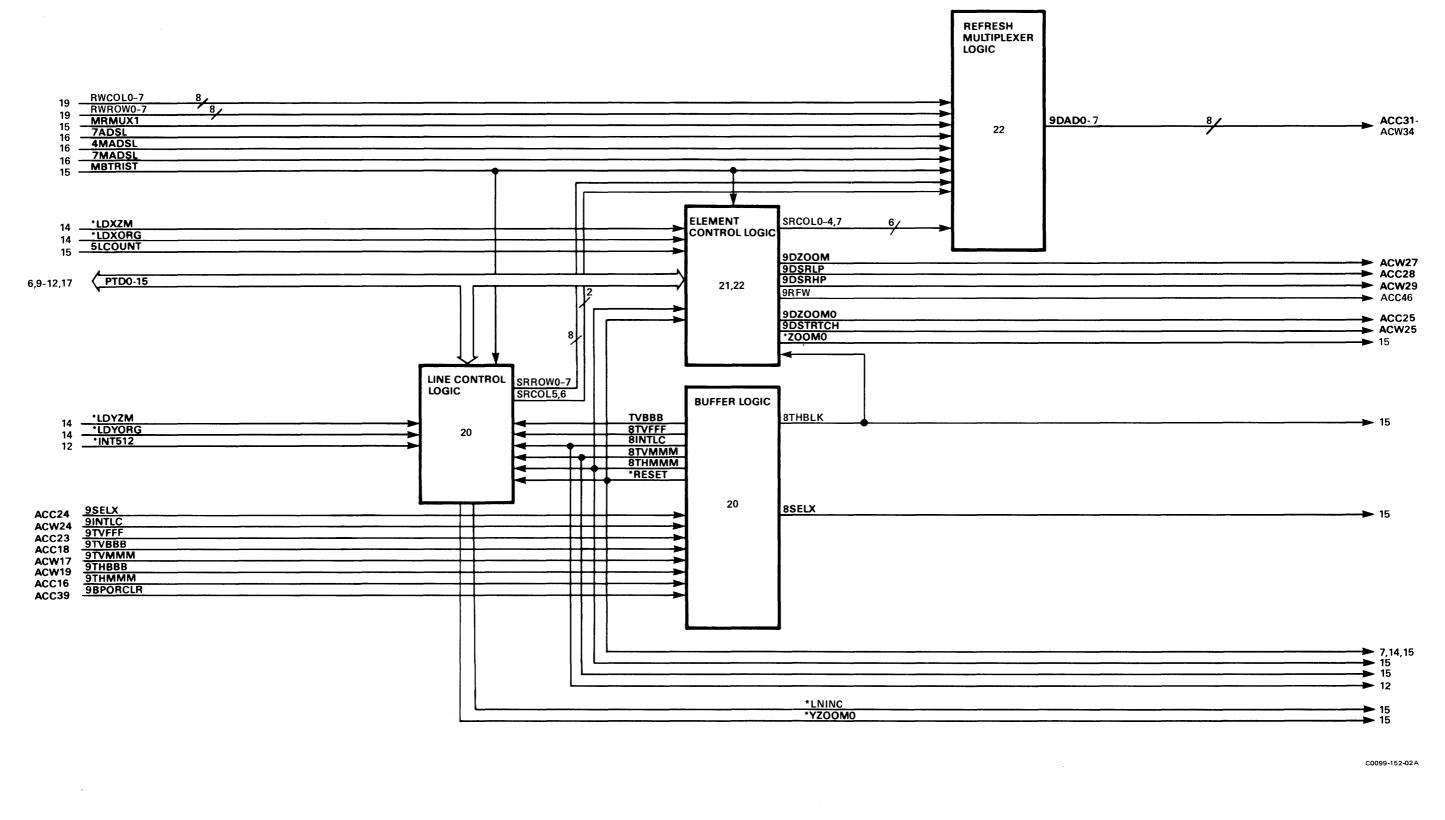

| F04-17                    | MCP2 PCB                                                                                                     |

| F04-18                    | BSM                                                                                                          |

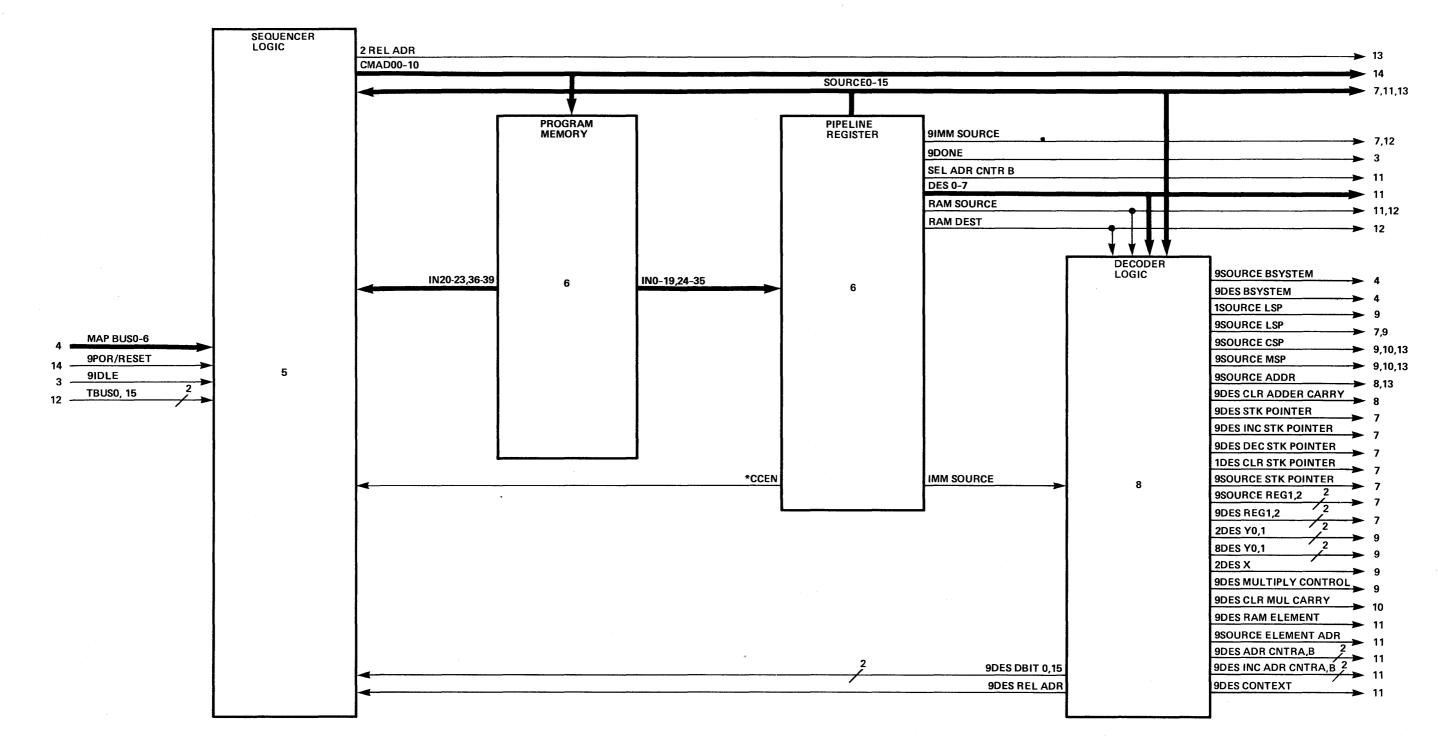

| F04-19                    | MTS                                                                                                          |

| F04-20                    | ZPR                                                                                                          |

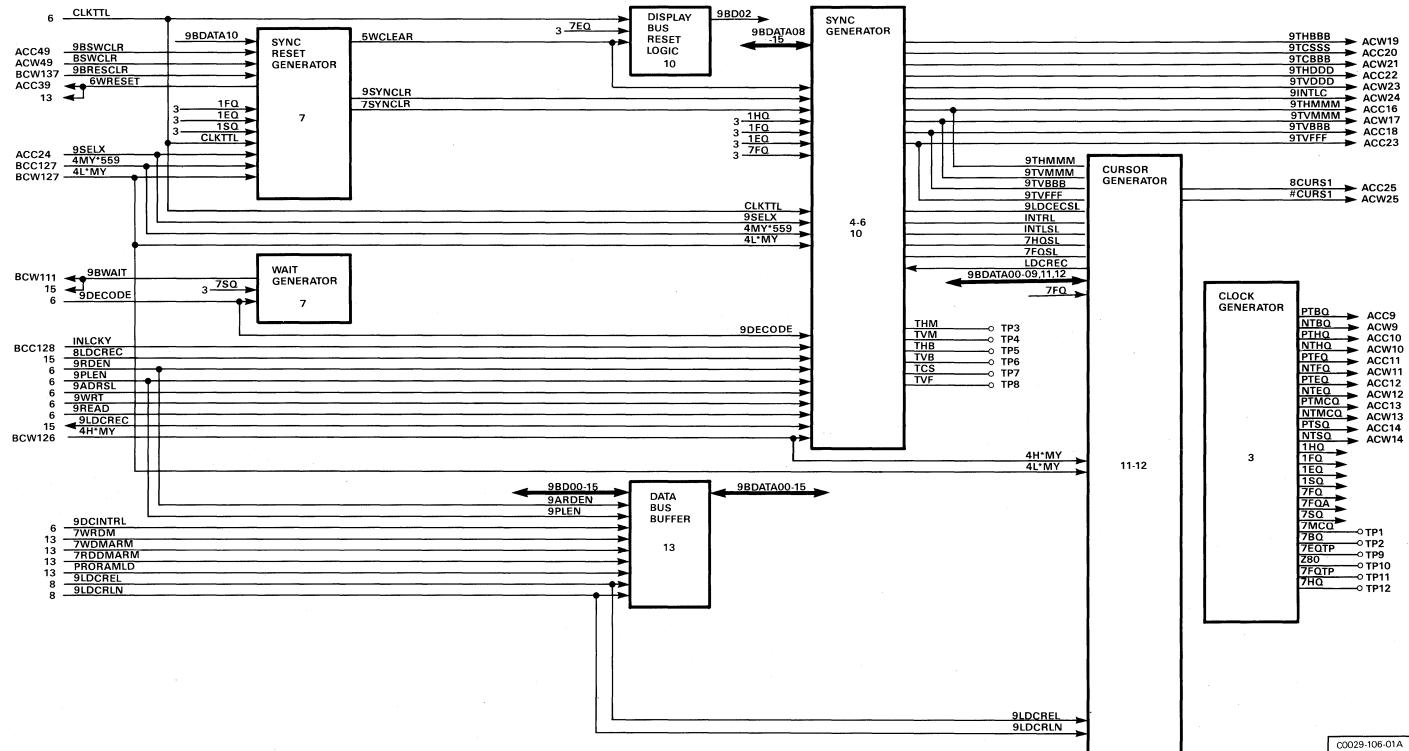

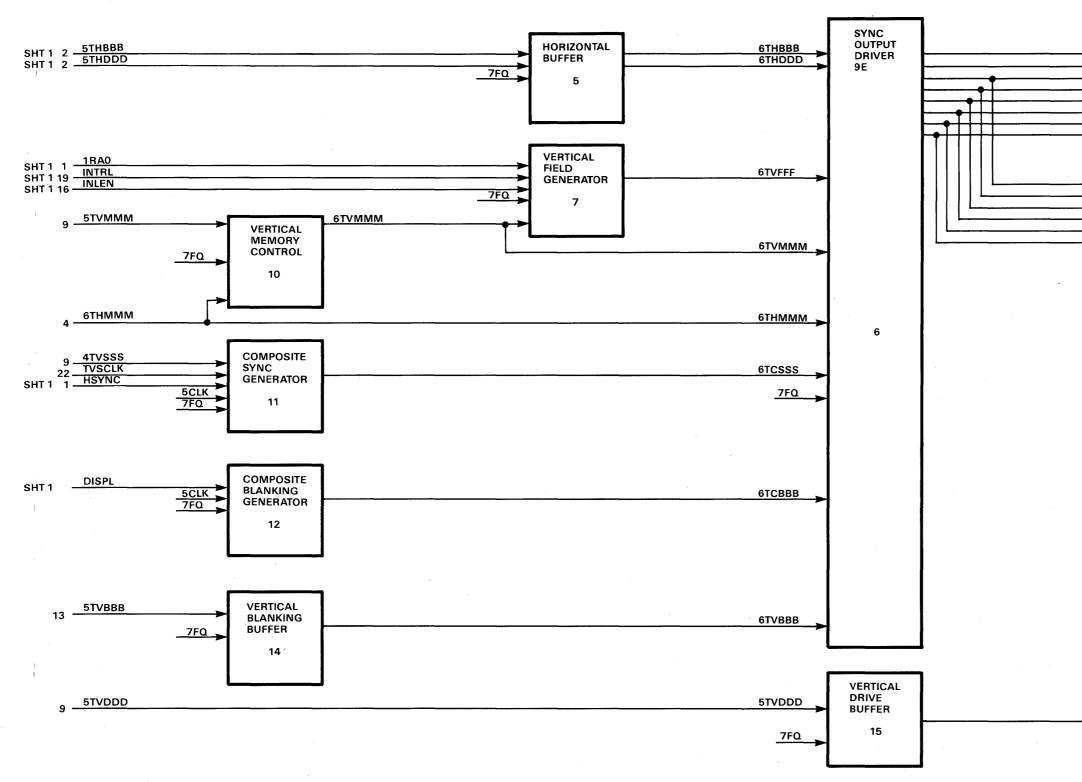

| F04 <del>-</del> 21       | Sync PCB                                                                                                     |

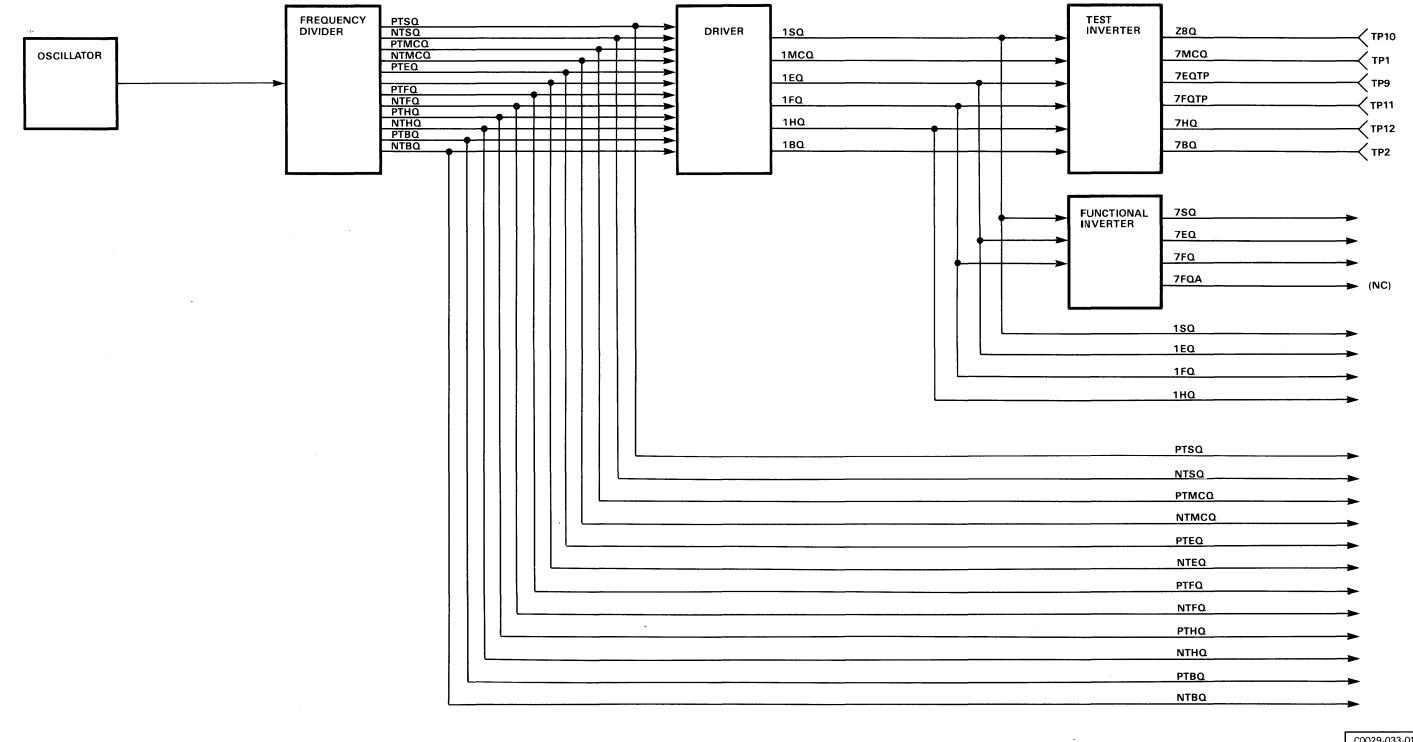

| F04-22                    | Clock Generator                                                                                              |

|                           |                                                                                                              |

8000080-02B

Figure

~

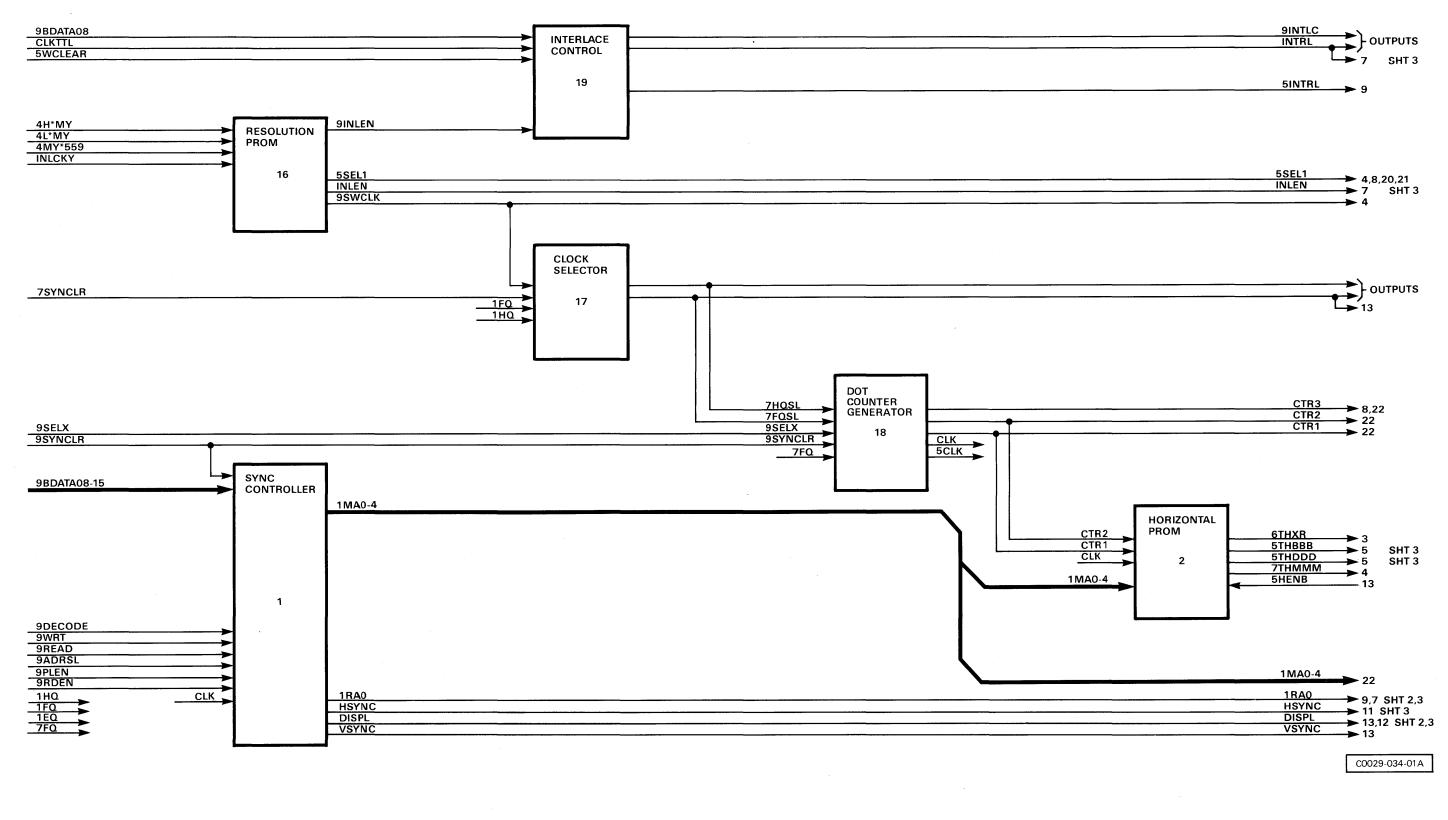

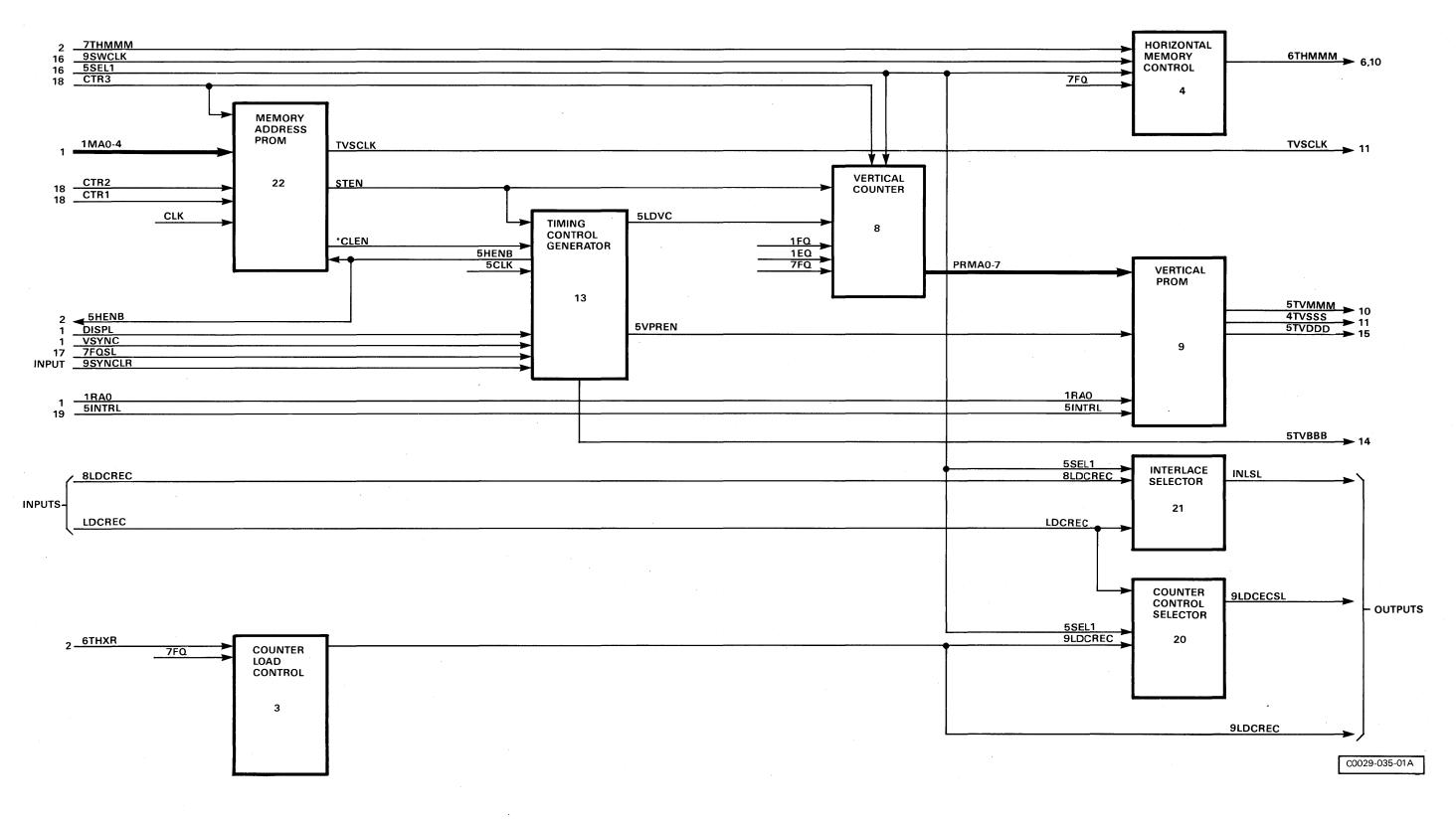

| F | -04 <b>-</b> 23  | Sync Generator                                  |

|---|------------------|-------------------------------------------------|

| F | -04-24           | Cursor Generator                                |

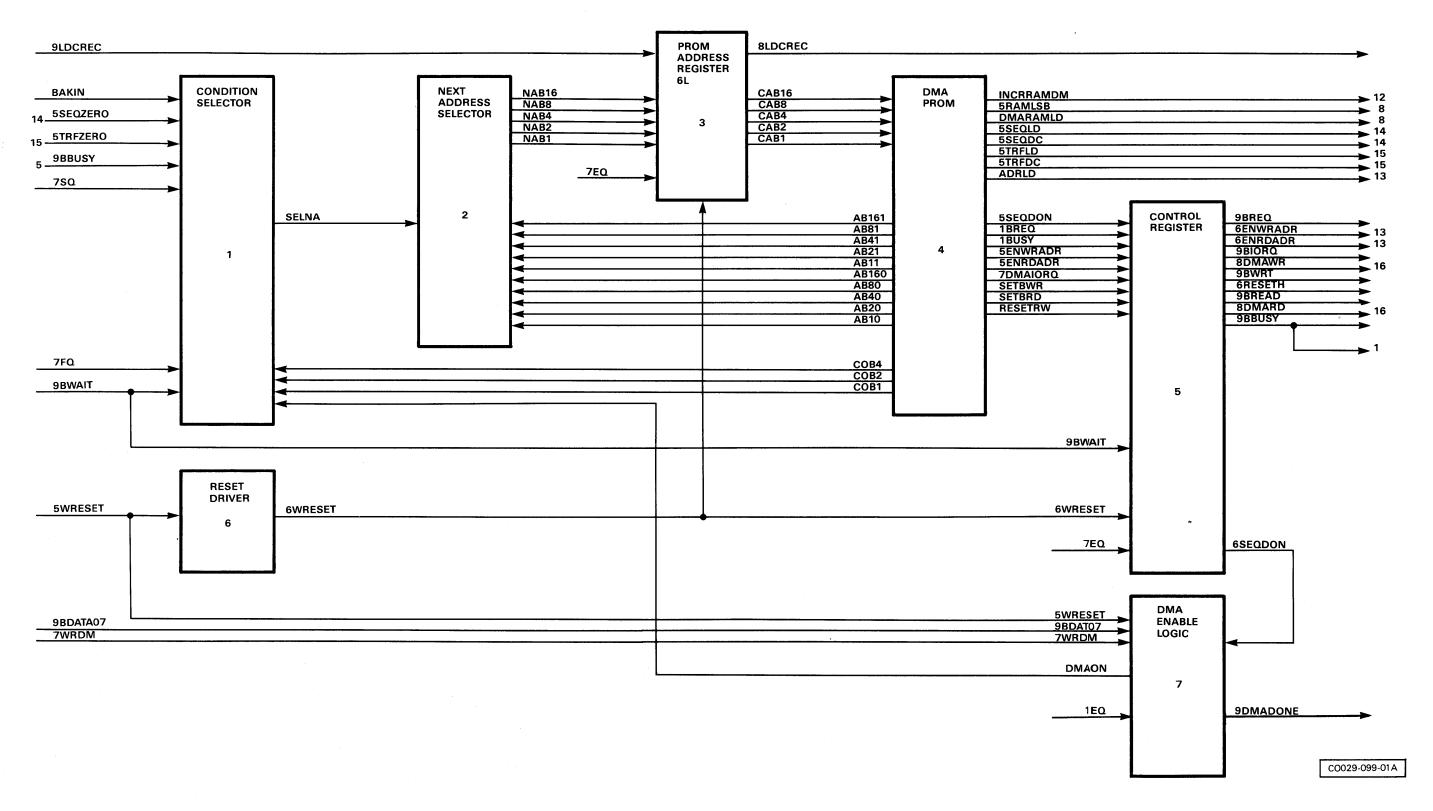

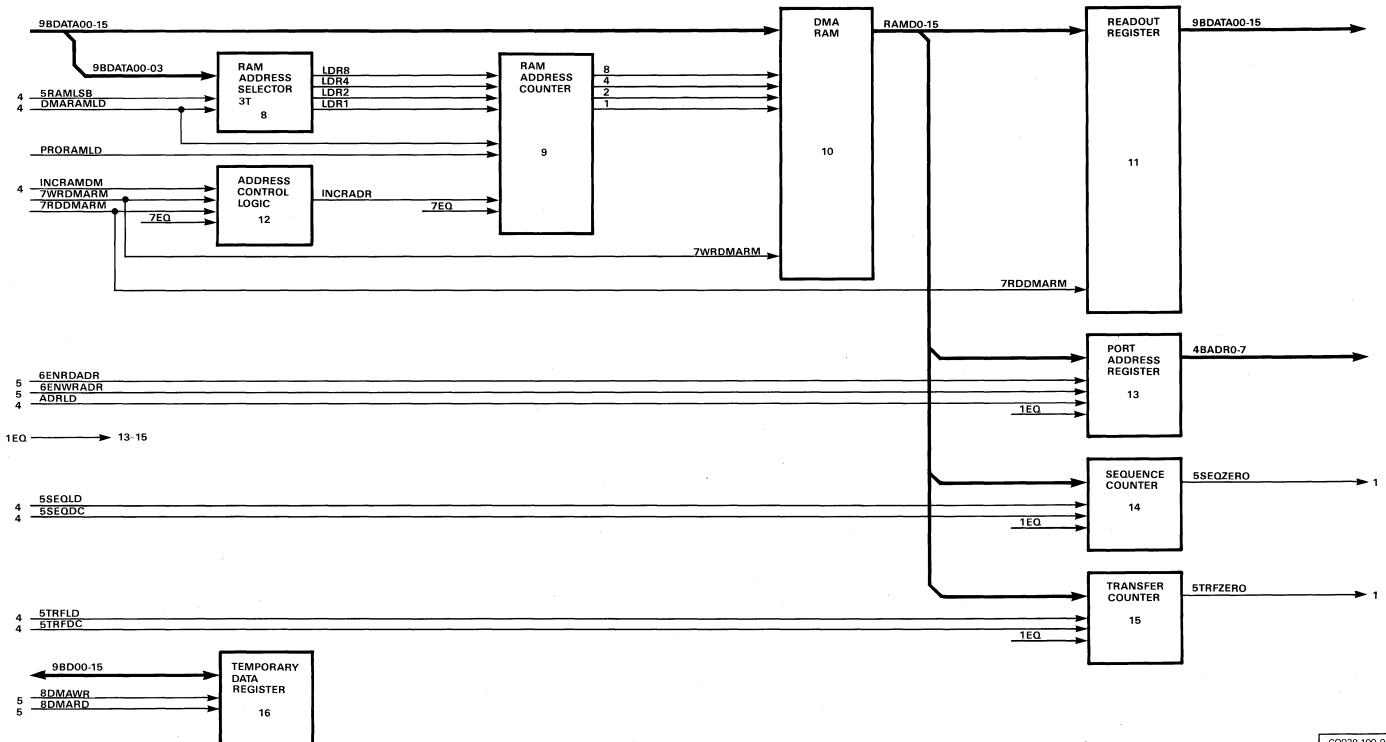

| F | -04-25           | TTL DMA                                         |

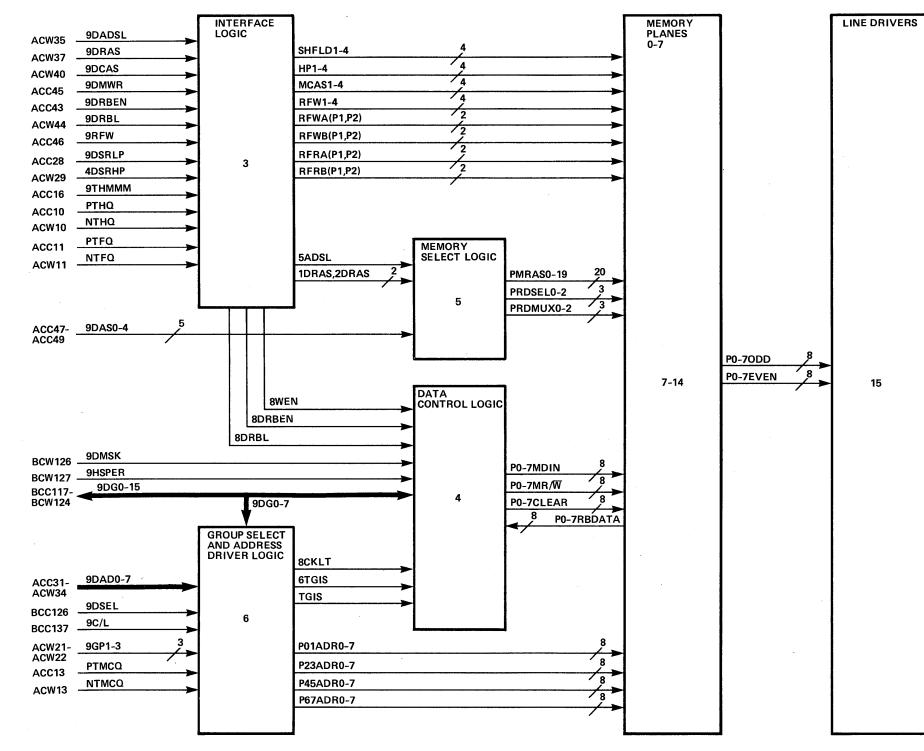

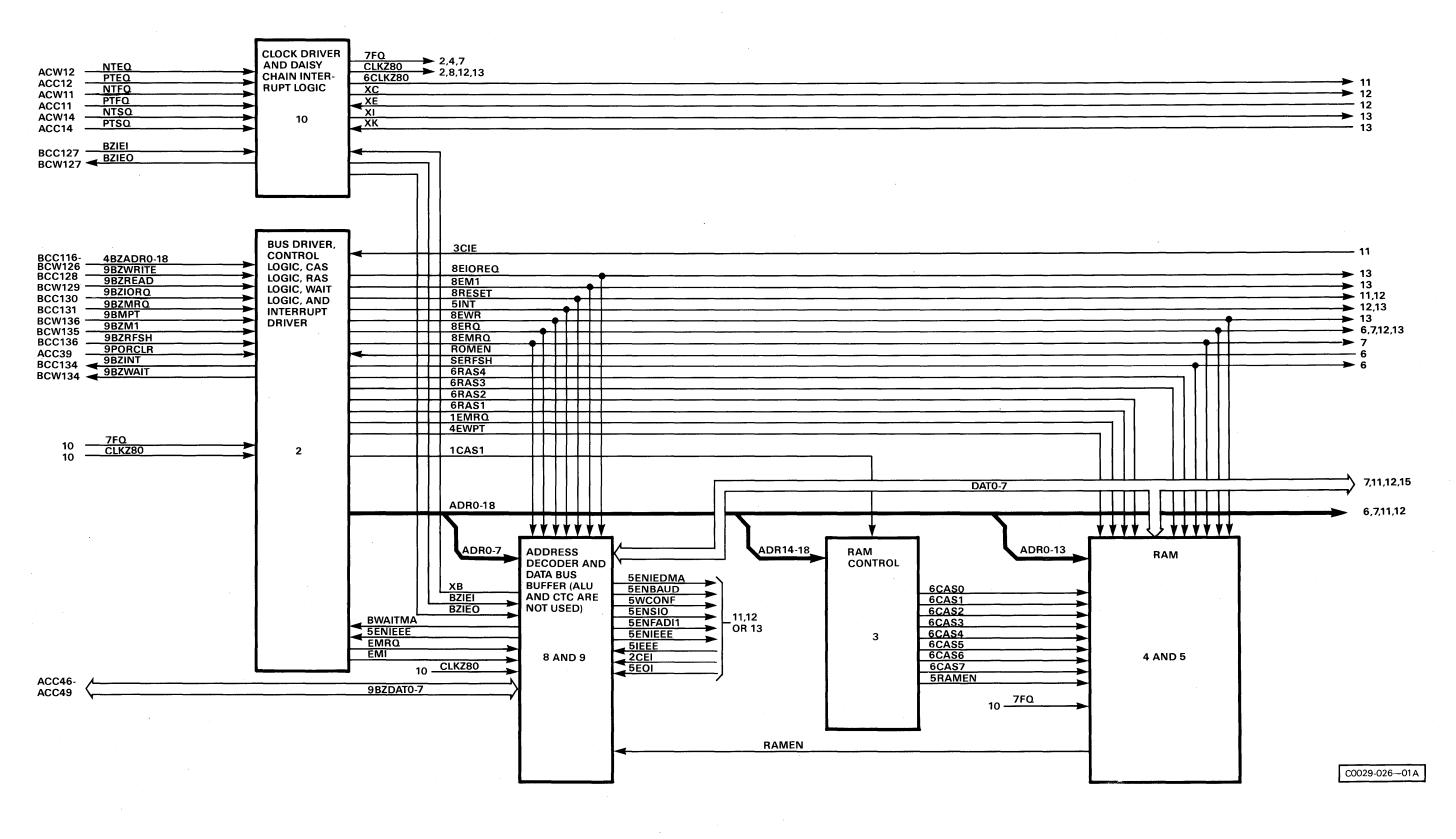

| F | -04 <b>-</b> 26  | Memory PCB                                      |

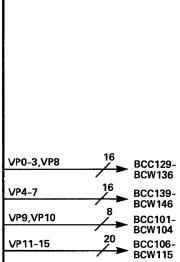

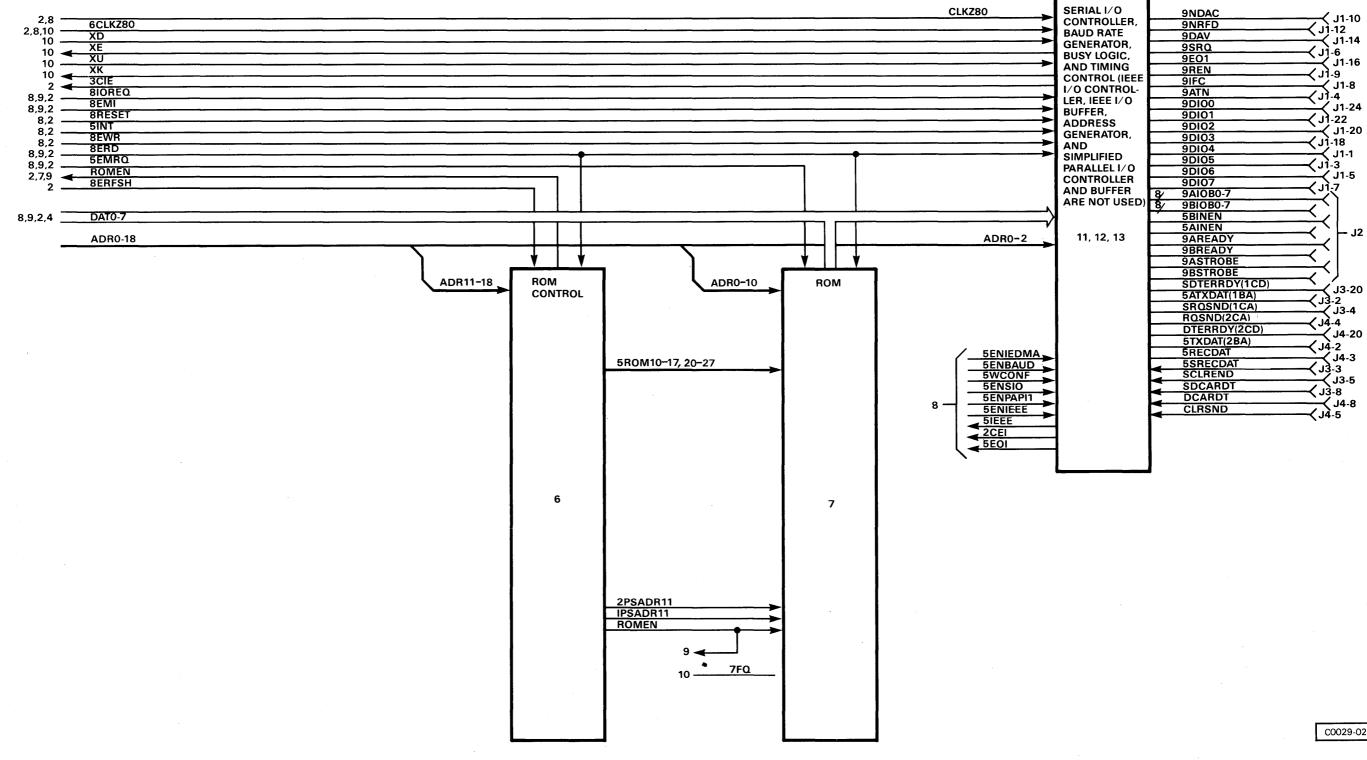

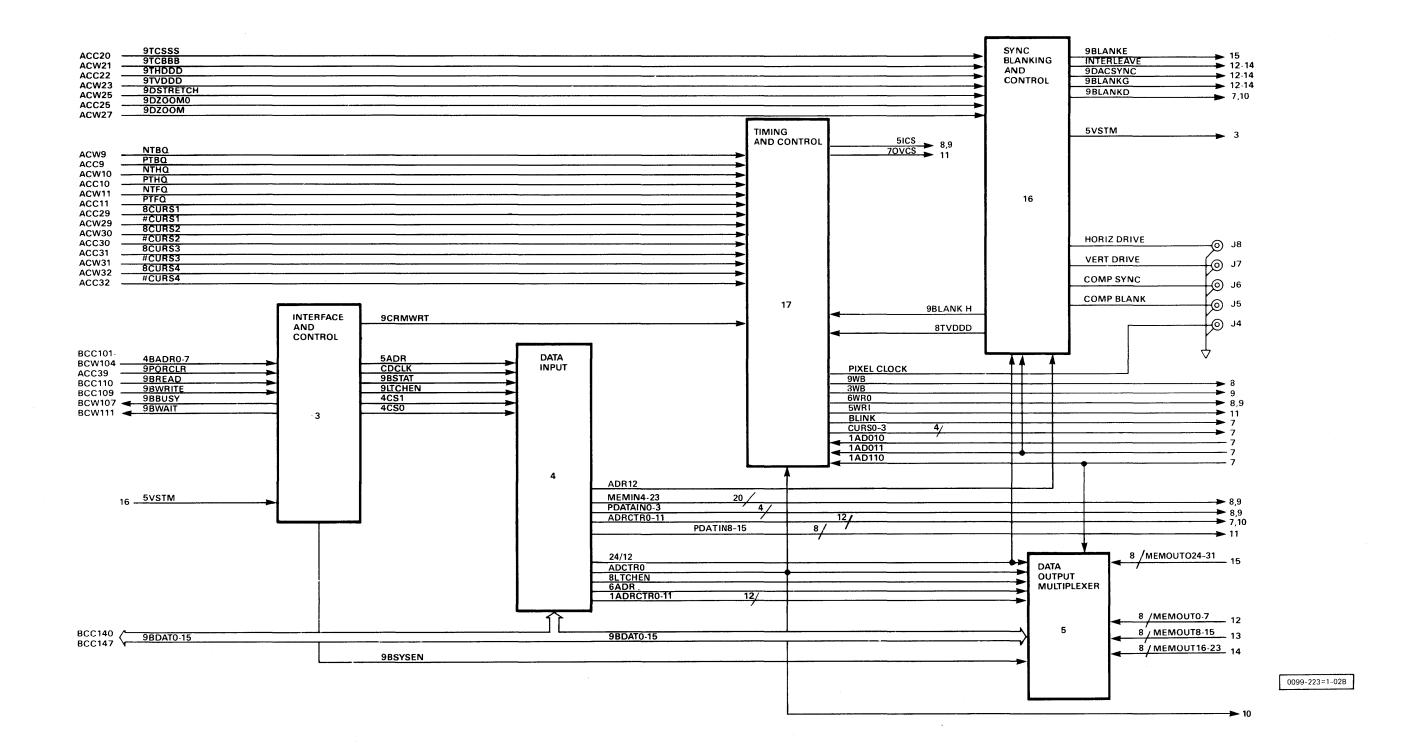

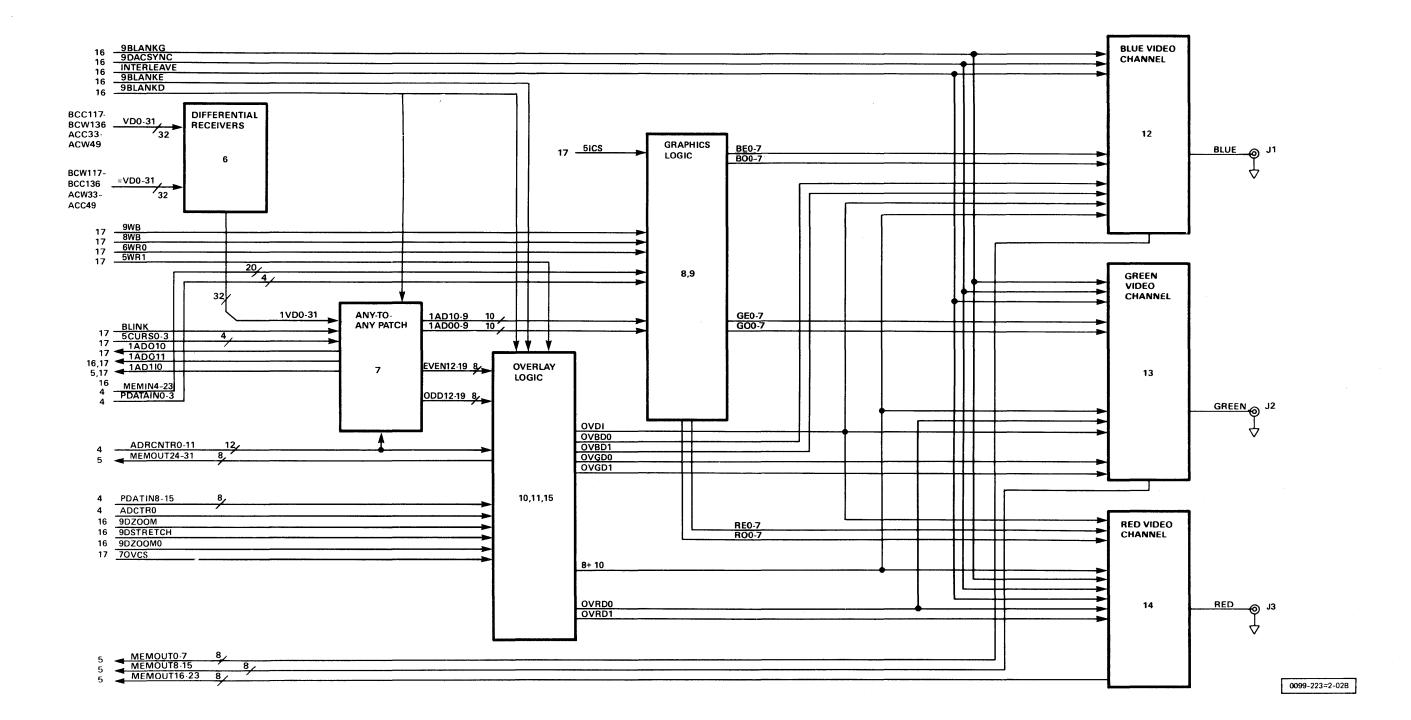

| F | -04-27           | Video 7 PCB                                     |

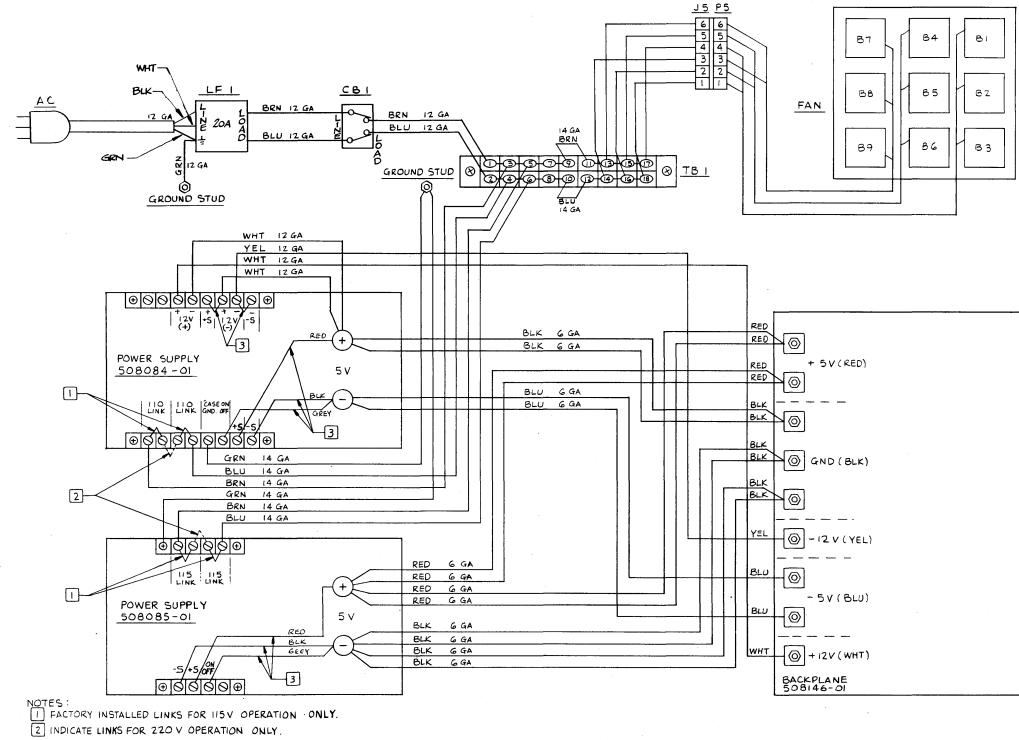

| F | -04 <b>-</b> 28  | AC Power Distribution                           |

| F | -04-29           | Expansion PCB                                   |

| F | -04-30           | Video 1 PCB                                     |

| F | -04 <b>-</b> 30a | Video 6 PCB                                     |

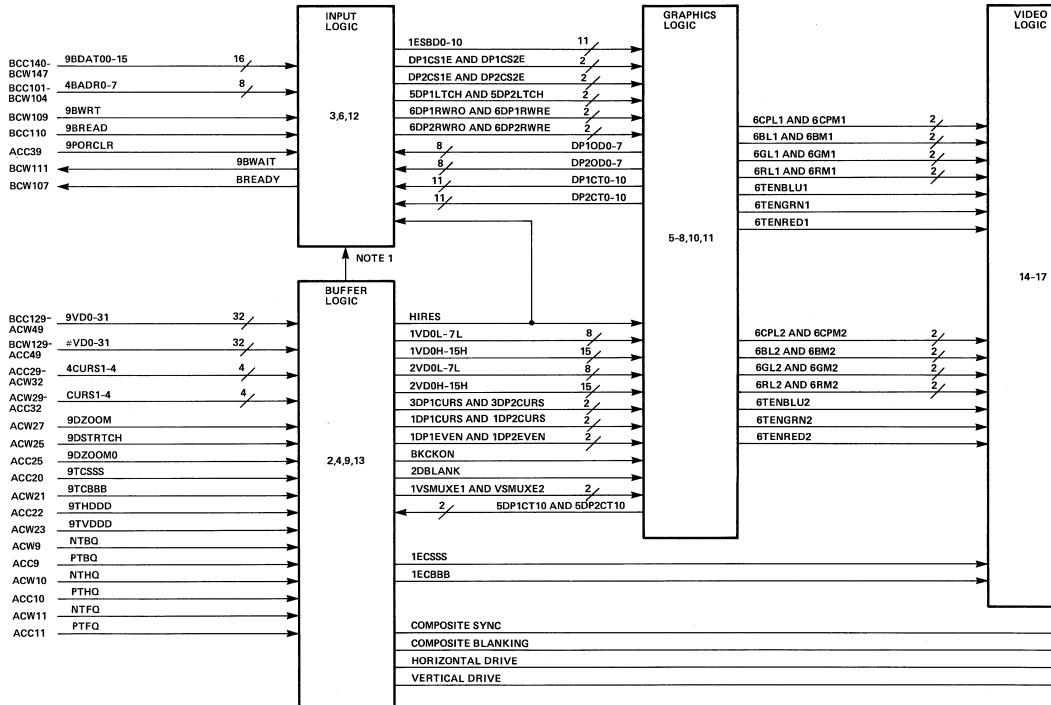

| F | -04-31           | Video 8 PCB                                     |

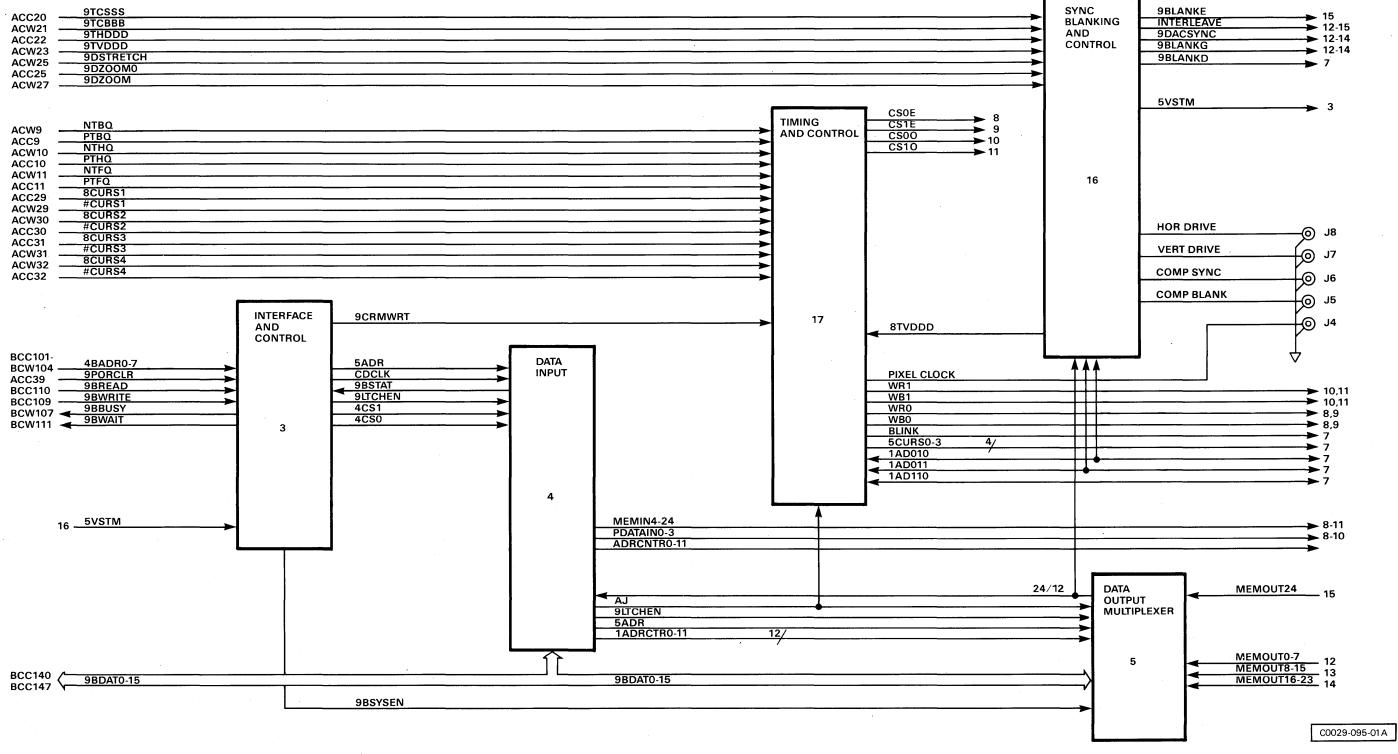

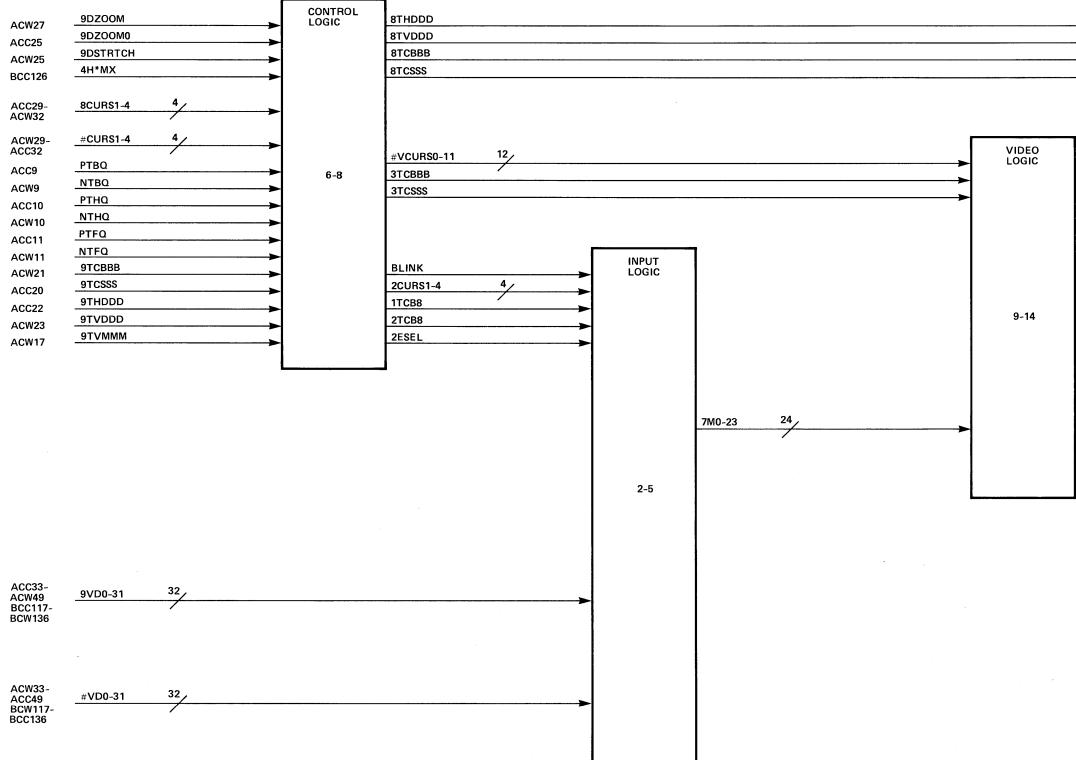

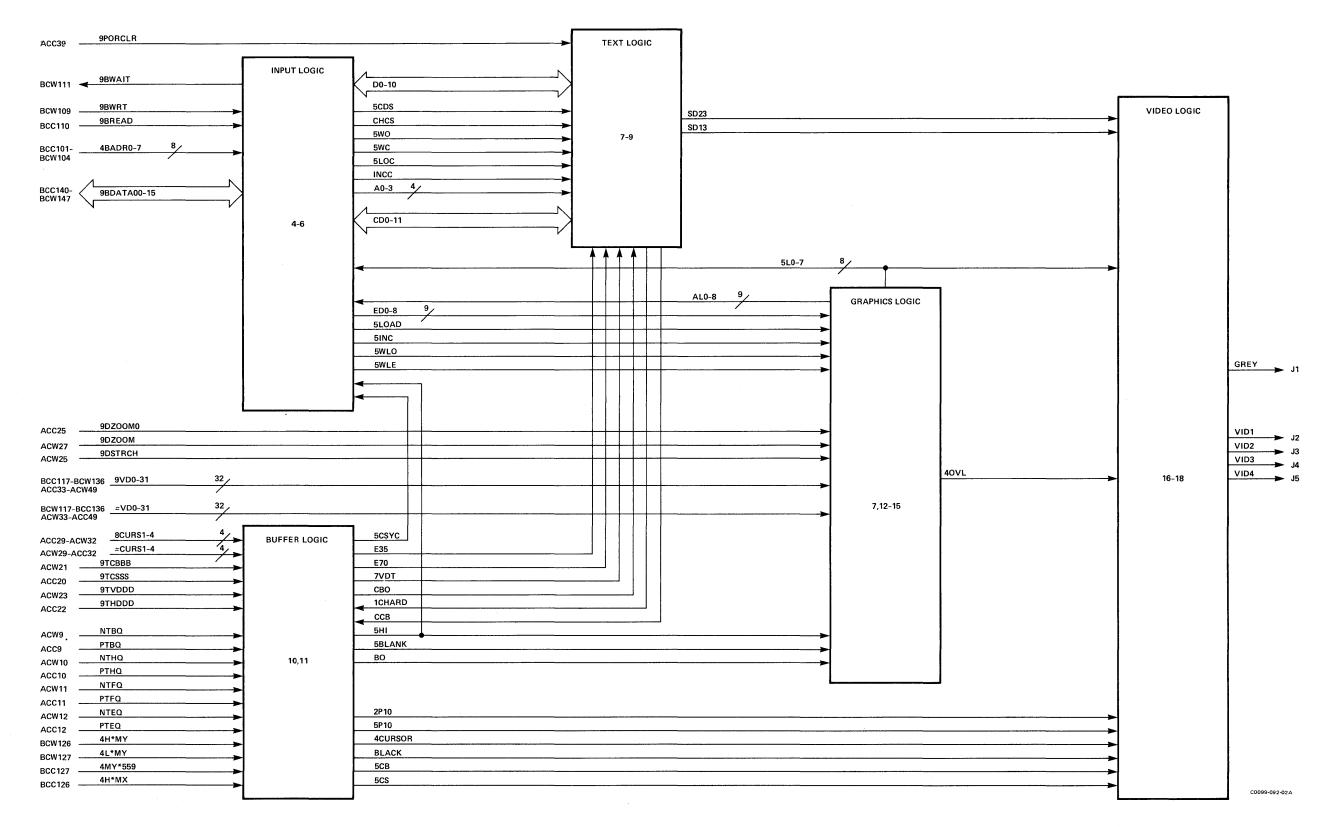

| f | -04-32           | Video 12 PCB                                    |

| F | -04-33           | Transform Processor PCB                         |

| F | -04-34           | Processor Logic                                 |

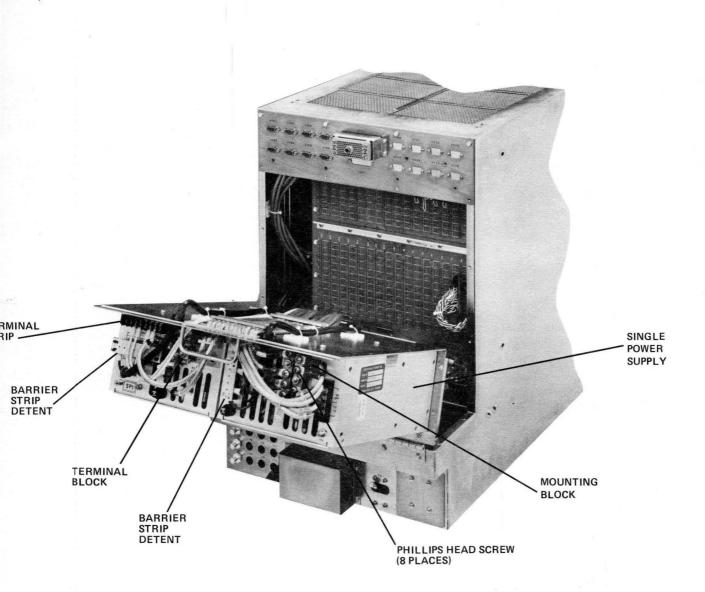

| F | -05-1            | Power Supply Assemblies Removal And Replacement |

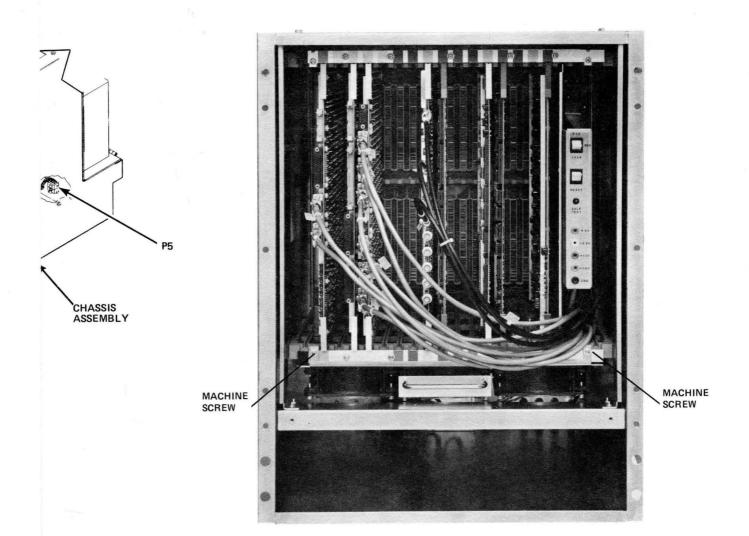

| F | F05 <b>-</b> 2   | Fan Plate Assembly Removal and Replacement      |

### Chapter 1

#### GENERAL INFORMATION

### 1.1 INTRODUCTION

The 9460 product line is designed and manufactured by Ramtek Corporation, 2211 Lawson Lane, Santa Clara, California 95050. This hardware reference manual provides a qualified technician with all the information necessary to install, configure, operate, and maintain the 9460.

### 1.2 HOW TO USE THIS MANUAL

This manual is a single volume reference for the 9460 operator or technician. Chapters and appendices are as follows:

- ¤ Chapter 1 General Information

- ¤ Chapter 2 Installation

- ¤ Chapter 3 Operation

- ¤ Chapter 4 Functional Description

- ¤ Chapter 5 Maintenance

- ¤ Chapter 6 Parts List

- ¤ Appendix A Glossary

- ¤ Appendix B Index

## 1.2.1 General Information

Chapter 1 gives an overview of the manual, a summary of related documents, safety precautions and warnings, Ramtek service information, and a detailed equipment description.

### 1.2.2 Installation

Chapter 2 contains receiving and reshipping information and detailed facility requirements. System configuration, turn-on, checkout, and expansion are included.

### 1.2.3 Operation

Chapter 3 describes and locates 9460 controls and indicators. Instructions include turn-on, operation, and turnoff.

### 1.2.4 Functional Description

Chapter 4 contains a functional description. Following a discussion of 9460 concepts, functional elements are described and analyzed.

### 8000080-02A

### 1.2.5 Maintenance

Chapter 5 contains preventive, corrective, removal, and replacement procedures.

#### 1.2.6 Parts List

Chapter 6 contains parts information and ordering procedures.

#### 1.2.7 Glossary

Appendix A lists glossary terms and abbreviations encountered in graphic display systems.

#### 1.2.8 Index

Appendix B lists manual topics referenced to page numbers.

### 1.3 MANUAL REVISION INFORMATION

Periodically, a change package or a reissued manual is published to stay current with circuit and component improvements as they develop and are tested. This manual has the following revision information:

- ¤ List of effective pages

- ¤ Request for changes form

- ¤ Reader comment form

- m Notice of changes (not included in new or reissued manuals)

#### 1.3.1 List of Effective Pages

This is a list of all manual pages referenced to current revision number. Ramtek publishes a list of effective pages each time a manual is issued, reissued or a change package is issued. Insert the list of effective pages when you add or delete change pages.

#### 1.3.2 Request for Changes Form

If you wish to receive changes, please fill out and mail the self-addressed postcard at the front of this manual. You will then receive change packages as they are published.

#### 1.3.3 Reader Comment Form

Ramtek Technical Publications Department supplies a self-addressed reader comment form to obtain user feedback. Please enter any comments, suggestions, or complaints on the form. Include page, paragraph, figure, or table number as applicable. The reader comment form is inserted after the last manual page.

### 1.3.4 Notice of Changes

A notice of changes will accompany each change package. Follow the information in the notice when inserting and deleting pages. New or reissued manuals do not require a notice of changes.

### 1.4 RELATED DOCUMENTS

Peripherals that connect to the 9460 are documented in separate manuals. Table 1-1 lists peripheral manuals, reference manuals for related Ramtek products, and commercial publications.

The information supplied under date and issue columns was correct when this manual was published. Request the latest issue when ordering.

### 1.5 SAFETY

This paragraph has important safety information that you should read and understand before installing, operating, or servicing the 9460. Only qualified maintenance technicians should service or adjust internal components. Never reach into the equipment unless someone who can render aid is present.

Throughout this manual you will encounter safety warning and caution notices. A warning alerts you to conditions that could result in personal injury, loss of life, or long-term health impairment. A caution alerts you to conditions that could result in damage to, or destruction of, equipment.

#### 1.5.1 Electrical Safety

The 9460 is equipped with switching power supplies. Therefore, you could encounter high voltage capable of causing death or serious injury; be extremely cautious when servicing equipment with power applied. The following warning is inserted before all hazardous procedural steps.

### WARNING

High voltage capable of causing death or serious injury exists when power is applied and internal components are exposed.

Within the 9460, signal ground is isolated from earth ground, but the chassis can develop an electric charge if leakage occurs between the low side of the ac supply and the chassis. This condition can pose a definite health hazard to anyone touching the cabinet. For this reason, you must ground the chassis, via the power cable, to earth ground. 8000080-02A

Table 1-1. Related Documents

| Title                                                                            | Date           | Issue         |

|----------------------------------------------------------------------------------|----------------|---------------|

| Ramtek RM-9460 Software Reference Manual                                         | September 1982 | 8000081-01A   |

| VAX/VMS RM-9400/RM-9460 Device Driver                                            | 1983           | 8000085-01A   |

| RM-9400 Series Graphics Display System<br>Internal Programming Manual            | September 1981 | 01A           |

| Advanced Micro Devices Bipolar Micropro-<br>cessor Logic And Interface Data Book | 1981           | 02            |

| Zilog Z80A-CPU                                                                   | 1977           |               |

| Motorola MC68000 Processor                                                       |                | MC68000UM/AD3 |

| Bit Pad One Users Manual, Summagraphics<br>Corporation                           | May 1969       | Revision A    |

| Ramtek General Purpose Keyboard Hardware<br>Reference Manual                     |                |               |

| Ramtek GM-850 Series Graphic Monitor<br>Hardware Reference Manual                | 1980           | 504615 F      |

| Ramtek General Purpose Interface Manual<br>RM-9000                               |                | 503161        |

| DEC PDP11 Interface Manual                                                       |                | 503702        |

| Interdata Interface Manual                                                       |                | 503173        |

| AN/YUK7 Interface Manual                                                         |                | 503175        |

| HP 21XX Interface Manual                                                         |                | 504309        |

| Varian 73 Interface Manual                                                       |                | 503168        |

| Data General Interface Manual                                                    |                | 503167        |

| 2701 PDA Interface Manual                                                        |                | 503176        |

| Cursor Controller Manual                                                         | <b></b>        | 503158        |

| GC-104 Trackball Manual                                                          |                | 504170        |

| DEC LSI-II Interface Manual                                                      |                | 8000033       |

| GC-105 Lightpen Manual                                                           |                | 80000018      |

#### WARNING

To avoid serious injury or death, verify that chassis ground is connected to a good earth ground.

The 9460 is shipped with a three-conductor power cable and corresponding three conductor plug. The 120 Vac power plug (NEMA 5-20P) has three prongs; one prong connects to the high side of the ac supply, one prong connects to the low side, and the third, offset, prong connects to ground. At the installation site, the mating power receptacle must have the ground socket tied to a good earth ground. Chapter 2 has additional grounding information.

#### 1.5.2 Fire Safety

Warning systems are available that detect overheating or smoke before a fire becomes apparent. Detection systems designed for installations requiring fire protection or special building construction are listed in the National Fire Protection Association (NFPA) Standard Number 75. To obtain a copy of this standard, write to:

### National Fire Protection Association 470 Atlantic Avenue Boston, Massachusetts 02210

Fire control requirements are normally included in local building codes, and your insurance carrier can recommend appropriate fire control apparatus. Since water based systems can damage electronic equipment, Ramtek recommends carbon dioxide.

### 1.6 FCC COMPLIANCE

The 9460 complies with FCC requirements for a Class A computing device when installed and operated as directed in this manual. The cabinet front access panel must remain closed when power is applied. During installation, you must tighten the screws that fasten peripheral cables to respective jacks. Likewise, all BNC connectors must mate securely to avoid unwanted radio frequency interference (RFI).

### 1.7 RAMTEK SERVICE

Ramtek maintains a complete Field Engineering Department which includes onsite service, depot repair facilities, and a full staff of technical specialists. For special situations or problems that cannot be resolved by our field offices, Ramtek specialists are available for phone consultation, or if necessary, for on-site consultation.

Ramtek maintenance agreements cover complete on-site service including all parts, labor, and expenses for Field Engineer on-site support. If a one-year maintenance agreement is purchased with the 9460, Ramtek will provide on-site

### 8000080-02B

installation and checkout in lieu of the 90-day, F.O.B. factory warranty. If installation is purchased with the 9460 we will not only install the hardware, but upgrade the 90-day factory warranty to on-site. On-site service is also available on a time and material basis.

Ramtek maintains a full service depot to repair or exchange modules during or after the warranty period. You must obtain prior approval and a request for material authorization (RMA) number before returning any merchandise to the our depot. Parts must be shipped prepaid.

For additional information regarding service offered by Ramtek's Field Engineering Department, call your local Ramtek Office or call Field Engineering, at (408) 988-2211.

#### 1.8 DESCRIPTION

This paragraph describes physical aspects of 9460 components and supplies information about peripherals and accessories. Electrical, functional, and environmental specifications are also described.

#### 1.8.1 Components

Modular 9460 components (table 1-2) simplify maintenance and enhance configuration flexibility. Official Ramtek nomenclature, common names, and part numbers appear in table 1-2.

| Official Description        | Common Name                | Part Number            |

|-----------------------------|----------------------------|------------------------|

| Cabinet assembly            | Roll-around Cabinet        | 508424 <b>-</b> XX     |

| 9460 Final Assembly Chassis | Chassis Assembly           | 508490 <b>-</b> XX     |

| Processor PCB               | System Processor (Z80)     | 504047-07              |

| Processor PCB               | System Processor (MC68000) | 508217                 |

| Serial Link Cursor PCB      | Serial Link PCB            | 504075 <b>-</b> 04     |

| Serial Link Cursor PCB      | Serial Link PCB            | 508952                 |

| MCP 2 PCB                   | MCP PCB                    | 508221 <b>-</b> 01     |

| Sync PCB                    | Sync PCB                   | 508268-01              |

| 10X12 Refresh Memory PCB    | Memory PCB                 | 508072 <b>-</b> 01     |

| Video 7 PCB                 | Video 7 PCB                | 505955-00*             |

| Processor Expansion II PCB  | Expansion PCB              | 504907-20              |

| Video 1 PCB                 | Video 1 PCB                | 504079-02              |

| Video 6 PCB                 | Video 6 PCB                | 509287 <b>-</b> 01     |

| Video 8 PCB                 | Video 8 PCB                | 505542-01              |

| Video 12 PCB                | Video 12 PCB               | 506407-XX*             |

| Video Load PCB              | Video Load PCB             | 504970                 |

| Pixel Formatter PCB         | Pixel Formatter PCB        | 505508 <del>-</del> 00 |

| Transform Processor PCB     | Transform PCB              | 506577 <b>-</b> 01     |

| Power Supply (5V)           | Single Power Supply        | 508084-01              |

| Power Supply (5V/12V)       | Triple Power Supply        | 508085-01              |

#### Table 1-2. 9460 Components

\* Manufactured in an A or B configuration.

Ł

A specific 9460 may not have all of these components, and component part numbers may vary depending upon date of manufacture and configuration. Depending upon site power availability, you can order the 9460 in a 120 Vac version or a 220 Vac version.

For some applications, an interface PCB may be desirable. Ramtek manufactures nine interface PCBs (table 1-3). Four interface PCBs install in the 9460: the GPIF, the UYK IF, the Varian IF, and the IBM IF. The other five interface PCBs install in the corresponding host computer.

Peripherals and monitors are listed in table 1-4. Monitors are available for color or monochrome applications. Screen sizes are 13-, 19-, and 25-inches measured diagonally. A "-C" means cabinet mounted, "-R" means rack mounted, "-S" means stylized. The designation "LP" means long persistence phosphor. Please note that some peripheral options require specific 9460 configurations. Consult your Ramtek sales representative when ordering.

Accessories include miscellaneous hardware items, cables for peripheral devices, and a test extender PCB. Standard peripheral cables are manufactured in 25, 50 or 100 foot lengths. Non-standard length cables are available, subject to factory quotes.

#### 1.8.2 Physical Description

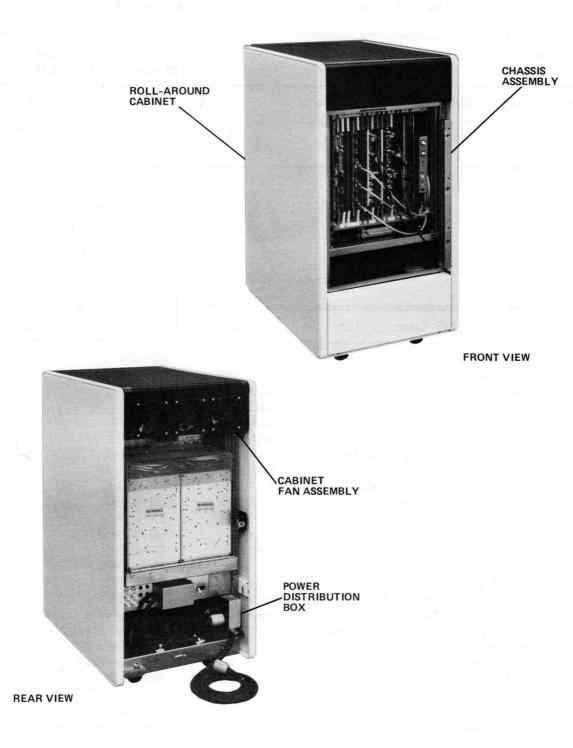

The 9460 (figure 1-1) is a modularized cabinet-mounted device that processes text, image or graphics data for display in monochrome or color. A standard 9460 consists of a roll-around cabinet that supports and protects a chassis assembly, a cabinet fan assembly, and a power distribution box, The cabinet has a hinged front access panel and a hinged rear access panel which are removed for clarity in figure 1-1.

If desired, customers can order the 9460 without the roll-around cabinet. In this event, the chassis assembly installs in a standard 19-inch equipment rack. (Refer to chapter 2 for applicable installation instructions.)

The cabinet fan assembly is a metal plate with cutouts for three rotary fans. Fan power comes from the power distribution box, which also supplies ac power to the chassis assembly.

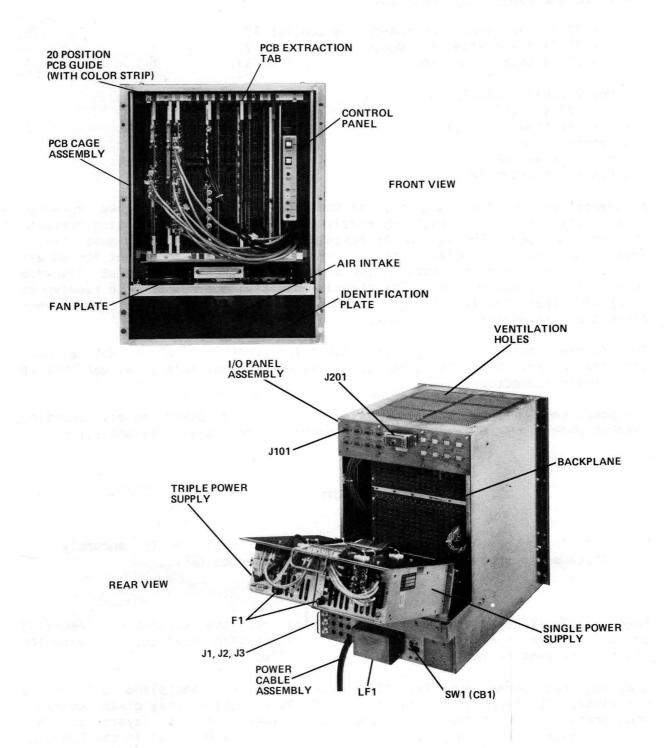

**1.8.2.a** <u>Chassis Assembly</u>. The chassis assembly (figure 1-2) is formed of sheet metal and protects and supports sub-assemblies which are fastened with screws. Components include

¤ Input/output (IO) panel assembly

- J301 is for future use

- J201 is a host computer cable connector

- J101 is one of up to 16 peripheral cable connectors (J101-116)

m Triple power supply (fused by F1)

m Single power supply (fused by F1)

| Model<br>Number | Description                                                                                                                                                                               | Prerequisite                                                                                                                                               | Standard Cable<br>Length (ft.)                    |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| RM-9460-40      | General purpose bidirectional<br>interface. Operation in PIO<br>and DMA modes.                                                                                                            |                                                                                                                                                            | Not provided<br>(mating<br>connector<br>provided) |

| RM-9460-53      | DEC PDP-11 Series bidirec-<br>tional interface. Operation<br>in PIO and DMA modes. Util-<br>izes one SPC slot.                                                                            | Non-processor grant<br>line at the inter-<br>face slot for DMA<br>operation                                                                                | 50                                                |

| RM-9460-54      | DEC LSI-11 Series bidirec-<br>tional Q-bus interface.<br>Operation in QIO and DMA<br>modes.                                                                                               | Non-processor grant<br>line at the inter-<br>face slot for DMA<br>operation                                                                                | 50                                                |

| RM-9460-56      | Interdata 7/8XX Series<br>bidirectional intertace to<br>programmed I/O multiplexer<br>bus or SELCH.                                                                                       | M48-13 compatible<br>card (provided)                                                                                                                       | 50                                                |

| RM-9460-59      | Univac AN/UYK-7 bidirectional<br>interface to NAVY Type B<br>(NTDS FAST) digital data<br>interface (0 V, -3 V logic<br>levels). Usually a DMA<br>interface. See MIL-Std. 1397<br>(ships). | Navy Type B NTDS<br>FAST digital data<br>interface (I/O con-<br>troller)                                                                                   | Not provided<br>(mating<br>connector<br>provided) |

| RM-9460-61      | HP-21MX Series bidirectional<br>PIO/DMA interface.                                                                                                                                        |                                                                                                                                                            | 50                                                |

| RM-9460-64      | Varian 620 and 73 Series<br>bidirectional interface to<br>buffered I/O controller.                                                                                                        | Varian (BIOC) buf-<br>fered I/O con-<br>troller board (P/N<br>E2832) and priority<br>interrupt module<br>(PIM) Model 620/i-<br>l6, and CPU for<br>checkout | 15                                                |

| RM-9460-65      | Data General Nova and Eclipse<br>bidirectional interface                                                                                                                                  | Data General Model<br>4192 cable in CPU                                                                                                                    | 50                                                |

Table 1-3. Intertace PCBs and Cables

| Model<br>Number | Description                                                         | Prerequisite | Standard Cable<br>Length (ft.)                     |

|-----------------|---------------------------------------------------------------------|--------------|----------------------------------------------------|

| RM-9460-71      | IBM 2701 Parallel Data<br>Adapter (PDA) bidirectional<br>interface. |              | Not provided<br>(special<br>I/F panel<br>provided) |

Table 1-3. Interface PCBs and Cables (Continued)

# Table 1-4. 9460 Peripherals

| Official Description            | Common Name | Part Or Model Number |

|---------------------------------|-------------|----------------------|

| Trackball Cursor Controller     | Trackball   | GC-104               |

| Lightpen Cursor Controller      | Lightpen    | GC-105               |

| Joystick Cursor Controller      | Joystick    | GC-106               |

| Graphic Tablet                  | Tablet      | GC-108               |

| 3X Magnification Puck           | Puck        | GC-PUCK              |

| General Purpose Keyboard        | Keyboard    | GK-120               |

| Monitor Assembly, CLR, 13, P22  | Monitor     | GM-853-C             |

| Monitor Assembly,CLR,13,P22     | Monitor     | GM-853-R             |

| Monitor Assembly,CLR,19,P22     | Monitor     | GM-859-C             |

| Monitor Assembly,CLR,19,P22     | Monitor     | GM-859-R             |

| Monitor Assembly,CLR,19,P22     | Monitor     | GM-859-S             |

| Monitor Assembly,CLR,19,LP      | Monitor     | GM-859-CLP           |

| Monitor Assembly,CLR,19,LP      | Monitor     | GM-859-RLP           |

| Monitor Assembly,CLR,19,LP      | Monitor     | GM-859-SLP           |

| Monitor Assembly,CLR,25,P22     | Monitor     | GM-865-C             |

| Monitor Assembly,MON0,13,P4     | Monitor     | GM-873-CP4           |

| Monitor Assembly,MON0,13,P4     | Monitor     | GM-873-RP4           |

| Monitor Assembly,MON0,19,P4     | Monitor     | GM-879-CP4           |

| Monitor Assembly, MON0, 19, P39 | Monitor     | GM-879-CP39          |

| Monitor Assembly,MON0,19,P39    | Monitor     | GM-879-RP39          |

| Monitor Assembly,MON0,19,P4     | Monitor     | HVD-GM879R           |

| Monitor Assembly,MON0,19,P39    | Monitor     | HVD-GM879R           |

| Monitor Assembly,MON0,19,P43    | Monitor     | HVD-GM879R           |

A0099-142-02A

Figure 1-1. 9460

A0099-143-02

# Figure 1-2. Chassis Assembly

#### 8000080-02B

m Three BNC feedthrough connectors (J1-3)

J1 is red video (or monochrome monitor 1)

J2 is green video (or monochrome monitor 2)

J3 is blue video (or monochrome monitor 3)

¤ Power cable assembly ¤ Line filter (LF1) ¤ Circuit breaker (CB1) ¤ Control panel ¤ PCB cage assembly ¤ Fan plate assembly

An identification plate is affixed to the floor of the air intake opening. This plate is printed with the model, operating voltage, operating current, and serial number. The air intake beneath the fan plate assembly must remain free of obstruction. Holes in the top of the chassis assembly vent forced air to the intake side of the cabinet fan assembly. These holes must likewise remain free of obstruction. The chassis assembly is prepunched to receive up to 21 additional BNC feedthrough connectors. Unused positions are either plugged or sealed off with a plate.

The I/O panel assembly is a junction point for peripheral cables and a host computer cable. Depending upon configuration ordered, this panel can have up to 16 9-pin connectors.

The power supply assemblies are mounted on a hinged power supply mounting bracket which in turn is fastened with screws to the chassis assembly.

#### NOTE

The hinged power supply mounting bracket must remain securely fastened to suppress radio-frequency interference (RFI).