# Attaché Portable Computer Technical Manual

# OTRONA

#### Attache

# Portable Computer

Technical Manual

Published by Otrona Advanced Systems Corporation Copyright 1983 by Otrona Advanced Systems Corporation Otrona Pub. No. 92051210 Version 1.1 July, 1983

#### Copyright

Copyright (c) 1982 by Otrona Corporation. All rights reserved. No part of this publication may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of Otrona Corporation, 4755 Walnut St., Boulder, Colorado 80301.

#### <u>Disclaimer</u>

Otrona Corporation makes no representations or warranties with respect to the contents hereof and especially disclaims any implied warranties of merchantability or fitness for any particular purpose. Further, Otrona Corporation reserves the right to revise this publication and to make changes from time to time in the content without obligation of Otrona Corporation to notify any person of such revisions or changes.

#### Trademarks

ATTACHE, Charton, and Valet are trademarks of Otrona Corporation, 4755 Walnut St., Boulder, Colorado. References are made throughout this document to the WordStar word processing system and to the Control Program for Microcomputers, commonly known as CP/M. WordStar is a registered trademark of MicroPro International Corporation of San Rafael, California. CP/M is a trademark of Digital Research Inc. of Pacific Grove, California. PREFACE

#### How to Use This Manual

This manual is intended for readers with knowledge of electronics or software who seek information about Attache's design or interface capabilities.

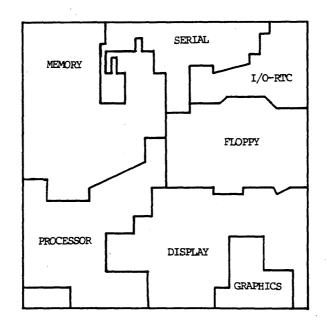

The manual is divided into three sections. The first section is an overview of Attache hardware, which contains a general description of the five Attache modules: the processor board, the display, the diskette drives, the keyboard, and the power supply.

The second section is the theory of operations, which contains a description of system logic flow and the theory of operations for each of the seven logic sections on the processor board.

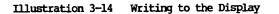

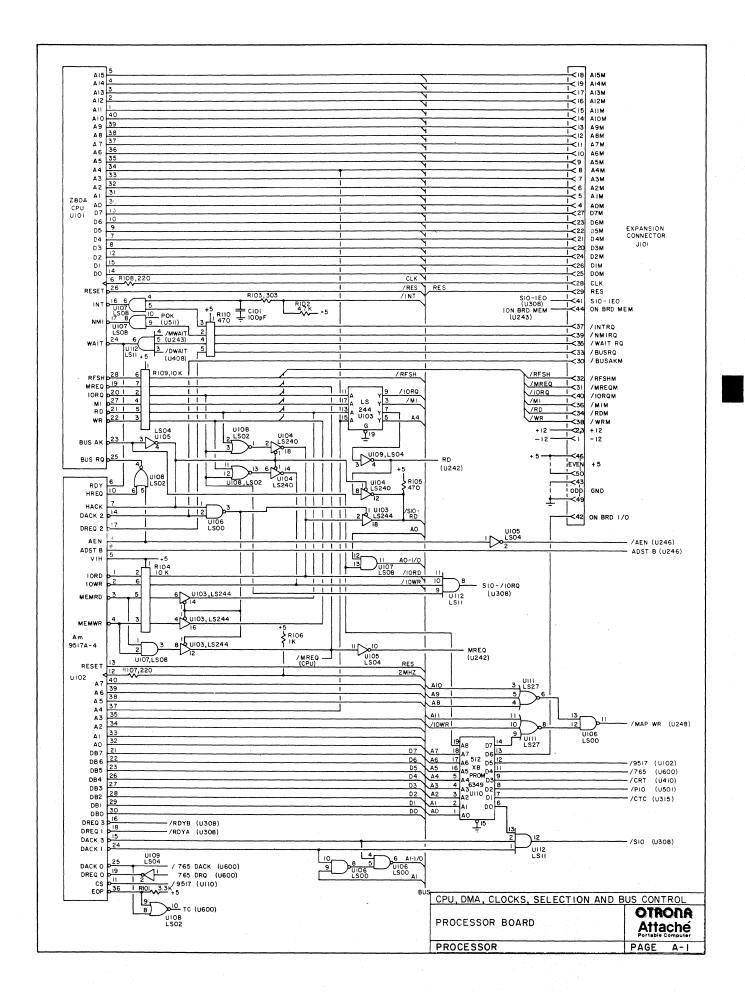

The logic sections are clearly marked on the board with white borders. Each section corresponds to a schematic page in Appendix A. The logic of the modules is also described.

The third section of the manual concerns Attache software. This chapter describes BIOS (Basic Input/Output System), ROM (Read-Only Memory) software, and memory locations.

Common programming functions are included with the appropriate software topic, and are also listed as illustrations on page viii for quick referencing.

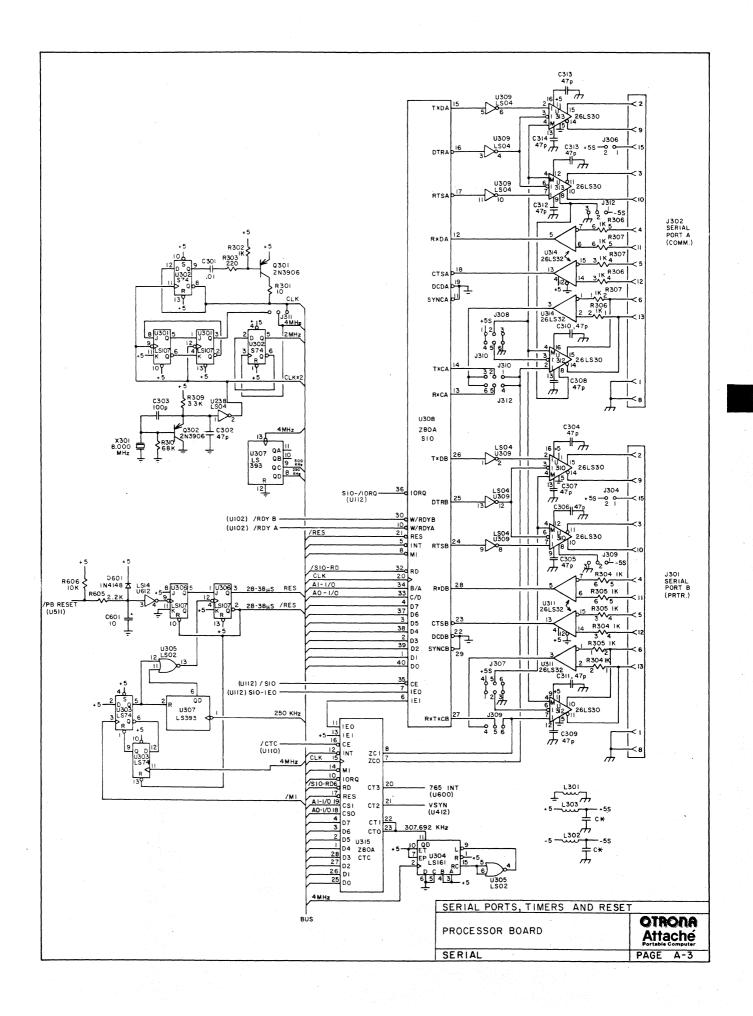

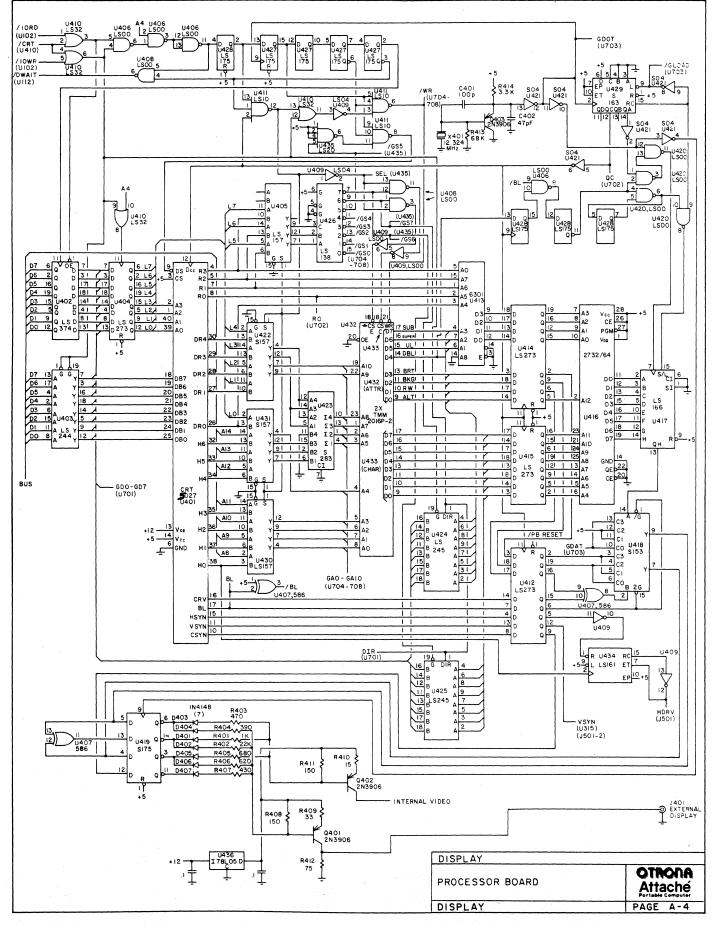

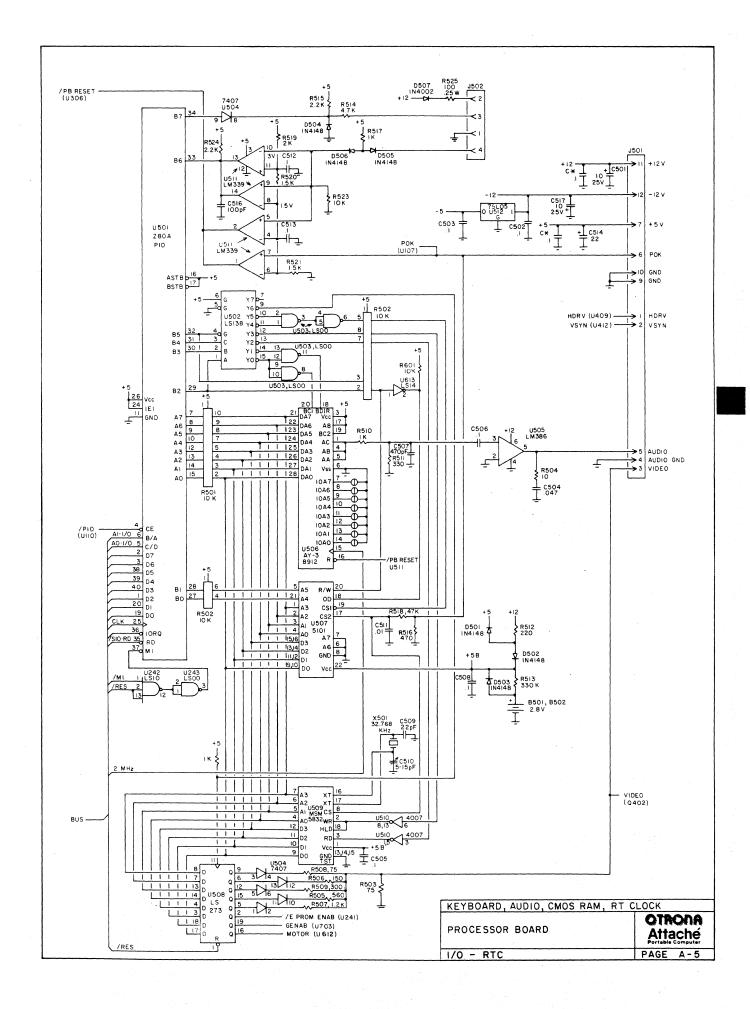

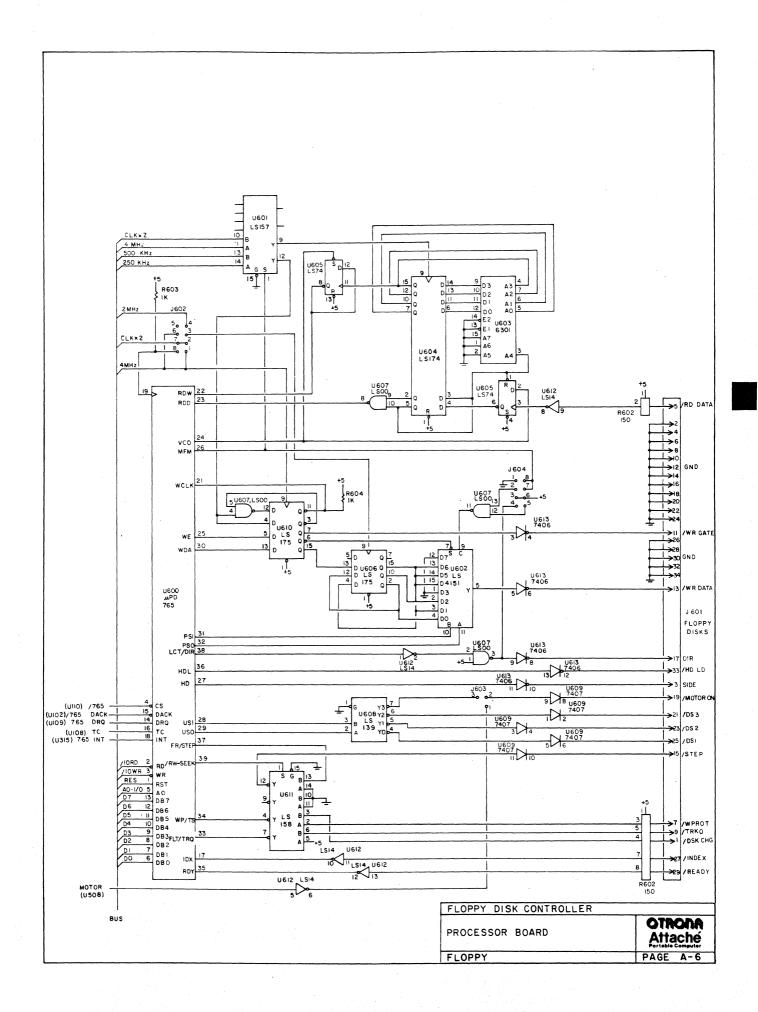

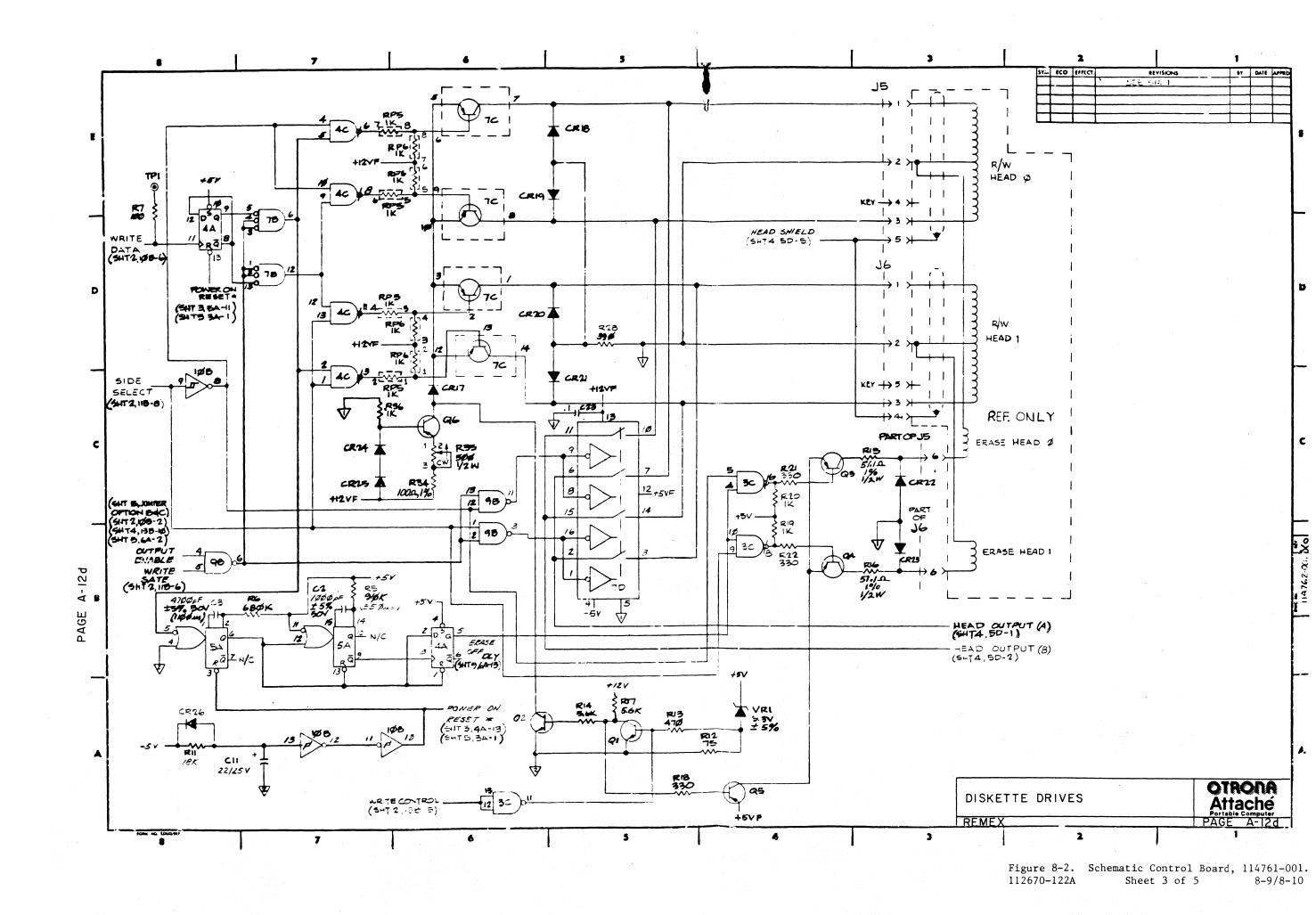

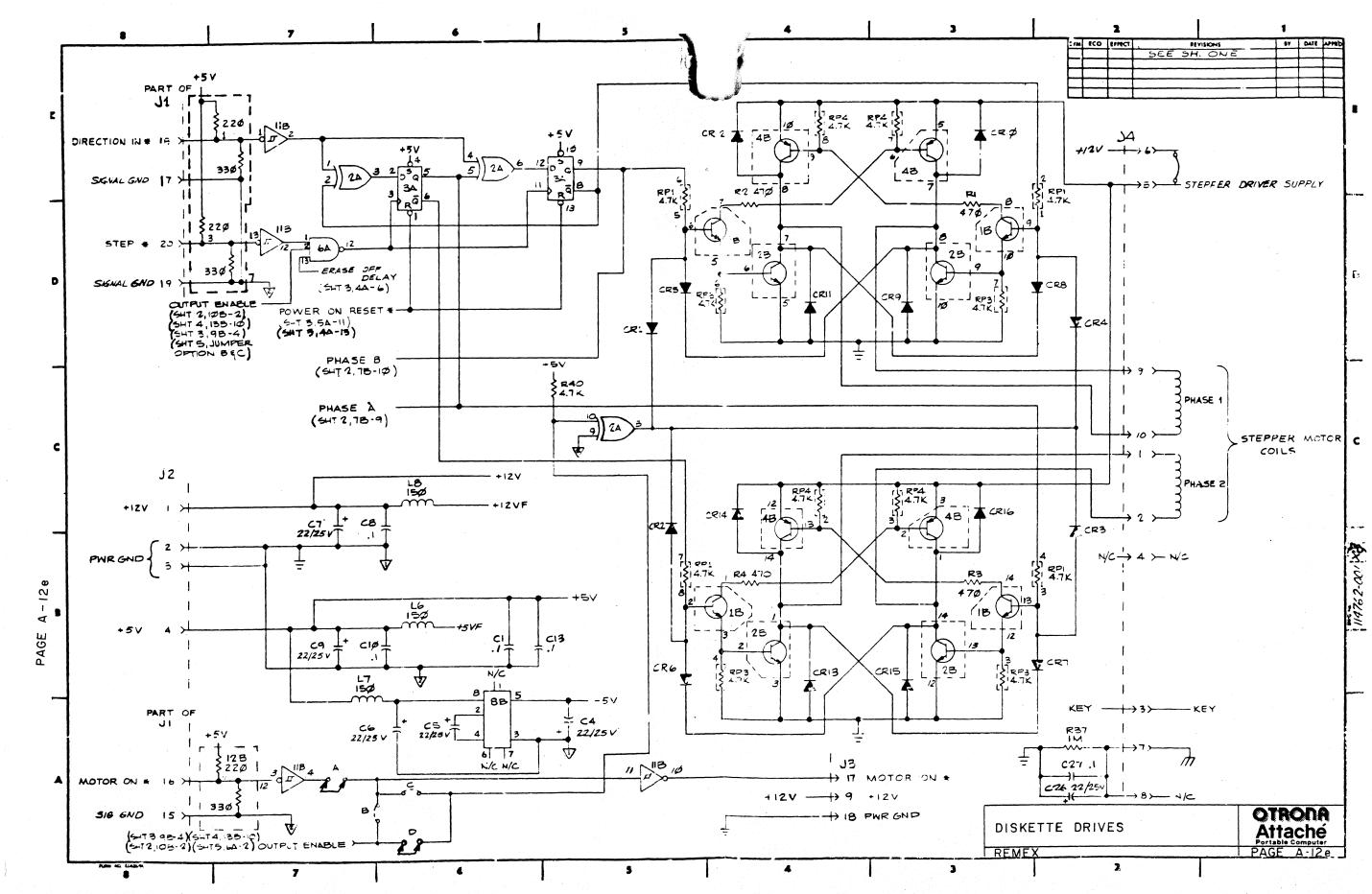

Appendix A contains Attache schematics.

Appendix B is a list of referenced publications.

Appendix C is a list of acronymns.

Appendix D is the glossary.

Appendix E is the index.

# Contents

## I. Hardware

| Hardware Overview 1-1                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

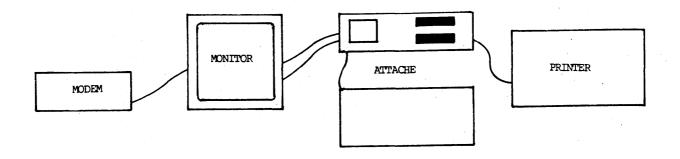

| Attache System 1-2                                                                                                                                        |

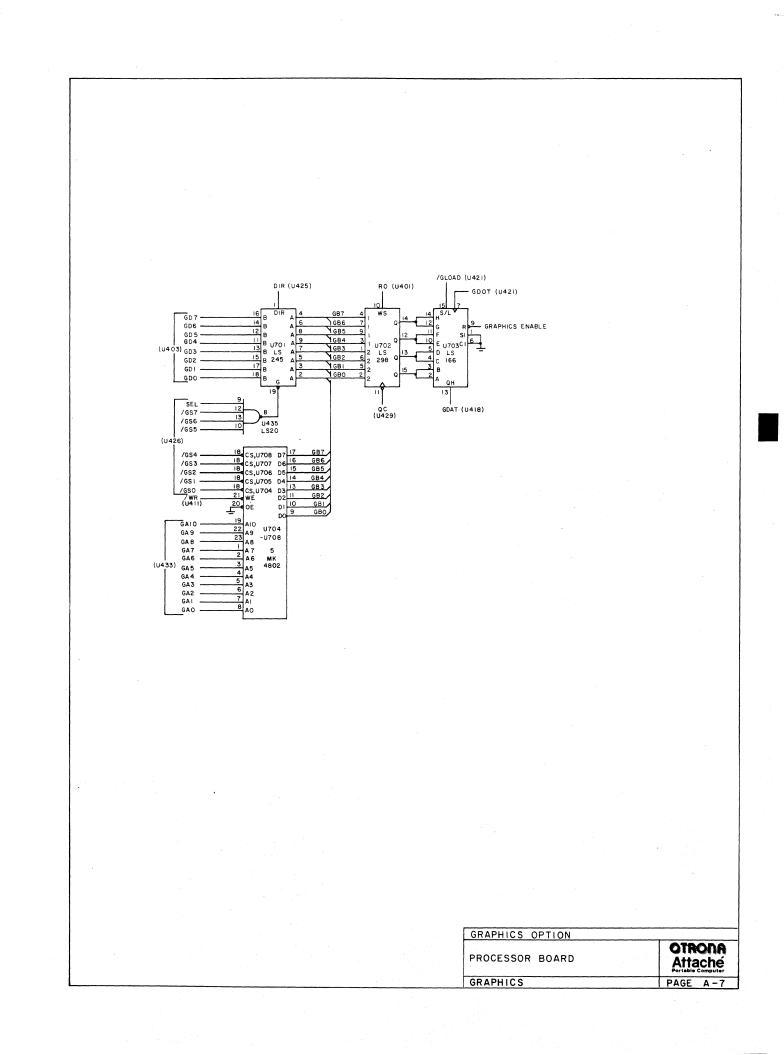

| Processor Board 1-3<br>Processor 1-3<br>Memory 1-4<br>I/O RTC 1-4<br>Floppy Disk 1-4<br>Display 1-4<br>Graphics 1-4<br>Serial 1-5<br>Expansion Option 1-5 |

| Display 1-5<br>Alphanumeric Display 1-5<br>Graphic Display 1-6                                                                                            |

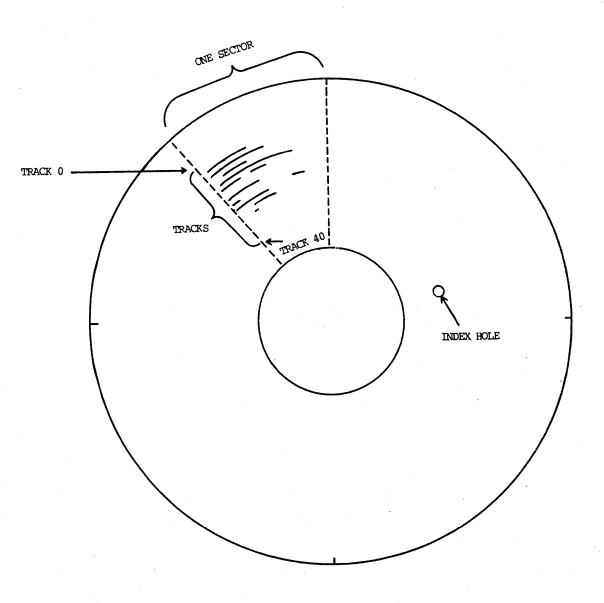

| Diskette Drives 1-6<br>Standard Format 1-6                                                                                                                |

| Keyboard 1-7<br>Multi-function Keys 1-7<br>10-Key Mode 1-7                                                                                                |

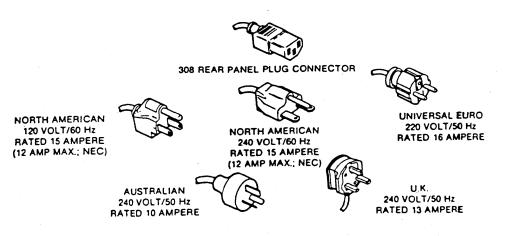

| Power Supply 1-8<br>Setting the Voltage 1-8                                                                                                               |

# II. Theory of Operations

| Introduction                                                                                                                                                       | 2-1                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

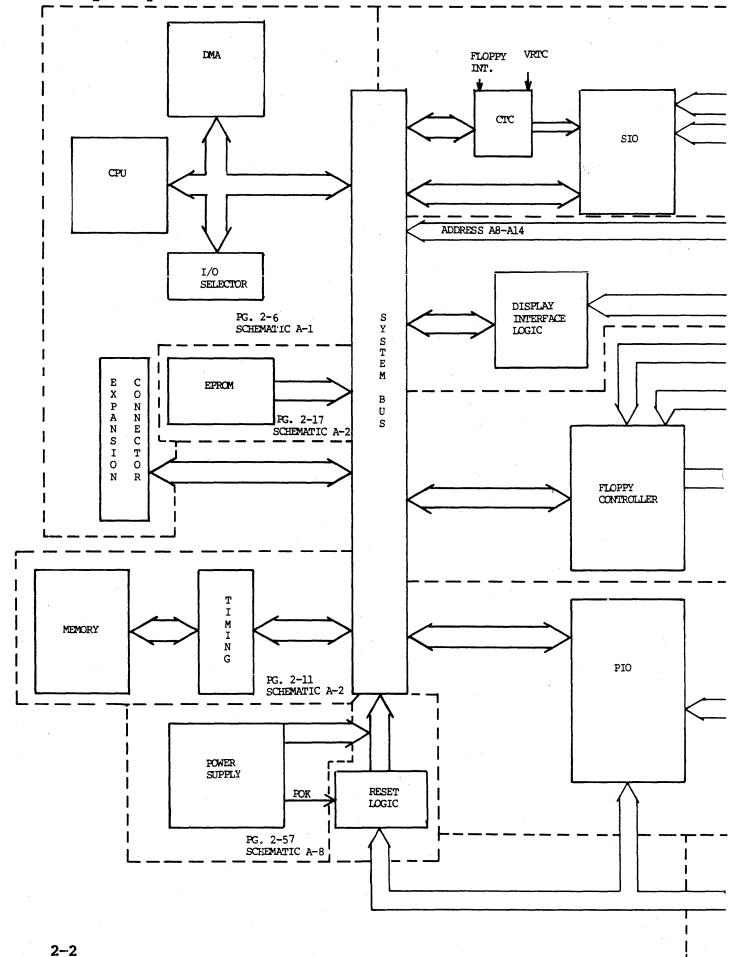

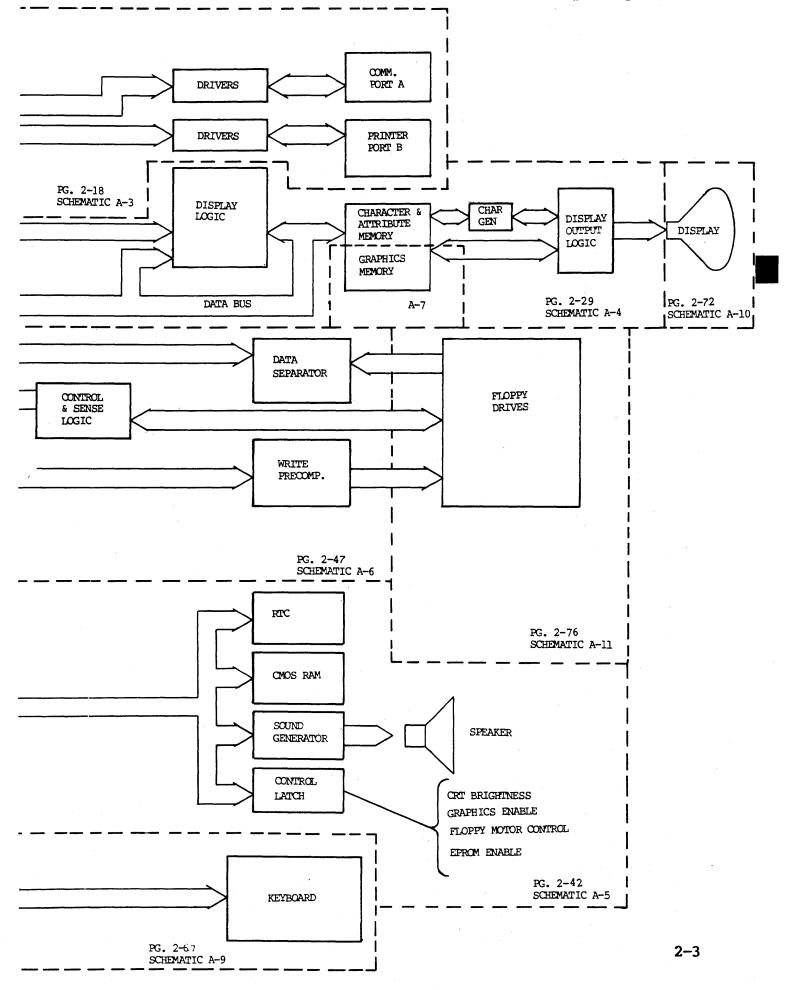

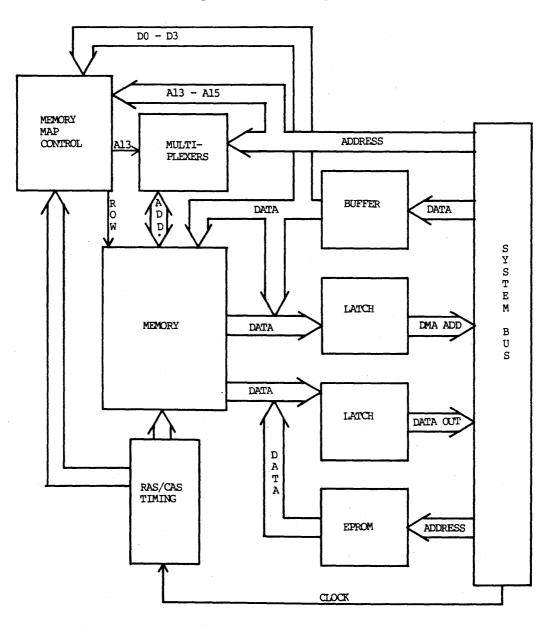

| System Block Diagram                                                                                                                                               | 2-2                                     |

| Logic Overview                                                                                                                                                     | 2-4                                     |

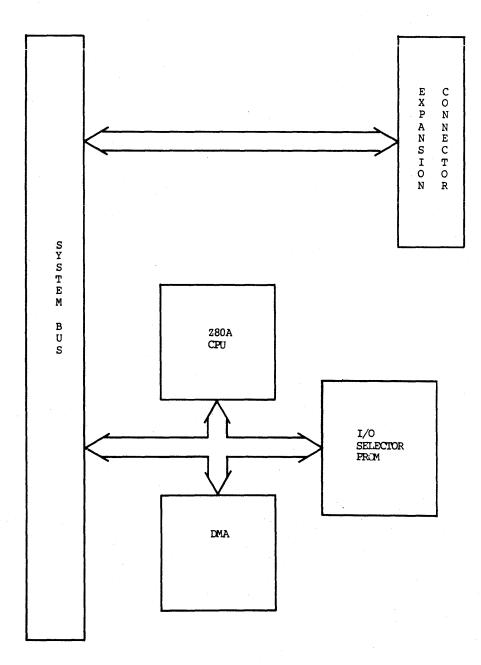

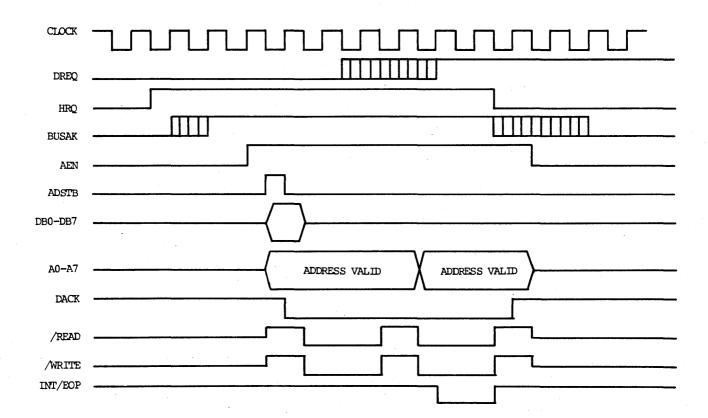

| Processor<br>Central Processing Unit<br>Pin Functions<br>Direct Memory Access Controller<br>Pin Functions<br>DMA Operation<br>I/O Selection<br>Expansion Connector | 2-7<br>2-7<br>2-8<br>2-8<br>2-9<br>2-10 |

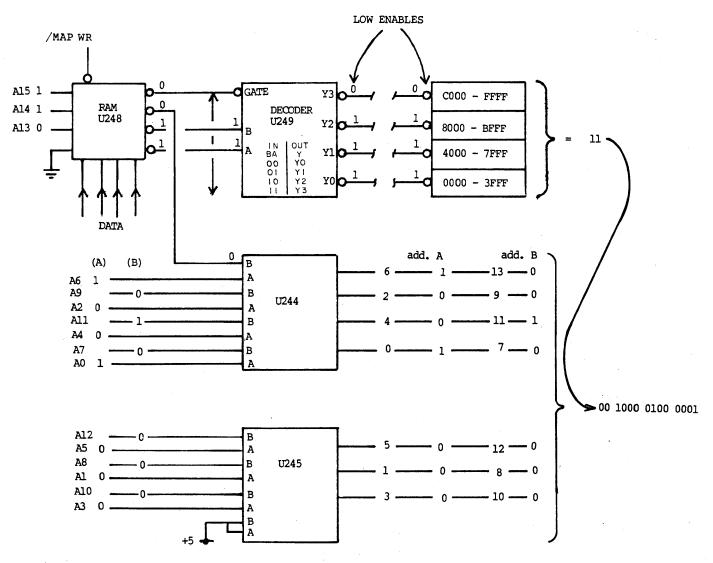

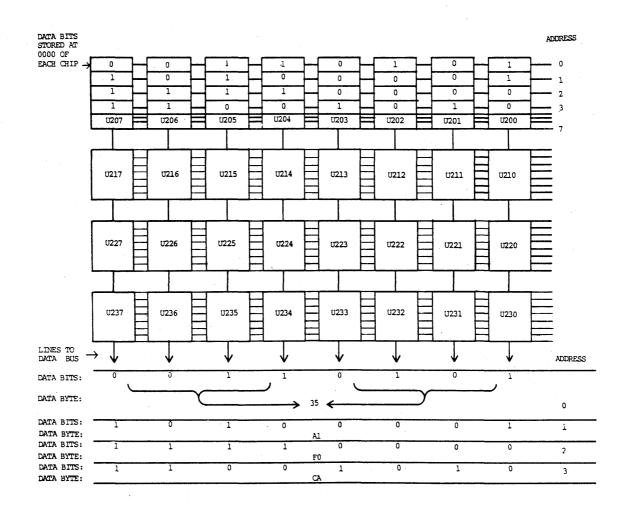

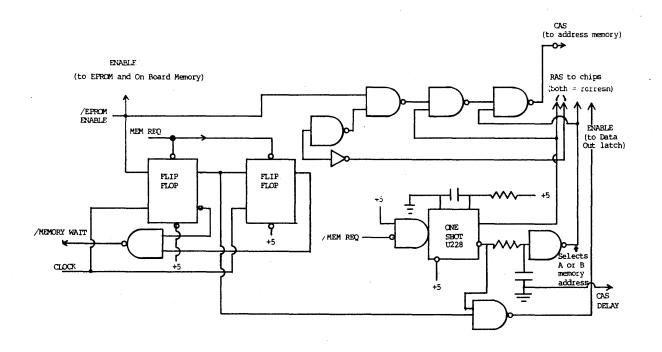

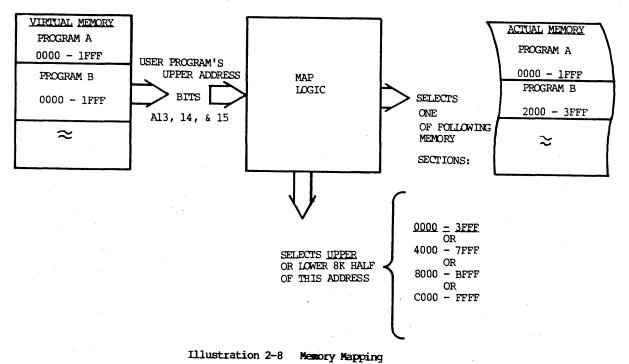

| Memory<br>Addressing RAM<br>Writing or Reading Data<br>Generating RAS/CAS<br>Memory Mapping<br>Erasable Programmable Read-Only Memory                                                             | 2-12<br>2-14<br>2-15<br>2-16                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

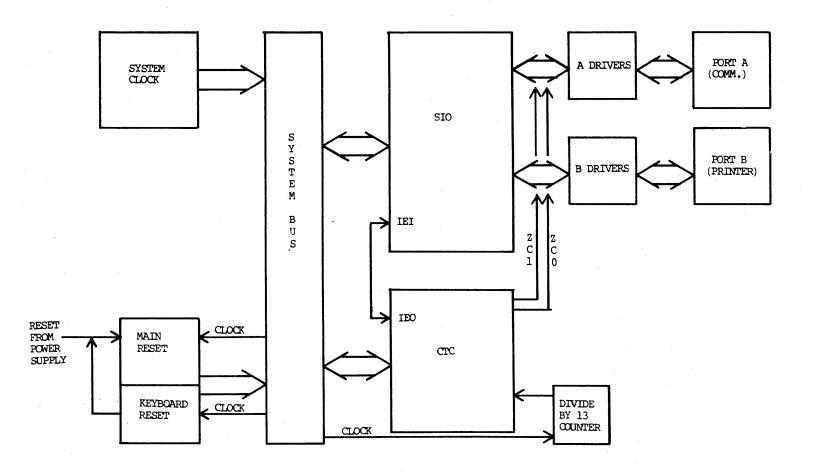

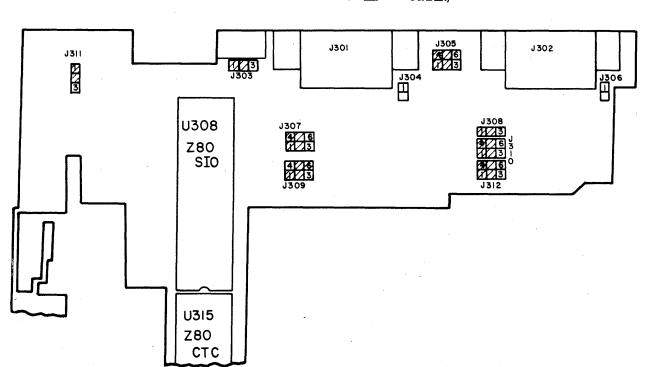

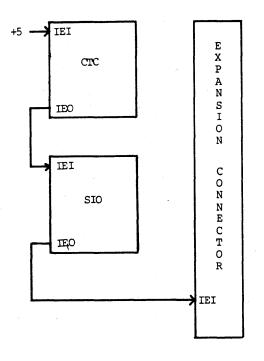

| Serial<br>Clock<br>Reset<br>Serial Input/Output Controller<br>Pin Functions<br>SIO Operation<br>The Ports<br>Jumpers<br>Counter Timer Circuit<br>Pin Functions<br>Interrupts                      | 2-20<br>2-21<br>2-21<br>2-23<br>2-26<br>2-26                 |

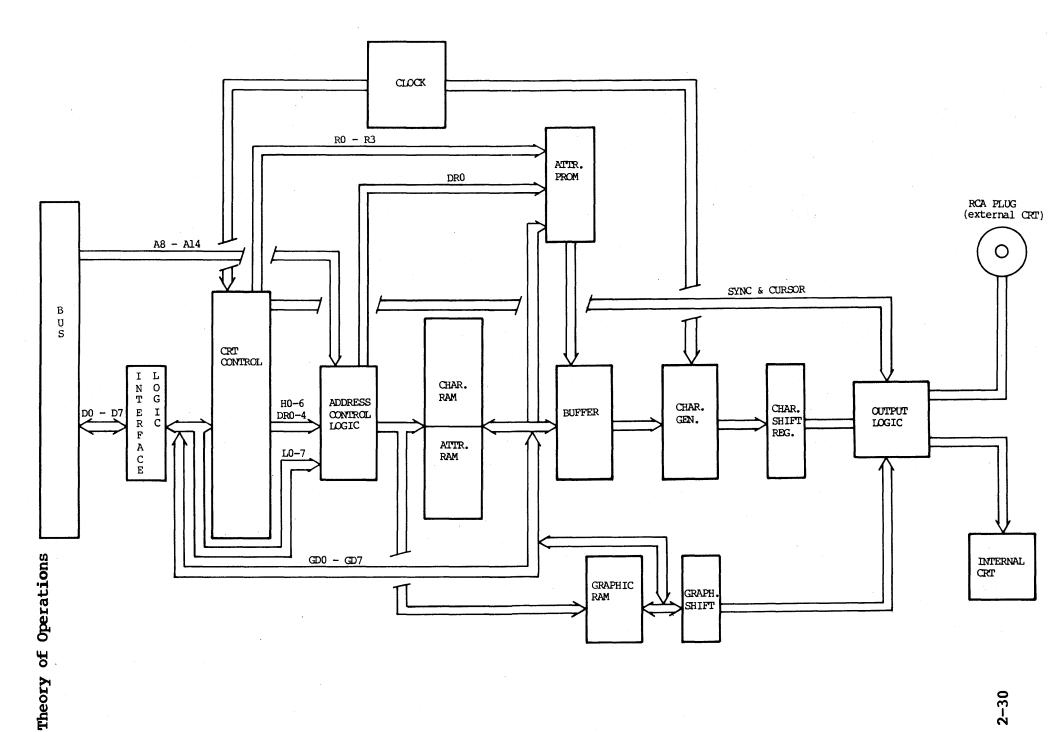

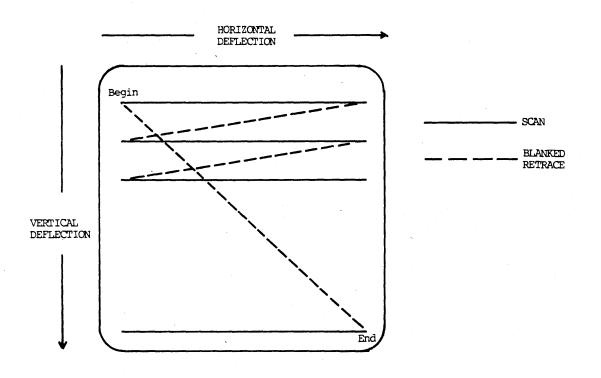

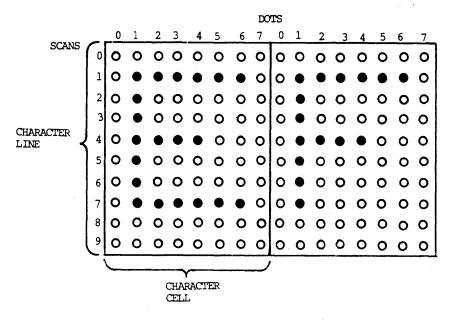

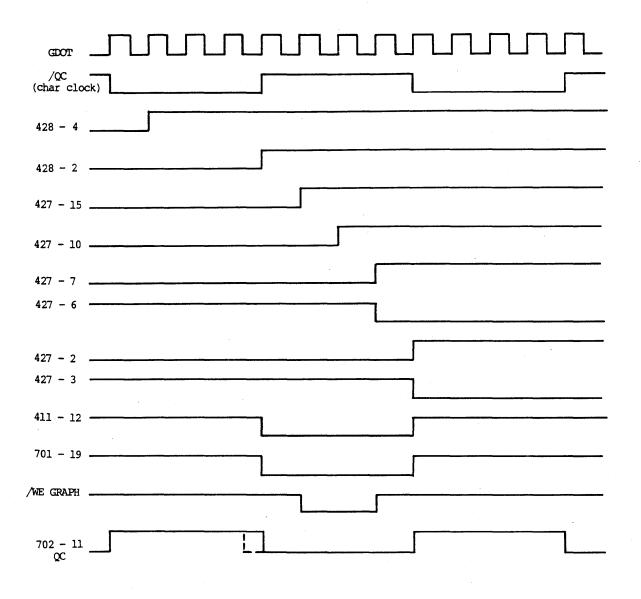

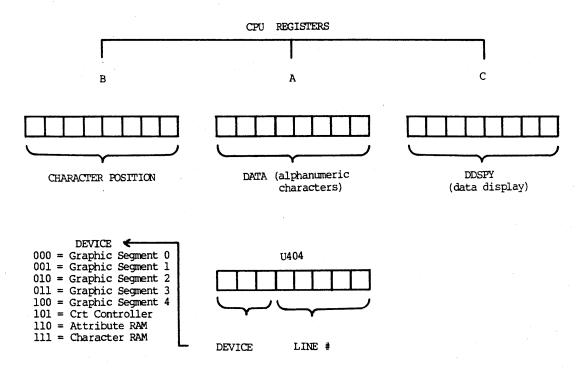

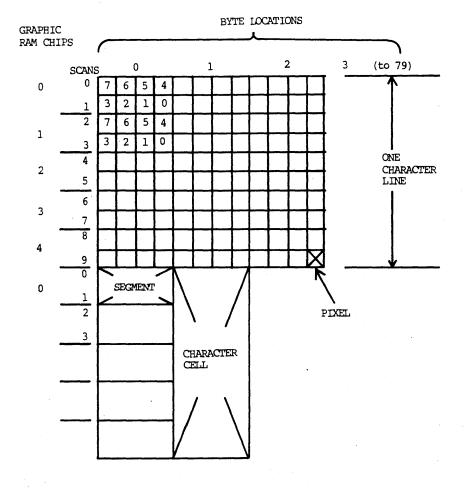

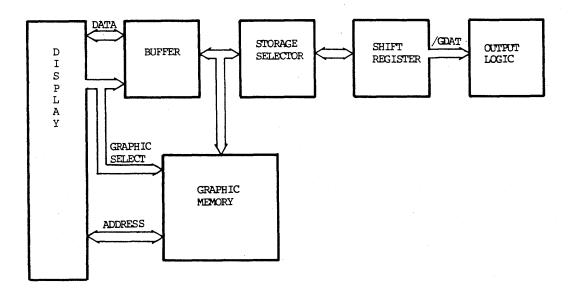

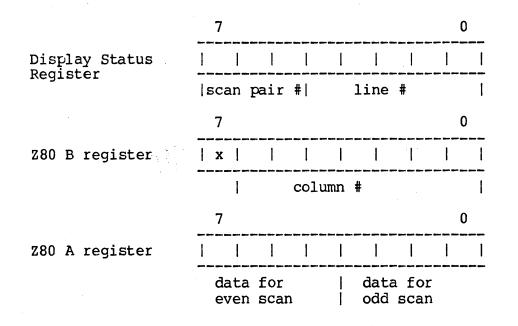

| Display<br>Cathode Ray Tube<br>CRT Controller<br>Pin Functions<br>Timing<br>Reading or Writing to the Screen<br>Selecting the Address<br>Writing the Data on the Screen<br>Attributes<br>Graphics | 2-31<br>2-32<br>2-32<br>2-33<br>2-36<br>2-36<br>2-38<br>2-39 |

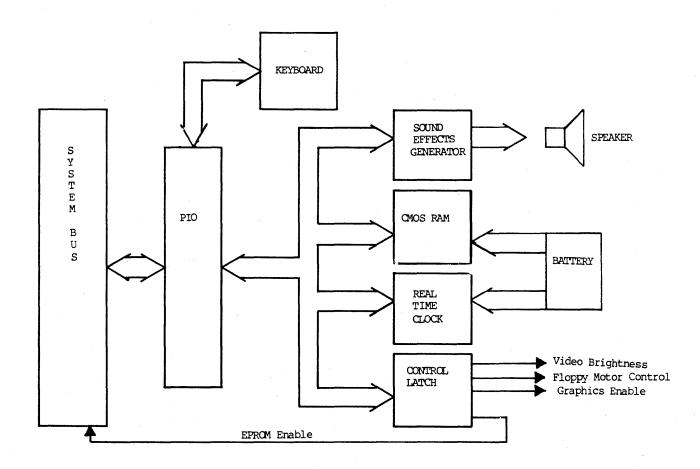

| <pre>I/O RTC Parallel Input/Output Controller Pin Functions Sound Effects Generator CMOS Random Access Memory Control Latch Real Time Clock Keyboard Interface</pre>                              | 2-43<br>2-43<br>2-44<br>2-44<br>2-45<br>2-45                 |

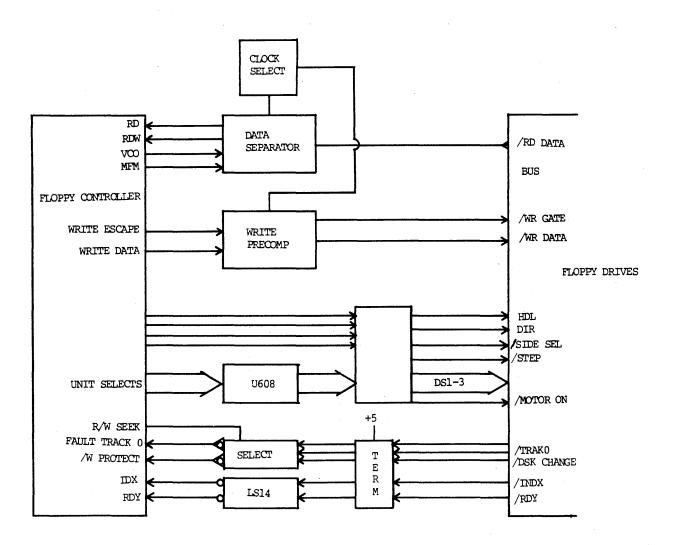

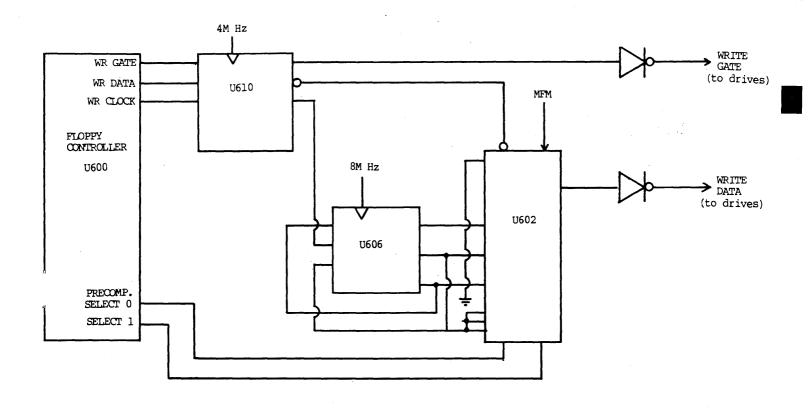

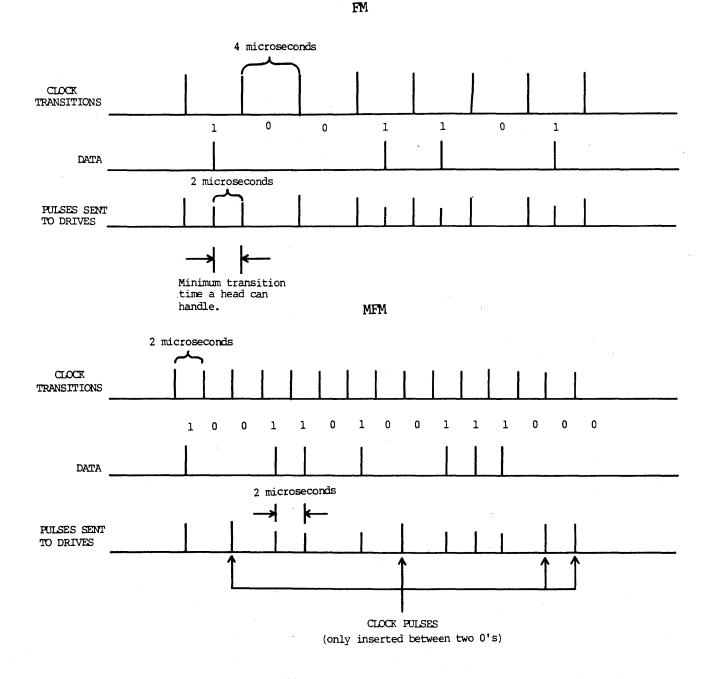

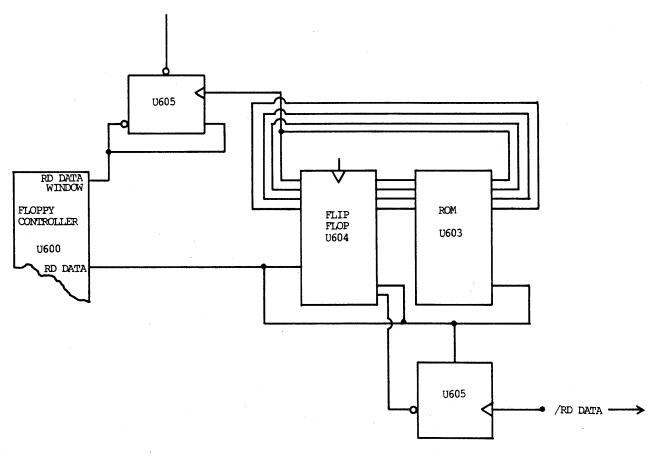

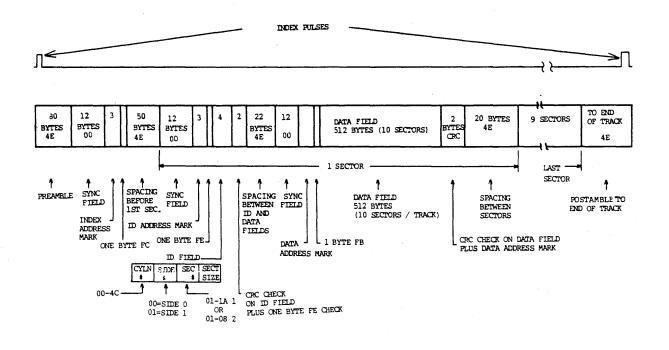

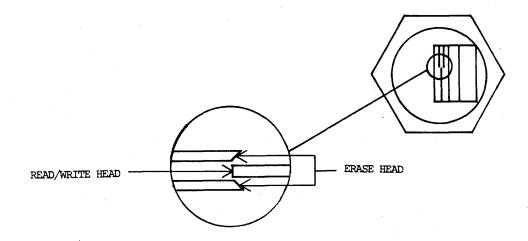

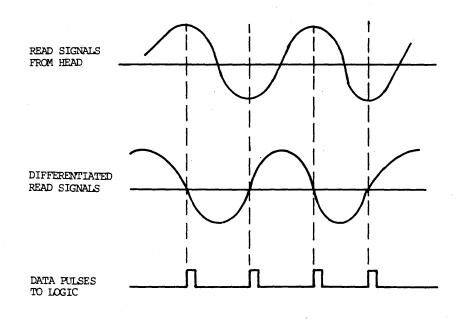

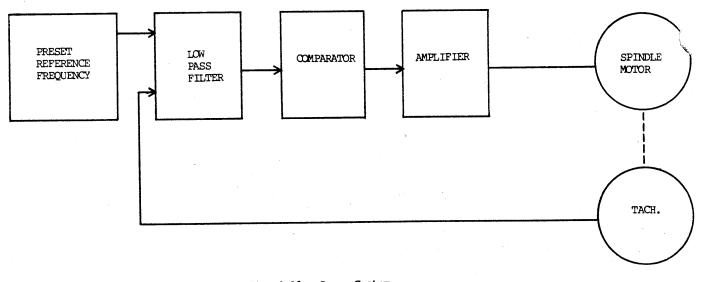

| Floppy<br>Basic Mechanism<br>Read/Write<br>Writing Data on the Diskette<br>MFM and FM<br>Reading Data From the Diskette<br>Diskette Format<br>Diskette Track Format                               | 2-48<br>2-49<br>2-49<br>2-50<br>2-52<br>2-54                 |

| Graphics                                                                                                                                                                                          | 2-56                                                         |

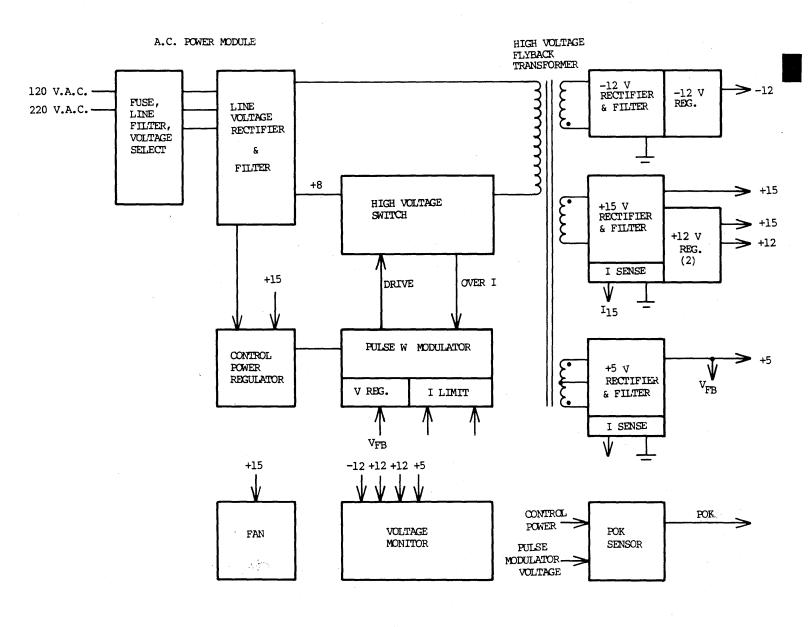

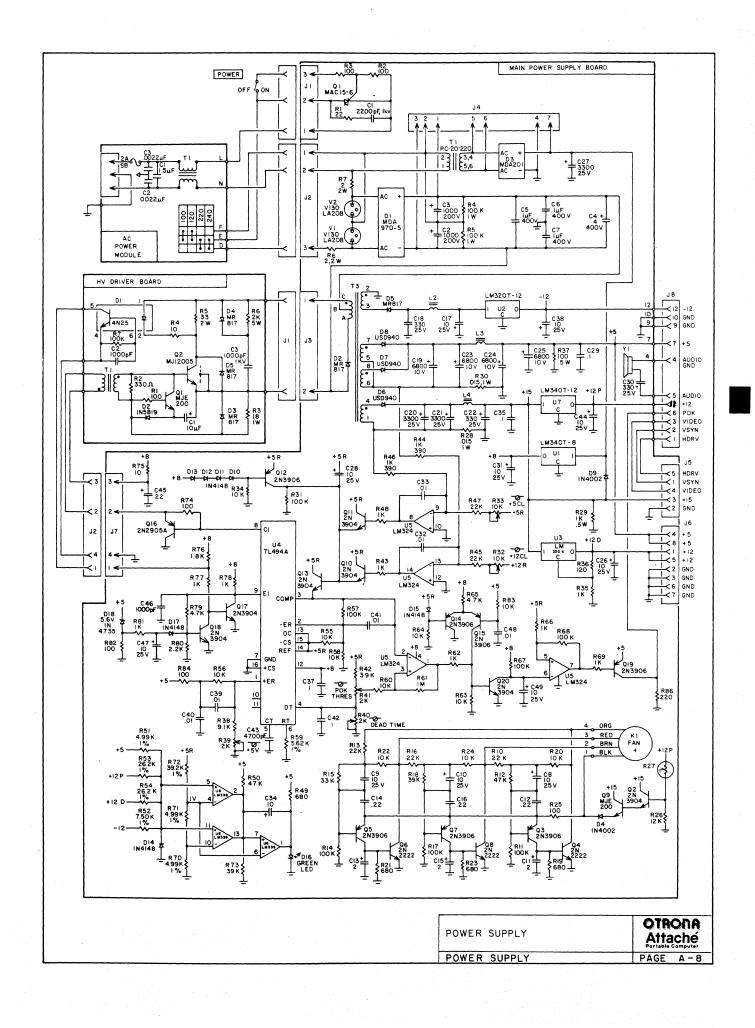

| Power Supply<br>Introduction         |           |

|--------------------------------------|-----------|

| AC Power Module                      |           |

| Control Power Regulator              |           |

| Pulse Width Modulator                |           |

| PWM Dead Time                        | . 2-61    |

| Over-current and Soft Start          |           |

| High Voltage Driver Board            | . 2-63    |

| Flyback Transformer                  | . 2-64    |

| Output Supply Rectifiers and Filters |           |

| Power Okay Sensor                    |           |

| Voltage Monitor                      |           |

| Fan Driver                           |           |

| Connectors                           | • 2-66    |

|                                      |           |

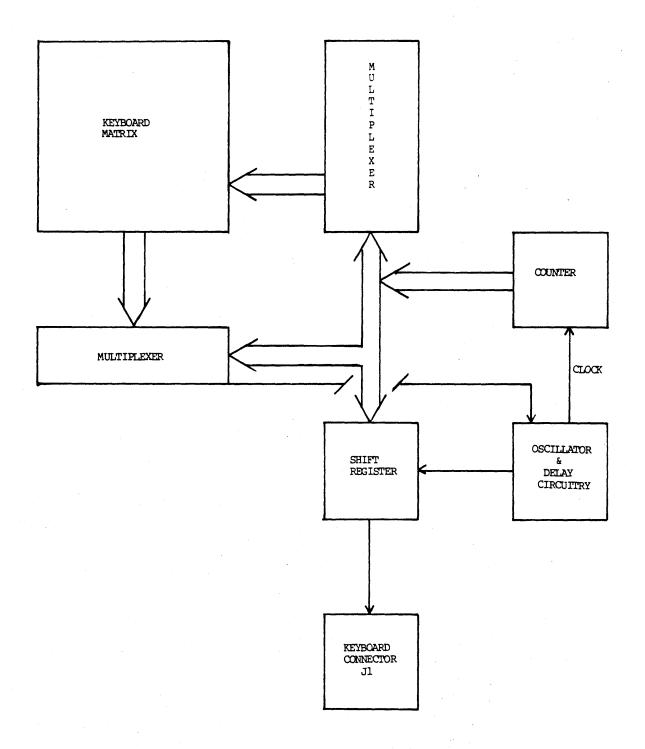

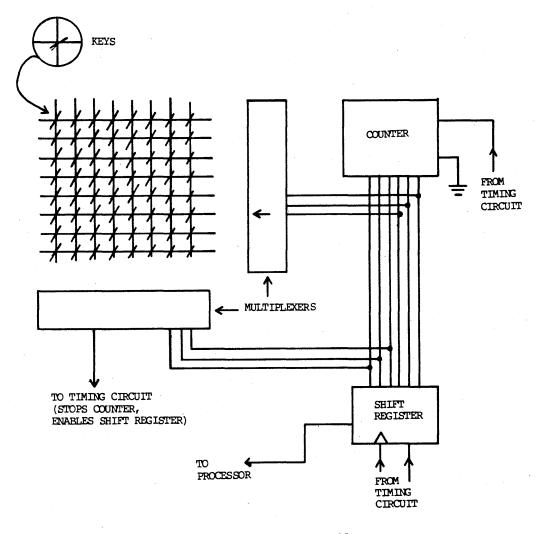

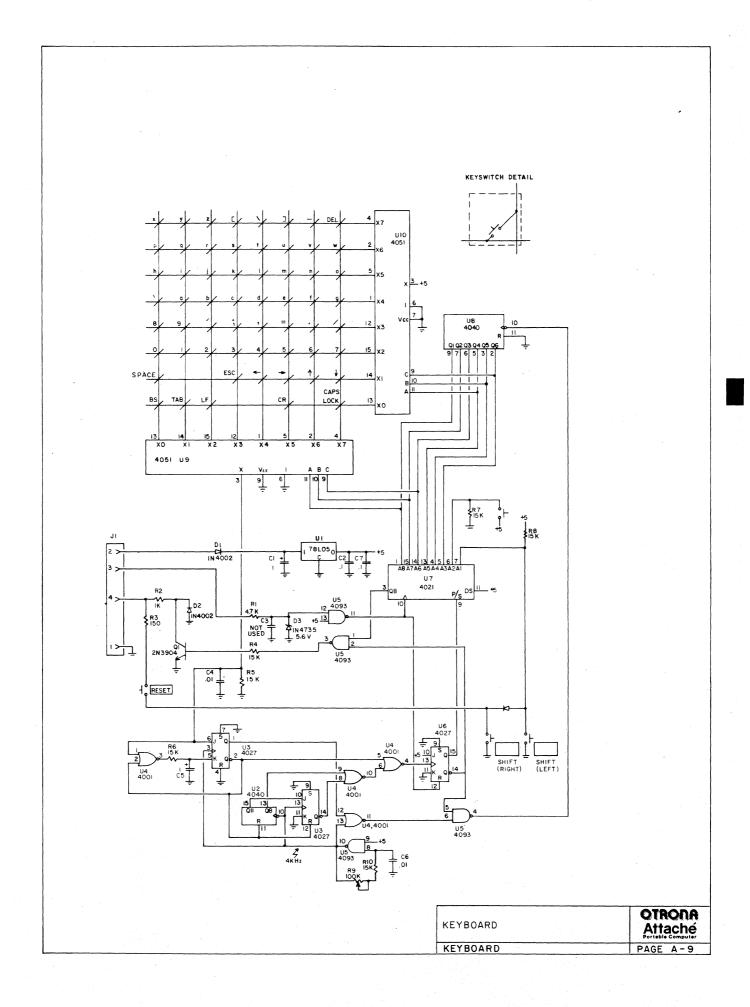

| Keyboard                             | . 2-67    |

| Introduction                         | . 2-68    |

| Basic Keyboard Logic                 | . 2-69    |

| Additional Circuitry Functions       | . 2-70    |

| Keyboard Layout                      | . 2-70    |

| ASCII Character Codes                | . 2-71    |

|                                      | 0.70      |

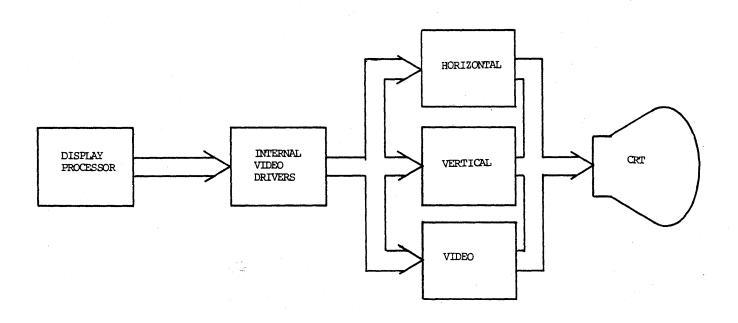

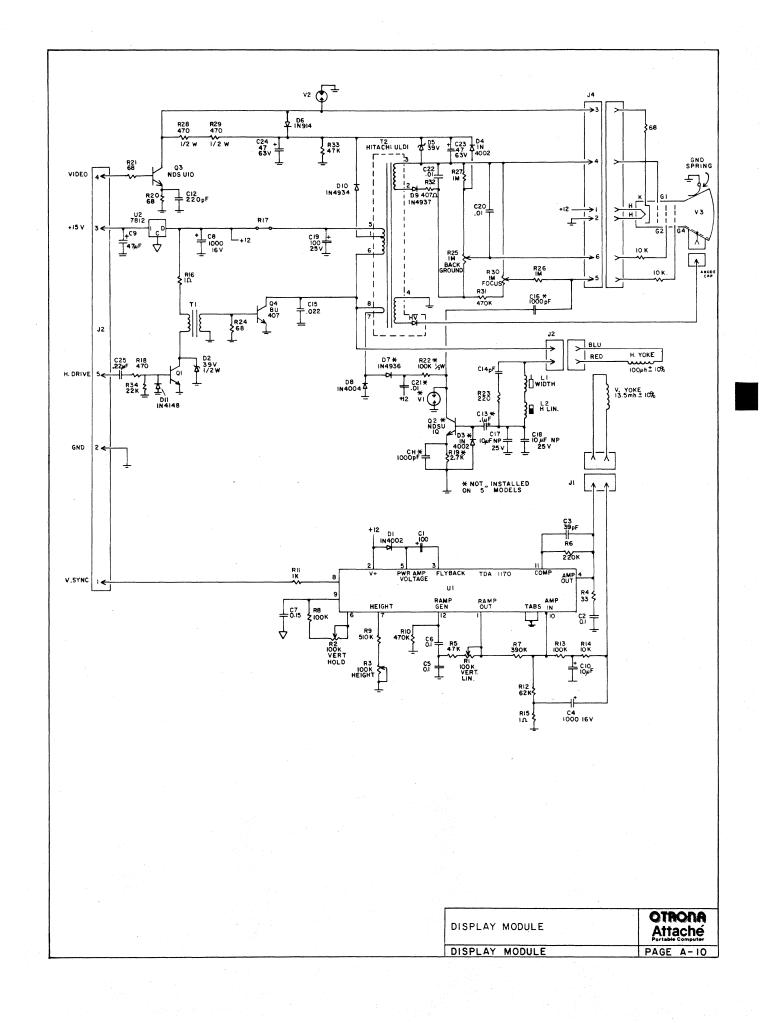

| Display Module                       |           |

|                                      |           |

| Vertical                             |           |

| Video                                | • - • •   |

| CRT                                  | . 2-75    |

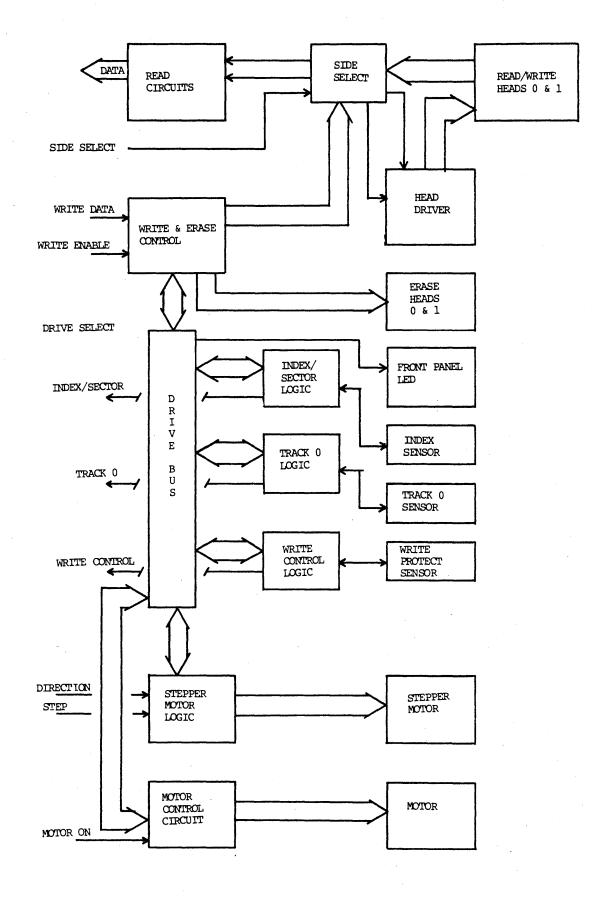

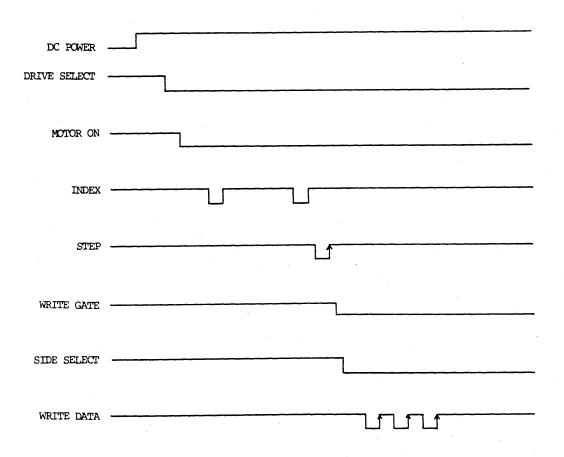

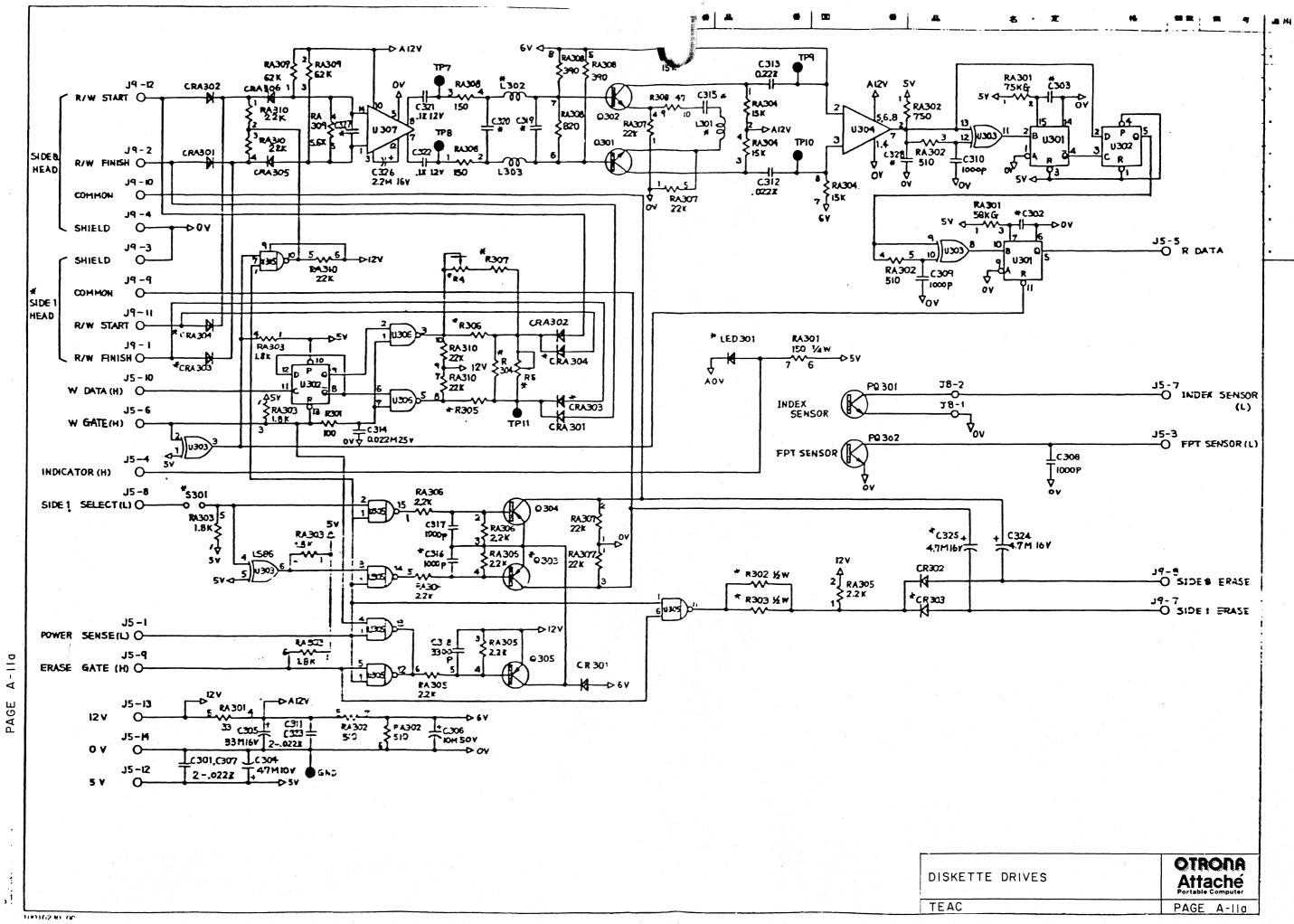

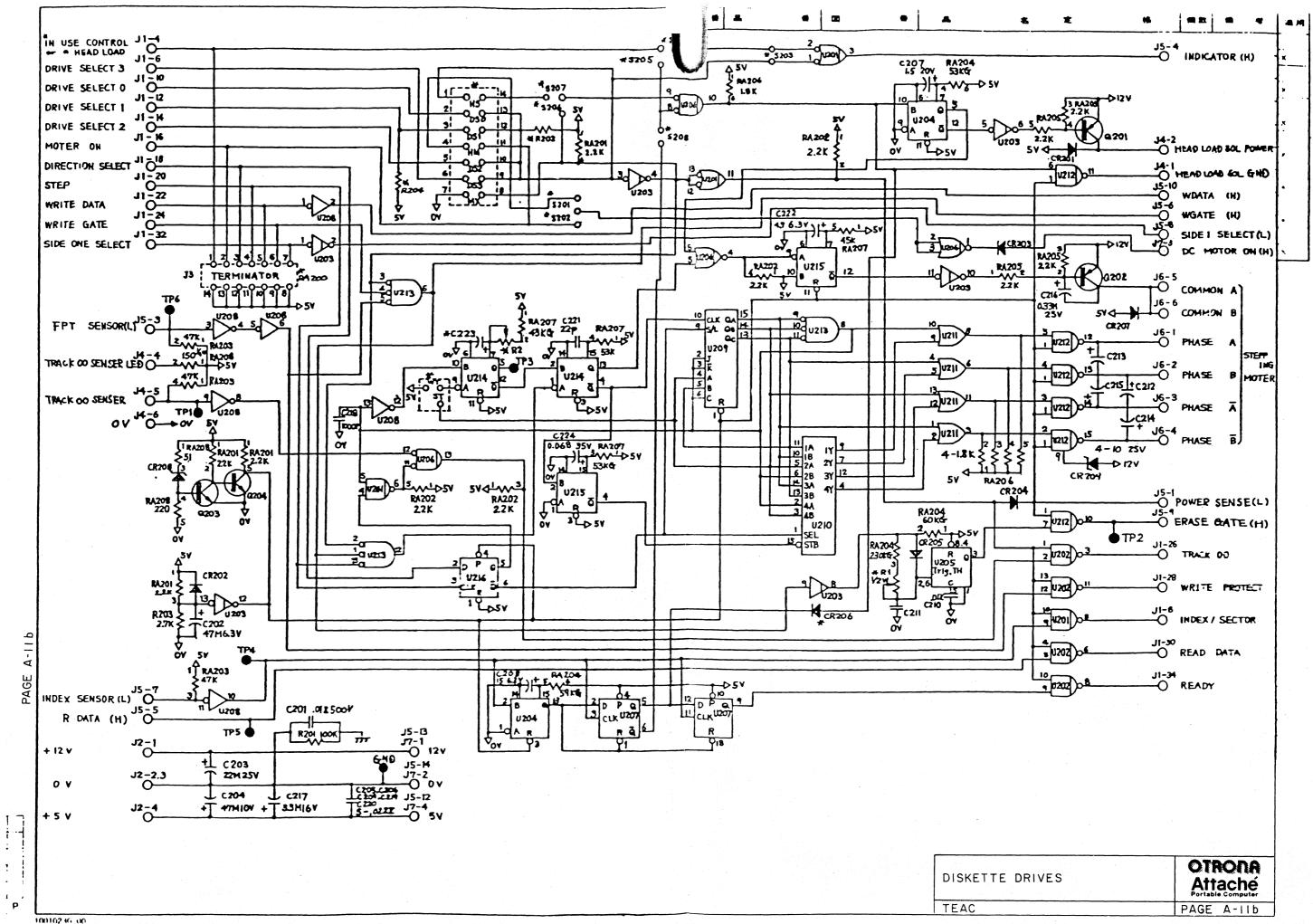

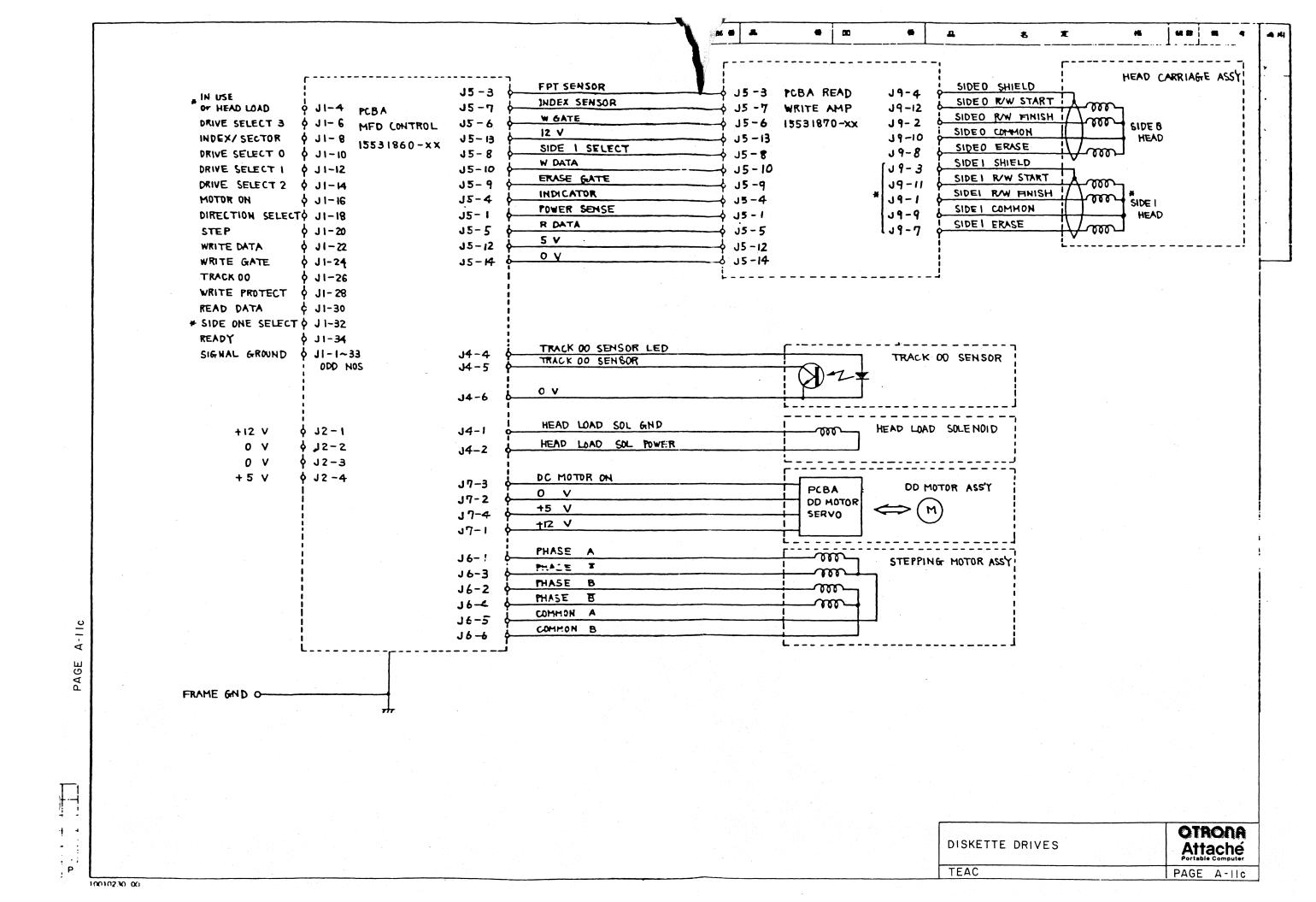

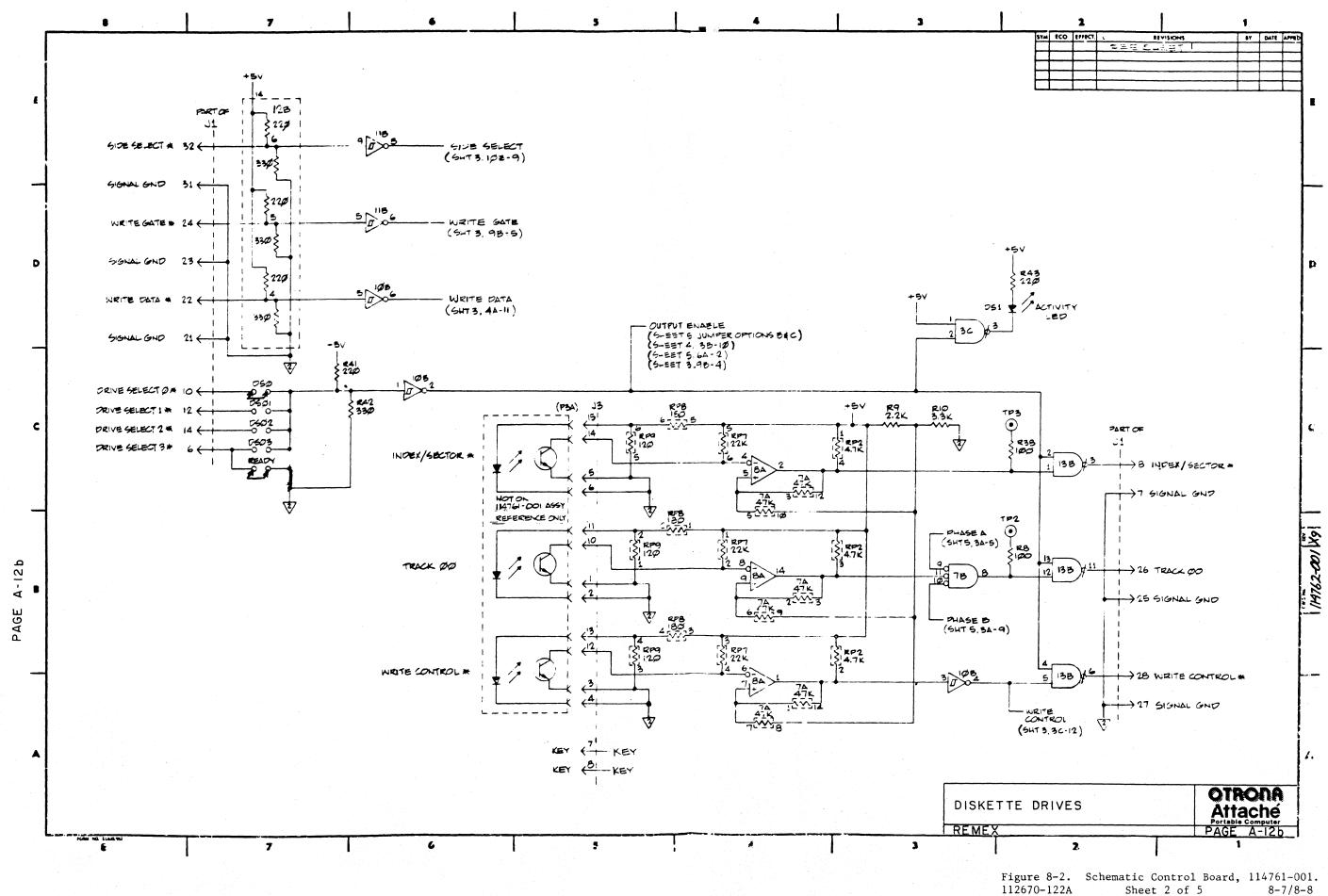

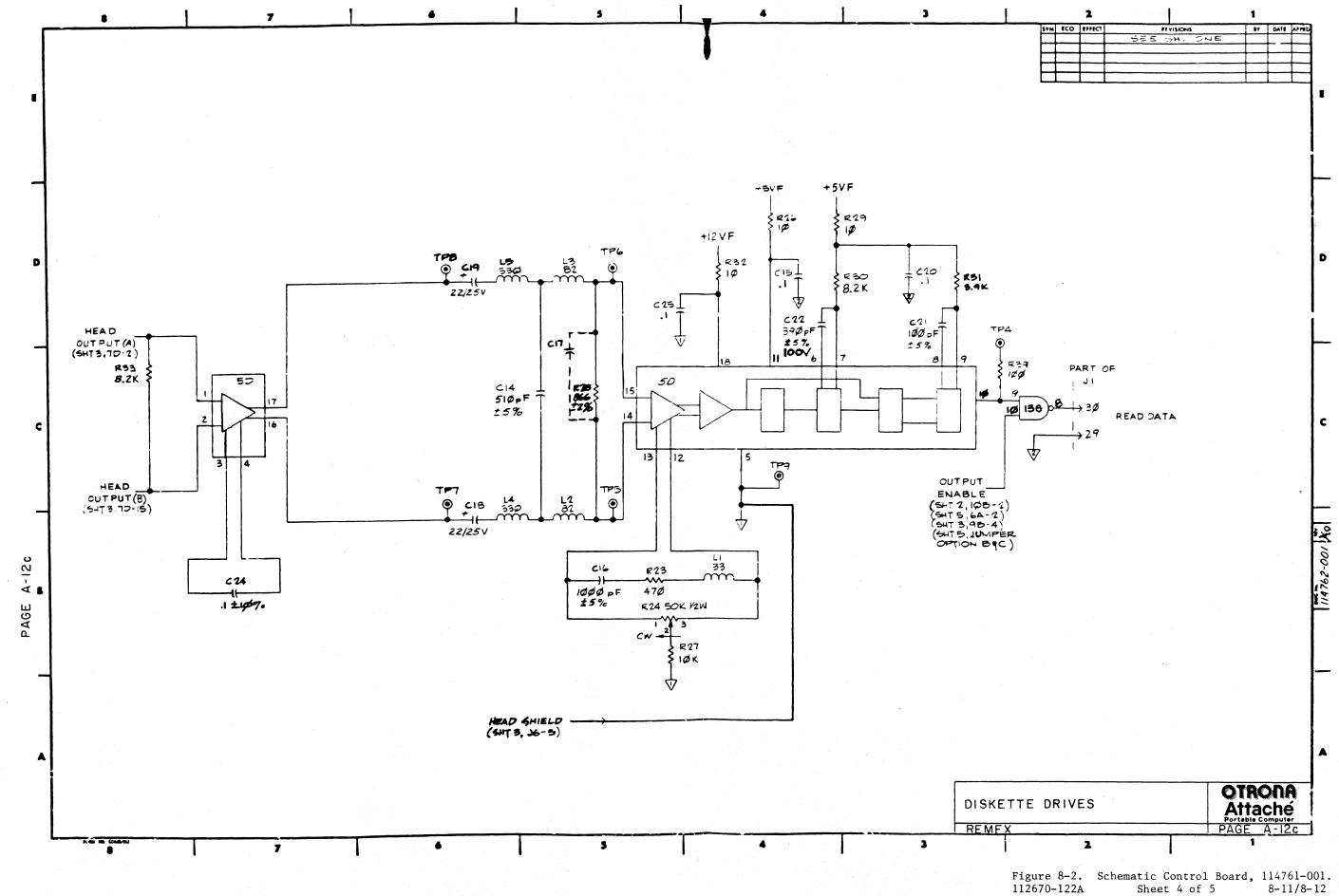

| Diskette Drive                       | . 2-76    |

| Head Movement                        |           |

| Sensors                              | • • •     |

| Writing                              | • - • • • |

| Reading                              |           |

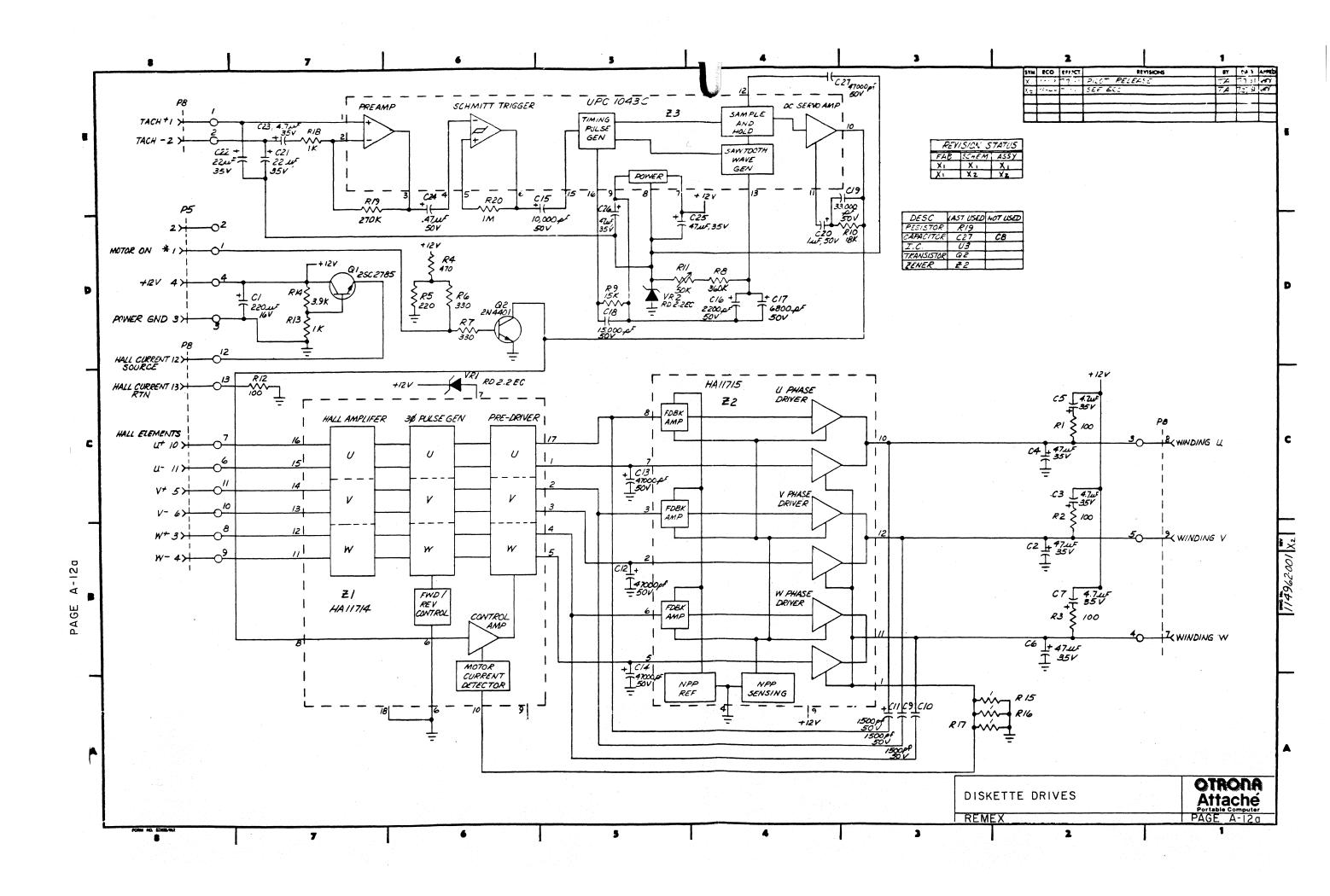

| Turning the Diskette                 | •         |

|                                      |           |

# III.Software

| Software Introduction | 3-1 |

|-----------------------|-----|

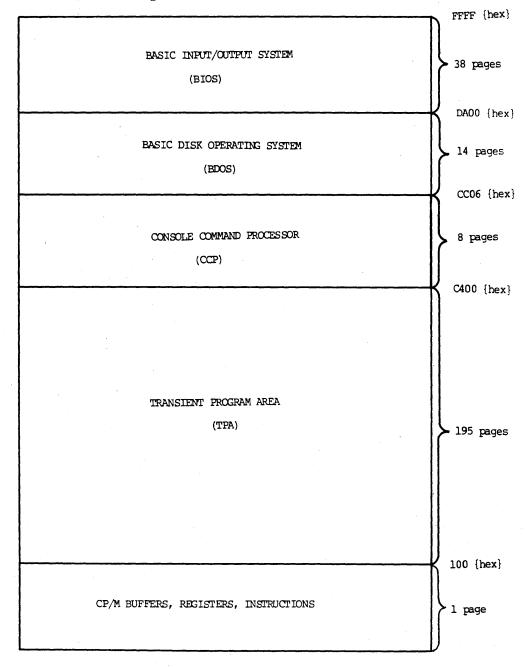

| CP/M Introduction     | 3-2 |

| CP/M Memory Locations | 3-3 |

| Low Memory Map        | 3-4 |

| IOBYTE                | 3~6 |

| Deftware.<br>Terminal Emulation<br>Monitor Mode - Diagnostics<br>Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction<br>Loader |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-8<br>3-10<br>3-11<br>3-11<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Terminal Emulation<br>Monitor Mode - Diagnostics<br>Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Dutput Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Vrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-8<br>3-10<br>3-11<br>3-11<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                |

| Terminal Emulation<br>Monitor Mode - Diagnostics<br>Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Dutput Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Vrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-8<br>3-10<br>3-11<br>3-11<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                |

| Monitor Mode - Diagnostics<br>Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Nrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-10<br>3-11<br>3-11<br>3-12<br>3-12<br>3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-14<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                               |

| Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Dnited Tests<br>Read a Sector From a Disk<br>Vrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-11 3-11 3-11 3-12 3-12 3-12 3-12 3-13 3-13 3-13 3-13 3-13 3-14 3-14 3-15 3-14 3-15 3-16 3-16 3-17 3-17 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Generate Display Pattern<br>Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Dnited Tests<br>Read a Sector From a Disk<br>Vrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-11 3-11 3-11 3-12 3-12 3-12 3-12 3-13 3-13 3-13 3-13 3-13 3-14 3-14 3-15 3-14 3-15 3-16 3-16 3-17 3-17 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Display RAM Test<br>Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-11 3-11 3-12 3-12 3-12 3-13 3-13 3-13 3-13 3-13 3-14 3-14 3-14 3-15 3-16 3-16 3-16 3-17 3-17 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Input Test<br>Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Nrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-11 3-12 3-12 3-12 3-13 3-13 3-13 3-13 3-14 3-14 3-14 3-15 3-15 3-16 3-16 3-17 3-17 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Jump<br>Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-12<br>3-12<br>3-13<br>3-13<br>3-13<br>3-13<br>3-14<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Keyboard Test<br>Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-12<br>3-12<br>3-13<br>3-13<br>3-14<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Loop Tests<br>Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>United Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-12<br>3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Map Test<br>Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13<br>3-13<br>3-14<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>United Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Dutput Test<br>Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>United Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13<br>3-13<br>3-14<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Format Diskette Test<br>CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>United Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>Vrite a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-13<br>3-14<br>3-15<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CMOS RAM Test<br>Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-14<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Main RAM Test<br>Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-14<br>3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Select Output Ports<br>Real-Time Clock Test<br>Jnited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-15<br>3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Real-Time Clock Test<br>Inited Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-15<br>3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| United Tests<br>Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-16<br>3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                                                                     | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Read a Sector From a Disk<br>Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                                                                     | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-16<br>3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Write a Sector to a Disk<br>I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                                                                                                  | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-17<br>3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O Port Transmit<br>I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                              | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-17<br>3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| I/O Port Receive<br>Automatic Disk Test<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   | • • • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Automatic Disk Test                                                                                                                                                                                                                                                                                                                                                                                                                                                       | •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| loader                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| LOADOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Cboot                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Blocking/Deblocking                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Physical Read/Write                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Autout Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Programming the SIO Baud Rate                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| I/O Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | • • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| av Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Accessing the Display Driver                                                                                                                                                                                                                                                                                                                                                                                                                                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |