# 8025 CRT TERMINAL

# MAINTENANCE MANUAL

OMRON CORPORATION OF AMERICA INFORMATION PRODUCTS DIVISION 432 TOYAMA DRIVE, SUNNYVALE, CA. 94086 (408) 734-8400 TWX 910-339-9341 OMRON

No information contained herein may be reproduced or disseminated to any person or company without the express written permission of Omron Corporation of America, Information Products Division.

October 1, 1975

OMRON P/N 88-036-XXX

### FOREWORD

This manual gives accurate, usable information to help you get the best service from your 8025 CRT Terminal.

It supplies you with the details needed to:

- become thoroughly familiar with the 8025

- operate the 8025

- understand how the 8025 operates

- service the 8025

We have taken care to make this manual as complete, accurate, and understandable as possible. Your comments and suggestions for increasing its quality and effectiveness will be most welcome. A convenient, pre-addressed "Publication Change Request" form for this purpose is provided on the next page.

To receive updated materials, your manual must be registered with Omron. A pre-addressed form is also supplied for this purpose.

(iii)

TABLE OF CONTENTS

| SEC | TION |                                           |                                  | PAGE                                 |

|-----|------|-------------------------------------------|----------------------------------|--------------------------------------|

|     | List | of Fig                                    | ures                             | xiv                                  |

|     | List | of Tab                                    | les                              | xvi                                  |

| 1   | Gene | ral Inf                                   | ormation                         | 1-1                                  |

|     | 1.1  | Genera                                    | 1 Description                    | 1-1                                  |

| ~   |      | 1.1.1<br>1.1.2<br>1.1.3                   | Functional Description           | 1-1<br>1-2<br>1-3                    |

|     | 1.2  | Specif                                    | ications                         | 1-4                                  |

| ,   |      | 1.2.1                                     | Standard Terminal Specifications | 1-4                                  |

|     | 1.3  | Warran                                    | ty Information                   | 1-8                                  |

|     | ÷    | 1.3.1<br>1.3.2<br>1.3.3<br>1.3.4<br>1.3.5 | Claim for Transit Damage         | 1-8<br>1-8<br>1-9<br>1-9             |

|     | 1.4  | Repair                                    | and Return of Equipment          | 1-10                                 |

|     |      | 1.4.1<br>1.4.2<br>1.4.3<br>1.4.4<br>1.4.5 | Policy                           | 1-10<br>1-10<br>1-10<br>1-10<br>1-10 |

|     | 1.5  | List o                                    | f OMRON Mnemonics                | 1-12                                 |

| 2   | Inct |                                           | n and Checkout                   | 2-1                                  |

| 2   | 2.1  |                                           | ing Procedure                    | 2-1                                  |

|     | 201  | -                                         | Inspection                       | 2-1                                  |

|     | 2.2  | Off-lin                                   | ne Checkout                      | 2-2                                  |

|     | ·    | 2.2.1<br>2.2.2                            | Mechanical Inspection            | 2-2<br>2-7                           |

|     | 2.3  | Instal                                    | lation                           | 2-7                                  |

|     |      | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4          | Physical Requirements            | 2-7<br>2-7<br>2-8<br>2-8             |

|     | 2.4  | On-lin                                    | e Checkout                       | 2-8                                  |

SECTION

-

# TABLE OF CONTENTS (continued)

.

Р

| 3 | Oper. | ating Ir                         | nstructions                          |    |

|---|-------|----------------------------------|--------------------------------------|----|

|   | 3.1   | Operati                          | ing Controls                         |    |

|   |       | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4 | 8                                    |    |

|   | 3.2   |                                  |                                      |    |

|   |       |                                  | splay Screen                         |    |

|   | 3.3   |                                  | Indicators                           |    |

|   |       |                                  | The Click Sound                      |    |

|   | 3.4   | Visual                           | Indicators                           | ۰. |

|   | 3.5   | Basic (                          | Operating Modes                      |    |

|   |       | 3.5.1                            | KSR Mode                             |    |

|   | 3.6   |                                  | rd Keys                              |    |

|   |       | 3.6.1                            | Operating Features                   | 1  |

|   |       | 3.6.2<br>3.6.3                   | "Typewriter" Keys                    | 4  |

|   |       | 3.6.4                            | Escape (ESC) and Control (CTRL) Keys | 4  |

|   | •     |                                  | Cursor Control Keys                  |    |

|   |       |                                  | Next Line () Key                     |    |

|   | 3.7   |                                  | lual Key Descriptions                |    |

|   |       |                                  | Alphanumeric-Punctuation-Symbol Keys | 5  |

|   |       |                                  | Store Input Key/Indicator            |    |

|   |       |                                  | Storage Transmit Key/Indicator       |    |

|   |       |                                  | KSR Mode Key/Indicator               |    |

|   |       |                                  | Print Key                            |    |

|   |       |                                  | Store Key                            |    |

|   |       |                                  | Read Key                             |    |

|   |       |                                  | Keyboard Disabled Indicator          |    |

|   |       |                                  | Received Parity Error Indicator      |    |

|   |       |                                  | Frame Transmit Key                   |    |

|   |       |                                  | Local Copy Key/Indicator             |    |

|   |       |                                  | Break Key                            |    |

|   |       |                                  | Reset Key                            |    |

|   |       |                                  | Screen Erase Key                     |    |

|   |       |                                  | Control (CTRL) Key                   |    |

|   |       |                                  | Shift Key                            |    |

|   |       |                                  | Lock Key                             |    |

|   |       |                                  | Space Bar                            | ð  |

|   |       |                                  |                                      |    |

|   |       | 3.7.20                           | Line Feed Key                        | ð  |

# TABLE OF CONTENTS (continued)

PAGE

|   |      | 3.7.22<br>3.7.23                 | Carriage Return (CR) Key                                                                  |

|---|------|----------------------------------|-------------------------------------------------------------------------------------------|

|   | 3.8  | Operat:                          | ing Procedures                                                                            |

|   |      | 3.8.1<br>3.8.2                   | Turning the Terminal On and Off                                                           |

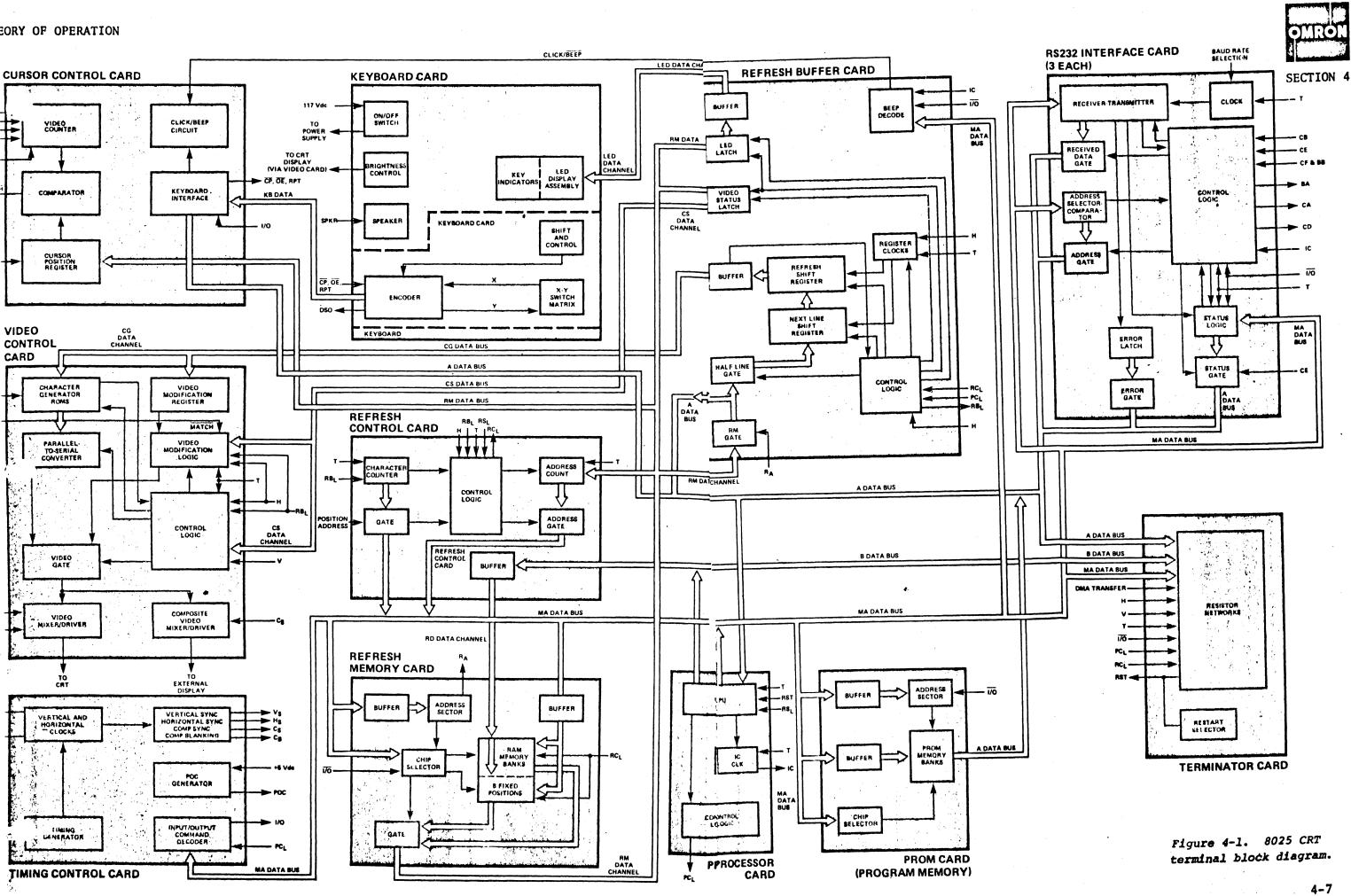

| 4 | Theo | ry of Oj                         | peration                                                                                  |

|   | 4.1  | Termina                          | al Block Diagram Analysis                                                                 |

|   |      | 4.1.1                            | Timing, Control, and Data Signals                                                         |

|   | 4.2  | 8025 CI                          | RT Terminal Input/Output Structure                                                        |

|   |      |                                  | Memory Cards4-6Program-Processor Controlled I/O Cards4-16DMA Transfer I/O Cards4-16       |

|   | 4.3  | Charact                          | ter Generation                                                                            |

|   |      | 4.3.1<br>4.3.2                   | Upper Case Characters                                                                     |

|   | 4.4  | Card/Se                          | ection Descriptions                                                                       |

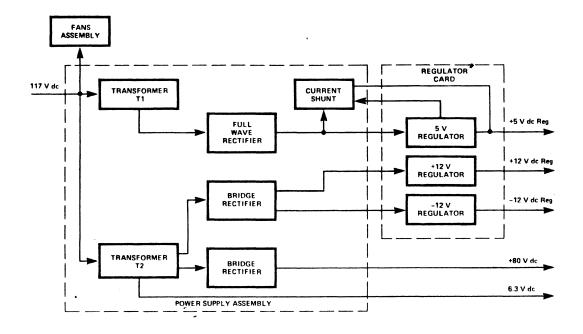

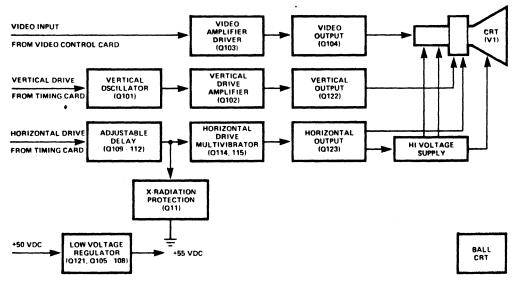

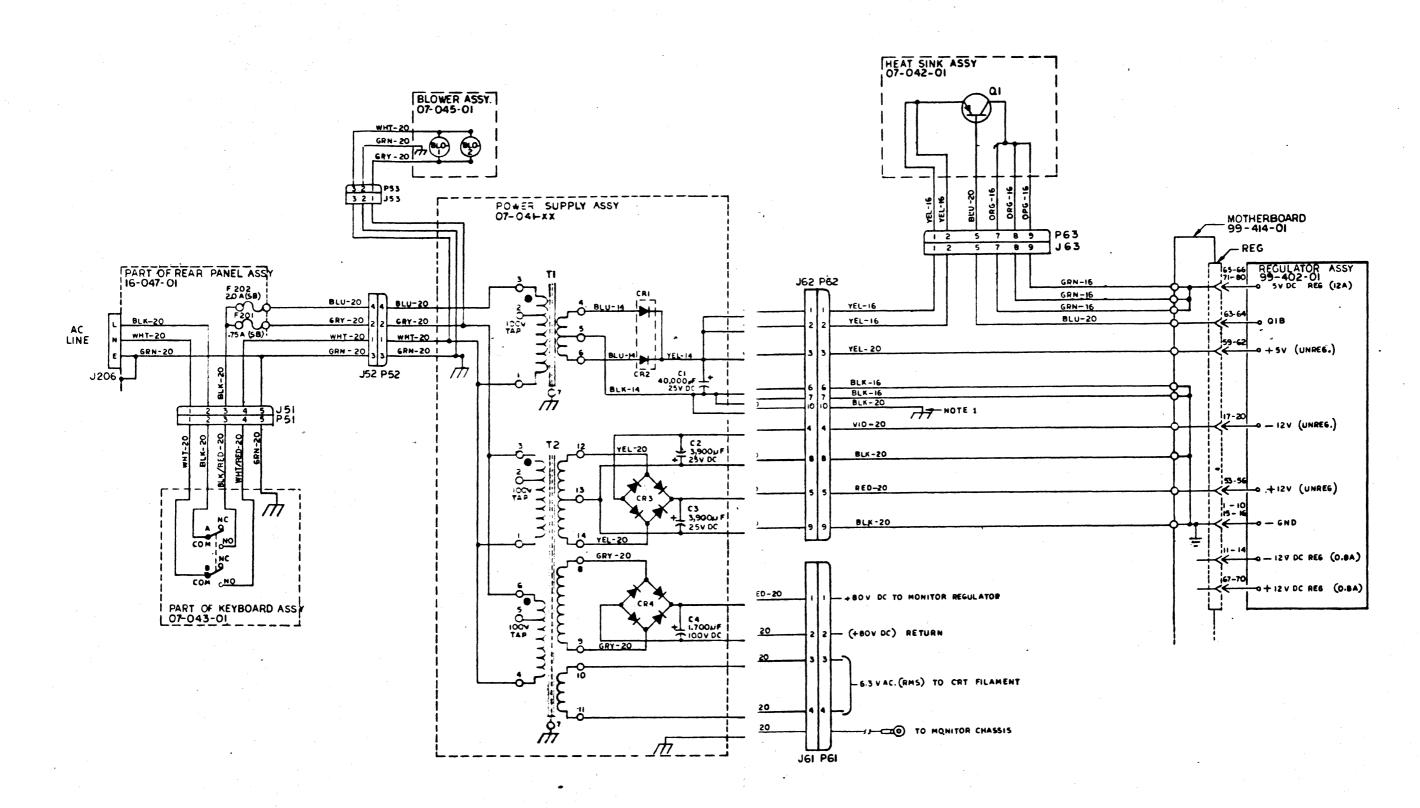

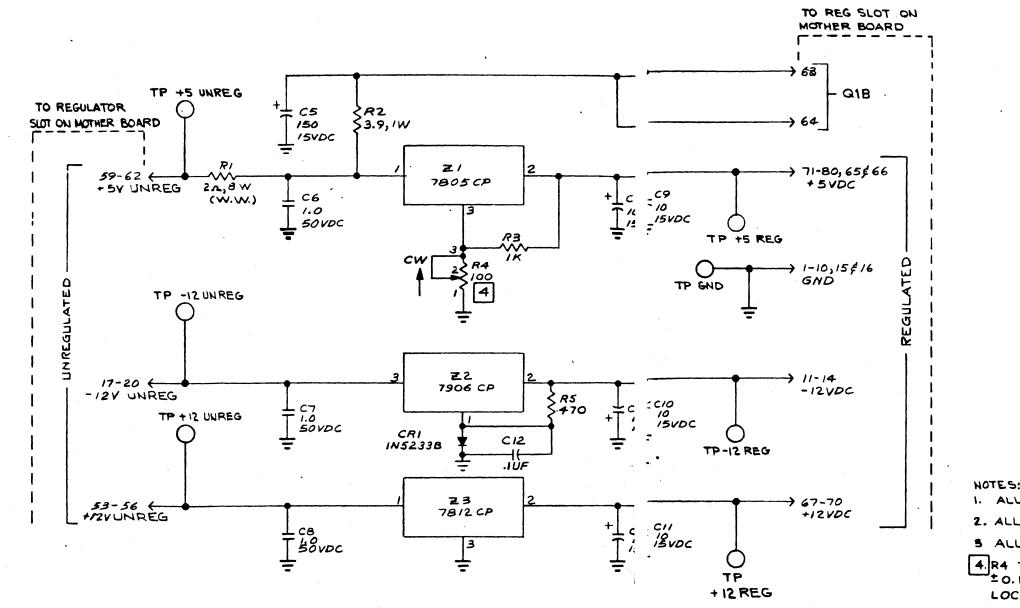

|   |      | 4.4.10<br>4.4.11<br>4.4.12       | Power Supply                                                                              |

| 5 | (Not | Applica                          | able to 8025G Terminal)                                                                   |

| 6 | Main | tenance                          | and Repair                                                                                |

|   | 6.1  | Prevent                          | tive Maintenance                                                                          |

|   |      | 6.1.1<br>6.1.2<br>6.1.3<br>6.1.4 | Objective6-1Required Equipment and Materials6-1General Procedure6-1Specific Procedures6-2 |

TA

SECTION

| ABLE | OF   | CONTENTS |

|------|------|----------|

| (co  | onti | inued)   |

PAGE

|   | 6.2  | Field Maintenance                             | 5              |

|---|------|-----------------------------------------------|----------------|

|   |      | 6.2.1 Objective                               | 3              |

|   |      | 6.2.2 Required Equipment                      | 3              |

|   |      | 6.2.3 Rules of Good Maintenance               | 1              |

|   |      | 6.2.4 Field Troubleshooting Procedure         | ŧ              |

|   |      | 6.2.5 Removal and Replacement Procedures 6-2  | 13             |

|   | 6.3  | Bench Maintenance                             | 19             |

|   |      | 6.3.1 Objective                               | 19             |

|   |      | 6.3.2 Required Equipment and Materials 6-3    | 19             |

|   |      | 6.3.3 Rules of Good Maintenance               | 20             |

|   |      | 6.3.4 Replaceable Parts                       | 20             |

|   |      | 6.3.5 Workmanship                             |                |

|   |      | 6.3.6 General Troubleshooting Procedure       |                |

|   |      | 6.3.7 Specific Troubleshooting Procedures 6-2 |                |

|   |      | 6.3.8 Removal and Replacement Procedures      | 52             |

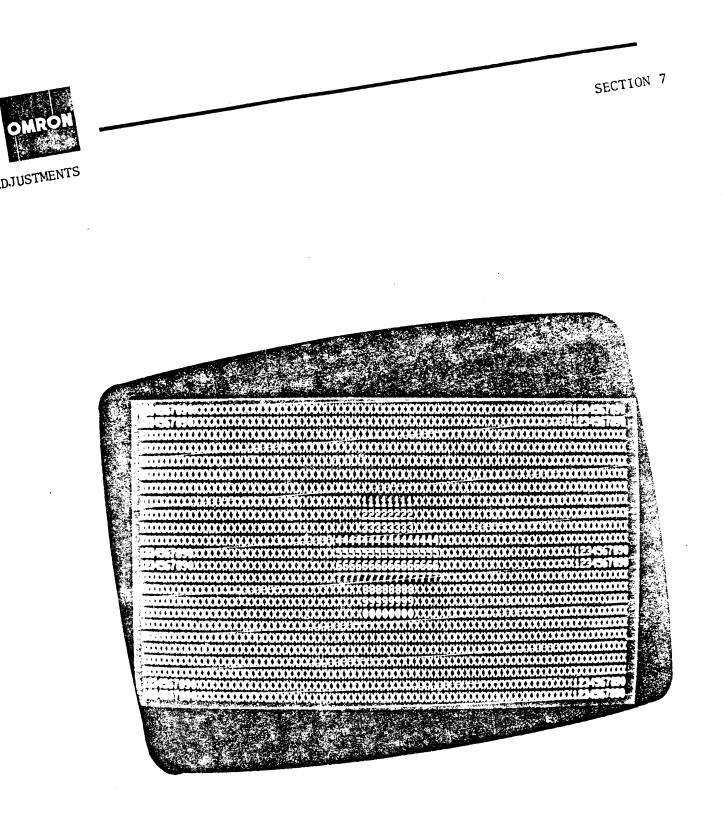

| 7 | Adju | stments                                       | and the second |

|   | 7.1  | Required Equipment                            | a state        |

|   | 7.2  | +5 V dc Regulated Output                      | 840.           |

|   | 7.3  | Click/Beep Volume                             | L              |

|   | 7.4  | CRT Display Adjustments                       | 2              |

|   |      | 7.4.1 Preliminary Procedure                   | ,              |

|   |      | 7.4.2 +55 V dc (B+) Adjust                    | -              |

|   |      | 7.4.3 Video Gain                              |                |

|   |      | 7.4.4 Vertical Adjustments                    |                |

|   |      | 7.4.5 Horizontal Adjustments                  |                |

|   |      | 7.4.6 Centering Adjustments                   |                |

|   |      | 7.4.7 Yoke Adjustments                        |                |

|   |      | 7.4.8 Focus                                   |                |

|   |      |                                               | 2              |

| 8 | Draw |                                               |                |

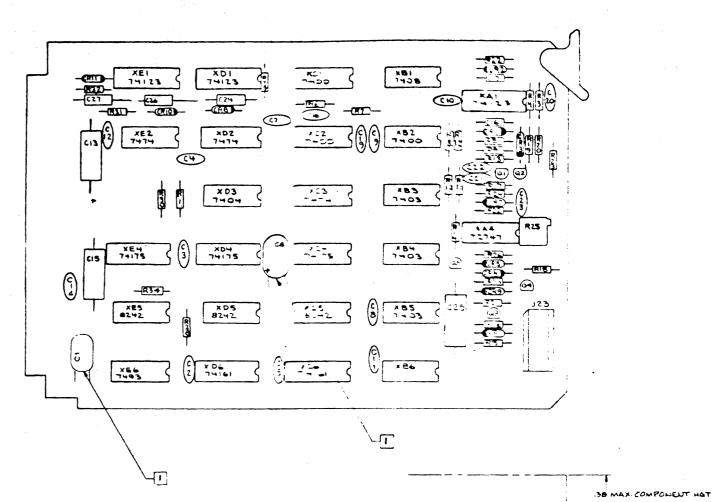

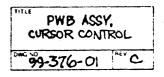

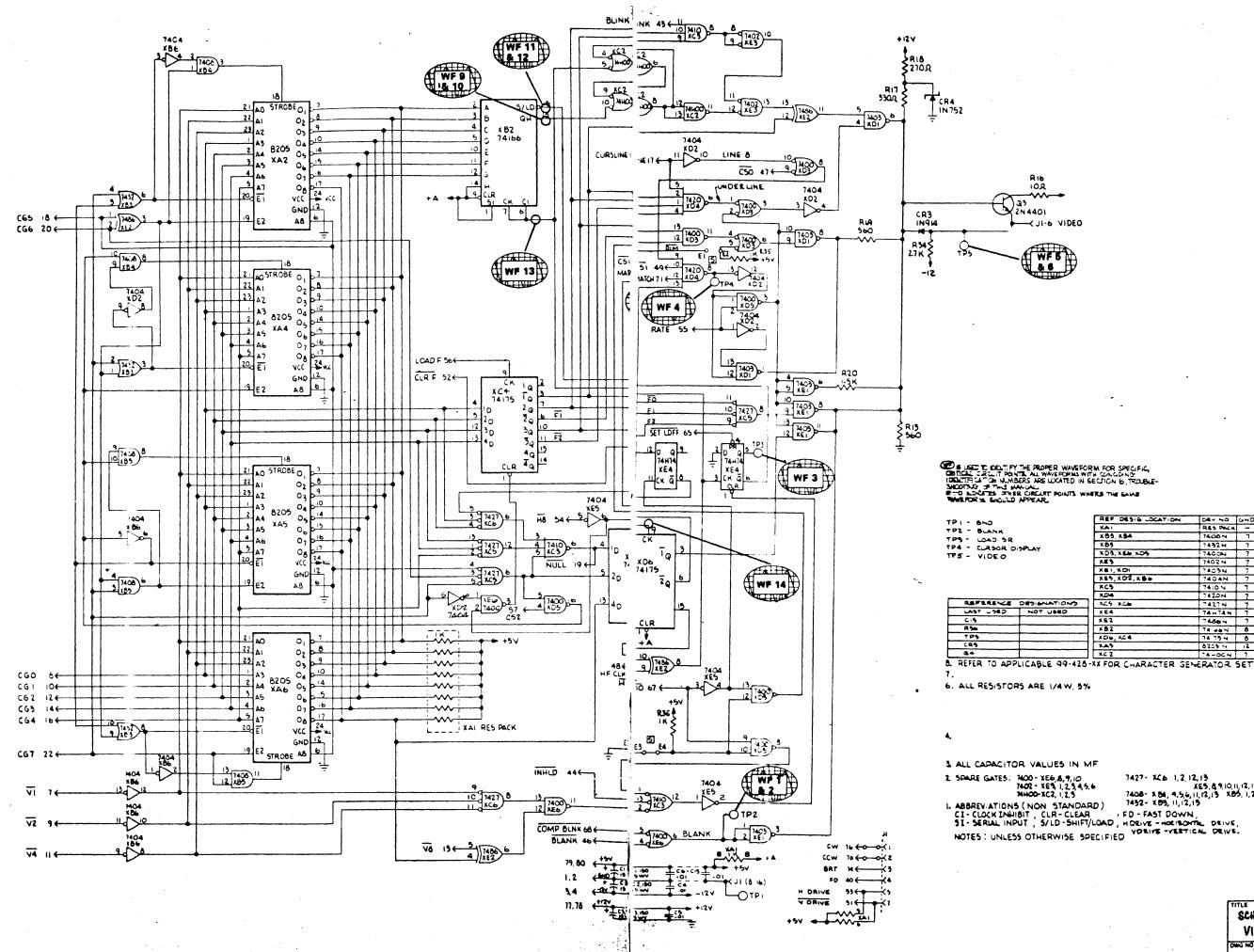

|   |      | Cursor Control Card                           |                |

|   |      | Display Monitor                               | 5              |

|   |      | Keyboard                                      | ,              |

|   |      | L.E.D                                         | /              |

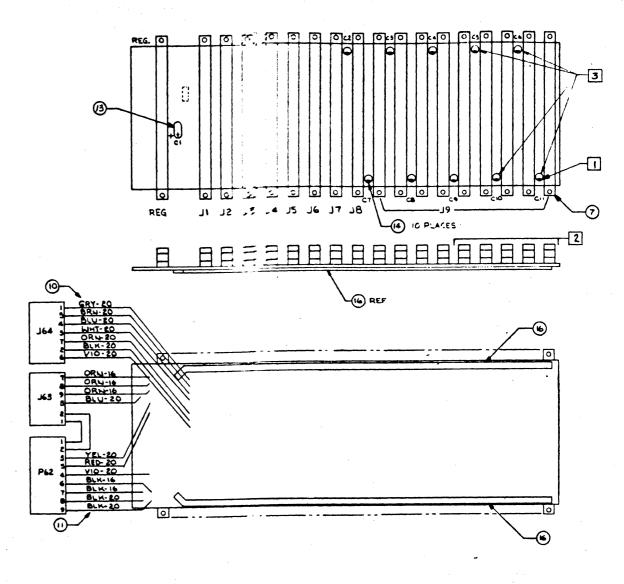

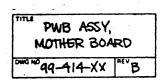

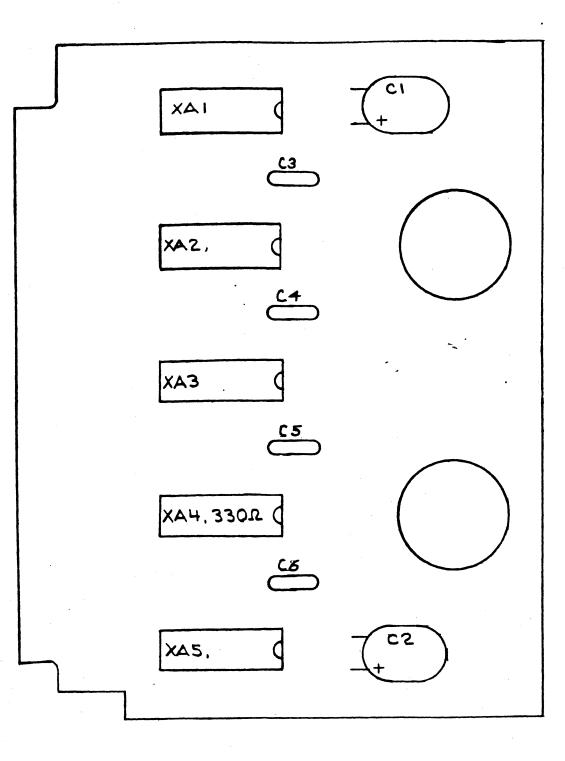

|   |      | Mother Board                                  | ,              |

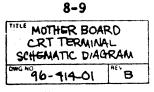

|   |      | Power Supply                                  | 1              |

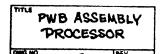

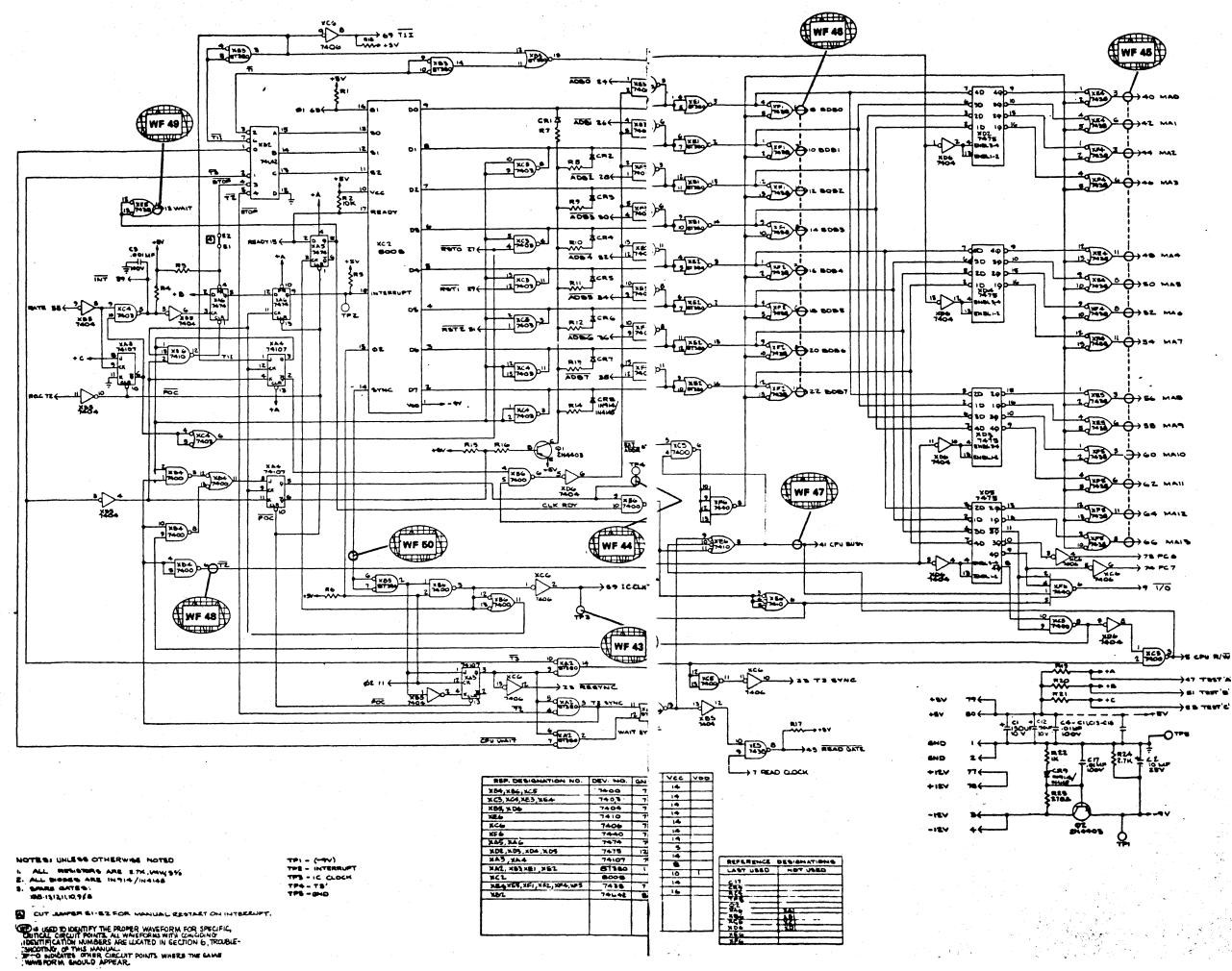

|   |      | Processor Card                                | 5              |

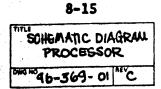

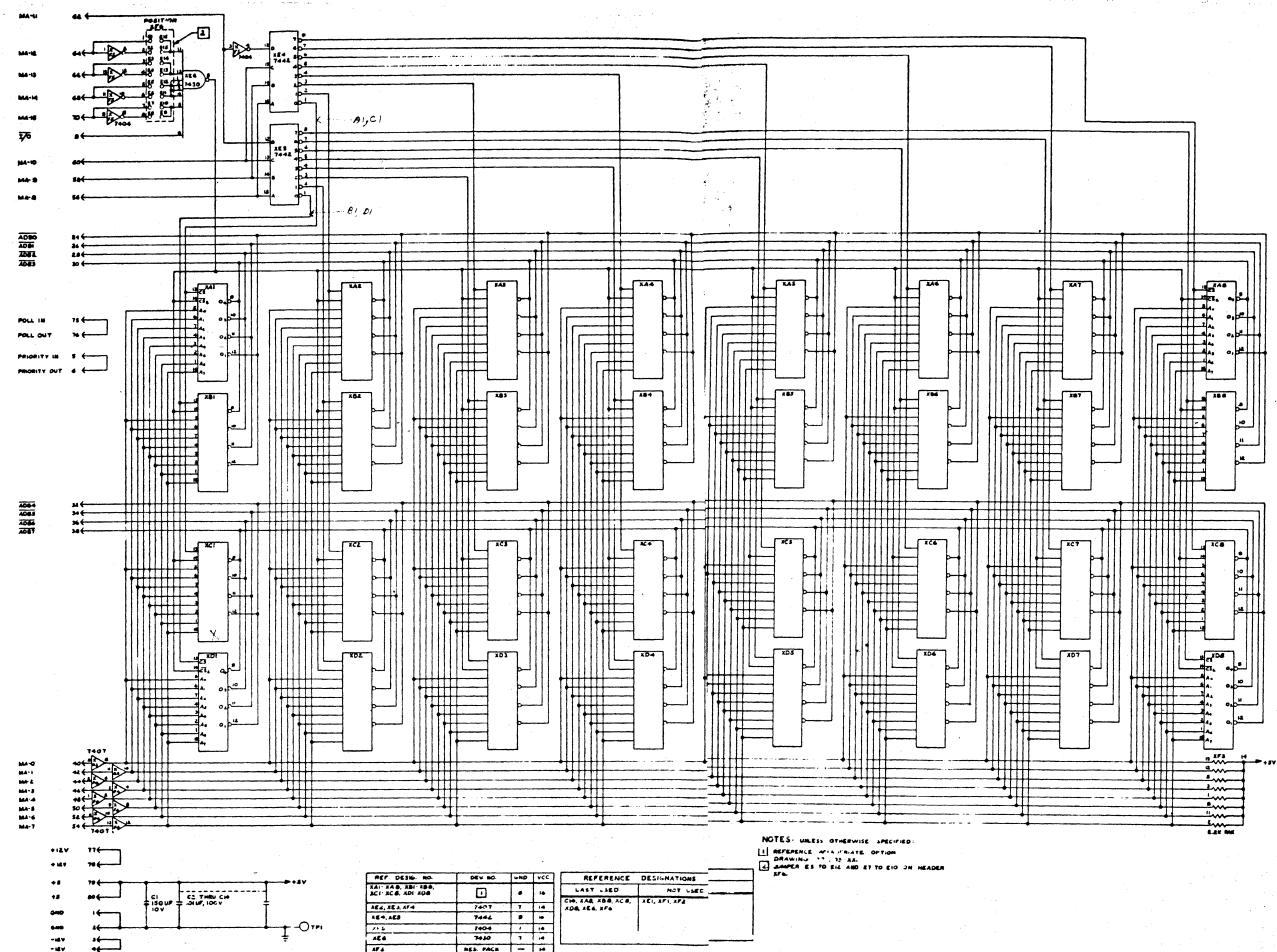

|   |      | PROM Card                                     |                |

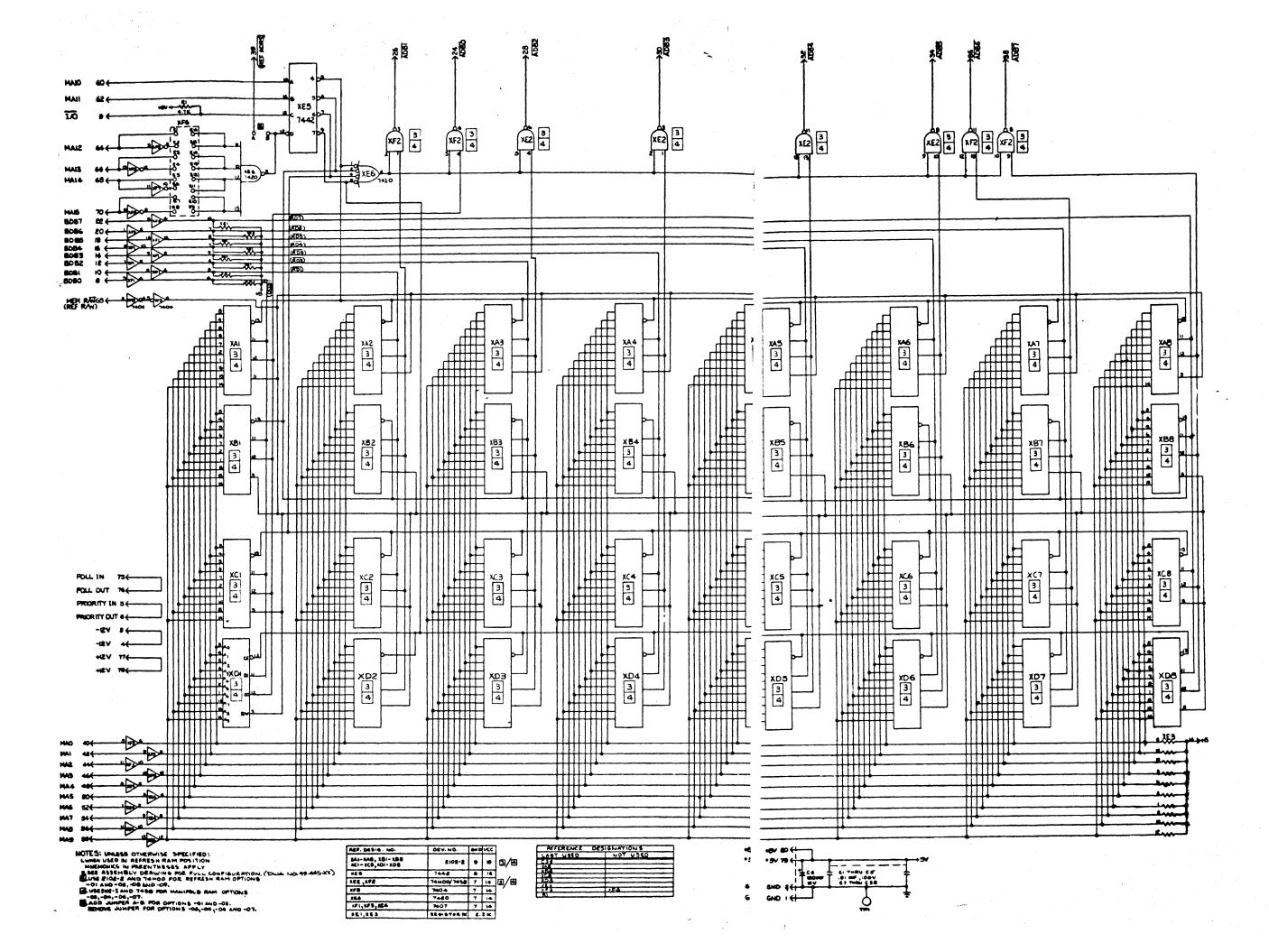

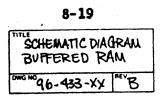

|   |      | RAM Card                                      | 5              |

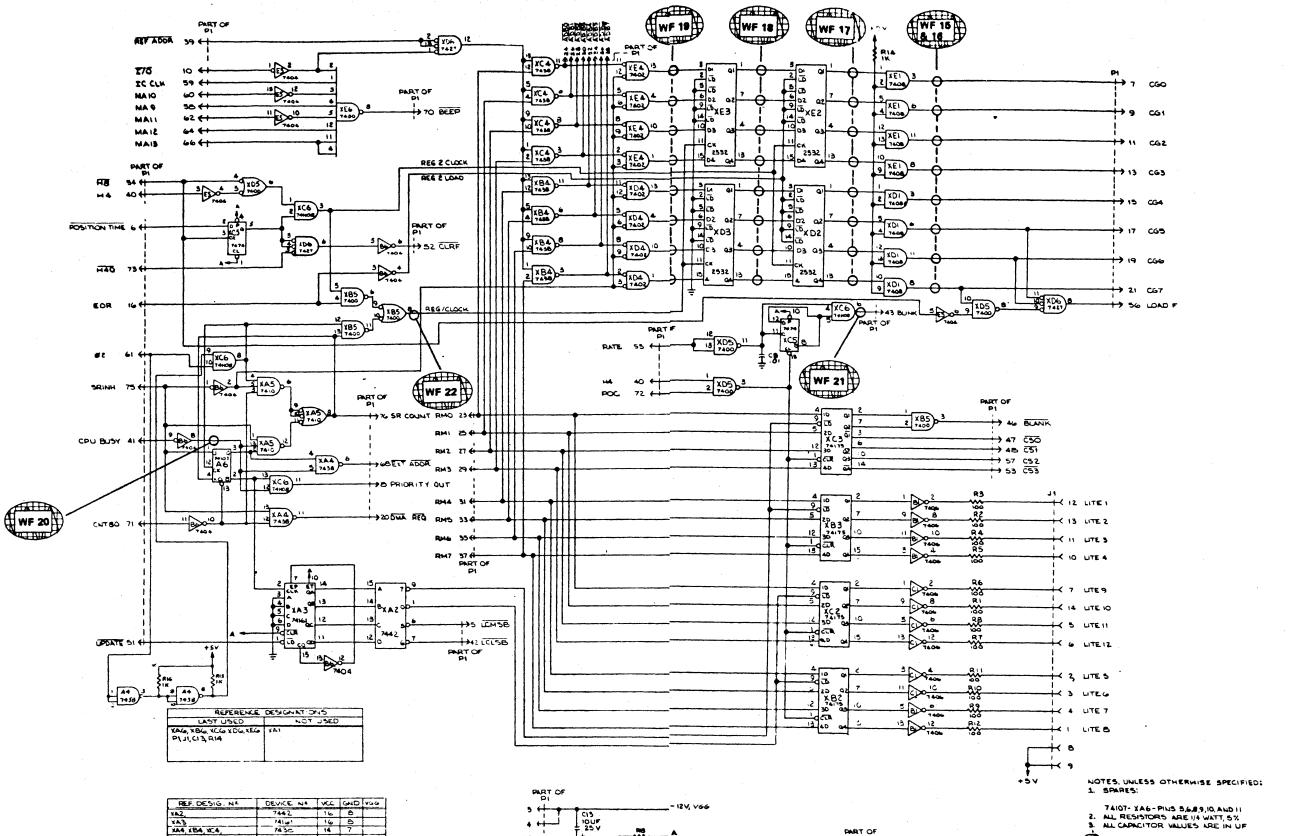

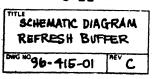

|   |      | Refresh Buffer Card                           | 1              |

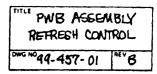

|   |      | Refresh Control Card                          | 5              |

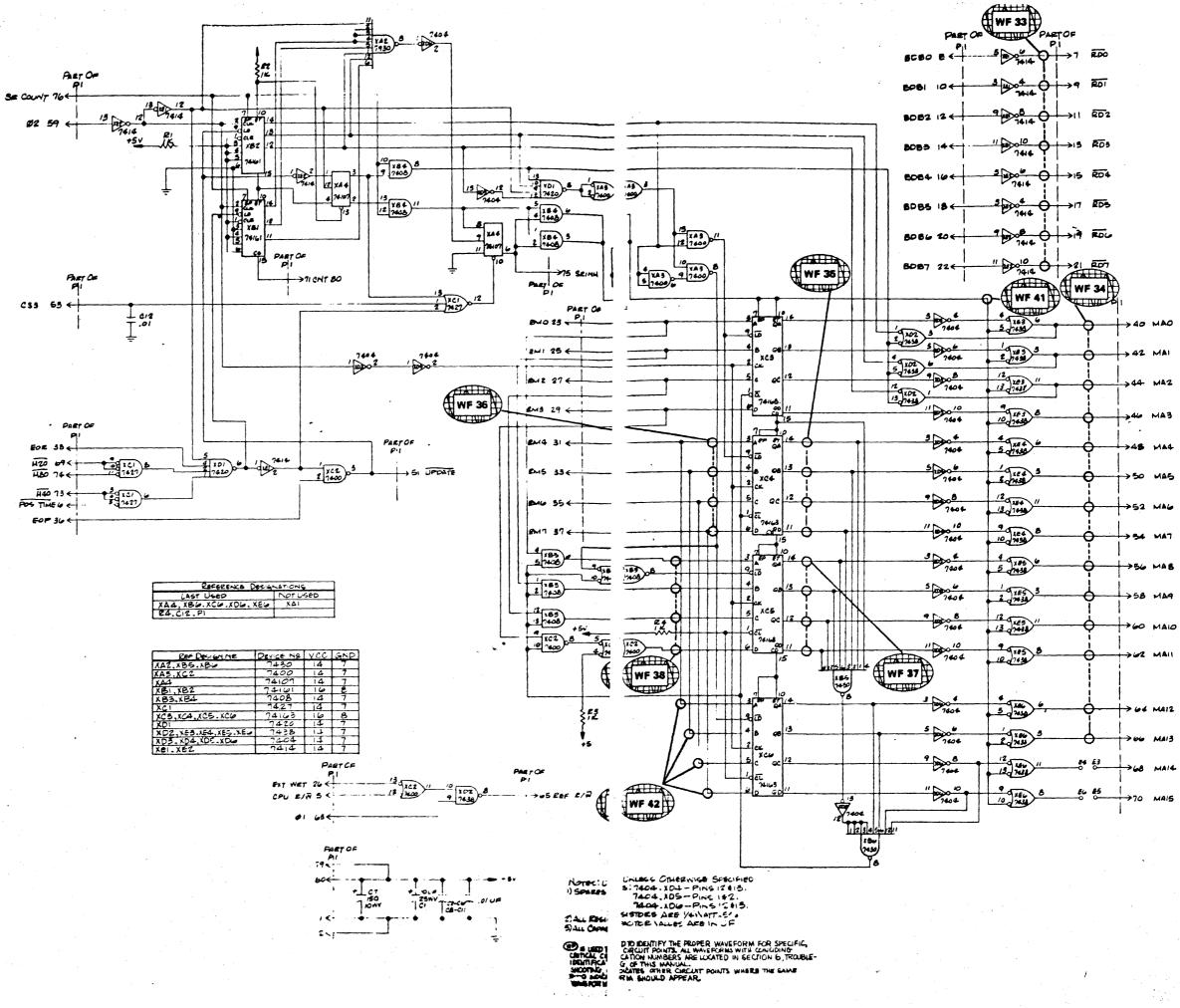

|   |      | Regulator Card                                | 5              |

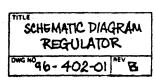

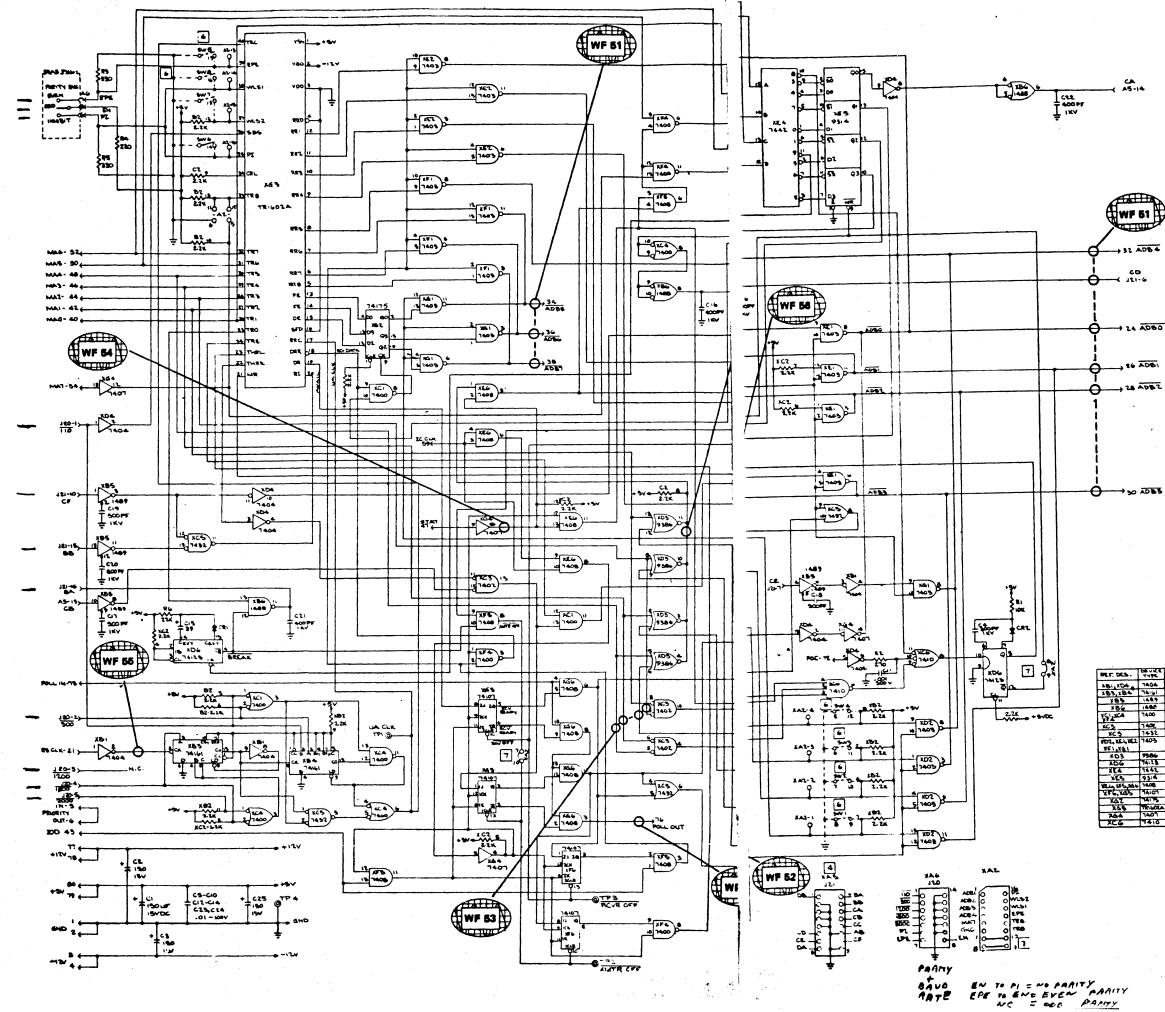

|   |      | RS-232 Interface Card                         | 7              |

# TABLE OF CONTENTS (continued)

PAGE

.

.

| SECTION |

|---------|

|---------|

١

|    |                                                                                                                                                   | -29  |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | William Company Compl                                                                                                                             | - 31 |

|    |                                                                                                                                                   | - 33 |

| 9  | Component Parts List                                                                                                                              | -1   |

|    | Cursor Control Card                                                                                                                               | - 1  |

|    |                                                                                                                                                   | - 3  |

|    |                                                                                                                                                   | -4   |

|    | Mother Board                                                                                                                                      | -4   |

|    | Power Supply                                                                                                                                      | -5   |

|    |                                                                                                                                                   | -6   |

|    |                                                                                                                                                   | - 7  |

|    | RAM Card                                                                                                                                          | -9   |

|    |                                                                                                                                                   | -11  |

|    |                                                                                                                                                   | -12  |

|    |                                                                                                                                                   | -13  |

|    |                                                                                                                                                   | -14  |

|    |                                                                                                                                                   | -15  |

|    |                                                                                                                                                   | -16  |

|    |                                                                                                                                                   | -18  |

| 10 | Poferences                                                                                                                                        | -    |

| 10 | References                                                                                                                                        |      |

|    | 10.1 EIA Standard RS-232C                                                                                                                         |      |

|    | 10.1.1 Transmit Data (BA), Pin 2                                                                                                                  | - 1  |

|    | 10.1.2 Receive Data (BB), Pin 3                                                                                                                   | - 1  |

|    | 10.1.3 Request to Send (CA), Pin 4                                                                                                                | -1   |

|    | 10.1.4 Clear to Send (CB), Pin 5                                                                                                                  | - 1  |

|    | 10.1.5 Data Set Ready (CC), Pin 6                                                                                                                 | - 1  |

|    | 10.1.6 Received Line Signal Detector (CF), Pin 8                                                                                                  | - 1  |

|    | 10.1.7 Data Terminal Ready (CD), Pin 20                                                                                                           |      |

|    | 10.1.8 Ring Indicator (CE), Pin 22                                                                                                                | -2   |

|    | 10.2 ISO Character Assignments                                                                                                                    | - 3  |

|    | 10.2.1 Mnemonics and Their Definitions                                                                                                            | 7    |

|    | 10.2.1 milemonics and merr berinicions                                                                                                            |      |

|    | $10.2.2 \text{ The ASSIT CODE} \dots \dots$ | -4   |

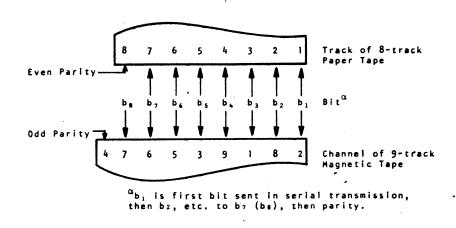

|    | 10.2.3 Tape Track Assignments                                                                                                                     | - 5  |

|    | List of Abbreviations                                                                                                                             | 1    |

|    | Glossary                                                                                                                                          | 1    |

|    |                                                                                                                                                   | 1    |

FIGURE

1

# LIST OF FIGURES

PAGE

|       | •                                                                                     |

|-------|---------------------------------------------------------------------------------------|

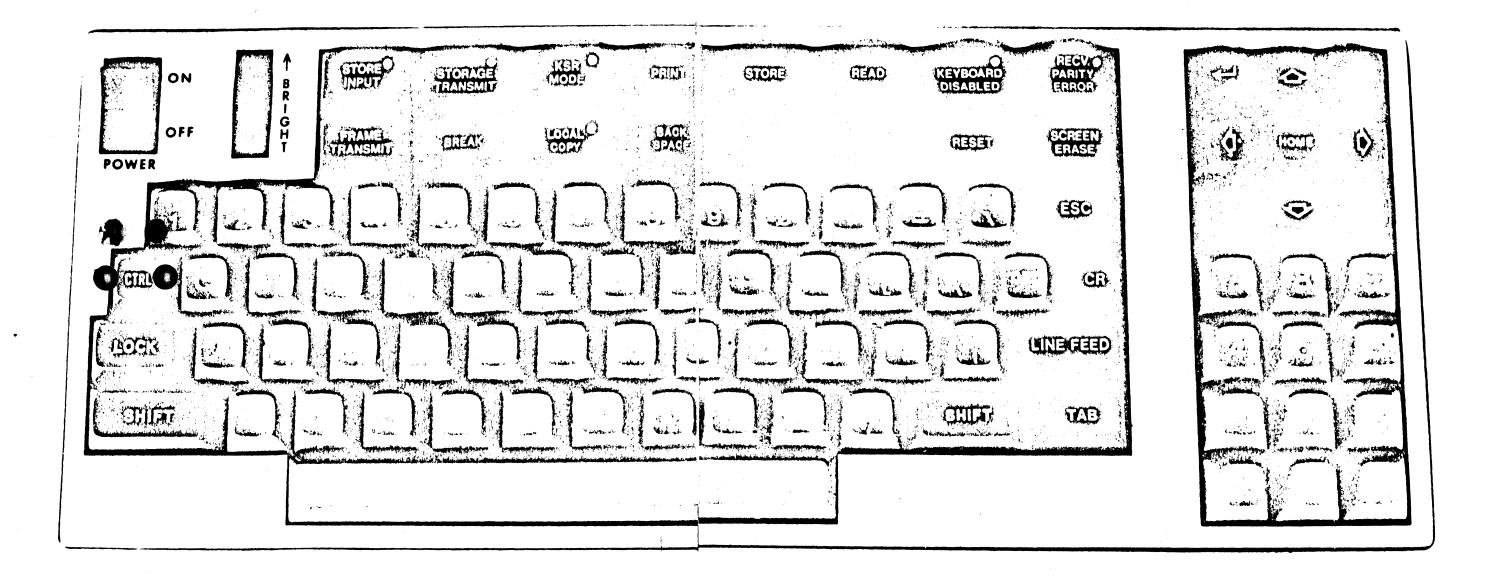

| 1-1   | Keyboard arrangement                                                                  |

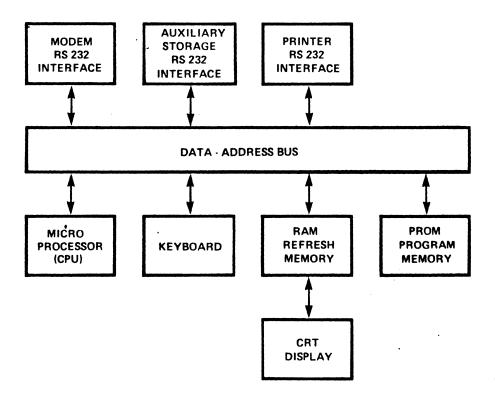

| 1-2   | Exterior of 8025 CRT terminal                                                         |

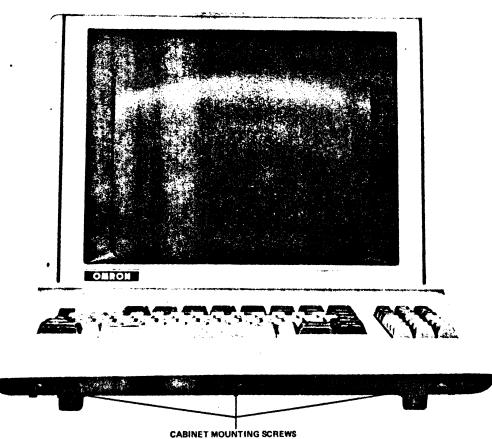

| 1-3   | Interior of 8025 CRT terminal                                                         |

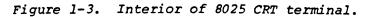

| 1-4   | 8025 CRT terminal, simplified block diagram                                           |

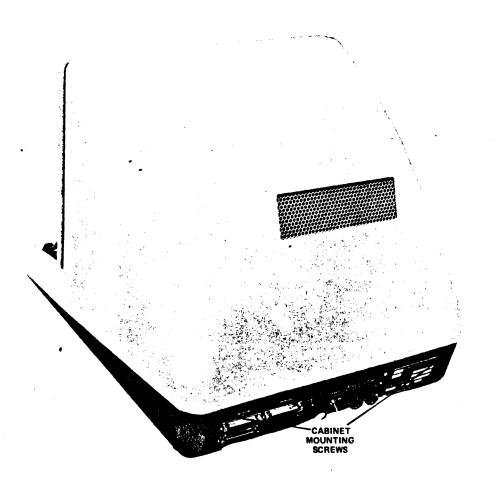

| 2-1   | Cabinet mounting screws (front)                                                       |

| 2-2   | Cabinet mounting screws (rear)                                                        |

| 2-3   | CRT display high voltage circuits (mounted below Monitor<br>Deflection Board)         |

| 2-4   | Printed circuit card locations                                                        |

| 2-5   | Monitor Deflection Board connections (viewed from top of terminal) . 2-4              |

| 2-6   | Flat cable connections                                                                |

| 2-7   | Flat-line connector configurations                                                    |

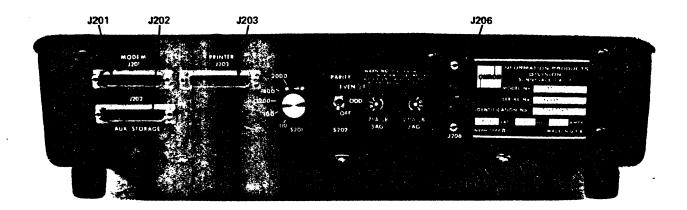

| 2-8   | 8025 CRT terminal: rear panel connectors                                              |

| 3-1   | 8025 CRT terminal keyboard                                                            |

| 4-1   | 8025 CRT terminal block diagram $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $4$      |

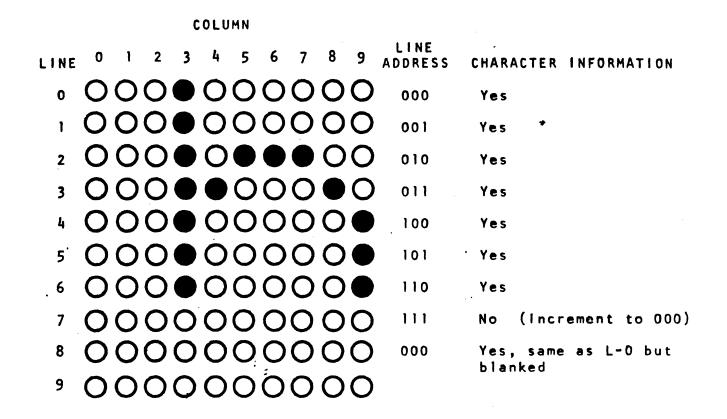

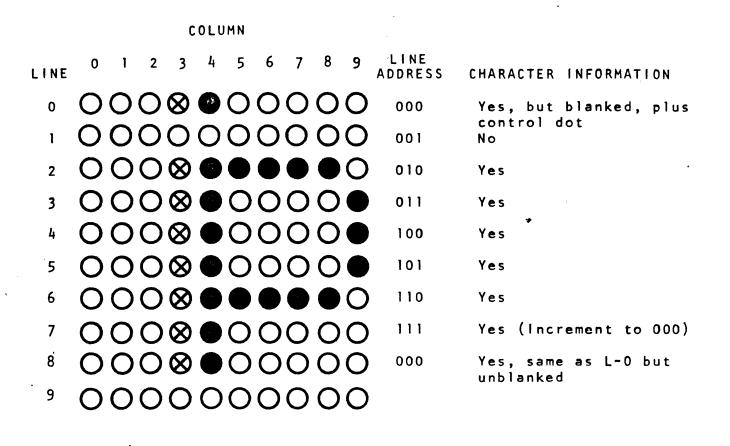

| 4-2   | Example of upper case character (H)                                                   |

| 4-3 · | Example of upper case character (V) $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 4-19 |

| 4-4   | Example of lower case character (h)                                                   |

| 4-5   | Example of lower case character (p)                                                   |

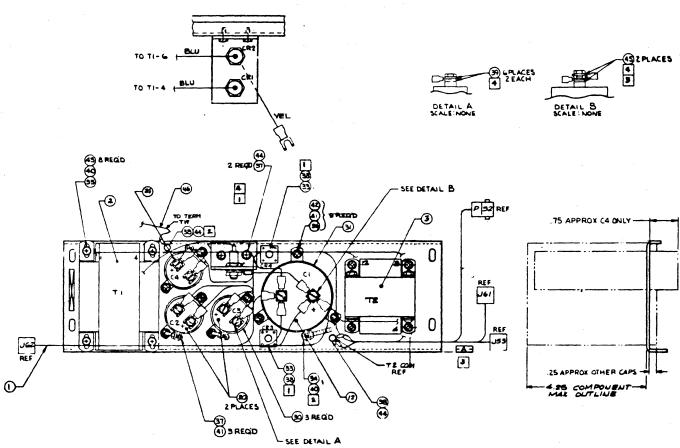

| 4-6   | Power supply block diagram                                                            |

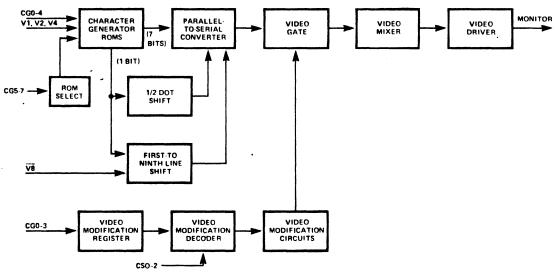

| 4-7   | CRT display block diagram                                                             |

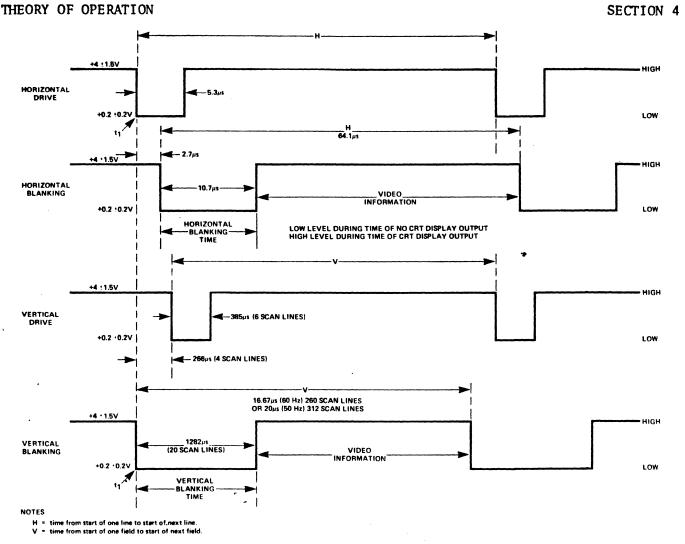

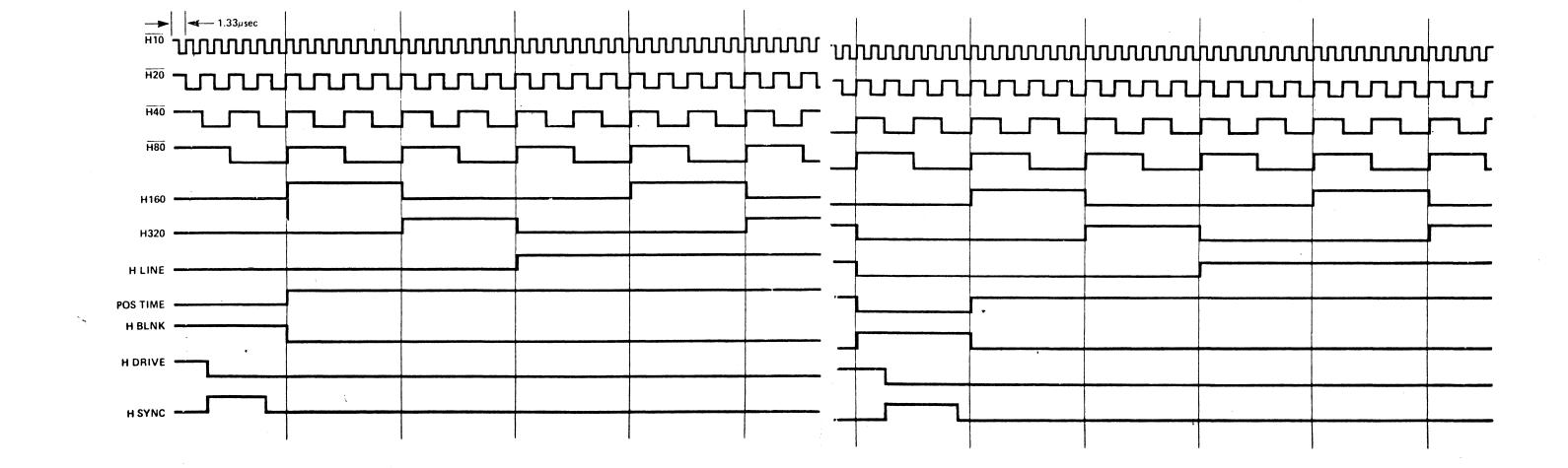

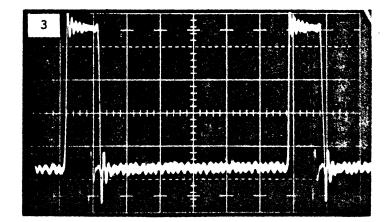

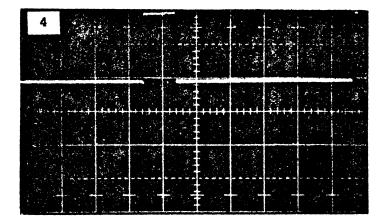

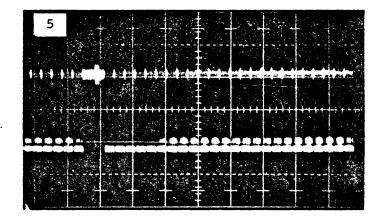

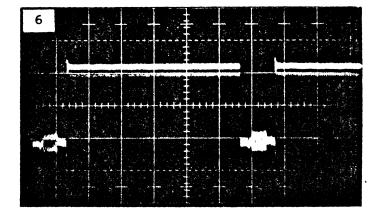

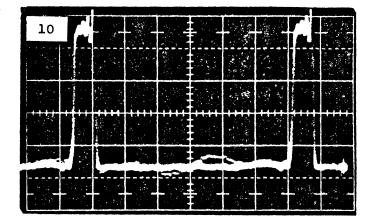

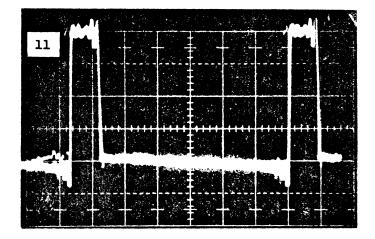

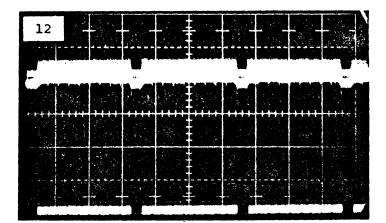

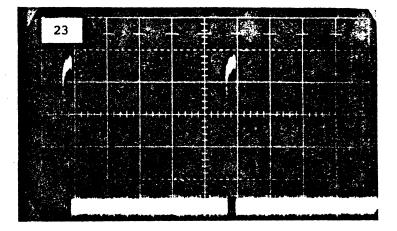

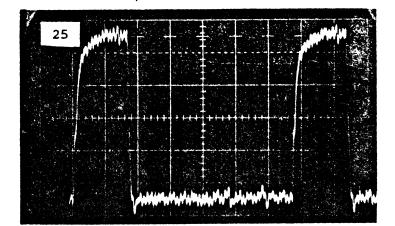

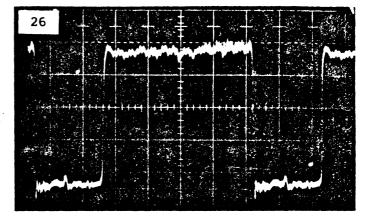

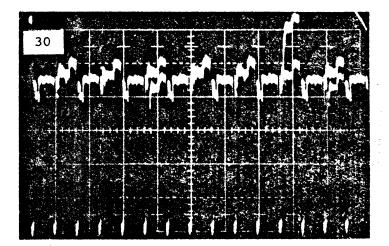

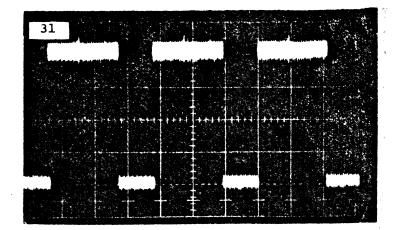

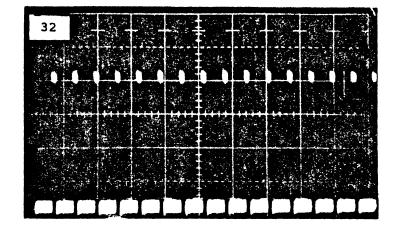

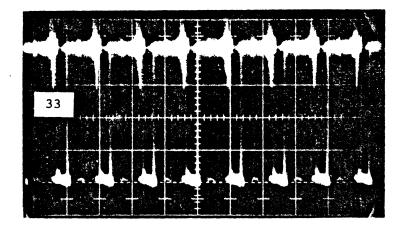

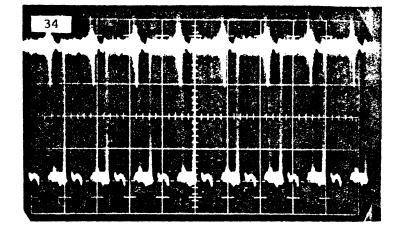

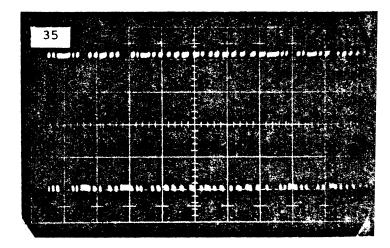

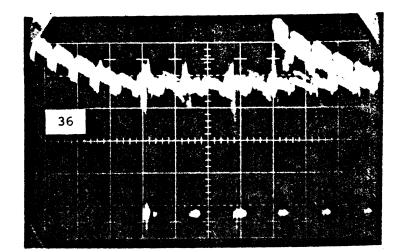

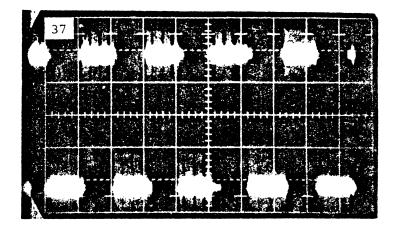

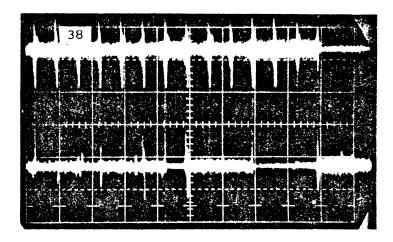

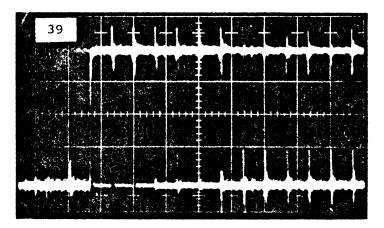

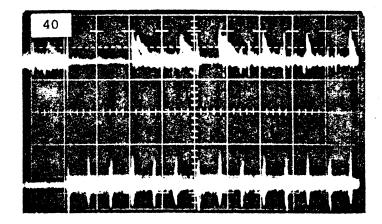

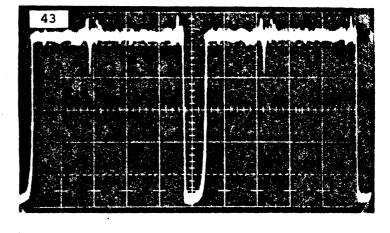

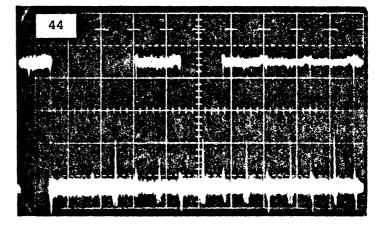

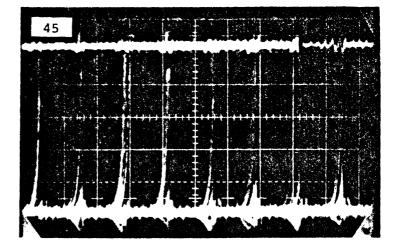

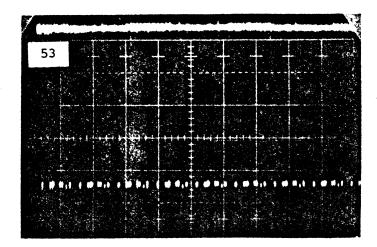

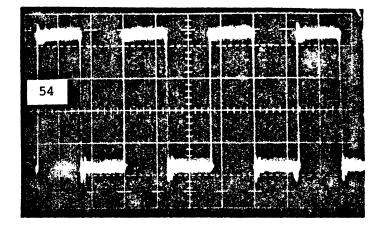

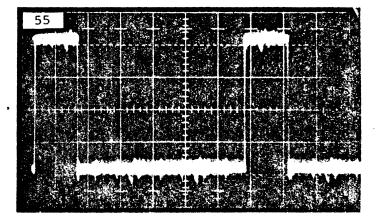

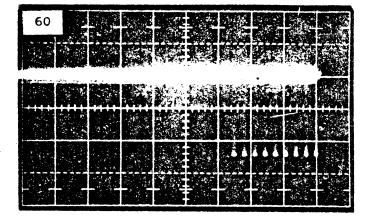

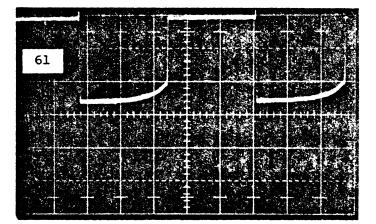

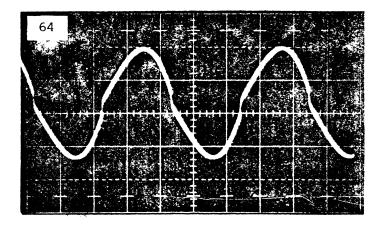

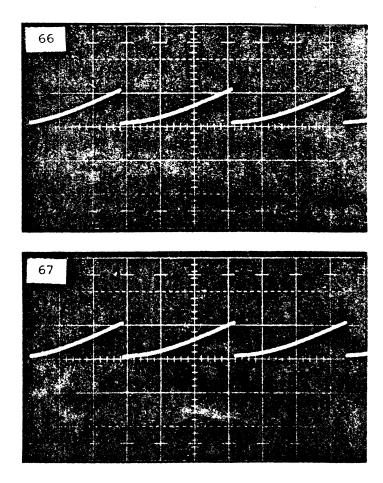

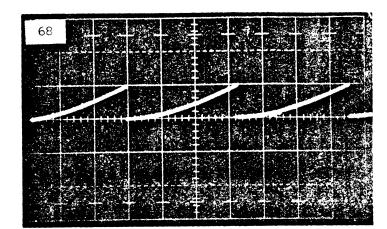

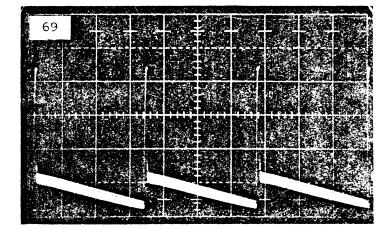

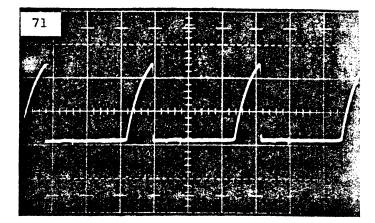

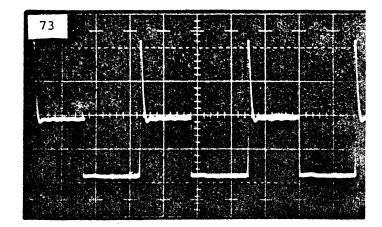

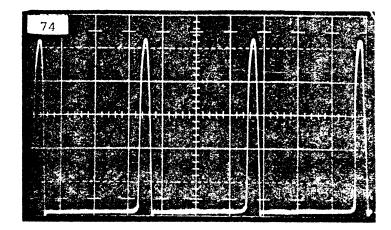

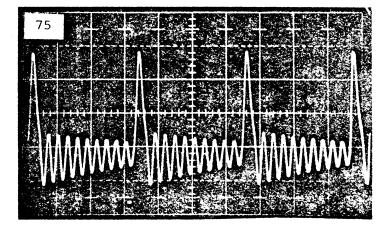

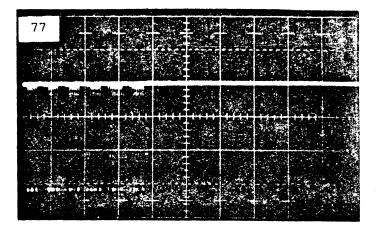

| 4-8   | CRT waveforms                                                                         |

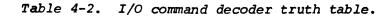

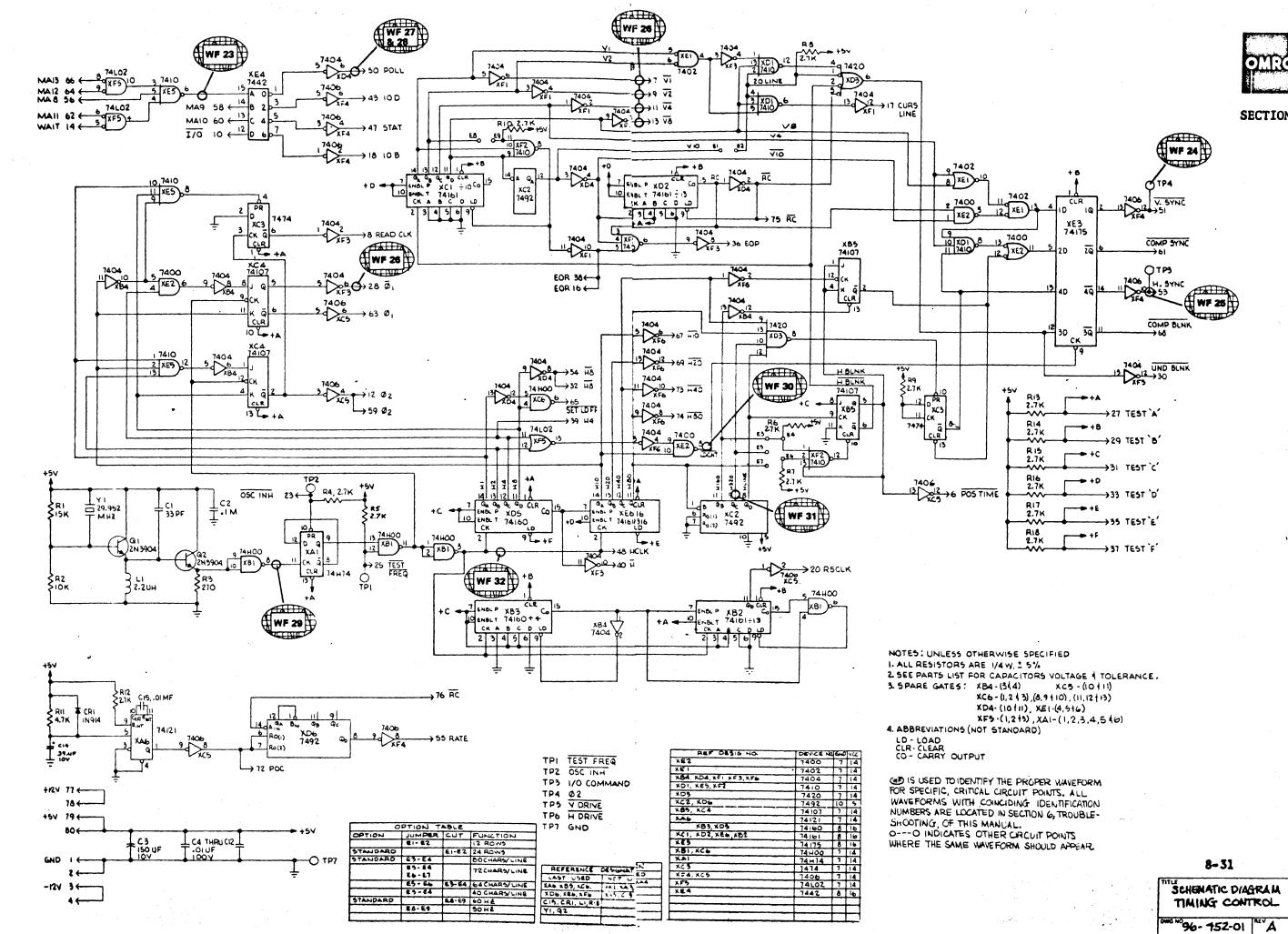

| 4-9   | Timing control card block diagram                                                     |

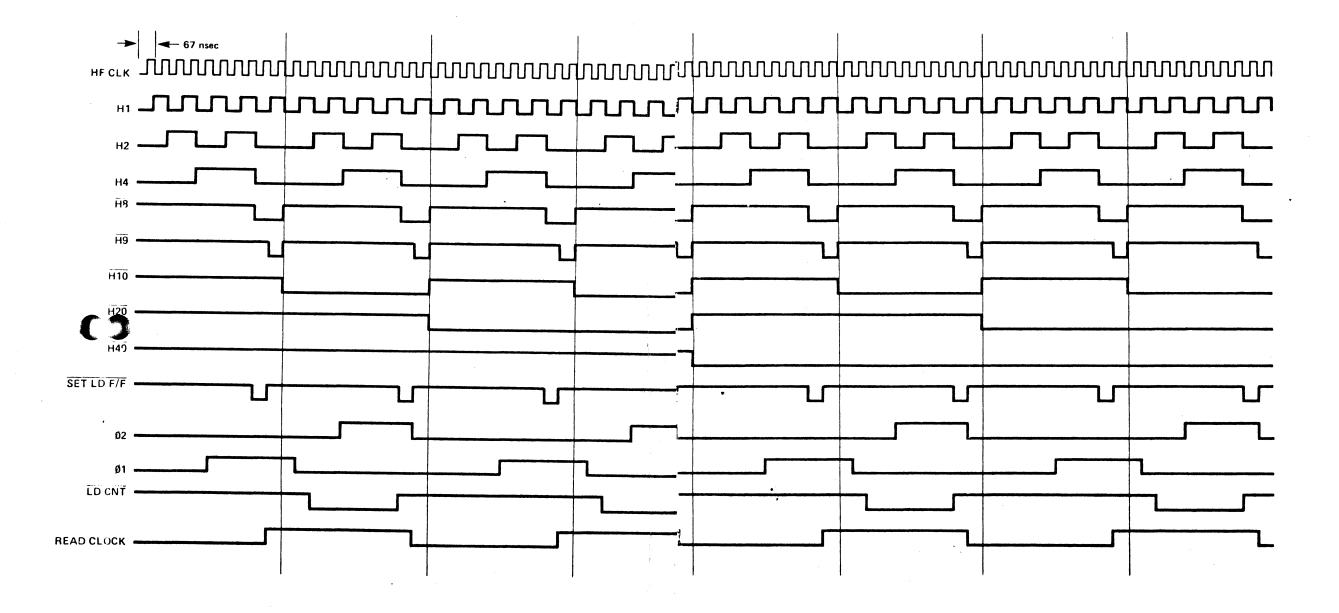

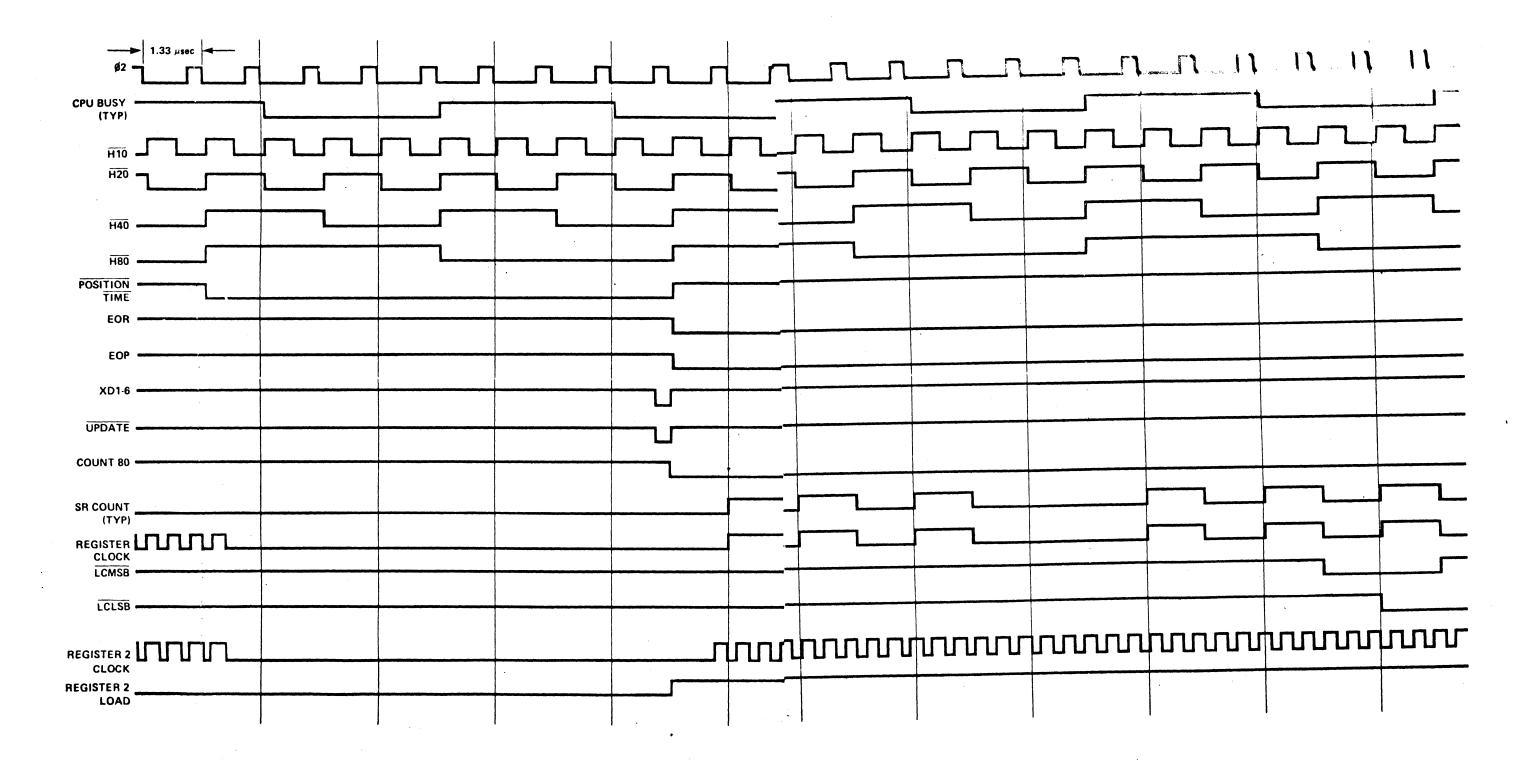

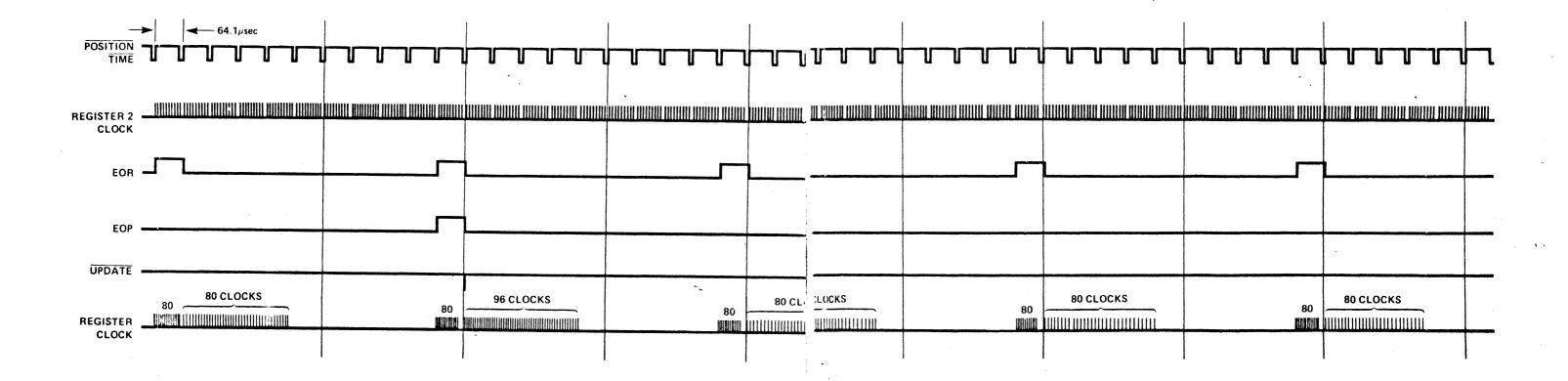

| 4-10  | Timing control card timing diagram                                                    |

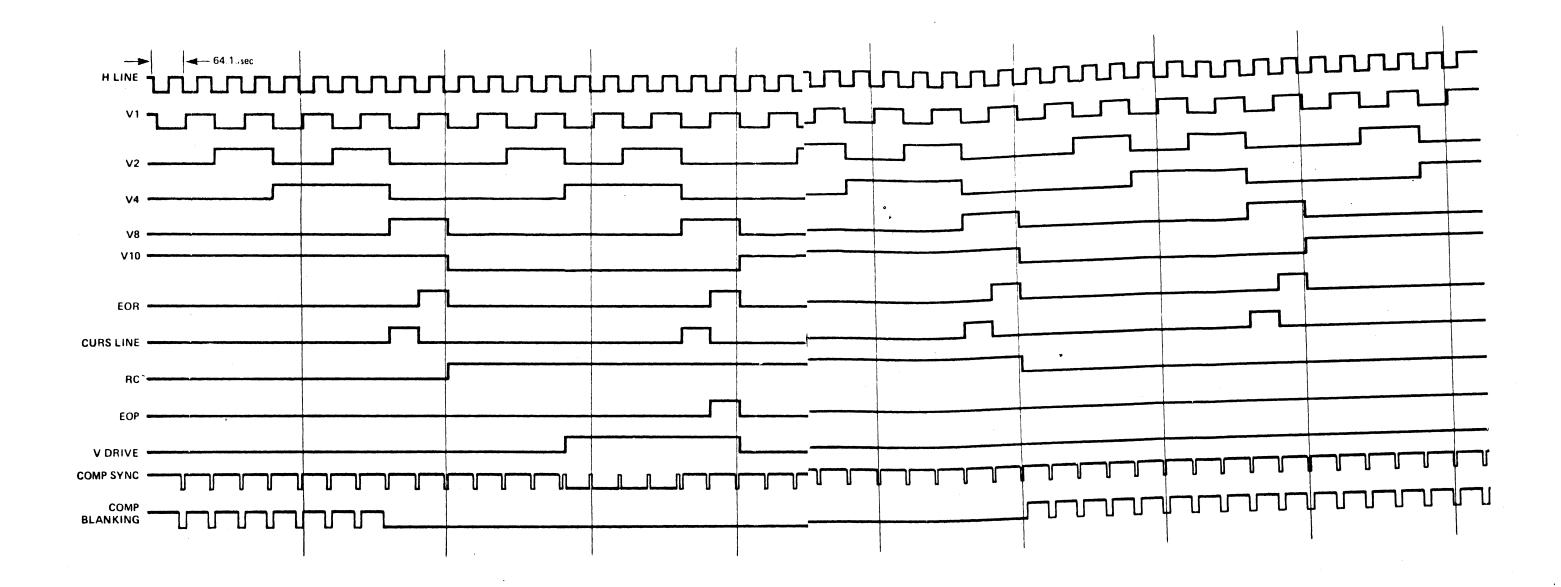

| 4-11  | Timing control card timing diagram                                                    |

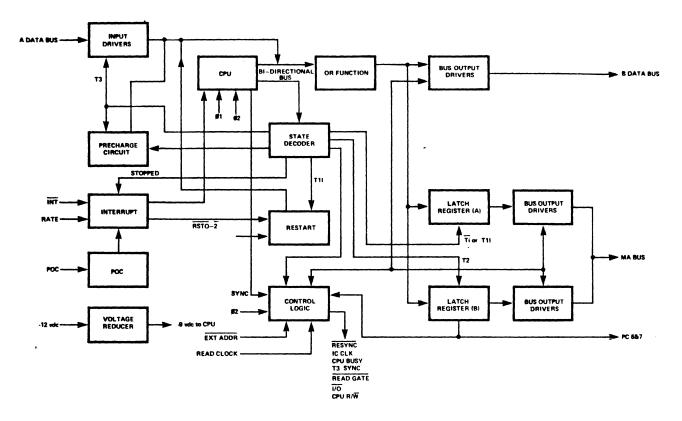

| 4-12  | Processor card block diagram                                                          |

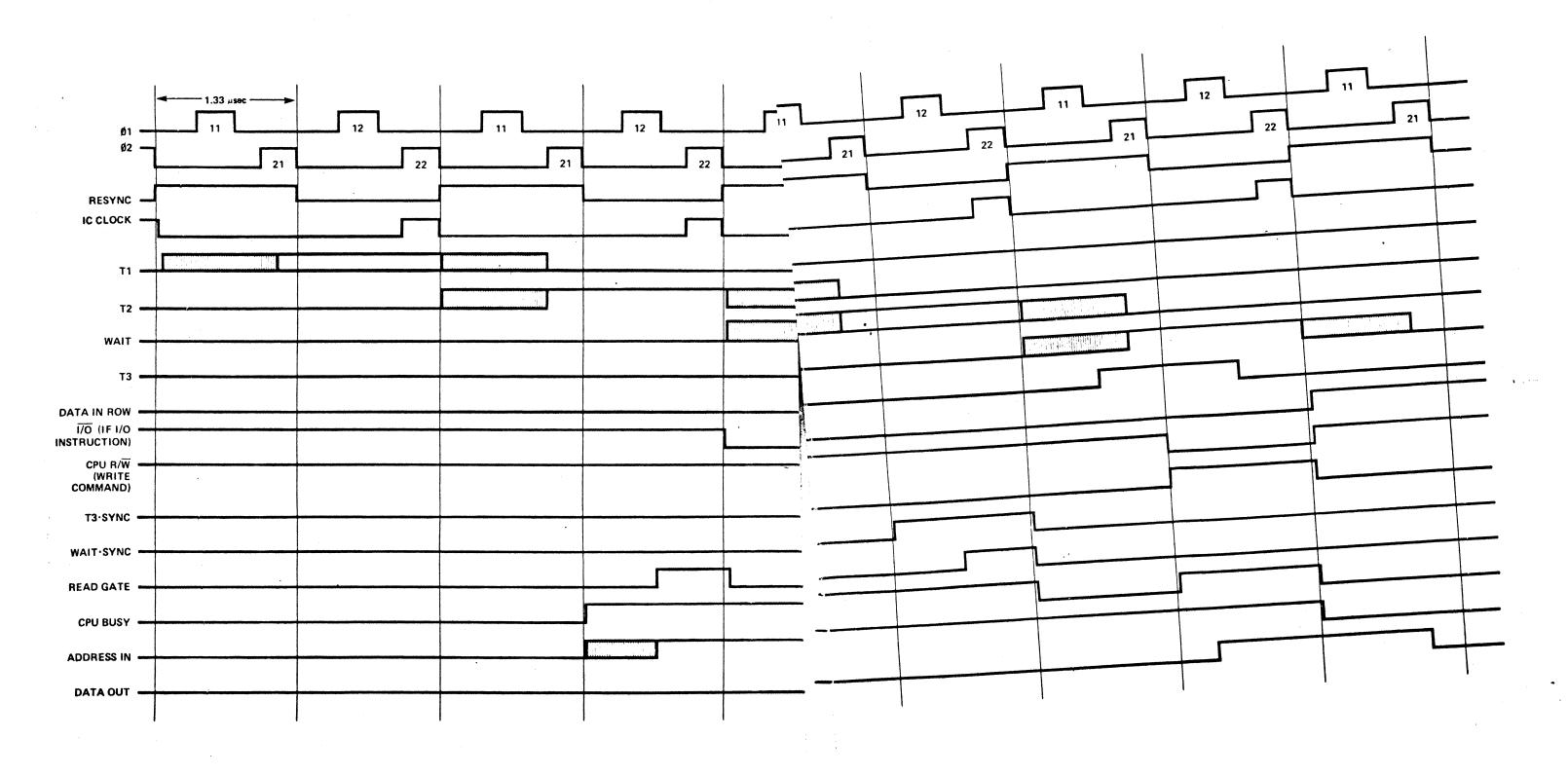

| 4-13  | Processor card (CPU) timing diagram                                                   |

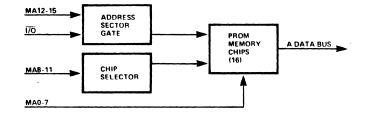

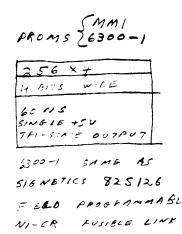

| 4-14  | Buffered PROM board block diagram                                                     |

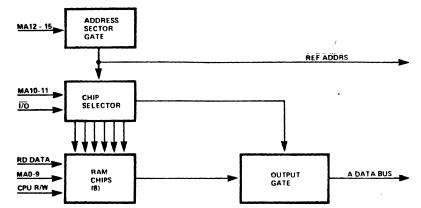

| 4-15  | Buffered RAM memory card block diagram                                                |

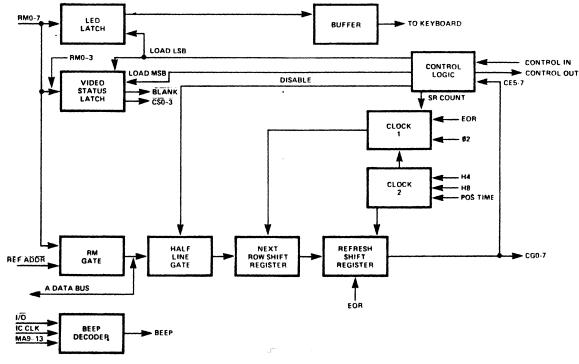

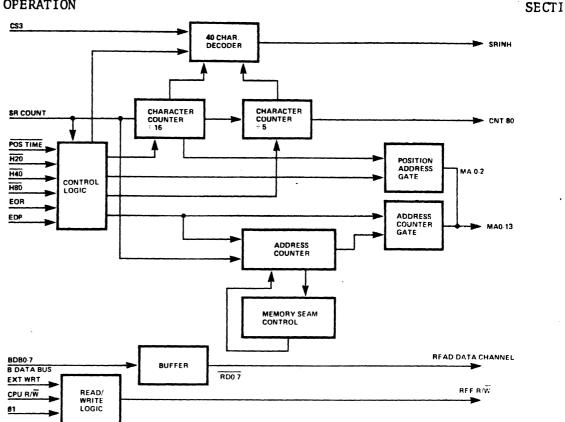

| 4-16  | Refresh buffer card block diagram                                                     |

| 4-17  | Refresh buffer/control card timing diagram 4-51                                       |

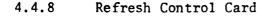

| 4-18  | Refresh control card block diagram                                                    |

| 4-19  | Cursor control card block diagram                                                     |

|       |                                                                                       |

# LIST OF FIGURES (continued)

PAGE

# FIGURE

|      |                                                                                                                               | -    |

|------|-------------------------------------------------------------------------------------------------------------------------------|------|

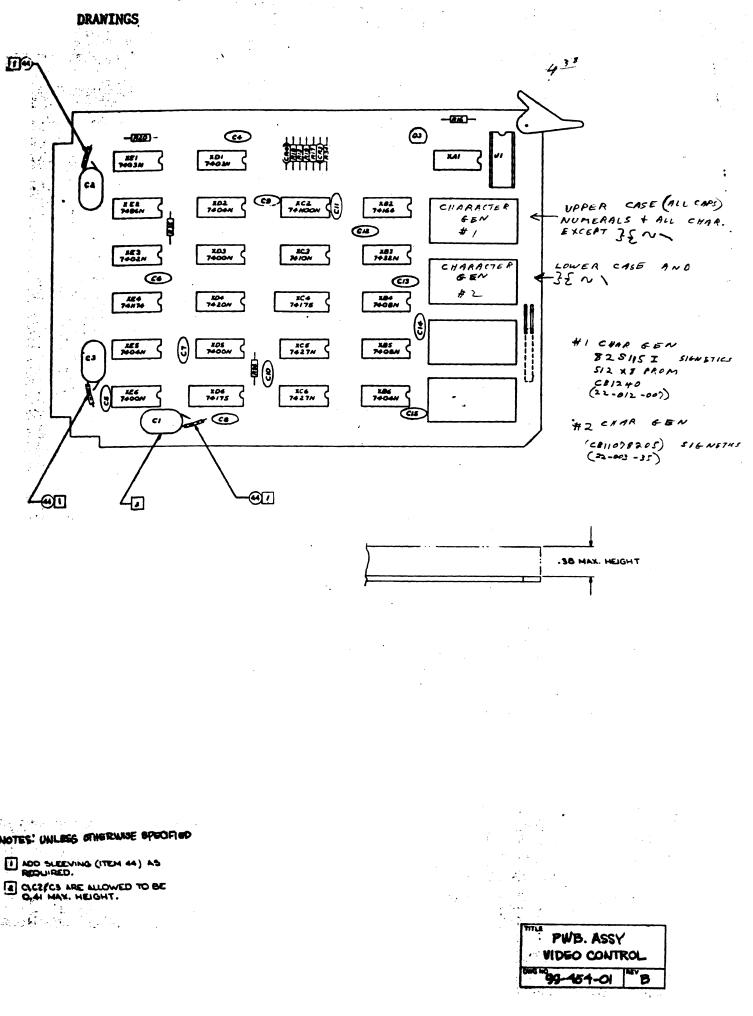

| 4-20 | Video control card block diagram                                                                                              | 4-62 |

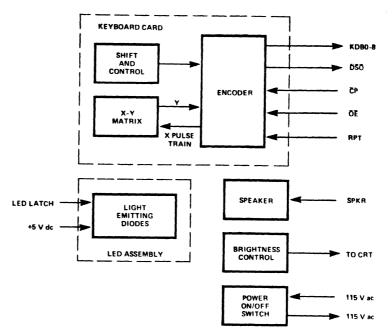

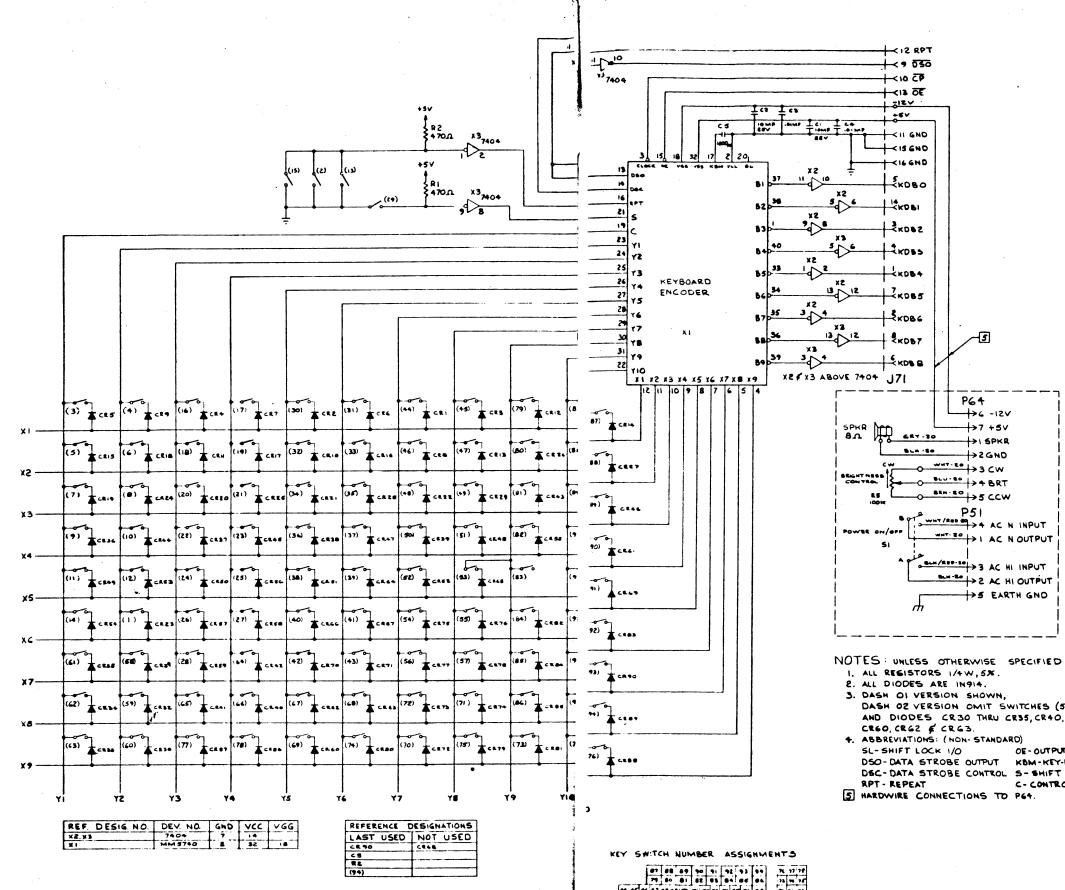

| 4-21 | Keyboard block diagram                                                                                                        | 4-68 |

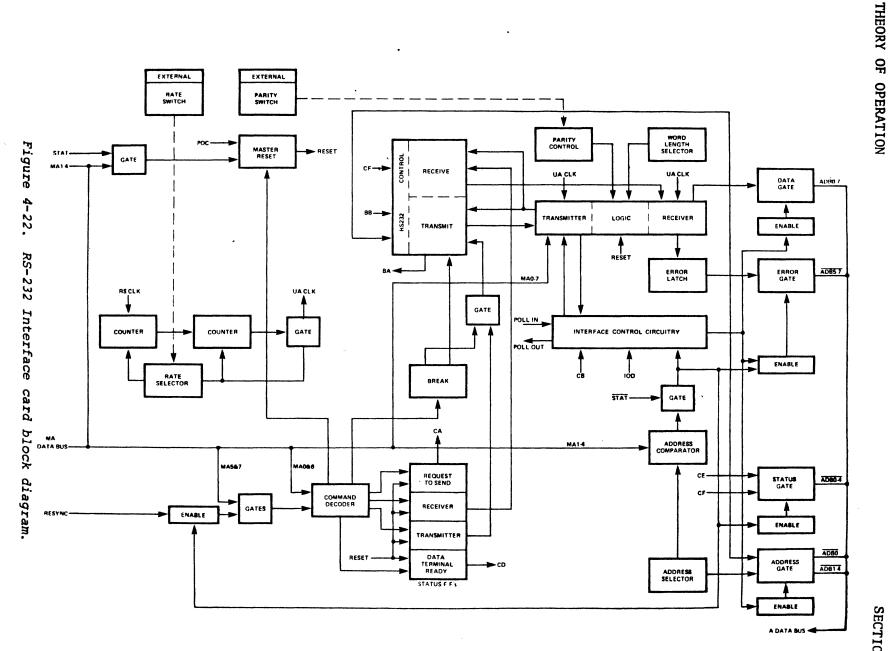

| 4-22 | RS-232 interface card block diagram                                                                                           | 4-72 |

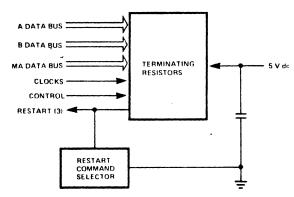

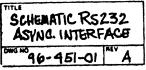

| 4-23 | Terminator card block diagram                                                                                                 | 4-79 |

| 6-1  | Cabinet mounting screws (front)                                                                                               | 6-14 |

| 6-2  | Cabinet mounting screws (rear)                                                                                                | 6-14 |

| 6-3  | Card cage                                                                                                                     | 6-15 |

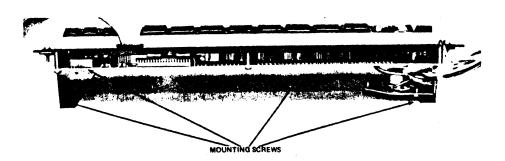

| 6-4  | Keyboard mounting screw locations                                                                                             | 6-16 |

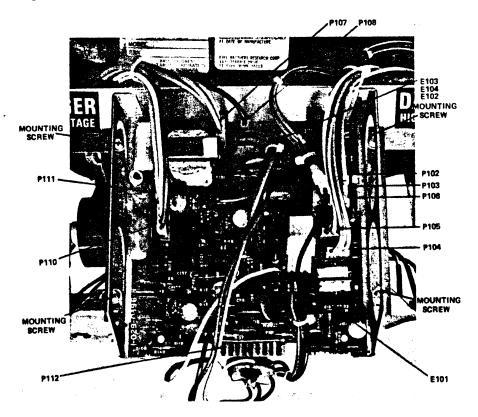

| 6-5  | Monitor Deflection Board interconnections and mounting screws                                                                 | 6-18 |

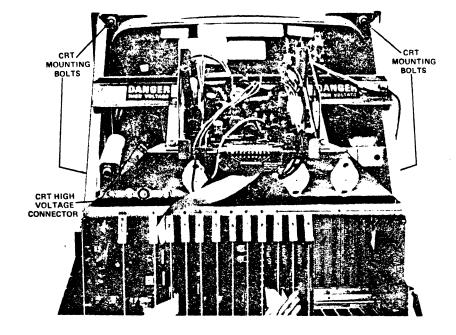

| 6-6  | CRT mounting bolts and high voltage connector                                                                                 | 6-54 |

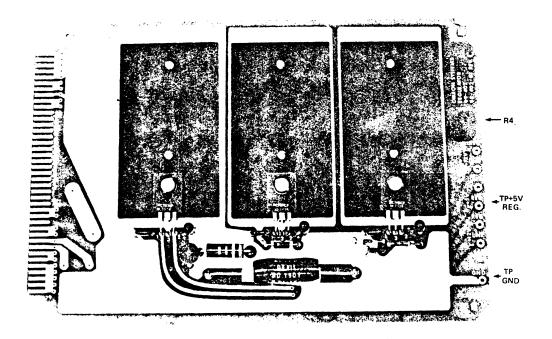

| 7-1  | Regulator Card: +5 V dc adjustment and test point locations                                                                   | 7-1  |

| 7-2  | Cursor Control Card click/beep volume adjustment location                                                                     | 7-2  |

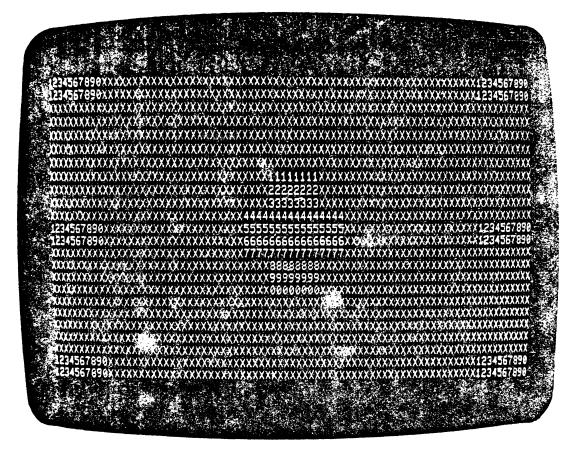

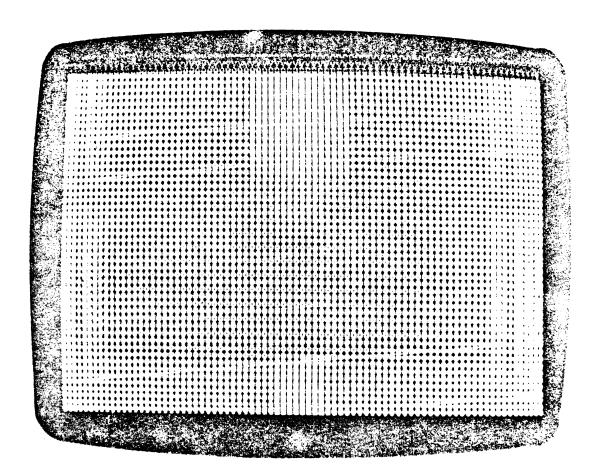

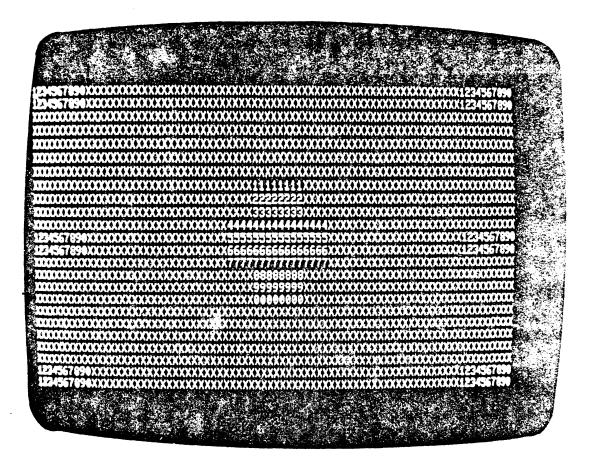

| 7-3  | Normal 8025 CRT presentation                                                                                                  | 7-3  |

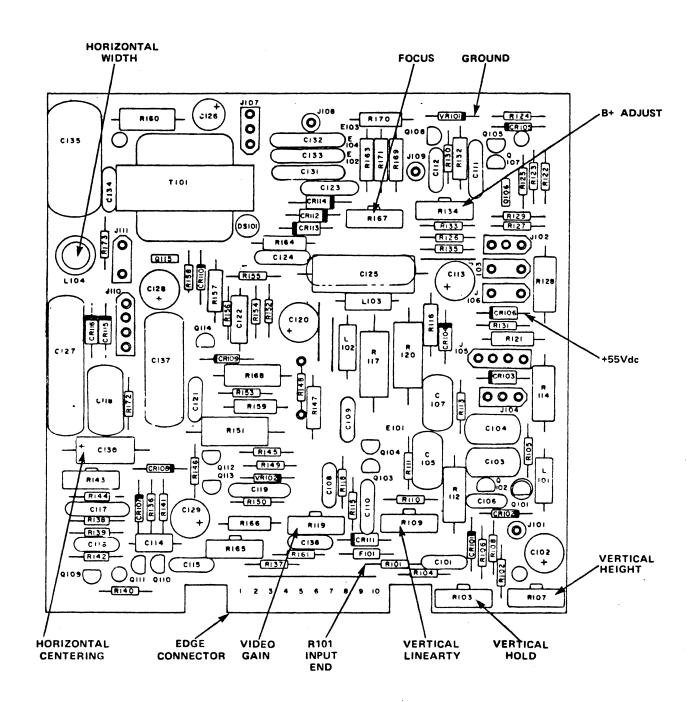

| 7-4  | Monitor Deflection Card: CRT adjustment and "test point" locations                                                            | 7-4  |

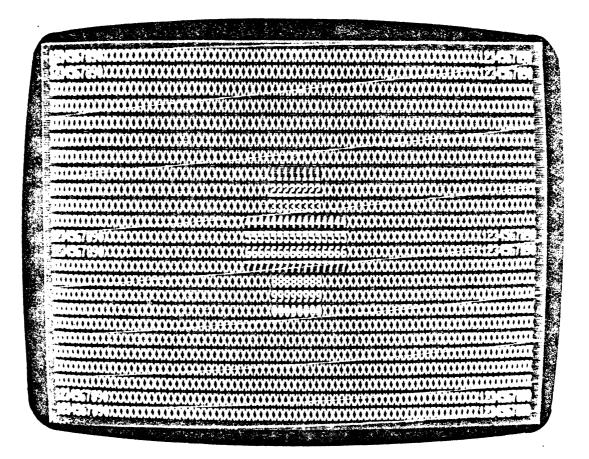

| 7-5  | Vertical linearity adjustment (R109) incorrectly set                                                                          | 7-6  |

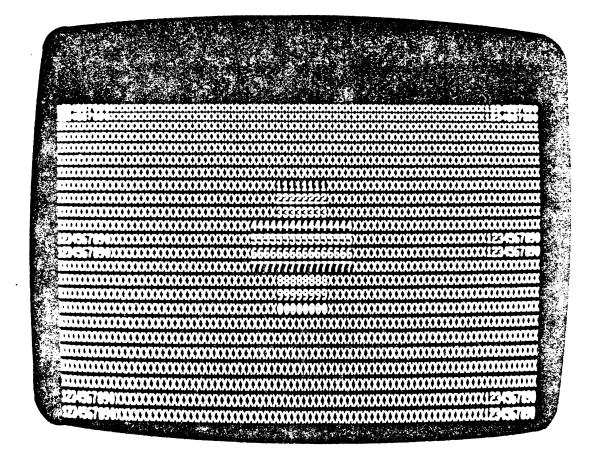

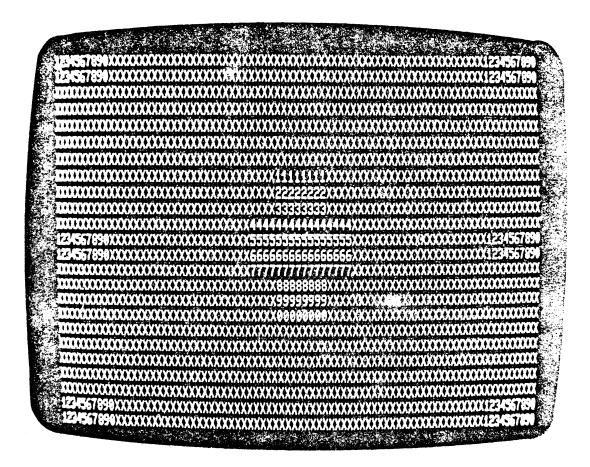

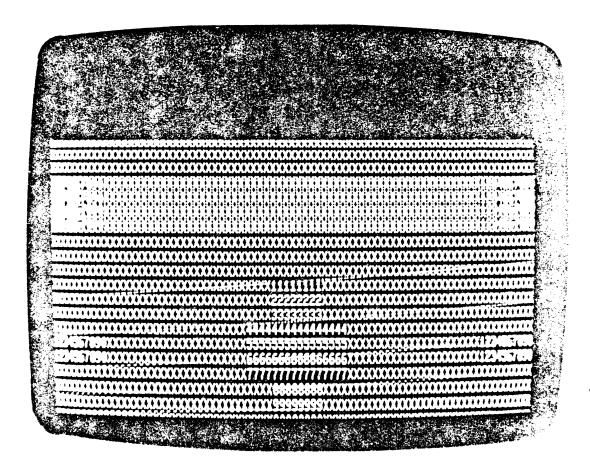

| 7-6  | Height adjustment (R107) incorrectly set                                                                                      | 7-7  |

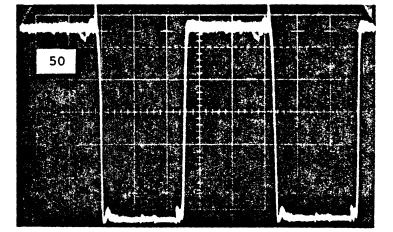

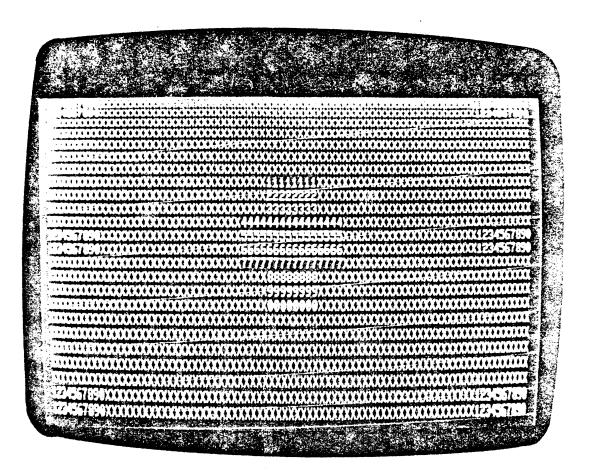

| 7-7  | Vertical hold adjustment (R103) incorrectly set                                                                               | 7-8  |

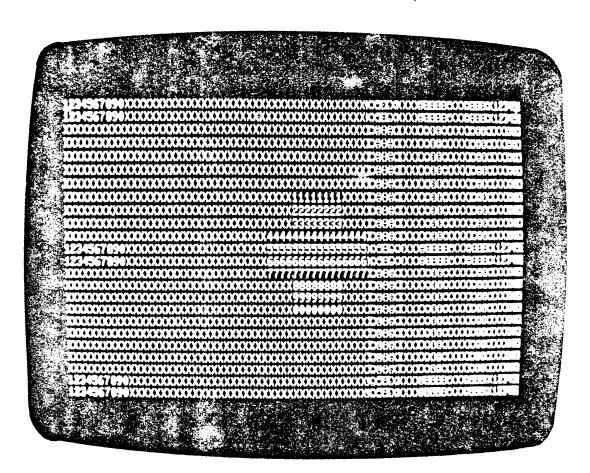

| 7-8  | Vertical hold adjustment (R103) incorrectly set                                                                               | 7-9  |

| 7-9  | Horizontal width adjustment (L104) incorrectly set, brightness                                                                |      |

| -    | control too high                                                                                                              | 7-10 |

| 7-10 | Severe misadjustment of horizontal centering adjustment (R143)                                                                | 7-11 |

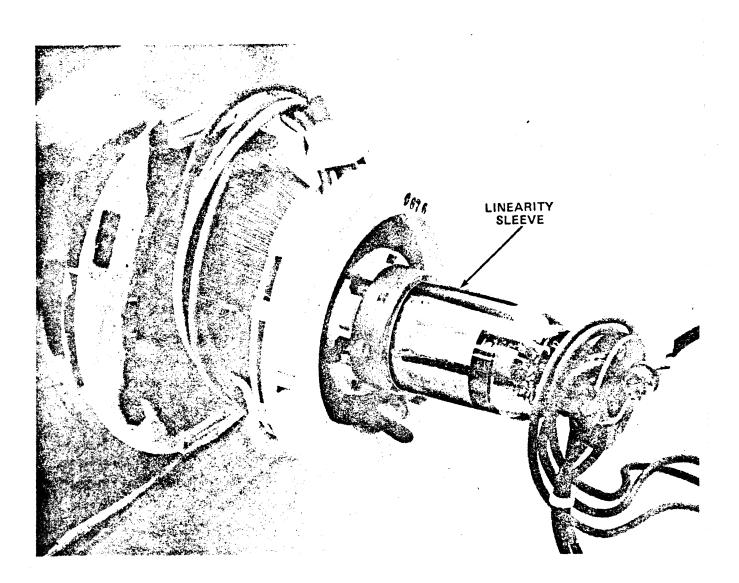

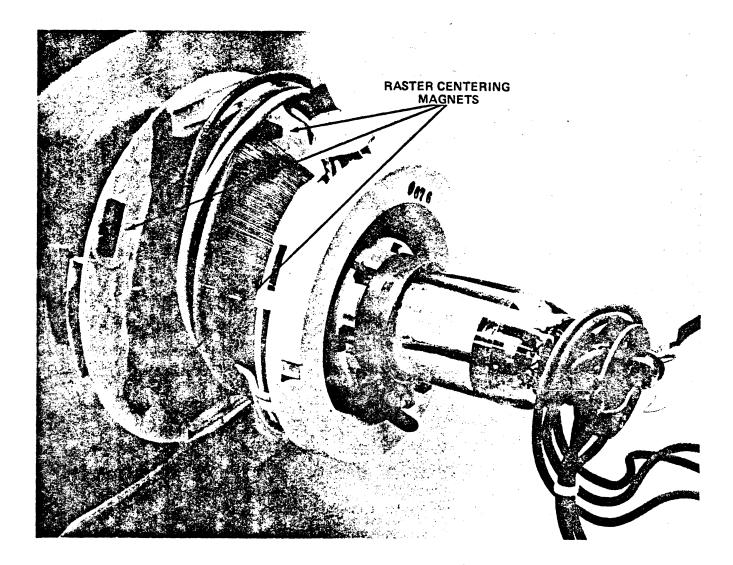

| 7-11 | Linearity sleeve inserted part way under yoke                                                                                 | 7-13 |

| 7-12 | Example of a horizontal centering problem caused by incorrect setting of the horizontal centering adjustment (R143) or of the |      |

|      | raster centering magnet discussed in paragraph 7.4.6                                                                          | 7-14 |

| 7-13 | Correct setting of the horizontal (video) centering adjustment (R143) and the raster centering magnets                        | 7-15 |

| 7-14 | Raster centering magnets                                                                                                      | 7-16 |

| 7-15 | Deflection yoke incorrectly set                                                                                               | 7-17 |

| 10-1 | Tape track assignments for ISO/ASCII codes                                                                                    | 0-5  |

|      |                                                                                                                               |      |

# LIST OF TABLES

P

TABLE

|        |                                                              |   |   | • |   |   |             |

|--------|--------------------------------------------------------------|---|---|---|---|---|-------------|

| 1-1    | 8025 CRT terminal specifications                             |   | • | • | • | • | 1-4         |

| 2-1    | Terminal-system interconnection                              |   | • | • | • | • | 2-8         |

| 3-1    | Visual Indicator On-Off States                               |   |   | • | • | • | 3-3         |

| 3-2    | Control code generation in the 8025 terminal                 |   |   | • | • | • | 3-1         |

| 4-1    | Sources and distribution of signals in the 8025 CRT terminal |   | • | • | • | • | <b>4-</b> 9 |

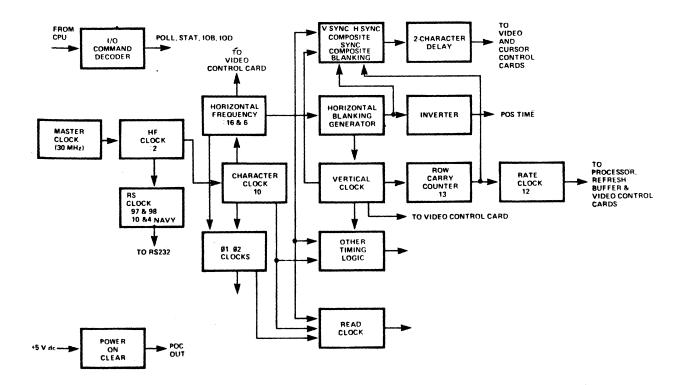

| 4-2    | I/O command decoder truth table                              |   |   | • | • | • | 4-3         |

| 4-3    | PROM chip location vs. memory address                        |   |   | • | • | • | 4-4         |

| 4-4    | RAM chip location vs. memory address                         |   |   | • | • | • | 4-4         |

| 4-5    | Video status functions                                       |   |   | • | • | • | 4-5         |

| 4-6    | Character generator ROM selection                            |   |   | • | • | • | 4-6.        |

| 4-7    | Video modification register (XC4) input-output parameters .  | • | , | • |   | • | 4-6!        |

| 4-8    | X-Y matrix switches and their functions                      | • | • | • | • | • | 6!          |

| 4-9    | LED Keyboard indicators                                      |   | • | • | • | • | 4-71        |

| 4-10   | Inputs and output states of command decoder (XD2)            |   | • | • |   | • | 76          |

| 4-11   | Status bits                                                  |   |   |   |   |   |             |

| 4-12   | UA CLK Configuration for various baud rates                  |   |   | • | • | • | 4-78        |

| 4-13 . | Program restart addresses provided by E1-E6 jumper options . |   |   | • | • | • | 4-80        |

| 6-1    | Symptoms vs. probable malfunctions in 8025 terminal          |   |   |   |   | • | 6-7         |

| 10-1   | RS-232C Pin Number - Signal Flow - Nomenclature relationship | • | • | • | • |   | 10-2        |

| 10-2   | ISO/ASCII Mnenonics and their definitions                    |   |   | • | • | • | 10-4        |

| 10-3   | ISO Code                                                     |   | • | • | • | • | 10-7        |

•

OMRON

GENERAL INFORMATION

1.1 GENERAL DESCRIPTION

The 8025 CRT Terminal is a versatile, simple-to-operate, self-contained cathode ray tube (CRT) display with keyboard entry that is capable of performing data processing functions. Capabilities of the 8025 cover a broad spectrum...from simple teletype (TTY) replacement to stand-alone operations.

Primary application for the 8025 is as a remote intelligent interactive terminal. In this role, it provides direct input of source data via keyboard entry, in addition to editing, information retrieval, and visual display of both transmitted and received data.

1.1.1 Functional Description

The 8025 CRT Terminal is a computer system designed around an internal microprocesor (CPU) interfaced to memory. The CPU allows the terminal to be easily adapted to many applications and functional routines without hardware changes. In addition, data bus organization permits the 8025 to be interfaced to a wide selection of peripherals such as communications modems, auxiliary storage devices, and printers.

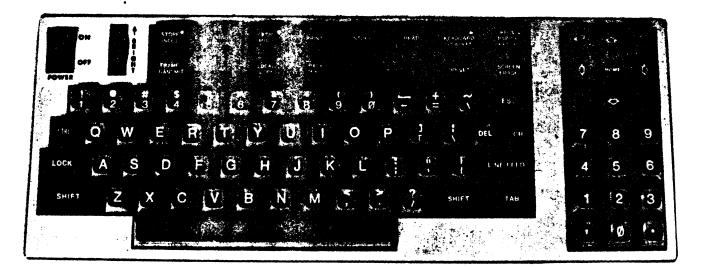

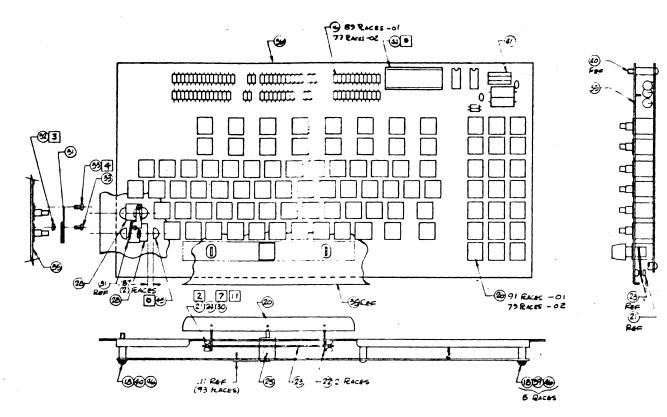

The 8025 Terminal has an ASCII (American Standard Code for Information Interchange)96- or 64-character keyboard. Keyboard arrangement, shown in Figure 1-1, conforms with the QWERTY format. In addition, there are 14 special function keys and 6 basic cursor control keys. The terminal also has a 12-key numeric pad.

Figure 1-1. Keyboard arrangement

On 24-line-per-page terminals, up to 1,920 characters (80 characters r line) can be displayed on a 15-inch CRT display. Up to 960 characters can be displayed on 12-line-per-page terminals. The basic memory consists of a 1,024 byte RAM (random access memory) refresh memory and a 2,048 byte PROM (programmed read only memory) or ROM (read only memory) program memory. Communications I/O (input/ output) interfacing conforms with Electronic Industries Association (EIA) Standard RS-232C. Additional RS-232 interfaces are included to interface the terminal with a printer and an auxiliary memory.

SECTION

Paragraph 1.2 gives complete specifications for the terminal.

#### 1.1.2 Mechanical Description

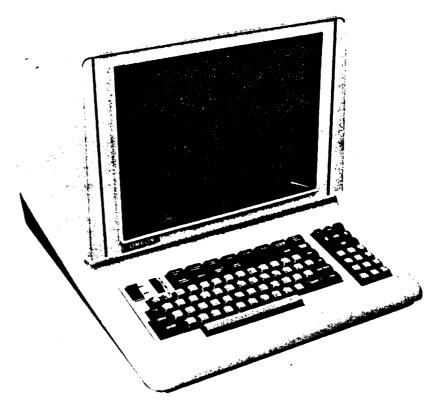

External. Figure 1-2 shows the outside of the 8025. The terminal is con tained within a two-piece, free-standing plastic housing. Its size, weight, and design make the unit ideal for table or desk-top installation. Interfacing with external equipment and primary power is done at the rear panel. Only five screws need to be removed to take off the top section of the housing. With this section removed, the internal assemblies are easy to reach.

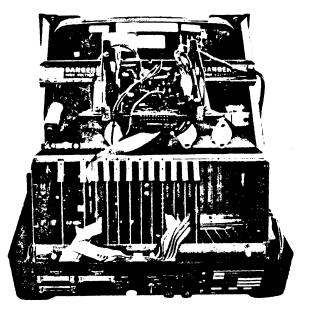

Internal. Figure 1-3 shows the inside of the 8025. Most of its circuitr is contained in a card cage that accommodates up to 18 plug-in circuit cards. Immediately above the cage is the CRT electronic circuitry. CRT electronics are mounted on the chassis and circuit cards. A removable power supply assembly is ted behind the card cage, below the CRT. The keyboard assembly is also removable.

Figure 1-2. Exterior of 8025 CRT terminal.

SECTION 1

### 1.1.3 Basic Operation

A simplified block diagram of the basic 8025 terminal is shown in Figure 1-4. For simplicity, the diagram shows internal communications taking place over only one data-address bus.

Figure 1-4. 8025 CRT terminal, simplified block diagram.

SECTION 1

Nearly all operations in the terminal are controlled by the CPU accorded to instructions stored in the program memory. Typical operation is briefly descrebe in the following paragraphs.

The CPU periodically polls the I/O cards and other functional modules on the bus to find whether any are ready to send or receive data. Assume the keyboard has data for the CPU. The keyboard intercepts a poll and identifies itself to the CPU. The CPU then enters the keyboard routine in program memory and enables the key board to transfer the data.

Following program instructions, the CPU processes the data. If the data is a character for display, the CPU determines where the next character is to be dis played and stores it at that location in the refresh memory. The refresh memory can then supply the data to the CRT display. If the data is a function code (e.g., carriage return), the CPU executes the instructions to move the cursor to the start of the line in refresh memory.

A data transfer from an I/O interface is performed in the same manner. In this case, the interface intercepts the poll and identifies itself to the CPU. The CPU enables the transfer and processes the data as if it came from the keyboard.

Assume the CPU has data for the interface. The CPU addresses, enables, an sets up the interface for the transfer. When the interface responds to the next poll, the CPU places the data on the bus for the interface.

#### 1.2 SPECIFICATIONS

#### 1.2.1 Standard Terminal Specifications

Specifications for the 8025 CRT Terminal are given in Table 1-1.

Table 1-1. 8025 CRT terminal specifications

| PARAMETER        | SPECIFICATION                                                                                         | · . |

|------------------|-------------------------------------------------------------------------------------------------------|-----|

| 8025 CRT Display |                                                                                                       |     |

| Screen Size      | Nominal 8" x 10", 15" diagonal.                                                                       |     |

| Safety Glass     | Integral part of CRT face.                                                                            |     |

| Phosphor         | P4 (white, medium persistence).                                                                       |     |

| Deflection Angle | 110°.                                                                                                 |     |

| Refresh Rate     | 60 Hz.                                                                                                | ~   |

| Resolution       | 1,000 TV lines at 40 fL, center.<br>800 TV lines at 40 fL, corner.<br>0.010" diameter spot at center. | 0   |

SECTION 1

# Table 1-1. 8025 CRT terminal specifications (continued)

| PARAMETER               | SPECIFICATION                                                                                                                                                                                                                 |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Radiation<br>Mechanical | Complies with DHEW Rules 42-CFR-Part 78.<br>Integral part of 8025 Terminal.                                                                                                                                                   |

| Display Format          |                                                                                                                                                                                                                               |

| Scanning                | Modified raster, 60 frames/sec.                                                                                                                                                                                               |

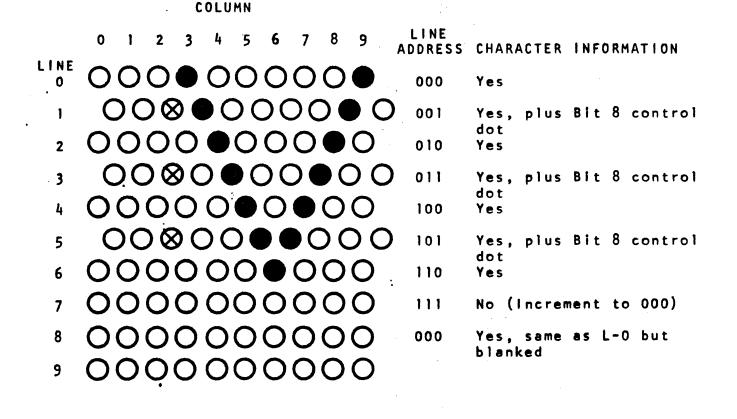

| Symbol Formation        | Upper case and numerics, $7 \times 7$ dot matrix; $14 \times 7$<br>effective dot matrix with $1/2$ dot shift provides<br>more natural-looking characters; lower case, $7 \times 9$<br>dot matrix ( $7 \times 7$ displayable). |

| Character Size          | 0.125" x .0875" (H x W).                                                                                                                                                                                                      |

| Page Format             | 80 characters/line, 24 lines/frame (1,920 charac-<br>ters/frame max. displayable) or 80 characters/line,<br>12 lines/frame (960 characters/frame max. display-<br>able).                                                      |

| Character Set           | ASCII, 64 or 96 characters.                                                                                                                                                                                                   |

| Memory System           |                                                                                                                                                                                                                               |

| Display Refresh         | RAM, 1,024 bytes.                                                                                                                                                                                                             |

| Program                 | PROM or ROM, 2,048 bytes.                                                                                                                                                                                                     |

| Keyboard                |                                                                                                                                                                                                                               |

| I/O Code                | ASCII, 64 or 96 alphanumeric character.                                                                                                                                                                                       |

| Arrangement             | QWERTY.                                                                                                                                                                                                                       |

| Numeric Pad             | 12-key including decimal point and comma.                                                                                                                                                                                     |

| Cursor Type             | Nondestructive blinking underline.                                                                                                                                                                                            |

| Cursor Control          | 6-wayup, down, left, right, home, and return left<br>to next line on "Next Line" (الم) command.                                                                                                                               |

SECTION

# Table 1-1. 8025 CRT terminal specifications (continued)

| PARAMETER                   | SPECIFICATION                                                                                                                               |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Control Keys                | 14carriage return, line feed, tab, delete, shift<br>lock, cursor controls, escape, and control.                                             |

| Special Function Keys       | 12store input, storage transmit, KSR mode, frame<br>transmit, print, store, break, backspace, local<br>copy, read, reset, and screen erase. |

| Indicator Lights            | 6receive parity error, keyboard disabled, KSR mode, local copy, storage transmit, and store.                                                |

| Input/Output                |                                                                                                                                             |

| Modem Interface             | RS-232 asynchronous - 110, 300, 1,200, 1,800 and 2,000, switch selectable.<br>ASR/KSR half/full duplex.<br>11-bit character, 110 baud.      |

|                             | 10-bit character, all other rates.                                                                                                          |

|                             | Parity - odd, even, or none, switch selectable.                                                                                             |

| Printer Interface           | RS-232 asynchronous - 1,200 baud standard; 110,<br>300, 1,200, 1,800, 2,000 selectable by internal<br>jumper option.                        |

| Auxiliary Storage Interface | RS-232 asynchronous - 1,200 baud standard; 110,<br>300, 1,200, 1,800, 2,000 selectable by internal<br>jumper option.                        |

| Operating Features          |                                                                                                                                             |

| N-Key Rollover              | No data loss when two or more keys are simultane-<br>ously depressed.                                                                       |

| Acoustic Feedback           | Programmable beep indicates that an event has<br>taken place, or is taking place, in the terminal<br>(e.g., end of line).                   |

| Automatic Repeat            | Character repeats 15 times/sec if key is depressed for 0.5 sec or longer.                                                                   |

| Tab                         | Transmits TAB code in KSR mode.                                                                                                             |

| Editing                     | Automatic character insertion at position indicated by cursor replaces previously recorded character.                                       |

SECTION 1

# Table 1-1. 8025 CRT terminal specifications (continued)

| PARAMETER     | SPECIFICATION                                                    |  |

|---------------|------------------------------------------------------------------|--|

| Electrical    |                                                                  |  |

| Input Power   | 115 V ± 11.5 V ac, 59-61 Hz, 300 watts.                          |  |

| Mechanical    |                                                                  |  |

| Size          | 16" height, 17.5" width, 23" depth.                              |  |

| Weight        | 50 lb.                                                           |  |

| Mounting      | Free standing.                                                   |  |

| Cabinet       | Plastic, beige finish.                                           |  |

| Environmental |                                                                  |  |

| Temperature   | Operating, +5° C to 40° C ambient.<br>Storage, -40° C to +65° C. |  |

| Humidity      | 5 to 80%, noncondensing.                                         |  |

| Altitude      | 10,000 feet maximum.                                             |  |

.

#### 1.3 WARRANTY INFORMATION

This section contains OMRON's warranty and explains the warranty policy as it pertains to your 8025 CRT Terminal. Your 8025 Terminal was fully inspected and tested for workmanship and proper operation prior to shipment.

### 1.3.1 Claim for Transit Damage

It is important that the instrument be inspected for physical damage an tested for proper operation (see Section 3) upon arrival at its destination. If i does not operate properly, or is damaged in any way, a claim should be filed immediately with the carrier. A complete report of the damage should be furnished the claim agent and a copy forwarded to OMRON. <u>Do not proceed with repair</u>; OMRON wil advise you of the disposition to be made of the terminal and arrange for repair or replacement. Please include name of equipment, model number, serial number and your purchase order number in any correspondence regarding the terminal.

### 1.3.2 Statement of OMRON Warranty

OMRON warrants to the original purchaser, for a period of three (3) monifrom the date of shipment, that the 8025 CRT Terminal shall be free from defects in material and workmanship, but does not cover shipping damage, physical abuse, fire theft, damage incurred during field repair, or damage as a result of not following proper preventive maintenance procedures.

All parts and labor will be provided free of charge for three (3) moths at the OMRON-designated facility (see Paragraph 1.3.4) with shipping being paid in both directions by the customer.

The customer has the option of returning either the complete terminal, individual assemblies, or components. All items will be system tested before return to the customer. A Merchandise Return Authorization should be used for this purpose. (See the sample on page 1-11).

This warranty does not apply to fuses, lamps and other such parts for which normal periodic replacement is required.

Vendor-supplied subassemblies and sealed units are subject to their individual warranties and cannot be opened or repaired by the customer during the warranty period without voiding their warranties. Paragraph 1.3.5 provides informa tion on such items used in the 8025 Terminal.

This warranty is in lieu of all other warranties, expressed or implied, statutory or otherwise, including any implied warranty of merchantability. OMRON shall not otherwise be liable to any inquiries, loss or damage direct or consequential arising out of the use or inability to use the equipment.

1.3.3 Warranty Claims Against OMRON

When making a warranty claim on your 8025 CRT Terminal, follow the repair and return policies outlined in Paragraph 1.4 of this manual.

OMRON

GENERAL INFORMATION

SECTION 1

If damage to the 8025 Terminal has been caused by improper use, abnormal operating conditions, improper maintenance or other factors excluded by the warranty, repairs will be billed at cost. In such cases an estimate will be submitted before the work starts.

1.3.4 OMRON Designated Facility

The following facility is authorized to repair the 8025 CRT Terminal:

OMRON Corporation of America Information Products Division Field Service Department 432 Toyama Drive Sunnyvale, Ca. 94086

### 1.3.5 Suppliers Warranties

Vendor-supplied subassemblies and units used in the 8025 CRT Terminal which are covered by supplier warranties are as follows:

| Item        | Supplier | Warranty Period |

|-------------|----------|-----------------|

| CRT Display | Miratel  | 12 months       |

SECTION 1

1.4 REPAIR AND RETURN OF EQUIPMENT

1.4.1 Policy

OMRON shall provide maintenance (labor and parts) and shall keep the equipment in good operating condition. Maintenance shall not include repair of damage resulting from accident, transportation between sites, neglect, misuse, failure of electrical power or air conditioning or humidity control, or cause other than ordinary use.

### 1.4.2 Equipment Failure

When equipment failure occurs, regardless of cause, and the equipment is determined to be non-repairable on-site, it shall be returned to OMRON.

### 1.4.3 Non-repairable Determination

Normally, the determination of non-repairable equipment will be made with an OMRON representative present. If a representative is not available, authorization to return non-repairable equipment must be received from this repair facility:

> OMRON Corporation of America Information Products Division Field Service Department 432 Toyama Drive Sunnyvale, Ca. 94086 (408) 734-8400 TWX 910-339-9341

### 1.4.4 Equipment Return Procedure

The OMRON representative, whether present on-site or using communication media, will prepare the appropriate Merchandise Return Authorization (Form No. MRA-83-001).. This authorization must be individually numbered. It must properly identify the non-repairable equipment by description, part number, and serial number. The reason or reasons for return must also be stated in adequate detail. A sample Merchandise Return Authorization appears on page 1-11. A copy of the Authorization shall be filed at the returnee's site. The remaining copies will be attached to the shipping crate as shown on the form.

1.4.5 Packing and Packaging Procedure

After proper completion of MRA form, return the equipment as follows:

- 1. Pack the unit in a container appropriate for the method of shipment. Ideally, use a package similiar to the one in which the unit was delivered. Attach the MRA to the container.

- 2. Ship the unit, transportation prepaid, to the address mentioned in paragraph 1.4.3. All sub-assemblies and parts described in the warranty will be replaced if OMRON's examination discloses that the defects are within the limits of the warranty. If damage or defect(s) are not covered by the warranty, the returnee will be told what repairs are required and how much they will cost. The unit will be repaired and returned upon agreement.

| ••• | -    | •   | •     | •   | • | - |

|-----|------|-----|-------|-----|---|---|

|     |      |     |       |     |   |   |

|     | 1    |     | 1     | 1   |   |   |

| 御史  | Real | ιe? | THE P | 200 |   |   |

|    | OMR                         | ON                        | OMRON CORPO<br>Information Product<br>432 TOYAMA DRIVE<br>SUNNYVALE, CALIF<br>(408) 734-8400 TWX | . 94086                        | ERICA                       | ľ                                     | Nº     | 00    |

|----|-----------------------------|---------------------------|--------------------------------------------------------------------------------------------------|--------------------------------|-----------------------------|---------------------------------------|--------|-------|

|    |                             |                           | M                                                                                                | IERCHANDISE P                  | ETURN AUTHORIZATION         |                                       |        |       |

| (  | USTOME                      | R: <u>M1</u><br>OC        | . Ron J. Fe                                                                                      | jeran                          |                             | Date:                                 | 9-8-   | -75   |

|    |                             |                           | 01 Indian H<br>con Hill, MD                                                                      |                                |                             |                                       |        |       |

| 3  | PLEASE<br>DIVISIO           | COMPL<br>N, ATTA          | ETE THIS FORM AI<br>ACHED TO THE SHI                                                             | ND RETURN IT TO<br>PPING CRATE | OMRON CORPORATION OF AMI    | ERICA, INFORMATI                      | ON PRO | DUCTS |

| 2  | SHIP PR                     | EPAID T                   | <b>O</b> :                                                                                       |                                |                             |                                       |        |       |

|    |                             | MENTS                     |                                                                                                  |                                | EX-U.S.                     | SHIPMENTS                             |        |       |

| *• | INFORM<br>432 TOY<br>SUNNYA | ATION<br>AMA D<br>(ALE, C | RATION OF AMERI<br>PRODUCTS DIVISIO<br>RIVE<br>ALIFORNIA 94086<br>ized by:                       |                                | Merch                       | *                                     |        |       |

|    | ITEM                        | QTY                       | PART NO.                                                                                         | L. Aleczko,<br>SERIAL NO.      | Asst Division Mana<br>DESCR | IGOT<br>IPTION                        |        |       |

|    | 1                           | 1                         | 99-399-001                                                                                       | 501                            | RS232                       | · · · · · · · · · · · · · · · · · · · |        |       |

|    |                             |                           |                                                                                                  |                                |                             |                                       |        |       |

REASON FOR RETURN: ..... Does not transmit.

|                | 4                     |                                       |        |

|----------------|-----------------------|---------------------------------------|--------|

| AUTHORIZED BY: | Ron J. Fejeran        | <u>Government Marketing Ngr.</u>      | 9-8-75 |

|                | Ron J. Fejeran        | Title                                 | Date   |

| RECEIVED BY:   |                       |                                       |        |

|                | Name                  | Title                                 | Date   |

| ROUTE TO:      | Quality Assurance for | evaluation.                           | ~      |

| -              |                       | · · · · · · · · · · · · · · · · · · · |        |

No 009

SECTION 1

1.5 LIST OF OMRON MNEMONICS

The following list defines the various mnemonics developed for the 8025 CRT Terminal.

| ADB0-7:    | A Data Bus bits.                                                                                                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| BA:        | RS 232 signal used by modem.                                                                                                                    |

| BDB0-7:    | B Data Bus bits.                                                                                                                                |

| BEEP:      | Decode of CPU $\overline{1/0}$ command; triggers beep circuit which produces audible output whenever a Keyboard key is depressed.               |

| BLANK:     | Blanks screen under program control.                                                                                                            |

| BLINK:     | Signal from Refresh Buffer to enable blink function on Video<br>Control Card.                                                                   |

| CA:        | RS 232 signal used by modem.                                                                                                                    |

| CD:        | RS 232 signal used by modem.                                                                                                                    |

| CG0-7:     | Character generator input bits; 8-bit ASCII code.                                                                                               |

| CLK RDY:   | Clock ready; synchronous 8008 Ready with IC clock.                                                                                              |

| CLRF:      | Clear 'F'; clears video attribute register on Video Control card<br>at end of each scan line.                                                   |

| CNT 80:    | Indicates next line shift register is loaded.                                                                                                   |

| COMP BLNK: | Composite blanking signal.                                                                                                                      |

| CPU BUSY:  | Indicates CPU is using memory busses.                                                                                                           |

| CP:        | Clock pulse; Keyboard encoder clock at H40 rate.                                                                                                |

| CPU R/W:   | CPU read/write; signal controlling writing of data into memories by CPU.                                                                        |

| CS0-3:     | Video status bits; CSO, CS1, CS2 and CS3 control video on/off,<br>block/off, cursor underline, control/character display and half<br>line mode. |

| CURS LINE: | Cursor line; defines the scan line in each character row on which cursor is displayed.                                                          |

| DSO:       | Data strobe out; indicates Keyboard wants to send a character.                                                                                  |

•

| GENERAL INFORM | SECTION                                                                                                                                          |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| EOP:           | End of page; timing signal used to control the update of hard-<br>ware parameters from 6 fixed locations in memory.                              |

| EOR:           | End of row; timing signal used to control loading of character display shift register.                                                           |

| EXT ADRS:      | External address; allows an external device to address memory.                                                                                   |

| H1:            | Timing signal; 7.488 MHz, one-half HF CLK.                                                                                                       |

| H2:            | Timing signal; 3.744 MHz, one-fourth HF CLK.                                                                                                     |

| H4:            | Timing signal; 1.872 MHz, one-eighth HF CLK.                                                                                                     |

| H8:            | Timing signal; character clock, 670 nsec period.*                                                                                                |

| H10:           | Timing signal; two character clock periods (1.34 usec).                                                                                          |

| H20:           | Timing signal; four character clock periods (2.68 usec).                                                                                         |

| H40:           | Timing signal; eight character clock periods (5.36 usec).                                                                                        |

| H80:           | Timing signal; 16 character clock periods (10.72 usec),<br>equals horizontal blanking time.                                                      |

| H160:          | Timing signal; period equals 1/3 of horizontal scan line (21.44 usec).                                                                           |

| H320:          | • Timing signal; period equals 1/2 of horizontal scan line (32.16 usec).                                                                         |

| HF CLK:        | Basic timing signal; provides reference for all terminal timing signals.                                                                         |

| H LINE:        | Horizontal line; 15,000 Hz (63.32 usec), horizontal frequency.                                                                                   |

| H SYNC:        | Timing signal at scan line rate used to drive scan circuits in monitor (same as H DRIVE).                                                        |

| IC CLK:        | Timing signal in sync with alternate $\emptyset$ 2 clocks; indicates 2nd half of CPU cycle.                                                      |

| INH LD:        | Inhibit load; inhibits loading of video parallel-to-serial converter when Refresh Memory is accessed by anything other than the video generator. |

| IOB:           | Decode of CPU I/O command INP3; initiates data transfer to or from peripheral without resetting the interface.                                   |

| IOD:           | Decode of CPU I/O command INP1; initiates data transfer to or from peripheral with reset of the interface.                                       |

|                |                                                                                                                                                  |

:

GENERAL INFORMATION

| KDB0-7:   | Keyboard data bus bits; data out of Keyboard.                                                                                           |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| LCLSB:    | Load count least significant bits; loads row position stored<br>in Refresh Memory into cursor row register on Cursor Control Card.      |

| LCMSB:    | Load count most significant bits; loads column position stored in<br>Refresh Memory into cursor column register on Cursor Control Card. |

| LDCNT:    | Load count; clocks two-character delay, clocks write command to Refresh Memory.                                                         |

| LITE1-12: | Interconnect circuits for Keyboard LED indicators.                                                                                      |

| LOAD F:   | Decode of video attribute character on CG0-7; controls loading of video attribute register.                                             |

| MA0-15:   | Memory address bits.                                                                                                                    |

| MATCH:    | Signal generated whenever outputs from video counter and cursor position register are equal; used to generate cursor.                   |

| NULL:     | Detection of blank "character" in row (i.e., blank memory).                                                                             |

| OE:       | Output enable; resets DSO and enables Keyboard output register for next key depression.                                                 |

| PC6:      | D6 output of CPU during T2 state; one of two bits that define CPU cycle type.                                                           |

| PC7:      | D7 output of CPU during T2 state; second of two bits that define<br>CPU cycle type.                                                     |

| POC:      | Power on clear; initializes Terminal when power is applied.                                                                             |

| POLL:     | Decode of CPU I/O command (INPO); poll signal initiates select-<br>ion of peripheral device for data transfer.                          |

| POS TIME: | Position time; occurs at scan line rate (see timing diagrams in Section 4).                                                             |

| RATE:     | 5 pps clock; controls video blink rate.                                                                                                 |

| RC:       | Row carry; blanks CRT during vertical retrace.                                                                                          |

| RD0-7:    | Data bits into Refresh Memory.                                                                                                          |

| READ CLK: | Read clock; used as a reference to generate timing signals for ROM memories.                                                            |

| REF ADRS: | Refresh address; indicates refresh memory is being accessed.                                                                            |

|   |                        | ······································                                                                      |

|---|------------------------|-------------------------------------------------------------------------------------------------------------|

|   | REF $R/\overline{W}$ : | Refresh read/write; controls writing of data into Refresh Memory.                                           |

|   | <b>RESYNC:</b>         | CPU SYNC output reclocked with $\emptyset$ 2.                                                               |

|   | RM0-7:                 | Output data bits from Refresh Memory.                                                                       |

|   | RPT:                   | Repeat; signal to Keyboard telling it to repeat last character transferred as long as the key is depressed. |

|   | RS CLK:                | Clock used to generate timing reference for I/O data transfer RS 232 cards.                                 |

|   | RST0-2:                | Restart command bits; inserts program address into CPU.                                                     |

|   | SET LDFF:              | Set load flip-flop; output of load flip-flop*loads video parallel-<br>to-serial converter.                  |

|   | SPKR:                  | Speaker; produces audible energy generated by BEEP oscillator circuit.                                      |

|   | SR COUNT:              | Indicates refresh logic has control of memory bus.                                                          |

|   | SRINH:                 | Shift register inhibit; controls loading of display shift register in half line mode.                       |

| • | STAT:                  | Status; decode of CPU I/O command (INP2).                                                                   |

|   | SYNC:                  | Output of CPU; indicates CPU is on second half of a timing state.                                           |

|   | T2 SYNC:               | Second half of CPU T2 timing state.                                                                         |

|   | T3':                   | Early T3 timing state; synced with IC CLK.                                                                  |

|   | T3 SYNC:               | Second half of CPU T3 timing state.                                                                         |

|   | UA CLK:                | Universal asynchronous clock; clocks transmitter-receiver on<br>RS 232 Interface card.                      |

|   | UND BLNK:              | Undelayed blanking signal.                                                                                  |

|   | UPDATE:                | Pulse occuring at frame rate controlling updating of hardware parameter from 6 fixed locations in memory.   |

|   | V1, V2, V4:            | Timing signal; defines scanning lines one through eight (character row lines are numbered 0 through 9).     |

|   | V8:                    | Timing signal; defines scan line nine (8) by itself, defines scan line ten (9) in conjunction with V1.      |

|   | V10:                   | Differentiates between even and odd vertical rows.                                                          |

|   |                        |                                                                                                             |

:

GENERAL INFORMATION

| VIDEO:     | Signal which drives the monitor to produce the white areas on screen which form characters, video attributes, etc. |

|------------|--------------------------------------------------------------------------------------------------------------------|

| V DRIVE:   | Vertical drive.                                                                                                    |

| V SYNC:    | Timing signal at frame rate used to drive scan circuits in monitor (same as V DRIVE).                              |

| WAIT:      | CPU timing state; indicates READY was low prior to end of T2 state.                                                |

| WAIT SYNC: | Second half of CPU WAIT state.                                                                                     |

| Ø1, Ø2:    | Timing signal that provides timing reference for all data trans-<br>fer on memory busses.                          |

SECTION 2

Every 8025 CRT terminal is fully inspected and tested before shipment to ensure that it meets specifications. It is packaged for safe transit under normal freight-handling conditions. The terminal should normally arrive ready for use.

Claims with the carrier should be filed within 15 days from delivery. OMRON therefore recommends that you unpack and test the terminal upon receipt.

Terminal installation should be made as outlined in this section.

2.1 UNPACKING PROCEDURE

### 2.1.1 Inspection

Before unpacking the terminal, inspect the shipping container for signs of possible damage to the unit during transit.

## 2.1.2 Unpacking

Set the crate "Right End Up" and use a knife blade, 1/4" or less long, to open the top of the crate. Save the shipping container and packing materials in case the terminal must someday be returned to OMRON or shipped to a repair facility.

Figure 2-1. Cabinet mounting screws (front).

2.2 OFF-LINE CHECKOUT

2.2.1 Mechanical Inspection

External Inspection. Inspect the terminal for external damage such as broken keys or cracked cabinet. Should there be any damage, refer to paragraph 1.3.1 in Section 1.

If there is no damage, perform the operational check described in paragraph 2.2.2. Proceed with installation if the terminal is operating correctly. Should the terminal not operate correctly, first check that line voltage is present and the fuses are intact. Then remove the cabinet and make an internal inspection.

<u>Cabinet Removal</u>. To take off the top of the cabinet, remove the five screws (three on the front, two on the back) as shown in Figure 2-1 and Figure 2-2. Lift the cabinet top straight up. With the top portion of the cabinet removed, the internal assembly is easily reached.

Figure 2-2. Cabinet mounting screws (rear).

SECTION 2

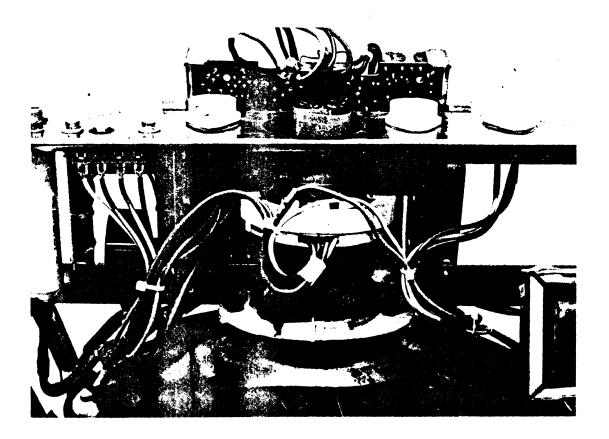

Internal Inspection. Inspect the entire terminal for physical damage. Especially check around the neck of the cathode ray tube (CRT) and the Monitor Deflection Card (see Figures 2-3 and 2-5). If there is damage, refer to paragraph 1.3.1 in Section 1.

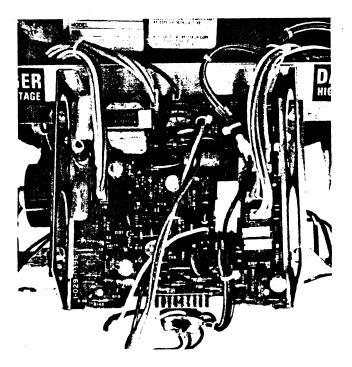

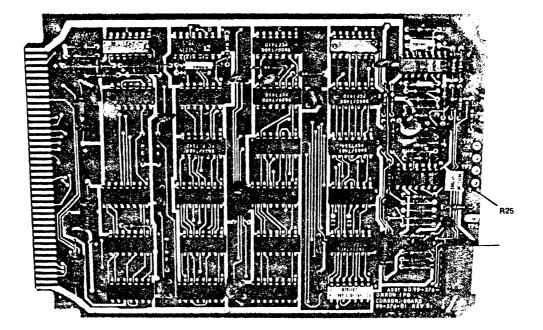

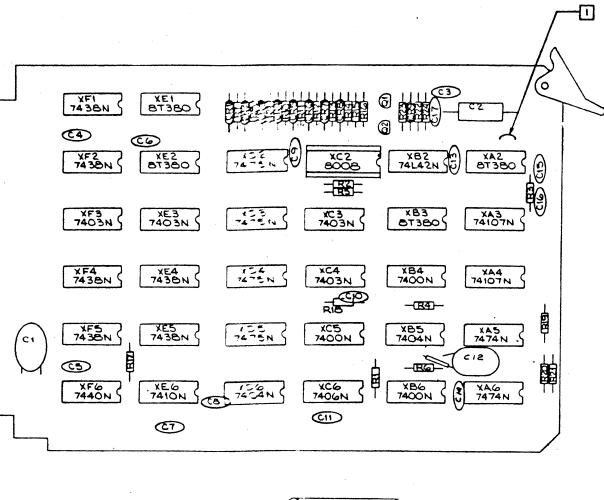

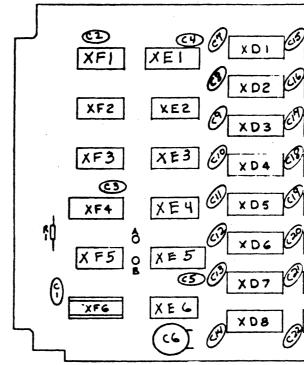

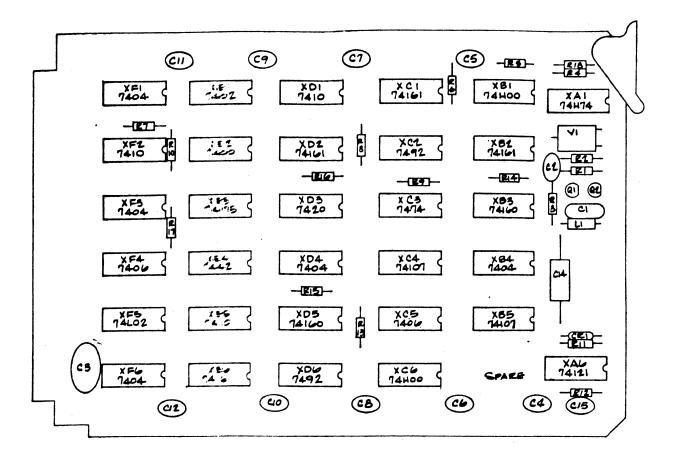

Make sure all circuit boards are properly seated and that the terminal has a full complement of cards, as shown in Figure 2-4. From left to right these are: Regulator Card, Cursor Control Card, Video Control Card, Refresh Buffer Card, Timing Control Card, Refresh Memory Card, Refresh Control Card, Processor Card, PROM Card, RS-232 Interface Card, Auxiliary Storage RS-232 Interface Card, Printer RS-232 Interface Card, and Terminator Card.

> CAUTION: MOS ELEMENTS USED ON CIRCUIT CARDS ARE EASILY DAMAGED BY STATIC DISCHARGE. ALWAYS HANDLE CARDS SO THAT ANY DISCHARGE WILL NOT FLOW THROUGH THE CARD. BEFORE TOUCHING A CARD, PLACE ONE HAND ON THE TERMINAL CHASSIS AND USE THE OTHER HAND FOR THE CARD.

Figure 2-3. CRT display high voltage circuits (mounted below Monitor Deflection Board.)

Figure 2-4. Printed circuit card locations.

Figure 2-5. Monitor Deflection Board connections (viewed from top of terminal).

SECTION 2

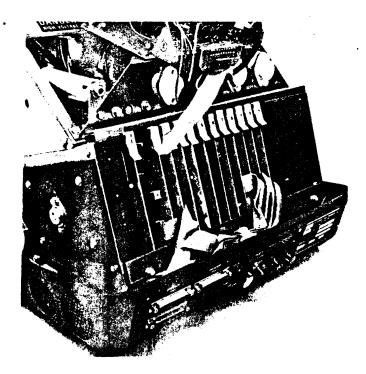

Figure 2-6 shows the correct routing of all flat-line interconnect cables in the terminal. Cable routing is as follows:

- 1) The cable on the far right (a 16-conductor flat-line) connects the Printer RS-232 Interface Card to J203, mounted on the rear panel of the terminal.

- 2) The second cable from the right (a 16-conductor flat-line) connects the Auxiliary Storage RS-232 Interface Card to J202, mounted on the rear panel of the terminal.

- 3) The next card, the Communications (Modem) RS-232 Interface Card, has two cables. A 14-conductor flat-line (top-connector) connects it to the Baud Rate Switch mounted on the rear panel of the terminal. A 16-conductor flat-line (just below the Baud Rate cable) connects the card to J201 mounted on the rear panel of the terminal.

- 4) The cable on the far left (a 16-conductor flat-line) connects the Cursor Control Card to the keyboard. This cable is routed along the right side of the terminal (viewed from front).

- 5) The cable running to the top of the photo (a 16-conductor flat-line) connects the Video Control Card to the Monitor Deflection Board.

- 6) The remaining cable (a 14-conductor flat-line) connects the Refresh Buffer Card to the keyboard indicator lights. This cable is routed along the right side of the terminal (viewed from front).

Figure 2-6. Flat cable connections.

SECTION 2

Figure 2-7 illustrates flat-line connector configurations. Each flat line connector is labeled with pin numbers on the back. Pin 1 should be inserted into pin 1 on the socket.

If all cards are properly installed, interconnect cabling is correct, and there is no visible damage, replace the cabinet top and the screws.

Figure 2-7. Flat-line connector configurations.

OMRON

### INSTALLATION AND CHECKOUT

2.2.2 Operational Check

The purpose of the operational check is to determine that the terminal is operational as a stand-alone unit. To perform this check, proceed as follows:

1) Make certain that the Baud Rate Switch on the rear of the terminal is in the correct position for your application.

2) Connect the power cord to the NEMA-approved three-contact grounding outlet that supplies 117 V ac  $\pm 10\%$ , 60 Hz, 1 Ø or the voltage specified on the identification label located on the bottom of the terminal. The outlet must provide at least 400 Watts of noise-free power. (If only a two-contact outlet is available, use a properly grounded two-wire-to-three-wire adapter or some other appropriate means to ensure chassis grounding).

3) Turn the terminal on with the On-Off Switch at the extreme upper left of the keyboard.

4) Listen for the sound of the cooling fans. If you cannot hear them, turn the terminal off and refer to paragraph 1.3.1. in Section 1.

5) Advance the Brightness Control (located to the immediate right of the On-Off Switch) all the way up. When the raster appears, reduce brightness until the raster disappears but characters are visible.

6) Allow the terminal to operate for a few minutes. Until the raster appears on the CRT, be alert to any abnormal sounds or odors. If you detect any, turn the terminal off and refer to paragraph 1.3.1 in Section 1.

7) Check out all keyboard functions (e.g., cursor and screen movements, edit functions, escape sequences, and alpha-numeric-symbol keys) for proper operation.