### **INDEX OF SECTIONS**

|   | 1. Introduction Pages 1 - 3                                                                          |

|---|------------------------------------------------------------------------------------------------------|

| כ | 2. Constructing the Memory Printed<br>Circuit Board Pages 4 - 6                                      |

| ] | 3. Performing Experiments 81 Through 83 Pages 7 - 27                                                 |

| ] | 4. Assembling the A1 and A2 Circuit Boards Pages 28 - 31                                             |

| ] | 5. Performing Experiments 84 Through 88 Pages 32 - 67                                                |

| ] | <ol> <li>Constructing the C1 Circuit Board and<br/>Performing Experiment 89 Pages 68 - 75</li> </ol> |

| ] | 7. Assembling the C3 Circuit Board and<br>Performing Experiment 90                                   |

### NATIONAL RADIO INSTITUTE, WASHINGTON, D.C. 20016

FP5C975

Γ

**1975 EDITION**

Litho in U.S.A.

# INSTRUCTIONS FOR PERFORMING EXPERIMENTS 81 THROUGH 90

At this point you have thoroughly studied most of the basic digital logic circuits that are used in practical digital systems. You have studied both sequential and combinational logic networks, particularly the most common ones used in computers and digital instruments. In this kit you will learn additional digital techniques and applications.

In the previous two kits you demonstrated digital logic fundamentals at the gate and functional circuit levels. It is easier to learn how different types of digital circuits operate when they are demonstrated individually. However, in this kit you will begin to combine these circuits to form larger circuits that perform some useful functions, involving arithmetic computations by digital techniques. These circuits will be more sophisticated than those you have worked with in the past. As a result you will be interconnecting more circuitry, using the experimental chassis and as many as five of the computer printed circuit boards at a time. There will be numerous interconnections to make and you should be extremely careful to make these properly. Complete and detailed instructions are given for each experiment in wiring these circuits. If you follow the directions carefully, you should have no trouble in getting the circuits to work.

Despite the seemingly complex nature of some of these experiments, they are typical of what you will encounter in industry. As a technician, you will be working with even more sophisticated equipment. In many cases the experimental circuits that you wire here are identical to typical breadboarding setups that you will make as a development technician.

The experiments in this kit are designed to teach you memory applications and arithmetic circuitry. In the first three experiments, you will build and use one type of digital memory. You will demonstrate read and write operations and use the memory to perform a wide variety of logic functions. The memory that you will build is known as the readonly-memory (ROM) that finds wide application in modern digital systems. The memory that you construct is a programmable read-only-memory that permits you to vary its function easily and demonstrate important concepts. After building this memory and demonstrating it in the experiments, you will test it thoroughly and use it as the main memory element in the digital computer that you will construct in the next kit.

Most of the remaining experiments cover arithmetic circuitry – logic circuits for performing addition, subtraction, and multiplication by digital methods. You will review basic binary arithmetic and construct circuits for performing these arithmetic operations. In addition, you will perform experiments covering BCD and other special arithmetic circuits.

The experiments in this kit will conclude your detailed study of digital circuitry. In the next kit you will construct the digital computer and use it to learn computer organization, operation, programming, and troubleshooting. In this kit as in the others, you will construct several of the printed circuit boards to be used in the computer. You will use some of these boards in performing the experiments. In each case, construct the PC boards carefully. Because of the large amount of circuitry involved in the digital computer, problems can occur due to poor construction techniques. This means paying particular attention to your soldering. As with your previous kits, check the contents against the photo in Fig. 1 and the related parts list. Be sure that you have all of the components so that you can proceed with the experiments without interruption. If you should be missing a part or some important piece of your kit, let the NRI Consultation Service know immediately.

12.2

Fig. 1. Some of the experimental parts for this training kit are shown above.

|       | Part   |                                    | Price |

|-------|--------|------------------------------------|-------|

| Quan. | No.    | Description                        | Each  |

| 31    | CN102  | .01 mfd, 50 volt disc cap.         | .38   |

| 1     | CN104  | .1 mfd disc cap.                   | .36   |

| 6     | CN112  | 100 mfd, 10 volt electrolytic cap. | .45   |

| 1     | CN143  | 500 pf disc cap.                   | .15   |

| 3     | CN 218 | .001 mfd disc cap.                 | .15   |

| 130   | CR 23  | 1N914 silicon diode                | .40   |

| 1     | EC32   | C1 printed circuit board           | 4.00  |

| 1     | EC34   | A1 printed circuit board           | 4.00  |

| 1     | EC35   | A2 printed circuit board           | 4.00  |

| 1     | EC36   | M3 printed circuit board           | 15.50 |

| 1     | EC37   | C3 printed circuit board           | 5.00  |

| 2     | HA80   | 10 ft. roll .032" solder           | .75   |

| 1     |        |                                    |       |

2

|            | Part        |                                 | Price        |

|------------|-------------|---------------------------------|--------------|

| Quan.      | No.         | Description                     | Each         |

| <u></u>    |             |                                 |              |

| 9          | 165         | 7400 integrated circuit         | 1.00         |

| 3          | 166         | 7420 integrated circuit         | 1.00         |

| 6          | 167         | 15844 integrated circuit        | 1.00         |

| 1          | IG9         | 7451 integrated circuit         | 1.00         |

| 2          | IG10        | 7442 integrated circuit         | 3.50         |

| 5          | IG12        | 7404 integrated circuit         | 1.00         |

| 2          | IG13        | 7440 integrated circuit         | 1.00         |

| ī          | IG14        | 74164 integrated circuit        | 3.75         |

| 1          | IG17        | 7480 integrated circuit         | 1.75         |

| 2          | IG18        | 7476 integrated circuit         | 2,00         |

| ī          | IG19        | 7453 integrated circuit         | 1.00         |

| i          | IG20        | 7460 integrated circuit         | 1.00         |

| ĩ          | IG21        | 7423 integrated circuit         | 1.50         |

| - 1        | IG25        | 74198 integrated circuit        | 7.80         |

| \$ 225     | LU9         | Tubular terminals               | 12/.25 - 4.2 |

| - 5        | NU1         | 6-32 hex nut                    | 12/.15       |

| / 18       | RE 30       | 1k-ohm, 1/2 watt resistor       | .15          |

| <u>·</u> 4 | RE 33       | 22k-ohm, 1/2 watt resistor      | .15          |

| . 5 3      | <b>RE58</b> | 2.2k-ohm, 1/2 watt resistor     | .15          |

| / / 1      | RE166       | 4.7k-ohm, 1/4 watt resistor     | .25          |

| 5 2        | RE167       | 470-ohm, 1/4 watt resistor      | .25          |

| ે 5        | SC5         | $6-32 \times 1''$ machine screw | 12/.15       |

| 31         | SO84        | 14-pin DIP socket               | .75          |

| 5          | SO86        | 16-pin DIP socket               | .75          |

| 1          | SO87        | 24-pin DIP socket               | 1.00         |

| 130        | SW68        | SPST slide switch, black        | .25          |

| 1          | SW70        | Push button switch, black       | .87          |

| 11         | SW71        | SPDT slide switch, white        | .30          |

| 1          | SW72        | SPDT slide switch, red          | .30          |

| 3          | TS21        | 2N5134 transistor               | .19          |

| 1          | TS22        | 2N5138 transistor               | .19          |

| 1          | WR 286      | 30 ft. #22 yellow wire          | .12          |

3

## Constructing the Memory Printed Circuit Board

Before you can proceed with the first three experiments in this kit, you will need to construct the memory printed circuit board. This is the large printed circuit board labeled EC36 that you received with this kit. Gather the following components in preparation for constructing this circuit board.

- 1 M3 circuit board (EC36)

- 4 14-pin integrated circuit sockets (SO84)

- 4 .01 mfd disc capacitors (CN102)

- 4 Type 15844 integrated circuits (IG7)

- 1 100 mfd, 10-volt electrolytic capacitor (CN112)

- 8 Ik-ohm, 1/2 watt 10% resistors (RE30)

- 28 Miniature tubular terminals (LU9)

- 128 1N914 diodes (CR23)

- 128 Single-pole, single-throw PC mounting slide switches (SW68)

- 5 6-32 × 1" machine screws

- 5 6-32 nuts Hookup wire Solder

The assembly of the circuit board is relatively simple. It is just a matter of installing the components in the proper locations and soldering them in place. The screening on the board designates the location of each of the components. By following the illustration, the board screening, and the instructions to follow, you should have no difficulty in constructing this board.

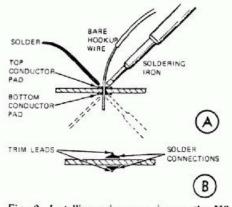

Install short wire jumpers in the J1

through J16 positions. A short piece of hookup wire is used to connect the copper pattern on the top of the board to another copper pattern on the bottom of the board at 16 different locations. This is done by passing a short piece of bare wire through the board and soldering it on both the top and the bottom sides. There are 16 individual positions. Simply strip the insulation from two pieces of hookup wire and push it through the hole from the top side of the board. Next, solder the wire to the conductor pad on the top side of the board, then solder the wire to the pad on the bottom side of the board. Finally, trim off the leads on both the top and bottom sides of the board.

Fig. 2 shows the proper procedure for doing this. Be careful not to use too much heat. Remember that the connection is so short that when you apply heat to solder the top connection, this will also melt the solder on the bottom connection.

Fig. 2. Installing a jumper wire on the M3 circuit board. (A) soldering the jumper, and (B) the completed connection.

Install the 28 miniature tubular terminals in the peripheral holes provided on the left and bottom sides of the EC36 PC board. Insert the terminals from the top and crimp each tightly on the bottom to hold the terminal firmly in place. Solder all terminals on both the top and the bottom of the board.

Install a 100 mfd, 10-volt electrolytic capacitor between terminals G1 and +5B. Wrap the leads of the capacitor around these terminals neatly near the bottom, trimming off the excess. Solder both connections. Be sure to observe the polarity indicated by the screening on the top of the board.

Install four .01 mfd disc capacitors in the four locations designated to the right of the IC socket holes. Insert the capacitors from the top and mount them so that they are flush with the board. Solder both leads of each capacitor on the bottom of the board to hold them in position. Also in those locations provided, solder the capacitor leads on top of the board as well. As with the other circuit boards, these capacitor leads are used to carry power and ground connections from the top to the bottom of the board, making it very important for these capacitor leads to be soldered on both top and bottom. Double check your work here before you go on and clip off any excess lead lengths.

Install eight 1k-ohm, 1/2-watt resistors in the eight locations shown on the top of the EC36 circuit board. Bend the resistor leads at right angles as close to the body as possible. Insert each resistor from the top and push it down so that it is mounted flush with the PC board. Bend the leads slightly on the back and solder each of the leads. One lead of each resistor must also be soldered on the top of the board. Solder these connections carefully, then clip off any excess leac lengths.

Install four 14-pin DIP IC sockets ir the locations designated by the screening on the circuit board. Insert the sockets from the top so that the notches are pointing to the left as indicated. Be sure that the sockets are flush with the top of the board, then using the thin solder supplied, solder the 14 pins on each socket.

You are now ready to install 128 1N914 diodes. The diode symbols are screened on top of the board with the correct polarity; however, you will mount the diodes on the bottom of the printed circuit board. As you mount each diode, be absolutely certain that you install it with the correct polarity. Remember that the black band around the end of each diode designates the cathode. In all cases, the cathode should be toward the top of the board.

Bend the leads of the diode at right angles very near to the body and insert the diode from the bottom of the board in the holes provided. These holes are marked with the diode symbol on top of the board. Bend the leads slightly on the top of the board to hold the diode flush with the board as you solder it. Solder each diode on both the bottom and the top of the board, but do not use too much heat because the diodes are very sensitive. Apply just enough heat to make a good solder connection, using the thin solder provided with this kit. Clip off the excess lead lengths. Install each diode this way. Once they are installed, scan all 128 diodes on the bottom of the board to be sure that all of the cathode ends are in the same direction, upward, Double check to be sure that all the leads are soldered on both the top and the bottom. Now be extremely careful when you lay the board

back down on your workbench. The diodes are made of glass and can be cracked. Therefore, from this point on the memory should be treated carefully so that no diodes on the bottom of the board will be damaged.

To prevent diode damage, install a one-inch long 6-32 screw and nut in each of the four corner holes of the PC board. Also install a one-inch screw and nut in the center hole. Insert the screw head from the top and tighten the nut on the bottom. This provides one-inch legs that will hold the memory board off the bench to prevent damage to the diodes.

Next install all of the 128 black slide switches on the top side of the PC board, beginning with the 16 switches across the top of the circuit board. Be sure to install them correctly so that the body of each switch fits within the areas screened on the PC board. Solder all of the switch terminals which protrude on the bottom side of the board. Since each switch has two terminals, a total of 256 solder connections must be made on the bottom side of the board. Be certain each switch rests squarely on the board before soldering.

Now install the four 15844 IC's at positions IC35, IC36, IC37 and IC38. Be sure that the IC and socket notches are properly aligned. Notice that all of the notches must point to the left.

The assembly of your M3 board is complete. You may now proceed with the first experiment in this kit to demonstrate the operation of this board.

# Performing Experiments 81 Through 83

### **EXPERIMENT 81**

Purpose: To demonstrate the operation of a programmable switch-diode matrix read-only-memory.

Introductory Discussion: Most digital computers today use magnetic core memories. These memories are extremely reliable, versatile, and can achieve the high speed necessary for fast computations. However, their complexity and high cost prevent us from demonstrating such a memory here. For that reason, we use a simpler, less expensive form of memory to help you in demonstrating memory concepts.

One of the simplest means of representing binary data is by using a switch. The switch has two positions, off and on, which we can assign to the binary 0 and binary 1 states. By providing a group of switches, complete binary words can be represented. This is exactly what we do in the memory board you have just constructed. This memory contains sixteen 8-bit words of binary data. A slide switch is used for each bit of the data word. There is a diode associated with each switch. The diode and switches are connected to form a large matrix. The diodes in series with the switches prevent the switches from interferring with one another. These switches are connected to the integrated circuits in groups, that are used to buffer the 8-bit parallel output word. The separate drawing (insert sheet) shows the detailed circuit of the M3 circuit board.

In this experiment you are going to demonstrate the switch memory you have just constructed. You will study its theory of operation so that you will thoroughly understand its use.

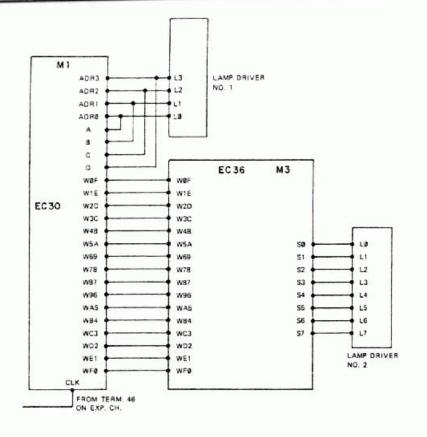

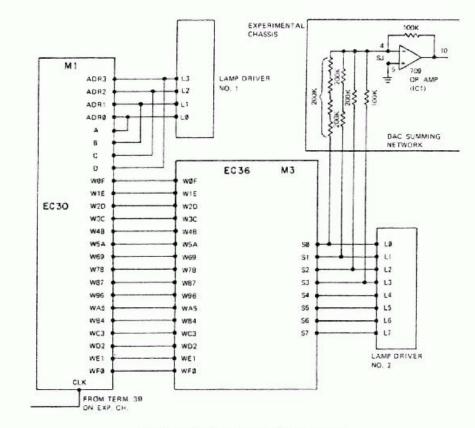

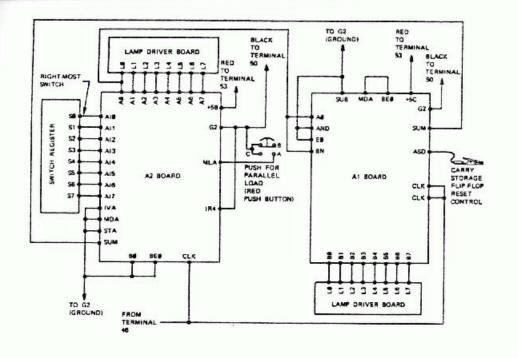

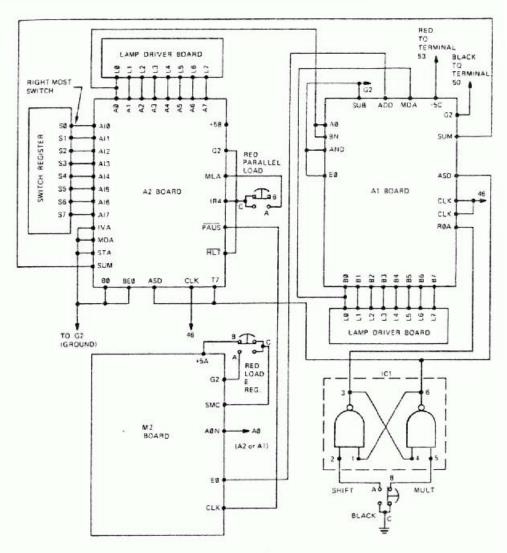

Experimental Procedure: The experimental circuit for this experiment is shown in Fig. 81-1. Before you begin wiring your circuit, you must partially disassemble the ADC circuit that is wired on your experimental chassis. First disconnect the resistive summing network from the MI board, but do not unsolder the individual 100k-ohm and 200k-ohm resistors in the network. Also remove the wire going from this network to terminal IC14 on the experimental chassis PC board. Set the resistive network with its attached wire aside for later use. Leave the four yellow wires on terminals A, B, C and D of the M1 board connected to the lamp driver board. Disconnect the jumper between JA and KA, and remove the wire between KA and terminal IC1-10. Also, remove the yellow lamp driver lead from terminal IC1-10. Leave the other end connected to the lamp driver board.

Next remove the .001 mfd capacitor between terminals G1 and CLR on the M1 board. Then remove the 4.7k-ohm resistor between the +5A and CLR terminals; also remove the red push button switch with its attached wires simply by removing the yellow' and black switch leads from the CLR and G1 terminals. Set aside the switch with its attached leads for later use.

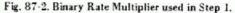

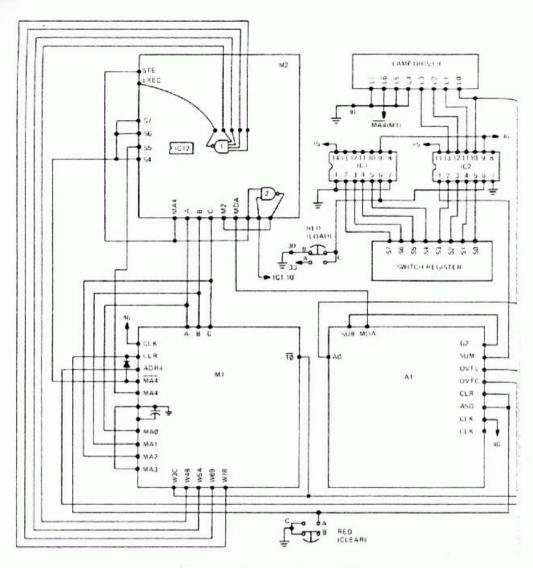

Fig. 81-1. Circuit for Experiment 81.

You will make one additional change on the experimental chassis PC board. Move the M1 clock wire from terminal 39 to terminal 46. This will apply the output of the buffered latch circuit to the CLK input on the M1 board.

Now you are ready to wire the experimental circuit shown in Fig. 81-1. In addition to the M1 board and lamp driver board which are now connected to the experimental chassis, you will need the M3 circuit board and the other lamp driver board. Wire them as shown in Fig. 81-1, using the yellow hookup wire.

You must provide power to the M3

board with an 18-inch piece of red hookup wire and an 18-inch piece of black hookup wire. Connect the red wire between terminal +5A on the M3 board and terminal 43 on the experimental chassis. Connect the black wire between terminal G2 on the M3 board and terminal 40 on the experimental chassis. Also connect the red and black power leads coming from the second lamp driver board to terminals 43 and 40 respectively on the experimental chassis.

Check all of your wiring to be sure that it is exactly as shown in Fig. 81-1. Also make certain that a 7400 IC is not installed at the IC8 position on the M1 board. You are now ready to perform the experiment.

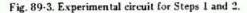

### Step 1: To demonstrate basic memory operation.

The memory storage locations on the printed circuit board are organized into 8-bit word locations. These are numbered in hexadecimal,  $\emptyset$  through 9 and A through F down the center of the board, with switches  $\emptyset$  through 7 on the left and switches 8 through F on the right, reading from top to bottom. These designations are the addresses or locations of each memory word. Since there are a total of sixteen words, we can address these with a 4-bit address word. We feed a 4-bit address word to the memory, then that particular memory location is read out.

Turn on the experimental chassis. Depress the black push button and step the binary counter on the M1 circuit board until lamps I3 through IØ on the lamp driver board connected to lines A. B, C and D read 0000. Lamps I7 through I4 should be on at this time, but you can disregard them since they are not used here. You may disable these lamps if you wish by grounding L4 though L7 or by removing the bulbs. For the moment, you can also disregard the light pattern on the other lamp driver printed circuit board. Switch all eight switches in memory word Ø to the down position, noting the state of the lights on the light driver PC board that is connected to the SØ through S7 output terminals. Then switch the eight memory switches in word Ø to the up position one at a time, making note of the results on the indicator lamps as you do so.

Connect the ground clip of your twom to one of the 1-inch screw legs on the memory PC board. This will permit yot to pick up the common ground at a convenient location. Set the twom fo reading positive voltage on the +12 vol scale. Now touch the probe to the sixteer lines labeled WØF through WFØ one at a time. Mentally note the voltage at each of these sixteen pins.

Discussion of Step 1: Refer to the separate logic diagram of the MI circuit board. In this experiment you are using the 4-bit binary counter on the M1 circuit board to provide an address for the switch memory. We take the 4-bit word from the binary counter and feed it directly to the memory address register. The strobing of the 4-bit address (by signal TØ) into the memory address register (7475) has been disabled because IC8 on the M1 circuit board has been removed. This means that the 4-bit address directly from the counter is applied through the memory address register flip-flops to the two 7442 decoders. These two decoders look at the 4-bit address, decode it, and generate a signal to enable one of the sixteen memory words.

In the first part of the experiment when you set the counter to the 0000 position, the decoder output selected word  $\emptyset$  in the memory. This is identified by the W $\emptyset$ F line on the M3 circuit board. The decoder enables *only* this word.

With all eight switches of memory word  $\emptyset$  in the down position, the eight lamps on the light driver board should have been off, indicating binary 0's. With all of the switches in the up position all of the lamps should have been on, indicating binary 1's. The lamps should have turned on as you set the switches from the down (0) to the up (1) position one at a time. This indicates that on the memory printed circuit board a switch in the down position is a binary 0 and a switch in the up position is a binary 1. The logical output signals from the memory correspond to the switch indication as you observed on the lamp driver lamps.

By switching the individual switches off and on you should have found that the lamp corresponding to that bit position in the word changed as you switched between the binary 0 and binary 1 positions.

Next you used your toom to measure the voltage at the sixteen address lines coming from the M1 circuit board. You should have found all of the lines at the binary 1 voltage level (between +4 and +5 volts) except for one, the WØF line. The WØF line should be in the binary 0 state (near zero volts). The decoder on the M1 circuit board selects one of the sixteen words, the selected line being a binary 0 while all others are at the binary 1 indication. You can always determine which word on the memory printed circuit board has been enabled by looking at the voltage on the address input lines. The line that is in the binary 0 position is enabled.

To understand how the switch memory works, refer to the memory printed circuit board logic diagram on the separate insert sheet. Notice the large diode-switch matrix. Each bit position consists of a switch and a diode connected in series to one of the 128 points formed by the 8 by 16 matrix. Eight lines feed the input node

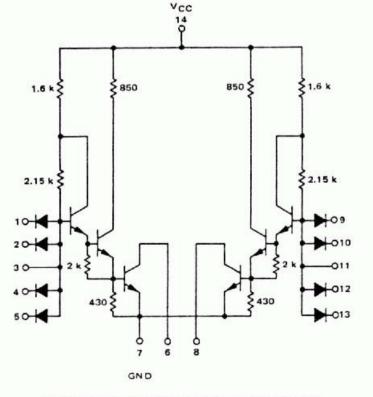

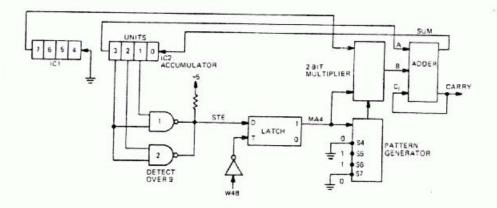

Fig. 81-2. Circuit of 15844 (or 944) IC used in the memory.

connections to the 15844 IC NAND gates used. The circuitry in each NAND gate is shown in Fig. 81-2. This is a DTL NAND gate. There are two 4-input gates with an open collector output in each IC. We are using external 1k-ohm load resistors for these NAND gates on the memory printed circuit board, but we are not using the input diodes on the NAND gate. These are connected together and enabled by a +5 volt line on the memory circuit board, as you can see in the illustration. However, we are using the node input, which is pins 3 and 11 respectively. As you can see in Fig. 81-2, the diodes in the matrix are connected to the gate node and are used to enable the gates, depending upon how the switches are set.

To fully understand how the memory works, recall the method of operation of the NAND gate. If any one of the diode inputs to the NAND gate is brought to ground (or made a binary 0), the output of the NAND gate goes high. If all of the diode inputs to the NAND gate are open or at the binary 1 level, the NAND gate output will be a binary 0.

Now refer to the memory board diagram. When the WØF address input line goes low, it will bring the cathode side of the diodes connected to it to ground, forcing the output of the corresponding NAND gate to be high if the switch in series with the diode is closed. Consider the NAND gate associated with output SØ in the diagram. Notice the diode connected to the switch attached to pin 11, the node of the NAND gate. The cathode of the diode is connected to the WØF input. If this switch is closed and WØF is grounded indicating that word  $\emptyset$  is addressed, the SØ output will be a binary 1. However, opening the switch will simply leave the node open and the NAND gate will have all of its normal

diode inputs enabled. This will cause th  $S\emptyset$  output to go low. As you can see, wit the switch closed the NAND gate output is forced high and a binary 1 is produced. With the switch open, a binary 0 i produced. This same action occurs or each of the eight bit positions for the word  $\emptyset$  in the memory.

As you refer to the memory logidiagram, keep in mind that all othe address input lines at this time are at the binary 1 level. For that reason none o the other switches in the memory affec the state of the output. If the switches should be open they will have no effect on the circuit. If the switch happens to be closed, it will also have no effect since all of the other address lines are at a binary 1 level at this time. These conditions clearly enable the NAND gates in such a way as to permit only the diodes and switches in the addressed word to control the state of the output.

### Step 2: To check the condition of all bits in every memory word.

In this step you are going to verify the operation of every memory word. You will address each memory word in sequence and test all bit switches to be sure that they are functioning properly. You have already tested memory location  $\emptyset$  by first setting the address to the 0000 state. You stepped the counter by depressing the black push button until the desired address was obtained. You placed all eight switches in the down position, then in the up position, and observed the outputs on the indicator lights. You will now test the remaining fifteen words in memory this same way.

Depress the black push button once to step the address counter to the 0001 position. You have addressed the memory location number 1. Place all of the memory word 1 switches in the down position and observe the indicator lights. Now put all of them in the binary 1 position one at a time, noting that they should go on as they are switched to the up position.

Using the black push button, step the address to the 0010 position, repeating this test on memory location 2. First put all of the switches in the down position and observe the lights. Then place them in the up position and continue to watch the lights. Repeat this for all of the remaining memory word locations through address 1111 or hex F.

Discussion of Step 2: You sequenced through each of the memory locations and repeatedly wrote all 0's and all 1's into all eight bit positions of the memory location. You should have found that with all the switches down, that all of the eight indicator lamps are off. With the eight switches in the up position, the indicator lamps should be on. All memory locations should have given you exactly the same result. If you should find a lamp that did not respond properly to the memory switch in question, it is possible that you have a defective switch or diode.

If you should have trouble, follow this procedure. First check your solder connections for that particular switch and diode, by simply touching the hot soldering iron to the diode and switching terminals one at a time to let the solder remelt again and flow over the connections. Then retest the switch. Sometimes the switches themselves will have dirty contacts. This can often be cleared up by turning the switch off and on rapidly several times to clean off the dirt. If you should find a defective or intermittent switch, replace it with one of the extras we supplied you in this kit. With the experimental chassis power off, you can use your toom in the ohmmeter mode to test each diode with a forward and reverse resistance test. Replace any defective diodes or reverse any that may have been installed backwards on the board.

Step 3: To become familiar with the memory switch positions and the method for writing data into the memory locations.

Step the counter to the 1011 position with the black push button. Then go to the appropriate memory location and set the switches from left to right according to the following pattern, 11001100. Observe the indicator lights. Treating this as a binary number, convert it into its decimal equivalent. Write your result in the margin of the text.

While you are observing the indicator lamps, try switching any of the other memory switches in locations other than 1011 and notice the effect on the indicator lamps.

Discussion of Step 3: The purpose of this particular step is to help you become familiar with the locations of the various memory word locations on the printed circuit board and how they correspond to the 4-bit input address. By setting the counter to the 1011 position, you addressed memory location B. This is the fourth group of eight switches down from the top on the right-hand side of the memory printed circuit board. You then set the bit pattern 11001100 from left to right at this memory location. The lamps should display the same bit pattern as the addressed switches. By interpreting this bit pattern as a binary number with the right-hand switch position and lamp  $I\emptyset$  representing the LSB position, you should have been able to convert this binary number into its decimal equivalent of 204. In using the memory in the future, you will use this arrangement. The right-hand bit position in a word is the least significant bit while the left-most bit is the most significant bit. In some of the experiments that follow, the left-most bit will be the sign bit of a signed binary number while bit 6 will be the most significant bit of the number.

Instructions for Statement 81: For this statement you are going to demonstrate what happens when two of the memory words are addressed simultaneously. Solder a short piece of black hookup wire between terminals W78 and G2 on the M3 board. Then step the black push button so that you address memory location 0000. By connecting the piece of black hookup wire to ground, you have also addressed word 7 in the memory.

In word location  $\emptyset$  set the following bit pattern into the switches: 0011 0011. Set the pattern 0101 0101 from left to right in memory location 7. Observe the eight outputs on the lamp driver board and record your results in Fig. 81-3. Carefully study the words stored in memory locations  $\emptyset$  and 7 and the result obtained at the output, then answer the statement question.

| MEM LOC Ø | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

|-----------|---|---|---|---|---|---|---|---|

| MEM LOC 7 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| MEM OUT   |   |   |   |   |   |   |   |   |

Fig. 81-3. Record your results for Statement 81 in this table. After you answer the statement ques tion, turn off the experimental chassi and remove the wire between terminal-W78 and G2 on the memory board However, leave the remaining circuits connected as they are used for your next experiment.

Statement No. 81: The binary number that I observed on the output lamps was:

| (1) | 1110 | 1110 |

|-----|------|------|

| (2) | 0111 | 0111 |

| (3) | 1100 | 1100 |

which indicates that both memory words are being read out simultaneously since they have been effectively:

ANDed

added

subtracted

ORed

to produce the result.

### **EXPERIMENT 82**

Purpose: To demonstrate a readonly-memory and to show several useful applications.

Introductory Discussion: A readonly-memory (ROM) is a special type of memory for storing fixed binary data. In other words, data is permanently written into each storage location. Once this is done, only read-out operations can be performed. Each word stored in the memory can be addressed either randomly or sequentially. As it is addressed, the data is read out of the memory.

In this experiment you are going to demonstrate several useful applications of the ROM. The memory printed circuit board that you constructed earlier in this kit is a form of ROM. It is not a true ROM in the sense that data is permanently stored in it; it can only perform the read function. Data cannot be written into the memory under logic control, but the contents of the memory can be programmed by setting the switches to the desired bit pattern. For that reason the memory is best called a *programmable* read-only-memory. By being able to program the contents of the memory, we can illustrate many ROM applications.

Experimental Procedure: The test setup that you used in the previous experiment will be used in this experiment also. However, you will need to make a few modifications to the circuit.

First, remove the wire coming from the clock input on the M1 circuit board from terminal 46 on the experimental chassis. Solder it to terminal 39. This will permit the clock oscillator on the experimental chassis to step the binary counter.

Now you must remove some of the wiring on your experimental chassis. First remove the 1N914 diode and the 2N5134 transistor that are connected between terminals IC1-4 and IC1-10 on the experimental chassis PC board. Also remove the 220k-ohm resistor between terminal IC1-4 and terminal 16 on the 1k-ohm potentiometer, the wire between terminal 15 on the 1k-ohm potentiometer and terminal 9, and the wire between terminal 17 on the 1k-ohm potentiometer and terminal 14.

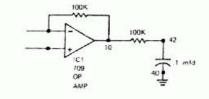

Connect a 100k-ohm resistor between terminals IC1-4 and IC1-10. Then connect the DAC resistive summing network to terminals  $S\emptyset$ , S1, S2 and S3 on the M3 circuit board, referring to Fig. 82-1 as you make these connections. Connect the wire coming from the resistive network to terminal IC1-4.

Check all of your wiring against Fig. 82-1. Notice that you have converted the ADC circuit that was wired on the experimental chassis into a DAC circuit, identical to the one you used in an earlier experiment. The 709 IC at position IC1 is used in conjunction with the 100k-ohm feedback resistor and the summing resistors to form the DAC circuit. Although not shown in Fig. 82-1, a wire should be connected between terminals 9 and IC1-6 and between terminals 13 and IC1-11. These two connections provide power to the IC. The rest of the experimental circuit is identical to the circuit used in your last experiment.

### Step 1: To demonstrate a hybrid function generator.

Fig. 82-2 is a table showing the contents of each memory location for this step. Using the table as a guide, set the switches in all sixteen memory words to those specified in the table. Place the switches up for binary 1's and down for binary 0's. In order to obtain the proper results from this experiment, the memory words should be exactly as shown in the table. Therefore, it is a good idea to go back once you have programmed the memory to double check it. Notice that the four left-hand or most significant bits of each memory word are 0's for all portions of the step.

Turn on the experimental chassis. Connect the vertical input of your oscilloscope to terminal IC1-10, and connect the ground clip of the oscilloscope to the experimental chassis (ground). Adjust the vertical and horizontal controls to display at least one or preferably two cycles of the DAC output waveform on the screen.

Fig. 82-1. Circuit for Step 1, Experiment 82.

| MEM. LOC. | CONTENTS | MEM. LOC. | CONTENTS   |

|-----------|----------|-----------|------------|

| 0         | 00000111 | 8         | 00000111   |

| 1         | 00000100 | 9         | 00001010   |

| 2         | 00000010 | A         | 00001100   |

| 3         | 00000001 | В         | 00001101   |

| 4         | 00000000 | C         | 00001110   |

| 5         | 00000001 | D         | 00001101   |

| 6         | 00000010 | E         | - 00001100 |

| 7         | 00000100 | F         | 00001010   |

Fig. 82-2. Memory contents for Step 1.

Adjust the controls to stabilize the waveform and then sketch the waveform on a separate sheet of paper.

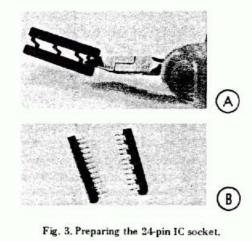

Next, solder a 100k-ohm resistor between terminal IC1-10 and terminal 42 on the 4-lug terminal strip on the experimental chassis PC board. Solder a .1 mfd capacitor between terminals 40 and 42. Your circuit should appear as shown in Fig.82-3. Leave the ground clip of your oscilloscope on the experimental chassis, but move the vertical input lead to terminal 42. There is no need to turn off the experimental chassis while adding these components.

Fig. 82-3. Experimental circuit for addition in Step 1.

Observe the waveform at terminal 42. Readjust the vertical gain control and other controls as necessary to stabilize the waveform. Again note the waveform shape and copy it on a separate sheet of paper beneath the waveform you just copied. Turn off the experimental chassis.

Discussion of Step 1: In this step you are using the four least significant output bits of the programmable read-onlymemory to drive the resistor summing network of the digital-to-analog converter that you constructed in previous kits. The DAC will accept the words stored in memory and generate an output voltage proportional to the binary word value. We are using the binary counter stepped by the high speed clock circuit to sequentially address all sixteen memory locations. As the counter steps through its sixteen states, 0000 through 1111, the contents of each of the memory locations in sequence will be fed to the DAC. As the clock pulses step the counter, the counter will continually recycle from 1111 to 0000, repetitively transferring the memory contents in sequence to the DAC.

The output waveform produced by the DAC will be a function of the contents of each memory location. Since the memory is fully programmable, virtually any waveform can be generated. Because the DAC has only four input bits, we can use a maximum of four bit memory words and specify the magnitude in any sequence we desire.

In this experiment you stored a sequence of binary words in the memory like that shown in Fig. 82-2. This sequence of words closely approximates a sine curve. Therefore, the output waveform that you should have observed at the DAC output at terminal IC1-10 should closely approximate a sine wave. Naturally it is not smooth and perfect because of the stepped or discrete level nature of the DAC. However, for many practical applications such a simulated sine wave would produce a result just as good as that of a pure sine wave.

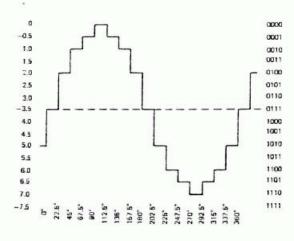

Fig. 82-4 shows the waveform that you should have observed. As you know, the DAC output voltage swings from a minimum of 0 volts to a maximum of -7.5 volts. The sine wave is set up to swing between 0 volts and 7 volts. Therefore, this is a peak-to-peak waveform of 7 volts. It is equivalent to a sine wave riding or superimposed upon a -3.5 volt dc level. The sine wave swings above and below this value.

If you will notice the waveform of Fig.

82-4, one cycle of the sine wave is split into sixteen time increments. Since there is a total of  $360^{\circ}$  for each sine wave cycle, each increment represents 360/16= 22.5°. To generate this waveform, we program the memory with sixteen sequential words of data that are representative of the value of the sine of the angles 0° through  $360^{\circ}$  in 22.5° steps. Using these values of the sine, we scale the value to match the capabilities of the DAC circuit. As you can see, the results closely approximate the sine wave.

At the output of the DAC op amp you next connected a resistor/capacitor combination and observed the output voltage across the capacitor. This R-C network forms a low pass filter which will reject all of the high frequency components in the step waveform appearing at the op amp output. For that reason the output

Fig. 82-5. Output of low pass filter on the DAC.

of the low pass filter at terminal 42 should be very nearly equal to a smooth sine wave. For those applications which require a more nearly perfect sine wave, filters such as this can be easily added. The waveform that you should have observed at terminal 42 is shown in Fig. 82-5.

Step 2: To show how an ROM can be used to perform binary multiplication by using table look-up techniques.

Remove the wires connecting terminals A, B, C and D to terminals  $ADR\emptyset$ , ADR1, ADR2, and ADR3 on the M1 circuit board. Next, connect the four least significant bit positions of your switch register to the  $ADR\emptyset$  through ADR3 lines. Connect the right-hand or LSB switch to the  $ADR\emptyset$  terminal, etc. This will permit you to use these switches as the input to the read-only-memory rather than the binary counter on the M1 circuit board. Don't forget to connect the black and red wires from the switch register to ground and +5 volts on the experimental chassis before proceeding. Connect the

| LOC | HEX CONTENTS |

|-----|--------------|

| 0   | 00           |

| 1   | 00           |

| 2   | 00           |

| 3   | 00           |

| 4   | 00           |

| 5   | 01           |

| 6   | 02           |

| 7   | 03           |

| 8   | 00           |

| 9   | 02           |

| A   | 04           |

| В   | 06           |

| С   | 00           |

| D   | 03           |

| E   | 06           |

| F   | 09           |

Fig. 82-6. ROM contents for Step 2 in hexadecimal form.

MULTIPLIER

red lead to terminal 33 and the black lead to terminal 30.

In this step you are going to demonstrate the multiplication of binary numbers. You will use two 2-bit numbers, both of which will be represented by the four switches in the switch register that you just connected. The two right-most switches will represent the multiplicand and the two switches to the left will represent the multiplier. With 2-bit numbers there will be a total of four decimal numbers that can be represented, 0, 1, 2 and 3. For this step you will multiply these numbers by themselves in all possible combinations. To do this you will need to set the switch register switches to the various combinations of input numbers. You will then record the output on the lamp driver.

To begin the experiment, set the

PRODUCT

memory switches as shown in the table of Fig. 82-6, which shows the memory location or address in hexadecimal notation. Notice also that the contents of the memory are expressed in hexadecimal format. All of the programming of the memory that you will do from now on will be presented to you in hexadecimal form to simplify the programming. Since each word in the memory contains eight bits, it can hold two hexadecimal digits. As you recall, hexadecimal digits are those sixteen states represented by all possible combinations of a 4-bit number. For each hex digit in the table of Fig. 82-6, you will store in memory the binary equivalent in each 4-bit section of the word. For example, for memory location A the contents in hex is 04; therefore, you will store the following binary word in memory: 0000 0100.

Once you have programmed the memory according to Fig. 82-6, turn on the experimental chassis. Refer to the table in Fig. 82-7. This table shows you all possible combinations of the multiplier and multiplicand inputs that can occur with two 2-bit binary numbers. Set the switch register switches to the positions indicated for the multiplier and multiplicand. Record the 4-bit product in the space provided. You will monitor the product on the four right-hand lamps on the lamp driver No. 2 board. Once you have filled in the table, convert all of your binary numbers into their decimal equivalent. Then turn off the experimental chassis.

Discussion of Step 2: Figs. 82-8 and 82-9 show the results you should have obtained in this step. If you entered the

|   | MULTIPLIER | MULTIPLICAND | PRODUCT |

|---|------------|--------------|---------|

| [ | 00         | 00           | 0000    |

|   | 00         | 01           | 0000    |

| 1 | 00         | 10           | 0000    |

|   | 00         | 11           | 0000    |

|   | 01         | 00           | 0000    |

|   | 01         | 01           | 0001    |

|   | 01         | 10           | 0010    |

| 1 | 01         | 11           | 0011    |

| 1 | 10         | 00           | 0000    |

|   | 10         | 01           | 0010    |

|   | 10         | 10           | 0100    |

| 1 | 10         | 11           | 0110    |

| 1 | 11         | 00           | 0000    |

| 1 | 11         | 01           | 0011    |

|   | 11         | 10           | 0110    |

|   | 11         | 11           | 1001    |

Fig. 82-8. Correct results for Step 2.

| 00 | 00 |  |

|----|----|--|

| 00 | 01 |  |

| 00 | 10 |  |

| 00 | 11 |  |

| 01 | 00 |  |

| 01 | 01 |  |

| 01 | 10 |  |

| 01 | 11 |  |

| 10 | 00 |  |

| 10 | 01 |  |

| 10 | 10 |  |

| 10 | 11 |  |

| 11 | 00 |  |

| 11 | 01 |  |

| 11 | 10 |  |

| 11 | 11 |  |

MULTIPLICAND

Fig. 82-7. Table for Step 2.

| MULTIPLIER | MULTIPLICAND | PRODUCT |

|------------|--------------|---------|

| 0          | 0            | 0       |

| 0          | 1            | 0       |

| 0          | 2            | 0       |

| 0          | 3            | 0       |

| 1          | 0            | 0       |

| 1          | 1            | 1       |

| 1          | 2            | 2       |

| 1          | 3            | 3       |

| 2          | 0            | 0       |

| 2          | 1            | 2       |

| 2          | 2            | 4       |

| 2          | 3            | 6       |

| 3          | 0            | 0       |

| 3          | 1            | 3       |

| 3          | 2            | 6       |

| 3          | 3            | 9       |

Fig. 82-9. Correct results for Step 2.

multiplier and multiplicand properly in the switch register and programmed the memory correctly, then for each of the two input numbers you should have obtained a product output displayed on the lamp driver.

The key to the operation of this multiplier is in how the memory has been programmed. If you will look carefully at Fig. 82-8 yoù will see that the 2-bit multiplier and multiplicand numbers, when combined, form a 4-bit binary number. These binary numbers are used to address a particular word in memory. The addressed memory location contains the product of the two numbers that constitute the address.

Instructions for Statement 82: For this statement you will need to make a few changes in your experimental setup. First, completely disconnect the switch register from the circuit and set it aside for later use. Reconnect the four wires between lines A, B, C and D and ADR $\emptyset$  through ADR3 on the M1 board as shown in Fig. 82-1. The lamp driver No. 1 lines should still be connected. In addition, move the wire from the CLK input on the M1 circuit board from terminal 39 back to terminal 46. This will permit you to step the counter with the black push button switch as you have done previously.

For this statement you are going to apply the decimal numbers 0 through 15 in binary form to the read-only-memory. These numbers, of course, will come from the binary counter on the M1 circuit board. Turn on the experimental chassis and step the counter with the black push button until the lamp driver reads 0000.

Now program the ROM according to the table in Fig. 82-10. Again the memory location or address and the

| LOC | CONTENTS (HEX) |

|-----|----------------|

| 0   | 00             |

| 1   | 40             |

| 2   | 5A             |

| 3   | 6E             |

| 4   | 80             |

| 5   | 8F             |

| 6   | 90             |

| 7   | A9             |

| 8   | B5             |

| 9   | co             |

| А   | CA             |

| В   | D4             |

| С   | DD             |

| D   | E6             |

| E   | EE             |

| F   | F7             |

Fig. 82-10. ROM program for Statement 82.

contents are given in hexadecimal notation. Be very careful in programming the memory to be sure that the switches are positively set to the up or down position as required by the program.

Next step the binary counter, using the black push button switch for each of the numbers 0 through 15, and record the output displayed by lamp driver No. 2 in the second column of Fig. 82-11.

To interpret the output data that you obtain from the ROM, you will assume that the 8-bit number stored in these memory locations consists of two whole number bits and six fractional bits. In other words, the binary point for the number will be placed between the second and third bit positions from the left. By referring to Fig. 82-11, you can see that the output you should record for a zero input is a string of zero's. However, note the position of the binary point. The

| INPUT  | OUTPUT (BINARY) | OUTPUT (DECIMAL) |

|--------|-----------------|------------------|

| 0      | 00.000000       | 0                |

| 1      |                 | _                |

| 2      |                 |                  |

| 2<br>3 | 1               |                  |

| 4      |                 |                  |

| 5      |                 |                  |

| 6      |                 |                  |

| 7      |                 |                  |

| 8      |                 |                  |

| 9      |                 |                  |

| 10     |                 |                  |

| 11     |                 |                  |

| 12     |                 |                  |

| 13     |                 |                  |

| 14     |                 |                  |

| 15     |                 |                  |

Fig. 82-11. Table for Statement 82.

numbers that you will record in here will have both integer and fractional parts.

After you have recorded all sixteen 8-bit output states, use you knowledge of the conversion of binary numbers to their decimal form and fill in the column provided in Fig. 82-11 with the decimal equivalent. When you have done this, study the decimal output equivalents and compare them to the decimal input number. By observing both the input and output numbers, you should be able to determine the relationship between them.

After you answer the statement question, turn off the experimental chassis. However, leave you wiring as it is since the same circuit will be used in your next experiment.

Statement No. 82: By carefully examining the output numbers obtained from the ROM in this statement, I find that the output number has the following mathematical relationship to the input number.

(1) The number obtained by dividing the input number by 3.

(2) Square of the input number.

(3) Square root of the input number.

(4) Common logarithm of the input number.

### **EXPERIMENT 83**

Purpose: To demonstrate several additional applications of read-onlymemories.

Introductory Discussion: In the previous experiment you saw how the ROM could be used for function generation and arithmetic processing. The ROM is capable of many additional operations. In this experiment you are going to demonstrate the application of an ROM performing basic logic operations, such as code conversion.

Experimental Procedure: At this point you do not need to make any further changes to your experimental circuit. However, you will be required to modify the program stored in the memory. Complete instructions are given to you as to how to do this for each step.

Step 1: To show how a read-onlymemory can be used to perform basic logic functions and to implement Boolean techniques.

Program your memory according to the chart in Fig. 83-1. As before, the chart designates each memory location and the contents of that location in hexadecimal notation.

| LOC | HEX CONTENTS |  |

|-----|--------------|--|

| 0   | 01           |  |

| 1   | 02           |  |

| 2   | 04           |  |

| 3   | 08           |  |

| 4   | 10           |  |

| 5   | 20           |  |

| 6   | 40           |  |

| 7   | 80           |  |

| 8   | 00           |  |

| 9   | 00           |  |

| A   | 00           |  |

| в   | 00           |  |

| C   | 00           |  |

| D   | 00           |  |

| E   | 00           |  |

| F   | 00           |  |

Fig. 83-1. Program for Step 1.

After you have programmed the memory according to the table, turn on the experimental chassis. Step the black push button until the counter is in the 0000 state, then step the counter through each of the sixteen states, 0000 through 1111, and record the memory output for each condition in the table of Fig. 83-2. Examine your results and try to determine the function that the ROM is performing. It is a common digital logic function that you have studied before, so make every effort to recognize it and write the result in the margin of the text. Refer to your earlier lessons or kit manuals if you should need to do so.

| INPUT | OUTPUT |

|-------|--------|

| 0000  |        |

| 0001  |        |

| 0010  |        |

| 0011  |        |

| 0100  |        |

| 0101  |        |

| 0110  | 1      |

| 0111  |        |

| 1000  |        |

| 1001  |        |

| 1010  |        |

| 1011  |        |

| 1100  |        |

| 1101  |        |

| 1110  |        |

| 1111  |        |

Fig. 83-2. Table for Step 1.

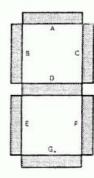

Discussion of Step 1: The correct results for Step 1 are shown in Fig. 83-3. The ROM is performing the function of an octal or one-of-eight decoder. An output is generated for only the first

| INPUT | OUTPUT   |

|-------|----------|

| 0000  | 00000001 |

| 0001  | 00000010 |

| 0010  | 00000100 |

| 0011  | 00001000 |

| 0100  | 00010000 |

| 0101  | 00100000 |

| 0110  | 01000000 |

| 0111  | 10000000 |

| 1000  | 00000000 |

| 1001  | 00000000 |

| 1010  | 00000000 |

| 1011  | 00000000 |

| 1100  | 00000000 |

| 1101  | 00000000 |

| 1110  | 00000000 |

| 1111  | 00000000 |

### Fig. 83-3. Results for Step 1.

eight states of the input. Since the left-most bit of this 4-bit input is a binary 0, we can consider the input word to be an octal number. The ROM looks at the input number, performing the function of a decoder by enabling one of the eight outputs. For example, with a 000 input the IØ lamp is on, indicating that the zero state has been decoded. With an input of 001, the Il lamp is on, indicating that the 1 state has been decoded. When the I7 lamp is on, the 111 state is decoded. The other eight states (1000 through 1111) are not octal numbers; therefore, the memory has been programmed not to respond to them. The output for these eight states should be all zeros.

This decoder application of the ROM is a simple but frequently used one. It also clearly illustrates that the ROM can be programmed to implement any Boolean algebra function. When a number of logic signals that are a function of a certain number of logical input signals are to be generated, an ROM can be used to implement all of the signals that are functions of these inputs. In other words, virtually any combinational logic function can be implemented with the ROM.

### Step 2: To show how the ROM can be used to perform code conversion.

Program the memory according to the table in Fig. 83-4. By now you should be familiar with the hexadecimal programming scheme we are using, and the programming process should be simpler and quicker.

When you have programmed the memory, step the counter with the black push button through its sixteen states,

| LOC | HEX CONTENTS |

|-----|--------------|

| 0   | 00           |

| 1   | 01           |

| 2   | 02           |

| 3   | 03           |

| 4   | 04           |

| 5   | 05           |

| 6   | 06           |

| 7   | 07           |

| 8   | 08           |

| 9   | 09           |

| А   | 10           |

| в   | 11           |

| С   | 12           |

| D   | 13           |

| E   | 14           |

| F   | 15           |

Fig. 83-4. Program for first part of Step 2.

| INPUT | OUTPUT |

|-------|--------|

| 0000  |        |

| 0001  |        |

| 0010  | 1      |

| 0011  |        |

| 0100  |        |

| 0101  |        |

| 0110  |        |

| 0111  |        |

| 1000  |        |

| 1001  |        |

| 1010  |        |

| 1011  |        |

| 1100  |        |

| 1101  |        |

| 1110  |        |

| 1111  |        |

Fig. 83-5. Table for first part of Step 2.

0000 through 1111, and record the 8-bit output word for each step in Fig. 83-5.

Next, reprogram the memory according to the chart in Fig. 83-6. Step the counter through its sixteen states and record the 8-bit output of the memory in the table provided in Fig. 83-7. Turn off the experimental chassis.

Now examine the results recorded in Figs. 83-5 and 83-7 and identify the output by comparing it with the binary input. Note your decisions in the margin of the text.

Discussion of Step 2: This step shows how the ROM can be used to perform code conversion. By carefully studying the results that you recorded in Fig. 83-5, you should have found that the 8-bit output of the ROM should be interpreted as two 4-bit BCD digits. In other words, the binary input applied to the ROM

| LOC | HEX CONTENTS |  |

|-----|--------------|--|

| 0   | 03           |  |

| 1   | 04           |  |

| 2   | 05           |  |

| 3   | 06           |  |

| 4   | 07           |  |

| 5   | 08           |  |

| 6   | 09           |  |

| 7   | 0A           |  |

| 8   | OB           |  |

| 9   | OC           |  |

| A   | 00           |  |

| В   | 0E           |  |

| С   | OF           |  |

| D   | 10           |  |

| E   | 11           |  |

| F   | 12           |  |

Fig. 83-6. Program for second part of Step 2.

| INPUT | OUTPUT |

|-------|--------|

| 0000  |        |

| 0001  |        |

| 0010  |        |

| 0011  |        |

| 0100  |        |

| 0101  |        |

| 0110  |        |

| 0111  |        |

| 1000  |        |

| 1001  |        |

| 1010  |        |

| 1011  |        |

| 1100  |        |

| 1101  |        |

| 1110  |        |

| 1111  |        |

Fig. 83-7. Table for second part of Step 2.

from the counter on the MI circuit boar causes the equivalent BCD number to b reproduced at the 8-bit memory output

In the next program you should hav found that the ROM is converting a 4-bi binary number into its equivalent XS: code. Remember, to find the XS3 valuof a number, take the decimal equivalen of the binary number, add three to it then convert it back to binary.

As you can see, it is very easy to convert one code into another with ar ROM. The input code is simply applied to the addressing lines of the ROM. The input code then addresses some particular memory location where the desired output code for that input is stored. With such an arrangement, virtually any form of code conversion can be handled with an ROM, which further proves that virtually any combinational logic network can be implemented with an ROM.

Instructions for Statement 83: In this statement you are going to show how the ROM can be used as a special decoder for driving a seven-segment decimal display. Fig. 83-8 shows a typical seven-segment decimal display. There are seven lighted segments labeled A through G. When we wish to display one of the 10 decimal numbers 0 through 9, we simply turn on

Fig. 83-8. Seven-segment decimal display.

|         | BCD   | SEGMENTS |

|---------|-------|----------|

| DECIMAL | INPUT | ABCDEFG  |

| 0       | 0000  |          |

| 1       | 0001  |          |

| 2       | 0010  |          |

| 3       | 0011  |          |

| 4       | 0100  |          |

| 5       | 0101  |          |

| 6       | 0110  |          |

| 7       | 0111  |          |

| 8       | 1000  |          |

| 9       | 1001  |          |

Fig. 83-9. Table for Statement 83.

the appropriate segments of the display. For example, to display the number 1 we would turn on segments C and F. To display the number 6, we would turn on segments A, B, D, E, F and G. There would be a light driver and lamp associated with each of the segments. Our purpose here is to convert the 4-bit 8421 BCD input code into seven signals that can be used to operate the light drivers for each of the segments in the display.

To do this, simply consider the seven segment display in Fig. 83-8 and determine which segments should be on for each of the decimal numbers 0 through 9. Record your results in the table in Fig. 83-9. Place a binary 1 under the lettered column corresponding to the lamp segment that should be on for the specified decimal digit. All other segments will be off, so record a binary 0 in those columns. Once you have established the sequence in Fig. 83-9, you will readily see that you can use the ROM as a decoder to operate such a display.

For this statement question fill in the table in Fig. 83-10 giving in hexadecimal notation the contents of each of the desired memory locations for this application. Assume that the left or most significant bit of your memory output always remains at 0, and that only ten of the sixteen memory locations will be used.

After you complete the statement question you may proceed to the next experiment. Do not change any of your wiring until you are instructed to do so in your next experiment.

| LOC                        | HEX CONTENTS |

|----------------------------|--------------|

| 0                          |              |

| 1                          |              |

| 2                          |              |

| 1<br>2<br>3<br>4<br>5<br>6 |              |

| 4                          |              |

| 5                          |              |

| 6                          |              |

| 7                          |              |

| 8                          |              |

| 9                          |              |

Fig. 83-10. Record your answer for Statement 83 here.

Statement No. 83: The table representing the BCD to seven-segment conversion program is shown in Fig.

| (1) 83-11. | (3) 83-13. |

|------------|------------|

| (2) 83-12. | (4) 83-14. |

| LOC    | HEX CONTENTS |   |

|--------|--------------|---|

| 0      | 7            | 7 |

| 1      | 2            | 1 |

| 2<br>3 | 5            | D |

| 3      | 6            | В |

| 4      | 4            | A |

| 5      | F            | 6 |

| 6      | 2<br>F       | 5 |

| 7      | F            | 7 |

| 8      | F            | A |

| 9      | 1            | 2 |

| LOC | HEX CONTENTS |        |

|-----|--------------|--------|

| 0   | 7            | 7      |

| 1   | 1            | 2      |

| 2   | 5            | D      |

| 3   | 5            | В      |

| 4   | 3            | A      |

| 5   | 6            | В      |

| 6   | 6            | F      |

| 7   | 5            |        |

| 8   | 7            | 2<br>F |

| 9   | 7            | В      |

Fig. 83-11.

Fig. 83-12.

| LOC | HEXC | ONTENTS |

|-----|------|---------|

| 0   | 7    | 7       |

| 1   | 1    | 2       |

| 2   | D    | 5       |

| 3   | B    | 6       |

| 4   | A    | 4       |

| 5   | 6    | F       |

| 6   | 5    | 2       |

| 7   | 7    | F       |

| 8   | A    | F       |

| 9   | 2    | 1       |

| LOC    | HEX CONTENTS |   |  |  |  |  |  |

|--------|--------------|---|--|--|--|--|--|

| 0      | 7            | 7 |  |  |  |  |  |

| 1      | 2            | 1 |  |  |  |  |  |

| 2      | 6            | В |  |  |  |  |  |

| 2<br>3 | 5            | D |  |  |  |  |  |

| 4      | 4            | A |  |  |  |  |  |

| 5      | 2            | 5 |  |  |  |  |  |

| 6      | F            | 6 |  |  |  |  |  |

| 7      | F            | 7 |  |  |  |  |  |

| 8      | F            | A |  |  |  |  |  |

| 9      | 2            | 1 |  |  |  |  |  |

Fig. 83-13.

Fig. 83-14.

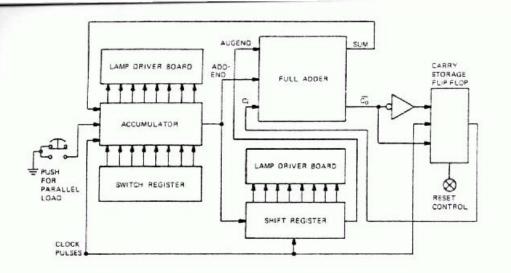

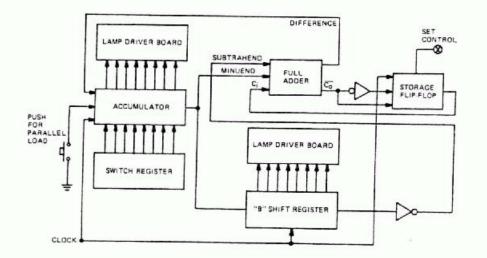

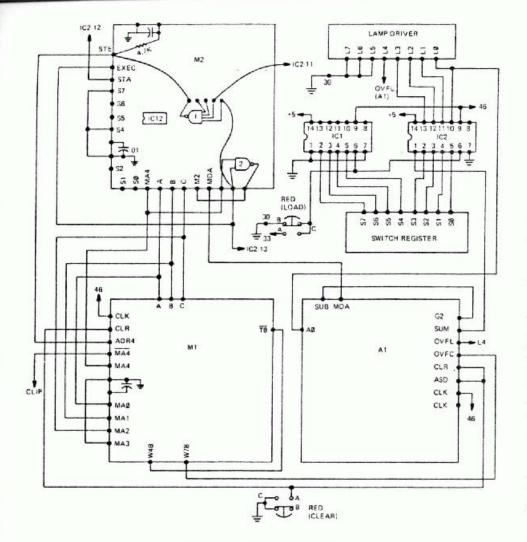

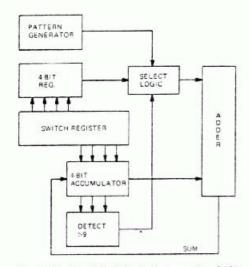

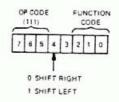

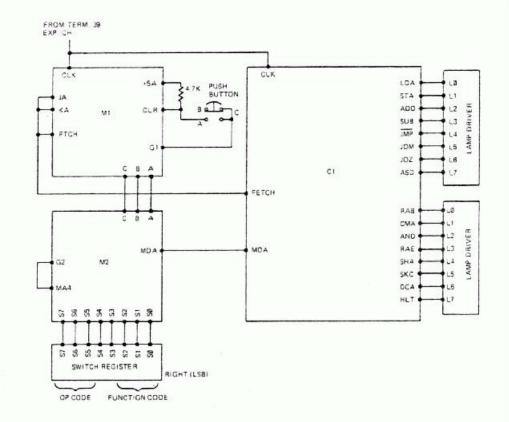

# Assembling the Al and A2 Circuit Boards

Before you can proceed with the remaining experiments in this kit, you will need to assemble the A1 and A2 printed circuit boards. These boards contain the arithmetic circuitry for the digital computer that you will build in the final kit, but you will use the logic circuitry and registers on these boards in the experiments prior to this.

### ASSEMBLING THE A1 BOARD

To assemble this board you will need the following parts:

- 1 Printed circuit board (EC34)

- 1 100 mfd, 10-volt capacitor (CN112)

- 44 Terminal lugs (LU9)

- 7 14-pin IC sockets (SO84)

- 1 16-pin IC socket (SO86)

- 7 .01 mfd disc capacitors (CN102)

- 1 500 pf disc capacitor

- 1 470-ohm, 1/4 watt resistor (RE167)

- 1 7420 IC (IG6)

- 1 7400 IC (IG5)

- 1 7404 IC (IG12)

- 1 7451 IC (IG9)

- 1 7476 IC (IG18)

- 2 7495 IC's (IG16)

### ASSEMBLY PROCEDURE

Insert the 44 terminal lugs in the labeled peripheral holes from the top of the EC34 board. Press the terminals into the board so that they are seated properly, and then use your longnose pliers to crimp the terminal on the bottom of the board to hold it in place. Solder each of the terminals on the bottom of the board. Also solder the terminals on the top of the board where a copper pad appears.

Install a short jumper wire, designated J1, on the top of the board directly to the left of IC41. Bend a short piece of bare hookup wire to fit neatly into the holes, flush with the board. Solder both connections and clip off the excess lead length.

Install seven .01 mfd disc capacitors in the locations designated on the circuit board. These are installed adjacent to IC39, IC40, IC41, IC42, IC44, IC45, and IC46. Push the capacitor into the board from the top so that about 1/16'' of the lead is exposed above the board, then solder the connections. Be sure to solder the leads on both the top and the bottom of the board since these leads carry the power and ground connection from one side of the board to the other. Clip off the excess lead length.

Install the 470-ohm resistor and 500 pf disc capacitor in the locations designated below IC41. Bend the leads of the resistor close to the body and mount the resistor so that it is flush with the board. Solder both the resistor and capacitor connections, then clip off the excess lead length.

Install a 100 mfd capacitor between

terminals G1 and +5D. The positive terminal of the capacitor should go to the +5D terminal. Simply wrap the capacitor lead around the appropriate terminal and clip off the excess length after you solder it.

Install seven 14-pin IC sockets in the locations designated IC39, IC40, IC41, IC42, IC44, IC45, and IC46. Be sure that the notch in the end of the socket is aligned properly with the notch on the screening on the top of the board. Check to see that the socket is pressed into the holes firmly and that it is set flush with the board. Solder the IC socket terminals using the thin solder supplied with this kit.

Install a 16-pin IC socket in location IC43. Again double check to be sure that the notch in the end of the socket is pointing in the correct direction. With the socket mounted flush against the board, solder all 16 terminals with the thin solder.

Install the integrated circuits (except the 7480, IC46) as designated on the top of the board in the sockets. The two 7495 IC's are left over from Kit 7K. Be sure that each IC is aligned properly with respect to the socket and that it is pressed firmly into place to seat all pins.

As a final step it is a good idea to look over the board carefully once you complete it. Make sure that all of the components are in place, the sockets are aligned properly, the IC's are set in their sockets correctly and all connections have been soldered. It is particularly important to make a check of the solder connections. Check to see that the sockets are soldered and that there are no solder bridges between pins. Inspect the terminal lugs to be sure they are soldered on top of the board in those places where copper pads are provided.

### ASSEMBLING THE A2 BOARD

To construct this board, you will need the following components:

- 1 Circuit Board (EC35)

- 1 100 mfd, 10 volt capacitor (CN112)

- 50 Terminal lugs (LU9)

- 7 .01 mfd disc capacitors (CN102)

- 1 470-ohm, 1/4 watt resistor (RE167)

- 1 .1 mfd disc capacitor (CN104)

- 1 4.7k-ohm, 1/4 watt resistor (RE166)

- 8 14-pin IC sockets (SO84)

- 1 16-pin IC socket (SO86)

- 1 24-pin IC socket (SO87)

- 2 7400 IC's (IG5)

- 1 7404 IC (IG12)

- 1 7420 IC (IG6)

- 1 7423 IC (IG21)

- 1 7453 IC (IG19)

- 2 15844 IC's (IG7)

- 1 7460 IC (IG20)

- 1 74198 IC (IG25)

### ASSEMBLY PROCEDURE

Install the 50 terminal lugs in the marked holes on the top of the circuit board. Press the terminals into place to be sure that they are flush with the top of the board. Crimp each terminal with your longnose pliers on the bottom of the board to hold it firmly in place. Solder all terminals on both the top and the bottom of the board.

Install a short wire in the J1, J2 and J3 positions as designated on the top of the board in the block labeled accumulator. Cut short pieces of bare hookup wire the proper length and install them in the J1 and J3 positions. Use a short piece of insulated hookup wire at the J2 position. This will prevent the jumper from accidentally shorting the +5 volt line to ground. Bend the leads neatly so that the jumper drops into the holes provided and rests flush with the board. Solder all connections and clip off excess lead length.

Install the 470-ohm resistor and .1 mfd disc capacitor at the locations designated in the block labeled accumulator. This is directly to the left of IC56. Bend the resistor leads close to the body of the resistor so that the resistor drops into the holes provided and fits flush with the board. Install the capacitor so that about 1/16'' of lead is exposed above the board. Solder the resistor and capacitor leads and clip off any excess lead length. Be sure to solder the capacitor lead on top of the board where a foil pad is provided.

Install a 4.7k-ohm resistor in the holes provided directly to the right of position IC51. Again bend the resistor leads close to the body so that the resistor will drop into the holes and lay directly on the board. Solder the resistor leads and clip off the excess lead length. Solder the resistor at the pad provided on top of the board.

Install the seven .01 mfd disc capacitors in the locations designated. These are the positions directly to the right of IC47, IC48, IC49, IC50, IC52, IC53, and IC54. Drop the capacitor into the holes provided so that about 1/16" of the capacitor lead is exposed on top of the board. Solder the capacitor leads on both the top and the bottom of the board, then clip off any excess lead length.

Install the 100 mfd electrolytic capacitor between terminals +5C and G1. Wrap the leads around the terminals and solder them into place, then clip off the excess lead length. The positive terminal of the capacitor should connect to the +5C. Install the eight 14-pin IC sockets in positions IC47 through IC53 and IC56. The notches on the sockets should be aligned with the notches on the screening on top of the board. As before, be sure that the socket is mounted firmly in place, flush with the board before you solder the pins on the bottom. Use the thin solder and the small tip, low wattage soldering iron to make the solder connections. Be extremely careful not to cause solder bridges between adjacent terminals, but use enough heat and solder to thoroughly cover the connection.

Install a 16-pin IC socket in location IC55. Be sure that the notch is aligned properly with the screened designation. Be sure that the socket is flush with the top of the board, then solder all 16 pins with the thin solder.

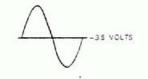

Install a 24-pin IC socket in location IC54. This socket cannot be used exactly as it is supplied. The two sections containing the pins must be broken apart from one another. You can use your side cutters to cut through the soft plastic holding the two strips together. Trim the excess plastic from each strip. Fig. 3 shows the before and after versions. Next, install the two 12-pin strips in the IC54

position. Solder all 24 pins with the thin solder.

Install the designated IC's in the appropriate sockets. Note the alignment of the notch in the socket and the IC so that they correspond. Press each IC firmly into its socket so that it makes good connection. When installing the 24-pin IC, align pin 1 of the IC with the number 1 screened on the board. Double check all of the connections on the circuit board. Be sure that you have soldered all terminal lugs on both the top and bottom where designated. Also check all of the solder connections on the IC sockets to be sure that there are no solder bridges between adjacent pins. When you have thoroughly examined this board, you are ready to continue the experiments in this kit.

# Performing Experiments 84 Through 88

### **EXPERIMENT 84**

Purpose: To demonstrate the principles of binary addition and examine several methods of accomplishing this function.

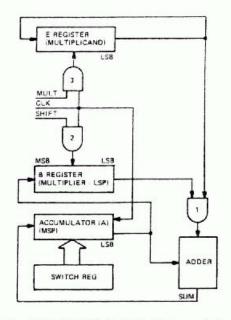

Introductory Discussion: Binary addition is the basic function performed within the arithmetic section of any digital computer. Other arithmetic functions such as subtraction, multiplication, and division are often performed by adding complements, using successive additions, or by using successive additions and subtractions. Since binary addition is so fundamental to all digital computations, it is extremely important for you to understand exactly how it is performed.

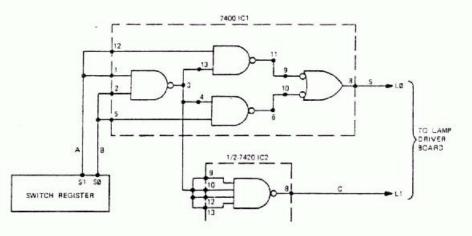

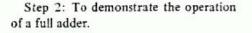

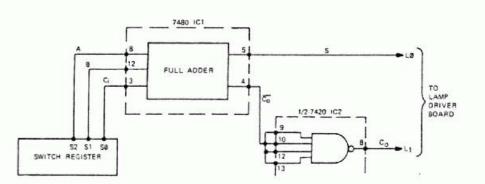

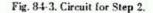

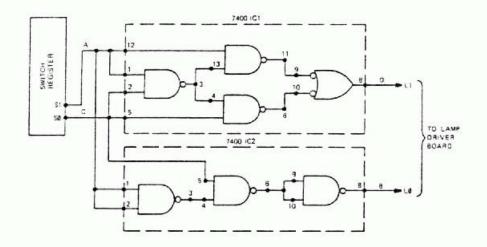

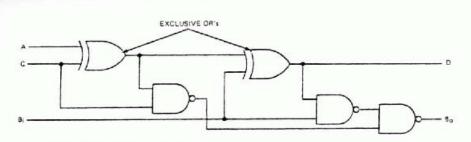

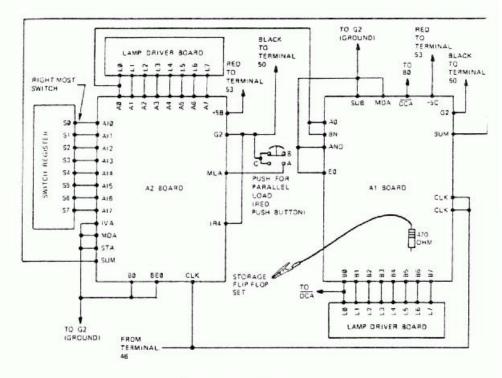

In this experiment you will demonstrate single-bit half adder and full adder circuits. You will actually wire a half adder circuit using NAND gates and demonstrate its operation. However, the full adder circuit that you will demonstrate will be contained within a single IC and will not require extensive wiring. You will also demonstrate how two binary words can be added serially.

Experimental Procedure: Before you can begin this experiment, you must partially disassemble the circuit that was used in your last experiment. First disconnect the resistive summing network from terminals SØ through S3 on the M3 circuit board. Also remove the wire coming from this network from terminal IC1-4 of the experimental chassis. Next, disconnect all of the wires on the M3 board including the red and black power and ground leads, which will also be disconnected from the experimental chassis. Set the M3 board aside for use in the next kit.