# ND-500 Reference Manual ND-05.009.3 EN

The information in this manual is subject to change without notice. Norsk Data A.S assumes no responsibility for any errors that may appear in this manual. Norsk Data A.S assumes no responsibility for the use or reliability of its software on equipment that is not furnished or supported by Norsk Data A.S. Copyright ©1987 by Norsk Data A.S.

| PRIN     | ITING RECORD |

|----------|--------------|

| PRINTING | NOTES        |

| 10/80    | Version 1    |

| 07/82    | Version 2    |

| 06/87    | Version 3    |

|          |              |

|          |              |

|          |              |

|          |              |

|          |              |

## **UPDATING**

Manuals can be updated in two ways, new versions and revisions. New versions consist of a completely new manual which replaces the old one, and incorporate all revisions since the previous version. Revisions consist of one or more single pages to be merged into the manual by the user, each revised page being listed on the new printing record sent out with the revision. The old printing record should be replaced by the new one.

New versions and revisions are announced in the ND Customer Support Information and can be ordered from the address below.

The reader's comments form at the back of this manual can be used both to report errors in the manual and give an evaluation of the manual. Both detailed and general comments are welcome.

## RING BINDER OR PLASTIC COVER

The manual can be placed in a ring binder for greater protection and convenience of use. Ring binders may be ordered in two sizes: B5 and A-4.

The manual may also be placed in a plastic cover. This cover is more suitable for manuals in A4 size of less than 100 pages than for larger manuals. Please send your order, as well as all types of inquiries and requests for documentation to the local ND office, or (in Norway) to:

Norsk Data A.S Graphic Centre P.O.Box 25 BOGERUD N-0621 OSLO 6 - Norway

O

| _ | <b>X</b>                                |

|---|-----------------------------------------|

|   | I would like to order                   |

|   | Ring binders, B5, at NOK 35 per binder  |

|   | Ring binders, A4, at NOK 45 per binder  |

|   | Plastic Covers, A4, at NOK 10 per cover |

|   | Name:                                   |

|   | Company:                                |

|   | Address:                                |

## Preface:

#### PREFACE

## THE PRODUCT

This manual describes the instruction set, the trap-handling system and the memory management system of the central processing unit of the ND-500 series computer systems and the ND-5000 series computer systems.

The ND-5000 CPU has a completely new and unique physical implementation, but is based on the ND-500 systems architecture. The ND-5000 uses the same instructions as the ND-500 .

# THE READER

The ND-500 CPU reference manual is intended for anybody using the ND-500 assembler and for system programmers needing to know the exact format of the generated code.

Programmers making advanced use of the memory management system for segmenting, or writing their own trap-handling routines will find detailed information in this manual.

## PREREQUISITE KNOWLEDGE

No previous knowledge of the ND-500 or the ND-5000 is required, but assembly programming experience is desirable. Understanding the memory management system, making programs that handle communication between the  $\rm I/O$  processor and the ND-500 or the ND-5000 and the inner kernel of the operating system requires a more detailed description of both ND-500 , or ND-5000 , and ND-100 hardware. This can be found in

ND-5000 Hardware Description - ND-05.020 ND-500/2 Hardware Description - ND-05.015 ND-100 Functional description - ND-06.026

Use of the ND-500 assembler and how to link and load an ND-500 program is described in the manuals

ND-500 Assembler Reference manual - ND-60.113 ND-500 Loader Monitor - ND-60.136 This manual is organized as a reference manual. It is intended for looking up the exact syntax of machine instructions and hardware details relevant to software. Each chapter is independent and can be understood without reading previous chapters.

This manual is valid for both the ND-500 and the ND-5000 computer systems. When the manual uses the name ND-5000 this is also valid fore the ND-500 .

The chapters are organized as follows:

# PART I General design

Chapter 1: A general introduction to the ND-5000 system

Chapter 2: The register block

Chapter 3: Stack and heap management Chapter 4: Memory management system

Chapter 5: Cache memory system

Chapter 6: The trap system

Chapter 7: Data types handled by the CPU Chapter 8: Operand specifiers and addressing

Chapter 9: Instruction formats

## PART II Instruction set

Chapter 10: Data transfer and logical instructions

Chapter 11: Arithmetical instructions Chapter 12: Mathematical functions Chapter 13: Control instructions Chapter 14: String instructions

Chapter 15: Miscellaneous instructions

Chapter 16: Special instructions

Chapter 17: Packed decimal instructions (Option)

Part II is organized in a logical way. You find related instructions when leafing through the neighbouring pages to a specific lookup.

The appendices contain tables of address codes, instructions, cross references, and notational conventions.

## NEW INSTRUCTIONS

A number of new instructions are introduced with the ND-5000 . These instructions also run on computer systems with the ND-500/1 and the ND-500/2 CPUs. The instructions are labelled: ('87 extension).

# CPU - I/O PROCESSOR

The term 'CPU' is used for the ND-500/ND-5000 processor throughout this manual. Whenever the I/O processor is mentioned, this means the ND-100/ND-110 processor.

Due to the large number of instruction formats and address modes available, it is not possible to illustrate more than a small fraction of the legal combinations. An attempt has been made to show the use of each format and mode at least once.

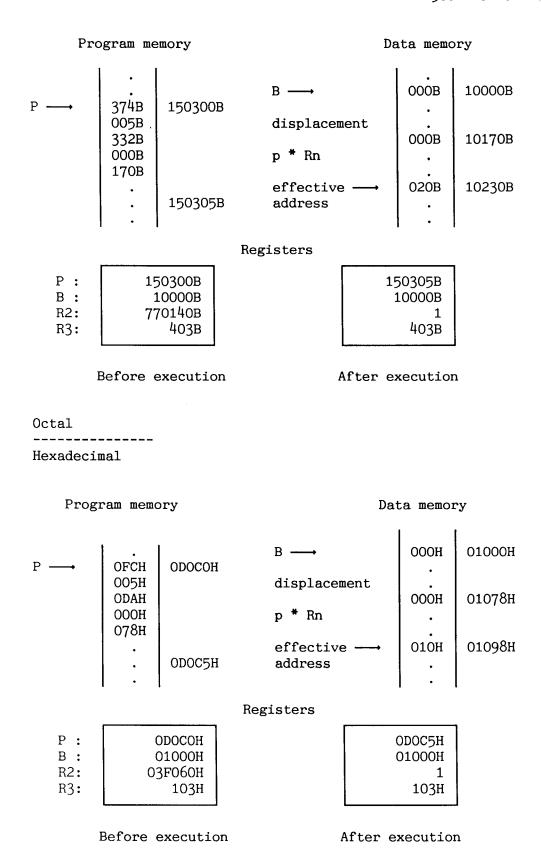

Numeric quantities are presented in decimal, octal and/or hexadecimal format. Octal numbers are followed by a 'B' and hexadecimal numbers by an 'H'. Hexadecimal numbers must always start with a decimal number to avoid confusion with identifiers (that is, FFH must be written as OFFH). In this manual hexadecimal numbers are always preceded by a zero.

Absence of a following letter indicates decimal number.

When reading examples containing word and halfword quantities displayed as octal bytes, the values in the upper bytes have to be shifted. Example:

Binary pattern:

000100000001000010010010101010

Displayed as: Four octal bytes:

020B 010B 111B 122B

Two octal halfwords:

010010B 044522B

Octal word:

02002044522B

Hexadecimal numbers require no shifting; the hexadecimal digits can be concatenated as they are, two digits per byte.

The term WORD always refers to 32-bit words. 16-bit data items (ND-100 words) are referred to as HALFWORDS. The term BYTE refers to 8-bit bytes.

In the figures, address values increase downwards.

# TABLE OF CONTENTS

| <u>Section</u> Pag                                                                                                                                                                                                                                                                                                                                                   | <u>e</u>                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                                                                                                                                                                                                                                                                                                                      |                            |

| 1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                       | 3                          |

| 1.2 System configuration                                                                                                                                                                                                                                                                                                                                             | 5<br>5<br>8<br>9           |

| 2 THE REGISTER BLOCK                                                                                                                                                                                                                                                                                                                                                 | 11                         |

| 3 STATIC DATA, STACK AND HEAP                                                                                                                                                                                                                                                                                                                                        | 17                         |

| 3.2 Stack allocation                                                                                                                                                                                                                                                                                                                                                 | 19<br>20<br>22             |

| 4 MEMORY MANAGEMENT SYSTEM                                                                                                                                                                                                                                                                                                                                           | 25                         |

| 4.2 Memory management architecture 4.2.1 Address domain 4.2.2 Process 4.2.3 Process environment 4.2.3.1 Process registers 4.2.3.2 Capability tables 4.2.3.3 Domain information 4.2.4 Logical addressing 4.2.5 Domain communication 4.2.5.1 Alternative domain 4.2.5.2 Domain calls and monitor calls 4.2.5.3 Trap handling 4.3 Physical implementation 4.4 Buffering | 36<br>39<br>40<br>44       |

|                                                                                                                                                                                                                                                                                                                                                                      | 45                         |

| 6 THE TRAP SYSTEM                                                                                                                                                                                                                                                                                                                                                    | 49                         |

| 6.2 Trap handler routines                                                                                                                                                                                                                                                                                                                                            | 51<br>52<br>52<br>55<br>57 |

| Section        | n Pag                                                       |

|----------------|-------------------------------------------------------------|

| 6.5.1          | Data status bits 5                                          |

| 6.5.2          | Tracing status bits                                         |

| 6.5.3          | Instruction and operand reference status bits 6             |

| 6.5.3.         | Ignorable trap conditions 6                                 |

| 6.5.3.         | Non-ignorable trap conditions 6                             |

| 6.5.3.         |                                                             |

| 6.5.4          | Signalling, synchronization and miscellaneous status bits 6 |

| 6.5.5          | System error status bits 6                                  |

| 6.5.6          | Addressing traps 6                                          |

| 6.5.7          | Status bits survey 6                                        |

| 7 D            | ATA TYPES                                                   |

| D 4            |                                                             |

| 7.1            | Introduction                                                |

| 7.2            | Data types                                                  |

| 7.2.1<br>7.2.2 | Bit                                                         |

| 7.2.3          | Byte                                                        |

| 7.2.4          | Halfword                                                    |

| 7.2.5          |                                                             |

| 7.2.6          | Single precision floating point                             |

| 7.2.7          | Double precision floating point                             |

| 7.2.8          | Floating point rounding                                     |

| 7.2.0          |                                                             |

| 7.4            | Data formats in main memory                                 |

| 7.4            | Data in registers                                           |

| 8 01           | PERAND SPECIFIERS AND ADDRESSING                            |

|                | PERAND SPECIFIERS AND ADDRESSING                            |

| 8.1            | Introduction                                                |

| 8.2            | General and direct operands                                 |

| 8.2.1          | General operands                                            |

| 8.2.2          | Post-Index                                                  |

| 8.3            | Survey of addressing modes                                  |

| 8.4            | Local addressing                                            |

| 8.5            | Local, post-indexed addressing                              |

| 8.6            | Local indirect addressing                                   |

| 8.7            | Local indirect, post-indexed addressing 9                   |

| 8.8            | Record addressing                                           |

| 8.9            | Pre-indexed addressing                                      |

| 8.10           | Absolute addressing                                         |

| 8.11           | Absolute, post-indexed addressing                           |

| 8.12           | Constant operand addressing                                 |

| 8.13           | Register addressing                                         |

| 8.14           | Alternative addressing                                      |

| 8.15           | Descriptor addressing                                       |

| 8.16           | Direct operands                                             |

| 8.16.1         | Displacement addressing                                     |

| 8.16.2         | Absolute program addressing                                 |

| 8.16.3         | Absolute data addressing                                    |

| Sectio | n Page                                             |

|--------|----------------------------------------------------|

| 9 Т    | HE ND-500 INSTRUCTION SET                          |

| 10 D   | ATA TRANSFER AND LOGICAL INSTRUCTIONS              |

| 10.1   | Load                                               |

| 10.2   | Load local base register                           |

| 10.3   | Load record register                               |

| 10.4   | Store                                              |

| 10.5   | Store local base register                          |

| 10.6   | Store record register                              |

| 10.7   |                                                    |

| 10.8   | Move                                               |

| 10.9   | Swap                                               |

| 10.10  | Compare                                            |

| _      | Compare two operands                               |

| 10.11  | Test against zero                                  |

| 10.12  | Negate                                             |

| 10.13  | Invert                                             |

| 10.14  | Invert with carry add                              |

| 10.15  | Absolute value                                     |

| 10.16  | Clear register                                     |

| 10.17  | Store zero                                         |

| 10.18  | Set to one                                         |

| 10.19  | Increment                                          |

| 10.20  | Decrement                                          |

| 10.21  | And                                                |

| 10.22  | Or                                                 |

| 10.23  | Exclusive or                                       |

| 10.24  | Logical shift                                      |

| 10.25  | Arithmetical shift                                 |

| 10.26  | Rotational shift                                   |

| 10.27  |                                                    |

| 10.28  |                                                    |

| 10.29  | Put bit                                            |

|        | Clear bit                                          |

| 10.30  | Set bit                                            |

| 10.31  | Get bit field                                      |

| 10.32  | Put bit field                                      |

| 10.33  | Floating point remainder                           |

| 10.34  | Integer part                                       |

| 10.35  | Integer part with rounding                         |

| 10.36  | AMODB - Integer modulo ('87 extension)             |

| 10.37  | ENTIER - SIMULA Entier function ('87 extension) 16 |

| 11 A   | RITHMETICAL INSTRUCTIONS                           |

|        |                                                    |

| 11.1   | Add                                                |

| 11.2   | Subtract                                           |

| 11.3   | Multiply                                           |

| 11.4   | Divide                                             |

| Sectio | n P                                         | age            |

|--------|---------------------------------------------|----------------|

| 11.5   | Add two operands                            | 1.00           |

| 11.6   | Add two operands                            | 169            |

| 11.7   | Subtract two operands                       | 170            |

| 11.8   | Multiply two operands                       | 171            |

|        | Divide two operands                         | 172            |

| 11.9   | Add three operands                          | 173            |

| 11.10  | Subtract three operands                     | 174            |

| 11.11  | Multiply three operands                     | 175            |

| 11.12  | Divide three operands                       | 176            |

| 11.13  | Multiply with overflow to register          | 177            |

| 11.14  | Divide with remainder to register (modulo)  | 178            |

| 11.15  | Unsigned multiply with overflow to register | 170            |

| 11.16  | Unsigned divide                             | 120            |

| 11.17  | Add with carry                              | 100            |

| 11.18  | Subtract with carry                         | 107            |

| 11.19  | Subtract with carry                         | 102            |

| 11.20  | Multiply and add                            | 183            |

| 11.20  | Sum of products                             | 184            |

| 12 M   | ATHEMATICAL DINORTONG                       | _              |

| 12 M   | ATHEMATICAL FUNCTIONS                       | 185            |

| 12.1   | A to the I'th power                         | 1 0 7          |

| 12.2   | I to the I'th nower                         | 1 0 0<br>1 0 ∫ |

| 12.3   | I to the J'th power                         | 100            |

| 12.4   | Polynomial                                  | 189            |

|        | Square root                                 | 190            |

| 12.5   | Sine                                        | 191            |

| 12.6   | Arc sine                                    | 192            |

| 12.7   | Cosine                                      | 193            |

| 12.8   | Arc cosine                                  | 1 Q.L          |

| 12.9   | Tangent                                     | 10E            |

| 12.10  | Arc tangent                                 | 190            |

| 12.11  | Arc tangent                                 | 190            |

| 12.12  | Arc tangent two argument                    | 197            |

|        | Exponential                                 | 198            |

| 12.13  | Natural logarithm                           | 199            |

| 12.14  | Binary logarithm                            | 200            |

| 12.15  | Common logarithm                            | 201            |

|        |                                             |                |

| 13 C   | ONTROL INSTRUCTIONS                         | 203            |

| 13.1   | Unconditional audiet                        |                |

|        | Unconditional relative jump                 | 205            |

| 13.2   | Unconditional absolute jump                 | 206            |

| 13.3   | Conditional jump                            | 207            |

| 13.4   | Loop with increment                         | 209            |

| 13.5   | Loop with decrement                         | 211            |

| 13.6   | Loop general                                | 212            |

| 13.7   | Call subroutine general                     | 215            |

| 13.8   | Call subrouting shoulds                     | マエク            |

| 13.9   | Call subroutine absolute                    | 216            |

|        | Initialize stack                            | 217            |

| 13.10  | Subroutine entry points                     | 218            |

| 13.11  | Subroutine return                           | 226            |

| 14 S7  | DING INCORPLOSE                             |                |

| 14 S.  | RING INSTRUCTIONS                           | 229            |

# xiii

| Section        | 1                                                         | Page         |

|----------------|-----------------------------------------------------------|--------------|

|                |                                                           |              |

| 14.1           | Introduction                                              | . 231        |

| 14.2           | String move                                               | . 234        |

| 14.3           | String move while                                         | . 235        |

| 14.4           | String move until                                         | . 236        |

| 14.5           | String move translated                                    | . 237        |

| 14.6           | String move translated until                              | . 238        |

| 14.7           | String move m elements                                    | . 239        |

| 14.8           | String move m elements                                    | 240          |

| 14.9           | String fill m elements                                    | 241          |

| 14.10          | String compare                                            | 242          |

| 14.11          | String compare translated                                 | 243          |

| 14.12          | String compare with pad                                   | . 244        |

| 14.13          | String compare translated with pad                        | . 240<br>206 |

| 14.14          | String skip elements                                      | 240          |

| 14.15          | String locate element                                     | 247          |

| 14.16          | String scan                                               | 240          |

| 14.17          | String span                                               | 250          |

| 14.18<br>14.19 | String match                                              | 250          |

| 14.19          | Set parity in string                                      | 252          |

| 14.20          | oneck parity in string                                    | ۔ حرے        |

| 15 M           | ISCELLANEOUS INSTRUCTIONS                                 | . 253        |

| 1 = 1          | Disals many and Edil                                      | 255          |

| 15.1           | Block move and Fill                                       |              |

| 15.2           | Data type conversion                                      | 258          |

| 15.3           | Load address                                              | 250          |

| 15.4<br>15.5   | Load address into record register                         | 260          |

| 15.6           | Load address into base register                           | 261          |

| 15.7           | Load address of multilevel chain                          | 262          |

| 15.8           | Load index                                                | . 263        |

| 15.9           | Calculate index                                           | 264          |

| 15.10          | No operation                                              | 265          |

| 15.11          | Set flag                                                  | 266          |

| 15.12          | Clear flag                                                | 267          |

| 15.13          | Get buddy element                                         | . 268        |

| 15.14          | Free buddy element                                        | . 269        |

| 15.15          | PLCCN - Convert PLANC descriptor to ND-500 descriptor ('8 | 7<br>7       |

| *)•*)          | extension)                                                |              |

| 15.16          | NCPLC - Convert ND-500 descriptor to PLANC descriptor ('8 | 7            |

| 1).10          | extension)                                                | . 271        |

| 15.17          | CLINIT - Initialize local clock ('87 extension)           | . 272        |

|                | CLREAD - Read local clock ('87 extension)                 |              |

|                |                                                           |              |

| 16 5           | SPECIAL INSTRUCTIONS                                      | . 275        |

| 16.1           | Disable process switch                                    | . 277        |

| 16.2           | Enable process switch                                     | . 278        |

| 16.3           | Test and set                                              | . 279        |

| Sectio  | n                                                       |   | Page       |

|---------|---------------------------------------------------------|---|------------|

| 16.4    | Break noint                                             |   |            |

| 16.5    | Break point                                             | • | 280        |

| 16.6    | Set bit in trap enable register                         | • | 281        |

| 16.7    | Clear bit in trap enable register                       | • | 282        |

| •       | Load special register                                   |   | 283        |

| 16.8    | Store special register                                  |   | 284        |

| 16.9    | Integer float register communication                    |   | 285        |

| 16.10   | Data cache clear                                        |   | 286        |

| 16.11   | DDIRT - Dump dirty ('87 extension)                      |   | 287        |

| 16.12   | Program cache clear                                     |   | 288        |

| 16.13   | Data memory management on                               | • | 280        |

| 16.14   | Program memory management on                            | • | 200        |

| 16.15   | Data memory management off                              | • | 290        |

| 16.16   | Program memory management off                           | • | 291        |

| 16.17   | Read Written In Dags table                              | • | 292        |

| 16.18   | Read Written In Page table                              | • | 293        |

| 16.19   | Clear Written In Page bit                               | • | 294        |

| 16.20   | Clear Written In Page table                             | • | 295        |

|         | Read Page Used table                                    |   | 296        |

| 16.21   | Clear Page Used bit                                     |   | 297        |

| 16.22   | Clear Page Used table                                   | _ | 298        |

| 16.23   | Read 1/0 processor memory                               |   | 299        |

| 16.24   | Clear translation speedup buffer                        |   | 300        |

| 16.25   | Load bypassing cache                                    | • | 301        |

| 16.26   | OPERATING SYSTEMS SUPPORT INSTRUCTIONS                  | • | 202        |

| 16.26.  | RHOLE - read from NUCLEUS Hole ('87 extension)          | • | 302        |

| 16.26.  | WHOLE - write to NUCLEUS hole ('87 extension)           | • | 303        |

| 16.26   | S SEND - Send to port ('87 extension)                   | • | 304        |

| 16 26   | 1 RECVE - Receive from nearly (197                      | ٠ | 305        |

| 16 27   | RECVE - Receive from port ('87 extension)               | • | 306        |

| 16 27   | INSTRUCTIONS MANIPULATING REGISTER- AND CONTEXT BLOCK   | • | 307        |

| 16 27   | SREGBL - Save register block ('87 extension)            |   | 309        |

| 10.2/.2 | 2 LREGBL - Load register block ('87 extension)          |   | 310        |

| 10.2/.  | SUNIXI - Save context block ('87 extension)             |   | 211        |

| 10.2/.  | t LUNIXI - Load context block ('87 extension)           |   | 312        |

| 10.20   | REAL - Read from device external to CPU ('87 extension) |   | 212        |

| 16.29   | WEXT - Write to device external to CPH ('87 extension)  |   | 21/1       |

| 16.30   | TUSSP - Special load of TOS ('87 extension)             |   | 215        |

| 16.31   | RPHS - Read from physical segment ('87 extension)       | • | 216        |

| 16.32   | WPHS - Write to physical segment ('87 extension)        | • | 217        |

| 16.33   | CAD - load CAD ('87 extension)                          |   | 212        |

| 16.34   | JUMPS - Call supervisor ('87 extension)                 | • | 210        |

| 16.35   | SVERS - Store microprogram version ('87 extension)      | • | 213        |

|         | SCPUNO - Store CPU number ('87 extension)               | ٠ | 320        |

| 16.37   | PHYLADR - Get physical address ('87 extension)          | ٠ | 321        |

|         | This det physical address ("o/ extension)               | • | 322        |

|         |                                                         |   |            |

| 17 BI   | NARY CODED DECIMAL INCUDIORIONS (O )                    |   |            |

| -, DI   | NARY CODED DECIMAL INSTRUCTIONS (Option)                | • | 323        |

| 17.1    | Introduction                                            |   | 3.22       |

| 17.2    | Packed add                                              | • | 220        |

|         | Packed subtract                                         | • | ეე∪<br>221 |

| 17.4    | Packed multiply                                         | • | 222        |

|         | Packed compare                                          | • | 332        |

| 17.6    | Packed shift                                            | • | 333        |

| -1.5    | Packed shift                                            |   | 334        |

| Sectio                        | on                                     | Page                              |

|-------------------------------|----------------------------------------|-----------------------------------|

| 17.7<br>17.8<br>17.9<br>17.10 | Convert ASCII to packed                | <ul><li>336</li><li>337</li></ul> |

| APPEND                        | IX                                     |                                   |

| Α                             | Address codes                          | . 339                             |

| В                             | Address code table                     | . 343                             |

| С                             | Symbols and abbreviations              | . 347                             |

| D                             | New instructions - 1987 extension      | . 351                             |

| E                             | Instruction table                      | . 355                             |

| F                             | Alphabetical instruction table         | . 373                             |

| G                             | Instruction code table                 | . 381                             |

| Н                             | Instruction code cross reference table | . 393                             |

| I                             | Setting of status bits                 | . 401                             |

| Index                         |                                        | 1                                 |

# 1 INTRODUCTION

# 1.1 CPU Architecture and CPU Implementation

By introducing the ND-5000 systems, Norsk Data also introduces the ND-5000 CPU. This is the third generation of implementations of the ND-500 CPU architecture.

The CPU software architecture is still named ND-500, while the new systems, with the ND-5000 CPU implementation, are named the ND-5000 series computer systems. The concepts <u>software architecture</u> and <u>implementation</u> are outlined in table 1.

| CPU-                                                               | Name     | Systems                                    |

|--------------------------------------------------------------------|----------|--------------------------------------------|

| software architecture instruction set addressing modes trap system | ND-500   | All                                        |

| physical implementation                                            | ND-500/1 | ND-520/540/560 ND-510/530/550/ 560/570/580 |

|                                                                    | ND-5000  | ND-5X00                                    |

Table 1. CPU Architecture and CPU Implementation

The ND-5000 CPU runs the same instruction set, uses the same register set and the same addressing modes as the ND-500/1 and the ND-500/2 CPUs.

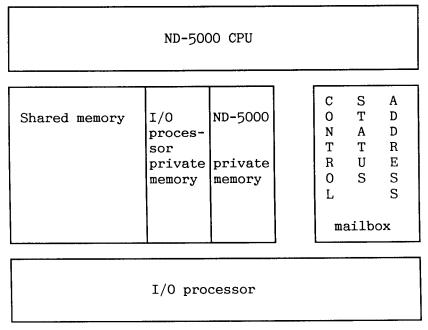

## 1.2 System configuration

The ND-5000 central processing unit is part of the ND-5000 computer system. This system is a combination of an I/O processor, an ND-5000 CPU and a shared memory, see figure 1. Until now the I/O processor has been an ND-100, but when the DOMINO I/O system is introduced, other types of I/O processors will be possible.

THE I/O PROCESSOR:

- Supervises the CPU

- Runs the  ${\rm I/O}$  system, file system, operating system and job scheduling

- Runs local I/O-processor jobs

# THE ND-500 type CPU:

- 32-bit logical address

- Addressing system implemented twice by the memory management system to allow user programs of 4 gigabytes of instructions and 4 gigabytes of data

- CPU shared by many user programs through efficient use of the memory management system

- Operations on data units ranging from 1 to 64 bits

- Byte-oriented instructions designed for efficient execution of high-level language programs

- Cache memory employing a forward fetch mechanism for main memory access

- Main memory access up to 16 bytes wide, eliminating the memory bandwidth bottleneck

- Two independent but identical cache systems, one for instructions and one for data

- The majority of machine level instructions requiring only one basic cycle

- Asynchronous floating point arithmetic for increased instruction execution speed

- Instruction and data pipelining techniques employed to optimize execution speeds

- Specialized high-speed hardware for 32/64-bit floating point multiplication and division

- Optional BCD hardware for operations on packed binary-coded decimal numbers.

## **MEMORY:**

- Multi Function Bus main memory with direct access for the ND-5000 CPU, the I/O processor CPU and DMA transfer devices

- Physical main memory up to 32 Mbytes

- Virtual memory management system

- Memory fully or partially shared between the I/O processor and ND-500 type CPU.

Figure 1. The ND-5000 computer system

# 1.3 Communication between the I/O Processor and the CPUs

All or part of the memory can be shared between the CPU, the I/O processor and associated I/O devices. This allows for easy access and control by all components of the system.

The communication between the I/O processor and the CPU is set up as a mailbox and DMA transfer system. The mailbox contains 3 registers:

- Control register: For the I/O processor to give the CPU a command

- Status register: For the CPU to give the I/O processor status

- Address register: A pointer to where in the I/O-processor memory a chain of message buffers will be found. Message buffers may contain commands or data from the I/O processor to the CPU or may be used by the CPU for storing extended status information

Some examples of commands to the CPU are context switch, reset, wait or data transfer.

The status information returned to the I/O processor reports that a job is finished, the reason for the CPU termination and the type of possible CPU malfunctions.

The CPU microprogram initiates and controls the DMA access channel to the I/0-processor memory. The communication channel is also used extensively for diagnostic and test program information. The I/0-processor is used as a diagnostic vehicle for the CPU.

# 1.4 Domains, segments and processes

The memory in an ND-500 type system is logically structured into DOMAINS. A domain has one 32-bit address area (4 gigabytes) for executable code (the program domain) and another one for data (the data domain).

Each domain is divided into SEGMENTS, with up to 32 per domain. A segment can be up to 128 Mbytes, which is equivalent to 27 address bits. The smallest unit for access protection (write and parameter access protection) is a segment. An instruction segment may access any data segment in the domain.

Two (or more) domains may have segments in common in order to share code or data.

A sequence of operations requiring no parallel execution is called a PROCESS. A process is carried out sequentially in the CPU, but several processes started at different times may, in effect, run concurrently. The processes, however, are "time-sliced".

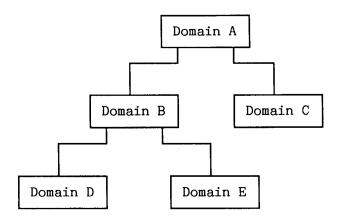

A process may refer to up to 256 domains of data and instructions. These are connected in a tree stucture called a domain tree, specified by the process description kept by the memory management system. The links between the domains are determined at the creation of each domain. The domain closest above (that is, closer to the root) a domain D is the mother of D, and D is the child. D may itself be the mother of other child domains.

Control can be switched from one domain to another by calling a routine in the other domain, or by causing an error situation (trap condition) not taken care of by a routine in the current domain. A routine may access data in the domain from which it was called through an address prefix (ALT).

Within a domain, routines are called directly by address. Routines in other domains are called through their routine number, not by address.

Communication between processes is possible through monitor calls or through a shared data segment.

## 2 THE REGISTER BLOCK

The ND-500 type CPU has four registers for program and data addressing. These are the program counter P, the L (link) register containing the subroutine return address, the local variable base register B, and the record base register R.

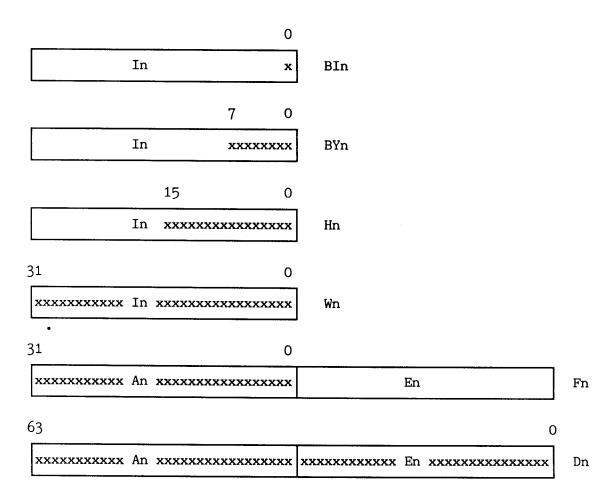

The four 32-bit general registers, I1, I2, I3, and I4, may be used as integer accumulators or as index registers. They are used for both word and partial word operations (halfword, byte, bit and bit field).

The A1, A2, A3, and A $^4$  registers are 32-bit floating-point accumulators used for real number arithmetic. Each floating point accumulator may be extended with a 32-bit Extension register (E1, E2, E3 and E $^4$ ), making four 6 $^4$ -bit floating point accumulators for double precision arithmetic.

The ND-5000 also has several special purpose registers:

| ST<br>OTE<br>CTE<br>MTE | Status register Own trap enable register Child trap enable register Mother trap enable register |

|-------------------------|-------------------------------------------------------------------------------------------------|

| TEMM                    | Trap enable modification mask                                                                   |

Table 2. 64-bit Special Purpose Registers

| TOS | Top of stack register         |

|-----|-------------------------------|

| LL  | Low limit trap register       |

| HL  | High limit trap register      |

| THA | Trap handler address register |

Table 3. 32-bit Special Purpose Registers

The ST, OTE, CTE, MTE and TEMM registers are treated as two 32-bit registers when referenced in instructions. The least significant parts (bits 0:31) are called ST1, OTE1, CTE1, MTE1 and TEMM1. The most significant parts (bits 32:63) are called ST2, OTE2, CTE2, MTE2 and TEMM2.

The memory management system utilizes a number of registers accessible only to the microprogram. These include:

| CED  | Cumpont occavities descis societies |

|------|-------------------------------------|

| V —— | Current executing domain register   |

| CAD  | Current alternative domain register |

| PS   | Process segment register            |

| PSTP | Physical segment table pointer      |

|      |                                     |

Table 4. Memory Management Utilized Registers

Each process in the system has its own copy of the CED, CAD and PS registers. PSTP is one global register for the whole system.

The context block is made up from these registers except from PSTP. In addition, it contains scratch registers named 'mic'. These are registers accessable from microprogram only, for use in macroinstructions that may be interupted while operating on more data than are handled by the general registers.

The registers are numbered according to the table below. Note that 64-bit registers are given consecutive numbers.

| arg1 : | Trapping P | arg17 | : | E4   | arg33 : | CTE1    |

|--------|------------|-------|---|------|---------|---------|

| 2 :    | P          |       | : | ST1  | 34 :    | CTE2    |

| 3 :    | L          | 19    | : | ST2  | 35 :    | MTE1    |

| 4:     | В          | 20    | : | PS   | 36:     | MTE2    |

| 5 :    | R          | 21    | : | TOS  | 37 :    | TEMM1   |

| 6:     | I1         | 22    | : | LL   | 38:     | TEMM2   |

| 7 :    | 12         | 23    | : | HL   | 39:     | mic     |

| 8:     | 13         | 24    | : | THA  | 40 :    | mic     |

| 9:     | 14         | 25    | : | CED  | 41-50:  | copy of |

| 10:    | A1         | 26    | : | CAD  |         | program |

| 11:    | A2         | 27    | : | mic  |         | memory  |

| 12:    | A3         | 28    | : | mic  |         |         |

| 13:    | A4         | 29    | : | mic  |         |         |

| 14:    | E1         | 30    | : | mic  |         |         |

| 15:    | E2         | 31    | : | OTE1 |         |         |

| 16:    | E3         | 32    | : | OTE2 |         |         |

|        |            | , ,   | • |      |         |         |

Table 5. Register Numbers

| 31      | 0     |        |                                                                               |  |  |  |  |

|---------|-------|--------|-------------------------------------------------------------------------------|--|--|--|--|

|         | P     |        | Program counter                                                               |  |  |  |  |

|         | L     |        | Link (subroutine return address)                                              |  |  |  |  |

|         | В     |        | local variable Base                                                           |  |  |  |  |

|         | R     |        | Record base                                                                   |  |  |  |  |

|         | TOS   |        | Top Of Stack register  Low Limit trap register                                |  |  |  |  |

|         | LL    |        |                                                                               |  |  |  |  |

|         | HL    |        | High Limit trap register                                                      |  |  |  |  |

|         | THA   |        | Trap Handler Address register                                                 |  |  |  |  |

|         |       |        |                                                                               |  |  |  |  |

|         | I1    |        | Integer accumulators                                                          |  |  |  |  |

|         | 12    |        | or Index registers                                                            |  |  |  |  |

|         | 13    |        | The In accumulators are named BIn, BYn, Hn and Wn when used                   |  |  |  |  |

|         | 14    |        | for BIt, BYte, Halfword or Word operations (n=1,2,3,4).                       |  |  |  |  |

| 1<br>63 |       | ı<br>O |                                                                               |  |  |  |  |

| Γ       | A1    | E1     | Floating point accumulators and Extension registers                           |  |  |  |  |

|         | A2    | E2     | A=E= 32 bits, D=A+E= 64 bits                                                  |  |  |  |  |

| -       | A3    | E3     | The An accumulators are named Fn when used as single-precision floating point |  |  |  |  |

| -       | A4    | E4     | registers. The (An, En) register pair is named Dn when used as double-        |  |  |  |  |

| L       | П¬    | LT     | precision floating-point registers.                                           |  |  |  |  |

| Г       | ST1   | ST2    | STatus register                                                               |  |  |  |  |

| -       |       |        | Own Trap Enable register                                                      |  |  |  |  |

| -       | OTE1  | OTE2   | •                                                                             |  |  |  |  |

| -       | MTE1  | MTE2   | Mother Trap Enable register                                                   |  |  |  |  |

| -       | CTE1  | CTE2   | Child Trap Enable register                                                    |  |  |  |  |

|         | TEMM1 | TEMM2  | Trap Enable Modification Mask                                                 |  |  |  |  |

Figure 2. The Register Block

## 3 STATIC DATA, STACK AND HEAP

When a subroutine is called, space is required to store return information and local variables. This space may be allocated

- in a fixed location in memory, referenced relative to the B register or by absolute address (static allocation)

- on a stack growing from low to high memory, referenced relative to the B register

- in a block released from a freelist. The block may be anywhere in otherwise unused memory, referenced relative to the B register.

Static or dynamic allocation of the local data area of a routine is determined by the kind of entry point instruction, and a program system may contain a mixture of procedures with statically and dynamically allocated data areas.

The initialization of the header of the local data area is in most respects equivalent for static, stack and heap allocation. Usually, the calling procedure need not be concerned with the allocation strategy used.

# 3.1 Static allocation

Data allocated in fixed locations may be addressed by a full 32-bit address referencing any segment within the domain. Statically allocated data are not released during program execution for other use, and local variables in routines keep their values from one call to the next.

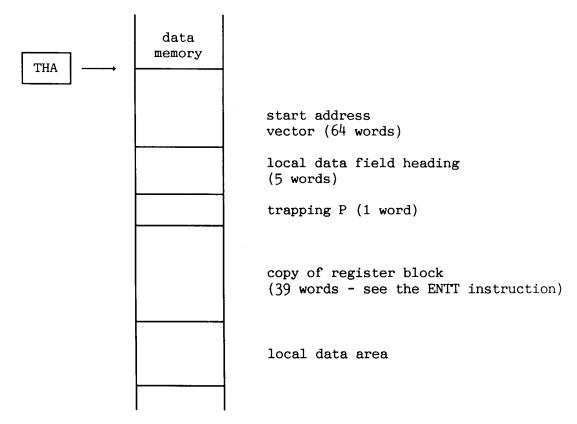

Routines with static data areas are entered through an ENTF or ENTFN instruction. Such routines are by definition non-reentrant and cannot be called recursively, but in other respects they behave like other routines. The fixed local data area is initialized as shown in figure 3. The B register is updated to point to the local data area and data references may be addressed relative to the B register, as with stack routines, and may also be addressed directly.

Trap handlers always have a fixed local data area which has a special layout discussed in chapter 6.

#### 3.2 Stack allocation

A stack is initialized through the INIT or ENTM instruction, either one can declare the lowest stack address and its maximum extent. When a stack is initialized, the TOS register is loaded with the address of the first free location beyond the stack's maximum extent. TOS serves to prevent the stack from growing too large, and as a pointer to the variables describing the heap. The first free location beyond the current extent of the stack is pointed to by the B.SP location.

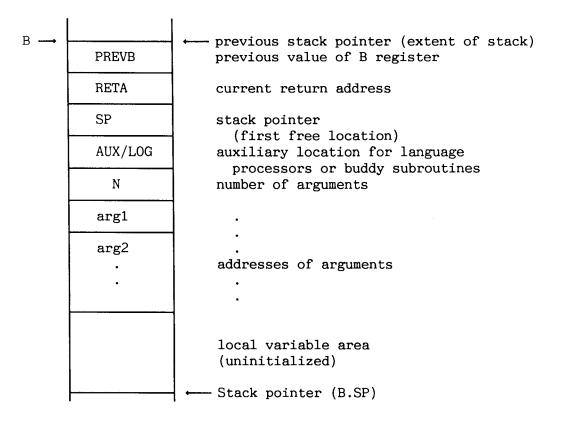

A new data block on the stack is allocated by executing an ENTS or ENTSN instruction. On routine entry the data block is automatically initialized as follows:

Figure 3. Local Data Area Layout

If the number of arguments supplied exceeds the maximum allowed by the ENTSN entry point instruction, only the maximum allowed number of argument addresses will be put on the stack and the N location will contain the value of the "maximum number of arguments" operand. (This also applies to the ENTFN instruction.)

The INIT instruction initializes the stack in a similar way, but the PREVB and RETA will be zeroed, so that an attempt to link downwards beyond the lower stack address will cause an Address Zero or Stack Underflow trap.

The ENTM instruction initializes a new stack starting from a specified address, giving the TOS register a new value. If the module called is within the current domain, the old TOS value is saved on the current

top of the old stack, pointed to by B.SP. Initialization of the new stack is the same as for a routine entry; the base address of the previous stack block is saved in PREVB. If the module is in another domain, TOS, PREVB and RETA are stored in the domain information table and restored on return.

The ENTM is typically used for initializing a stack for the routines on a segment, being called from other segments in the same domain or from other domains. Executing the same ENTM instruction twice will overwrite the old initial values, possibly destroying the return address and other information.

Stack space is released through the RET or RETK instructions. The B register is loaded from the PREVB location. On exit from a module (a subroutine entered through ENTM) in the current domain, the TOS register is <u>not</u> updated; this must be done explicitly. After a domain call, TOS is restored from the domain information table.

Stack displacements (relative to the B register) are always non-negative, the displacement being the number of bytes to add to the B register. The symbols PREVB, RETA, SP, AUX and N are predefined as 0, 4, 8, 12 and 16 respectively.

### 3.3 Heap allocation

When running several routines "concurrently" (see section 1.4), stack allocation of local data areas will cause problems if the routine finishing first is not the one with its data area on top of the stack.

Complex data structures like trees, lists and networks, may grow and shrink dynamically, and elements acquired during the execution of a procedure should not be released upon exit.

For both these uses, data elements may be allocated from a pool of unreserved space called the heap. The heap is described by a set of heap variables pointed to by the TOS register. The heap variables are the MAXL, STAH and ENDH locations and an array of pointers to linked lists of free elements, each block size has its own free list. The first word of an element contains the address of the next element in the list, zero indicating the end of the list. The block size is always a power of two and is indicated by the logarithm to the base two (the "log size") of the number of words.

MAXL, the first location beyond the stack, is pointed to by the TOS register and contains the maximum size of elements to be allocated. The next two locations, STAH and ENDH, are reserved for the lower and upper address limits of the pool respectively. Beyond these two locations is the array of pointers, FLOGO to FLOG<MAXL>.

|        | l I                | 1                                                                         |

|--------|--------------------|---------------------------------------------------------------------------|

| TOS -> | MAXL               | Max log size of elements allowed                                          |

|        | STAH               | Start of heap                                                             |

|        | ENDH               | End of heap                                                               |

|        | FLOG0              | Head pointers for freelists of                                            |

|        | FLOG1              | elements of the different log sizes. The freelist pointers have the value |

|        | FLOG2              | O if no element of the log size is available.                             |

|        | FLOG3              |                                                                           |

|        | •                  |                                                                           |

|        | •                  |                                                                           |

|        | •                  |                                                                           |

|        | FLOG <maxl></maxl> |                                                                           |

|        |                    |                                                                           |

Figure 4. Layout of heap variables

The heap variables must be initialized by the user program and the user is responsible for building the lists. The STAH and ENDH variables are not used by the heap instructions, but are available for a heap administration routine implemented as a trap handler for the stack overflow trap.

A local area for use by a subroutine may be allocated by executing the ENTB instruction. This contains an indication of the required block size. On routine entry, the address of the allocated block is loaded into the B register, and the block size is stored in the AUX/LOG location. In all other respects the local data area is initialized as for a stack routine.

A data element is allocated by the GETB instruction, which specifies the size of the desired element. The address of the element is loaded into the specified register.

If a block of the requested size is available, it is unlinked from the list. If the list head is zero, indicating that the list is empty, lists representing larger blocks are examined. If a larger block is available, it is split in halves and one half is left in the appropriate freelist. The block may have to be split several times before an element of the requested size can be given to the program. If no larger element is available, or if the requested size is larger than the MAXL value, a stack overflow trap condition occurs.

A routine entered through ENTB may release its local data area by returning through the RETB or RETBK instruction. An element acquired by the GETB may be released by the FREEB instruction.

A released element will be linked to the appropriate freelist according to the size of the element. Elements are not combined; this may be done by the trap handler for the stack overflow trap condition.

The stack overflow trap is used to signal that all lists containing blocks of wanted size or larger are empty.

Be aware that initializing a new stack by INIT or ENTM will change TOS, thus another set of heap variables will be used by the buddy instructions. The new heap variables may be initialized to the values of the old ones or to new values.

If ENTB is used to allocate space for co-routines, care should be exercised if the called routines make further calls to stack routines. When co-routines use a common stack and a second co-routine is activated before the return, the stack areas will overlap because B.SP is the same in both routines. No problems will occur if all routines in the system are entered through ENTB or if the stack routine is certain to terminate before another co-routine is activated. (Standard library routines may be used freely; they will not cause activation of other co-routines.)

No assumptions should be made about initial values of locations of stack or heap elements not explicitly mentioned in this chapter.

#### 4 MEMORY MANAGEMENT SYSTEM

#### 4.1 Introduction

A process is a sequential computation requiring no parallel execution. A process may refer to up to 256 domains. Each domain is a full 32-bit address area for program instructions and another one for data. A process may easily access two such data domains, the so-called Current Executing Domain (CED) and the Current Alternative Domain (CAD). Instructions will always be fetched from CED, but data will be taken from CAD when the address code prefix ALT is used. If ALT is omitted, data accesses will be done in CED.

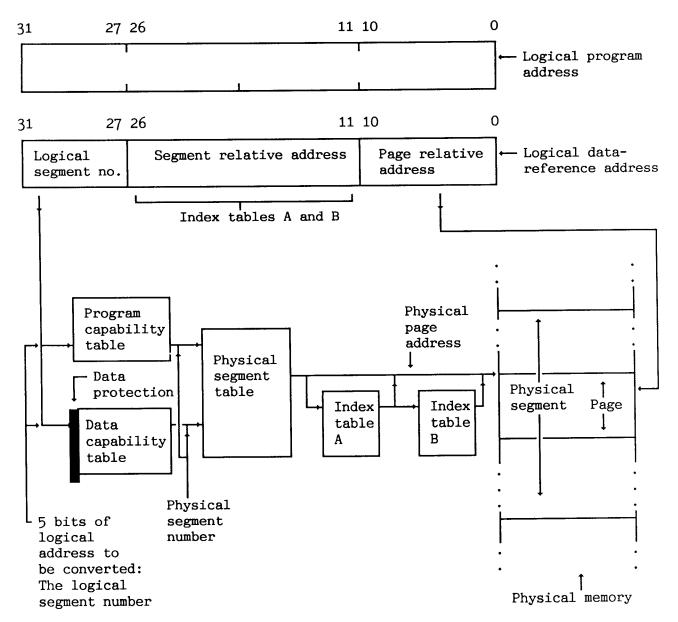

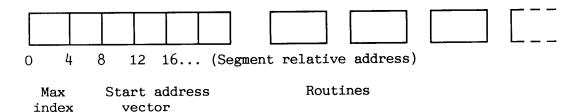

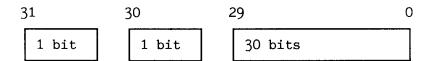

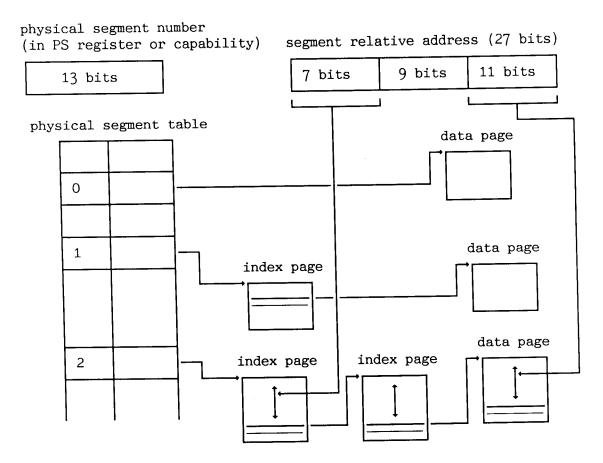

Each domain is divided into 32 logical segments with 27 address bits each. A 27-bit logical segment address is translated by the memory management system so that it addresses a location in a so-called physical segment. Physical segments contain the data and programs for the CPU. A physical segment is divided into blocks of 2k bytes called pages, and may have any size from 2\*\*11 to 2\*\*27 bytes in units of 2k bytes (1 page). Pages can be moved (swapped) between main memory and secondary storage as the need arises.

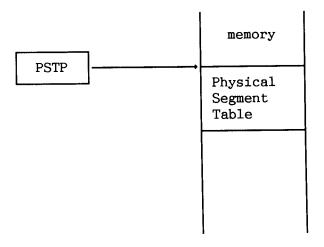

All physical segments in the system are described in the Physical Segment Table (PST). The PST always resides in the main memory and it is used by the translation mechanism to find the physical segment. If a physical segment consists of more than one page, an indexing mechanism is used to address the segment. Each physical segment is described by a 16-bit entry in PST.

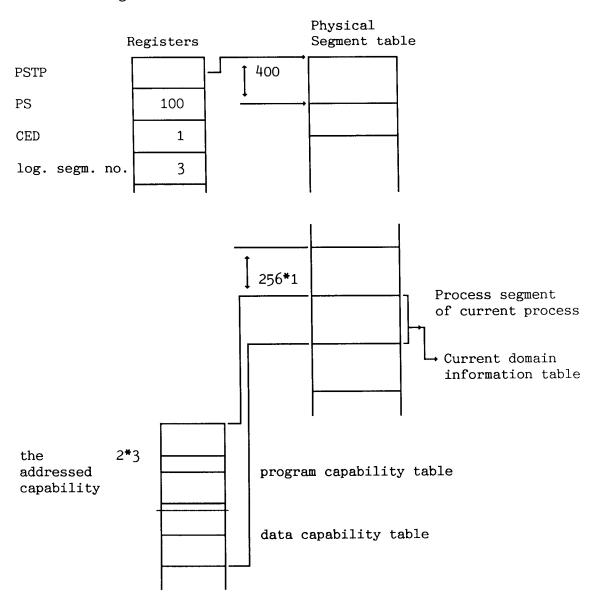

By following this scheme each process may use up to 256\*32 physical segments of program, and an equal number of physical segments of data. The structure and properties of the domains and segments of a process are kept on a special physical segment generated and maintained by supervising mechanisms. This physical segment is called the Process Segment (PS). There is one PS for each process in the CPU. The size of a PS will depend on the number of domains the process can use.

The PS of a process cannot be accessed directly by the process itself. It is used by supervising mechanisms which may be other processes, other domains or the I/O processor. Each domain used by a process has one entry in the PS.

One part of the process segment is called the domain information table. A domain information table contains 32 pointers for data (the data capability table) and 32 pointers for program (the program capability table), one pointer for each logical segment of the domain. The pointers indicate the PST entry describing the physical segment to be addressed by the logical address. Information on legal access modes for each logical segment is also kept in the domain information table, together with the pointers. One PST pointer with the corresponding legal access mode indicators is called a capability. The domain information table also contains the necessary information for the trap and domain call system.

The PS of a process will be referenced frequently when the process

executes. Since the PS is an ordinary physical segment, it will be addressed through the PST entry that describes it. A pointer to the PST entry describing the PS of the executing process is kept in the PS register and is updated when a new process starts execution. The PS register is part of the process description of a process, together with the contents of the register block and some other information.

This scheme for the translation from logical to physical addressing makes it easy for different domains or processes to share data or programs. Sharing is done by having the capabilities in the different domain information tables point to the same PST entry. By doing this, the same physical segment will be addressed.

If the translation mechanism were to perform all the outlined table lookups on each memory access, the result would be unacceptably slow. A speed-up mechanism is therefore introduced. Whenever an access is completed, the number of the referenced page is stored in a cache-like Translation Speedup Buffer (TSB). The physical page number is stored together with the corresponding logical page number, the domain number and a process identification. The next time an access to the same logical page is done by the same domain, the physical page number is found in TSB without any need to perform other lookups. The index in the TSB is found by using a hashing algorithm that takes into account the logical address including the segment number, the domain number and the process identification.

The detailed description that follows is divided into the Memory Management Architecture and its Physical Implementation. The architecture section involves the transformation from logical to physical segment numbers, and includes descriptions of the capability tables and the process segment. The implementation section covers the mechanisms by which physical segments are placed and accessed in main memory. The present architecture is implemented with a paging mechanism, but no inherent property of the architecture prohibits other implementation strategies.

Figure 5. Logical addressing scheme

## 4.2 Memory management architecture

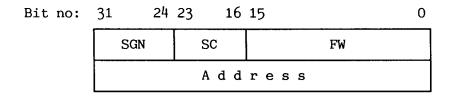

## 4.2.1 Address domain

An address has 32 bits, i.e. is in the range 0 to (2\*\*32)-1. Instruction fetches and data references refer to different areas of the memory. If the memory request is an instruction fetch, the address value range is called a program domain. If the memory request is a data reference, the address value range is called a data domain.

A logical address domain is divided into 32 segments. The 5 upper bits of an address are the segment number and the 27 lower bits are the address within the segment.

5 bits 27 bits

Logical segment no. Segment relative address

Figure 6. Logical Address

If the program or data domain is not explicitly stated, the domain is understood to be both the program domain and its corresponding data domain.

The division of domains into segments makes different protection and cache setup possible for each segment (see figure 9).

The scheme does not, however, forbid accesses to data structures crossing segment borders as long as the access capabilities are the same for both segments.

#### 4.2.2 Process

The operations of a computation must be carried out in a certain order to ensure a meaningful result. The simplest possible rule is to execute the operations one at a time in strict sequential order. This type of computation is called a process.

Information about a process is kept in the process description. The term process will hereafter mean a sequential computation described by a process description.

An ND-500 process may have up to 256 different logical domains, each comprising an address space of up to  $2^{**}32$  bytes of program and  $2^{**}32$  bytes of data.

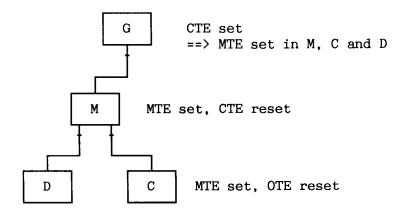

The domains of a process are hiearchically structured in a tree. The closest domain above a domain D is called the mother domain of D; D is called the child. In figure 7, D and E are both child domains of B; B is their mother. A is the mother of B and C. The hierarchical structure is reflected in the process description.

Figure 7. Hierarchy of Domains

Transfer of control between domains may take place by routine calls (domain calls) or enabled traps. Routine calls may transfer control to any of the domains of the process. The child-to-mother links are followed when a trap occurs in a child domain and no trap handler is defined locally in the child domain.

Parameter transfer between different domains is performed by the alternative address mode. (See section about addressing modes.) When a routine in domain A calls a routine in domain B, domain A is set as alternative domain to B and operands accessed via alternative address mode are accessed in domain A.

More extensive data exchanges and exchanges between arbitrary domains are done by letting the domains have one or more data segments in common.

## 4.2.3 Process environment

The memory management system needs information about existing processes. This information resides on a physical segment, the Process Segment. This segment is not directly accessible to the process, but is used by microcode routines and by supervising mechanisms, which may be other processes, other domains or the I/O processor. There is one process segment for each process; the number of this segment is held in the Process Segment register (PS). For each domain owned by the process, the process segment contains one domain information table which consists of

- the program capability table

- the data capability table

- domain call information

- trap handling information

## 4.2.3.1 Process registers

| CED | Current Executing Domain   |

|-----|----------------------------|

| CAD | Current Alternative Domain |

| PS  | Process Segment            |

Figure 8. Memory management registers

Some information about a process is used so frequently by the memory management system that it must be kept in hardware registers while the process is executing. The three registers CED, CAD and PS are part of the process description of the running process, i.e. the registers' contents are saved and loaded when the process is changed.

The Current Executing Domain register holds the current domain number of the currently executing process. When a domain call is performed, or when a trap condition is not own but mother enabled, the domain number of the calling domain is stored in the Current Alternative Domain register. CAD is used with the alternative addressing mode.

### 4.2.3.2 Capability tables

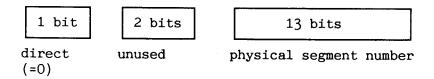

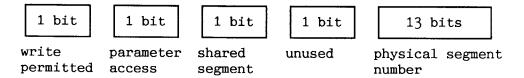

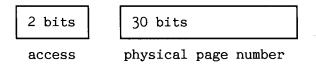

Each domain has two capability tables, one for instructions and one for data. Each table has 32 elements, one for each segment in the domain. Each element consists of 16 bits, numbered from 0 to 15. Such an element is called a capability, and it specifies the physical segment number and its access rights. A program capability has a layout different from a data capability.

In a program capability, bit 15 indicates whether the segment is in the current domain or not. If the bit is zero, the segment is in the

current domain. A segment not in the current domain, called an indirect segment, has bit 14 set if the physical segment resides in another machine, otherwise it is reset. The capability of an indirect segment contains the logical domain and segment numbers of another segment, and the physical segment number is found in the capability of that segment.

In a data capability, bit 15 indicates write permission. If this bit is reset, the segment is a read-only segment. Bit 14 indicates whether routines in other domains may refer to this segment through the ALT prefix. Violation of the protection set by these two bits causes a protect violation trap. Bit 13 is set if the physical segment is shared between different domains or different processes. If a segment is shared, data will always be read from main memory rather than from cache to ensure that different processes are aware of each other's updating of a data item.

Direct program segments and data segments contain the physical segment number in the lower 13 bits.

Program segment capability:

## a) Direct segment

#### b) Indirect segment

Data segment capability:

Figure 9. Capability Layout

### 4.2.3.3 Domain information

When performing domain calls and trap handling, some extra table space is needed for each domain. The first part of a domain information is made up of 2 capability tables. The next part has two save areas; one used when performing domain calls, and one used during trap handling. The last part holds the domain characteristics.

All the above constitute one domain information table. This table is followed by an unused area to a total size of 256 bytes.

The "category" column below uses the following abbreviations:

M - set by hardware at domain call

T - set by hardware at trap handling

0 - set by operating system and read by hardware

The domain information table layout is shown on the next page.

|    |                                                                                                                                                                                                                                       | Relative<br>address                                     |                                                              | No.of<br>bytes                       | Cate-<br>gory                                              |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------|--------------------------------------|------------------------------------------------------------|

| a. | Program capability table                                                                                                                                                                                                              |                                                         | OB                                                           | 64                                   | 0                                                          |

| b. | Data capability table                                                                                                                                                                                                                 |                                                         | 100B                                                         | 64                                   | 0                                                          |

| c. | Domain call information Calling domain Alternative of calling domain P of calling domain B of calling domain                                                                                                                          | P<br>B                                                  | 200B<br>201B<br>203B<br>207B                                 | 1<br>1<br>4<br>4                     | M<br>M<br>M<br>M                                           |

| d. | Trap handling information Trapped domain Alternative of trapped domain Status register save area Inside trap handler flag                                                                                                             | ST1<br>ST2                                              | _                                                            | 1<br>1<br>4<br>4<br>1                | T<br>T<br>T<br>T                                           |

| е. | Domain characteristics Own trap enable Child trap enable Mother trap enable Trap enable modification mask Trap handler address Mother domain Top of stack register Low limit register High limit register Domain status (PiA = bit 0) | OTE1 OTE2 CTE1 CTE2 MTE1 MTE2 TEMM1 TEMM2 THA TOS LL HL | 236B<br>242B<br>246B<br>252B<br>256B<br>262B<br>266B<br>272B | 4<br>4<br>4<br>4<br>4<br>4<br>4<br>4 | O/M<br>O/M<br>O<br>O<br>O<br>O<br>O/M<br>O/M<br>O/M<br>O/M |

Table 6. Domain Information Table

## 4.2.4 Logical addressing

A logical address consists of the logical segment number and the segment relative address. The memory management system will transform the logical segment number to a physical segment number. The segment relative address is relative to the start of the physical segment.

The logical segment number is used as an index in the capability table. The addressed element in this table gives the physical segment number.

### 4.2.5 Domain communication

Within the domain hierarchy of the process, program control may change from one domain to another. Data may be accessed in either the called or the calling domain. In this section change of control and communication between different domains are described.

# 4.2.5.1 Alternative domain

The alternative domain is used when accessing and returning parameters from or to a calling domain. The calling domain is set as the alternative to the called domain by loading its number into the CAD register. This is done by hardware at a domain call. Access to operands in the alternative domain is by the alternative address code prefix, ALT(operand). When using the ALT address code prefix, only the final data access goes to the alternative domain; indirect addresses and descriptors are taken from the current domain. (See the chapter on operand specifiers and addressing modes for further explanation.)

The calling domain may protect its data from illegal access from other domains by resetting the parameter access bit of its capability. This is done through monitor calls.

#### 4.2.5.2 Domain calls and monitor calls

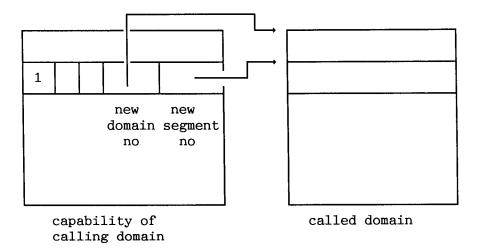

From one domain, a routine on any other domain of the process may be called through the CALL and CALLG instructions. This is only possible if an indirect capability to that domain has been set up. This is indicated by bit 15 being set in the capability of the segment. An indirect capability is set up through monitor calls. An indirect segment resides in another domain than the current one. A call to a routine on such a segment implies a change of domain, and is referred to as a domain call.

Domain calls to supervising domain routines performing specific functions are called monitor calls. Service requests to the operating system are implemented as monitor calls.

Figure 10. Indirect segment

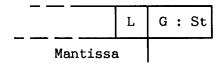

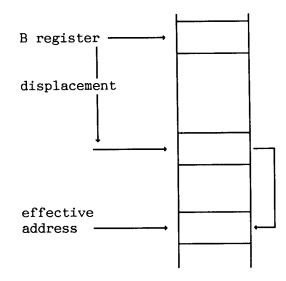

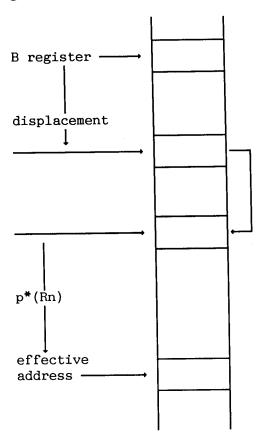

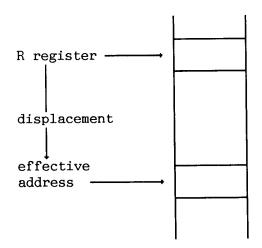

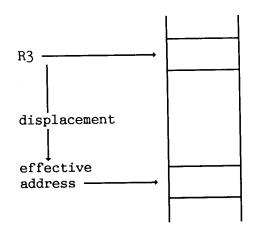

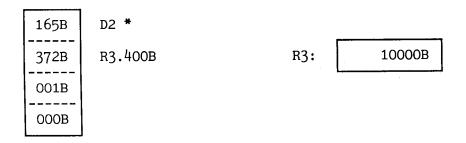

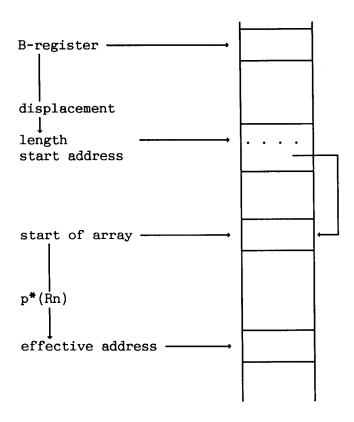

The new domain and segment number are taken from the capability of the calling segment. The P and B registers, domain number and alternative domain number of the calling domain are saved in the domain information table of the called domain. When a subroutine is called, certain initializations of the local data field are made. (See the CALL, CALLG and ENTM instructions.) The return address and old base register field of the local data field of the new routine are filled with zeroes.