# CATALOG 1977

Xezoie 03130 NEC

E DXSe

BOBOAF PISZE NEC 03720 K66011

# NEC micro computers, inc.

##

## CONTENTS

1. Numerical Index

2. Memories Index Selection Guide Alternate Source Guide

- **3.** Random Access Memories (RAMs) Dynamic Static

- **4.** Read Only Memories (ROMs) Electrically Eraseable (EEPROMs) Field Programmable (PROMs) Mask Programmable (ROMs) ROM Ordering Information

- 5. New Memory Products RAMs EPROMs

- 6. Microcomputers Index Selection Guide Alternate Source Guide

- **7.** μCOM-4 Microcomputers

- 8. μCOM-8 Microcomputers Processors Peripherals New Products

- **9.** New Microcomputer Families

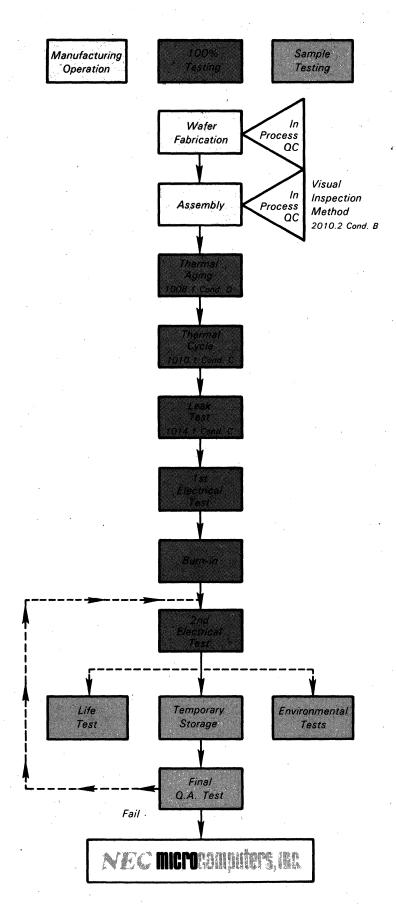

- 10. Reference Section Representatives and Distributors  $\mu$ COM-8 Microcomputer Program Card Process Flow Chart

# NEC MICTOCOMPUTERS, INC.

## NUMERICAL INDEX

| •                                     |                       |                       |      |

|---------------------------------------|-----------------------|-----------------------|------|

| PRODUCT                               | ÷.,                   | · P/                  | AGE  |

| μ <b>PD371</b>                        |                       |                       | 175  |

|                                       |                       |                       |      |

| μPD379                                |                       |                       | 189  |

|                                       |                       |                       |      |

| μ <b>PB405</b>                        |                       |                       |      |

| μ <b>PB406</b>                        |                       |                       |      |

| μ <b>PB408</b>                        |                       |                       |      |

| p                                     |                       |                       |      |

| P                                     |                       | • • • • • • • • • • • |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

| P                                     | ••••••••••            |                       |      |

|                                       |                       |                       |      |

| p                                     | • • • • • • • • • • • |                       |      |

| μ <b>PD418</b>                        |                       |                       | ,    |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       |                       |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | •••••                 |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | ••••••                |                       |      |

| • • • • • •                           |                       |                       |      |

| p                                     | •••••                 |                       |      |

| p                                     | ••••                  |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

| ··· · · · · · · · · · · · · · · · · · | •••••                 |                       |      |

| μPD2102AL                             |                       |                       |      |

| μPD2111AL                             |                       |                       |      |

|                                       | . <i>.</i>            |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

|                                       | • • • • • • • • • • • |                       |      |

| μ <b>PB2401</b>                       |                       |                       | .124 |

| PRODUCT PA       | GE  |

|------------------|-----|

| μPD2716          | 27  |

| μPB2901          | 251 |

| μPB2902          | 251 |

| μPB2905          | 251 |

| μPB2906          | 251 |

| μPB2907          |     |

| μΡΒ2909          | 251 |

| μPB2911          | 251 |

| μPB2915          |     |

| μPB2916          |     |

| μPB2917          |     |

| μPB2918          |     |

| μPD41041         |     |

| μPD5101          |     |

| μPD5101L         |     |

| μPD65081         |     |

| μPD8035          |     |

| μPD8048          |     |

| μΡ <b>D8080A</b> |     |

| μPD8080AF1       |     |

| μPD8085          |     |

| μPD8155          |     |

| μPD8156          |     |

| μΡΒ8212          |     |

| μPB8214          |     |

| μPB8216          |     |

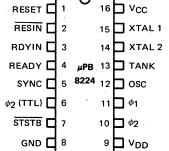

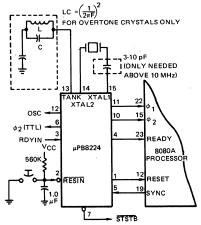

| μPB8224          |     |

| μΡΒ8226          |     |

| μPB8228          |     |

| μPB82381         |     |

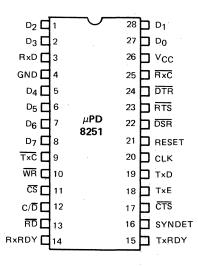

| μPD8251          |     |

| $\mu$ PD8253     |     |

| p. 20200         |     |

| μPD8255A         |     |

| μPD8257          |     |

| $\mu$ PD8259     |     |

| μΡD8355          |     |

| μΡD8748          |     |

| μΡD8755          |     |

| μευ2.ου          | .01 |

#

## **MEMORY INDEX**

| RANDOM ACCESS MEMORIES           Dynamic RAMs         PAGE           μPD411         9           μPD411A         16           μPD411-M         24           μPD414         29           μPD416         37           μPD418         46 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Static Bipolar RAMs<br>μPB2205                                                                                                                                                                                                       |

| Static MOS RAMs         54           μPD410         54           μPD2101AL         58           μPD2102AL         63           μPD2111AL         67           μPD5101         72           μPD5101L         77                       |

| READ ONLY MEMORIESElectrically Erasable Programmable ROMsμPD454μPD45888                                                                                                                                                              |

| Field Programmable ROMs         μPB403         96           μPB405/425         100         100           μPB406/426         104         104                                                                                          |

| Mask Programmable ROMs         108           μPD464         108           μPD2308         112           μPD2316A         115           μPD2332         119           ROM Ordering Information         122                            |

| NEW PRODUCTS           RAMs $\mu$ PD414A         123 $\mu$ PD6508         123 $\mu$ PD2114         124 $\mu$ PB2400/2401         124 $\mu$ PD4104         125                                                                        |

| PROMs         126           μPB427         126           μPD2716         127           μPD2316E         127                                                                                                                          |

#

## MEMORY SELECTION GUIDE

|              |                                |               |              |         | SUPPLY      | PACKAG   | GE   |

|--------------|--------------------------------|---------------|--------------|---------|-------------|----------|------|

| DEVICE       | SIZE                           | TECHNOLOGY    | ACCESS TIME  | CYCLE   | VOLTAGES    | MATERIAL | PINS |

| х<br>х       | DYNAMIC RANDOM ACCESS MEMORIES |               |              |         |             |          |      |

| μPD411       | 4K x 1 TS                      | NMOS          | 150 ns       | 380 ns  | +12, +5, -5 | Cerdip   | 22   |

| μPD411-4     | 4K x 1 TS                      | NMOS          | 135 ns       | 320 ns  | +15, +5, -5 | Cerdip   | 22   |

| μPD411A      | 4K x 1 TŚ                      | NMOS          | 200 ns       | 400 ns  | +12, +5, -5 | Plastic  | 22   |

| μPD411M      | 4K x 1 TS                      | NMOS          | 200 ns       | 400 ns  | +12, +5, -5 | Cerdip   | 22   |

| μPD418       | 4K x 1 TS                      | NMOS          | 200 ns       | 400 ns  | +12, -5     | C/P      | 18   |

| μPD414       | 4K x 1 TS                      | NMOS          | 200 ns       | 375 ns  | +12, +5, -5 | C/P      | 16   |

| μPD414A (F)  | 4K x 1 TS                      | NMOS          | 150 ns       | 320 ns  | +12, +5, -5 | C/P      | 16   |

| μPD416       | 16K x 1 TS                     | NMOS          | 150 ns       | 375 ns  | +12, +5, -5 | C/P      | 16   |

|              |                                | STATIC RA     | ANDOM ACCESS | MEMORIE | S           |          |      |

| μPD2101AL    | 256 x 4 TS                     | NMOS          | 250 ns       | 250 ns  | +5          | Plastic  | 22   |

| µPD2102AL    | 1K x 1 TS                      | NMOS          | 250 ns       | 250 ns  | +5          | Plastic  | 16   |

| μPD2111AL    | 256 x 4 TS                     | NMOS          | 250 ns       | 250 ns  | +5          | Plastic  | 18   |

| μPD5101      | 256 x 4 TS                     | CMOS          | 800 ns       | 800 ns  | +5          | Plastic  | 22   |

| μPD5101L     | 256 x 4 TS                     | CMOS          | 450 ns       | 450 ns  | +5          | Plastic  | 22   |

| μPB2205      | 1K x 1 OC                      | Bipolar       | 50 ns        | 50 ns   | +5          | Cerdip   | 16   |

| μPD410       | 4K x 1 TS                      | NMOS          | 100 ns       | 220 ns  | +12, +5, -5 | Cerdip   | 22   |

| μPB2400 (F)  | 4K x 1 OC                      | Bipolar       | 50 ns        | 50 ns   | +5          | Cerdip   | 18   |

| μPB2401 (F)  | 4K x 1 TS                      | Bipolar       | 50 ns        | 50 ns   | +5          | Cerdip   | 18   |

| μPD4104 (F)  | 4K x 1 TS                      | NMOS          | 200 ns       | 3.10 ns | +5          | C/P      | 18   |

| μPD2114 (F)  | 1K x 4 TS                      | NMOS          | 300 ns       | 300 ns  | +5          | C/P      | 18   |

| μPD6508 (F)  | 1K x 1 TS                      | CMOS          | 200 ns       | 200 ns  | +5          | C/P      | 16   |

|              | 1                              | MASK PROGRA   | MMED READ ON |         | DRIES       |          |      |

| μPD464       | 256 x 8 TS                     | NMOS          | 450 ns       | 450 ns  | +12, +5     | C/P      | 24   |

| μPD2308      | 1K x 8 TS                      | NMOS          | 450 ns       | 450 ns  | +12, +5, -5 | Cerdip   | 24   |

| μPD2316A     | 2K x 8 TS                      | NMOS          | 450 ns       | 450 ns  | +5          | C/P      | 24   |

| μPD2316E (F) | 2K x 8 TS                      | NMOS          | 450 ns       | 450 ns  | +5          | C/P      | 24   |

| μPD2332      | 4K x 8 TS                      | NMOS          | 450 ns       | 450 ns  | +5          | C/P      | 24   |

|              |                                | FIELD PROGRAM | MABLE READ C |         | NORIES      |          |      |

| μPB403       | 256 x 4 OC                     | Bipolar       | 60 ns        | 60 ns   | +5          | Cerdip   | 16   |

| μPB405       | 512 x 8 OC                     | Bipolar       | 70 ns        | 70 ns   | +5          | Cerdip   | 24   |

| μPB425       | 512 x 8 TS                     | Bipolar       | 70 ns        | 70 ns   | +5          | Cerdip   | 24   |

| μPB406       | 1K x 4 OC                      | Bipolar       | 70 ns        | 70 ns   | +5          | Cerdip   | 18   |

| μPB426       | 1K x 4 TS                      | Bipolar       | 70 ns        | 70 ns   | +5          | Cerdip   | 18   |

| μPB408 (F)   | 1K x 8 OC                      | Bipolar       | 85 ns        | 120 ns  | +5          | Cerdip   | 24   |

| μPB428 (F)   | 1K x 8 TS                      | Bipolar       | 85 ns        | 120 ns  | +5          | Cerdip   | 24   |

| μPB427 (F)   | 1K x 8 TS                      | Bipolar       | 120 ns       | 120 ns  | +5          | Cerdip   | 24   |

| μPD2716 (F)  | 2K x 8 TS                      | NMOS          | 450 ns       | 450 ns  | +5          | Cerdip   | 24   |

| μPD454       | 256 x 8 TS                     | NMOS          | 800 ns       | 800 ns  | +12, -5*    | Cerdip   | 24   |

| μPD458       | 1K x 8 TS                      | NMOS .        | 450 ns       | 450 ns  | +12, -5*    | Cerdip   | 28   |

|              |                                |               |              | L       |             | L        | L    |

(F) Future Product

\* Read Mode

# NEC MICRO

| MANUFACTURER | PART NUMBER  | DESCRIPTION    | NEC<br>REPLACEMENT  | MANUFACTURER | PART NUMBER    | DESCRIPTION    | NEC<br>REPLACEMENT |

|--------------|--------------|----------------|---------------------|--------------|----------------|----------------|--------------------|

| AMD          | AM2101       | 256 × 4 SRAM   | μPD2101AL           | Harris       | HPROM-1024A    | 256 × 4 PROM   | μPB403             |

|              | AM2101       | 1024 x 1 SRAM  | µPD2102AL           |              | HM6501         | 256 x 4 SR AM  | μPD5101            |

|              | AM2111       | 256 x 4 SRAM   | μPD2111AL           |              | HM6508         | 1024 × 1 SRAM  | µPD6508            |

|              | AM27LS00     | 256 x 1 SRAM   | µPB2200/µPB2202     |              | HM7610         | 256 x 4 PROM   | μPB403             |

|              | AM27LS01     | 256 x 1 SRAM   | μPB2206             |              | HM7640         | 512 × 8 PROM   | μPB405             |

|              | AM27LS02     | 16 × 4 SRAM    | µPB2089/µPB2289     |              | HM7641         | 512 x 8 PROM   | μPB425             |

|              | AM27LS10     | 256 x 4 PROM   | μPB403              |              | HM7642         | 1024 x 4 PROM  | μPB406             |

| 1.<br>       | AM27S80      | 1024 x 8 PROM  | μPB408              |              | HM7643         | 1024 x 4 PROM  | μPB426             |

|              | AM27S81      | 1024 × 8 PROM  | μPB428              |              |                |                |                    |

|              | AM3101       | 16 x 4 SRAM    | μPB2089             | Intersil     | 2608           | 1024 × 8 ROM   | μPD2308            |

|              | Sn7489       | 16 x 4 SRAM    | μPB2089             | 1            | 2616           | 2048 x 8 ROM   | μPD2316            |

|              | Sn74S289     | 16 × 4 SRAM    | μPB2289             |              | IM5501         | 16 x 4 SRAM    | µPB2089/µPB2289    |

|              | AM9050       | 4096 × 1 DRAM  | μPD418              |              | IM5508         | 1024 x 1 SRAM  | μPB2205            |

|              | AM9060       | 4096 × 1 DRAM  | μPD411/μPD411A      |              | IM5523A        | 256 × 1 SRAM   | µPB2200/µPB2202    |

|              | AM9101       | 256 x 4 SRAM   | μPD2101AL           |              | IM5533A        | 256 x 1 SRAM   | μPB2206            |

|              | AM9102       | 1024 x 1 SRAM  | µPD2102AL           |              | IM5603         | 256 × 4 PROM   | μPB403             |

|              | 9107         | 4096 x 1 DRAM  | μPD411/μPD411A      |              | IM5605         | 512 x 8 PROM   | μPB405             |

|              | AM9111       | 256 x 4 SRAM   | µPD2111AL           |              | IM5625         | 512 x 8 PROM   | μPB425             |

|              | AM9208       | 1024 × 8 ROM   | μPD2308             |              | IM6508A        | 1024 × 1 SRAM  | μPD6508            |

|              | AM9216       | 2048 × 8 ROM   | μPD2316E            |              | 7005           | 4096 x 1 DRAM  | μPD414             |

|              |              |                |                     |              | 7027           | 4096 x 1 DRAM  | μPD414A            |

| EM&M Semi    | 4200         | 4096 x 1 SRAM  | μPD410              |              | 7101           | 256 x 4 SRAM   | μPD2101AL          |

|              | 4402         | 4096 × 1 SRAM  | μPD410              |              | 7111           | 256 x 4 SRAM   | μPD2111AL          |

|              | R03-8316A    | 2048 × 8 ROM   | μPD2316A            |              | 7114           | 1024 × 4 SRAM  | μPD2114            |

|              | R03-8316B    | 2048 x 8 ROM   | µPD2316A            | •            | 7116           | 16384 × 1 DRAM | μPD416             |

|              |              |                |                     |              | 7270           | 4096 × 1 DRAM  | μPD418             |

| Fairchild    | 2101L        | 256 × 4 SRAM   | µPD2101AL           |              | 7271A          | 4096 x 1 DRAM  | μPD418             |

|              | 2102         | 1024 x 1 SRAM  | #PD2102AL           |              | 7280/A         | 4096 x 1 DRAM  | μPD411/μPD411A     |

|              | 3508         | 1024 x 8 ROM   | µPD2308             |              | IM7552         | 512 x 1 SRAM   | μPD2102AL          |

|              | 3538         | 256 × 4 SRAM   | μPD2101AL           |              |                |                | ,                  |

|              | FM4027       | 4096 x 1 DRAM  | μPD414A             | Intel        | 2101           | 256 × 4 SRAM   | µPD2101AL          |

|              | 4096         | 4096 x 1 DRAM  | μPD414              |              | 2102           | 1024 x 1 SRAM  | μPD2102AL          |

| 4            | F16K         | 16384 x 1 DRAM | μPD416              |              | 2104           | 4096 x 1 DRAM  | μPD414/μPD414A     |

|              | 7489         | 16 x 4 SRAM    | μPB2089             |              | 2107           | 4096 × 1 DRAM  | μPD411/μPD411A     |

|              | 93411        | 256 x 1 SRAM   | μPB2206             |              | 2111           | 256 × 4 SRAM   | µPD2111AL          |

|              | 93415        | 1024 x 1 SRAM  | μPB2205             |              | 2114           | 1024 × 4 SRAM  | μPD2114            |

|              | 93417        | 256 x 4 PROM   | μPB403              |              | 2116           | 16384 × 1 DRAM | μPD416             |

|              | 93438        | 512 x 8 PROM   | μPB405              |              | 2308           | 1024 × 8 ROM   | μPD2308            |

|              | 93448        | 512 x 8 PROM   | μPB425              |              | 2316A          | 2048 × 8 ROM   | μPD2316A           |

|              | 93452        | 1024 x 4 PROM  | μPB406              |              | 2316E          | 2048 × 8 ROM   | μPD2316E           |

|              | 93453        | 1024 x 4 PROM  | μPB426              |              | 3101A          | 16 x 4 SRAM    | μPB2089/μPB2289    |

|              |              |                |                     |              | 3107           | 256 x 1 SRAM   | μPB2206            |

| Fujitsu      | MB2114       | 1024 × 4 SRAM  | μPD2114             |              | 3106           | 256 x 1 SRAM   | μPB2200/μPB2202    |

|              | MB7054       | 1024 × 4 PROM  | μPB426              |              | 3601           | 256 x 1 PROM   | μPB403             |

|              | MB7057       | 256 × 4 PROM   | μPB403              |              | 3604           | 512 × 8 PROM   | μPB405             |

|              | MB7059       | 1024 x 4 PROM  | μPB406              |              | 3605           | 1024 x 4 PROM  | μPB406             |

| ×            | MB8101       | 256 × 4 SRAM   | μPD2101AL           |              | 3608           | 1024 x 8 PROM  | μPB408             |

|              | MB8107       | 4096 x 1 DRAM  | μPD411/μPD411A      |              | 3624           | 512 × 8 PROM   | μPB425             |

|              | MB8111       | 256 × 4 SRAM   | μPD2111AL           |              | 3625           | 1024 x 4 PROM  | μPB425<br>μPB426   |

|              | MB8116       | 16384 x 1 DRAM | μPD2111AL<br>μPD416 |              | 3628           | 1024 x 4 PROM  | μPB426<br>μPB428   |

|              | MB8224       | 4096 x 1 DRAM  | μPD416<br>μPD414    |              | 4316A          | 2048 × 8 ROM   |                    |

|              | MB8227       | 4096 x 1 DRAM  |                     |              | 51.01          | 1              | μPD2316A           |

|              | MB8308       |                | μPD414A             |              |                | 256 x 4 SRAM   | μPD5101            |

|              | MBM93415     | 1024 × 8 ROM   | μPD2308             | · ·          | 8101A<br>8102A | 256 × 4 SRAM   | µPD2101AL          |

|              | 101010193415 | 1024 × 1 SRAM  | µPB2205             |              | 8102A<br>8111A | 1024 x 1 SRAM  | μPD2102AL          |

|              |              |                |                     |              |                | 256 × 4 SRAM   | µPD2111AL          |

|              |              |                |                     |              | 8308           | 1024 × 8 ROM   | μPD2308            |

|              | I            | L              |                     | L            | 8316A          | 2048 × 8 ROM   | μPD2316A           |

## MEMORY ALTERNATE SOURCE GUIDE

NEC MCOUPUIGES, and

| MANUFACTURER                          | PART<br>NUMBER     | DESCRIPTION                  | NEC<br>REPLACEMENT     | MANUFACTURER                              | PART<br>NUMBER  | DESCRIPTION    | NEC<br>REPLACEMENT     |

|---------------------------------------|--------------------|------------------------------|------------------------|-------------------------------------------|-----------------|----------------|------------------------|

| ммі                                   | 6300               | 256 x 1 PROM                 | μPB403                 | Signetics                                 | 2101            | 256 x 4 SRAM   | µPD2101AL              |

|                                       | 6340               | 512 x 8 PROM                 | μPB405                 |                                           | 2102            | 1024 x 1 SRAM  | μPD2102AL              |

|                                       | 6341               | 512 x 8 PROM                 | μPB425                 |                                           | 2111            | 256 x 4 SRAM   | µPD2111AL              |

|                                       | 6348               | 512 x 8 PROM                 | μPB405                 |                                           | 2316            | 2048 × 8 ROM   | μPD2316                |

|                                       | 6349               | 512 x 8 PROM                 | μPB425                 |                                           | 2601            | 256 x 4 SRAM   | µPD2101AL              |

|                                       | 6352               | 1024 x 4 PROM                | μPB406                 | ÷                                         | 2608            | 1024 x 8 ROM   | μPD2308                |

| · · · · · · · · · · · · · · · · · · · | 6353               | 1024 x 4 PROM                | μPB426                 |                                           | 2611            | 256 x 4 SRAM   | µPD2111AL              |

|                                       | 6380               | 1024 x 8 PROM                | μPB408                 |                                           | 2680            | 4096 × 1 DRAM  | µPD411/µPD411A         |

|                                       | 6381               | 1024 × 8 PROM                | μPB428                 |                                           | N3101A          | 16 x 4 SRAM    | µPB2089/µPB2289        |

|                                       | 6530               | 256 x 1 SRAM                 | μPB2206                |                                           | 74\$89          | 16 x 4 SRAM    | µPB2089/µPB2289        |

|                                       | 6531               | 256 x 1 SRAM                 | µPB2200/µPB2202        |                                           | 74\$200         | 256 × 1 SRAM   | µPB2200                |

|                                       | 6560               | 16 x 4 SRAM                  | μPB2089/μPB2289        |                                           | 7 <b>4</b> S201 | 256 x 1 SRAM   | μPB2200                |

|                                       |                    |                              | μ. υ                   |                                           | 74\$301         | 256 x 1 SRAM   | µPB2202                |

| Mostek                                | мкз0000            | 1024 x 8 ROM                 | μPD2308                |                                           | 82507           | 256 × 1 SRAM   | μPB2206                |

| moster                                | MK31000            | 2048 × 8 ROM                 | μPD2316A               |                                           | N82S10          | 256 x 1 SRAM   | μPB2206                |

|                                       | MK32000            | 4096 x 8 ROM                 | μPD2332                |                                           | 82516           | 256 x 1 SRAM   | μPB2206                |

|                                       | MK34000            | 2048 × 8 ROM                 | μPD2316E               |                                           | 82517           | 256 × 1 SRAM   | µPB2200/µPB2202        |

|                                       | MK4027             | 4096 x 1 DRAM                | μPD414A                |                                           | 82526           | 256 x 4 PROM   | μPB403                 |

|                                       | MK4102             | 1024 x 1 SRAM                | μPD2102AL              |                                           | N82S115         | 512 x 8 PROM   | μPB425                 |

|                                       | MK4102<br>MK4104   | 4096 x 1 SRAM                | μPD2102AL<br>μPD4104   |                                           | 825126          | 256 × 4 PROM   | μPB403                 |

|                                       | MK4104<br>MK4116   | 16384 x 1 DRAM               | μPD416                 |                                           | N82S136         | 1024 × 4 PROM  | μΡΒ406                 |

|                                       | WIK4110            | 10364 X T DRAM               | με0416                 | 5 m                                       | N82S137         | 1024 x 4 PROM  | μPB426                 |

| Motorola                              | MCM2102            | 1024 x 1 SRAM                | µPD2102AL              |                                           | 825140          | 512 × 8 PROM   | μPB405                 |

| wotorola                              | MCM2102<br>MCM2111 | 256 x 4 SRAM                 | μPD2102AL<br>μPD2111AL |                                           | 825140          | 512 × 8 PROM   | μPB425                 |

|                                       | MCM2111<br>MCM6604 | 4096 x 1 DRAM                | μPD2111AL<br>μPD414    |                                           | N93415A         | 1024 × 1 SRAM  | μPB2205                |

|                                       | MCM6616            | 16384 x 1 DRAM               | μPD414<br>μPD416       |                                           | 1000410A        |                | µ102200                |

|                                       |                    | 256 x 4 SRAM                 | 1 ·                    | т.і.                                      | TMS2101         | 256 × 4 SRAM   | µPD2101AL              |

|                                       | MCM68111           |                              | μPD2111AL              | 1.1.                                      | TMS2101         | 1024 × 1 SRAM  | μPD2102AL              |

|                                       | MCM68317           | 2048 × 8 ROM<br>512 × 8 PROM | μPD2316E               |                                           | TMS4027         | 4096 × 1 DRAM  | μPD2102AC              |

|                                       | MCM7640            |                              | μPB405                 |                                           | TMS4027         | 1024 x 1 SRAM  | μPD2102AL              |

|                                       | MCM7641            | 512 × 8 PROM                 | μPB425                 |                                           | TMS4033         | 1024 x 1 SRAM  | μPD2102AL              |

|                                       | MCM7642            | 1024 x 4 PROM                | μPB406                 |                                           |                 | 256 x 4 SRAM   | μPD2102AL<br>μPD2101AL |

|                                       | MCM7643            | 1024 × 4 PROM                | μPB426                 |                                           | TMS4039         |                | 1 ' '                  |

|                                       |                    |                              |                        | 1. A. | TMS4042         | 256 × 4 SRAM   | μPD2111AL              |

| National                              | MM2101             | 256 × 4 SRAM                 | μPD2101AL              | •                                         | TMS4050         | 4096 × 1 DRAM  | μPD418                 |

|                                       | MM2102A            | 1024 × 1 SRAM                | μPD2102AL              |                                           | TMS4051         | 4096 × 1 DRAM  | μPD418                 |

|                                       | MM2111             | 256 × 4 SRAM                 | µPD2111AL              |                                           | TMS4060         | 4096 × 1 DRAM  | μPD411/μPD411Λ         |

|                                       | MM2316A            | 2048 × 8 ROM                 | μPD2316A               |                                           | TMS4116         | 16384 x 1 DRAM | μPD416                 |

|                                       | MM4280             | 4096 × 1 DRAM                | μPD411M                |                                           | TMS4732         | 4096 × 8 ROM   | μPD2332                |

|                                       | MM5280A            | 4096 × 1 DRAM                | μPD411/μPD411A         |                                           | SN74S44         | 512 x 8 PROM   | μPB425                 |

|                                       | MM5281             | 4096 x 1 DRAM                | μPD411/μPD411A         |                                           | SN7489          | 16 × 4 SRAM    | µPB2089/µPB2289        |

|                                       | DM7489             | 16 × 4 SRAM                  | µPB2089/µPB2289        |                                           | SN74S201        | 256 × 1 SRAM   | μPB2200                |

| · · ·                                 | MM74S289           | 16 × 4 SRAM                  | µPB2089/µPB2289        |                                           | SN74S289        | 16 × 4 SRAM    | µPB2089/µPB2289        |

|                                       | DM74S387           | 256 x 4 PROM                 | μPB403                 |                                           | SN 74S301       | 256 × 1 SRAM   | µPB2200/µPB2202        |

|                                       | DM74S572           | 1024 × 4 PROM                | μPB406                 | 1                                         | SN 745,314      | 1024 x 1 SRAM  | μPB2205                |

|                                       | DM74S573           | 1024 × 4 PROM                | μPB426                 |                                           | SN74S387        | 256 x 4 PROM   | µPB403                 |

|                                       | MM74C920           | 256 × 4 SRAM                 | μPD5101                |                                           | SN 74S4 75      | 512 x 8 PROM   | μPB405                 |

|                                       | DM7535             | 256 × 4 PROM                 | μPB403                 |                                           |                 |                |                        |

|                                       | DM7574             | 256 × 4 PROM                 | μPB403                 |                                           |                 |                |                        |

|                                       | DM77S295           | 512 x 8 PROM                 | μPB405                 |                                           |                 |                |                        |

|                                       | DM77S296           | 512 x 8 PROM                 | μPB425                 |                                           |                 | · · · ·        | l                      |

|                                       | DM93415            | 1024 × 1 SRAM                | μPB2205                |                                           |                 |                |                        |

## MEMORY ALTERNATE SOURCE GUIDE

## NEC MICROLIMPITERS, INC.

### μ PD411-E μ PD411 μ PD411-1 μ PD411-2 μ PD411-3 μ PD411-4

## FULLY DECODED RANDOM ACCESS MEMORY

#### DESCRIPTION

The  $\mu$ PD411 Family consists of six 4096 words by 1 bit dynamic N-channel MOS RAMs. They are designed for memory applications where very low cost and large bit storage are important design objectives. The  $\mu$ PD411 Family is designed using dynamic circuitry which reduces the standby power dissipation.

Reading information from the memory is a non-destructive. Refreshing is easily accomplished by performing one read cycle on each of the 64 row addresses. Each row address must be refreshed every two milliseconds. The memory is refreshed whether Chip Select is a logic high or a logic low.

#### FEATURES

All of these products are guaranteed for operation over the 0 to  $70^{\circ}$ C temperature range.

Important features of the  $\mu$ PD411 family are:

- Low Standby Power

- 4096 words x 1 bit Organization

- A single low-capacitance high level clock input with solid ±1 volt margins.

- Inactive Power/0.3 mW (Typ.)

- Power Supply: +12, +5, -5V

- Easy System Interface

- TTL Compatible (Except CE)

- · Address Registers on the Chip

- Simple Memory Expansion by Chip Select

- Three State Output and TTL Compatible

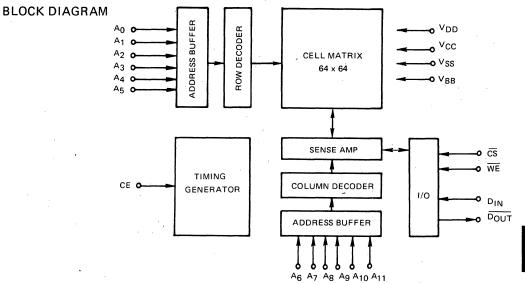

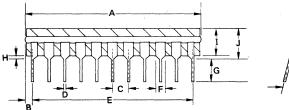

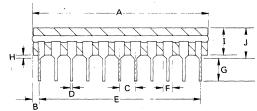

- 22 pin Ceramic Dual-in-Line Package

- Replacement for INTEL'S 2107B, TI'S 4060 and Equivalent Devices.

- 4 Performance Ranges:

|          | ACCESS TIME | R/W CYCLE | RMW CYCLE | REFRESH TIME |

|----------|-------------|-----------|-----------|--------------|

| μPD411-E | 350 ns      | 800 ns    | 960 ns    | 1 ms         |

| μPD411   | 300 ns      | 470 ns    | 650 ns    | 2 ms         |

| μPD411-1 | 250 ns      | 470 ns    | 640 ns    | 2 ms         |

| μPD411-2 | 200 ns      | 400 ns    | 520 ns    | 2 ms         |

| μPD411-3 | 150 ns      | 380 ns    | 470 ns    | 2 ms         |

| μPD411-4 | 135 ns      | 320 ns    | 320 ns    | 2 ms         |

#### PIN CONFIGURATION

| · · · · · |     | ~~~ |                      |

|-----------|-----|-----|----------------------|

| ∨ввС      | 1   | •   | 22 🗖 V <sub>SS</sub> |

| A9 🕻      | 2 ' |     | 21 🗖 A8              |

| A10 🗖     | 3   |     | 20 🗖 A7              |

| A11 🗖     | 4   |     | 19 🗖 A <sub>6</sub>  |

| cs 🗖      | 5   | μPD |                      |

| Din 🗖     |     | 411 | 17 🗖 CE              |

| POUT      | 7   |     | 16 🗖 NC              |

| A0 C      | 8 - |     | 15 🗖 A5              |

| A1 🗖      | 9   |     | 14 A4                |

| A2 🗖      | 10  |     | 13 🗖 A3              |

| Vcc 🗖     | 11  | ·   | 12 WE                |

|           |     |     |                      |

#### PIN NAMES

| A0 · A11   | Address Inputs    |

|------------|-------------------|

| A0 - A5    | Refresh Addresses |

| CE         | Chip Enable       |

| <u>Ĉ</u> Ŝ | Chip Select       |

| DIN        | Data Input        |

| DOUT       | Data Output       |

| WE         | Write Enable      |

| VDD        | Power (+12V)      |

| Vcc        | Power (+5V)       |

| VSS        | Ground            |

| VBB        | Power (-5V)       |

| NC         | No Connection     |

Rev/2

FUNCTIONAL DESCRIPTION

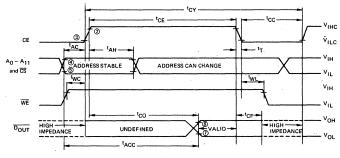

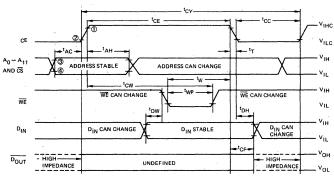

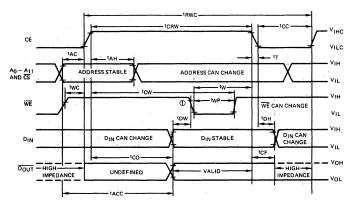

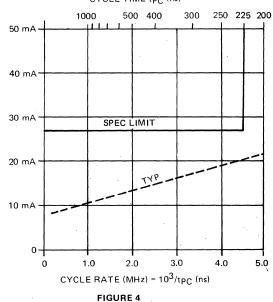

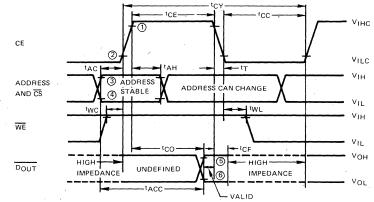

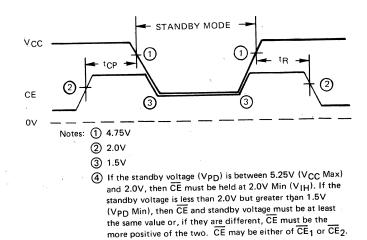

#### CE Chip Enable

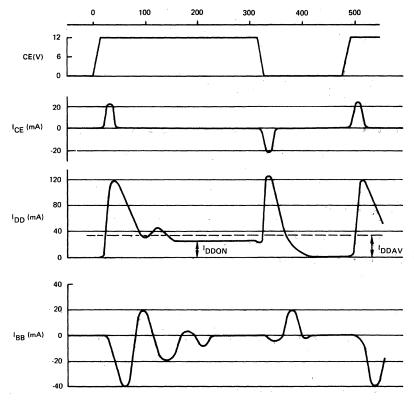

A single external clock input is required. All read, write, refresh and read-modify-write operations take place when chip enable input is high. When the chip enable is low, the memory is in the low power standby mode. No read/write operations can take place because the chip is automatically precharging.

#### CS Chip Select

The chip select terminal affects the data in, data out and read/write inputs. The data input and data output terminals are enabled when chip select is low. The chip select input must be low on or before the rising edge of the chip enable and can be driven from standard TTL circuits. A register for the chip select input is provided on the chip to reduce overhead and simplify system design.

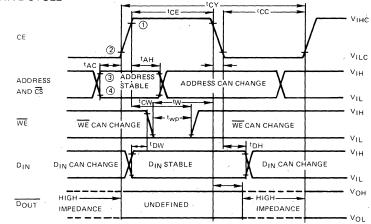

#### WE Write Enable

The read or write mode is selected through the write enable input. A logic high on the  $\overline{WE}$  input selects the read mode and a logic low selects the write mode. The  $\overline{WE}$  terminal can be driven from standard TTL circuits. The data input is disabled when the read mode is selected.

#### A0-A11 Addresses

All addresses must be stable on or before the rising edge of the chip enable pulse. All address inputs can be driven from standard TTL circuits. Address registers are provided on the chip to reduce overhead and simplify system design.

#### **DIN Data Input**

Data is written during a write or read-modify-write cycle while the chip enable is high. The data in terminal can be driven from standard TTL circuits. There is no register on the data in terminal.

#### DOUT Data Output

The three state output buffer provides direct TTL compatibility with a fan-out of two TTL gates. The output is in the high-impedance (floating) state when the chip enable is low or when the Chip Select input is high. Data output is inverted from data in.

#### Refresh

Refresh must be performed every two milliseconds by cycling through the 64 addresses of the lower-order-address inputs  $A_0$  through  $A_5$  or by addressing every row within any 2\*-millisecond period. Addressing any row refreshes all 64 bits in that row.

The chip does not need to be selected during the refresh. If the chip is refreshed during a write mode, the chip select must be high.

\* $\mu$ PD411-E = 1 millisecond refresh period.

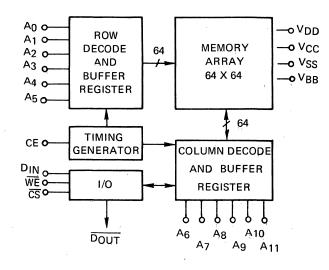

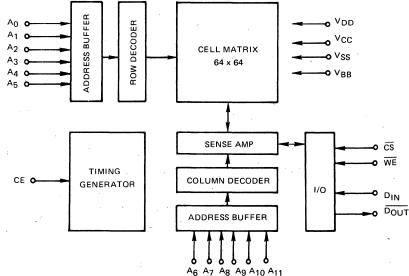

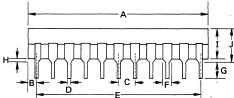

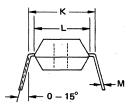

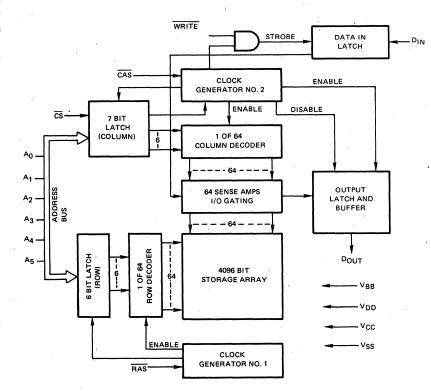

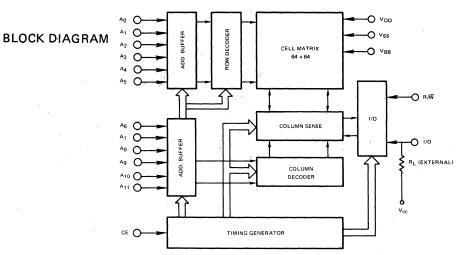

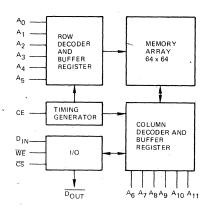

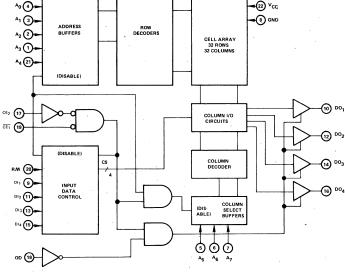

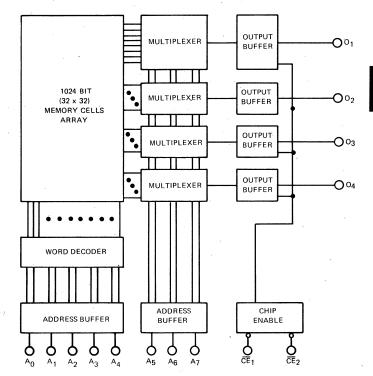

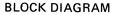

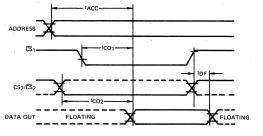

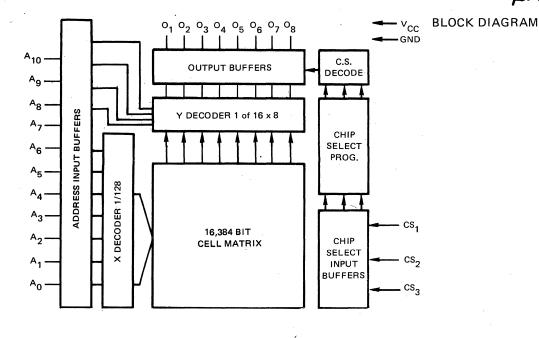

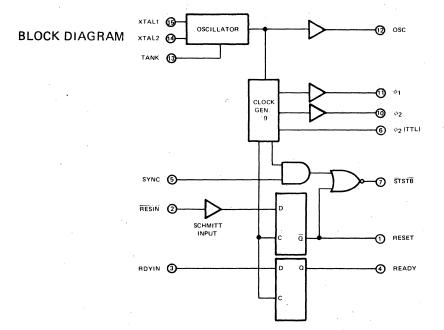

#### **BLOCK DIAGRAM**

#### μPD411 FAMILY (EXCEPT 411-4)

μPD411-4

|                       | •                                             |

|-----------------------|-----------------------------------------------|

| Operating Temperature | $0^{\circ}C$ to +70°C $+10^{\circ}C$ to +55°C |

| Storage Temperature   | -55°C to +150°C55°C to +150°C                 |

|                       | -0.3 to +20 Volts0.3 to +25 Volts ①           |

| All Input Voltages    | -0.3 to +20 Volts0.3 to +25 Volts ①           |

| Supply Voltage VDD    | -0.3 to +20 Volts0.3 to +25 Volts ①           |

| Supply Voltage VCC    | -0.3 to +20 Volts0.3 to +25 Volts ①           |

| Power Dissipation     |                                               |

| _                     |                                               |

Note: 1 Relative to VBB

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### $T_a = 25^{\circ}C$

### DC CHARACTERISTICS

ABSOLUTE MAXIMUM

**RATINGS\***

$$\label{eq:tau} \begin{split} T_a = 0^\circ C \mbox{ to } 70^\circ C, \mbox{ } V_{DD} = +12V \ \pm 5\%, \ V_{CC} = \pm 5V \ \pm 5\%, \ V_{BB} = -5V \ \pm 5\%, \ V_{SS} = 0V, \\ \mbox{ Except } V_{DD} = \pm 15V \ \pm 5\% \mbox{ for } 4114. \end{split}$$

| DADAMETER                                                                                             | SYMBOL                                                   |                    | LIMITS                           |                            |                            | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|----------------------------------|----------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PARAMETER                                                                                             | STWBUL                                                   | MIN                | түр 🕦                            | мах                        | UNIT                       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Input Load Current                                                                                    | ILI .                                                    |                    | 0.01                             | 10                         | μA                         | VIN = VIL MIN to VIH MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CE Input Load Current                                                                                 | LC                                                       |                    | 0.01                             | 10                         | μA                         | VIN = VILC MIN to VIHC MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Output Leakage Current<br>for High Impedance State                                                    | 'LO                                                      |                    | 0.01                             | ±10                        | μА                         | CE = V <sub>ILC</sub> or <del>CS</del> = V <sub>IH</sub><br>V <sub>0</sub> = 0V to 5.25V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VDD Supply Current<br>during CE off                                                                   | DDOFF                                                    |                    | 20                               | 200                        | μA                         | CE = -1.0V to 0.6V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VDD Supply Current<br>during CE on                                                                    | DD ON.                                                   |                    | 35°                              | 60 <sup>s</sup>            | mA                         | CE = VIHC, T <sub>a</sub> = 25°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

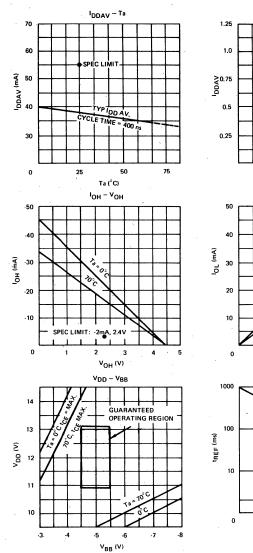

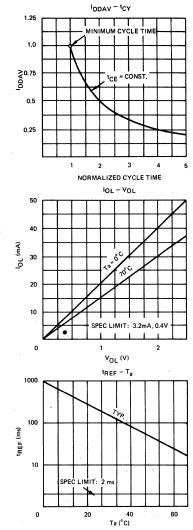

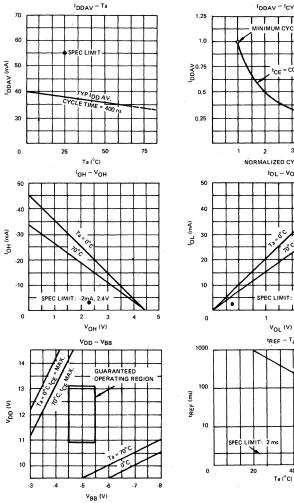

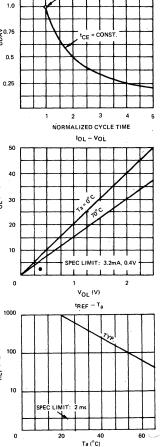

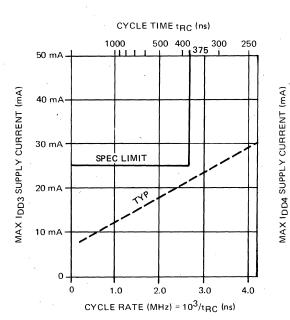

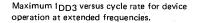

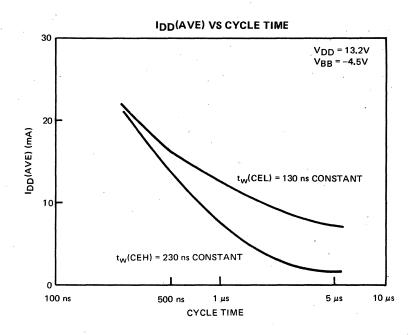

| Average V <sub>DD</sub> Current<br>µPD411-E<br>µPD411<br>µPD411-1<br>µPD411-2<br>µPD411-3<br>µPD411-4 | IDD AV<br>IDD AV<br>IDD AV<br>IDD AV<br>IDD AV<br>IDD AV |                    | 29<br>37<br>37<br>37<br>41<br>55 | 60<br>60<br>60<br>65<br>80 | mA<br>mA<br>mA<br>mA<br>mA | $T_a = 25 C. \\ Cycle Time = 800 ns \\ Cycle Time = 470 ns \\ Cycle Time = 470 ns \\ Cycle Time = 470 ns \\ Cycle Time = 400 ns \\ Cycle Time = 380 ns \\ Cycle Time = 320 ns \\ Cycle $ |

| VBB Supply Current ②                                                                                  | IBB                                                      |                    | 5                                | 100                        | μA                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>CC</sub> Supply Current<br>during CE off ③                                                     | ICC OFF                                                  |                    | 0.01                             | 10                         | μΑ                         | CE = VILC or CS = VIH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Input Low Voltage                                                                                     | VIL                                                      | -1.0               |                                  | 0.6                        | v                          | х                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Input High Voltage                                                                                    | VIH                                                      | 2.4 ④              |                                  | V <sub>CC</sub> +1         | v                          | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

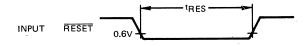

| CE Input Low Voltage                                                                                  | VILC                                                     | -1.0               |                                  | 0.6                        | v                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

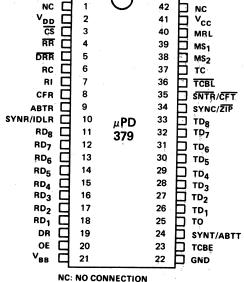

| CE Input High Voltage                                                                                 | VIHC                                                     | V <sub>DD</sub> -1 | V <sub>DD</sub>                  | V <sub>DD</sub> +1         | <                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |