ESD ACCESSION LIST. ISTI Call No. 70364 \_\_\_\_\_of \_\_\_\_ CYS. 2 Copy No. ESD-TR-70-198 ESTI FILE COPY

MTR-1843

# PRINCIPLES OF OPERATION OF THE VENUS MICROPROGRAM

B. J. Huberman

JULY 1970

Prepared for

DIRECTORATE OF PLANNING AND TECHNOLOGY ELECTRONIC SYSTEMS DIVISION AIR FORCE SYSTEMS COMMAND UNITED STATES AIR FORCE L. G. Hanscom Field, Bedford, Massachusetts

# ESD RECORD COPY

RETURN TO SCIENTIFIC & TECHNICAL INFORMATION DIVISION

Project 700A Prepared by THE MITRE CORPORATION Bedford, Massachusetts Contract F19(628)-68-C-0365

AD0709717

This document has been approved for public release and sole; its distribution is unlimited. When U.S. Government drawings, specificotions, or other doto are used for any purpose other than a definitely related government procurement operation, the government thereby incurs no responsibility nor any abligation whatsoever; and the fact that the government may have formulated, furnished, or in any way supplied the soid drawings, specifications, or other data is not to be regarded by implication or otherwise, as in any monner licensing the holder or any other person or corporation, or conveying any rights or permission to manufacture, use, or sell any potented invention that may in any way be related thereto.

Do not return this copy. Retoin or destroy.

# PRINCIPLES OF OPERATION OF THE VENUS MICROPROGRAM

B. J. Huberman

# JULY 1970

Prepared for

# DIRECTORATE OF PLANNING AND TECHNOLOGY

ELECTRONIC SYSTEMS DIVISION AIR FORCE SYSTEMS COMMAND UNITED STATES AIR FORCE L. G. Hanscom Field, Bedford, Massachusetts

This dacument hos been approved for public release and sale; its distributian is unlimited. Project 700A Prepared by THE MITRE CORPORATION Bedford, Massachusetts Contract F19(628)-68-C-0365

# FOREWORD

This report was developed under Air Force Contract F19(628)-68-C-0365 with The MITRE Corporation in Bedford, Massachusetts. It carries a MITRE Project Number of 700A. There is no Air Force project or task number. The report describes the Venus system, which is a computer system comprised of microprograms and software. It is implemented on the Interdata 3, a small, micro-programmable computer. This document contains a complete description of the micro-program part of Venus.

## **REVIEW AND APPROVAL**

This technical report has been reviewed and is approved.

Robert P. Savey ANTHONY P. TRUNFIO Technical Advisor

ANTHONY P. TRUNFIO Technical Advisor Development Engineering Division Directorate of Planning & Technology

# ABSTRACT

Venus is a computer system comprised of microprograms and software. It is implemented on the Interdata 3, which is a small, microprogrammable computer. This document contains a complete description of the microprogram part of Venus.

# TABLE OF CONTENTS

| LIST OF I | ILLUSTRATIONS |                                                                                                                                          | vii                             |

|-----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| SECTION 1 | I             | INTRODUCTION                                                                                                                             | 1                               |

| SECTION ] | II            | NOTATION<br>NUMBER BASES<br>ADDRESS SPACES<br>VALUES<br>SYNTAX<br>NOTATION FOR INSTRUCTIONS<br>CLASSES OF INSTRUCTIONS<br>CONDITION CODE | 2<br>2<br>3<br>4<br>6<br>7<br>7 |

| SECTION 1 | III           | THE JOB AREA<br>THE JOB AREA INSTRUCTION                                                                                                 | 9<br>9                          |

| SECTION 1 | IV            | VIRTUAL MEMORY<br>MAPPING OF VIRTUAL INTO REAL MEMORY<br>THE AGE CHAIN<br>THE CORE PAGE TABLE<br>STREAM REGISTER INSTRUCTIONS            | 10<br>10<br>13<br>14<br>18      |

| SECTION V | <b>V</b>      | BASIC INSTRUCTIONS<br>LOAD AND STORE INSTRUCTIONS<br>ARITHMETIC INSTRUCTIONS<br>LOGICAL INSTRUCTIONS<br>SHIFT INSTRUCTIONS               | 20<br>20<br>23<br>27<br>30      |

| SECTION V | VI            | CONDITIONS<br>CONDITION INSTRUCTIONS                                                                                                     | 33<br>35                        |

| SECTION V | VII           | PUSHDOWN STACKS<br>STACK INSTRUCTIONS                                                                                                    | 36<br>36                        |

| SECTION V | VIII          | THE CONTROL STACK<br>CONTROL STACK INSTRUCTIONS                                                                                          | 41<br>42                        |

| SECTION ] | IX            | PROCEDURES<br>BRANCH INSTRUCTIONS<br>CALL AND RETURN INSTRUCTIONS                                                                        | 44<br>46<br>49                  |

# TABLE OF CONTENTS (Concluded)

| SECTION X     | MULTIPROGRAMMING AND SEMAPHORES<br>P AND V INSTRUCTIONS                                                      | 53<br>55                   |

|---------------|--------------------------------------------------------------------------------------------------------------|----------------------------|

| SECTION XI    | THE MICROPROGRAMMED MULTIPLEX CHANNEL<br>THE CHANNEL-COMMAND PROGRAM<br>THE CHANNEL                          | 57<br>60<br>62             |

| SECTION XII   | INPUT/OUTPUT<br>CHANNEL INPUT/OUTPUT INSTRUCTIONS<br>NON-CHANNEL INPUT/OUTPUT INSTRUCTIONS                   | 70<br>70<br>70             |

| SECTION XIII  | LEVEL 1<br>LEVEL 1 INSTRUCTIONS                                                                              | 74<br>75                   |

| SECTION XIV   | NON-INSTRUCTION PARTS OF VENUS<br>TIME-SLICING<br>INSTRUMENTATION<br>BOOTS<br>DISPLAY PANEL<br>THE IDLE LOOP | 78<br>78<br>79<br>82<br>85 |

| APPENDIX I    | OPCODE MATRIX                                                                                                | 87                         |

| APPENDIX II   | INSTRUCTIONS LISTED ALPHABETICALLY BY<br>OPCODE MNEMONIC                                                     | 88                         |

| APPENDIX III  | LOCATIONS IN THE JOB AREA                                                                                    | 95                         |

| APPENDIX IV   | GLOBAL CORE LOCATIONS KNOWN TO THE<br>MICROPROGRAM                                                           | 98                         |

| APPENDIX V    | ILLEGAL OPCODES                                                                                              | 100                        |

| APPENDIX VI   | CONTROL STACK FORMATS                                                                                        | 101                        |

| APPENDIX VII  | CONTENTS OF CORE PAGE TABLE FOR CORE<br>PAGES WHICH CONTAIN STREAM PAGES                                     | 102                        |

| APPENDIX VIII | INDEX TO LOCATIONS KNOWN TO THE<br>MICROPROGRAM                                                              | 104                        |

# LIST OF ILLUSTRATIONS

# Figure Number

| 1 | The Relationship between Registers, Stream | 11 |

|---|--------------------------------------------|----|

|   | Registers and Extensions                   |    |

| 2 | Example of Entries in Core Page Table      | 16 |

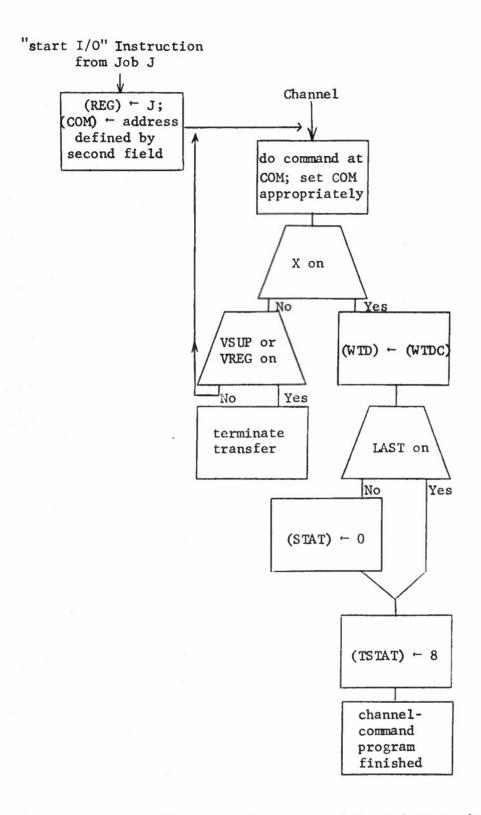

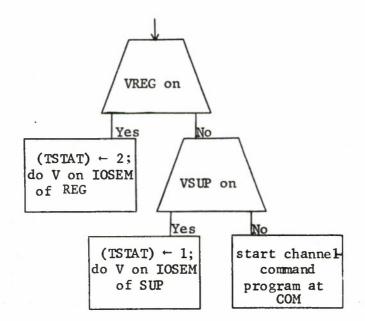

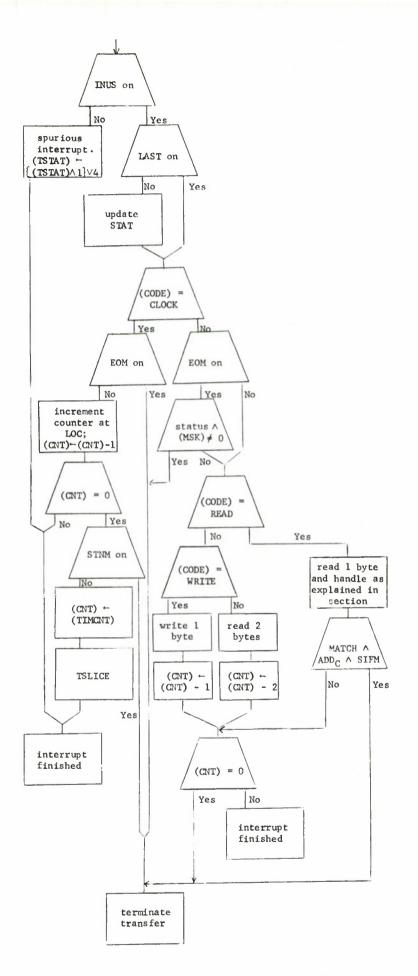

| 3 | How the Channel Fits into the Microprogram | 58 |

| 4 | Execution of Channel Commands              | 63 |

| 5 | Terminate Transfer                         | 65 |

| 6 | Channel Interrupt-Handling for a Device    | 69 |

|   |                                            |    |

#### SECTION I

#### INTRODUCTION

Venus is a computer system comprised of microprograms and software. It is implemented on the Interdata 3, which is a small, microprogrammable computer. The Venus system supports:

- 1. Multiprogramming;

- 2. Named virtual memories;

- 3. Recursive and reentrant procedures;

- 4. Interrupts for debugging;

- 5. A microprogrammed, multiplex channel.

This document contains a complete description of the microprogram part of Venus. Each of the above features is partially or fully implemented in the microprogram. In addition, the microprogram part of Venus completely defines the instruction set (used by the software part). The software part of Venus is not defined by this document; occasionally, however, a place will be described where the microprogram and the software communicate.

This document is intended to be read sequentially the first time, since the descriptions of important concepts in the Venus system appear as required for the definitions of instructions. Subsequently, the document may be used as a reference manual. Appendix II provides an index to the instructions.

#### SECTION II

#### NOTATION

## NUMBER BASES

Venus reflects the fact that the Interdata is a hexadecimal machine, addressable by 8-bit bytes. Each byte contains two hexadecimal digits. In this document, hexadecimal numbers will be used for locations and for constants, like FF. Decimal numbers are used to refer to quantities (for example, 16 general registers) and to refer to bits.

# ADDRESS SPACES

In Venus there are three address spaces: registers, core and streams. Locations in the various address spaces are represented as follows.

#### Registers

A user in Venus is supplied with 16, 16-bit general registers. The name of a register is a 4-bit number (hexadecimal digit); e.g., 2 or F. In this document registers are referred to symbolically by the letters X and R.

Associated with each register is a stream register. The stream register is named symbolically by putting an S before the symbolic name of the general register:

SR is the stream register associated with register R.

SX is the stream register associated with register X.

#### Core

Any 16-bit quantity can stand for a location in core. Core is divided into 256-byte pages. CP is frequently used as an abbreviation for core page.

#### Streams

Streams are named virtual memories. In order to specify a location in a stream, both the name of the stream (15 bits) and the location within the stream (16 bits) must be given. The following notation is used:

stream name.address in stream .

Streams are divided into 256-byte pages. SP is frequently used as an abbreviation for stream page.

# VALUES

Data in Venus occurs in 8- or 16-bit containers. <u>Bytes</u> are 8-bit containers while <u>halfwords</u> are 16 bits long. Bits in a halfword are numbered from 0 to 15. Core and streams are both addressed at byte boundaries. A halfword consists of two bytes and always starts on an even byte boundary:

If a reference is made to halfword m, where m is odd, then halfword m-1 will be accessed.

No particular meaning is assigned to bytes. However, halfwords contain different kinds of data.

#### Numeric Quantities

All numeric quantities are 16 bits long. A 16-bit quantity may stand for a signed 15-bit integer, an unsigned 16-bit integer, or an address in core or within a stream. Signed integers are all stored in two's complement notation. Bit 0 is the sign bit.

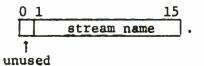

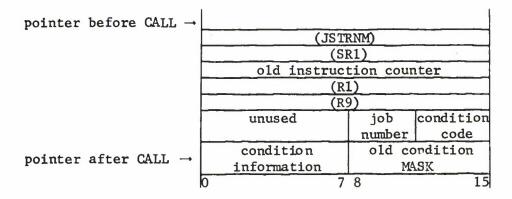

# Stream Names

Stream names are 15 bits long but are contained in a 16-bit halfword with bit zero unused:

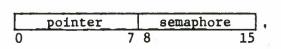

# Semaphores

Semaphores are 7-bit signed integers. They are always located in the right byte of a 16-bit halfword; the left byte contains a pointer to the queue associated with the semaphore:

SYNTAX

The following terminal characters are used to explain the meaning of instructions:

| <u>1f</u>    |                |

|--------------|----------------|

| then         |                |

| else         |                |

| begin        |                |

| end          |                |

| rotated left |                |

| +            | plus           |

| -            | minus          |

| mod          | modulo         |

| •            | stream address |

| *                 | times                                                                                                                                  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ^                 | and                                                                                                                                    |

| v                 | or                                                                                                                                     |

| -1                | not                                                                                                                                    |

| xor               | exclusive or                                                                                                                           |

| =                 | equal                                                                                                                                  |

| ¥                 | not equal                                                                                                                              |

| ;                 | end of statement                                                                                                                       |

| <u>2</u> E        | $\frac{\text{one's complement; for example,}}{2E} = D1$                                                                                |

| ←-                | assignment                                                                                                                             |

| ( )               | <pre>"the contents of"; for example, (R) means the contents of general   register R (A) means the contents of core    location A</pre> |

| <sup>R</sup> 8-15 | subscripts are used whenever less<br>than 16 bits of a 16-bit quantity                                                                 |

| <sup>R</sup> 6    | are used; e.g., $R_{8-15}$ means bits<br>8 through 15 of register R, and<br>$R_6$ means bit 6 of register R                            |

| { }               | used to clarify the extent of an operation                                                                                             |

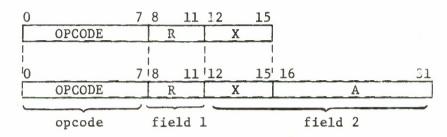

#### NOTATION FOR INSTRUCTIONS

Instructions in Venus consist of an opcode and two fields. They occupy one or two halfwords.

The opcode is 8 bits long. The first field, R, is 4 bits long  $ew^3$  usually contains the number of a general register. The second field is either 4 bits long or 20 bits long. If it is 4 bits long, it contains the number, X, of a general register and the instruction is called a short instruction. A short instruction is written:

OPCODE R,X ·

If the second field is 20 bits long, it is divided into two subfields, A and X. X is the number of a general register and A is a 16-bit quantity. Such an instruction is called a long instruction and is written:

OPCODE R,A(X).

A and X are combined together to form a 16-bit address or a 16- or 8- or 4-bit value.

Some instructions make use of only one field. The same notation is used for fields in this case, so the reader can tell which field is being used and which is omitted. For example:

| JOBA | R    | is a short instruction using only the first field.    |

|------|------|-------------------------------------------------------|

| Р    | A(X) | is a long instruction using only<br>the second field. |

The notation for instructions is introduced here only for the purposes of this document. It is not related to any language running under Venus.

#### CLASSES OF INSTRUCTION

Most instructions in Venus are members of one of the following five classes. Membership in a class determines what the second field of the instruction means.

Class C: Core instructions. Instructions in this class are all long (32 bits). The second field defines a location in core.

Class R: Register instructions. Instructions in this class are all short (16 bits) and the last letter of the opcode mnemonic is usually R. The second field contains the number of a general register.

Class I: Immediate instructions. These instructions are all long and the last letter of the opcode mnemonic is usually I. The second field defines an 8- or 16-bit constant.

Class S: Stream instructions. These instructions are all long and the last letter of the opcode mnemonic is always S. The second field defines a location in a stream.

Class P: Procedure instructions. These instructions are all long and the last letter of the opcode mnemonic is always P. The second field defines a location within the current procedure stream (the procedure which contains the instruction being executed). The name of this procedure is stored in JSTRNM in the job area.

The user should note that store instructions only occur in classes C, R and S. In class I the second field does not provide a location in which to store things. In class P the second field provides a location in a procedure; however, Venus encourages the writing of reentrant procedures by not providing instructions to store in procedures.

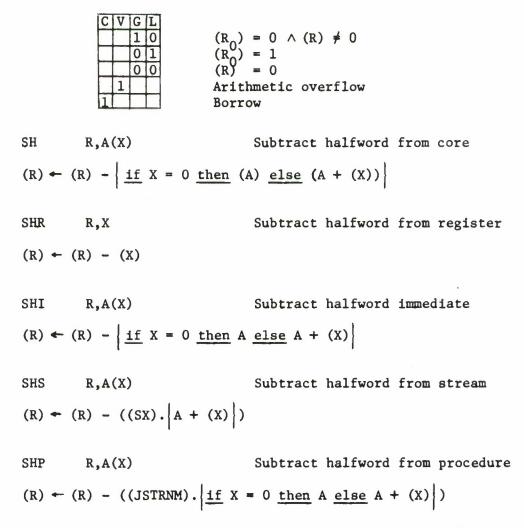

#### CONDITION CODE

The condition code contains information about the effect of a previous instruction. Many instructions set it; some instructions test it. It is composed of four bits: the C, V, G and L bits.

condition code= CVGL

In general these bits have the following meaning:

- C is the "carry" bit. In general it is on if a carry occurred (a 1 was carried out of bit 0) during the execution of a previous instruction.

- V is the "arithmetic overflow" bit. If it is on, then during the execution of some previous instruction the bit carried out of position 1 was not the same as the bit carried out of position 0.

- G is the "greater than zero" bit. If it is on, it means the result of the execution of some previous instruction had bit 0 (the sign bit) off.

- L is the "less than zero" bit. If it is on, then the result of the execution of some previous instruction had bit 0 (the sign bit) on.

#### SECTION III

#### THE JOB AREA

Venus is a multiprogramming system in which 16 jobs can run concurrently. These jobs are numbered in hex from 0 to F. A job area consisting of 156 contiguous bytes of core memory is assigned to each job running under the VENUS system. The first location in the job area for job n is the first location of core page n\*10. The core address of this location is n\*1000. The job area contains the general registers, instruction counter and all other job specific information. In addition it contains data which is used by the system to make the multiprogramming run smoothly.

Throughout the body of this paper, references are made to data in the job area. These references use the symbolic names whose locations are defined in the chart in Appendix III. The true location of any piece of data, D, for job n is

|n\*1000| + D.

For example, the location of the LINK register for job 3 is

|n\*1000| + LINK = |3\*1000| + 6A = 306A.

THE JOB AREA INSTRUCTION

Most instructions which refer to data in the job area are automatically interpreted by the microprogram to refer to the job area of the job executing the instruction. Sometimes, however, it is necessary for a job to know the location of the job area from which it is running. The JOBA instruction provides this information.

Job Area Instruction

JOBA R

As the result of the execution of JOBA, the core address of the first byte of the job area is stored in register R. For example, if job A performs

JOBA R

then the contents of register R become A000.

The condition code is not affected by the JOBA instruction.

## SECTION IV

## VIRTUAL MEMORY

Most data used by a program in Venus will be stored in streams. Streams are named virtual memories, containing 64K bytes of data and having 15-bit names. Streams are divided into 256-byte pages. Core is also divided into 256-byte pages, so that one stream page fits into one core page. The Interdata is supplied with a disk. Streams are paged between disk and core and the microprogram automatically maps stream addresses into core addresses.

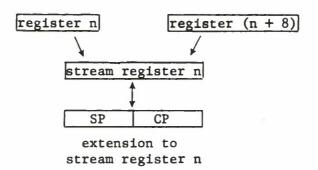

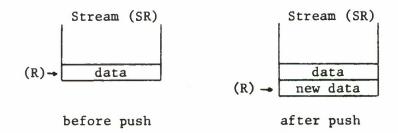

When accessing data within a stream, it is necessary to give the name of the stream and the 16-bit address within the stream. In order to provide space for this data, each job is provided with eight 16-bit stream registers. The stream registers are paired with the general registers: a stream register, general register pair provides the bits needed to reference a stream. The stream register holds the stream name, right adjusted, while the general register holds the address within the stream. Given the number of the general register, X, the number of the associated stream register, SX, is computed simply:

$SX = X \mod 8$ .

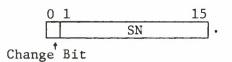

Each stream register is equipped with a 16-bit extension which is also located in the job area. This extension is used by the microprogram to hold information about the mapping of stream addresses into core addresses. Figure 1 shows the relationship between registers, stream registers and extensions.

## MAPPING OF VIRTUAL INTO REAL MEMORY

When a reference is made to a stream, only the general register, X, is mentioned. The microprogram computes the number of the associated stream register, SX, and uses its contents as the stream name, SN. This means that prior to making a reference to a stream, a program must load the stream register being used for the reference with the name of the stream being referenced. The value of the address within the stream, SA, depends upon the instruction being executed.

Figure 1. The Relationship between Registers, Stream Registers and Extensions

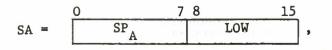

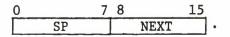

SA is broken into two parts:

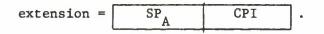

where  $SP_A$  is the stream page and LOW is the address within the stream page. The extension of SX is also broken into two parts:

extension =

$$\begin{bmatrix} 0 & 7.8 & 15 \\ SP & CP \end{bmatrix}$$

,

where SP is a stream page number and CP is a core page number. If CP  $\neq$  0, then stream page SP of the stream whose name is in SX is contained in core page CP. Therefore, if

$$CP \neq 0 \land SP_{A} = SP, \qquad (1)$$

the core address of the desired data is simply

core address = CP LOW .

The desired stream page in this case is called a locked-in page because it is guaranteed to be located in core at core page CP. The reason that this particular page is locked in is because previously a stream reference was made to it through stream register SX. This fact is central to the way programs run in Venus.

If a stream page is in core, the microprogram will find it. However, the amount of time required to locate it varies. If it is locked-in by the stream register being used to reference it, the minimum amount of time is required. Otherwise, the microprogram must search for it. The remainder of this section describes the details of this search.

Whenever (1) above is not true, the microprogram makes use of a table in core called the Core Page Table (CPT). This table contains information about the contents of each core page. Among other things, it contains the stream name and the number of the stream page which occupy a core page. The CPT is indexed by core page and entered by means of a hash chain from hash table HASH. An 8-bit hash code, H, is formed:

$H \leftarrow | SN \land FF | \underline{xor} SP_A.$

H is used as an entry into HASH and a search is made of the hash chain starting from  ${\rm HASH}_{\rm H}$  to see if the desired stream page is contained in core. If it is in core, say at core page CPI, then the core address is

core address = LOW CP1

In addition to forming the core address, the microprogram updates the contents of the extension of stream register SX to contain information about this reference (it locks in the stream page). It becomes

It is likely, of course, that the desired stream page is not in core. This is recognized when the microprogram reaches the end of the hash chain without finding the desired page. The end of the hash chain is recognized by finding a link equal to 0. In this case the microprogram stops right where it is, in the middle of executing an instruction, and starts a software program called the page fault handler (PFH). The PFH will fetch the desired page from the disk, store it in some core page, and update the Core Page Table and the HASH table. Then it returns, via a special instruction (UNQP), to the microprogram at the place from which it was started.

#### THE AGE CHAIN

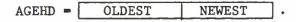

In order to bring a page into core, the PFH will very likely have to remove a page from core. Of course, it cannot remove any page which is locked in. Instead it must remove some page which is not referred to by any stream register extension. It does not need to search the Core Page Table for these pages, however, because the microprogram places all pages which are not locked in on an age chain. The head of the age chain is AGEHD at location 202:

OLDEST is the number of the core page containing the stream page which was released from being locked in longest ago, while NEWEST is the number of the core page containing the stream page which was most recently released. The microprogram is responsible for keeping all pages which are not locked in on the age chain. Two functions are performed by the microprogram to keep the age chain current: <u>aged</u> and <u>unaged</u>. <u>aged</u> is performed whenever a reference is made through a stream register whose extension locks in a different page than the desired one, while <u>unaged</u> is performed when the search through the Core Page Table via the hash chain successfully locates the desired stream page.

The definitions of <u>aged</u> and <u>unaged</u> take account of the fact that in Venus streams are shared. This is obvious from the way the microprogram searches the CPT for a desired stream page. Any job which wants to use a stream simply refers to it by name. This means that when a reference is made through a stream register whose extension locks in a different page, the microprogram cannot automatically put that page on the age chain because it may be referred to by some other stream register extension. Therefore, the microprogram keeps a count for each locked-in page of how many different extensions lock it in.

# THE CORE PAGE TABLE

Before definitions of <u>aged</u> and <u>unaged</u> are given, the Core Page Table must be defined. The CPT is located in core starting at location 200 and extending to 7FF. The table is actually divided into three separate tables. Each of these tables is indexed by core page. The user should note, however, that not all pages in core are available to hold stream pages. Among others, pages are reserved for the job areas and for data used by the microprogram, including the HASH table and the CPT. Spaces thus appear in the CPT and these are sometimes used to hold other information. This means that the CPT can be searched meaningfully only through the hash chains.

For core pages which contain stream pages, the CPT contains the following information.

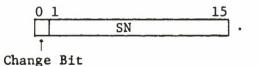

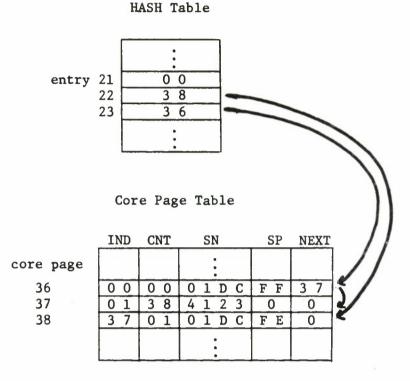

1. SN table. This table is located between 400 and 5FF. For each core page, there is one halfword of information:

Bit 0 of this halfword is set by the microprogram whenever data is stored in the core page. SN is the name of the stream whose page occupies this core page. 2. SPNEXT table. This table is located between 600 and 7FF. For each core page, there is one halfword of information:

SP is the number of the stream page which occupies this core page. NEXT is the core page of the next link on the hash chain. If NEXT = 0, this entry is the end of the chain.

3. INDCNT table. This table is located between 200 and 3FF. For each core page, there is one halfword of information:

This information has two different meanings, depending on whether the stream page is locked in or not.

a. Locked in. The page is locked in if

IND = 0.

In this case CNT equals one less than the number of extensions locking in the page.

b. Aged. The page is on the age chain if

IND  $\neq 0$ .

In this case IND equals the core page of the next newer page on the age chain and CNT equals the number of the next older page.

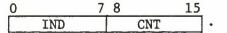

Figure 2 gives an example of how HASH and CPT are used.

- 1. Three entries in HASH are shown.  $HASH_{21} = 0$ , which means no stream page located in core at the moment hashes into 21. HASH<sub>22</sub> and HASH<sub>23</sub> both contain the starts of hash chains. The chain coming from  $HASH_{22}$  is only one link long ( $HASH_{22} = 38$  and  $NEXT_{38} = 0$ ). The chain coming from  $HASH_{23}$  is two links long ( $HASH_{23} = 36$ ,  $NEXT_{36} = 37$ , and  $NEXT_{37} = 0$ ).

- 2. Core page 36 contains stream 1DC, page FF, and core page 37 contains stream 4123, page 0. Both these stream pages produce the same hash code. Core page 38 contains stream 1DC, page FE. Since HASH<sub>21</sub> = 0, stream 1DC, page FD is not in core.

- 3. Stream 1DC, page FF is locked in  $(IND_{36} = 0)$  and has one user  $(CNT_{36} = 0)$ . The other two pages are on the age chain. Stream 1DC, page FE has been on the chain longer than stream 4123, page 0.

Figure 2. Example of Entries in Core Page Table

# Definitions of aged and unaged

Now definitions can be given for <u>aged</u> and <u>unaged</u>. If a stream reference is made through register X and

$CP \neq 0 \land SP \neq SP_A$ ,

then the stream page location in core page CP is aged. This means:

$$(CNT_{CP}) \leftarrow (CNT_{CP}) - 1;$$

if  $(CNT_{CP}) < 0$  then do begin

$(CNT_{CP}) \leftarrow (NEWEST);$

$(IND_{CP}) \leftarrow 1;$

$(IND_{(NEWEST)}) \leftarrow CP;$

$(NEWEST) \leftarrow CP$  end

When the desired stream page is found in core at core page CP1, it is unaged. This means:

$$\frac{\text{if }(\text{IND}_{\text{CP1}}) = 0 \text{ then }(\text{CNT}_{\text{CP1}}) \leftarrow (\text{CNT}_{\text{CP1}}) + 1 \text{ else}}{\text{do begin}}$$

$$(CNT_{(IND_{CP1})}) \leftarrow (CNT_{CP1});$$

$$(IND_{(CNT_{CP1})}) \leftarrow (IND_{CP1});$$

$$(IND_{CP1}) \leftarrow 0;$$

$$(CNT_{CP1}) \leftarrow 0 \quad end$$

17

## STREAM REGISTER INSTRUCTIONS

When a reference is made to a stream, only the general register, X, is mentioned. The microprogram computes the name of the associated stream register, SX, and uses its contents as the stream name. This means that prior to making a reference to a stream, a program must load the stream register, SX, being used for the reference with the name of the stream being referenced. The "load stream name" instructions are defined for this purpose. The "store stream name" instructions are used to save the contents of stream registers.

#### Load Stream Name

The second field defines a stream name. This name is compared with the current contents of the stream register, SR, associated with the general register R. If the names are the same, the instruction is finished. If the names are different and some stream page is locked in by the extension of SR, that stream page is <u>aged</u>. The core page in the extension is set to zero. The stream name is then loaded into SR. The condition code is not affected.

| LSN    | R,A(X)                                                                                 | Load stream nam     | e from core      |

|--------|----------------------------------------------------------------------------------------|---------------------|------------------|

| (SR) ← | $\frac{\text{if } X = 0 \text{ then } (A) \text{ el}}{\text{ then } (A) \text{ el}}$   | <u>se</u> (A + (X)) |                  |

| LSNR   | R,X                                                                                    | Load stream nam     | e from register  |

| (SR) ← | (X)                                                                                    |                     |                  |

| LSNI   | R,A(X)                                                                                 | Load stream nam     | e immediate      |

| (SR) ← | $\frac{\text{if } X = 0 \text{ then } A \text{ else}}{1 \text{ then } A \text{ else}}$ | A + (X)             |                  |

| LSNS   | R,A(X)                                                                                 | Load stream nam     | e from stream    |

| (SR) ← | ((SX).  A + (X) )                                                                      |                     |                  |

| LSNP   | R,A(X)                                                                                 | Load stream nam     | e from procedure |

| (SR) ← | $((JSTRNM).   \underline{if} X = 0 \underline{t}$                                      | hen A else A + (    | X)))             |

# Store Stream Name

The contents of the stream register, SR, associated with R are stored in the location specified by the second field. The condition code is not affected.

SSNR,A(X)Store stream name in coreifX = 0 then(A)  $\leftarrow$  (SR)else(A + (X))  $\leftarrow$  (SR)SSNRR,XStore stream name in register(X)  $\leftarrow$  (SR)Store stream name in stream((SX). |A + (X)|)  $\leftarrow$  (SR)

#### SECTION V

#### BASIC INSTRUCTIONS

# LOAD AND STORE INSTRUCTIONS

These instructions allow the user to move data from one location to another.

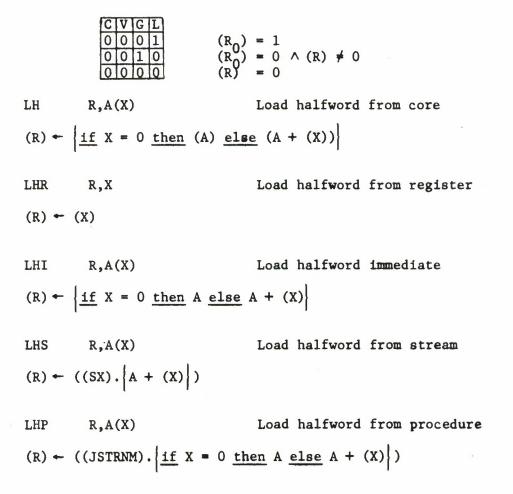

# Load Halfword

The value of the second field defines a 16-bit halfword. It is loaded into the general register R. Load instructions set the condition code as follows:

# Load Byte

The value of the second field defines an 8-bit byte. It is stored in the right byte of R. The left byte of R is set to 0. The condition code is not affected.

LB R,A(X)Load byte from core  $(R_{0-7}) \leftarrow 0$  $(R_{8-15}) \leftarrow \left| \underline{\text{if } X = 0 \underline{\text{then}}} (A) \underline{\text{else}} (A + (X)) \right|$ LBR R,X Load byte from register  $(R_{0-7}) \leftarrow 0$  $(R_{8-15}) \leftarrow (X_{8-15})$ LBI R,A(X) Load byte immediate  $(R_{0-7}) \leftarrow 0$  $(R_{8-15}) \leftarrow \left| \underline{if} X = 0 \underline{then} A_{8-15} \underline{else} \left| A + (X) \right|_{8-15} \right|$ LBS R,A(X)Load byte from stream  $(R_{0-7}) \leftarrow 0$  $(R_{8-15}) \leftarrow ((SX). |A + (X)|)$ LBP R,A(X) Load byte from procedure  $(R_{0-7}) \leftarrow 0$  $(R_{8-15}) \leftarrow ((JSTRNM) \cdot | \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | )$

# Store Halfword

The contents of R are stored in the location indicated by the second field. The condition code is not affected.

STHR,A(X)Store halfword in coreifX = 0 then(A)  $\leftarrow$  (R)else(A + (X))  $\leftarrow$  (R)STHRR,XStore halfword in register(X)  $\leftarrow$  (R)Store halfword in stream((SX). |A + (X)|)  $\leftarrow$  (R)

Store Byte

The contents of  $R_{8-15}$  are stored in the location specified by the second field. The condition code is not affected.

| STB       |   |   | R | R,A(X) |       | Store byte in core   |      |      | core |                        |

|-----------|---|---|---|--------|-------|----------------------|------|------|------|------------------------|

| <u>if</u> | X | = | 0 | then   | (A) ← | (R <sub>8-15</sub> ) | else | (A + | (X)) | ← (R <sub>8-15</sub> ) |

- STBR R,X Store byte in register  $(X_{8-15}) \leftarrow (R_{8-15})$

- STBS R,A(X) Store byte in stream  $((SX) \cdot | A + (X) |) \leftarrow (R_{8-15})$

#### ARITHMETIC INSTRUCTIONS

Addition and subtraction are the only arithmetic instructions supported by the Venus microprogram. These instructions operate on halfwords of data.

# Add Halfword

The second field defines a 16-bit value. It is added to the contents of R. The result is stored in R. The condition code becomes:

| С | V | G | $\mathbf{L}$ |                              |

|---|---|---|--------------|------------------------------|

|   |   | 1 | 0            | $(R_0) = 0 \land (R) \neq 0$ |

|   |   | 0 | 1            | $(R_0^0) = 1$                |

|   |   | 0 | 0            | (R) = 0                      |

|   | 1 |   |              | · Arithmetic overflow        |

| 1 |   |   |              | Carry                        |

AH R,A(X) Add halfword from core (R)  $\leftarrow$  (R) +  $\left| \underline{\text{if}} X = 0 \underline{\text{then}} (A) \underline{\text{else}} (A + (X)) \right|$

AHR R,X Add halfword from register  $(R) \leftarrow (R) + (X)$

AHIR,A(X)Add halfword immediate $(R) \leftarrow (R) + | \underline{if} X = 0 \underline{then} A \underline{else} A + (X) |$

AHS R,A(X) Add halfword from stream (R)  $\leftarrow$  (R) + ((SX). | A + (X) |)

AHP R,A(X) Add halfword from procedure (R)  $\leftarrow$  (R) + ((JSTRNM).  $| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | )$

23

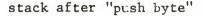

# Subtract Halfword

The second field defines a 16-bit value. It is subtracted from the contents of R. The result is stored in R. The condition code becomes:

Programmer's Note: The result of the subtraction is in two's complement form. For example, the result of subtracting 3 from 2 is FFFF, and C is set.

# Add with Carry Halfword

The second field defines a 16-bit value. This value and the carry bit, C, are added to the contents of R. The result is stored in R. The value of the condition code depends on its value prior to the execution of the instruction:

| C | V | G |   | 1                                                                                 |

|---|---|---|---|-----------------------------------------------------------------------------------|

|   |   | 1 | 0 | $(R_0) = 0 \land (R) \neq 0 \lor$ the G or L bit was on                           |

|   |   | 0 | 1 | $(R_0^0) = 1$                                                                     |

|   |   | 0 | 0 | $(\mathbf{R}_{0}^{U}) = 0 \land \{the  G \text{ and } L \text{ bits were off} \}$ |

|   | 1 |   |   |                                                                                   |

| 1 |   |   |   | Carry                                                                             |

ACH R,A(X) Add with carry halfword from core (R)  $\leftarrow$  (R) +  $\left| \underline{\text{if}} X = 0 \underline{\text{then}} (A) \underline{\text{else}} (A + (X)) \right| + C$

ACHR R,X Add with carry halfword from register  $(R) \leftarrow (R) + (X) + C$

ACHI R,A(X) Add with carry halfword immediate (R)  $\leftarrow$  (R) +  $\left| \underbrace{\text{if } X = 0 \underbrace{\text{then}} A \underbrace{\text{else}} A + (X) \right| + C$

ACHS R,A(X) Add with carry halfword from stream  $(R) \leftarrow (R) + ((SX).|A + (X)|) + C$

ACHP R,A(X) Add with carry halfword from procedure (R)  $\leftarrow$  (R) + ((JSTRNM).  $| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | ) + C$

Programmer's Note: Multiple precision addition may be accomplished by using an "add" instruction for the least significant portion of the two operands and then using an "add with carry halfword" instruction for the remainder of the operation. The result will be in two's complement form. The G and L bits will tell the sign of the multiple precision result.

# Subtract with Carry Halfword

The second field defines a 16-bit value. This value and the carry bit, C, are subtracted from the contents of R. The result is stored in R. The value of the condition code depends on its value prior to the execution of the instruction:

Borrow

SCH  $R_A(X)$ Subtract with carry halfword from core  $(R) \leftarrow \left| (R) - \left| \underline{if} X = 0 \underline{then} (A) \underline{else} (A + (X)) \right| \right| - C$

SCHR R.X Subtract with carry halfword from register  $(R) \leftarrow |(R) - (X)| - C$

SCHI R.A(X) Subtract with carry halfword immediate  $(R) \leftarrow \left| (R) - \left| \underbrace{\text{if } X = 0 \text{ then } A \text{ else } A + (X) \right| \right| - C$

SCHS  $R_A(X)$ Subtract with carry halfword from stream  $(R) \leftarrow |(R) - ((SX).|A + (X)|)| - C$

$R_A(X)$ SCHP Subtract with carry halfword from procedure  $(R) \leftarrow |(R) - ((JSTRNM))| | if X = 0 then A else A + (X) | ) | - C$

Programmer's Note: See the "add with carry halfword" instructions.

## LOGICAL INSTRUCTIONS

The logical instructions permit the user to perform logical "and", "or", and "exclusive or" operations. These operations are always performed on 16-bit unsigned integers. A logical comparison is also available.

# And Halfword

A logical "and" is performed on the 16-bit value defined by the second field and the 16-bit contents of R. The result is stored in R. The condition code is set:

|     | / G | L<br>0 | $(R_0) = 0 \land (R) \neq 0$<br>$(R_0) = 1$ | 1 |

|-----|-----|--------|---------------------------------------------|---|

| 0 ( | 0 0 | 1      | $(R_0^0) = 1$                               |   |

| 010 | 00  | 0      | (R) = 0                                     |   |

NH  $R_A(X)$ And halfword from core  $(R) \leftarrow (R) \land \left| \underline{if} X = 0 \underline{then} (A) \underline{else} (A + (X)) \right|$ NHR R,X And halfword from register  $(R) \leftarrow (R) \land (X)$ NHI R,A(X)And halfword immediate  $(R) \leftarrow (R) \land \left| \underline{\text{if}} X = 0 \underline{\text{then}} A \underline{\text{else}} A + (X) \right|$ NHS R,A(X)And halfword from stream  $(R) \leftarrow (R) \land ((SX). |A + (X)|)$ NHP R,A(X)And halfword from procedure  $(R) \leftarrow (R) \land ((JSTRNM), | \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | )$

27

# Or Halfword

A logical "or" is performed on the 16-bit value defined by the second field and the 16-bit contents of R. The result is stored in R. The condition code is set:

|       | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                            | = $0 \wedge (R) \neq 0$<br>= 1<br>= $0$ |

|-------|-----------------------------------------------------------------------------------|-----------------------------------------|

| ОН    | R,A(X)                                                                            | Or halfword from core                   |

| (R) ← | (R) $\vee   \underline{\text{if}} X = 0 \underline{\text{then}} $ (A              | ) <u>else</u> $(A + (X))$               |

| OHR   | R,X                                                                               | Or halfword from register               |

| (R) ← | (R) V (X)                                                                         |                                         |

| OHI   | R,A(X)                                                                            | Or halfword immediate                   |

| (R) ← | $(R) \vee \left  \underline{\text{if }} X = 0 \underline{\text{then }} A \right $ | else $A + (X)$                          |

| OHS   | R,A(X)                                                                            | Or halfword from stream                 |

| (R) ← | $(R) \vee ((SX) \cdot  A + (X) )$                                                 |                                         |

| OHP   | R,A(X)                                                                            | Or halfword from procedure              |

| (R) ← | (R) $\vee$ ((JSTRNM). $  \underline{1f} X \rangle$                                | = 0 then A else A + $(X)$ )             |

28

# Exclusive Or Halfword

A logical "exclusive or" is performed on the 16-bit value defined by the second field and the 16-bit contents of R. The result is stored in R. The condition code is set:

|       | C         V         G         L           0         0         1         0         (R           0         0         0         1         (R           0         0         0         0         (R | $ \begin{array}{l} 0) = 0 \land (R) \neq 0 \\ 0) = 1 \\ 0) = 0 \end{array} $             |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| ХН    | R,A(X)                                                                                                                                                                                         | Exclusive or halfword from core                                                          |

| (R) ← | (R) $\underline{\operatorname{xor}} \left  \underline{\operatorname{if}} X = 0 \underline{t} \right $                                                                                          | hen (A) else (A + (X))                                                                   |

| XHR   | R,X                                                                                                                                                                                            | Exclusive or halfword from register                                                      |

| (R) ← | (R) <u>xor</u> (X)                                                                                                                                                                             |                                                                                          |

| XHI   | R,A(X)                                                                                                                                                                                         | Exclusive or halfword immediate                                                          |

| (R) ← | (R) $\underline{\operatorname{xor}} \left  \underline{\operatorname{if}} X = 0 \underline{\operatorname{th}} \right $                                                                          | en A else A + (X)                                                                        |

| XHS   | R,A(X)                                                                                                                                                                                         | Exclusive or halfword from stream                                                        |

| (R) ← | (R) <u>xor</u> ((SX). $ A +$                                                                                                                                                                   | (X))                                                                                     |

|       | R,A(X)                                                                                                                                                                                         | Exclusive or halfword from procedure                                                     |

| (R) ← | (R) xor ((JSTRNM).                                                                                                                                                                             | $\underline{\text{if } X = 0 \underline{\text{then}} A \underline{\text{else}} A + (X)}$ |

29

#### Compare Logical Halfword

The 16-bit value defined by the second field is compared logically with the contents of R. The different versions of the instruction differ only in the computation of the value. The condition code is set by subtracting the value defined by the second field from (R). This is exactly the same as if the instruction were a subtract. However, only the condition code is affected by the instruction.

CLH R,A(X)Compare logical halfword from core value =  $\frac{\text{if } X = 0 \text{ then}}{\text{then}}$  (A) else (A + (X)) CLHR R,X Compare logical halfword from register value = (X)CLHI R.A(X) Compare logical halfword immediate value =  $\left| \frac{\text{if } X = 0 \text{ then } A \text{ else } A + (X) \right|$ CLHS R,A(X) Compare logical halfword from stream value = ((SX). |A + (X)|)CLHP R,A(X)Compare logical halfword from procedure value = ((JSTRNM).  $| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | )$

### SHIFT INSTRUCTIONS

Shift instructions permit the user to shift a 16-bit halfword to the left or right, or to rotate a 16-bit halfword to the left. In addition, a signed 15-bit integer may be shifted arithmetically to the right. Rotate Left Halfword

RLH R,A(X)

The contents of R are rotated left the number of bits specified by the second field  $\underline{mod}$  16. The result is stored in R:

(R) - (R) rotated left  $| | \underline{1f} X = 0 \underline{then} A \underline{else} A + (X) | \underline{mod} 16 |$ .

The condition code is set as follows:

| C | V | G | L |                                             |

|---|---|---|---|---------------------------------------------|

|   | 0 | 1 | 0 | $(R_0) = 0 \land (R) \neq 0$<br>$(R_0) = 1$ |

|   | 0 | 0 | 1 |                                             |

| 0 | 0 | 0 | 0 | $(\mathbf{R}) = 0$                          |

| 1 | 0 |   |   | $(R_{15}) = 1$                              |

| 0 | 0 |   |   | $(R_{15}^{13}) = 0$                         |

Shift Left Halfword Logical

SLHL R,A(X)

The contents of R are shifted left the number of bits specified by the second field mod 16:

Amount of shift =  $\left| \frac{\text{if } X = 0 \text{ then } A \text{ else } A + (X) \right| \mod 16$ .

Bits shifted out of position 0 are shifted through the carry bit of the condition code. Zeros are shifted into position 15. The result is stored in R. The condition code is set as follows:

| C | V | G | L |                   |     |         |     |    |          |   |     |   |   |

|---|---|---|---|-------------------|-----|---------|-----|----|----------|---|-----|---|---|

| Γ | 0 | 1 | 0 | (R <sub>0</sub> ) | = 0 | ^ (R) ≠ | 0   |    |          |   |     |   |   |

|   | 0 | 0 | 1 | $(R_0)$           | = 1 | ^ (R) ≠ |     |    |          |   |     |   |   |

|   | 0 | 0 | 0 | (R)               | = 0 |         |     |    |          |   |     |   |   |

| 1 | 0 |   |   | last              | bit | shifted | out | of | position | 0 | was | а | 1 |

| 0 | 0 |   |   | last              | bit | shifted | out | of | position | 0 | was | а | 0 |

31

# Shift Right Halfword Logical

SRHL R,A(X)

The contents of R are shifted right the number of bits specified by the second field mod 16:

Amount of shift =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right| \underline{mod} 16$ .

Bits shifted out of position 15 are shifted through the carry bit of the condition code. Zeros are shifted into position 0. The result is stored in R.

The condition code is set as follows:

|    | G<br>1 | L<br>0 | (R <sub>0</sub> ) | = 0 | ^ (R)  | <b>≠</b> 0 |    |          |    |     |   |   |

|----|--------|--------|-------------------|-----|--------|------------|----|----------|----|-----|---|---|

| 0  | 0      | 1      | $(R_0^0)$         | = 1 | ^ (R)  |            |    |          |    |     |   |   |

| 0  | 0      | 0      | (R)               | = 0 |        |            |    |          |    |     |   |   |

| 10 |        |        | last              | bit | shifte | d out      | of | position | 15 | was | а | 1 |

| 00 |        |        | last              | bit | shifte | d out      | of | position | 15 | was | а | 0 |

Shift Right Halfword Arithmetic

SRHA R,A(X)

$(R)_{1-15}$  are shifted right the number of bits specified by the second field mod 16:

Amount of shift =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right| \underline{mod} 16$ .

The sign bit  $(R_0)$  is unchanged. Bits shifted out of position 15 are shifted through the carry bit. The sign bit  $(R_0)$  is propagated into position 1, for each bit shifted.

The condition code is set as follows:

| С | V | G | L |                         |     |            |       |     |     |    |          |    |     |   |   |

|---|---|---|---|-------------------------|-----|------------|-------|-----|-----|----|----------|----|-----|---|---|

|   | 0 | 1 | 0 | $(R_{0})$               | = 0 | <b>^</b> ( | (R) 🕴 | ŧ I | 0   |    |          |    |     |   |   |

|   | 0 | 0 | 1 | $(R_0) \\ (R_0) \\ (R)$ | = 1 |            |       |     |     |    |          |    |     |   |   |

|   | 0 | 0 | 0 | (R)                     | = 0 |            |       |     |     |    |          |    |     |   |   |

| 1 | 0 |   |   | last                    | bit | shi        | lfte  | d   | out | of | position | 15 | was | a | 1 |

| 0 | 0 |   |   | last                    | bit | shi        | lfte  | d   | out | of | position | 15 | was | a | 0 |

### SECTION VI

## CONDITIONS

Conditions represent a set of events which, when enabled by a mask, can cause interrupts in a running job. These interrupts are intended to aid the user in debugging his program. The microprogram or software recognizes the occurrence of an event. The interrupt which results causes the execution of an instruction out of sequence. This instruction can start a software debugging routine. Conditions should not be confused with the condition code.

Conditions are controlled by a 16-bit condition register, COND, and an 8-entry instruction table, with room for one 32-bit instruction per condition. COND is broken into two bytes: ON and MASK.

COND = ON MASK

Each bit in ON, if set to 1, indicates the occurrence of a condition. The corresponding bits in MASK are used as a mask. If the bit for an interrupt is set in ON, then the condition is said to be on; if the bit is set in MASK, the condition is enabled.

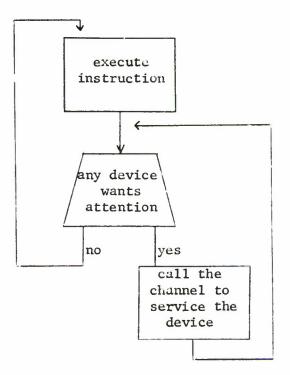

The microprogram checks for the occurrence of conditions at the beginning of each instruction cycle. If a condition is both on and enabled, an interrupt occurs: the corresponding condition instruction (16 or 32 bits long) in the instruction table is executed, and the condition is turned off. The core location of the instruction which would have been executed if the interrupt had not occurred is stored in TEMPIC. The event which caused the condition bit to be turned on must have happened before the start of the current instruction cycle.

Each condition is assigned a priority, which is reflected in the assignment of the bits, with the highest priority conditions on the left, decreasing toward the right. If more than one on/mask combination is on, the higher priority condition is honored first. If the instruction for this condition is a CALL, as will very frequently be the case, the condition which is being handled and all lower priority conditions (with the exception of the "in-stream illegal instruction" condition) are disabled. They are re-enabled by the execution of the corresponding RETN. The eight condition bits are assigned as follows:

| Bit | Interrupt Condition                 |  |  |  |  |  |  |  |

|-----|-------------------------------------|--|--|--|--|--|--|--|

| 0   | ki11                                |  |  |  |  |  |  |  |

| 1   | every instruction                   |  |  |  |  |  |  |  |

| 2   | undefined                           |  |  |  |  |  |  |  |

| 3   | <pre>stack overflow/underflow</pre> |  |  |  |  |  |  |  |

| 4   | call                                |  |  |  |  |  |  |  |

| 5   | undefined                           |  |  |  |  |  |  |  |

| 6   | illegal in-core instruction         |  |  |  |  |  |  |  |

| 7   | illegal in-stream instruction       |  |  |  |  |  |  |  |

<u>Kill</u> would normally be turned on by system software when it determines that this job should be terminated. The "kill" condition is always enabled for user programs.

Every instruction is turned on after the execution of every instruction, except the instruction executed as a result of the "every instruction" interrupt. It is turned off by RETN if the return is from a procedure whose execution began as the result of the "every instruction" interrupt.

Undefined occurs only when turned on by software.

<u>Stack overflow/underflow</u> is set when a push or a pop of a stack would store or retrieve from beyond the stack.

<u>Call</u> is set when a CALL instruction is executed, except when the CALL is the instruction to be executed on a "call" condition.

Illegal in-core instruction will be set when an unimplemented instruction is encountered while processing instructions in-core (as opposed to in-stream). The job executing this instruction will normally be running a level 1 program. The microprogram enables this interrupt as well as turning it on.

<u>Illegal in-stream instruction</u> occurs when an unimplemented instruction is encountered in a program running from a procedure stream. This condition is always enabled for programs running from streams, and is used by the microprogram to distinguish between in-core and in-stream programs. When an illegal instruction is encountered, the instruction counter is stepped by the assumed length of the illegal instruction. The microprogram stores information about the amount of change to the instruction counter in TUTFF in the job area. If bit 6 of TUTFF is on, the program counter has been stepped by 4; otherwise it has been stepped by 2. If the illegal instruction is a condition instruction, the address of this condition instruction relative to the job area is stored in OLDTP. A value for the second field may have been developed before the instruction was discovered to be illegal. This value is stored in TR5R6. A list of the opcodes for which this value is developed is given in Appendix V.

#### CONDITION INSTRUCTIONS

Two instructions have been defined to modify COND. SET will turn bits on in COND and RSET will turn them off. However, RSET will not turn off either the "kill" bit or the "in-stream" bit. Neither instruction affects the condition code.

Reset Condition Register

RSET R,A(X)

.

RSET turns off bits in the condition register of the job specified in register R, or the job in which the RSET occurred if R = 0. The bits to be turned off are those which correspond to the bits set in the 16-bit value defined by the second field:

1.1

$$(COND) \leftarrow (COND) \land \left| 81 \lor \left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right| \right|.$$

.

Programmer's Note: The "kill" condition and the "in-stream" condition cannot be disabled.

Set Condition Register

SET R,A(X)

SET turns on bits in the condition register of the job specified in register R, or the job in which the SET occurred if R = 0. The bits turned on correspond to the bits which are on in the 16-bit value defined by the second field:

(COND)

$$\leftarrow$$

(COND)  $\vee$   $\left| \underline{\text{if } X} = 0 \underline{\text{then}} A \underline{\text{else}} A + (X) \right|.$

Programmer's Note: When a condition is enabled, an interrupt will take place if the condition occurred in the past. To avoid this, RSET may be used prior to SET to turn off the condition.

#### SECTION VII

#### PUSHDOWN STACKS

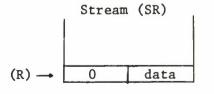

Streams may be used as pushdown stacks in Venus. When used as a stack, a stream is considered to be a collection of halfwords. Associated with each stack is a stack pointer. A stack pointer is a 32-bit entity contained in a general register, R, and the associated stream register, SR. This pointer always points to the piece of data in the top of the stack.

Stack operations do not affect the condition code. They may, however, turn on the "stack underflow/overflow" bit in the condition register COND. If a stack operation would cause a stack to underflow or overflow, the "underflow/overflow" bit in COND is turnel on and the instruction is not executed. In addition, the number of the stream register being used to reference the stack is stored in SAVREG<sub>3-5</sub> in the job area. That is:

<u>if</u>  $(R) = FFFE \land instruction is push <math>\lor$   $(R) = 0 \land$

instruction is pop then

1) The underflow/overflow bit in COND is turned on.

2) The instruction is not executed.

3) (SAVREG<sub>3-5</sub>)  $\leftarrow$  SR.

In the following descriptions of the stack instructions, it is assumed that overflow/underflow does not occur.

#### STACK INSTRUCTIONS

## Push Halfword

The contents of R are incremented by two. The 16-bit value defined by the second field is pushed into the stack named by SR at the location specified by the incremented value of R.

Push halfword from core PU R.A(X) $(R) \leftarrow (R) + 2$  $((SR).(R)) \leftarrow | if X = 0 then (A) else (A + (X)) |$ PUR R.X Push halfword from register  $(R) \leftarrow (R) + 2$  $((SR).(R)) \leftarrow (X)$ PUI R,A(X)Push halfword immediate  $(R) \leftarrow (R) + 2$  $((SR).(R)) \leftarrow | if X = 0 then A else A + (X) |$ PUS R,A(X)Push halfword from stream (R) ← (R) + 2  $((SR).(R)) \leftarrow ((SX).|A + (X)|)$ PUP R,A(X)Push halfword from procedure  $(R) \leftarrow (R) + 2$  $((SR).(R)) \leftarrow ((JSTRNM). | \underline{if} X = 0 \underline{then} A \underline{else} A + (X) | )$

# Push Byte

The contents of R are incremented by two. A sixteen-bit value consisting of a zero in the high byte and the eight-bit value defined by the second field in the low byte is placed in the stack named by SR at the location specified by the incremented value of the R.

#### Pop Halfword

A sixteen-bit value is fetched from the stack named by SR at the location specified by R and stored in the location specified by the second field. Then the contents of R are decremented by two.

PO R,A(X) Pop halfword into core <u>if</u> X = 0 <u>then</u> (A)  $\leftarrow$  ((SR).(R)) <u>else</u> (A + (X))  $\leftarrow$  ((SR).(R)) (R)  $\leftarrow$  (R) - 2 POR R,X Pop halfword into register (X)  $\leftarrow$  ((SR).(R)) (R)  $\leftarrow$  (R) - 2 POS R,A(X) Pop halfword into stream ((SX).  $|A + (X)| ) \leftarrow$  ((SR).(R)) (R)  $\leftarrow$  (R) - 2

## Pop Byte

A halfword is fetched from the stack named by SR at the location specified by R. The low eight bits of this halfword are stored in the location indicated by the second field. Then the contents of R are decremented by two.

POB R,A(X) Pop byte into core if X = 0 then (A)  $\leftarrow$  (|(SR).(R)|<sub>8-15</sub>) else (A + (X))  $\leftarrow$  (|(SR).(R)|<sub>8-15</sub>) (R)  $\leftarrow$  (R) - 2

POBR R,X Pop byte into register

$$(\mathbf{X}_{8-15}) \leftarrow (|(SR).(R)|_{8-15})$$

$(R) \leftarrow (R) - 2$

POBS R,A(X) Pop byte into stream  $(|(SX).|A + (X)||_{8-15}) \leftarrow (|(SR).(R)|_{8-15})$  $(R) \leftarrow (R) - 2$

#### SECTION VIII

#### THE CONTROL STACK

Each job is provided with a control stack which is used to hold information about the environment. A user may save the contents of a register, stream register or condition instruction by means of a "push into control stack" (PUC) instruction. The "pop from the control stack" instruction (POC) restores information entered in the control stack by a PUC.

The only other instructions which affect the control stack are the CALL and RETN instructions. These instructions are defined in the next section. CALL leaves a record of seven halfwords, called the activation record, in the control stack. This means that the control stack contains a running history of the job. Some programs are interested in using this history -- for example, debugging aids. Such programs may use the control stack as a stream. This can be done by picking up the name of the control stack from location CSNAME in the job area. The pointer to the top of the control stack is also needed. The stream page of this pointer is in  $CSEXT_{0-7}$ ; the low part of the pointer is in  $CSREG_{8-15}$ .

Stack overflow and underflow are recognized for all operations on the control stack. In addition, pseudo overflow is recognized for the control stack.

- True overflow or underflow: If during the course of a control stack instruction, true overflow or underflow occurs, then SAVREG<sub>0</sub> is turned on, the "stack overflow/underflow" bit is turned on, and the instruction becomes a NOP.

- 2. Pseudo overflow occurs if during the interpretation of a PUC or CALL, the last page of the control stack stream is entered. In this case SAVREG<sub>0</sub> is turned on and the "stack overflow/underflow" bit is turned on, but the execution of the instruction is continued.

In the descriptions of control stack instructions which follow, it is assumed that underflow and overflow do not occur.

# CONTROL STACK INSTRUCTIONS

# Push into the Control Stack

PUC N

The format of PUC is different from that of any other instruction. It is a short instruction:

| 0  | 78 | 15  |

|----|----|-----|

| 52 |    | N • |

N is the 8-bit address of the halfword in the job area which is to be saved. N must be the address of a general register, stream register or (part of a) condition instruction. These are all grouped together in the bottom of the job area. If N is not an allowable address, which is true if N  $\geq$  50, then the microprogram will not execute the PUC. It becomes a NOP.

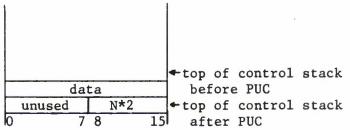

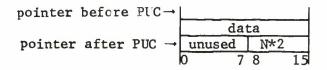

If N is legal, first the halfword pointed to by N is pushed into the control stack. Then a control word equal to N\*2 is pushed in. We have

The condition code is not changed.

#### Pop from Control Stack

## POC

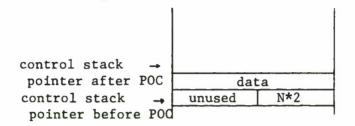

The halfword in the top of the control stack is examined. If bit 15 = 1, then the top record in the control stack is an activation record (see CALL) rather than a PUC record. In this case the POC has no effect, but the carry bit in the condition code is turned on. If bit 15 is off, then the top record in the control stack is a PUC record. This means bits 8 to 14 of the top halfword contain the address in the job area in which the data should be stored.

This data is fetched (from the next word in the control stack) and stored in the correct place. Recall that N is the address of a general register, stream register or (part of a) condition instruction. If N is the address of a stream register, then the effect of the POC instruction on N is precisely the same as if a "load stream name" instruction were being used to set the stream register at N. This means, if

then nothing further is done, but otherwise the page referred to by the extension of the stream register at N is <u>aged</u> and then

# (N) ← data.

If N is the address of a general register or condition instruction, then

The effect of POC on the condition code is:

Top record in Control Stack is an activation record. Top record in Control Stack was a PUC record.

POC does not affect the V, G or L bits.

Programmer's Note: POC is defined so that a user can restore the job area without having to count the number of PUC's. Instead he performs

> A POC BFC 8,A(0) (see next section)

The branch falls through when the activation record is reached.

### SECTION IX

# PROCEDURES

Procedures reside in streams, one procedure per stream. Procedure streams have the following format:

| bytes 0 - 1     | alternate name for job in job area 0.                                     |

|-----------------|---------------------------------------------------------------------------|

| bytes 2 - 3     | alternate name for job in job area 1.                                     |

| •               |                                                                           |

| bytes 1E - 1F   | alternate name for job in job area F.                                     |

| bytes 20 - 23   | pointer to control information for procedure.                             |

| bytes 24 - FFFF | body of procedure; the first location of the procedure is at location 24. |

An alternate name is the stream name of a procedure stream. Alternate names have the following use. Suppose a job, job n, wishes to use an alternate representation of a system procedure, say SQRT, in such a way that even system routines which it calls will use its version of SQRT. Other jobs running simultaneously may also refer to SQRT; these jobs will want the original version of SQRT. Both requirements are satisfied if job n sets halfword 2n in the procedure stream containing the original version of SQRT to the stream name of the procedure stream containing its version of SQRT. This binding may only occur at execution time and must be undone when job n stops running. A zero in halfword 2n means there is no alternate name for job n.

The pointer to control information is large enough to hold an entire stream address. What the control information is and where it is stored will be defined by software.

Jobs under Venus are almost always running from a procedure (in stream mode with COND<sub>15</sub> on). The name of the procedure which is running from a job area is stored in JSTRNM in that job area. When this job is the running job, the core address of the next instruction to be executed is kept in the micro-registers. When the job is not running, this pointer is kept in PC in the job area. In either case the number of the stream page containing the next instruction to be executed is kept in ICSTRP in the job area. This stream page is locked in.

In addition to this page, one other procedure page may be locked in. This is called the alternate procedure page. The alternate procedure page is the page of the procedure referenced immediately before the current page. The number of this page and the number of the core page containing it are stored in JEXT in the job area. JEXT is like any stream register extension: if the core page equals zero, this indicates no page is locked in.

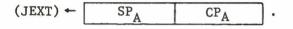

The stepping of the instruction counter in stream mode may cause a page fault within the procedure stream. When the microprogram determines that a new procedure page may be required, which would happen as the result of a branch instruction, it compares the new stream page, SP, with the current stream page,  $SP_C$ . If these pages are the same, there is no difficulty. If they are different, or if the instruction counter has run over the top of the current stream page, the microprogram compares the new stream page with the alternate stream page,  $SP_A$ .  $SP_A$  is stored in JEXT:

If

$$CP_A \neq 0 \land SP = SP_A,$$

then the current and alternate procedure pages are exchanged. This means:

1) (JEXT) ← SP<sub>C</sub> current core page

2) (ICSTRP) -  $SP_A$

The new core location is stored in the micro-registers. No page swapping is required in this case.

If

$$CP_{A} = 0 \vee SP \neq SP_{A}$$

,

then the alternate procedure page is <u>aged</u>, and the current procedure page becomes the alternate procedure page:

Then the new stream page is located (and possibly fetched from the disk). Finally,

# (ICSTRP) ← SP

and the new core location is stored in the micro-registers.

Two instructions, CALL and RETN, are supplied for transfer of control between procedures. Branch instructions only transfer control within a procedure.

## BRANCH INSTRUCTIONS

The result of executing a branch instruction in Venus depends on the mode in which the job is running. Jobs in Venus usually run in stream mode, but occasionally a job will run in core mode. Bit 15 of COND in the job area tells what the mode is. If bit 15 in COND is off, the branch will be to a location in core.

If bit 15 in COND is on, then the job is in stream mode. The branch will be to another location in the same stream in this case; in other words, the branch goes to another location in the same procedure. Control cannot be switched from one procedure to another by means of a branch instruction.

Branch instructions do not affect the condition code. However, some branch instructions test the condition code. In these instructions the first field is a 4-bit mask, M. This mask is compared with the condition code. The four bits of the condition code are arranged:

condition code = CVGL.

Therefore,  $M_0$  is compared with C,  $M_1$  with V,  $M_2$  with G and  $M_3$  with L.

#### Branch on True Condition

A logical "and" is performed on the 4-bit mask M specified in the instruction and the condition code. If the result is non-zero, which means at least one of the conditions being tested is on, then the branch is taken. Otherwise the next instruction is executed. The second field defines the branch address (depending on the class of the instruction). This address is interpreted according to the value of bit 15 of COND. BTC M,A(X) Branch on True Condition branch address =  $\left| \frac{\text{if } X = 0 \text{ then } A \text{ else } A + (X) \right|$

BTCR M,X Branch on True Condition

branch address = (X)

Programmer's Note: If M = 0, then BTC and BTCR are NOPs.

## Branch on False Condition

A logical "and" of the mask M and the condition code is performed. If the result is zero, which means all conditions being tested are off, then the branch is taken; otherwise the next instruction is executed. The second field defines the branch address. This address is interpreted as being in the procedure stream if bit 15 of COND is on; otherwise it is interpreted as being in core.

BFC M,A(X) Branch on False Condition branch address =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right|$

BFCR M,X Branch on False Condition

branch address = (X)

Programmer's Note: If M = 0, then BFC and BFCR are unconditional branches.

# Branch and Link

First the current instruction counter, which is a 16-bit pointer in core or within the procedure stream, depending on  $COND_{15}$ , is saved in R:

(R)  $\leftarrow$  current instruction counter.

Then the branch is taken to the branch address defined by the second field. The branch address is interpreted according to the value of bit 15 of COND.

BAL R,A(X) Branch and Link branch address =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right|$

BALR R,X Branch and Link from Register

branch address = (X)

Branch on Index High

Prior to the execution of this instruction:

(R) = 16-bit count (R + 1) = 16-bit increment (R + 2) = 16-bit limit.

First of all

$(R) \leftarrow (R) + (R + 1).$

Then (R) is compared with (R + 2). If  $(R) \le (R + 2)$ , the program continues in sequence. If (R) > (R + 2), then the branch is taken to the branch address specified by the second field. The branch address is interpreted according to the value of bit 15 of COND.

BXHR,A(X)Branch on Index Highbranch address =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right|$

BXHR R,X Branch on Index High

branch address = (X)

# Branch on Index Low or Equal

Prior to the execution of this instruction:

(R) = 16-bit count (R + 1) = 16-bit increment (R + 2) = 16-bit limit.

First of all

$(R) \leftarrow (R) + (R + 1).$

Then (R) is compared with (R + 2). If (R) > (R + 2), the program continues in sequence. Otherwise, if  $(R) \leq (R + 2)$ , the branch is taken to the branch address specified by the second field. The branch address is interpreted according to the value of bit 15 of COND.

BXLE R,A(X) Branch on Index Low or Equal branch address =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right|$

BXLR R,X Branch on Index Low or Equal

branch address = (X)

CALL AND RETURN INSTRUCTIONS

Call Procedure

CALL A(X)

CALL is the instruction which passes control from the present procedure to a new one. The name of the new procedure is given by the second field:

Name =  $\left| \underline{if} X = 0 \underline{then} A \underline{else} A + (X) \right|$ .

49

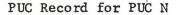

CALL has two primary tasks to perform: it must save a snapshot of the present environment in the control stack, and then it must start the new procedure. This snapshot is called the activation record:

|              |                         |           | control   | stack  |  |  |  |  |

|--------------|-------------------------|-----------|-----------|--------|--|--|--|--|

|              |                         |           | ← pointer | before |  |  |  |  |

| (JS:         | (JSTRNM)                |           |           |        |  |  |  |  |

| ()           | (SR1)                   |           |           |        |  |  |  |  |

| old instruct | old instruction counter |           |           |        |  |  |  |  |

| (1           | (R1)                    |           |           |        |  |  |  |  |

| (1           | R9)                     |           |           |        |  |  |  |  |

| unused       | job                     | condition | ]         |        |  |  |  |  |

|              | number                  | code      |           |        |  |  |  |  |

| condition    | condi                   | tion      | +control  | s ack  |  |  |  |  |

| information  | nformation mask         |           |           |        |  |  |  |  |

| 0 7          | 8                       | 15        | CALL      |        |  |  |  |  |

## Activation Record

The contents of JSTRNM, SR1, R1 and R9 are picked up from the job area. The old instruction counter is the stream address of the instruction after the CALL. The job number and condition code are taken from the micro-registers.

The condition information given depends on whether the CALL being executed is a condition instruction. If not,

condition information =  $|| MASK * 2 | \land FF | \lor 1.$