#### CODING

# for the

# MIT-IBM 704 COMPUTER

# F. Helwig, editor

# Prepared at the MIT Computation Center

#### by

| D. Arden   | J. McCarthy |

|------------|-------------|

| S. Best    | A. Siegel   |

| F. Corbato | F. Verzuh   |

| F. Helwig  | M. Watkins  |

|            |             |

# M. Weinstein

# The Technology Press Massachusetts Institute of Technology Cambridge 39, Mass.

Copyright © 1957 Massachusetts Institute of Technology

# TABLE OF CONTENTS

Preface

Errata

Introduction

I An Introduction to the 704

II Floating-Point Arithmetic in the 704

III The Control Instructions

IV Indexing: Counting and Address Modification

V The SHARE Assembly Program

VI The MIT Post-Mortem Program

VII Subroutines

VIII Fixed-Point Arithmetic in the 704

IX The Shifting Instructions

X The Logical Instructions

XI Input and Output

XII Overflow, Underflow, and Miscellaneous Topics

# Appendixes

- A Description of the SHARE Assembly Program for the IBM 704 Computer

- B A User's Abstract of the Post-Mortem Program

- C The IBM-704 Instructions

- D Revised and Updated Index of Available SHARE 704 Subroutines

#### PRFFACE

This is a new and slightly revised edition of a set of notes prepared by staff members of the M.I.T. Computation Center specifically to serve as a basis for a two-week course in coding for the IBM 704 given at the M.I.T. Computation Center during August, 1957. The notes are a drastic revision of a similar set of notes prepared by the staff for use during August, 1956. They are being issued in their present (rather unpolished) form as the result of a large demand for such material at the Computation Center.

The notes are written for the novice and do not assume any previous knowledge of digital computers. It is not intended, however, that these notes replace the <u>IBM 704 Manual</u> <u>of Operation</u>. Indeed certain topics, such as input and output, are treated briefly in the notes, and the manual must be referred to for complete descriptions.

Basically our topic is coding, and since there is more to coding than description of a digital computer, we have provided the reader with many illustrative examples of codes. We have also included material describing the operational systems presently available at the M.I.T. 704. This includes a brief description of the SHARE organization; descriptions of the SHARE assembly program, which provides a common language for 704 users; and a description of a post-mortem program written at M.I.T. for SHARE distribution.

A listing of subroutines distributed by the SHARE organization is also included. This list was reasonably complete at the time of publication, but will certainly become incomplete as new subroutines are developed by SHARE members.

In addition, the reader's attention is called to the FORTRAN programming system which is already described in IBM publications. These include the FORTRAN Programmer's Reference <u>Manual</u> and the new FORTRAN Introductory Programmer's Manual, which is to be published shortly.

Frank C. Helwig

17 October, 1957

# ERRATA

| Page / I   | -         | 8,  | line 8: should read "numerical addresses whenever"<br>instead of "numerical adress whenever"                                                                                       |

|------------|-----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| II         | -         | 4,  | line 6: comment should read " $x \rightarrow C(MQ)$ ."<br>line 7: comment should read " $x \rightarrow C(101)$ ."                                                                  |

| II         | -         | 9,  | line 7: comment should read "a/b $\rightarrow$ C(R)."<br>line 10: comment should read "c/d $\rightarrow$ C(MQ)."<br>line 12: comment should read "(a/b) (c/d) $\rightarrow$ C(R)." |

| II         | -         | 10, | line 8: comment should read " $(a_3x+a_2)x + a_1 \rightarrow C(R)$ ."                                                                                                              |

| II         | -         | 11, | line 1: replace "DVP" by "FDP."<br>line 3 from bottom: replace "DVP C" by "FDP C."                                                                                                 |

| IV         | -         | 12, | line 9: replace "-8190" by "-8191."<br>line 10: replace "-8191" by "8192."                                                                                                         |

| v          | -         | 4,  | line 14: insert the following sentence: "Columns 8 to 10 make<br>up the operation field."                                                                                          |

| v          | -         | 5,  | line 9 from bottom: replace "assmelby" by "assembly."                                                                                                                              |

| v          | . <b></b> | 8,  | line 6 from bottom: there should be no blanks after the commas, so that it should read:<br>B DEC 23178195, -251 + 251, 48                                                          |

| V          | -         | 13, | line 9: delete the word "he."<br>line 15: replace "one" by "once."                                                                                                                 |

| VI         | -         | 3,  | line 10: replace "location" by "variable."                                                                                                                                         |

| VIII       | -         | 5,  | line 8 from bottom: replace "if" by "it."                                                                                                                                          |

| X          | _         | 7,  | line 16: comment should read "C(NUM)/C(DENOM) $\rightarrow$ C(MQ)."                                                                                                                |

| XII        | -         | 7,  | line 12: should read "AMTST TQO* +1" instead of<br>"AMTST TQO +1."                                                                                                                 |

| XII        | -         | 10, | last line: should read "reenter the trapping mode again after<br>the transfer." instead of "reenter the trapping mode."                                                            |

| Appendix I | 3         | Pag | e 1, line 4 from bottom: replace "is" by "and is."                                                                                                                                 |

11

#### ERRATA (Continued)

Appendix C

Page 2, line 9: The following instruction should be inserted as a new line between "Store Logical Word" (line 9) and "Store Left-Half MQ"

| Instructio         | $\underline{S}tore \underline{Z}ero$ |               |

|--------------------|--------------------------------------|---------------|

| Mnemoni            | S TZ α, β                            |               |

| Octal Val          | +0600                                |               |

| AC                 | :                                    | A' = A        |

| MQ                 | :                                    | M' = M        |

| $\mathbf{IR}\beta$ | :                                    | $I_i = I$     |

| R                  | :                                    | $\omega' = O$ |

|                    |                                      |               |

(no comments)

Page 3, 7th entry in column headed "mnemonic code" should be "CAD $\alpha$ ,  $\beta$ " instead of "CPA  $\alpha$ ,  $\beta$ "

> 14th entry in column headed "Octal Value" should be +0761 instead of -0761

Page 3, line 18 from bottom: octal value for REW i should read "+0772...200+i."

Page 3, line 17 from bottom: octal value for WEF i should read "+0770...200+i."

Page 3, line 16 from bottom: octal value for BST i should read "+0764...200+i."

Page 4, line 3 from bottom:

The following instruction should be inserted between "Leave Trapping Mode" and "Redundancy Tape Test"

Instruction: End of Tape Test

Mnemonic Code: ETT

Octal Value: -0760...011

Comments: L<sup>1</sup> = L+2 if tape indicator is off, tape must still be selected.

#### INTRODUCTION

The MIT Computation Center, which was established in July, 1956, is an interdepartmental activity located in the new Karl T. Compton Laboratory (Building 26). The principal objective of the Center is to increase the number of students, staff members, and scientists qualified to use modern computing machines to further their research efforts.

The Computation Center is an activity which has many assets: qualified staff, modern computing equipment, and a brand new physical plant. The participating personnel in the Center program are located at MIT, IBM, or one of the participating New England Colleges or Universities. Specifically, the Center represents a cooperative activity involving MIT, the IBM Corporation and, at present, 25 New England Colleges and Universities.

# Participating Colleges

The following New England Colleges and Universities -in addition to MIT -- are currently participating in this program:

> Amherst College Bates College Bennington College Boston College Boston University Bowdoin College Brandeis University Brown University Connecticut, University of Dartmouth College Harvard University Maine, University of Massachusetts, University of Middlebury College Mount Holyoke College New Hampshire, University of

# Participating Colleges (Continued)

Northeastern University Rhode Island, University of Tufts University Vermont, University of Wellesley College Wesleyan College Williams College Worcester Polytechnic Institute Yale University

An active participating by the staffs of the New England Colleges in the Computation Center program was initiated by the appointment of 24 Research Assistants and Associates at these institutions during the academic year 1956-1957. These appointees provide active liaison between the staff at the Center and the students and staff at their individual institutions. Appointments of this type will be made each year -- to insure a widespread and dynamic participating program.

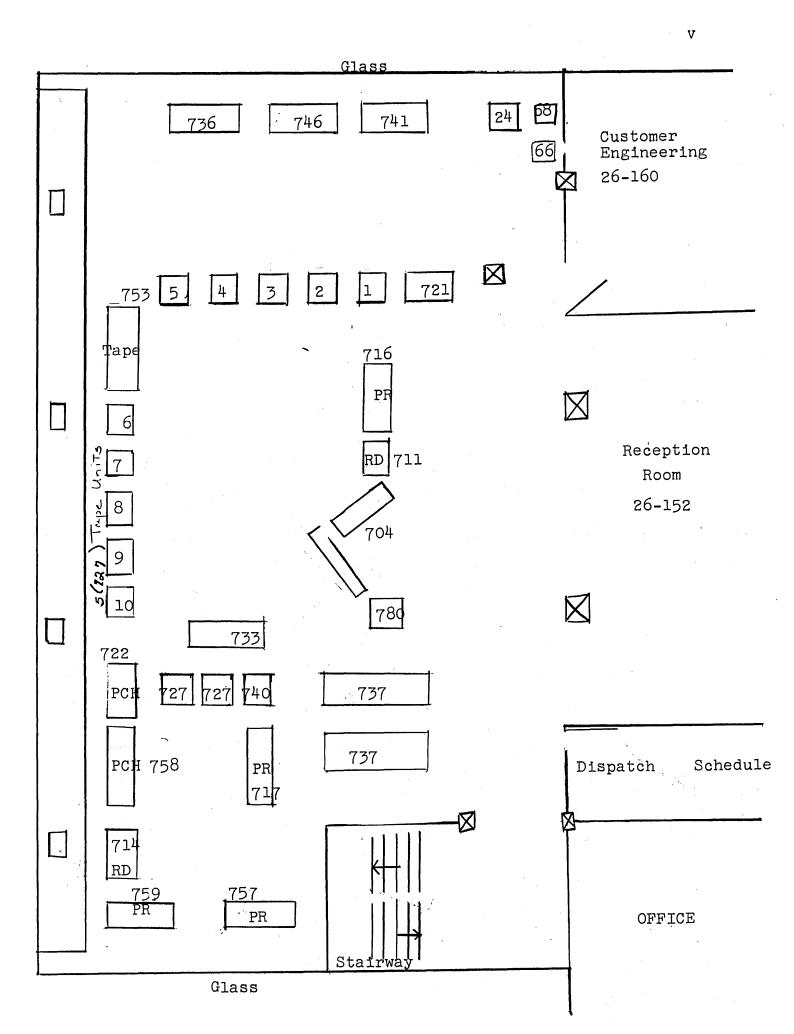

# Physical Plant

The physical plant of the MIT Computation Center consists of 18,000 square feet located in the recentlyerected Karl T. Compton Laboratory. Specifically, the Center occupies <u>part</u> of the basement, the entire first floor, and <u>part</u> of the second floor of the Compton Laboratory. In addition, a two-story annex is used to house the IBM Type 704 Electronic Data Processing Machine (EDPM) and the associated Electric Accounting Machine (EAM) equipment.

The first floor contains adequate space for the headquarters staff, the operations staff (analysts, programmers, machine operators, etc.), IBM Institutional Representatives, New England University Research Assistants and Associates, MIT Research Assistants and Associates, classroom and seminar room, as well as the 704 computer. The basement provides space for the EAM machines, the systems research laboratory, dark room facilities, the electrical power plant, and the air conditioning equipment. The second - floor provides space for the programming research staff, the visiting professors, and the library and document room.

All this area has been furnished in a first-class manner to facilitate the progress of research at the Center.

# The 704 Computer and Associated Equipment

The computational facilities in the Center are supported in large measure by the IBM Corporation. Specifically, IBM is providing the 704 computer, the associated EAM equipment, and the associated maintenance personnel on a gratis basis. The following machine complement is available in the Center:

| Quantity | Туре | Description                        |

|----------|------|------------------------------------|

| l        | 704  | Analytical Control Unit            |

| 1        | 711  | Punched Card Reader                |

| l        | 716  | Alphabetic Printer                 |

| l        | 721  | Punched Card Recorder              |

| l        | 733  | Magnetic Drum Unit (8192 words)    |

| 1        | 736  | Power Frame No. 1                  |

| 2        | 737  | Magnetic Core Storage (8192 words) |

| 1        | 740  | CRT Output Recorder                |

| l        | 741  | Power Frame No. 2                  |

| 1        | 746  | Power Distribution Unit            |

| l        | 753  | Magnetic Tape Control Unit         |

| 10       | 727  | Magnetic Tape Units                |

| l        | 780  | CRT Display Unit                   |

|          |      |                                    |

# MACHINE COMPLEMENT IN THE MIT COMPUTATION CENTER

# Off-Line Equipment

ŧ

**t**,

• 1

e

| Quantity | Туре      | Description                          |

|----------|-----------|--------------------------------------|

| 1        | 714       | Card Reader                          |

| 1        | 717       | Alphabetic Printer                   |

| 1        | 722       | Card Punch                           |

| 2        | 727       | Magnetic Tape Units                  |

| l        | 757       | Printer Control Unit                 |

| 1        | 758       | Punch Control Unit                   |

| 1        | 759       | Card Reader Control Unit             |

|          |           |                                      |

|          | Auxiliary | Machines                             |

| 1        | 024       | Key Punch                            |

| 5        | 026       | Key Punches                          |

| 3        | 056       | Verifiers                            |

| 1        | 066       | Printing Card Unit )Data Transceiver |

| 1        | 068       | Telephone Signal Unit)and Receiver   |

| 1        | 077       | Collator                             |

| 1        | 082       | Sorter                               |

| l        | 407       | Accounting Machine                   |

| 1        | 519       | Reproducer                           |

| 1        | 552       | Interpreter                          |

The actual location of the machines in the 704 Room is shown on the attached physical layout sheet.

# Additional Description of 704 Components

The Type 66-68 IBM Transceiver equipment will permit remote programming for the Type 704 computer. Specifically, the Type 66 Printing Card Unit will receive approximately 14 card columns of information per second over <u>telephone</u> lines. The received information is simultaneously <u>printed</u> along the top of the card while it is being <u>punched</u> into the same card. At this transmission speed an average of ten (10) fully-punched 8-column cards may be received each minute -- more if fewer than 30 columns are punched in each card.

Four independent transmissions can be made simultaneously over the same telephone wires, provided each independent transmitter has its own transceiver at each end of the line. Simultaneous transmission is accomplished by use of the following four channel frequencies: 800, 1300, 1800, and 2300 cycles per second.

Initially, the MIT Computation Center will use only one transceiver operating at 1300 cycles per second on a 4-wire signal unit. The initial telephone circuit will connect the 704 Computer installation at Poughkeepsie, New York to the Center in Cambridge, Massachusetts.

#### Use of Dual-Purpose Equipment

There are only 12 magnetic tape units at the Center and ten (10) of these are directly connected to the main frame and are available to the programmer. Since there are three (3) additional sets of peripheral or off-line equipment, namely:

- 1. Magnetic tape-to-punched card converter,

- 2. Magnetic tape-to-printer converter,

- 3. Punched card-to-magnetic tape converter,

there is need for dual use of one of the magnetic tape units.

Accordingly, the physical layout of the equipment and cables has been designed to permit use of tape unit <u>No. 10</u> on a dual basis, either as on-line tape unit No. 10, or as an off-line unit with the off-line card punch Type 722. (The change from on-line to off-line usage is effected by manually changing the signal cable connector on tape unit No. 10.)

#### Personnel at the Center

The personnel of the Computation Center may be roughly classified into the following groups:

- 1. Administrative and Supervisory Staff,

- 2. Members of the Teaching Staff,

- 3. Members of the Operations Unit,

- 4. Members of the Programming Research Unit,

- 5. Members of the IBM Research and Associate Program.

The core of the above groups was obtained by selecting key individuals from the staff of the Office of Statistical Services and the staff of the Scientific and Engineering Calculation Group at the Digital Computer Laboratory.

The composition of the IBM Research Assistant and Associate program will naturally vary from time to time, since these appointments are made on an annual basis. Some of these appointments are renewed for a second year; however, the principal purpose of the appointment -- that of indoctrination in computer application and programming -- is accomplished the first year. At the end of the first year, these men are well-qualified to transmit their knowledge to other students and staff at their respective universities.

### CHAPTER I

#### AN INTRODUCTION TO THE 704

The modern computer is really a large, but elementary device -- at least in principle. An understanding of a computer is perhaps best given by listing the major components of a particular computer, the IBM 704, and then describing how these components interact with each other. Briefly, these components are:

- A large, fast-access memory or information storage device

- 2. An arithmetic element

- 3. An electronic control element

- 4. Input and output equipment

- 5. Auxiliary memory devices to supplement items 1 and 4.

The first item, a large memory unit, is a device capable of storing (although not necessarily all at once) all the information required to perform a computation. This information is stored in convenient units by <u>words</u>. Thus in the IBM 704 computer at MIT there is an 8192 word high-speed magnetic core memory. Although it need not unduly concern the user <u>at present</u>, each word consists of 36 binary digits (<u>bits</u>), each bit capable of having a value of one or zero. Finally each of the one-word storage locations in the memory unit, (often called a <u>register</u> or cell), has an arbitrary numerical <u>address</u> from 0 to 8191 which is permanently wired into the machine. In effect then the memory unit of the computer is a collection of labelled pigeon holes which will hold all the numerical values of a problem before, during, and after computation.

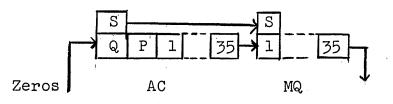

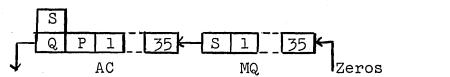

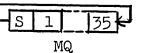

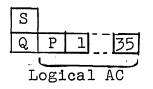

The second item, the Arithmetic Element, consists of several special registers: the Accumulator Register (AC) the Multiplier-Quotient Register (MQ) and a Storage Register (SR). Each of these registers can contain one word and will respond to signals from the Control Element, described shortly. Usually the SR will contain a word which is to be combined in some definite manner with a word in the AC or the MQ according to signals sent from the Control Element. For example the simple addition of two numbers, one in the AC and the other in the SR, will result in the sum being left in the AC.

The third item, the Control Element, is analogous to a "central nervous system" in the computer. An important part of this system is two registers: the Instruction Location Counter (ILC) and the Instruction Register (IR). Having established in this way the more important terms, it is now possible to clarify their meaning by considering the process of computer operation. The most basic operation consists, in general, of information being brought from memory to the arithmetic unit, processed by

means of a standard operation and the resultant information perhaps being stored in the memory; to accomplish this operation an <u>instruction</u> (i.e. a number code for the process desired) is given to the Control Element which then selects from the memory the specified information and places it in the SR, impulses the Arithmetic Element to perform the operation and then stores the result whenever the instruction so specifies.

Now clearly if instructions were to be given to the Control Element by a human machine operator, the execution of a sequence of instructions could be no faster than the human operator. A possible solution would be to prepare the sequence of instructions in a loop of perforated coded paper tape, but this too would be limited by the speed of mechanical rotation and reading of the tape; (some of the earlier computers did just this). An ingenious solution to this problem is to place the sequence of number-coded instructions in the memory unit of the computer itself, for then the execution of the instructions is only limited by the speed of the electronic circuitry and suffers from neither mechanical nor human This latter concept, often called that of intervention. the stored-program, is one of the important distinctions of the modern high-speed digital computer. A second distinction and a very important feature of a stored program computer is that since both the instructions and

data are stored in the same memory unit, it is quite possible for sequences of instructions to actually modify themselves. The ramifications of this second distinction will be explored in later chapters.

Let us consider as an example the execution of an elementary sequence of instructions arbitrarily located in memory locations 127, 128, etc.

| Location | Operation | Address<br>(of word | to be | e operated on) |

|----------|-----------|---------------------|-------|----------------|

| 127      | CLA       | 199                 |       |                |

| 128      | ADD       | 198                 |       |                |

| 129      | STO       | 200                 |       |                |

| 130      | TRA       | 353                 |       |                |

|          | • • • •   |                     |       |                |

| 198      | (Contains | value of            | x)    |                |

| 199      | (Contains | value of            | у)    |                |

| 200      | (Contains | value of            | sum)  |                |

As implied here, the 704 computer is a singleaddress computer so that each instruction consists of an operation, (usually abbreviated by 3 letters) and an address referring to one word in the memory. (Many other computers for reasons of design efficiency use multiaddress instructions). A second implication in the example shown is that the Control Element performs the instructions in the sequence of their location in memory. There are a few instructions, which cause exceptions to this rule, but these discrepancies are considered part of the instruction definition. In fact these exceptional instructions which cause jumps in the instruction execution sequence will be seen in later chapters to play a vital role in the decision and repetition capabilities of the computer.

Returning to the example given, the computer operation now will be traced to ensure that the basic concepts are established. The assumption made is that the Control Element is manually started with the Instruction Location Counter (ILC) preset to the value 127. The first step the Control Element performs is to copy the instruction in memory location 127 into the instruction register (IR). Examination by the Control Element of the address section of the IR reveals that the word located at address 199 is to be operated on so this word is copied into the Storage Register (SR). Next the Control Element carries out the operation indicated by that section of the instruction in the IR. In the particular example here, CLA means "clear and add (to the AC)" so the effect of the operation is to copy the contents of the SR into the AC. The final step performed by the Control Element is to increase the ILC by one (to 128 in this case), and then repeat the pattern described by placing the instruction located in 128 in the IR, placing the word stored at location 198 in the SR and so It should be clear from this description that the forth. computer can operate at high speeds in a fully automatic

fashion. It should also be clear that all sequences of instructions were pre-arranged inside the computer. The practical use of a computer hinges on this latter accomplishment which is called programming if it involves the totality of computer operation or coding if it concerns only the sequences of instructions.

Having completed the basic operating description of a computer it is now possible to finish discussing the major computer components. The fourth item listed previously, input-and-output equipment, serves to transmit information to-and-from the outside world and the memory unit. Thus for input devices on the 704 computer there are a card-reader or magnetic tape units. Similarly for output equipment there is a printer, a card punch, magnetic tape units and a photographing oscilloscope. It is an important feature that all the input and output devices can be actuated and controlled whenever special instructions are executed in the computer; thus the devices are said to be under "program control."

The auxiliary storage devices mentioned previously as item five are of two types. The first is the use of magnetic tape also as a supplement to the storage capacity of the memory unit. The second device is a rotating magnetic drum. The drum units on the MIT 704 offer another 8192 words of storage, any word of which may be brought into the main core memory unit in a time bounded by that

of one drum rotation. Thus for some purposes the drum as a storage device is inferior to core memory but superior to magnetic tape where the time required to bring a word into core memory depends on the position of the word on the tape.

This concludes the broad brush-stroke description of a computer. The remaining chapters will discuss various aspects of the essential details. As a general introduction, though, a quick survey will be made of some of the conventions involving computer words.

It was already noted earlier that there were two broad categories of words used in the 704. These were instructions and data words, each composed of 36 binary bits and indistinguishable except by usage. However there are several convenient word usage conventions which are strongly favored by the instruction codes available on the 704. Thus the binary bits of an instruction are divided into standard sections. In most of the instructions, the first 18 bits give the operation code, the next 3 bits the tag value (the use of this is described under the chapter on indexing), and the last 15 bits give the address section of the word that the instruction refers In a few instructions the first 18 bits of the to. operation section are further divided into a 3 bit prefix and a 15 bit decrement section, again described in the chapter on indexing.

No attempt has been made to describe in any detail the binary nature of the computer because in practice there are standard "translation" procedures always available. Hence when a person writes down CLA as an instruction, this when read into the computer is translated into an 18 bit operation code. An additional and similar convenience is to be able to avoid the use of numerical address whenever writing down sequences of instructions. This is done by using what are known as <u>symbolic locations</u> or more generally <u>symbols</u>. These are merely arbitrary 5-character (or less) names for specific locations or addresses. Thus the previous example of coding might have been written as:

| Location | Instruction | Address       |

|----------|-------------|---------------|

| START    | CLA         | Y             |

|          | ADD         | X             |

|          | STO         | ARG           |

|          | TRA         | NEXT          |

|          | 0000        |               |

| x        | (Contains   | value of x)   |

| Y        | (Contains   | value of y)   |

| ARG      | (Contains   | value of sum) |

It is important to realize that this algebra-like convenience produces exactly the same numerical values for instructions and locations inside the computer as the previous numerical example; all that has changed is the convention for describing these instructions and locations.

ens (C)

The other major category of words used in the 704 is that of words used to represent arithmetic quantites. There are two major types, those for fixed-point numbers and those for floating-point numbers. Again it should be emphasized that these conventions are only useful because there are explicit 704 instructions which manipulate words according to these conventions. In fixed-point words, the first bit is used to describe the sign (0 is positive, 1 is negative) and the remaining 35 bits give the <u>magnitude</u> of the significant figures. Inasmuch as the binary point is not a tangible thing inside the computer, a fixedpoint number can either be an integer or a fraction depending on whether one interprets the binary point as being at the left-hand end or the right-hand end of the magnitude.

In a similar way, floating-point numbers, that is, numbers which are represented by a fraction multiplied by 2 raised to a power, are represented in the following way: The first bit is the sign of the fraction, the next 8 bits are the always-positive <u>characteristic</u> (by definition, the exponent plus 128), and the remaining 27 bits are the magnitude of the fraction.

Just as in the instructions, where the convenient abbreviations and symbols are translated whenever instructions are placed in the computer, there are convenient ways of writing fixed-and floating-point numbers in normal

decimal form for the computer. For example, simply writing down the pseudo-instruction DEC -5, will translate (because there is no decimal point) into the computer as the fixed-point integer minus five. Similarly DEC -5, translates (because there is a decimal point) into a floating-point minus five, and DEC -.5B translates (because there is a B) into the fixed-point fraction minus one-half. Further discussion of this translation process (often misleadingly called <u>assembly</u>) and the translation syntax or rules are given in the chapter describing the SHARE Assembly Program.

The foregoing chapter briefly describes the basic word structure used in the 704 computer. For clarification of details and definitions the IBM 704 manual will be found useful as a reference. In particular binary arithmetic and conversion are described in an Appendix.

#### CHAPTER II

### FLOATING POINT ARITHMETIC IN THE 704

In this chapter we will show how the 704 can be made to evaluate simple numerical expressions, as for example (a + b)c.

### Some Conventions

The reader already knows that in order to have the computer do any computations a program must be written in terms of the elementary <u>instructions</u> which the machine can obey. When we write programs down on paper, we represent the instructions by three letter abbreviations which are derived from the name of the instruction. <u>Clear and add</u> is represented by the abbreviation CLA. Such abbreviations we call <u>operation codes</u>. In general, the instruction will have an address. Usually the address determines which storage location the instruction refers to, and accordingly it may be the integer number of that storage location. For example: CLA 100 refers to storage location 100.

We will more often want to write some symbol instead of an integer with the understanding that the symbol represents an integer. For example:

### CLA A

where A stands for a permissible integer.

Furthermore it is often convenient to write

comments on the same line with the instruction to explain its purpose or define it, like this:

CLA A This is a 704 instruction

When composing a program, we arrange the instructions in a vertical column and imagine that the computer obeys them in sequence reading down. Thus:

| CLA            | А                  | First this one |

|----------------|--------------------|----------------|

| STO            | В                  | then this one  |

| CLA            | С                  | then this one  |

| STO            | D                  | etc.           |

| S. S. S. S. S. | $e^{-i\omega_{1}}$ |                |

#### Conventions Used in Comments and Definitions

The two most important registers in the arithmeticelement, the accumulator and the multiplier-quotient registers, we will abbreviate by (AC) and (MQ) respectively.

Often we will want to talk about the contents of a certain storage location. We will write

#### C(100)

for "the contents of storage location 100," and

C(A), C(AC)

for "the contents of storage location A" and "the contents of the accumulator" respectively. Also we will use the symbol "->" to mean "replaces." Thus

$C(A) \longrightarrow C(AC)$

will mean "the contents of storage location A replaces the contents of the accumulator."

#### Now we are ready to begin.

# The Administrative Instructions

First we will consider some instructions, which do no computing, but are very important. They are used to transmit words between storage and arithmetic element. We call them administrative instructions. They are:

#### Definition

| 1. | <u>Clear</u> and <u>Add</u> |                              |

|----|-----------------------------|------------------------------|

|    | CLA A                       | $C(A) \longrightarrow C(AC)$ |

| 2. | Load MQ                     |                              |

|    | LDQ A                       | $C(A) \rightarrow C(MQ)$     |

| 3. | Store                       |                              |

|    | STO A                       | C(AC)→C(A)                   |

| 4. | Store MQ                    |                              |

|    | STQ A                       | $C(MQ) \rightarrow C(A)$     |

Some Simple Examples of Programs

We will write the following computer instruction at the end of sample programs which we exhibit:

# 5. Halt and Proceed

HPR

causes computer to halt; it will proceed to the next instruction if then started manually.

Example I: If C(100) = x, then either of the following programs may be used to place x in location 101.

|    |       |         | -                          |

|----|-------|---------|----------------------------|

|    | OPER. | Address | Comments                   |

|    | CLA   | 100     | $x \rightarrow C(AC)$      |

|    | STO   | 101     | x →C(101)                  |

|    | HPR   |         | HALT                       |

| or |       |         |                            |

|    | LDQ   | 100     | $x \longrightarrow C(MQ)$  |

|    | STQ   | 101     | $x \longrightarrow C(101)$ |

|    | HPR   |         | HALT                       |

|    | •     |         |                            |

In both cases C(100) remains <u>undisturbed</u> so that x ends up in both locations 100 and 101.

Example II: Suppose it is desired to exchange C(A) and C(B), Let:

C(A) = x; C(B) = y

| 1 | LDQ<br>CLA | А | $x \longrightarrow C(MQ)$           |

|---|------------|---|-------------------------------------|

|   | CLA        | В | y>C(AC)                             |

|   | STO        | А | у —— С(А)                           |

|   | STQ        | В | х — С(В)                            |

|   | HPR        |   | halt, x and y are inter-<br>changed |

Next, we shall consider how the administrative instructions can be combined with <u>arithmetic</u> instructions to do simple calculations; but first we will briefly discuss a kind of number that the 704 is designed to deal with.

# Floating Point Numbers

In many of the computational problems that arise in the sciences and engineering one encounters numbers that vary greatly in magnitude. To save writing and to save paper such numbers are usually written, for example, in this way:

5.213 x  $10^{-6}$  , 3.213 x  $10^{10}$  rather than in the equivalent forms:

.000005213 , 32130000000.

The first way of writing these numbers is an example of what we shall call <u>floating point notation</u>. As a convenience for doing calculations where the magnitudes of the numbers do vary widely, the 704 has instructions which do arithmetic with numbers of a similar form. We call numbers of this kind <u>floating</u> <u>point numbers</u>. Since the 704 is a binary machine, these numbers are of the form

$$N = x \cdot 2^{1}$$

(rather than  $x \cdot 10^{1}$ ). The integer i is called the exponent and is restricted to lie in the range

# -128≤i≤ + 127

and x is called the <u>fraction</u> and is restricted to lie in the range

# -14x<1.

If x also satisfies either of the two conditions

$\frac{1}{2} \le |x| < 1 \qquad \text{or} \qquad x = 0$ then we say that  $N = x \cdot 2^{1}$  is a <u>normalized floating</u> point number. In what follows, we shall assume that all floating point numbers are normalized unless a specific statement to the contrary is made.

The fraction, x, is not a continuous variable but can assume only integral multiples of the number  $2^{-27}$ . This fact we usually express by saying that x (and therefore N) has a <u>precision</u> of 27 binary digits. This is a precision slightly greater than 8 decimal digits.

# How Floating Point Numbers are Written When Programming

When we are writing a program, we may write floating point numbers in ordinary decimal notation since there is an assembly program which can translate this notation into the internal binary floating point numbers of the 704.

To be specific, if we wanted to have the number  $.51 \times 10^{+2}$  stored as a floating point number, we would write on our coding sheet:

# DEC 51.

(The decimal point is essential because we wish to reserve the notation

# DEC 51

to mean something quite different). However, we may also write:

DEC .51E+2 notice E+2 means 10<sup>2</sup>

Now it may be helpful to restate two properties of the 704's floating point numbers in decimal notation.

1. The absolute value of a floating point number must either be 0 or must lie between the approximate limits  $(10^{-38}, 10^{+38})$ .

2. The maximum precision of a floating point number is slightly more than 8 decimal digits.

Thus we see from (1) that the number 5.0 x  $10^{-41}$  cannot be stored as a floating point number because its magnitude is too small; and from (2) we see that it would be silly to write

DEC -1.234567890123E+2

because nothing beyond the 9th significant digit could possibly affect the stored result.

#### The Floating Arithmetic Instructions

We are now ready to introduce the four basic floating arithmetic instructions. In every case, if the operands are normalized floating point numbers, the results will be also

| 1. | Floating Add      |                                  |

|----|-------------------|----------------------------------|

|    | FAD B             | $C(AC) + C(B) \rightarrow C(AC)$ |

| 2. | Floating Subtract |                                  |

|    | FSB B             | $C(AC) - C(B) \rightarrow C(AC)$ |

\* The 704 also has some floating-point instructions which do not produce normalized results. In practice these instructions (UFA,UFS, and UFM) are used only rarely and in rather tricky and obscure ways. The interested reader may consult the <u>IBM 704 Manual</u> under the topic of "Fixing a Floating-Point Number." We advise him to first study the 704 fixed point instructions, however. FMP B C(MQ)★C(B) → C(AC)

4. <u>Floating Divide or Proceed</u>

FDP B if  $C(B) \neq 0$ ;  $C(AC)/C(B) \longrightarrow C(MQ)$

The instructions FAD, FSB, and FMP do not leave the MQ undisturbed. In fact, these instructions leave a value in the MQ such that the number

C(AC) + C(MQ)

is a better approximation to the true result than C(AC) is. In "single precision" work, however, the C(MQ) is ignored.

The instruction FDP leaves the <u>remainder</u> in the AC. This is also usually ignored.

Examples of Programs Using the Floating Arithmetic Instructions Example III: If

$\dot{C}(A) = a \text{ and } C(B) = b$

then the following program computes

<u>3a -2b</u>

and stores the result in location C:

$$\begin{array}{c|c} CLA & A \\ FAD & A \\ FAD & A \\ FSB & B \\ FSB & B \\ FSB & B \\ STO & C \\ HPR \\ \end{array}$$

Example IV: If locations A,B,C, and D contain the numbers a,b,c, and d respectively, then the following program computes

and stores it in location R:

$\begin{array}{c|c} CLA & A \\ FDP & B \\ STQ & R \end{array} & a/b \longrightarrow C(R) \\ STQ & R \\ \hline \\ CLA & C \\ FDP & D \\ \hline \\ CLA & C \\ FDP & D \\ \hline \\ STO & R \\ \hline \\ STO & R \\ \hline \\ R \\ \hline \\ (a/b)(c/d) \longrightarrow C(R) \\ \hline \\ HPR \\ \hline \end{array}$

The following equivalent program requiring fewer instructions can also be used:

$$\begin{array}{c|c} CLA & A \\ FDP & B \end{array} & a/b \longrightarrow C(MQ) \\ FMP & C & (a/b)c \longrightarrow C(AC) \\ FDP & D \\ STQ & R \end{array} & ((a/b)c)/d \longrightarrow C(R) \\ HPR & \end{array}$$

Example V:

Suppose that

$$C(A3) = a_3$$

$$C(A2) = a_2$$

$$C(A1) = a_1$$

$$C(A0) = a_0$$

$$C(X) = x$$

then the following program evaluates the polynomial

$a_3x^3 + a_2x^2 + a_1x + a_0 = ((a_3x + a_2)x + a_1)x + a_0$

and stores it in location R:

| LDQ | A3 |                                                     |

|-----|----|-----------------------------------------------------|

| FMP | Х  |                                                     |

| FAD | A2 |                                                     |

| STO | R  | $a_3 x + a_2 \longrightarrow C(R)$                  |

| LDQ | R  |                                                     |

| FMP | Х  |                                                     |

| FAD | Al | $(a_3x + a_2) x + a_1 \longrightarrow C(R)$         |

| STO | R  |                                                     |

| LDQ | R  |                                                     |

| FMP | Х  | $((a_3x + a_2)x + a_1)x + a_0 \longrightarrow C(R)$ |

| FAD | AO |                                                     |

| STO | R  |                                                     |

| HPR |    |                                                     |

Underflow, Overflow, and Division by Zero

If during the course of a floating point calculation an attempt is made to compute a result whose magnitude is too large or too small i.e. lies outside the approximate range

$(10^{-38}, 10^{+38})$ ,

then a very wrong answer will result!

In this chapter, we have been and will continue to ignore this complication. We only remark that there are two lights on the 704 console, the <u>AC Overflow light</u> and the <u>MQ Overflow light</u>, which are turned on by an overflow (or underflow) in the AC or MQ, and that there are 704 instructions which can be used to determine whether these lights are on.

Co. 8

Also, if division by zero is attempted, the DVP instruction turns on the Divide Check Tight and goes on to the next instruction leaving C(AC) unchanged.

We will have more to say about these things later.

## Some Instructions with only One Operand

The arithmetic instructions that we have just been considering each had two operands. That is, they combined two numbers by an arithmetic process to obtain a result. Now we wish to consider a few instructions which have only one operand.

> Clear and Subtract 1.

> > $-C(A) \longrightarrow C(AC)$ CLS А

2. Change Sign CHS

$$-C(AC) \longrightarrow C(AC)$$

3. Set Sign Plus SSP

$+ |C(AC)| \longrightarrow C(AC)$  $- |C(AC)| \longrightarrow C(AC)$ 4. Set Sign Minus SSM

Notice that CHS, SSP, and SSM do not have addresses.

If locations A and C contain the numbers Example: a and c, then the following program computes

-a/c

and stores the result in R

$\begin{array}{c} A & -a \longrightarrow C(AC) \\ C \\ R \end{array}$ STQ HPR . . . . .

FDP

#### CHAPTER III

#### THE CONTROL INSTRUCTIONS

If the 704 could execute only the instructions which we considered in the last chapter, it would not be any more useful than a desk calculator. For if we had only the arithmetic and administrative instructions, there would be no way we could cause the computer to execute the same instructions more than once. Thus for every addition, subtraction, multiplication or division we might wish the computer to perform, we would have to write one or more instructions; and it probably takes more time to write down a 704 instruction than it does to do a multiplication on a desk calculator. In this chapter we will introduce some of the instructions with which we can cause the 704 to profitably execute the same instructions many times and with which we can program the computer to make decisions. We will call them control instructions.

# Normal Sequence in Which the 704 Obeys Instructions

Let us first review briefly some basic facts about the computer. Both the numbers with which it computes and the instructions which it executes are stored in the memory. The instructions are stored one to a storage-location. When the computer has just finished executing an instruction in a certain storage location, say location N, it normally proceeds to next execute the instruction in the next storage location, i.e., location N+1. As a matter of fact, there is a special register in the control mechanism of the 704 which always contains <u>the</u> <u>location of the next instruction to be executed</u>. This register is called the <u>instruction location counter</u>, abbreviated (ILC). Now what we just said about the normal sequence in which instructions are executed can be illustrated by this diagram:

Execute instruction contained in C(ILC)  $C(ILC)+1 \rightarrow C(ILC)$

Normal Sequencing

#### The Control Instructions

Any instruction which can cause the 704 to select some instruction for execution <u>other</u> than the one in the next storage location following the instruction it last executed, that is, any instruction which can change the normal sequence of execution just described, we will call a <u>control instruction</u>. The control instructions are of two types: <u>unconditional</u> control instructions and <u>conditional</u> control instructions

The Transfer Instructions

(1) Transfer

#### TRA A

is an unconditional control instruction. The next instruction the computer will obey after obeying this one is the instruction in location A. That is, the TRA instruction TRA A  $A \rightarrow C(ILC)$

There are several conditional transfer instructions. Each of these has associated with it a condition which, if satisfied, causes the computer to take the next instruction from a specified storage location. If the condition is not satisfied, the computer takes the next instruction from the next storage location in normal sequence.

(2) Transfer on Minus

TMI A

causes the computer to take its next instruction from location A if the contents of the accumulator is negative and otherwise to execute the next instruction in normal sequence. We can summarize this as follows:

> TMI A if (C(AC) negative) then A $\longrightarrow$ C(ILC)

Some other conditional transfer instructions are:

- (3) <u>Transfer on Plus</u> TPL A if ((C(AC)) positive) then  $A \rightarrow C(ILC)$

- (4) <u>Transfer on MQ Plus</u> TQP A if ( C(MQ) positive) then  $A \rightarrow C(ILC)$

- (5) <u>Transfer on Low MQ</u> TLQ A if (C(MQ) < C(AC)) then  $A \rightarrow C(ILC)$

If the C(AC) = 0 or C(MQ) = 0, the behavior of these conditional transfer instructions is indeterminant. For the case where C(AC) = 0, we have the following conditional transfer instructions:

(6) Transfer on Zero

TZE A if (C(AC) = zero) then  $A \rightarrow C(ILC)$

(7) Transfer on No Zero

TNZ A if (  $C(AC) \neq zero$ ) then A  $\rightarrow C(ILC)$ None of the control instructions affect C(AC) or C(MQ).

#### Origin Pseudo-Instructions; Symbolic Locations

Up until now we have not worried about where in memory our little example programs were to be stored. We now adopt the convention that writing the operation code ORG with an integer address, say A, at the top of a program means that that program is to be stored in locations A, A+1, ... For example, if we wrote

| ORG 50 | Put         | this | program | in 50, | etc. |

|--------|-------------|------|---------|--------|------|

| LDQ A  |             |      |         |        |      |

| CLA B  |             |      |         |        |      |

| STO A  | -<br>-<br>- |      |         |        |      |

| STQ B  |             |      |         |        | یر . |

| HPR    |             |      |         |        |      |

\* This arises because there are two representations of zero in the 704, +0 and -0, which have zero magnitude but differ in sign. Either zero may be obtained as a result of arithmetic computations. The usual rule of signs holds for results obtained by multiplication or division, but a zero obtained by addition or subtraction has the same sign as the original contents of the accumulator. The reader should also note that the computer considers +0 to be larger than -0 whenever the question arises. Example 1:

Suppose C(A) = aC(B) = b

then the following program computes

min(a,b)

and stores it in R:

ORG 50

LDQ A

$$a \rightarrow C(R)$$

STQ R

CLA B

TLQ 55

STO R

if b < a then  $b \rightarrow C(R)$

HPR

Notice that our program is dependent upon where it is stored. It obviously wouldn't work if we changed the origin instruction to ORG 100. The trouble is that the TLQ has an absolute integer for an address. Let us instead use a symbol:

```

ORG 50

LDQ A

STQ R

CLA B

TLQ STOP

STO R

STOP HPR ←

```

We call the symbol, STOP, written to left of the HPR a symbolic location, and it serves to indicate that we are letting the symbol, STOP, represent the storage address at which the HPR is stored. With this understanding, our program will work wherever we choose to put it. For example:

ORG 1000

|      | LDQ A    | This | program | will work! |

|------|----------|------|---------|------------|

|      | STQ R    |      |         |            |

|      | CLA B    |      |         |            |

|      | TLQ STOP |      |         |            |

|      | STO R    |      |         |            |

| STOP | HPR      |      |         |            |

| A    |          | here | is a    |            |

| В    |          | here | is b    |            |

|      |          |      |         |            |

here will be min(a,b) R

Here we have indicated that a,b, and the result are to be in the 3 storage locations following the HPR.

## Example 2:

Suppose we desire to compute

|     | +1.0/C(A)             | if C(A) <b>‡</b> 0.0 |

|-----|-----------------------|----------------------|

| and | +1.0x10 <sup>38</sup> | if $C(A) = 0.0$      |

and store the result in ANSWER

| CLA A   | $C(A) \longrightarrow C(AC)$               |

|---------|--------------------------------------------|

| TZE Z   | if $C(AC)=0$ , then $Z \rightarrow C(ILC)$ |

| CLA ONE |                                            |

| FDP A   | $1.0/C(A) \rightarrow C(MQ)$               |

|      | TRA | STOR   |                  |             |                 |          |

|------|-----|--------|------------------|-------------|-----------------|----------|

| Z    | LDQ | LARG   | 10 <sup>38</sup> | <b>~~</b> ( | <b>C (</b> MQ ) | )        |

| STOR | STQ | R      | C ( MQ           | ) ->        | C(R)            | )        |

|      | HPR |        |                  |             |                 |          |

| ONE  | DEC | 1.0    | co               | onst        | cants           | 3        |

| LARG | DEC | 1.0E38 |                  |             |                 |          |

| А    |     |        | here             | is          | the             | argument |

| R    |     |        | here             | is          | the             | result.  |

## The Skipping Type Control Instructions

Some of the conditional control instructions do not transfer control to an arbitrarily specified location under certain conditions, but rather they skip one or more instructions under certain conditions. We will introduce one of them here and others will come up during a discussion of input-output and elsewhere.

## (8) Compare Accumulator with Storage

CAS A if C(AC)> C(A), go to the next instruction

if C(AC) = C(A), skip one instruction<sup>\*</sup> if C(AC) < C(A), skip two instructions

For convenience, we also will introduce this instruction:

(9) No Operation

NOP Do nothing; go to the next instruction The NOP instruction has an address but it is ignored.

Recall the previous footnote concerning +0 and -0.

Example 3:

Let us write another little program to compute min (C(A), C(B))

and put it in R:

В

|   | CLA A  | $C(A) \longrightarrow C(AC)$                    |

|---|--------|-------------------------------------------------|

|   | CAS B  |                                                 |

|   | CLA B  | if $C(B) < C(AC)$ then $C(B) \rightarrow C(AC)$ |

|   | NOP    | they are equal                                  |

|   | STO R  | store the minimum                               |

|   | HPR    |                                                 |

| A | Argume | ents                                            |

R Result

## Other Control Instructions

We shall meet other control instructions in the next chapter on indexing instructions; others will be discussed under miscellaneous topics and one or two may not get discussed at all. For these, consult the 704 Manual.

### CHAPTER IV

#### INDEXING: COUNTING, ADDRESS MODIFICATION

The instructions which we shall consider in this Chapter are called indexing instructions and are extremely useful for coding repetitive computations. They help in two ways: first, they help in address modification, that is, they help in making a sequence of instructions operate on different numbers each time they are executed. Secondly, they help in counting. A typical example of a computation where the indexing instructions are useful would be the formation of the scalar product of two vectors. We will use this as an example later.

### Index Registers

The 704 has three registers in its control element each of which is capable of storing any of the integers 0, 1, 2, ..., S-1 where S is the number of storage locations in the memory, These registers are referred to as <u>index</u> <u>registers</u> 1, 2, and 4; or for short, IR1, IR2, and IR4. Tag; Effective Address

To see how the index registers can help us in address modification, we must consider tagged instructions. Every 704 instruction may be tagged; and by this we mean that it may have appended to it, as a sort of second address, the

\* This number varies from one 704 to another, but is always one of the powers of two:  $2^{12}$ ,  $2^{13}$ ,  $2^{14}$ ,  $2^{15}$ . At present at MIT it is  $2^{13} = 8192$ , but it may be increased later. number of one of the three index registers. The following instruction is an example of an instruction with a tag of 4:

CLA A,4  $C(A-C(IR4)) \rightarrow C(AC)$ The comment shows symbolically what the effect of the tag is. The contents of the index register with which the instruction is tagged is subtracted from the address of the instruction before the instruction is executed. Thus the instruction acts as if it had an address of

$$A - C(IR4)$$

This value we call the <u>effective address</u>. All the instructions that we have considered in the last two chapters and <u>which have addresses</u> behave in the same way. Such instructions are called indexable instructions.

It is now easy to see that if we change the contents of an index register, we at the same time change the effective address of every instruction tagged with that index register. This would then provide us with the promised address modification facility.

#### Decrements

Before we can describe the indexing instructions, it is necessary to explain what a decrement is. Some of the indexing instructions have what amounts to still another address which we write separated from the tag by a comma. For example:

### TXI A,2,100

Here A is the address, 2 is the tag and 100 is the <u>decrement</u>. In the decrement of such an instruction, we can store any integer that could be stored in an address; that is, any of 0,1,2,...; 32767. The decrement is used to change or test the value contained in an index register, and does not normally refer to a storage location.

When we are writing a program, we will often find it necessary to have constants with integer values in the addresses and decrements. For this we use the <u>plus</u> <u>zero</u> operation code. For example:

PZE 1000, 0, 10

represents a 704 word with 1000 in the address and 10 in the decrement.

#### The Administrative Instructions for Index Registers

We have described a group of instructions which we called the administrative instructions and which did nothing more than move numbers in and out of the AC and the MQ. Now we are going to discuss some instructions which move integers in and out of the index registers. We will let K stand for any of 1, 2, or 4.

There are two instructions which move integers from storage locations to index registers:

(1) Load Index from Address

LXA A,K

This instruction loads into index register K the integer found in the address of storage location A. We can symbolize this as follows:

C(address of A) C(IRK)

IV-3

## (2) Load Index from Decrement

LXD A,K C(decrement of A) → C(IRK) There is only one instruction which moves an integer from an index register to a storage location:

IV-4

(3) Store Index in Decrement

SXD A,K C(IRK)→C(decrement of A) Only the decrement of A is disturbed by this instruction: the rest of the word is unchanged.

There is a similar set of three instructions for moving integers between the accumulator and the index registers:

(4) <u>Place Address in Index</u>

PAX O,K  $C(address of AC) \rightarrow C(IRK)$

(5) Place Decrement in Index

PDX 0,K  $C(\text{decrement of AC}) \rightarrow C(\text{IRK})$

(6) <u>Place Index in Decrement</u> PXD O,K Clear the AC; then  $C(IRK) \rightarrow C(decrement of AC)$

This last instruction has the interesting property that if it has no tag (i.e., if K is zero), then it clears the AC; that is:

# PXD +O →C(AC)

In these three "place" instructions the address is ignored.

It may be well to note that the pair of instructions

CLA A  $C(A) \rightarrow C(AC)$ PAX 0,1  $C(address of AC) \rightarrow C(IR1)$  puts the same number into IR1 that this single instruction does:

LXA A,1  $C(address of A) \rightarrow C(IR1)$ Counting With the TIX Instruction

We said that the index registers would be a help in counting. To prove our point, we now introduce the most popular indexing instruction which is used to count. It both changes (subtracts from) the contents of the index register and acts as a conditional transfer. Here it is:

(7) Transfer on Index

TIX A,K,N

The action of this instruction depends upon C(IRK). If C(IRK) > N, then it decrements IRK by N and transfers control to A. Symbolically; if C(IRK) > N, then  $C(IRK) - N \rightarrow C(IRK)$ and  $A \rightarrow C(ILC)$ . However, if  $C(IRK) \leq N$ , it does not change C(IRK) and it does not transfer control; it goes on to the next instruction in sequence without changing anything.

## Example 1:

As an example, suppose we wish to write a program to evaluate the scalar product of two 3-dimensional vectors:  $A \cdot B = A_1B_1+A_2B_2+A_3B_3$ . Suppose  $A_1, A_2, A_3$  are stored in storage locations VECTA, VECTA+1, VECTA+2, and  $B_1$ ,  $B_2$ ,  $B_3$ are stored in VECTB and following locations. Then the following program will compute the scalar product and leave the result in ANSWER:

|                                          | LXA COUNT,1%  | +3 → C(IR1)                           |

|------------------------------------------|---------------|---------------------------------------|

| LOOP                                     | LDQ VECTA+3,1 |                                       |

|                                          | FMP VECTB+3,1 |                                       |

|                                          | FAD ANSWER    |                                       |

|                                          | STO ANSWER    | •                                     |

|                                          | TIX LOOP,1,1  | Count to 3                            |

| A. A | HPR           |                                       |

| COUNT                                    | PZE 3         | a constant                            |

| ANSWER                                   |               | Originally contains O.                |

|                                          |               | • • • • • • • • • • • • • • • • • • • |

| Instructions<br>Executed                                   | -           | IR1           | Effective Address                             |

|------------------------------------------------------------|-------------|---------------|-----------------------------------------------|

| LXA COUNT,1                                                |             | 3             |                                               |

| LDQ VECTA+3,1<br>FMP VECTB+3,1<br>FAD ANSWER<br>STO ANSWER | •           | •             | VECTA+3-3 = VECTA<br>VECTB+3-3 = VECTB        |

| TIX LOOP,1,1                                               | · ·         | 2             | (since 3>1, we index and go back)             |

| LDQ VECTA+3,1<br>FMP VECTB+3,1<br>FAD ANSWER<br>STO ANSWER | •<br>•<br>• |               | VECTA+3-2 = VECTA+1<br>VECTB+3-2 = VECTB+1    |

| TIX LOOP,1,1                                               |             | 1             | (since 2>1, we index and go back)             |

| LDQ VECTA+3,1<br>FMP VECTB+3,1<br>FAD ANSWER<br>STO ANSWER |             |               | VECTA+3-1 = VECTA+2<br>VECTB+3-1 = VECTB+2    |

| TIX LOOP,1,1                                               |             | l             | (since 1 = 1, we do not<br>index; we proceed) |

| HPR                                                        |             | 1.            | stop                                          |

|                                                            |             |               |                                               |

| <b>2</b><br>                                               | FIGURI      | <u>E IV-l</u> |                                               |

|                                                            |             |               |                                               |

IV-6

Figure IV-1 shows a step-by-step history of this program. Notice how the effective address changes with the contents of the index register. The instructions themselves, of course, remain unchanged. This simple program illustrates several points worth remembering about such "TIX loops":

(a) The index register is set to the number of elements to be processed.

(b) The tagged instructions have an address equal to the sum of the location of the first element in the block to which they refer and the number of elements in the block.

(c) The effective address moves forward through the block.

(d) The instructions themselves don't change; only their effective addresses change.

The TIX instruction has a backward twin which acts exactly like the TIX except that it goes to the next instruction where the TIX would transfer and transfers control where the TIX would go to the next instruction:

(8) Transfer on No Index

TNX A,K,N

We can contrive to use the TNX instruction in our previous example.

IV-8

|       | LXA | COUNT,1    | +4 → C(IR1) |

|-------|-----|------------|-------------|

| LOOP  | TNX | STOP,1,1 < | count       |

|       | LDQ | VECTA+3,1  |             |

|       | FMP | VECTB+3,1  |             |

|       | FAD | ANSWER     |             |

|       | STO | ANSWER     |             |

|       | TRA | LOOP       | · · · ·     |

| STOP  | HPR |            |             |

| COUNT | PZE | 4          |             |

ANSWER

The reader should note that in this example the index register is set to one plus the number of elements to be processed. Another characteristic of this program is that counting and testing are done before the loop is entered.

The above example is somewhat forced; however, TNX does have some valid applications. In more complicated programs the number of times a loop is executed may be a variable computed by the program. If zero is an admissible value for this variable it may be possible to write neater loops using TNX than can be written using TIX.

In such program dependent loops, however, further complications arise in connection with the addresses of tagged instructions. In example 1 we noted that a tagged instruction must have an address equal to the sum of the location of the first element in the block and the number of elements in the block. For a program dependent loop this means that the addresses of all tagged instructions must be altered before execution. The physical modification of 704 instructions is possible (we do not know how to do it yet) but can be avoided in this case by an artiface: namely, instead of assigning a symbol to the location of the first element of the block we assign a symbol to the location of the last element of the block (or better still to this location plus 1).

Thus if we store  $A_1$ ,  $A_2$ , and  $A_3$  in VECTA-3, VECTA-2 VECTA-1, respectively, and we store  $B_1$ ,  $B_2$ , and  $B_3$  in VECTB-3, VECTB-2 and VECTB-1, respectively, then scalar multiplication could be performed by the following variation on example 1:

Example 3

|       | LXA | COUNT,1  | +3→C(IR1) |

|-------|-----|----------|-----------|

| LOOP  | LDQ | VECTA,1  |           |

|       | FMP | VECTB,1  | •         |

|       | FAD | ANSWER   |           |

|       | STO | ANSWER   |           |

|       | TIX | LOOP,1,1 | Count     |

|       | HPR |          |           |

| COUNT | PZE | 3        | •<br>•    |

ANSWER

It is suggested that the reader devise a similar variation on example 2.

There are two other conditional transfer instructions involving index registers: (9) Transfer on Index High

TXH A,K,N if (C(IRK) > N), then A  $\rightarrow C(ILC)$ (10) Transfer on Index Low or Equal

TXL A,K,N if  $(C(IRK) \leq N)$ , then A  $\rightarrow C(ILC)$ These two instructions act exactly like TIX and TNX respectively except that they don't change the index register.

One further unconditional transfer instruction will round out the picture.

(11) Transfer With Index Increased

TXI A,K,N  $C(IRK)+N \rightarrow C(IRK)$  and  $A \rightarrow C(ILC)$ Some Remarks About Notation

The reader may have noticed that:

a) All the indexing instructions have an X in their3-letter operation codes.

b) Transmission of information from storage to the index registers is designated by an initial L. (Load). We have LXA and LXD.

c) Transmission of information <u>from</u> the index registers to storage is designated by an initial S. (Store). We have <u>SXD</u> but not <u>SXA</u>.

d) Transmission of information in either direction between the AC and index registers is designated by an initial P. (Place). We have PXD, PDX, PAX, but not PXA.

e) Transfer of control is designated as usual by an initial T. We have four conditional transfers involving index registers, TIX, TNX, TXH, and TXL, and one unconditional transfer, TXI

\* One more, TSX, will be discussed under subject of subroutines.

Arithmetic in the Index Registers and Machine Size

Since the index registers can only hold positive integers less than S, the number of words in the memory; and since S may be less than the largest integer which can be stored in the address or decrement of an instruction, the following pair of instructions might change the integer in the decrement of A:

LXD A, 1

SXD A. 1

In fact our description of the instructions, which move integers into the index registers, was not quite correct. For example, the description of LXD ought to have been:

Load Index from Decrement

$C(\text{decrement of } A)(\text{mod } S) \longrightarrow C(IRK)$ LXD A, K where S is the number of words in the memory, sometimes called the machine size, and

> Χ (mod S)

means the remainder obtained after dividing X by S.

Also, our description of the conditional transfer instructions suffer from the same defect. A precise description of TXH would be:

Transfer on Index High TXH A, K, N if (C(IRK) > N (mod S)), then  $A \rightarrow C(ILC)$

There is a common convention according to which a negative integer, say -N, written in the address or decrement of an instruction is taken as an abbreviation for the positive integer:

$2^{15} - N = 32768 - N$

For the case,  $N \ll C(IR1)$ , this can be justified by the following equation:

$\lceil (2^{15} - N) + C(IR1) \rceil \pmod{S} = C(IR1) - N$ which holds because S is always a factor of  $2^{15}$ . It follows that the instruction:

> A, l, -N TXI

acts as if it were adding a negative number to index register 1.

The address spectrum for the 8192 word machine is illustrated below:

| Binary                | Decimal    |

|-----------------------|------------|

| 11                    | 8191 or -1 |

| 1110                  | 8190 or -2 |

| • • • • • • • • • • • | •••••••••• |

| 0001                  | 1 or -8190 |

| 00                    | 0 or -1191 |

For example, if C(IR1) > 1, then the instruction TXI A, 1, -1

acts exactly as the following instruction would

TIX A, 1, 1

Our convention for negative numbers leads us to a rather peculiar algebra, however, in connection with the TXH and TXL instructions. The usual algebra applies when we are comparing two numbers of like sign, however, if numbers of unlike sign are being compared we see from the table that negative numbers are frequently larger than positive numbers.

Thus, for example, the instructions:

TXL A, 1, -1 and TNX A, 1, -1 would be unconditional control instructions.

Example 4. We rewrite example 1 to illustrate these points.

|        | LXA            | COUNT, 1    |

|--------|----------------|-------------|

| LOOP   | LDQ            | VECTA +3, 1 |

|        | $\mathbf{F}MP$ | VECTA +3, 1 |

| ;      | FAD            | ANSWER      |

|        | STO            | ANSWER      |

|        | TXI            | TEST, 1, -1 |

| TEST   | TXH            | LOOP, 1, 0  |

|        | HPR            |             |

| COUNT  | PZE            | 3           |

| ANSWER |                |             |

|        |                |             |

Decrease C(IR1) by 1

<u>Example 5</u>. We again rewrite example 1 to illustrate a powerful technique for writing program dependent loops.

IV-13

|       | LXA | COUNT, 1        |

|-------|-----|-----------------|

| LOOP  | LDQ | VECTA, 1        |

|       | FMP | VECTB, 1        |

|       | FAD | ANSWER          |

| •     | STO | ANSWER          |

|       | TXI | TEST, 1, -1 / 2 |

| TEST  | TXH | LOOP, 1, -3     |

|       | HPR |                 |

| COUNT | PZE | 0               |

ANSWER

The next example may take some study, but it illustrates the fact that coding loops in terms of the TXI and TXL or TXH instructions may be more convenient than using the TIX.

Example 6. Suppose we have 10 numbers stored in locations A + 1, A + 2, ..., A + 10. Then the following rather complicated routine will sort these numbers in order of increasing size. It does it by the so-called interchange method. First it scans through the list interchanging adjacent numbers if they are out of order. When it gets to the end of the list, the largest element is in last place. Then it repeats the process for the other 9 numbers, etc.

|       | LXA            | CONST, 2        | Set count of no. of passes      |

|-------|----------------|-----------------|---------------------------------|

| Pass  | LXD            | SKIP, 1         | Consider 1st pair               |

|       | SXD            | TEST, 2         | Set test for end of pass.       |

| NEXT  | LDQ            | A, l            |                                 |

|       | CLA            | A + l, l        |                                 |

|       | $\mathrm{TLQ}$ | SKIP            | is the pair out-of-order?       |

|       | STO            | A, 1            | yes, interchange them           |

|       | STQ            | A + 1, 1        |                                 |

| SKIP  | TXI            | SKIP + 1, 1, -1 | Consider next pair              |

| TEST  | TXH            | NEXT, 1, -      | go to NEXT if not end of pass   |

| Q     | TXI            | Q + 1, 2, 1     | Prepare for next pass           |

|       | $\mathtt{TXL}$ | PASS, 2, -2     | Go back for next pass, or       |

|       | HPR            |                 | stop                            |

| CONST | PZE            | - 10            | Address has $2^{15}-10 = 32758$ |

|       |                |                 |                                 |

## Some Pathological Points about the Index Registers

Any of the indexing instructions may be written without a tag. If this occurs the instruction behaves as if there were an imaginary index register, numbered 0 by convention, whose contents is always 0. An application for

#### PXD 0,0

has already been described. Another useful case is the instruction

### TXL A,0

which now becomes an unconditional control instruction and can almost always be used in place of TRA. The advantage in doing so is that TXL can have a decrement and decrements are useful for storing integers needed in the program. (What is the point in ever using TRA?)

An indexable instruction may also (in a certain sense) refer to more than a single index register. For an explanation of this the reader is referred to pll of the 704 manual and to the definition of SXD as given on p26. Such multiple reference is indeed tricky and must be done with care. The following two examples illustrate some uses for reference to multiple index registers. The reader may, if he wishes, defer study of these examples until he has a better feel for the binary nature of the machine.

Example 8. Here we multiply two n by n matrices

$A = (a_{ij}) \qquad i, j = l_{j}, \dots, n$  $B = (b_{ij}) \qquad i, j = l_{j}, \dots, n$ to obtain the matrix

$C = (c_{ij})$   $i_{j} = 1, \dots, n$

We assume that the matrices are stored in "row by row" form, i.e.

a<sub>ij</sub> is in register MATA + (i-l)n + (j-l) b<sub>ij</sub> is in register MATB + (i-l)n + (j-l) c<sub>ij</sub> appeares in register MATC + (i-l)n + (j-l) The rule for matrix multiplication is

$$c_{ij} = \sum_{l=k}^{n} a_{ik} b_{kj}$$

IV-14

The program follows:

| 1 0    |       |                     |                                          |

|--------|-------|---------------------|------------------------------------------|

|        | LXA   | SETUP, 7            | $n^2 \rightarrow C(IR1), C(IR2), C(IR4)$ |

| l LOOP | · PXD |                     |                                          |

|        | STO   | MATC+N <b>*</b> N,4 | N*N means N <sup>2</sup>                 |

| LOOP   | LDQ   | MATA+N*N,1          |                                          |

|        | FMP   | MATB+N#N,2          |                                          |

|        | FAD   | MATC+N <b>*</b> N,4 | Form C                                   |

|        | STO   | MATC+N <b>*</b> N,4 | 0                                        |

|        | TXI   | NEXT,1,-1           |                                          |

| NEXT   | TIX   | LOOP,2,N            |                                          |

|        | TNX   | STOP,4,1            | S <sub>t</sub> op when finished          |

|        | TNX   | 2 LOOP,2,1          | Count within row                         |

|        | TXI   | l NEXT,l,N          | Same row                                 |