#

# JULY 1995

## **IMPORTANT NOTICE**

LOGIC DEVICES INCORPORATED (LDI) reserves the right to make changes to or to discontinue any semiconductor product or service identified in this publication without notice. LDI advises its customers to obtain the latest version of the relevant information to verify, before placing orders, that the information being relied upon is current.

LDI warrants performance of its semiconductor products to current specifications in accordance with LDI's standard warranty. Testing and other quality control techniques are utilized to the extent that LDI deems necessary to support this warranty. Unless mandated by government requirements, specific testing of all parameters of each device is not necessarily performed.

LDI assumes no liability for LDI applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does LDI warrant or represent that any license, either expressed or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of LDI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

LOGIC DEVICES INCORPORATED products are not intended for use in life support applications, devices or systems. Use of a LOGIC Devices product in such application without the prior written consent of the appropriate LOGIC Devices officer is prohibited.

Copyright © 1995, LOGIC Devices Incorporated

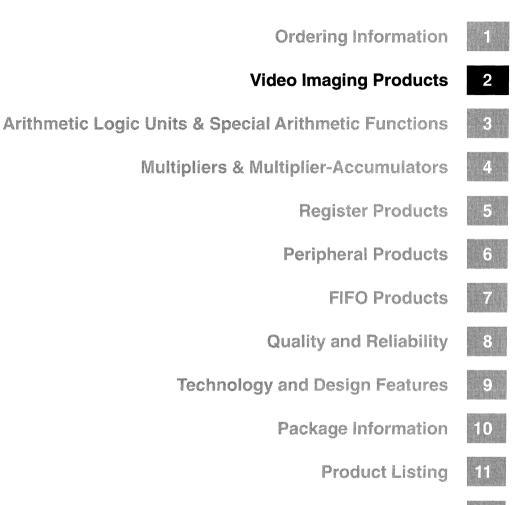

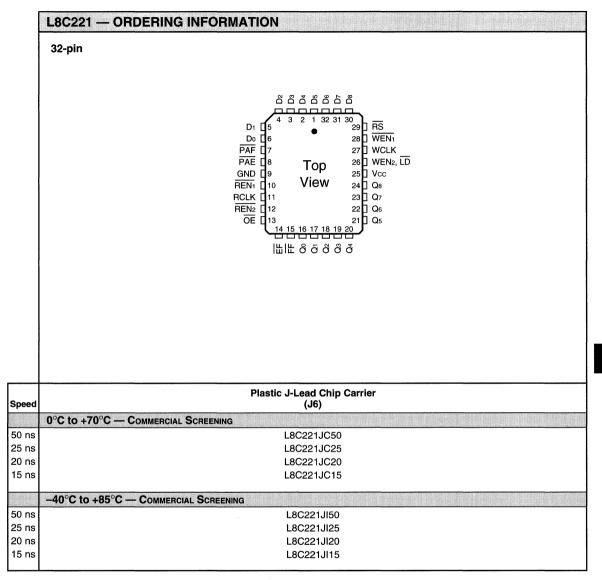

## **Ordering Information** 1 2 **Video Imaging Products Arithmetic Logic Units & Special Arithmetic Functions** 3 4 **Multipliers & Multiplier-Accumulators Register Products** 5 **Peripheral Products** 6 **FIFO Products** 7 8 **Quality and Reliability Technology and Design Features** 9 10 **Package Information** 11 **Product Listing Sales Offices** 12

#### PUBLICATION TEAM

| Darren Andrus:   | Production Team, Cover Design                                                                                 |

|------------------|---------------------------------------------------------------------------------------------------------------|

| Michael De Caro: | Project Leader, Production Coordinator, Production Team,<br>Technical Editing, Cover Design, Cover Production |

| Tim Flaherty:    | Technical Editing                                                                                             |

| Cecelia Kong:    | Cover Design                                                                                                  |

Table of Contents

| 1. | ORDERING                  | SINFORMATION                                                      | 1-1 |

|----|---------------------------|-------------------------------------------------------------------|-----|

| 2  | VIDEO IMA                 | AGING PRODUCTS                                                    | 2-1 |

|    | LF2242                    | 12/16-bit Half-Band Digital Filter                                |     |

|    | LF2246                    | 11 x 10-bit Image Filter                                          |     |

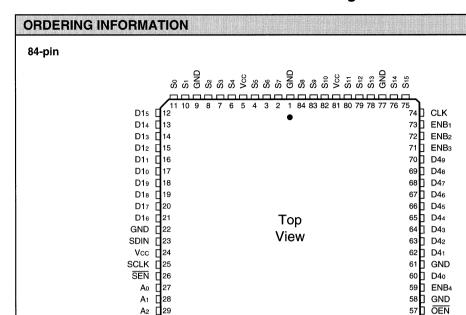

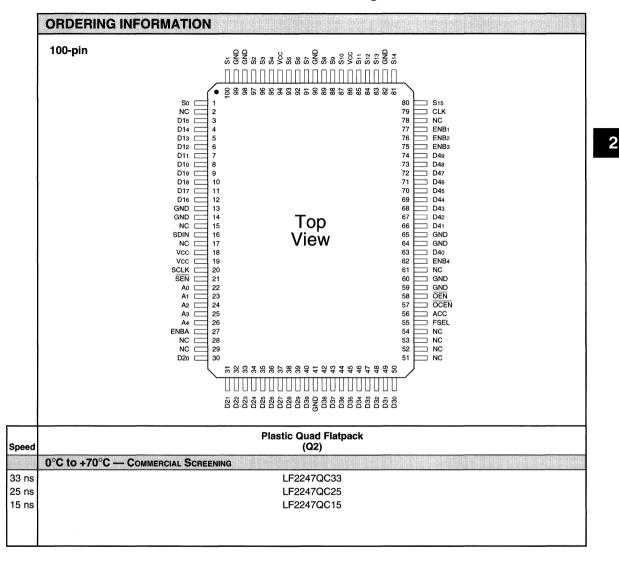

|    | LF2247                    | 11 x 10-bit Image Filter with Coefficient RAM                     |     |

|    | LF2249                    | 12 x 12-bit Digital Mixer                                         |     |

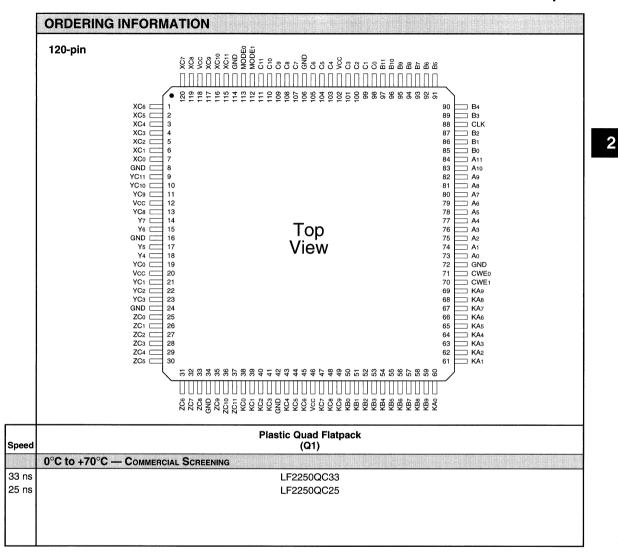

|    | LF2250                    | 12 x 10-bit Matrix Multiplier                                     |     |

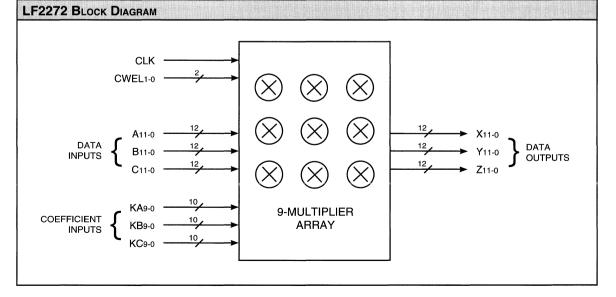

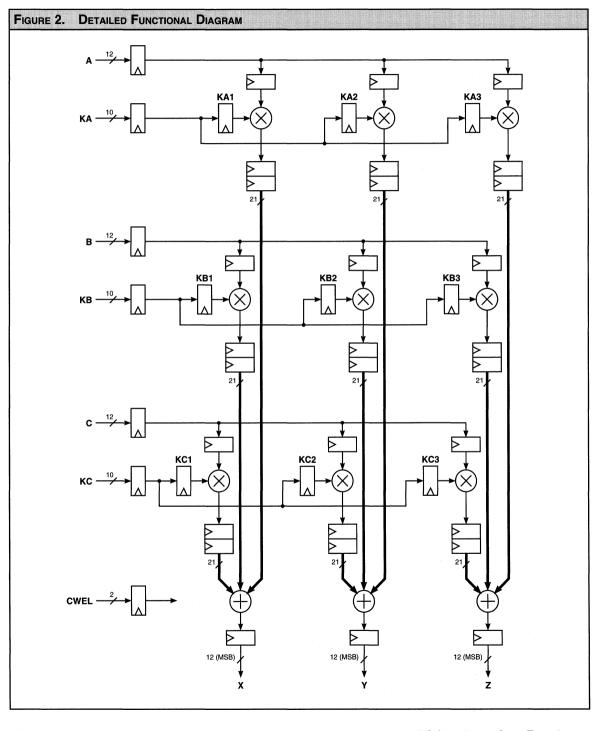

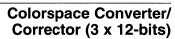

|    | LF2272                    | Colorspace Converter/Corrector (3 x 12-bits)                      |     |

|    | LF43168                   | Dual 8-Tap FIR Filter                                             |     |

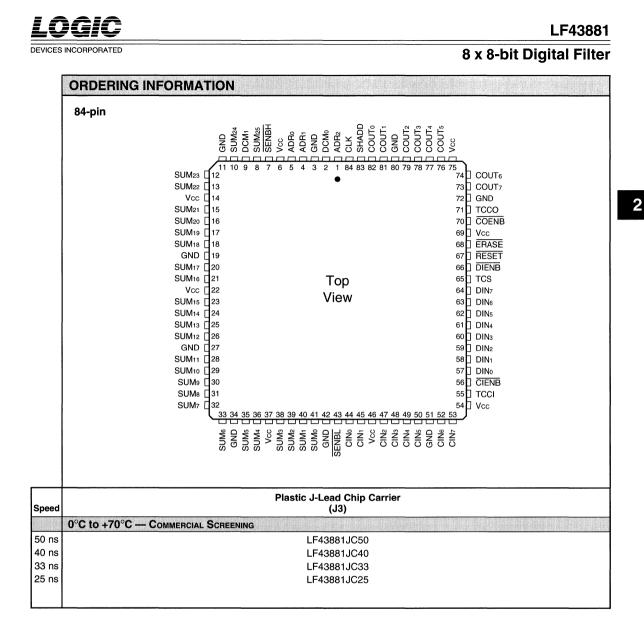

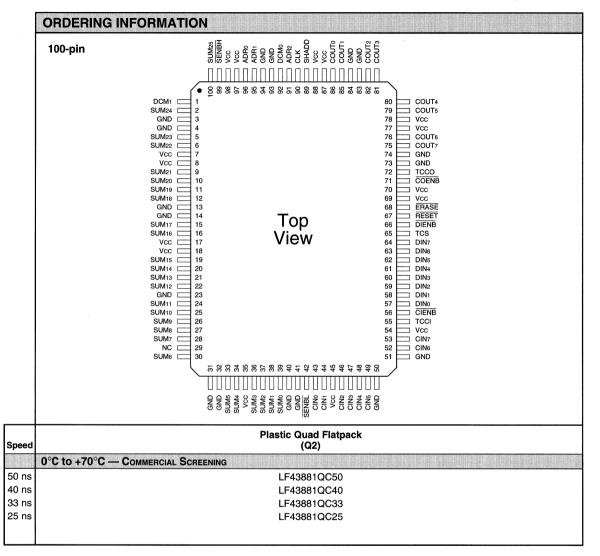

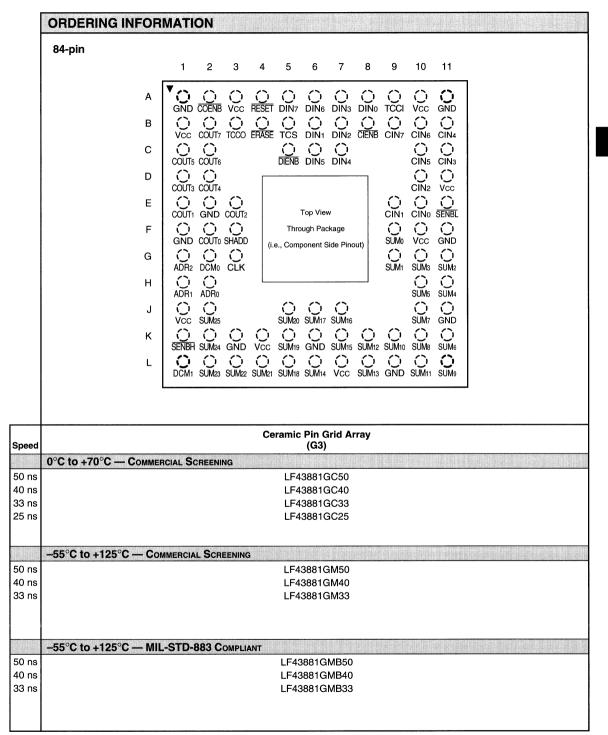

|    | LF43881                   | 8 x 8-bit Digital Filter                                          |     |

|    | LF43891                   | 9 x 9-bit Digital Filter                                          |     |

|    | LF48212                   | Alpha Mixer                                                       |     |

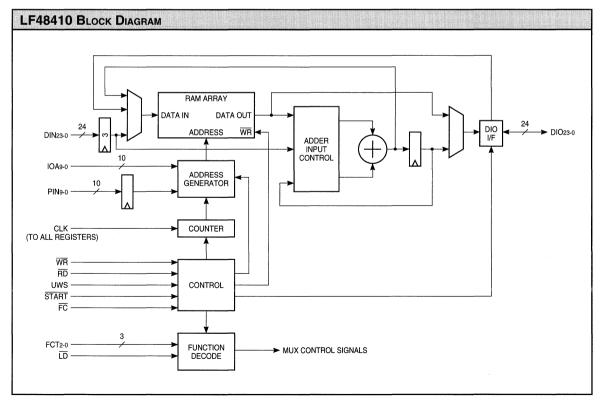

|    | LF48410                   | 1024 x 24-bit Video Histogrammer                                  |     |

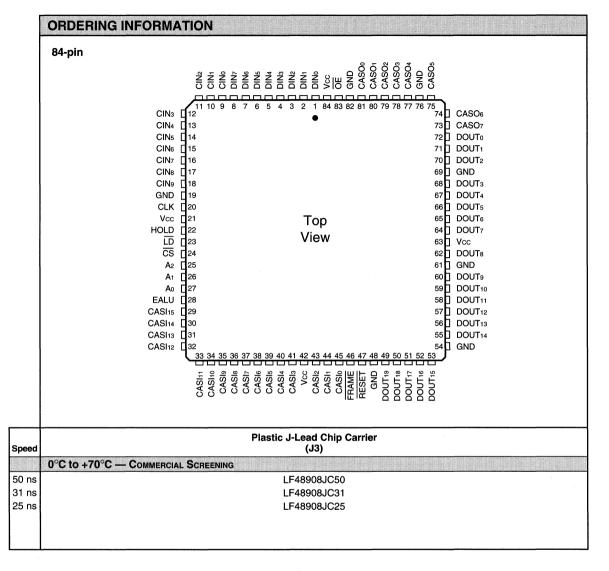

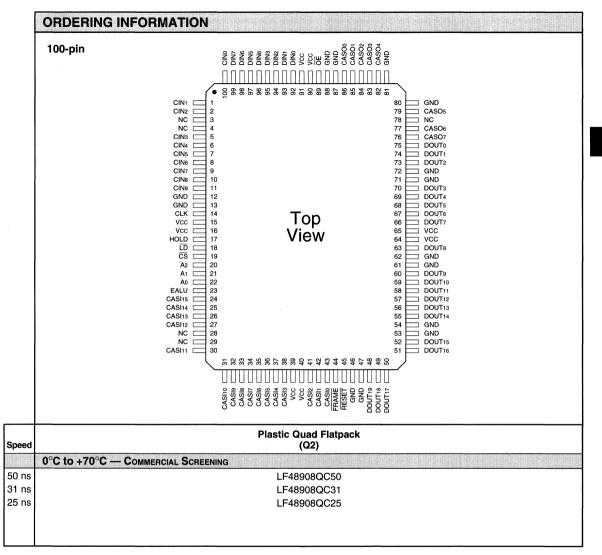

|    | LF48908                   | Two Dimensional Convolver                                         |     |

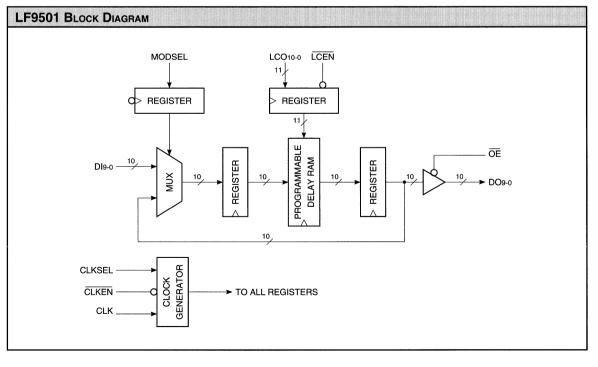

|    | LF9501                    | 1K Programmable Line Buffer                                       |     |

|    | LF9502                    | 2K Programmable Line Buffer                                       |     |

| 3. | ARITHMET<br>Arithmetic Lo | IC LOGIC UNITS & SPECIAL ARITHMETIC FUNCTIONS                     |     |

|    | L4C381                    | 16-bit Cascadable ALU                                             |     |

|    | Special Arith             | metic Functions                                                   |     |

|    | LSH32                     | 32-bit Cascadable Barrel Shifter                                  |     |

|    | LSH33                     | 32-bit Cascadable Barrel Shifter with Registers                   |     |

|    | L10C23                    | 64 x 1 Digital Correlator                                         |     |

| 4. | MULTIPLIE<br>Multipliers  | RS & MULTIPLIER-ACCUMULATORS                                      |     |

|    | LMU08                     | 8 x 8-bit Parallel Multiplier, Signed                             |     |

|    | LMU8U                     | 8 x 8-bit Parallel Multiplier, Unsigned                           |     |

|    | LMU12                     | 12 x 12-bit Parallel Multiplier                                   |     |

|    | LMU112                    | 12 x 12-bit Parallel Multiplier, Reduced Pinout                   |     |

|    | LMU16                     | 16 x 16-bit Parallel Multiplier                                   |     |

|    | LMU216                    | 16 x 16-bit Parallel Multiplier, Surface Mount                    |     |

|    | LMU18                     | 16 x 16-bit Parallel Multiplier, 32 Outputs                       |     |

|    | LMU217                    | 16 x 16-bit Parallel Multiplier, Microprogrammable, Surface Mount |     |

|    | Multiplier-A              |                                                                   |     |

|    | LMA1009                   | 12 x 12-bit Multiplier-Accumulator                                |     |

|    | LMA2009                   | 12 x 12-bit Multiplier-Accumulator, Surface Mount                 |     |

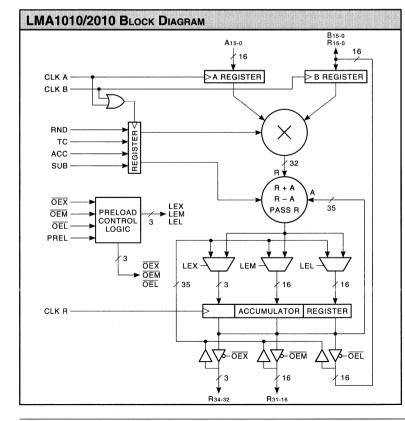

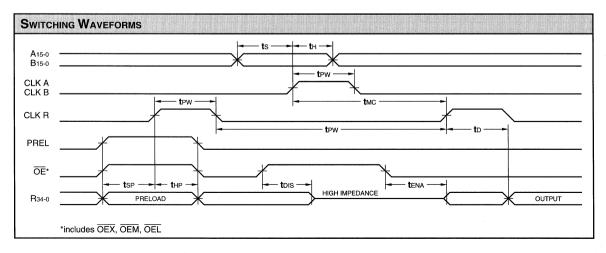

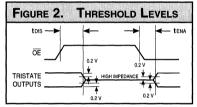

|    | LMA1010                   | 16 x 16-bit Multiplier-Accumulator                                |     |

|    | LMA2010                   | 16 x 16-bit Multiplier-Accumulator, Surface Mount                 |     |

|    | Multiplier-Su             |                                                                   |     |

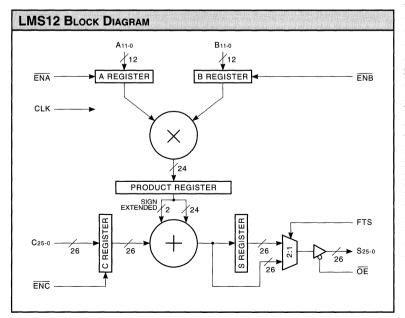

|    | LMS12                     | 12 x 12 + 26-bit Cascadable Multiplier-Summer, FIR                |     |

v

| 5.  | REGISTER    | R PRODUCTS                                             |      |

|-----|-------------|--------------------------------------------------------|------|

|     | Pipeline Re | gisters                                                |      |

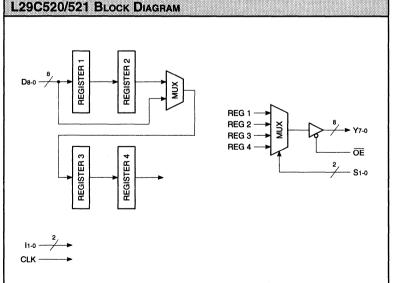

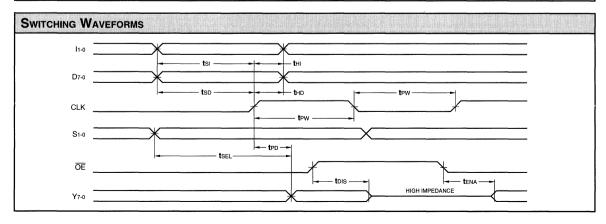

|     | L29C520     | 4 x 8-bit Multilevel Pipeline Register (1-4 Stages)    |      |

|     | L29C521     | 4 x 8-bit Multilevel Pipeline Register (1-4 Stages)    |      |

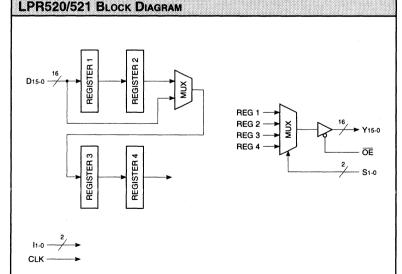

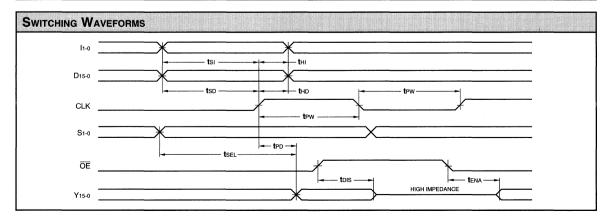

|     | LPR520      | 4 x 16-bit Multilevel Pipeline Register (1-4 Stages)   |      |

|     | LPR521      | 4 x 16-bit Multilevel Pipeline Register (1-4 Stages)   |      |

|     | LPR200      | 8 x 16-bit Multilevel Pipeline Register (1-8 Stages)   |      |

|     | LPR201      | 7 x 16-bit Multilevel Pipeline Register (1-7 Stages)   |      |

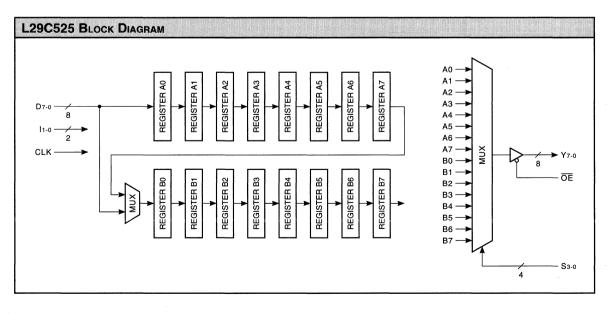

|     | L29C525     | 16 x 8-bit Dual 8-Deep Pipeline Register (1-16 Stages) |      |

|     | L10C11      | 4/8-bit Variable Length Shift Register (3-18 Stages)   |      |

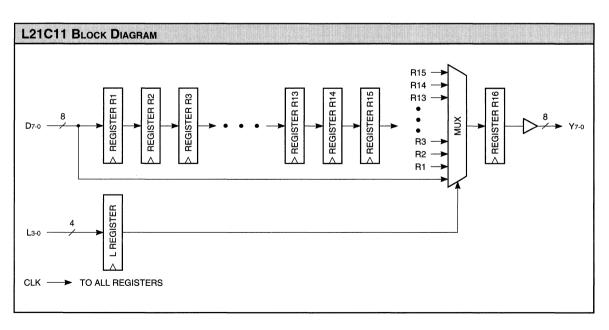

|     | L21C11      | 8-bit Variable Length Shift Register (1-16 Stages)     |      |

|     | Shadow Reg  |                                                        |      |

|     | L29C818     | 8-bit Serial Scan Shadow Register                      |      |

| 6.  | PERIPHER    | AL PRODUCTS                                            | 6-1  |

| 0.  | L5380       | SCSI Bus Controller                                    |      |

|     | L53C80      | SCSI Bus Controller                                    |      |

| 7   | FIFO PROI   | DUCTS                                                  | 7_1  |

| 7.  | L8C201      | 512 x 9, Asynchronous                                  |      |

|     | L8C201      | 1K x 9, Asynchronous                                   |      |

|     | L8C202      | 2K x 9, Asynchronous                                   |      |

|     | L8C203      | 4K x 9, Asynchronous                                   |      |

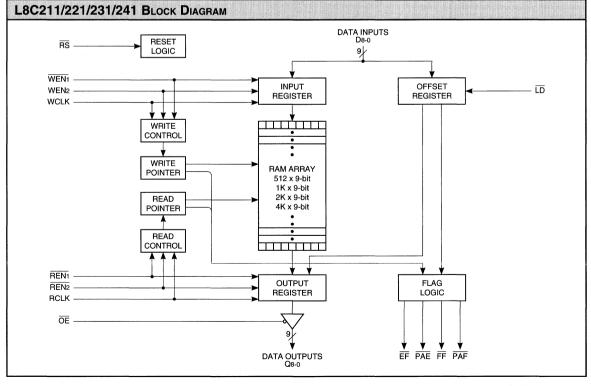

|     | L8C211      | 512 x 9, Synchronous                                   |      |

|     | L8C2211     | 1K x 9, Synchronous                                    |      |

|     | L8C231      | 2K x 9, Synchronous                                    |      |

|     | L8C241      | 4K x 9, Synchronous                                    |      |

| 8.  | QUALITY     | AND RELIABILITY                                        |      |

| 9.  | TECHNOI     | .OGY AND DESIGN FEATURES                               | 0.1  |

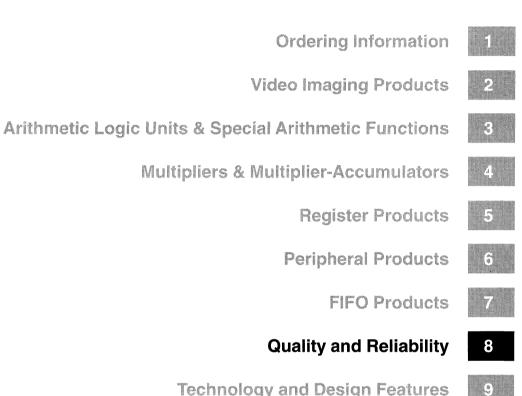

| ۶.  |             | and ESD Protection                                     |      |

|     | -           | ssipation in LOGIC Devices Products                    |      |

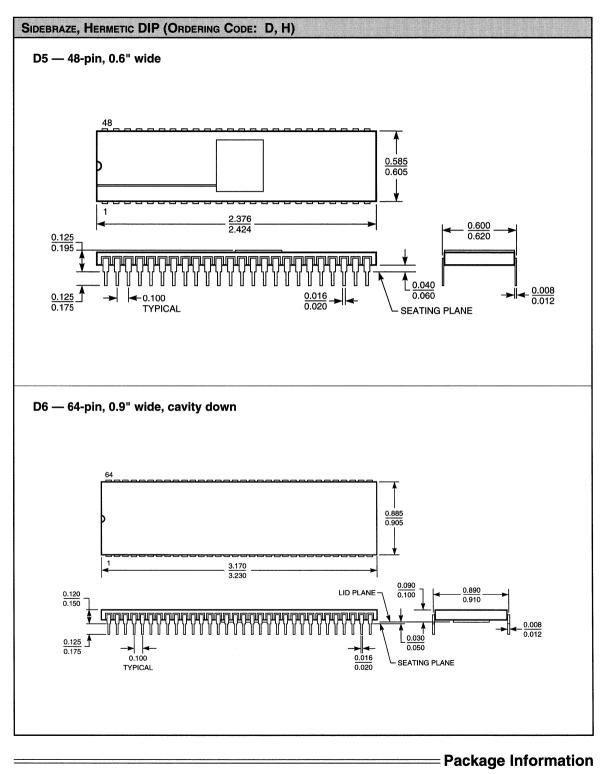

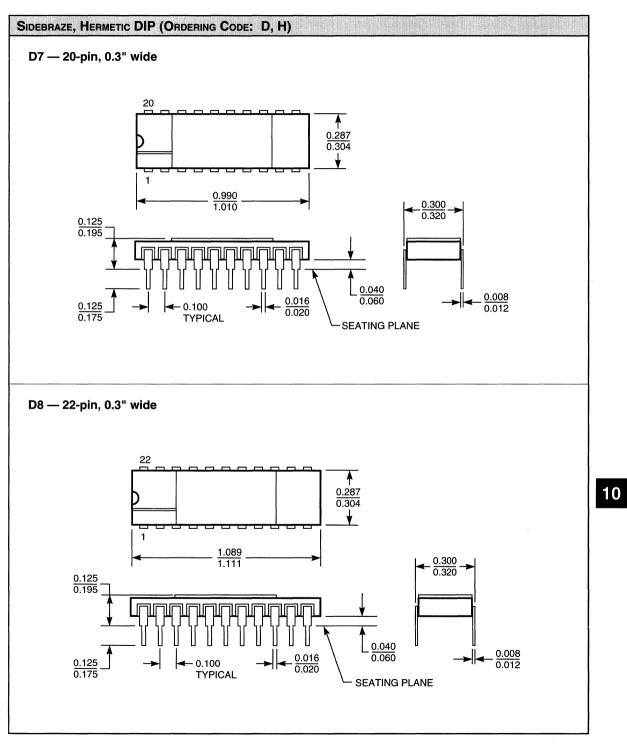

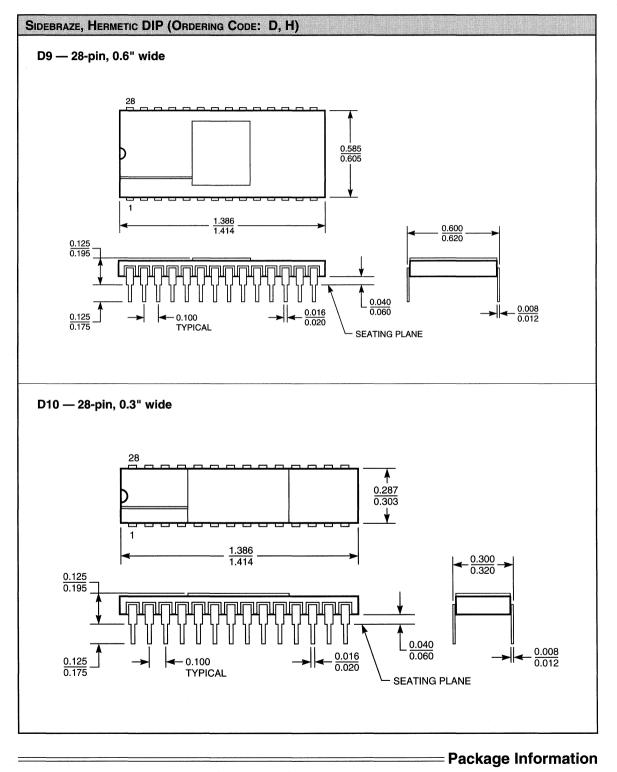

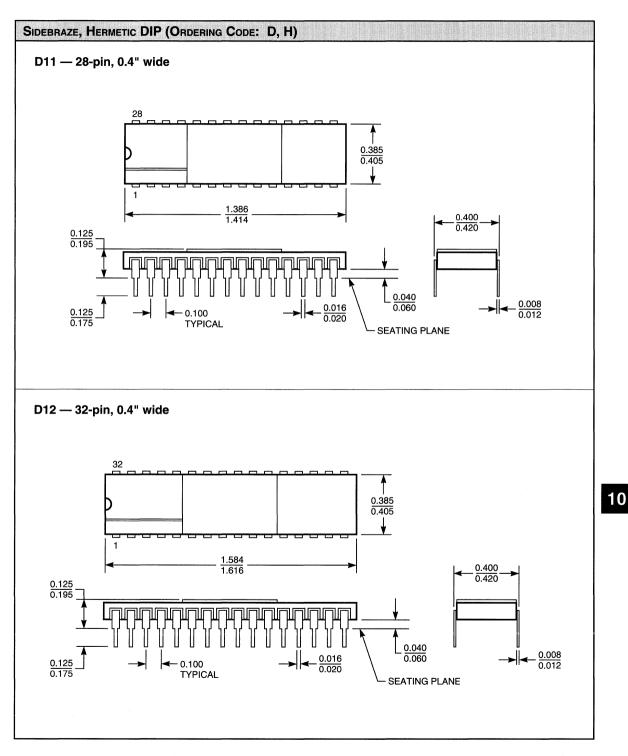

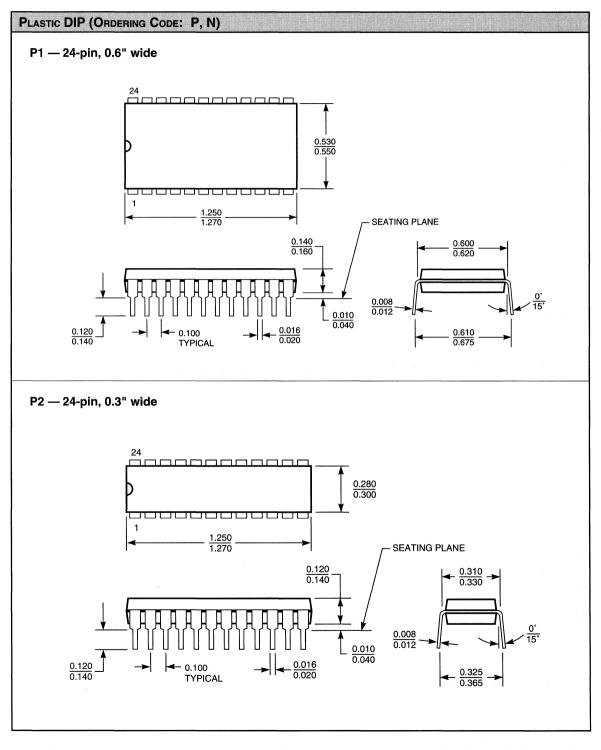

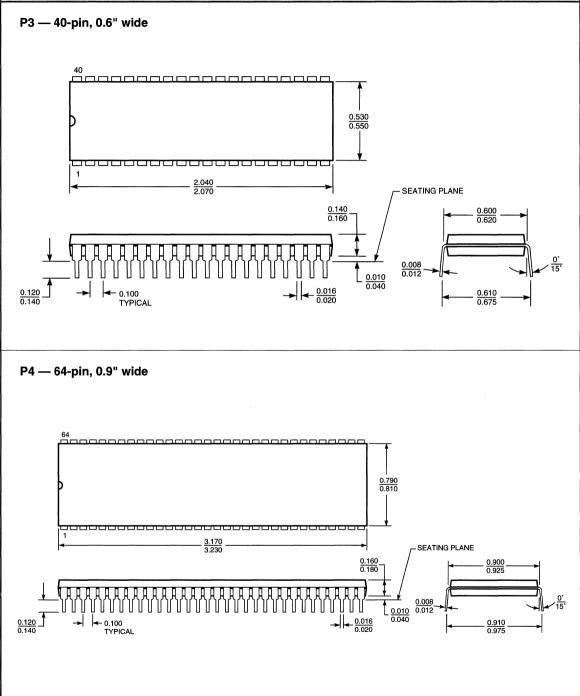

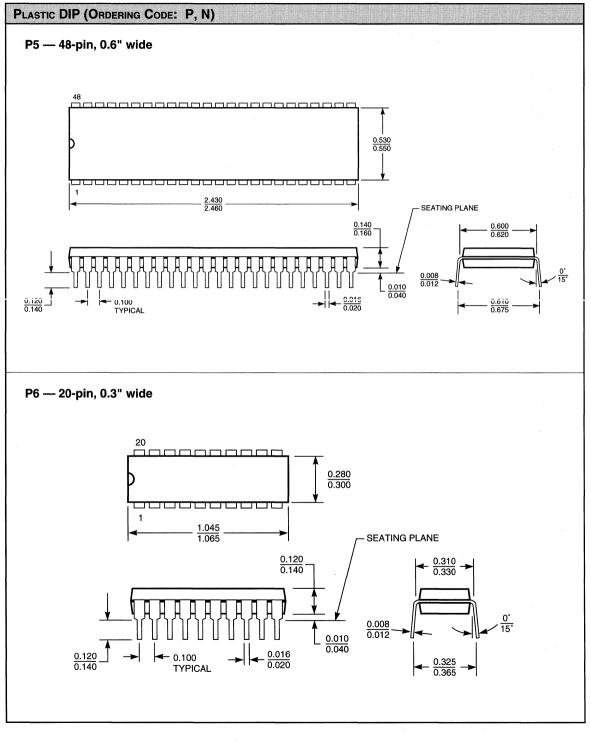

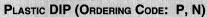

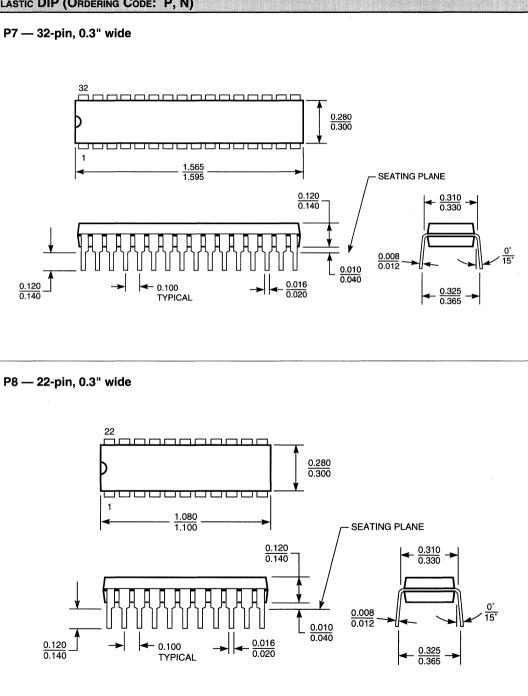

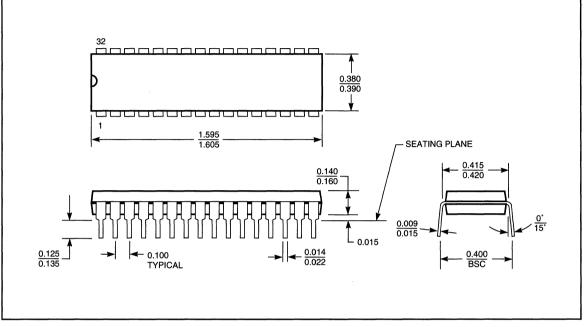

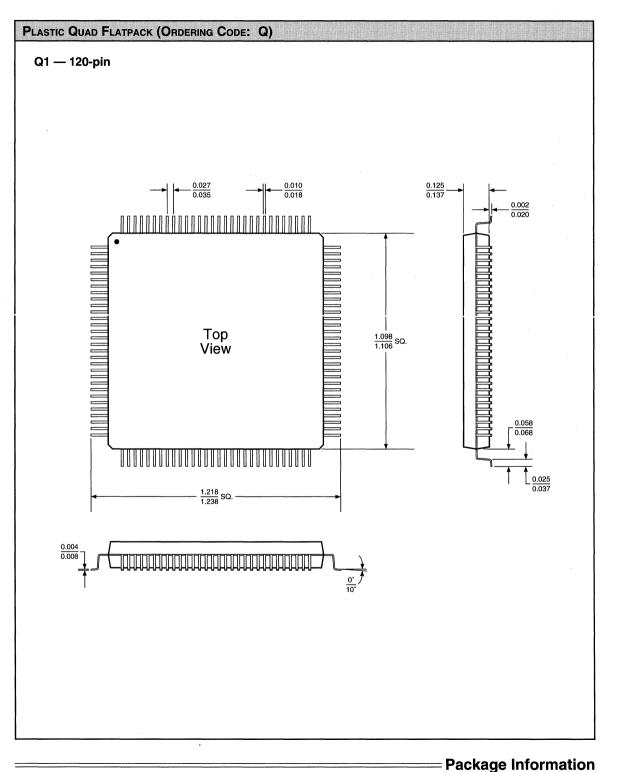

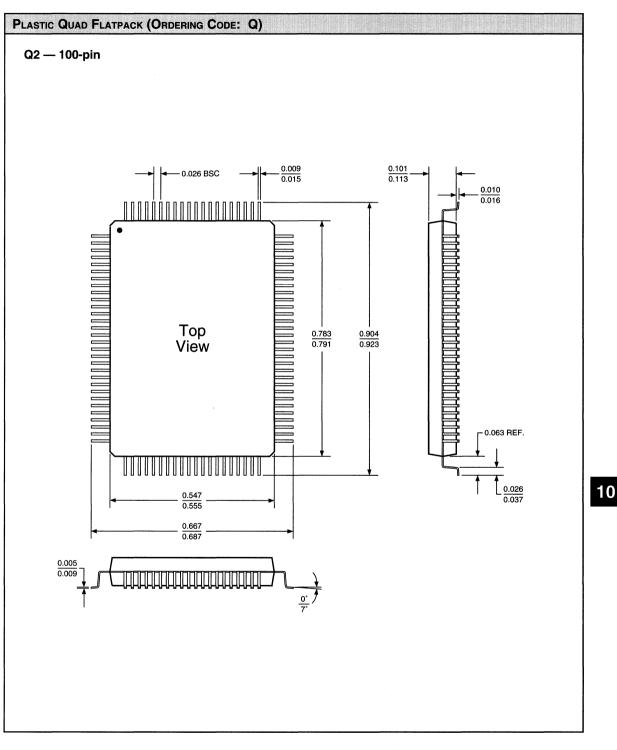

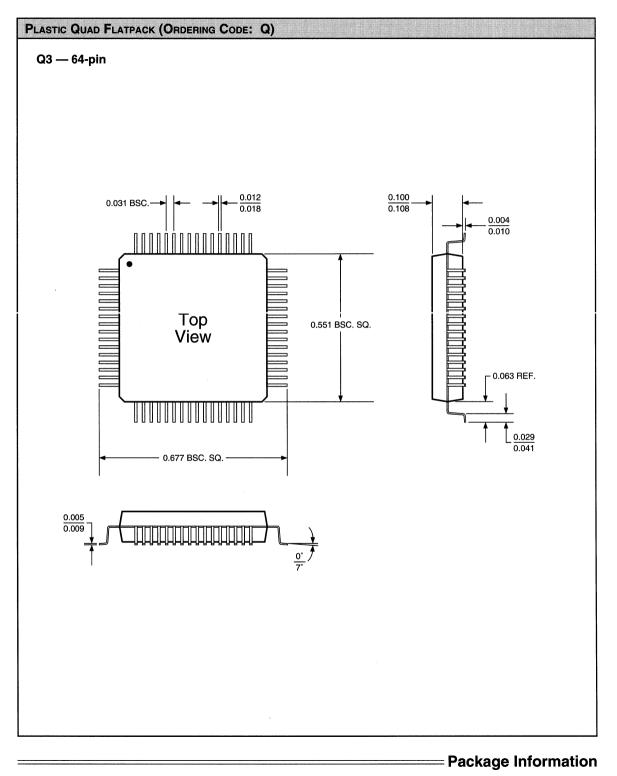

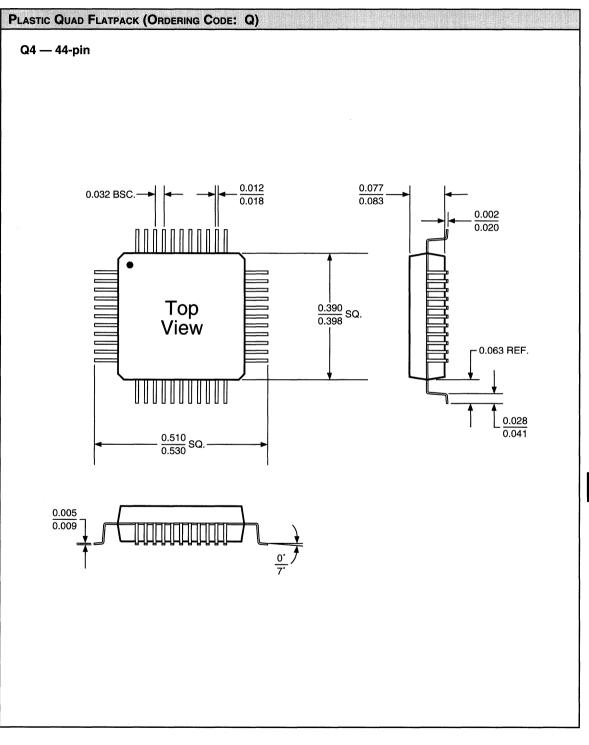

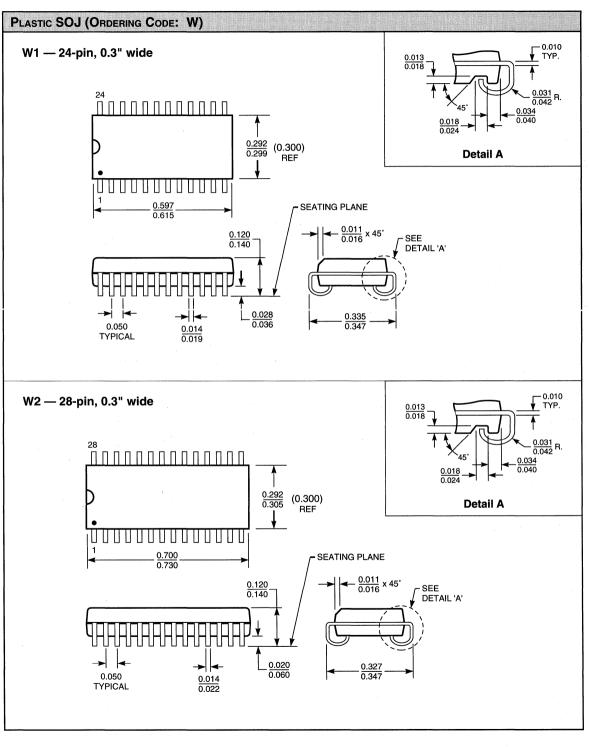

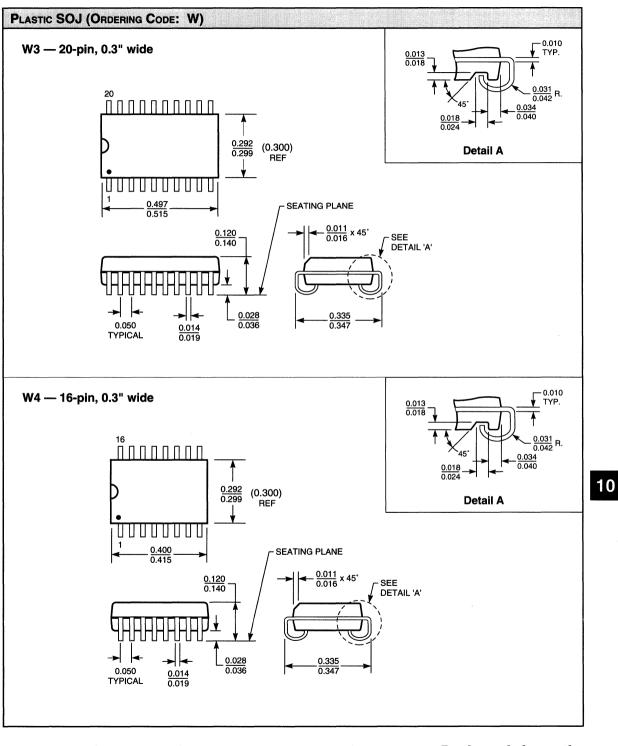

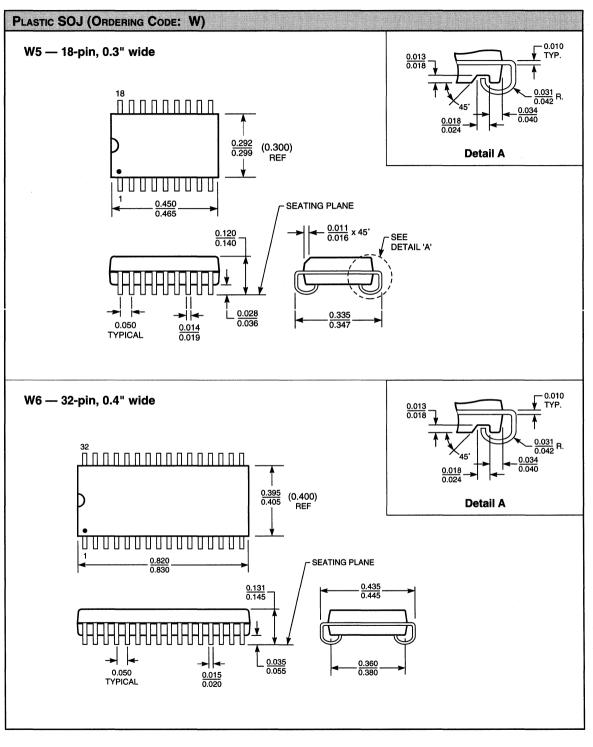

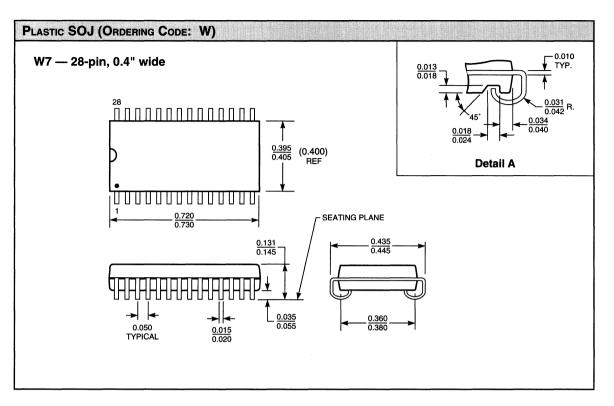

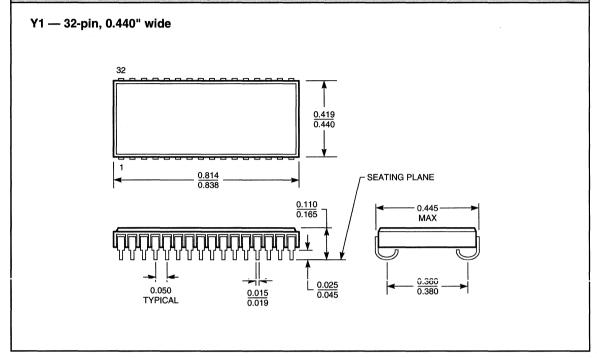

| 10  | DACKACE     | INFORMATION                                            | 10.1 |

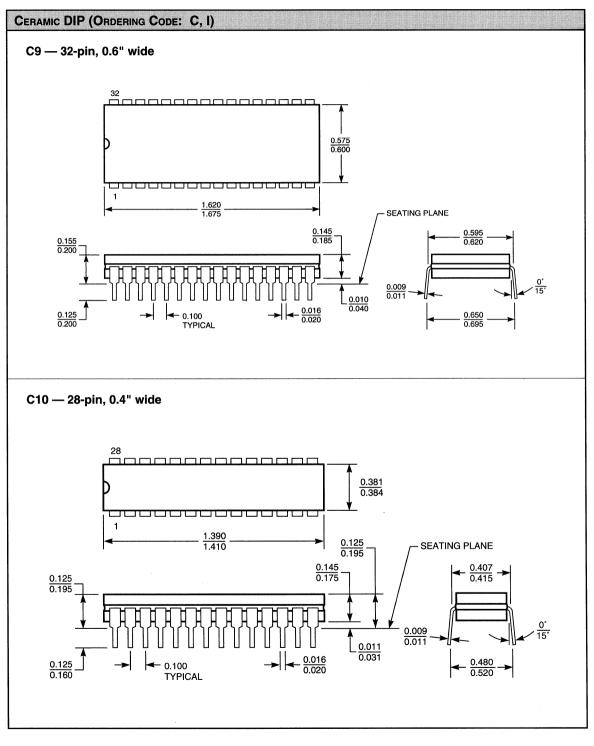

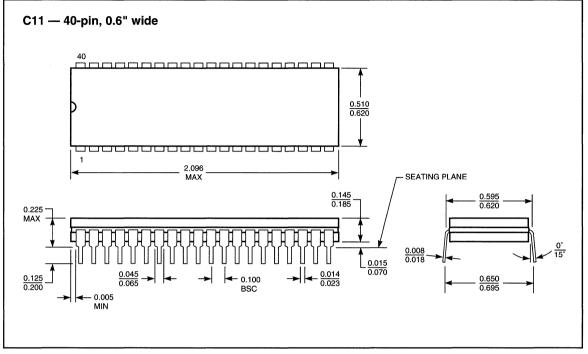

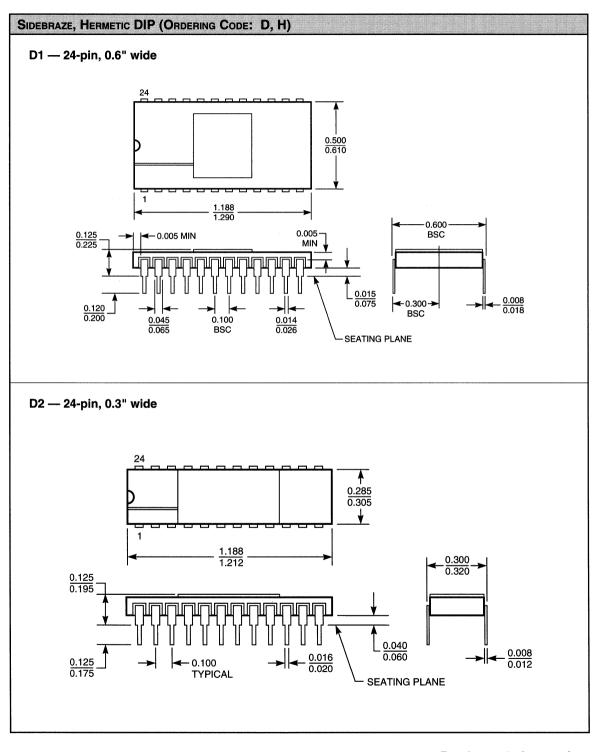

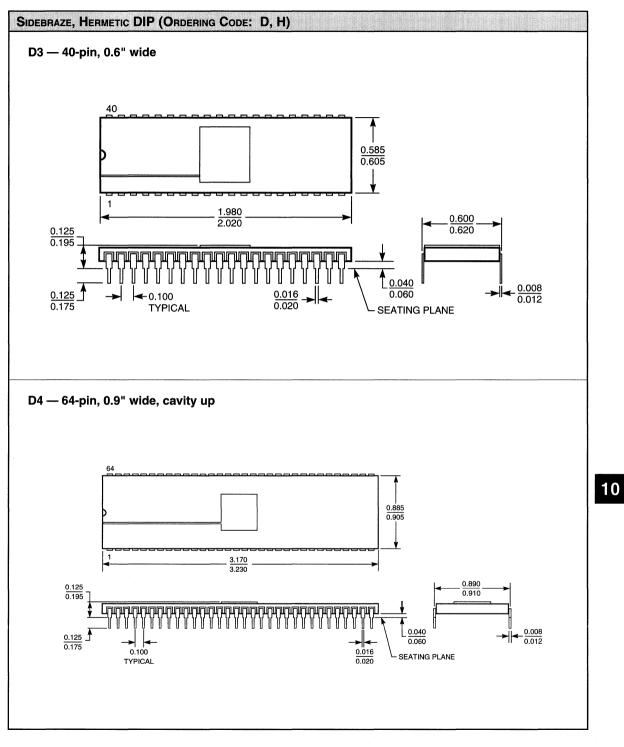

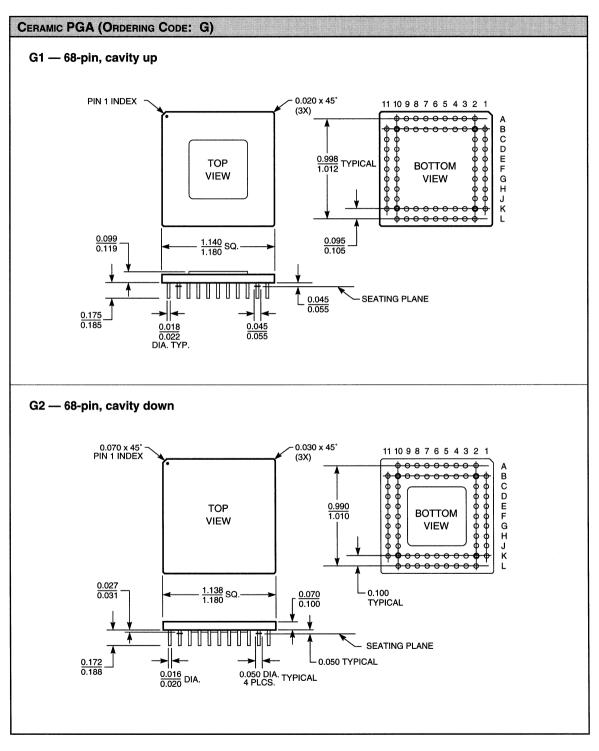

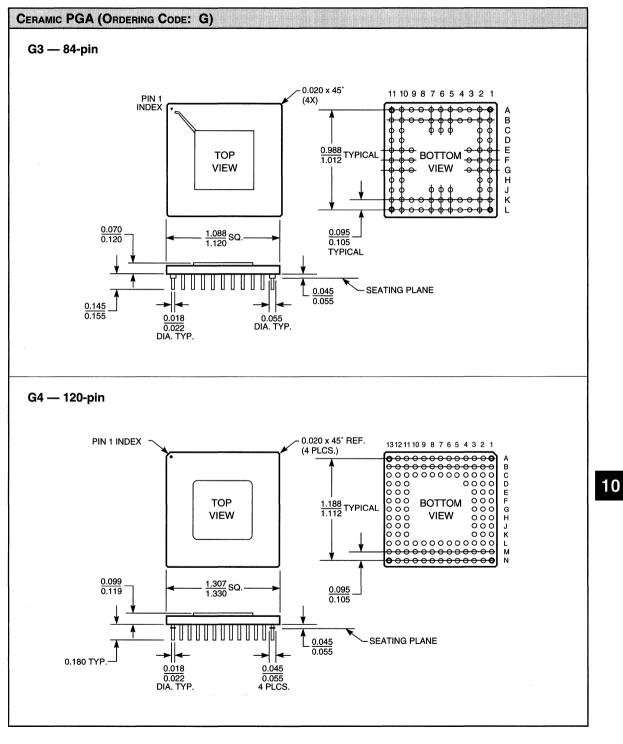

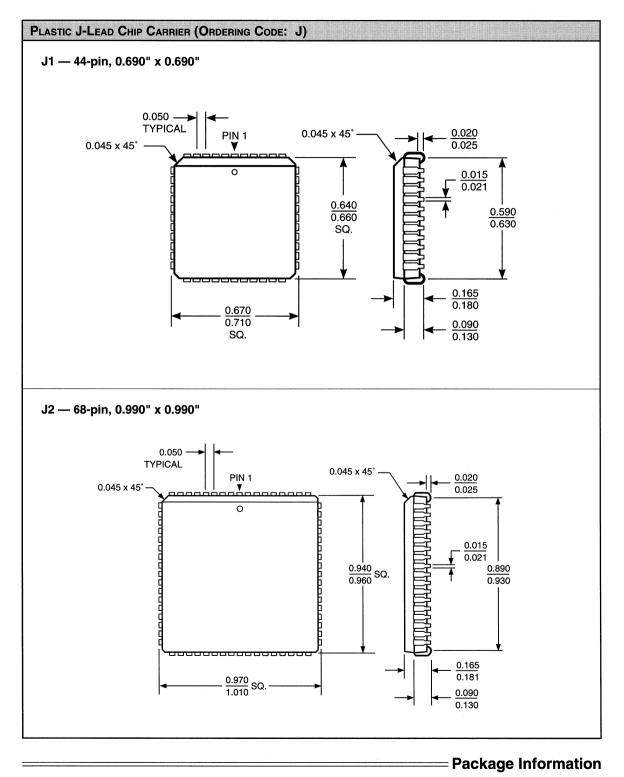

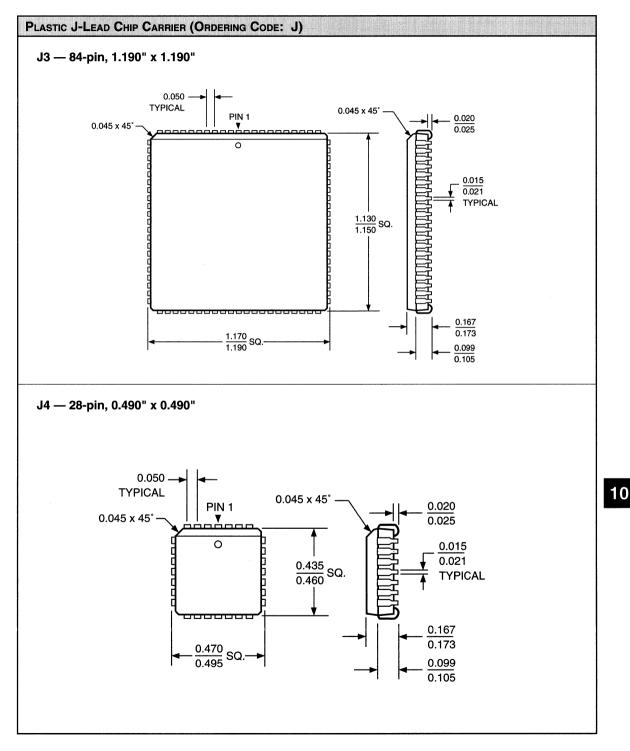

| 10. |             | evices/MIL-STD-1835 Package Code Cross-Reference       |      |

|     |             | Considerations                                         |      |

|     |             | Considerations                                         |      |

|     | 0           |                                                        |      |

|     | wiechanic   | al Drawings                                            |      |

| 11. | PRODUCT     | LISTING                                                |      |

| 12. | SALES OF    | FICES                                                  | 12-1 |

|     |             |                                                        |      |

| L10C11  | 4/8-bit Variable Length Shift Register (3-18 Stages)              |  |

|---------|-------------------------------------------------------------------|--|

| L10C23  | 64 x 1 Digital Correlator                                         |  |

| L21C11  | 8-bit Variable Length Shift Register (1-16 Stages)                |  |

| L29C520 | 4 x 8-bit Multilevel Pipeline Register (1-4 Stages)               |  |

| L29C521 | 4 x 8-bit Multilevel Pipeline Register (1-4 Stages)               |  |

| L29C525 | 16 x 8-bit Dual 8-Deep Pipeline Register (1-16 Stages)            |  |

| L29C818 | 8-bit Serial Scan Shadow Register                                 |  |

| L4C381  | 16-bit Cascadable ALU                                             |  |

| L5380   | SCSI Bus Controller                                               |  |

| L53C80  | SCSI Bus Controller                                               |  |

| L8C201  | 512 x 9, Asynchronous FIFO                                        |  |

| L8C202  | 1K x 9, Asynchronous FIFO                                         |  |

| L8C203  | 2K x 9, Asynchronous FIFO                                         |  |

| L8C204  | 4K x 9, Asynchronous FIFO                                         |  |

| L8C211  | 512 x 9, Synchronous FIFO                                         |  |

| L8C221  | 1K x 9, Synchronous FIFO                                          |  |

| L8C231  | 2K x 9, Synchronous FIFO                                          |  |

| L8C241  | 4K x 9, Synchronous FIFO                                          |  |

| LF2242  | 12/16-bit Half-Band Digital Filter                                |  |

| LF2246  | 11 x 10-bit Image Filter                                          |  |

| LF2247  | 11 x 10-bit Image Filter with Coefficient RAM                     |  |

| LF2249  | 12 x 12-bit Digital Mixer                                         |  |

| LF2250  | 12 x 10-bit Matrix Multiplier                                     |  |

| LF2272  | Colorspace Converter/Corrector (3 x 12-bits)                      |  |

| LF43168 | Dual 8-Tap FIR Filter                                             |  |

| LF43881 | 8 x 8-bit Digital Filter                                          |  |

| LF43891 | 9 x 9-bit Digital Filter                                          |  |

| LF48212 | Alpha Mixer                                                       |  |

| LF48410 | 1024 x 24-bit Video Histrogrammer                                 |  |

| LF48908 | Two Dimensional Convolver                                         |  |

| LF9501  | 1K Programmable Line Buffer                                       |  |

| LF9502  | 2K Programmable Line Buffer                                       |  |

| LMA1009 | 12 x 12-bit Multiplier-Accumulator                                |  |

| LMA1010 | 16 x 16-bit Multiplier-Accumulator                                |  |

| LMA2009 | 12 x 12-bit Multiplier-Accumulator, Surface Mount                 |  |

| LMA2010 | 16 x 16-bit Multiplier-Accumulator, Surface Mount                 |  |

| LMS12   | 12 x 12 + 26-bit Cascadable Multiplier-Summer, FIR                |  |

| LMU08   | 8 x 8-bit Parallel Multiplier, Signed                             |  |

| LMU112  | 12 x 12-bit Parallel Multiplier, Reduced Pinout                   |  |

| LMU12   | 12 x 12-bit Parallel Multiplier                                   |  |

| LMU16   | 16 x 16-bit Parallel Multiplier                                   |  |

| LMU18   | 16 x 16-bit Parallel Multiplier, 32 Outputs                       |  |

| LMU216  | 16 x 16-bit Parallel Multiplier, Surface Mount                    |  |

| LMU217  | 16 x 16-bit Parallel Multiplier, Microprogrammable, Surface Mount |  |

| LMU8U   | 8 x 8-bit Parallel Multiplier, Unsigned                           |  |

# Numeric Table of Contents

| LPR200 | 8 x 16-bit Multilevel Pipeline Register (1-8 Stages) | 5-17   |

|--------|------------------------------------------------------|--------|

|        | 7 x 16-bit Multilevel Pipeline Register (1-7 Stages) |        |

|        | 4 x 16-bit Multilevel Pipeline Register (1-4 Stages) |        |

|        | 4 x 16-bit Multilevel Pipeline Register (1-4 Stages) |        |

| LSH32  | 32-bit Cascadable Barrel Shifter                     |        |

| LSH33  | 32-bit Cascadable Barrel Shifter with Registers      | 3-25   |

| LSH33  | 32-bit Cascadable Barrel Shifter with Registers      | . 3-25 |

# 1 **Ordering Information Video Imaging Products Arithmetic Logic Units & Special Arithmetic Functions** 4 **Multipliers & Multiplier-Accumulators Register Products** 5 **Peripheral Products** 6 **FIFO Products** 7 8 **Quality and Reliability** 9 **Technology and Design Features** 10 **Package Information** 11 **Product Listing**

12

# Ordering Information

1

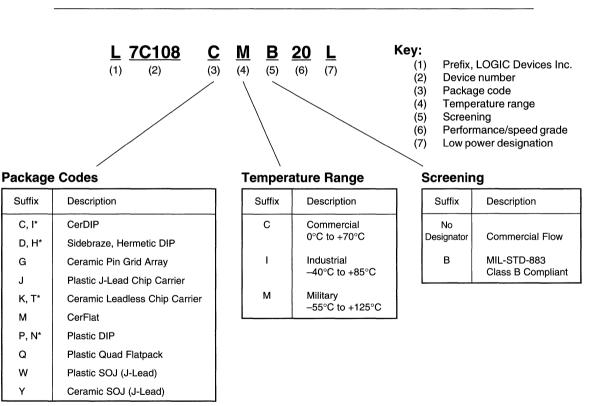

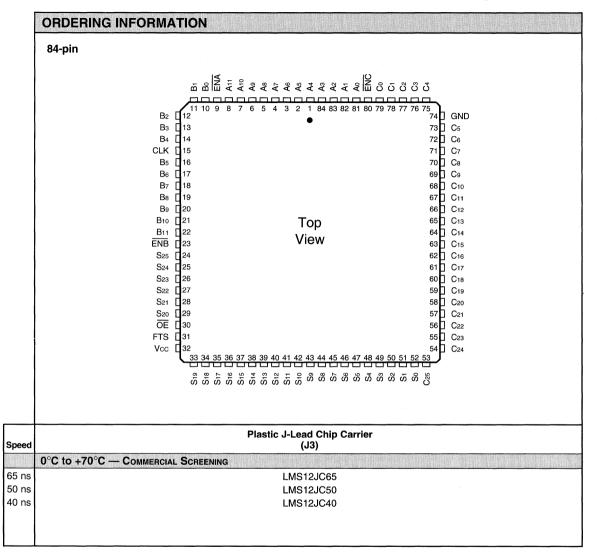

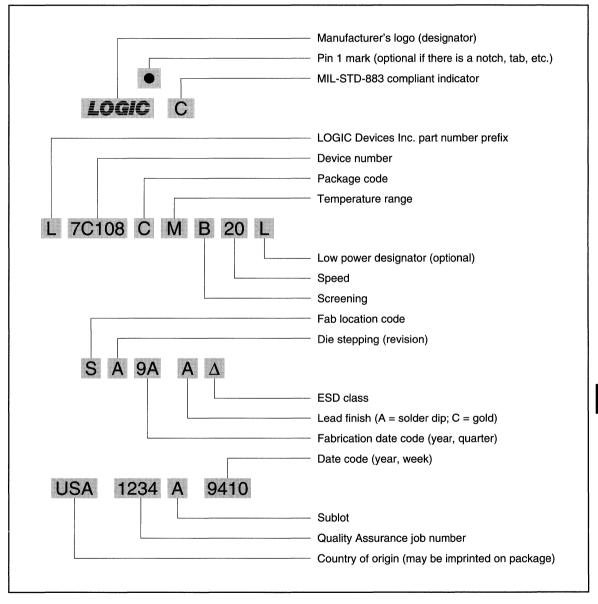

## TO CONSTRUCT A VALID PART NUMBER:

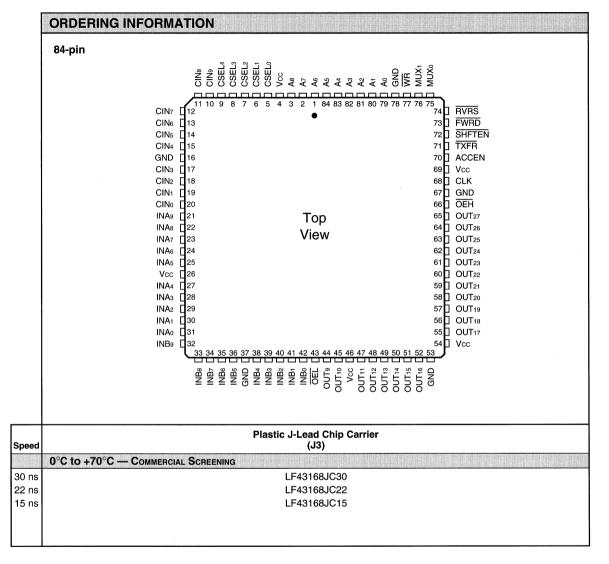

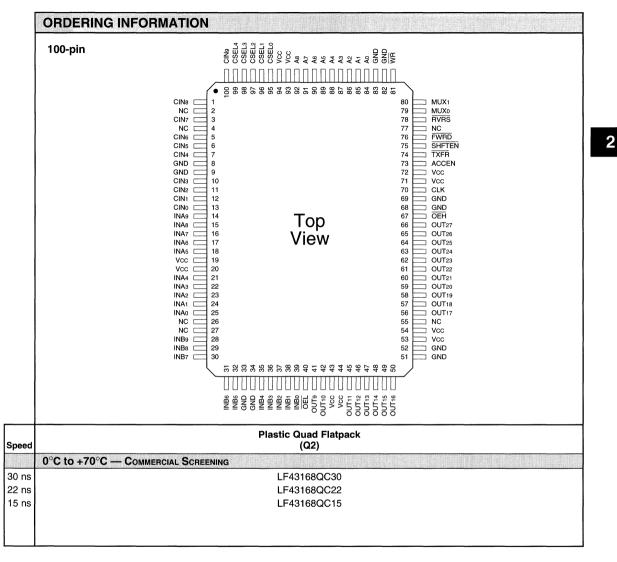

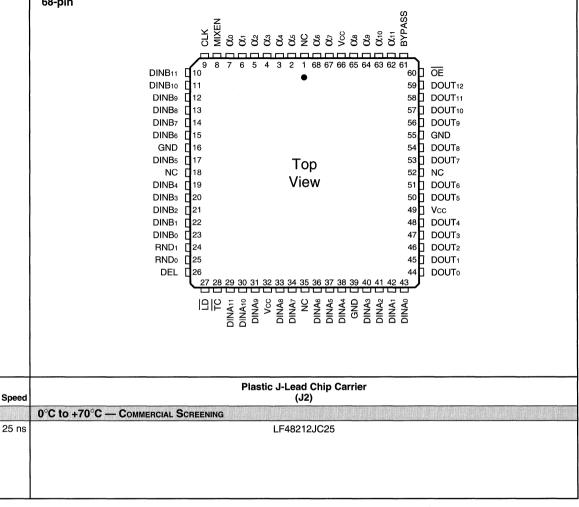

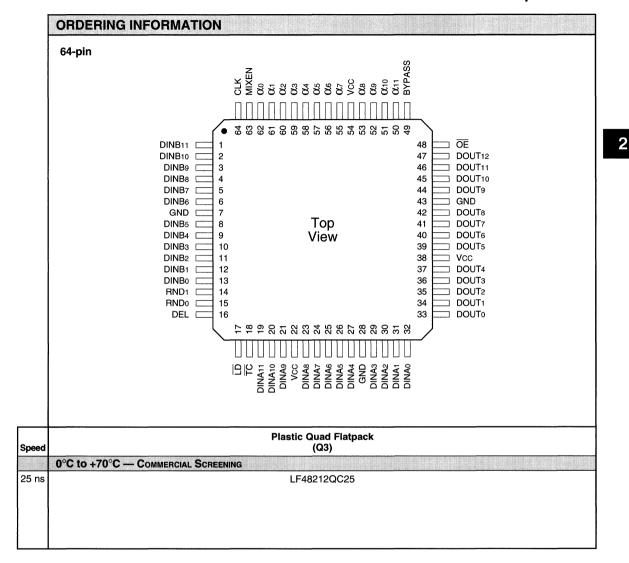

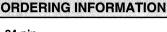

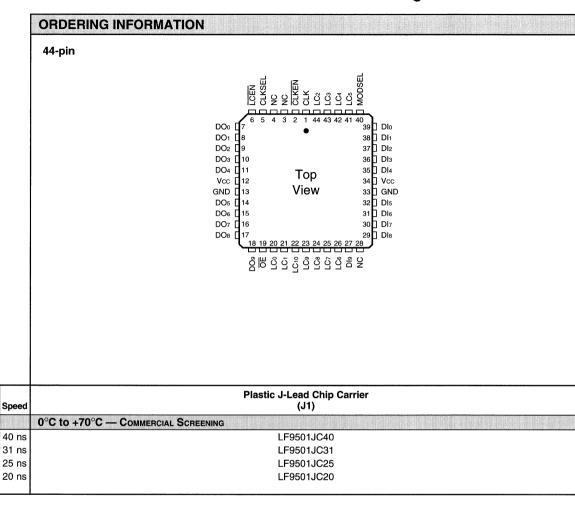

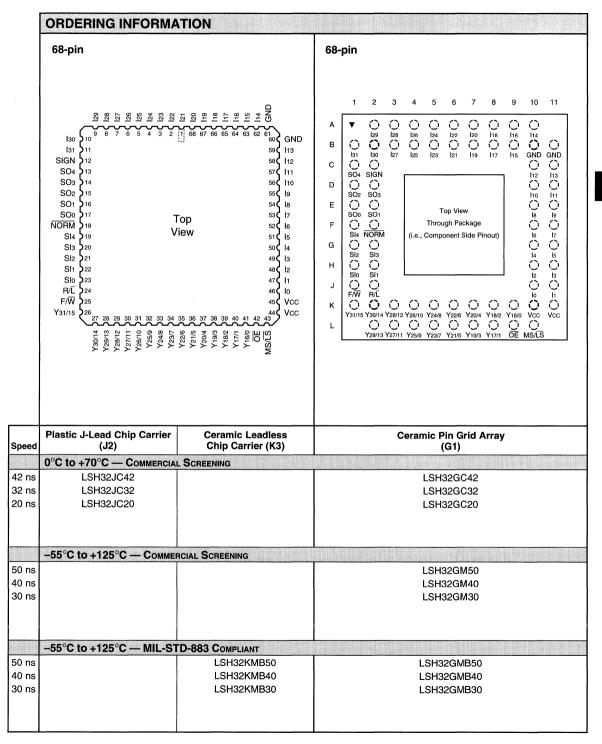

In order to construct a valid LOGIC Devices part number, begin with the generic number obtained from the data sheet header. To this number, append two or three characters from the tables below indicating the desired package code, temperature range, and screening. Finally, append one or two digits indicating the performance grade desired. Most devices are offered in several speed grades with the part number suffix indicating a critical path delay in nanoseconds.

## FOR MORE INFORMATION ON AVAILABLE PART NUMBERS:

All products are not offered with all combinations of package styles, temperature ranges, and screening. The Ordering Information table on the last page of each data sheet indicates explicitly all valid combinations of package, temperature, screening, and performance codes for a given product.

\* Some devices are available in packages of two widths. For devices available in a single width, C, D, K, and P are used.

1-3

Sales Offices 12

| VIDEO IMA |                                               |       |

|-----------|-----------------------------------------------|-------|

| LF2242    | 12/16-bit Half-Band Digital Filter            |       |

| LF2246    | 11 x 10-bit Image Filter                      |       |

| LF2247    | 11 x 10-bit Image Filter with Coefficient RAM |       |

| LF2249    | 12 x 12-bit Digital Mixer                     |       |

| LF2250    | 12 x 10-bit Matrix Multiplier                 |       |

| LF2272    | Colorspace Converter/Corrector (3 x 12-bits)  |       |

| LF43168   | Dual 8-Tap FIR Filter                         |       |

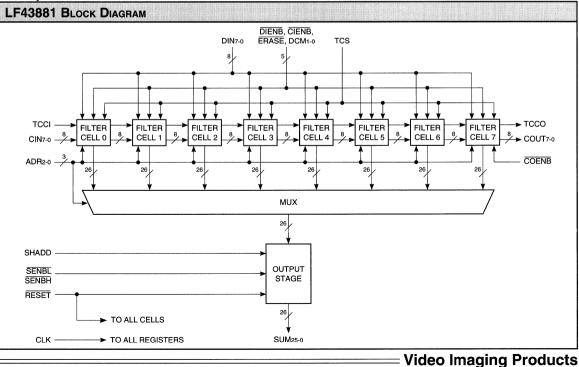

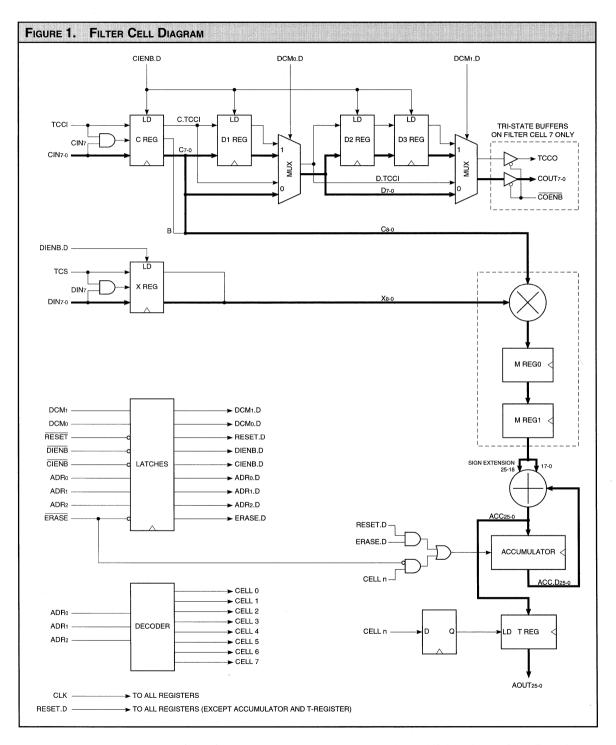

| LF43881   | 8 x 8-bit Digital Filter                      |       |

| LF43891   | 9 x 9-bit Digital Filter                      |       |

| LF48212   | Alpha Mixer                                   |       |

| LF48410   | 1024 x 24-bit Video Histogrammer              |       |

| LF48908   | Two Dimensional Convolver                     |       |

| LF9501    | 1K Programmable Line Buffer                   |       |

| LF9502    | 2K Programmable Line Buffer                   | 2-153 |

|           |                                               |       |

2

-

# FEATURES

- 40 MHz Clock Rate

- □ Passband (0 to  $0.22f_S$ ) Ripple:  $\pm 0.02 \text{ dB}$

- □ Stopband  $(0.28f_{\rm S} \text{ to } 0.5f_{\rm S})$ Rejection: 59.4 dB

- User-Selectable 2:1 Decimation or 1:2 Interpolation

- 12-bit Two's Complement Input and 16-bit Output with User-Selectable Rounding to 9 through 16 Bits

- User-Selectable Two's Complement or Inverted Offset Binary Output Formats

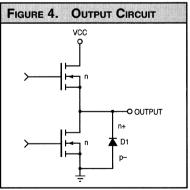

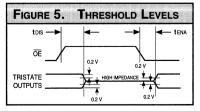

- □ Three-State Outputs

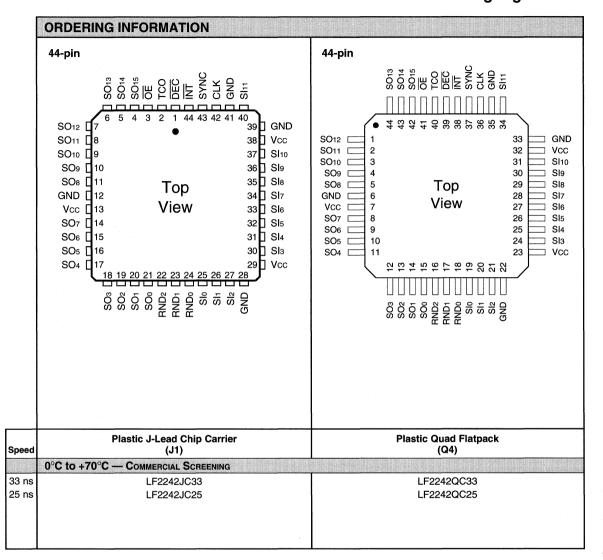

- □ Replaces TRW/Raytheon TMC2242

- □ Package Styles Available:

- 44-pin Plastic LCC, J-Lead

- 44-pin Plastic Quad Flatpack

## DESCRIPTION

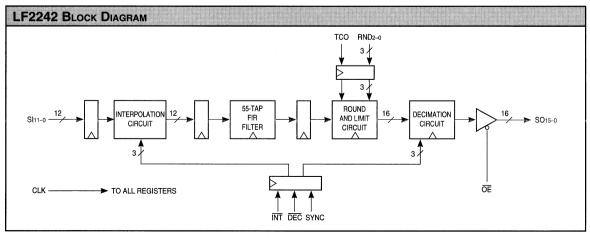

The LF2242 is a linear-phase, halfband (low pass) interpolating/ decimating digital filter that, unlike intricate analog filters, requires no tuning. The LF2242 can also significantly reduce the complexity of traditional analog anti-aliasing prefilters without compromising the signal bandwidth or attenuation. This can be achieved by using the LF2242 as a decimating post-filter with an A/D converter and by sampling the signal at twice the rate needed. Likewise, by using the LF2242 as an interpolating pre-filter with a D/A converter, the corresponding analog reconstruction post-filter circuitry can be simplified.

The coefficients of the LF2242 are fixed, and the only user programming required is the selection of the mode (interpolate, decimate, or passthrough) and rounding. The asynchronous three-state output enable control simplifies interfacing to a bus.

Data can be input into the LF2242 at a rate of up to 40 million samples per second. Within the 40 MHz I/O limit, the output sample rate can be one-half, equal to, or two times the input

sample rate. Once data is clocked in, the 55-value output response begins after 6 clock cycles and ends after 60 clock cycles. The pipeline latency from the input of an impulse response to its corresponding output peak is 33 clock cycles.

The output data may be in either two's complement format or inverted offset binary format. To avoid truncation errors, the output data is always internally rounded before it is latched into the output register. Rounding is user-selectable, and the output data can be rounded from 16 bit values down to 9 bit values.

DC gain of the LF2242 is 1.0015 (0.0126 dB) in pass-through and decimate modes and 0.5007 (-3.004 dB) in interpolate mode. Passband ripple does not exceed  $\pm 0.02$  dB from 0 to  $0.22f_{\rm S}$  with stopband attenuation greater than 59.4 dB from  $0.28f_{\rm S}$  to  $0.5f_{\rm S}$  (Nyquist frequency). The response of the filter is -6 dB at  $0.25f_{\rm S}$ . Full compliance with CCIR Recommendation 601 (-12 dB at  $0.25f_{\rm S}$ ) can be achieved by cascading two devices serially.

## **Video Imaging Products**

#### FREQUENCY RESPONSE OF FILTER FIGURE 1. 0 -10 -20 -30 GAIN (dB) -40 -50 -60 -70 -80 0.1fs $0.5f_{S}$ 0 0.2fs 0.3fs 0.4fs FREQUENCY (NORMALIZED)

## SIGNAL DEFINITIONS

#### Power

Vcc and GND

+5 V power supply. All pins must be connected.

#### Clock

CLK — Master Clock

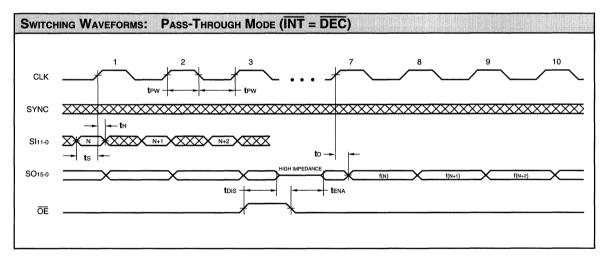

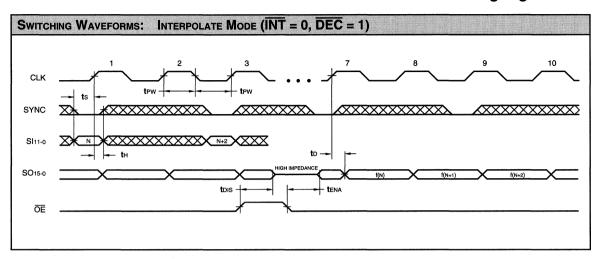

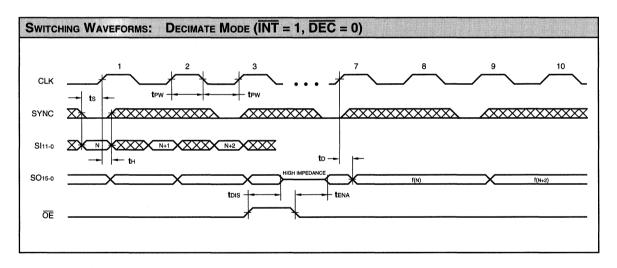

The rising edge of CLK strobes all registers. All timing specifications are referenced to the rising edge of CLK.

#### SYNC — Synchronization Control

Incoming data is synchronized by holding SYNC HIGH on CLKN, and then by bringing SYNC LOW on CLKN+1 with the first word of input data. SYNC is held LOW until resynchronization is desired, or it can be toggled at half the clock rate. For interpolation ( $\overline{INT}$  = LOW), input data should be presented at the first rising edge of CLK for which SYNC is LOW and then at every alternate rising edge of CLK thereafter. SYNC is inactive if  $\overline{DEC}$  and  $\overline{INT}$  are equal (pass-through mode).

#### Inputs

SI11-0 - Data Input

12-bit two's complement data input port. Data is latched into the register on the rising edge of CLK. The LSB is SI0 (Figure 2).

#### Outputs

#### SO15-0 Data Output

The current 16-bit result is available on the SO15-0 outputs. The LF2242's limiter ensures that a valid full-scale (7FFF positive or 8000 negative) output will be generated in the event of an internal overflow. The LSB is SO0 (Figure 2).

## Controls

#### INT — Interpolation Control

When INT is LOW and DEC is HIGH (Table 1), the device internally forces every other incoming data sample to zero. This effectively halves the input data rate and the output amplitude.

#### $\overline{DEC}$ — Decimation Control

When DEC is LOW and INT is HIGH (Table 1), the output register is strobed on every other rising edge of CLK (driven at half the clock rate), decimating the output data stream.

| TABLE 1. MODE SELECTION |     |               |  |  |

|-------------------------|-----|---------------|--|--|

| ĪNT                     | DEC | MODE          |  |  |

| 0                       | 0   | Pass-through* |  |  |

| 0                       | 1   | Interpolate   |  |  |

| 1                       | 0   | Decimate      |  |  |

| 1                       | 1   | Pass-through* |  |  |

\*Input and output registers run at full clock rate

06/27/95-LDS.2242-C

FIGURE 2. INPUT AND OUTPUT FORMATS **Two's Complement Input Format** 11 10 9 8 🗰 3 2 1 0 -2° 2<sup>-1</sup> 2<sup>-2</sup> 2<sup>-3</sup> 2-8 2-9 2-10 2-11 (Sign) Two's Complement Output Format (TCO = 1, Non-interpolate) 15 14 13 12 🗰 3 2 1 0 -20 2-1 2-2 2-3 2-12 2-13 2-14 2-15 (Sign) Two's Complement Output Format (TCO = 1, Interpolate) (Sign) Inverted Offset Binary Output Format (TCO = 0, Non-interpolate) 15 14 13 12 🗰 3 2 1 0 2° 2-1 2-2 2-3 2-12 2-13 2-14 2-15 (Sign) Inverted Offset Binary Output Format (TCO = 0, Interpolate) 15 14 13 12 🗰 3 2 1 0 2-11 2-12 2-13 2-14 2<sup>1</sup> 2<sup>0</sup> 2<sup>-1</sup> 2<sup>-2</sup>

#### TABLE 2. **ROUNDING FORMAT** RND2-0 **SO**15 SO14 **SO**13 **SO**12 SO<sub>8</sub> **SO**7 SO<sub>6</sub> SO<sub>5</sub> SO<sub>4</sub> SO<sub>3</sub> SO<sub>2</sub> SO1 SO<sub>0</sub> ... х х х 000 х Х ... Х Х х х х Х х R 001 Х Х Х Х х х Х Х х х х R 0 ... 010 х Х Х х х х х Х х х R ... 0 0 х х х 011 Х х х х Х R ... Х 0 0 0 100 х х Х Х х х х х R 0 ... 0 0 0 х х 101 х х х х х R ... n n n 0 0 х 110 х Х Х ... х х R 0 0 0 0 0 0 х 111 х Х х х R 0 0 0 0 0 0 0 ...

'R' indicates the half-LSB rounded bit (effective LSB position)

(Sign)

#### RND2-0 — Rounding Control

The rounding control inputs set the position of the effective LSB of the output data by adding a rounding bit to the internal bit position that is one below that specified by RND2-0. All bits below the effective LSB position are subsequently zeroed (Table 2).

#### TCO — Two's Complement Format Control

The TCO input determines the format of the output data. When TCO is HIGH, the output data is presented in two's complement format. When TCO is LOW, the data is in inverted offset binary format (all output bits are inverted except the MSB — the MSB is unchanged).

#### $\overline{OE}$ — Output Enable

When the  $\overline{OE}$  signal is LOW, the current data in the output register is available on the SO15-0 pins. When  $\overline{OE}$  is HIGH, the outputs are in a high-impedance state.

## MAXIMUM RATINGS Above which useful life may be impaired (Notes 1, 2, 3, 8)

| Storage temperature                       | –65°C to +150°C       |

|-------------------------------------------|-----------------------|

| Operating ambient temperature             |                       |

| Vcc supply voltage with respect to ground |                       |

| Input signal with respect to ground       | –0.5 V to Vcc + 0.5 V |

| Signal applied to high impedance output   |                       |

| Output current into low outputs           |                       |

| Latchup current                           |                       |

|                                           |                       |

OPERATING CONDITIONS

To meet specified electrical and switching characteristics

Mode

Temperature Range (Ambient)

Supply Voltage

Active Operation, Commercial

0°C to +70°C

4.75 V ≤ Vcc ≤ 5.25 V

| ELECTRIC     | ELECTRICAL CHARACTERISTICS Over Operating Conditions (Note 4) |                                          |     |     |     |      |  |

|--------------|---------------------------------------------------------------|------------------------------------------|-----|-----|-----|------|--|

| Symbol       | Parameter                                                     | Test Condition                           | Min | Тур | Max | Unit |  |

| <b>V</b> он  | Output High Voltage                                           | Vcc = Min., IOH = -2.0 mA                | 2.4 |     |     | V    |  |

| VOL          | Output Low Voltage                                            | <b>V</b> CC = Min., <b>I</b> OL = 4.0 mA |     |     | 0.4 | V    |  |

| <b>V</b> iH  | Input High Voltage                                            |                                          | 2.0 |     | Vcc | v    |  |

| <b>V</b> IL  | Input Low Voltage                                             | (Note 3)                                 | 0.0 |     | 0.8 | V    |  |

| lix          | Input Current                                                 | Ground $\leq$ VIN $\leq$ VCC (Note 12)   |     | _   | ±10 | μA   |  |

| loz          | Output Leakage Current                                        | (Note 12)                                |     |     | ±40 | μA   |  |

| ICC1         | Vcc Current, Dynamic                                          | (Notes 5, 6)                             |     |     | 140 | mA   |  |

| ICC2         | Vcc Current, Quiescent                                        | (Note 7)                                 |     |     | 10  | mA   |  |

| CIN          | Input Capacitance                                             | <b>T</b> A = 25°C, f = 1 MHz             |     |     | 10  | pF   |  |

| <b>C</b> OUT | Output Capacitance                                            | <b>T</b> A = 25°C, f = 1 MHz             |     |     | 10  | pF   |  |

06/27/95-LDS.2242-C

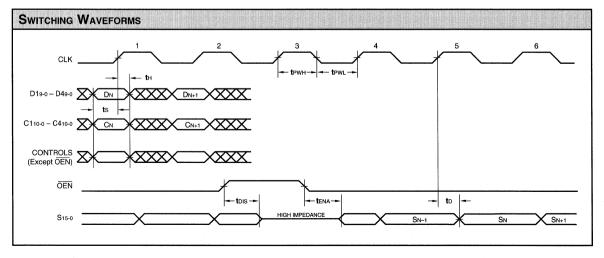

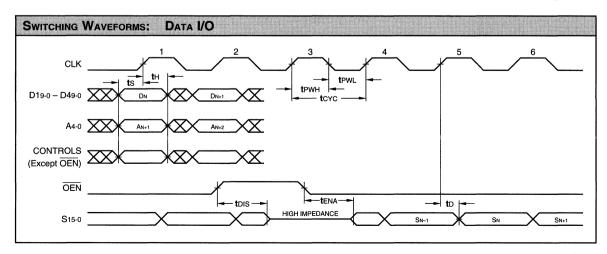

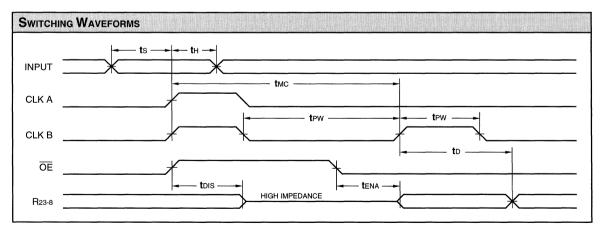

## **SWITCHING CHARACTERISTICS**

| Сомме        | Commercial Operating Range (0°C to +70°C) Notes 9, 10 (ns) |     |        |     |     |  |

|--------------|------------------------------------------------------------|-----|--------|-----|-----|--|

|              |                                                            |     | LF2242 |     |     |  |

|              |                                                            | 3   | 33     |     | 25  |  |

| Symbol       | Parameter                                                  | Min | Max    | Min | Max |  |

| tcyc         | Cycle Time                                                 | 33  |        | 25  |     |  |

| <b>t</b> PW  | Clock Pulse Width                                          | 10  |        | 10  |     |  |

| ts           | Input Setup Time                                           | 10  |        | 8   |     |  |

| tн           | Input Hold Time                                            | 0   |        | 0   |     |  |

| tD           | Output Delay                                               |     | 20     |     | 16  |  |

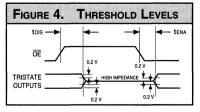

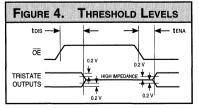

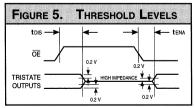

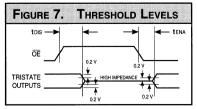

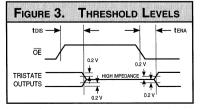

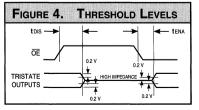

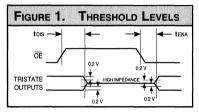

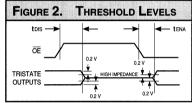

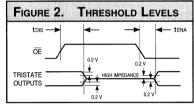

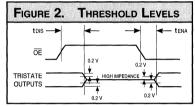

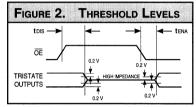

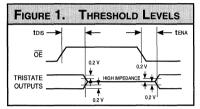

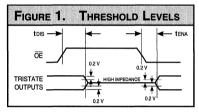

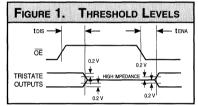

| tDIS         | Three-State Output Disable Delay (Note 11)                 |     | 15     |     | 15  |  |

| <b>t</b> ENA | Three-State Output Enable Delay (Note 11)                  |     | 15     |     | 15  |  |

= Video Imaging Products

——— Video Imaging Products

## NOTES

DEVICES INCORPORATED

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.

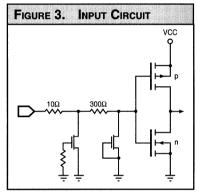

2. The products described by this specification include internal circuitry designed to protect the chip from damaging substrate injection currents and accumulations of static charge. Nevertheless, conventional precautions should be observed during storage, handling, and use of these circuits in order to avoid exposure to excessive electrical stress values.

3. This device provides hard clamping of transient undershoot and overshoot. Input levels below ground or above VCC will be clamped beginning at -0.6 V and VCC + 0.6 V. The device can withstand indefinite operation with inputs in the range of -0.5 V to +7.0 V. Device operation will not be adversely affected, however, input current levels will be well in excess of 100 mA.

4. Actual test conditions may vary from those designated but operation is guaranteed as specified.

5. Supply current for a given application can be accurately approximated by:

# $\frac{NCV^2F}{4}$

where

N = total number of device outputs

- C = capacitive load per output

- V = supply voltage

- F = clock frequency

6. Tested with all outputs changing every cycle and no load, at a 20 MHz clock rate.

7. Tested with all inputs within 0.1 V of VCC or Ground, no load.

8. These parameters are guaranteed but not 100% tested.

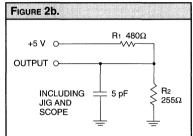

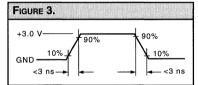

9. AC specifications are tested with input transition times less than 3 ns, output reference levels of 1.5 V (except tENA/tDIS test), and input levels of nominally 0 to 3.0 V. Output loading may be a resistive divider which provides for specified IOH and IOL at an output voltage of VOH min and VOL max respectively. Alternatively, a diode bridge with upper and lower current sources of IOH and IOL respectively, and a balancing voltage of 1.5 V may be used. Parasitic capacitance is 30 pF minimum, and may be distributed. For tENABLE and tDISABLE measurements, the load current is increased to 10 mA to reduce the RC delay component of the measurement.

This device has high-speed outputs capable of large instantaneous current pulses and fast turn-on/turn-off times. As a result, care must be exercised in the testing of this device. The following measures are recommended:

a. A 0.1  $\mu$ F ceramic capacitor should be installed between VCC and Ground leads as close to the Device Under Test (DUT) as possible. Similar capacitors should be installed between device VCC and the tester common, and device ground and tester common.

b. Ground and VCC supply planes must be brought directly to the DUT socket or contactor fingers.

c. Input voltages should be adjusted to compensate for inductive ground and VCC noise to maintain required DUT input levels relative to the DUT ground pin.

10. Each parameter is shown as a minimum or maximum value. Input requirements are specified from the point of view of the external system driving the chip. Setup time, for example, is specified as a minimum since the external system must supply at least that much time to meet the worst-case requirements of all parts. Responses from the internal circuitry are specified from the point of view of the device. Output delay, for example, is specified as a maximum since worst-case operation of any device always provides data within that time.

11. Transition is measured ±200 mV from steady-state voltage with specified loading.

12. These parameters are only tested at the high temperature extreme, which is the worst case for leakage current.

= Video Imaging Products

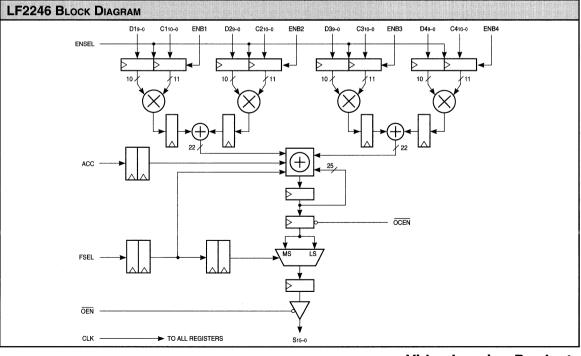

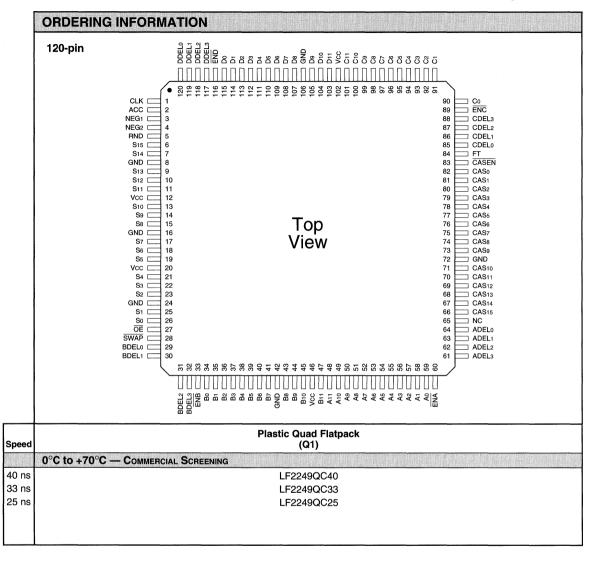

## FEATURES

- 66 MHz Data and Coefficient Input and Computation Rate

- □ Four 11 x 10-bit Multipliers with Individual Data and Coefficient Inputs and a 25-bit Accumulator

- User-Selectable Fractional or Integer Two's Complement Data Formats

- Fully Registered, Pipelined Architecture

- Input and Output Data Registers, with User-Configurable Enables

- □ Three-State Outputs

- Fully TTL Compatible

- Ideally Suited for Image Processing and Filtering Applications

- Replaces TRW/Raytheon TMC2246

- □ Package Styles Available:

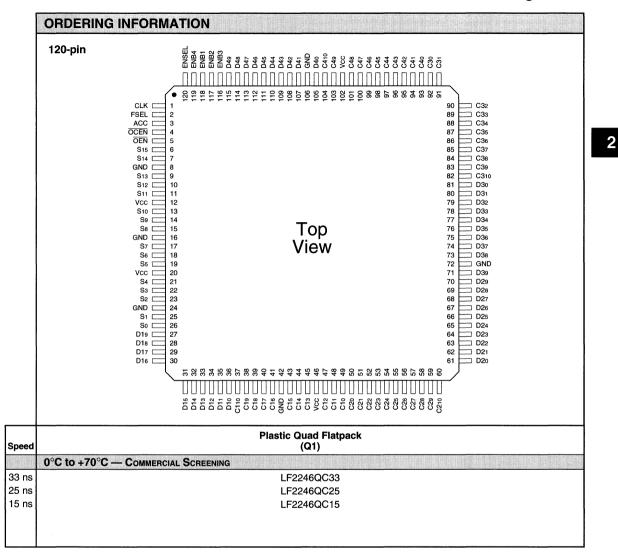

- 120-pin Pin Grid Array

- 120-pin Plastic Quad Flatpack

## DESCRIPTION

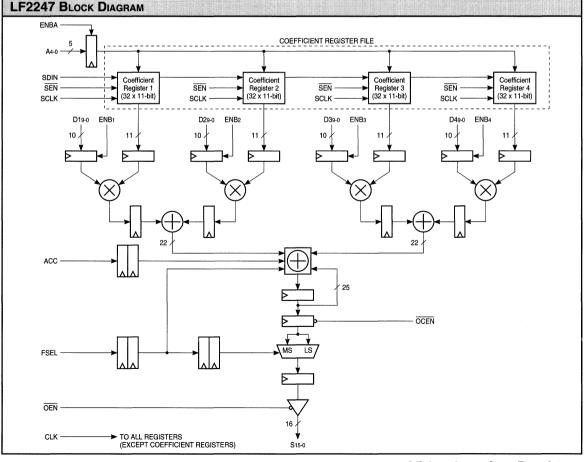

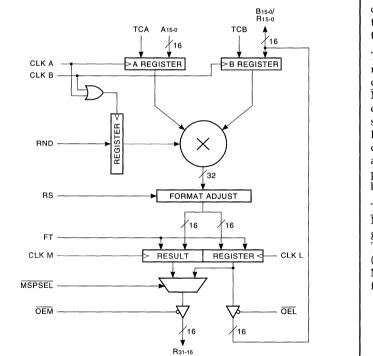

The **LF2246** consists of an array of four 11 x 10-bit registered multipliers followed by a summer and a 25-bit accumulator. All multiplier inputs are user accessible and can be updated every clock cycle with either fractional or integer two's complement data. The pipelined architecture has fully registered input and output ports and an asynchronous three-state output enable control to simplify the design of complex systems. The pipeline latency for all inputs is five clock cycles.

Storage for mixing and filtering coefficients can be accomplished by holding the data or coefficient inputs over multiple clock cycles. A 25-bit accumulator path allows cumulative word growth which may be internally rounded to 16 bits. Output data is updated every clock cycle and may be held under user control. All inputs, outputs, and controls are registered on the rising edge of clock, except for  $\overline{\text{OEN}}$ . The LF2246 operates at a clock rate of 66 MHz over the full temperature and supply voltage ranges.

The LF2246 is applicable for performing pixel interpolation in image manipulation and filtering applications. The LF2246 can perform a bilinear interpolation of an image (4pixel kernels) at real-time video rates when used with an image resampling sequencer. Larger kernels or more complex functions can be realized by utilizing multiple devices.

Unrestricted access to all data and coefficient input ports provides the LF2246 with considerable flexibility in applications such as digital filters, adaptive FIR filters, mixers, and other similar systems requiring high-speed processing.

## Video Imaging Products

2

# <u>LOGIC</u>

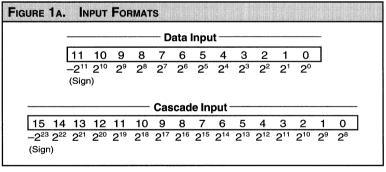

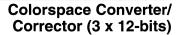

| FIGURE 1A. INPUT FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                          |

| Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Coefficient                                                                                                                                                                                                              |

| Fractional Two's Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | mplement (FSEL = 0)                                                                                                                                                                                                      |

| 987 🗰 210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10 9 8 🗰 2 1 0                                                                                                                                                                                                           |

| $-2^{0} 2^{-1} 2^{-2} 2^{-7} 2^{-8} 2^{-9}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | $-2^{1} 2^{0} 2^{-1} 2^{-7} 2^{-8} 2^{-9}$                                                                                                                                                                               |

| (Sign)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Sign)                                                                                                                                                                                                                   |

| Integer Two's Com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | plement (FSEL = 1)                                                                                                                                                                                                       |

| 9 8 7 🔶 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10 9 8 🗰 2 1 0                                                                                                                                                                                                           |

| $-2^9 2^8 2^7 2^2 2^1 2^0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $-2^{10} 2^9 2^8 2^2 2^1 2^0$                                                                                                                                                                                            |

| (Sign)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | (Sign)                                                                                                                                                                                                                   |

| (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | (Sign)                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                          |

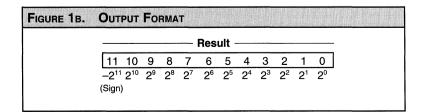

| FIGURE 1B. OUTPUT FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | (וער)                                                                                                                                                                                                                    |

| FIGURE 1B. OUTPUT FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                          |

| FIGURE 1B. OUTPUT FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mplement (FSEL = 0)                                                                                                                                                                                                      |

| FIGURE 1B. OUTPUT FORMATS<br>————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mplement (FSEL = 0)<br>7 6 5 4 3 2 1 0                                                                                                                                                                                   |

| FIGURE 1B. OUTPUT FORMATS<br>————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mplement (FSEL = 0)                                                                                                                                                                                                      |

| Figure 1b.         Output Formats           —         Fractional Two's Co           15         14         13         12         11         10         9         8           -2 <sup>6</sup> 2 <sup>5</sup> 2 <sup>4</sup> 2 <sup>3</sup> 2 <sup>2</sup> 2 <sup>1</sup> 2 <sup>0</sup> 2 <sup>-1</sup> (Sign)         ( | T       6       5       4       3       2       1       0         2 <sup>-2</sup> 2 <sup>-3</sup> 2 <sup>-4</sup> 2 <sup>-5</sup> 2 <sup>-6</sup> 2 <sup>-7</sup> 2 <sup>-8</sup> 2 <sup>-9</sup>                        |

| FIGURE 1B. OUTPUT FORMATS<br>————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | mplement (FSEL = 0)         7       6       5       4       3       2       1       0 $2^{-2}$ $2^{-3}$ $2^{-4}$ $2^{-5}$ $2^{-6}$ $2^{-7}$ $2^{-8}$ $2^{-9}$ mplement (FSEL = 1)                                        |

| FIGURE 1B.         OUTPUT FORMATS           —         Fractional Two's Co           15         14         13         12         11         10         9         8           -2 <sup>6</sup> 2 <sup>5</sup> 2 <sup>4</sup> 2 <sup>3</sup> 2 <sup>2</sup> 2 <sup>1</sup> 2 <sup>0</sup> 2 <sup>-1</sup> (Sign)          Integer Two's Corr          15         14         13         12         11         10         9         8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | T       6       5       4       3       2       1       0         7       6       5       4       3       2       1       0 $2^{-2}$ $2^{-3}$ $2^{-4}$ $2^{-5}$ $2^{-6}$ $2^{-7}$ $2^{-8}$ $2^{-9}$ applement (FSEL = 1) |

| FIGURE 1B. OUTPUT FORMATS<br>————————————————————————————————————                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | T       6       5       4       3       2       1       0         7       6       5       4       3       2       1       0 $2^{-2}$ $2^{-3}$ $2^{-4}$ $2^{-5}$ $2^{-6}$ $2^{-7}$ $2^{-8}$ $2^{-9}$ applement (FSEL = 1) |

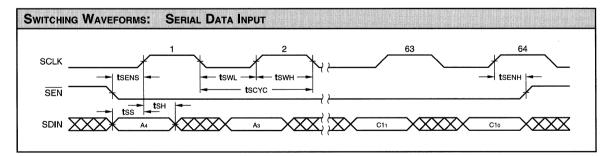

#### SIGNAL DEFINITIONS

#### Power

Vcc and GND

+5 V power supply. All pins must be connected.

#### Clock

CLK — Master Clock

The rising edge of CLK strobes all enabled registers. All timing specifications are referenced to the rising edge of CLK.

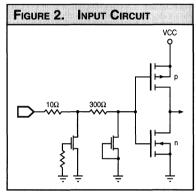

#### Inputs

D19-0-D49-0 — Data Input

D1–D4 are 10-bit data input registers. The LSB is DN0 (Figure 1a).

C110-0-C410-0 — Coefficient Input

C1–C4 are 11-bit coefficient input registers. The LSB is CN0 (Figure 1a).

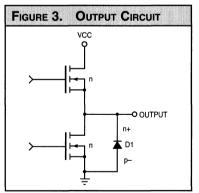

#### Outputs

S15-0 — Data Output

The current 16-bit result is available on the S15-0 outputs (Figure 1b).

#### Controls

ENB1–ENB4 — Input Enable

The ENBN (N = 1, 2, 3, or 4) input allows either or both the DN and CN registers to be updated on each clock cycle. When ENBN is LOW, registers DN and CN are both strobed by the next rising edge of CLK. When ENBN is HIGH and ENSEL is LOW, register DN is strobed while register CN is held. If both ENBN and ENSEL are HIGH, register DN is held, and register CN is strobed (Table 1).

#### ENSEL — Enable Select

The ENSEL input in conjunction with the individual input enables ENB1– ENB4 determines whether the data or the coefficient input registers will be held on the next rising edge of CLK (Table 1).

#### **OEN** — Output Enable

When the  $\overline{\text{OEN}}$  signal is LOW, the current data in the output register is available on the S15-0 pins. When  $\overline{\text{OEN}}$  is HIGH, the outputs are in a high-impedance state.

## 11 x 10-bit Image Filter

| TABLE 1      | REGISTER CONTROL |                        |

|--------------|------------------|------------------------|

| ENB1-4 ENSEL |                  | INPUT REGISTER<br>HELD |

| 1            | 1                | Data 'N'               |

| 1            | 0                | Coefficient 'N'        |

| 0            | x                | None                   |

X = "Don't Care" 'N' = 1, 2, 3, or 4

#### $\overline{OCEN}$ — Clock Enable

When OCEN is LOW, data in the premux register (accumulator output) is loaded into the output register on the next rising edge of CLK. When OCEN is HIGH, data in the pre-mux register is held preventing the output register's contents from changing (if FSEL does not change). Accumulation continues internally as long as ACC is HIGH, despite the state of OCEN.

#### FSEL — Format Select

When the FSEL input is LOW, the data input during the current clock cycle is assumed to be in fractional two's complement format, and the upper 16 bits of the accumulator are presented at the output. Rounding of the accumulator result to 16 bits is performed if the accumulator control input ACC is LOW. When FSEL is HIGH, the data input is assumed to be in integer two's complement format, and the lower 16 bits of the accumulator are presented at the output. No rounding is performed when FSEL is HIGH.

#### ACC — Accumulator Control

The ACC input determines whether internal accumulation is performed on the data input during the current clock cycle. If ACC is LOW, no accumulation is performed, the prior accumulated sum is cleared, and the current sum of products is output. If FSEL is also LOW, one-half LSB rounding to 16 bits is performed on the result. This allows summations without propagating roundoff errors. When ACC is HIGH, the emerging product is added to the sum of the previous products, without additional rounding.

## = Video Imaging Products

DEVICES INCORPORATED

LOI

## 11 x 10-bit Image Filter

|  |  |  |  | ve n |  |  |  |  |  |  |  |  |

|--|--|--|--|------|--|--|--|--|--|--|--|--|

|  |  |  |  |      |  |  |  |  |  |  |  |  |

|  |  |  |  |      |  |  |  |  |  |  |  |  |

| Storage temperature                       | –65°C to +150°C       |

|-------------------------------------------|-----------------------|

| Operating ambient temperature             | –55°C to +125°C       |

| Vcc supply voltage with respect to ground |                       |

| Input signal with respect to ground       | –0.5 V to Vcc + 0.5 V |

| Signal applied to high impedance output   | 0.5 V to Vcc + 0.5 V  |

| Output current into low outputs           |                       |

| Latchup current                           |                       |

| <b>OPERATING CONDITIONS</b> To meet specified electrical and switching characteristics |                                                             |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Temperature Range (Ambient)                                                            | Supply Voltage                                              |  |  |  |  |  |  |  |  |  |

| 0°C to +70°C                                                                           | $4.75 \text{ V} \leq \text{V}\text{cc} \leq 5.25 \text{ V}$ |  |  |  |  |  |  |  |  |  |

| –55°C to +125°C                                                                        | $4.50 \text{ V} \leq \text{V}\text{cc} \leq 5.50 \text{ V}$ |  |  |  |  |  |  |  |  |  |

|                                                                                        | Temperature Range (Ambient)<br>0°C to +70°C                 |  |  |  |  |  |  |  |  |  |

| ELECTRIC    | CAL CHARACTERISTICS OVE | r Operating Conditions (Note 4)                        |     |     |     | dan ber |

|-------------|-------------------------|--------------------------------------------------------|-----|-----|-----|---------|

| Symbol      | Parameter               | Test Condition                                         | Min | Тур | Max | Unit    |

| <b>V</b> он | Output High Voltage     | Vcc = Min., Iон = -2.0 mA                              | 2.4 |     |     | v       |

| VOL         | Output Low Voltage      | <b>V</b> CC = Min., <b>I</b> OL = 4.0 mA               |     |     | 0.4 | v       |

| <b>V</b> ін | Input High Voltage      |                                                        | 2.0 |     | Vcc | v       |

| Vi∟         | Input Low Voltage       | (Note 3)                                               | 0.0 |     | 0.8 | v       |

| lix         | Input Current           | Ground $\leq$ <b>V</b> IN $\leq$ <b>V</b> CC (Note 12) |     |     | ±10 | μA      |

| loz         | Output Leakage Current  | (Note 12)                                              |     |     | ±40 | μA      |

| ICC1        | Vcc Current, Dynamic    | (Notes 5, 6)                                           |     |     | 100 | mA      |

| ICC2        | Vcc Current, Quiescent  | (Note 7)                                               |     |     | 6   | mA      |

| CIN         | Input Capacitance       | <b>T</b> <sub>A</sub> = 25°C, f = 1 MHz                |     |     | 10  | pF      |

| COUT        | Output Capacitance      | <b>T</b> <sub>A</sub> = 25°C, f = 1 MHz                |     |     | 10  | pF      |

DEVICES INCORPORATED

# LF2246

11 x 10-bit Image Filter

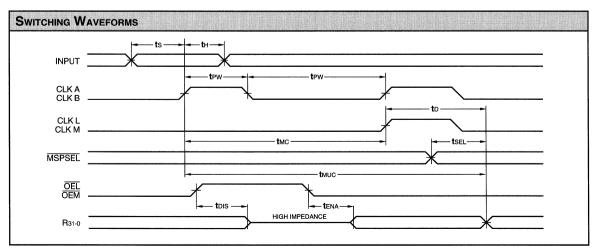

## SWITCHING CHARACTERISTICS

| Сомме        | RCIAL OPERATING RANGE (0°C to +70°C) Note  | s 9, 10 (ns) |     |     |     |     |     |  |  |  |  |  |

|--------------|--------------------------------------------|--------------|-----|-----|-----|-----|-----|--|--|--|--|--|

|              |                                            | LF2246       |     |     |     |     |     |  |  |  |  |  |

|              |                                            | 3            | 13  | 2   | 25  | 15  |     |  |  |  |  |  |

| Symbol       | Parameter                                  | Min          | Max | Min | Max | Min | Max |  |  |  |  |  |

| <b>t</b> CYC | Cycle Time                                 | 33           |     | 25  |     | 15  |     |  |  |  |  |  |

| <b>t</b> PWL | Clock Pulse Width Low                      | 15           |     | 10  |     | 7   |     |  |  |  |  |  |

| <b>t</b> PWH | Clock Pulse Width High                     | 10           |     | 10  |     | 7   |     |  |  |  |  |  |

| ts           | Input Setup Time                           | 10           |     | 8   |     | 5   |     |  |  |  |  |  |

| tн           | Input Hold Time                            | 0            |     | 0   |     | 0   |     |  |  |  |  |  |

| tD           | Output Delay                               |              | 15  |     | 13  |     | 10  |  |  |  |  |  |

| tDIS         | Three-State Output Disable Delay (Note 11) |              | 15  |     | 15  |     | 15  |  |  |  |  |  |

| <b>t</b> ENA | Three-State Output Enable Delay (Note 11)  |              | 15  |     | 15  |     | 15  |  |  |  |  |  |

| MILITAP      | Y OPERATING RANGE (-55°C to +125°C) Notes 9, 1 | 0 (ns)  |     |     |     |  |  |  |  |  |

|--------------|------------------------------------------------|---------|-----|-----|-----|--|--|--|--|--|

|              |                                                | LF2246– |     |     |     |  |  |  |  |  |

|              |                                                | 3       | 3   | 25  |     |  |  |  |  |  |

| Symbol       | Parameter                                      | Min     | Max | Min | Max |  |  |  |  |  |

| tCYC         | Cycle Time                                     | 33      |     | 25  |     |  |  |  |  |  |

| <b>t</b> PWL | Clock Pulse Width Low                          | 15      |     | 10  |     |  |  |  |  |  |

| <b>t</b> PWH | Clock Pulse Width High                         | 10      |     | 10  |     |  |  |  |  |  |

| ts           | Input Setup Time                               | 10      |     | 8   |     |  |  |  |  |  |

| tн           | Input Hold Time                                | 0       |     | 0   |     |  |  |  |  |  |

| tD           | Output Delay                                   |         | 15  |     | 13  |  |  |  |  |  |

| tDIS         | Three-State Output Disable Delay (Note 11)     |         | 15  |     | 15  |  |  |  |  |  |

| <b>t</b> ENA | Three-State Output Enable Delay (Note 11)      |         | 15  |     | 15  |  |  |  |  |  |

## = Video Imaging Products

## LF2246

# <u>LOGIC</u>

DEVICES INCORPORATED

## NOTES

1. Maximum Ratings indicate stress specifications only. Functional operation of these products at values beyond those indicated in the Operating Conditions table is not implied. Exposure to maximum rating conditions for extended periods may affect reliability.