## LA-1725

# THE MANIAC

## LA-1725

DCT 26 1954

# THE MANIAC

#### **PREFACE**

The construction program on the MANIAC was started in the summer of 1949 and the computer was completely tested in March, 1952. The group of engineers is under the direction of J. Richardson and consisted, at various times, of W. Orvedahl, E. Klein, H. Demuth, T. Gardiner, H. Parsons, R. Merwin, and J. Breese. In addition, V. Gafke and J. Caulfield provided considerable assistance. Since its completion, solutions to many numerical problems have been computed.

There are several phases to the solution of a problem by an electronic computer. First, there is the formulation of the problem itself by the mathematician or theoretical physicist. Second, this is followed by the detailed preparation of the problem by the programmer for the specific computer. Finally, there is the actual running of the problem on the computer. The present work is primarily an attempt to discuss in some detail the last two stages.

The volume consists of six chapters. Chapter I, Introduction, describes some of the general features of the computer and defines the field of activity associated with it. The treatment is intentionally brief. The remaining chapters are devoted to an elaboration of the salient points.

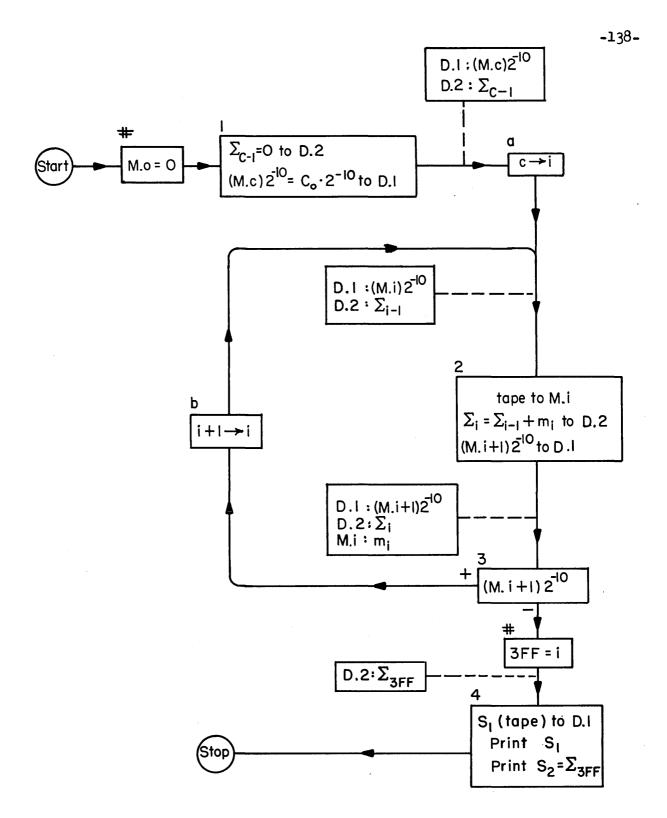

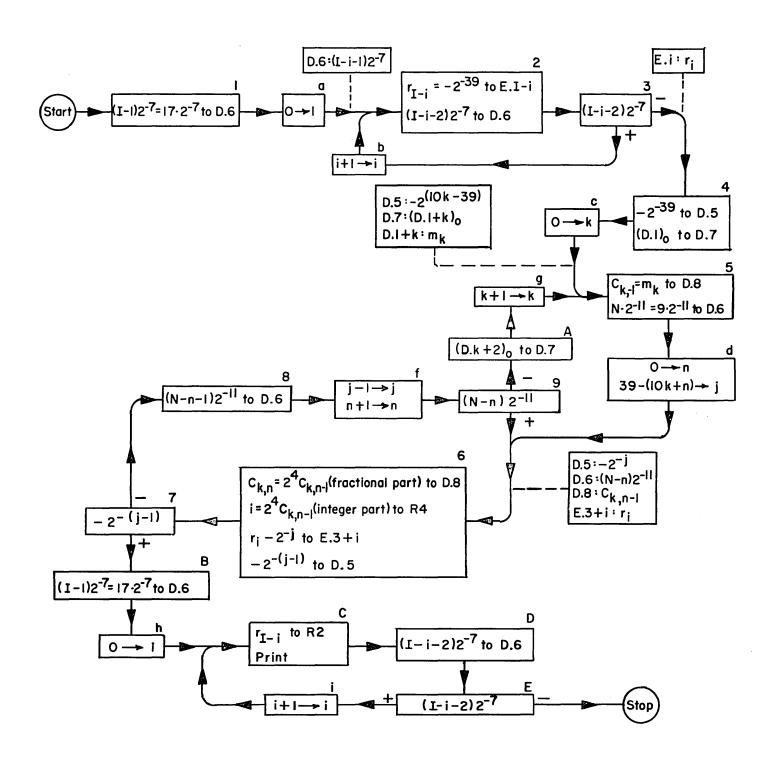

Chapter II, Coding and Flow Diagrams, is the "raison d'etre" of the opus. Beginning with some elementary problems, it gradually takes the reader through a coding preparation of some complex exercises. The elements of a flow diagram are discussed.

Chapter III, Binary Arithmetic, discusses the various arithmetic operations in terms of the binary system. By the time the reader finishes this part, it is hoped he will regard the binary system as the "natural" one for arithmetic.

Chapter IV, The Computer, is concerned with a simplified discussion of the various components. The objective here is that some knowledge of the engineering side of a computer is very useful to personnel running problems on it. Aiding in the detection of malfunctions and in the localization of them, the programmer helps the engineer in maintaining high performance of the computer.

Chapter V, Descriptive Coding and Subroutines, describes the methods of descriptive coding the the use of the computer itself to aid the programmer in the preparation of problem codes. The discussion of subroutines finds a natural place here.

Chapter VI, Operating Procedures, essentially summarizes some of the material of the earlier sections and describes systematically the steps involved in automatic computational processes, including "which buttons on the computer to press when".

Finally, an Appendix is included. It contains some optional and, we hope, useful material.

John B. Jackson N. Metropolis

Los Alamos, New Mexico December 15, 1951.

Acknowledgements: To Mary Boswell, whose patience was excelled only by Job, for typing (and re-typing) the manuscript; to Jean Cornell for converting our sketches into neat drawings and figures; and to all members of the MANIAC group who deluged us with criticisms, especially Mark Wells.

J. B. J.

N. M.

Los Alamos, New Mexico December 15, 1951.

Revised: July 16, 1954

#### I. INTRODUCTION

We shall give first a brief description of the general features and characteristics of the computer which has been constructed here.

- (i) It is a general purpose computer in contradistinction to a special purpose type. Its design engenders adequate flexibility to handle a wide variety of mathematical problems. The special purpose type may be much simpler in design and more direct in its application to a particular type of problem, but it has its obvious limitations. We do not discuss it further.

- (ii) It is a <u>digital</u>, rather than an analogue, computer. Computers have been built which use various analogy devices that correspond to a continuous variable representation. In such analogy computers, numerical information is expressed as measurements of some physical quantity. Among other reasons, it may be mentioned that accuracy requirements argue for the digital type.

- (iii) It is <u>electronic</u> (vacuum tubes) in character, as opposed to electro-mechanical (relays). Although both methods are sufficiently reliable, the former is many times faster. For the majority of problems, where the number of operations involved is at least in the hundred thousand range, the difference in speed is quite serious.

The four basic arithmetical operations performed are addition, subtraction, multiplication and division. In principle, one might conceive of a simple computer that does only subtraction, and effects the others by repeated application of that fundamental operation.

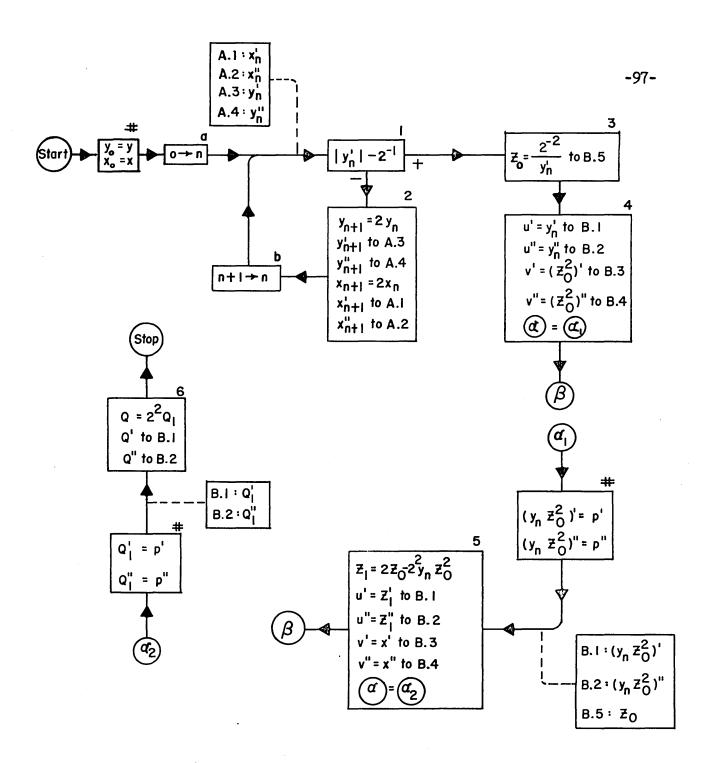

This is not very practical. On the other hand, one might have argued for including other operations in the basic list; e.g., square rooting, as indeed the ENIAC has included. It appears, however, that the frequency of occurrence of any of these does not warrant the added complication in equipment, especially since these more complicated operations can be effected by rather simple iterative procedures based on the four fundamental operations.

Besides these four arithmetical processes, there are included a few operations which are of a purely logical character, but first,

#### Some Remarks on Arithmetic

The handling of numerical quantities is done in a <u>digital</u> fashion. The binary system is used for the representation of numbers rather than the conventional decimal system. Everyone knows that in the latter system a number is expressed as a sum of powers of ten with individual cofactors 0 to 9; e.g.,

$$47.23 = 4.10^{1} + 7.10^{0} + 2.10^{-1} + 3.10^{-2}$$

In a similar fashion a number may be expressed in the binary system by powers of two with co-factors either 0 or 1; e.g.,

$$101.01 = 1.2^{2} + 0.2^{1} + 1.2^{0} + 0.2^{-1} + 1.2^{-2}$$

As in the decimal system, the binary point separates the terms with positive exponents from those with negative exponents. The standard capacity for handling numbers in the present computer is 39 numerical bigits preceded by a sign bigit. (The word bigit is defined as binary digit.) There is sufficient flexibility to permit rather easy treatment of those cases requiring higher precision.

For the various arithmetical operations in the computer, it is assumed that the binary point lies immediately to the left of the first numerical bigit, so that all numbers lie in the range

$$-1 < x < 1$$

.

It may appear at first that this restriction places a considerable additional burden on the preparation of a problem for the computer. Actually, however, it is quite a simple matter to scale numbers to the appropriate size beforehand, such that the result of any operation does not exceed the allowed range. In those instances where it is not possible to provide appropriate scaling factors in advance, one does have recourse to procedures which adjust the sizes of numbers—the so-called floating point routines.

As mentioned above, the first bigit on the left is used to indicate the sign of a number. One possible convention that might be used would be to say that bigit  $\underline{0}$  in that location indicates a positive quantity and that a  $\underline{1}$  is to be interpreted as a negative sign. However, it is more convenient to do something different in the case of negative numbers.

In the computer, a negative number  $\underline{x}$  is represented by its complement c with respect to 2, namely

$$c = 2 - |x|$$

Since

|x| < 1,

c will be in the range

1 < c < 2

so that the "sign" bigit will be  $\underline{1}$  in every case of complementation. For positive numbers it will always be 0. For example, suppose

x = -.101110101....011;

then

c = 1.010001010....101

is its representation in the computer. One observes that a very simple method for obtaining the complement of a number with respect 2, is to "reflect" the number, that is, to replace 0 with 1 and conversely, then to add 1 in the extreme right place. Electronically, interchanging O and 1 is easily done. As discussed in detail in later sections, a "flip-flop", or "toggle", is an electronic device which has two stable states; it is essentially a twin triode (a standard type of vacuum tube); either one side is in a conducting state (and its tube elements have one set of definite voltages) with the other side non-conducting (cut-off, and its corresponding elements have another set of voltages) or the opposite situation obtains. It is a symmetrical situation. Normally one examines the voltage level at some particular point of the circuit, say the grid voltage of one of the triodes, and assigns one voltage to the bigit 0 and the other to 1. To obtain the complement of a number in a series of such flip-flops, one would merely examine the opposite symmetrical point of the circuit of each flip-flop; since, if a given flip-flop is in a state corresponding to a l, the other side of the flip-flop would have a voltage level at the corresponding point identified as a 0. Additional circuitry is required to insert a 1 in the extreme right-hand position.

The notion of complement numbers is a very useful one. Subtraction of two numbers can be replaced by addition. This is convenient since the same electronic circuitry designed to effect addition suffices for the subtraction process. Instead of performing d = (a-b) by direct subtraction techniques, one may add to a the complement of b. That this yields the correct difference can be seen from the following:

Assume a, b > 0.

$$a + (2-b) = 2 + (a-b) = 10. + (a-b)$$

in binary form. If a > b, and since both <u>a</u> and <u>b</u> have absolute magnitudes less than unity, the difference (a-b) is positive and less than unity. The co-factor <u>l</u> of  $2^l$  does not appear in the computer, the capacity of the computer has been exceeded and that bigit is lost. The <u>O</u> co-factor of  $2^O$  does of course appear, and indicates that the difference (a-b) is positive. In the event a < b, our answer would be:

$$1 < d = 2 - (b-a) < 2$$

which is precisely the desired form for a negative difference, namely the complement with respect to 2. Here the co-factor of  $2^{\circ}$  is appropriately a <u>1</u>. The cases where <u>a</u> and/or <u>b</u> are negative are left as exercises for the curious students.

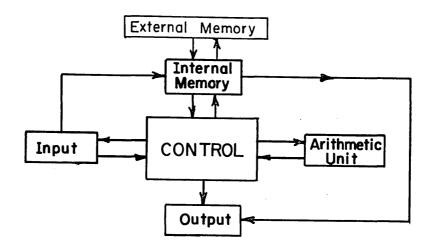

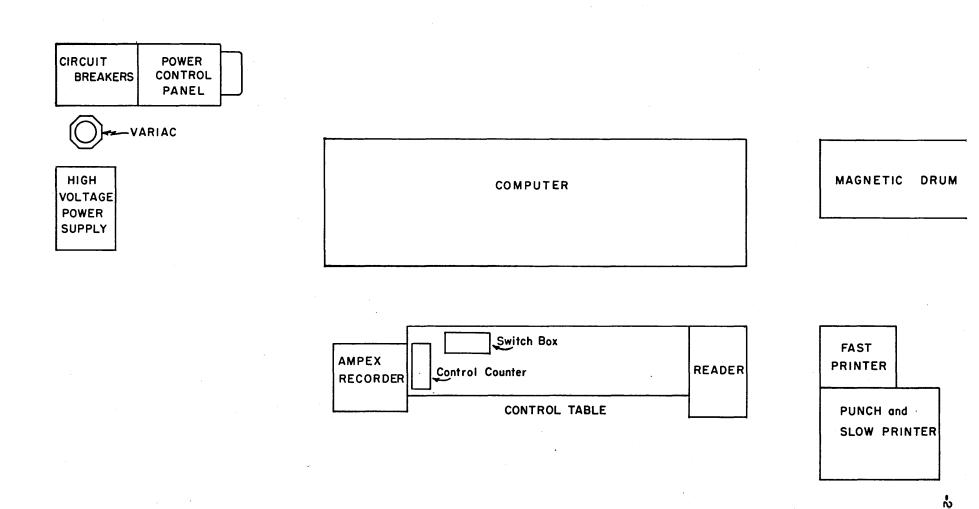

#### Principal Components

Although the computer functions as an entity, it is convenient to speak of its various components. These are:

- (i) arithmetic unit

- (ii) memory

- (iii) input-output

- (iv) control

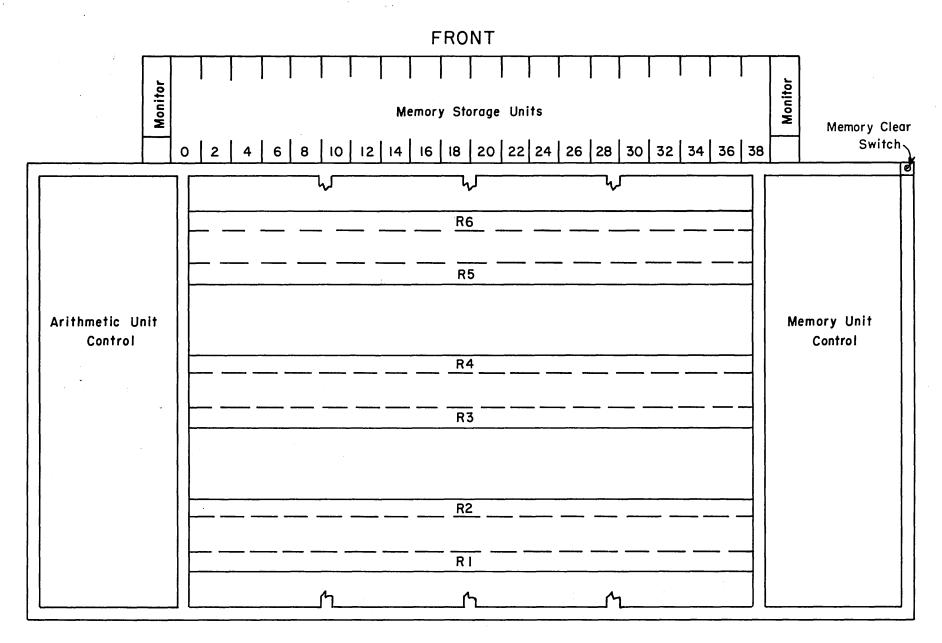

#### Arithmetic Unit

The arithmetic unit performs the operations of addition, subtraction, multiplication and division in binary fashion. It is also concerned with such auxiliary operations as shifting of a number to the left or right. Finally, it is associated with certain logical operations.

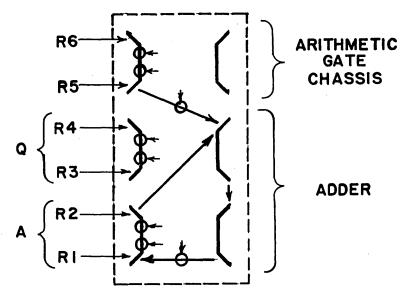

In appearance the arithmetic unit is similar to the one in Princeton. A parallepiped structure of channel aluminum has six panels on each of its two long sides. The outer panels in each case are reserved for control chassis, the middle four are used for the arithmetic unit proper. Three horizontal rows of arithmetical chassis are located on one of the two principal sides. Each chassis contains two <u>registers</u>. The various registers are designated Rl, R2,...R6, starting with the lowest. A register is the residence, or temporary storage, of one of the numerical

factors in an arithmetical operation. In each such operation three factors occur, so that at first it might be supposed that three registers would suffice. However, the requirement of shifting in multiplication and division necessitates two more. These considerations account for the first five registers; the last, R6, is used exclusively in association with the control and does not participate in any of the basic arithmetical operations, although physically it is located within the arithmetic unit. R1 is the associated register for shifting a number in R2, a principal register. Physically, the pair forms a chassis. Similarly, R3 is associated with the principal register, R4. R5 is a non-shifting register with respect to arithmetic operations.

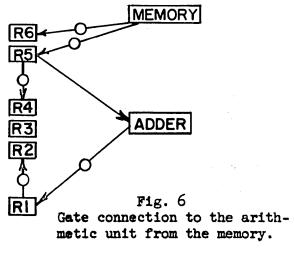

Before discussing the four basic arithmetical operations, we digress to consider the manner in which a number in one of the two principal registers is shifted. To begin with, a register is an ensemble of 40 "flip-flops", or "toggles", and as mentioned earlier, each flip-flop has two stable states. One of these states represents the binary digit <u>0</u> and the other the binary digit <u>1</u>. The set of flip-flops may then be used to represent a 39-bigit number and its sign.

There exists a variety of methods for electronically transferring information contained in one set of toggles to another. For example, suppose that a given toggle contains a <u>l</u> and it is desired to transfer this information to a second toggle. By means of an interconnecting "gate" tube, it is possible (as a result of a voltage change on the gate tube) to set the receiving toggle to a <u>l</u>, irrespective of its previous state. Another scheme is to have first set the receiving toggle, say to <u>O</u>, as a separate operation. When the appropriate voltage change is applied to the gate tube, the receiving toggle is set to a <u>l</u>, otherwise it remains appropriately unchanged. This method is actually the simpler of the two and is the one used. In common parlance we say the receiving flip-flops are "cleared" to <u>O</u>'s and <u>l</u>'s are "gated in". Clearly, <u>O</u>'s and <u>l</u>'s could be interchanged in the preceding statement and provide an alternative scheme.

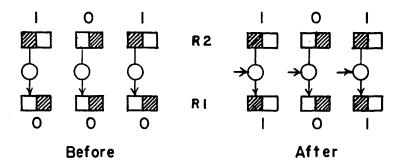

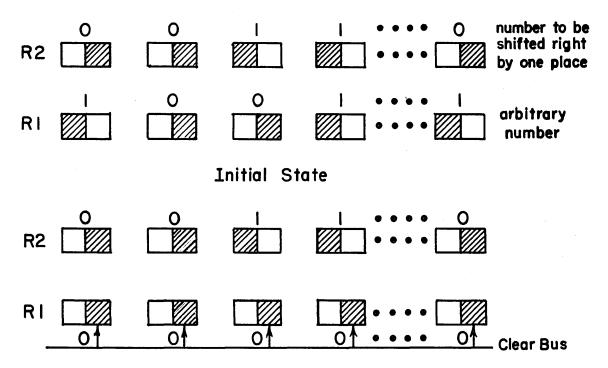

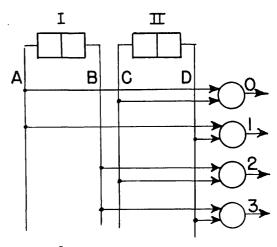

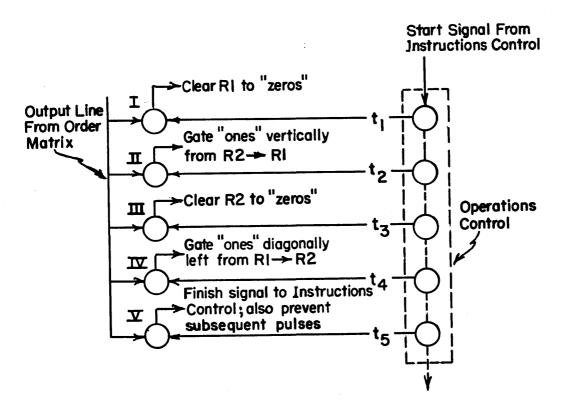

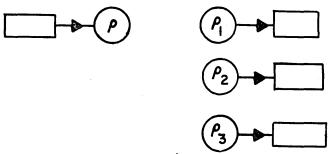

A flip-flop may be symbolically represented as a rectangle in the form of two squares; the shading of one square may be said to correspond to a 0, the shading of the other to a 1. A gate tube is indicated by a circle.

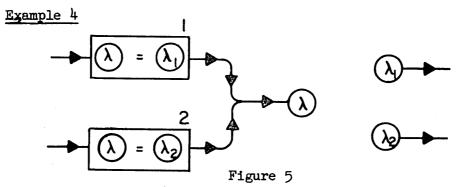

There is a set of gates which connects the flip-flops of R2 to the corresponding ones of R1. These may be shown diagrammatically.

Rl has been previously cleared to 0's. The information in R2 is 101. When an appropriate voltage change is applied to the gate tubes, the first flip-flop of Rl will change its state to represent a 1, the second remains unchanged, and the third behaves like the first. Rl will then have received the information 101.

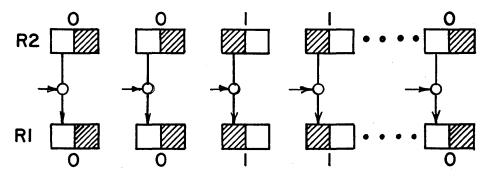

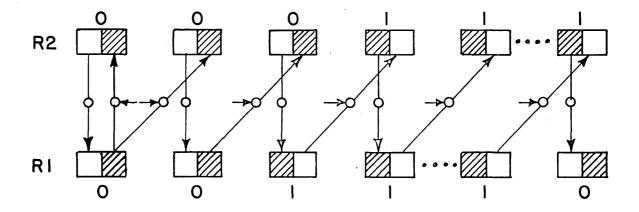

There is a second set of gates which connects the flip-flops of Rl with the flip-flops of R2 displaced one to the left.

R2 is cleared to 0's. When these gates are opened, the information in R1 is transferred to R2 displaced once to the left. Thus, by these sequences of operations, a number originally in R2 is shifted one place to the left.

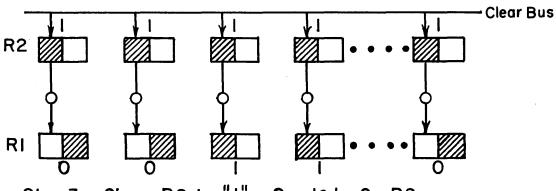

Finally, there is a set of "diagonally-right" gates to provide for a shift to the right. Repeated application of the sequence of operations results in a shift by <u>n</u> places. It perhaps should be mentioned that these three sets of gates are unilateral in action and represent all of the interconnections between Rl and R2.

The four basic arithmetical operations are done in terms of simple additions, with shifts where required. Subtraction of a number a is performed by the addition of its complement. Multiplication is done by the detection of the successive bigits of the multiplier, beginning with the rightmost bigit. If the bigit is a 1, an addition of the multiplicand to the partial product is performed followed by a shift of the partial product one place to the right. A O multiplier bigit merely shifts the partial product to the right by one, and the next multiplier bigit is examined. For division, the so-called "non-restoring" scheme is used. The complement of the divisor is added to the partial remainder if the signs of the divisor and partial remainder agree; if the signs disagree, the divisor is added directly. A O is indicated for the corresponding quotient bigit in the first case, and a 1 for the latter. Strictly speaking, -1 and not 0 is the appropriate bigit. But -1 is indeed very inconvenient to represent in the computer. As von Neumann first pointed out, the pseudo-quotient obtained in this way is very simply related to the true quotient. We shall go into details later.

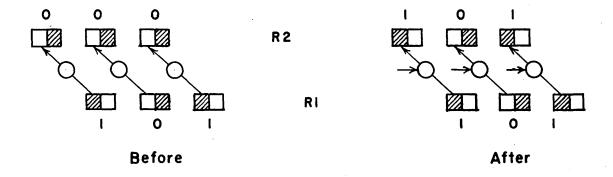

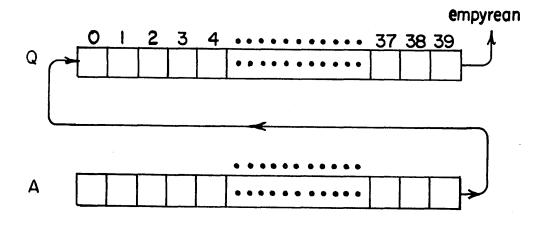

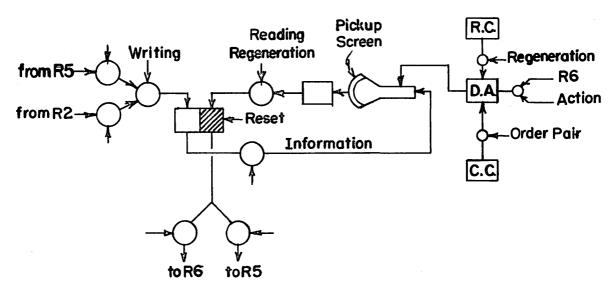

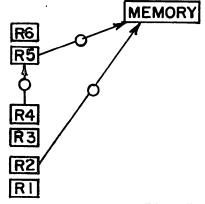

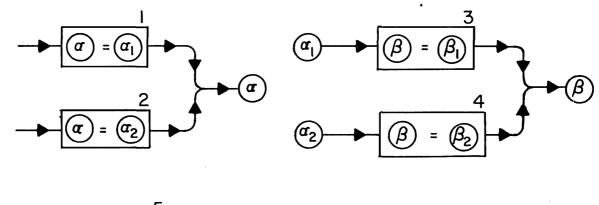

The adder proper is physically located on the side opposite the registers, and consists of two rows of chassis. One of the two inputs is directly from the register R2. The second input is from R5. Here, however, a choice is made between the number itself or its complement, corresponding to the operation of addition or subtraction. The output of the adder is transferred by means of a set of gates to R1. R2 is then cleared and the sum transferred from R1 to R2. Symbolically,

To recapitulate, the addition process (or subtraction) involves adding to the number in R2 the number (or its complement) in R5. The sum appears finally in R2. The fact that the sum replaces one of the terms is very convenient for the multiplication and division processes, where the sum is the partial product or the partial remainder, respectively. The multiplicand or the divisor resides accordingly in R5.

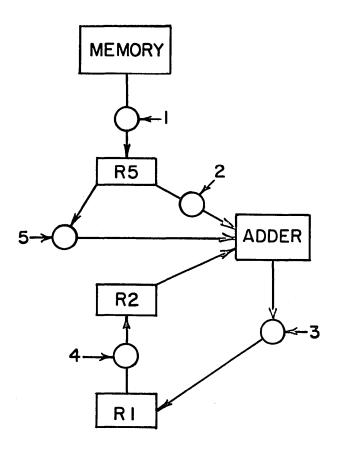

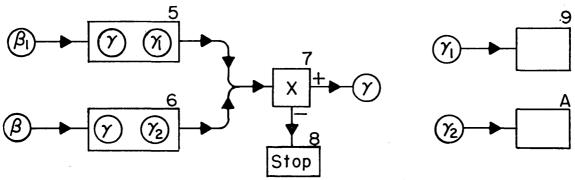

In the multiplication process the multiplier factor is in R4 and the multiplicand is in R5. R2 is cleared initially. The 39th flip-flop of R4 is examined. If it is a 1, an addition is ordered and the first partial product is formed in R2. (In this first step, the trivial sum of the multiplicand and O's is done.) The multiplier is now shifted one place to the right, thus placing the next digit to be examined in the end flip-flop of R4. Simultaneously, the partial product in R2 is also shifted one place to the right. In the event that the first digit is a O, the addition of course is not done but the shifting in both R2 and R4 does take place. It will be noted that the multiplier factor is gradually disappearing in R4. It is convenient, therefore,

to insert the bigits of the partial product that would otherwise be lost as a result of the right shift in R2, into the leftmost flip-flop of R4. Thus the right half of the complete product appears finally in R4 and the significant portion in R2.

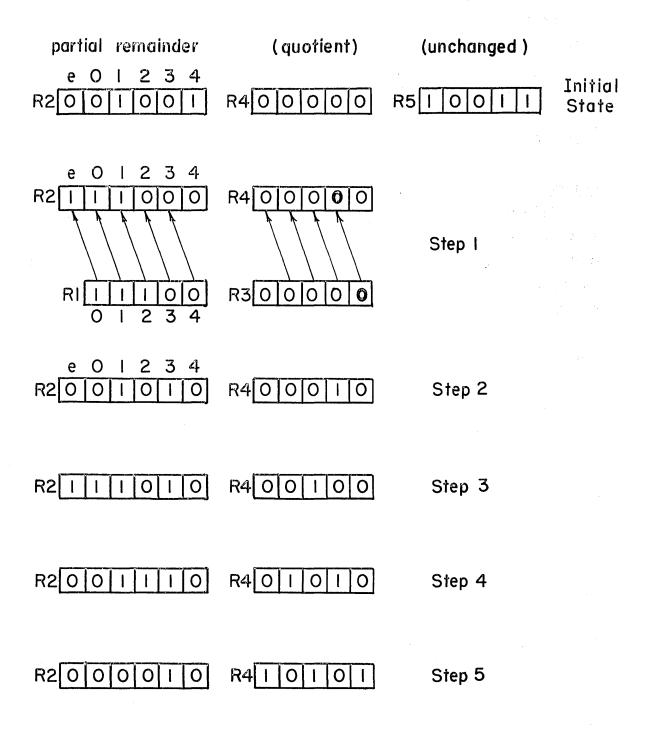

For division, the dividend is in R2 and the divisor in R5. A comparison of signs is made and a direct addition is made for unlike signs; for like signs the complement of the divisor is sent to the adder. Accordingly, a O or a 1 is introduced into the 39th flip-flop of R4. Both R2 and R4 are shifted one place to the left. The sign of the partial remainder is again compared with that of the divisor and the process repeated 39 times. The quotient appears in R4, and the remainder in R2.

The following short table summarizes the above:

| Addition       | a + b = | Sum              |              |

|----------------|---------|------------------|--------------|

| Location       | R2 R5   | R2               |              |

| Subtraction    | a - b = | Difference       |              |

|                | R2 R5   | R2               | ·            |

| Multiplication | a X b = | Product Left + P | roduct Right |

|                | R5 R4   | R2               | R4           |

| Division       | a + b = | Quotient + Rer   | nainder      |

|                | R2 R5   | R4 R             | 2            |

#### Memory

Thus far we have talked of the various arithmetical operations without indicating how the numbers get to the several registers initially, or where the intermediate results are stored. Nor have we said anything about the location of the sequence of orders associated with a problem. The component of the computer associated with this

activity is described as the memory. Clearly, some of its desired functions are:

- (i) to receive and store information from the outside--sequences of instructions as well as initial sets of numbers,

- (ii) to transfer numbers upon instruction to the arithmetic unit,

- (iii) to receive and retain intermediate results of a calculation until needed at some later stage of the calculation,

- (iv) to send instructions as needed to the control,

- (v) to transfer the final results to the output mechanism for external consumption.

We distinguish two levels of memory, internal and external. The internal memory is more intimately related to the arithmetic unit and control. It communicates directly with these two units and provides individual numbers and instructions as needed.

Physically, the internal memory is an ensemble of 40 cathode-ray tubes that act in concert, each tube simultaneously providing one bigit of a 40-bigit number upon instruction. The access time, or total time required to transfer a number from the internal memory to the arithmetic unit, is less than ten micro-seconds. The capacity of the internal memory is 1024 forty-bigit numbers; these may be arbitrarily divided between numbers and instructions.

The location or reference in the internal memory of a particular number or instruction is called its <u>address</u>. In our system of instructions there is, associated with each instruction, a single address that refers to a particular number to be called up and operated upon in the arithmetic unit. An instruction consists therefore of a particular operation specified by a group of bigits, together with an address specified by another set of bigits. It turns out that less than 20 bigits are required for each complete instruction, so that it is convenient to place two instructions in one memory location. We shall amplify these remarks in the discussion of the control.

Normally, 40 bigits are used for the representation of a true number. For those cases where sufficient accuracy is obtained from 20 bigits, including sign, there is sufficient flexibility to store conveniently two 20-bigit numbers in one memory location; separation taking place when needed in the arithmetic unit by shifting.

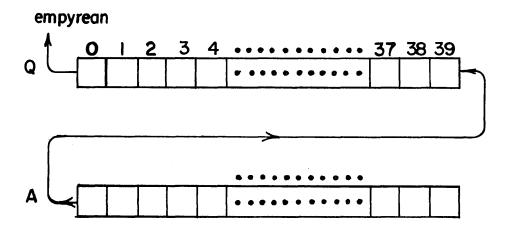

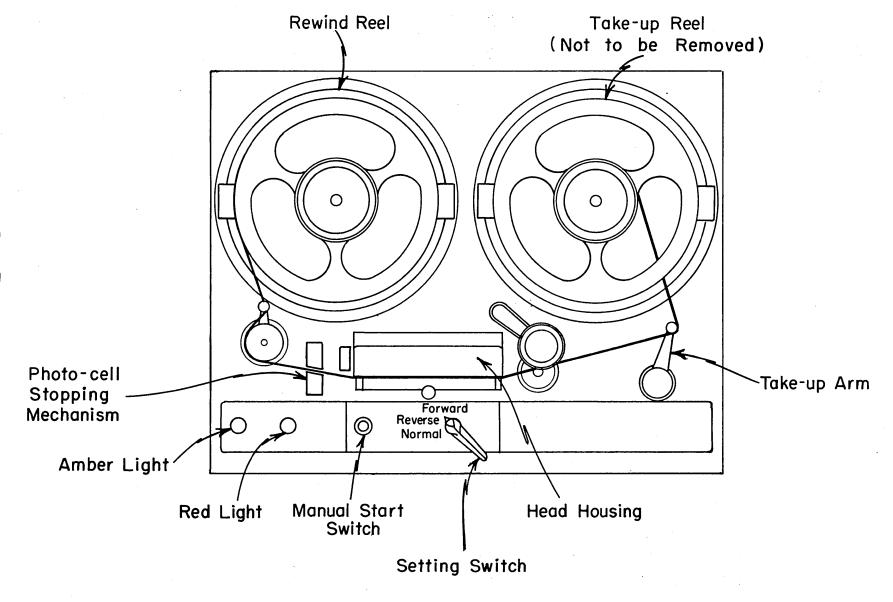

The external memory is a magnetic drum. It communicates only with the internal memory; therefore, when numbers stored on the magnetic drum are to be used in computation, they are first sent into the electrostatic memory and operated upon from there. The drum has a capacity of 10,000 forty-bigit numbers. Numbers are transferred between the external and internal memory in groups of fifty; hence the addressing of numbers on the drum is by groups of fifty rather than as single numbers. Any group of fifty numbers is stored serially along the circumference of the drum. Such a group of storage is called a drum track, and there are 200 such tracks on the drum. The access time for the drum is 85 milliseconds per block of fifty words.

#### Input-Output

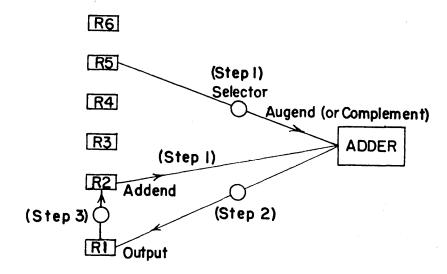

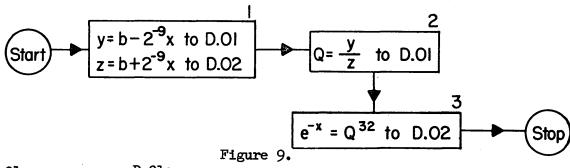

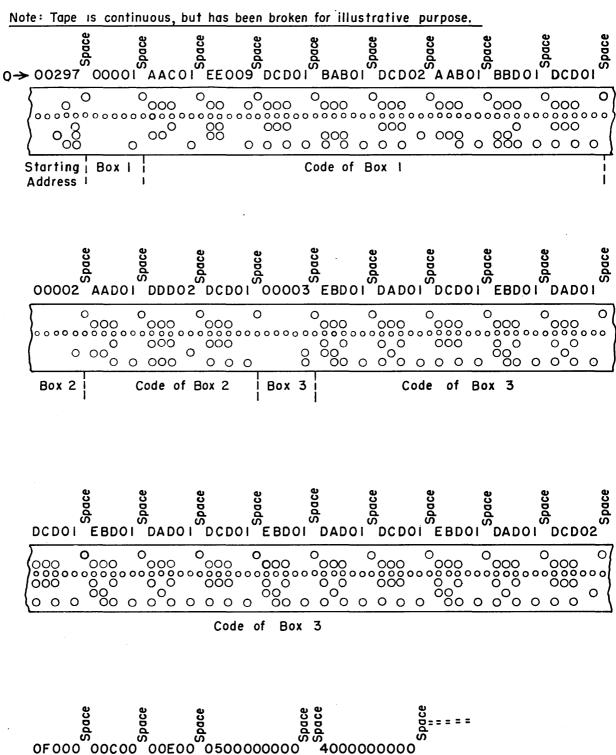

The set of coded symbols corresponding to the sequence of instructions, together with the set of initial numbers and parameters, is first punched on paper tape with the use of a modified Flexowriter. A second tape is then prepared, being punched independently of the first but simultaneously compared with the first; this is merely a checking procedure. The information is then transferred from the verified tape to the internal memory by means of the input device.

The initial set of numbers on the tape is in coded-decimal form; that is, each decimal character is represented by a tetrad of binary digits. For example, the aggregate 1234567890 together with accompanying space symbols would appear on the tape as:

The punched holes correspond to the bigit  $\underline{1}$  and unpunched positions to  $\underline{0}$ . A sequence of such tetrads of binary digits is obviously not

the true binary representation of the corresponding decimal number; e.g.,

decimal number 24

coded decimal 0010 0100

true binary 11000

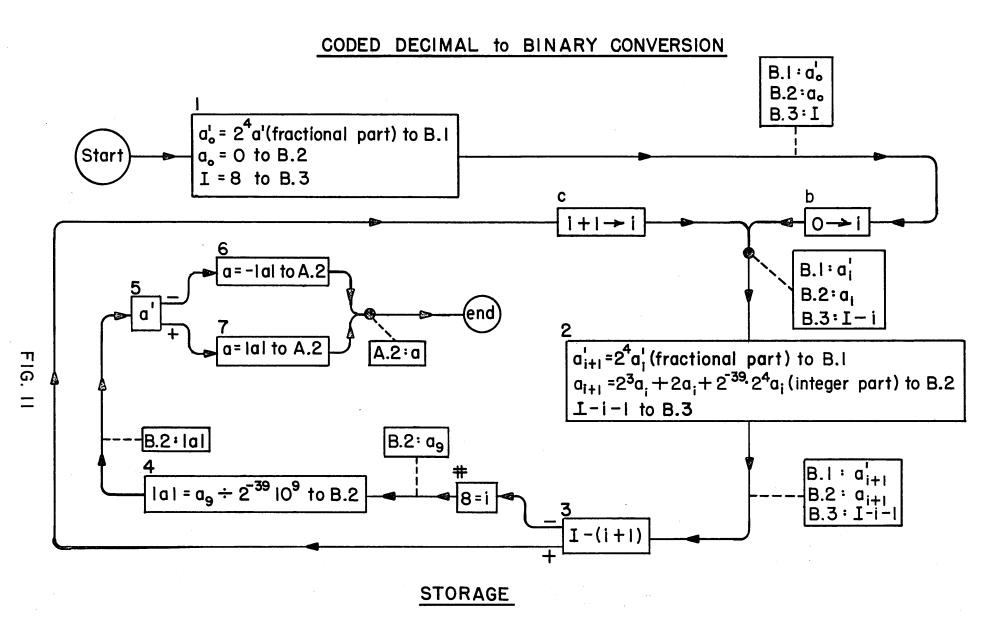

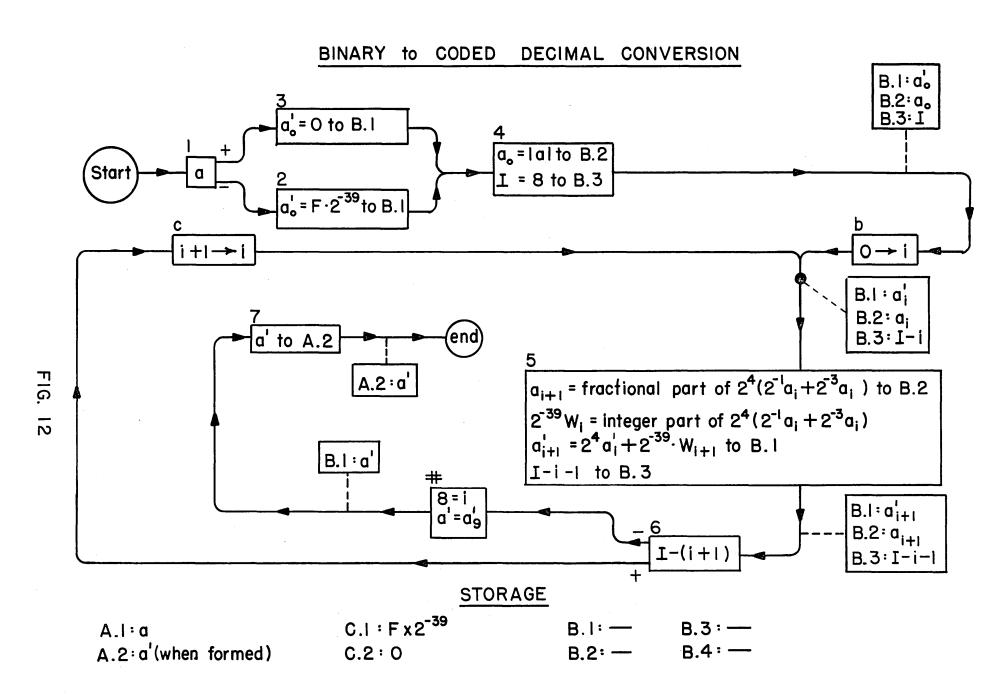

Consequently, it is first necessary to convert the initial set of coded-decimal numbers into true binaries. But this is a quite simple algorithm which the computer can be directed to perform before entering upon the problem proper. The initial set which must thus be converted is usually quite small compared to the number of numbers the computer handles in the course of the problem, so that the time invested for the conversion is relatively negligible. The same remark applies for the conversion from true binary to coded-decimal representation for the output process; it being still desirable to view answers in decimal notation.

When the desired results are properly converted into coded-decimal notation, they may be directed to the output. The output will simultaneously print the results and punch them on teletype tape. This tape is desirable in the event that the answers are to be reintroduced into the computer.

It should be remarked that beginning with the second problem of any given type it will not again be necessary to manual punch the sequence of instructions. The original tape will be adequate. It is only necessary to punch the new initial numbers and parameters. This portion is usually a small fraction of the total. Finally, it should be noted that the casual observer need never be aware of the fact that internally the computer uses the binary representation for numbers.

#### Control

The control may be likened to a central nervous system. Its parts spread out physically over the whole computer. It interconnects the various other components and transfers information from one to the other, as well as directs the operations associated with them individually.

Among its various activities, it must:

- (i) direct the input component to read information from the teletype tape and transfer it to the internal memory,

- (ii) conversely, direct the memory to transfer information to the output tape and printer,

- (iii) effect the basic arithmetic operations,

- (iv) be able to start at some point in a sequence of orders, extract the first order (from the internal memory), interpret and provide pulses and voltage changes to the components concerned so as to execute the particular order, and when finished proceed to the next order.

These activities are specified by a variety of orders.

In the present control scheme, a <u>one-address</u> system is used; that is, associated with each order is an address referring to some memory location which contains the number upon which the particular order operates. For example, there are eight orders that transfer a number from the memory to R2. The eight possibilities arise from the three choices:

- (1) Clear or do not clear R2 before adding number into it.

- (2) Complement or do not complement the number being added to R2.

- (3) Add the number or its magnitude.

These are the addition and subtraction orders. There are two multiplication orders; one rounds off the product to 39 bigits, the other provides a precise 78 bigit product. There is one division order, one order transferring a number from the memory to R4. There are six orders associated with transfers to the memory, a right and left shift, print, read, and stop orders. Finally, there are a few logical orders that involve an interruption of the present sequence of orders and a transfer of control to some other sequence.

Eight bigits are used to designate an order. Twelve more are conveniently available, of which ten are actually used at present, for the address. Thus each order is 20 bigits, and two orders are equivalent in storage to one true number. Word is used to describe a 40-bigit aggregate; this may be either an order pair or a true number. A coder

is provided with the set of symbols that correspond to the various orders. These code symbols are various pairs of the six letters, A,B,...F.

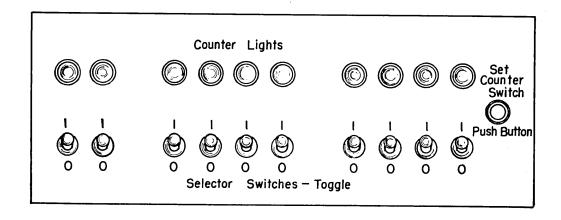

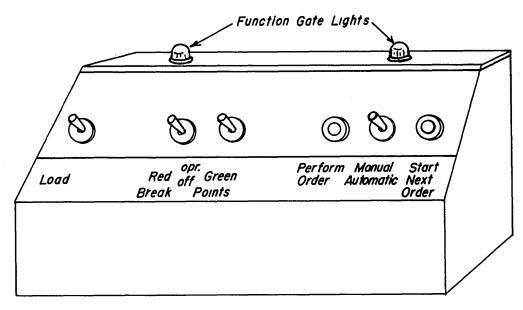

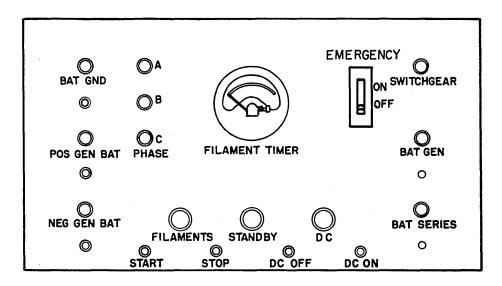

Let us now attempt a summary by describing the various steps in machine operation. Assume a tape has been prepared with instructions and initial set of numbers. First the tape is fed into the input. The tetrads are read into R5 in serial fashion. Ten tetrads, corresponding to either a true number or to two orders fill R5. A signal is automatically provided that causes the contents of R5 to be transferred to the first memory location; the second set of ten tetrads is read into R5, etc. When the complete tape has been read into the memory, the computer is ready to do business. The operator presses a "start" button. The contents of the first memory location or first word go to R6; these are the first two orders. The first one is examined and executed, then the second. The next word goes to R6 and the sequence continues. Flexibility exists which enables the sequence to be interrupted at some point and the control transferred to some other point in the sequence. For example, it may be desired to repeat a sequence a fixed number of times before proceeding further, as in some iteration scheme. This is conveniently handled by the logical orders. In fact, it is possible to have the number of repetitions be dependent on the fulfillment of some condition in the problem, so that the number of repetitions varies from case to case. Finally, the desired numerical quantities can be reconverted from binary to binary-decimal form, and printed.

#### Problem Preparation and Operating Techniques

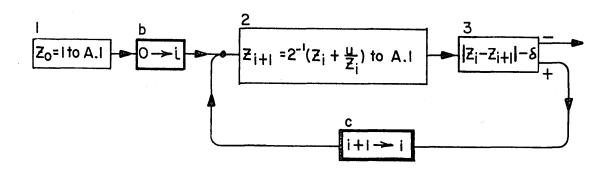

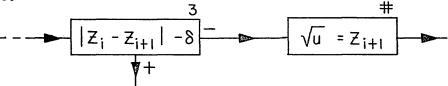

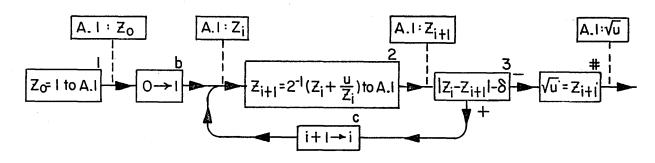

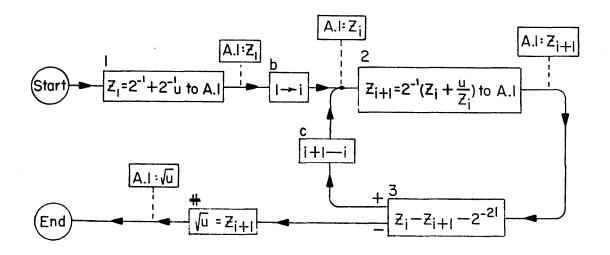

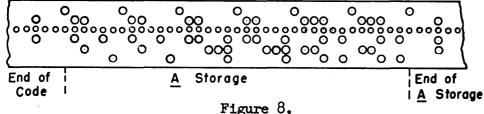

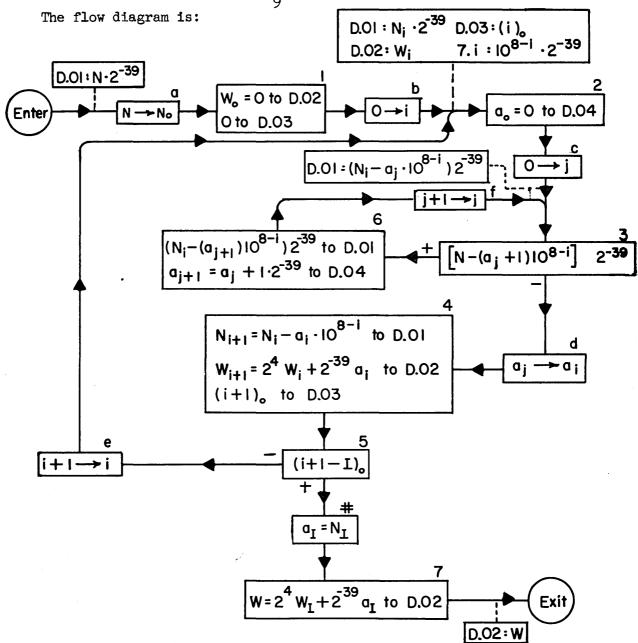

We conclude the present introductory chapter with a brief commentary on the various steps leading up to the execution of a problem by the computer. The first step concerns the formulation of the problem itself. One method would be simply the writing down of the various equations and the various steps to be taken, tegether with the necessary explanatory remarks. This approach, although feasible, may often become quite complicated and untractable. Instead we follow von Neumann

who proposed the idea of a <u>flow-diagram</u>. This is a very elegant, logical and mathematical description of the problem to be computed. It makes use of a set of conventionalized symbols to describe the course of the control at every stage of the problem. Represented in a very concise way are: (i) the purely mathematical operations, (ii) various logical steps and decisions together with a precise indication of the nature of the corresponding criteria, (iii) the contents of the relevant part of the memory at points where the question might naturally arise.

The flow-diagram of a problem is prepared by the mathematician or physicist. The symbols are few in number, their meanings simple enough so that they are easily mastered. A flow-diagram may be drawn without a specific computer in mind. In practice, however, one usually does plan on the use of a specific computer and takes advantage of this fact in his planning of a problem. A quite superficial knowledge of the particular computer suffices. The important characteristics are:

(i) the capacity of the inner memory, (ii) the nature of the external memory, (iii) the extent of the vocabulary, both arithmetical and logical.

The next step in the preparation is the coding. This process consists conveniently of two parts. In the first, the coder prepares a sequence of instructions using a set of readily interpretable symbols that indicate the general nature of the operations. For example, say at some point in the sequence a number is in register R2 and it is intended to add to it another number at the moment residing somewhere in the memory. A possible notation, and the one used here, is:

$$m \rightarrow Ah$$

where m indicates that a number in the memory is to be sent to R2. For historical reasons, the letter A has been used as a symbol for R2; the original intent being that R2 is the accumulator register. h indicates that R2 is not to clear its contents before receiving from the memory but to hold them for a true addition process. It is observed that the specific binary symbols which the computer can interpret are not used yet, nor is the specific location of the number in the memory given.

There is, however, some point to this preliminary step in the coding. In the first place, there are likely to be several improvements or modifications made before one is satisfied with the sequence of instructions finally adopted for a given problem. This form is much easier to follow, both from the point of making a sample hand calculation (for checking purposes) as well as in trouble-shooting (in the event this is necessary) after the problem has reached the computer.

The second step in the coding is a straightforward transliteration from the coder's notation to teletype symbols. This is routine.

A given large problem may often be divided into a set of smaller problems. Some members of this set may occur frequently enough so that it becomes worthwhile to have these portions coded in quite general terms and, in a sense, treated as individual orders but on a somewhat broader basis. For example, integration by Simpson's Rule, or the inversion of an (n x n) matrix. These sub-routines, as they are conventionally called, would form a library of general orders. A problem at hand would then first be decomposed into the sub-routines available from the library, and the remainder coded from the basic individual orders. Obviously some preparations are required for each individual use of a sub-routine; in the case of the inversion of a matrix, the location of the particular elements for the problem at hand must be specified. Nevertheless, there is a great reduction in effort, especially in checking.

#### II. CODING AND FLOW DIAGRAMS

#### Introduction

The computer can perform a set of basic operations, both arithmetical and logical. It may be desirable to keep the set small as added electronic equipment (which is roughly proportional to the number of operations) increases the physical complexity of the computer and complicates maintenance. A modest number of thirty-six operations have been chosen to comprise this set. The choice, however, is fluid in that the set may be modified as the need for change is shown.

We say that the computer has a language of its own, for it is able to interpret and execute the given set of orders. We speak of the orders as the <u>vocabulary</u> of the computer. <u>Coding</u> is the translation of the language of the mathematician into the language of the computer.

The four fundamental arithmetic operations (addition, subtraction, multiplication and division) are a part of the vocabulary. All of the arithmetic operations of the vocabulary, of which there are about twenty, involve the four fundamental operations.

The first step in the preparation of any problem for the computer is to arrange the work so that the only arithmetic operations involved are addition, subtraction, multiplication and division. In other words, the problem must be reduced to a form in which it can be solved by numerical procedures.

The usual mathematical formulation of the problems with which we shall be concerned is a differential equation, or a coupled set of such equations, together with a group of boundary (or initial) conditions. There are other types of problems, but they occur less frequently.

The differential equations are of such complexity that analytical methods are not known for obtaining their solutions. The only recourse is to numerical procedures; therefore these problems are ideally suited for the computer.

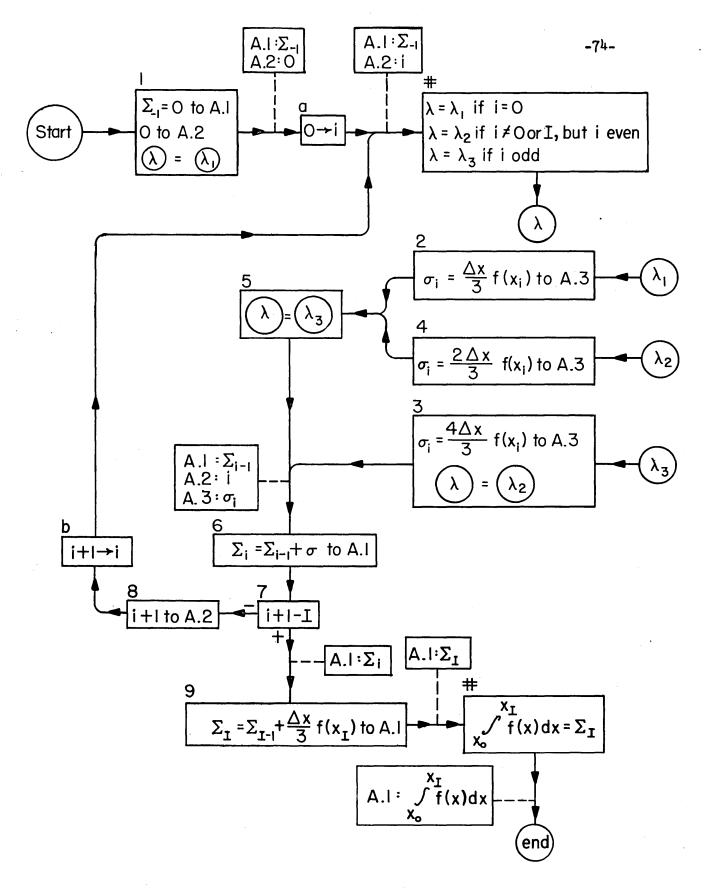

The first step in the solution of the problem is to replace the differential equations by a set of finite difference equations. We do not discuss here the stability or convergence of such methods, but only mention them as necessary considerations in writing the difference equations. In such a process of translation, derivatives are replaced by difference quotients, integrals by sums, transcendental functions by algebraic functions, etc. The problem is now tractable in terms of the vocabulary of the computer as it involves only the fundamental operations.

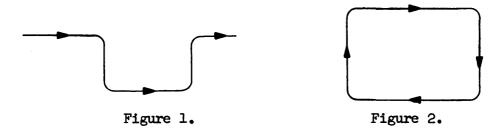

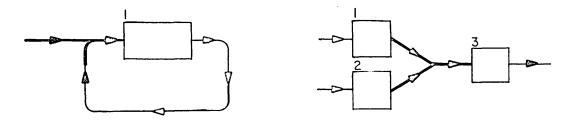

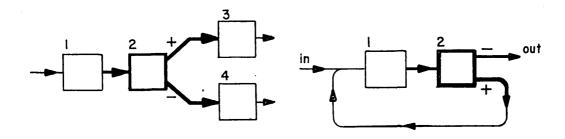

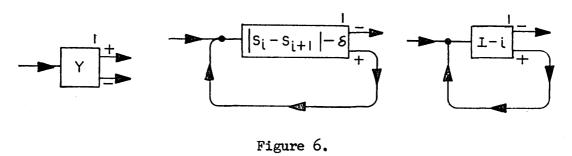

The next step toward a solution is the preparation of the flow diagram. The flow diagram represents the path to be followed by the computer in the solution of the problem. It represents this by sequences of lines oriented with direction arrows. At points of the diagram where computation is to be performed, the lines are interrupted and boxes are inserted that indicate the "local" computation that is to be performed. The diagram represents the purely mathematical operations, the logical steps and decisions, and the relevant memory storage that is required. Five kinds of boxes represent the desired information:

- (i) The operation box

- (ii) The alternative box

- (iii) The substitution box

- (iv) The assertion box

- (v) The storage box

These are discussed in detail later.

When the flow diagram is completed, the solution is at the coding level; but before discussing the coding we first discuss some background matters. Each of the thirty-six operations of the vocabulary is referred to as an order. Each order has associated with it a number that specifies the location in the memory of the number upon which the order is to operate; e.g., in the multiply order the associated number specifies the location in the memory of the multiplicand factor. This number location is called an address. The memory contains 1024 words. The addresses of these words consist of the decimal numbers 0 through 1023. Binary-wise, Eight bigits are used for each order; hence eighteen bigits are necessary for each order with its address. It is convenient, however, to allow twenty bigits for their expression as twenty bigits comprise half of a word. Each order with its associated address is called an instruction. Two instructions are stored per word, giving the memory in principle a capacity of 2048 instructions. However, memory storage is also necessary for true numbers, so that in general there will be some combination of instructions and numbers stored.

The computer uses a one-address system. Each instruction may refer to at most one memory location. Some instructions involve only the arithmetic unit and do not refer to the memory. In these instances the address portion has a different function which is described later.

To illustrate the one-address system consider a simple example of summing two numbers,  $\underline{a}$  and  $\underline{b}$ , which are residing in the memory: The sum s = (a+b) is to be stored in the memory. Three instructions are required:

- (i) An instruction to bring a into the arithmetic unit

- (ii) An instruction to bring  $\underline{b}$  into the arithmetic unit and to form the sum s = (a+b)

- (iii) An instruction to store s in the memory

If <u>a</u> is in the arithmetic unit as a result of some previous operation, only the latter two instructions are needed. If a three-address system were used, the above sequence could be expressed with one order which specified all three addresses: the location of <u>a</u>, the location of <u>b</u>, and the location at which <u>s</u> is to be stored. We defer any discussion of the merits of the one-address system versus those of the multiple address type.

The process of coding involves writing down a sequence of instructions to perform the operations indicated on the flow diagram with the desired set of numbers.

The coding in all but the simplest of problems is not a linear sequence. (That is, the control does not follow a unique path; at various points in a problem several courses may be available.) Certain portions of the coded sequence may be performed several times, whereas other sections are omitted temporarily. The logical orders that have been included in the vocabulary provide for such procedures. Furthermore, the coding is not a static sequence in that it usually does not remain fixed throughout the course of the problem. There are certain orders that allow portions of the coding to be altered so that subsequent traversals through the sequence give rise to a variety of patterns.

It is these dynamic and non-linear characteristics of the coding which provide the desired flexibility for scientific computation but which, on the other hand, give rise to complications in coding. The remainder of this chapter presents a step-by-step approach to coding, beginning with very simple examples and systematically progressing to examples of increasing complexity.

Before coding any actual examples we first discuss the vocabulary as shown in Table I. It contains a list of the explicit orders with a description of each. It will be noted that there are two types of symbols. The first column gives the abbreviated logical symbol for each order, while the second column gives the actual code for the computer.

Orders 1 through 8 are the addition and subtraction orders. All of these involve R2 (the accumulator register) and a memory location that is specified in the instruction. The first four of these orders clear R2 (set it to O's) and then add (subtract) the specified word to the O's in R2. The remaining four orders actually add (subtract) the contents of the specified memory location to the number residing in R2. In a sense, the first four orders are communication orders (they do, however, also allow the magnitude or complement of a number to be inserted) while the latter four are true add or subtract orders.

Consider the example of forming the sum (difference) of two numbers,  $\underline{a}$  and  $\underline{b}$ , and storing the sum s = (a + b), (difference s = a - b) in the memory. Assume that  $\underline{a}$  and  $\underline{b}$  are residing in the memory, say at addresses  $\underline{l}$  and  $\underline{l}$ , respectively; and the sum (difference) is to be stored in 3. The instructions are:

1.

$$m \longrightarrow Ac$$

1 a to R2

2.  $(m \longrightarrow Ah)$  2  $(s = a + b)$  to R2

3.  $A \longrightarrow m$  3 s to 3

Each order has immediately following it the memory address to which the instruction refers. In a column to the right of the instruction is shown the action that takes place due to each instruction.

If the sum of more than two numbers is formed it is not necessary to send each sum of two numbers into the memory and repeat the three orders. A sum of several numbers may be formed in R2 which requires one additional order for each new number added to the sum; only the final sum is sent to the memory.

In orders 2, 4, 6, and 8 where subtraction is desired this is done by taking the complement of the number with respect to 2 and then performing

TABLE I  $(\underline{m} \text{ is the word at address m in the memory})$  (The word at its original position is never cleared)

| .1  | Abbreviation               | Code | original position is never didded,                              |

|-----|----------------------------|------|-----------------------------------------------------------------|

| 1.  | m—→Ac                      | AA   | Replace the number in R2 by m.                                  |

| 2.  | m→Ac-                      | AΒ   | Replace the number in R2 by the complement (the                 |

|     |                            |      | negative) of m.                                                 |

| 3.  | m-AcM                      | ΑE   | Replace the number in R2 by the absolute value                  |

| •   |                            |      | of m.                                                           |

| 4.  | mAc-M                      | AF   | Replace the number in R2 by the complement of                   |

|     |                            |      | the absolute value of m.                                        |

|     |                            |      | <del></del>                                                     |

| 5.  | m—→Ah                      | BA   | Add m to the number in R2.                                      |

| 6.  | m—→Ah-                     | BB   | Add to the number in R2 the complement of m.                    |

| 7.  | m ——AhM                    | BE   | Add to the number in R2 the absolute value of $\underline{m}$ . |

| 8.  | $m \longrightarrow Ah - M$ | BF   | Add to the number in R2 the complement of the                   |

|     |                            |      | absolute value of m.                                            |

|     |                            |      |                                                                 |

| 9•  | m <del>→</del> Q           | EB   | Replace the number in $R^{4}$ by $\underline{m}$ .              |

| 10. | X                          | DA   | Clear R2 and multiply m by the number in R4. The                |

|     |                            |      | 39 most significant bigits of the product appear                |

|     |                            |      | in R2. The 2 <sup>-39</sup> bigit position of R2 is set to 1.   |

|     | •                          |      | R4 is set to $\underline{0}$ 's.                                |

| 11. | X *                        | DB   | Clear R2 and multiply m by the number in R4. The                |

|     |                            |      | left-hand 39 bigits appear in R2, the right-hand                |

| 10  | •                          | DD   | 39 bigits in R4. The sign bigit of R4 is set to 0.              |

| 12. | •                          | DD   | Divide the number in R2 by m. The quotient appears              |

|     |                            |      | in R4, two times the remainder appears in R2.                   |

| 13. | T                          | CA   | Transfer the control to the left-hand order of m.               |

| 14. | T*                         | СВ   | Transfer the control to the right-hand order of m.              |

| 15. | С                          | CC   | If the number in R2 is $\geq$ 0, transfer the control           |

|     |                            |      | as in T, otherwise continue to next order in sequence.          |

| 16. | C¹                         | CD   | If the number in R2 is $\geq$ 0, transfer the control           |

|     |                            |      | as in T', otherwise continue to next order in sequence.         |

|     |                            |      |                                                                 |

| 17. | $Q \longrightarrow m$      | EC   | Replace $\underline{m}$ by the number in $\mathbb{R}^{l_{+}}$ . |

| 18. | A-→m                       | DC   | Replace $\underline{\underline{m}}$ by the number in R2.        |

### TABLE I (Cont.)

| 19. | S→m         | FA | Replace the address (bigits 8-19) of the left-<br>hand order of m by the 12 bigits 8-19 in R2.                                                                                |

|-----|-------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20. | S-m         | FB | Replace the address (bigits 28-39) of the right-                                                                                                                              |

|     |             |    | hand order of $\underline{m}$ by the 12 bigits 28-39 in R2.                                                                                                                   |

| 21. | HS──m       | FC | Replace the left-hand 20 bigits (bigits 0-19) of                                                                                                                              |

|     |             |    | $\underline{m}$ by the 20 bigits 0-19 in R2.                                                                                                                                  |

| 22. | HS→m *      | FD | Replace the right-hand 20 bigits (bigits 20-39)                                                                                                                               |

|     |             |    | of $\underline{m}$ by the 20 bigits 20-39 in R2.                                                                                                                              |

| 23. | Rn          | EE | Right shift R2 and R4 n places where n is                                                                                                                                     |

|     |             |    | specified in the address bigits of the order.                                                                                                                                 |

|     |             |    | This replaces the contents $\lambda_0$ , $\lambda_1 \cdots \lambda_{39}$ of R2                                                                                                |

|     |             |    | and $\sigma_0$ , $\sigma_1 \cdots \sigma_{39}$ of R4 by $\lambda_0 \cdots \lambda_0$ , $\lambda_1 \cdots$                                                                     |

|     |             |    | $\cdots$ $\lambda_{38-n}$ , $\lambda_{39-n}$ , and $\lambda_{39-n+1}$ , $\lambda_{39-n+2}$ $\cdots$ $\lambda_{39}$ ,                                                          |

| ol. | ▼           | 77 | o, o <sub>1</sub> ··· o <sub>39-n</sub> .                                                                                                                                     |

| 24. | Ln          | DE | Left shift R2 and R4 n places where n is speci-                                                                                                                               |

|     |             |    | fied in the address bigits of the order. This re-                                                                                                                             |

|     |             |    | places the contents $\lambda_0$ , $\lambda_1 \cdots \lambda_{39}$ of R2 and $\sigma_0$ ,                                                                                      |

|     |             |    | $\sigma_1 \cdots \sigma_{39}$ of R4 by $\lambda_n$ , $\lambda_{n+1} \cdots \lambda_{39}$ , 0 \cdots 0 and                                                                     |

|     |             |    | $\sigma_{n}$ , $\sigma_{n+1}$ ··· $\sigma_{39}$ , $\lambda_{o}$ , $\lambda_{1}$ ··· $\lambda_{n-2}$ , $\lambda_{n-1}$ .                                                       |

| 25. | аАс         | EF | Replace the number in R2 by the 12 address bigits                                                                                                                             |

|     |             |    | of this order (into positions 0-11 of R2).                                                                                                                                    |

| 26. | aAh         | DF | Add to the number in R2 the 12 address bigits of                                                                                                                              |

|     |             |    | this order (into positions 0-11 of R2).                                                                                                                                       |

| 27. | DS          | ED | Set the sign bigit of the number in R2 to O.                                                                                                                                  |

| 28. | Flexo Print | EA | Print $\underline{m}$ on the page printer (slow speed).                                                                                                                       |

| 29. | Read        | FF | Replace $\underline{\underline{m}}$ by the next word to come under the read-                                                                                                  |

|     | •           |    | ing head of the paper tape reader.                                                                                                                                            |

| 30. |             | FE | (NOT PRESENTLY USED)                                                                                                                                                          |

| 31. | Punch       | CF | Punch <u>m</u> on paper tape.                                                                                                                                                 |

| 32. | Sync Print  | CE | To be used in a subroutine which simultaneously                                                                                                                               |

|     |             |    | prints $\underline{m}_{-i}$ , $\underline{m}_{-i+1}$ , $\underline{m}_{-i+2}$ and $\underline{m}_{-i+3}$ ; $\underline{i}$ is to be communicated to the routine (high speed). |

|     |             |    |                                                                                                                                                                               |

### TABLE I (Concl.)

| 33• | m—→D | BD  | Read 50 successive words from the memory       |

|-----|------|-----|------------------------------------------------|

|     |      |     | starting with the word at the address speci-   |

|     |      |     | fied by bigits 8-19 of the instruction. Write  |

|     |      |     | these 50 words into the drum on the track      |

|     |      |     | specified by bigits 20-27. Then transfer the   |

|     |      |     | control to the left-hand instruction of the    |

|     |      |     | word at the address specified by the bigits    |

|     |      |     | 28-39.                                         |

| 34. | D→m  | BC  | Read the 50 words from the track of the drum   |

|     |      |     | specified by bigits 20-27 of the instruction.  |

|     |      |     | Write these words into 50 successive memory    |

|     |      |     | locations starting with the address specified  |

|     |      |     | by bigits 8-19. Then transfer the control to   |

|     |      |     | the left-hand instruction of the word at the   |

|     |      |     | address specified by bigits 28-39.             |

|     |      |     |                                                |

| 35• | Q→t  | AD  | Write the number in R4 onto the magnetic tape. |

| 36. | t →Q | AC  | Replace the number in R4 by the first word to  |

|     |      |     | come under the reading head of the magnetic    |

|     |      |     | tape reader.                                   |

|     |      |     |                                                |

| 37• | Stop | OFF | Stop computation. (Pressing start next order   |

|     |      |     | button will allow machine to continue in nor-  |

|     |      |     | mal sequence.)                                 |

NOTE: An address of 800 refers to the quotient register (R4) when using orders 1 through 8; i.e., AA800 says replace the number in R2 by the number in R4.

a normal addition. The complement scheme is described in detail in the chapter on binary arithmetic. When an address 100000000000 which corresponds to 2048 decimally is used with any of the orders 1 through 8, it has the effect of treating R4 (the quotient register) as a memory position with the address 2048. The number residing in R4 can then be added into R2 as described by any one of the orders 1 through 8.

Order 9 transmits a number from the memory to R4 (the quotient register). R4 does not have add facilities; hence a number being transmitted to R4 replaces the number that is in R4.

Orders 10 and 11 are the two multiplication orders. Before either of these orders may be given, the multiplier must be in  $R^4$  (either as the result of some previous operation or by a preceding  $m \rightarrow Q$  order). The 39 most significant bigits of the product appear in R2. Order 10 gives only the 39 most significant bigits of the product rounded off. Order 11 gives a full 78 bigit product; the rightmost 39 bigits appear in  $R^4$ . The multiply order supplies the multiplicand.

Order 12 is the divide order. It is assumed that the dividend is in place in R2; the divide order itself provides the divisor. The quotient is located in R4, and two times the remainder appears in R2.

Order 13 is a transfer order. This interrupts a sequence and causes the computer to continue with another sequence beginning with the instruction specified by the address part of the transfer instruction. As an example of a transfer instruction, suppose that a sequence of instructions is being performed and in the 25th step of the sequence a transfer is encountered:

25 T 125

124

125

The transfer instruction has the address 125, so that the sequence of code from 26 to 124 is omitted. The computer would execute Instruction 125 and continue sequentially from there.

Since an instruction word consists of two instructions and the flexibility of being able to transfer into either instruction of a word is desired, it is necessary to have two transfer orders to accomplish this. This accounts for Order 14, the T' order, as well as Order 13. Hence, in the above example, 25 may have read <u>T 125</u> or <u>T' 125</u>, depending on whether the transfer was desired to the left or right instruction of Instruction Word 125.

The two conditional transfer orders, 15 and 16, either execute the transfer as in the T orders discussed immediately above, or the orders require no action, in which case the computer continues along the original sequence. The conditional transfer is effective or not, depending on the sign of the number, N, in R2 at the time the order is to be performed: if  $N \ge 0$ , the transfer does occur, and a new sequence of instructions is started at the location specified by the address part of the instruction; if N < 0, the computer continues with the original sequence of instructions.

Orders 17 and 18 are the two orders that send information from the arithmetic unit to the memory. Order 17 transmits from R4 to the memory, and 18 transmits from R2 to the memory. When any register or memory location sends information to any other register or memory location, the information is still available at its original position.

Orders 19 through 22 are the substitution orders. These orders make alterations in instructions. By means of 19 and 20, any instruction may have its address changed. The new address is first formed in R2 and then inserted into the desired instruction by means of a substitution order. The use of the substitution orders is explained in detail in Problem 2. The two half word substitution orders (Numbers 21 and 22) may alter whole instructions rather than just the address. These two orders may also be used in storing half precision numbers. The details of their use will be covered by later examples.

Orders 23 and 24 are the right and left shift orders. They give a means of dividing or multiplying by powers of 2 by shifting a number right or left in R2; e.g., if a number a = 0.00001111 is residing in R2

and it is desired to multiply this number by 2<sup>4</sup>, this can be effected by a left shift of 4 places, which displaces the number 4 units to the left.

$$a = 0.00001111$$

$a \times 2^{14} = 0.11110000$

A right shift effects division by powers of 2 by displacing the number to the right. In a left shift R4 may be considered an extension of R2 to the left; hence a number shifting left out of R2 fills into R4 beginning in the least significant end of R4. In a right shift R4 may be considered an extension of R2 to the right and a number shifting right out of R2 fills into R4 beginning in the most significant end of R4. Since R2 and R4 are so interconnected for shifting operations, these operations may be used for separating a multiplex of numbers occupying one word. Either a left or right shift of 40 places will transfer completely a number from R2 to R4.

Orders 25 and 26, a $\rightarrow$ Ac and a $\rightarrow$ Ah, treat their associated addresses as true numbers. The addresses of these instructions are sent into R2 (either a clearing or an adding action) into bigit positions 0 through 11. Many times in the type of problem in which we will be interested there are small numerical constants of three significant decimal digits or less. Rather than use an entire memory location to store such constants, they can often be expressed in the address position of an  $a\rightarrow$ A instruction. As an example consider that a quantity

$$ax^2 + bx$$

has been formed and is in R2. It is desired to add a constant term  $\underline{k}$  where  $\underline{k} = .583$ . This may be expressed in the a—Ah order as

.

$$ax^2 + bx$$

in R2

(iii)  $a \rightarrow Ah$  583  $ax^2 + bx + (.583 = k)$  to R2

where .583 is expressed by its binary equivalent. Eleven bigits give the same precision as 3.3 decimal digits, so any three-decimal digit fraction may be expressed in the address position of an  $a \rightarrow A$  order.

The explanation of the remainder of the orders as given in Table I is adequate; hence we return to the task at hand, the coding of typical problem-examples.

The coding of a problem may be divided into two parts:

- (i) The logical coding

- (ii) The computer (numerical) coding

Each of these parts involves several steps. At the present level of our knowledge and skill, it seems convenient to have both a logical and a numerical symbol for each order. The logical symbols are used in part (i), while the numerical symbols are used in part (ii).

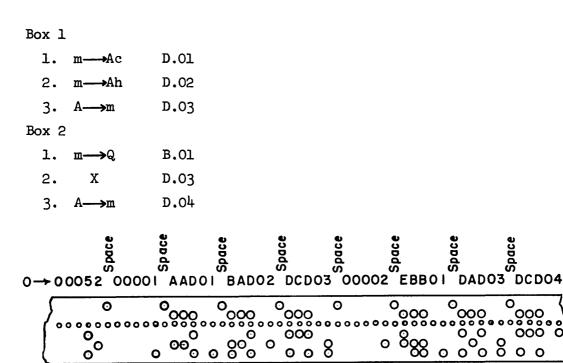

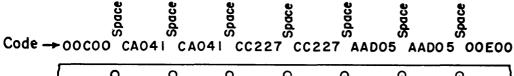

The logical symbol attempts to be a descriptive abbreviation of the action of that instruction; the associated memory location is preliminarily specified by a combination of a letter and a number; the letter identifies some group storage and the number identifies a member of that group; e.g., m Ac B.4 is interpreted as: Bring from the memory to the Accumulator (R2), clearing the accumulator first, the number at memory location B.4. One reason for not assigning specific numerical memory locations at the outset of a problem is that the extent and disposition of the memory requirements are not immediately obvious. A set of logical symbols is more meaningful to the coder than an abstract code; it expedites the actual coding and facilitates checking.

The abstract coding is merely a transliteration from the logical code to the numerical code. The numerical code is shown in the second column from the left in Table I. Each order is represented by a combination of two of the letters, A,B,C,D,E,F, where each letter expresses a tetrad (4) of bigits. These are:

| A | 1010 | D ,          | 1101 |

|---|------|--------------|------|

| В | 1011 | E            | 1110 |

| C | 1100 | $\mathbf{F}$ | 1111 |

When the coding has been written in numerical form, the teletype tape (which is the present means of putting the coded sequence into the memory unit) is prepared. The actual coding examples are treated in the following pages.

#### Problem 1

We propose to form the rational function  $\underline{y}$  with constant coefficients where

$$y = \frac{ax^2 + bx + c}{ex + f}$$

Assume that  $\underline{x}$ ,  $\underline{a}$ ,  $\underline{b}$ ,  $\underline{c}$ ,  $\underline{e}$ , and  $\underline{f}$  are in the memory at known addresses. As previously mentioned, the memory locations are denoted by capital letters rather than using true number addresses; e.g., the notation A.l:  $\underline{a}$  implies that the quantity  $\underline{a}$  is stored in the memory at address A.l. The storage of the problem is:

| A.l:a              | A.4:e              |

|--------------------|--------------------|

| $A.2:\overline{b}$ | A.5: T             |

| A.3:c              | $A.6:\overline{x}$ |

and when y is formed it is to be stored in A.7.

As a preparatory step in coding the problem, we form  $\underline{y}$  by a sequence of arithmetic operations in which each step involves only one operation. Such a sequence is:

1.

$$e \cdot x$$

2.  $ex + f$

3.  $a \cdot x$

4.  $ax + b$

5.  $(ax + b)x$

6.  $ax^2 + bx + c$

7.  $y = \frac{ax^2 + bx + c}{ex + f}$

Since the computer can accomplish only one arithmetic operation at a time, the above sequence is precisely the procedure that one must go through in coding the problem, insofar as the arithmetic is concerned.

We now proceed with the coding. In the preliminary logical code, each instruction is treated as a word rather than the actual case of two instructions per word. The left-hand column is the code abbreviation, and the next column indicates the operations that have taken place in the arithmetic unit, while the last column is conveniently used for memory storage. During the course of the problem, a storage location in the memory is needed to store an intermediate value of the computation. This position is denoted as B.1.

The sequence is:

Note that the denominator was formed before the numerator. If the reverse had been the case, the numerator when formed would have been stored in, say, B.1. When the denominator was formed it, too, would have been stored in, say, B.2. The numerator would then be brought in and the division performed. Coding in this fashion, however, would have required two additional instructions and one word more storage in all making the coding two words longer than it is at present.

Instruction 8 in the above sequence, which is L40, is a means of communication from R2 to R4. L40 shifts the entire word including the sign from R2 to R4. If this were not available, it would be necessary to send the word from R2 to the memory and then from the memory to R4, thus requiring one additional instruction.

Recall that each instruction word in the memory actually contains two instructions. The next step of the coding is to arrange the sequence of instructions into words. If we assume that the routine starts at address 1 in the memory, the sequence then occupies memory locations 1 through 6 (since it contains 12 instructions, 6 words are required). At this time, the constants of the problem are given true memory addresses. Since there are six such quantities (where each quantity comprises one word), memory locations 7 through 12 are allotted for these. When y is formed it will be stored at address 13. One temporary location is needed which is designated as 14.

The sequence becomes:

| 1.  | $m \longrightarrow Q$  | 12 | X                      | 10 |

|-----|------------------------|----|------------------------|----|

| 2.  | $m \longrightarrow Ah$ | 11 | A-→m                   | 14 |

| 3•  | m→Q                    | 7  | X                      | 12 |

| 4.  | $m \longrightarrow Ah$ | 8  | L                      | 40 |

| 5•  | X                      | 12 | $m \longrightarrow Ah$ | 9  |

| 6.  | +                      | 14 | $Q \longrightarrow m$  | 13 |

| 7.  | a                      |    |                        |    |

| 8.  | ъ                      |    |                        |    |

| 9•  | c                      |    |                        |    |

| 10. | е                      |    |                        |    |

| 11. | f                      |    |                        |    |

| 12. | x                      |    |                        |    |

| 13. | -                      |    |                        |    |

| 14. | -                      |    |                        |    |

Memory locations 13 and 14 are used for quantities formed within the routine; hence they must be empty or their contents must be irrelevant at the time the sequence is to be executed by the computer.

When the coding is in final form such that the input teletype tape is to be prepared, one has the instructions reduced to numerical form and has available the true numerics for all of the involved quantities. Assume, for example, that

| 8.                   | = .075329  | е : | 83291       |

|----------------------|------------|-----|-------------|

| ъ                    | = .12391   | f : | 69736       |

| c                    | = .017326  | х : | 32915       |

| The final coding is: |            |     |             |

| 1.                   | EB012DA010 | 8.  | 0.123910000 |

| 2.                   | BAOLIDCO14 | 9•  | 0.017326000 |

| 3                    | ED007D4030 | 10  | 000010000   |

2. BAO11DCO14 9. 0.017326000

3. EBOO7DAO12 10. 0.832910000

4. BAO08DE040 11. 0.697360000

5. DAO12BAO09 12. 0.329150000

6. DDO14ECO13 13. 0.000000000

7. 0.07532900 14. 0.000000000

#### Problem 2

We modify the preceding problem with a slight logical twist. Assume that the calculation of the rational function  $\underline{y}$  is a part of some larger problem and that  $\underline{x}$  has been computed as part of a previous routine and stored in some memory location other than the one assigned to it (A.6 in the preceding example). Indeed, there may be a series of such  $\underline{x}$  values. Further, when  $\underline{y}$  is computed it is to be stored, not in A.7, but at some other memory location where it will be used in subsequent parts of the calculation. In other words, we ask what modifications must be made to the sequence of instructions in Problem 1 in order to render it more flexible and assimilable in a larger problem.

One possibility is to reserve memory location A.6, not for storing  $\underline{x}$  itself as was done earlier, but instead to store the <u>address</u> at which  $\underline{x}$  may be found. A.6 does not contain  $\underline{x}$ , but it does tell us where in the memory  $\underline{x}$  is located. Similarly, we may use A.7, not to store  $\underline{y}$  itself, but to contain the address at which  $\underline{y}$  is to be stored when formed.

Suppose then, as a preceding part of some problem,  $\underline{x}$  has been computed and stored in, say, memory location M.l; and we wish to use the routine outlined in Problem 1 to calculate the rational function given there with the stipulation that y should be stored in N.l.

It is necessary to place the <u>address M.l</u> in location A.6 and <u>address N.l</u> in location A.7. Thus, in the course of the calculation, when  $\underline{x}$  is required, A.6 is consulted, giving the information where  $\underline{x}$  is actually located. Finally, A.7 provides the information where  $\underline{y}$  is to be stored, namely in N.l. Thus, this rational function routine may be used several times in the course of a large problem; each time, however, it is necessary to provide the corresponding address for the locations  $\underline{x}$  and  $\underline{y}$ .

Making these changes in this routine leads to the simplest illustration of using the substitution order. Without attempting to justify the utility of it at this point, we proceed with the simple example.

Instructions 1 through 6 of the following code sequence are the additional instructions required for the substitutions. The function of these first instructions is to provide appropriate addresses to subsequent instructions that involve x and y. Recall that x resides at

location M.1, and the numerical value of M.1 is at A.6. The preliminary instructions thus involve taking the numerical quantity M.1 from location A.6 in the memory to the arithmetic unit. From there it may be inserted into the address part of the instruction that first involves  $\underline{x}$ . This is accomplished by the substitution order. Repeated application of this order introduces this same address into all the other instructions that require it. In the example observe that Instruction 8 of the code is the first instruction referring to  $\underline{x}$  and requiring the particular address where  $\underline{x}$  resides. Two instructions, here taken to be 1 and 2, are required to provide Instruction 8 with the appropriate address. These are:

- (i) An instruction to transfer the contents of A.6, namely the address of x, to the arithmetic unit;

- (ii) A substitution order which has the effect of transferring this address of  $\underline{x}$  into Instruction 8.

Inasmuch as this address is also required for Instructions 11 and 15, two more substitution orders, Instructions 3 and 4, are needed for them. Finally, the address referring to the location of  $\underline{y}$  is needed for Instruction 18; two more instructions, 5 and 6, accomplish this, thus accounting for the six preparatory instructions.

At the start of the problem, Instructions 8, 11, 15, and 18 have blank addresses. After the control has proceeded through Instruction 6, all of the instructions have the proper addresses.

The storage is as before, with the changes as noted above,

A.1: a

A.2: b

A.3: c

A.4: e

A.5: f

A.6: M.1

A.7: N.1

B.1:

M.1: x

N.l:

The coding is:

In coding the problem into word form, the instructions into which addresses are being substituted may be either the left-hand or the right-hand instruction of a word. In Table I, Orders 19 and 20 account for this. They read:

- "19. S-m Replace the address (bigits 8-19) of the left-hand order of m by the 12 bigits 8-19 in R2.

- 20. S $\rightarrow$ m' Replace the address (bigits 28-39) of the right-hand order of m by the 12 bigits 28-39 in R2."

Since it is desirable to substitute into either a left-hand or right-hand instruction from an address which has been brought into R2, the following custom in storing addresses is adopted: Consider an address  $\underline{x}$  as an integer which may assume values from  $\underline{0}$  to 1023. Rather than storing  $\underline{x}$ , store

$$(x)_0 \equiv 2^{-19}\underline{x} + 2^{-39}\underline{x},$$

where  $(x)_0$  is called the memory position mark  $\underline{x}$ . Since  $\underline{x}$  is an integer, when  $(x)_0$  is brought into R2 the addresses are so positioned that either  $S \longrightarrow m$  or  $S \longrightarrow m$  may be used as required.

The instructions are now paired into words. There are 18 instructions or 9 words which, if the coding starts at word  $\underline{1}$ , give instruction-words from address  $\underline{1}$  through 9. The numerics then start with address 10 and go through address 17.

```

1. m \longrightarrow Ac

15

S \longrightarrow m'

4

2.

S →m

6

8

S \longrightarrow m

3.

16

S \longrightarrow m

9

m \longrightarrow Ac

4.

m \longrightarrow Q

13

X

14

5.

m \longrightarrow Ah

17

A \longrightarrow m

m \longrightarrow Q

X

10

11

7.

m \longrightarrow Ah

L40

8.

X

12

m \longrightarrow Ah

9.

17

Q \longrightarrow m

10.

<u>b</u>

11.

12.

c

13.

<u>e</u>

<u>f</u>

14.

(M.1)_{\alpha}

15.

(N.1)_{0}

16.

17.

```

The storage has been changed to include the appropriate values  $(M.1)_{O}$  and  $(N.1)_{O}$ .

In the final coding, Instructions  $4^{\circ}$ , 6, 8, and  $9^{\circ}$  may initially be given any address as this address is irrelevant (the correct addresses are supplied during the course of the computation). For uniformity, the plan of initially setting these addresses to 0 is adopted.

#### Problem 3

The numbers  $a_1$ ,  $a_2$ ,  $a_3$  ···  $a_n$  and the numbers  $b_1$ ,  $b_2$ ,  $b_3$  ···  $b_n$  are stored in the memory. It is desired to form the following product sum

$$\sum_{i=1}^{n} a_i b_i = a_1 b_1 + a_2 b_2 + \dots + a_n b_n$$

The storage of the  $\underline{a}$ 's and  $\underline{b}$ 's is arranged so that

A.1:

$$a_1$$

, A.2: $a_2$  ··· A.i: $a_i$  ··· A.n: $a_n$

and

That is, the  $\underline{\mathbf{a}}$ 's are stored consecutively in one section of the memory and the  $\underline{\mathbf{b}}$ 's are stored consecutively in another section. The sum, when it is formed, is to be stored in the memory at address C.1.

If n = 1, the coding is trivial; it is:

1.

$$m \longrightarrow Q$$

A.1  $a_1$  to R4

2.  $X$  B.1  $a_1b_1$  in R2

3.  $A \longrightarrow m$  C.1  $a_1b_1$  to C.1

The problem may be extended to n = 2 by adding the following instructions:

4.

$$m \rightarrow Q$$

A.2  $a_2$  to R4

5. X B.2  $a_2b_2$  in R2

6.  $m \rightarrow Ah$  C.1  $a_1b_1 + a_2b_2$  in R2

7.  $A \rightarrow m$  C.1  $a_1b_1 + a_2b_2$  to C.1

One method of extending the coding to the general case of  $\underline{n}$  elements in the sum is to have the first three instructions followed by (n-1) repetitions of Instructions 4 through 7 with the appropriate A.i and B.i being used in place of the A.2 and B.2. This method becomes very costly with respect to available memory space as  $\underline{n}$  becomes large, since each increase of  $\underline{n}$  by  $\underline{1}$  increases the code by four instructions.

The coding for the general case  $\underline{n}$  is:

By using this method, 4n instructions are needed. If <u>n</u> is large, say 50-100, then 200 to 400 instructions or 100 to 200 words of coding are needed.

Note, however, that the only changes in the coding for each  $\underline{i}$  are the changes in the addresses of the instructions ( $m \longrightarrow Q$  A.i) and (X B.i), and as  $\underline{i}$  is increased by  $\underline{l}$  the addresses of these two instructions are also increased by  $\underline{l}$ .

If by some means the computer can be directed to go repeatedly through the coding and at each traversal to increase by  $\underline{1}$  the addresses of the instructions ( $m \longrightarrow Q$  A.i) and (X B.i), the length of the total coding can be shortened greatly. By means of the transfer orders a section of the coding can be traversed as many times as is desired; and at each passage through the coding the instructions ( $m \longrightarrow Q$  A.i) and (X B.i) are brought into the arithmetic unit and  $\underline{1}$  is added (in the correct address position) to each of them. It is, of course, necessary to have available in the memory the

appropriate  $\underline{1}$  to increase the addresses. It may be either  $1 \times 2^{-19}$ ,  $1 \times 2^{-39}$  or, in fact, both may be needed. At present we store  $1 \times 2^{-m}$  in C.2, and fix upon m later in the coding. The sequence is:

1.

$$m \rightarrow Q$$

A.1  $a_1$  to R4

2.  $X$  B.1  $a_1b_1$  in R2