# **Operation** and maintenance manual

# KENNEDY CO.

# Model 1600/360 Magnetic Tape Recorder

# SECTION I

# GENERAL INFORMATION

# SECTION I

# **GENERAL INFORMATION**

#### PRINCIPLES OF OPERATION

Kennedy Incremental Recorders prepare IBM compatible tape from sources of data operating at random or non-standard rates. This means that tapes recorded can be mounted on standard computer tape drives and read as though they had been written by the computer itself.

All the characteristics of computer written tape are duplicated. Data characters are evenly spaced as required by the computer, parity bits are generated internally and properly placed on tape and gaps of standard lengths are inserted on command.

Incremental recorders are capable of producing evenly spaced data even though the data source may be operating in a sporadic or random manner. Continuous, or start-stop tape drives, cannot do this without use of a large and costly memory.

As an example, consider the problem of recording the output of an electric typewriter operated manually. Keys are struck with variable rapidity and if the recording tape were in smooth motion, the variability would result in uneven spacing on the tape. Even if the operator were capable of absolutely consistent typing, time for carriage return would differ from key stroke time.

In an incremental recorder, each character is recorded upon command. The tape then steps one increment--which may be 0.005" for 200 BPI; 0.0018" for 556 BPI; or 0.0012" for 800 BPI--then stops and awaits the next step command, thus the data is evenly recorded assuming that the maximum asynchronous stepping rate of the recorder has not been exceeded. The incremental recorder has numerous advantages over other methods of performing this function:

- 1. The recorder is an inexpensive device because tape speeds are very low.

- 2. No expensive memory is required.

- 4. Tapes produced are immediately usable on computers without conversion.

#### Stepping Mechanism

The heart of the incremental recorder is its stepping mechanism which must be accurate and reliable. Not only must its step size be accurate, but there must be no possibility that the step is not accurately transmitted to the tape itself. When the drive is stationary, as it may be for long periods of time, there must be no possibility that the tape may creep or otherwise move.

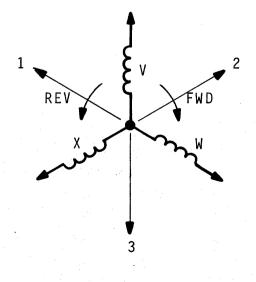

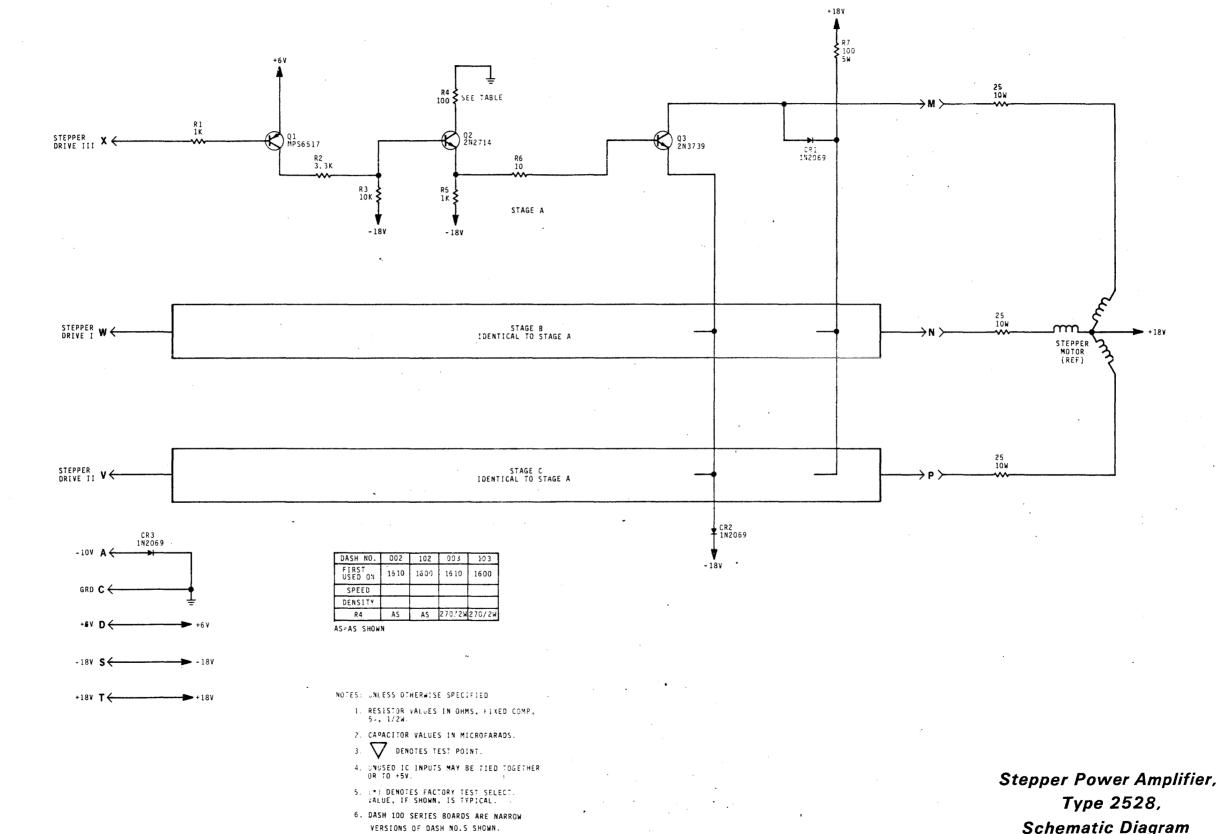

All these requirements together with the obvious requirement for high asynchronous stepping rates are met by the stepper motor drive used in Kennedy Incremental Recorders. The stepping motor itself is a special ultra-high speed, variable reluctance motor which moves 15<sup>o</sup> per step. Each position of the motor is strongly detented magnetically. This 15<sup>o</sup> step motion is reduced through precision gearing to the proper angular motion to advance the tape the required increment.

Tape is driven by a capstan and pinch roller in such a way as to make slippage a virtual impossibility at any speed.

The drive mechanisms on all standard Kennedy Incremental Recorders are identical--the only variation being in step size as determined by gear ratio and capstan diameter.

#### Electronics

Ease of application has been the primary consideration in design of the recorder interface. Internally, recorder electronics are all solid state, silicon. Integrated circuits are used in all appropriate applications.

#### INCREMENTAL RECORDING SYSTEMS

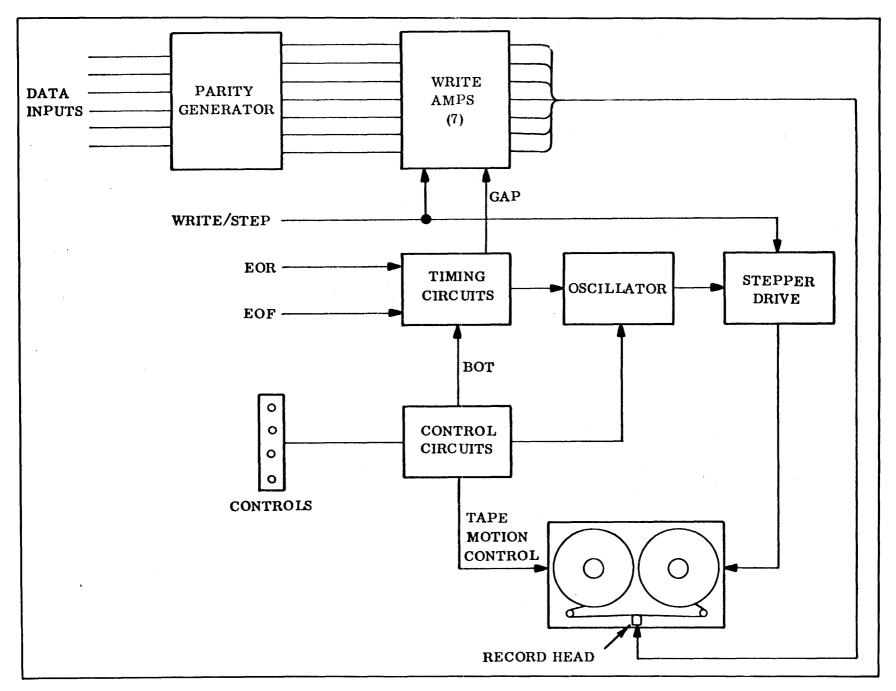

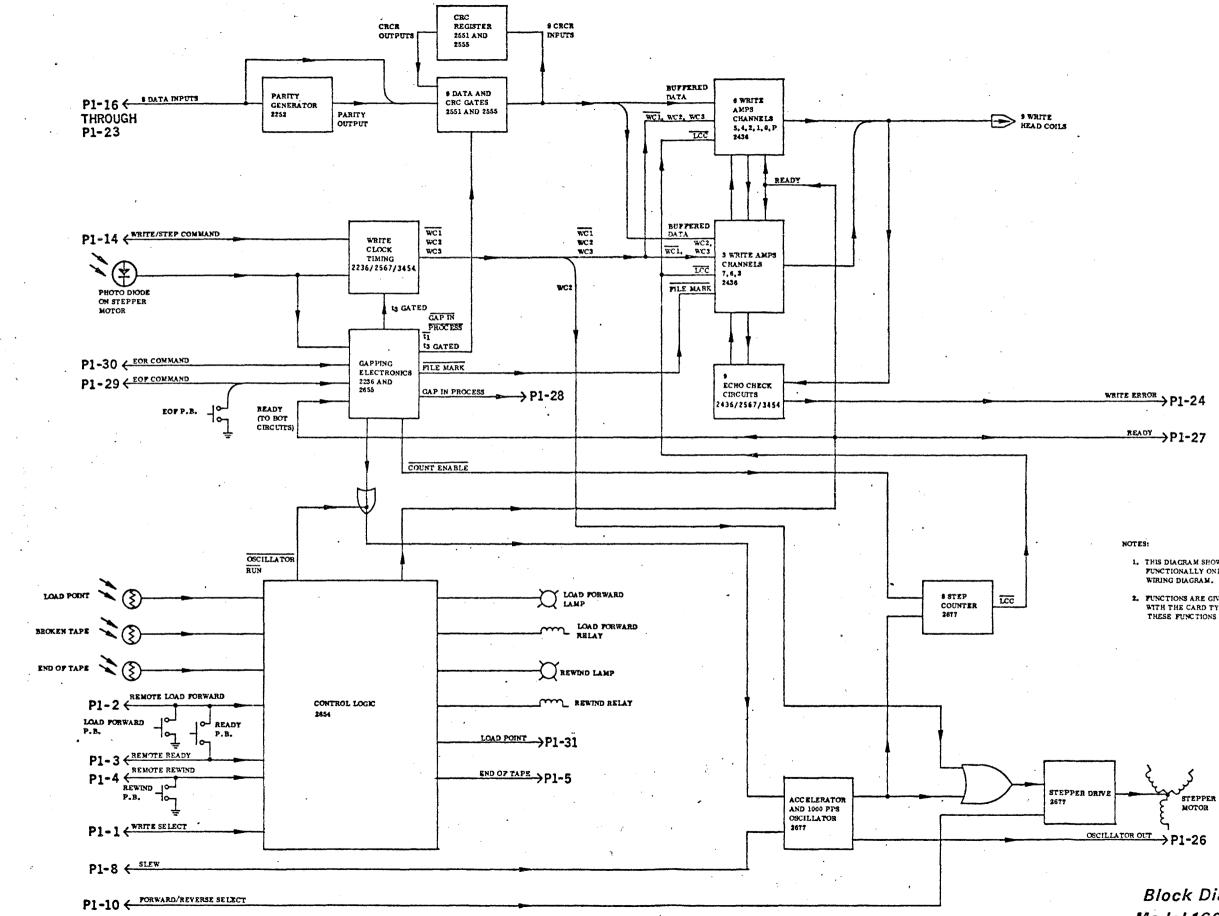

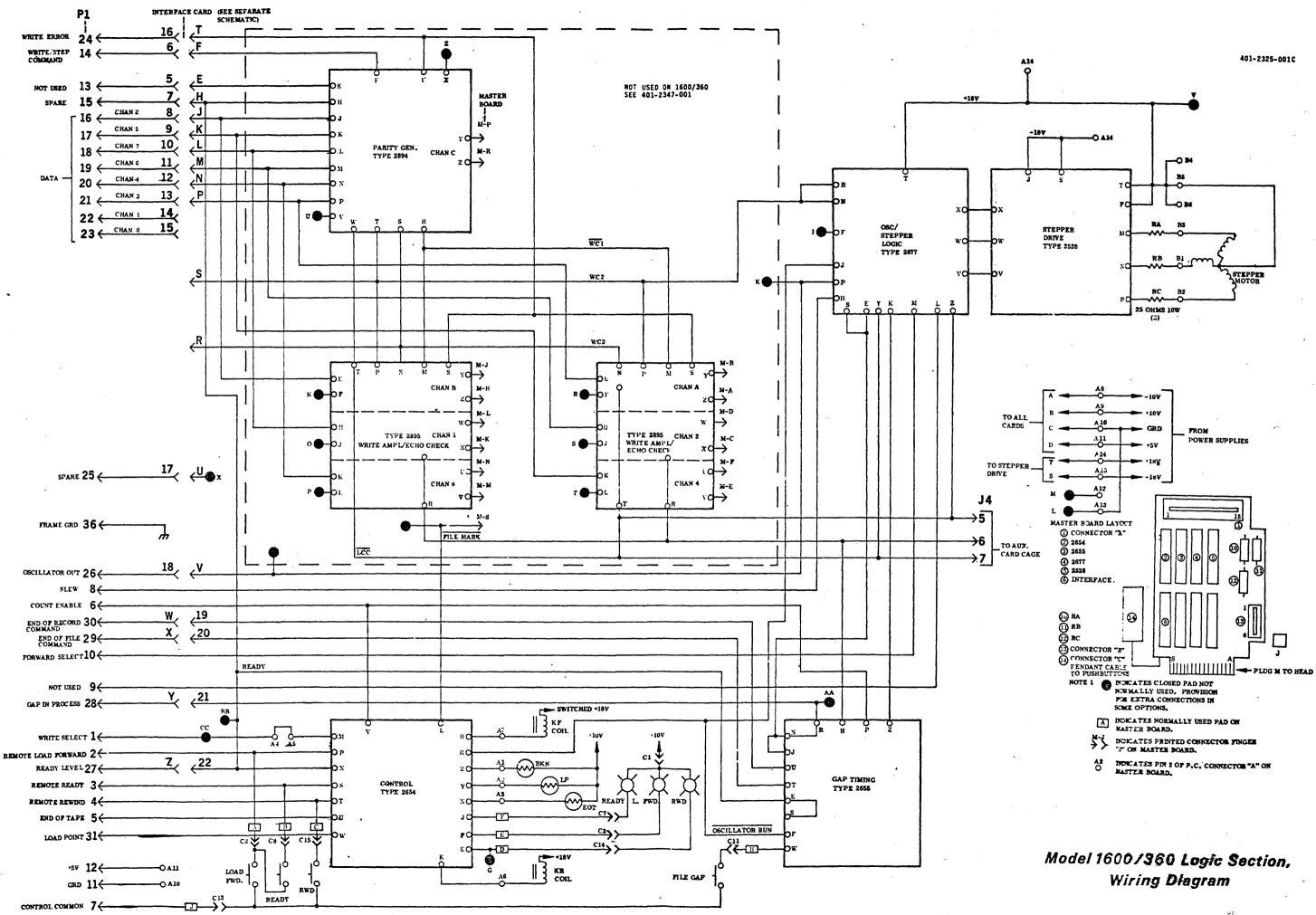

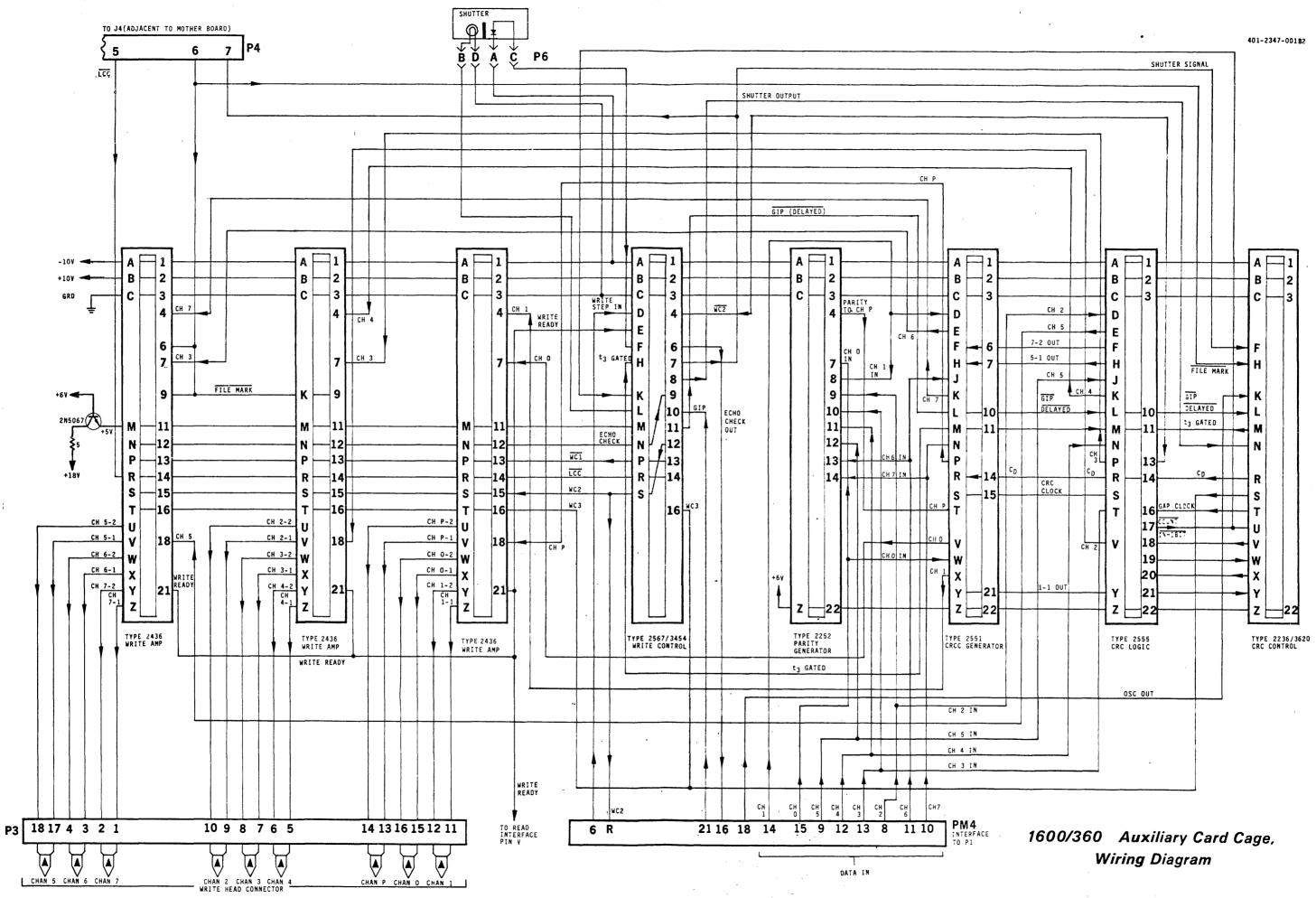

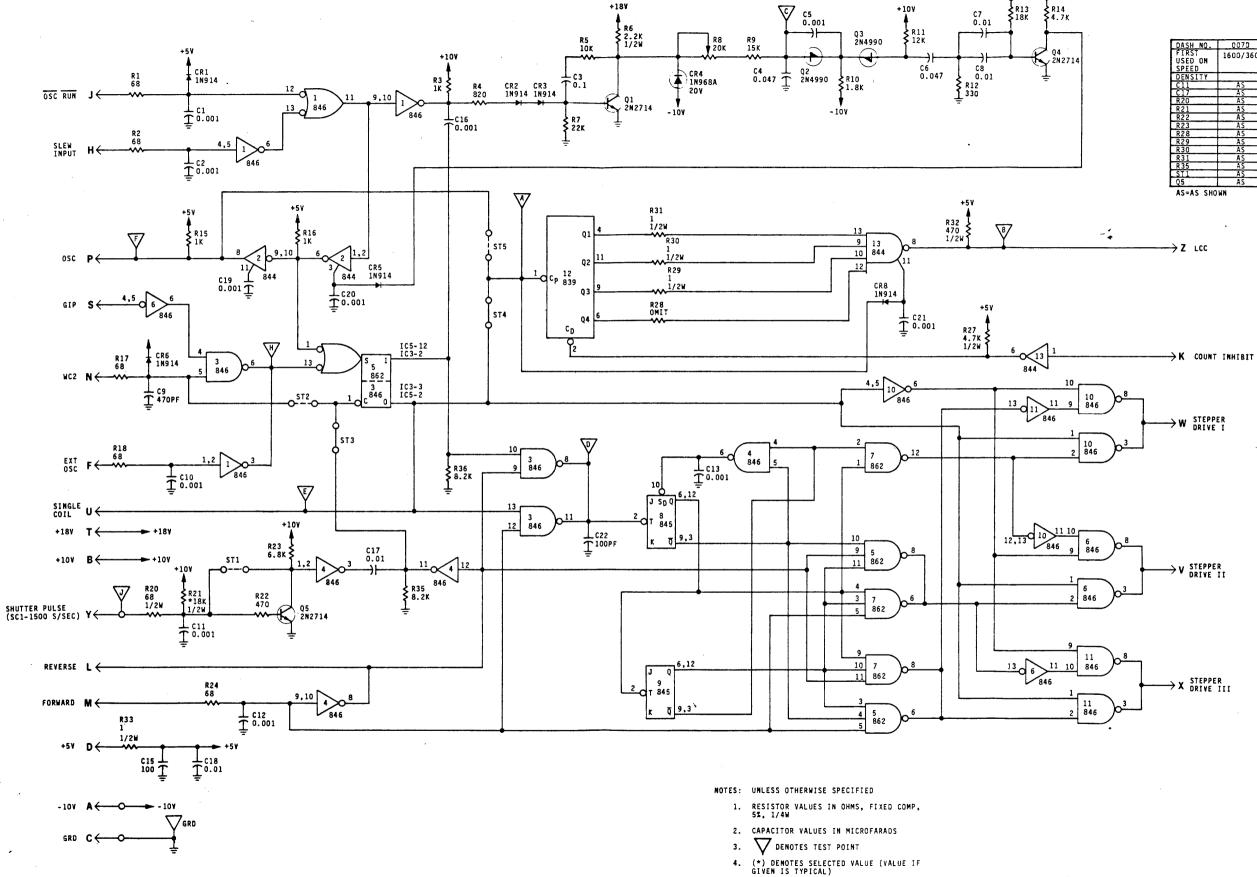

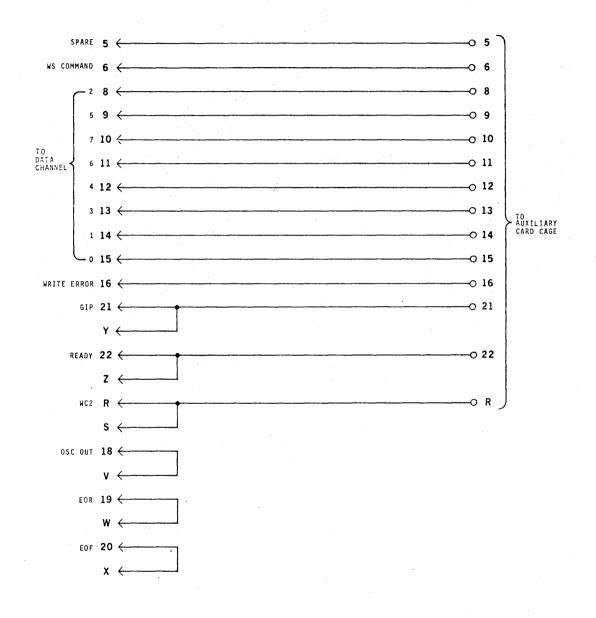

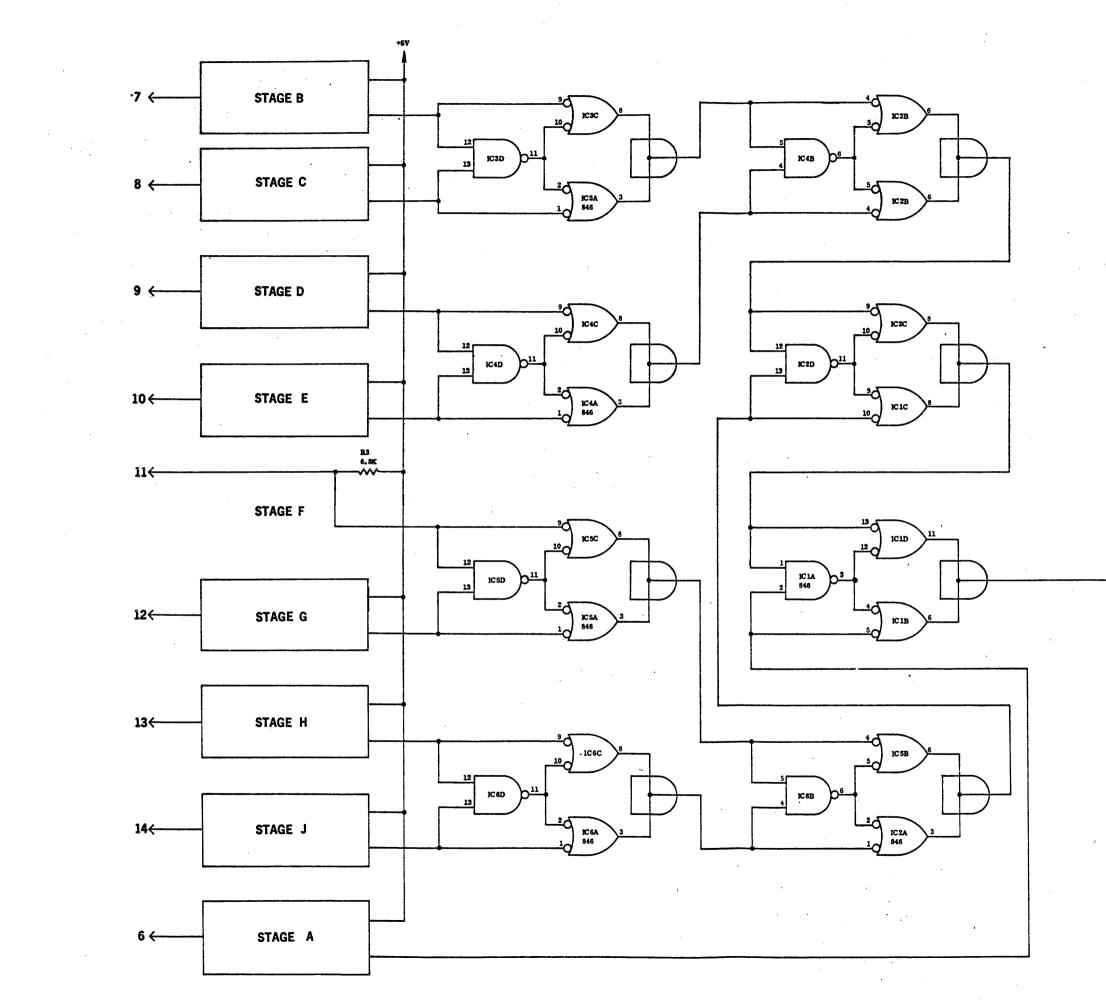

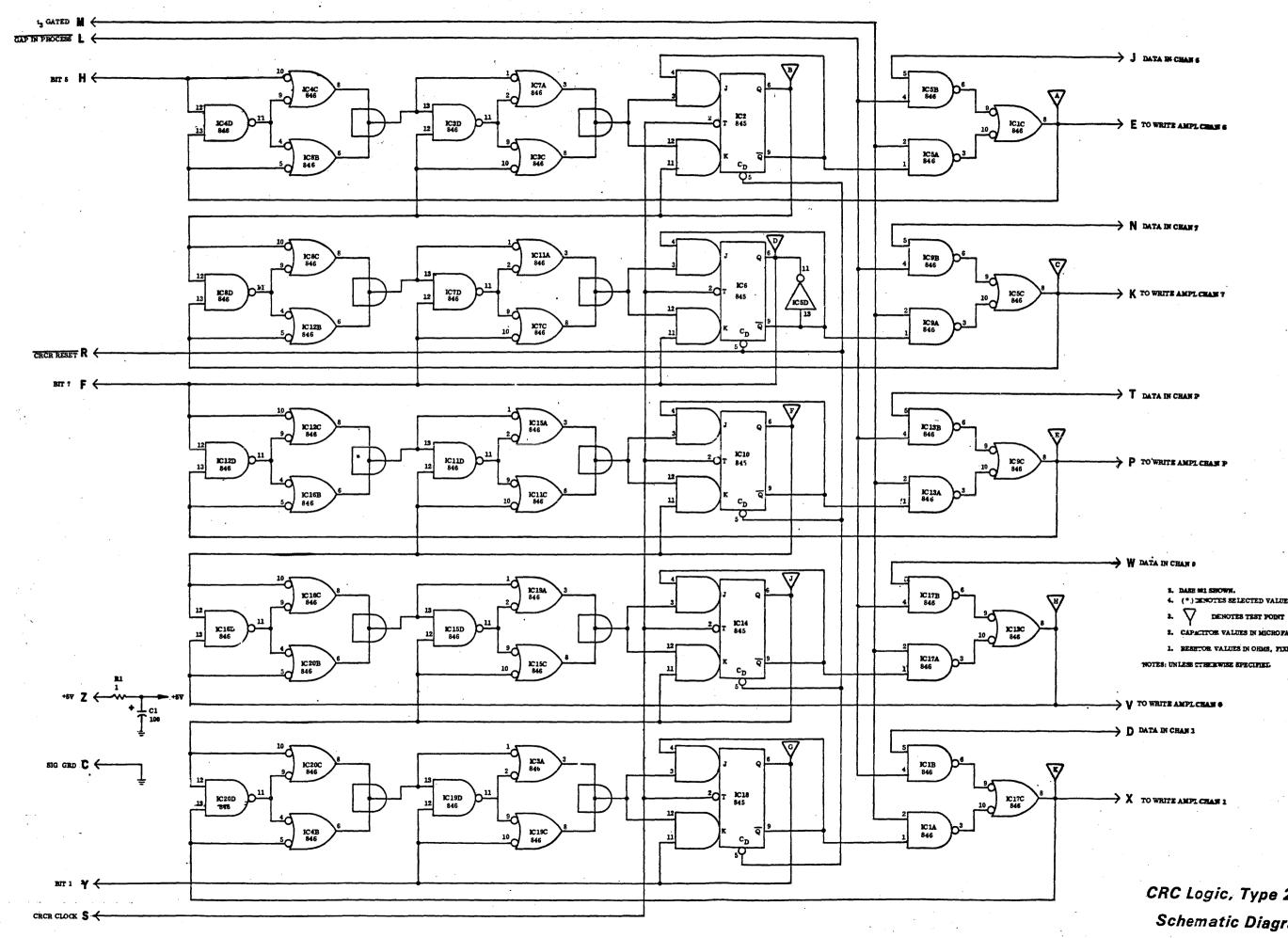

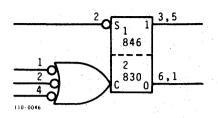

A block diagram is shown in Figure 1-1 of a typical Kennedy Incremental Recorder illustrating its principal components. It will be noted that electronics may be divided into sections having inter-related but separate functions.

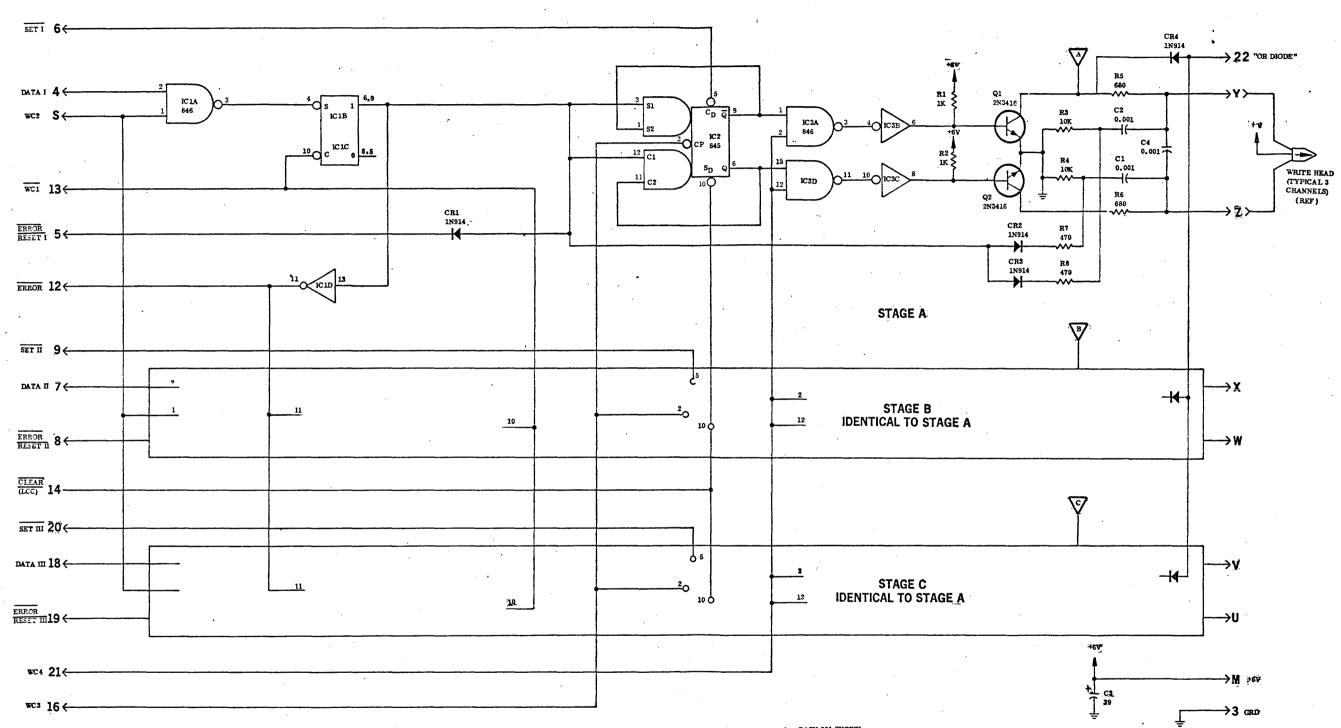

- 1. Parity-Write Amplifier section produces the actual recording on tape.

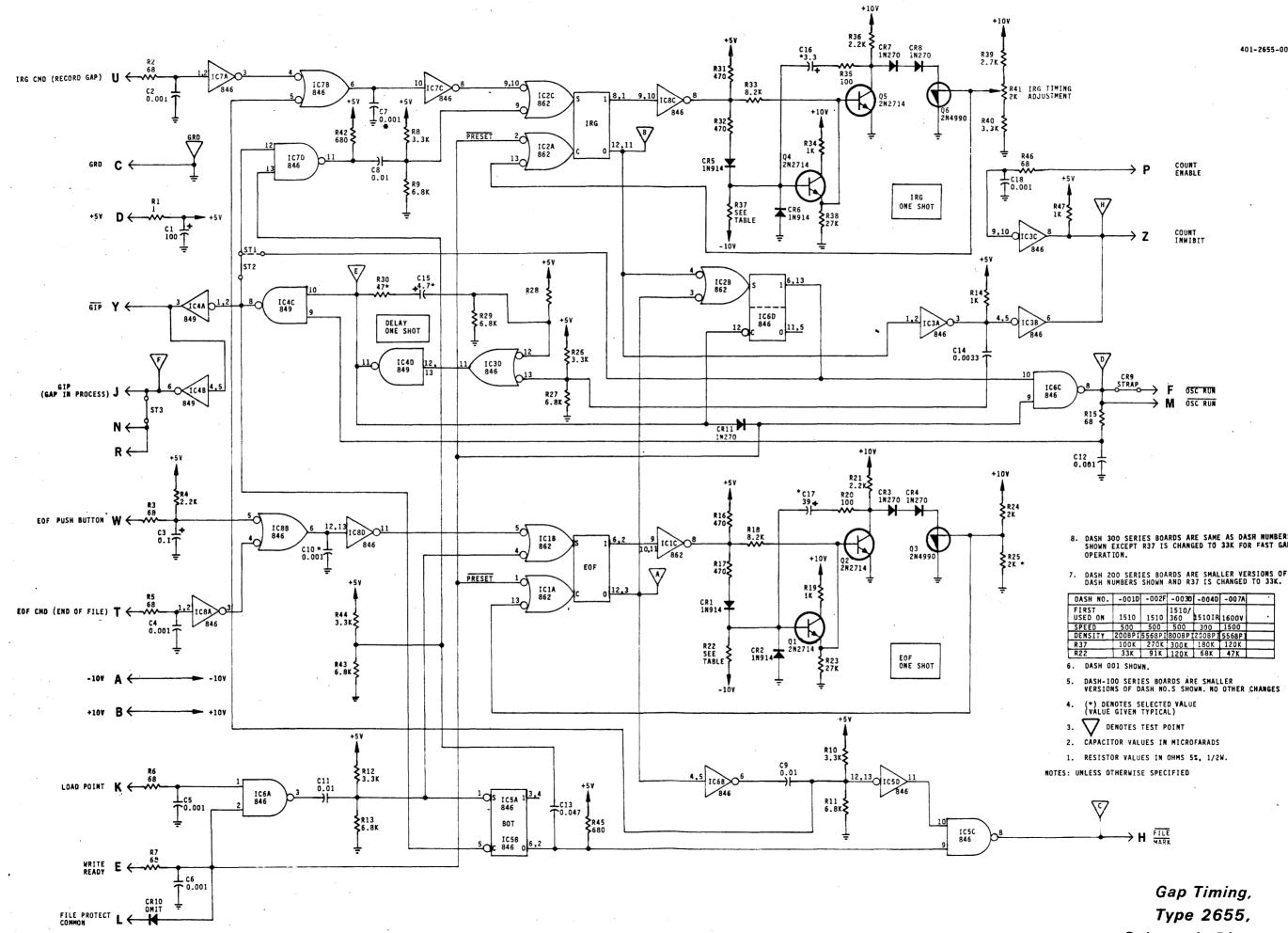

- 2. Gap generation system develops the drive signals necessary to insert gaps.

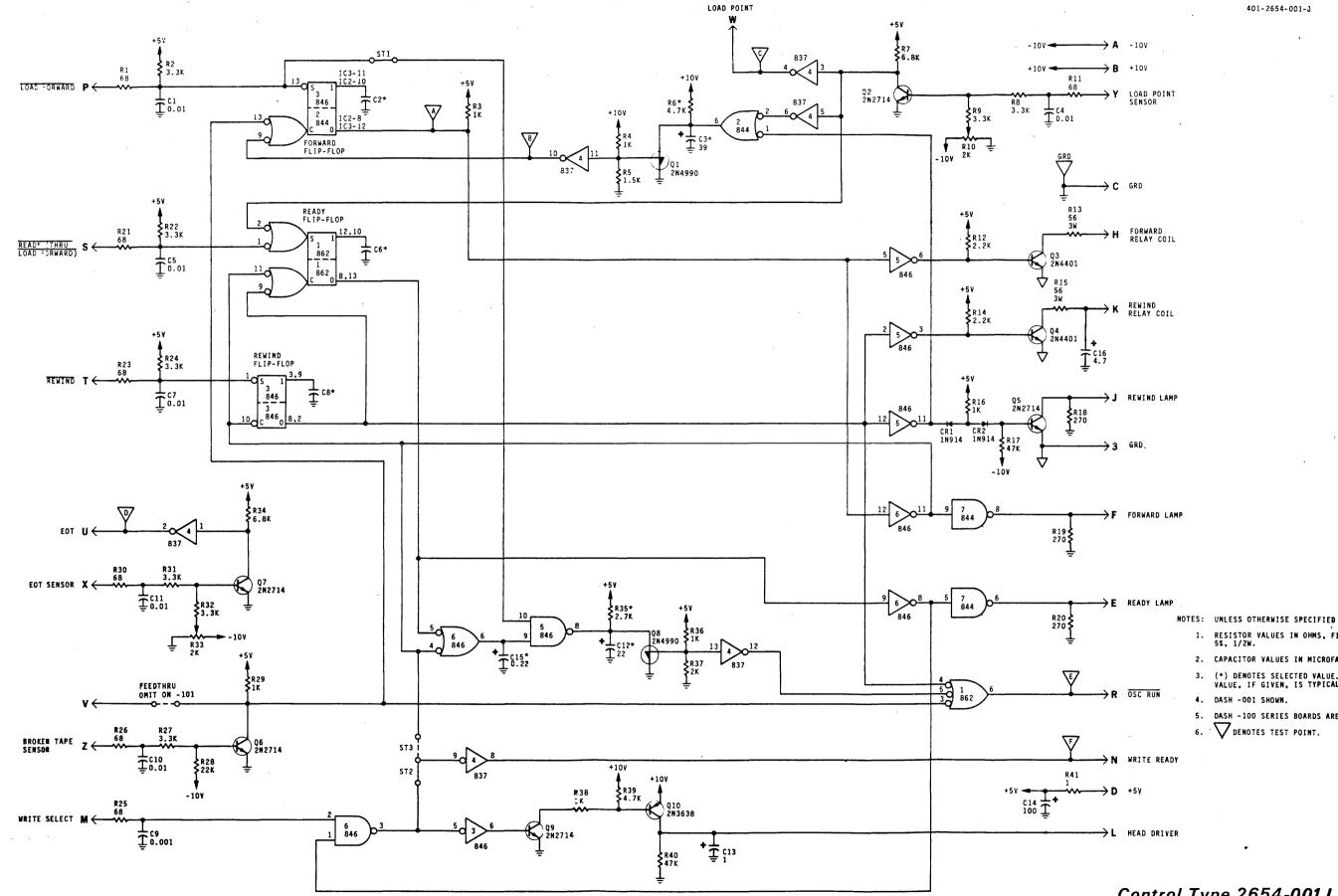

- 3. Control section provides circuits operable by pushbuttons and remote signals to control tape motion.

- 4. Stepper drive system receives step commands and produces signals which cause the stepper motor to increment.

Each of these sections will be shown in detail in this book.

In addition to the basic system shown, there are other functions which may be added for special purposes. They do not basically alter the system but add to its complexity.

Figure 1-1. Incremental Recording System

#### DIGITAL MAGNETIC RECORDING

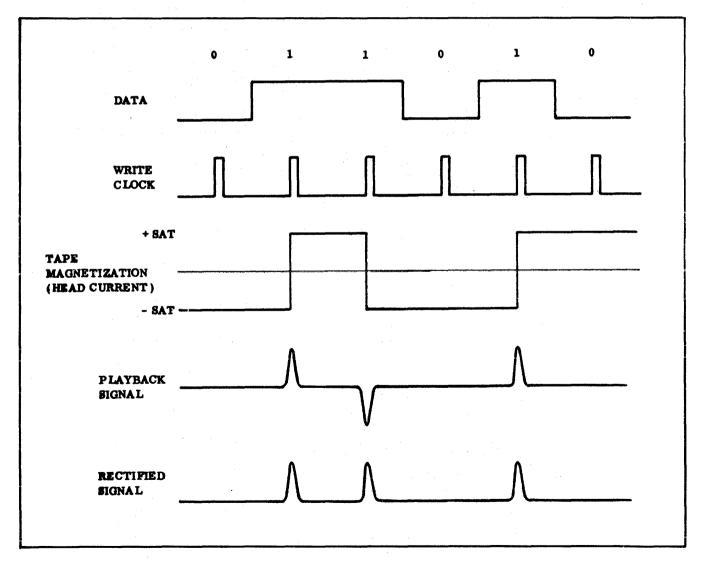

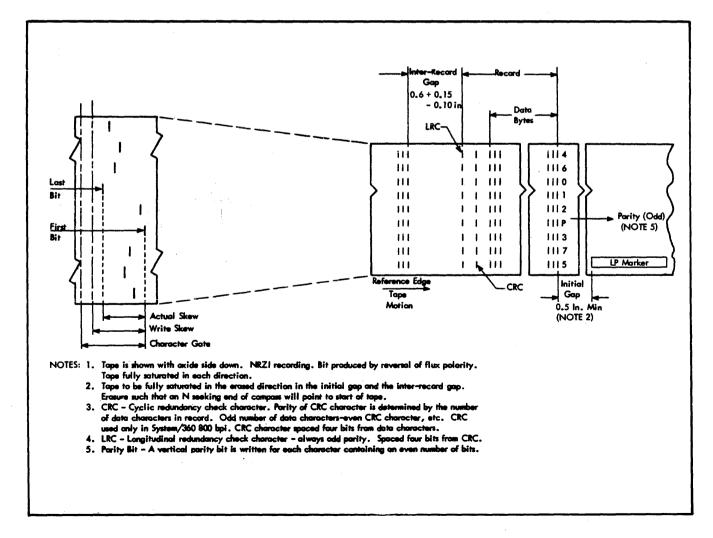

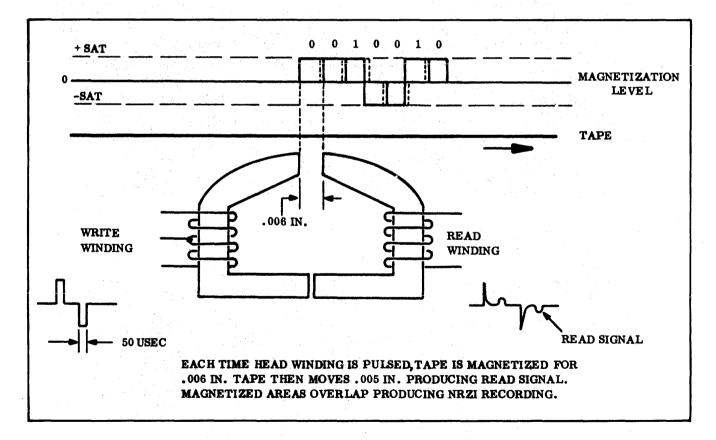

To record digital data on magnetic tape it is necessary, in some way, to magnetize the tape discretely to indicate binary ones and zeros. Of several different schemes, the IBM NRZI system has been most widely adopted. As shown in Figure 1-2, ones are represented by transitions between saturation magnetism (+ and -) on the tape.

Since magnetic heads respond to the rate of change of flux but not to steady flux, when tape is read output waveforms, such as those shown in Figure 1-2, are produced. No change in flux represents a binary zero and no voltage is recovered from the head.

In order to be usable as a recording scheme, the NRZI system requires at least one bit to be recorded for all characters; otherwise, in an all zero character there would be no indication that a character was supposed to be in that location.

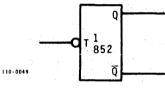

NRZI recording is implemented by driving current through the head winding in a direction determined by a flip-flop which toggles for each one to be recorded.

Figure 1-2. NRZ Waveforms

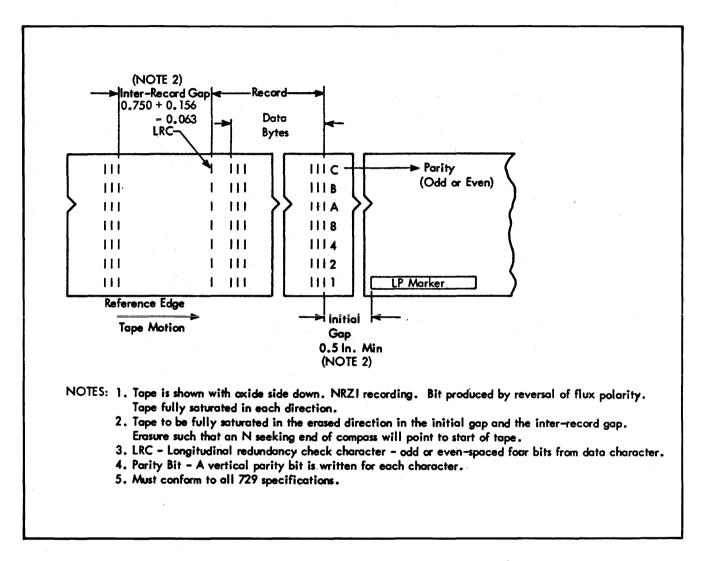

In a seven-track system, as shown in Figure 1-3, six of the tracks are data channels while the seventh is the parity channel. Parity may be either odd or even which is to say that bits may be added in the C track to make the sum of the bits in the character either odd or even. Even parity is used with BCD coding while odd parity is used when operating in the binary mode.

108-0007-0

Figure 1-3. Data Format - Seven Track

#### BCD

IBM seven-channel BCD code is shown in Figure 1-4. It will be noted that there are 63 combinations of the 6-data bits available to stand for numerics, letters, and special symbols. Actually, a somewhat larger variety of symbols may be used, depending upon the print chain, by leaving out some unused symbols and substituting others.

<u>الله</u>

| Collating       | Gra                                            | ohics      |               |               | Eig   | ht – Bil | Code    |      |     |                                                      |               |                                              | B          | CD             |     |         |

|-----------------|------------------------------------------------|------------|---------------|---------------|-------|----------|---------|------|-----|------------------------------------------------------|---------------|----------------------------------------------|------------|----------------|-----|---------|

| Sequence        | 8 Bit                                          | BCD        | 0             | 1             | 2     | 3        | 4       | 5    | 6   | 7                                                    | В             | A                                            | 8          | 4              | 2   | 1       |

| 00              | blank                                          | blank      | 0             | 1             | 0     | 0        | 0       | 0    | 0   | 0                                                    | 0             | 0                                            | 0          | 0              | 0   | 0       |

| 01              |                                                | •          | 0             | 1             | 0     | 0        | 1       | 0    | 1   | 1.1                                                  | 1             | 1                                            | 1          | 0              | 1   | 1       |

| 02              |                                                | <u>(</u> ) | 0             | 1             | 0     | 0        |         |      | 0   | 0                                                    | 1             |                                              |            | <u> </u>       | 0   | 0       |

| 03              | <u>      (                                </u> | E<br><     | 0             |               | 0     | 0        | 1       | -1   | 0   | 0                                                    |               |                                              |            |                | 0   |         |

| 04              | +<br>GM                                        | GM         | 0             |               | 0     | 0        |         |      |     |                                                      |               | 1                                            | 1          |                |     | 0       |

| 06              | 8                                              | & +        | 0             |               | 0     | 1        | 0       | 0    | 0   | 0                                                    |               |                                              | 0          | 0              | 0   | 0       |

| 07              | <u>s</u>                                       | S          | Ŏ             | l i           | 0     | i        | Ť       | Ō    | 1 i | t i                                                  | $\frac{1}{1}$ | o                                            | t i        | ŏ              | 1 i | t i l   |

| 08              | *                                              | *          | Ō             | 1             | Ō     | 1        | 1       | 1    | Ó   | 0                                                    | 1             | Ō                                            | 1          | ī              | 0   | 0       |

| 09              |                                                | ]          | 0             | 1             | 0     | 1        | 1       | 1    | 0   | 1                                                    |               | 0                                            | 1          | 1              | 0   | 1       |

| 10              | ;                                              | ;          | 0             | 1             | 0     | 1        | 1       | 1    | 1   | 0                                                    | 1             | 0                                            | 1          | 1              | 1   | 0       |

| 11              | MC                                             | MC         | 0             | 1             | 0     | 1        | 1       | 1    |     |                                                      |               | 0                                            | 1          | 1              |     |         |

| 12              |                                                |            | 0             | 1             | 1     | 0        | 0       | 0    | 0   | 0                                                    |               | 0                                            | 0          | 0              | 0   | 0       |

| 13              | ļ                                              | ļ/         | 0             | $\frac{1}{1}$ |       | 0        | 0       | 0    | 0   | $\left  \begin{array}{c} 1 \\ 1 \end{array} \right $ | 0             | <u>                                     </u> | 0          | 0              | 0   |         |

| 14              | %                                              | %(         | 0             |               |       | 0        | 1       | 1    | 0   | 0                                                    | 0             |                                              |            |                | 0   | 0       |

| 16              | WS                                             | WS         | 0             |               |       | 0        |         | 1    | 0   | 1 i                                                  | 0             | 1                                            | i i        |                | 0   |         |

| 17              |                                                |            | ŏ             | i             | 1     | 0        | i       | 1    | 1   | 0                                                    | ō             | 1                                            | t i        | 1              | ī   | Ö       |

| 18              | SM                                             | SM         | 0             | 1             | 1     | 0        | 1       | 1.   | 1   | 1                                                    | 0             | 1                                            | 1          | 1              | 1   | i       |

| 19              | 15                                             | <b>K</b>   | 0             | -1            | 1     | 1        | 1       | 0    | 1   | 0                                                    | 0             | 1                                            | 0          | 0              | 0   | 0       |

| 20              |                                                | / =        | 0             | 1             | 1     | 1        | . 1     | 0.   |     | 1                                                    | 0             | 0                                            | 1          | 0              | 1   |         |

| 21              | @                                              | @ '        | 0             | 1             |       | 1        | 1       | 1    | : 0 | 0                                                    | 0             | 0                                            | 1          | 1              | 0   | 0       |

| 22              | <b>▽</b>                                       |            | 0             |               | 1     | 1        | 1       |      | 0   | 1                                                    | 0.            | 0                                            |            | 1              | 0   |         |

| 23              | TM                                             | TM         | 9             |               |       |          |         |      |     | 1 0                                                  | 0             | 0                                            |            | $-\frac{1}{1}$ |     |         |

| 25              | 8                                              | 5          |               |               | 0     | 0        | 0       | 0    | 0   | i o                                                  | t i           |                                              | 1          | 0              | 1   | 0       |

| 26              | Ā                                              | A          | $\frac{1}{1}$ | 1 1           | ō     | ŏ        | Õ       | 0    | ŏ   | 1 i                                                  | $\frac{1}{1}$ | l i                                          | 0          | 0              | Ö   | Ť       |

| 27              | B                                              | B          | 1             | 1             | Ŏ     | 0        | 0       | 0    | 1   | 0                                                    | 1.            | 1                                            | 0          | 0              | 1   | 0       |

| 28              | С                                              | С          | 1             | 1             | 0     | 0        | 0       | 0    | 1   | 1                                                    | 1             | 1                                            | 0          | 0              | 1   | 1       |

| 29              | D                                              | D          | 1             | 1             | 0     | 0        | 0       | 1    | 0   | 0                                                    | . 1           | - 1                                          | 0          | 1              | 0   | 0       |

| 30              | E                                              | E          |               | 1             | 0     | 0        | 0       | 1    | 0   | 1                                                    | 1             | 1                                            | 0          | 1              | 0   | 1       |

| 31              | F                                              | F          |               | 1             | 0     | 0        | 0       | 1    |     | 0                                                    | 1             | 1                                            | 0          | 1              | 1   | 0       |

| <u>32</u><br>33 | G<br>H                                         | G<br>H     |               |               | 0     | 0        | 0       | 0    | 0   | 0                                                    |               |                                              | 0          | 1              | 1   | 1       |

| 34              |                                                | 1          | $\frac{1}{1}$ | $\vdash$      | 0     | 0        | 1       | 0    | 0   |                                                      |               |                                              |            | 0              | 0   | - i - i |

| 35              | ð                                              | δ          |               | +             | 0     | Ĭ        | Ö       | Ö    | ŏ   | 0                                                    | +             | 0                                            | $\vdash$ i | 0              | Ť   | Ö       |

| 36              | J                                              | Ĵ          | ti            | i             | 0     | 1        | 0       | 0    | 0   | 1                                                    | 1             | 0                                            | 0          | Ō              | ò   | - i     |

| 37              | K -                                            | ĸ          | 1             | 1             | 0     | 1        | 0       | 0    | 1   | 0                                                    | 1             | 0                                            | 0          | 0              | 1   | 0       |

| 38              | L                                              | L          | 1             | 1             | 0     | 1        | 0       | 0    | 1   | 1                                                    | 1             | 0                                            | 0          | 0              |     |         |

| 39              | M                                              | M          |               | 1             | 0     | 1        | 0       | 1    | 0   | 0                                                    | 1             | 0                                            | 0          | 1              | 0   | 0       |

| 40              | N                                              | N          | 1             |               | 0     | · ]      | 0       | 1    | 0   |                                                      |               | 0                                            | 0          |                | 0   |         |

| 41 42           | O<br>P                                         | O<br>P     |               |               | 0     | 1        | 0       | 1    | 1   | 0                                                    | 1             | 0                                            | 0          | 1              |     | 0       |

| 42              | Q                                              | à          | 1             | <u> </u>      | 0     |          | 1       | 0    | 0   | 0                                                    | 1             | 0                                            |            | 0              | Ö   | Ö       |

| 44              | R                                              | R          | $\frac{1}{1}$ | 1             | 0     | 1        | -i      | 0    | 0   | 1                                                    | 1             | 0                                            | 1          | 0              | ō   | -Ť-     |

| 45              | RM                                             | RM         | i             | 1             | 1     | 0        | 0       | Ō    | 0   | 0                                                    | 0             | 1                                            | 1          | Ö              | 1   | 0       |

| 46              | S                                              | S          | 1.            | 1             | 1     | 0        | 0       | 0    | 1   | 0                                                    | 0             | 1                                            | -0         | 0              | 1   | 0       |

| 47              | T                                              | T          | . 1           | 1             | 1     | 0        | 0       | 0    | 1   | 1                                                    | 0             | 1                                            | 0          | 0              | 1   | 1       |

| 48              | U                                              | U          | 1             | 1             | 1     | 0        | 0       | 1    | 0   | 0                                                    | 0             | 1                                            | 0          | 1              | 0   | 0       |

| 49              | V                                              | V          | 1             | 1             | 1     | 0        | 0       | 1    | 0   | 1                                                    | 0             | 1                                            | 0          | 1              | 0   | 1       |

| <u>50</u><br>51 | W<br>X                                         | W<br>X     |               |               | 1     | 0        | 0.<br>0 | 1    |     | 0                                                    | 0             | 1                                            | 0          | $-\frac{1}{1}$ | 1   | 0       |

| 52              | Ŷ                                              | Ŷ          |               |               |       | 0        | 1       | 0    | 0   | 0                                                    | 0             |                                              | 1          | 0              | 0   | 0       |

| 53              | Z                                              | z          | +             | 1             | t i c | 0        | 1       | Ő    | 0   | Ť                                                    | Ő             | 1                                            | 1          | 0              | Ō   | Ť       |

| 54              | 0                                              | 0          | 1             | 1             | 1     | 1        | 0       | 0    | Ō   | 0                                                    | 0             | 0                                            | . 1        | 0              | 1   | 0       |

| 55              | 1                                              | 1          | 1             | - 1           | 1     | 1        | 0       | 0    | 0   | 1                                                    | 0             | 0                                            | 0          | 0              | 0   |         |

| 56              | 2                                              | 2          | 1             | 1             | 1     | 1        | 0       | 0    |     | 0                                                    | 0             | 0                                            | 0          | 0              | 1   | 0       |

| 57              | 3                                              | 3          |               | 1             | 1     | 1        | 0       | 0    | 1   |                                                      | 0             | 0                                            | 0          | 0              | 1   |         |

| 58              | 4                                              | - 4        | $\frac{1}{1}$ | 1             | 1     | 1        | 0       | . 1. | 0   | 0                                                    | 0             | 0                                            | 0          | 1              | 0   | 0       |

| <u>59</u><br>60 | 5                                              | 5          |               |               | 1     | 1        | 0       | 1    | 0   | 0                                                    | 0             | 0                                            | 0          |                | 1   | 0       |

| 61              | 0<br>7                                         | 0<br>7     |               |               |       | 1        | 0       | 1    |     |                                                      | 0             | 0                                            | 0          |                | 1   | 1       |

| 62              | 8                                              | 8          |               | 1             | 1     | r        | 1 I     | 0    | i o | Ö                                                    | 0             | 0                                            | ĩ          | 0              | 0   | Ö       |

| 63              | 9                                              | 9          | t i           | l i           | i     | i        | 1       | 0    | 0   | 1                                                    | Ō             | 0                                            | 1          | 0              | 0   | 1       |

|                 |                                                |            |               |               |       |          |         |      |     |                                                      |               |                                              |            |                |     |         |

Figure 1-4. Eight Bit Code - BCD Relations

#### Binary Mode

In the binary mode, the computer is programmed to accept tape characters as binary numbers. This mode obviously is useful only with straight numeric input.

Thus, a six-bit character can represent a six-digit binary number, or 0-63. By using more than one character, larger numbers may be represented. In some cases this results in considerable saving in space on the tape and in computer time. For example, the number 56 would require two character spaces in BCD but only one in binary. Obviously, odd parity must be used because six zeros can be a perfectly valid portion of a binary number.

#### Nine-track Coding

Nine-track tape, as used in IBM System/360, uses a modified ASCII code also shown in Figure 1-5. Parity in the nine-track 800 BPI system is always odd.

Operation in binary mode is possible with proper programming. An interesting possibility is recording two 4-bit numerics per byte with consequent doubling of effective data rate.

Figure 1-5. Data Format - Nine Track

#### Longitudinal Parity

In writing blocks on tape, it is necessary to return to the reference magnetic condition in the gaps if records are to be rewritten at any future time. Otherwise, the direction for any track would not be known and spurious characters would result. In returning to reference state those tracks which are in the opposite state, spurious characters are also generated. This difficulty has been cleverly converted to an asset in the NRZI system by accurately locating the "spurious" character and using it as a check.

Since it started and returned to reference level, each track must have had an even number of transitions. The number of transitions are counted and if the result is odd, an error is indicated.

The Longitudinal Check Character, as it is called, is spaced four or five character spaces from the end of the block so that it will not be interpreted as data.

#### Other Checks

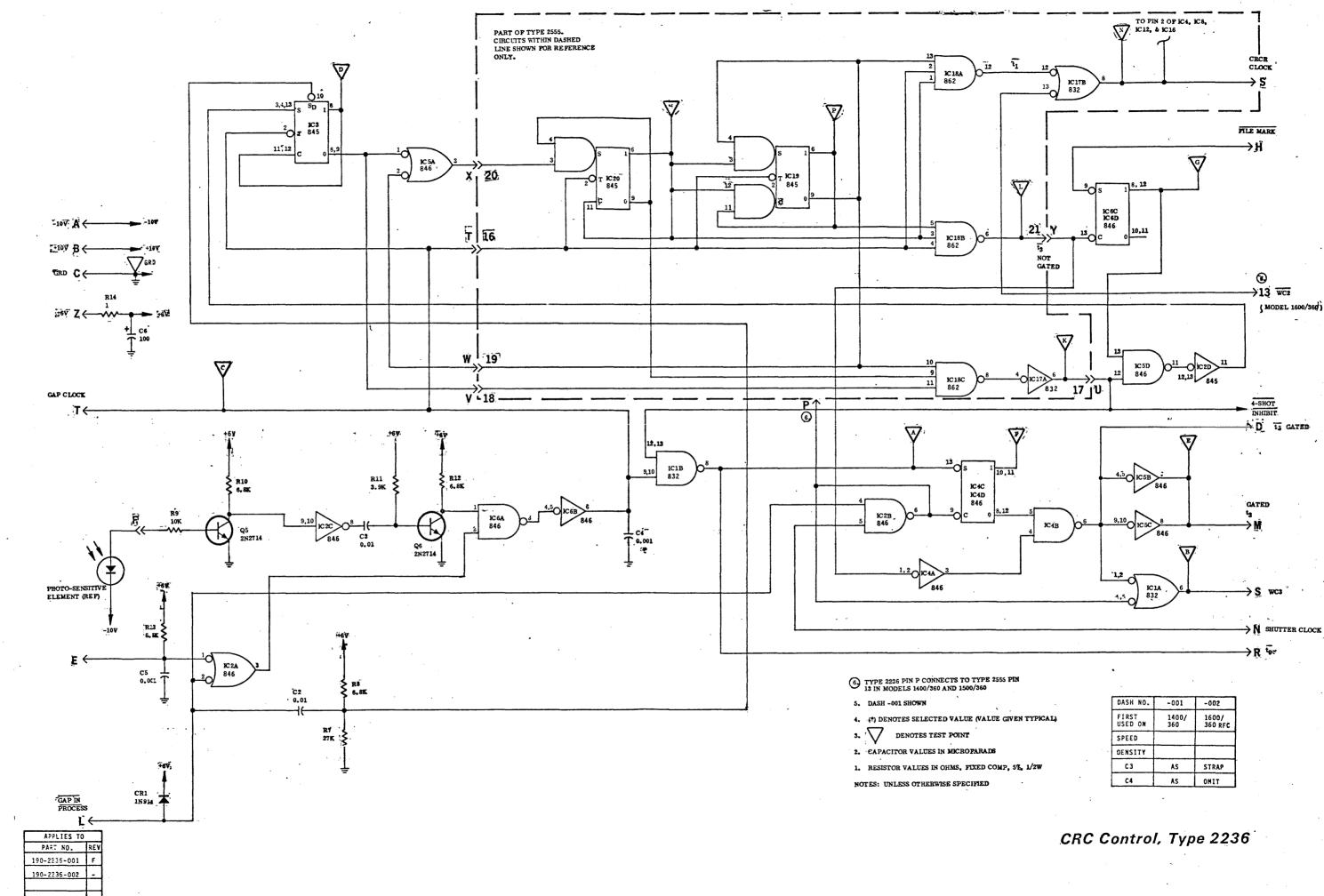

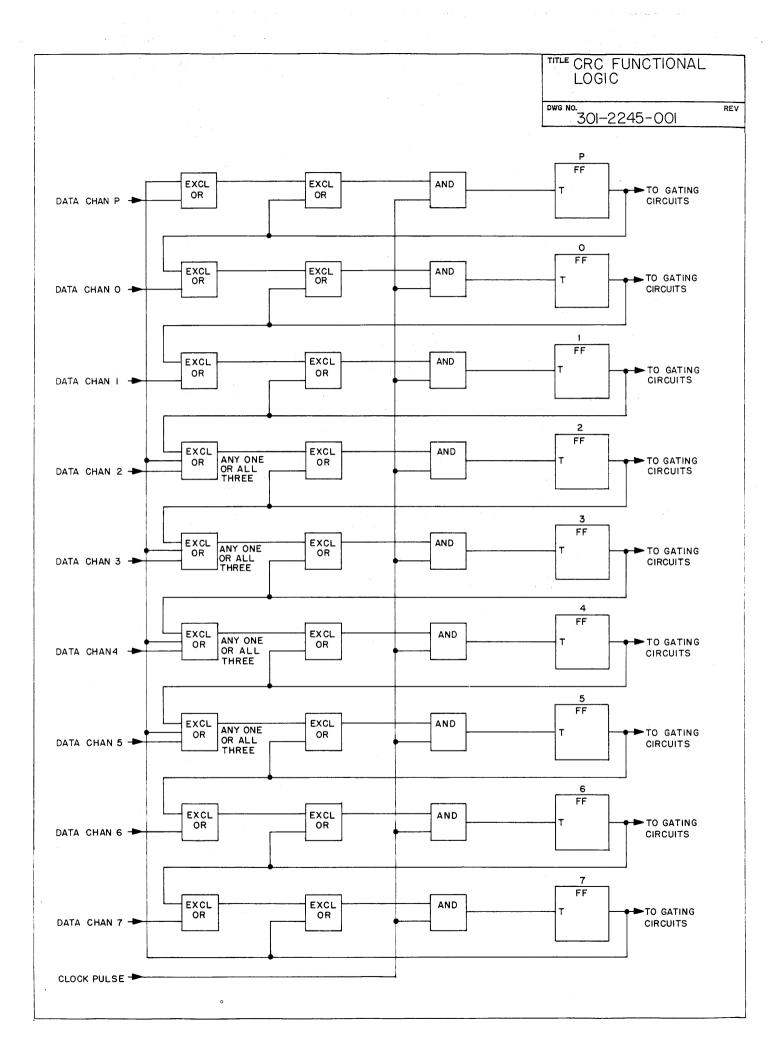

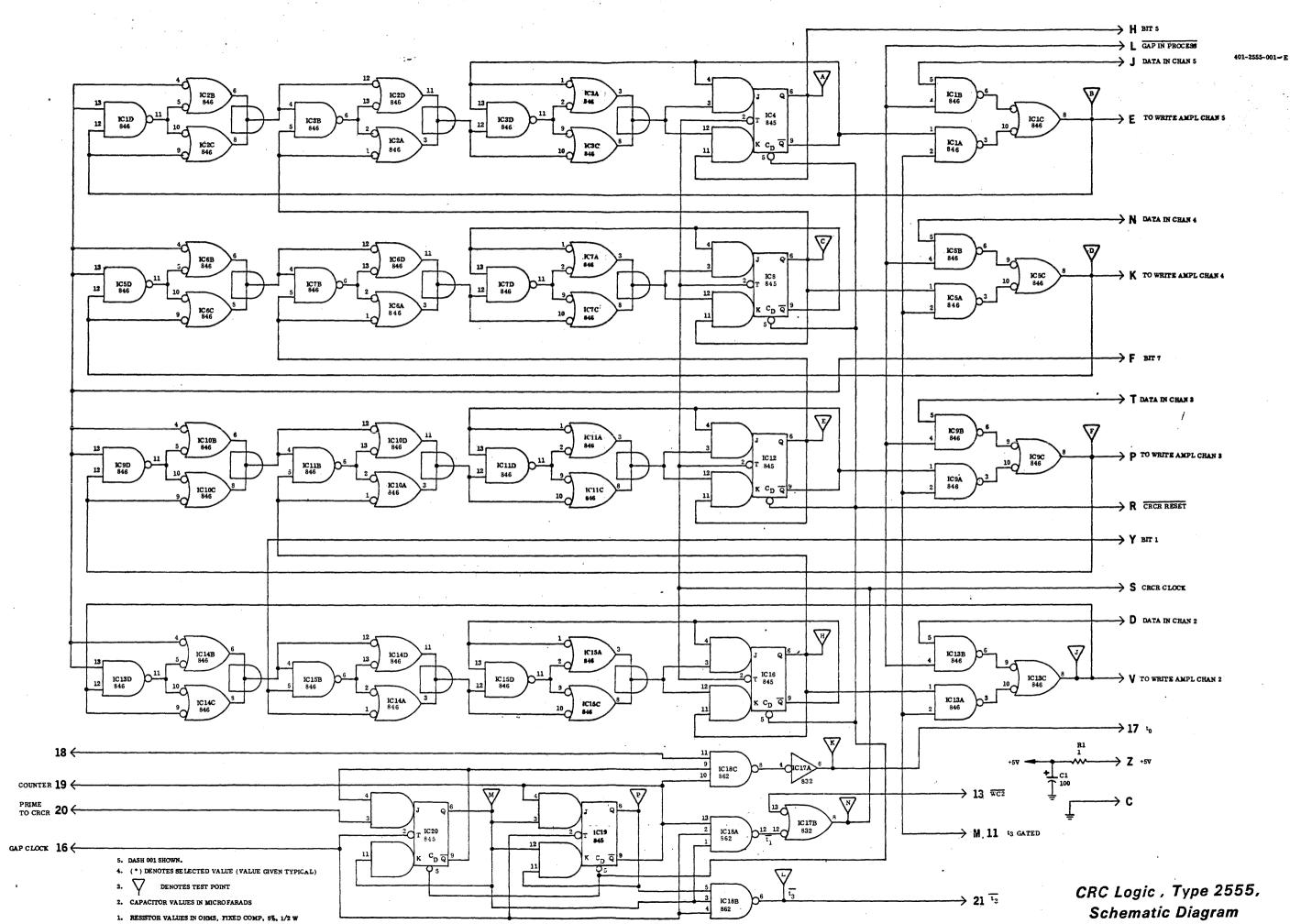

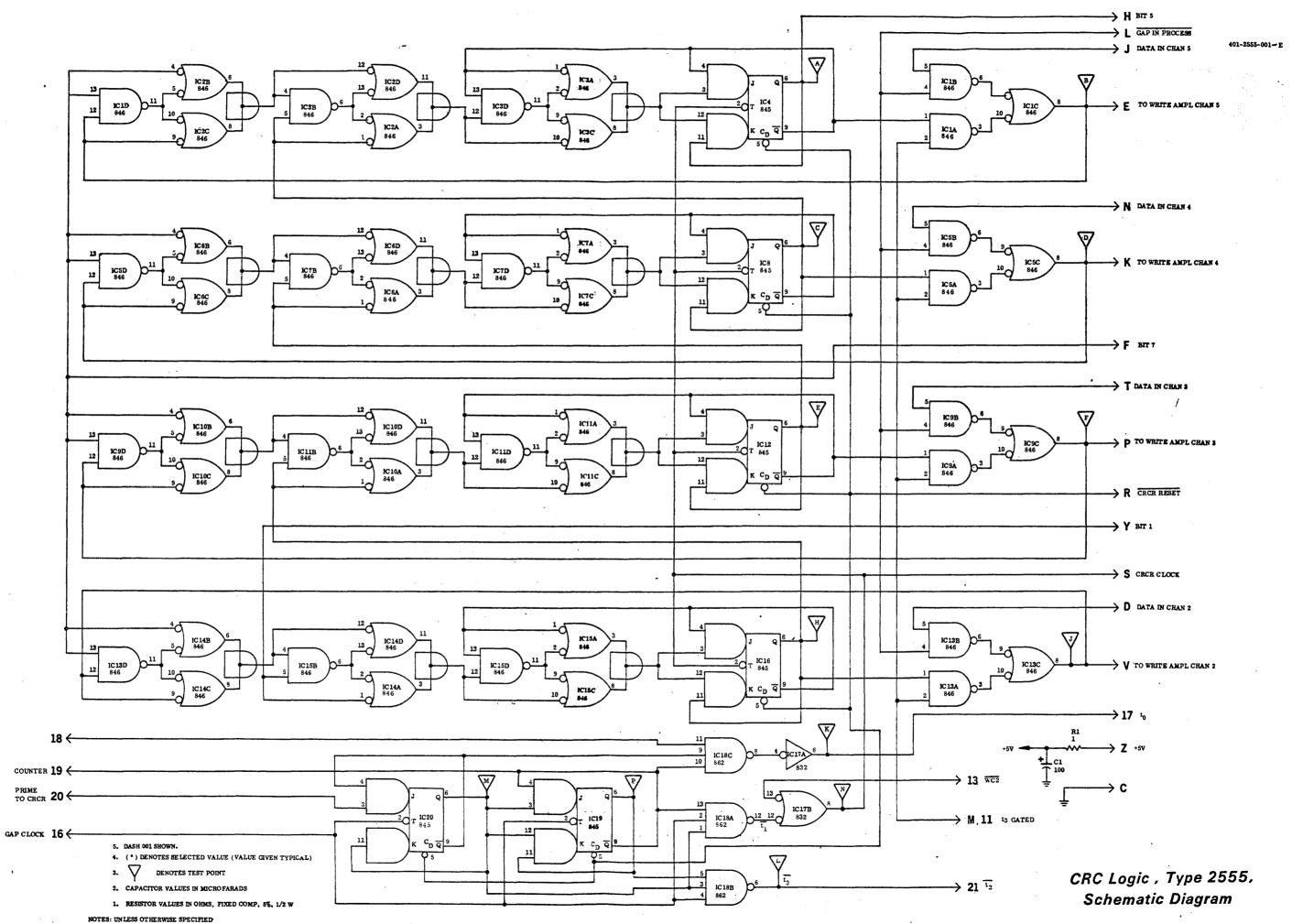

In the newer IBM transports built for 800 BPI, nine-track recording, another check, called "Cyclic Redundancy Check", is included. This check has the ability to direct correction of a certain limited class of errors. Kennedy Incremental Recorders built for System 360 compatibility include circuits for generation of the CRC.

Additionally, in the nine-track system there is a "Lost Character Check" which implements the error correction routine. In this check a character is expected to have been read within 15 clock times of the last. If it has not been read in 17 clock times, an error is flagged.

This requirement places fairly stringent criteria on character spacing accuracy. While not used in the seven-track 2400 series transport, lost character detection circuits are retained placing the same restrictions on spacing as in the nine-track system.

#### FLUX CHECK<sup>™</sup>

Flux Check<sup> $\mathbb{M}$ </sup> is a system of checking data as it is written on tape. A true read-after-write check, it uses only one gap for both operations. If a character is incorrectly written for any reason, including tape flaws, an error signal is produced before another character is due to be written.

Available as an option on nearly all Kennedy Incremental Recorders, Flux Check<sup>™</sup> is the ultimate safeguard against lost data.

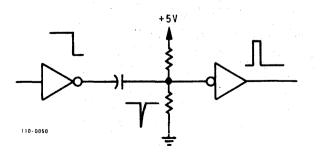

While it may be argued with perfect logic that good tape operating in a good machine will not have any errors recorded on it, the human factor cannot be entirely eliminated, and once precious data is lost it may be impossible to replace. Basic principles of Flux Check<sup>M</sup> recording are shown in Figure 1-6. Magnetically neutral tape is passed over the head which is built with a 0.006" gap--wider than the widest increment, 0.005" at 200 BPI. The head has two windings, a write winding and a read winding. Short pulses of current in the head magnetize a portion of the tape as wide as the gap. Polarity of the pulses is controlled by a flip-flop in the Flux Check<sup>M</sup> Write Amplifier.

If zeros are being recorded, pulses are all in the same direction. This produces smooth magnetism on the tape as required for zeros. Polarity of write pulses reverses for ones. After writing, the tape moves, pulling the recorded section out of the gap and inducing a signal in the read windings.

Write pulses are suppressed by the Flux  $Check^{M}$  read amplifiers; but the read signal is amplified and compared on a bit-by-bit basis with the input data. If disagreement is found, an error is signalled.

Time to signal an error does not exceed 1.9 ms. This allows for a maximum operating speed of 500 steps per second, still retaining the ability to locate an erroneous character before the next is recorded.

#### READERS

Kennedy Company Incremental Magnetic Recorders may also be equipped for reading as well as writing tape. Model numbers are suffixed by designation as shown in the following examples:

| 1600 <b>R</b> | Incremental Record/Continuous Read  |

|---------------|-------------------------------------|

| 1600IR        | Incremental Record/Incremental Read |

| 2059RO        | Continuous Read Only                |

Principles and equipment requirements for the various models are identical or similar and, in many cases, the read portion of the machine is modular to simplify interfacing and construction.

The description in this section is general in nature. Specifics for a particular model may be found in the Performance Specifications section and in the circuit descriptions of the circuit cards used.

#### File Protect Switch

Kennedy recorders equipped for both reading and writing are also equipped with a File Protect Switch and Indicator Light. This switch detects the presence of the File Protect Ring in the reel of tape mounted on the supply side of the machine. If this flexible ring is removed from the reel, it indicates that the tape must not be written on under any circumstances. This treatment is often reserved for library and program tapes or, in some instances, the ring may be removed immediately after the tape is written to prevent erasure of a tape.

On a machine so equipped it is impossible to select the Write mode in the machine or to write or erase data on tape when the File Protect Ring has been removed from the reel. If an attempt is made to write on a tape which does not have the File Protect Ring in place, the red FILE PROTECT Light will glow either immediately or when the machine goes into Ready, depending on the model, to indicate to the operator that he has made a procedural error. An indication of this is also provided to the interface plug so that external equipment may sense this condition. Machines which are Write Only or Read Only do not have a File Protect Switch.

#### Controls and Loading Procedure

The controls and loading procedure for a Read machine are identical to those of a Write Only machine. However, when the tape is loaded, no Beginning of Tape gap is inserted. The read head will come to a stop at a point prior to the place where recording began. In other words, it will stop immediately when the Load Point sensor is under the photo cell instead of the customary 3-1/2" after this point.

#### Interface Connector

On all recent Kennedy Incremental Recorders a separate interface connector is provided for the functions associated with reading. This enables a machine equipped for reading to be directly substituted for a Write Only machine using the same wiring. The read signals do not compromise or affect the normal signals on the connector associated with writing.

#### Skew Delay

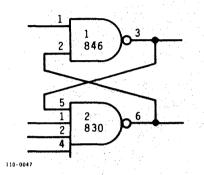

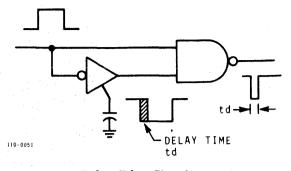

In writing a tape certain tolerances with regard to the gap scatter in the heads, the skew of the head (that is, the failure of the gaps to be absolutely perpendicular to the tape), and other causes can accumulate in tolerances which make it necessary to provide electronic circuitry to compensate for these variables and to assure that the output data is timed correctly. These conditions are aggravated when a tape is written on one machine and read on another which is a normal circumstance. The common method for achieving this is to read each track independently and sense the first "one" that is detected on any track. This is done by connecting the outputs of all of the data tracks into an "OR" gate. The first "one" then triggers a delay which is usually set to be approximately 45% of the prescribed time for one character.

At this time the data in the output register is changed to reflect the new character, and a few microseconds later a Clock pulse is provided to enable strobing this data into the external system. This assures that data is transferred at a time when it is valid and correct and eases the interfacing of the machine to an external system. (On old machines the output register was not provided, and Data pulses and Clock pulses were coincident with each other.)

#### **Gap Detector**

Another output provided at the interface connector is the Gap Detector output. In either Incremental Read or Continuous Read machines a Clock pulse should be detected within a prescribed time after a Read/Step or Read command is given. Internal circuitry has been provided to detect whether or not this clock is available within approximately two or three time intervals. If no clock is received within this time, then it follows that the read head must be passing through a gap. This output is called the Gap Detect output and may be used to control stopping of a Continuous machine in the gap.

#### Longitudinal Check Character

This Gap Detect output is also used internally to inhibit the Clock pulse for the Longitudinal Check Character. The Longitudinal Check Character will appear at the data output terminals and will remain there during the gap until the first character of the succeeding block is detected. However, the Clock pulse for it is deliberately inhibited since, in most simplified systems where a reader of this type is employed, the character is not desired. Where it is required, it may be reconstituted by a simple modification to one of the circuit cards. The factory should be consulted regarding this if it is required.

#### Error Rates

Maximum error rates are difficult to define. Many variables, such as tape condition, environment, etc., enter the picture. Continuous reading with error rates of less than one error in  $10^6$  characters is reasonable to expect under ordinary conditions and may be improved several orders of magnitude with reasonable precautions. Incremental reading is much more difficult to implement and is less tolerant of tape imperfections. Therefore, typical error rates may be expected to be slightly higher.

#### CONTINUOUS READING

On machines equipped for Continuous reading, the tape is run at a fixed speed and should be stopped only in Inter-Record gaps. In most recorders this is done by running the stepper motor at a slewing rate fast enough so that the steps blend together into a smooth continuous motion. This speed is usually 1000 steps per second.

On some machines, such as the 3700 Series, an auxiliary capstan motor is employed to run the tape at a pre-selected speed of up to 30 inches per second. Other machines, such as the 2059 Series, use a servo controlled dc motor system which allows pre-selected tape speeds of 1.5 inches to 6 inches per second. All of these systems have in common the fact that:

- 1. the tape is running at a pre-selected fixed speed,

- 2. a data register is filled at a synchronous rate,

- 3. a Read Clock output is provided to enable strobing out the register into memory or other external devices.

The control of these recorders is relatively simple. A Read Select level is applied followed by a Slew level which will cause the tape to accelerate rapidly to the prescribed speed and run continuously at that speed emitting Data and Clock pulses. When a gap is detected, a signal is available which may be used to control the slew level which should be removed to enable the tape to stop in the desired gap.

#### INCREMENTAL READING

The Incremental Read feature permits reading of 200 BPI NRZI tapes one character at a time. Standard computer tapes may be read into such low speed devices as typewriters, data sets, plotters, etc. without the necessity of buffering. In operation the machine is given a Read/Step command. The tape advances to the next character (read search) and stops upon having read that character. Output information is held in storage until the next Read/Step command. Read commands may be repeated at rates up to 150 characters per second.

In order to read incrementally, a means must be provided to assure orientation with the information on the tape. The motion of the tape must be such that the head gap falls between characters when the tape comes to a stop. A step size equal to the character spacing cannot be used since density and step size variations will eventually accumulate to a point where information could be lost.

Kennedy Incremental Recorders use a unique method of correcting tape position. The step size, instead of being 0.005" as it is in Incremental Write Only machines, is set at 0.0025". Thus, two steps will be required to move the tape one character space under ideal conditions. However, since magnetic tape does not have sprockets or other mechanical means to assure that the tape is between characters over the recorder gap, a technique is required which will assure that the tape always stops between characters and that it takes the correct number of steps to assure this. While two steps are usually required, one may be adequate or perhaps three may be necessary. To achieve this an internal oscillator is started when the Read/Step pulse is applied at the interface. The stepper motor then advances the tape. As soon as a character is sensed, the oscillator is cut off and no more pulses are produced and the motor stops. In this way a closed loop system is produced which keeps the tape properly oriented.

106-0044-40

Upon entering a blank region of tape, that is, an Inter-Record gap or End of File gap, the stepper drive will advance as many steps as may be required to reach the next character. A Read/Stop input is provided at the interface to allow stopping this action at the end of data on the tape.

Since the stepper motor and gear box must be arranged to provide two steps per character in the Incremental Read mode, it follows that the same unit being used in the Write mode requires that two steps be taken for each character written. This is automatically provided for internally so that each Write/Step results in a character on the tape with the proper 0.005" spacing. However, this does restrict the upper speed of the writing to 300 characters per second, and the high speed option is thus not available on machines equipped to incrementally read.

# SECTION II

# PERFORMANCE SPECIFICATIONS

# SECTION II

# MODEL 1600/360

# **PERFORMANCE SPECIFICATIONS**

#### GENERAL SPECIFICATIONS

TAPE USED

TAPE FORMAT

TAPE REELS

TAPE COMPATIBLE WITH

WRITE MODE

Recording Speed

Density

RECORD GAP TIME

SLEW RATE

REWIND TIME

0.5" wide, 1.5 mil thick computer tape

206-1636-100

Nine-track NRZ1

Up to 8.5" diameter, IBM compatible

IBM 2400 series tape transports

0-500 characters per second

800 bpi

550 milliseconds (maximum)

1000 characters per second (nominal) (1.25 ips)

Less than 2 minutes

#### OPERATOR CONTROLS AND INDICATORS

All front panel controls (except AC POWER switch) are duplicated by logic inputs at Write Interface connector P1.

#### AC POWER Switch

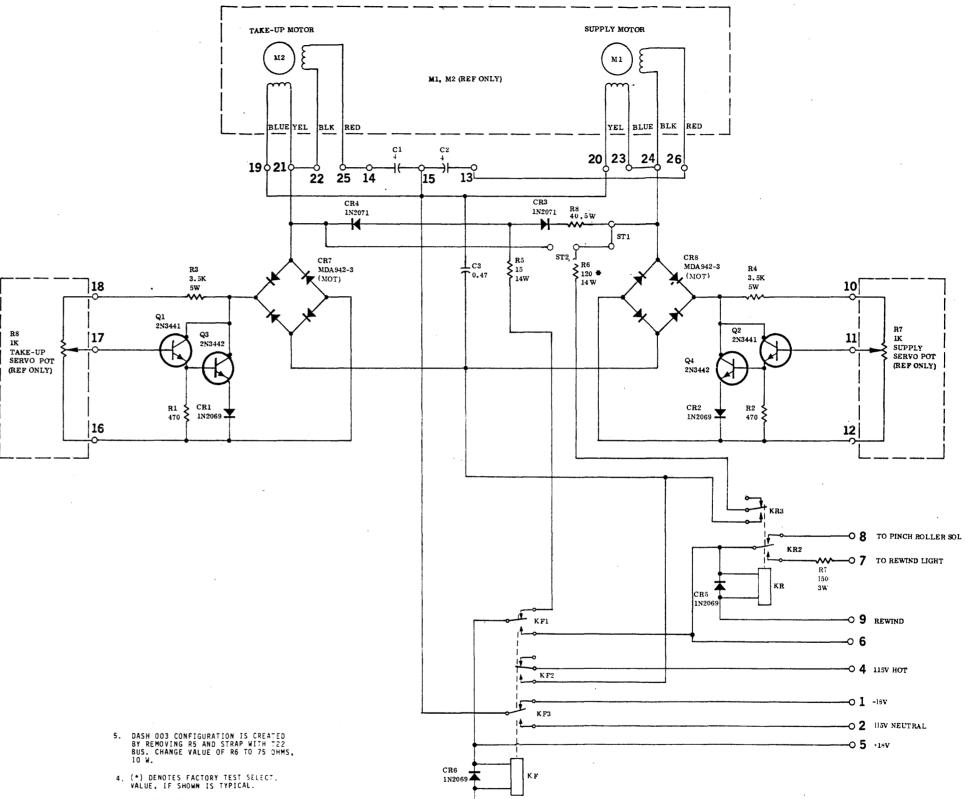

Applies power to the tape unit, presets the control circuits, and places dc braking voltage across the reel motors.

#### LOAD FORWARD Pushbutton With Indicator

Automatically advances the tape to the Load Point marker during a loading operation and generates a Beginning of Tape (BOT) Gap (see below) when the Load Point marker is sensed.

After the loading operation, pressing this button causes tape to be advanced at 1000 characters per second. Indicator illuminates when the button is first pressed and remains lit until the automatic stop following a Rewind operation. The indicator also goes out if Broken Tape is sensed.

206-1636-200.B

#### **READY** Indicator With Pushbutton

Indicator illuminates whenever the tape unit is in READY (ready to accept data). The pushbutton may be used to place the tape unit in READY by pressing it simultaneously with the LOAD FORWARD Pushbutton. This is an interlock to guard against inadvertently pushing this button. Since the tape unit automatically enters READY when the Load Point marker passes under the sensor assembly, this feature should be used only in the rare instances where no Load Point marker is present.

# Note

Use of this feature will not result in a BOT Gap (see below).

#### FILE GAP Pushbutton Only

Manually inserts the IBM File Gap (see below), File Mark, and IRG.

#### **REWIND** Pushbutton With Indicator

Drops the tape unit from READY and rewinds tape at high speed until the Load Point marker is sensed or until tape winds off the reel. In either case, stop is automatic.

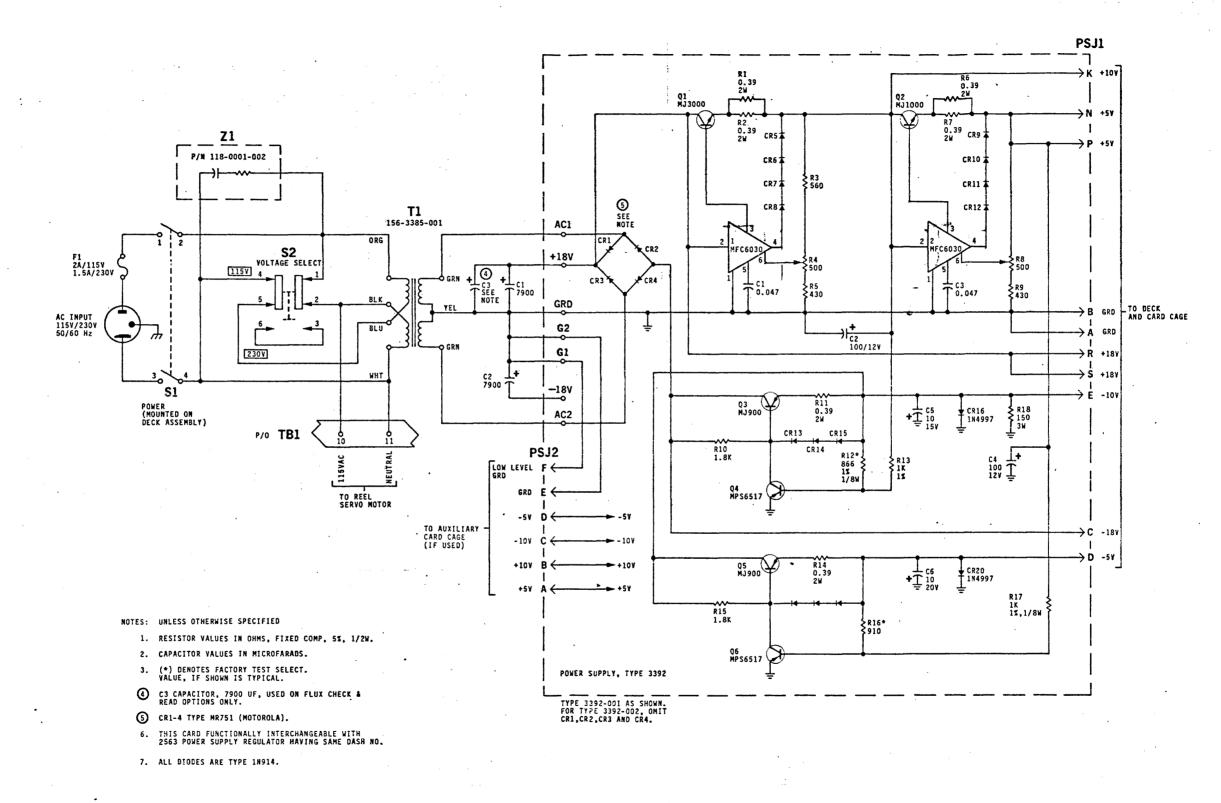

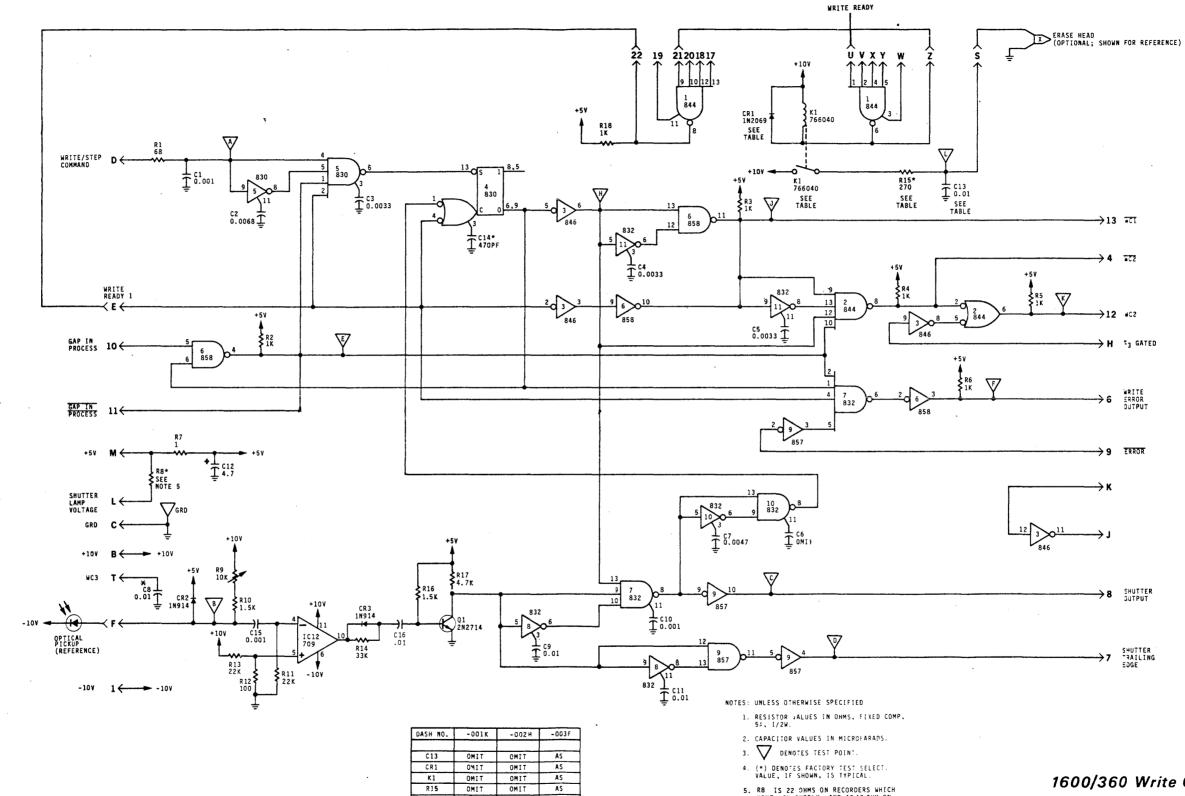

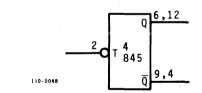

#### INTERNAL CONTROLS AND FEATURES (Also See Figure 1-5, Data Format - Nine Track)

#### Parity Generator

Lateral Parity is generated and written on Channel P. Odd parity is supplied as required by IBM standards.

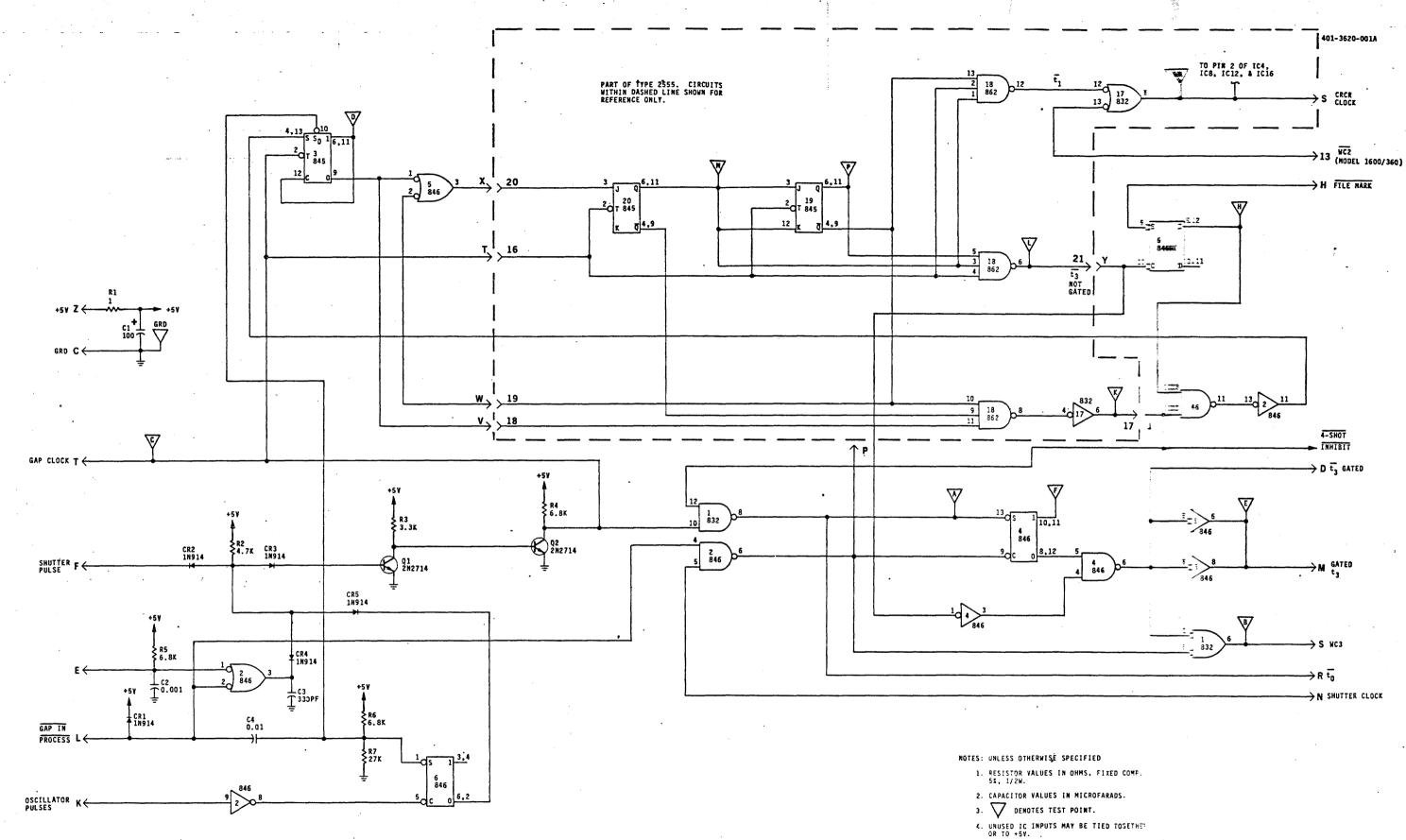

The Cyclic Redundancy Check Character (CRCC), required in the 9-track format in addition to Lateral Parity and the LCC, is written four character spaces after the last data character in a block. Its generation is part of the Inter-Record Gap and File Gap sequences.

Longitudinal Parity (the Longitudinal Check Character, or LCC) is written eight character spaces after the last data character in a block and four character spaces after the CRCC. Its generation is part of the Inter-Record Gap and File Gap sequences.

#### Continuous (Slew) Operation

For applications requiring a higher data input rate, continuous writing at 1000 characters per second may be achieved with this recorder. In this mode, data is recorded in bursts, and all starts and stops take place in the IRG (see below).

The high speed is achieved by accelerating the motor beyond its normal asynchronous rate. Internally generated motor clock pulses are brought out to the interface for use as a system data clock. Thus, stepping and writing are exactly synchronized.

#### Gaps and Marks

Inter-Record Gaps and File Gaps which are compatible with IBM format are generated automatically on command from the interface. File Gaps may also be automatically generated with a front panel control.

Inter-Record Gap (IRG)

File Gap (EOF)

File Mark

Beginning of Tape Gap (BOT)

Also called End of Record Gap (EOR). A 0.6" IRG generated upon command from the interface. A properly spaced CRCC and LCC are inserted as part of the gap timing sequence.

206-1636-300 B

Standard 3-3/4" File Gap generated upon command from the interface or with a front panel control.

Also called Tape Mark. A "one" in Channels 3, 6, and 7 written automatically upon completion of the File Gap. The File Mark is followed automatically by a properly spaced File Mark Check Character (another 3, 6, 7) and an additional 0.6" IRG. A CRCC is not written at this time.

Also called Initial Gap. A 1/2'' (minimum) BOT Gap is automatically inserted when the Load Point marker is sensed during a loading operation.

#### Tape Sensors

Load Point, End of Tape, and Broken Tape sensors are provided. Signals generated by the first two of these sensors are amplified and brought out to the interface connector. The Load Point sensor is used during a loading operation to generate a BOT Gap. It is also used to halt a Rewind operation.

The End of Tape sensor has no internal function. It provides a control signal to the external equipment when the End of Tape marker is under the sensor assembly.

The Broken Tape sensor halts all machine operations in the event of broken or missing tape at the sensor assembly.

#### INTERFACE CHARACTERISTICS

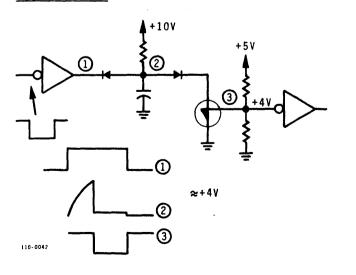

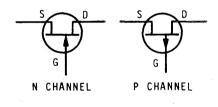

Model 1600/360 Standard Write interface is compatible with current sinking positive logic having a "one" level of +4V to +6V and a "zero" level of  $0V \pm 0.5V$ . "Zero" levels should be capable of sinking 5 ma. All input functions except remote controls are initiated by "one" levels. Remote

control inputs require closures to ground to be activated. Maximum current through the closure is 5 ma; open circuit voltage is  $\pm 10V$ . This may be loaded or clamped to  $\pm 5V$  (minimum) for use with IC logic.

# Note

Because of the nature of DTL logic used in the tape unit, the following inputs must be tied to Signal Ground if they are not used: COUNT ENABLE, CONTROL COMMON, SLEW, EOF COMMAND, and EOR COMMAND. All P1 pins not assigned are reserved by Kennedy Company for future use and should <u>not</u> be used as tie points.

The P1 connector is Part No. 121-5004-036 (Amphenol 57-40360 or equivalent). The mating connector (supplied) is Part No. 121-5003-036 (Amphenol 57-30360 or equivalent).

Modified interfaces are available. Consult the factory.

#### Inputs

PULSES are to be a minimum of 20 usec long and a maximum of 100 usec long.

LEVELS are to be static at the time of the leading edge of the pulse which clocks them in. They must remain static for at least 50 usec thereafter.

CLOSURES TO GROUND are to be a minimum of 20 usec long and a maximum of 100 ms long.

| DATA LINES                           | LEVEL                            | Channel 7 | P1-18 |

|--------------------------------------|----------------------------------|-----------|-------|

|                                      |                                  | 6         | P1-19 |

|                                      |                                  | 5         | P1-17 |

|                                      |                                  | 4         | P1-20 |

|                                      |                                  | 3         | P1-21 |

|                                      |                                  | 2         | P1-16 |

|                                      |                                  | 1         | P1-22 |

|                                      |                                  | 0         | P1-23 |

| WRITE/STEP Comm<br>Clocks in informa | and PULSE<br>tion on data lines. |           | P1-14 |

EOR CommandPULSEP1-30Starts IRG sequence.Must be applied no sooner than 2 ms after the trailing edge<br/>of the last Write/Step Command in the block.P1-30

P1-29

P1-1

#### EOF Command

#### PULSE

Starts File Gap sequence. Must be applied no sooner than 2 ms after the trailing edge of the last Write/Step command. This function is duplicated by the File Gap front panel control.

#### WRITE SELECT

#### LEVEL

Enables Write mode when True and the tape unit is READY. Disables Write mode when False. In normal Write-Only operation this input should be tied directly to +5V.

#### REMOTE LOAD FORWARD CLOSURE TO GROUND P1-2

Prepares tape unit for writing after tape has been loaded. Causes tape to feed at 1000 characters per second until Load Point marker is reached. BOT Gap is automatically generated at this point. This function is duplicated by the Load Forward front panel control.

#### **REMOTE READY** CLOSURE TO GROUND P1-3 Not normally used. Places machine in READY. This input should be used only in the rare instances where no Load Point marker is present on tape.

#### **REMOTE REWIND** CLOSURE TO GROUND P1-4

Drops READY and rewinds tape at high speed until the Load Point marker is sensed. To further rewind the tape off the reel for unloading, the tape unit must be placed in the Load Forward mode after the tape has stopped. Rewind may then be activated again to remove tape completely from the take-up reel. Rewind stops automatically when tape is completely wound on to the supply reel. This function is duplicated by the front panel Rewind control.

#### COUNT ENABLE

This input is not used in nine-channel tape units and must be tied to Signal Ground to avoid erroneous operation.

#### CONTROL COMMON

Connect to Signal Ground to enable front panel pushbuttons. Buttons are disabled if this connection is not made.

#### SLEW

#### LEVEL

LEVEL

Used during Continuous Writing operation only. A True level activates an oscillator which gradually accelerates the stepping motor to 1000 steps per second. Outputs from this oscillator are brought to the interface (see below) for use in synchronizing the data inputs to the stepper motor pulses.

#### FORWARD SELECT

Used in Read/Write models to control the direction of the stepper motor.

P1-10

P1-8

P1-6

P1-7

A True Forward Select level causes the stepper motor to run forward. A False level causes the stepper motor to run backward.

206-1636-600 A

P1-12

P1-11 P1-36

P1-27

In Write-Only models the Forward Select input should be tied directly to +5V or +6V to avoid driving tape backward and erasing it.

+5V

The internal +5V supply is brought to this pin for use as an external reference. Maximum external loading is 100 ma.

Signal Ground and Chassis Ground are not connected together within the tape unit. For best results, run these two lines separately to the Main System Ground and connect them together only at that point.

#### Outputs

P1 signal outputs are terminated in the tape unit through a source impedance of 1.5K (nominal), and are capable of sinking up to 10 ma of external load current. Levels are  $+5V \pm 1V$  True and  $0V \pm 0.5V$  False. Outputs may be loaded or clamped to  $\pm 3V$  (minimum).

#### READY

#### LEVEL

Indicates that the loading process is complete and head current is flowing. Data may be recorded whenever this output is True and the Gap in Process output is False. This output is duplicated by the READY Indicator on the front panel.

GAP IN PROCESS LEVEL P1-28 Indicates that the tape unit is under the control of the gapping electronics and is inserting an IRG, End of File, or BOT Gap. The output includes a delay at the end of each gap for the tape unit to come to a stop. Writing should not be attempted while this level is True.

## END OF TAPE

LEVEL P1-5 Indicates that the End of Tape marker is under the sensor assembly. This function is not used internally.

#### WRITE ERROR LEVEL P1-24

Indicates that the Echo Check circuits have detected an error in the write electronics. Level will go True a maximum of 1.95 ms after the Write/Step Command has been given and will remain True until the next Write/Step Command is given.

#### OSCILLATOR OUT

#### PULSE

P1-26

206-1636-700

Pulse duration 10 usec (minimum). Pulses from an internal oscillator, used primarily to drive the stepper motor at high speed during gapping operations, are brought out to this pin for use as a system clock in the Continuous Writing mode. Pulses are produced whenever the Slew input is applied or whenever the tape unit is inserting a gap. Nominal rate is 1000 pulses per second; however, the motor must accelerate to this speed over a number of steps.

### Note

These pulses are used internally to drive the stepper motor during loading and gapping operations in either the Incremental or the Continuous Writing mode. Therefore, they must be properly gated externally to avoid system errors when a loading or gapping operation is in progress.

#### LOAD POINT

#### LEVEL

P1-31

Indicates that the Load Point marker is under the sensor assembly. This function is used internally to generate a BOT Gap during a loading operation and to halt tape during a Rewind operation.

#### POWER REQUIREMENTS

#### PHYSICAL CHARACTERISTICS

$115V/230V \pm 10\%$ , 50/60 Hz is standard. Power consumption: 150VA.

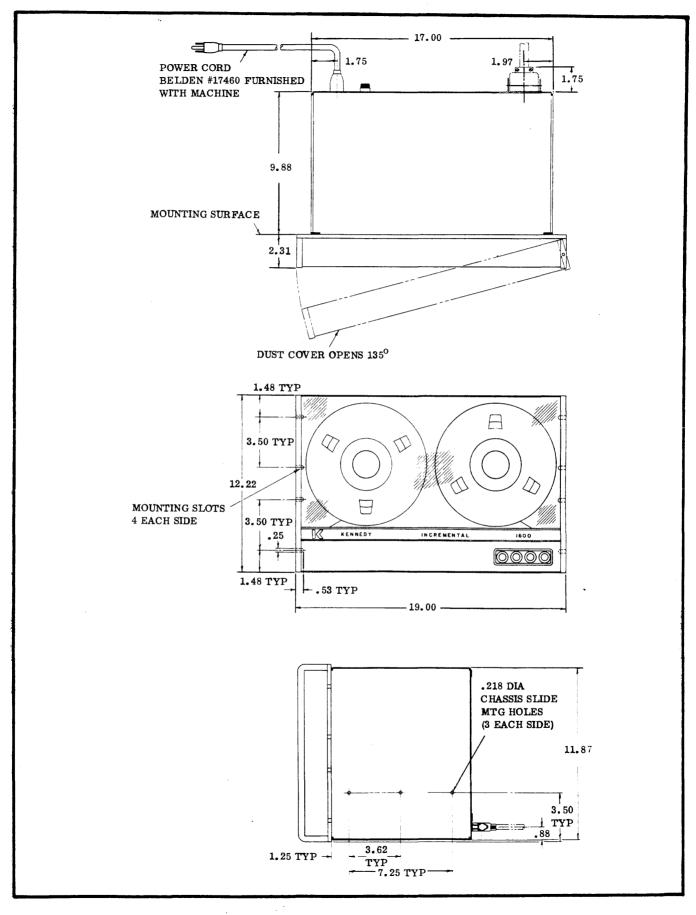

Panel 19 inches x 12-1/4 inches, fits standard rack. Depth behind panel: 10 inches. Added 8-inch depth clearance required to open auxiliary card cage. Weight: 45 lbs.

#### ENVIRONMENTAL

Operating Temperature Storage Temperature Storage Altitude Relative Humidity +2°C to +50°C (+35°F to +122°F) -40°C to +75°C (-40°F to +167°F) 20,000 feet (maximum) 15% to 95%

## Note

No condensation is allowed on any portion of the tape unit during operation. Any condensation accumulated during shipping and/or storage must be thoroughly removed before tape unit is operated. Tape manufacturers' specifications may impose more stringent environmental limitations than those given above. Consult tape supplier.

# SECTION III

# CHECKOUT AND INSTALLATION

# SECTION III

# CHECKOUT AND INSTALLATION

#### INTRODUCTION

This section contains information on unpacking, inspection, repacking, storage, and installation.

#### UNPACKING AND INSPECTION

If the shipping carton is damaged, ask that the carrier's agent be present when the recorder is unpacked. Inspect the recorder for damage (scratches, dents, broken knobs, etc.). If the recorder is damaged or fails to meet specifications, notify the carrier and Kennedy Company immediately. Retain the shipping carton and the padding material for the carrier's inspection. Kennedy Company will arrange for the repair or replacement of your recorder without waiting for the claim against the carrier to be settled.

#### STORAGE AND SHIPMENT

#### Packaging

To protect valuable electronic equipment during storage or shipment always use the best packaging methods available. Kennedy Company can provide packing material such as that used for original factory packaging. Contract packaging companies in many cities can provide dependable custom packaging on short notice. Here are a few recommended packaging methods:

Rubberized Hair: Cover painted surfaces of recorder with protective wrapping paper. Pack recorder securely in strong corrugated container (350 lbs./sq. in. bursting test) with 2-inch rubberized hair pads placed along all surfaces of the recorder. Insert fillers between pads and container to ensure a snug fit.

Excelsior: Cover painted surfaces of recorder with protective wrapping paper. Pack recorder in strong corrugated container (350 lbs./sq. in. bursting test) with a layer of excelsior about 6 inches thick packed firmly against all surfaces of the recorder.

#### Environment

Conditions during storage and shipment should normally be limited as follows:

- a. Maximum altitude: 20,000 feet

- b. Minimum temperature:  $-40^{\circ}$  F ( $-40^{\circ}$ C)

- c. Maximum temperature:  $167^{\circ}$  F (75°C)

#### Shipping Frame

Some Kennedy Company recorders are shipped in steel frames for protection. This frame fits snugly inside the shipping carton. Remove unit and frame from box. The frame is suitable for holding the machine in an upright position during initial handling and checkout.

306-0008-3

#### RACK MOUNTING

Rack mounting slots are accessible with the recorder door open. If desired for greater ease of access, the door may be removed during mounting and replaced when the machine is in place.

Appropriate washers under mounting screw heads will prevent damage to painted surfaces of the panel.

### POWER CONNECTION

A 3-wire detachable power cable is supplied with each machine. Exposed portions of the machine are grounded for safety. When only a 2-blade outlet is available, use connector adapter and ground the short wire from the side of the adapter.

Before plugging in to a 230V main, be sure the machine is wired for 230V operation. 230V wiring will be indicated by a prominent stamp near the power connector, or some models have a switch to select 115V/230V operation.

# SECTION IV

# OPERATION

## SECTION IV

### OPERATION

#### INTRODUCTION

In order to operate the recorder properly it is necessary to have it connected to a suitable interface. This is particularly true in the case of machines with DTL logic; they will not operate unless inputs specified to be zero are connected to ground.

It is assumed in the following that suitable preparations have been made and the machine is in an operable condition.

#### TAPE LOADING

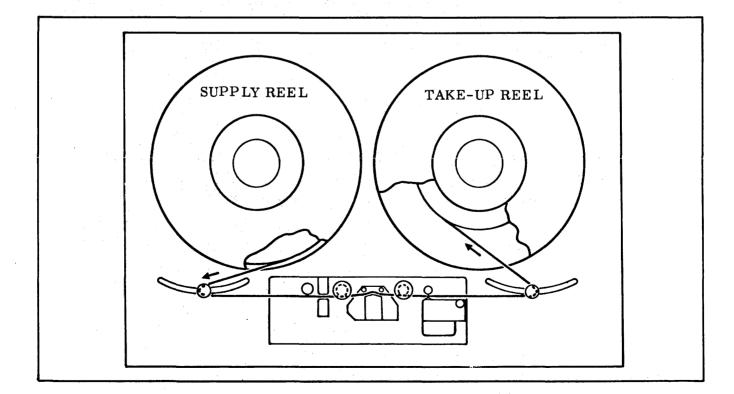

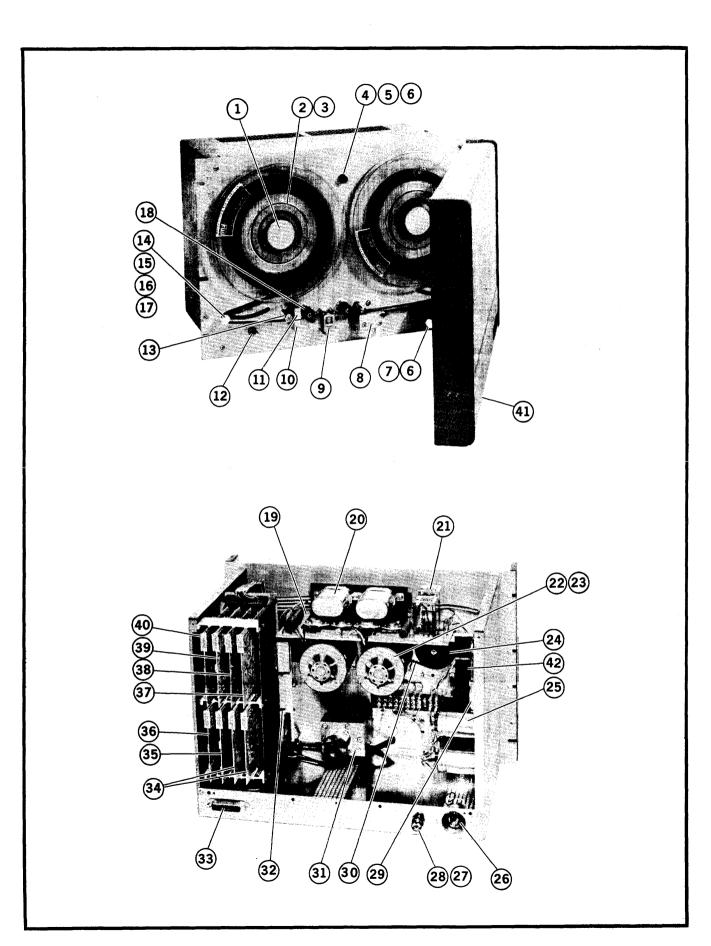

- 1. With power off, place a full reel on the supply hub as shown in Figure 4-1.

- 2. Thread tape along tape path as shown in Figure 4-1 to the take-up reel.

- 3. Holding end of tape with a finger, wrap a few turns around the take-up reel.

- 4. Turn power on.

# Figure 4-1. Tape Threading Diagram

6. READY light comes on and machine is now prepared to accept data.

#### INCREMENTAL WRITING

- 1. Feed a series of data inputs and Write/Step Commands to the interface connector, observing the proper relative timing requirements for these inputs. Input rate must not exceed that shown in the Performance Specifications.

- 2. At intervals, determined solely by system requirements, an IRG must be inserted. At these times, apply an EOR Command to the interface. Be sure to observe the timing requirements with respect to the final Write/Step Command of the record.

- 3. At the end of a job, or at other times determined by system requirements, an EOF Gap must be inserted. This can be done by applying the appropriate command to the interface or by pressing the FILE MARK Pushbutton on the front panel.

# Note

In the case of systems that apply an IRG at the end of each record, no improper formatting results from following the last IRG of a job with an EOF Command; however, the separate EOR Command is not required.

#### REWIND

- 1. Press REWIND Pushbutton. Tape will rewind until Load Point marker is sensed and then stop. Rewind cannot be stopped (except by turning off power) once initiated. This is to prevent partial rewinding and subsequent possible destruction of data.

- 2. After tape has stopped it may be removed by manually completing the rewind with power off or by pressing LOAD FORWARD quickly, followed by pressing REWIND. Tape will then wind completely out of the machine and the reels will stop.

To avoid tape damage, always wait at least one second after the Load Point marker is sensed before activating any machine function. This allows the tape to stop completely.

# SECTION V

# MAINTENANCE

## SECTION V

## MAINTENANCE

#### ROUTINE MAINTENANCE

Primarily, routine maintenance consists of keeping mechanical parts clean. At regular intervals, depending in length upon use of machine and cleanliness of machine environment, the following steps should be taken:

- 1. Clean head surface and entire guide plate area with soft cloth and a mild organic solvent such as IBM head cleaner.

- 2. Clean surface of pinch roller to remove accumulation of oxide with a similar solvent.

- 3. Remove any accumulation of dust within the main cover and on the panel.

It should be kept in mind that while incremental recorders are very reliable devices and can operate under conditions more adverse than high speed computer tape transports, dirt is always a major source of difficulty and potential error. The tape path must be kept as clean as possible.

All bearings in the machine are lubricated for life. No further lubrication should be attempted since ball bearing lubrication can be destroyed by oil.

#### CHECKOUT AND ADJUSTMENT PROCEDURE

Relatively few adjustments are required on Kennedy Incremental Recorders. These can be divided into two classes, mechanical adjustments and electrical adjustments. Electrical adjustments, if any, will be found in Sections VI and VII. Mechanical adjustment procedures are given below.

#### Mechanical Adjustments

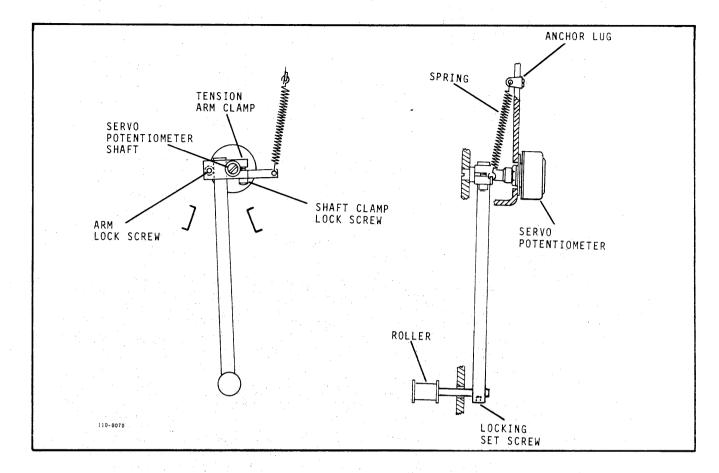

Tension Arm Adjustment: Two tape tension arms are provided for sensing tape tension and providing a buffer loop to allow free tape motion. Tension arms are coupled to potentiometers which control reel motor torque to maintain tension constant. Adjustments required are:

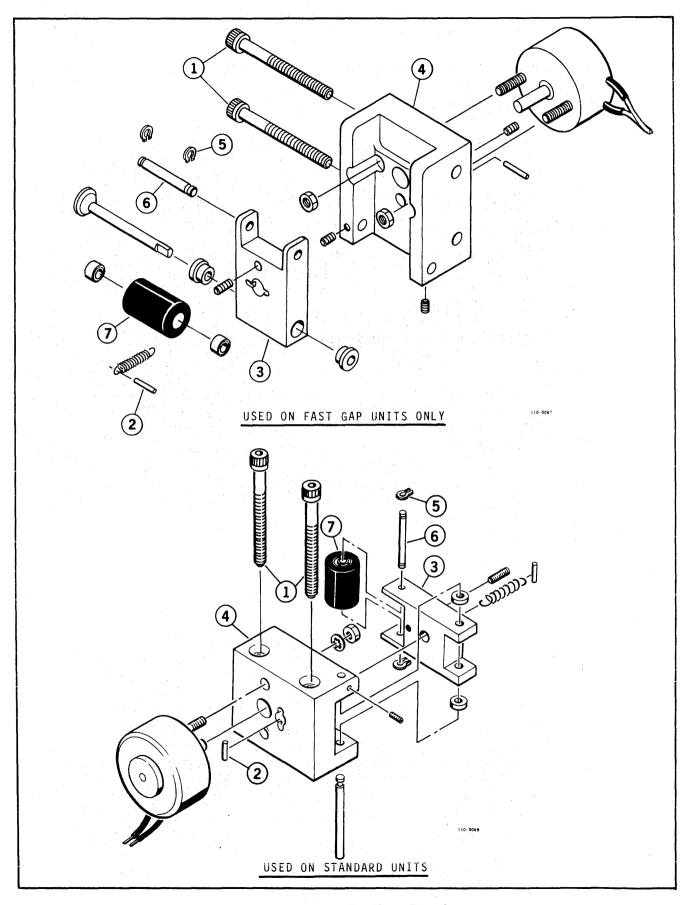

1. Tension Arm Return Force (Ref. Figure 5-1)

Tension arms are spring loaded to provide proper tape tension. To set tape tension:

- b. Measure return force at the end of the arm with a spring scale.

- c. Adjust anchor lug position for a spring scale reading of 4 oz (113 gm). This setting will establish 2 oz of tape tension.

506-1600-200

2. Servo Potentiometer Angular Position (see Figure 5-1)

Tension arm is coupled to servo potentiometer by a shaft clamp. Potentiometer shaft extends through the panel and is slotted to accept a screwdriver. Servo potentiometer must be positioned to give proper motor torque.

- a. Loosen shaft clamp lock screw until potentiometer shaft may be rotated with a screwdriver but still is snug enough to be rotated by tension arm. Press LOAD FORWARD pushbutton.

- b. Hold tension arm in approximate center of arc. Turn potentiometer shaft until torque produced by reel servo drops to zero.

- c. Tighten clamp lock screw.

- d. With tape in place energize servos. Note position assumed by tension arm. If not close to center of arc, readjust potentiometer shaft to correct.

### Note

Potentiometer shafts are accessible only with reels removed.

3. Tape Path Location

Tension arm rollers establish approximate tape path. To assure that no skew is introduced this path must conform closely to guide path. To adjust:

- a. Loosen locking setscrew (Figure 5-1).

- b. Measure height of rear edge of tape (closest to panel) at the guide plate. Tape should clear guide plate surface by 0.437 inch (1.72 cm) ±0.005 inch (0.127 mm), and be parallel to guide plate surface throughout its length.

c. When proper tape height is obtained lock roller in plate by tightening locking setscrew.

# Figure 5-1. Tension Arm Adjustments

4. Capstan Drive Gear Mesh

Adjustment of Capstan Drive Gear Mesh is accomplished by rotating the stepper motor in its eccentric mounting. This adjustment should not be attempted unless there is strong reason to believe it is required. Gears are properly meshed when units leave the factory and should not require re-adjustment over long periods.

Mesh adjustment cannot be measured directly; it must be accomplished by feel. With power off:

- a. Loosen three clamp screws holding motor in place.

- b. Rotate motor clockwise (from rear) to tighten mesh.

- c. Rotate capstan shaft as motor is rotated to detect zero backlash setting.

- d. Lock motor in place and check again for zero backlash and free rotation. It should be possible to rotate motor from the capstan without difficulty.

- e. If necessary, repeat procedure until zero backlash with free rotation is achieved. In the proper setting a slight "toothy" feel will be noticed.

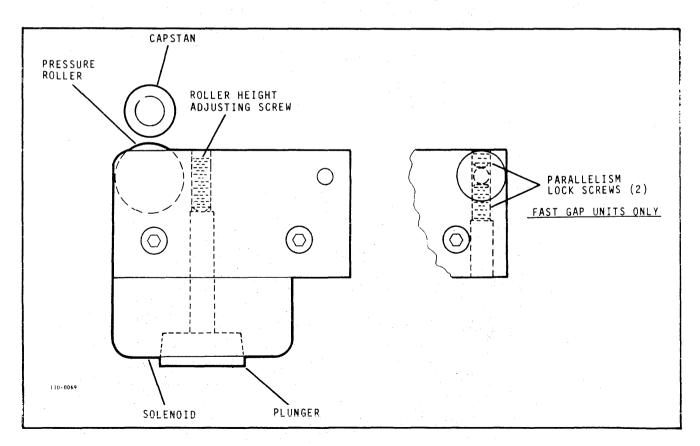

The standard pinch roller should be adjusted to supply sufficient frictional force to drive the tape properly. To adjust the pinch-roller pressure proceed as follows:

506-1600-400

- a. Clean pinch roller well before making any adjustments.

- b. With power applied to pinch roller, or holding solenoid in energized position, adjust roller height adjusting screw until roller does not touch capstan.

- c. Turn screw an additional quarter turn.

- d. Feed about 2 feet of tape through guides and over head, through pinch roller capstan.

- e. Attach a spring scale to tape and press LOAD FORWARD button. Hold tape back until it slips at the drive.

- f. Spring scale should read at least 6 oz (170 gm). If not, rotate the height adjusting screw slightly and remeasure.

- g. Lock the height adjusting screw with Loctite grade H.

Tape recorders with the fast gap feature require an additional parallelism adjustment not required by the standard decks. To adjust the parallelism proceed as follows:

Figure 5-2. Pinch Roller Adjustments

- a. Using a length of tape, say, 3 feet long (about 1 meter), feed through machine as above.

- b. Press LOAD FORWARD and observe tape motion. Tape should pull evenly through pinch roller/capstan with no tendency to skew either in or out.

- c. If tape does not pull straight, readjust parallelism screws (Figure 5-2) until straight motion is obtained. Tape will tend to move toward the tight side of engagement.

- d. Lock screws in place and apply Loctite grade H.

- e. Recheck as above after locking.

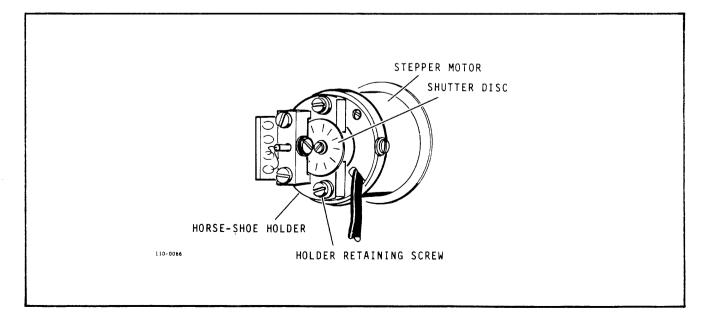

#### PHOTO SHUTTER ADJUSTMENT PROCEDURE

The photo shutter setting is preadjusted, and should not be changed during normal use and maintenance. Should readjustment become necessary, proceed as follows:

Do NOT touch the shutter disc while making the photo shutter adjustment; its knifelike edge may cause injury.

- a. Remove the three retaining screws of the shutter cover, and then remove the cover itself, exposing the shutter mechanism.

- b. Loosen the two retaining screws of the shutter horseshoe holder, as shown in Figure 5-3.

# Figure 5-3. Photo Shutter Adjustment

c. Attach an oscilloscope probe to the OPTICAL PICKUP output at either test point B of the write control module in the Model 1600/360 or test point C of the interface module in the Model 1600.

506-1600-600

- d. Thread a tape on the reels and place the recorder in the LOAD FORWARD mode.

- e. Rotate the horseshoe shutter holder until 1,000 pulses per second are shown by the oscilloscope.

- f. To prevent the recorder from switching to 500 steps per second during slewing, tape off the BOT and BROKEN TAPE sensors from their respective light sources, disabling the BROKEN TAPE detection. Remove the reels from the hubs, and place the recorder in the LOAD FORWARD mode again. Load the capstan by pressing the capstan roller with the thumb and index fingers, and rotate the shutter holder until the 1,000 steps per second rate is recovered immediately after the capstan roller is released.

- g. Supply write step commands to the recorder covering the possible writing range. The shutter pulses displayed by the oscilloscope should be free of extraneous peaks. If extraneous peaks are detected, rotate the shutter holder slightly until the peaks just disappear.

- h. For a final check trigger the oscilloscope probe (attached the OPTICAL PICKUP) off the WRITE/STEP command and locate the resonance stepping frequency. The resonance frequency is the point at which the interval between the shutter pulse and the WRITE/STEP command is at a maximum. Ascertain that at this point the shutter pulse trails the WRITE/STEP command by a maximum of 1.2 milliseconds.

- i. When the adjustment is complete, lock the shutter holder retaining screws and apply Loctite grade H (supplied with the K-21 maintenance kit). Replace the shutter cover.

#### REPLACEMENT OF PARTS

In the event of damage to the machine, parts not normally expected to be replaced might require maintenance. The following discussion describes procedures for maintenance under these circumstances.

- 1. Servo Potentiometer Replacement

- a. Remove potentiometer by removing two screws holding potentiometer mounting plate. Remember to loosen shaft clamp screw in tension arm clamp.

- b. Mount new potentiometer with lugs in same approximate location of old nut.

- c. Return potentiometer and mounting plate to assembly replacing tension arm.

- d. Return mounting screws. Be sure potentiometer shaft rotates freely after screws are tightened.

- e. Go through adjustment procedure as outlined above.

- 2. Tension Roller

Under extreme circumstances shaft of tension arm roller may be bent. In this case it requires replacement.

- a. Remove old roller together with shaft.

- b. Install new roller and shaft.

- c. Adjust as previously described in step 3.

- 3. Pinch Roller

After long service the pinch roller may become worn and require replacement. To replace pinch roller:

- a. Remove assembly from mounting surface by removing screws (item 1, Figure 5-4).

- b. Remove pin (item 2) by means of a small hook formed from stiff wire.

- c. Lift pinch roller yoke (item 3) clear of housing (item 4).

- d. Remove retaining ring (item 5) from front of shaft.

- e. Remove shaft (item 6) from rear of assembly, freeing pinch roller (item 7).

- f. Replace pinch roller and reassemble.

- g. Readjust pinch roller as previously described in step 5.

- 4. Capstan Assembly

In the event that through wear or other cause the capstan assembly needs replacement:

- a. Remove old assembly by removing wires from terminal block and removing two mounting screws from front side of panel.

- b. Replace with new assembly. Bearing must seat in counterbore on reverse side of mounting plate.

- c. Readjust pinch roller (as previously described in step 5). Repair of capstan assemblies in the field is not advised. Return used assembly together with complete information to factory for credit.

Figure 5-4. Pinch Roller Replacement

. \* .

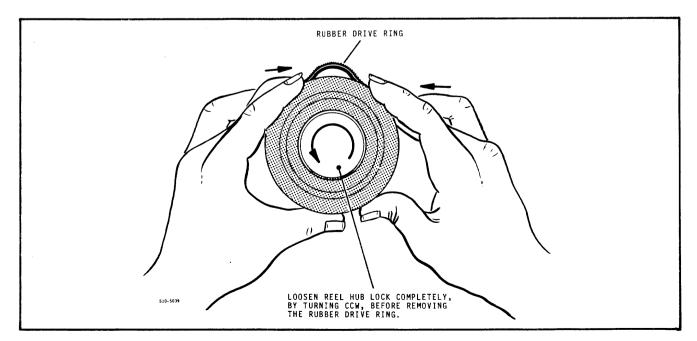

5. Reel Hub Grip Ring (Figure 5-4)

A rubber ring is used as an expansion ring to hold the tape reel in place. If it should require replacement, simply pry old ring off without disassembling hub and snap new ring in its place.

6. Guides

If a guide becomes worn, it is usually adequate to simply loosen its mounting screw, turn the guide a few degrees, and retighten.

If complete replacement is desired, remove screw and guide. Replace with new guide; no adjustment is required.

7. Magnetic Head

Heads have very long life at speeds encountered in incremental recorders. If replacement is required:

- a. Unplug head.

- b. Remove two mounting screws.

- c. Pass connector through hole in panel and remove head.

- d. Replace with new head.

No adjustment of heads is possible or required. Return head to factory with complete details of cause for replacement.

Figure 5-5 Rubber Ring Drive Replacement

# SECTION VI

## MECHANICAL

Model 1600 Outline and Installation Drawing

| ITEM<br>NO.     | PART NO.                                                                                                                                               | DESCRIPTION                                              | QTY PER<br>MACHINE |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--------------------|

| 1               | 190-1141-001                                                                                                                                           | ASSEMBLY, hub handle                                     | 2                  |

| 2               | 190-1140-001                                                                                                                                           | ASSEMBLY, reel hub                                       | 2                  |

| 3               | 191-0574-001                                                                                                                                           | RING, hub drive                                          | 2                  |

| 4               | 139-2900-001                                                                                                                                           | HOLDER, lamp                                             | 1                  |

| 5               | 139-1900-501                                                                                                                                           | COVER, lamp, green                                       | 1                  |

| 6               | 139-0214-001                                                                                                                                           | LAMP, no. 330                                            | 4                  |

| 7               | 151-1005-101                                                                                                                                           | SWITCH                                                   | 4                  |

| 8               | 190-1995-000                                                                                                                                           | ASSEMBLY, pressure roller actuator                       | 1                  |

| 9               | 190-2451-001                                                                                                                                           | ASSEMBLY, magnetic head                                  | 1                  |

| 10              | 190-1139-001                                                                                                                                           | ASSEMBLY, sensor, broken tape                            | 1                  |

| 11              | 190-1139-001                                                                                                                                           | ASSEMBLY, sensor, end of tape                            | 1                  |

| 12              | 151-2001-101                                                                                                                                           | SWITCH, toggle, spst                                     | 1                  |

| 13              | 191-0549-001                                                                                                                                           | POST, brake                                              | 1                  |

| 14              | 190-0637-000                                                                                                                                           | ASSEMBLY, roller, tension                                | 2                  |

| 15              | 191-0766-005                                                                                                                                           | ARM, tension                                             | 2                  |

| 16              | 125-0036-001                                                                                                                                           | SPRING, extension 251A                                   | 2                  |

| 17              | 191-0635-002                                                                                                                                           | POTENTIOMETER                                            | 2                  |

| 18              | 191-0033-002                                                                                                                                           | ASSEMBLY, guide, split tape                              | 2                  |

| 19              | 190-1303-001<br>190-2273-001                                                                                                                           |                                                          |                    |

| 20              | 130-2273-001<br>115-3625-798                                                                                                                           | ASSEMBLY, control board, deck power<br>CAPACITOR         | 1 2                |

| $\frac{20}{21}$ | 145-0005-001                                                                                                                                           |                                                          | 1                  |

| $\frac{21}{22}$ |                                                                                                                                                        | RELAY, 3pdt                                              | 2                  |

| 22<br>23        | 135-0001-001                                                                                                                                           | MOTOR                                                    | 2                  |