# J500 Videocomputer System

Reference Manual

JPS 500-01

1 APRIL 1979

# **REFERENCE MANUAL**

# J500 VIDEOCOMPUTER SYSTEM

Equipment specifications published herein are subject to change without prior notice.

Changed 15 October 1979

| REVISION                               | REVISION RECORD DESCRIPTION                    |  |  |  |  |

|----------------------------------------|------------------------------------------------|--|--|--|--|

| ne v 1810N                             |                                                |  |  |  |  |

|                                        | Manual Released - 1 April 1979                 |  |  |  |  |

| 1                                      | Revised and Reprinted 15 October 1979          |  |  |  |  |

| 2                                      | Revised Page 1-2 and Figure 1-2 - 15 June 1980 |  |  |  |  |

|                                        |                                                |  |  |  |  |

| ·                                      |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

| ۰.                                     |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

| - <u></u>                              |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

| ·····                                  |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

| ······································ | · · · · · · · · · · · · · · · · · · ·          |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

| ······                                 |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

|                                        |                                                |  |  |  |  |

A Comment Sheet is included at the back of this manual.

| SECTION     | 1. INTRODUCTION                                   | 1-1        |

|-------------|---------------------------------------------------|------------|

| 1-1         | Introduction                                      | 1-1        |

| 1-1<br>1-2  | Physical/Functional Organization                  | 1-1<br>1-2 |

|             | Physical I unchonal Organization                  |            |

| 1-3         | Physical Organization                             | 1-2        |

| 1-4         | Functional Organization.                          | 1-4        |

| 1-5         | System Features                                   | 1-4        |

|             | 1-6 Expansion Capabilities                        | 1-4        |

|             | 1-7 User Interface                                | 1-4        |

| 1-8         | Hardware Features                                 | 1 - 4      |

|             | 1-9 Diskettes                                     | 1 - 4      |

| 1 - 10      | Peripheral and Communication Options .            | 1-4        |

|             | ··· _                                             |            |

| SECTION     |                                                   | 2-1        |

| 2-1<br>2-2  | IntroductionArithmetic and Logic Units Referenced | 2-1        |

|             | in Instructions<br>2-3 Push-Down Stack Register   | 2-1        |

|             | 2-3 Push-Down Stack Register<br>(LIFO)            | 2-1        |

|             | 2-4 Status Register                               | 2 - 1      |

|             | 2–5 Program Counter (PC)                          | 2-1        |

|             |                                                   | 2-1        |

|             |                                                   | 0 0        |

| 0 7         | (AC0, AC1, AC2, and AC3) $\ldots$                 | 2-2        |

| 2-7         | Data and Instructions                             | 2-2        |

|             | 2-8 Data Representation                           | 2 - 2      |

|             | 2–9 Instructions                                  | 2 - 2      |

| 2 - 10      | Memory Addressing                                 | 2 - 2      |

|             | 2-11 Base Page Addressing                         | 2 - 2      |

|             | 2-12 Program-Counter Relative<br>Addressing       | 2-2        |

|             | 2–13 Indexed Addressing.                          | 2-2        |

|             | 2–14 Indirect Addressing                          | 2-2<br>2-2 |

| 2-15        | 2-14 Indirect Addressing                          | 2-2        |

| 2-10        | Notations and Symbols Used In Micro-              |            |

| 0.40        | processor Instruction Descriptions                | 2-2        |

| 2-16        | Instruction Descriptions                          | 2-4        |

| 2-17        | Load and Store Instructions                       | 2-4        |

| 2-18        | Arithmetic Instructions                           | 2-4        |

| 2-19        | Logical Instructions                              | 2-5        |

| 2 - 20      | Skip Instructions                                 | 2-6        |

| 2 - 21      | Transfer-of-Control Instructions                  | 2 - 7      |

| 2 - 22      | Shift Instructions                                | 2-10       |

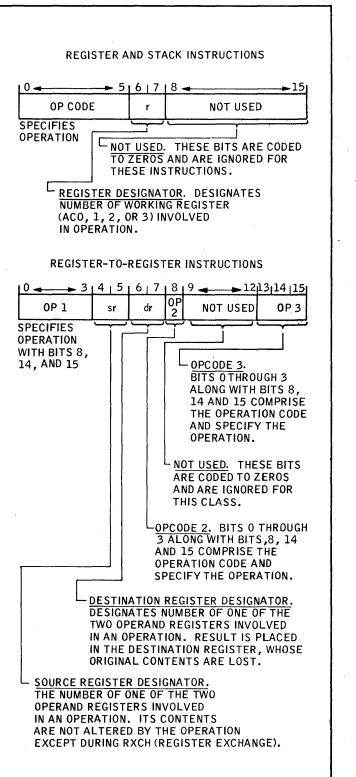

| 2-23        | Register Instructions                             | 2-13       |

| 2-24        | Input/Output Instructions                         |            |

| 2-2-2-2-2-5 | Holt and Eleg Instructions                        | 2-15       |

|             | Halt and Flag Instructions                        | 2-18       |

| 2 - 26      | Interrupt System                                  | 2-20       |

|             | 2-27 Device Controllers                           | 2 - 20     |

|             | 2-28 Machine Stack Overflow                       | 2-20       |

| SECTION     |                                                   | 3-1        |

| 3-1         | Introduction                                      | 3-1        |

| 3-2         | Microprogram Memory                               | 3-1        |

| 3-3         | Microprogram Control Logic                        | 3-1        |

| 3-4         | Main Memory                                       | 3-1        |

| 3-5         | Register File.                                    | 3-1        |

| 3-6         | Arithmetic/Logic Unit (ALU)                       | 3-1        |

| 3-7         | Input Multiplexor and Condition-Bit               | 3-2        |

|             | Output Flip-Flops and Flag RAM                    | 3-2        |

| 3-9         | Peripheral Buffer Registers                       | 3-2<br>3-2 |

| 3-10        | Programmable Sync/Async                           | 3-2        |

| 3-10        | Communication Chips                               | • •        |

| 9 11        | Communication Unips                               | 3-2        |

| 3-11        | CRT Character Generator Memory                    | 3 - 2      |

| 3-12        | J500 Microprogram Description                     | 3 - 2      |

| SECTION 4   | 4. CRT AND KEYBOARD                               | 4-1        |

| 4-1         | Keyboard                                          | 1 1        |

| 4-1         | Keyboard                                          | 4-1        |

| 4-2<br>4-3  | CRT Display                                       | 4-1        |

| 4-3         | Audio Volume, Brightness and                      |            |

|             | Contrast Controls.                                | 4-1        |

| 4-4        | Specia      | l Display Attributes                                   | 4-3          |

|------------|-------------|--------------------------------------------------------|--------------|

| 4-5        |             | structions                                             | 4-3          |

|            | 4-6         | Data In A (DIA) Instruction                            | 4-3          |

|            | 4-7         | Data In B (DIB) Instruction. ,                         | 4-3          |

|            | 4-8<br>4-9  | Data In C (DIC) Instruction                            | 4-3          |

|            | 4-9<br>4-10 | Data Out A (DOA) Instruction                           | 4-3          |

|            | 4-10        | Data Out B (DOB) Instruction<br>Without Start Function | 1 9          |

|            | 4-11        | Data Out B (DOB) Instruction                           | 4-3          |

|            | 1-11        | With Start Function.                                   | 4-3          |

|            | 4-12        | Data Out C (DOC) Instruction .                         | 4-4          |

|            | 4-13        | No I/O (NIO) Instruction                               | 4-4          |

|            | 4-14        | Read Done (RDDNE)                                      |              |

|            |             | Instruction                                            | 4-4          |

|            | 4-15        | Read Busy (RDBSY)                                      |              |

|            |             | Instruction                                            | 4-4          |

|            | 4-16        | Mask Out (MSKO) Instruction                            | 4-4          |

| SECTION    | 5. UN       | IVERSAL DISK CONTROLLER                                | 5-1          |

| F 1        | T J.        |                                                        |              |

| 5-1<br>5-2 |             | action                                                 | 5-1          |

| 0-2        | 5-3         | structions                                             | 5-1<br>5-1   |

|            | 5-3<br>5-4  | Data In A (DIA) Instruction -                          | 9-1          |

|            | 0-1         | Without Clear                                          | 5-3          |

|            | 5-5         | Data In A (DIA) Instruction –                          | 0-0          |

|            | 00          | With Clear                                             | 5-3          |

| 5-6        | Writin      | g Considerations                                       | 5-3          |

| 5-7        | Additio     | onal Floppy Considerations                             | 5-3          |

| 5-8        | Initiali    | zing Floppies                                          | 5-3          |

|            |             |                                                        |              |

| SECTION    |             | OGRAMMABLE COMMUNICA-                                  |              |

|            | TIC         | ONS CONTROLLER                                         | 6-1          |

|            | <b>.</b>    |                                                        |              |

| 6-1        | Introdu     | action                                                 | 6-1          |

| 6-2        | I/O Ins     | structions                                             | 6-1          |

|            | 6-3         | Data Out A (DOA) Instruction                           | 6-2          |

|            | 6-4         | Data Out B (DOB) Instruction                           | 6-4          |

|            | 6-5         | Data Out C (DOC) Instruction                           | 6-5          |

|            | 6-6         | Data In A (DIA) Instruction                            | 6-6          |

|            | 6-7<br>6-8  | Data In B (DIB) Instruction                            | 6-6          |

|            | 6-9         | Data In C (DIC) Instruction<br>No Input/Output (NIO)   | 6-6          |

|            | 0-3         | Instruction                                            | 6-6          |

|            | 6-10        | Mask Out (MSKO) Instruction .                          | 6-6          |

| 6-11       |             | pt Processing                                          | 6-7          |

| 6-12       | RBCC8       | Instruction                                            | 6-7          |

|            |             |                                                        | 01           |

| SECTION    | 7. AU       | <b>FO-DIALER CONTROLLER</b>                            | 7-1          |

|            |             |                                                        | - ·          |

| 7-1        | Introdu     | iction                                                 | 7-1          |

| 7-2        |             |                                                        | 7-1          |

|            | 7-3<br>7-4  | Data Out A (DOA) Instruction                           | 7-1          |

|            | 7-4<br>7-5  | Data In A (DIA) Instruction                            | $7-1 \\ 7-2$ |

| 7-6        |             | Mask Out (MSKO) Instruction                            | 7-2          |

| 7-0        |             | mming Rules                                            | $7-2 \\ 7-2$ |

| • • •      | 110510      |                                                        | 174          |

|            |             |                                                        |              |

| SEC TION   | 8. PRI      | NTER CONTROLLER                                        | 8-1          |

|            |             |                                                        | ~ 1          |

| 8-1        | Introdu     | ction                                                  | 8-1          |

| 8-2        | Line P      | rinter I/O Instructions                                | 8-1          |

|            | 8-3         | Data Out A (DOA) Instruction                           | 8-1          |

|            | 8-4         | Data In A (DIA) Instruction                            | 8-3          |

|            | 8-5         | Mask Out (MSKO) Instruction                            | 8-3          |

| 8-6        |             | ter Printer I/O Instruction                            | 8-3          |

|            | 8-7         | Data Out A (DOA) Instruction                           | 8-3          |

|            | 8-8         | Data In A (DIA) Instruction.                           | 8-3          |

|            | 8-9         | Mask Out (MSKO) Instruction                            | 8-3          |

## TABLE OF CONTENTS (Continued)

| SECTION | 9. INITIALIZE PROCEDURE | 9-1 | • - | Initialize Procedure          |     |

|---------|-------------------------|-----|-----|-------------------------------|-----|

|         | Introduction            |     | 9-5 | Looping In Initialize Routine | 9-2 |

## LIST OF ILLUSTRATIONS

| Figure                                                                            | Title              | Page                                                                                | Figure                                                                    | Title                                                                                                                                                                                                                                                                                                                                                                           | Page                                                                                    |

|-----------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

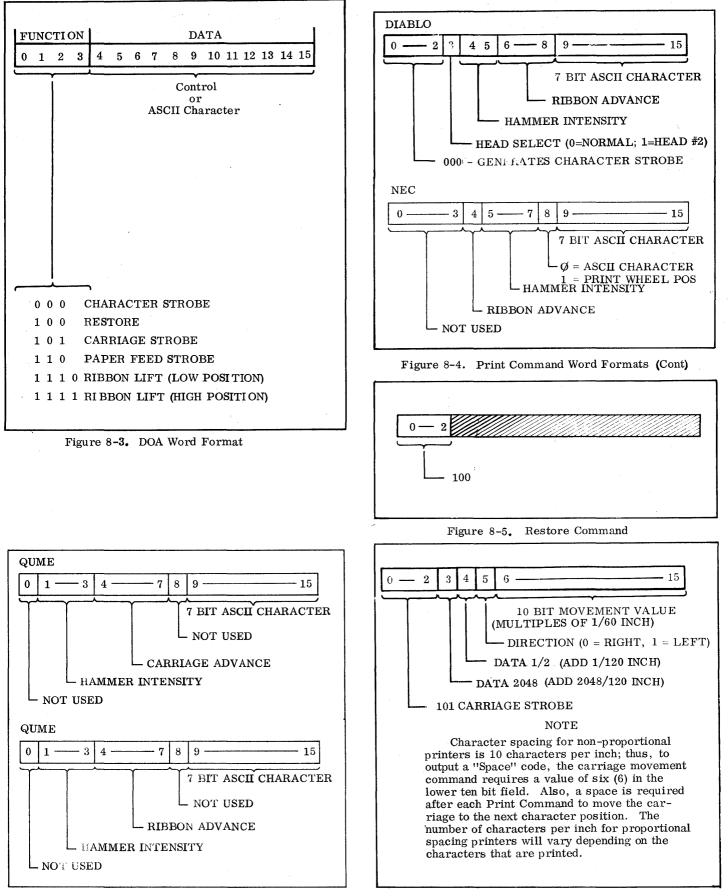

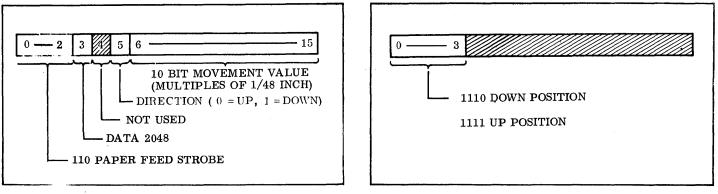

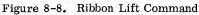

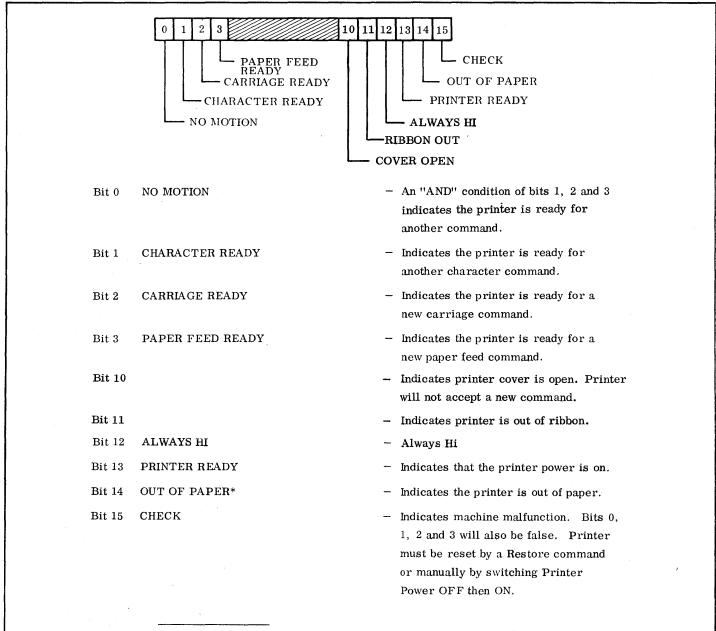

| 1-1<br>1-2<br>2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9<br>2-10 | J500 Videocomputer | 1-1<br>1-3<br>2-1<br>2-2<br>2-4<br>2-5<br>2-5<br>2-6<br>2-7<br>2-10<br>2-13<br>2-18 | 4-1<br>8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7<br>8-8<br>8-9<br>9-1 | International Keyboard (American)         Line Printer Data Character -         DOA Instruction.         Line Printer DIA Format         DOA Word Format.         Print Command Word Format.         Restore Command         Carriage Strobe Command.         Paper Feed Command.         Ribbon Lift Command         Status Word Format.         Normal Initialize CRT Display | 4-1<br>8-3<br>8-4<br>8-4<br>8-4<br>8-4<br>8-4<br>8-4<br>8-4<br>8-4<br>8-4<br>8-5<br>9-2 |

## LIST OF TABLES

| Table  | Title                            | Page   | Table | Title                               | Page   |

|--------|----------------------------------|--------|-------|-------------------------------------|--------|

| 1-1    | Functional and Physical          |        | 2-14  | Mask Out Bits                       | 2-18   |

|        | Specifications                   | 1-2    | 2-15  | Halt and Flag Instructions          | 2-19   |

| 1 - 2  | Controls and Switches            | 1 - 2  | 2-16  | Status Flags                        | 2 - 19 |

| 2-1    | Summary of Addressing Modes      | 2-2    | 2-17  | Control Flag Codes                  | 2-19   |

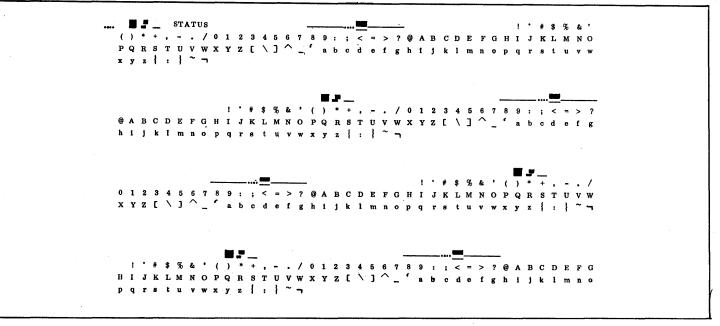

| 2-2    | Notation Used in Instruction     |        | 4-1   | Eight Bit ASCII Code                | 4 - 2  |

|        | Descriptions                     | 2-3    | 5-1   | Diskette Initializing Format -      |        |

| 2-3    | Load and Store Instructions      | 2-4    |       | Single Density                      | 5 - 4  |

| 2-4    | Arithmetic Instructions          | 2-5    | 5-2   | Diskette Initializing Format -      |        |

| 2-5    | Logical Instructions             | 2-5    |       | Double Density                      | 5-5    |

| 2-6    | Skip Instructions                | 2-8    | 8-1   | Line Printer Character Set          | 8-2    |

| 2-7    | Transfer-of-Control Instructions | 2-8    | 8-2   | Seven Bit ASCII Code for 96 Char-   |        |

| 2-8    | Branch-on-Condition Codes        | 2 - 10 |       | acter Diablo Hy Type II and Qume    |        |

| 2-9    | Shift Instructions               | 2 - 12 |       | Printers                            | 8-6    |

| 2 - 10 | Register Instructions            | 2-12   | 8-3   | Seven Bit ASCII Code for 88 Char-   |        |

| 2-11   | Input/Output Instructions        | 2-15   |       | acter Diablo Word Processing        |        |

| 2 - 12 | Interrupt Priorities             | 2-16   |       | Printer                             | 8-7    |

| 2 - 13 | Device Addresses                 | 2-16   | 9-1   | DIP Switch Functions - Location 24H | 9-1    |

| - 10   |                                  |        | A-1   | Instruction Set                     | A-1    |

|        |                                  |        | M=1   |                                     | A-1    |

## 1-1. INTRODUCTION.

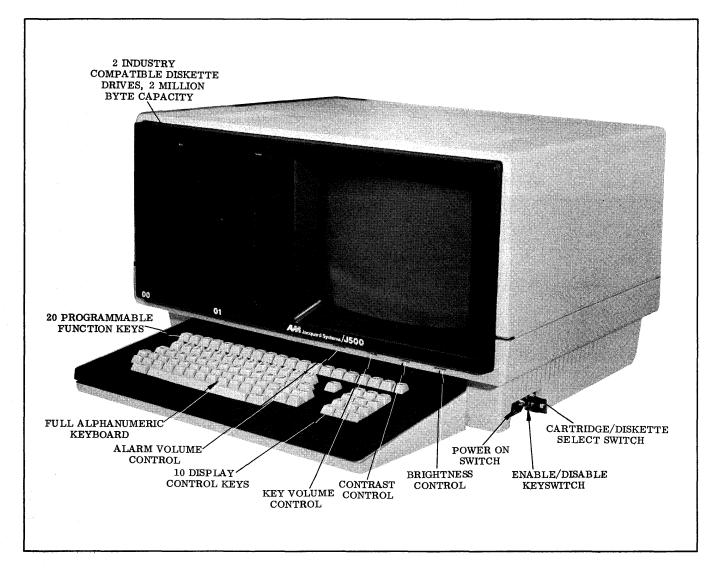

The J500 Videocomputer is a versatile single user word processing and business oriented data processing system. The system is a complete self-contained, stand alone system that uses the same vast store of programs as larger systems currently produced by Jacquard. The J500 system, Figure 1-1, is packaged in an attractive cabinet designed to compliment and blend with standard office equipment and furniture. Optional peripheral devices are similarly packaged. The J500 and peripheral options have internal power strapping provisions which allow factory set-up for operation on international power standards of 100VAC, 115VAC or 230VAC at 50Hz or 60Hz. Refer to Table 1-1 for functional and physical specifications.

Figure 1-1. J500 Videocomputer

Table 1-1. Functional and Physical Specifications

PROCESSOR

- Word Size 16 Bits

- Accumulators Four

- Push Down Stack 16 Deep

- Status Register

- Program Counter

- Memory Address Register

Direct Memory Access

- 1,500,000 bytes/sec.

Programmed I/O approx.

375 K bytes/sec.

- Interrupt System

- Real Time Clock

- Powerful instruction set

- KEYBOARD

- Removable via cable

- Full Upper/Lower ASCII Key Layout

- Display Control

- Keys (10) • Edit/Function Keys (20)

- "n" Key Rollover

- PHYSICAL

J500 Videocomputer: Height 14.5 in. Width 24.5 in. Depth 17.25 in. Weight 95 lbs.

Keyboard:

Height 3.5 in. Width 18.5 in. Depth 9.25 in. Weight 2.5 lbs Total Depth (J500 and Keyboard): 26.5 inches.

- CRT DISPLAY

- 12" CRT

- 80 x 24 Format

High Resolution

- Characters

- Full ASCII Character Set

- 128 User Programmable Characters

- High Contrast

- Low Reflectance faceplate

- No flicker

- Update at CPU speed

## DISKETTES

- 2 Drives Built-in

- Industry compatible format

- 250K, 500K or 1M bytes/Drive

- Random access

- Removable Media

## MEMORY

Semi-Conductor

128K bytes (Standard)

## ENVIRONMENTAL

Operating Temperature 60° F to 85° F (15.5° C to 294° C) ambient air Humidity: 20% to 80% RH (non-condensing)

## 1-3 PHYSICAL ORGANIZATION.

The design of the J500 Videocomputer simplifies system configuration and I/O Peripheral needs for variety of applications. The central processor, memory, controllers and interfaces are contained on a single 13  $I/4" \ge 25"$  printed circuit board. This CPU board is mounted in the rear of the J500 chassis and has plug-in interfacing for the available peripheral options. The CRT, Keyboard and the power supply also connect to the CPU board. Operating controls and switches for the J500 are defined in Table 1-2.

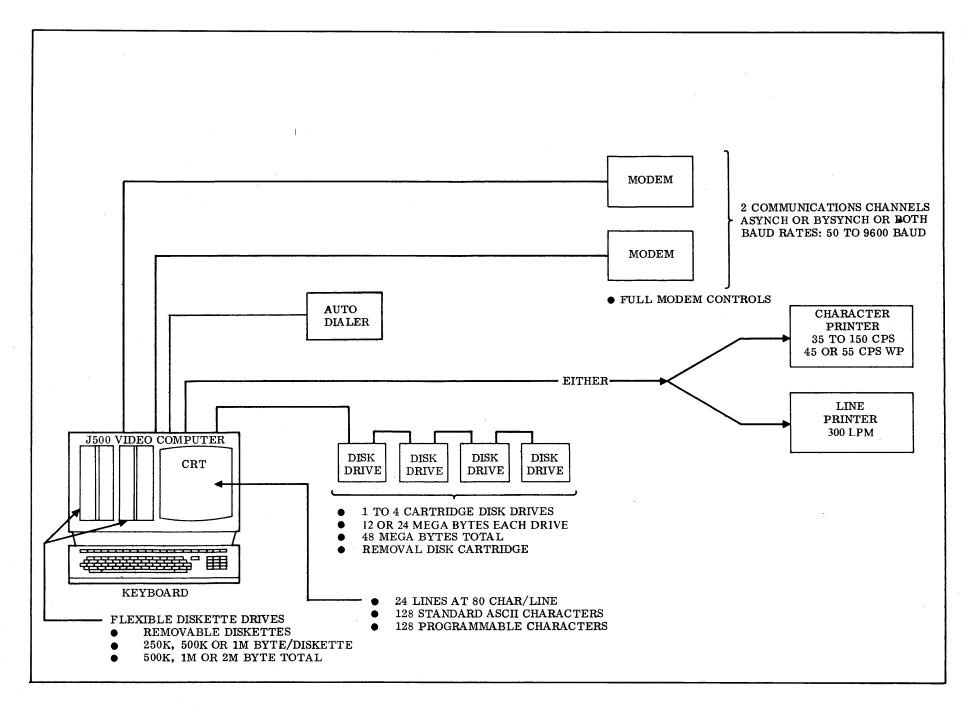

The J500 Videocomputer is complete and ready to interface to:

- 1. Two single or double density floppy disks (internal to J500 cabinet).

- 2. One 24 line, 80 characters per line CRT display (internal to J500 cabinet).

- 3. One Printer (external) either character or line.

- 4. Two Communication ports of either BISYNC or ASYNC compatible at all standard Baud Rates with complete Modem Controls.

- 5. An Automatic Dialer.

- 6. Either 12, or 24 megabyte disk storage with fixed and removable media. Each J500 will support 4-12 M disks or 2-24M disks.

The two Communication Ports provide a completely open ended means of interfacing with Optical Character Readers, Printers, Embossers, etc. In most cases programs are already available for these installations.

## Table 1-2. Controls and Switches

| Control/Switch                    | Function                                                                                       |

|-----------------------------------|------------------------------------------------------------------------------------------------|

| POWER ON<br>Switch                | Applies AC line voltage to power supply and internal cooling fans.                             |

| ENABLE/<br>DISABLE<br>Keyswitch   | Allows unit to operate in ENABLE position.                                                     |

| CARTRIDGE/<br>DISKETTE<br>Switch  | Device select switch which specifies<br>which device the Auto-Program Load<br>will occur from. |

| A LARM<br>VOLUME<br>potentiometer | Audible alarm volume control.                                                                  |

| KEY VOLUME<br>potentiometer       | Keyboard audible "click" volume control.                                                       |

| CONTRAST<br>potentiometer         | CRT contrast control.                                                                          |

| BRIGHTNESS<br>potentiometer       | CRT brightness control.                                                                        |

|                                   |                                                                                                |

1-2 PHYSICAL/FUNCTIONAL ORGANIZATION.

The J500 consists of:

- (1) A l6-bit general purpose digital computer which incorporates state-of-the-art Bi-Polar Proms and discrete TTL logic.

- (2) 128K, 8 bit bytes of memory for storage of data and application programs.

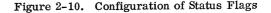

- (3) Typewriter style keyboard for data entry plus special function keys.

- (4) A 12-inch, 1920 character CRT screen for data display.

- (5) Two industry compatible diskette drives (floppy disk) for data entry and additional program and data storage.

1-3

## 1-4. FUNCTIONAL ORGANIZATION.

The J500 is a general purpose computer system with a 16bit word length. The central processor is organized around four accumulators, two of which can be used as index registers. This accumulator/index register organization provides ease in programming and greater efficiency both in time and memory use.

The J500 contains a fast and powerful microprocessor that reads, interprets, and executes MACRO instructions from the J500 main memory. Because of the processor's high speed and powerful micrologic, it is also quite capable of:

- 1. Controlling the CRT directly

- 2. Controlling the Floppy Disks including Direct Memory Access

- 3. Controlling both communication ports

- 4. Controlling D3000 Disks

- 5. Controlling the printer

- 6. Controlling the keyboard

- 7. Controlling the Auto Dialer

Plus performing lesser tasks such as:

- 1. Updating the real time clock

- 2. Managing interrupts

- 3. Control panel operations

- 4. Hardware diagnostics for both fault detection and location

The central processor is the control unit for the entire system: it governs all peripheral I/O equipment, performs all arithmetic, logical and data handling operations, and sequences the program. It is connected to the memory by a SUM bus and to the peripheral equipment by a data bus.

The processor handles sixteen bit words that are numbered 0 to 15, left to right. Words are used either as computer instructions in a program, as addresses, or as operands, i.e., dynamic data for processing. The arithmetic instructions operate on fixed point binary numbers, either unsigned or the equivalent signed numbers using the two's complement convention.

## 1-5. SYSTEM FEATURES.

1-6. EXPANSION CAPABILITIES. The design of the J500 Videocomputer simplifies system configuration and I/O peripheral needs for a variety of applications. Both software and hardware are presently designed to accommodate a combination of printers, communication terminals, disk drives and floppy drives. System expansion is achieved through the cable connectors on the J500 CPU board.

1-7. USER INTERFACE. Data input at the keyboard is entered directly into the processor and displayed on the CRT. Additional data and/or records stored in either the processor's memory or on its diskette can be accessed by the application program. Attachment of a peripheral device such as a printer permits reports to be generated directly or as a result of calculations and data manipulation performed within the processor, after data entry at the keyboard. Thus, the entire data processing operation from data entry to finalized report can be conducted by the user directly and without delay.

## 1-8. HARDWARE FEATURES.

The J500 has extensive data processing facilities which include: an interrupt system, real time clock and a direct memory access channel.

1-9. DISKETTES. The J500 has two "IBM 3740 format compatible" diskette units. Each diskette unit has a storage capacity of approximately 250K for single-sided single density, 500K for single-sided double-density or 1M bytes for double-sided double density. Programs and/or data may be stored on each of these two diskette units. The J500 has provisions for the addition of two externally mounted diskette units. This increases the on-line data storage capacity for diskettes to approximately four million bytes of data.

Up to four devices can be attached in a daisy chain fashion. All types of diskettes can be mixed within a daisy chain: single-sided single-density, single-sided double-density, and double-sided double-density.

#### 1-10. PERIPHERAL AND COMMUNICATION OPTIONS.

Optional equipment and peripheral and communications interfaces available with the J500 Videocomputer are shown in Figure 1-2. All of the peripheral equipment controllers are contained on the J500 CPU board.

#### **OPERATING PROCEDURES**

Refer to Section 9 for information on power turn-on procedures and initialization of the J500.

## 2-1. INTRODUCTION.

The J500 Instruction Set consists of eight functional classes of instructions:

- LOAD AND STORE

- ARITHMETIC

- LOGICAL

- SKIP

- SHIFTS

- TRANSFER OF CONTROL

- REGISTER

- INPUT/OUTPUT AND MISCELLANEOUS

The instructions in each functional class are described as a group. The description of each instruction includes the name of the instruction, its mnemonic, its word format, its operation in the form of an equation, and an explanation of its operation. A tabulated summary of each type of instruction precedes the detailed descriptions. Brief descriptions of the registers referred to in the instruction descriptions are also provided.

## 2-2. ARITHMETIC AND LOGIC UNITS REFERENCED IN INSTRUCTIONS (See Figure 2-1).

- PUSH-DOWN STACK

- STATUS REGISTER

- PROGRAM COUNTER (PC)

- ACCUMULATOR 0 (AC0)

- ACCUMULATOR 1 (AC1)

- ACCUMULATOR 2 (AC2)

- ACCUMULATOR 3 (AC3)

2-3. PUSH-DOWN STACK (LIFO). The microprocessor has a hardware stack that data may be stored in or retrieved from on a last-in/first-out basis. The stack is 16 words deep and is accessible through the top location. As a data word is entered into the stack, the contents of the top location and each other location are pushed downward to the next lower level; if the stack is full, the word in the bottom location is lost. Conversely, the contents of the top location are pulled from the stack during retrieval of a data word; the top location and each lower location are replaced by the contents of the next lower location, and zeroes are entered into the bottom location.

The stack is used primarily for saving status during interrupts and for saving subroutine return addresses. It may be used also for temporary storage of data using the PUSH, PULL, XCHRS, PUSHF, and PULLF instructions (described later in this section).

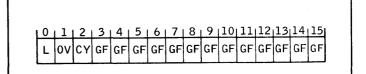

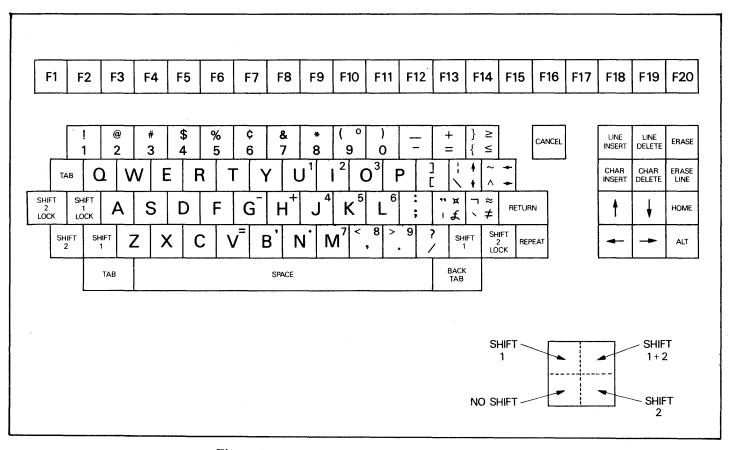

2-4. STATUS REGISTER. There are 16 status flags in the status register. These flags may be pushed onto the stack (saved) or may be loaded from the stack (restored). During such operations, the flags are configured as a 16bit word: The LNK (Link), OV (Overflow), and CY (Carry) flags are the first, second, and third most significant bits,

- PUSH DOWN STACK

- STATUS REGISTER

- PROGRAM COUNTER (PC)

- ACCUMULATOR 0 (AC0)

- ACCUMULATOR 1 (AC1)

- ACCUMULATOR 2 (AC2)

- ACCUMULATOR 3 (AC3)

|   | PUSH DOWN STACK<br>(LIFO) |

|---|---------------------------|

|   | STATUS REG<br>(16 FLAGS)  |

|   | PROGRAM COUNTER (PC)      |

|   | WORKING REGISTERS         |

|   | ACCUMULATOR 3 (AC3)       |

| - | ACCUMULATOR 2 (AC2)       |

|   | ACCUMULATOR 1 (AC1)       |

|   | ACCUMULATOR 0 (ACO)       |

## Figure 2-1. Arithmetic and Logic Units Referenced in Instructions

respectively, and the remaining 13 general-purpose flags comprise the remaining 13 less significant bits (Figure 2-11). Note that the SELECT flag is not included in the status register.

The LNK flag is primarily used in some shifting operations, and the CY and OV flags are adjuncts for arithmetic operations. The specific uses of the flags are elaborated upon in the appropriate instruction descriptions.

2-5. PROGRAM COUNTER (PC). The Program Counter (PC) holds the address of the next instruction to be executed. When there is a branch to another address in the main memory, the branch address is set into the Program Counter. A skip instruction merely increments the Program Counter by 1, thus causing one instruction to be skipped. 2-6. ACCUMULATORS 0, 1, 2, AND 3 (AC0, AC1, AC2, AND AC3). The accumulators are used as working registers for data manipulation. Data may be fetched from a location in memory to an accumulator, and may be stored from an accumulator to a location in memory. The particular accumulator to take part in an operation is specified by the programmer in the appropriate instruction.

#### 2-7. DATA AND INSTRUCTIONS.

2-8. DATA REPRESENTATION. Data is represented in the microprocessor in twos-complement integer notation. In this system, the negative of a number is formed by complementing each bit in the data word and adding 1 to the complemented number. The sign is indicated by the most significant bit. In the 16-bit word of the CPU, when bit "0" is a "0", it denotes a positive number; when it is a "1", it denotes a negative number. Maximum number ranges for this system are  $7FFF_{16}$  (+32767<sub>10</sub>) and  $8000_{16}$  (-32768<sub>10</sub>). The carry flag will be set if there is a carry out of bit 0 as the result of an addition operation. The overflow flag will be set if bit 0 of the result of an addition is different than the signs of the operands. Overflow cannot occur if the operands have different signs. Since subtraction is performed by adding the 2's complement of the subtrahend to the minuend, these rules apply to subtraction as well.

2-9. INSTRUCTIONS. There are eight classes of instructions. Each class of instruction and the associated instructions are summarized in a table preceding the descriptions of the instructions. Also, the applicable instruction word formats are defined.

## 2-10. MEMORY ADDRESSING.

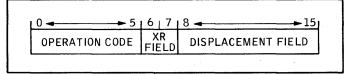

The instruction set provides for direct and indirect memory addressing. For direct addressing, three distinct modes are available: base page (or absolute), program-counter relative, and indexed. The mode of addressing is specified by the XR field of the simplified instruction word format shown in Figure 2-2.

Figure 2-2. Instruction Word for Addressing Memory

2-11. BASE PAGE ADDRESSING. When the XR field is 00, it specifies base page addressing. Base page is directly accessible from any location in the address space of the memory. In this mode, the effective address is formed by setting bits 0 through 7 to zero and using the value of the 8-bit displacement field as an absolute address. Up to 256 words (locations 0 through 255) may be addressed in this way.

2-12. PROGRAM-COUNTER RELATIVE ADDRESSING. Program-counter relative addressing is specified when the XR field is 01. The displacement is treated as a signed number such that its sign bit (bit 8) is propagated to bits 0 through 7, and the effective address is formed by adding the contents of the PC to the resulting number. This permits PC-relative addressing -128 and +127 locations from the PC value; however, at the time of formation of the address, the PC has already been incremented in the microprogram and is pointing to the next macroinstruction. Because of this, the actual addressing range is from -127to +128 from the current instruction.

2-13. INDEXED ADDRESSING. Indexed addressing is done with reference to only Accumulator 2 or 3 (AC2 or AC3). In this mode, the displacement field is again interpreted as a signed 8-bit number from -128 to +127 with the sign (bit 8) extended through bits 0 through 7. The contents of the chosen index register (AC2 when  $XR = 10_2$  and AC3 when  $XR = 11_2$ ) are added to the number formed from the displacement value to yield an effective address that can reach any location in 65,536 words of memory. A summary of addressing modes is shown in Table 2-1.

Table 2-1. Summary of Addressing Modes

| XR<br>FIELD | ADDRESSING<br>MODE                | EFFECTIVE<br>ADDRESS | RANGE                          |

|-------------|-----------------------------------|----------------------|--------------------------------|

| 00          | Base                              | EA = disp            | $0 \le disp \le 255$           |

| 01          | Relative to<br>Program<br>Counter | EA = disp + (PC)     | -128≤disp≤127                  |

| 10          | Relative to<br>AC2                | EA = disp + (AC2)    | $-128 \le disp \le 127$        |

| 11          | Relative to<br>AC3                | EA = disp + (AC3)    | $-128 \le \text{disp} \le 127$ |

2-14. INDIRECT ADDRESSING. Indirect addressing is accomplished by first calculating the effective address (EA) using the same method used for direct addressing; the memory location at this address contains a number that is then used as the address of the operand. Only the following instructions use indirect addressing:

- Load Indirect (See Table 2-3)

- Store Indirect (See Table 2-3)

- Jump Indirect (See Table 2-7)

- Jump to Subroutine Indirect (See Table 2-7)

#### 2-15. <u>NOTATIONS AND SYMBOLS USED IN MICROPRO-</u> CESSOR INSTRUCTION DESCRIPTIONS.

Definitions of the notations and symbols used in the J500 descriptions are listed in Table 2-2. The notations are listed in alphabetical order followed by the symbols. Uppercase mnemonics refer to fields in the instruction word; lower-case mnemonics refer to the numerical value of the corresponding fields. In cases where both lower- and uppercase mnemonics are composed of the same letters, only the lower-case mnemonic is shown in Table 2-2. The use of a lower-case notation designates variables.

## Table 2-2. Notation Used In Instruction Descriptions

| NOTATION     | MEANING                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| ACr          | Denotes a specific working register (AC0, AC1, AC2, or AC3), where $\underline{r}$ is the number of the accumula-<br>tor referenced in the instruction.                                                                                                                              |  |  |  |  |  |

| AR           | Denotes the address register used for addressing memory or peripheral devices.                                                                                                                                                                                                       |  |  |  |  |  |

| cc           | Denotes the 4-bit condition code value for conditional branch instructions.                                                                                                                                                                                                          |  |  |  |  |  |

| ctl          | Denotes the 7-bit control-field value for flag, input/output, and miscellaneous instructions.                                                                                                                                                                                        |  |  |  |  |  |

| CY           | Indicates that the Carry flag is set if there is a carry due to the instruction (either an addition or a subtraction).                                                                                                                                                               |  |  |  |  |  |

| disp         | Stands for displacement value and it represents an operand in a non-memory reference instruction or<br>an address field in a memory reference instruction. It is an 8-bit, signed twos-complement number<br>except when base page is referenced; in the latter case, it is unsigned. |  |  |  |  |  |

| dr           | Denotes the number of a destination working register that is specified in the instruction-word field.<br>The working register is limited to one of four: AC0, AC1, AC2, or AC3.                                                                                                      |  |  |  |  |  |

| EA           | Denotes the effective address specified by the instruction directly, indirectly, or by indexing. The con-<br>tents of the effective address are used during execution of an instruction. (See Table 2-1).                                                                            |  |  |  |  |  |

| fc           | Denotes the number of the referenced flag (See Table 2-13).                                                                                                                                                                                                                          |  |  |  |  |  |

| INT EN       | Denotes the Interrupt Enable Control Flag.                                                                                                                                                                                                                                           |  |  |  |  |  |

| IOREG        | Denotes an input/output register in a peripheral device.                                                                                                                                                                                                                             |  |  |  |  |  |

| L            | Denotes 1-bit link (L) flag.                                                                                                                                                                                                                                                         |  |  |  |  |  |

| ov           | Indicates that the overflow flag is set if there is an overflow due to the instruction (either an addition or a subtraction). (See Par. 2-8)                                                                                                                                         |  |  |  |  |  |

| PC           | Denotes the program counter. During address formation, it is incremented by 1 to contain an address 1 greater than that of the instruction being executed.                                                                                                                           |  |  |  |  |  |

| r            | Denotes the number of a working register that is specified in the instruction-word field. The working register is limited to one of four: AC0, AC1, AC2, or AC3.                                                                                                                     |  |  |  |  |  |

| SEL          | Denotes the Select control flag. It is used to select the carry or overflow for sensing with the Branch-On Condition instruction, and to include the link bit (L) in shift operations. Note that this flag is not included in the Status flag register (Figure 2-11).                |  |  |  |  |  |

| sr           | Denotes the number of a source working register that is specified in the instruction-word field. The working register is limited to one of four: AC0, AC1, AC2, or AC3.                                                                                                              |  |  |  |  |  |

| STK          | Denotes the hardware Push-Down Stack that data is stored in or retrieved from.                                                                                                                                                                                                       |  |  |  |  |  |

| xr           | When not zero, this value designates the register to be used in the indexed and relative memory-addressing modes. (See Table 2-1).                                                                                                                                                   |  |  |  |  |  |

| ()           | Denotes the contents of the item within the parentheses. (ACr) is read as "the contents of ACr." (EA) is read as "the contents of EA."                                                                                                                                               |  |  |  |  |  |

| []           | Denotes "the result of, "                                                                                                                                                                                                                                                            |  |  |  |  |  |

| ~            | Indicates the logical complement (ones complement) of the value on the right-hand side of $\sim$ .                                                                                                                                                                                   |  |  |  |  |  |

|              | Means "replaces."                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| <b>←</b>     | Means "is replaced by. "                                                                                                                                                                                                                                                             |  |  |  |  |  |

| @            | Appearing in the operand field of an instruction, denotes indirect addressing.                                                                                                                                                                                                       |  |  |  |  |  |

| • ^          | Denotes an AND operation (either).                                                                                                                                                                                                                                                   |  |  |  |  |  |

| $\mathbf{V}$ | Denotes an OR operation.                                                                                                                                                                                                                                                             |  |  |  |  |  |

| ₩            | Denotes an exclusive OR operation.                                                                                                                                                                                                                                                   |  |  |  |  |  |

## 2-16. INSTRUCTION DESCRIPTIONS.

Each class and subclass of instruction is introduced by a table that lists and summarizes the instructions and then the word format is illustrated. The detailed descriptions provide the following information:

- Name of instruction followed by operation code mnemonic in parentheses

- Operation Code in word format diagram

- Operation in equation notation

- Detailed description of operation

- 2-17. LOAD AND STORE INSTRUCTIONS.

The four instructions in this group are summarized in Table 2-3, then individually described. The word format is shown in Figure 2-3.

| Table 2-3. Load and | Store | Instructions |

|---------------------|-------|--------------|

|---------------------|-------|--------------|

| INSTRUC-<br>TION  | OP<br>CODE | OPERATION             | ASSEMBLER<br>FORMAT |

|-------------------|------------|-----------------------|---------------------|

| LOAD              | 1000       | (ACr)← (EA)           | LD r, disp(xr)      |

| LOAD<br>INDIRECT  | 1001       | (ACr) <b>→</b> ((EA)) | LD r, @disp(xr)     |

| STORE             | 1010       | (EA) 🖛 (ACr)          | ST r, disp(xr)      |

| STORE<br>INDIRECT | 1011       | ((EA)) <b>←</b> (ACr) | ST r, @disp(xr)     |

#### NOTE

For indirect operations, the symbol @ must precede the memory location designated in the operand field of the assembler instruction.

Figure 2-3. Load and Store Instruction Format

|   |   | (பப) |     |     | 6.7 | ο.   |  |  |  |  | .15 |

|---|---|------|-----|-----|-----|------|--|--|--|--|-----|

| 0 |   | L    | 2   | 4 5 | 0 / | 0    |  |  |  |  |     |

| 1 | 0 | 0    | . 0 | r   | ×r  | disp |  |  |  |  |     |

Operation:  $(ACr) \leftarrow (EA)$

TOAD /TD) 8000

Description: The contents of ACr are replaced by the contents of EA. The initial contents of ACr are lost; the contents of EA are unaltered.

LOAD INDIRECT (LD@) 900016

|     | 2 | 4 5 | 6 / |      |

|-----|---|-----|-----|------|

| 100 | 1 | r   | xr  | disp |

Operation: (ACr) - ((EA))

Description: The contents of ACr are replaced indirectly by the contents of EA. The initial contents of ACr are lost; the contents of EA and the location that designates EA are unaltered.

| STORE | (ST) | $A000_{16}$ |  |

|-------|------|-------------|--|

|-------|------|-------------|--|

|     |     |    | 8           15 |

|-----|-----|----|----------------|

| 101 | 0 r | xr | disp           |

Operation: (EA) - (ACr)

Description: The contents of EA are replaced by the contents of ACr. The initial contents of EA are lost; the contents of ACr are unaltered.

## STORE INDIRECT (ST@) B00016

|            | 3 | 4 5      | 6 7     | 8 |      |  | 15 |

|------------|---|----------|---------|---|------|--|----|

| 101        | 1 | r        | xr      |   | disp |  |    |

| Operation: |   | ((EA)) ◄ | — (ACr) | ) |      |  |    |

Description: The contents of EA are replaced indirectly by ACr. The initial contents of EA are lost; the contents of ACr and the location that designates EA are unaltered.

Programming Note: Since the J500 fetches the "next" instruction from memory while executing an instruction, it is incorrect to store into the "next" location with the expectation that the value stored will then be accessed for execution. Storage into a location which will be executed "after next" may also be unsafe.

## 2-18. ARITHMETIC INSTRUCTIONS.

The two instructions in this group are summarized in Table 2-4 and then described individually. Either of these instructions may be carried out with any of the four generalpurpose accumulators (AC0, 1, 2, or 3). The word format is shown in Figure 2-4.

Table 2-4. Arithmetic Instructions

| INSTRUCTION    | OPCODE | OPERATION                                        | ASSEMBLER<br>FORMAT |

|----------------|--------|--------------------------------------------------|---------------------|

| ADD (ADD)      | 1100   | $(ACr) \leftarrow (ACr) + (EA), OV, CY$          | ADD r, disp(xr)     |

| SUBTRACT (SUB) | 1101   | $(ACr) \leftarrow (ACr) + \sim (EA) + 1, OV, CY$ | SUB r, disp(xr)     |

Figure 2-4. Arithmetic Instructions

|   | ADD (ADD) C000 <sub>16</sub> |   |   |   |            |       |   |      |  |   |  |   |    |  |

|---|------------------------------|---|---|---|------------|-------|---|------|--|---|--|---|----|--|

| ŀ | 0                            |   |   | 3 | <u>4 5</u> | 6   7 | 8 |      |  | 1 |  | _ | 15 |  |

|   | 1                            | 1 | 0 | 0 | ŗ          | xr    |   | disp |  |   |  |   |    |  |

|   |                              |   |   |   |            |       |   |      |  |   |  |   |    |  |

Operation:  $(ACr) \leftarrow (ACr) + (EA), OV, CY$

Description: The contents of ACr are added algebraically to the contents of the effective memory location EA. The sum is stored in ACr, and the contents of EA are unaltered. The preceding contents of ACr are lost. The carry and overflow flags are set according to the result of the operation. (Refer to para. 2-8)

# SUBTRACT (SUB) D00016

| 0 |   |   | 3 | 4 5 | 6   7 | 8           15 |

|---|---|---|---|-----|-------|----------------|

| 1 | 1 | 0 | 1 | ۲.  | xr    | disp           |

Operation: (ACr)  $\leftarrow$  (ACr) +  $\sim$  (EA) + 1, OV CY

Description: The contents of ACr are added to the twos complement of the effective memory location EA. The result is stored in ACr, and the effective memory location is unaltered. The carry and overflow flags are set according to the result of the operation. (Refer to para. 2-8.)

#### 2-19. LOGICAL INSTRUCTIONS.

There are two instructions in this group, summarized in Table 2-5 and then described individually. Either of the instructions may be carried out with only two of the general-purpose accumulators, AC0 or AC1. The word format is shown in Figure 2-5.

| INSTRUC-<br>TION | OPCODE | OPERATION                            | ASSEMBLER<br>FORMAT |             |  |  |  |

|------------------|--------|--------------------------------------|---------------------|-------------|--|--|--|

| AND              | 01100  | $(ACr) \rightarrow (ACr) \land (EA)$ | AND                 | r, disp(xr) |  |  |  |

| OR               | 01101  | $(ACr) \rightarrow (ACr) \lor (EA)$  | OR                  | r, disp(xr) |  |  |  |

Figure 2-5. Logical Instruction Format

AND (AND) 600016

| 0 |   |   |   | 4 | 5 | 6 7 | 8 | I |    | 1  | I | 15 |

|---|---|---|---|---|---|-----|---|---|----|----|---|----|

| 0 | 1 | 1 | 0 | 0 | r | ×r  |   |   | di | sp |   |    |

Operation: (A

$(ACr) - (ACr) \wedge (EA)$

Description: The contents of ACr (where r is either 0 or 1) and the contents of the effective memory location EA are ANDed, and the result is stored in ACr. The initial contents of ACr are lost, and the contents of EA are unaltered. OR (OR) 6800<sub>16</sub>

| <br>0 |      |     | 1 | 4    | 5    | 6 7     | 8      |      | 15 |

|-------|------|-----|---|------|------|---------|--------|------|----|

| 0     | 1    | 1   | 0 | 1    | r    | xr      |        | disp |    |

| Ope   | rati | on: |   | (AC1 | c) 🔫 | — (ACr) | √ (EA) |      |    |

W. Car

**Description:** The contents of ACr (where r is either 0 or 1) and the contents of the effective memory location EA are ORed inclusively, and the result is stored in ACr. The initial contents of ACr are lost, and the contents of EA are unaltered.

## 2-20. SKIP INSTRUCTIONS.

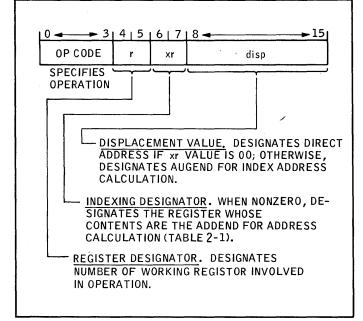

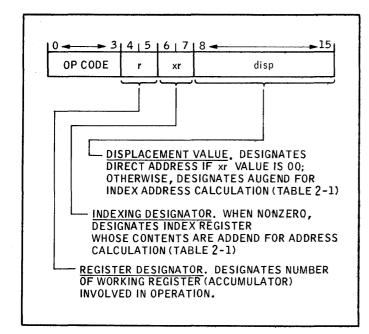

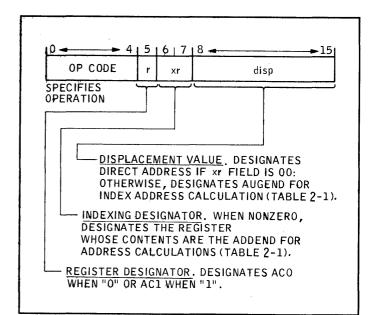

The five skip instructions are summarized in Table 2-6. The three word formats required are shown in Figure 2-6.

| MEMORY REFERENCE SKIP INSTRUCTION                                                                                                                                                                  |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                                                                                                                                                                                    | 15  |

| OP CODE xr disp                                                                                                                                                                                    |     |

|                                                                                                                                                                                                    | _   |

| DISPLACEMENT VALUE. DESIGNATES DIREC<br>ADDRESS IF xr VALUE IS 00; OTHERWISE,<br>DESIGNATES AUGEND FOR THE ADDRESS CAL<br>CULATION (TABLE 2-1).                                                    | 1   |

| INDEXING DESIGNATOR. WHEN NONZERO,<br>DESIGNATES THE REGISTER<br>WHOSE CONTENTS ARE THE ADDEND FOR<br>ADDRESS CALCULATION (TABLE 2-1).                                                             |     |

| REGISTER REFERENCE INSTRUCTION                                                                                                                                                                     |     |

| 10 - 31415161718 -                                                                                                                                                                                 | 151 |

| OP CODE r xr disp                                                                                                                                                                                  |     |

| 22                                                                                                                                                                                                 |     |

|                                                                                                                                                                                                    |     |

|                                                                                                                                                                                                    |     |

| DISPLACEMENT VALUE, DESIGNATES<br>DIRECT ADDRESS IF xr VALUE IS 00;<br>OTHERWISE DESIGNATES AUGEND FOR<br>THE ADDRESS CALCULATION<br>(TABLE 2-1).                                                  |     |

| INDEXING DESIGNATOR. WHEN NONZERO,<br>DESIGNATES THE REGISTER<br>WHOSE CONTENTS ARE THE ADDEND FOR<br>ADDRESS CALCULATIONS (TABLE 9-1).                                                            |     |

| REGISTER DESIGNATOR. SPECIFIES NUMBER<br>OF REGISTER WHOSE CONTENTS ARE COMPARED<br>WITH CONTENTS OF EFFECTIVE ADDRESS IN<br>DETERMINING WHETHER SKIP OPERATION<br>OCCURS. MAY BE ACO, 1, 2, OR 3. |     |

|                                                                                                                                                                                                    |     |

Figure 2-6. Skip Instruction Formats

LIMITED REGISTER REFERENCE INSTRUCTION 15161718 --15 OP CODE disp r xr DISPLACEMENT VALUE. DESIGNATES DIRECT ADDRESS IF xr VALUE IS 00; OTHERWISE, DESIGNATES AUGEND FOR THE ADDRESS CALCULATION (TABLE 2-1). INDEXING DESIGNATOR. WHEN NONZERO. DESIGNATES THE REGISTER WHOSE CONTENTS ARE THE ADDEND FOR ADDRESS CALCULATIONS (TABLE 2-1). REGISTER DESIGNATOR. SPECIFIES NUMBER **OF REGISTER WHOSE CONTENTS ARE COMPARED** WITH CONTENTS OF EFFECTIVE ADDRESS IN DETERMINING WHETHER SKIP OPERATION OCCURS. MAY BE ONLY ACO OR AC1.

INCREMENT AND SKIP IF ZERO (ISZ) 780016

| I | 0 |   |   | l | 1 | 5 | 6 7 | 8           15 |

|---|---|---|---|---|---|---|-----|----------------|

|   | 0 | 1 | 1 | 1 | 1 | 0 | ×r  | disp           |

**Operation:**

$(EA) \leftarrow (EA) + 1$ ; if (EA) = 0,  $(PC) \leftarrow (PC) + 1$

**Description:** The contents of EA are incremented by 1. The new contents of EA are tested to determine whether they equal zero. If the new contents of EA equal zero, the contents of PC are incremented by 1, thus skipping the memory location designated by the initial contents of PC.

#### DECREMENT AND SKIP IF ZERO (DSZ) 7C0016

| ļ | 0   |      |     |   |      | 5  | 6 7     | 8       |      |      |     | ,<br> |       | 15     |

|---|-----|------|-----|---|------|----|---------|---------|------|------|-----|-------|-------|--------|

|   | 0   | 1    | 1   | 1 | 1    | 1  | ×r      |         |      | d    | isp |       |       |        |

|   | Ope | rati | on: |   | (EA) | -( | EA) - 1 | ; if (E | A) - | - 0, | (PC | ;) 🚽  | - (PC | C) + 1 |

**Description:** The contents of EA are decremented by 1. The new contents of EA are tested to determine whether they equal zero. If the new contents of EA equal zero, the contents of PC are incremented by 1, thus skipping the memory location designated by the initial contents of PC.

# SKIP IF GREATER (SKG) E00016

| L | 0 |  | 3 | 4 5 | 6 7 | 8 | <br>1 |    | 1 | 1 | 15 |

|---|---|--|---|-----|-----|---|-------|----|---|---|----|

|   |   |  | 0 |     | xr  |   | dis   | sp |   |   |    |

Operation:

on: If (ACr) > (EA),  $(PC) \leftarrow (PC) + 1$

Description:

The contents of ACr (when r is AC0, 1, 2, or 3) and the contents of the effective memory location EA are compared on an algebraic basis with due regard to the signs of the two operands. If the contents of ACr are greater than the contents of EA, the contents of PC are incremented by 1, thus skipping the memory location designated by the initial contents of PC.

Programming note: Care must be exercised when using the SKG instruction to compare memory addresses since the address in the upper half of address space ( $8000_{16}$ : FFFF<sub>16</sub>) will compare less than the address in the lower half (0:7FFF<sub>16</sub>) due to the arithemetic rather than logical compare which is employed in the CPU.

SKIP IF NOT EQUAL (SKNE) F00016

| 01 | 1 | 3 | 4 5 | 6 7 | 8         15 |

|----|---|---|-----|-----|--------------|

|    |   |   | r   |     | disp         |

Operation: If  $ACr \neq (EA)$ ,  $(PC) \leftarrow (PC) + 1$

Description: The contents of ACr (where ACr is AC0 1, 2, or 3) and the contents of the effective memory location EA are compared. If the contents of ACr and the effective memory location EA are not equal, the contents of PC are incremented, thus skipping the memory location designated by the initial contents of PC.

## SKIP IF AND IS ZERO (SKAZ) 700016

|            | 0 |           |  | l | 4     | 5   | 6 7      | 8         15              |

|------------|---|-----------|--|---|-------|-----|----------|---------------------------|

|            | 0 | 0 1 1 1 0 |  |   |       | r   | ×r       | disp                      |

| Operation: |   |           |  | ] | [f [( | ACı | r) ^ (EA | (PC) = 0, (PC) = (PC) + 1 |

Description: The contents of ACr (where r is either 0 or 1) and the contents of the effective memory location EA are ANDed. If the result equals zero, the contents of PC are incremented by 1, thus skipping the instruction designated by the initial contents of PC. Note that the contents of the register r is not altered by this instruction.

## 2-21. TRANSFER-OF-CONTROL INSTRUCTIONS,

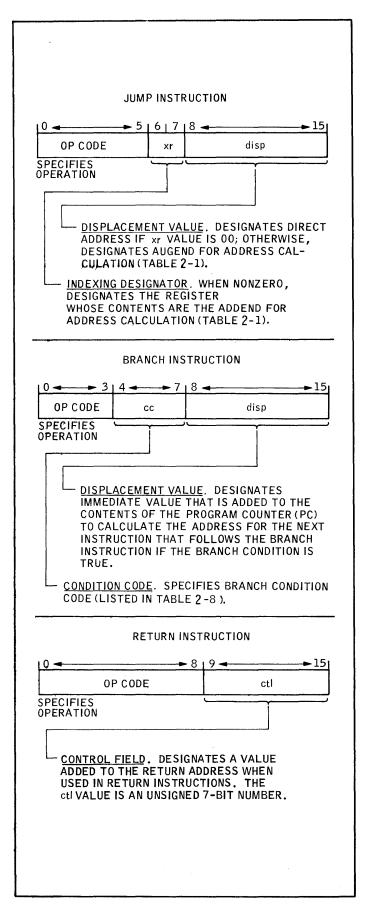

The eight instructions in this group are summerized in Table 2-7. The three wordformats required are shown in Figure 2-7.

| INSTRUCTION                | OPERATION<br>CODE | ASSEMBLER<br>FORMAT                                                    |                  |

|----------------------------|-------------------|------------------------------------------------------------------------|------------------|

| Memory References          |                   |                                                                        |                  |

| INCREMENT AND SKIP IF ZERO | 011110            | $(EA) \leftarrow (EA) + 1;$<br>IF (EA) = 0, (PC) $\leftarrow$ (PC) + 1 | ISZ disp (xr)    |

| DECREMENT AND SKIP IF ZERO | 011111            | $(EA) \leftarrow (EA) - 1;$<br>IF $(EA) = 0, (PC) \leftarrow (PC) + 1$ | DSZ disp (xr)    |

| Register References        |                   |                                                                        |                  |

| SKIP IF GREATER            | 1110              | IF $(ACr) > (EA)$ , $(PC) \leftarrow (PC) + 1$                         | SKG r, disp(xr)  |

| SKIP IF NOT EQUAL          | 1111              | IF (ACr) $\neq$ (EA), (PC) $\leftarrow$ (PC) +1                        | SKNE r, disp(xr) |

| Limited Register Reference |                   |                                                                        |                  |

| SKIP IF AND IS ZERO        | 01110             | IF $[(ACr) \land (EA)] = 0$ ,<br>(PC) $\checkmark$ (PC) +1             | SKAZ r, disp(xr) |

## Table 2-6. Skip Instructions

| Table 2-7. | Transfer-of-Control | Instructions |

|------------|---------------------|--------------|

|            |                     |              |

| INSTRUCTION                 | OPERATION<br>CODE                     | OPERATION                             | ASSEMBLER<br>FORMAT                   |

|-----------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| Jumps                       |                                       |                                       |                                       |

| JUMP                        | 001000                                | (PC) <del>→</del> EA                  | JMP disp(xr)                          |

| JUMP INDIRECT               | 001001                                | (PC) <b>←</b> (EA)                    | JMP@ disp(xr)                         |

| JUMP TO SUBROUTINE          | 001010                                | (STK) ← (PC); (PC) ← EA               | JSR disp(xr)                          |

| JUMP TO SUBROUTINE INDIRECT | 001011                                | (STK)                                 | JSR@ disp(xr)                         |

| Branch                      | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · | · · · · · · · · · · · · · · · · · · · |

| BRANCH-ON CONDITION         | 0001                                  | If CC IS TRUE<br>(PC)                 | BOC cc, disp                          |

| Returns                     | · · · · · · · · · · · · · · · · · · · |                                       |                                       |

| RETURN FROM INTERRUPT       | 00000010                              | (PC) ← (STK) + ctl;<br>INTEN FLAG SET | RTI ctl                               |

| RETURN FROM SUBROUTINE      | 000000100                             | (PC) 🖛 (STK) + ctl                    | RTS ctl                               |

|                             |                                       |                                       |                                       |

|                             |                                       |                                       |                                       |

| JUMP (JMP) 2000 <sub>16</sub>                                                                                                                              |         |      |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--|--|--|--|--|--|--|--|--|

| 0 0 1 0 0 0                                                                                                                                                | ×r      | disp |  |  |  |  |  |  |  |  |  |

| Operation: (PC) 	EA                                                                                                                                        |         |      |  |  |  |  |  |  |  |  |  |

| Description: The effective address EA replaces the contents of PC. The next instruction is fetched from the location designated by the new contents of PC. |         |      |  |  |  |  |  |  |  |  |  |

| JUMP (JMP@) INDIRE                                                                                                                                         | CT 2400 | 16   |  |  |  |  |  |  |  |  |  |

|                                                                                                                                                            | 6 7     |      |  |  |  |  |  |  |  |  |  |

| 0 0 1 0 0 1                                                                                                                                                | ×r      | disp |  |  |  |  |  |  |  |  |  |

| Operation: $(PC) \leftarrow (EA)$                                                                                                                          |         |      |  |  |  |  |  |  |  |  |  |

Description: The contents of the effective address (EA) replaces the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

JUMP TO SUBROUTINE (JSR) 280016

|  | 0 |   |   |   | L | 5 | 6 7 |      | 15 |

|--|---|---|---|---|---|---|-----|------|----|

|  | 0 | 0 | 1 | 0 | 1 | 0 | xr  | disp |    |

|  |   |   |   |   |   |   |     |      |    |

- Operation:  $(STK) \leftarrow (PC)$ ,  $(PC) \leftarrow (EA)$

- Description: The contents of PC are stored in the top of the stack. The effective address EA replaces the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

Programming Note: Subroutine jumps utilize stack locations and a series of JSR's without intervening returns (see Return From Subroutine) may cause a stack overflow. Jacquard's System II Operating System provides user services which require some stack locations. It is advisable to limit the depth of subroutine calls within user programs.

# JUMP TO SUBROUTINE INDIRECT (JSR@) 2C00

| 1 | 0 |   |   |   |   | 5 | 6 7 | 811 | 11   | 1 | I. | 15 |

|---|---|---|---|---|---|---|-----|-----|------|---|----|----|

|   | 0 | 0 | 1 | 0 | 1 | 1 | xr  |     | disp |   |    |    |

Operation:  $(STK) \leftarrow (PC) (PC) \leftarrow (EA)$

Description: The contents of PC are stored in the top of the stack. The contents of the effective address (EA) replace the contents of PC. The next instruction is fetched from the location designated by the new contents of PC.

## BRANCH-ON CONDITION (BOC) 100016

| 0 0 0 1 cc disp |  |

|-----------------|--|

Operation:

$(PC) \leftarrow (PC) + disp (sign extended from bit 8 through bit 0)$

Description:

There are 16 possible condition codes (cc). These are listed in Table 2-8. If the condition for branching designated by cc is true, the value of disp (sign extended from bit 8 through bit  $\emptyset$ ) is added to the contents of PC, and the sum is stored in PC. The initial contents of PC are lost. Program control is transferred to the location specified by the new contents of PC.

## NOTES

- PC is always incremented by 1 immediately following the fetching of an instruction, so the contents of PC during execution of an instruction is 1 greater than the address of that instruction. This must be considered during execution of the BOC instruction: for example, if the address of the BOC instruction is 100, then 101 is added to the value of disp (sign extended).

- (2) The disp field is a signed 8-bit number, whose sign is extended from bit 8 through bit Ø to form a 16-bit number (including sign). Thus, the range of addressing with a BOC instruction is -127 to +128 relative to the address of the current instruction.

- (3) Alternate mnemonics are offered in the System II assembler for certain commonly used condition codes. The assembler will recognize the BOC operation code along with a condition code value in the operand field. As an alternate the following table lists certain op-codes which imply a condition code; the explicit condition code value must be omitted when using op-codes from this table.

| <u>Equiva</u> | alent                                         | Condition                         |

|---------------|-----------------------------------------------|-----------------------------------|

| BOC           | 1                                             | AC0 = 0                           |

| BOC           | 2                                             | AC0 > 0                           |

| BOC           | 3                                             | AC0 bit 15 = 1                    |

| BOC           | 4                                             | AC0 bit $14 = 1$                  |

| BOC           | 5                                             | AC0 $\neq$ 0                      |

| BOC           | 10                                            | CY/OV = 1<br>(per SELECT<br>flag) |

| BOC           | 11                                            | $AC0 \leq 0$                      |

| BOC           | <b>1</b> 2                                    | I/O busy =true                    |

| BOC           | 13                                            | I/O done=true                     |

|               | BOC<br>BOC<br>BOC<br>BOC<br>BOC<br>BOC<br>BOC | BOC2BOC3BOC4BOC5BOC10BOC11BOC12   |

## Table 2-8. Branch-On-Condition Codes

|                        | · · · · · · · · · · · · · · · · · · · |                      | I                       |

|------------------------|---------------------------------------|----------------------|-------------------------|

| CONDI-<br>TION<br>CODE | CONDITION<br>TESTED                   | ALTERNATE<br>OP-CODE | REMARKS                 |

| 0000                   |                                       |                      | Undefined               |

|                        |                                       |                      |                         |

|                        |                                       |                      |                         |

| 0001                   | (AC0) = 0                             | BZR                  |                         |

| 0010                   | $(AC0) \ge 0$                         | BGE                  |                         |

| 0011                   | Bit 15 of AC0 = 1                     | BB15                 |                         |

| 0100                   | Bit 14 of AC0 = 1                     | BB14                 |                         |

| 0101                   | (AC0) ≠ 0                             | BNZ                  |                         |

| 0110                   |                                       |                      | Undefined               |

|                        |                                       |                      |                         |

| 0111                   |                                       |                      | Undefined               |

|                        |                                       |                      | -                       |

| 1000                   | STACK FULL                            | BOCSFL               |                         |

| 1000                   | FLAG                                  | Doorn                |                         |

| 1001                   | INTERRUPT<br>ENABLE FLAG              | INTEN                |                         |

| 1010                   | CARRY/                                | BCYOF                | Carry if                |

| 1                      | OVERFLOW = 1                          |                      | SEL = 0;<br>overflow if |

|                        |                                       | 4                    | SEL = 1                 |

| 1011                   | $(AC0) \leq 0$                        | BLE                  |                         |

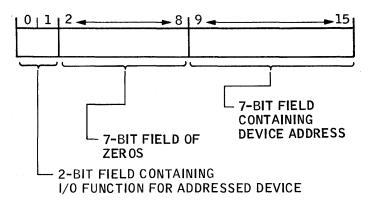

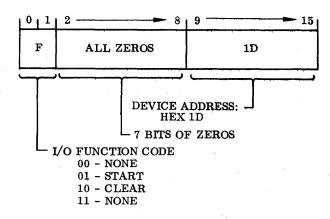

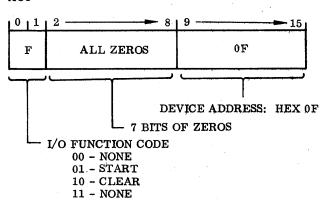

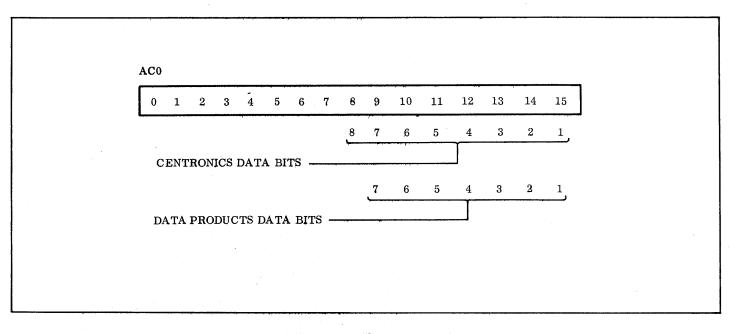

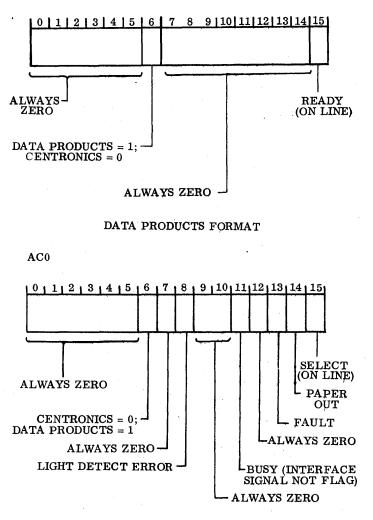

| 1100                   | I/O BUSY<br>FLAG = 1                  | BIOBS                |                         |