**METRIC**

# M 83-SERIES MODELS 8/32,8/32C,AND 8/32D PROCESSORS USER MANUAL

# PERKIN-ELMER

**Computer Systems Division** 2 Crescent Place Oceanport. N. J. 07757

# PAGE REVISION STATUS SHEET (Sheet 1 of 2)

PUBLICATION NUMBER 29-428

TITLE M83-Series Models 8/32, 8/32C and 8/32D Processors User Manual, PATE May 1978

| PAGE                                           | REV.                            | DATE                                 | PAGE                                                  | REV.                                   | DATE                                         | PAGE                                                  | REV.                                          | DATE                                                 |

|------------------------------------------------|---------------------------------|--------------------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------------|-------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|

| i<br>ii<br>thru<br>v<br>vi<br>vii<br>viii      | R06<br>R01<br>R02<br>R06<br>R01 | 5/78<br>1/76<br>2/77<br>5/78<br>1/76 | 2-40<br>thru<br>2-46<br>2-47<br>2-48<br>thru<br>2-51/ | R02<br>R01                             | 2/77<br>1/76                                 | 5-11<br>5-12<br>5-13<br>5-14<br>5-15<br>5-16<br>5-17  | R06<br>R02<br>R02<br>R06<br>R01<br>R02<br>R01 | 5/78<br>2/77<br>2/77<br>5/78<br>1/76<br>2/77<br>1/76 |

| 1-1<br>thru<br>1-3<br>1-4<br>thru<br>1-6       | R06                             | 5/78<br>2/77                         | 2-52<br>3-1<br>3-2<br>3-3<br>3-4<br>3-5               | R02<br>R01<br>R02<br>R02<br>R06<br>R02 | 2/77<br>1/76<br>2/77<br>2/77<br>5/78<br>2/77 | 5-18<br>5-19<br>5-20<br>5-21<br>5-22<br>5-23<br>5-24  | R02<br>R02<br>R01<br>R02<br>R01<br>R02<br>R06 | 2/77<br>2/77<br>1/76<br>2/77<br>1/76<br>2/77<br>5/78 |

| 1-7<br>1-8<br>1-9<br>thru<br>1-19/<br>1-20     | R01<br>R01                      | 1/76<br>1/76<br>5/78                 | 3-6<br>3-7<br>thru<br>3-24<br>4-1<br>4-2              | R02<br>R05<br>R02<br>R05               | 2/77<br>5/78<br>2/77<br>5/78                 | 5-25<br>5-26<br>5-27<br>thru<br>5-33<br>5-34<br>5-35/ | R02<br>R06<br>R02<br>R06                      | 2/77<br>5/78<br>2/77<br>5/78                         |

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>thru<br>2-7 | R01<br>R01<br>R01               | 1/76<br>2/77<br>1/76<br>1/76         | 4-3<br>4-4<br>4-5<br>4-6<br>thru<br>4-12<br>4-13      | R01<br>R02<br>R06<br>R02<br>R06        | 1/76<br>2/77<br>5/78<br>2/77<br>5/78         | 5-36<br>6-1<br>6-2<br>6-3<br>6-4<br>6-5               | R02<br>R02<br>R02<br>R01<br>R02<br>R02        | 2/77<br>2/77<br>2/77<br>1/76<br>2/77<br>2/77         |

| 2-8<br>2-9<br>thru<br>2-18<br>2-19<br>2-20     | R05<br>R02<br>R06<br>R06        | 5/78<br>2/77<br>5/78<br>5/78         | 4-14<br>4-15<br>4-16<br>4-17<br>thru<br>2-23/<br>4-24 | R02<br>R02<br>R06                      | 2/77<br>2/77<br>5/78<br>2/77                 | 6-6<br>6-7<br>6-8<br>6-9<br>6-10<br>6-11<br>6-12      | R01<br>R04<br>R06<br>R06<br>R06<br>R06        | 1/76<br>5/78<br>5/78<br>5/78<br>5/78<br>5/78         |

| thru<br>2-26<br>2-27<br>2-28                   | R02<br>R06                      | 2/77<br>5/78                         | 5-1<br>5-2<br>5-3                                     | R02<br>R01<br>R01                      | 2/77<br>1/76<br>1/76                         | thru<br>6-16<br>7-1                                   | R02<br>R04                                    | 2/77<br>5/78                                         |

| thru<br>2-33<br>2-34<br>2-35<br>2-36           | R02<br>R06<br>R02               | 2/77<br>5/78<br>2/77                 | 5-4<br>5-5<br>5-6<br>5-7<br>5-8                       | R01<br>R02<br>R01<br>R06<br>R02        | 1/76<br>2/77<br>1/76<br>5/78<br>2/77         | 7-2<br>7-3<br>7-4<br>thru<br>7-15                     | R06<br>R01                                    | 5/78<br>1/76<br>2/77                                 |

| thru<br>2-39                                   | R06                             | 5/78                                 | 5-9<br>5-10                                           | R01<br>R02                             | 1/76<br>2/77                                 | 7-16<br>7-18                                          | R01<br>R01                                    | 1/76<br>1/76                                         |

# PAGE REVISION STATUS SHEET (Sheet 2 of 2)

PUBLICATION NUMBER 29-428

TITLE M83-Series Models 8/32, 8/32C, and 8/32D Processor User Manual REVISION R06 DATE May 1978

| PAGE                                                         | REV.                                   | DATE                                         | PAGE                                     | REV.                                   | DATE                                         | PAGE | REV. | DATE |

|--------------------------------------------------------------|----------------------------------------|----------------------------------------------|------------------------------------------|----------------------------------------|----------------------------------------------|------|------|------|

| 7-19<br>7-20<br>7-21<br>7-22<br>7-23<br>7-24<br>7-25<br>thru | R06<br>R02<br>R02<br>R02<br>R06<br>R02 | 2/77<br>2/77<br>2/77                         | 11-5<br>thru<br>11-10<br>11-11/<br>11-12 | R01<br>R02<br>R06<br>R06               | 1/76<br>2/77<br>5/78                         |      |      |      |

| 7-27/<br>7-28<br>8-1<br>8-2                                  | R01<br>R01<br>R02                      | 2/77                                         | thru<br>A2-4                             | R02                                    | 2/77                                         |      |      |      |

| 8-3<br>8-4<br>8-5<br>8-6<br>8-7/<br>8-8                      | R01<br>R06<br>R06<br>R01               | 1/76<br>5/78<br>5/78<br>1/76                 | thru<br>A3-5/<br>A3-6                    | R02                                    | 2/77<br>2/77                                 |      |      |      |

| 9-1<br>9-2<br>9-3<br>9-4<br>9-5                              | R06<br>R06<br>R01<br>R02<br>R02<br>R06 | 5/78<br>5/78<br>1/76<br>2/77<br>2/77<br>5/78 | A5-2<br>A5-3<br>A5-4<br>A5-5             | R02<br>R06<br>R01<br>R01<br>R02<br>R01 | 2/77<br>5/78<br>1/76<br>1/76<br>2/77<br>1/76 |      |      |      |

| 9-7/<br>9-8<br>10-1<br>10-2<br>10-3<br>10-4                  | R02<br>R06<br>R02<br>R01<br>R02        | 2/77<br>5/78<br>2/77<br>1/76<br>2/77         | A6-8                                     | R01<br>R03<br>R06                      | 1/76<br>1/78<br>5/78                         |      |      |      |

| 10-5<br>10-6<br>10-7<br>10-8<br>10-9<br>10-10                | R02<br>R01<br>R01<br>R02<br>R06<br>R01 | 2/77<br>1/76<br>1/76<br>2/77<br>5/78<br>1/76 | A7-2<br>A7-3<br>A8-1<br>A8-2             | R01<br>R06<br>R01<br>R02<br>R01        | 1/76<br>5/78<br>1/76<br>2/77<br>1/76         |      |      |      |

| 11-1<br>11-2<br>11-3<br>11-4                                 | R06<br>R01<br>R06<br>R06               | 5/78<br>1/76<br>5/78<br>5/78                 |                                          | R01<br>R06<br>R01                      | 1/76<br>5/78<br>1/76                         |      |      |      |

# TABLE OF CONTENTS

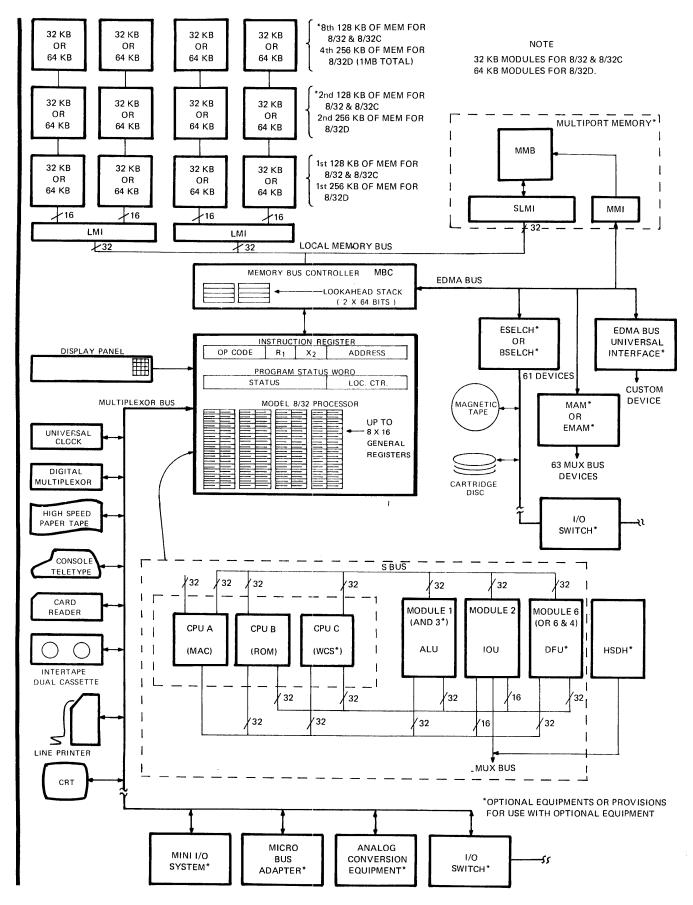

| CHAPTER 1 SYSTEM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                        |

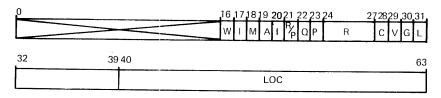

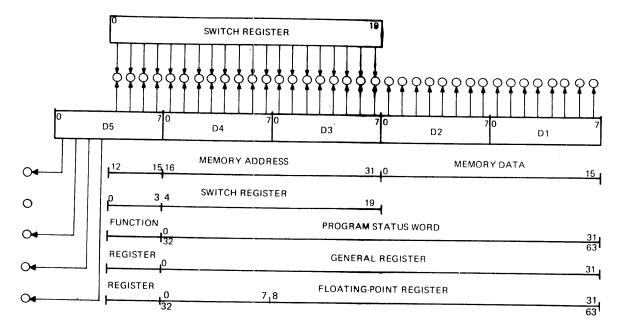

| Program Status Word                                                                                                                                                                                                                                                                                                                                                                              |

| Wait State (W)                                                                                                                                                                                                                                                                                                                                                                                   |

| General Register       1-7         Floating Point Register       1-7         Processor Interrupts       1-7         Reserved Memory Locations       1-7         Processor Operations       1-8                                                                                                                                                                                                   |

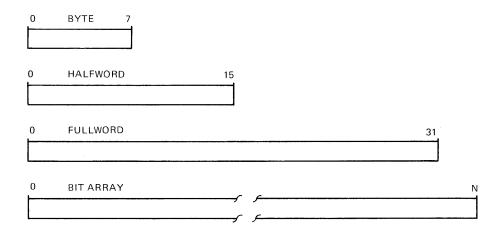

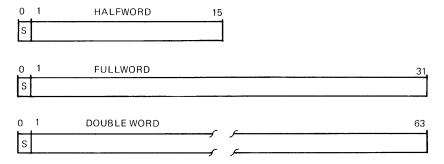

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                     |

| Fixed Point Data       1-8         Floating Point Data       1-8         Logical Data       1-9         DATA ALIGNMENT       1-9                                                                                                                                                                                                                                                                 |

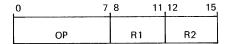

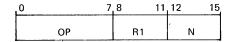

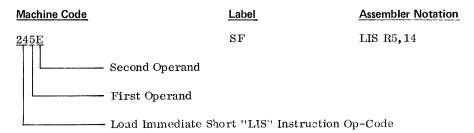

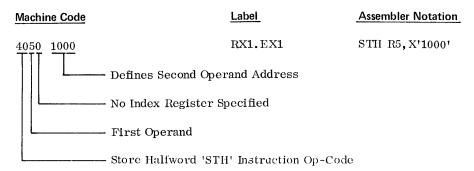

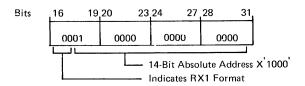

| NSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                               |

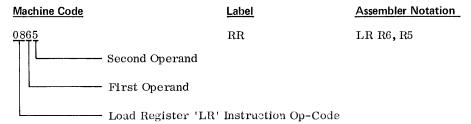

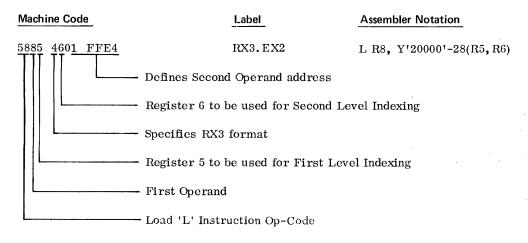

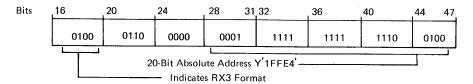

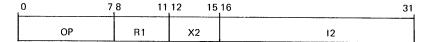

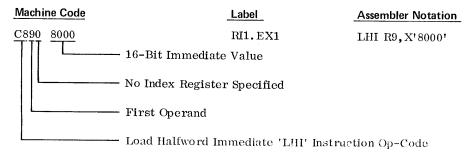

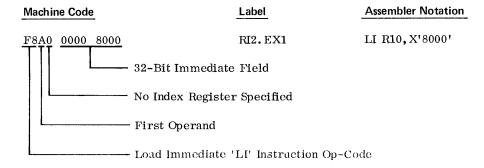

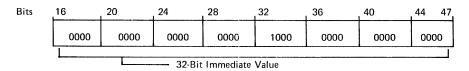

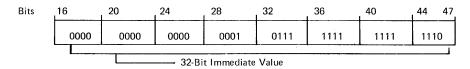

| Branch Instruction Formats 1-11 Programming Examples 1-11 Register to Register (RR) Format 1-11 Short Form (SF) Format 1-11 Register and Indexed Storage One (RX1) Format 1-13 Register and Indexed Storage Two (RX2) Format 1-14 Register and Indexed Storage Three (RX3) Format 1-16 Register and Immediate Storage One (RI1) Format 1-17 Register and Immediate Storage Two (RI2) Format 1-18 |

| CHAPTER 2 LOGICAL OPERATIONS                                                                                                                                                                                                                                                                                                                                                                     |

| DATA FORMATS                                                                                                                                                                                                                                                                                                                                                                                     |

| Boolean Operations       2-2         Translation       2-2         List Processing       2-3                                                                                                                                                                                                                                                                                                     |

| LOGICAL INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                      |

| Load       2-5         Load Register       2-5         Load Immediate       2-5         Load Immediate Short       2-5         Load Complement Short       2-5         Load Halfword       2-6         Load Halfword Immediate       2-6         Load Address       2-7         Load Real Address       2-8         Load Halfword Logical       2-9                                              |

| Load Multiple                               |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-10  |

|---------------------------------------------|-------|-------|-----|-------|-------|-----|-----|-------|-------|-----|-------|-----|-----|-----|-----|-----|-------|

| Load By te                                  |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-11  |

| Load Byte Register                          |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-11  |

| Exchange Halfword Register                  |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-12  |

| Exchange Byte Register Store                | • •   |       | ٠.  | • •   |       |     |     |       |       |     |       |     |     |     |     |     | 2-13  |

| Store                                       |       |       | • • |       |       |     |     |       |       |     | • •   |     |     |     | ٠.  |     | 2-14  |

| Store Multiple                              | • • • |       | ٠.  |       | • • • |     | • • |       |       |     | • •   |     | •   | • • |     |     | 2-15  |

| Store Byte                                  | • • • |       |     |       |       |     |     |       |       | ٠.  |       |     | •   |     |     |     | 2-16  |

| Store Byte Register                         |       | • • • | • • |       | • •   |     | • • |       |       |     |       |     | •   |     |     |     | 2-17  |

| Compare Logical                             |       |       |     |       |       |     |     |       | • • • | • • |       |     | •   | ٠.  |     | ٠.  | 2-17  |

| Compare Logical Register                    |       |       |     |       |       |     |     |       |       | •   | · ·   |     |     |     |     |     | 2-18  |

| Compare Logical Immediate                   |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-18  |

| Compare Logical Halfword                    |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-19  |

| Compare Logical Halfword Immed              | liate |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-19  |

| Compare Logical Byte                        |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-20  |

| AND                                         |       |       | • • |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-21  |

| AND Register                                |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-21  |

| AND Halfword                                |       | • •   | • • |       | • •   |     |     |       |       |     | • •   |     |     |     |     |     | 2-21  |

| AND Halfword                                |       |       | ٠.  |       | • •   |     |     |       |       | • • | • •   |     |     |     |     |     | 2-22  |

| AND Halfword Immediate OR                   |       |       | ٠.  |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-22  |

| OR Register                                 |       | ٠.    |     |       | • •   |     |     | • • • |       | • • |       |     |     |     |     |     | 2-23  |

| OR Immediate                                |       | ٠.    |     |       | •     |     |     |       |       |     |       |     |     |     |     |     | 2-23  |

| OR Halfword                                 |       |       |     |       |       |     |     | • •   |       |     | • • • |     | ٠.  | ٠.  | ٠.  |     | 2-23  |

| OR Halfword Immediate                       |       |       |     |       |       |     |     |       | · · · |     |       |     |     |     |     |     | 2-24  |

| Exclusive OR                                |       |       |     |       |       |     |     |       |       |     |       |     |     | •   |     |     | 2-25  |

| Exclusive OR Register                       |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-25  |

| Exclusive OR Immediate                      |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-25  |

| Exclusive OR Halfword                       |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-26  |

| Exclusive OR Halfword Immediat              |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-26  |

| Test Immediate                              |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-27  |

| Test Halfword Immediate                     |       |       | • • |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-28  |

| Shift Left Logical                          |       | • •   | ٠.  |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-29  |

| Shift Left Logical Short                    |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-29  |

| Shift Right Logical Short                   |       |       | • • |       |       |     |     | • •   |       |     |       | • • |     |     |     |     | 2-30  |

| Shift Left Halfword Logical                 |       | • •   |     |       |       |     |     |       |       |     |       |     | ٠.  |     |     |     | 2-30  |

| Shift Left Halfword Logical Short           |       |       |     |       |       |     |     |       |       |     |       |     | ٠.  |     | • • | • • | 2-31  |

| Shift Right Halfword Logical                |       |       |     |       |       |     |     | • •   |       | • • |       | • • |     |     |     |     | 2-32  |

| Shift Right Halfword Logical Shor           | t     |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-32  |

| Rotate Left Logical                         |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-33  |

| Rotate Right Logical                        |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-34  |

| Test and Set                                |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-35  |

| Test Bit                                    |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-36  |

| Set Bit                                     |       |       | • • |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-37  |

| Complement Bit                              |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     |       |

| Reset Bit<br>Cyclic Redundancy Check Modulo | 12    |       |     |       |       |     |     |       |       | • • |       |     | ٠.  |     | ٠.  |     | 2-39  |

| Cyclic Redundancy Check Module              | 16    | ٠.    |     |       |       |     |     | • •   |       | • • |       |     |     | ٠.  |     |     | 2-40  |

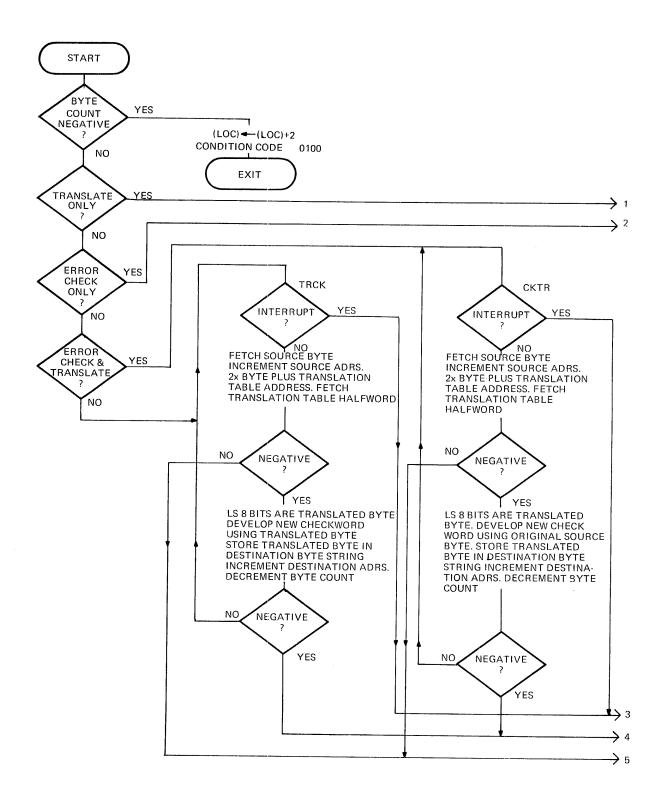

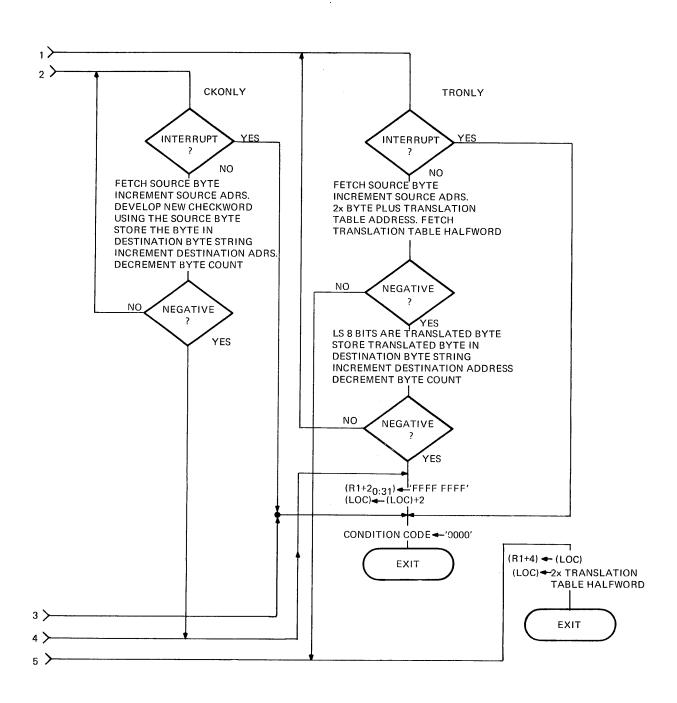

| Translate                                   |       | · ·   |     | · · · |       |     |     | • •   |       | • • |       | ٠.  | • • | • • |     |     | 2-40  |

| Add to Top of List                          |       |       |     |       |       |     |     |       |       |     |       |     | •   | • • |     | ٠.  | 2-45  |

| Add to Bottom of List                       |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-45  |

| Remove from Top of List                     |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-46  |

| Remove from Bottom of List                  |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 2-46  |

|                                             |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     |       |

| CHAPTED 2 DD ANGERS                         |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     |       |

| CHAPTER 3 BRANCHING                         |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     | ٠.  | . 3-1 |

| OPERATIONS                                  |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     |       |

| OLEMATIONS                                  | • • • |       |     |       |       |     |     | • •   |       | • • |       |     | ٠.  |     |     | ٠.  | . 3-1 |

| Decision Making                             |       |       |     |       |       |     |     |       | _     |     |       |     |     |     |     |     | 3.1   |

| Subroutine Linkage                          |       |       |     |       |       |     |     |       |       |     |       |     |     |     |     |     | 3-1   |

| <b>5</b>                                    |       |       |     | •     | •     | - • | • • |       |       |     | • • • |     |     | • • |     |     |       |

| BRANCH INSTRUCTION FORMATS               | 3-1         |

|------------------------------------------|-------------|

| BRANCH INSTRUCTIONS                      |             |

| Branch on True Condition                 | 3-3         |

| Branch on True Condition Register        | 3-3         |

| Branch on True Condition Backward Short  | 3.3         |

| Branch on True Condition Forward Short   | 3-3         |

| Branch on False Condition                | 3-4         |

| Branch on False Condition Register       | 3-4         |

| Branch on False Condition Backward Short | 3-4         |

| Branch on False Condition Forward Short  | 3-4         |

| Branch and Link                          | 3-5         |

| Branch on Index Low or Equal             | 3-5         |

| Branch on Index High                     | 3-0<br>/2-8 |

|                                          | 3-0         |

| CHAPTER 4 FIXED POINT ARITHMETIC         | 4 1         |

|                                          |             |

| DATA FORMATS                             | 4-1         |

| FIXED POINT NUMBER RANGE                 | 4.1         |

| OPERATIONS                               | 4-7         |

| CONDITION CODE                           | 4-7         |

| FIXED POINT INSTRUCTION FORMATS          | 4-3         |

| FIXED POINT INSTRUCTIONS                 | 4-3         |

|                                          |             |

| Add                                      | 4-4         |

| Add Immediate                            | 4-4         |

| Add Immediate                            | 4-4         |

| Add Immediate Short                      | 4-4         |

| Add Halfword Immediate                   | 4-5         |

| Add to Memory                            | 4-3         |

| Add Halfword to Memory                   | 4-7         |

| Subtract                                 | 4-8         |

| Subtract Register                        | 4-8         |

| Subtract Immediate                       | 4-8         |

| Subtract Immediate Short                 | 4-8         |

| Subtract Halfword                        | 4-9         |

| Subtract Halfword Immediate              | 4-9         |

| Compare                                  | -10         |

| Compare Register                         | -10         |

| Compare Immediate                        | r-10        |

| Compare Halfword Immediate               | /-1:        |

| Multiply                                 | -11         |

| Multiply Register                        | 1-12        |

| Multiply Halfword                        | -13         |

| Multiply Halfword Register               | -13         |

| Divide                                   | -14         |

| Divide Register                          | -14         |

| Divide Halfword                          | -16         |

| Divide Halfword Register                 | -16         |

| Shift Left Halfword Arithmetic           |             |

|                                          | -19         |

| Shift Right Arithmetic                   | -20         |

|                                          | -21         |

| CHAPTER 5 FLOATING POINT ARITHMETIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |     |           |     |     |       |     |     |         |     |     |     |       |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------|-----|-----|-------|-----|-----|---------|-----|-----|-----|-------|------------|

| INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     | •         |     |     |       |     |     |         |     |     |     |       | <b>5</b> 1 |

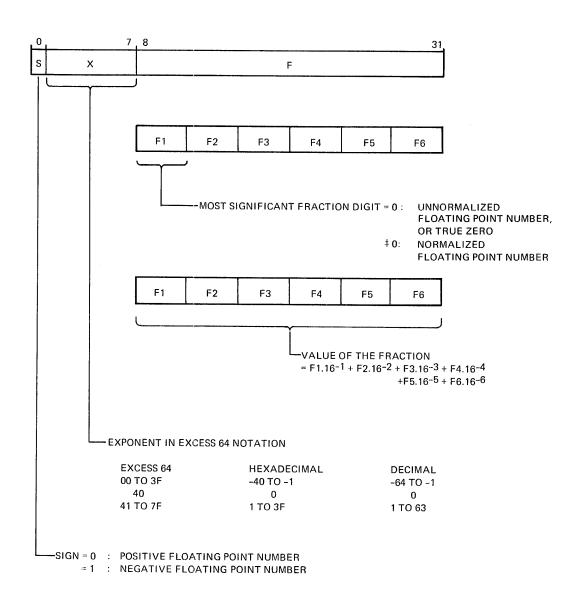

| FLOATING POINT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |     | • •       |     | • • |       |     |     | <br>٠.  |     |     |     |       | 3-1        |

| LOATING TOINT NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |     |           |     | • • |       |     |     | <br>    |     |     |     | • •   | 5-3        |

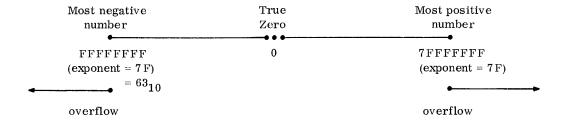

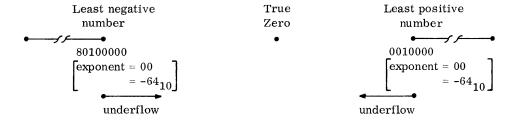

| Floating Point Number Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |     |           |     |     |       |     |     |         |     |     |     |       | 5 /        |

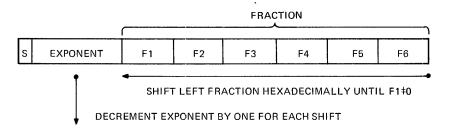

| Normalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |     |           |     |     |       |     |     | <br>    |     |     |     |       | 5.4        |

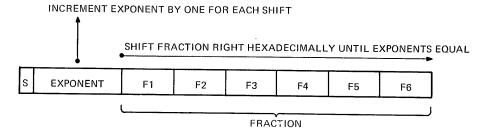

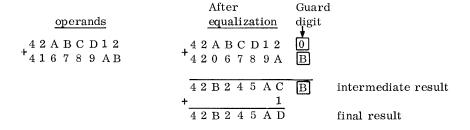

| Equalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     | • •       |     |     |       |     |     | <br>    |     |     |     | • •   | 5-4        |

| True Zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |     |           |     |     |       |     |     | <br>    |     |     |     |       | 5-5        |

| Exponent Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |     |           |     |     |       |     |     | <br>    |     |     | • • |       | 3-3        |

| Exponent Underflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |     |           |     |     |       |     |     | <br>    |     |     |     |       | 5-0        |

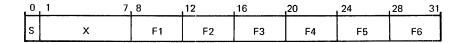

| Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     |           |     |     |       |     | • • | <br>    |     |     |     |       | 5-0        |

| Guard Digit and Rounding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |     |           |     | • • |       |     | • • | <br>• • | • • | • • |     | • •   | 5-0        |

| Conversion from Decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |     |           |     |     |       |     |     | <br>    | • • |     |     | • •   | 5-/        |

| Conversion from Decimal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |     | • •       |     |     |       |     |     | <br>    |     |     |     | • •   | 5-8        |

| CONDITION CODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |     |           |     |     |       |     |     |         |     |     |     |       | - 0        |

| FLOATING POINT INSTRUCTION FORMATS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                 |     | • •       |     |     |       |     | • • | <br>    |     |     |     | • •   | 5-8        |

| FLOATING POINT INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |     | • •       |     |     |       |     | • • | <br>٠.  |     |     |     |       | ე-გ        |

| LOATING TOTAL INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |     | • •       |     |     |       |     | • • | <br>٠.  | • • |     |     |       | 5-8        |

| Load Floating Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |     |           |     |     |       |     |     |         |     |     |     |       | F 10       |

| Load Floating Point Designar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     | • •       |     |     |       |     |     | <br>    |     |     |     | • •   | . 5-10     |

| Load Floating Point Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     | • •       |     |     |       |     |     | <br>    |     |     |     | • •   | . 5-10     |

| Load Floating Point Multiple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 | • • |           |     |     |       |     |     | <br>    |     |     |     |       | . 5-11     |

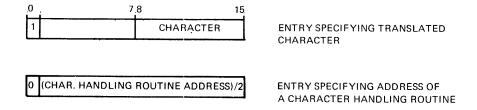

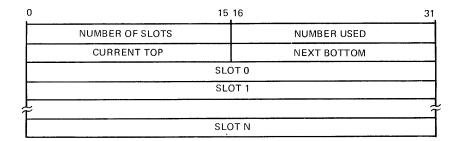

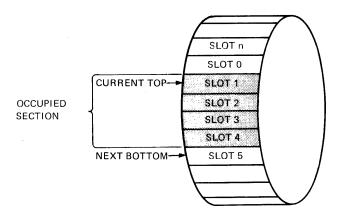

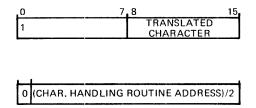

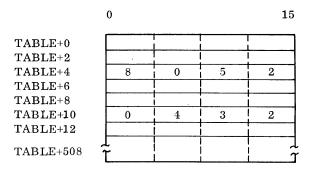

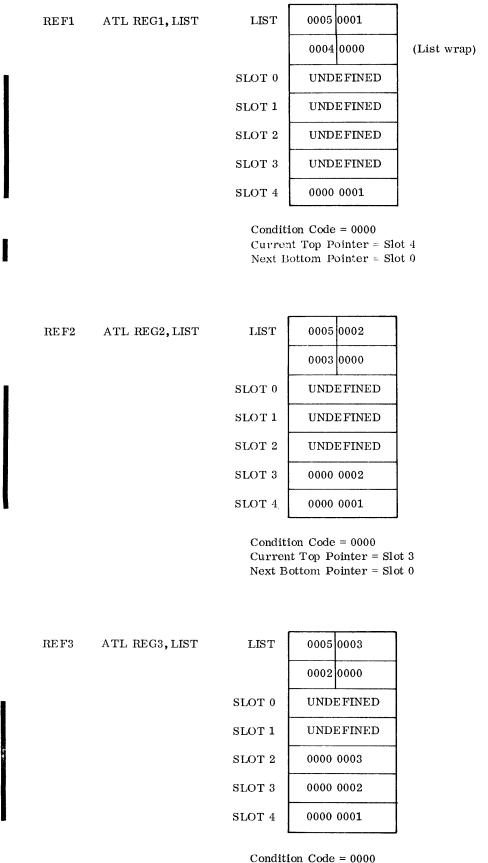

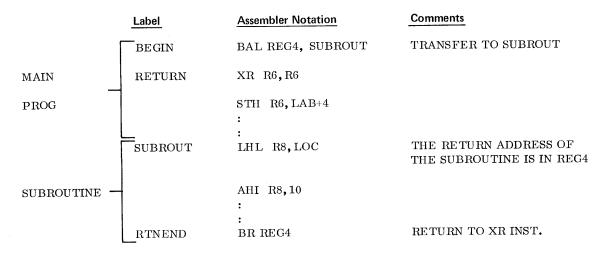

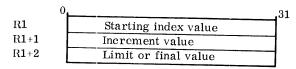

| Store Floating Point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |     |           |     |     |       |     | • • | <br>    | • • |     |     |       | . 5-12     |