SY34-0091-1

IBM Series/1

Common Features

Theory Diagrams

# **Preface**

This manual describes the IBM Series/1 common features, a group of attachment features that communicate directly with the Series/1 processor via the I/O channel. Also described are three unit devices that extend the capabilities of the Series/1 family of processors.

This manual is designed to be used in classrooms for instructing maintenance personnel in the theory of operation of the Series/1 common features. It may also be used as a self-study or reference document in the field.

The presentation level of this manual is oriented to the field replaceable unit (FRU). Diagrams are high-level block-flow that show only the major units within a FRU. Signal lines and power lines between FRUs are described. Voltage levels and pin numbers are given for descriptive purposes only, and must not be used for machine problem analysis. Cable connector information, voltage levels, and pin numbers are listed in the engineering-generated and engineering-change-controlled documentation shipped with each machine.

#### **Related Publications**

IBM Series/1 processors and associated devices are described in separate maintenance publications. These publications are shipped from the plant of origin and accompany the device.

Refer to the *IBM Series/1 Graphic Bibliography*, GA34-0055, for a complete listing and description of all IBM Series/1 publications.

#### Second Edition (November 1979)

This is a major revision of and obsoletes SY34-0091-0. The primary change is the addition of Chapter 11, "Series/1-5250 Information Display System Attachment Feature."

This publication contains information relating the certain feature attachments that are common to the Series/1 family of processors. With the exceptions of Chapters 1, 10, and 11, which were written for this document, this information was previously contained in the IBM 4953 Processor and Processor Features Theory Diagrams manual and the IBM 4955 Processor and Processor Features Theory Diagrams manual, SY34-0042 and SY34-0041, respectively.

Use this publication only for the purpose stated in the Preface.

Changes are periodically made to the information herein; any such changes will be reported in subsequent revisions or Technical Newsletters.

It is possible that this material may contain reference to, or information about, IBM products (machines and programs), programming, or services that are not announced in your country. Such references or information must not be construed to mean that IBM intends to announce such IBM products, programming, or services in your country.

Publications are not stocked at the address given below. Requests for copies of IBM publications should be made to your IBM representative or the IBM branch office serving your locality.

This publication could contain technical inaccuracies or typographical errors. A form for readers' comments is provided at the back of this publication. If the form has been removed, address your comments to IBM Corporation, Systems Publications, Department 27T, P.O. Box 1328, Boca Raton, Florida 33432. IBM may use and distribute any of the information you supply in any way it believes appropriate without incurring any obligation whatever. You may, of course, continue to use the information you supply.

© Copyright International Business Machines Corporation 1979

|  |   |    | • | • |

|--|---|----|---|---|

|  |   |    |   |   |

|  |   | *. |   |   |

|  |   |    |   |   |

|  |   |    |   |   |

|  |   |    |   |   |

|  |   |    |   |   |

|  |   |    |   |   |

|  |   |    |   |   |

|  | , |    |   |   |

|  |   |    |   |   |

# **Contents**

| Chapter 1. Introduction 1-1                                      | I/O Interrupt 5-8                                       |

|------------------------------------------------------------------|---------------------------------------------------------|

| •                                                                | •                                                       |

| Common Features 1-1                                              | Exception Interrupt 5-8                                 |

| Timer Feature 1-1                                                | Device-End Interrupt 5-8                                |

| Teletypewriter Adapter Feature 1-1                               | Attention Interrupt 5-8                                 |

| Integrated Digital Input/Output Non-Isolated Feature 1-1         | Attention and Exception Interrupt 5-8                   |

| Customer Direct Program Control Adapter 1-1                      | Attention and Device-End Interrupt 5-8                  |

| Series/1-System/370 Channel Attachment Feature 1-1               | I/O Interrupt Condition Codes 5-8                       |

| Two-Channel Switch Feature 1-1                                   | Status After Resets 5-8                                 |

| 4959 Input/Output Expansion Unit 1-1                             |                                                         |

| 4993 Model 1 Series/1-System/370 Termination Enclosure 1-1       | Chapter 6. Teletypewriter Adapter Feature 6-1           |

| 4999 Battery Backup Unit 1-1                                     | Description 6-1                                         |

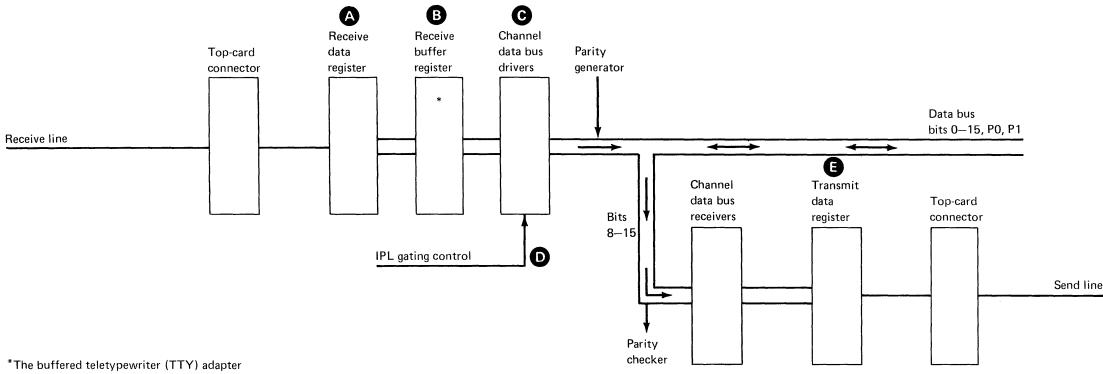

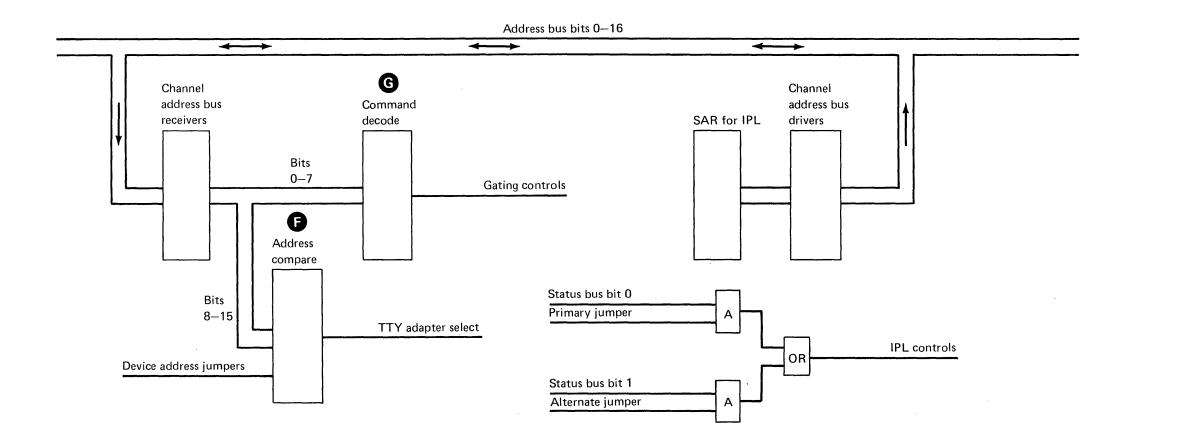

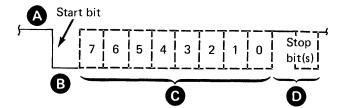

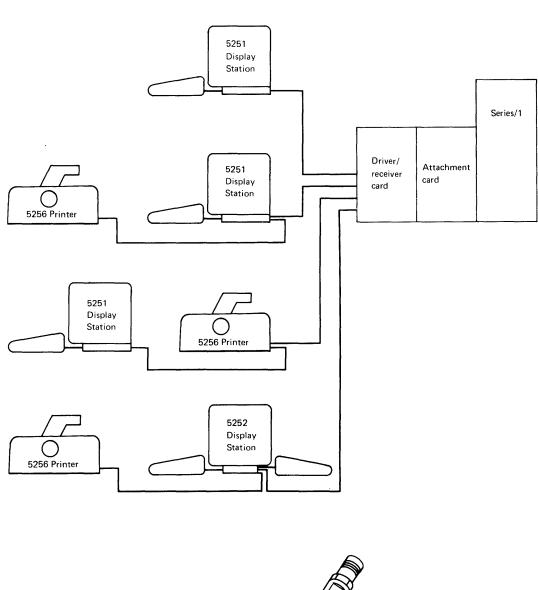

| Series/1-5250 Information Display System Attachment Feature 1-1  | Teletypewriter Adapter Feature Card 6-2                 |

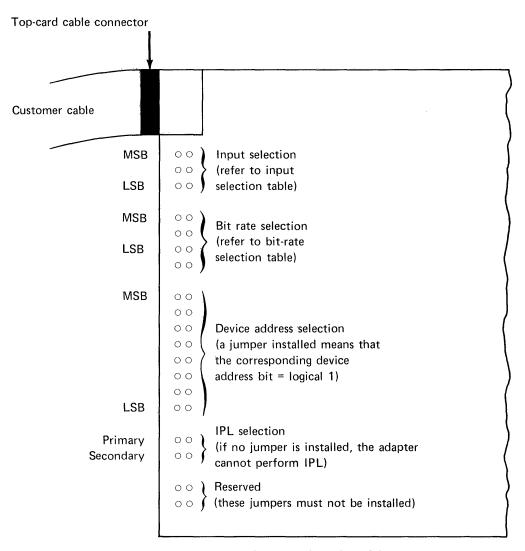

|                                                                  | Adapter Options 6-3                                     |

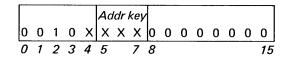

| Processor I/O Channel 1-1                                        | Teletypewriter Adapter Data Flow 6-4                    |

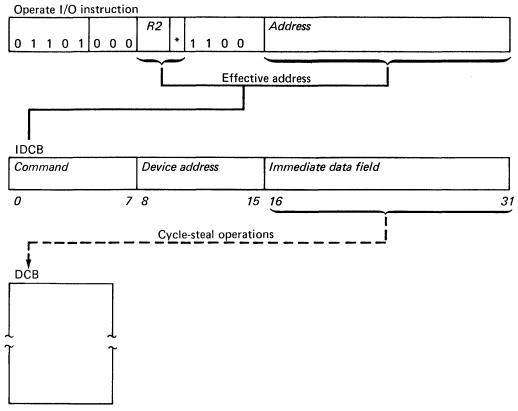

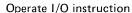

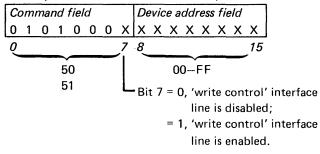

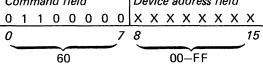

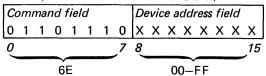

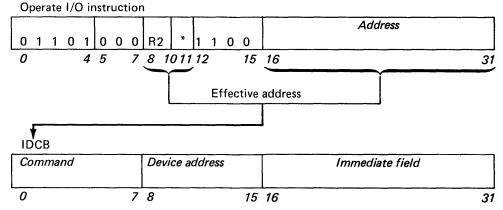

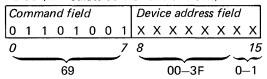

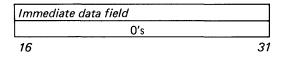

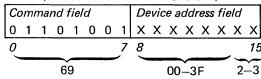

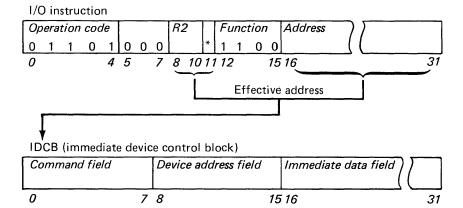

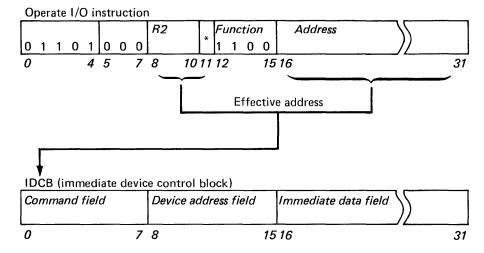

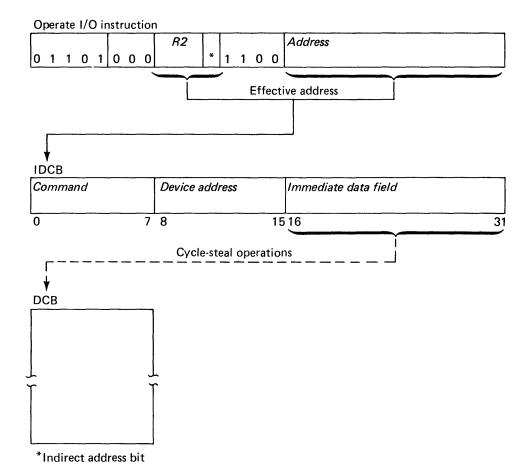

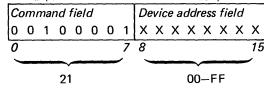

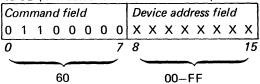

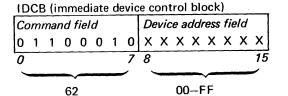

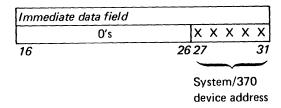

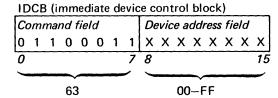

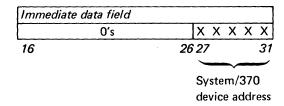

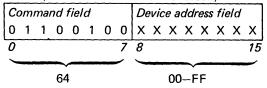

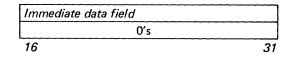

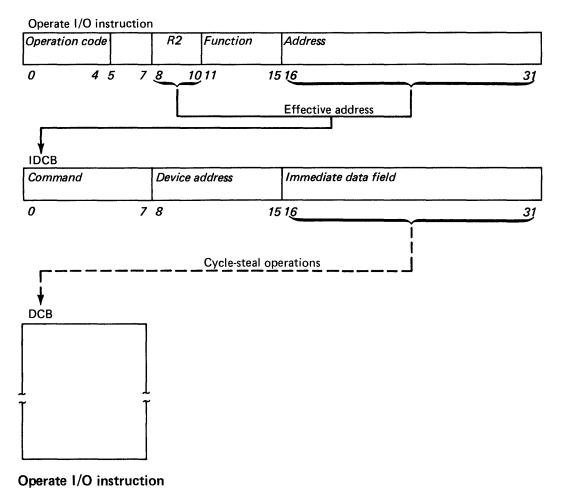

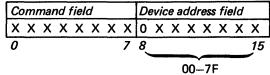

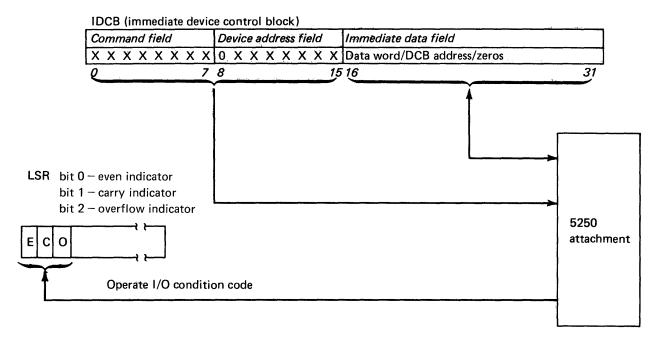

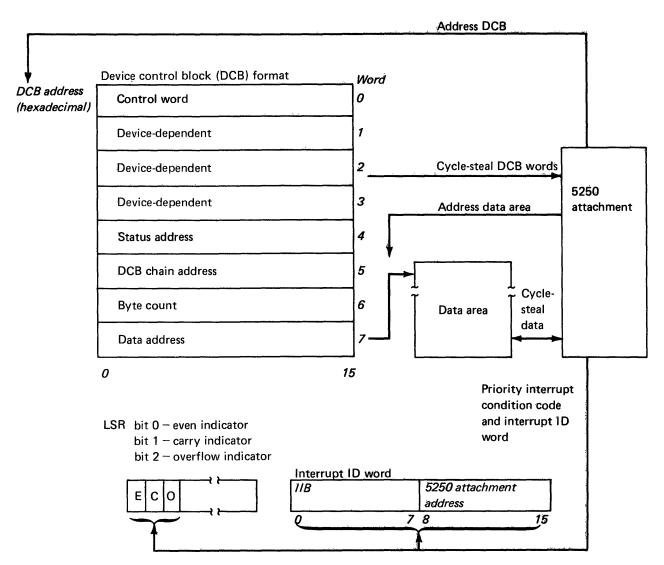

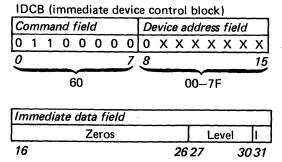

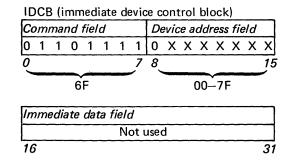

| Operate I/O Instruction 1-2                                      | Data Transmit and Receive Operations 6-5                |

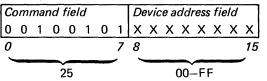

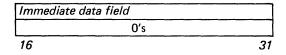

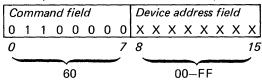

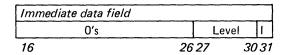

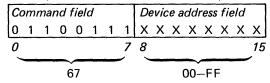

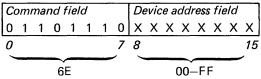

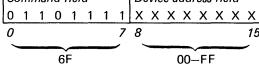

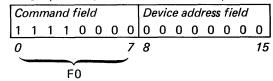

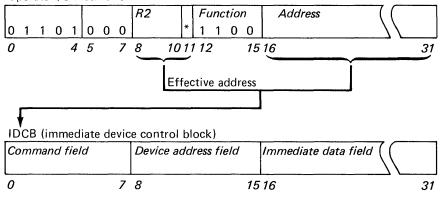

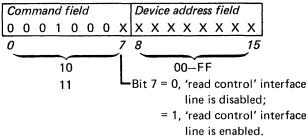

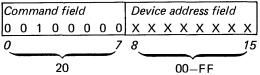

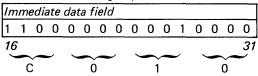

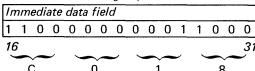

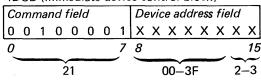

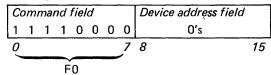

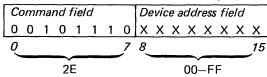

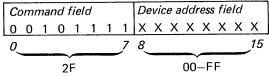

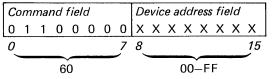

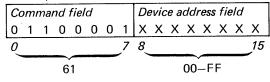

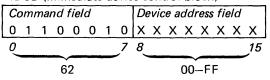

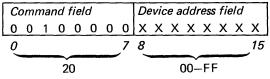

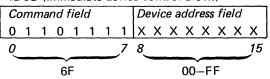

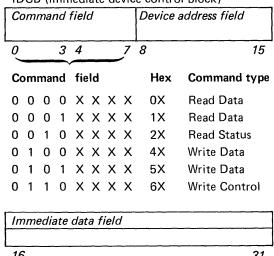

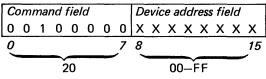

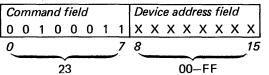

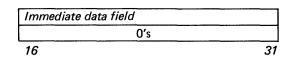

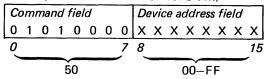

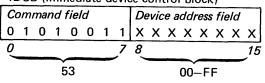

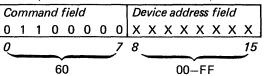

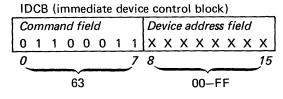

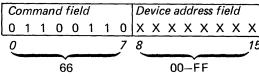

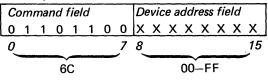

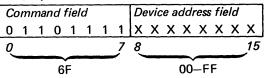

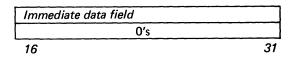

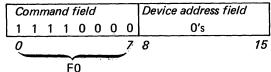

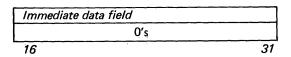

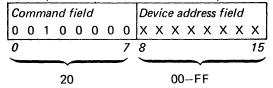

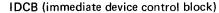

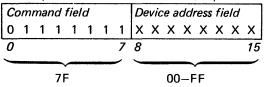

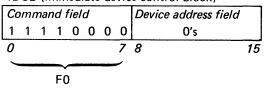

| I/O Commands 1-2                                                 | <u>.</u>                                                |

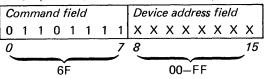

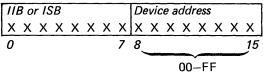

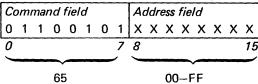

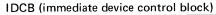

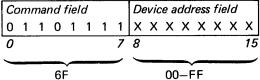

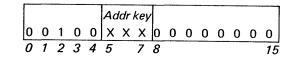

| Device Address 1-2                                               | Transmit Operation 6-5                                  |

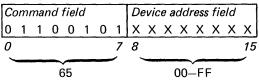

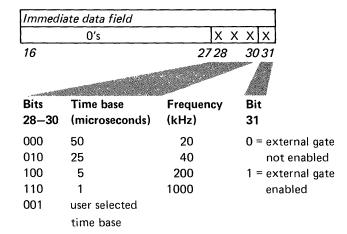

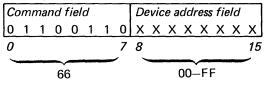

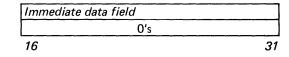

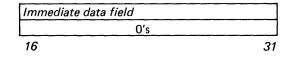

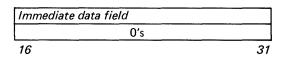

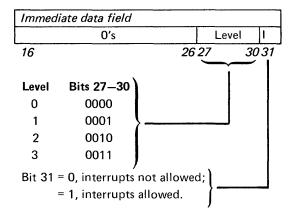

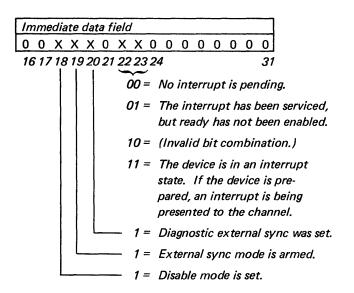

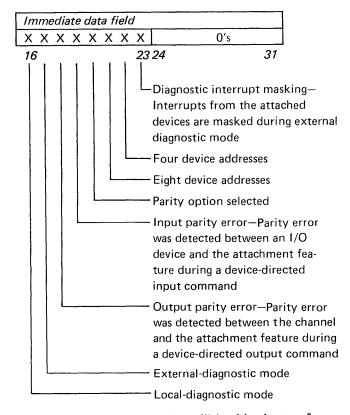

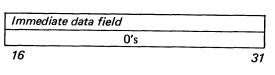

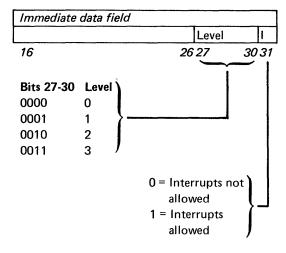

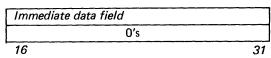

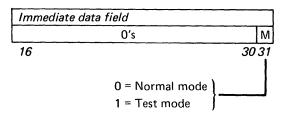

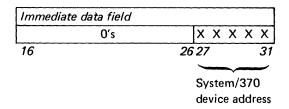

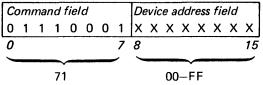

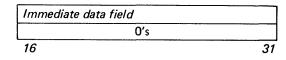

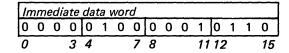

| Immediate Data Field 1-2                                         | Receive Operation 6-6                                   |

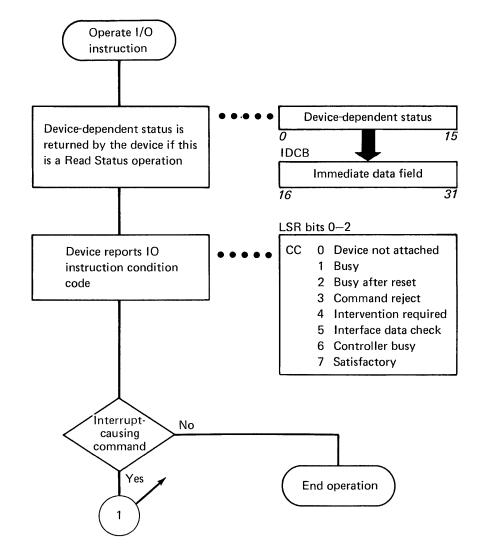

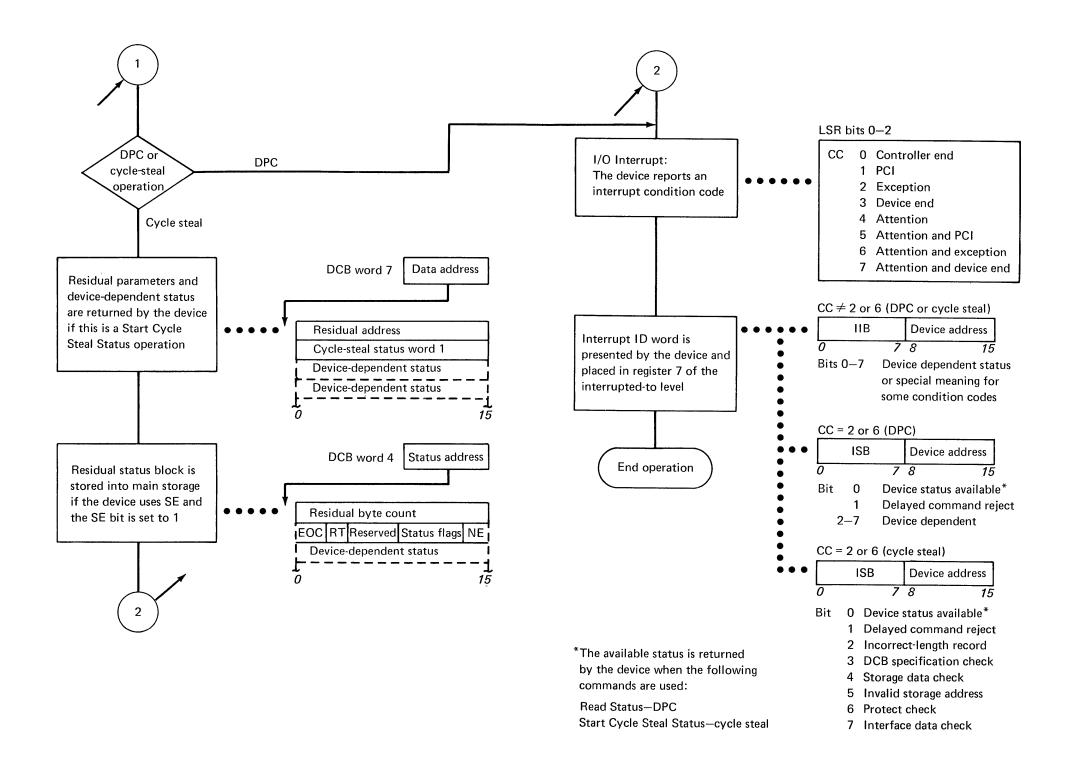

| I/O Instruction Condition Codes 1-3                              | Program Control 6-7                                     |

| Interrupts 1-3                                                   | Operate I/O Instruction 6-7                             |

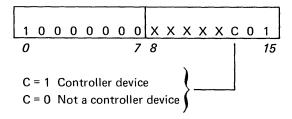

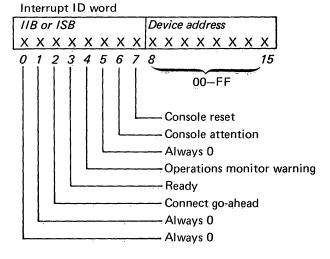

| Interrupt ID Word 1-3                                            | Addressing 6-7                                          |

| I/O Interrupt Condition Codes 1-3                                | Commands 6-7                                            |

| I/O Device Condition Codes and Status Information Flowchart 1-4  | I/O Instruction Condition Codes 6-9                     |

|                                                                  | I/O Interrupt 6-9                                       |

| Chapter 2. Special Maintenance Equipment 2-1                     | I/O Interrupt Condition Codes 6-9                       |

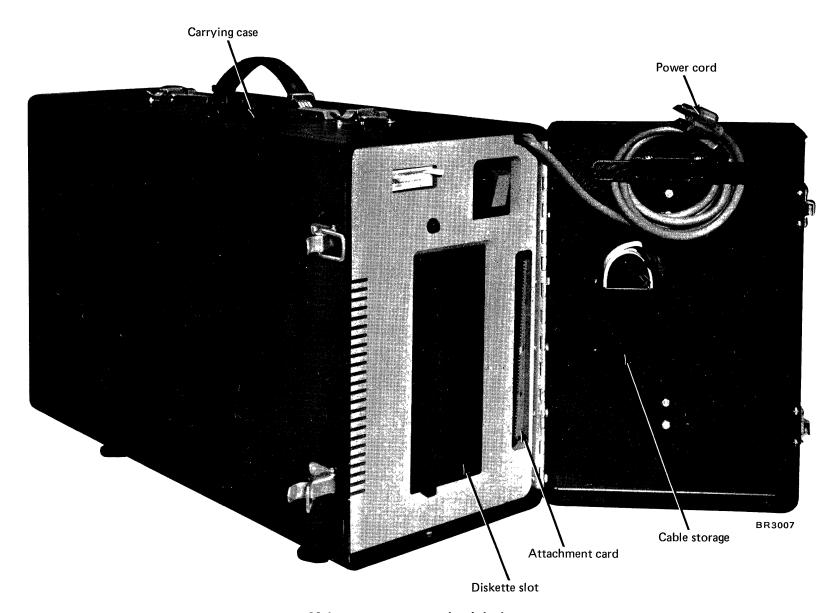

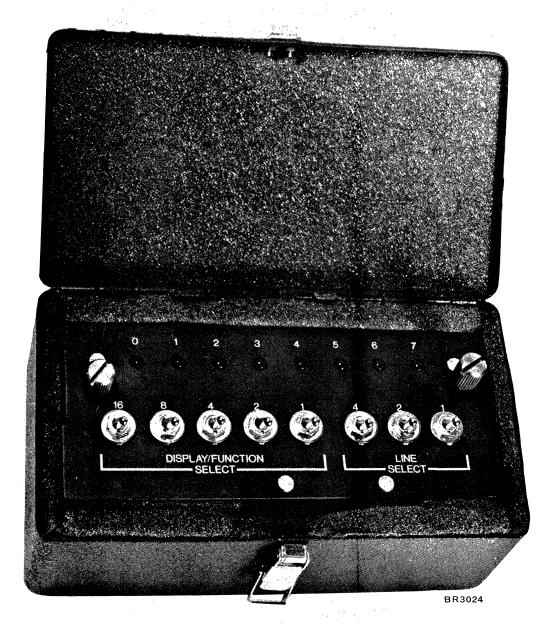

| Maintenance Program Load Device 2-1                              | Initial Program Load (IPL) 6-10                         |

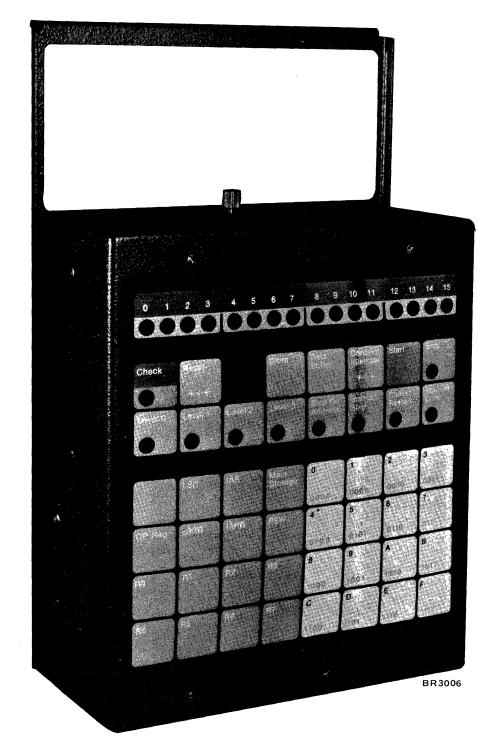

| Maintenance Communications Panel 2-2                             | Status After Resets 6-10                                |

| Maintenance Console 2-3                                          |                                                         |

| Maintenance Console 2-3                                          | Chapter 7. Integrated Digital Input/Output Non-Isolated |

| Classic 2 IDM Carter /4 4050 Invest/Outcome Francisco III-la 2.1 | Feature 7-1                                             |

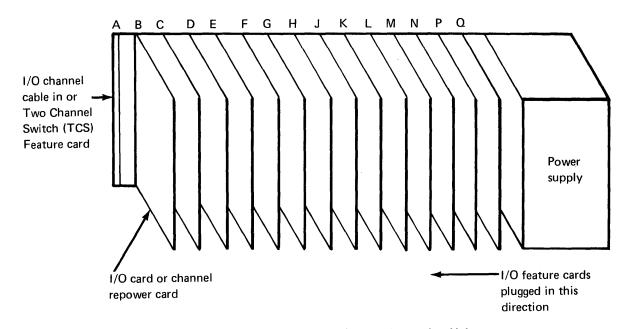

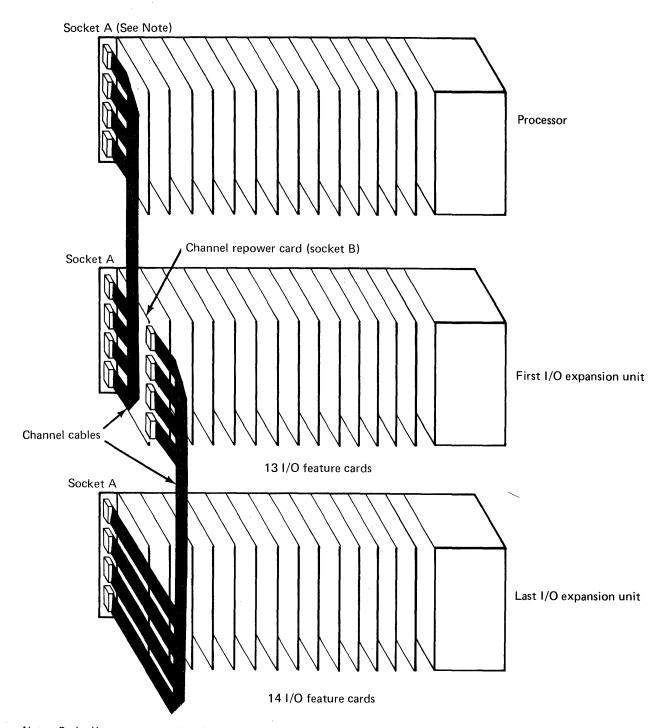

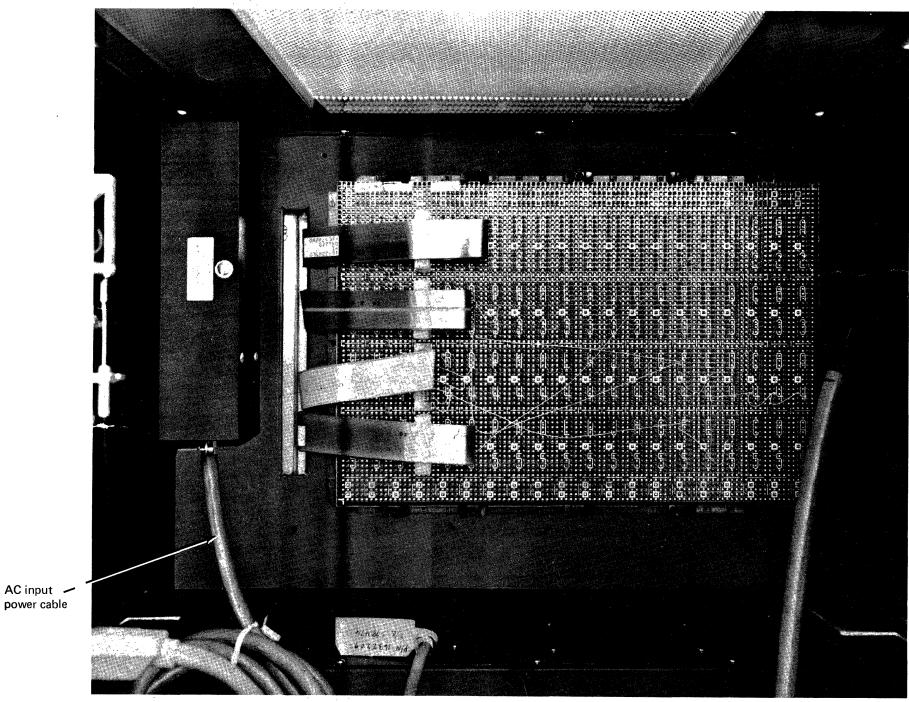

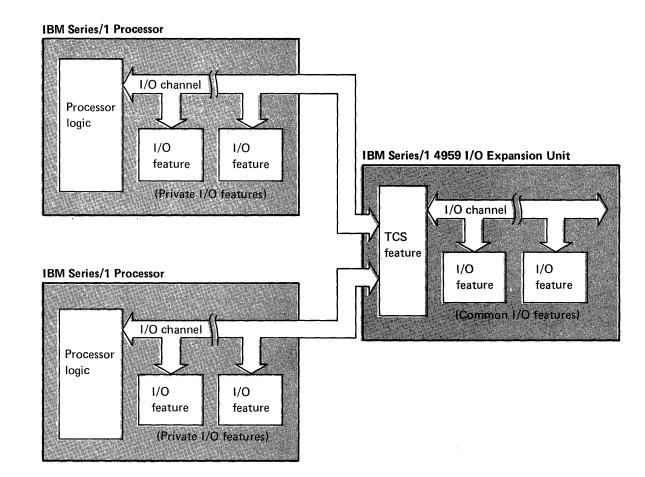

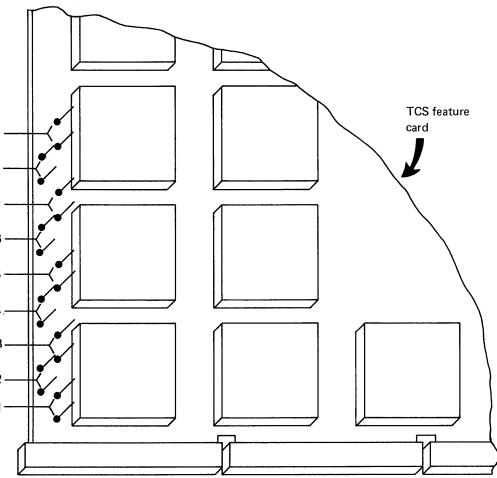

| Chapter 3. IBM Series/1 4959 Input/Output Expansion Unit 3-1     |                                                         |

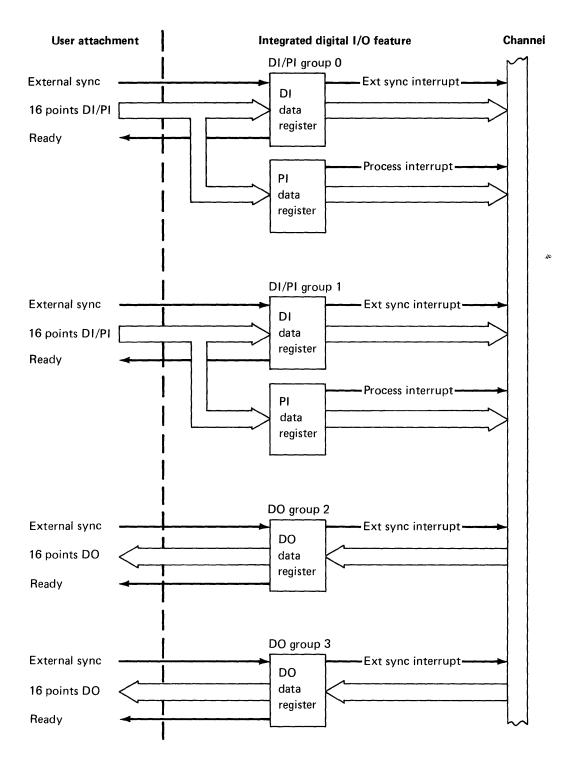

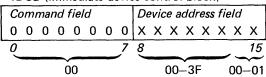

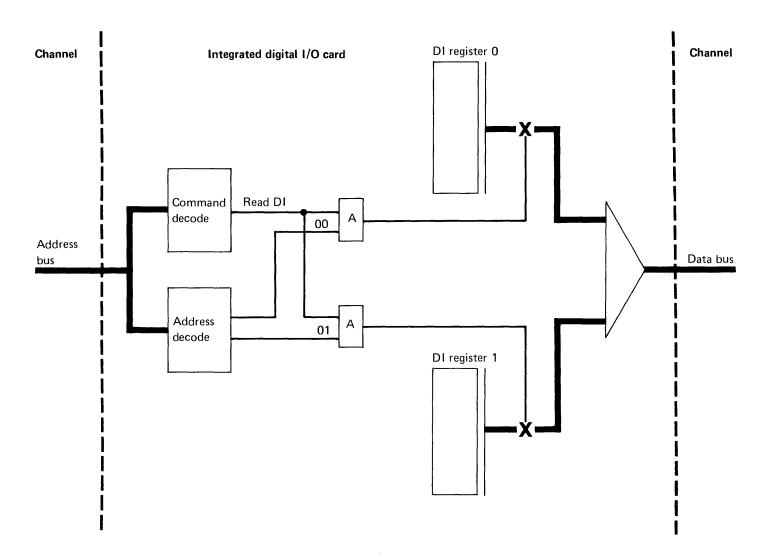

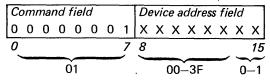

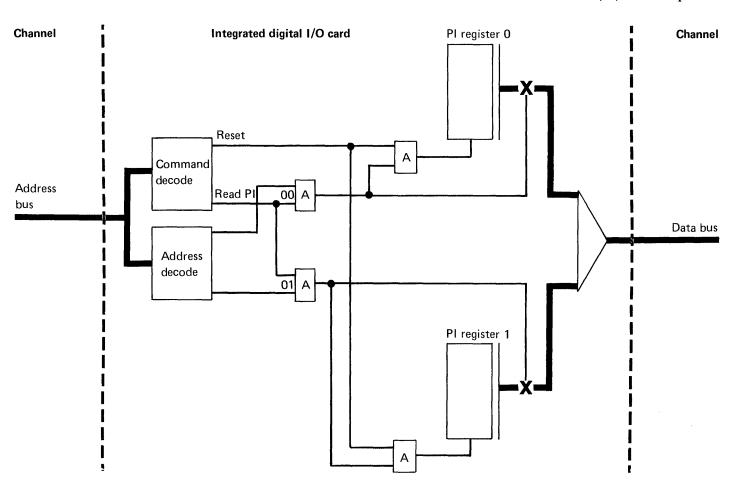

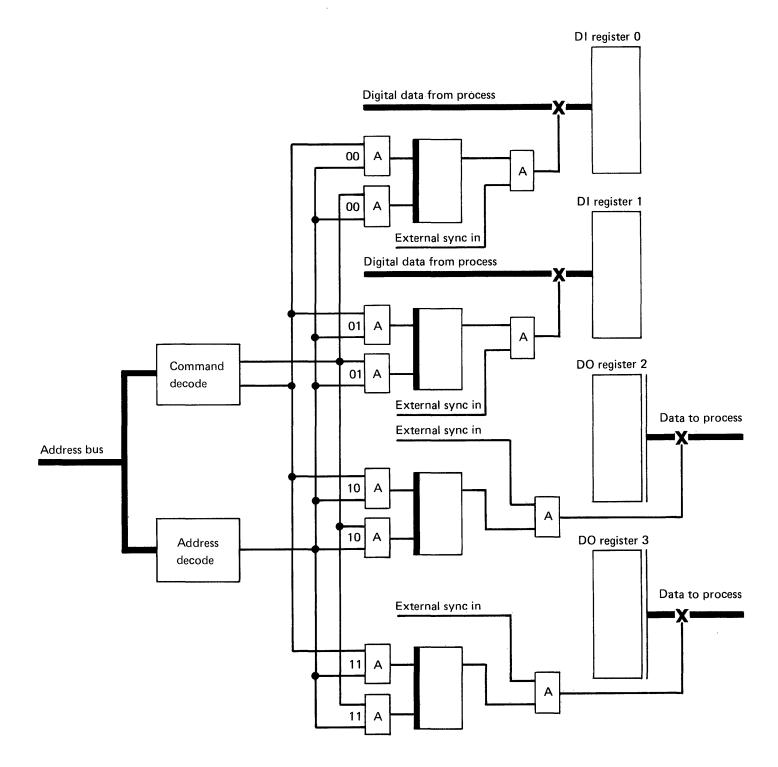

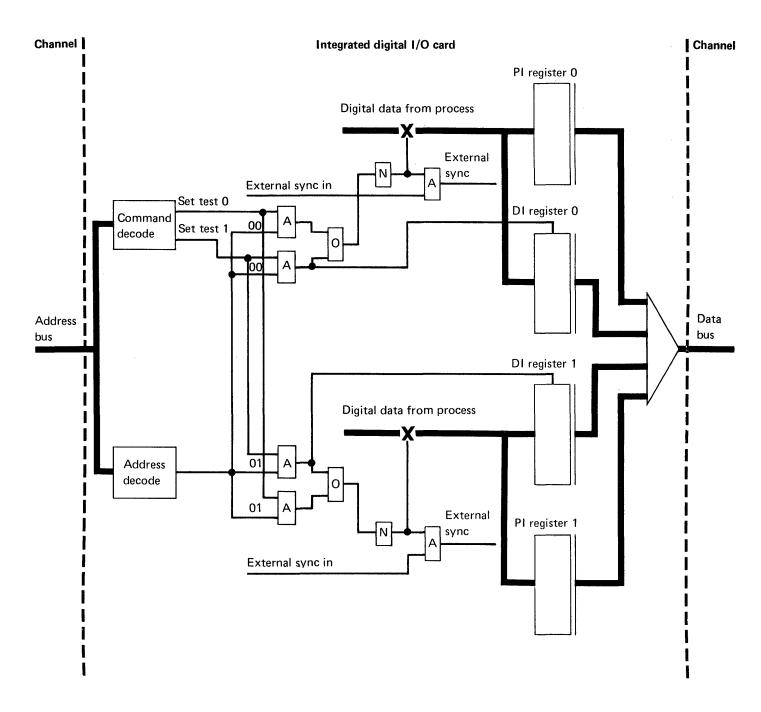

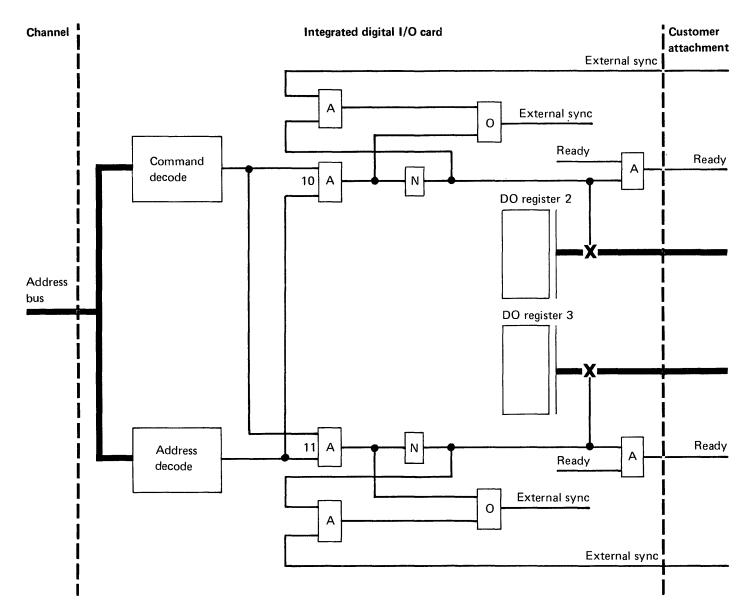

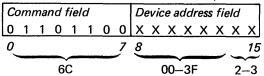

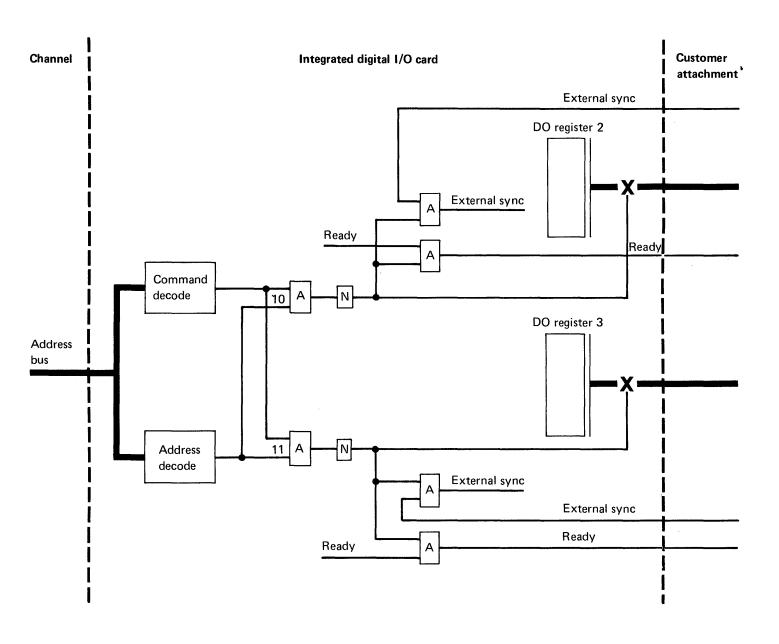

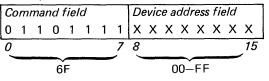

| Description 3-1                                                  | Description 7-1                                         |

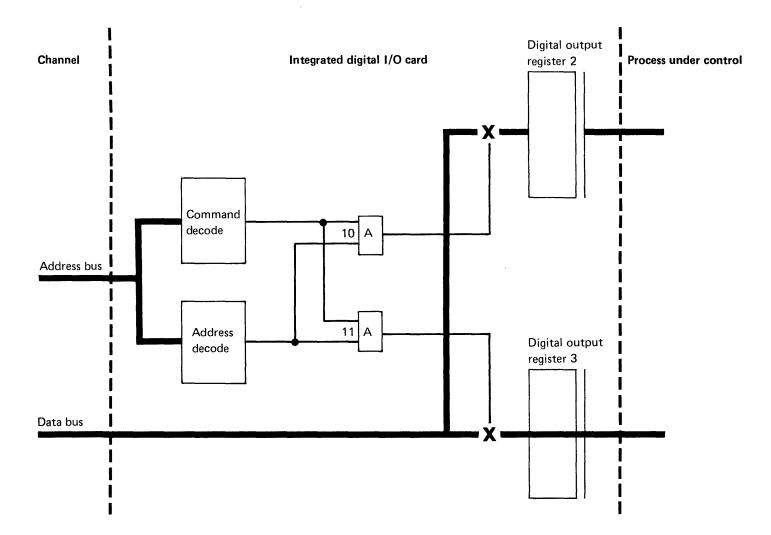

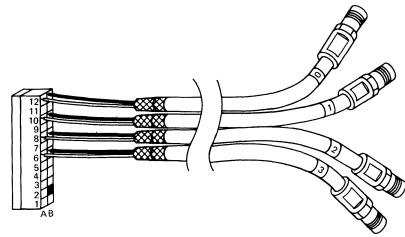

| Cabling 3-2                                                      | Digital Input 7-1                                       |

| Power Supply Voltage/Signal Distribution 3-3                     | Digital Output 7-1                                      |

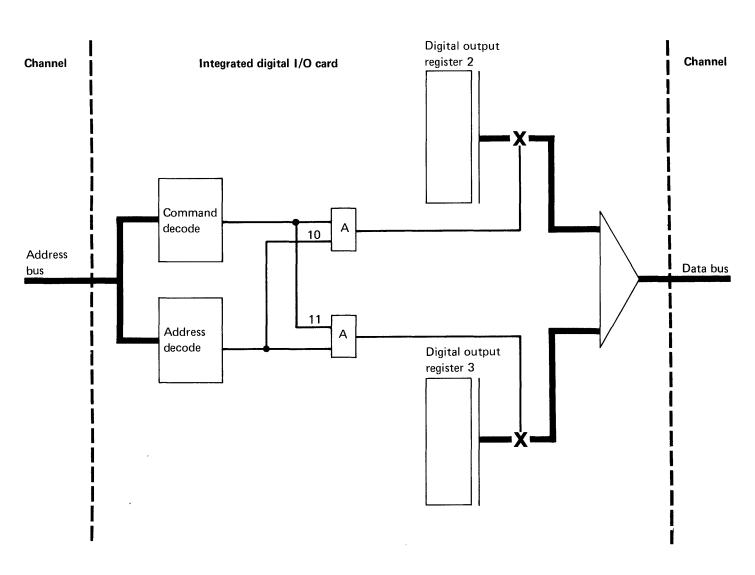

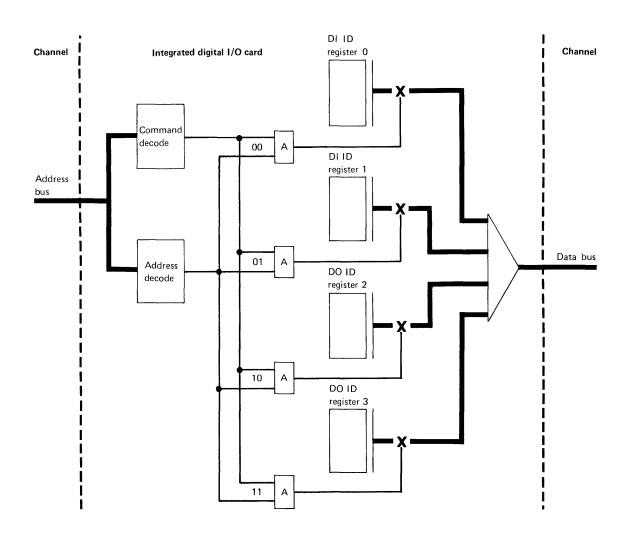

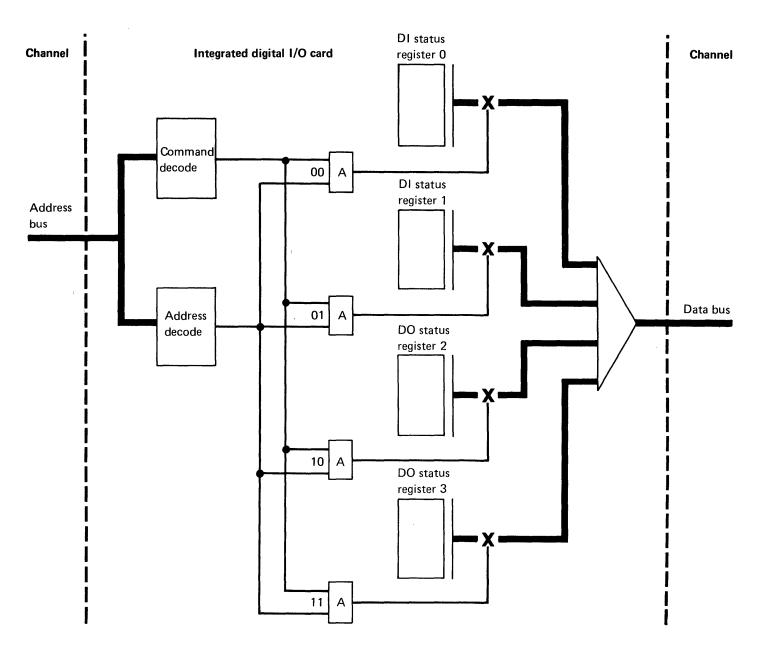

| Power Supply Signals 3-3                                         | Data Flow 7-2                                           |

| Optional Features 3-4                                            | Addressing 7-2                                          |

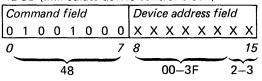

| Communications Indicator Panel 3-4                               | Program Control 7-3                                     |

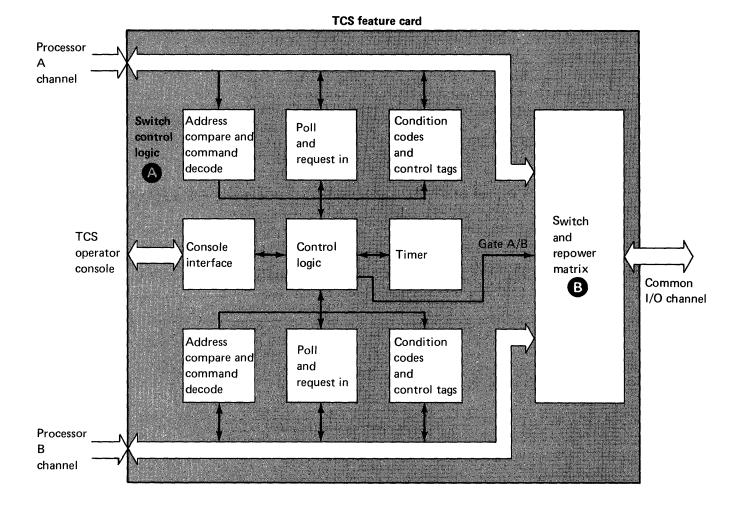

| Two-Channel Switch Feature 3-4                                   | Operate I/O Instruction 7-3                             |

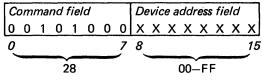

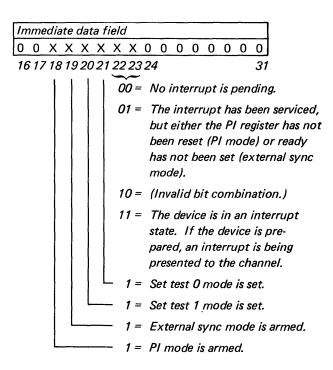

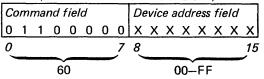

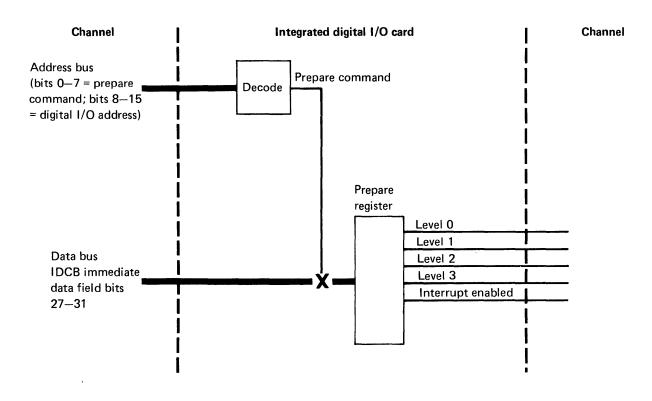

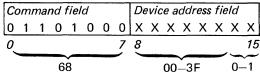

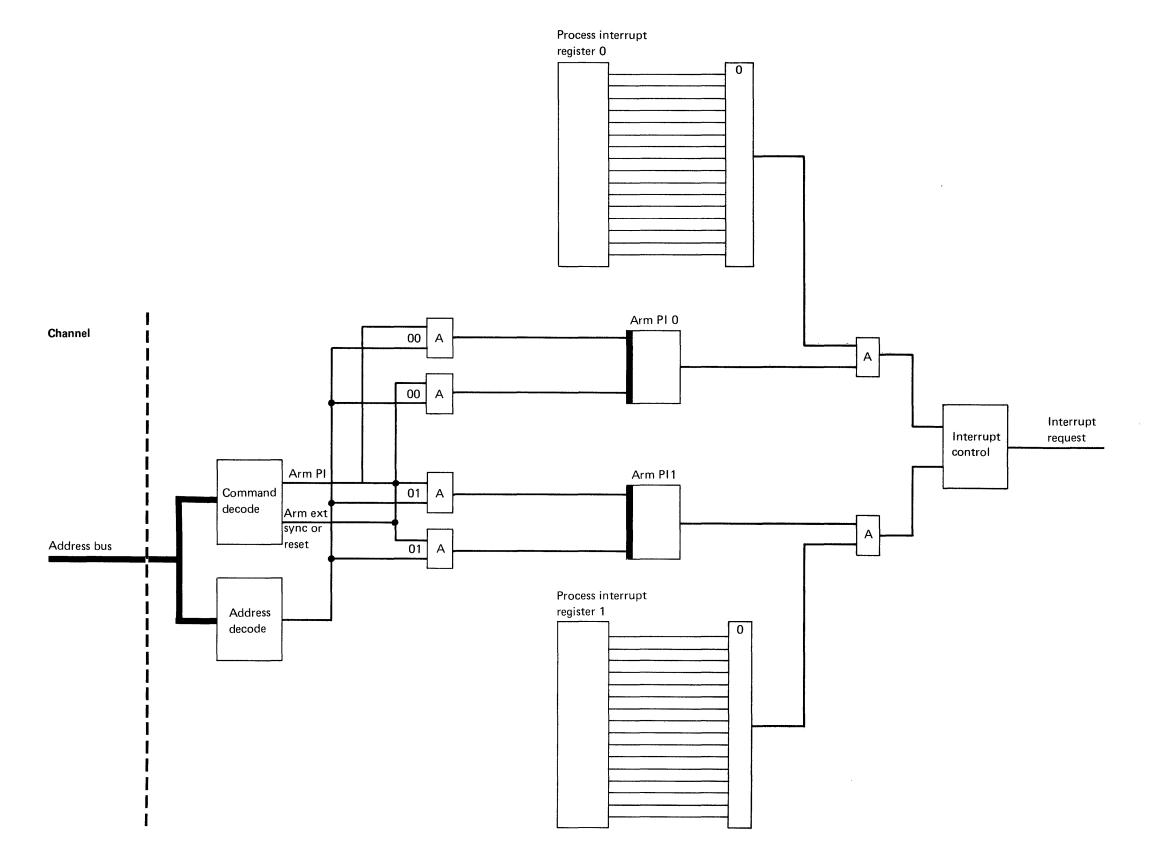

|                                                                  | Commands 7-3                                            |

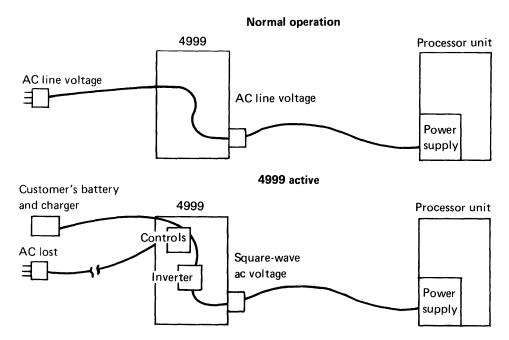

| Chapter 4. IBM Series/1 4999 Battery Backup Unit                 | I/O Instruction Condition Codes 7-12                    |

| Models 1 and 2 4-1                                               | I/O Interrupt 7-13                                      |

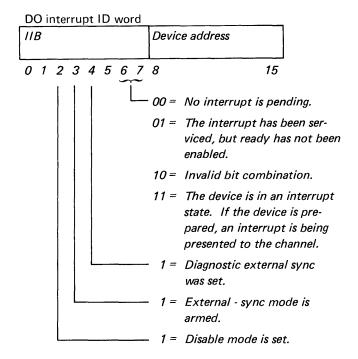

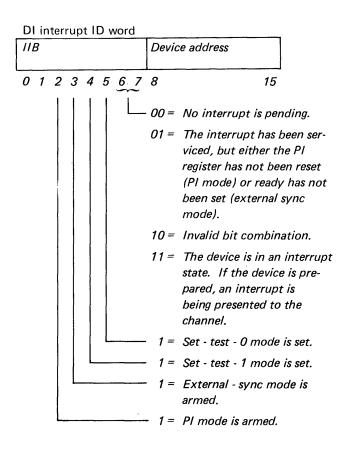

| Description 4-1                                                  | DO Interrupt ID Word 7-13                               |

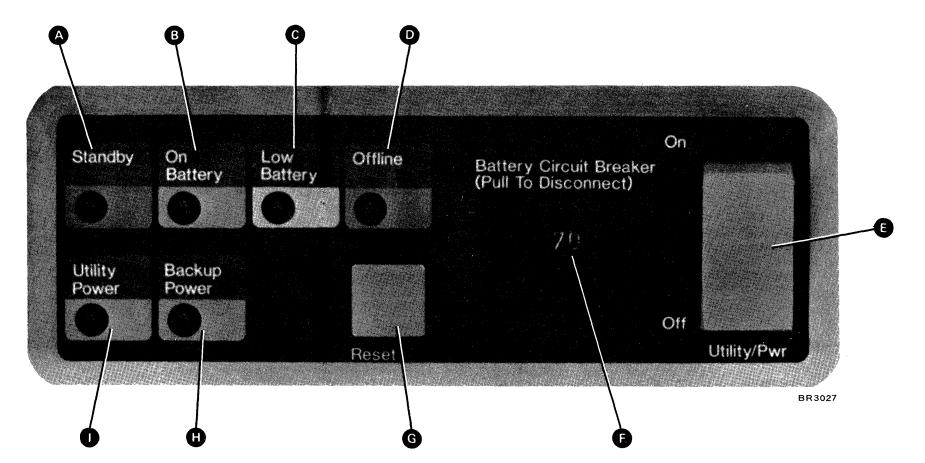

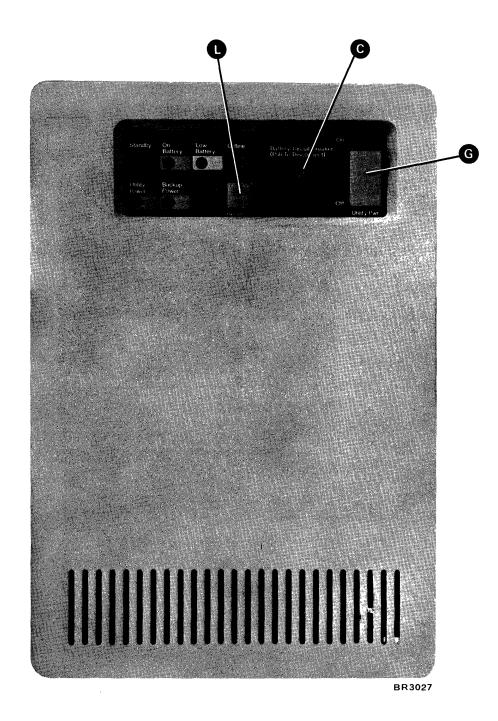

| 4999 Console 4-2                                                 | DI Interrupt ID Word 7-13                               |

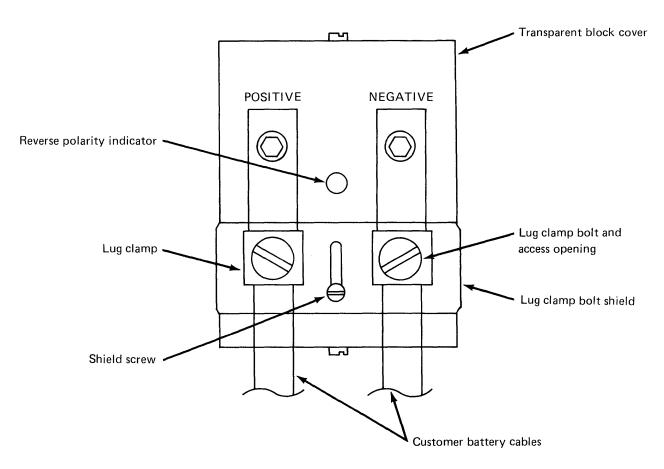

| Battery and Battery Charger 4-3                                  | I/O Interrupt Condition Codes 7-13                      |

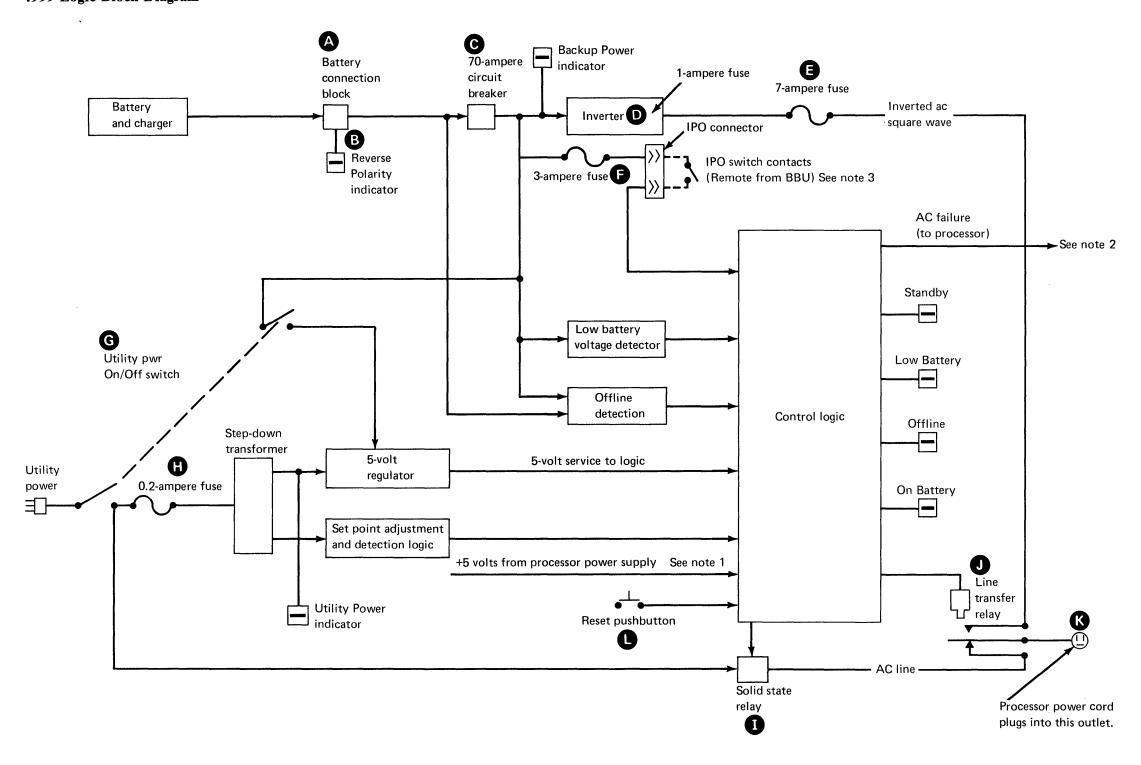

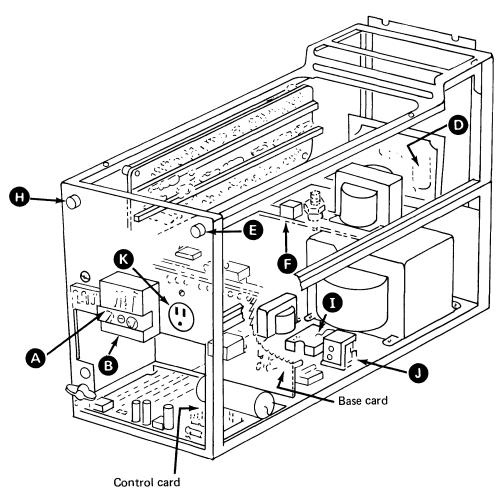

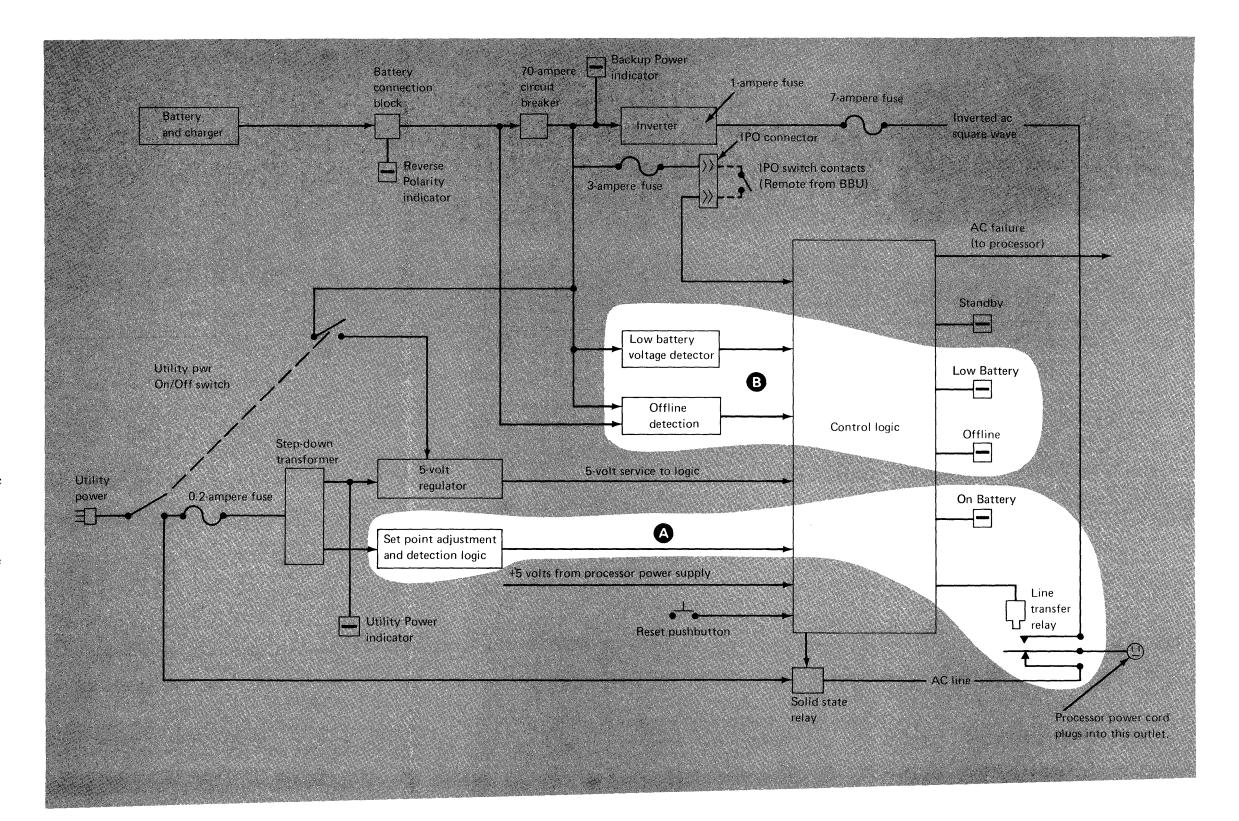

| 4999 Logic Block Diagram 4-4                                     | Status After Resets 7-13                                |

| Logic Block Diagram Locations 4-5                                |                                                         |

| Line Voltage Sensing 4-6                                         | Chapter 8. Customer Direct Program Control Adapter      |

| Battery Voltage Sensing 4-6                                      | Feature 8-1                                             |

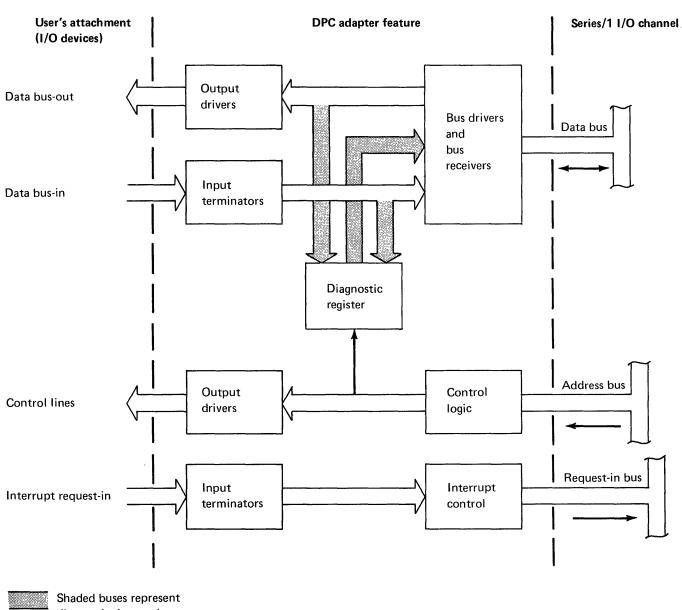

| battery vortage sensing 4-0                                      | Description 8-1                                         |

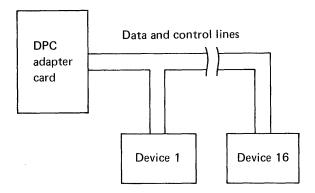

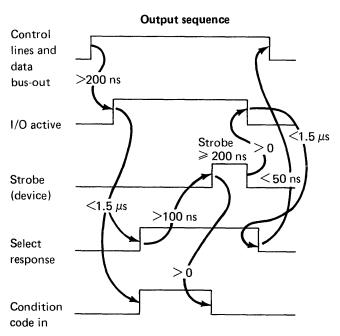

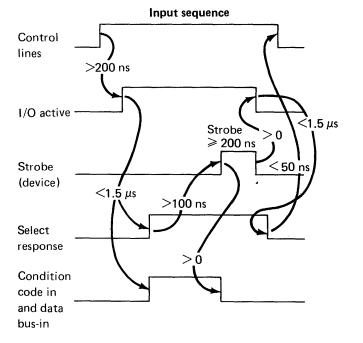

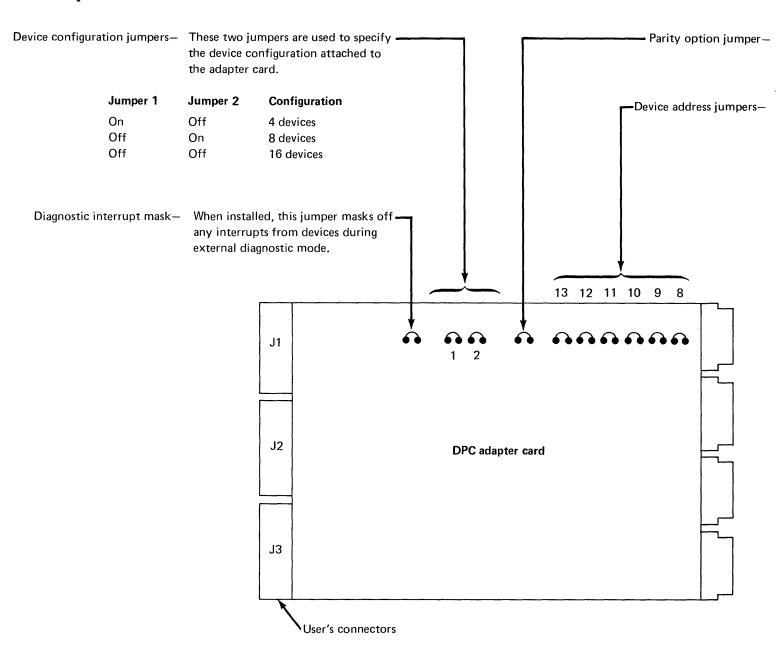

| Chantan 5 Timon Facture 5 1                                      | Data Flow 8-1                                           |

| Chapter 5. Timer Feature 5-1                                     |                                                         |

| Description 5-1                                                  | Data and Control Lines to the Attached Devices 8-2      |

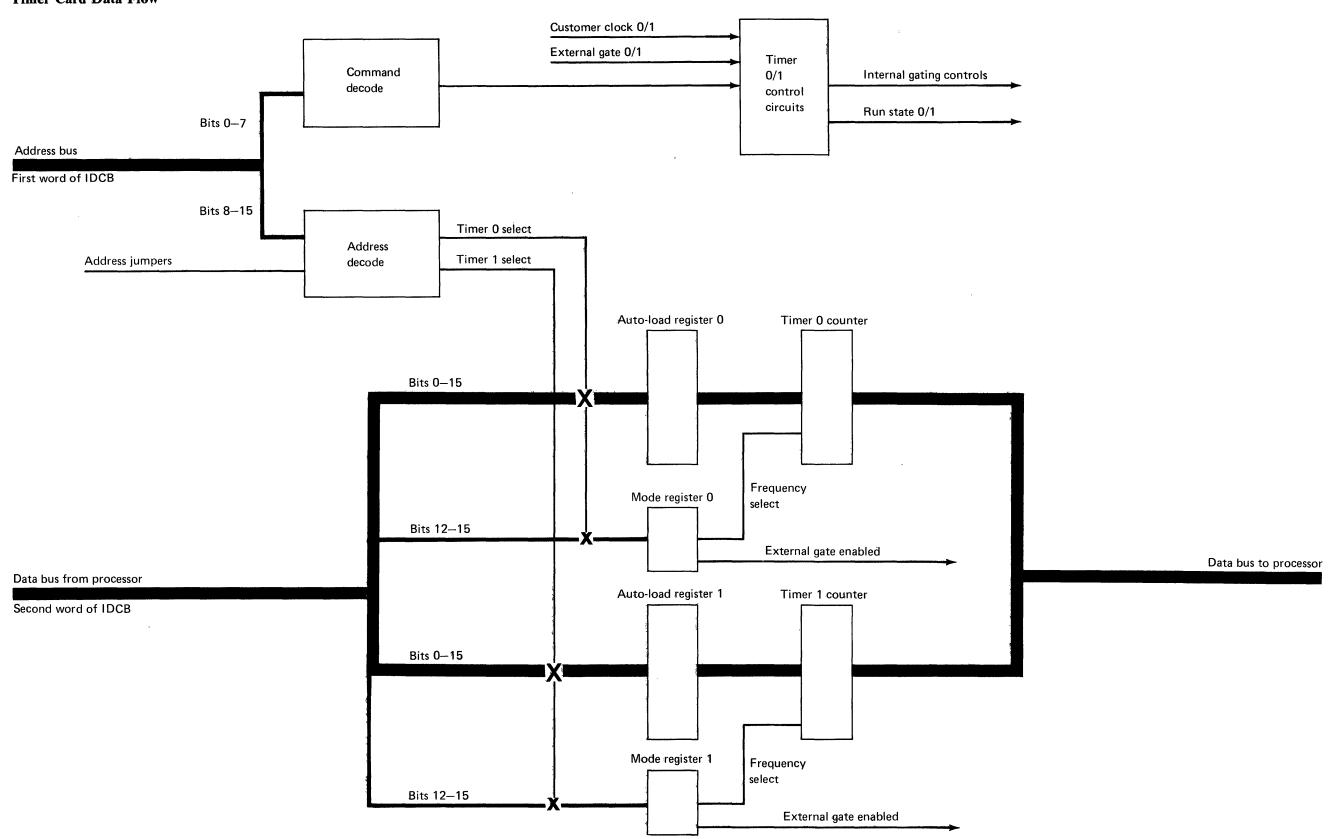

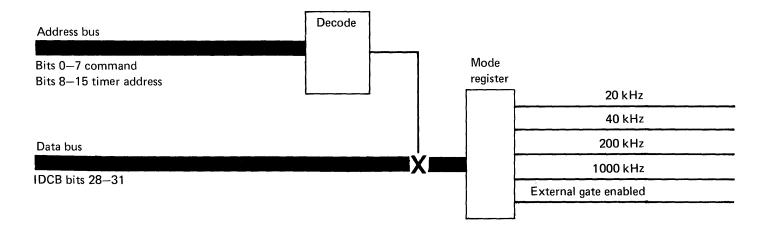

| Timer Card Data Flow 5-2                                         | DPC Adapter Operating Sequences 8-3                     |

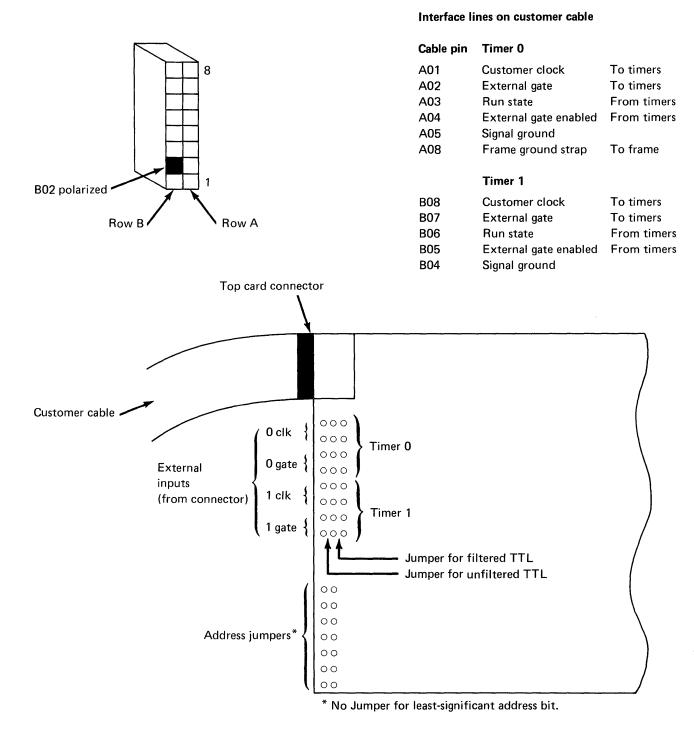

| Timer Card Locations 5-3                                         | DPC Adapter Feature Card 8-4                            |

| Addressing 5-3                                                   | Addressing 8-4                                          |

| Program Control 5-4                                              | Program Control 8-5                                     |

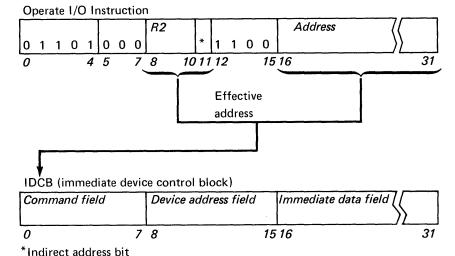

| Operate I/O Instruction 5-4                                      | Operate I/O Instruction 8-5                             |

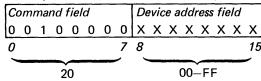

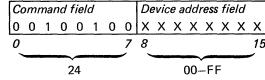

| Commands 5-4                                                     | Commands 8-5                                            |

| I/O Instruction Condition Codes 5-7                              | Adapter-Directed Commands 8-5                           |

|                                                                  | Device-Directed Commands 8-7                            |

| I/O Instruction Condition Codes 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Controller-End Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Exception Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Device-End Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Attention Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Attention and Exception Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Attention and Device-End Interrupt 8-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Interrupt ID Word 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Adapter Status Information 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Adapter Status Word 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Device Status Word 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Status After Resets 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 9. Two-Channel Switch Feature for 4959 I/O Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Unit 9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

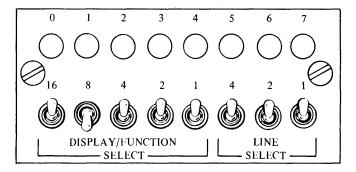

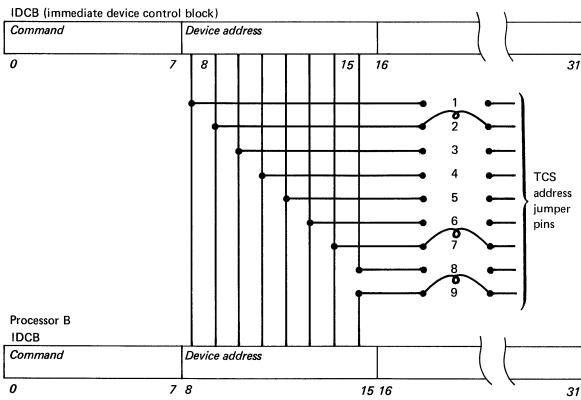

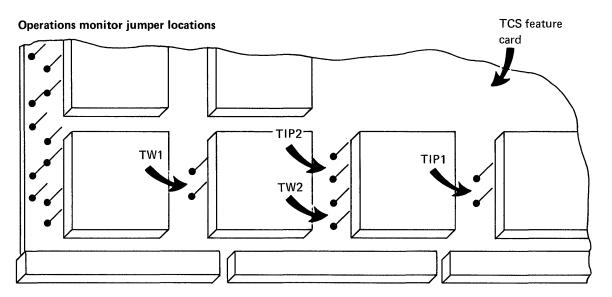

| Addressing 9-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Operations Monitor 9-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

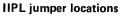

| Timing Jumper Options 9-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Program Control 9-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Commands 9-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| I/O Instruction Condition Codes 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| I/O Interrupts 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I/O Interrupt Condition Codes 9-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

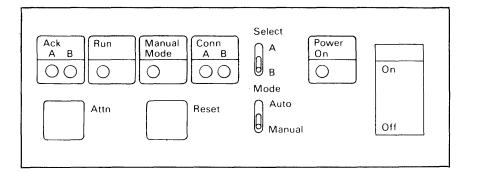

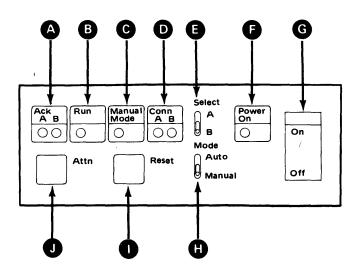

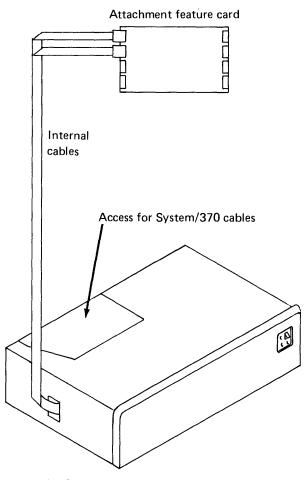

| TCS Operator Console 9-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TCS Operator Console Card 9-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

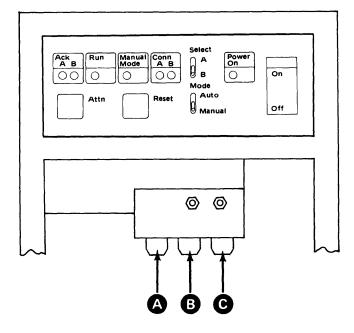

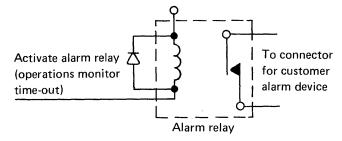

| Customer Output Alarm Relay 9-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Initial Program Load 9-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |