# **IBM RT Personal Computer Technology**

*IBM RT Personal Computer Technology* is a collection of papers by the developers of the RT PC. These papers describe the innovative aspects of the RT PC—what we set out to build, how we built it, and how it works today. The papers were written by technical professionals for readers who are conversant with the vocabulary and concepts of computers and programming.

This book is a one-time statement by the developers for historical and background purposes. Although there are several overview articles that describe how the various components work together, the emphasis is on the novel parts of the RT PC system. *IBM RT Personal Computer Technology* is intended to supply the reader with an understanding of the things that make the RT PC unique, not to provide detailed descriptions of all of the elements of the RT PC system.

The papers in this book are not intended to replace IBM publications in describing the capabilities of the system components and how to use them. Keep in mind that the papers are for general technical communication purposes; they do not represent an IBM warranty or commitment to specific capabilities in the referenced products. A variety of structures and levels of detail may exist in the papers because they were written as technical articles by different specialists. In order to preserve their authenticity and vitality, the papers have not been revised for consistency of style or method of presentation. These papers will not be updated to incorporate future developments.

This book is the work of many hands, but special acknowledgment is due to Bert Buller of the Hardware Architecture Group for coordinating the engineering articles, and to Herb Michaelson, Publications Consultant, for shaping both the book and the individual articles.

Frank Waters, Editor

©Copyright International Business Machines Corporation, 1986. Inquiries related to permission to republish an article in full or in part should be directed to the IBM Corporation, IBM Austin, 854/003, 11400 Burnet Road, Austin, TX 78758.

Copies of this book, SA23-1057, can be obtained from the local IBM branch office. IBM employees can order copies from Mechanicsburg.

Cover: An IBM RT Personal Computer Model 10 with a larger and somewhat faster ancestor in the background—an IBM System/ 370 Model 158 MP. Introducing a new architecture to the computer marketplace is never done casually. The cost and effort of transition from one architecture to another must be justified by substantial advantages. It is always tempting to apply advances in technology to improving the performance of existing architectures. Ultimately, however, refinement is subject to the law of diminishing returns. Continuing advancement requires fundamental changes.

The hardware and software architectures that were originally created for personal computers had to accommodate the speed and size constraints of the processors and storage devices that were available at the time. Techniques that were known to be effective on mainframes and minicomputers were simply too costly to implement on personal computers. Our intent in designing the RT PC has been to use recent technological and architectural advances to avoid the structural limitations of earlier designs.

The IBM RT PC is a new synthesis of computer concepts. It combines:

• A very fast Reduced Instruction Set 32-bit processor for efficient execution of programs compiled from a higher-level language,

- a resource manager to provide virtual machine, storage, and I/O functions and to ensure data integrity and processing continuity,

- a multitasking, multiuser operating system that can be tailored to make the RT PC suitable for a variety of user requirements,

- a coprocessor feature that allows users to run programs written for the IBM PC without interfering with the normal operation of the RT PC,

- and a wide variety of displays, printers, communications adapters, and processing features,

- in a box that fits on or under a desk.

With the RT PC, the architectural sophistication of the personal computer has caught up with that of the mainframe. Perhaps more important, we have laid a foundation for more efficient exploitation of future advances in both hardware and software technology. The open-endedness of the resource manager and operating system at all levels means that we can easily take advantage of new applications, devices, and communications techniques. The development of the RT PC system has been a multi-location effort. We have incorporated architectural advances from Yorktown Heights, technology innovations from Burlington, graphics peripherals and applications from Kingston, and engineering and programming developments from Austin. The RT PC has been the work of hundreds of individuals, both within and outside of IBM. The articles in this book describe some of their contributions. I want to convey to everyone involved my gratitude for their efforts and my respect for their accomplishments.

#### W. Frank King

Group Director of Advanced Engineering Systems Development Engineering Systems Products independent Business Unit

# Contents

| M RT PC Architecture and Design Decisions G. Glenn Henry         |                                                                                                          | 2  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----|

| Hardware Description                                             | P.D. Hester, J.T. Hollaway, and F.T. May                                                                 | 6  |

| Processor Card                                                   | D.E. Waldecker, K.G. Wilcox, J.R. Barr,<br>W.T. Glover, C.G. Wright, H. Hoffman                          | 12 |

| System Memory Cards                                              | Ronald E. Rowland                                                                                        | 18 |

| Floating Point Accelerator                                       | Scott M. Smith                                                                                           | 21 |

| System Board and I/O Channel for the IBM RT PC System            | Sheldon L. Phelps and John D. Upton                                                                      | 26 |

| IBM RT PC Displays and Adapters                                  | Joe C. St. Clair                                                                                         | 31 |

| Use of Artificial Intelligence to Diagnose<br>Hardware           | Nancy A. Burns and C. Edward Williams                                                                    | 35 |

| Manufacturing Innovations to Increase Quality<br>and Reduce Cost | Charles W. Bartlett, A.V. Burghart,<br>George M. Yanker                                                  | 40 |

| ROMP/MMU Technology Introduction                                 | D.E. Waldecker and P.Y. Woon                                                                             | 44 |

| The IBM RT PC ROMP and Memory Management Unit Architecture       | P.D. Hester, Richard O. Simpson,<br>Albert Chang                                                         | 48 |

| ROMP/MMU Implementation                                          | D.E. Waldecker, C.G. Wright,<br>M.S. Schmookler, T.G. Whiteside,<br>R.D. Groves, C.P. Freeman, A. Torres | 57 |

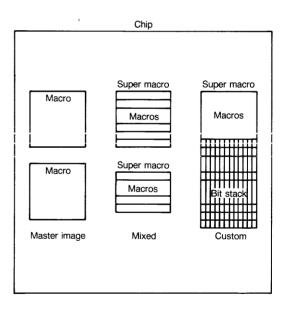

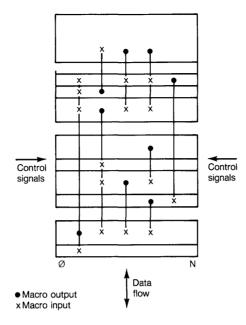

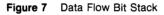

| ROMP/MMU Circuit Technology and Chip Design                         | Raymond A. DuPont, Ed Seewann,<br>Peter McCormick, Charles K. Erdelyi,<br>Mukesh P. Patel, P.T. Patel | 66  |

|---------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|

| Software Development Tools for ROMP                                 | Alan MacKay and Ahmed Chibib                                                                          | 72  |

| Compiling for the RT PC ROMP                                        | M.E. Hopkins                                                                                          | 76  |

| Advanced Interactive Executive (AIX™)<br>Operating System Structure | Larry Loucks                                                                                          | 83  |

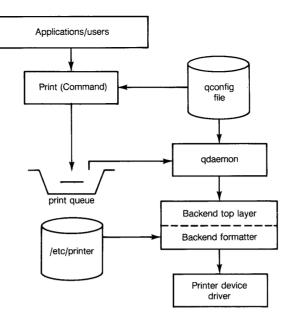

| Restructuring the AIX User Interface                                | P.J. Kilpatrick and Carolyn Greene                                                                    | 88  |

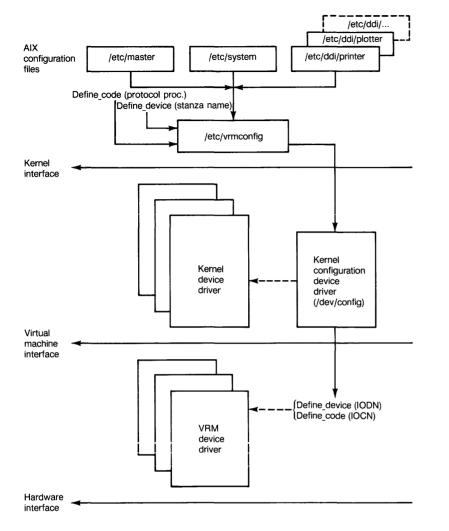

| Configuration Methods for a Personal Computer<br>System             | Shirley Lerom, Lee Terrell, and Hira Advani                                                           | 91  |

| IBM RT PC AIX Kernel — Modifications and<br>Extensions              | Larry Loucks                                                                                          | 96  |

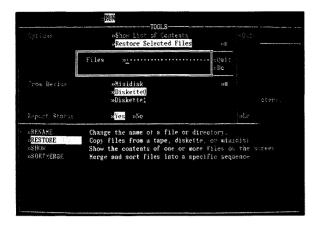

| Extendable High-Level AIX User Interface                            | Tom Murphy and Dick Verburg                                                                           | 110 |

| Extended File Management for AIX                                    | John M. Bissell                                                                                       | 114 |

| The Virtual Resource Manager                                        | Thomas G. Lang, Mark S. Greenberg, and<br>Charles H. Sauer                                            | 119 |

| Design of the IBM RT PC Virtual Memory Manager                      | J.C. O'Quin, J.T. O'Quin, Mark D. Rogers,<br>T.A. Smith                                               | 126 |

| The IBM RT PC Subroutine Linkage Convention                         | J.C. O'Quin                                                                                           | 131 |

| Implementation of a Virtual Terminal Subsystem                      | D.C. Baker, G.A. Flurry, K.D. Nguyen                                                                  | 134 |

| Use of a Coprocessor for Emulating the PC AT                        | John W. Irwin                                                                                         | 137 |

| Coprocessor Software Support                                        | Rajan Krishnamurty and Terry Mothersole                                                               | 142 |

| PC DOS Emulation in the AIX Environment                             | Leonard F. Brissette, Roy A. Clauson,<br>Jack E. Olson                                                | 147 |

| Authors                                                             |                                                                                                       | 149 |

## **Reader's Guide**

The *IBM RT Personal Computer Technology* book is divided into four parts. The first describes the main hardware elements of the RT PC system. The second section discusses the RT PC's 32-bit microprocessor. The third section covers the RT PC software and the fourth the PC AT coprocessor and AIX's PC DOS emulation functions.

A reader's guide, for a topical approach to this book, is as follows:

### **Overview Articles** Henry Hester et al. Waldecker and Woon Loucks **Major Hardware Components** Waldecker et al. Rowland Smith Phelps and Upton St. Clair **RT PC Microprocessor** Waldecker and Woon Hester et al. Waldecker et al. DuPont et al. User Interface Kilpatrick and Greene Lerom et al. Murphy and Verburg

Brissette et al.

**Operating System Modifications and** Extensions Loucks 83 96 Loucks Bissell 114 O'Quin 131 Virtual Resource Manager Lang et al. 119 O'Quin et al. 126 Baker et al. 134 Brissette et al. 147 PC AT Coprocessor Irwin 137 Krishnamurty and Mothersole 142

2

6

44

83

12

18

21

26

31

44

48

57

66

88

91

110

131

G. Glenn Henry

#### Introduction

The architect of a new system must start by making a series of high-level decisions about the hardware and software structure. These early choices shape all of the ultimate details of the product. An understanding of the "reasons why" is important to the person who is trying the understand the resulting system. In this paper, I will give a very general overview of the structure of the RT PC and explain the rationale for each of the major decisions that dictated that structure.

#### **Product Objectives**

The original objective of the project that resulted in the RT PC was to build a highfunction workstation with capabilities far beyond those of personal computers. Specifically required were:

- A high-performance 32-bit processor

- Large amounts of primary and secondary storage

- High-function virtual storage capabilities

- High-function APA display devices

- A full-function, multi-tasking operating system

- · A high degree of usability

- A flexible, extendable, and open architecture.

In addition to these technical objectives, there were a number of important practical requirements relative to producing a successful product:

- Easy portability of existing IBM and non-IBM applications

- Easy migration of users and their applications and data from existing systems

- The ability to take advantage of I/O attachments and devices used on other systems

- Straightforward ways for other IBM and non-IBM development areas to add and modify system functions (i.e., an "open" system).

These challenging and, in some cases, conflicting objectives, when combined with available technology, shaped the system design as described in the following sections.

#### System Structure

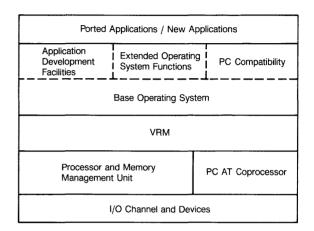

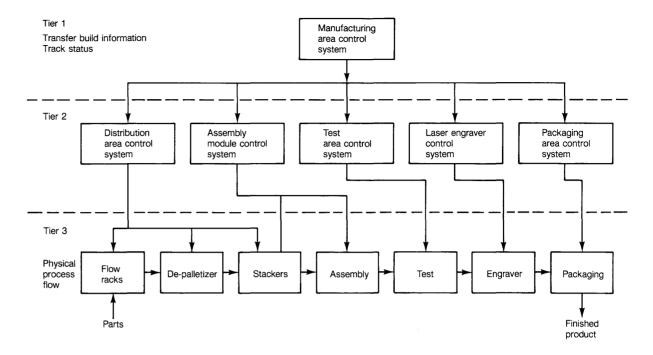

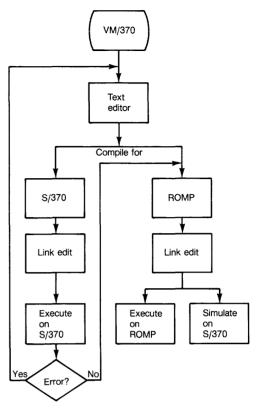

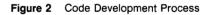

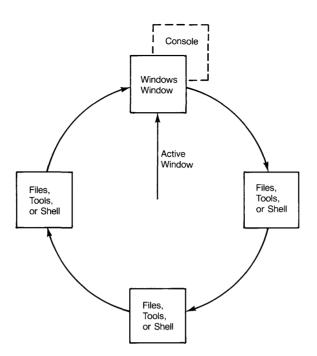

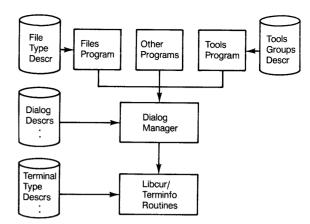

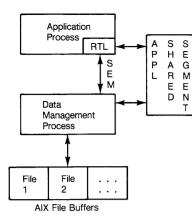

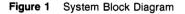

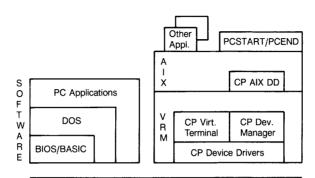

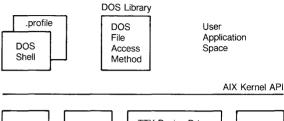

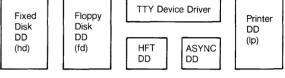

Figure 1 shows the logical structure resulting from the objectives and design systems.

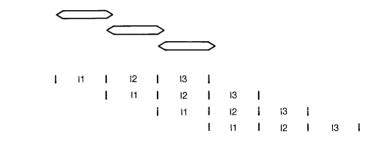

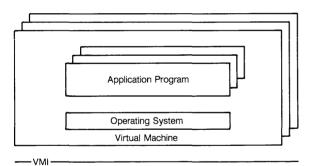

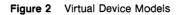

Figure 2 provides a more detailed look at the structure of the RT PC from a physical viewpoint. As you will see, the specifics of the system components reflect "something old, something new, something borrowed, and something Blue." The RT PC includes proven technologies and functions, innovations,

interfaces that are compatible with other systems, and IBM-exclusive technology. It is this combination of approaches that allows the RT PC to meet its sometimes conflicting objectives.

#### I/O Channel and Devices

The I/O structure chosen for the RT PC was basically the PC AT 16-bit I/O Channel, with some performance improvements. This choice makes it possible to use most of the existing PC AT I/O attachment cards, while providing acceptable levels of I/O performance with native RT PC I/O devices. While providing compatibility with the PC AT, the RT PC I/O channel provides more usable capacity to I/O devices, since processor RAM is not connected to the I/O channel and the RT PC

| Applications                     |  |

|----------------------------------|--|

| Application Development Products |  |

| AIX Kernel                       |  |

| VRM                              |  |

Figure 2 Physical Structure of the RT PC

I/O Channel Controller includes performanceassist features such as 32-bit "assembly" burst transfer.

#### **Processor and MMU**

The most critical choice was obviously that of the processor and associated Memory Management Unit (MMU). In spite of the obvious implications of the objective to ease migration of existing applications, we chose a new processor—the IBM Research/OPD Microprocessor (ROMP).

The major reasons for choosing the IBM ROMP were:

- It provides a full 32-bit architecture,

- with high performance (approximately 2 MIPs),

- using a Reduced Instruction Set Computer (RISC) architecture making it particularly suitable as a target for compilers (the

preponderance of code expected to be executed on the RT PC was anticipated to be generated by compilers),

- on a single chip for a low-cost, highperformance solution,

- with an associated MMU chip providing advanced virtual storage capabilities,

- and finally, there was no vendor microprocessor available with the full set of these capabilities.

The IBM ROMP is a single-chip derivative of the 801 processor project of IBM Research and thus benefits from the processor architecture analysis and advanced compiler architecture design activities associated with the 801. In addition, the IBM ROMP has special features such as "Load Multiple" and "Store Multiple" that extend the RISC architecture approach to provide increased efficiency and performance in a microprocessor implementation.

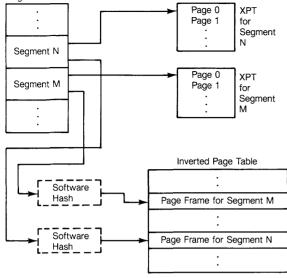

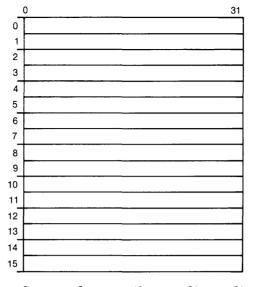

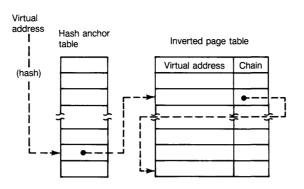

The virtual storage functions provided by the MMU chip are very powerful. For example, the 32-bit processor address is extended to a 40-bit virtual address with a highperformance, hardware-managed "inverted" page table translation approach. This significantly reduces the size of the page tables for the large virtual address space while providing very fast virtual-to-physical address translation. Even today, I do not know of another MMU that provides this level of function and performance.

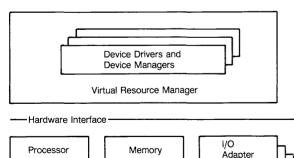

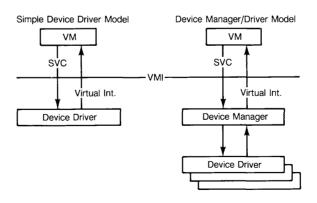

#### Virtual Resource Manager

When designing the software structure for the RT PC, we decided to build a Virtual Resource Manager (VRM) to control the real

hardware of the machine. The VRM presents operating systems with a Virtual Machine Interface (VMI) that not only conceals the complexities of virtual memory management and numerous I/O device types, but provides the operating system with a significantly more powerful set of functions than are available on the bare machine. It is therefore not accurate to think of the VRM as a pure hypervisor, like VM/370. The VMI is, in effect, a higher-level machine to which guest operating systems can be converted. We considered the VRM necessary because:

- The operating system base that we wanted to use for the RT PC was not built to run on a computer with virtual memory, did not provide real-time I/O capabilities, and didn't provide dynamic install and configuration functions. We decided to provide these important functions "under" the operating system, as opposed to making extensive modifications to the kernel of the existing operating system. For example, the VRM provides a very fast preemptive interruptbased I/O structure, virtual storage management functions, and dynamic loading and binding of I/O device drivers. This allows, for example, the operating system kernel to be paged and complex, multi-tasking I/O device drivers to be implemented.

- We wanted to achieve a higher degree of program isolation from the hardware details than is possible with the current personal computer operating systems. That is, the VRM resembles BIOS on the IBM PC, but it provides a much higher level of hardware independence. For example, generic device classes are supported at the VMI, allowing high levels of device transparency and I/O redirection.

- We wanted to allow hardware coprocessors to execute concurrently with ROMP without making major changes to the existing base and with minimal overhead for resource allocation and management (see PC Compatibility, below).

- We needed to isolate the development of the RT PC software from changing hardware characteristics during the development process. While this was an "internal" IBM requirement, the success of the VRM in meeting this goal validates its architecture and implementation features relative to providing high levels of hardware transparency to the user software.

Consistent with the objectives for a flexible and open system, the VRM provides complete facilities for the user to implement and install code in the VRM. That is, the detailed hardware structure is isolated from software in the preponderance of cases where that is desirable, but conversely, all hardware details are available to user functions that require them.

#### **Operating System and Extensions**

As the base for the RT PC's Advanced Interactive Executive (AIX<sup>1</sup>) operating system, we chose AT&T's UNIX<sup>2</sup> System V<sup>3</sup>. We chose UNIX because it provides considerable

""Aix" is a trademark of International Business Machines Corporation.

<sup>2</sup>Trademark of AT&T Bell Laboratories.

<sup>3</sup>The UNIX component of AIX was developed by IBM and INTERACTIVE Systems Corporation. The UNIX component is based on INTERACTIVE's IN/ix, which is based in turn on UNIX System V, as licensed by AT&T Bell Laboratories. (IN/ix is a registered trademark of INTERACTIVE Systems Corporation.) functional power to the individual user, provides multi-user capabilities where needed, is open-ended, and has a large user and application base. We concluded that AT&T's System V suited our purposes better than alternative UNIXes because of the larger number of applications that had been built to run on that base, as well as for a variety of practical reasons.

In choosing UNIX, however, we accepted the need to make significant extensions and enhancements to meet the needs of our expected customers and target applications. This is, of course, the classical trade-off between choosing an existing software system for its pragmatic characteristics versus developing a new system with (hopefully) fewer deficiencies but limited applications and user familiarity. We chose to start with UNIX and fix the deficiencies while retaining upward compatibility for all UNIX System V interfaces.

Some of the major enhancements made were:

- A Usability package to provide easier access to the capabilities of the UNIX command language and to simplify the implementation of full-screen dialogs

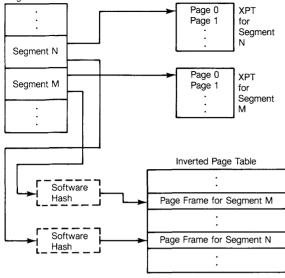

- Multiple, full-screen virtual terminal support to permit a single user to run several interactive applications concurrently, timesharing the console display

- Enhanced console support including extended ANSI 3.64 controls, color support, sound support, and mouse support

- An indexed data management access method that is integrated into the base UNIX file system structure (this allows UNIX

system utility functions such as "cp" to transparently operate on composite data management objects consisting of an index file and a data file)

- Extensions to exploit use of the powerful virtual storage support; in particular, mapped file support which allows an application to "map" a file into a 256 megabyte virtual address space, and access it with loads and stores, versus reads and writes (a derivative is used by the system to provide mapped text segment support, allowing paging "in place").

- Enhanced signals to allow flexible exception-condition handling

- A variety of floating point support functions

- Simplified installation and configuration processes.

#### **PC Compatibility**

In addition to UNIX application portability, our original objective of easing user and application migration required a high level of compatibility with the IBM PC family. This was provided by:

- An IBM PC AT hardware coprocessor that includes an Intel 80286 along with associated hardware to provide a high level of PC AT hardware compatibility

- An IBM PC DOS "shell" on the AIX Operating System allowing DOS command syntax and semantics to be used to invoke AIX functions

- IBM PC compatibility modes in the RT PC BASIC and Pascal compilers, providing IBM PC BASIC and Pascal-compatible functions

IBM PC diskette access utilities and access methods.

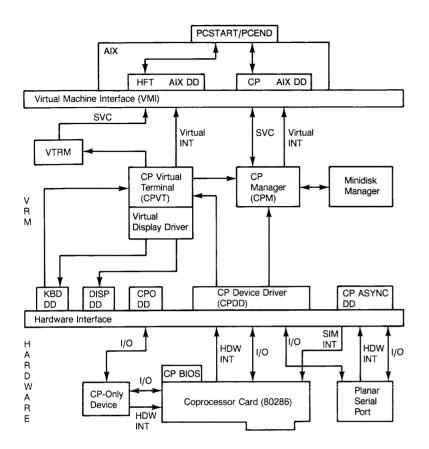

One of our key technical decisions relative to compatibility was to allow the PC AT coprocessor to execute PC programs concurrently with ROMP programs, sharing system resources such as main storage and the system console. This unique capability is provided by a combination of the coprocessor hardware card and the VRM, which manages the allocation and sharing of resources in such a way that the coprocessor's concurrent execution is transparent to the operating system and application programs. For example, the VRM allocates the console keyboard to either the coprocessor or the ROMP and monitors keystrokes for a "hot key" sequence signalling a need to switch to the other processor. In a similar fashion, other system resources are managed so that the coprocessor applications seem to execute in a virtual terminal just as the ROMP applications do.

#### **Application Development Facilities**

For the initial release of the RT PC, we placed a high priority on providing function to facilitate application development. We extended the already rich UNIX application development support functions with:

- a host-compatible SQL data base manager providing both an API and a full-screen user interface,

- a FORTRAN compiler, BASIC compiler and interpreter, and Pascal compiler (in addition to the C compiler and assembler included in the base operating system),

- a "net BIOS" set of facilities for access to the IBM PC Network,

and many base operating system extensions: message services, shared segment manager, etc.

#### The Result

We believe the design choices presented here and the specific designs highlighted in the following papers allow the IBM RT PC to meet its original objectives. Further, these directions provide the architectural and design base for improvement with minimal disruption as technology progresses. P.D. Hester, J.T. Hollaway, and F.T. May

#### Introduction

#### Design Philosophy

The IBM RT PC system hardware was designed with the following basic philosophy in mind.

- A new family of workstation systems should be based on the most recent advances in microcomputer technology.

- An architecture should be established to ensure:

- The effective integration of a 32-bit virtual memory microprocessor with existing and new 8-bit and 16-bit I/O adapters

- The effective addition of I/O devices and adapters as technology trends progress

- The attachment of coprocessors for compatibility and performance enhancements

- The ability to incorporate user-installable performance enhancements over the life of the product

- A strong relationship should be maintained with the IBM Personal Computers.

- The product should allow customer setup and service.

• The initial product offering should clearly demonstrate the long-range potential of the design.

#### Hardware Summary

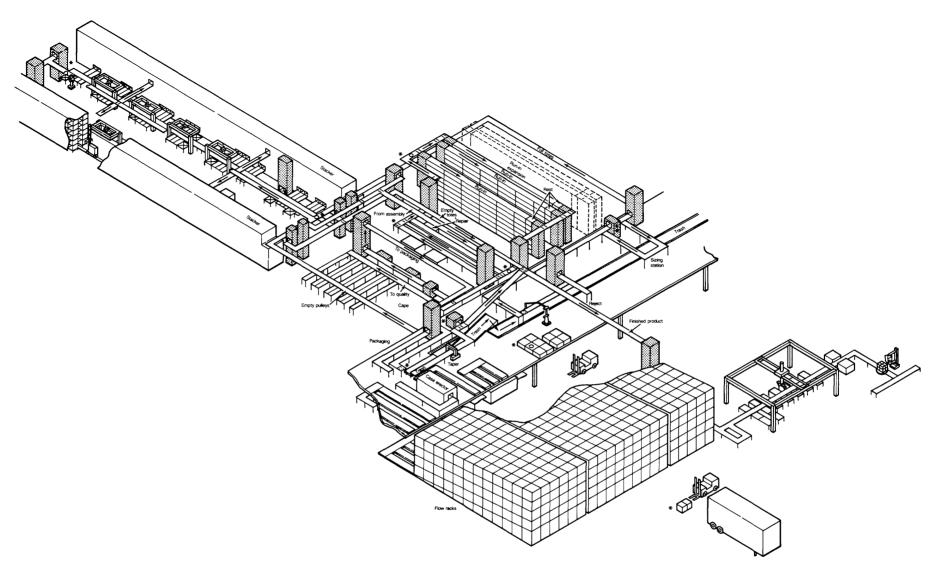

The RT PC workstations have consoles that contain the electronics, storage devices and power supply. They cable attach to the display, keyboard and other optional devices to meet the configuration requirements for the customer's applications. The IBM RT PC is available in two basic packages: the IBM 6150 is a floor-standing unit and the IBM 6151 is a desk-top console similar in size to the IBM PC AT. The 6150 Model 25 provides the maximum extendability, but most options are available on all models.

The workstations have a wide range of standard and optional hardware components. Data storage is provided on 5-1/4-inch hard disks and diskettes. A large system board is used to package the base electronics and card slots in each model. A number of cards and adapters have been designed specifically for the RT PC, and the I/O channel slots are designed so that many existing IBM PC and PC AT cards can also be used. Operator input can be made with a 101-key keyboard and an optional two-button mouse or tablet pointing device.

In addition to the standard I/O channel slots on the system board, there are unique slots for each of the 32-bit system components. The new IBM-designed ROMP 32-bit microprocessor and its corresponding Memory Management Unit (MMU) are packaged on a processor card which comes with each model. There is also a separate 32bit slot for an optional floating point accelerator card. Two other dedicated slots are provided for system memory cards.

The unique ability to execute both IBM PC and IBM PC AT programs concurrently with native RT PC programs is provided by an optional coprocessor card which plugs into one of the I/O slots. Other coprocessor options provide for faster performance with additional PC AT memory cards and a math coprocessor chip.

The system memory is packaged on 1- and 2-megabyte cards which plug into two dedicated memory slots and provide expansion of models up to 3 and 4 megabytes. The hardware architecture allows for addressing up to 16 megabytes of real memory.

A wide variety of display subsystem options is available. In addition to existing IBM PC displays and adapters, three new offerings are available with monochrome and color APA features. Also, computer-aided design applications can be run using a serial link adapter card attached to an IBM 5085 Graphics Workstation in a host-based network.

#### **Hardware Architecture**

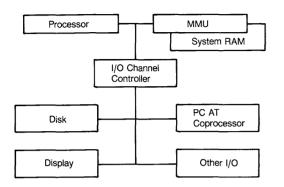

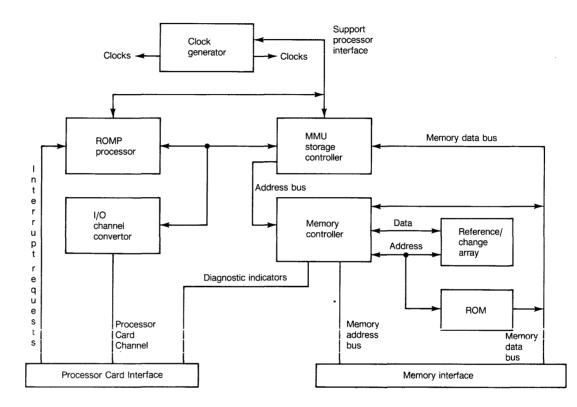

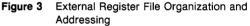

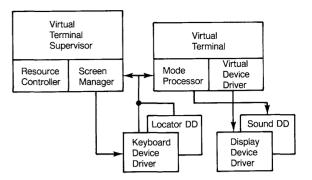

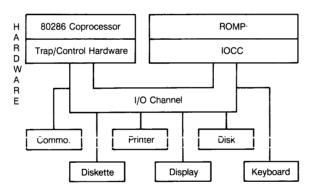

The RT PC system combines a 32-bit microprocessor (ROMP) and Memory Management Unit (MMU) with a standard 16-bit I/O channel. The system is partitioned so that the 32-bit system components operate independently from the 16-bit I/O channel. This approach provides both highperformance, 32-bit processing and compatibility with standard 16-bit I/O adapters. The RT PC hardware structure is shown in Figure 1.

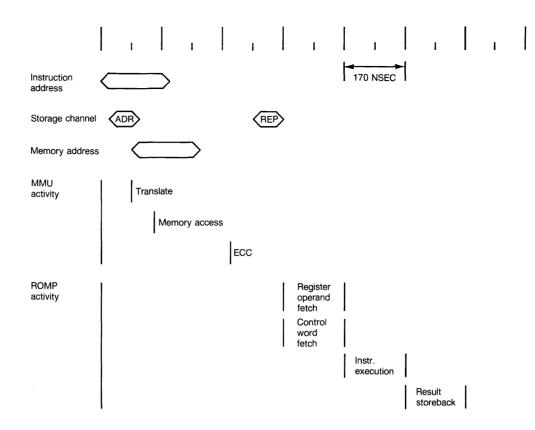

The RT PC utilizes the IBM-developed ROMP microprocessor and corresponding MMU packaged on a processor card which plugs into the system board. The ROMP implements a Reduced Instruction Set Computer (RISC) architecture with 118 instructions, 16 32-bit general-purpose registers, and a full 32-bit data flow for both addresses and data. Most register-to-register operations execute in one 170-nanosecond cycle. Performance is typically 1.5 to 2.1 MIPs, depending on the instruction mix.

The MMU implements a "single level store" address translation architecture which converts the 32-bit system address to a 40-bit (1 terabyte) virtual address for translation. Internal translation buffers within the MMU convert the 40-bit virtual address to a 24-bit (16 megabyte) real address. Hardware is also provided in the MMU to automatically reload the translation buffers from main memory page tables as required. The MMU also contains the ECC logic for system memory, and some of the control logic for system memory and the IPL and power-on self test ROM.

Details of the ROMP microprocessor and MMU architecture are described by Hester, et

Figure 1 RT PC System Architecture

# al.[1]. Chip implementation details are described by Waldecker, et al.[2].

Both the ROMP microprocessor and the MMU are custom designed VLSI components using an IBM 2 micron NMOS process. Both components are packaged in a pin grid array package on a 36-millimeter ceramic substrate. The ROMP contains approximately 45,000 devices on a 7.65 x 7.65 millimeter chip, with the MMU containing approximately 62,000 devices on a 9.0 x 9.0 millimeter chip.

In addition to the ROMP and MMU, the processor card (see Waldecker, et al. [3]) contains logic to adapt the 32-bit packetswitching microprocessor channel to an asynchronous 32-bit processor channel connected to the optional floating point accelerator card and the system board I/O Channel Converter (IOCC). A dedicated memory channel is also generated from the MMU for connection to the system memory cards. Five IBM technology bipolar gate arrays of approximately 300 gates each and vendor TTL logic are used for interfacing to the processor channel and memory channel.

Clock generation for the microprocessor, memory management unit, and system memory is provided on the processor card. Independent clock generation is provided on the system board for I/O channel timing. This makes it possible for higher performance processor cards and system memory cards to be supported as technology permits, without affecting I/O channel timing.

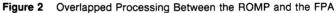

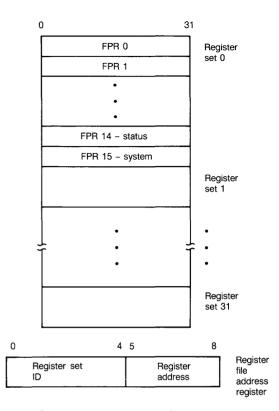

The optional Floating Point Accelerator (FPA) card attaches to the 32-bit processor channel and provides improved performance for floating point applications. This card utilizes a National Semiconductor NS32081 Floating Point Unit and operates independently of the ROMP. Multiple floating point register sets are provided for rapid context switching. Performance is approximately 200,000 Whetstone instructions per second. Various aspects of the FPA are covered by Smith [4].

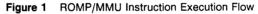

Two dedicated slots are provided for system memory, which attaches to the processor card through the memory channel. The memory channel consists of an independent 40-bit data bus and 24-bit address bus. The data bus includes 32 bits of data and 8 bits of error correcting code (ECC). The RT PC ECC allows automatic detection and correction of all single-bit system memory errors, and detection of all double-bit errors. The 24-bit address bus is capable of addressing up to 16 megabytes of system memory.

Standard 256K RAM technology is used on the system memory cards, with a minimal amount of support logic. All memory timing, control, and ECC functions are provided by the processor card. System memory is twoway interleaved on each memory card, with one bank containing only even addresses and the other bank containing only odd addresses. This interleaving technique, combined with 150-nanosecond access time RAMs, provides a system memory bandwidth of 23.5 megabytes per second (4 bytes every 170 nanoseconds). Details of the memory cards are described by Rowland [5].

The system board contains all of the channel conversion functions to adapt the 32-bit ROMP Storage Channel (RSC) to a PC AT-like I/O channel. I/O channel support functions such as an interrupt controller, DMA controller, and real time clock and timer are also provided on the system board. Timings, address assignments, interrupt assignments, DMA assignments, and related functions of the RT PC I/O channel were designed to be as compatible as possible with the PC AT I/O channel. In addition, new features such as burst and buffered DMA and shareable interrupts were added to improve the channel performance and usability. The IBM 6151 provides one 8-bit PC slot and five 16-bit PC AT slots. The IBM 6150 provides two 8-bit PC slots and six 16-bit PC AT slots. Timing and performance of the I/O channel are the same in all models. Phelps and Upton [6] discuss various characteristics of the RT PC I/O channel.

In addition to the channel conversion functions, the system board contains a programmable translation control facility to support accesses from adapters on the I/O channel to system memory. A separate dedicated microprocessor is provided to handle the keyboard, speaker, mouse, and tablet interface. The IBM 6150 also includes two built-in RS-232 serial ports with DMA capability for attaching terminals, printers, or other I/O devices.

The optional Intel 80286 based coprocessor card plugs into an I/O channel slot and provides compatibility with PC and PC AT programs. In addition to the 80286 and optional 80287 math coprocessor, this card contains control logic that intercepts 80286 accesses to selected I/O addresses. A combination of this logic and system software allows sharing of system I/O adapters such as displays, keyboards, and files. Alternately, system software can program this logic to allow direct coprocessor access to private I/O adapters. Appropriate mapping is also provided by system software that allows PC applications written for the PC monochrome or color adapter to run on an RT PC using a native APA display. Operation of the coprocessor card is described by Irwin [7].

PC programs for the coprocessor can be stored either in system memory or in dedicated, I/O channel-attached memory. Coprocessor performance is typically that of a PC when executing programs in system memory and about 80 percent that of a PC AT when using I/O channel-attached memory.

#### I/O Devices

The selection of I/O devices was made by considering technology trends, the requirements of evolving applications, system performance, and physical power and packaging constraints. The generic set of devices required for electronic workstations is well established in the industry. There are a number of vendors that specialize in each of these devices and are very competitive in advancing the state of the art in their respective areas of the industry. The architecture of the RT PC system allowed the designers to select the preferred devices to meet the anticipated marketing opportunities as the project proceeded and the requirements changed. A few examples are outlined below.

#### Hard File Subsystem

The major decision in the selection of hard files was to use the 5-1/4-inch form factor. The size of the desk-top and floor-standing consoles is most directly affected by the size of the files. The technology was moving toward 5-1/4-inch files even though the 8-inch files were still improving in capacity and cost. The main reservation in the selection of these files was the average access time, which is in the range of 40 milliseconds versus 25 to 30 milliseconds for 8-inch files. Transfer rates are the same, at 5 megabits per second. System performance work was done to understand and compensate for this difference. The capacity of the files to make available in the models also varied as the project advanced. Files as small as 10 to 20 megabytes were seriously considered, but the final system design point required the larger capacities of 40 and 70 megabytes. The combination of these larger files, and the option to have a model with three files, substantially expanded the range of potential applications that can be adapted to the product.

Another example of the flexibility of the design approach to the file area is illustrated by the fact that the disks and diskettes are attached by the use of the IBM PC AT Fixed-Disk and Diskette Drive Adapter, an existing card in the IBM PC product family.

An external streaming tape drive and a separate adapter card that attaches to the RT PC I/O channel are available as an option. The streaming tape unit provides a capacity of 55 megabytes using a standard 1/4-inch tape cartridge.

#### **Display Subsystems**

The display subsystem is generally the most obvious I/O device to the users of electronic workstations. The characteristics of the display are described by the parameters of size, number of picture elements (PELs), PEL density, monochrome and color, and front-of-screen performance. Substantial cost differences exist among these parameters. The applications selected by the users determine which of these parameters affect their choice of display subsystem. Details of the various displays and adapters are described by St. Clair [8].

The design decision was to offer a wide variety of display options and ensure that the architecture allowed for future options to be provided as the applications evolve. The RT PC can meet the needs of a wide variety of users, so their display needs are expected to be diverse.

The RT PC system provides for the attachment of existing adapters and displays of the IBM PC products. Specific IBM PC displays which have been tested for announcement are the Monochrome Display and the Enhanced Color Display with their respective adapters.

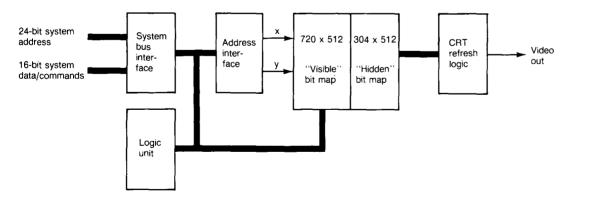

The new displays and adapters provide direct processor access to a 1024 x 512 bit map with a display viewing area of 720 x 512 PELs. Hardware assist provides for text and graphics alignment to the PEL level. This design point was determined to be a good trade-off between cost and total screen PELs for both monochrome and color applications.

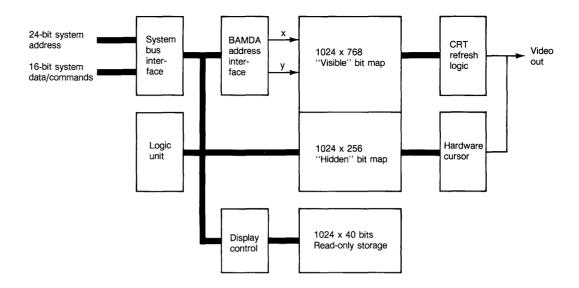

A higher function monochrome display subsystem provides a larger viewing area of 1024 x 768 PELs and extensive hardware assist for high-speed vector-to-raster conversion from a vector list buffer. This design point is also considered to be a good trade-off between cost and total screen PELs.

A full 1024 x 1024 color display with existing advanced computer-aided design, CAD, applications is provided by the ability to use a serial link adapter card to attach the RT PC system to an IBM 5085 Graphics Workstation in a host-based network.

#### **Mechanical And Electrical Packaging**

Two different physical packages were selected for the RT PC system. The IBM 6151 package is very similar to the IBM PC AT desk-top configuration. The IBM 6150 has a floor-standing console to provide room and power for more adapter cards and files. The key requirements for the packaging were set in compliance with the basic design philosophy mentioned above. One was to provide for the use of existing IBM PC cards, which established minimum physical dimensions and power requirements. File capacity requirements to support the addressing capabilities of the processor dictated the need to have models that can hold multiple files. A system board is used to mount connectors for the various cards that make up the base models and to provide extra slots for options.

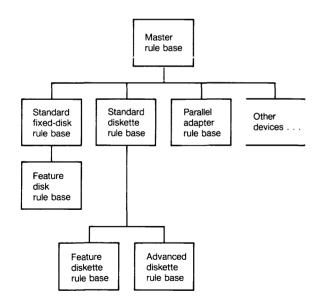

Equally important were the requirements to design the product for automated manufacturing. This included limiting the number of separate subassemblies, establishing a standard packaging form for each of the subassemblies delivered to the manufacturing line, minimal use of internal cables for interconnections, and selection of one standard card size for all cards. Details of the manufacturing process are described by Bartlett, et al.[9].

#### **Quality And Reliability**

Many design and manufacturing decisions during RT PC development were made to ensure a high quality and reliable product. These included design for automation concepts in the original design, development of an automated manufacturing process, component selection process, analysis of early life failures, and automated error logging during system run-in testing.

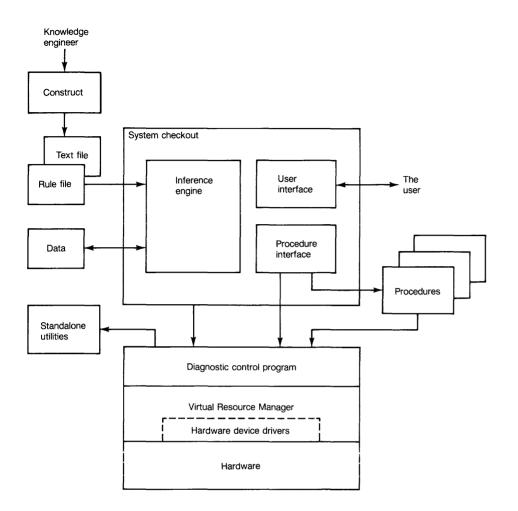

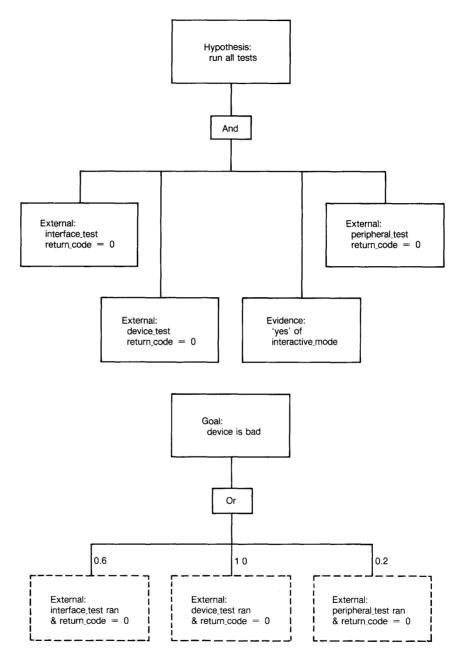

A diagnostic program based on an expert system (see Burns and Williams [10]) is provided to aid the customer in diagnosing system problems. This program tests all RT PC system board functions and all I/O adapter functions. Major considerations in the development of the diagnostic program were providing a user interface with simple selection of desired tests and reporting test results in a concise manner. These characteristics were considered mandatory for a machine with customer setup and service.

Both the RT PC design and manufacturing processes have resulted in the ability to produce a complex workstation in high volumes. The component selection and qualification process, failure analysis, and run-in testing allowed supporting a 12-month warranty.

#### Conclusion

The RT PC system was designed to bridge the gap between the personal computer products introduced during the past few years and emerging advanced 32-bit workstations with extensive virtual memory management facilities. These workstations will become the basis of computing systems that have extensive storage, display and communications requirements to satisfy new applications as they evolve. Specifically, the RT PC:

- Introduces an IBM-developed, highperformance, 32-bit RISC architecture with virtual memory.

- Combines the new 32-bit features with a standard PC I/O channel.

- Provides an optional PC coprocessor for compatibility with existing PC application programs.

The development cycle for the product was executed during a period of continual change in technologies and design specifications, so an architecture was defined to provide consistency of design decisions in this environment. The architecture was tested on numerous occasions and allowed for needed design changes that preceded the initial product announcement.

The use of an open architecture similar to the earlier IBM PC products allows for extension by anyone who chooses to develop hardware attachments and applications that enhance the features of the base machines. This approach continues to be successful in personal computer systems and should be successful in the more advanced workstationoriented systems.

Numerous enhancement possibilities are obvious to designers and users of this new class of advanced product. The architecture is capable of supporting increased memory capacity, higher capacity files, higher performance displays, other local area networks, higher speed host attachments, and other coprocessors. Enhancements should follow as time and new technologies allow interested companies in the computer industry to respond to the business opportunities.

Some enhancements may be limited by the I/O devices, or by the I/O channel characteristics. Others may be limited by computational speeds in the main processor, the IBM PC AT coprocessor, or the floating point accelerator. Performance requirements of new applications will reveal these constraints. Potential solutions to many anticipated future requirements have already been defined by the development team.

It is hoped that the decisions made during the RT PC system development process will survive the test of time, that the technologies provided by the product will satisfy the needs of developers, and that the applications built on the product will meet the needs of users ranging from technical professionals to office workers.

#### References

- 1. P.D. Hester, Richard O. Simpson, Albert Chang, "The RT PC ROMP and Memory Management Unit Architecture," *IBM RT Personal Computer Technology*, p. 48.

- D.E. Waldecker, C.G. Wright, M.S. Schmookler, T.G. Whiteside, R.D. Groves, C.P. Freeman, A. Torres, "ROMP/MMU Implementation," *IBM RT Personal Computer Technology*, p. 57.

- 3. D.E. Waldecker, K.G. Wilcox, J.R. Barr, W.T. Glover, C.G. Wright, H. Hoffman, "Processor Card," *IBM RT Personal Computer Technology*, p. 12.

- 4. Scott M. Smith, "Floating Point Accelerator," IBM RT Personal Computer Technology, p. 21.

- 5. Ronald E. Rowland, "System Memory Cards," *IBM RT Personal Computer Technology*, p. 18.

- Sheldon L. Phelps and John D. Upton, "System Board and I/O Channel For The IBM RT PC System," IBM RT Personal Computer Technology, p. 26.

- John W. Irwin, "Use Of a Coprocessor For Emulating The PC AT," *IBM RT Personal Computer Technology*, p. 137.

- 8. Joe C. St. Clair, "IBM RT PC Displays and Adapters," IBM RT Personal Computer Technology, p. 31.

- Charles W. Bartlett, A.V. Burghart, George M. Yanker, "Manufacturing Innovations to Increase Quality and Reduce Cost," *IBM RT Personal Computer Technology*, p. 40.

- Nancy A. Burns, C. Edward Williams, "Use Of Artificial Intelligence To Diagnose Hardware," *IBM RT Personal Computer Technology*, p. 35.

# **Processor Card**

D.E. Waldecker, K.G. Wilcox, J.R. Barr, W.T. Glover, C.G. Wright, H. Hoffman

#### Introduction

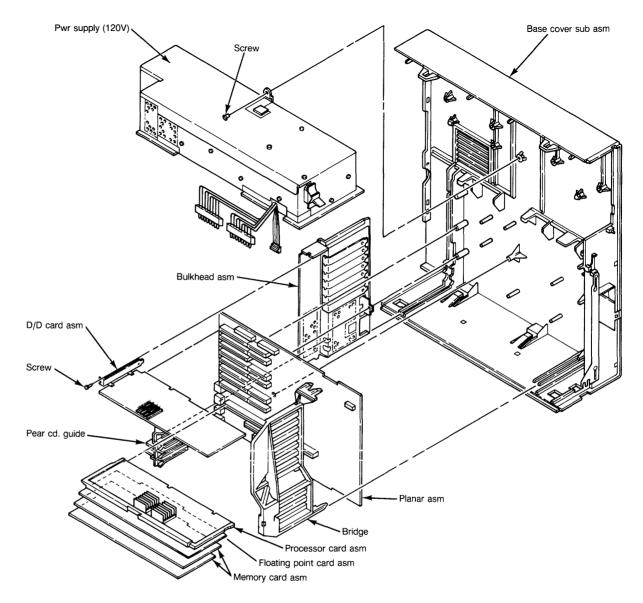

The processor card provides the central processing and memory management functions of an IBM RT PC system. It interfaces with memory cards [1] and I/O hardware on the RT PC system boards [2] in a manner which readily supports future enhancements of memory cards or the processor card itself. The card contains the ROMP processor and MMU memory management chips [3] plus support functions including ROM and internal clock generation.

#### **Card Functional Overview**

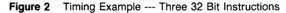

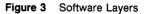

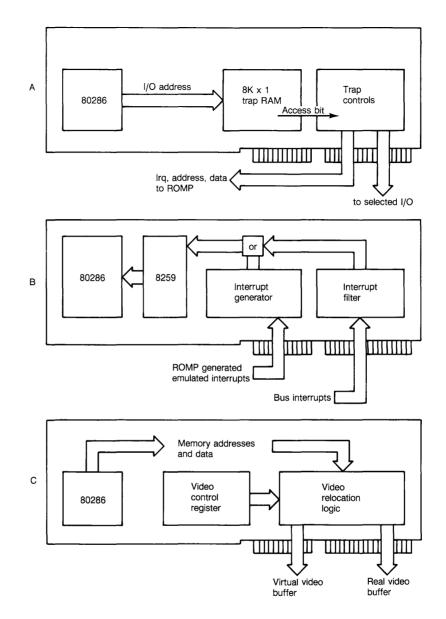

A functional diagram for the processor card is given in Figure 1. Logic on the card adapts the ROMP and MMU interfaces for other system components and develops a special test interface [3] that supports hardware and software debug without removal of the ROMP processor chip or any perturbation of the physical card components.

The MMU connects to ROM and a Referenceand-Change Array on the processor card as well as with the interleaved memory cards. The ROM contains programs to perform power-on diagnostics and IPL functions for the system. The diagnostic display indicators are also driven by logic on the card. Failure isolation is improved by packaging the diagnostic ROM and the display drivers with the processor components.

The memory-specific controls were placed external to the MMU to improve flexibility in

Figure 1 Processor Card Functional Diagram

selecting dynamic RAM and ROM modules for optimum cost/performance characteristics in the system. The Reference-and-Change Array is external to the MMU due to space limitations on the chip. (The function of the Reference and Change Array is explained later.)

I/O interface adapter logic was included on the processor card to improve fault isolation and to enhance performance. This approach also restricts the high frequency, repetitive clocks to the card and minimizes electromagnetic interference exposures for the system.

The clock generator logic is driven by a 23.5294 MHz oscillator to provide clocks for a 170-nanosecond processor cycle time. The

timing relationship between clocks on the card is tightly controlled by synchronizing the clocks in FAST TTL modules.

#### **Processor Card Interfaces**

Two independent system interfaces, the processor channel and the memory channel, connect the processor card to the rest of an RT PC system. A test interface is also available for special hardware and software debug functions.

The memory channel can connect to one or two memory cards containing a maximum of 16 megabytes of memory. The memory cards are described in the article by Rowland [1].

The processor channel is an asynchronous, 32-bit, bidirectional channel which connects to the I/O Channel Controller (IOCC) on the RT PC system board [2] and to the Floating Point Accelerator Card [4].

#### **Memory Interface**

The memory interface logic manages an address bus, a data bus, and control signals permitting two memory accesses to be in progress simultaneously. The interface connects to both ROM and RAM and is flexible regarding the amount of each which may be present in a system. Memory refresh is managed and directed to an idle memory bank when possible, thus reducing refresh interference.

The memory interface logic contains two IBM bipolar gate arrays, TTL logic for memory card interface buffering, four ROM modules, and a 16K by 1 static RAM which is the Reference-and-Change Array.

Two memory card slots on the system board and a range of memory card configurations are supported. Memory cards ranging in size from 512K bytes to 8M bytes can be supported by decoding four control lines (two from each memory card slot in use). During a memory access, the memory card capacity indicators and several bits of the storage address bus are used to verify that the access is to a valid memory address. Although the processor card accepts a one or two memory card configuration, "slot-0" must be used first. Also, the memory capacity of the card in slot-0 must be greater than or equal to the memory capacity of the card in slot-1.

The RAM on each memory card is divided into two independent banks (an even bank and an odd bank) for interleaving purposes. The even bank operates on requests with an even fullword storage address from the MMU and the odd bank operates on the odd address requests. All accesses to storage are done using fullword data transfers. Interleaved memory improves system performance by allowing two memory accesses to be in progress at the same time. (A timing diagram which shows interleaved memory operation is included in the paper on ROMP/MMU Implementation [3].) A separate 10-bit RAS/CAS address bus is provided for each bank of storage. The memory card interface consists of the two 10-bit address buses, a 40-bit bidirectional data bus (including 8 bits ECC), and 21 control lines.

The processor card memory interface generates all clocks and controls needed to operate the memory modules on the memory cards. Four separate row address strobe clocks are created to support the maximum memory card configuration (i.e., even bank/ slot-0, odd bank/slot-0, even bank/slot-1, and odd bank/slot-1). Two column address strobe clocks are provided: one for the two even banks, and one for the two odd banks. Enable signals are provided to control read/ write of the memory as well as the direction of the data bus.

The MMU chip makes use of an external array consisting of one"Reference" bit and one "Change" bit for each page of real storage in the system. The Reference bit indicates if the corresponding page has been accessed, and the Change bit indicates if the page has been altered. This information is used by system software for page replacement decisions. The Reference-and-Change Array is implemented with a 16K by 1 static RAM. The storage address bits and the storage interface control signals from the MMU are used to determine if a RAM access has taken place and, if so, to set the appropriate bits in the array. The Referenceand-Change Array is also accessible to system programmers via the Programmed Input/Output (PIO) commands to the MMU.

Eight bits of data (comprising two decimal digits) for the Diagnostic Display LED indicators are driven by the memory interface logic. During IPL the LED indicators are used by software to show the hardware diagnostic program that is either currently executing or which has failed. In addition, the memory interface logic automatically sets the LED indicators to ''88'' if the ROMP processor stops due to a severe error or due to a halt command during debug.

#### Interface to the System Board

The design objectives of the processor card's interface to the system board (the "processor channel") were high performance, non-critical timings, simple system board attachment logic, and isolation of the processor card from the system board. The desirability of high performance, relaxed timing, and simple attachment is obvious. Isolation is

advantageous because it limits the most timecritical signals and clocks to the processor card, allowing better performance. It also allows future improvement of processor cycle time without impact on system design. Finally, restricting the high-speed signals to the processor card reduces the potential for electromagnetic radiation problems.

The interface between the processor card and the system board is 32-bits wide, multiplexed, and asynchronous. The address and data transferred over the processor channel are in the same format as when transferred over the RSC. The processor channel has some attributes of a general-purpose bus, but the processor card is the sole bus master, and all bus timing is under its control.

On the system board interface, there are two slaves, the I/O Channel Controller (IOCC), which develops the I/O channel, and an optional floating point card. The processor may access the IOCC or floating point card using Load or Store instructions (memorymapped I/O) to segment 15 of the virtual or real memory space. In addition, the IOCC may access system storage through DMA.

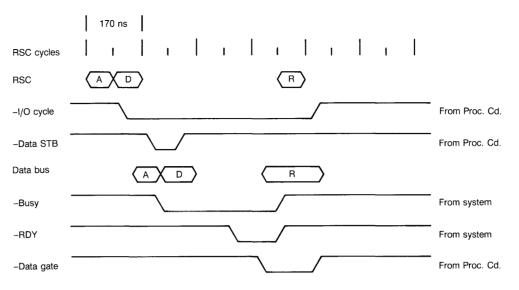

The basic memory-mapped I/O operation involves two types of transfer: request and reply. All operations begin with a request, and replies occur if the operation is a read or a translated write. The requests and replies may be uncoupled from each other, or they may be attached. This is controlled by the slave using handshaking signals. A request consists of address and data. In response to a request from the system processor, the processor channel interface logic outputs address, then asserts DATA STROBE, changes the address to data, removes DATA STROBE, and finally disables its data bus drivers. Address and data are latched on the

Figure 2 Programmed I/O Cycle

positive and negative transitions of DATA STROBE, respectively. If the slave requires a "single envelope" cycle, it may lock the channel by activating the BUSY line. Otherwise, new requests may appear on the interface. A reply to a request may occur either within a single envelope cycle or at some later time. When a reply is available, the READY line is asserted. The processor card responds with a gating signal which is used to enable the slave's drivers onto the interface. The basic PIO cycle is shown in Figure 2.

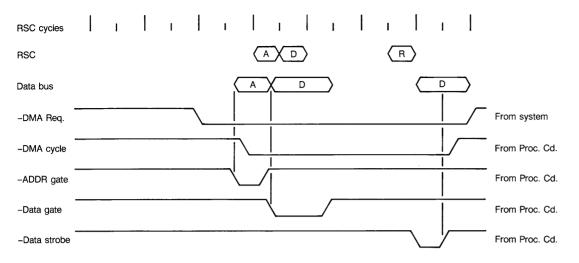

The DMA cycle is managed by the processor card. The system board makes a request, and when able, the processor responds with gating signals used by the system board to gate out the address and data for the transaction. The I/O interface logic generates a request on the internal storage channel and sends a reply (if required) to the system board. Overlapping DMA requests are not performed. The basic DMA cycle is shown in Figure 3. In the RT PC system, the IOCC always causes a single envelope cycle. Accesses to the floating point card, however, may overlap each other or IOCC cycles.

For processor-originated I/O cycles, the maximum transfer rate is approximately 7.8 megabytes per second. Transfers to the system I/O channel are paced by the speed of the I/O channel. Transfers to the floating point card could approach the theoretical maximum, limited primarily by the program doing the transfer. For DMA transfers, the interface supports a transfer rate of about 4 megabytes per second.

The I/O interface is implemented primarily with three bipolar IBM gate arrays, with a total of about 1000 gates.

#### **Test Support**

The processor card provides many functions which aid in the testing of both hardware and software in the RT PC system. These functions are built into the ROMP chip set,

Figure 3 DMA Cycle

and are accessed by simply connecting another computer (currently an IBM PC with special interface card) to the processor card.

The ROMP, MMU, and clock chips were designed to provide easy testability with minimal external hardware. This means that unlike many development systems, no special emulator circuit is required and the physical hardware configuration is not altered for test. This is an especially important advantage for card-level test, as the ROMP processor is soldered on the card and removal is time consuming and inconsistent with high-volume manufacturing.

The support computer, called the ROMP Support Processor, processes commands typed in by the user, sends required signals to the processor card, and displays the internal state of the ROMP and MMU, as well as ROM or RAM memory.

The test features can be divided into three categories based on function provided:

- register display and alter

- · clock control for breakpoints, etc.

- · memory display and alter.

The first set of functions gives display and alter capability for the internal registers and control state of the ROMP. The ROMP provides access to its internal state through its Level-Sensitive Scan Design (LSSD) scan strings (i.e., all registers and latches are connected as shift registers for test purposes). By scanning data into or out of these registers, all of the ROMP's registers may be examined or altered. By scanning certain data into the shift registers and clocking the ROMP, the general-purpose registers may be accessed. Examining the contents of the ROMP's registers does not interfere with what would be the normal processor execution if the Support Processor were not attached (other than requiring the processor to be halted and then restarted), and in fact provides excellent control and visibility into the workings of the processor card and internal chip logic.

The second set of functions provides control of the system; stopping, starting, setting breakpoints, and other functions. Stopping and starting the processor card is done by causing the clock chip to stop or start the ROMP clocks. Breakpoints, which can be specified as either instruction or microcode addresses, are set up by scanning information into the ROMP which causes it to signal via a sync output just prior to executing the instruction or microcode at the indicated address. The clock chip can then stop execution by turning off the ROMP's clocks if a stop on compare has been selected. The sync signal is also available as an output from the ROMP, and is very useful as a trigger event for a logic analyzer. Microcode cycle or instruction stepping is performed by clocking the ROMP for a single machine cycle (for microcode stepping) or until its instruction complete line goes active (for instruction stepping). This provides very accurate visibility into the execution sequence down to the microcode level, if desired.

The third set of functions provides the ability to display and alter memory and internal MMU registers. The MMU provides a serial port to allow memory or register reads and writes to be performed. The serial port is completely separate from the memory interface, and therefore can be used whether or not the ROMP is functional. This provides a good starting point for system debug, since a substantial part of the processor card logic (MMU, ROM, and memory interface) can be checked without the services of the ROMP. Accesses to memory through the serial port do not affect any outstanding memory requests which the MMU may have previously buffered; therefore the system may be stopped, memory displayed, and the system restarted with no effect on normal execution.

The serial port is also used to upload or download programs between memory and PC disk/diskette.

Test features providing stopping plus register and memory display/alter capability are built into the RT PC processor card and are extremely useful for both hardware and software debug. The hardware debug aids are helpful in debugging many software problems which are time critical, branch off to an unknown point, or result in a processor stopped condition (e.g., closely-spaced, multiple program checks).

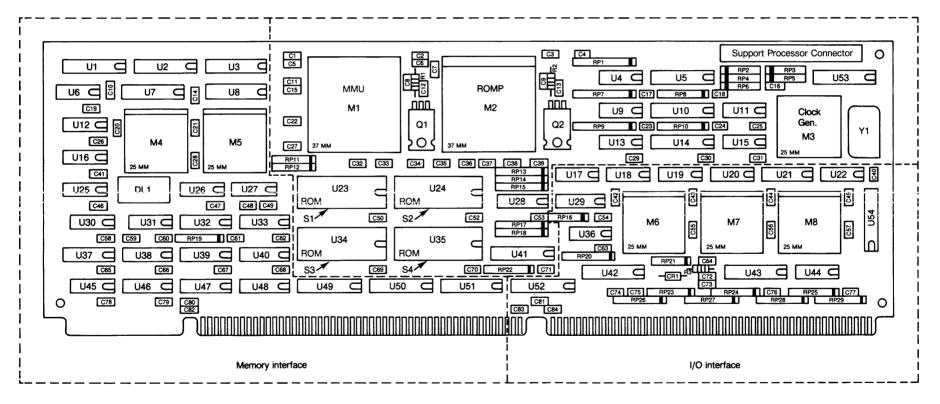

#### **Physical Configuration**

In addition to the ROMP and MMU modules, the 4.5" X 13" card contains six bipolar IBM gate arrays, TTL components (including ROM), and various passive components such as resistors and decoupling capacitors. There are two 100-pin connectors—one for the system board and the floating point accelerator card, and a second which connects to the memory cards. The special test interface is via a 60-pad arrangement on the top of the card, which is gripped by a special connector on the ROMP Support Processor cable. Figure 4 shows the processor card layout. The physical card contains four signal planes plus one ground and one voltage plane.

#### Conclusion

The RT PC packaging and processor card design approach are well suited to responding to future technology developments. The memory cards connect only to the processor card memory interface, permitting the relative timing between the memory and processor to be easily changed as technology improves.

Figure 4 Processor Card Layout

The interface to the system board effectively decouples the processor card from the remainder of the system timing. Thus the processor card performance can be improved without impacting the system design.

#### References

- 1. Ronald E. Rowland "System Memory Cards," *IBM RT Personal Computer Technology*, p. 18.

- Sheldon L. Phelps and John D. Upton, "System Board and I/O Channel for the IBM RT PC System," IBM RT Personal Computer Technology, p. 26.

- D.E. Waldecker, C.G. Wright, M.S. Schmookler, T.G. Whiteside, R.D. Groves, C.P. Freeman, A. Torres, "ROMP/MMU Implementation," *IBM RT Personal Computer Technology*, p. 57.

- 4. Scott M. Smith, "Floating Point Accelerator," *IBM RT Personal Computer Technology*, p. 21.

## System Memory Cards

Ronald E. Rowland

#### Introduction

Each IBM RT PC system memory card contains two independent memory arrays and associated support circuitry. The architecture of these cards provides for full two-way interleaving between the two arrays, with one array containing only even-addressed words and the other containing only odd-addressed words. This on-card interleaving scheme allows for a data word access every 170-nanosecond machine cycle while using industry-standard 150-nanosecond dynamic random access memories (DRAMs). Each data word access consists of 32 data bits and eight error correction code (ECC) bits. The availability of four data bytes every 170 nanoseconds results in a memory interface bandwidth of 23.5 megabytes per second.

The RT PC contains two dedicated slots for the system memory cards. The memory chips are packaged on 1-megabyte and 2-megabyte memory cards which provide for system memory configurations of 1M bytes, 2M bytes, 3M bytes, and 4M bytes. The 1M-byte interleaved ECC memory card design is based upon 64Kx4 DRAM technology while the 2M-byte card uses 256Kx1 DRAM technology.

The hardware architecture allows for cards containing up to 8M bytes of memory per card and for a total system memory addressing capability of 16M bytes. The use of eight ECC bits per data word supports the use of an error correction scheme capable of correcting all single-bit errors, detecting all double-bit errors and detecting the majority of multiple-bit package errors. The architecture also provides a means of automatically identifying the characteristics of the system memory configuration to the remainder of the system.

#### **Memory Card Architecture**

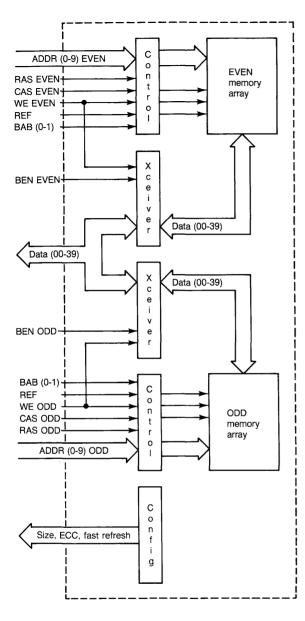

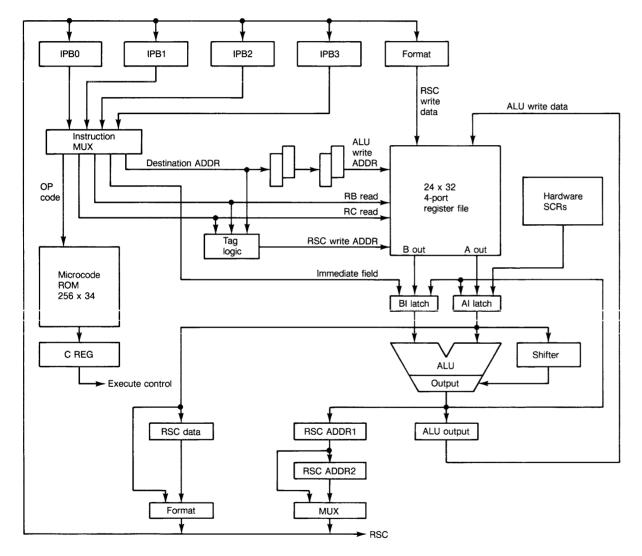

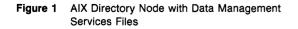

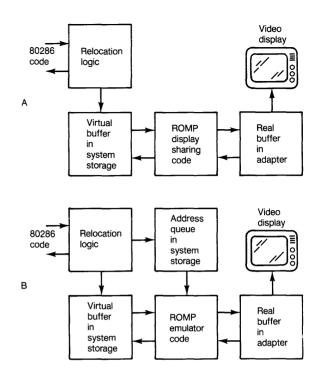

The RT PC system memory card architecture is shown in Figure 1. The card is divided into two independent arrays with each array having its own support circuitry to allow for full two-way interleaving between the arrays. The interleaving between the arrays is performed on a word (32 data bit) boundary. One array is used only for even-addressed word references and the other is used only for odd-addressed word references. The interleaving function is provided on a single memory card, allowing for a system memory configuration utilizing only one memory card and leaving room for memory expansion in the other dedicated memory slot.

The processor card operates on a basic machine cycle of 170 nanoseconds and the processor can cycle each of the memory arrays in two machine cycles. This translates to a memory array cycle time of 340 nanoseconds with one memory reference performed every array cycle. Each memory reference gains access to 32 bits (four bytes) of usable data. Since the two memory arrays on the memory card are independent, the processor card can operate them one machine cycle out of phase with each other in an interleaved fashion. The two-way interleaving allows for a memory reference to occur every machine cycle. The 4-byte data access in combination with the two-way interleaving results in a system memory channel throughput rate of four bytes every 170 nanoseconds (or a 23.5 megabytes per second bandwidth). This memory interface performance is approximately quadrupled over a conventional 16-bit microprocessor system operating at 12 MHz.

The figure shows that the input signals required to control these cards are very similar to a standard DRAM component. The card interface consists of 10 multiplexed address lines (ADDR 0-9), a Row Address Strobe (RAS), a Column Address Strobe (CAS), a Write Enable (WE), and a Bus Enable (BEN) for each array on the card. The 40 data lines (DATA 00-39) are shared by the two arrays. Since the cards were architected to accept various DRAM technologies, two additional Bank Address Bit (BAB) lines and a Refresh (REF) line were added. These additional lines are shared between the two arrays on the card and are only valid when the RAS line for a given array is activated. The BAB lines contain the same information that the high order address lines contain during the column address phase of the memory cycle. This information is required at the beginning of the cycle (during the row address phase) for cards with multiple banks

Figure 1 System Memory Card Logical Dataflow

per array so that the appropriate bank of the array can be activated. The Refresh line is required on these types of cards in order for the on-card logic to refresh the entire array (and not just one of the banks). The RT PC system memory cards are attached to the system processor card via the memory channel. All controls for proper operation of memory read, write, and refresh cycles are provided by the processor card. Since the memory arrays share a common data bus (on the memory interface), the processor card also has the responsibility to ensure that there are no data bus usage conflicts between the two arrays.

#### **DRAM Technology**

Due to the interleaved nature of the card. each card must be able to supply the system with a minimum of 80 bits (32 data bits and 8 ECC bits from each array). When using standard 256Kx1 DRAMs in 16-pin dual inline packages (DIPs) to achieve this minimum, the result is 80 DRAM modules per card. Since the physical card size is approximately 60 square inches (one side), the minimum of 80 256Kx1 DRAM DIPs is also the maximum quantity that can be packaged on one card. Use of this standard packaging technique dictates a memory card capacity of two megabytes (2MB) with 256Kx1 DRAM DIPs. If such a card were to be implemented using standard 64Kx1 DIPs, the resulting card capacity would be 512 kilobytes.

Technical and marketing considerations deemed that a 1M-byte memory card would be necessary for the RT PC system. Since using 256Kx1 DRAM DIPs resulted in a card with a minimum of 2M bytes and using 64Kx1 DRAM DIPs resulted in a card with a maximum of 512K bytes, a new approach was needed. Various packaging methods which would allow doubling the quantity of 64K memory chips on the cards were explored. These alternative techniques included the use of surface-mounted components (SMCs), single in-line packages (SIPs), zigzag in-line packages (ZIPs), and piggy-back modules. Any of these 64K DRAM solutions to the problem would require a total of 160 DRAM chips and the use of a nonstandard packaging technique to achieve the desired 1M byte capacity. The added cost and power requirements of these approaches made them unattractive for production.

The granularity question of how to combine 1M byte of memory, a 32-bit data access. and two-way interleaving on a card with 60 square inches of surface space was resolved by using a new version of the 256K DRAM chip. The answer came in the form of the 64Kx4 DRAM. The 64Kx4 DRAM is a 256K DRAM technology, but it is four bits wide instead of the usual one bit wide arrangement. With the 64Kx4 DRAM the minimum requirement of 80 bits per card could now be accomplished with only 20 DIPs and the 1MB card could be implemented with 40 modules (instead of the 160 required when using a 64K DRAM technology). The 64Kx4 DRAM also provided for a card design with varying capacities. The quantity of DRAM components could now be increased in increments of 20, yielding card capacities of 512K bytes, 1M bytes, 1.5M bytes and 2M bytes. With the merchant DRAM marketplace commanding a price premium for the 64Kx4 over the 256Kx1 DRAMs, it was decided to keep the 2M byte card design based on the 256Kx1 DRAM modules rather than designing it to be an expanded version of the 1M byte card.

#### **Automatic Memory Identification**

The RT PC system memory cards provide information to the processor card and to the system board identifying the system memory configuration. This identification indicates the capacity and functional requirements of the installed memory cards. The information is provided on five static output lines, with three of the five lines identifying a card capacity of 512K bytes, 1M bytes, 2M bytes, 4M bytes, or 8M bytes of memory. Another identification line indicates that the card has an increased refresh requirement allowing the processor card to automatically double the refresh rate. This line was added due to the uncertainty of the refresh requirements for future 1M-bit DRAM technologies.

These identification lines are basically "hardwired" on each memory card and provide the RT PC system with all the information required for proper operation of the installed system memory. This automatic identification mechanism relieves the customer of having to adjust any switch settings whenever the system memory configuration has changed.

These lines are routed to the Memory Configuration Register (MCR) on the system board and to the Memory Management Unit (MMU) on the processor card. The MCR is read by the system software to determine the memory configuration and the MMU uses this information for proper control of the memory. The information and functions provided by this mechanism include determining:

- a. the amount of physical memory installed (on a per card basis),

- b. the physical address range of each card,

- c. whether or not the current memory configuration is a valid one,

- d. whether or not the current memory reference is to a valid physical location,

- e. and if the memory requires a normal or a doubled refresh rate.

#### Summary

The RT PC system memory cards achieve a bandwidth roughly quadruple that of a PC AT. This improvement is the result of employing a full 32-bit data interface and utilizing two-way interleaving. In addition to the 32 data bits, eight ECC bits are provided for correction of all single-bit errors and detection of most multiple-bit errors by the system MMU. The architecture allows for use of any of the common DRAM technologies now in production or envisioned over the next several years. The automatic cardidentification features provide the system with the capability of determining the system memory configuration and relieve the customer of switch setting whenever the configuration is altered.

The cards are somewhat restrictive when trying to maximize their memory capacity using standard DIP type components, due to the physical size of the cards. This limitation can be overcome, however, by using other packaging techniques (SMC, SIP, ZIP, etc.) with 256K DRAMs or with the availability of 1M-bit DRAM technologies. The performance of the system memory interface could be extended beyond the current 23.5 megabytes per second limit by utilizing faster DRAMS in conjunction with a decreased basic machine cycle time. Other alternatives to extending the memory interface performance include using a different interleaving scheme, the addition of a cache, or a combination of the above approaches.

### **Floating Point Accelerator**

Scott M. Smith

#### Introduction

The IBM RT PC Floating Point Accelerator (FPA) is an optional feature which provides significantly enhanced performance for floating point, math-intensive applications. It consists of one 4.5" x 13" circuit board which plugs into a special slot in the RT PC system board. The FPA is based upon the 10 MHz National Semiconductor NS32081 Floating Point Unit (FPU).

Since the NS32081's hardware interface is considerably different than the RT PC internal bus, logic is added to adapt the part to the RT PC. In any such non-native adapter design there is a risk of decreasing performance. Several features are included in the design to minimize and compensate for the potential performance loss. The most significant of these are discussed in this paper. They are: overlapped processing between the system 32-bit microprocessor (ROMP) [1] and the FPA, use of an external register file, and program synchronous exception handling.

Note that while the topic of discussion here is design features which improve floating point accelerator performance, it is difficult to assess the contribution of each feature to overall system performance. That level of analysis is beyond the scope of this paper.

# Overlapped Processing between ROMP and FPA

Before we begin the discussion which is the subject of this section, some background material on the ROMP's use in a floating point environment is needed.

The ROMP itself has no explicit floating point commands. In the base RT PC system, a software floating point emulator provides the floating point arithmetic capabilities. If the customer requires improved floating point performance, the optional FPA may be added to his system. There is a compiler option called "compatible mode" which allows the resulting object code to run on either the emulator or the FPA. The other option, called "direct mode," produces code which will run only with the FPA installed.

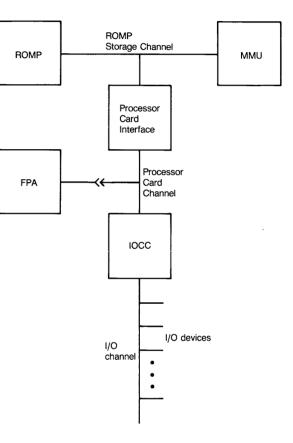

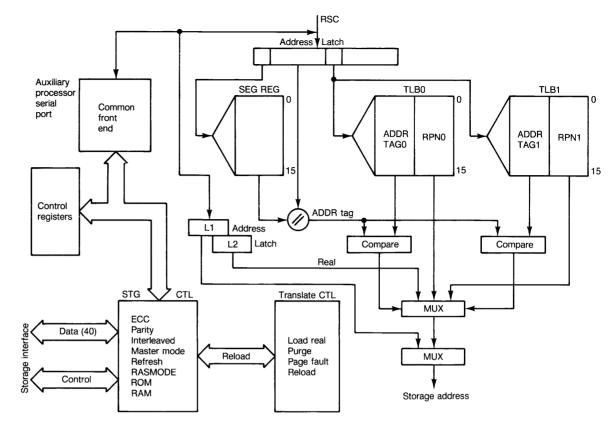

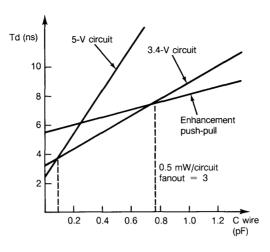

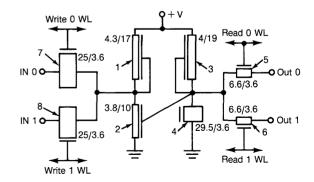

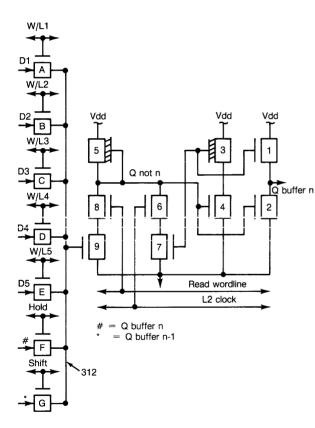

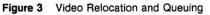

The FPA is attached as a memory-mapped I/O device and its commands are encoded in the address. Specifically, the address is x'FFxxxxx' where 'FF' is the FPA's channel address and 'xxxxxx' is the FPA command. Figure 1 shows a block diagram of the RT PC system and how the FPA is attached to it.

In order to execute an FPA command, the ROMP loads the command (x'FFxxxxxx') into one of its registers. If data is to be sent as part of the command, it is also loaded into a ROMP register. Several ROMP instructions are required to accomplish loading of these registers. The instructions require a minimum

Figure 1 Attachment of Floating Point Accelerator

of 170 nanoseconds each to execute and the memory accesses that they initiate take a minimum of 850 nanoseconds. The command is then sent to the FPA using a ROMP Load or Store command. When the address and (optional) data appear on the ROMP Storage Channel, the Processor Card Interface recognizes the FPA's address and accepts the command. The command is then sent to the FPA over the Processor Card Channel. Depending upon logic delays, 115 to 188 nanoseconds elapse between the address/ command first appearing on the bus and its being strobed to the FPA. The data (if any) will be strobed 242 to 315 nanoseconds from the first appearance of the address. Because the FPU clock is 10 MHz and the ROMP clock is asynchronous, an additional 0 to 100 nanoseconds delay is incurred due to synchronization.

Once the command is received, a reply is returned to the ROMP indicating successful receipt of the command. In the case of commands issued using ROMP Loads, the requested data is also returned in the reply.

If the ROMP were used to drive the NS32081's protocol directly, several such command/reply sequences would be required to execute an FPA command, e.g., Floating Add, Subtract. The ROMP cannot execute the protocol fast enough to avoid significantly degrading the NS32081's performance. Logic is therefore provided on the FPA to execute the NS32081's protocol while receiving only complete floating point commands such as Fadd, Fsub, and Fmul from the ROMP. This logic provides the base mechanism for overlapping ROMP and FPA operation.

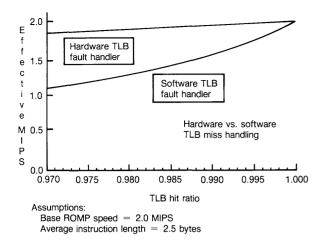

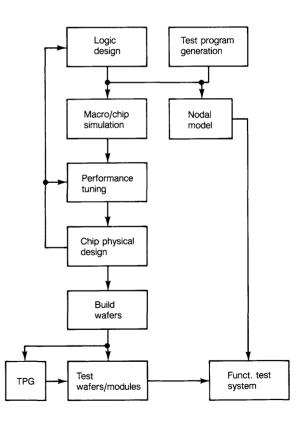

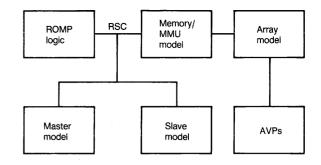

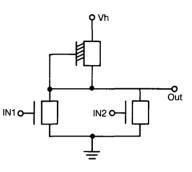

If the reply is sent back to the ROMP early on FPA commands issued by ROMP Stores, the ROMP can continue to do other work such as setting up the next FPA command while the FPA executes the current command. In fact this concept is extended in the FPA to allow it to actually receive the next command from the ROMP while executing the current command.