# Collating List of Pages

This reference drawing contains the collating sequence, page side, and EC level of pages for IBM 3480 Magnetic Tape Subsystem Maintenance Information Manual (MI) Volume A04, SY32-5055-13.

The part number of the divider tab list is 8673746.

This reference drawing is to be placed at the front of the

| manual.            |       | •          |           |               |                        | 2012/ 133              |

|--------------------|-------|------------|-----------|---------------|------------------------|------------------------|

| PAGE               | SIDE  | LEVEL      | PAGE      | SIDE          | LEVEL                  | SDISK 140<br>SDISK 145 |

| FRONT COV          |       | EC C13783  | SPROC Tab |               |                        | SDISK 146              |

| PREF 1             | Back  | EC 336395  |           |               |                        | SDISK 150              |

|                    |       |            | SPROC 1   | Front         | EC A57723              | 20101/ 455             |

| TAB 1              | Front | EC 336395  | SPROC 2   | Back          | EC A57723              | SDISK 155              |

| TAB 2              | Back  | EC 336395  | 22222     |               |                        | SDISK 160              |

|                    |       |            | SPROC 3   | Front         | EC 336395              | EDIEN 465              |

| LGND Tab           |       |            | SPROC 4   | Back          | EC A57723              | SDISK 165<br>SDISK 170 |

| LGND 1             | Front | EC 336395  | SPROC 100 | Front         | EC A57723              |                        |

| LGND 5             | Back  | EC 336395  | SPROC 110 | Back          | EC A57723              | DIAG Tab               |

|                    |       |            |           |               |                        |                        |

| LGND 10            | Front | EC 336396  | SPROC 120 | Front         | EC A57723              | DIAG 1                 |

| LGND 15            | Back  | EC 336396  | SPROC 130 | Back          | EC A57723              | DIAG 2                 |

|                    |       |            |           |               |                        |                        |

| LGND 20            | Front | EC 336395  | SPROC 140 | Front         | EC A57723              | DIAG 3                 |

| LGND 25            | Back  | EC 336395  | SPROC 150 | Back          | EC A57723              | DIAG 4                 |

| LGND 30            | Front | EC 336395  | SDISK Tab |               |                        | DIAG 5                 |

| LGND 35            | Back  | EC 336395  |           |               |                        | DIAG 6                 |

|                    |       |            | SDISK 1   | Front         | EC 336395              |                        |

| LGMD 40            | Front | EC 336395  | SDISK 100 | Back          | EC 336395              | DIAG 7                 |

| LGND 45            | Back  | EC 336395  |           |               |                        | DIAG 20                |

|                    |       |            | SDISK 105 | Front         | EC A57724              |                        |

| LGND 46            | Front | EC 336395  | SDISK 110 | Back          | EC 336395              | DIAG 30                |

| LGND 47            | Back  | EC 336395  |           |               |                        | DIAG 32                |

|                    |       |            | SDISK 111 | Front         | EC 336396              |                        |

| LGND 48            | Front | EC 336396  | SDISK 115 | Back          | EC A57724              | DIAG 34                |

| LGND 50            | Back  | EC 336396  |           |               |                        | DIAG 50                |

|                    |       |            | SDISK 116 | Front         | EC A57724              | <b>5</b> 11.5.5        |

| LGND 55            | Front | EC 336395  | SDISK 120 | Back          | EC 336396              | DIAG 55                |

| LGND 60            | Back  | EC 336395  |           |               |                        | DIAG 60                |

| LONDOR             |       | E 0 000000 | SDISK 121 | Front         | EC 336396              | DIA 0.05               |

| LGND 65            | Front | EC 336396  | SDISK 125 | Back          | EC 336396              | DIAG 65                |

| LGND 70            | Back  | EC 336396  | SDISK 126 | Emant         | EC 225205              | DIAG 66                |

| LGND 75            | Front | EC 336395  | SDISK 130 | Front<br>Back | EC 336395<br>EC 336395 | DIAG 70                |

| LGND 75<br>LGND 80 | Back  | EC 336395  | 3013K 130 | Dack          | EC 330383              | DIAG 100               |

| LOND OU            | Dack  | EC 330383  |           |               |                        | DIAG 100               |

PAGE

SDISK 131

SDISK 135

SIDE

Front

Back

LEVEL

EC 336395

EC 336395

EC 336395

EC A47957

EC A57723

EC 336396

EC 336395

EC 336395

EC A47957

EC 336396

EC A57723

EC A57723

EC A57723

EC 336395

EC A57723

EC A57723

EC A57723

EC 336395

| PAGE                 | SIDE  | LEVEL                  |

|----------------------|-------|------------------------|

|                      |       | EC A57723<br>EC 336395 |

|                      |       | EC A57723<br>EC A57721 |

|                      |       | EC A57723<br>EC A57723 |

| DIAG 114<br>DIAG 118 |       | EC A57723<br>EC A57723 |

| DIAG 120             | Front | EC A57723              |

| DIAG 124             | Back  | EC A57723              |

| DIAG 150             | Front | EC 336395              |

| DIAG 152             | Back  | EC 336395              |

| DIAG 160             | Front | EC 336395              |

| DIAG 162             | Back  | EC 336395              |

| DIAG 164             | Front | EC 336395              |

| DIAG 166             | Back  | EC 336395              |

| DIAG 170             | Front | EC 336395              |

| DIAG 200             | Back  | EC A57693              |

| DIAG 202             | Front | EC A57724              |

| DIAG 204             | Back  | EC A57693              |

| DIAG 206             | Front | EC A57693              |

| DIAG 208             | Back  | EC 336395              |

|                      |       |                        |

1 of 3

3480 | PN 8673721 | EC A57721 | EC A57723 | EC A57724 | EC C13783 27 Oct 88 24 Jul 89 11 May 90 | 30 Sep 91

# **Collating List of Pages**

| PAGE            | SIDE          | LEVEL      | PAGE       | SIDE                                    | LEVEL     | PAGE            | SIDE  | LEVEL     | PAGE    | SIDE  | LEVEL     |

|-----------------|---------------|------------|------------|-----------------------------------------|-----------|-----------------|-------|-----------|---------|-------|-----------|

| DIAG 210        | Eront         | EC 336395  | DIAG 346   | Front                                   | EC 336395 | <b>DIAG 538</b> | Front | EC 336396 | DF Tab  |       |           |

| DIAG 210        | Front<br>Back | EC 336395  | DIAG 348   | Back                                    | EC 336395 | DIAG 540        | Back  | EC 336396 | o. Tab  |       |           |

| DIAG 212        | Dack          | EC 330393  | DIAG 340   | Dack                                    | EC 330393 |                 |       |           | DF 1    | Front | EC A57723 |

| DIAG 214        | Front         | EC 336395  | DIAG 400   | Front                                   | EC A57723 | DIAG 542        | Front | EC 336395 | DF 3    | Back  | EC 336395 |

| DIAG 214        | Back          | EC 457693  | DIAG 402   | Back                                    | EC 336395 | DIAG 544        | Back  | EC 336395 |         | Dack  | EC 330393 |

| DIAG 210        | Dack          | EC 737030  | DING 402   | Ouck                                    | 2000000   |                 |       |           | DF 5    | Front | EC A57723 |

| DIAG 219        | Front         | EC A57693  | DIAG 410   | Front                                   | EC 336396 | DIAG 550        | Front | EC C13783 | DF 10   | Back  | EC 336395 |

| DIAG 220        | Back          | EC 336395  | DIAG 412   | Back                                    | EC 336396 | DIAG 551        | Back  | EC 336395 |         |       | 2000000   |

| 5               |               | 2000000    |            |                                         | 2000000   |                 |       |           | DF 12   | Front | EC A57723 |

| DIAG 222        | Front         | EC 336396  | DIAG 450   | Front                                   | EC 336396 | DIAG 552        | Front | EC 336395 | DF 15   | Back  | EC 336395 |

| DIAG 224        | Back          | EC 336396  | DIAG 452   | Back                                    | EC 336396 | DIAG 554        | Back  | EC C13783 |         |       |           |

|                 |               | 20 000000  |            |                                         |           |                 |       |           | DF 20   | Front | EC 336395 |

| DIAG 226        | Front         | EC 336396  | DIAG 454   | Front                                   | EC 336395 | DIAG 556        | Front | EC 336395 | DF 25   | Back  | EC 336395 |

| DIAG 228        | Back          | EC 336396  | DIAG 460   | Back                                    | EC 336395 | DIAG 558        | Back  | EC 336395 |         |       |           |

| 00 220          |               | 2000000    |            |                                         | 2000000   |                 |       |           | DF 30   | Front | EC 336395 |

| DIAG 229        | Front         | EC 336395  | DIAG 462   | Front                                   | EC 336395 | DIAG 560        | Front | EC 336395 | DF 33   | Back  | EC 336395 |

| DIAG 300        | Back          | EC A57724  | DIAG 500   | Back                                    | EC 336395 | DIAG 562        | Back  | EC 336395 |         |       |           |

| J., (2 000      |               |            |            |                                         | 2000000   |                 |       |           | DF 35   | Front | EC 336395 |

| DIAG 301        | Front         | EC A47957  | DIAG 501   | Front                                   | EC 336395 | DIAG 564        | Front | EC 336396 | DF 36   | Back  | EC A57723 |

| DIAG 302        | Back          | EC A47957  | DIAG 502   | Back                                    | EC 336395 | DIAG 566        | Back  | EC 336396 |         |       |           |

| 51110 002       | Dack          | 20 /14/00/ | 51710 002  | Duck                                    | 2000000   |                 |       |           | DF 37   | Front | EC A57723 |

| DIAG 304        | Front         | EC 336395  | DIAG 503   | Front                                   | EC 336396 | <b>DIAG 568</b> | Front | EC 336395 | DF 40   | Back  | EC 336395 |

| DIAG 306        | Back          | EC 336395  | DIAG 504   | Back                                    | EC 336396 | DIAG 570        | Back  | EC 336395 |         |       | 2000000   |

| 5               | Dack          | 2000000    | 21110 004  | Dack                                    | 2000000   |                 |       |           | DF 45   | Front | EC A57724 |

| DIAG 308        | Front         | EC 336395  | DIAG 506   | Front                                   | EC 336395 | DIAG 572        | Front | EC 336395 | DF 50   | Back  | EC 336395 |

| DIAG 310        | Back          | EC 336395  | DIAG 508   | Back                                    | EC 336395 | DIAG 574        | Back  | EC 336395 |         |       | 20 300000 |

| Bii (C C 10     | Dack          | 20 000000  | 21712 000  | 2.30                                    |           |                 |       |           | DF 55   | Front | EC 336395 |

| DIAG 312        | Front         | EC 336395  | DIAG 509   | Front                                   | EC 336395 | DIAG 576        | Front | EC 336395 | DF 60   | Back  | EC A57721 |

| DIAG 320        | Back          | EC 336395  | DIAG 510   | Back                                    | EC 336395 | DIAG 578        | Back  | EC 336395 |         |       | 207107721 |

| 5170 323        | Dack          | 20 000000  | DIAC 310   | Dack                                    | 2000000   |                 |       |           | DF 62   | Front | EC 336395 |

| DIAG 321        | Front         | EC 336396  | DIAG 511   | Front                                   | EC 336395 | DIAG 580        | Front | EC 336396 | DF 65   | Back  | EC 336395 |

| DIAG 322        | Back          | EC 336396  | DIAG 512   | Back                                    | EC 336395 | DIAG 582        | Back  | EC 336396 |         |       |           |

| 5               | Dack          | 2000000    | 51,100,12  | • • • • • • • • • • • • • • • • • • • • | 2000000   |                 |       |           | DF 70   | Front | EC 336396 |

| DIAG 323        | Front         | EC 336396  | DIAG 514   | Front                                   | EC 336395 | DIAG 584        | Front | EC 336395 | DF 75   | Back  | EC 336396 |

| DIAG 324        | Back          | EC 336396  | DIAG 516   | Back                                    | EC 336395 | DIAG 586        | Back  | EC 336395 |         |       |           |

| 0.710 021       | Dack          | 2000000    | 2., (2.0.0 | Daon                                    | 2000000   |                 |       |           | DF 80   | Front | EC 336395 |

| DIAG 326        | Front         | EC 336395  | DIAG 518   | Front                                   | EC 336395 | DIAG 600        | Front | EC A57723 | DF 82   | Back  | EC 336395 |

| DIAG 328        | Back          | EC 336395  | DIAG 520   | Back                                    | EC 336395 | DIAG 605        | Back  | EC 336396 |         |       |           |

| 510 020         | Dack          | 2000000    | 517,0 020  | Dan                                     | 2000000   |                 |       |           | DF 85   | Front | EC 336395 |

| DIAG 330        | Front         | EC 336395  | DIAG 522   | Front                                   | EC 336396 | DIAG 610        | Front | EC 336395 | DF 88   | Back  | EC A57723 |

| DIAG 332        | Back          | EC 336395  | DIAG 524   | Back                                    | EC 336396 | DIAG 615        | Back  | EC 336395 |         |       | 207101720 |

|                 | - 20.1        | 2000000    |            |                                         |           |                 |       |           | DF 88-1 | Front | EC A57723 |

| <b>DIAG 334</b> | Front         | EC 336395  | DIAG 526   | Front                                   | EC 336395 | DIAG 620        | Front | EC 336395 | DF 88-2 | Back  | EC A57723 |

| DIAG 336        | Back          | EC 336395  | DIAG 528   | Back                                    | EC 336395 | DIAG 720        | Back  | EC A57723 |         |       |           |

|                 |               |            |            | _ ~~.,                                  |           |                 |       |           | DF 90   | Front | EC 336395 |

| DIAG 338        | Front         | EC 336395  | DIAG 530   | Front                                   | EC 336395 | DIAG 721        | Front | EC A47957 | DF 95   | Back  | EC 336395 |

| DIAG 340        | Back          | EC 336395  | DIAG 532   | Back                                    | EC 336395 | DIAG 722        | Back  | EC 336396 |         | •     |           |

| · <del>-</del>  |               |            |            |                                         |           |                 |       |           | DF 100  | Front | EC 336395 |

| DIAG 342        | Front         | EC 336395  | DIAG 534   | Front                                   | EC 336395 | DIAG 725        | Front | EC A57693 | DF 105  | Back  | EC 336395 |

| DIAG 344        | Back          | EC 336395  | DIAG 536   | Back                                    | EC 336395 | DIAG 755        | Back  | EC 336395 |         |       |           |

PN 8673721 2 of 3

EC A57721 EC A57723 EC A57724 EC C13783 27 Oct 88 24 Jul 89 11 May 90 30 Sep 91

Reference Drawing A04-2

| Collating | List of | <b>Pages</b> |

|-----------|---------|--------------|

|-----------|---------|--------------|

| PAGE             | SIDE          | LEVEL                  | PAGE       | SIDE           | LEVEL       |

|------------------|---------------|------------------------|------------|----------------|-------------|

| DF 110<br>DF 115 | Front<br>Back | EC 336395<br>EC 336395 | OPER 95    | Back           | EC A57693   |

|                  |               |                        | OPER 96    | Front          | EC 336395   |

| DF 117           | Front         | EC 336395              | OPER 100   | Back           | EC A57723   |

| DF 120           | Back          | EC A57723              |            |                |             |

| DF 120           | Dack          | EC AST LO              | OPER 105   | Front          | EC 336395   |

| DF 125           | Front         | EC 336395              | OPER 106   | Back           | EC 336395   |

| DF 130           | Back          | EC 336395              | O. 21. 100 | <i>D</i> .,, o | 2000000     |

| DF 130           | Dack          | EC 330333              | OPER 110   | Front          | EC 336395   |

| DF 135           | Front         | EC 336395              | OPER 115   | Back           | EC A57693   |

| DF 140           | Back          | EC 336396              | 01211710   | Discin         | 20 710,000  |

| DF 140           | Dack          | 2000000                | OPER 120   | Front          | EC 336396   |

| DE 44E           | Front         | EC 336396              | OPER 125   | Back           | EC 336396   |

| DF 145           |               | EC 336395              | OI LIV 123 | Dack           | LC 330330   |

| DF 150           | Back          | EC 320393              | ODER 120   | Eroot          | EC 336395   |

| 55.455           |               | E 0 000005             | OPER 130   | Front          |             |

| DF 155           | Front         | EC 336395              | OPER 131   | Back           | EC 336395   |

| DF 160           | Back          | EC A57721              | 0050 405   | <b>5</b> t     | F.C. 00000F |

| <b>-</b> .       |               |                        | OPER 135   | Front          | EC 336395   |

| OPER Tab         |               |                        | OPER 140   | Back           | EC 336395   |

|                  |               |                        | 0050444    |                | E 0 00000E  |

| OPER 1           | Front         | EC 336395              | OPER 141   | Front          | EC 336395   |

| OPER 2           | Back          | EC A47957              | OPER 142   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 5           | Front         | EC 336396              | OPER 145   | Front          | EC 336395   |

| OPER 10          | Back          | EC A57721              | OPER 150   | Back           | EC 336395   |

|                  |               |                        |            | _              |             |

| OPER 15          | Front         | EC 336395              | OPER 155   | Front          | EC A57723   |

| OPER 20          | Back          | EC A57723              | OPER 160   | Back           | EC 336395   |

|                  |               |                        |            | _              |             |

| OPER 25          | Front         | EC A57693              | OPER 165   | Front          | EC A57723   |

| OPER 30          | Back          | EC A57693              | OPER 170   | Back           | EC A57723   |

|                  |               |                        |            |                |             |

| OPER 35          | Front         | EC 336395              | OPER 175   | Front          | EC 336395   |

| OPER 40          | Back          | EC 336395              | OPER 180   | Back           | EC 336395   |

|                  |               |                        | _          |                | _           |

| OPER 45          | Front         | EC 336396              | OPER 185   | Front          | EC 336395   |

| OPER 50          | Back          | EC 336396              | OPER 186   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 55          | Front         | EC 336396              | OPER 187   | Front          | EC 336395   |

| OPER 60          | Back          | EC 336396              | OPER 188   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 65          | Front         | EC 336395              | OPER 190   | Front          | EC 336395   |

| OPER 70          | Back          | EC 336395              | OPER 196   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 75          | Front         | EC 336395              | OPER 200   | Front          | EC 336395   |

| OPER 80          | Back          | EC 336395              | OPER 205   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 81          | Front         | EC 336396              | OPER 210   | Front          | EC 336395   |

| OPER 85          | Back          | EC C13783              | OPER 215   | Back           | EC 336395   |

|                  |               |                        |            |                |             |

| OPER 90          | Front         | EC A57723              | OPER 220   | Front          | EC A57723   |

| PAGE                 | SIDE          | LEVEL                  |

|----------------------|---------------|------------------------|

| OPER 230             | Back          | EC A57723              |

| OPER 240<br>OPER 245 | Front<br>Back | EC A57693<br>EC A47957 |

| RCF-1<br>RCF-2       | Front<br>Back |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

|                      |               |                        |

| EC A57721 EC A57723 EC A57724 EC C13783 27 Oct 88 24 Jul 89 11 May 90 30 Sep 91 |  |

|---------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------|--|

Reference Drawing A04-3

m;

# **PUBLICATIONS REFERENCE DRAWING**

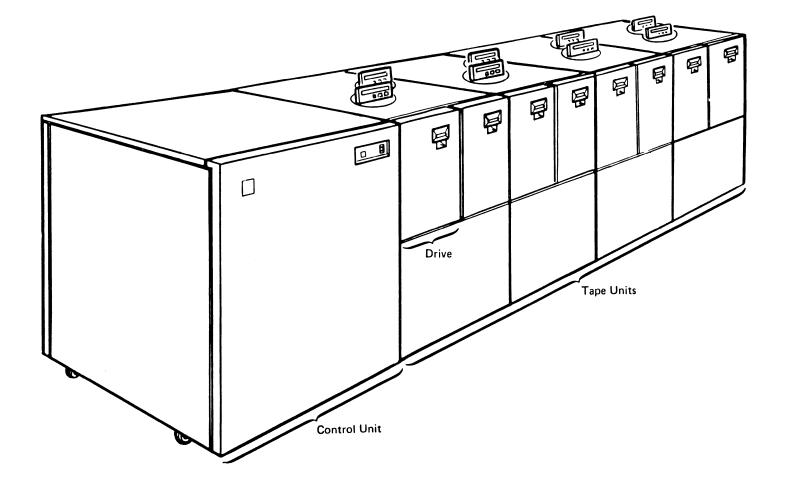

MACHINE TYPE/MODEL NO. 3480

MACHINE NAME - Magnetic Tape Subsystem

| FORM NO.     | E C NO. | DESCRIPTION/COMMENTS                                                                           |

|--------------|---------|------------------------------------------------------------------------------------------------|

| SY32-5055-0  | 991552  | VOL. A04 - Maintenance Information<br>REA 12-11655                                             |

|              | 336326  | TNL SN32-0310<br>IEC 001122571 (REA 12-25744)<br>IEC 002122571 (REA 12-25494,<br>REA 12-25496) |

| SY32-5055-1  | 336389  | Second Edition<br>IEC 0011215156<br>IEC 0011225996                                             |

| SY32-5055-2  | 336390  | Third Edition<br>IEC 0011225997<br>IEC 0011215157                                              |

| SY32-5055-3  | 336391  | Fourth Edition REA 77-11223 IEC 0011215158 IEC 0011215159 IEC 0011225842 IEC 0011225843        |

| SY32-5055-4  | 336392  | Fifth Edition<br>IEC 0011225998<br>IEC 0011228481                                              |

|              | 336393  | TNL SN32-5036                                                                                  |

| SY32-5055-5  | 336394  | Sixth Edition                                                                                  |

| SY32-5055-6  | 336395  | Seventh Edition<br>IEC 0011225844                                                              |

| SY32-5055-7  | 336396  | Eighth Edition<br>IEC 0011222986                                                               |

| SY32-5055-8  | A47957C | Ninth Edition                                                                                  |

| SY32-5055-9  | A57693  | Tenth Edition                                                                                  |

| SY32-5055-10 | A57721  | Eleventh Edition                                                                               |

| SY32-5055-11 | A57723  | Twelfth Edition                                                                                |

| SY32-5055-12 | A57724  | Thirteenth Edition                                                                             |

| SY32-5055-13 | C13783  | Fourteenth Edition                                                                             |

|        | IBI            | VI             | ·       | DATE             | CHANGE NO   |        | DATE  | CHANGE NO |     |

|--------|----------------|----------------|---------|------------------|-------------|--------|-------|-----------|-----|

| NAME.  | <b>PUB REF</b> | DWG (PRD)      | REL     | See EC           | History     |        |       |           | 1 _ |

|        |                | ·              |         | .7/24/89         | A57723      |        |       |           | 86  |

| DESIGN |                | SHT OF         |         | 5/11/90          | A57724      |        |       |           | 74( |

| DETAIL |                |                |         | 9/30/91          | C13783      |        |       |           | 065 |

| CHECK  |                | CLASSIFICATION | MUST CO | ONFORM TO ENG SP | EC DEVELOPM | ENT NO | LOGIC | PG NO     | O,  |

| APPRO  |                |                |         |                  |             |        | RD00  | 4         | B   |

# **Maintenance Information**

3480 S/N-

3480 S/N-Maintenance Information GLOSS PLAN INTRO \*START\* CART PNEU MSG INST INSP INDEX Vol A01

3480 S/N-Maintenance Information PWR SENSE PANEL LOC CARR-CU Vol A02

3480 S/N-Maintenance Information CARR-DR Vol A03

3480 S/N-Maintenance Maintenance Information Information LGND SPROC SDISK DIAG OPER Vol A04 Vol A05

**Maintenance Library** Maintenance Information **Logic Diagrams**

**Vols. A01 to A05** Vols. C01 and D01

3480 Magnetic Tape Subsystem

### Preface

This manual contains maintenance information about the IBM 3480 Magnetic Tape Subsystem and is intended for customer engineers responsible for servicing the 3480 tape subsystem. This publication is designed to be used with the IBM Maintenance Device (MD). Therefore, CEs using this manual should be familiar with that tool.

### Prerequisite Knowledge

It is assumed that you have a background in data processing concepts and that you are familiar with the hexadecimal numbering system, stored program concepts, and have a basic understanding of tape subsystems and their relationship to a processor I/O channel.

### **Related Publications**

IBM System/360 and System/370 I/O Interface Channel to Control Unit Original Equipment Manufacturers' Information, GA22-6974.

IBM 3480 Magnetic Tape Subsystem Description, GA32-0042.

# How to Update the Maintenance Information

This manual is form number controlled. The 3480 manuals will be updated by Technical Newsletters (TNLs). The TNL cover letter will indicate the new EC level. The entire manual will be updated by major revision. All updates are processed through normal MLC control. The Publications Reference Drawing (PRD) in the front of each volume contains the EC history.

### Preface PREF 1

### How to Order This Manual

This manual or pages can be ordered from one of the following:

- United States

- Europe/Middle East/Asia (E/ME/A)

- Americas/Far East (A/FE)

Use the wiring Diagram/Logic Page Request form, Z150-0130. Be sure to include the form number of the manual when ordering the new manual or pages. Please write your telephone number on the form in case there are any questions regarding your order.

### United States

IBM Corporation

General Products Division

Dept. 30L

Tucson, Arizona 85744

### E/ME/A

International Business Machines S.A.E., Division de Fabricacion Dept. 9290 Valencia, Spain

### A/FE

IBM Argentina SA Dept. 020 H. Yrigoyen 2149 1640 Martinec, Pcia. Buenos Aires Republic of Argentina

### Tab List

### Volume A01

GLOSS

Glossary

PLAN

Maintenance Plan

3480 Introduction

INTRO

Start Maintenance

START

Cartridge Analysis

PNEU

Pneumatic Analysis

MSG

Console Messages and EREP

INST

Installation/Removal

Safety Check Procedures

INSP

Index

### Volume A05

FSI

Fault Symptom Index

EAD

Error Analysis Diagrams

### Volume A02

PWR

R Power Maps

SENSE

PANEL Panel

MD

Maintenance Device

LOC

Locations

Sense/Status

CARR-CU Control Unit

Checks/Adjustments/Removal/Replacement

### Volume A03

CARR-DR Drive Checks/Adjustments/Removal/Replacement

### Volume A04

LGND Le

ID Legend

SPROC Support Procedures

SDISK

Support Diskette Procedures

Tab List TAB 1

DIAG

Support Diagnostic Descriptions

Data Fields and Registers

DF OPER

Theory of Operation

**3480 MI** EC336395 © Copyright IBM Corp. 1984, 1985, 1986

### Contents

Graphic Symbols and Lines

5

Keys

5

Connectors

5

Bus and Control Lines

5

Identifying Parts

10

Control Unit Location Area Definitions

15

Tape Unit and Drive Location Area Definitions

35

Error Analysis Diagram Logic Blocks

55

Logic Diagrams

60

Card Location Charts

60

Card Plug Lists

60

Multiple Logic Diagrams for One Card

60

Sample Logic Diagram

65

Bundled Lines

70

Logical/Physical Pins

70

Dot OR's of Output Lines

75

Field Wire Net Lists

80

Pin to Net List

80

Net to Pin List

80

Voltage Distribution List

80

Contents LGND 1

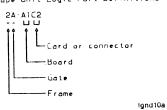

### **Graphic Symbols and Lines**

### Keys

### **Primary Key**

Reverse number in a black square. Used in text and diagrams.

### Secondary Key

Reverse letter in black circle. Used in text when keying to a test point symbol in a diagram.

### Connectors

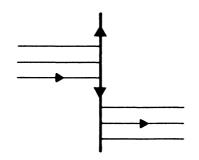

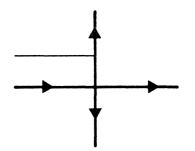

### **On-Page Connectors**

Connection between parts of the same diagram. Arrows point to remote connectors and indicate flow direction of the line.

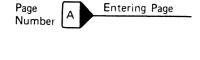

### **Off-Page Connectors**

Connection between diagrams on separate pages. Letter keys are used to identify corresponding points.

### **Bus and Control Lines**

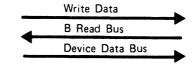

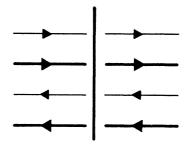

### Minor Bus Lines

### Major Bus Line

#### **Control Lines**

Bus or cable with multiple control lines entering and exiting.

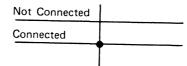

Bus and control lines that connect to a bus.

Bus and control lines that do not connect to a bus.

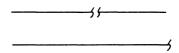

Standard line break, used when a line break is needed.

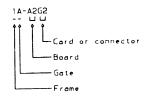

### **Identifying Parts**

Two different formats are used in the maintenance information (MI) and logic diagrams to represent the unit that a part is located.

### **Examples of the First Format:**

1A-A1H4 1A-A1D2-U06 1A-A1E2-W22 1A-A2G2 2A-A1C2

Control Unit Logic Part Definitions

Tape Unit Logic Part Definitions

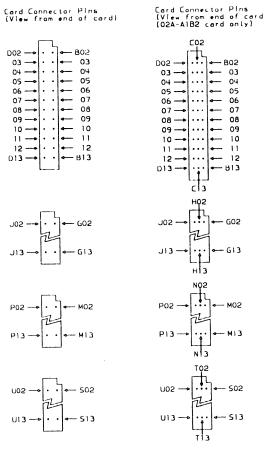

### Logic Board Card Pin Position Identifiers

Logic card and board pin U06 of the 1A-A1D2 board position (this is the pin connection between the logic board and the logic card bottom card connector (BCC) or other connector in that position.

### Logic Board Card Pin Position Identifiers

Logic card top card connector (TCC) pin

W22 for the logic card in position

1A-A1E2 (the TCC is a card to card

connector located on the non-pin side

of the card and provides for card to

card connections or a single wide TCC

connects TCC card pins within a card.

3480 MI

© Copyright IBM Corp. 1984, 1985; 1986, 1987

### Ignd 10b

# Top card connector (TCC) pins (View from the top of the card)

### **Examples of the Second Format:**

| 1A-T1A1         | TU-D1-PA-J1-D12   |

|-----------------|-------------------|

| 1A-T1A3Y        | TU-D0/D1-A1-C1B11 |

| 2A-A1Z2         | TU-D0/D1-P1-3     |

| 1A-A2Y2         | TU-D0/D1-DK-P7-4  |

| CU-P2A4         | TU-D0-EL-J7-1     |

| CU-PS-01-J1-3   | TU-D1-DSP-P1-D11  |

| CU-L/R-P2-2     | TU-PS-01-P11-3    |

| CU-A1-TB3-6     | TU-PS1-J2-9       |

| CU1AP1-3        | TU-D0-P1-WA2-D05  |

| TU-D0-PA-J1-D12 | TU-D1-A1-A2-B12   |

### **Subsystem Unit Identifiers**

| 1A | Control unit |

|----|--------------|

| CU | Control unit |

| 2A | Tape unit    |

| TU | Tape unit    |

### **Tape Drive Unit Identifiers**

For subsystems unit with identifiers of TU or 2A only.

TU-D1.... TU-D0/D1 TU-D0/D1 ---2A-D0/D1

TU-D0....

### Legend LGND 10

(when no D0 or D1) 2A-... --or The next numbers are the functional TU-... area within the tape unit, not the individual drives within the tape unit. Drive 0 - the remaining numbers pertain TU-D0-.. to FRUs or parts in drive 0. Drive 1 - the remaining numbers pertain TU-D1-.. to FRUs or parts in drive 1. Drive 0/1 - the remaining numbers TU-D0/D1-.. pertain to FRUs or parts in both drive 0 and drive

### **Logic Location Area Identifiers**

| 1A-T1A1   | TU-DO/D1-A1        |

|-----------|--------------------|

| CU-P2A4   | <br>TU-D0/D1-P1-P1 |

|           |                    |

| CU-PS-01  | TU-DO/D1-DK        |

| CU-L/R-P2 | TU-D1-DSP          |

|           |                    |

| CU-A1-TB3 | TU-PS-01           |

|           | TU-D0-P1-WA2       |

| TU-DO-MSG | 1U-UU-F1-WAZ       |

|           |                    |

**Note:** For descriptions, locations, and remove/replace procedures for the location area identifiers, see the following for:

- Control unit "Figure 1. Control Unit Location Area Definitions"

- Tape unit and tape drives "Figure 2. Tape Unit and Drives Location Area Definitions"

#### **Part Location Identifiers**

| CU-PS-01-J1-3     | (pin 3 of connector J1)    |

|-------------------|----------------------------|

| CU-L/R-P2-2       | (pin 2 of connector P2)    |

| TU-DO/D1-A1-C1B11 | (pin B11 of position C1)   |

| TU-PS-01-P11-3    | (pin 3 of connector P11)   |

| TU-PS1-J2-9       | (pin 9 of connector J2)    |

| TU-D0-P1-WA2-D05  | (pin DO5 of connector WA2) |

The following figures show how to locate parts in the 3480 documentation, using the identifying numbers that are shown in "Examples of the Second Format" on LGND 10.

For the part location area that is used in the logics, the figures show where they are located in the 3480 subsystem by referencing the "Table of Contents" entry in the LOC and CARR sections of the Maintenance Information. The LOC and CARR sections "Table of Contents" may not be the exact name or FRU number of the part referenced in the logic, however the page referenced by the "Table of Contents" will relate to the part you are looking for.

These figures also show where a part can be found in the logics. For example, if the power is suspected to be a problem, you can look for power parts (CBs, Power Supplies, and so forth) and find the logic pages that show these areas.

### **Control Unit Location Area Definitions**

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER | DESCRIPTION                                    | LOGIC<br>PAGE               | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE  | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

|-----------------------------------------|------------------------------------------------|-----------------------------|------------------------------------------|------------------------------------------|

| 1AP1                                    | Connectors<br>for gate fans                    | YF005                       | Fan Assemblies<br>1 and 2                | FRU165                                   |

| +24v<br>Service<br>Switch               | Service switch                                 | ZT020                       | CU—Al Logic Gate<br>(Hinge Side)         | FRU162                                   |

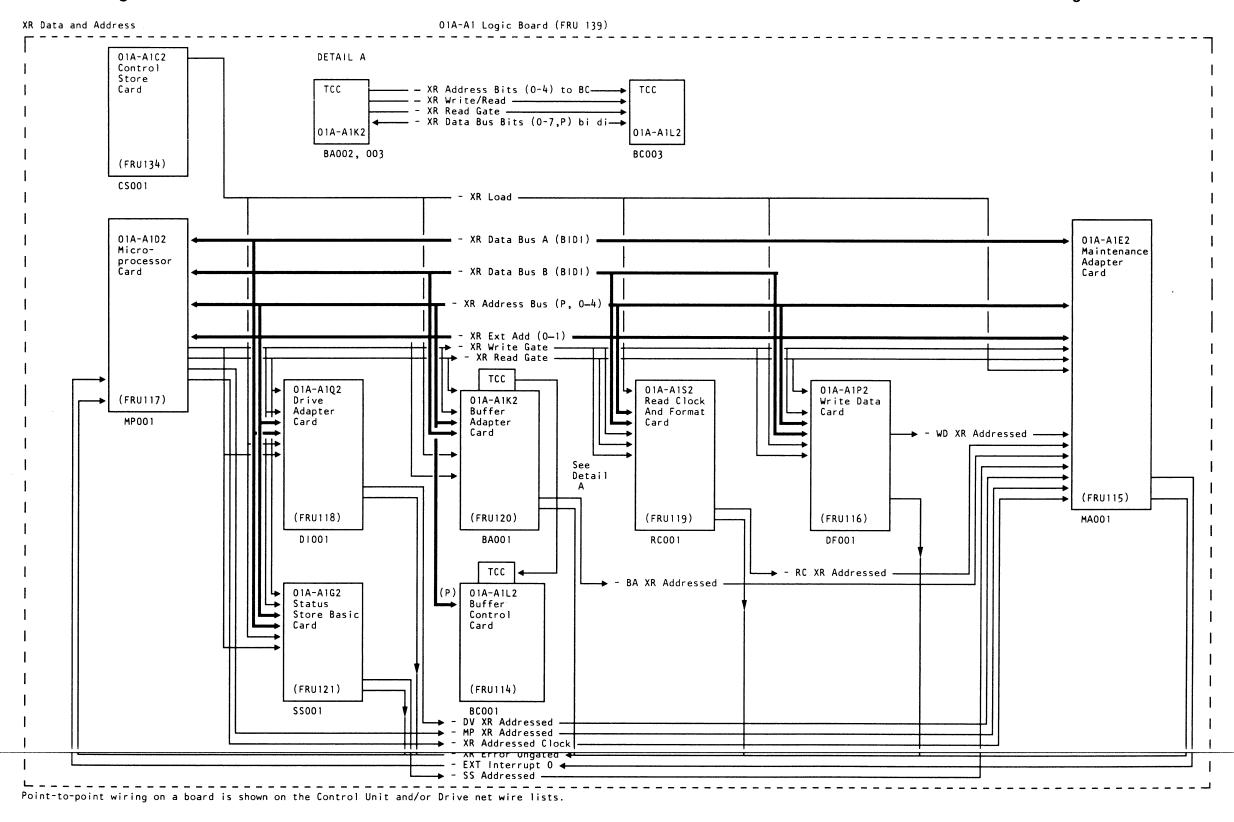

| A1                                      | Logic board                                    | AA000<br>AA100              | 01A-A1 Logic Board                       | FRU139                                   |

| A1A2                                    | Logic board<br>position A2                     | AA000                       | 01A-A1 Logic Board                       | FRU139                                   |

| A1Y2                                    | Logic board<br>connector Y2 at<br>top of board | AA000                       | 01A-A1 Logic Board                       | FRU139                                   |

| A1Z2                                    | Logic board<br>connector at<br>bottom of board | AA000                       | 01A-A1 Logic Board                       | FRU139                                   |

| A1P2Y                                   | Single wide TCC<br>board position P2<br>row y  | AA001                       | OlA-Al Top Card<br>Connectors and Cables | FRU181                                   |

| Alycde                                  | TCC row Y<br>across board<br>positions C-E     | AA000                       | 01A-A1 Top Card<br>Connectors and Cables | FRU193                                   |

| A1ZFG                                   | TCC row Z<br>across board<br>positions F-G     | AA000                       | 01A-A1 Top Card<br>Connectors and Cables | FRU187                                   |

| A2                                      | Logic board                                    | AA001<br>AA200              | 01A-A2 Logic Board                       | FRU140                                   |

| A2A2                                    | Logic board<br>position A2                     | AA001                       | 01A-A2 Logic Board                       | FRU140                                   |

| A2C2W                                   | Single wide TCC<br>board position C2<br>row W  | AA001<br>CA002<br>WA005/006 | 01A-A2 Top Card Cables                   | FRU170                                   |

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER | DESCRIPTION                                           | LOGIC<br>PAGE               | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

|-----------------------------------------|-------------------------------------------------------|-----------------------------|-----------------------------------------|------------------------------------------|

| A2C2W22                                 | Single wide TCC<br>board position C2<br>row W, pin 22 | AA001<br>CA002<br>WA005/006 | 01A-A2 Top Card Cables                  | FRU170                                   |

| A2Y2                                    | Logic board<br>connector Y2 at<br>top of board        | AA001                       | 01A-A2 Top Card Cables                  | FRU140                                   |

| A2Z2                                    | Logic board<br>connector Z2 at<br>bottom of board     | AA001                       | 01A-A2 Top Card Cables                  | FRU140                                   |

| Diskette<br>Drive                       | Diskette drive                                        | WZ001/002                   | Operator Set Up Panel                   | FRU086                                   |

| Fans<br>(Gate)                          | Gate fans                                             | YF005                       | Fan Assembly 1<br>Fan Assembly 2        | FRU150<br>FRU151                         |

| L/R                                     | Local/remote<br>power panel                           | YF020                       | Operator Set Up Panel                   | FRU084                                   |

| -J1                                     | Connector                                             | YF020                       | Operator Set Up Panel                   |                                          |

| -J2                                     | Connector                                             | YF020                       | Operator Set Up Panel                   |                                          |

| Local<br>Power<br>Enable                | Local power<br>enable                                 | YF020                       | Operator Set Up Panel                   |                                          |

| MD<br>Connector                         | CU connector for MD attachment                        | WX001                       | MD Connector                            | FRU169                                   |

| 0P                                      | Operator panel                                        |                             | Operator Set Up Panel                   | FRU142                                   |

| -J1/J2                                  | Connector                                             | WZ106                       |                                         |                                          |

| -J2/P2                                  | Connector                                             | WZ106                       |                                         |                                          |

| -J5                                     | Connector                                             | YF015<br>WZ106              | Operator Set Up Panel                   | FRU142                                   |

| -Power<br>On-<br>Indicator              | Power on<br>indicator                                 | YF015                       | Operator Set Up Panel                   | FRU142                                   |

| -(Sub)<br>System<br>Power<br>Switch     | (Sub) system<br>power switch                          | YF015                       | Operator Set Up Panel                   | FRU142                                   |

| -UEPO<br>Switch                         | UEPO switch                                           | YF015                       | Operator Set Up Panel                   | FRU198                                   |

Legend

### **Control Unit Location Area Definitions (Continued)**

|                                               | <del></del>                             |                    |                                         | r                                        |

|-----------------------------------------------|-----------------------------------------|--------------------|-----------------------------------------|------------------------------------------|

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER       | DESCRIPTION                             | LOGIC<br>PAGE      | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

| OSU                                           | Operator<br>(controller)<br>setup panel |                    | Operator Set Up Panel                   | FRU141                                   |

| -''A''<br>Channel<br>Type<br>(Mode)<br>Switch | Channel type<br>(mode) switch           | WZ 102             | Operator Set Up Panel                   | FRU141                                   |

| -"B"<br>Channel<br>Type<br>(Mode)<br>Switch   | Channel type<br>(mode) switch           | WZ 102             | Operator Set Up Panel                   | FRU141                                   |

| -"C"<br>Channel<br>Type<br>(Mode)<br>Switch   | Channel type<br>(mode) switch           | WZ 104             | Operator Set Up Panel                   | FRU141                                   |

| -Channel A<br>Disable<br>Indicator            | Channel disable<br>indicator            | YF010<br>(Sheet 1) | Operator Set Up Panel                   | FRU141                                   |

| -Channel A<br>Enable/<br>Disable<br>Switch    | Channel<br>enable/disable<br>switch     | YF010<br>(Sheet 2) | Operator Set Up Panel                   | FRU141                                   |

| -Channel B<br>Disable<br>Indicator            | Channel disable indicator               | YF010<br>(Sheet 1) | Operator Set Up Panel                   | FRU141                                   |

| -Channel B<br>Enable/<br>Disable<br>Switch    | Channel<br>enable/disable<br>switch     | YF010<br>(Sheet 2) | Operator Set Up Panel                   | FRU141                                   |

| -Channel C<br>Disable<br>Indicator            | Channel disable indicator               | YF010<br>(Sheet 1) | Operator Set Up Panel                   | FRU141                                   |

| -Channel C<br>Enable/<br>Disable<br>Switch    | Channel<br>enable/disable<br>switch     | YF010<br>(Sheet 2) | Operator Set Up Panel                   | FRU141                                   |

| -Channel D<br>Disable<br>Indicator            | Channel disable<br>indicator            | YF010<br>(Sheet 1) | Operator Set Up Panel                   | FRU141                                   |

| -Channel D<br>Enable/<br>Disable<br>Switch    | Channel<br>enable/disable<br>switch     | YF010<br>(Sheet 2) | Operator Set Up Panel                   | FRU141                                   |

# Legend LGND 20

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER     | DESCRIPTION                   | LOGIC<br>PAGE                         | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

|---------------------------------------------|-------------------------------|---------------------------------------|-----------------------------------------|------------------------------------------|

| -CUO/CU1<br>Switch                          | CUO/CU1 switch                | YF010                                 | Operator Set Up Panel                   | FRU197                                   |

| -CU ''A''<br>Address<br>Switch              | Channel address<br>switch     | WZ102                                 | Operator Set Up Panel                   | FRU197                                   |

| -CU ''B''<br>Address<br>Switch              | Channel address<br>switch     | WZ 102                                | Operator Set Up Panel                   | FRU197                                   |

| -CU ''C''<br>Address<br>Switch              | Channel address<br>switch     | WZ 104                                | Operator Set Up Panel                   | FRU197                                   |

| -CU ''D''<br>Address<br>Switch              | Channel address<br>switch     | WZ 104                                | Operator Set Up Panel                   | FRU197                                   |

| -CU Error<br>Indicator                      | CU error indicat-<br>or       | YF010                                 | Operator Set Up Panel                   | FRU141                                   |

| -CU Online<br>Switch                        | CU online switch              | YF010                                 | Operator Set Up Panel                   | FRU141                                   |

| -CU<br>Waiting<br>Indicator                 | CU wait indicator             | YF010                                 | Operator Set Up Panel                   | FRU141                                   |

| -"D"<br>Channel<br>Type<br>(Mode)<br>Switch | Channel type<br>(mode) switch | WZ 104                                | Operator Set Up Panel                   | FRU141                                   |

| -DC Power<br>On<br>Indicator                | DC power on indicator         | YF010                                 | Operator Set Up Panel                   | FRU141                                   |

| -IML/Power<br>On Reset<br>Switch            | IML/power on<br>reset switch  | YF010                                 | Operator Set Up Panel                   | FRU141                                   |

| -J1/P1                                      | Connector                     | WZ106<br>YF010<br>(Sheets<br>1 and 2) | Operator Set Up Panel                   | FRU141                                   |

| -J2/P2                                      | Connector                     | WZ106<br>YF010<br>(Sheets<br>1 and 2) | Operator Set Up Panel                   | FRU141                                   |

| -J3/P3                                      | Connector                     | YF010<br>(Sheet 2)                    | Operator Set Up Panel                   | FRU141                                   |

| -J4/P4                                      | Connector                     | YF010<br>(Sheet 2)                    | Operator Set Up Panel                   | FRU141                                   |

| -J5/P5                                      | Connector for thermal jumper  | YF010<br>(Sheet 2)                    | Operator Set Up Panel                   | FRU141                                   |

### **Control Unit Location Area Definitions (Continued)**

| LOGIC                               |                              |                                  | LOC 1                                                                        | CARR 1                                   |

|-------------------------------------|------------------------------|----------------------------------|------------------------------------------------------------------------------|------------------------------------------|

| AREA<br>IDENTIFIER                  | DESCRIPTION                  | LOGIC<br>PAGE                    | TABLE OF CONTENTS<br>REFERENCE                                               | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

| -Local<br>Power<br>Enable<br>Switch | Local power<br>enable switch | YF010                            | Operator Set Up Panel                                                        | FRU141                                   |

| -Offline<br>Indicator               | Offline indicator            | YF010                            | Operator Set Up Panel                                                        | FRU141                                   |

| -Test/<br>Normal<br>Switch          | Test/Normal<br>switch        | YF010                            | Operator Set Up Panel                                                        | FRU141                                   |

| P 1                                 | Cable panel                  |                                  | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| -A1                                 | Connector                    | WT004<br>WT006<br>WW020          | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| -A2                                 | Connector                    | WT001<br>WW010                   | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| -B1                                 | Connector                    | ww020                            | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| -B2                                 | Connector                    | ww010                            | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| -J1                                 | Thermal connector            | YF015                            | CU-P1 Read/Write<br>Bus Connectors                                           | FRU150                                   |

| P2                                  | Cable panel                  |                                  | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

| -A1                                 | Connector                    | ww020                            | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

| -A2                                 | Connector                    | WT008<br>WT010<br>WW020          | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

| -A3                                 | Connector                    | WK005<br>WW010                   | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

| -A4                                 | Connector                    | WK001<br>WK003<br>WK005<br>WW010 | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

3480 MI EC336395

|                                         |                              |                                     |                                                                              | <u> </u>                                 |

|-----------------------------------------|------------------------------|-------------------------------------|------------------------------------------------------------------------------|------------------------------------------|

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER | DESCRIPTION                  | LOGIC<br>PAGE                       | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE                                      | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

| -A5                                     | Connector                    | WK006<br>WT003<br>WW010             | CU-P2 Cable Connectors<br>(Dual Control Unit<br>Communication<br>Connectors) | FRU150                                   |

| PS-01                                   | Power supply                 | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| - C B 1                                 | Circuit breaker              | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -CB2                                    | Circuit breaker              | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -CB3                                    | Circuit breaker              | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -F1                                     | Fuse                         | YF001<br>YF003                      | CU-PS01<br>(two different types)                                             | FRU144                                   |

| -J1-J4B                                 | Connectors                   | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -J9-J10                                 | Connectors                   | YF001<br>YF003                      | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -J11                                    | Connector                    | YF001                               | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| -J13-J15                                | Connectors                   | YF003                               | CU-PSO1<br>(two different types)                                             | FRU144                                   |

| PS-02                                   | Power supply                 | YF002                               | CU-PS02                                                                      | FRU145                                   |

| -CB1                                    | Circuit breaker              | YF002                               | CU-PS02                                                                      | FRU145                                   |

| -CB2                                    | Circuit breaker              | YF002                               | CU-PSO2                                                                      | FRU145                                   |

| -CB3                                    | Circuit breaker              | YF002                               | CU-PS02                                                                      | FRU145                                   |

| -F1                                     | Fuse                         |                                     | CU-PSO2                                                                      | FRU147                                   |

| -F2                                     | Fuse                         | YF002                               | CU-PSO2                                                                      | FRU148                                   |

| -J1-J20                                 | Connectors                   | YF002                               | CU-PS02                                                                      | FRU145                                   |

| -K1                                     | Relay                        | YF002                               | CU-PS02                                                                      | FRU145                                   |

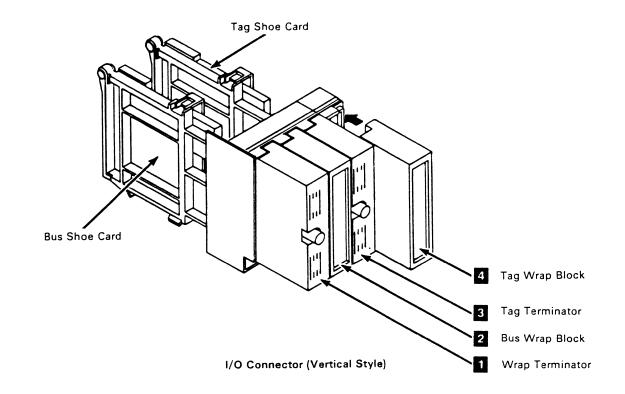

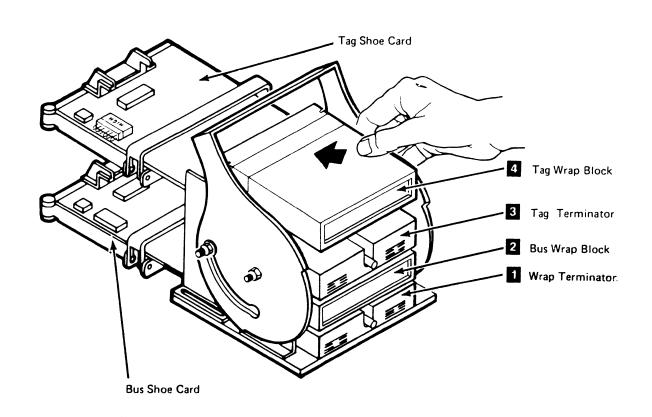

| Т1                                      | Tailgate                     | AA002<br>AT100                      | I/O Tailgate Connector                                                       | FRU136, 137<br>233-238                   |

| TIAI                                    | Tailgate position<br>Al      | AA002<br>  B001<br>  B002<br>  B003 | I/O Tailgate Connector                                                       | FRU136, 137<br>233-238                   |

| T1A3Y                                   | Tag shoe card<br>connector y | 1T003<br>WA004                      | I/O Tailgate Connector                                                       | FRU137, 234, 236,<br>238                 |

|                                         |                              |                                     |                                                                              |                                          |

<sup>&</sup>lt;sup>9</sup> Copyright IBM Corp. 1984, 1985

### **Control Unit Location Area Definitions (Continued)**

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER  | DESCRIPTION               | LOGIC<br>PAGE      | LOC 1<br>TABLE OF CONTENTS<br>RFFERENCE | CARR I<br>TABLE OF CONTENTS<br>REFERENCE |

|------------------------------------------|---------------------------|--------------------|-----------------------------------------|------------------------------------------|

| T1A3Z                                    | Tag shoe card connector z | T003<br> WA005/006 | I/O Tailgate Connector                  | FRU170                                   |

| TB1                                      | Terminal block            | ZT010              | CU-A1 Logic Gate<br>(hinge side)        | FRU160                                   |

| TB2                                      | Terminal block            | ZT011              | CU-Al Logic Gate<br>(hinge side)        | FRU160                                   |

| ТВ3                                      | Terminal block            | ZTOII              | CU-Al Logic Gate<br>(hinge side)        | FRU160                                   |

| Thermal<br>Switch<br>(Top of<br>gate)    | Thermal switch            | ZT020              | Thermal Switch Assembly                 | FRU224                                   |

| Thermal<br>Switch<br>(Bottom of<br>gate) | Thermal switch            | YF015              | Thermal Switch Assembly                 | FRU143                                   |

Legend LGND 30

### **Tape Unit and Drive Location Area Definitions**

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER               | DESCRIPTION                                                                               | LOGIC<br>PAGE          | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|-----------------------------------------|------------------------------------------|

| A1                                                    | Logic board in<br>each drive in the<br>tape unit                                          | AA000<br>AA100         | 02A-A1 Logic Board Pin<br>and Card Side | FRU058                                   |

| CB1                                                   | Circuit breaker<br>(primary power)                                                        | YF050<br>YF060         | Tape Unit AC Power CB                   | FRU218                                   |

| Compressor                                            | Compressor                                                                                | YF050<br>YF060         | Major FRU Locations<br>50/60 Hz         | FRU030                                   |

| DC Switch                                             | DC switch<br>(these are addi-<br>tional contacts<br>on the drive fan<br>and power switch) | SN001/002<br>(Sheet 2) | Tape Unit Locations                     | FRU104                                   |

| -P1                                                   | Plug                                                                                      | SN001/002<br>(Sheet 2) |                                         | FRU104                                   |

| DK                                                    | Deck assembly                                                                             |                        | Drive Locations                         |                                          |

| -Cartridge<br>Latched<br>Sensor<br>and LED            | Cartridge latched<br>sensor and LED                                                       | SN001/002<br>(Sheet 1) | Cartridge Latch<br>Assembly             | FRU011                                   |

| -Cartridge<br>Present<br>Sensor<br>and LED            | Cartridge present<br>sensor and LED                                                       | SN001/002<br>(Sheet 1) | Cartridge Present<br>Sensor             | FRU010                                   |

| -File Reel<br>Tach                                    | File reel tach-<br>ometer                                                                 | SN001/002<br>(Sheet 2) | File Reel Motor                         | FRU003                                   |

| -FPSW                                                 | Deck assembly<br>file protect<br>switch                                                   | SN001/002<br>(Sheet 2) | File Protect Switch                     | FRU009                                   |

| -J14                                                  | Connector for<br>tension<br>transducer                                                    | PA000/001<br>(Sheet 2) | Tension Transducer                      | FRU014                                   |

| -Machine<br>Reel Tach<br>Phase A<br>Sensor<br>and LED | Machine reel<br>tachometer phase<br>A sensor and LED                                      | SN001/002<br>(Sheet 1) |                                         | FRU225                                   |

| -Machine<br>Reel<br>Phase B<br>Sensor<br>and LED      | Machine reel<br>tachometer phase<br>B sensor and LED                                      | SN001/001<br>(Sheet 1) | Machine Reel Tach<br>Sensor B           | FRU226                                   |

| -P1                                                   | Connector for<br>tape path<br>sensor A                                                    | SN001/002<br>(Sheet 1) | Tape Path Sensor A                      | FRU006                                   |

| LOGIC                             |                                                                         |                                 |                                                        |                                          |

|-----------------------------------|-------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------|------------------------------------------|

| LOCATION<br>AREA<br>IDENTIFIER    | DESCRIPTION                                                             | LOGIC<br>PAGE                   | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE                | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

| -P2                               | Connector for tape path sensor B                                        | SN001/002<br>(Sheet 1)          | Tape Path Sensor B                                     | FRU007                                   |

| -P3                               | Connector for<br>cartridge present<br>sensor and file<br>protect switch | SN001/002<br>(Sheet 1<br>and 2) | Cartridge Present<br>Sensor and File<br>Protect Switch | FRU010                                   |

| -P4                               | Connector for<br>cartridge latch-<br>ed sensor                          | SN001/002<br>(Sheet 1)          | Cartridge Latch<br>Assembly                            | FRU011                                   |

| -P5                               | Connector for<br>machine reel tach<br>phase B sensor                    | SN001/002<br>(Sheet 1)          |                                                        | FRU226                                   |

| -P6                               | Connector for<br>machine reel tach<br>phase A sensor                    | SN001/002<br>(Sheet 1)          |                                                        | FRU225                                   |

| -P7                               | Connector for file reel tach                                            | SN001/002<br>(Sheet 2)          | File Reel Motor                                        | FRU003                                   |

| -Plenum<br>Press Sw               | Plenum pressure<br>sensor switch                                        | SN001/002<br>(Sheet 2)          |                                                        | FRU040                                   |

| -Tape Path<br>Sensor A<br>and LED | Tape path sensor<br>A and LED                                           | SN001/002<br>(Sheet 1)          | Tape Path Sensor A                                     | FRU006                                   |

| -Tape Path<br>Sensor B<br>And LED | Tape path sensor<br>B and LED                                           | SN001/002<br>(Sheet 1)          | Tape Path Sensor B                                     | FRU007                                   |

| -Tray<br>Solenoid                 | Cartridge latch<br>solenoid                                             | YG010<br>YG110                  | Latch Sensor                                           | FRU002                                   |

| Drive Fan<br>and Power<br>Switch  | Drive fan and<br>power switch                                           | YF020                           | Tape Unit Locations                                    | FRU104                                   |

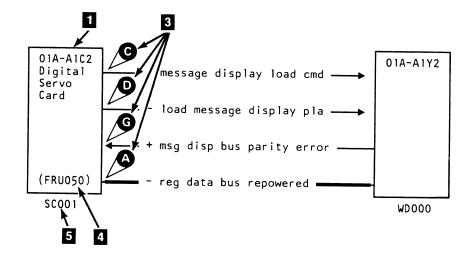

| DSP                               | Message display                                                         |                                 | Operator Control and<br>Display                        | FRU021                                   |

| -J1                               | Connector                                                               | WD000<br>WD001                  |                                                        |                                          |

| -J2                               | Connector                                                               | WD000<br>WD001                  |                                                        |                                          |

| -J3                               | Connector                                                               | WD000<br>WD001                  |                                                        |                                          |

| - J4                              | Connector                                                               | WD000<br>WD001                  |                                                        |                                          |

| -Ready<br>Switch                  | Switch                                                                  | WD000<br>WD001                  | Ready/Not Ready Switch                                 | FRU109                                   |

| LOGIC<br>LOCATION                 |                                                                                                                                                      |                                                    | 1                                                             |                                          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------|------------------------------------------|

| AREA<br>IDENTIFIER                | DESCRIPTION                                                                                                                                          | LOGIC<br>PAGE                                      | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE                       | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

| -Rewind<br>Switch                 | Switch                                                                                                                                               | WD000<br>WD001                                     | Rewind Switch                                                 | FRU109                                   |

| -Unload<br>Switch                 | Switch                                                                                                                                               | WD000<br>WD001                                     | Unload Switch                                                 | FRU109                                   |

| EL                                | External load<br>register panel                                                                                                                      | WD000<br>WD001                                     | Major FRU Locations<br>50/60 Hz (-5 V dc Re-<br>sister panel) | FRU036                                   |

| Fan                               | Fan (located near<br>the compressor in<br>the tape unit for<br>50 Hz)(fan is lo-<br>cated at the bot-<br>tom of the tape<br>unit frame for<br>60 Hz) | YF050<br>YF060                                     | Major FRU Locations<br>50/60 Hz                               | FRU071                                   |

| Fan                               | Fan for drive<br>gate                                                                                                                                | YG010<br>(drive 0)<br>YG110<br>(drive 1)           | 50/60 Hz Blower<br>Assembly                                   | FRU020                                   |

| File Reel<br>Motor                | File reel motor                                                                                                                                      | YG010<br>(drive 0)<br>YG110<br>(drive 1)           | File Reel Motor                                               | FRU003                                   |

| Head (Tape<br>Lifter)<br>Solenoid | Solenoid at the head to move tape away from the head during high-speed tape movement (tape lift-er)                                                  | YG010<br>(drive 0)<br>YG110<br>(drive 1)           | Tape Lifter Solenoid                                          | FRU216                                   |

| Local                             | Local read/write<br>and control DDB<br>cabling<br>CU/TU<br>CUO local drive<br>address 0-7<br>CU1 local drive<br>address 8-F                          | VP001<br>WW010<br>WW020<br>ZW101<br>ZW102<br>ZW103 | Read Adapter Cables and<br>Write Adapter Cables               | FRU087-089<br>FRU091-093                 |

| Machine<br>Reel Motor             | Machine reel<br>motor                                                                                                                                | YG010<br>(drive 0)<br>YG110<br>(drive 1)           | Machine Reel Motor                                            | FRU004                                   |

| Online/<br>Offline<br>Switch      | Online/offline<br>switch                                                                                                                             | SN001/002<br>(Sheet 2)                             | Tape Unit Locations                                           | FRU105                                   |

Legend LGND 40

| LOGIC<br>LOCATION<br>AREA<br>IDENTIFIER | DESCRIPTION                                                         | LOGIC<br>PAGE                    | LOC 1<br>TABLE OF CONTENTS<br>REFERENCE | CARR 1<br>TABLE OF CONTENTS<br>REFERENCE |

|-----------------------------------------|---------------------------------------------------------------------|----------------------------------|-----------------------------------------|------------------------------------------|

| OSU                                     | Operator set up<br>panel for drive<br>address switches              | SN001/002<br>(Sheet 2)           | Tape Unit Locations                     | FRU108                                   |

| -Drive<br>Logical<br>Address<br>Switch  | Drive logical<br>address switch                                     | SN001/002<br>(Sheet 2)           | Tape Unit Locations                     | FRU108                                   |

| -J1                                     | Connector for<br>drive logical<br>address switch                    | SN001/002<br>(Sheet 2)           | Tape Unit Locations                     | FRU108                                   |