# Field Engineering Instruction - Reference

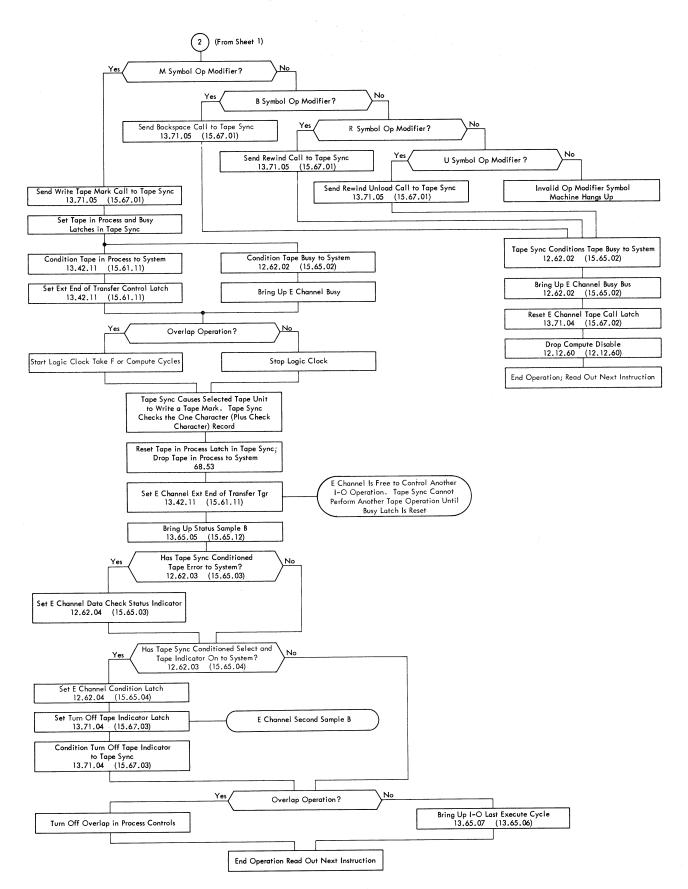

1414 Input-Output Synchronizer Models 1, 2 and 7

|   | $\sim$              |

|---|---------------------|

|   | }                   |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   | $\uparrow \bigcirc$ |

|   |                     |

|   | ,                   |

|   |                     |

|   | ,                   |

|   |                     |

|   |                     |

|   | 3~                  |

|   |                     |

|   |                     |

|   | برسر<br>م           |

|   | ,                   |

|   |                     |

| • | 6                   |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   | •                   |

|   | ~ ~                 |

|   | ,                   |

|   |                     |

|   | <b>√</b> √√         |

|   | *                   |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   |                     |

|   | *                   |

|   | $\sim$              |

|   | 1                   |

|   |                     |

Instruction-Reference

IBM 1414 Input-Output Synchronizer

Models 1, 2 and 7

# **Preface**

This manual describes IBM 1414 Input-Output Synchronizer (Models 1, 2, and 7) operation with the following IBM Data Processing Systems: 1410, 7010, and 7044. To show the relation of the Model 1414. Model 1, 2, or 7 to other units in the system, brief descriptions of processing unit and channel actions that occur in the execution of magnetic tape operations are included. Detailed information on the processing unit in the IBM 1410 System is included in the IBM Customer Engineering Manual of Instruction, 1411 Processing Unit Instructions and Special Features, Form 223-2698, and in the IBM Customer Engineering Instruction-Reference manual, 1410 System Fundamentals, Form 223-2589. Complete information on data channels and processing unit operations in the IBM 7040 and 7044 Systems is included in the IBM Customer Engineering Instruction-Reference manual, 7904 Data Channel, Preliminary Edition, Form R23-2595-1, and in the IBM Customer Engineering Manual of Instruction, 7106/7107 Central Processor, Preliminary Edition, Form R23-2574. The IBM Customer Engineering Instruction-Reference manuals, 7010 Data Processing System, Volumes 1 and 2, Preliminary Editions, Forms R23-2364 and R23-2636, contain information on the processing unit in the 7010 System.

Included in this manual are second level diagrams of circuits for the IBM 1414, Models 1 and 2, explanations of the CE panel, and several checking procedures.

This manual obsoletes Form R23-2554-1.

# MINOR REVISION AUGUST 1965

This manual, Form 223-2554-1, is a minor revision of the previous edition but does not obsolete Form 223-2554. The information presented herein has been corrected and brought up to the latest engineering level. Included is EC 281293, mandatory for 1414's connected to 7040/7044 systems.

Copies of this and other IBM publications may be obtained through IBM Branch Offices. Address comments concerning the contents of this publication to: IBM Corporation, FE Manuals, Dept. B96, PO Box 390, Poughkeepsie, N. Y. 12602

| Basic Concepts                                         | 5    | Functional Units and Checking Circuits Final Amplifiers |     |

|--------------------------------------------------------|------|---------------------------------------------------------|-----|

|                                                        | _    | Read Registers                                          |     |

| 7040/7044 Channel Tape Operations                      | 7    | Read-Write Register                                     |     |

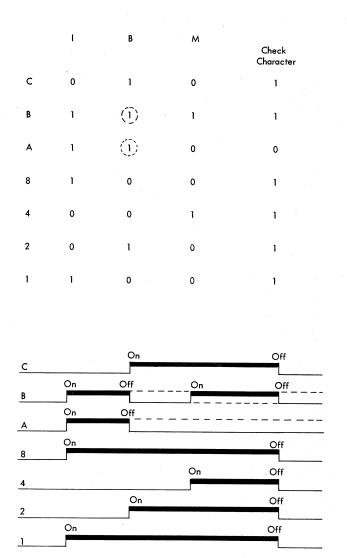

| Data Channel Tape Operation                            | 7    | Longitudinal Redundancy Check Register (LRCR)           |     |

| Data Channel A Tape Operation                          | 8    | Odd-Even Character Counter                              |     |

| IBM 7904 Data Channel Tape Operation                   | 10   | Vertical Redundancy Check (VRC)                         |     |

| Select Instructions                                    | 11   | Echo Errors                                             |     |

| Translation                                            | 11   | Write Compare                                           |     |

| Read, Write, Sense, and Control Select Instructions    | 12   | Write Delay Noise                                       |     |

| Read Select (RDS)                                      | 12   |                                                         |     |

| Write Select (wrs)                                     | 12   | Skew Error                                              | 120 |

| Sense Select (SEN)                                     | 12   |                                                         |     |

| Control Select (CTR)                                   | 12   | Tape Synchronizer Operations                            | 51  |

| Channel Control Instructions                           | 13   | Write                                                   | 51  |

| Reset and Load Channel Instruction (RCH)               | 13   | Preliminary Conditions                                  |     |

| Input-Output of a Record and Disconnect (IORD)         |      | Data Transfers                                          |     |

| Command                                                | 13   |                                                         |     |

| Tape Control Instructions                              | 14   | Write Circuits Disconnect                               |     |

| Tape Data Compatibility                                | 14   | Read Check of Write Operation                           |     |

| Write End-of-File (WEF) Instruction                    |      | Tape Write Operation Disconnect                         |     |

| Write Blank Tape (WBT) Instruction                     | 14   | Read                                                    |     |

| Backspace Record (BSR) Instruction                     | 14   | Preliminary Conditions                                  |     |

| <b>A</b> ' ' '                                         | 14   | Data Flow and Error Checks                              |     |

| Rewind (REW) Instruction                               | 15   | Check Character                                         |     |

| Rewind and Unload (RUN) Instruction                    | 15   | Tape Read Operation Disconnect                          |     |

| Channel Instructions that Apply Only to Magnetic Tapes |      | Tape Unit Control                                       |     |

| End of Tape Indicator                                  | 15   | Erase                                                   |     |

| End of Tape Test (ETTX) Instruction                    | 15   | Rewind                                                  |     |

| Other Applicable Instructions                          | 15   | Rewind Unload                                           | 74  |

| Redundancy Check Indicator                             | 15   | Write Tape Mark                                         | 75  |

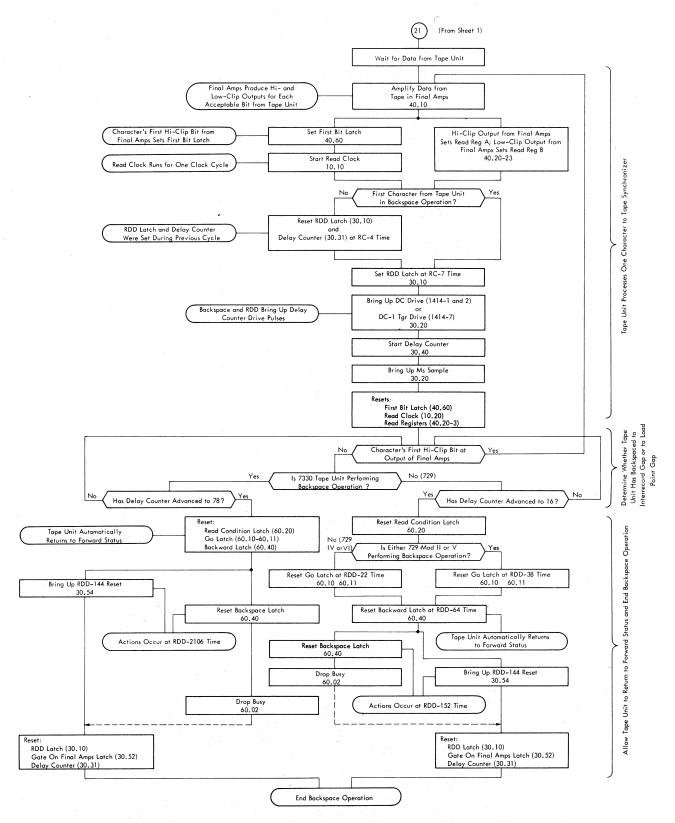

| Transfer On Redundancy Check (TRCX) Instruction        | 15   | Backspace                                               | 78  |

| End of File Indicator                                  | 16   |                                                         |     |

| Transfer On End of File (TEFX) Instruction             | 16   |                                                         |     |

| Channel-In-Use Indicator                               | 16   | Tape Synchronizer Timings                               |     |

| Transfer on Channel In Operation (TCOX) Instruction    | 16   | Delay Counter                                           |     |

| Input-Output Check Indicator                           | 16   | Read Clock                                              |     |

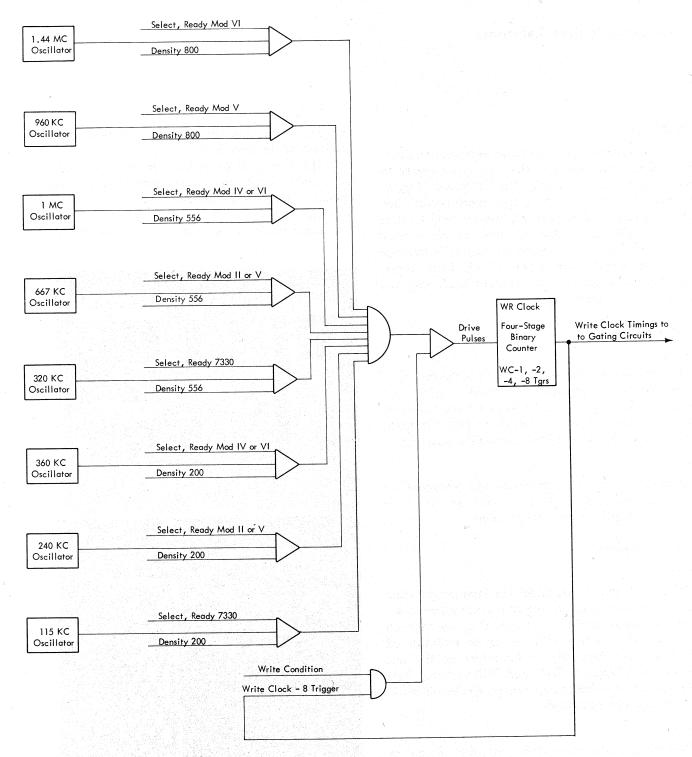

| Input-Output Check Test (10T) Instruction              | 16   | Write Clock                                             | 82  |

| Reset Data Channel (RDCX) Instruction                  | 16   |                                                         |     |

| Store Channel (schx) Instruction                       | 17   | Town Complement Defenses                                |     |

| Channel Traps                                          | 17   | Tape Synchronizer Reference                             |     |

| Enable (ENB) Instruction                               | 17   | CE Panel                                                |     |

| Inhibit Channel Traps (ICT) Instruction                | 17   | CE Panel Keys                                           |     |

| Restore Channel Traps (RCT) Instruction                | 18   | CE Panel Switches                                       |     |

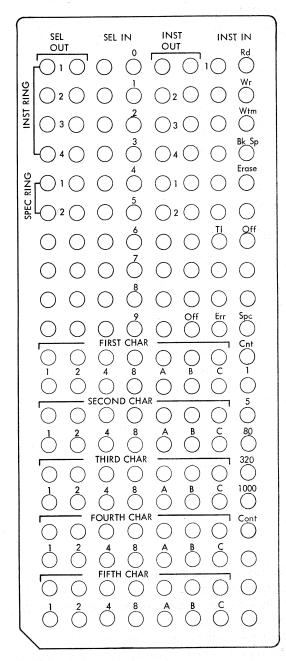

| Channel Trap Stores                                    | 18   | CE_Control Plug Board                                   |     |

|                                                        |      | Instruction Ring                                        |     |

| 1410/7010 Channel Tana Operation                       | - 00 | Special Ring                                            |     |

| 1410/7010 Channel Tape Operation                       | 20   | Character Counter                                       | 9:  |

| Channel Tape Write Operations                          | 22   | 1414-1 (Without 800 CPI Feature) and 2 Clipping         |     |

| 7010 E-Channel Tape Write Operation                    | 22   | Level Checks                                            | 9:  |

| 1410 E-Channel Tape Write Operation                    | 23   | Write Clipping Level Check                              | 9   |

| Channel Tape Read Operation                            | 31   | Read Clipping Level Check                               | 92  |

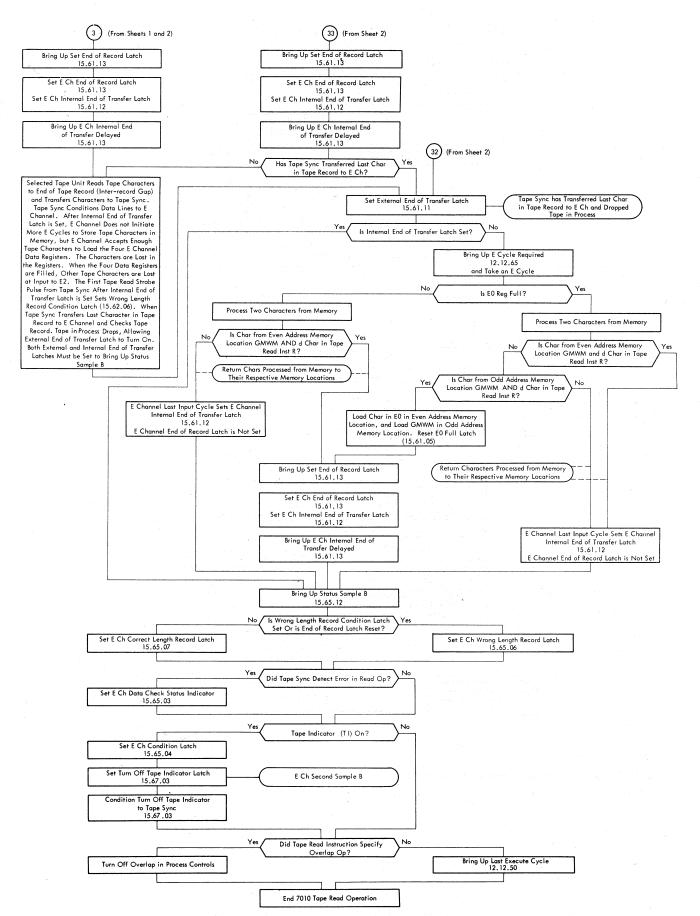

| 7010 E-Channel Tape Read Operation                     | 31   | Clipping Level Error Check                              | 93  |

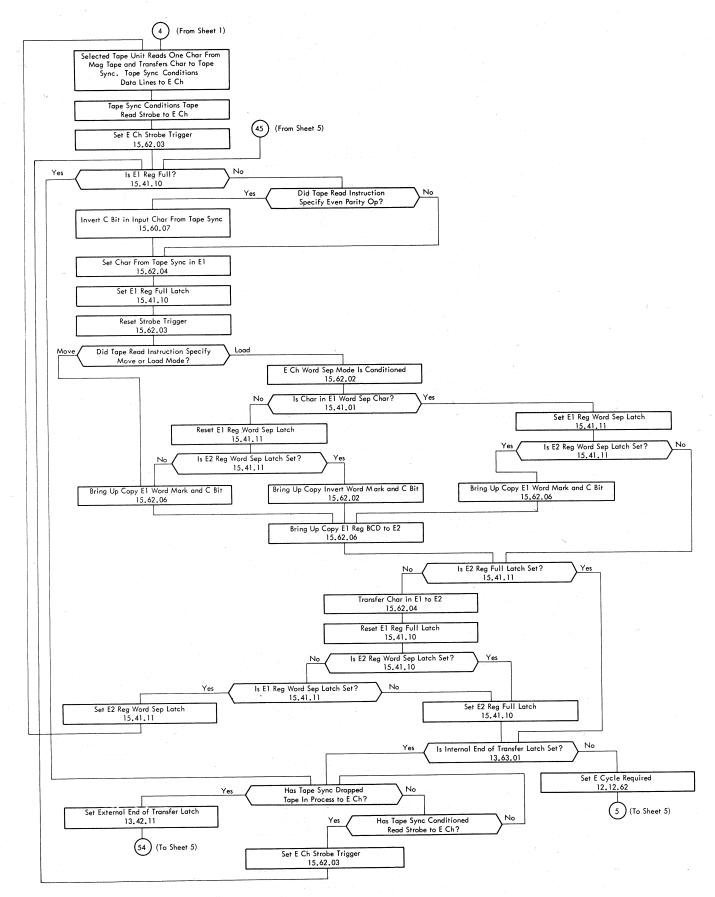

| 1410 E-Channel Tape Read Operation                     | 33   | Tape Synchronizer Error Circuits Check                  |     |

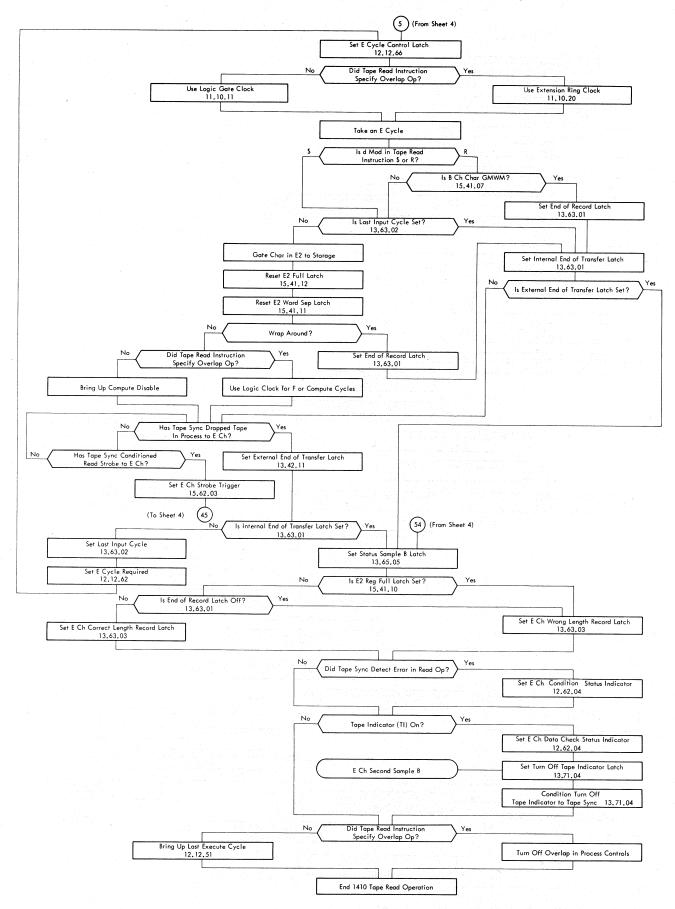

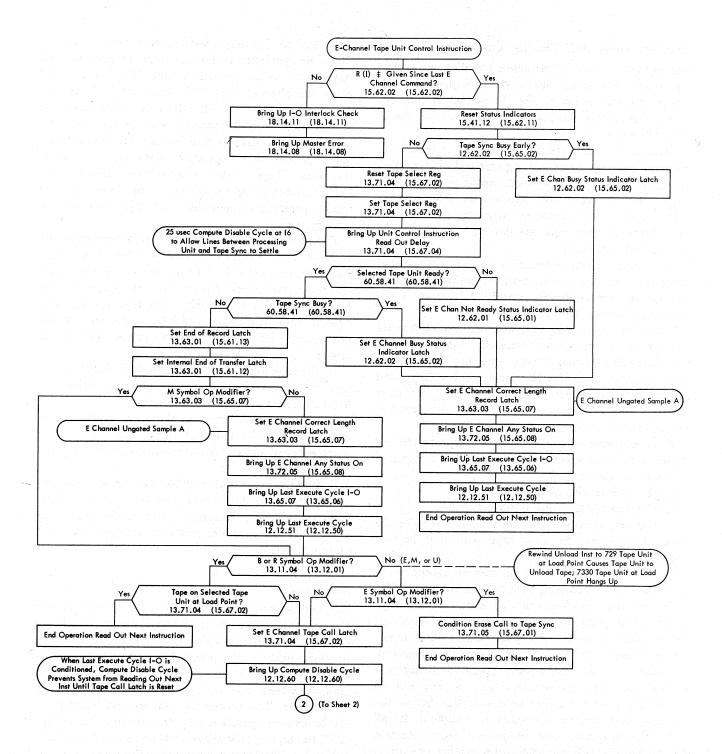

| Channel Tape Unit Control Operation                    | 39   |                                                         |     |

| Write Tape Mark                                        | 39   |                                                         |     |

| Backspace                                              |      | Appendix                                                | 94  |

| Rewind and Rewind Unload                               |      | 1414 Tape Synchronizer (Models 1 and 2) Second          |     |

| Erase                                                  | 40   | Level Diagrams                                          | 94  |

# Illustrations

| FIGUR | E TITLE PAGE                                         | FIGUE | RE TITLE                                        | PAGE  |

|-------|------------------------------------------------------|-------|-------------------------------------------------|-------|

| 1.    | Tape Units Attached to 1414 Tape Synchronizer 5      | 31.   | Simplified Read Operation Sequence              | 73    |

| 2.    | Magnetic Tape Unit Characteristics 5                 | 32.   | Backspace Operation                             | 77    |

| 3.    | Tape Synchronizer-System Relation 6                  | 33.   | Backspace Timings (Sheets 1 and 2)              | 78 79 |

| 4.    | 7040/7044 Tape Operation Data Flow                   | 34.   | Backspace Circuits                              | 80    |

| 5.    | Data Channel A 9                                     | 35.   | Tape Synchronizer Oscillators                   | 82    |

| 6.    | Data Channel B (with Tapes) 10                       | 36.   | Read Clock Outputs                              | 83    |

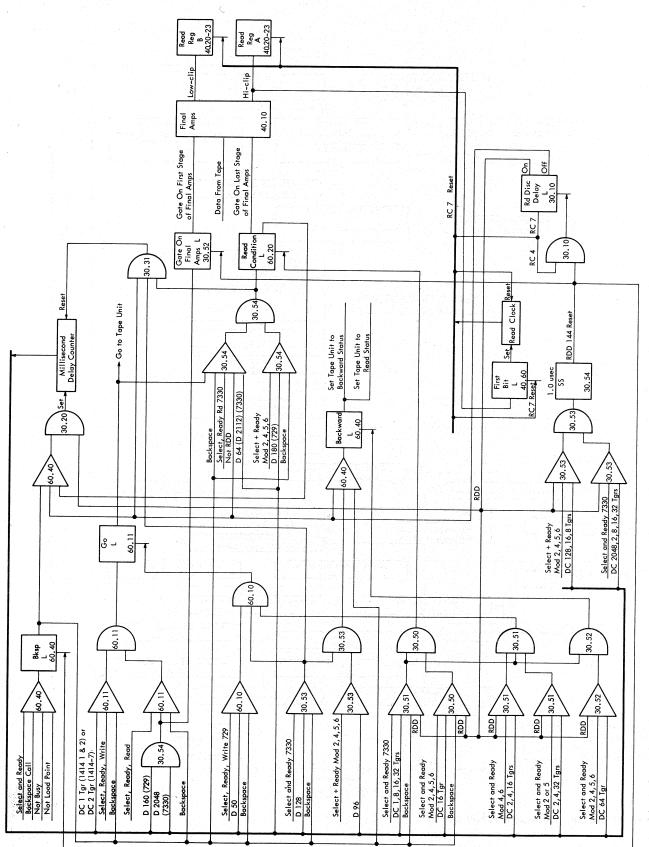

| 7.    | Addresses of Magnetic Tape Units on Data Channels 11 | 37.   | Write Clock Outputs                             | . 84  |

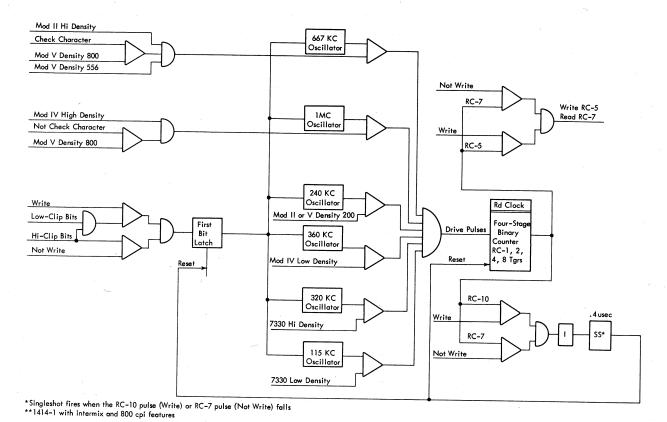

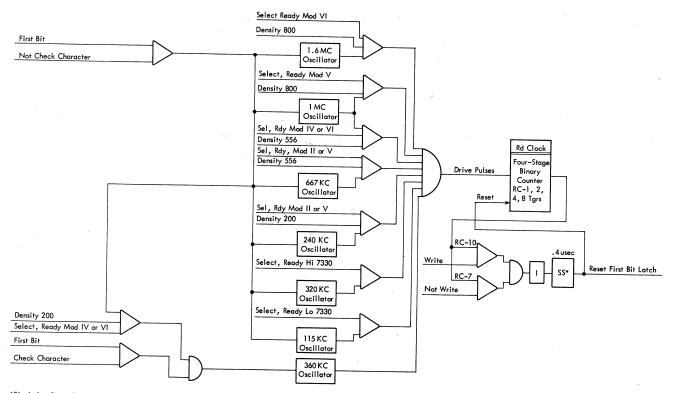

| 8.    | Breakdown of Address Part of Select Instruction 11   | 38.   | Delay Counter — Microsecond Outputs             | . 84  |

| 9.    | Zone Bit Alteration 12                               | 39.   | Delay Counter - Millisecond Outputs             | . 85  |

| 10.   | Maximum Times Between Select and                     | 40.   | 1414-1 Read Clock Drive                         | 86    |

|       | RCH Instructions                                     | 41.   | 1414-7 Read Clock Drive                         | 86    |

| 11.   | End-Of-File-Gap                                      | 42.   | 1414-1 or 7 Write Clock Drive                   | 87    |

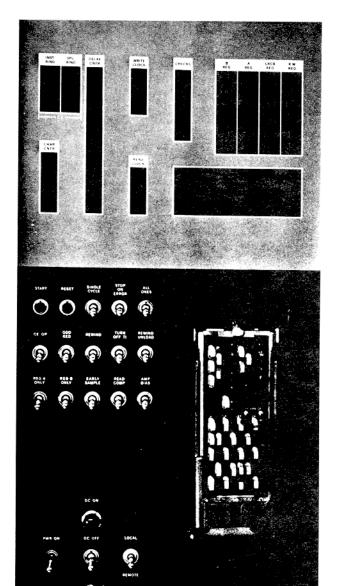

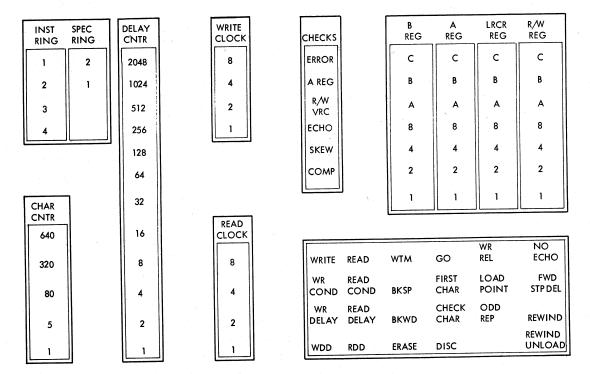

| 12.   | Format for Magnetic Tape Instructions                | 43.   | Tape Synchronizer CE Panel                      | . 88  |

| 13.   | Simplified E-Channel Tape Write Operation            | 44.   | Tape Synchronizer CE Panel Indicators           | . 89  |

| 14.   | E-Channel Tape Write Operation (Sheets 1-6) 25-30    | 45.   | CE Control Plug Board                           | . 91  |

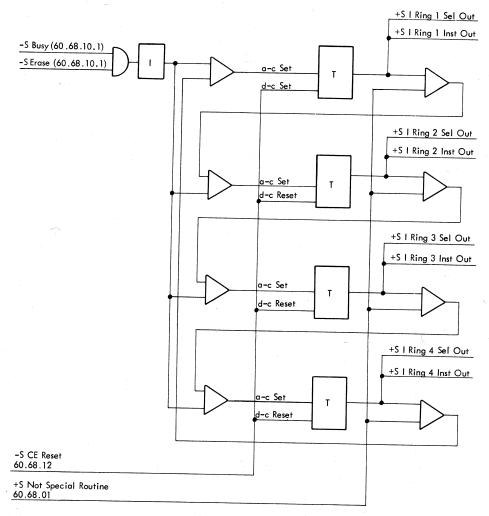

| 15.   | E-Channel Tape Read Operation (Sheets 1-5) 34-38     | 46.   | Instruction Ring                                | . 92  |

| 16.   | E-Channel Tape Unit Control Operation                | 47.   | Write Clipping Level Check for 1414-1 and 2     | . 93  |

|       | (Sheets 1 and 2)                                     | 48.   | Read Clipping Level Check for 1414-1 and 2      | . 93  |

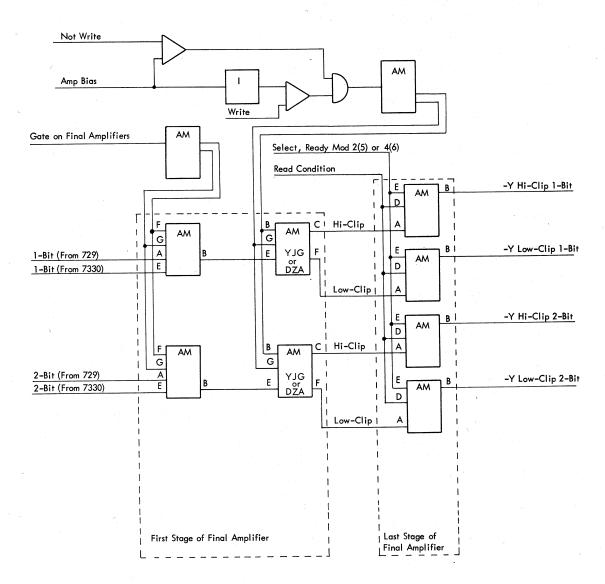

| 17.   | Final Amplifiers 43                                  | 180.  | Reference                                       | . 95  |

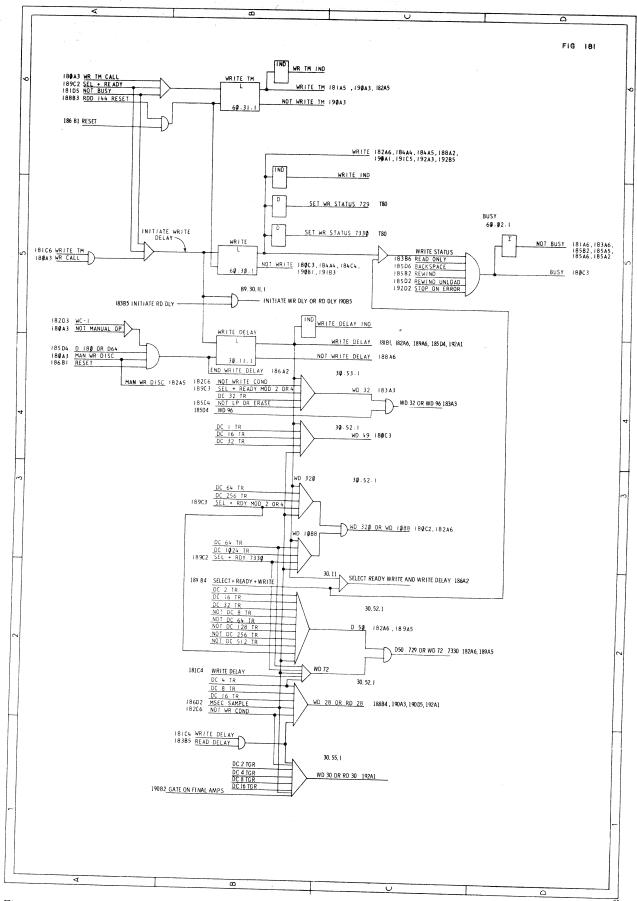

| 18.   | High-Clip and Low-Clip Outputs of Final              | 181.  | Write Controls 1                                | . 96  |

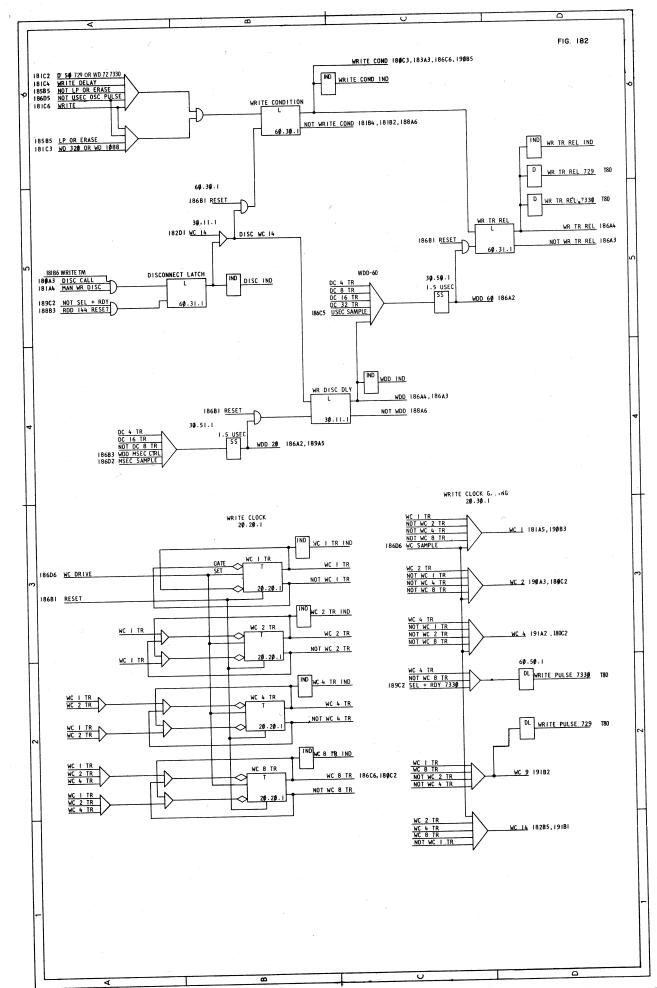

|       | Amplifier Clipper Card 44                            | 182.  | Write Controls II                               | 97    |

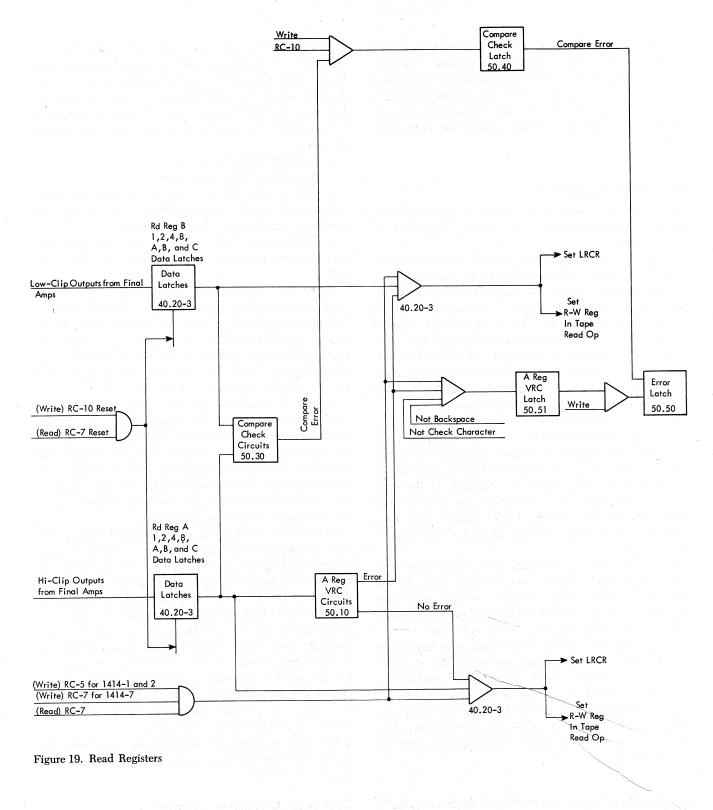

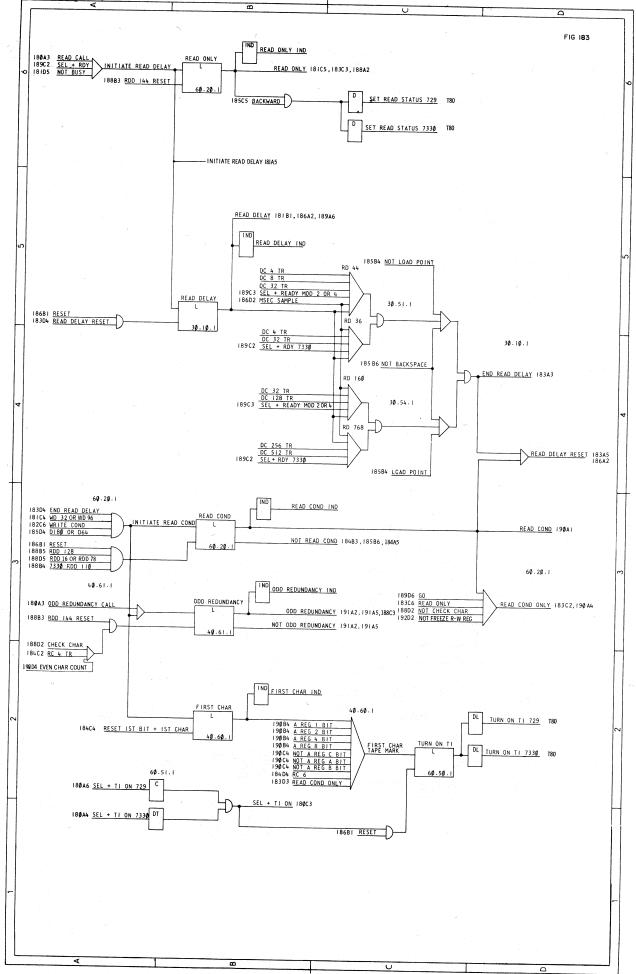

| 19.   | Read Registers 45                                    | 183.  | Read Controls I                                 | . 98  |

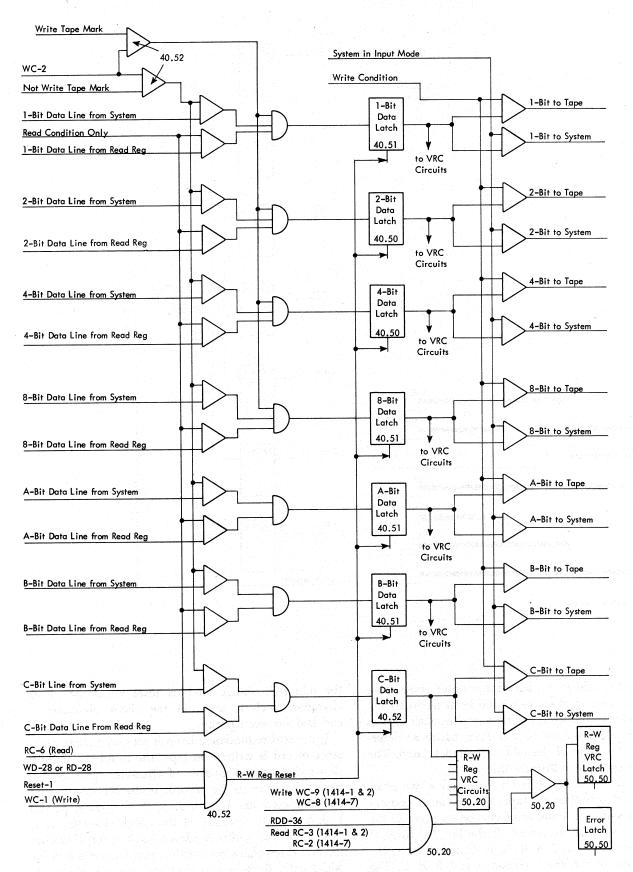

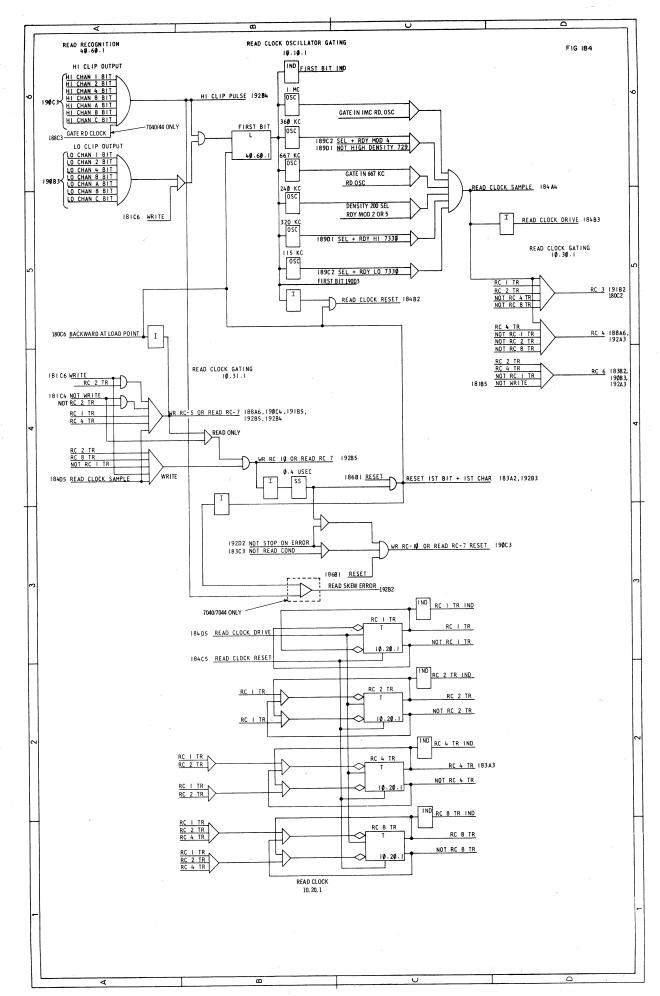

| 20.   | Read-Write Register 47                               | 184.  | Read Controls II                                | . 99  |

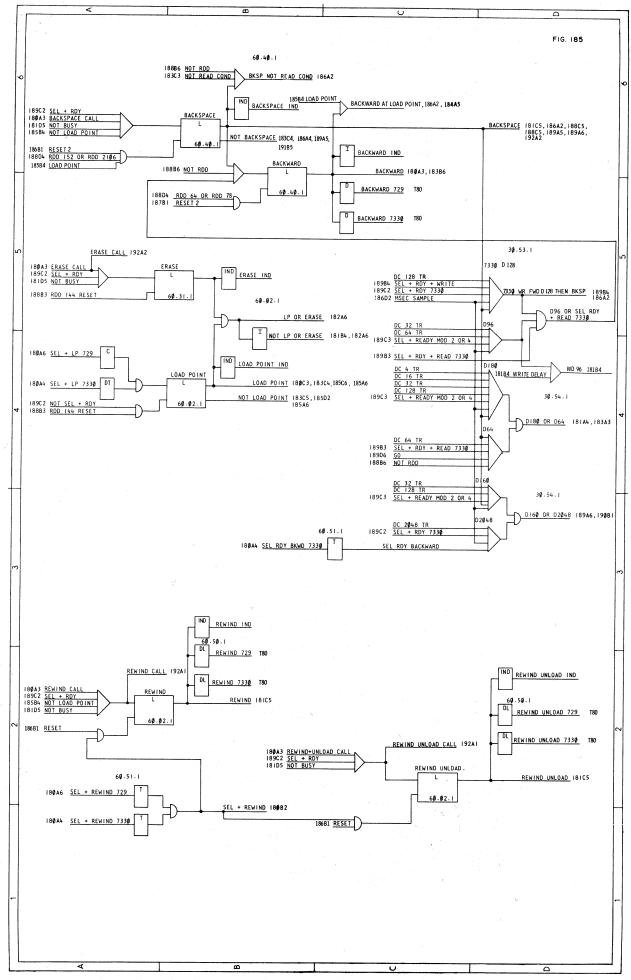

| 21.   | LRCR Check 48                                        | 185.  | Unit Control                                    | . 100 |

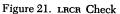

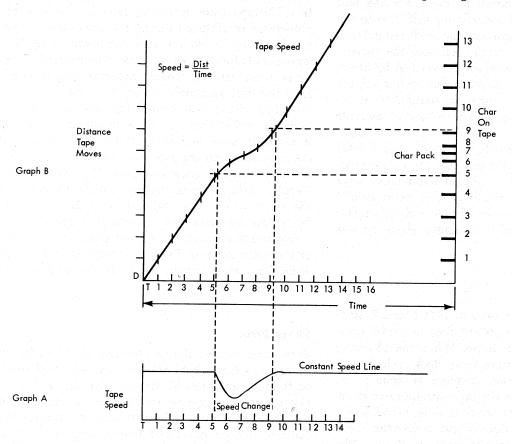

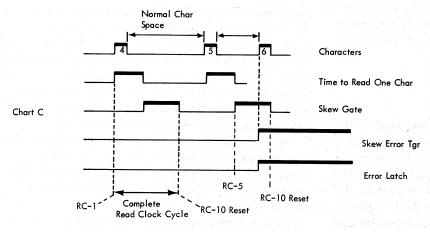

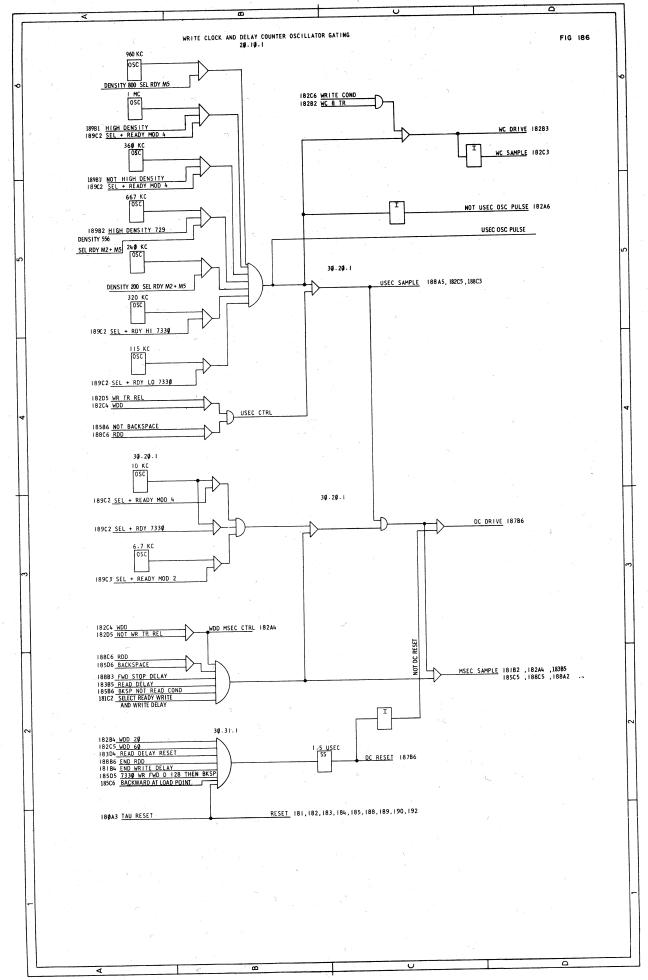

| 22.   | Skew Error and Check Circuits 50                     | 186.  | Write Clock and Delay Counter Oscillator Gating | . 101 |

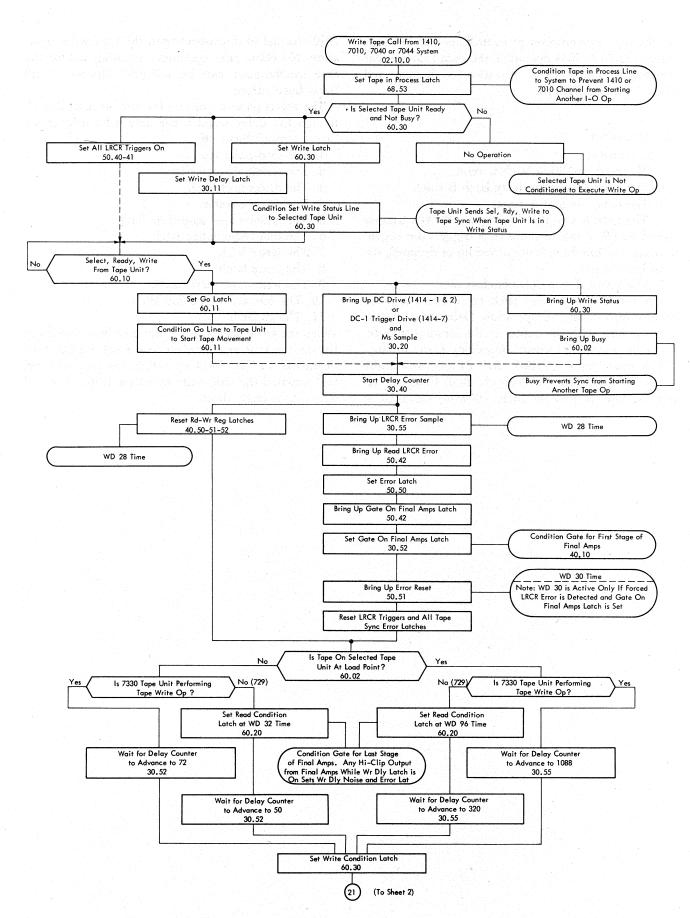

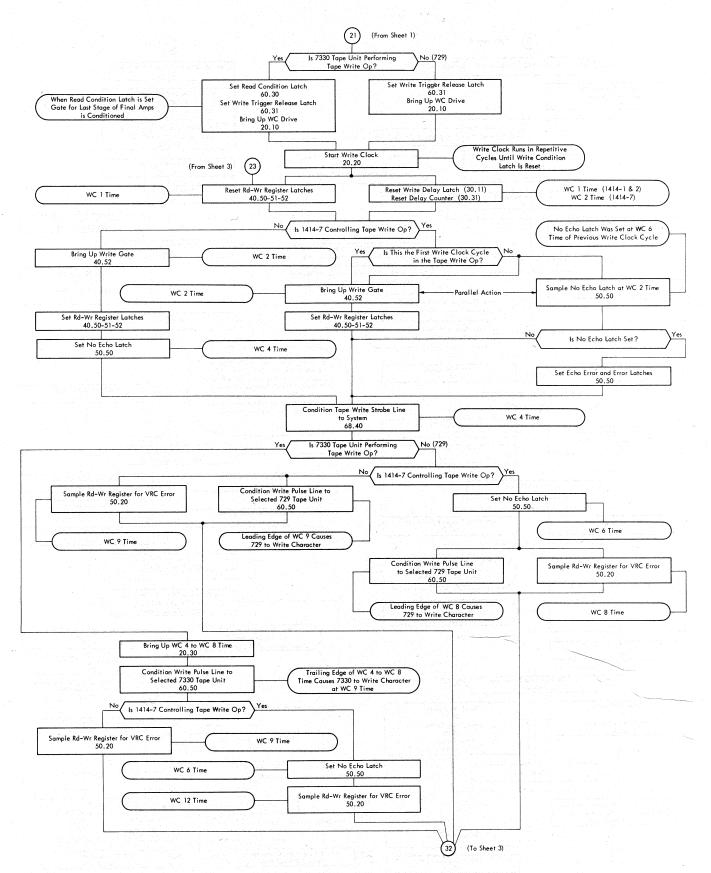

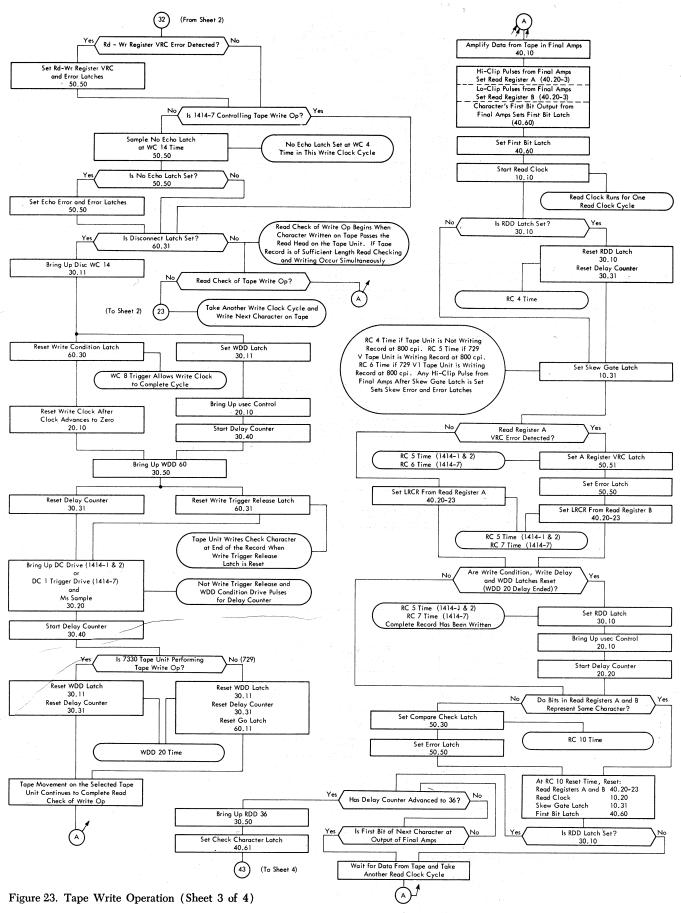

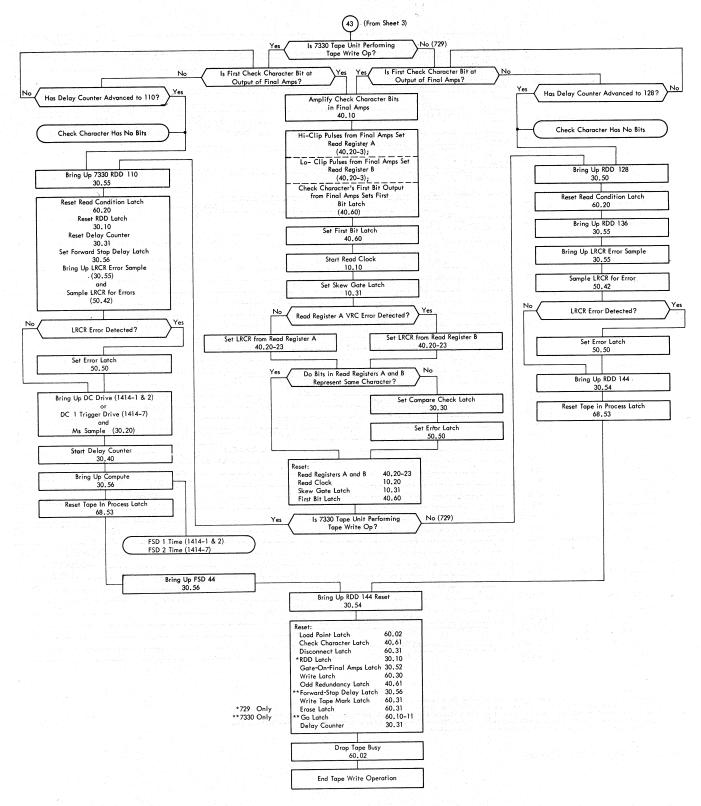

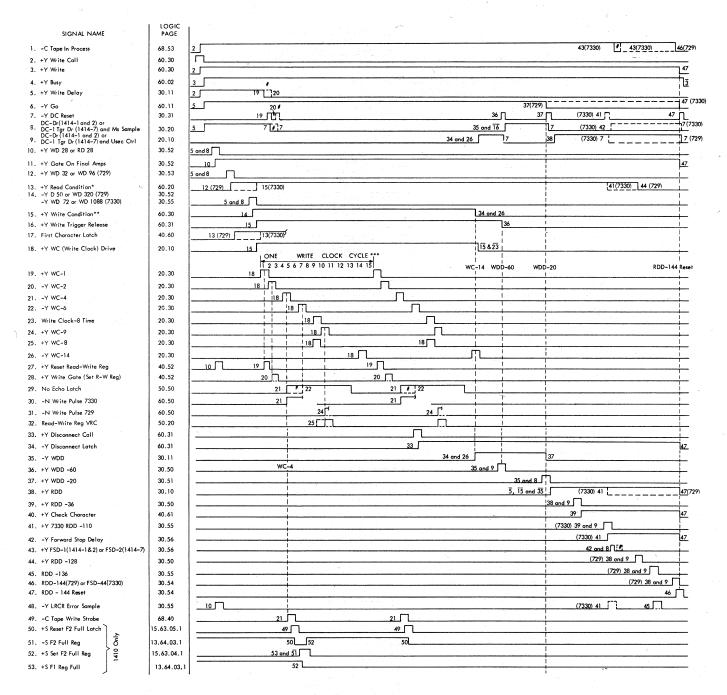

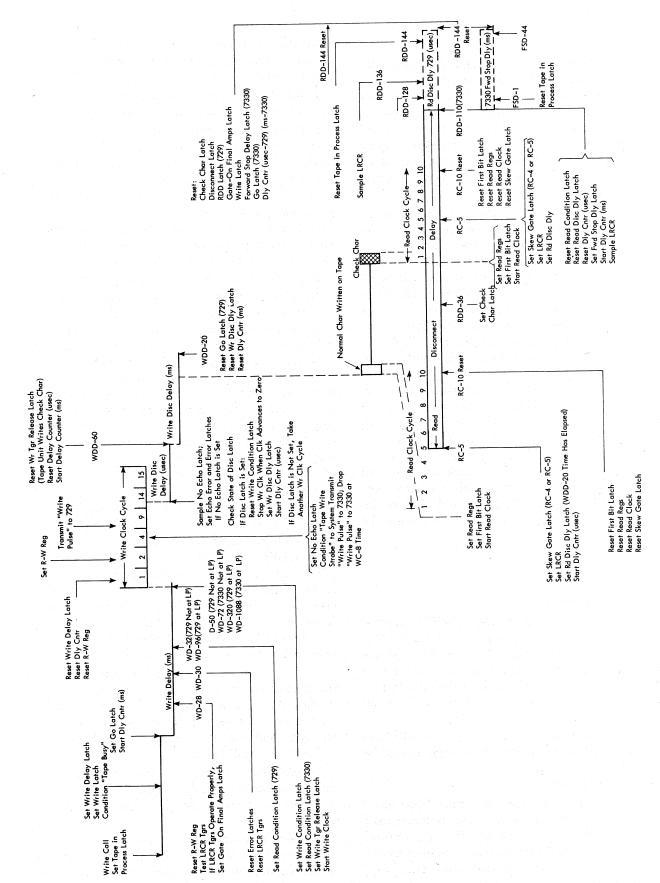

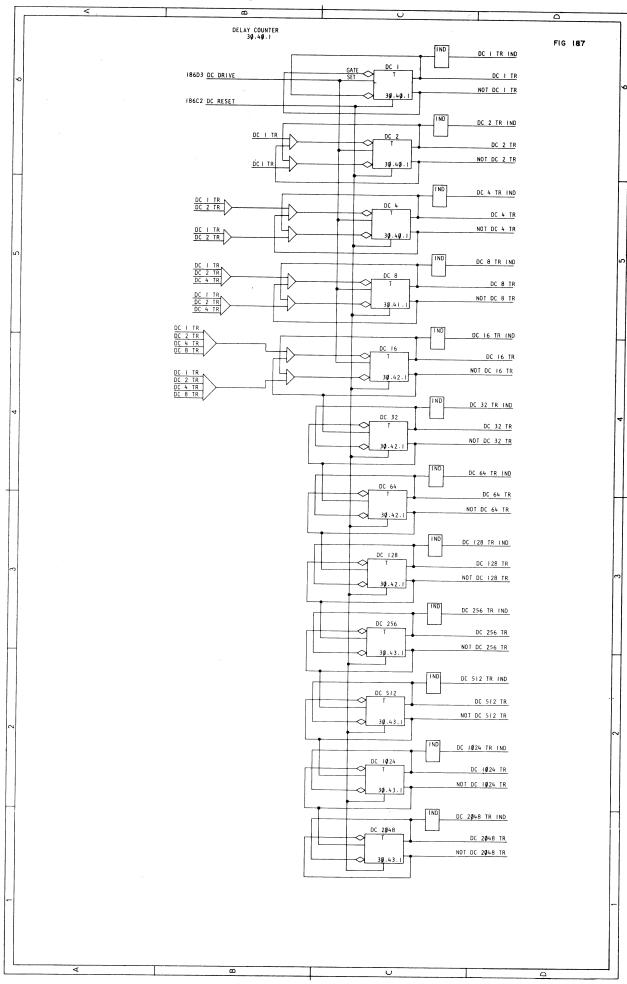

| 23.   | Tape Write Operation (Sheets 1-4) 56-59              | 187.  | Delay Counter                                   | . 102 |

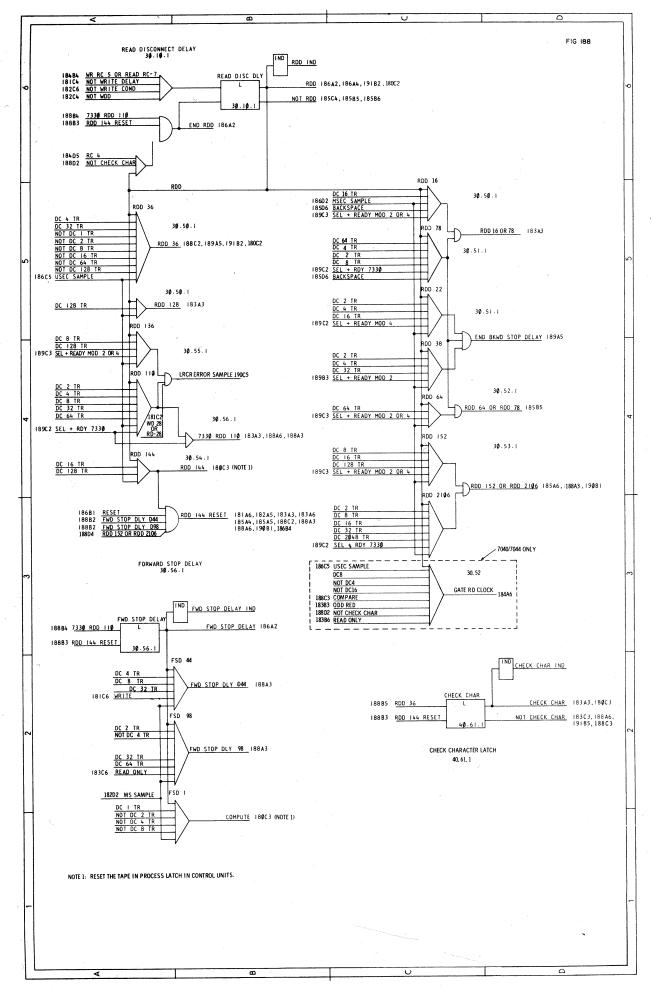

| 24.   | Tape Write Timings 60                                | 188.  | RDD, FSD, and Check Character                   | . 103 |

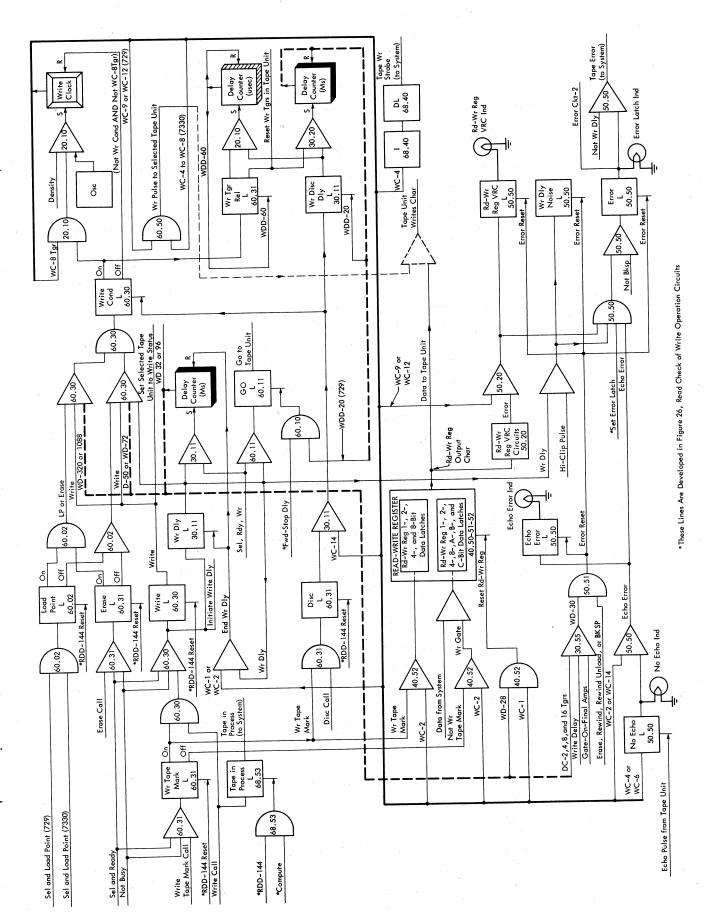

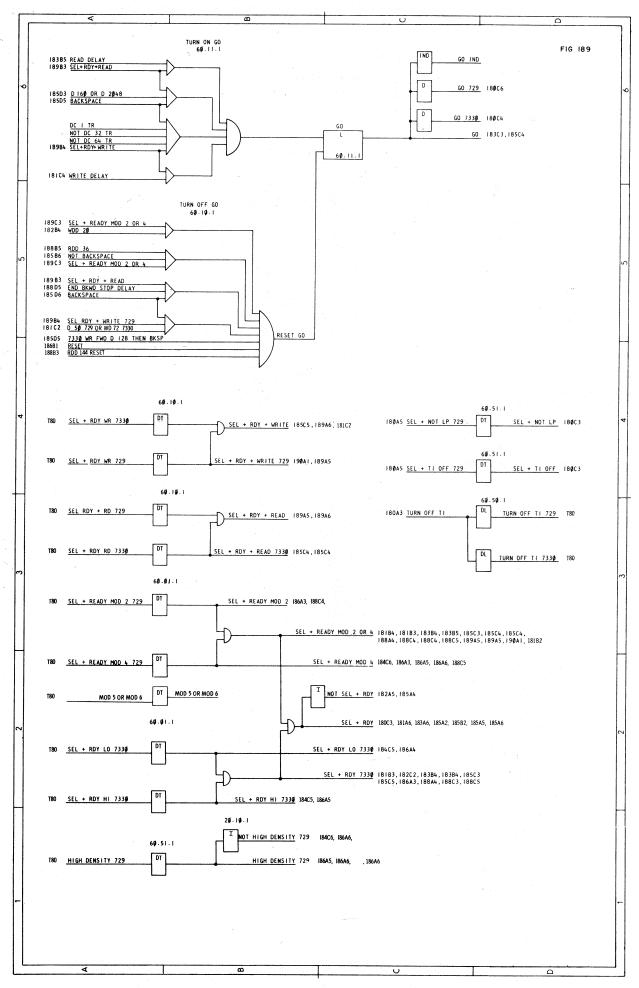

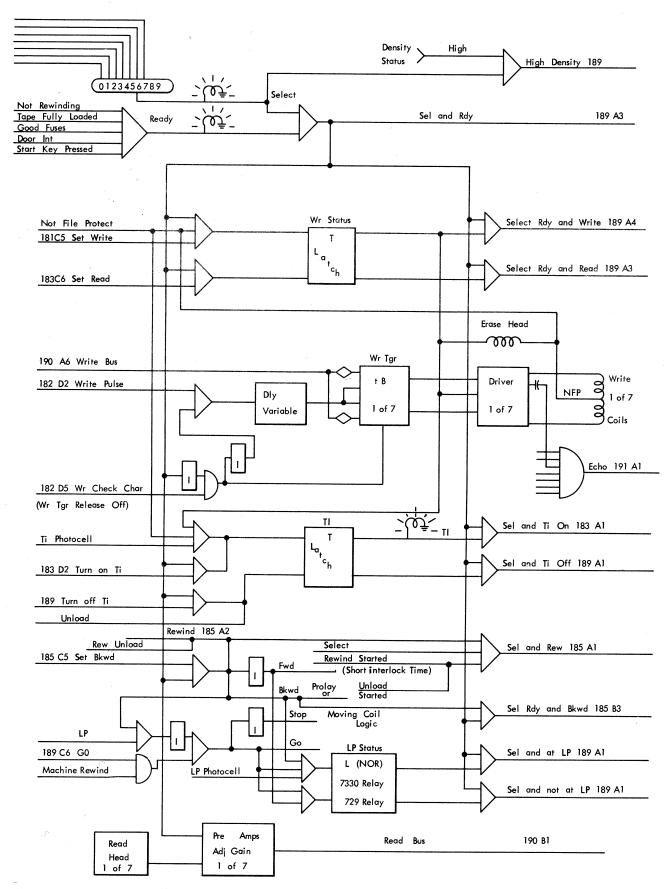

| 25.   | Write Circuits 61                                    | 189.  | Go and Tape Drive Inputs                        | . 104 |

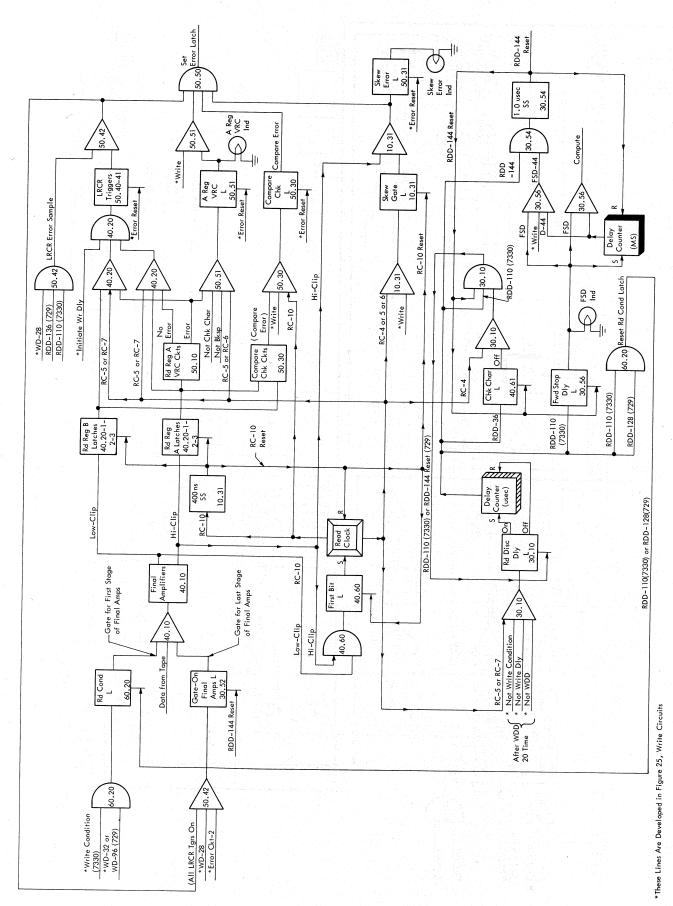

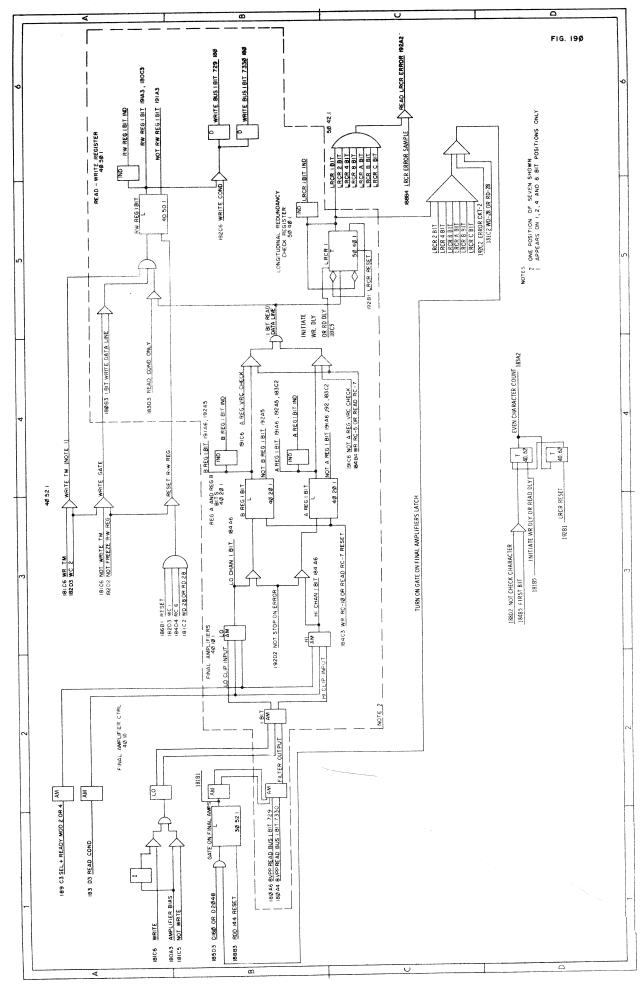

| 26.   | Read Check of Write Operation Circuits               | 190.  | Final Amplifiers                                | . 105 |

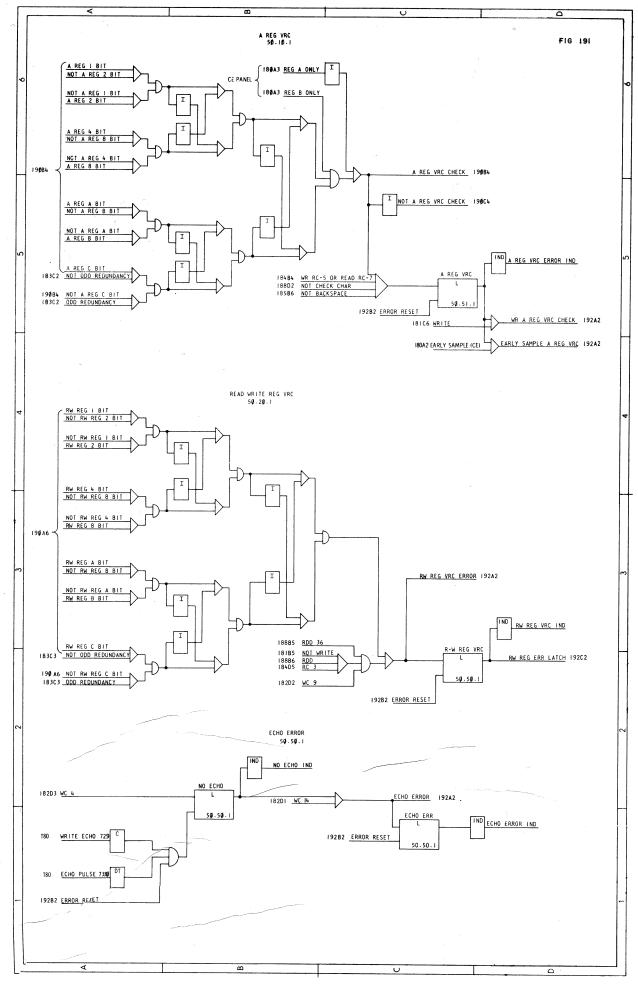

| 27.   | Simplified Write Operation Sequence 63               | 191.  | Error Circuits 1                                | 106   |

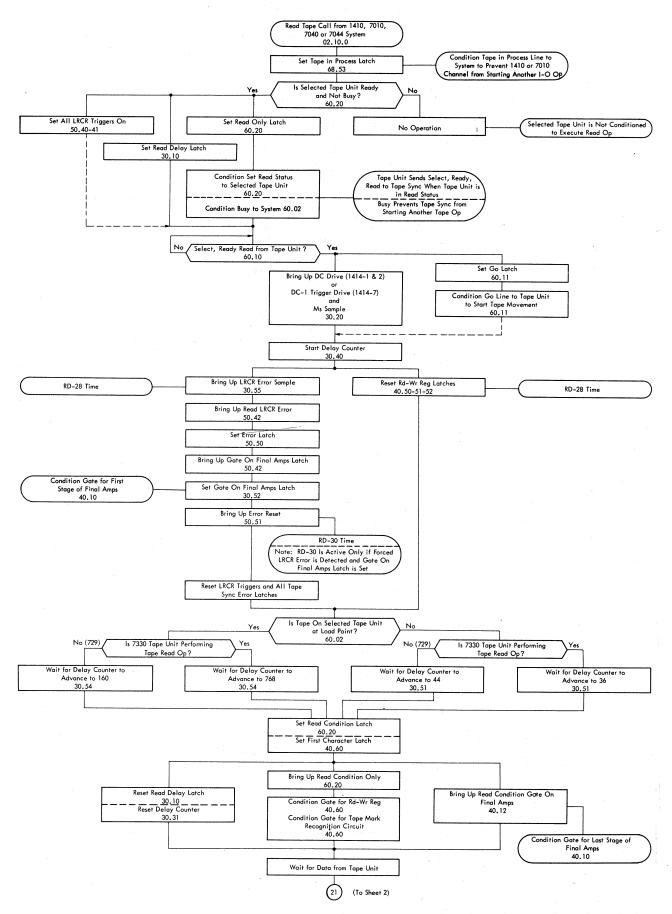

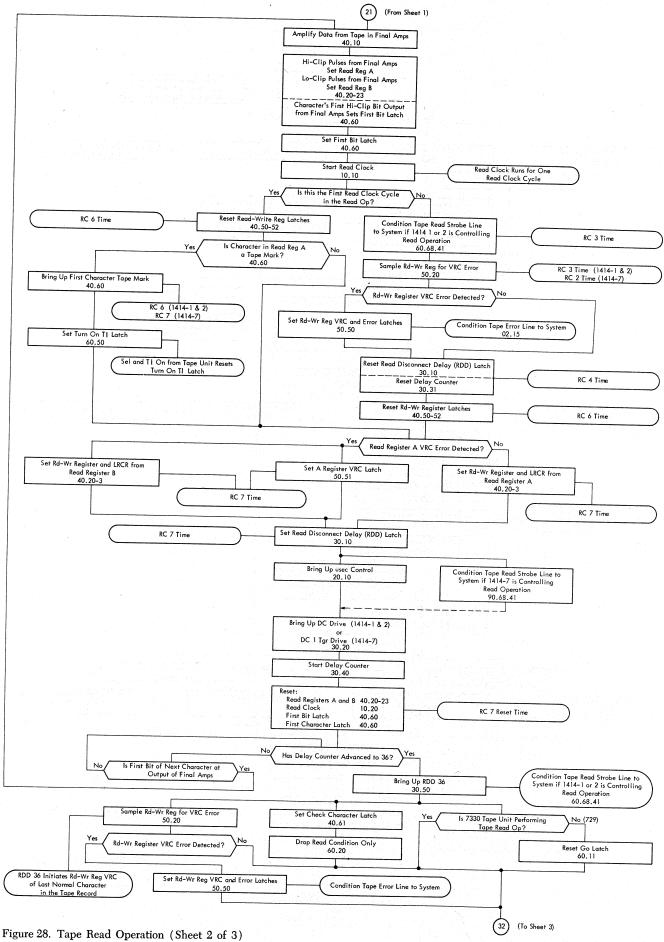

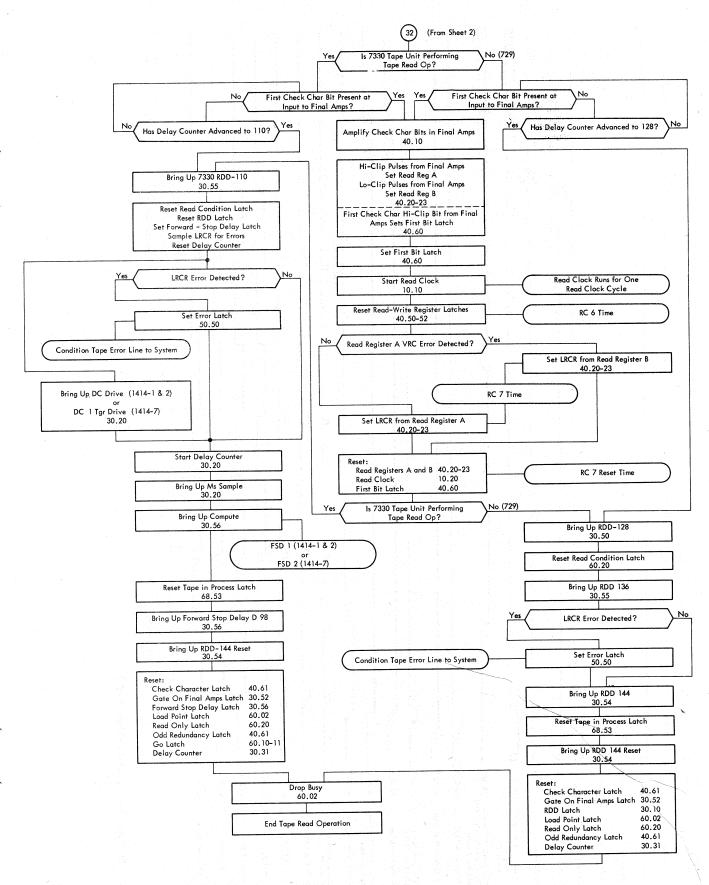

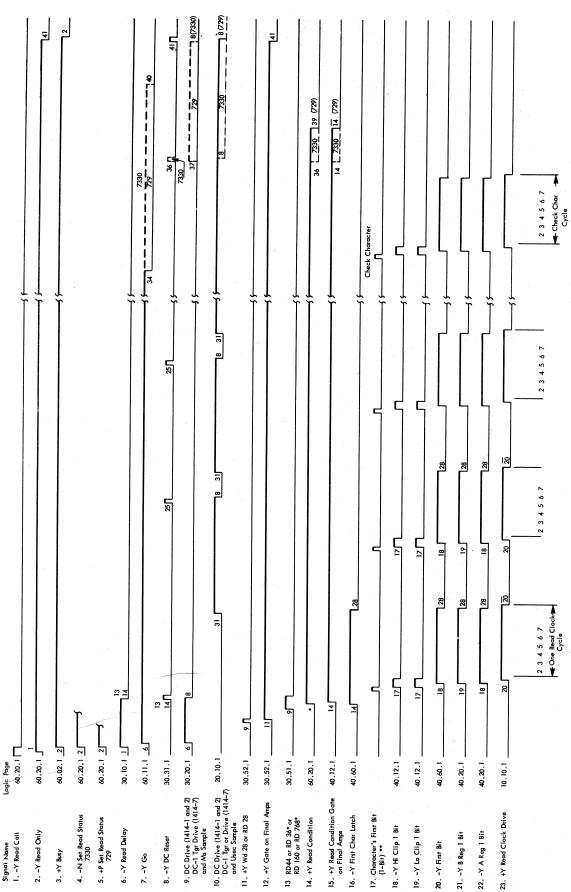

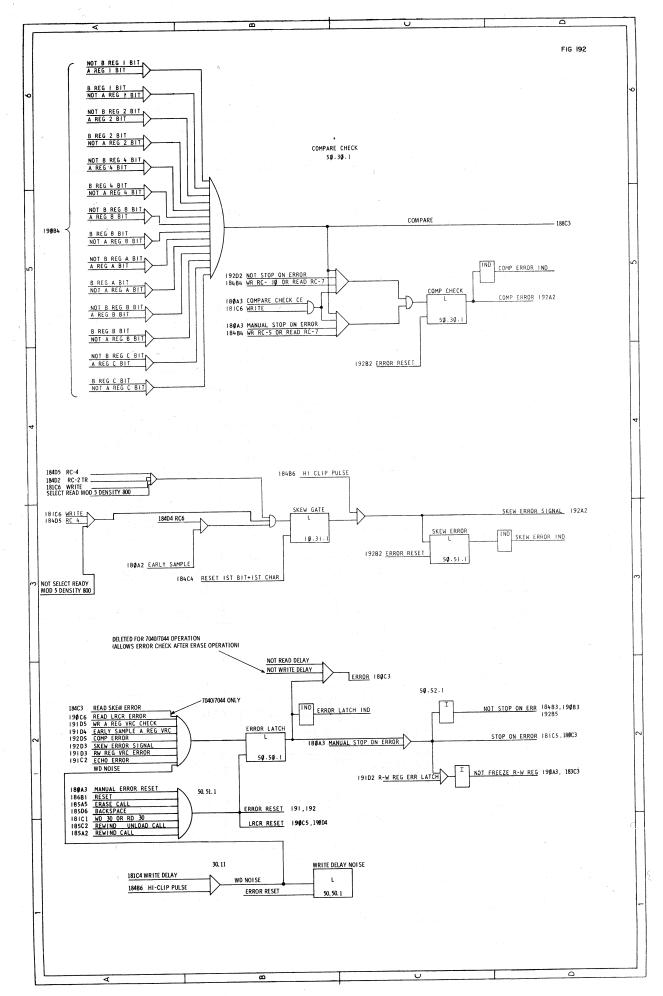

| 28.   | Tape Read Operation (Sheets 1-3) 67-69               | 192.  | Error Circuits II                               | 107   |

| 29.   | Tape Read Timings (Sheets 1 and 2)                   | Т 80. | Tape Unit Response Logic                        | 108   |

| 30.   | Read Circuits 79                                     |       |                                                 |       |

The IBM 1414 (Models 1, 2, and 7) Input-Output Synchronizer controls magnetic tape units operation with the IBM 1410, 7010, 7040, and 7044 Data Processing Systems. Because other models of the 1414 Input-Output (I-O) Synchronizer perform different functions, Models 1, 2, and 7 are called tape synchronizers.

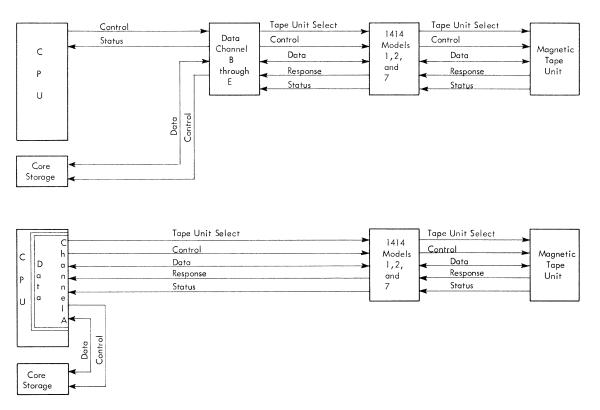

Channels E and F on the 1410 System and channels E, F, G, and H on the 7010 System can accommodate one 1414 tape synchronizer per channel. On the 7040 and 7044 Systems, one 1414 tape synchronizer can be attached to data channels A, B, C, D, and E.

Each 1414 tape synchronizer includes a tape adapter unit and a control section.

The tape adapter unit:

- 1. Controls tape movement on the selected tape unit.

- 2. Supplies signals that the tape unit requires to write characters on magnetic tape.

- 3. Checks all characters written on magnetic tape. The control section:

- 1. Provides for off-line testing of the tape synchronizer and tape units.

- 2. Processes all signals between the processing unit (1410/7010) or data channel (7040/7044) and the 1414 tape synchronizer.

Corresponding circuits in each tape synchronizer model function to accomplish the same purpose; data flow paths in the 1414 Models 1, 2, and 7 are identical. Only timings differ to perform specific functions in various tape unit models. Figure 1 lists the tape units that can be attached to each 1414 tape synchronizer model. Characteristics of magnetic tape units that 1414 tape synchronizers control are listed in Figure 2.

| Tape Synchronizer Model                      | Tape Units                                |

|----------------------------------------------|-------------------------------------------|

| 1414-1                                       | 729 II and 729 IV                         |

| 1414–1 With Intermix Feature                 | 729 II, 729 IV, and 7330                  |

| 1414-1 With 800 cpi Feature                  | 729 II, 729 IV and 729 V                  |

| 1414–1 With Intermix and 800 cpi<br>Features | 729 II, 729 IV, 729 V, and 7330           |

| 1414-2                                       | 7330                                      |

| 1414-7                                       | 729 II, 729 IV, 729 V, and 729 VI         |

| 1414–7 With Intermix Features                | 729 II, 729 IV, 729 V, 729 VI<br>and 7330 |

Figure 1. Tape Units Attached to 1414 Tape Synchronizer

The tape synchronizer processes all signals between the processing unit (1410/7010) or the data channel (7040/7044) and the selected tape unit (Figure 3). Because magnetic tape units are basically tape transport devices with the capacity to read and write characters, the tape synchronizer supplies all timings necessary to execute tape operations. To begin a tape operation, the processing unit (1410/7010) or the data channel (7040/7044) must condition control lines to the tape synchronizer designating a tape unit and the tape operation to be performed. The tape synchronizer assumes control and directs the specified operation. The tape synchronizer has the capacity to store only one character at a time; therefore, the tape synchronizer controls all data transfers between the processing unit or data channel and the selected tape unit.

The 729 II, IV, and 7330 tape units operate at one of two densities, 200 or 556 characters-per-inch (cpi). The 729 V and VI tape units operate at one of three

| Tape Unit                                      | 72     | 9 11   | 729    | IV .   |        | 729 V  |        |        | 729 V  | 1      | 73    | 30     |

|------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-------|--------|

| Tape Speed<br>(Inches per Second)              |        | 75     | 11:    | 2.5    |        | 75     |        |        | 112.5  | 5      | ;     | 36     |

| Density<br>(Characters per Inch)               | 200    | 556    | 200    | 556    | 200    | 556    | 800    | 200    | 556    | 800    | 200   | 556    |

| Characters per Second                          | 15,000 | 41,667 | 22,500 | 62,500 | 15,000 | 41,667 | 60,000 | 22,500 | 62,500 | 90,000 | 7,200 | 20,016 |

| Average Tape Access Time (Milliseconds)        | 1      | 0.8    |        | 7.3    |        | 10.8   |        |        | 7.3    | 3      | 20    | 8.0    |

| Character Time<br>(Microseconds per Character) | 67.2   | 24     | 44.7   | 16     | 67.2   | 24     | 17     | 44.7   | 16     | 11     | 139   | 50     |

Figure 2. Magnetic Tape Unit Characteristics

densities, 200, 556, or 800 characters-per-inch (cpi). Changing the operating density of a tape unit is a manual operation. Because 729 II, IV, and 7330 tape units record characters at only two densities, the HIGHLOW density switch setting on the selected tape unit determines the operating density. In high density, 729 II, IV, and 7330 tape units read or write characters at 556 cpi; in low density, these tape units operate at 200 cpi. A three-position tape density switch for each channel to which a tape synchronizer is attached is installed on the operator's console for density selections on 729 V and VI tape units. The positions of the controlling tape density switch and the HIGH-LOW

density switch on the 729 v or vI tape unit determine the density at which the 729 v or vI tape unit operates. If the appropriate console tape density switch is in the high position, the HICH-LOW density switch on the tape unit selects either 800 cpi (high) or 556 cpi (low) operation. If the console tape density switch is in the low position, the HICH-LOW density switch on the unit selects 556 cpi (high) or 200 cpi (low) operation. The center position of the console tape density switch allows the HICH-LOW density switch on the 729 v or vI tape unit to select 200 cpi (low) or 800 cpi (high) operation. The console tape density switches do not affect density selections for 729 II, IV, or 7330 tape units.

\* 1410/7010 Operation Only

Figure 3. Tape Synchronizer-System Relation

# 7040/7044 Channel Tape Operations

The three magnetic tape operations are read, write, and unit control. In a tape read operation, the selected tape unit reads characters from magnetic tape and transfers data through the tape synchronizer to core storage. In a tape write operation, the selected channel transfers characters through the tape synchronizer to the designated tape unit; the tape unit records characters on magnetic tape. A tape unit control instruction specifies one of five tape operations: rewind, rewind and unload, backspace, write blank tape, or write end of file. Only tape read and write operations require data transfers between core storage and a magnetic tape unit. The IBM 7040 and 7044 Data Processing Systems either use data channels and tape synchronizers as intermediate units between core storage and the selected tape unit (Figure 4) or direct tape operations to an on-line IBM 1401 Data Processing System. A tape synchronizer is not used when a 1401 system controls the tape operation.

Instructions to the processing unit initiate all magnetic tape operations. The instructions specify:

- 1. The data channel and the tape unit.

- 2. A tape operation.

If the instruction designates the tape read or write operation, the instruction must also supply the following information to the channel.

- 3. The starting core storage address.

- 4. The number of words to be processed to (input) or taken from (output) storage.

- 5. Binary or BCD mode.

The processing unit assigns system control of the input-output (1-0) operation to the data channel that the tape instruction specifies.

# **Data Channel Tape Operation**

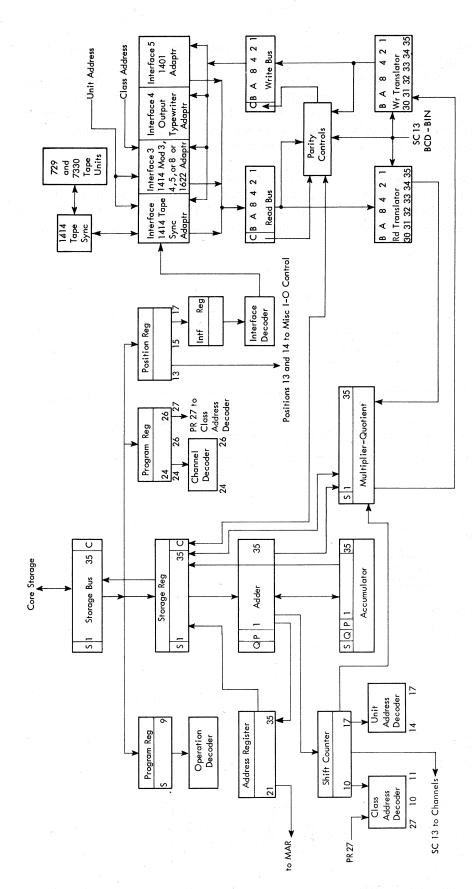

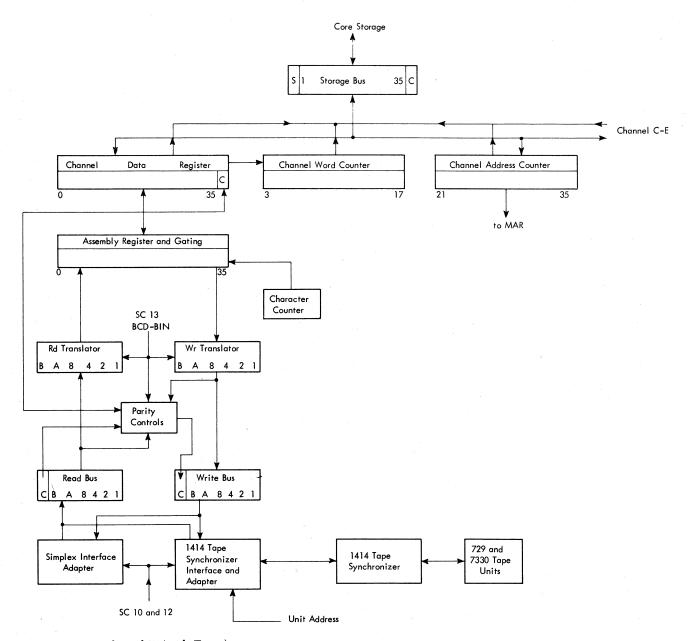

IBM 7040/7044 Data Processing Systems use the command word technique to pass control of r-o operations from the central processing unit (CPU) to data channels. The channels perform such functions as word counting, address modification, assembly of bytes

Figure 4. 7040/7044 Tape Operation Data Flow

(characters) into CPU words, disassembly of words into bytes, code translation, and parity assignment and checking.

# **Data Channel A Tape Operation**

Data channel A uses CPU registers and data paths to perform I-O control functions (Figure 5); therefore, channel A tape and CPU operations cannot be overlapped.

The CPU starts an 1-0 operation when it decodes a select instruction. The output of the channel A interface decoder selects the interface and unit that the instruction designates. Execution of the select instruction is not completed until the 1-0 unit is in ready status. When selection is complete, the channel terminates select operation, and CPU decodes the next instruction. Normally, the reset and load channel A (RCHA) instruction follows the select instruction to specify the core storage location in which the channel command is stored. When CPU executes the RCHA instruction, it places the channel command in the accumulator register (AC). The command specifies the number of words to be either transmitted or received and the address of the storage position in which the first word is to be stored or from which the first word is to be taken. The shift counter is set to six. When a word (36 bits) is processed:

- 1. The address part of the command word (ac positions 21-35) is modified to indicate the next sequential storage position.

- 2. The shift counter (decreased by one each time that six bits are processed on the channel) is reduced to zero.

- 3. The word counter is decreased by one.

If the word count is not reduced to zero when a complete word is processed, the address part of the command word transfers to the address register (AR), the shift counter is reset to six, and the channel receives or transmits another word. If the word count is zero, the channel ends execution of the RCHA instruction.

# READ OPERATION

The tape synchronizer sends seven bit characters (six data bits and check bit) to channel A. The channel removes the check bit and tests the character (byte) for a parity error. A parity error causes the channel redundancy check indicator to turn on, but the read operation continues. Depending on the mask controlling trapping, the channel may or may not transmit succeeding words to core storage. If no parity error is detected, the six data bits are set in the multiplier-quotient register (MQ) in positions 30-35; the shift counter, set to six at the beginning of the operation,

is reduced by one, and bits in the Mo are shifted left six positions. When the tape synchronizer transfers the next data byte to the channel, the channel loads the six data bits in MQ positions 30-35, reduces the shift counter by one, and shifts bits in the MQ left six positions. The channel loads six bit bytes in the mo until the shift counter is reduced to zero, indicating that a complete word has been assembled. The word in the Mo is placed in the storage register to be transferred to the location that the AR specifies; a check bit is then assigned to the storage register. The address count is increased by one to indicate the address of the storage position into which the next word will be loaded. The word count is decreased by one. If the word count is not zero after the reduction, the shift counter is again set to six, and channel A assembles the next word from tape synchronizer bytes. If the word count is set to zero, the channel does not write more characters in core storage, but the tape synchronizer continues to make characters available to the channel until the tane unit reads the complete record. When the tape unit reads the last character in the record and the tape synchronizer completes checks on the record written, the tape synchronizer signals the channel that the read operation is complete. Channel A terminates operation on the RCHA instruction and disconnects the tape synchronizer. The channel also ends operation on the RCHA instruction if the tape synchronizer signals the channel that the read operation is complete before the word counter is decreased to zero.

### WRITE OPERATION

The word in the core storage location that the AR designates is set in the Mo. Data bits in Mo positions S, 1-5 transfer to parity generating circuits where a check bit is added to the six data bits if the tape record is to be written in odd parity. The channel then transmits the byte to the tape synchronizer. Bits in the MQ are shifted left six positions; the shift counter, set to six earlier in the operation, is reduced to zero, indicating that a 36-bit word has been disassembled and transferred to the tape synchronizer. While the word is being disassembled, the channel performs command modification by setting the address in the adders, incrementing the address by one, and returning the address to the AC (positions 21-35). During disassembly, the word count (AC positions 3-17) is reduced by one. If the word count is not zero after the reduction, the address transfers to the AR; the shift counter is reset to six when the tape synchronizer accepts the complete word. If the word count is zero, the channel ends operation on the RCHA instruction and disconnects the tape synchronizer when the complete word is transferred.

Figure 5. Data Channel A

# **IBM 7904 Data Channel Tape Operation**

The IBM 7904 Data Channel is attached to the 7040/7044 systems as channels B, C, D, and E. Each 7904 data channel contains registers which allow channels B through E to perform I-o control operations independent of the CPU (Figure 6). A description of 7904 data channel registers used in tape operations is as follows:

Data Register: The 37-bit position data register is a buffer between core storage and the assembly register. The data register accepts inputs from the storage bus and the assembly register. In magnetic tape operations, the data register is similar in function to the channel A storage register.

Word Counter: The 15-position word counter indicates the number of words to be processed in the tape operation. Bits loaded in the word counter transfer from the storage bus through the data register. The word counter is decreased by one as each word is processed.

Address Counter: The 15-position address counter indicates the address of the core storage location into which the next word will be stored or from which the next word will be unloaded. Data from the storage bus

Figure 6. Data Channel B (with Tapes)

loads the address counter. The address counter is increased by one as each word is processed.

Assembly Register: The 36-position assembly register is a buffer between the data register and the tape synchronizer. The assembly register assembles and disassembles words in tape operations in channels B through E as the MQ assembles and disassembles words in channel A tape operations. A character counter in the 7904 data channel selects one of six character positions in the assembly register to be loaded or unloaded in one parallel operation. Like the shift counter in Channel A, the character counter steps six times for each CPU word (once for each six bit byte). However, characters are processed directly from their assembly register positions; bits in the assembly register are not shifted.

The 7904 data channel performs tape operations in basically the same manner as data channel A executes the operations. The outstanding difference is that CPU registers are not used with the 7904, and, therefore, the CPU and the 7904 data channels can operate independently (Figure 6). Even when all 7904 data channels are executing 1-0 operations the CPU is only required to transfer words to or from core storage. When channel A is in use, CPU cannot perform a different operation since the CPU and channel A share the same registers. However, four 7904 data channels and data channel A can perform 1-0 operations simultaneously.

# Select Instructions

Select instructions effect the selection and control of I-O devices. All select instructions accomplish the following functions.

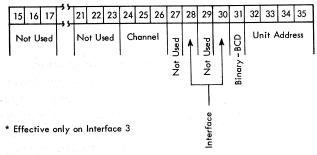

- 1. Bit positions 24 through 30 and 32 through 35 in select instructions identify the 1-0 unit or buffer and the data channel to perform the operation.

- 2. When required, bit position 31 in a select instruction specifies the appropriate code translator to allow automatic translation from one form of BCD coding to another form of BCD coding.

- 3. When data channel A performs the 1-0 operation, bit positions 15, 16, and 17 identify the interface to be used.

- 4. Bit positions S, and 3 through 11 determine whether the 1-0 operation is input (from 1-0 to core storage) or output (from core storage to 1-0).

- 5. Select instructions prepare the data channel to accept the channel command word (IORD); a subsequent reset and load channel (RCH) instruction causes the command word to transfer to the channel.

- 6. When a select instruction designates a magnetic tape operation, the instruction initiates action to start tape movement on the specified tape unit. Figure 7

| Channel | Interface | BCD Mode | Addresses | Binary Mod | le Addresses |

|---------|-----------|----------|-----------|------------|--------------|

| Α       | 0         | 01201    | 01212     | 01221      | 01232        |

| В       | N/A       | 02201    | 02212     | 02221      | 02232        |

| С       | N/A       | 03201    | 03212     | 03221      | 03232        |

| D       | N/A       | 04201    | 04212     | 04221      | 04232        |

| Е       | N/A       | 05201    | 05212     | 05221      | 05232        |

Figure 7. Addresses of Magnetic Tape Units on Data Channels

### Channel A

| - | 15  | 10 | 5   | 17 | -51-       | 21 | 22    | 23 | 24 | 25   | 26  | 27    | 28                    | 29          | 30       | 31         | 32 | 33    | 34   | 35  |

|---|-----|----|-----|----|------------|----|-------|----|----|------|-----|-------|-----------------------|-------------|----------|------------|----|-------|------|-----|

|   | Int | er | fac | е  | <b>-,,</b> | No | ot Us | æd | Cł | nanr | iel | Class | Address 7<br>(Type of | I-O Device) | Not Used | Binary-BCD | Uı | nit A | ddre | ess |

# Channels B Through E

Figure 8. Breakdown of Address Part of Select Instruction

shows addresses of magnetic tape units on data channels. Figure 8 shows a breakdown of the address part of select instructions.

Ten tape unit select lines are routed from the data channel to the tape synchronizer. To permit the synchronizer to perform unit control instructions independent of channel control, the channel checks to determine if the tape synchronizer is busy before resetting the previous 1-0 operation and selecting a new tape unit.

## **Translation**

Because magnetic tape units can read and write in binary or BCD mode, the address part of the select instruction must specify BCD or binary operation. A zero in bit position 31 of the select instruction designates BCD mode; a one in bit position 31 designates binary mode

When the tape synchronizer transfers 7-bit BCD characters to the channel, zone bits in some characters

are altered so that characters A through Z are represented in core storage by 6-bit binary numbers of increasing magnitude. Altered zone bits are shown in Figure 9.

Six-bit binary numbers 000 001 through 001 001 represent digits 1 through 9; the zone part of the digits is 00. The digit zero is represented on tape by the bit configuration 001 010; the bit configuration 000 000 represents the digit zero in core storage. The read translator in the data channel alters characters in BCD read operations so that their codes are compatible with the unit to which they are being transferred. During a BCD write operation, the write translator in the data channel translates core storage characters into tape BCD form.

| Class       | In Core | Storage | On  | Таре |

|-------------|---------|---------|-----|------|

|             | В       | Α       | В   | Α    |

| Numeric     | 0       | 0       | 0   | 0    |

| A Through I | 0       | 1       | . 1 | 1    |

| J Through R | 1       | 0       | 1   | 0    |

| S Through Z | 1       | 1       | 0   | 1    |

Figure 9. Zone Bit Alteration

# Read, Write, Sense, and Control Select Instructions

If the channel-in-use indicator is on when CPU decodes a read, write, sense, or control select instruction, execution of the instruction is delayed until the channel-in-use indicator is turned off. A WRS, WBT, or WEF, to a file protected tape unit on overlap channel hangs-up the selected channel (channel-in-use stays on).

## Read Select (RDS)

The read select instruction conditions the designated data channel to receive data from the 1-0 device that I and Y specify; the channel processes data from the 1-0 unit to core storage. Only bit positions 28 through 35 are subject to effective address modification; bit position 14 must contain a zero.

# Write Select (WRS)

The write select instruction conditions the designated data channel to transmit data from core storage to the 1-0 device that I and Y specify. Only bit posi-

tions 28 through 35 are subject to effective address modification; bit position 14 must contain a zero.

# Sense Select (SEN)

The sense select instruction conditions the designated data channel to transmit status data from the 1-0 device that I and Y specify to core storage. Only bit positions 28 through 35 are subject to effective address modification; bit position 14 must contain a one. The sense select instruction causes a store and trap on 7090/7094 systems. If the select instruction addresses a device in BCD mode, no translation occurs.

When an RCH instruction loads the channel with an IORD command with a word count greater than zero and follows a sense select instruction, the channel stores the following sense data in character position zero (Bits S, 1 through 5) of the first word.

S-bit (B-bit) not ready

3-bit (4-bit) rewinding (not ready indication is also given)

5-bit (1-bit) load point

In real time or teleprocessing applications, it is possible to lose information if the system cannot respond to an interrupt signal soon enough. The 7040/7044 systems select instructions have undesirable features in that they cause CPU to hang up if a not ready tape unit is selected. In order to minimize the hang up hazard, the sense select instruction is used to ascertain the ready status of a selected 1-0 device. The sense select instruction will not cause CPU to hang up if the channel is not in use, even if the addressed 1-0 device is not ready. A sense select instruction hangs up CPU if a non-existent channel is specified.

# **Control Select (CTR)**

The control select instruction conditions the channel to transmit control data from core storage to the 1-0 device that I and Y specify. Only positions 28 through 35 are subject to effective address modification; bit position 14 must contain a one. The control select instruction causes a store and trap on the 7090/7094 systems.

Although the control select instruction is not normally used with magnetic tapes, it initiates the same action that the write blank tape instruction causes.

# **Channel Control Instructions**

When a select instruction has conditioned the channel to transmit data to or from an r-o device, a reset and load channel (RCH) instruction must be given to deliver the command word to the channel. The command word contains a starting core storage address and a word count to control the transmission of data to or from core storage.

Because the select instruction initiates action to start tape movement on the specified tape unit, the RCH instruction must be executed within a definite time after the select instruction has been performed. Maximum times that should elapse between the execution of the select and RCH instructions are shown in Figure 10.

| Tape Unit | Read | explication of the second | Write |

|-----------|------|---------------------------|-------|

| 7330 - I  | 3.7  |                           | 6.2   |

| 729 - 11  | 4.0  |                           | 6.5   |

| 729 - IV  | 4.0  |                           | 6.5   |

| 729 - V   | 2.5  |                           | 4.0   |

| 729 - VI  | 2.5  |                           | 4.0   |

All Timings Are in Milliseconds and Allow for a 10% Variation in 1414 Tape Synchronizers

Figure 10. Maximum Times Between Select and RCH Instructions

In a write operation if either the CPU does not execute the RCH instruction within the specified time or the RCH instruction loads the channel with an IORD command with a word count of zero, the tape unit disconnects, the I-O check indicator turns on, and the channel-in-use indicator turns off. In a read operation, the channel checks parity for the entire tape record even if an RCH instruction is not given.

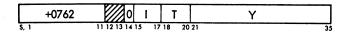

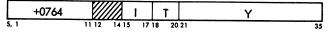

# Reset and Load Channel Instruction (RCH)

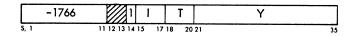

| OP CODE | F 0 T                   | Υ     |

|---------|-------------------------|-------|

| S, 1    | 11 12 13 14 16 17 18 20 | 21 35 |

| MNEMONIC | OP CODE | CHANNEL  |

|----------|---------|----------|

| RCHA     | +0540   | <b>A</b> |

| RCHB     | -0540   | В        |

| RCHC     | +0541   | C        |

| RCHD     | -0541   | <b>D</b> |

| RCHE     | +0542   | E        |

|          |         |          |

If a select instruction has conditioned the channel, the contents of Y, c(y), transfer to the channel as a command word; the channel can then transmit data to or from the selected 1-0 device. If a select instruction has not conditioned the channel, the 1-0 check indicator turns on; the c(y) are sent to the channel as a command word, but transmission does not occur.

If a second RCH instruction is given to a channel already in operation, the c(y) transfer to the channel and replace the previous command word. Transmission continues with the new address and word count. A second RCH instruction cannot be issued to channel A; overlap operation cannot occur on channel A.

Because timings vary between the data channels on the 7040/7044 systems and the data channels on the 7090/7094 systems and between the overlap and non-overlap channels on the 7040/7044 systems, the selected channel should be tested to be sure that it is no longer in use prior to using the data area assigned to the channel. This test can be performed by executing a TCOX instruction.

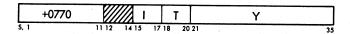

Input-Output of a Record and Disconnect (IORD) Command

| +3     | WORD | COUNT | 0  |       | STARTING ADDRESS | ]  |

|--------|------|-------|----|-------|------------------|----|

| S, 1 2 | 3    | 17    | 18 | 20 21 |                  | 35 |

Execution of the RCH instruction causes the channel command word (IORD) to transfer to the channel to control the tape operation. The IORD command word provides:

- 1. a 15-bit word count that specifies the number of words to be transferred between core storage and the tape unit.

- 2. a 15-bit starting address that specifies the location in core storage for the first word of the record. Additional words are taken from or sent to successively higher locations in storage until either the 1-0 device reads the end of the record or the number of words specified in the word count have been transmitted.

The 7040/7044 systems do not interpret positions S, 1, 2, 18, 19, and 20 when the IORD is used as a channel command word.

The iord may appear at any point in the program. If the iord transfers to the CPU operation decoder as an instruction word (during I cycle), the iord is interpreted as a TXH instruction because of the +3 prefix. A TXH instruction with no index register specified causes no operation; the next sequential instruction is performed. Thus, the CPU processes an iord with a prefix of +3 and a tag of zero as an NOP instruction.

# **Tape Control Instructions**

If the channel-in-use indicator is on when cru decodes a unit control instruction (write end of file, write blank tape, backspace record, rewind, or rewind unload), execution of the instruction is delayed until the channel-in-use indicator turns off. A unit control instruction or a select instruction turns on the designated channel's channel-in-use indicator. The channel-in-use indicator turns off when the specified 1-0 operation is completed.

# **Tape Data Compatibility**

If the first character of a BCD tape record is a tape mark (8, 4, 2, and 1-bits) in the 7090/7094 systems, the tape mark and the following character are replaced by zeros, and the redundancy check indicator is set. If the first character of a BCD tape record is a tape mark in the 7040/7044 systems, all characters are received properly, and the redundancy check indicator is not set. For example, if the first six characters of a BCD tape record are VABCDE, the following word appears in core storage after the tape read operation.

7040/7044  $\sqrt{\text{ABCDE}}$  7090/7094 00BCDE -----the redundancy check indicator lights.

Tape marks should not be written as the first characters of BCD records for 7090 program compatibility considerations.

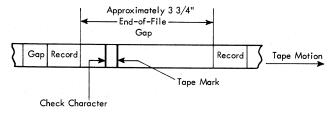

# Write End-of-File (WEF) Instruction

The write end of file instruction causes the channel to condition the write tape mark call and erase call lines to the tape synchronizer. The selected tape unit erases a 3½ inches end of file gap and writes a tape mark (with the check character) on tape (Figure 11). The 3½ inches end of file gap is required for compatibility with the IBM 7040 Data Processing System when operating in binary mode. An end of tape reflective spot encountered during execution of the wef instruction turns on the end of tape indicator. Only positions 28 through 35 of the address part of the instruction are subject to effective address modification.

# Write Blank Tape (WBT) Instruction

Figure 11. End-Of-File-Gap

The write blank tape instruction causes the channel to condition "erase call" and then "write call" to the tape synchronizer. The selected tape unit erases a section of tape approximately 3% inches in length. The WBT instruction is used to space over bad spots on tape that cause redundancy checks. An end of tape reflective spot encountered during execution of the WBT instruction causes the end of tape indicator to turn on. The 7090/7094 systems execute a write blank tape operation when a write select (wrs) instruction not followed by a reset and load channel (RCH) instruction is detected. Because the 7090/7094 Systems decode the 7040/7044 wer instructions as a was instruction, an RCH instruction should not follow a WBT instruction for 7090/7094 program compatibility. If a subsequent RCH instruction is given, the IORD command should specify a zero word count.

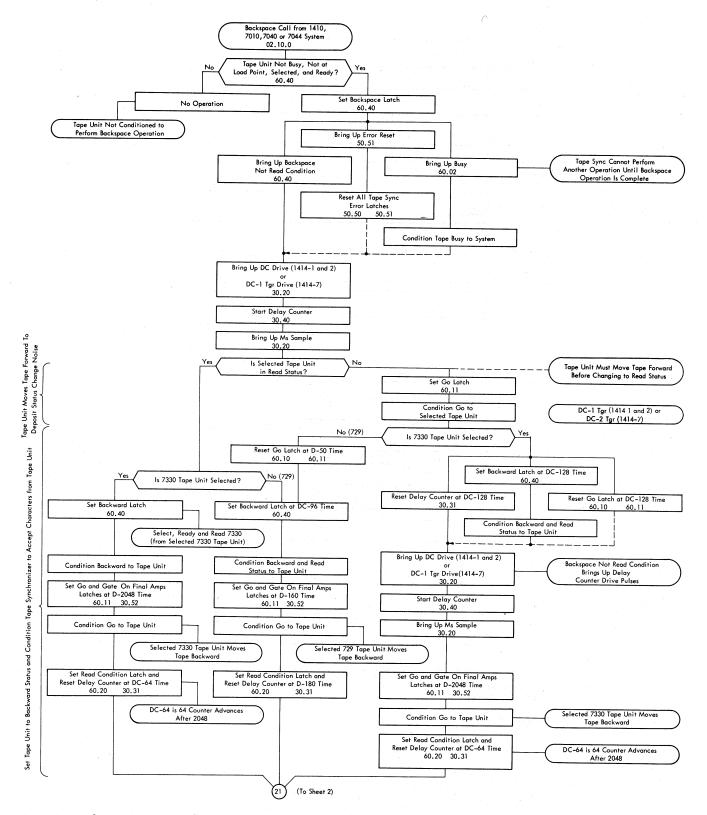

### **Backspace Record (BSR) Instruction**

The backspace record instruction causes the channel to condition "backspace call" to the 1414 tape synchronizer. The selected tape unit moves tape backward through one tape record or to load point; tape movement stops when either the interrecord gap or load point is sensed. The tape synchronizer performs no checks during execution of the backspace operation. If the selected tape unit is at load point when the BSR instruction is given, no operation occurs. Only bit positions 28 through 35 of the address part of the instruction are subject to effective address modification.

# Rewind (REW) Instruction

The rewind instruction causes the channel to condition "rewind call" to the 1414 tape synchronizer. The

selected tape unit rewinds tape to the load point position. If tape is positioned at load point when the tape synchronizer receives "rewind call," no operation occurs. Only bit positions 28 through 35 of the address part of the REW instruction are subject to effective address modification. When a 7330 tape unit is selected to perform the operation, the REW instruction causes the tape unit to rewind tape at low speed regardless of the amount of tape on the machine reel.

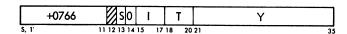

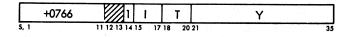

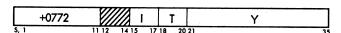

# Rewind and Unload (RUN) Instruction

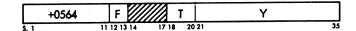

| -077 | 2     |        |       | T     | Υ |    |

|------|-------|--------|-------|-------|---|----|

| S, 1 | 11 12 | .14 15 | 17 18 | 20 21 |   | 35 |

The rewind and unload instruction causes the channel to condition "rewind unload call" to the 1414 tape synchronizer. The selected tape unit rewinds tape to the load point position and unloads tape. When a 7330 tape unit is selected to perform the operation, the RUN instruction causes the tape to unload and rewind tape at high speed. If a 7330 tape unit is at load point when the channel conditions "rewind unload call" to the tape synchronizer, the RUN instruction "hangs up" the channel. If a 729 tape unit is at load point when the channel issues "rewind unload call" to the tape synchronizer, the tape unit performs an unload operation.

# Channel Instructions That Apply Only To Magnetic Tapes

### **End of Tape Indicator**

When the tape unit senses the reflective strip marking the end of tape in a write, write end of file, or write blank tape operation, the end-of-tape indicator in the channel turns on. The tape operation is not interrupted; writing can be completed even though the end of tape marker has been sensed. If CPU initiates another operation causing tape to move forward, tape may be pulled from the file reel. The end-of-tape indicator is not turned on during a read operation.

# **End of Tape Test (ETTX) Instruction**

The end of tape test instruction tests the status of end-of-tape indicator on the data channel that the address part of the instruction specifies. Addresses for the channels are:

Channel A 01000

| Channel B | 02000 |

|-----------|-------|

| Channel C | 03000 |

| Channel D | 04000 |

| Channel E | 05000 |

If the end-of-tape indicator for the specified data channel is on, execution of the end of tape test instruction turns the indicator off; CPU performs the next sequential instruction. If the indicator is off, the instruction causes CPU to skip the next instruction and execute the second instruction in sequence.

# Other Applicable Instructions

# **Redundancy Check Indicator**

The channel redundancy check indicator can be turned on at any time during a tape read or write operation by one of the following tape synchronizer error conditions:

Read/write register vnc error

Longitudinal redundancy check register error

Skew error (write operation)

Write compare error (write operation)

Write echo error (write operation)

Read register A vRc error (write operation)

Write delay noise (write operation)

The data channel turns on the redundancy check indicator if it detects a parity error in the data received in a read or sense operation.

### Transfer on Redundancy Check (TRCX) Instruction

If the redundancy check indicator for the specified channel is on, execution of the TRCX instruction turns off the indicator, and the CPU takes the next instruction from location Y. If the indicator is off when the CPU executes the TRCX instruction, the CPU performs the next instruction in sequence. If the channel parity enable mask bit is set to one, the TRCX instruction is not effective; execution of the instruction does not turn off the redundancy check indicator, and no transfer is taken if the indicator is on. The instruction designates data channels in the following manner.

| TRCA | +0022 | Transfer on channel A redundancy             |

|------|-------|----------------------------------------------|

| TRCB | -0022 | Transfer on channel B redundancy             |

| TRCC | +0024 | Transfer on channel C redundancy             |

| TRCD | -0024 | check<br>Transfer on channel D redundancy    |

| TRCE | +0026 | check Transfer on channel E redundancy check |

### **End of File Indicator**

When the tape unit reads a single character tape mark record during a channel tape read operation, the channel end of file indicator turns on and disconnects the tape synchronizer through a normal read disconnect (EOR). The end of file indicator does not turn on when a tape mark (end of file character) is written on tape.

# Transfer on End of File (TEFX) Instruction

If the end of file indicator for the specified data channel is on, the transfer on end of file instruction turns off the indicator and causes CPU to execute the instruction in core storage location Y. If the indicator is off, the transfer on end of file instruction causes the CPU to execute the next sequential instruction. The instruction designates data channels in the following manner.

| TEFA | +0030 | Transfer on channel A end of file |

|------|-------|-----------------------------------|

| TEFB | -0030 | Transfer on channel B end of file |

| TEFC | +0031 | Transfer on channel C end of file |

| TEFD | -0031 | Transfer on channel D end of file |

| TEFE | +0032 | Transfer on channel E end of file |

If the tape unit senses the end-of-file indication (single character tape mark record) during a read operation, the end of file indicator on the channel turns on and disconnects the tape synchronizer. If the channel operation enable bit is a one, the TEFX instruction does not cause a transfer or turn off the end of file indicator.

# **Channel In Use Indicator**

The channel in use indicator on each data channel is turned on when any select instruction or tape unit control instruction specifies that channel to perform an operation. The indicator is turned off when the designated operation is completed. If an RDS, PRD, WRS, PWR, SEN, CTR, BSR, WEF, REW, RUN, or WBT instruction is given while the channel in use indicator is on, execution of the new instruction is delayed until the previous operation is terminated and the channel in use indicator is turned off.

# Transfer on Channel in Operation (TCOX) Instruction

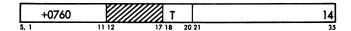

|    | OP CODE | F ///       | /// т |       | Y |    |

|----|---------|-------------|-------|-------|---|----|

| S, | 1       | 11 12 13 14 | 17 18 | 20 21 |   | 35 |

If the channel-in-use indicator for the specified channel is on when the CPU executes the TCOX instruction, the CPU performs the instruction in location Y. If the channel-in-use indicator is off, the CPU performs the next sequential instruction. The TCOX instruction does not effect channel operation. The instruction designates data channels in the following manner.

| TCOA | +0060 | Transfer on channel A in operation |

|------|-------|------------------------------------|

| тсов | +0061 | Transfer on channel B in operation |

| TCOC | +0062 | Transfer on channel C in operation |

| TCOD | +0063 | Transfer on channel D in operation |

| TCOE | +0064 | Transfer on channel E in operation |

# **Input-Output Check Indicator**

The 1-0 check indicator on the console turns on when:

- 1. An RCHX instruction is decoded, and the designated channel is not selected.

- 2. An IORD command with a zero word count follows a write select instruction to tape.

- 3. Write gate is inactive and the tape synchronizer has conditioned "write condition." This condition results when an RCHX instruction is not given soon enough; the tape synchronizer is reset.

- 4. The channel (B through E) data register or channel A storage register has not been loaded with a word from core storage by the time that its contents are to be sent to an output unit.

- 5. The channel (B through E) data register or channel A storage register has not transmitted its contents to core storage by the time that new data are available to be loaded in the register.

## Input-Output Check Test (IOT) Instruction

If the 1-0 check indicator is on when CPU executes the 10T instruction, the indicator turns off, and CPU performs the next sequential instruction. If the indicator is off, CPU skips the next instruction and performs the second instruction in sequence. Because the address in the instruction is part of the op code, any address modification may change the operation.

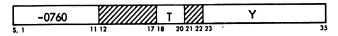

# Reset Data Channel (RDCX) Instruction

The reset data channel instruction resets all registers and indicators in the specified data channel (except in Channel A, the accumulator and MQ registers are not cleared). The channel terminates the I-O operation and disconnects the tape synchronizer immediates.

ately. If the instruction is executed while tape is in motion, tape movement stops regardless of the position of the tape head with respect to the interrecord gap. If the tape unit is rewinding tape, the rewind operation is completed. Status indicators previously set by an enable instruction are reset. The RDC instruction cancels the effect of a previous select instruction. The instruction designates data channels in the following manner:

| MNEMONIC OP CODE | ADDRESS | COMMENT              |

|------------------|---------|----------------------|

| +0760            | 01352   | Reset data channel A |

| +0760            | 02352   | Reset data channel B |

| RDCC $+0760$     | 03352   | Reset data channel C |

| RDCD + 0760      | 04352   | Reset data channel D |

| RDCE $+0760$     | 05352   | Reset data channel E |

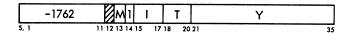

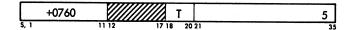

### Store Channel (SCHX) Instruction

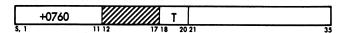

| OP CODE | F           | 0 т            | Υ |   |

|---------|-------------|----------------|---|---|

| S, 1    | 11 12 13 14 | 16 17 18 20 21 |   | 3 |

The store channel instruction replaces the contents of Y (bit positions 21-35) with the contents of the specified channel address counter. The contents of the channel word counter replace the contents of bit positions 3-17; bit positions S, 1, 2 and 18 through 20 are destroyed. Because channel A uses accumulator bit positions 3-17 for the word counter and 21-35 for the address counter, it is necessary to execute the store channel A instruction before changing the accumulator after a reset and load channel A instruction. Note, however, on channel A, bits 1-35 of accumulator are stored. A store channel instruction designating channels B through E can be executed even though the specified channel is in operation. If the channel is busy and the channel address register is in the process of changing, execution of the store channel instruction is delayed until the change is complete.

The address register is one greater than the storage location of the last word loaded in or taken from core storage. The instruction designates data channels in the following manner.

| SCHA | +0640      | Store channel A |

|------|------------|-----------------|

| SCHB | -0640      | Store channel B |

| SCHC | +0641      | Store channel C |

| SCHD | -0641      | Store channel D |

| SCHE | $\pm 0642$ | Store channel E |

# Channel Traps

A data channel can interrupt CPU processing by trapping the CPU program. One of many conditions can initiate a channel trap; conditions that apply to magnetic tape are as follows:

- 1. The completion of any channel operation

- 2. A redundancy check

- 3. An end of file (single character tape mark record)

- 4. A word parity check during a U or B cycle

- 5. An incomplete tape word (corporate interface unusual end)

When a channel trap occurs, the contents of the instruction counter are stored in the address portion of the store location. Bits indicating the conditions that caused the trap are loaded in the decrement section of the store location; other bits in the store location are destroyed. The CPU transfers to the instruction location for the next instruction; for 7090/7094 compatibility, the instruction should be an unconditional transfer. Store locations and instruction locations are as follows:

|              | STORE    | INSTRUCTION |

|--------------|----------|-------------|

| CHANNEL      | LOCATION | LOCATION    |

| $\mathbf{A}$ | 00012    | 00013       |

| В            | 00014    | 00015       |

| $\mathbf{C}$ | 00016    | 00017       |

| D            | 00020    | 00021       |

| E            | 00022    | 00023       |

A channel trap cannot occur if an executed trap or an inhibit channel traps instruction has reset the channel trap control.

### **Enable (ENB) Instruction**

Execution of each enable instruction cancels the effect of previous enable instructions and sets the channel mask bits to one or zero as indicated by the contents of Y. The enable instruction turns on channel trap control. Execution of a trap or inhibit channel traps instruction prevents further traps until CPU executes another enable or restore channel trap instruction. When either the reset or clear key is pressed or CPU executes a reset data channel instruction, all mask bits in the channel are set to zero.

ENB ZERO disables all channel and direct data traps and prevents the location of word parity errors in memory by use of the store channel instruction when a parity error occurs on a channel write operation. Therefore, the inhibit channel traps instruction should be used when necessary to prevent channel traps.

# **Inhibit Channel Traps (ICT) Instruction**

The inhibit channel traps instruction turns off channel trap control, inhibiting all channel traps and direct data traps until a new ENB or restore channel traps instruction is given. Because the address part of the instruction is part of the operation code, any address modification may change the operation.

### **Restore Channel Traps (RCT) Instruction**

The restore channel traps instruction turns on channel trap control, allowing traps to occur as specified by the previous enable instruction. The RCT instruction cancels the inhibiting effect of an executed channel trap or ICT instruction. The address in the instruction is part of the operation code; any address modification may change the operation.

# **Channel Trap Stores**

When a channel trap occurs, the condition(s) causing the trap are stored in the decrement part of the store location. Because more than one condition can set its bit position to a one simultaneously, all positions should be checked. Bit positions applicable to tape operations are:

# BIT POSITION IN THE

| 114 11112      |                    |               |

|----------------|--------------------|---------------|

| STORE LOCATION | INDICATOR          | MASK BIT NAME |

| 17             | Operation complete | Operation     |

| 16             | Redundancy check   | Parity        |

| 15             | End of file        | Operation     |

| 14             | Word parity        | Parity or     |

|                |                    | Operation     |

| 12             | Unusual end (tape  |               |

|                | word incomplete)   | Operation     |

### OPERATION COMPLETE

Bit 17 (operation complete) is turned on when the channel in use indicator changes from the on to the off state; this occurs either at the completion of every read, write, sense, and control operation (end of data transfer), or when the magnetic tape unit completes a BSR, WBT, or WEF operation or begins a REW or RUN operation. Even though bit 17 is stored when the indicator is on and a trap occurs (other conditions may be stored by the same trap), a TCOX instruction can be used to determine the status of the channel.

### REDUNDANCY CHECK

Either a parity error from the 1-0 device or a byte parity check in the channel turns on bit 16 (redundancy check). When the channel X parity mask bit is zero, a TRCX instruction can test and reset the redundancy check indicator. When the channel X parity mask bit is one, execution of the TRCX instruction does not transfer or turn off the indicator. When the parity mask bit is one and the redundancy check indicator is on, the channel stops the transfer of data to or from storage. The channel address register contains one plus the address of last word transferred. A trap or store operation does not occur if the channel is in use. In tape read operations, the designated data channel is in use while the tape unit reads the entire record even when data is not transferred to core storage. The parity bit masks the redundancy check indicator.

### END-OF-FILE

The end-of-file signal from the tape unit sets bit 15 (end-of-file). When the channel X operation mask bit is zero, a TEFX instruction can test and reset the end-of-file indicator. When the operation mask bit is one, execution of the TEFX instruction does not transfer or turn off the indicator. A trap or store operation does not occur if the channel is in use. The operation mask bit masks the end-of-file indicator.

### WORD PARITY

A word parity error during read or write (U or B) cycles to storage turns on bit 14 (word parity). The word parity bit can also be turned on during channel write operations by checking the 37th bit of a word with the sum of the six parity bits of a disassembled word. When the parity mask bit is one and the word parity indicator is on, the channel stops data transfers to or from core storage. The channel address register contains one plus the address of the last word transferred. Therefore, if the parity enable bit is one when an invalid word is taken from core storage during a write operation, an schx instruction stores one beyond the address of the invalid word. A trap or store operation does not occur if the channel is in use. When either the parity mask bit or the operation mask bit is one and the channel is not in use, the indicator may signal a trap and store.

Note: Two different mask bits can turn on the word parity indicator. The parity mask bit allows the channel to stop transmission when an error occurs, but the operation mask bit does not make this provision.

# UNUSUAL END (TAPE WORD INCOMPLETE)

If the total number of characters processed in the tape operation is not a multiple of six, bit 12 [unusual

end (tape word incomplete)] is set at the end of a tape read or write operation.

If the total number of characters in a tape record is not a multiple of six, the record probably contains an error. The unusual end indicator is not set when the tape unit reads the end of file character (tape mark). If this condition occurs while writing tape, a malfunction exists. At the completion of an iord, the simplex interface unusual end signal can also set the unusual end indicator. The indicator, masked by the operation mask bit, cannot signal a trap while the channel is in use.

# 1410/7010 Channel Tape Operations

The three magnetic tape operations are: read, write, and unit control. In a tape read operation, the selected tape unit reads characters from magnetic tape and transfers data through the tape synchronizer to core storage. In a tape write operation, the processing unit transfers core storage characters through the tape synchronizer to the designated tape unit; the tape unit records characters on magnetic tape. A tape unit control instruction specifies one of five tape operations: write tape mark, backspace, rewind, rewind unload, or erase. All tape instructions contain an operation code and select:

- 1. An input-output channel.

- 2. Overlap or unoverlap operation.

- 3. A tape unit.

- 4. A tape operation.

- 5. Odd or even parity operation.

In addition, tape read and write instructions designate a core storage address into which the first character is stored or from which the first character is taken and the condition(s) to end the operation. All 1410/7010 instructions designating magnetic tape operations are listed in Figure 12.

The processing unit checks the states of the tape synchronizer and the selected tape unit at status sample A time for all tape operations. If either the tape synchronizer is busy or the selected tape unit is not ready, the processing unit terminates the operation and decodes the next sequential instruction. In checking the state of the tape synchronizer, the processing unit examines the level of the tape busy line at I-ring 5 time to determine if the tape select register may be reset at I-ring 6 time. If the tape synchronizer is controlling another operation, the tape busy line prevents de-selecting of the tape unit. The processing unit sets the channel's busy status indicator latch and skips the designated tape instruction. The processing unit loads the channel's unit number register with the character designating the tape unit to perform the operation at I-ring 5 time (Last Logic Gate). The processor resets the tape select register in the tape synchronizer at I-ring 6 time (Logic Gate C), then conditions the tape select register in the tape synchronizer at I-ring 6 time (Last Logic Gate). The unit number register sets the tape select register at I-ring 6 time. The tape select register signals the designated tape unit. If the tape unit is in ready status, the tape unit conditions the select and ready line to the tape

| Character | Position in Instruction   | Function                                                   |

|-----------|---------------------------|------------------------------------------------------------|

| M         | Op Code (Read or Write)   | I-O Op Code Without Word Marks                             |

| or<br>L   | Op Code (Read or Write)   | I–O Op Code With Word Marks                                |

| U         | Op Code (Unit Control)    |                                                            |

| %         | X-Field 1                 | Use E Channel Unoverlap                                    |

| or<br>@   | X-Field 1                 | Use E Channel Overlap                                      |

| п         | X-Field 1                 | Use F Channel Unoverlap                                    |

| or<br>*   | X-Field 1                 | Use F Channel Overlap                                      |

| ?         | X-Field 1                 | Use G Channel Unoverlap (7010)                             |

| or<br>\$  | X-Field 1                 | Use G Channel Overlap (7010)                               |

| 1         | X-Field 1                 | Use H Channel Unoverlap (7010)                             |

| or<br>#   | X-Field 1                 | Use H Channel Overlap (7010)                               |

| U         | X-Field 2                 | Select Tape Operation (Even Parity)                        |

| or<br>B   | X-Field 2                 | Select Tape Operation (Odd Parity)                         |

| 0-9       | X-Field 3                 | Select Magnetic Tape Unit                                  |

| xxxx      | B-Address(Read or Write)  | High Order Position of the Field                           |

| W         | d-Modifier (Write)        | Write Tape to Group Mark-Word<br>Mark or to End of Storage |

| or<br>X   | d-Modifier (Write)        | Write Tape to End of Storage<br>(Unoverlap)                |

| R         | d-Modifier (Read)         | Read Tape to Group Mark-Word<br>Mark or to End of Storage  |

| or<br>\$  | d-Modifier (Read)         | Read Tape to End of Storage<br>(Unoverlap)                 |

| В         | d-Modifier (Unit Control) | Backspace a Tape Record                                    |

| E         | d-Modifier (Unit Control) | Skip and Blank Tape                                        |

| м         | d-Modifier (Unit Control) | Write a Tape Mark                                          |

| , R       | d-Modifier (Unit Control) | Rewind Tape                                                |

| U         | d-Modifier (Unit Control) | Rewind and Unload Tape                                     |

Figure 12. Format for Magnetic Tape Instructions

synchronizer. The tape synchronizer relays the ready indication to the processor, allowing the operation to proceed. If the selected tape unit is not conditioned to perform a tape operation, the processing unit sets the channel's not ready status indicator latch and decodes the next sequential instruction.

The write tape call, read tape call, or write tape mark call signal to the tape synchronizer causes the tape synchronizer to condition the tape in process and tape busy lines to the processing unit; "call" signals that initiate other tape operations cause the tape synchronizer to condition only the tape busy line. "Tape in process" blocks the set path to the channel's external end of transfer latch, holding the channel committed to the tape operation. "Tape busy" indicates that the tape synchronizer is performing an operation. If an IBM 7330 Magnetic Tape Unit is selected to execute the tape operation, the tape synchronizer cancels "tape in process" to the processing unit before dropping "tape busy"; this allows the processing unit to condition "external end of transfer" and perform status sample B checks while the tape synchronizer is still busy. Another tape operation on the same channel

cannot begin, however, until the previous tape operation is complete and the tape synchronizer drops "tape busy".

Sensing the end of tape reflective spot in a tape write operation or reading a tape mark as the first character in the record in a tape read operation causes the tape indicator  $(\pi)$  light on the selected tape unit to turn on. The tape unit then signals the involved 1-0 channel with the select and TI on line, causing the channel's condition and turn off tape indicator latches to turn on at status sample B and second sample B respectively. The turn off tape indicator latch gates "turn off  $\pi$ " to the selected tape unit to turn off the tape indicator light.

The tape synchronizer conditions "tape error" to the processing unit if it detects an error while executing the tape operation. "Tape error" sets the channel's data check status indicator at status sample B time.

# **Channel Tape Write Operations**

In tape write operations, the processing unit transfers characters from core storage to the channel designated by the tape write instruction. Channel circuits process, then hold the character(s) until the tape synchronizer is ready to transfer the data to the selected tape unit. The tape synchronizer controls all data transfers from the channel to the read-write register in the tape synchronizer.

The d-modifier in the tape write instruction determines the condition that causes the processing unit to transmit "disconnect call" to the tape synchronizer, ending the tape write operation. If the d-modifier in the write instruction is W, the processing unit conditions "disconnect call" when either the first group mark word mark in core storage is sensed or the end of storage condition is detected. If the d-modifier is X and the tape write operation is being performed in unoverlap mode, the processing unit conditions "disconnect call" when the end of storage condition is sensed; group mark word marks are processed as normal characters. If the write instruction with the X d-modifier is executed in overlap mode, the first group mark word mark sensed in storage or the end of storage indication causes the processing unit to issue "disconnect call". "Disconnect call" initiates tape synchronizer actions to end the tape write operation.

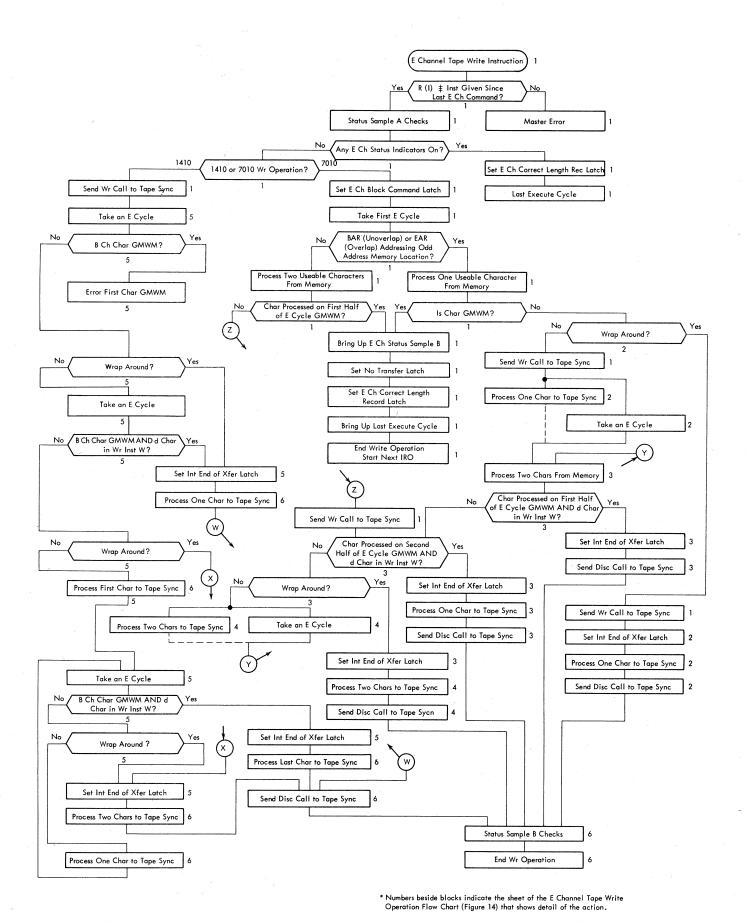

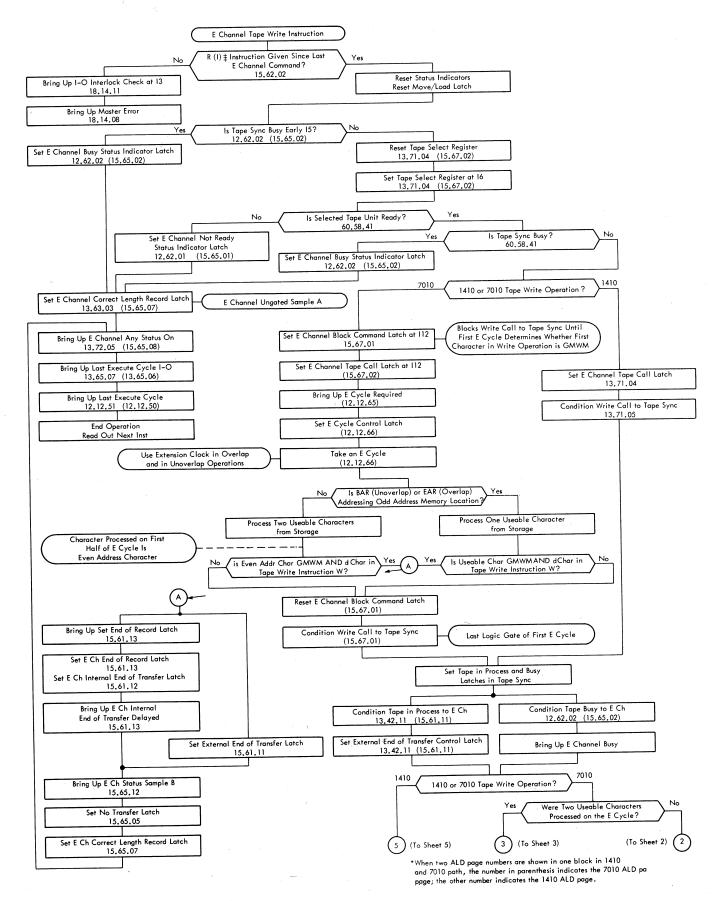

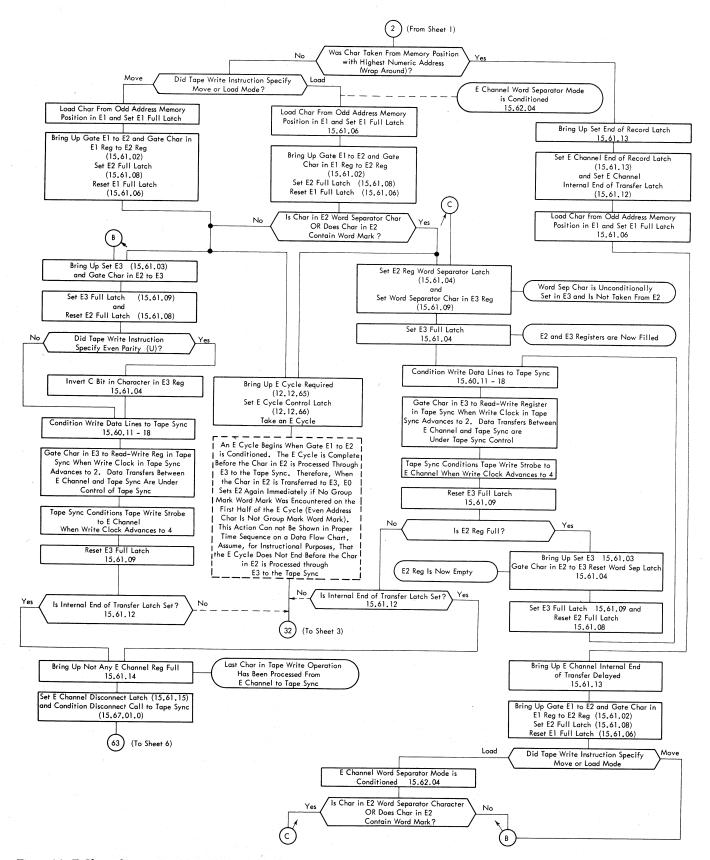

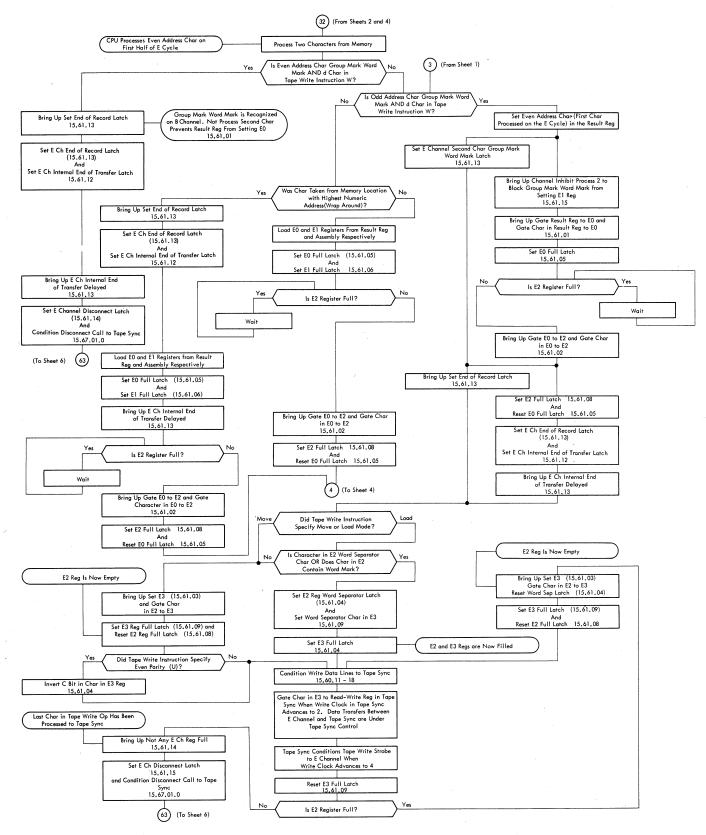

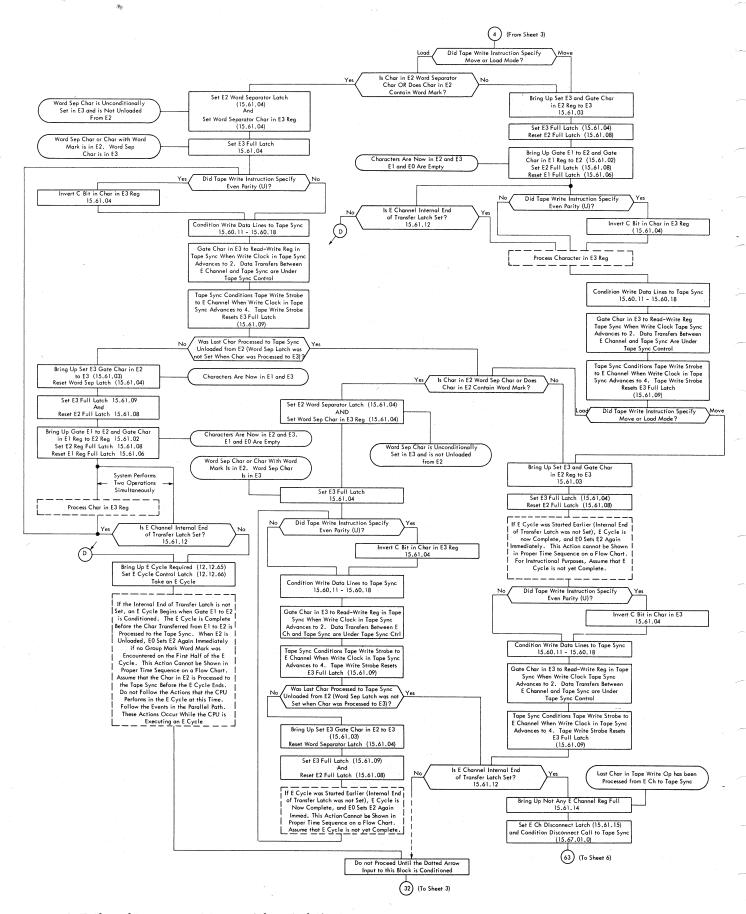

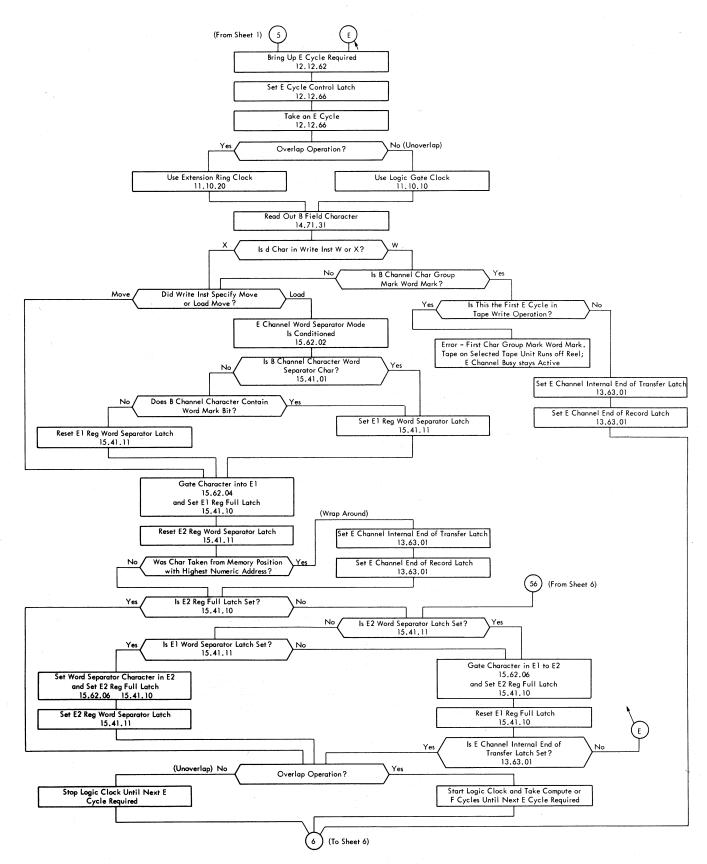

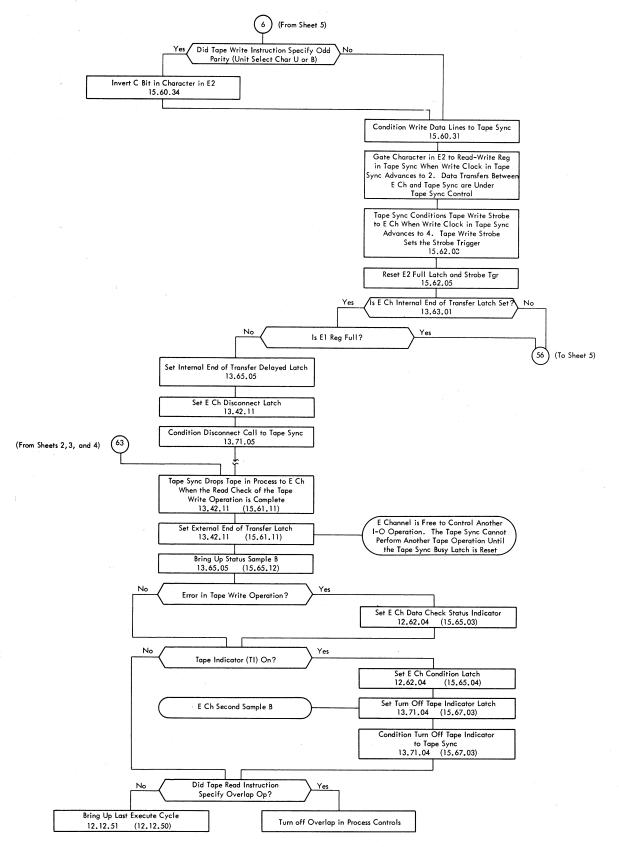

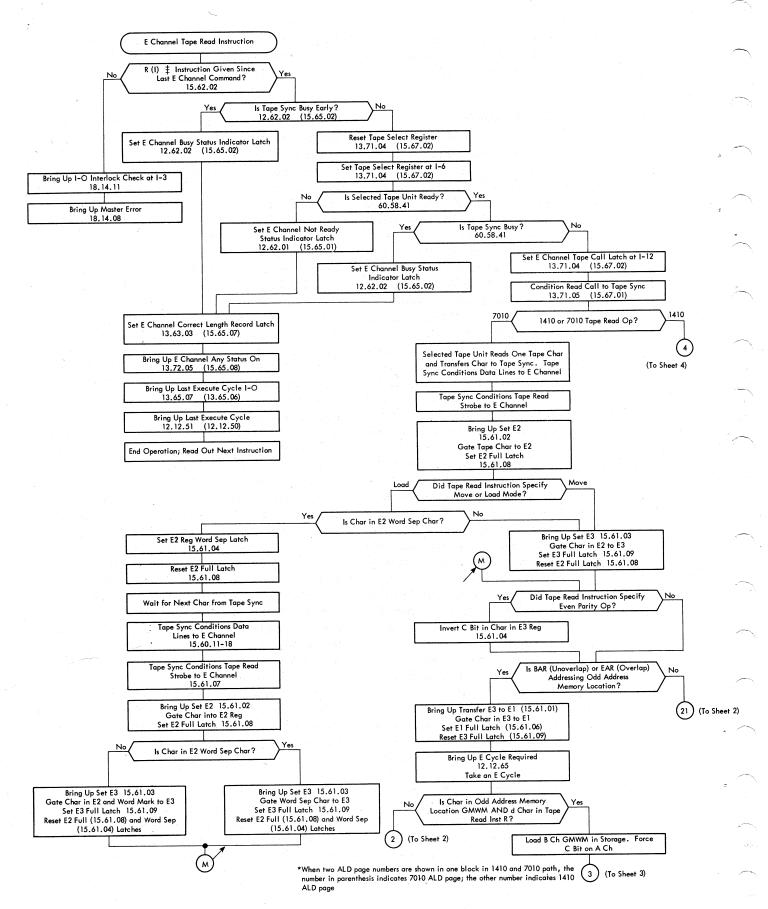

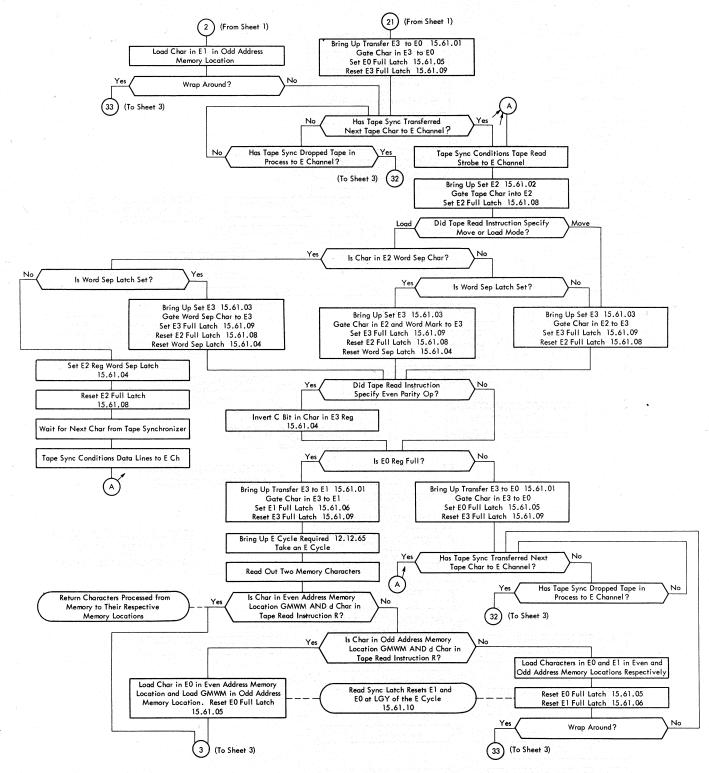

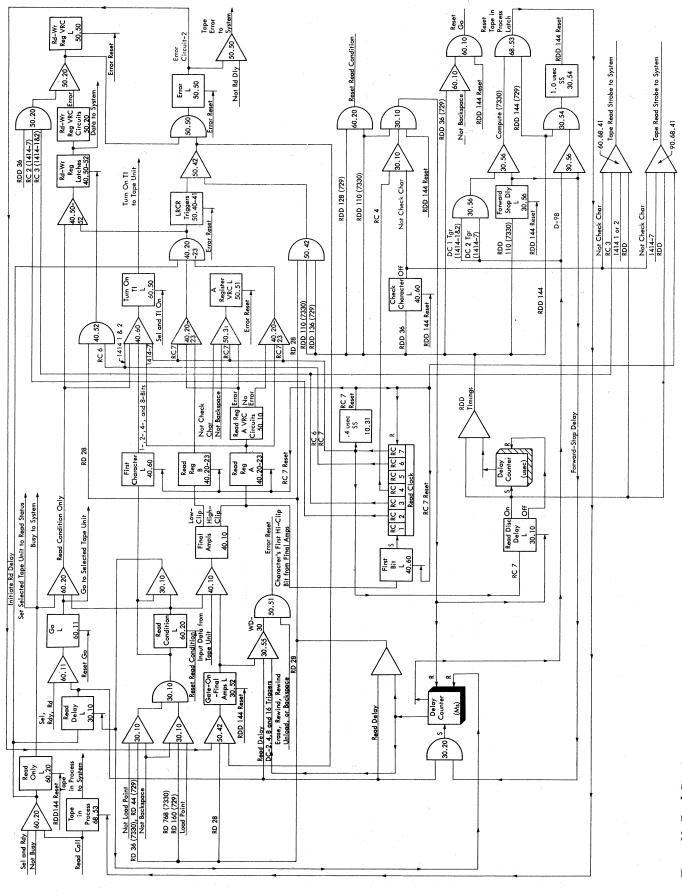

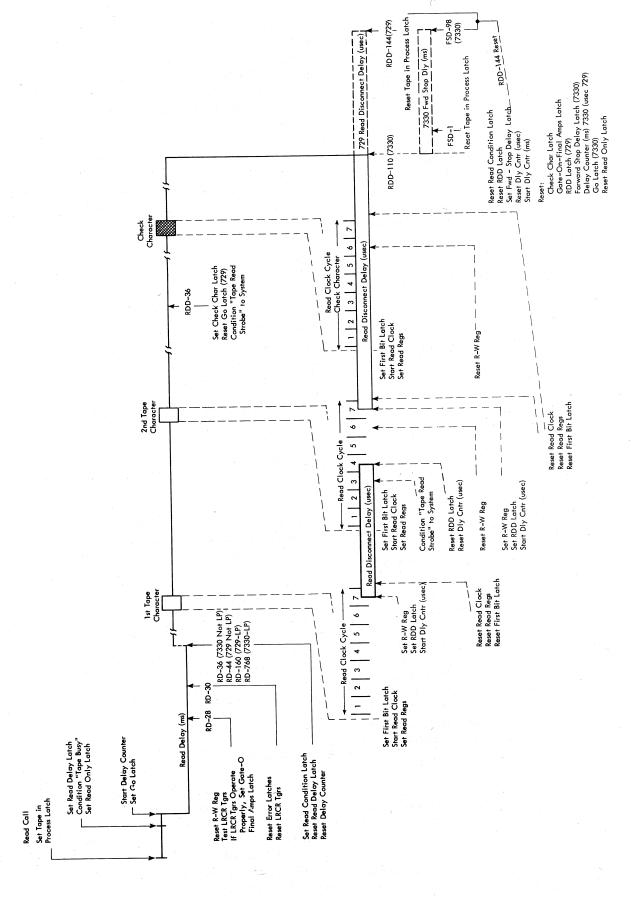

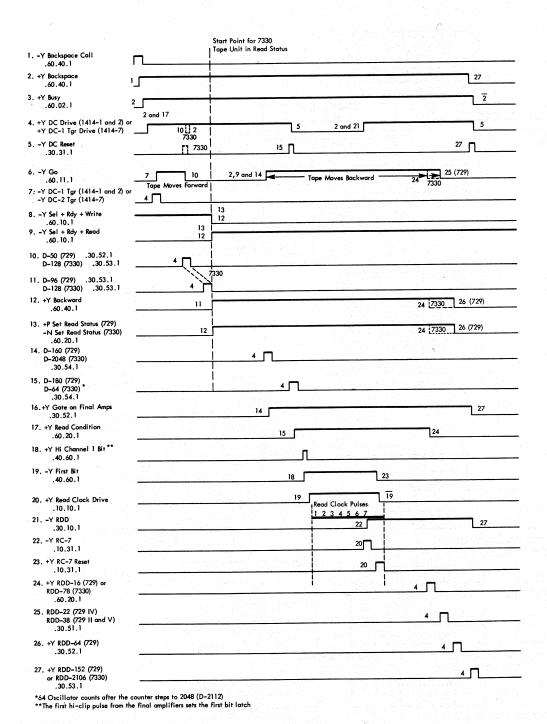

The E- and F-channels on the 1410 system process characters to the tape synchronizer in the same manner. The 7010 E-, F-, G-, and H-channel actions in tape operations are alike. Figures 13 and 14 show diagrammed E-channel actions in 1410 and 7010 tape write operations.

# 7010 E-Channel Tape Write Operation

In a 7010 E-channel tape write operation, the processing unit turns on the block command latch at the end of status sample A time to prevent the E-channel from conditioning "write tape call" to the tape synchronizer until the processing unit executes the first E-cycle. The B-address in the write instruction specifies the core storage position containing the first character to be transferred to the processing unit. If the character is a group mark word mark and the d-modifier in the write instruction is W, the processing unit initiates a series of actions that allow the block command latch to remain set and turn on the external end of transfer latch. The group mark word mark on the B-channel sets the internal end of transfer latch. "External end of transfer" and "internal end of transfer" set the status sample B latch. Because the block command latch is on at the end of the first E-cycle, the processing unit does not condition "write tape call" to the tape synchronizer to begin the write operation. At status sample B time, the ON output from the block command latch sets the no transfer and correct length record latches to indicate the programming error (first storage position addressed contains group mark word mark and d-modifier in instruction is W). "Last execute cycle" ends the simulated tape write operation in the normal manner although no data transfers occurred. The processing unit then executes the next instruction in numerical sequence.

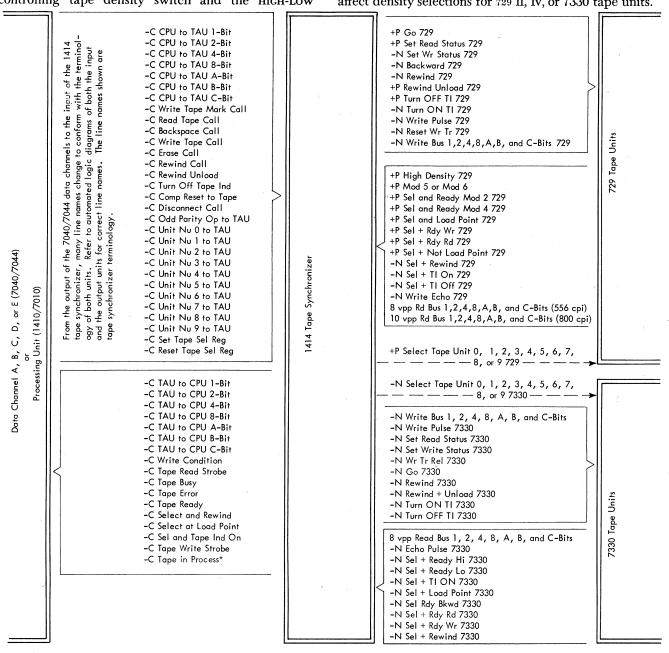

If the character in the storage position that the B-address designates is not a group mark word mark or if the d-modifier in the tape write instruction is not W, "last logic gate" of the first E-cycle resets the block command latch; the processing unit conditions "write tape call" to the tape synchronizer to begin the operation.