#### HEWLETT PACKARD

COMPUTER SYSTEMS - 19447 Pruneridge Ave. Cupertino CA 95014

-----

From: Alan Hewer Jim Miller Dave Salomaki Bert Speelpenning

To: ACD Distribution

Subject: VISION Architecture Control Document, Version 5

Date: August 19, 1982

We are proud to announce the release of Version 5 of the VISION ACD. Version 5 incorporates all changes and clarifications that have previously been transmitted only through memos. This single document provides a stable, self-consistent and complete description of the VISION processor architecture including I/O instructions. A version of the companion document "HP/3000 Compatibility Mode" incorporating the extended CST structure will be available in October.

Version 5 of the ACD replaces version 3, and the copy of version 3 in your possession must be shredded or returned to Bert Speelpenning at CSY. If you wonder what happened to version 4: there is no version 4 nor will there be. The designation "version 5" for the next major release of the ACD somehow gained currency within CSY, and it didn't seem particularly fruitful to buck that trend.

The organization of the architecture description has been thoroughly overhauled in order to improve clarity of exposition. These changes were sufficiently extensive that it was decided not to retain page or section numbers from version 3; change bars were also abandoned. Rather, version 5 is a stand-alone description of the architecture that should be read in full by implementors of VISION-specific products.

Turning to content, the architecture described in version 5 differs from that of version 3 in ways described in earlier memos published by us, as well as in other minor ways. These changes are summarized below. Their net effect is to make the VISION architecture more streamlined and easier to implement cost-effectively in hardware while minimizing the impact on software.

It is a pleasure to acknowledge the help and cooperation we have received in getting the architecture and its description to its current state; the implementation teams have been remarkably patient in helping us evaluate the effect of proposed changes as well as in accomodating those changes we decided to adopt.

Our main efforts will become focussed on monitoring the progress of VISION implementations; we remain committed to resolve problems in the present definition of the VISION architecture that these implementations may uncover.

# Summary of significant changes between version 3 and version 5

- 1. Virtual address space has been cut back from 74 to 64 bits.

- 2. The number of privilege levels has been reduced from 8 to 4.

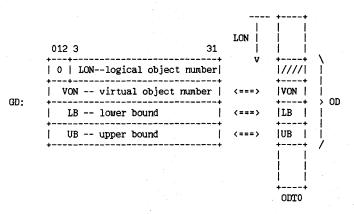

- 3. Object Descriptors have been streamlined to a 4-word format.

- 4. Procedure linkage has been simplified: the STT-mechanism is no longer required in Vision mode. Procedure stack markers have been reduced to three words instead of four; EXIT can distinguish between markers laid down by CALL and CALLX, this significantly streamlines exit from CALL.

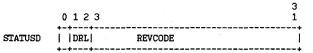

- 5. Some STATUS bits and other machine state (such as the TCB) have been rearranged to allow faster updates to the addressing environment, such as EXIT or IEXIT.

- Synchronization of caches and TLBs when making changes to the addressing tables has been made the explicit responsibility of operating system software.

- 7. The encoding of instructions has changed. Instructions or pairs of instructions now occupy a word or a multiple of words. Orthogonality of opcodes and operands has been retained.

- 8. 8 General registers have been added.

- 9. Instructions dealing with base registers have been separated out. Base registers are no longer treated as general operands.

- Several instructions that were marginal in terms of speed-up over their software equivalents were deleted.

All 16-bit arithmetic and all 12-byte packed decimal arithmetic has been deleted from the architecture.

- 11. Opcode assignments have been updated.

- 12. Several definitions of individual instructions have been streamlined.

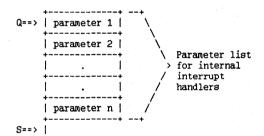

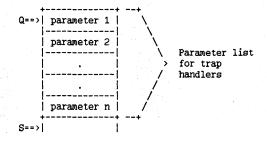

- 13. Arguments for trap handlers are pushed in the reverse order. The trap identification number is now always on top of the stack.

- 14. The interrupt structure for I/O and inter-processor communication has been defined and included. I/O instructions for PICMB-based systems and for MPB-based systems have been defined and included. The interface to the Control and Support Processor (CSP) has been defined and included.

# Not yet included in the Architecture Control Document are:

- 1. Instructions to support diagnostic capabilities.

- 2. Description of the data structures to support I/O.

| ARCHITECTURE | CONTROL   | DOCUMENT   |

|--------------|-----------|------------|

| CODV ND D    | DIVATE IN | TEODMATION |

|        |              | VISION ARCHITECTURE CONTROL DOC<br>DO NOT COPY HP PRIVATE INFOR |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|--------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 4 137        | PODUCET ON                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 1 IN.<br>1.1 | IRODUCTION<br>VISION Architecture Control Docume                | <b>*</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|        |              |                                                                 | nu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|        | 1.2          | Architecture Overview<br>Architecture Control                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 1.3          |                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 1.4          | Intended Audience                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 1.5          | Related Documents                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1.1    | 1.6          | Notations and Conventions                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 1.7          | Implementation Guidelines                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2 ADI        | DRESS SPACES                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

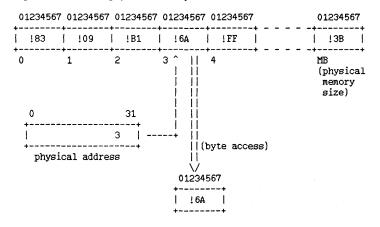

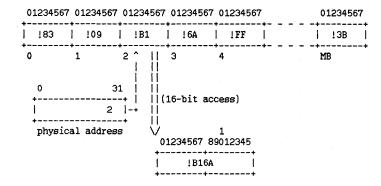

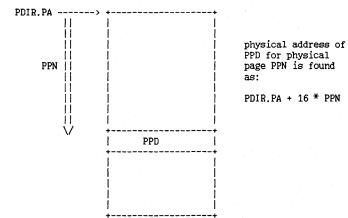

|        | 2.1          | Physical Address Space                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

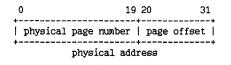

|        | 2.1.1        | Pages                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

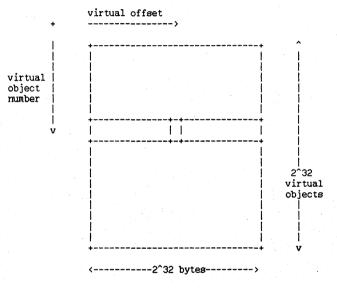

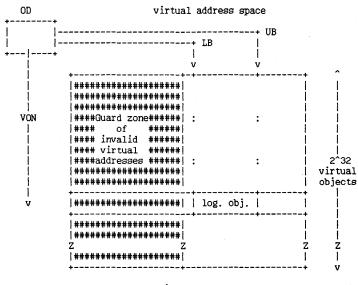

|        | 2.2          | Virtual Address Space                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.2.1        | Virtual Address Space: virtual obj                              | ects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

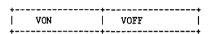

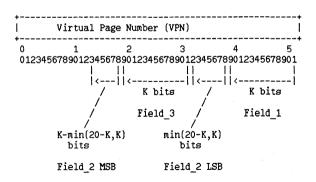

|        | 2.2.2        | Virtual Address Space: Paging                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

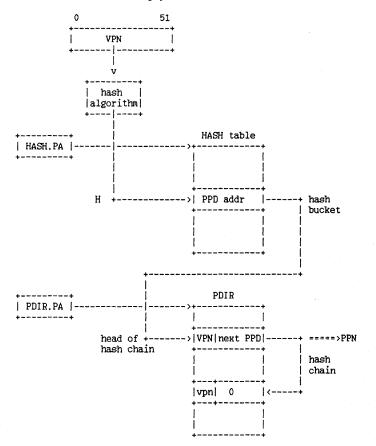

|        | 2.2.3        | The Physical Page Directory (PDIR)                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

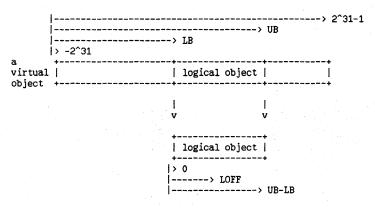

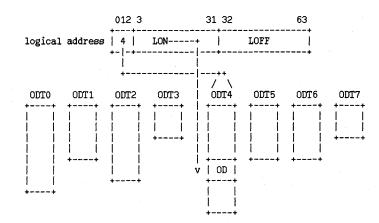

|        | 2.3          | Logical Address Space                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

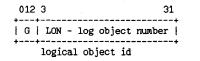

|        | 2.3.1        | Logical Objects                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

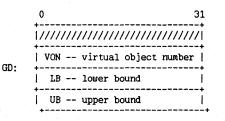

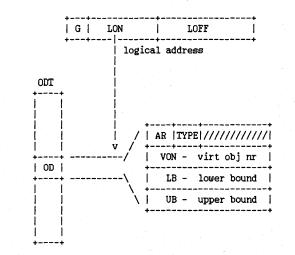

|        | 2.3.2        | Object Descriptor Format                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.2.1      | Object Types                                                    | 1. A. S. A. |

| 100 A. | 2.3.2.2      | Access Rights                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.2.3      | Lower and Upper Bounds                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.3        | Object Groups                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.4        | Object Descriptor Table                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

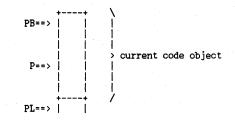

|        | 2.3.5        | Current Code Object                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

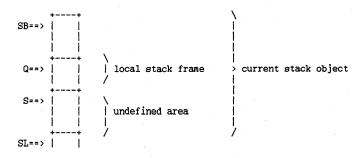

|        | 2.3.6        | Current Stack Object                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.7        | Nil Object                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.8        | Group Descriptors                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

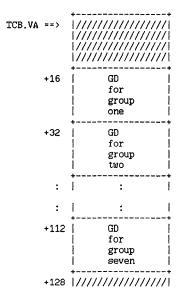

|        | 2.3.9        | Task Control Block                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 2.3.9        | LASK CONTIGL BIOCK                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |              | DRESS TRANSLATION                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|        | 3.1          | An access its characteristics                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

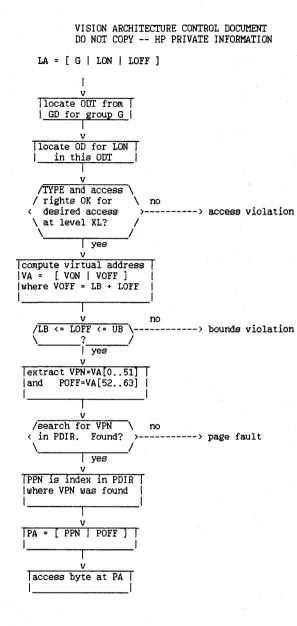

|        | 3.2          | Access Algorithm                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |