# **HP 27110A**

# HP-IB INTERFACE (HP-IB)

# **Technical Reference Manual**

Card Assembly: 27110-60001

Date Code: D-2321

# PRINTING HISTORY

The Printing History below identifies the Edition of this Manual and any Updates that are included. Periodically, update packages are distributed which contain replacement pages to be merged into the manual, including an updated copy of this Printing History page. Also, the update may contain write-in instructions.

Each reprinting of this manual will incorporate all past updates; however, no new information will be added. Thus, the reprinted copy will be identical in content to prior printings of the same edition with its user-inserted update information. New editions of this manual will contain new information, as well as updates.

First Edition.....November 1982 Second Edition.....June 1983

#### NOTICE

The information contained in this document is subject to change without notice.

HEWLETT-PACKARD MAKES NO WARRANTY OF ANY KIND WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Hewlett-Packard shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material.

This document contains proprietary information which is protected by copyright. All rights are reserved. No part of this document may be photocopied or reproduced without the prior written consent of Hewlett-Packard Company.

| Section I                                | Page |

|------------------------------------------|------|

| GENERAL INFORMATION                      | J    |

| Physical Description                     | 1-1  |

| Functional Description                   | 1-1  |

| Equipment Supplied                       |      |

| Identification                           |      |

| The Product                              |      |

| Interface Card                           |      |

| Manuals                                  |      |

| Specifications                           |      |

| HP-IB Capabilities                       |      |

| HP-IB Supported Functions                |      |

| Added the Table Links to the debates     | 1-8  |

| Addressing-Talking-Listening-Handshaking | 1-9  |

| Functions of Devices on the HP-IB        |      |

| HP-IB Bus Lines                          |      |

| Control Lines                            |      |

| Data Lines (DI01-DI08)                   |      |

| Transfer Lines                           |      |

| Data Transfer                            |      |

| NRFD                                     |      |

| PPOLL and ATN                            | 1-17 |

| Default and Power On Configurations      | 1-17 |

| Offline/Online                           |      |

| REN and IFC.                             |      |

|                                          |      |

| Section II<br>INSTALLATION               | Page |

| Computation of Current Requirements      | 2-1  |

| Firmware (ROM/EPROM) Installation.       | 2-1  |

| Configuration Switch Definitions         |      |

| Self-Test Mode Selection                 |      |

| Data Settling Time Selection             |      |

|                                          |      |

| System Controller Selection              |      |

| HP-IB Address Selection                  |      |

| External Memory Selection                |      |

| I/O Channel Interface                    |      |

| Peripheral Device Interface              |      |

| General Guidelines for HP-IB Operation   |      |

| Medium-Speed Operation                   | 2-9  |

| High-Speed Operation                     | 2-9  |

| Installation                             | 2-10 |

| Start-up                                 | 2-11 |

| Reshipment                               | 2-12 |

|                                          |      |

| Section III<br>PRINCIPLES OF OPERATION                     | Page  |

|------------------------------------------------------------|-------|

| Overview                                                   | . 3-1 |

| Backplane Interface                                        |       |

| HP-IB Interface                                            |       |

| HP-IB Chip DMA Read Timing                                 |       |

| HP-IB Chip DMA Write Timing                                |       |

| Z8 Interface                                               |       |

| Addressing                                                 | 3-17  |

| Switch Register Interface                                  | 3-19  |

| Z8 Control Signals                                         |       |

| SEND:ATN, SEND:EOI, LAST:EOI, and LED:ON Interface Signals | 3-20  |

| Interrupts                                                 |       |

| Direct Memory Access                                       |       |

| DMA Write                                                  |       |

| DMA Read                                                   | 3-25  |

|                                                            |       |

|                                                            |       |

| Section IV                                                 | Page  |

| PROGRAMMING                                                | 4-1   |

| Commands Supported                                         | 4-1   |

| Summary of Controls, Commands, and Orders                  | 4-1   |

| Attention Request (ARQ) Mechanism                          | 4-3   |

| Posting Status Bytes                                       |       |

| SRE                                                        |       |

| RQA                                                        |       |

| CMD                                                        |       |

| Effect of Freeze                                           |       |

| Error Handling                                             |       |

| Level 2 Abort Command                                      |       |

| Level 2 Identify Order                                     | . 4-6 |

| Card's Response to PPON, DCL, ABTn, and RST                |       |

| NRFD                                                       | . 4-6 |

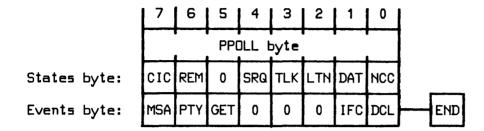

| PPOLL and ATN                                              | . 4-7 |

| Default and Power On Configurations                        | . 4-7 |

| Offline/Online                                             | . 4-7 |

| REN and IFC                                                |       |

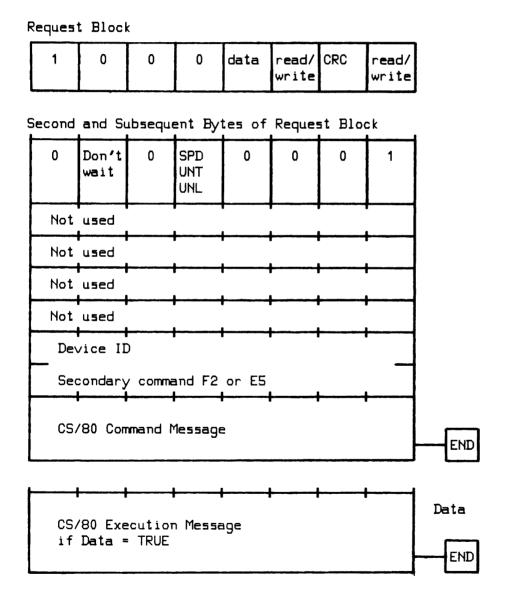

| Transactions                                               |       |

| Concept                                                    |       |

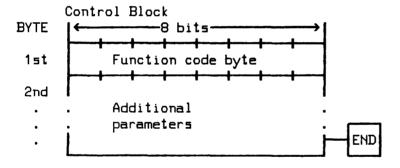

| Control Block                                              |       |

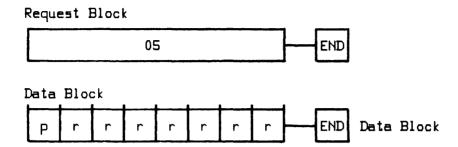

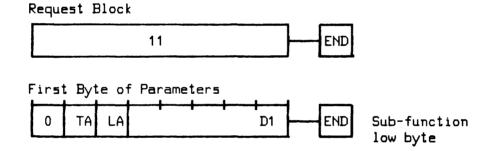

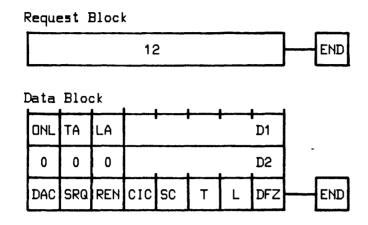

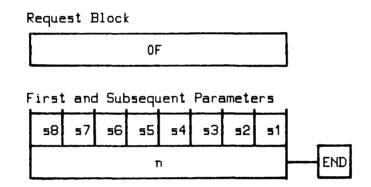

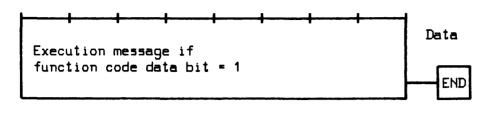

| Function Code                                              |       |

| General Transactions                                       |       |

| Additional Parameters                                      |       |

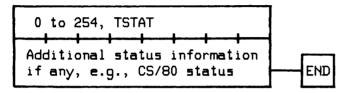

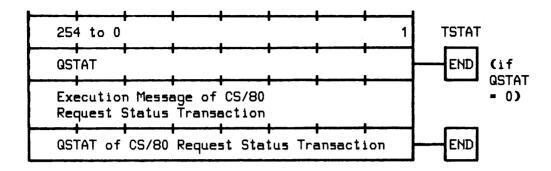

| Status Block                                               |       |

| TSTAT                                                      | 4-11  |

| Individual Transaction Descriptions4                    |     |

|---------------------------------------------------------|-----|

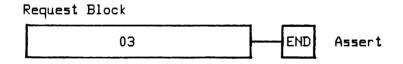

| Send Interface Clear (IFC Line Asserted for 100us)4     | -14 |

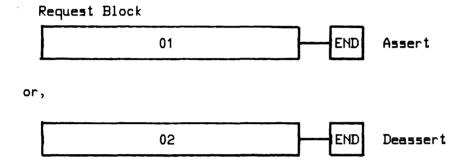

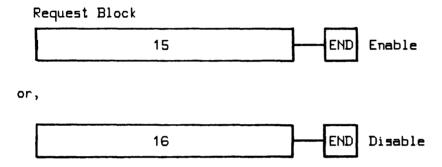

| Remote Enable (REN)4                                    |     |

| Configure Serial Poll Response & Request Service (SRQ)4 |     |

| Configure Interface Message Parity Freeze4              | -16 |

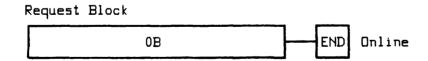

| Online4                                                 | -16 |

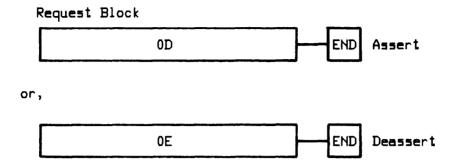

| ATN4                                                    |     |

| Data Transfer Between Card and Another HP-IB Device4    |     |

| Sending GET, DCL, SDC, TCT, LLO, SPE4                   |     |

| Conduct PPOLL and Read Response4                        |     |

| Configure Card's Response to PPOLL4                     |     |

| Read Card's PPOLL Response Configuration4               |     |

| HP-IB Address Configuration4                            | -24 |

| HP-IB Address and SC, CIC, TLK, and LTN Read4           |     |

| Last Secondary4                                         | -25 |

| Bus PPOLL Sense Configuration4                          |     |

| Interrupt Transactions4                                 |     |

| Format of Interrupt Block4                              |     |

| Write Interrupt Mask4                                   |     |

| Read Interrupt Mask4                                    |     |

| Read Reason for Interrupt4                              |     |

| Wait for Interrupt Conditions4                          |     |

| Interrupt Operation4                                    |     |

| Bit Definitions4                                        |     |

| CS/80 Transaction4                                      |     |

| Magnetic Tape Transaction4                              |     |

| AMIGO Identify Transaction4                             |     |

| AMIGO Identify Configuration4                           | -35 |

|                                                         |     |

| Section V                                               | age |

| MAINTENANCE                                             | 5-1 |

|                                                         |     |

| Section VI                                              | age |

| REPLACEABLE PARTS                                       | -3- |

| Replaceable Parts                                       | 6-1 |

| Ordering Information                                    |     |

| Section VII        | Page |

|--------------------|------|

| SCHEMATIC DIAGRAMS |      |

|                    |      |

|                    |      |

| APPENDIX           | A-'  |

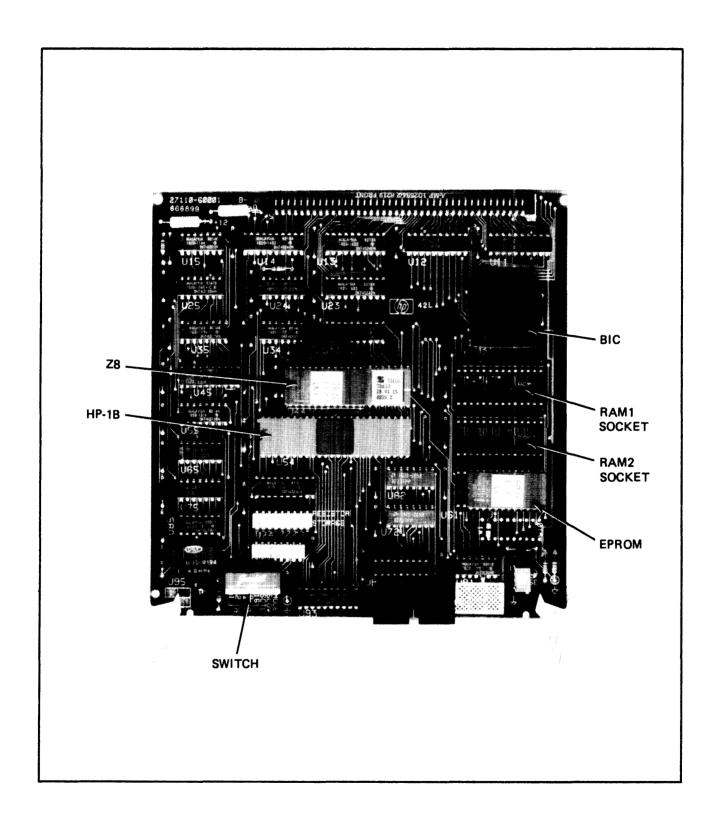

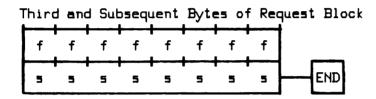

Figure 1-1. HP 27110A HP-IB Interface

# **GENERAL INFORMATION**

SECTION

This manual provides general information, installation, theory of operation, maintenance instructions, replaceable parts information, and servicing diagrams for the Hewlett-Packard HP 27110A Hewlett-Packard Interface Bus (HP-IB) Interface Card. This section contains general information concerning the HP-IB card, and includes a description and specifications.

# PHYSICAL DESCRIPTION

The HP 27110A Hewlett-Packard Interface Bus (HP-IB) Interface Card is shown in figure 1-1 and consists of a printed-circuit assembly, an interface cable, and an installation manual.

# **FUNCTIONAL DESCRIPTION**

The Hewlett-Packard Interface Bus (HP-IB) is Hewlett-Packard's implementation of the IEEE Standard 488-1978 and Supplement 488-1978A-1980.

The HP-IB card provides an interface between a host computer and up to 14 HP-IB-compatible peripheral devices such as disc drives, tape drives, printers, printers, etc.

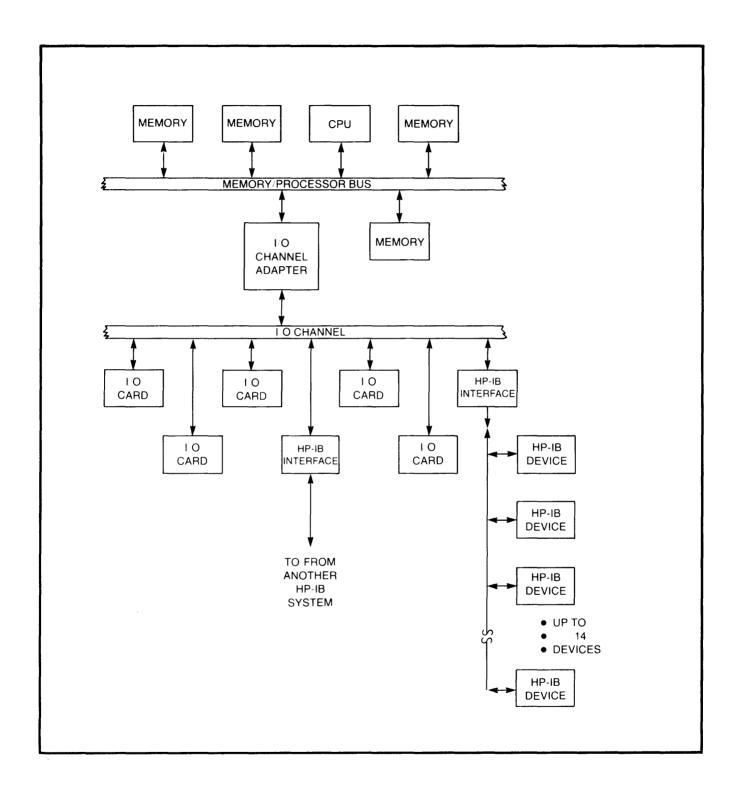

Figure 1-2 shows a Hewlett-Packard computer system using CHANNEL I/O and the HP-IB interface bus. (CHANNEL I/O is a Hewlett-Packard standard defining the physical and electrical characteristics for an I/O system consisting of an I/O channel adapter, an I/O channel, and I/O cards. The HP-IB card is one of the I/O cards.)

Figure 1-2. HP-IB Interface Card in a Hewlett-Packard Computer System

Note that the computer system CPU and memory communicate directly along a Memory/Processor Bus (MPB). I/O data to/from peripheral devices reaches the CPU/memory through the I/O channel, the I/O channel adapter, and an I/O card such as the HP-IB card. The I/O data is received from and transmitted to peripheral devices by the I/O card, which converts device-specific data to a format compatible with the I/O channel, and thus the computer. The I/O channel adapter (see figure 1-2) controls the flow of data traffic between the I/O channel and the memory/processor bus.

The HP-IB card can interface to up to 14 standard HP-IB peripheral devices (such as instruments), or up to seven high-speed HP-IB peripheral devices (such as disc drives). The HP-IB card is an intelligent interface card utilizing a Z8 microprocessor, and has the capability of relieving the host CPU of a large amount of overhead.

# **EQUIPMENT SUPPLIED**

The standard HP 27110A HP-IB Interface Card consists of the following items (see figure 1-1):

HP-IB interface card, part number 27110-60001

Two-meter HP-IB cable, part number 8120-4010

HP 27110A Installation Manual, part number 27110-90001

# IDENTIFICATION

#### The Product

Up to five digits and a letter (27110A in this case) are used to identify Hewlett-Packard products. The five digits identify the product; the letter indicates the revision level of the product.

# Interface Card

The interface card supplied with the HP 27110A product is identified by a part number marked on the card. In addition to the part number, the card is further identified by a letter and a four-digit date code (e.g., D-2230). This designation is placed below the part number. The letter identifies the version of the etched circuit on the card. The date code (the four digits following the letter) identifies the electrical characteristics of the card with components mounted. Thus, the complete part number on the HP-IB card could be:

27110-60001 D-2321 If the date code stamped on the card does not agree with the date code on the title page of this manual, there are differences between your card and the card described herein. These differences are described in manual supplements available at the nearest Hewlett-Packard Sales and Service Office (a list of Hewlett-Packard Sales and Service Offices is contained at the back of this manual).

# **Manuals**

The Installation Manual (part number 27110-90001, supplied with the product) and this manual (HP 27110A Technical Reference Manual, part number 27132-90002) are identified by name and part number. (Note that this manual is part of the HP 27132A Technical Reference Package.) The name, part number, and publication date are printed on the title page of each manual. If the manual is revised, the publication date is changed. In this manual, the "Printing History" page (page ii) records the reprint dates. Reprint dates for the Installation Manual are printed on the title page.

# **SPECIFICATIONS**

Table 1-1 lists the specifications of the HP-IB.

#### Table 1-1. Specifications

# **FEATURES**

# HP-IB Bus Signal Lines:

```

DI01 Data Input/Output 1

DI02 .

DI03 .

DI04 .

DI05 .

DI06 .

DI07 .

DI08 Data Input/Output 8

DAV Data Valid

NRFD Not Ready For Data

```

NDAC Not Data Accepted

IFC Interface Clear

ATN Attention

SRQ Service Request REN Remote Enable EDI End or Identify

Logic Levels: High > 2.4V Low < 0.5V

All signals are low true

#### Line Termination:

Each of the 16 HP-IB signal lines is terminated with a 2.3K ohm resistor to Vcc and a 4.7K ohm resistor to common without the optional load resistors.

#### Line Drivers:

Each of the 16 HP-IB signal lines is driven with a circuit having the following typical characteristics:

Type: Tri-state, open collector

Output Voltage, Low State: < 0.

Output Voltage, Low State: < 0.5V, 48 mA

Output Voltage, High State: < 2.5V, -5.2 mA

Table 1-1. Specifications (Continued)

#### Line Receivers:

Each of the 16 HP-IB signal lines is received with a circuit having the following characteristics:

Type: Schmitt Trigger

Threshold, Positive Transition: 1.6V

Threshold, Negative Transition: 0.9V for data lines

1.0V for control lines

Input Current, Low State: -1.3 mA minimum to -3.2 mA

maximum @ 0.5V

Input Current, High State: 0.7 mA minimum to 2.5 mA

maximum between 5V and 5.5V

#### Maximum Transfer Rates:

Standard Speed: 500K bytes/second High Speed: 980K bytes/second

(Dependent on host computer and software)

### Maximum Cable Length:

Standard Operation: 2 meters per device connected with

a 20-meter maximum length and a settling time of greater than 500

ns.

High-Speed Operation: 15 meters total maximum length, and

a settling time of less than 350 ns. See Section 2 for more information on high-speed operation.

Operating Temperature: 0 to 55 degrees Celsius

Address: 30 decimal when Controller-In-Charge (CIC), and set

by switches or host computer when not CIC.

Table 1-1. Specifications (Continued)

# PHYSICAL CHARACTERISTICS

Size:

172.7 mm long by 172 mm wide

(6.80 by 6.75 inches)

Weight:

234 grams (8.2 ounces)

I/O Channel Interconnects: 80-pin connector, J1

Device Interconnects:

26-pin connector, J2

# **POWER REQUIREMENTS**

| Voltage | Current | Power Dissipation |

|---------|---------|-------------------|

| +5V     | 1.8 A   | 9.0 watts         |

| +12V    | 35 mA   | 0.42 watts        |

# HP-IB CAPABILITIES

The Hewlett-Packard Interface Bus provides the capability of connecting from one to 14 compatible peripheral devices to a host computer via one interface card. Data is transferred over the HP-IB bidirectionally in 8-bit bytes. Data can be transferred from a device to the computer and to other devices simultaneously, or from the computer to one or more devices simultaneously, or from one device to other devices under the control of the computer.

Some HP-IB features must be used while other features are optional. For example, all devices must be capable of being addressed, but they need not be capable of being operated by remote control. An HP-IB system may have some devices operating under remote control, while other devices in the same system are operating under local (their own front and rear panel controls)

The same pins of all HP-IB connectors of all devices are connected in parallel making a parallel communication network. This permits information to flow in any direction on the bus and allows any device to talk directly with another device without going through a central control unit.

# **HP-IB SUPPORTED FUNCTIONS**

The interface card is designed to support the following HP-IB Interface Functions as defined by the IEEE Standard 488-1978. (The HP-IB is Hewlett-Packard's implementation of the IEEE Standard 488-1978.) These functions are fully supported by the HP 27110A unless noted otherwise.

#### Controller Functions:

- C1 -- System Controller

- C2 -- Send Interface Clear and Take Charge

- C3 -- Send Remote Enable

- C4 -- Respond to Service Request

- C5 -- Send Interface Messages, Receive Control, Pass Control, Pass Control to Self, Parallel Poll, Take Control Synchronously

#### Controlled Device Functions:

- SR1 -- Service Request

- RL2 -- Remote Local

- PP1 -- Parallel Poll

- DC1 -- Device Clear

- DT1 -- Device Trigger

The following utility functions are provided to support the above listed functions:

- SH1 -- Source Handshake

- AH1 -- Acceptor Handshake

- T1 -- Basic Talker, Serial Poll, Talk Only

- TE1 -- Basic Extended Talker, Serial Poll, Talk Only, Unaddress if My Listener Address and My Secondary Address (requires host software support)

- L1 -- Basic Listener, Listen Only Mode

- LE1 -- Basic Extended Listener, Listener Only Mode, Unaddress if My Secondary Address and Talker Primary Addressed State (requires host software support)

# ADDRESSING-TALKING-LISTENING-HANDSHAKING

An addressing technique is used to determine which device is to "talk" and which devices are to "listen". Data is sent from one device to another device in a bit-parallel, byte-serial format using an interlocked "Handshake" technique. This technique assures that the sender does not remove data before the receiver has finished using the data. It also ensures that data is not lost when devices having inherently different speeds communicate on the same bus.

# FUNCTIONS OF DEVICES ON THE HP-IB

Devices connected to the bus must be addressed by the Controller before they can function in one or more of the following ways:

**TALKER** - Any device that is capable of sending or transmitting information on the bus. There can be only one talker at a time on the bus.

LISTENER - Any device that is capable of receiving or accepting information on the bus is a listener. There may be up to 15 listeners at the same time on the bus.

TALKER-LISTENER - A device that has the capability of both sending and receiving information on the bus as defined previously is both a talker and a listener. For example, a counter is a talker when sending data and a listener when it is being programmed.

CONTROLLER - Any device that has been programmed to have the responsibility of managing the flow of information between devices connected to the bus is a controller. It is capable of addressing one of the devices as a talker and one or more of the others as listeners. The HP-IB permits a system to have more than one controller, but only one controller may be active at a time. (The Controller-in-Charge may be the System Controller.)

SYSTEM CONTROLLER - The system designer must designate one device as the System Controller at the time the system is configured. The System Controller can assert IFC and REN. The System Controller becomes the Controller-In-Charge by asserting IFC.

# **HP-IB BUS LINES**

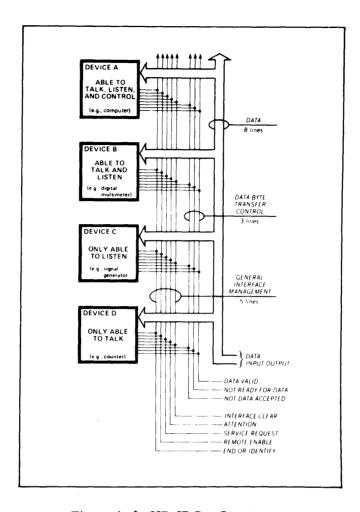

The HP-IB bus structure consisting of 16 signal lines is shown in figure 1-3. There are eight additional bus conductors, as follows: one ground, one cable shield, and six twisted-pair commons for six of the signal lines.

Figure 1-3. HP-IB Bus Structure

All 16 signal lines have been given names and mnemonic acronyms that describe the message being carried on each line. There are three types of lines: Data (8), Transfer (handshake) (3), and Control (management) (5).

NOTE

All devices connected to the bus, including the controller, must conform to the descriptions presented in the following paragraphs.

# **CONTROL LINES**

The five control lines are used to manage the flow of information over the data and transfer lines. They communicate control and status information between the active controller and the devices connected to the bus. All devices must use ATN and IFC. A device may or may not use REN, SRQ, and EOI.

ATN (Attention) is driven by the active controller to place the bus in either the COMMAND (low) or DATA (high) mode. All other devices must monitor ATN at all times.

When the controller sets ATN to its low state, the bus is in the Command Mode. The primary purpose of the Command Mode is to permit the controller to send commands or address those devices that are to communicate when the bus is placed in the Data Mode. Also, the controller may send "universal commands" while the bus is in the Command Mode.

When the controller sets ATN to its high state, the bus is in the Data Mode. The device that was addressed to talk and those that were addressed to listen will now communicate on the Data Lines.

ATN may be set low or high at any time by a controller, however, it is usually at the end of a transfer (handshake) cycle so that data is not lost. Timing of the transfer lines with respect to ATN is described in the paragraph "Transfer Lines".

IFC (Interface Clear) is used by the system controller to initialize the bus. Only the System Controller can drive IFC and it must be monitored by all other devices on the bus. When the System Controller sets IFC low, the following takes place: all talkers and listeners are stopped and unaddressed, serial poll mode is disabled, and control is returned to the HP-IB System Controller. When IFC is high it has no effect on the bus operation. The System Controller may set IFC low at any time.

REN (Remote Enable) is used by the System Controller to inform devices that are capable of remote operation that they are to operate under Remote Control. Such devices monitor REN at all times. Devices that are not capable of remote operation terminate REN in a resistive load. Only the System Controller may assert REN and may change its state at any time.

SRQ (Service Request) is driven to its low state by a device to indicate that it wants the attention of the System Controller. SRQ may be set low by a device at any time except when IFC is in the low state. Only the Controller-In-Charge senses SRQ. Some devices do not use SRQ, but all must terminate it in a resistive load.

EOI (End or Identify) may be used to indicate the end of a device's character string. When the bus is in the Data Mode (ATN is high), the addressed talker may indicate the end of its data by setting EOI low at the same time it places the last byte on the Data Lines. When ATN and EOI are both low, the bus is in the PPOLL mode.

# DATA LINES (DI01-DI08)

The Data Lines are used to communicate all data, including input, output, program codes, addresses, and control and status information between devices connected to the bus. This data is passed character (byte) at a time (i.e., byte serial and bit parallel) under control of the Transfer Lines.

#### TRANSFER LINES

Three Transfer (handshake) Lines are used to execute the transfer of each byte of information on the data lines. All devices use these lines and employ an interlocked handshake technique to pass information. This allows asynchronous data transfer without timing restrictions being placed on any device connected to the bus. The transfer of each byte is accomplished at the speed of the slowest device. The three transfer lines are: NRFD, NDAC, and DAV.

NRFD (Not Ready For Data) is the transfer (handshake) line that indicates all listeners are ready to accept information on the data lines. NRFD is driven by all the listeners (all devices when ATN is low, and only by those devices addressed to listen when ATN is high). It is sensed by talkers as follows: the controller when ATN is low, and the device addressed to talk when ATN is high.

When NRFD is high, all listeners are unconditionally ready for data. The talker may, at its own time, put a byte of information on the data lines and set DAV low. When NRFD is low, one or more listeners are not ready for data.

When the controller sets ATN true (low), all devices must prepare to receive interface messages within 200 nsec.

A listener must not set NRFD low until it senses DAV is low. It may do so before or at the same time that it sets NDAC high. It must not return NRFD to its high state until it senses DAV is high and may do so after, or at the same time that it sets NDAC low.

NDAC (Not Data Accepted) is the transfer line that indicates the acceptance of data on the data lines. NDAC is driven by all listeners. That is, all devices when ATN is low, and only those devices addressed to listen when ATN is high. It is sensed by the controller when ATN is low and by the device addressed to talk when ATN is high.

When NDAC is high, all listeners have unconditionally accepted the byte of information that is on the date lines and no longer need it. The talker may, at its own time, set DAV high, remove the byte of information, and continue. When NDAC is low, one or more listeners have not accepted the information on the data lines.

When the controller sets ATN high, the devices that have not been addressed to listen will not drive NDAC.

A listener must not set NDAC low until it senses DAV is high. It may do so before or at the same time that it sets NRFD high. It must not return NDAC high until it senses DAV is low and it may do so after or at the same time that it sets NRFD low.

DAV (Data Valid) is the transfer line that indicates the validity of information on the data lines. DAV is driven by the talkers: the controller when ATN is low and the device addressed to talk when ATN is high. DAV is sensed by all devices if ATN is low, and by those devices addressed to listen when ATN is high.

When DAV is low, the states of data lines DI01 through DI08 are unconditionally valid and may be accepted by all listeners at their own time. DAV can only be driven low if NRFD and IFC are high. When DAV is high, the information on the data lines is not valid. DAV cannot be set high unless NDAC is high and NRFD is low.

The talker has the responsibility of allowing enough time for cable rise time and ringing. It does this with DAV. After placing the bus in the Address Mode (setting ATN low), the controller must wait before setting DAV low. Of course DAV must not be asserted unless NRFD is high. In either the Address or Data Mode, a talker designed with open-collector circuits must not set DAV low for at least two microseconds after placing valid data at its output connector. Those designed with tri-state logic must wait at least 500 nsec.

The conditions described in the preceding paragraphs are summarized in tables 1-2 and 1-3.

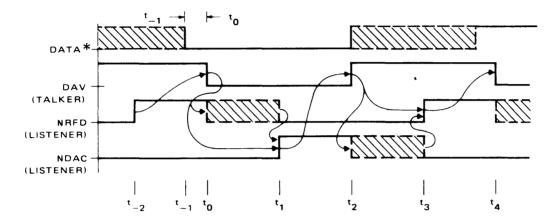

# **DATA TRANSFER**

The transfer of data on the bus is asynchronous and therefore places no restrictions on the data rates of devices connected to the bus. The timing and levels required to transfer a byte of data on the data lines are shown in figure 1-4. The transfer is under the control of the three lines DAV, NRFD, and NDAC. The talker (sender of data) drives the Data Lines and DAV (Data Valid), and the listeners (acceptors of data) drive both NRFD (Not Ready For Data) and NDAC (Not Data Accepted).

The transfer of a byte of data is initiated by all listeners signifying they are ready for data by setting NRFD high. When the talker recognizes NRFD is high and has placed valid data on the data lines, it sets DAV low. When the listeners sense that DAV is low and have finished using the data, they set NDAC high. Note that the assertion or active state of both NRFD and NDAC is low. Since all devices on the bus have their corresponding lines connected together (e.g., NRFD), all listeners must be in a high state before that line goes high. This wired-AND condition allows a talker to recognize when the slowest listener has accepted a byte of data and is ready for the next byte.

Figure 1-4 shows the timing of the transition to the assertive state of these lines. A listener may set NRFD low as soon as it recognizes that DAV has been set low and must do so before or at the same time it sets NDAC high. The talker may return DAV to its high state after it detects that NDAC is high. A listener may set NDAC low as soon as it recognizes that DAV is high and must do so before or at the same time it sets NRFD to its high state.

Table 1-2. Relationship Between ATN and Transfer (Handshake) Lines (NRFD, NDAC, and DAV)

| M           | Α    | NFRI                                                                                                                                                                                                                                                                                                                                           | )                                                  | NDA       | c                                                         | Г                                               | )AV                                 |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------|-----------------------------------------------------------|-------------------------------------------------|-------------------------------------|

| D<br>E      | ۲×   | LOW                                                                                                                                                                                                                                                                                                                                            | HIGH                                               | LOM       | HIGH                                                      | LOM                                             | HIGH                                |

| Z D Z Z O O | EOL  | One or<br>more units<br>not ready<br>for data                                                                                                                                                                                                                                                                                                  | All units<br>ready for<br>data                     |           | All units<br>have<br>accepted<br>data                     | Controller<br>has valid<br>data on<br>DIO lines | Controllers<br>data is not<br>valid |

| D           |      | 1. Driven by all units except controller 2. Sensed by controller 3. All units set NFRD and NDAC to valid state within 200 nsec after ATN goes low  1. Driven by controll 2. Sensed by listener 3. See DAV above for timing                                                                                                                     |                                                    |           |                                                           |                                                 | by listeners                        |

| D A T A     | HIGH | One or<br>more<br>listeners<br>not ready<br>for data                                                                                                                                                                                                                                                                                           | All<br>addressed<br>listeners<br>ready for<br>data | listeners | All<br>addressed<br>listeners<br>have<br>accepted<br>data | The addressed talker has valid data on lines    |                                     |

|             |      | 1. Driven by all units address to listen 2. Sensed by the unit addressed to talk 3. All units not addressed will not drive 4. All addressed listeners set both NRFD and NDAC to valid within 200 nsec after ATN goes high  2. Driven by the devices addressed to TALK 2. Sensed by all devices addressed to LISTEN 3. See DAV above for timing |                                                    |           |                                                           |                                                 |                                     |

|             |      | NOTE  Valid means either both asserted or both not asserted                                                                                                                                                                                                                                                                                    |                                                    |           |                                                           |                                                 |                                     |

Table 1-3. Summary of Bus Timing

| IFC INTERFACE CLEAR                        | The System Controller must set IFC low<br>for at least 100 usec to clear the bus                                                                                                                                                                                                                                                                                       |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRANSFER LINES WITH<br>RESPECT TO ATN      | When sending an Address or a Universal<br>Command the controller may set DAV low<br>only after sensing that NRFD is high,<br>and ATN has been low for a minimum<br>time.                                                                                                                                                                                               |

|                                            | When a controller changes ATN from its high to the low state, all non-listeners assert NRFD and NDAC in less than 200 nsec.                                                                                                                                                                                                                                            |

| TRANSFER LINES WITH<br>RESPECT TO THE DATA | After changing the information on one or more Data Lines, the talker (the Controller when ATN is low, or the device addressed to talk when ATN is high) must wait before setting DAV low. It waits 2 usec if designed with open-collector circuits, 500 nsec if designed with tri-state integrated circuits at standard speed, and 350 nsec if operated at high speed. |

# SEQUENTIAL REQUIREMENTS OF THE THREE WIRE TRANSFER

#### **EVENTS**

$t_{-2}$ : Listener becomes ready to accept data.

$t_{-1}$ : Talker has put data on the lines.

$t_0$ : Indicates data is valid.

t<sub>1</sub>: Listener has accepted the data and no longer requires it held valid.

to : Talker indicates the data is no longer valid and may change it.

t<sub>3</sub> : Listener indicates it is ready for new data.

$t_4$ : A new cycle begins (equivalent to  $t_0$ ).

$t_{-1}$  to  $t_0$ : Time that data is put on lines before DAV is set low.

\* A composite of the DIO1 through DIO7 lines for illustrative purposes. The curved lines indicate transfer (handshake) signal sequence.

Figure 1-4. Transfer Timing

#### **NRFD**

When the card is Controller-In-Charge and PPOLL is disabled and the card is neither sending or receiving data, Not Ready For Data (NRFD) will be asserted. The significance of this is: when the controller addresses one device to talk and another device to listen, the transfer will be blocked by this card's assertion of NRFD.

# **PPOLL and ATN**

The assertion of ATN during idle time is a function of whether PPOLL is to be asserted.

Normally, the ATN signal is not asserted except in the following cases:

- 1. A PPOLL interrupt has been enabled.

- 2. The last HP-IB message sent by the card was an interface message.

- 3. The assert ATN transaction is invoked.

- 4. During the execution of the "read PPOLL response" transaction.

The ATN signal will be deasserted in the following cases:

- 1. PPOLL interrupts are disabled and neither of conditions 2 or 3 above are true.

- 2. Last HP-IB message sent by the card was a data message.

- 3. The deassert ATN transaction is invoked.

- 4. The card is reset (PPON, DCL, or IFC).

- 5. The card is not System Controller and an IFC message is received.

- 6. The card sends a TCT (Take Control) message.

#### DEFAULT AND POWER ON CONFIGURATIONS

#### Offline/Online

Following a power on, the HP-IB card will be offline from the HP-IB bus. This means that it will not interact with the HP-IB bus in any way. The card will go online upon receipt of a "Go Online" transactions. Once the card is online it will not go offline unless another power reset is done or upon receipt of a "Go Offline" transaction.

The control of online timing allows you to configure the card for activities if different from the default - e.g., PPOLL sense - before the critical action of going online.

# **REN and IFC**

If the card comes online as System Controller, the REN (Remote Enable) signal will be deasserted by the card until explicitly controlled by the "Send Interface Clear" transaction; that is, the IFC signal is not automatically asserted when the card goes online.

The IFC signal is required before a card configured as the System Controller can assume the role of Controller-In-Charge (this may be accomplished offline).

# INSTALLATION

This section provides information on installing and checking the operation of the HP-IB card.

#### COMPUTATION OF CURRENT REQUIREMENTS

The HP-IB circuit card obtains its operating voltages from the computer power supply through the I/O channel. Before installing the card, it is necessary to determine whether the added current will overload the power supply. The current requirements of the HP-IB card are listed in the power requirements entry of table 1-1. Current requirements for all other I/O cards can be found in the appropriate Service Manuals.

# FIRMWARE (ROM/EPROM) INSTALLATION

#### CAUTION

SOME OF THE COMPONENTS USED IN THIS PRODUCT ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE REMOVING OR REPLACING THESE COMPONENTS.

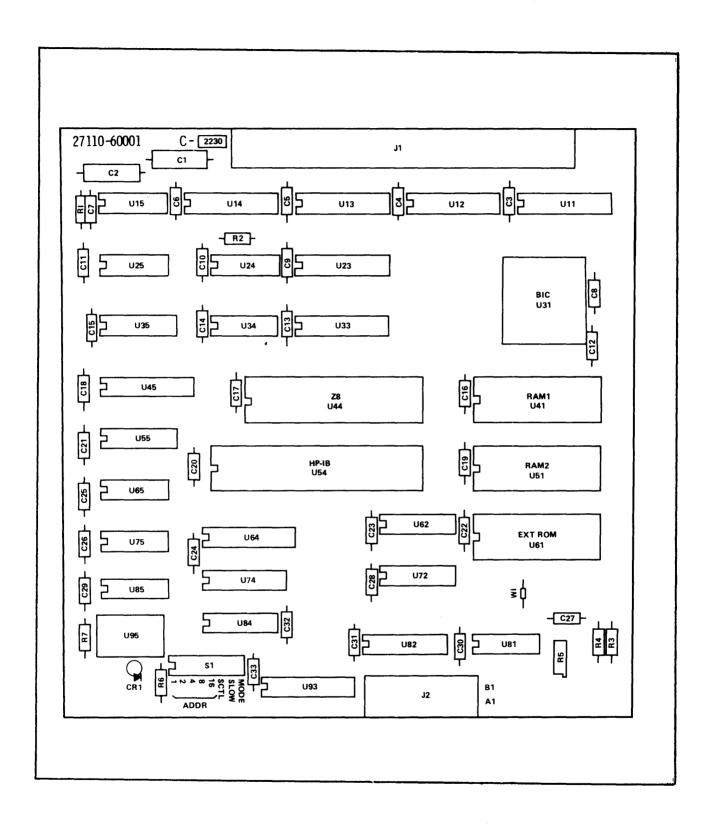

The firmware ROM is installed in a socket provided on the HP-IB card as shown in figure 2-1. Ensure that it is installed properly and that it has not been damaged or loosened from its socket during shipping.

Additionally, when installing or removing the ROM, guard against bending or breaking the pins on the component. These pins also can become folded between the component and its socket, which would result in intermittent operation of the HP-IB. In most cases, a bent or damaged pin can be straightened with careful use of needle-nose pliers.

Figure 2-1. Major Component Locations

# **CONFIGURATION SWITCH DEFINITIONS**

An eight-switch assembly is used to configure the HP-IB. The function of each switch is listed in table 2-1 and the location of the switch assembly is shown in figure 2-1. Note that the switches are ON in the up position and OFF in the down position.

Table 2-1. Configuration Switch Definitions

| SWITCH         | FUN                                         | CTION        |              |              | SETT         | INGS               |                        |     |    |  |

|----------------|---------------------------------------------|--------------|--------------|--------------|--------------|--------------------|------------------------|-----|----|--|

| S8             | Self-Test Mode                              |              |              | ľ            |              |                    | st Mode 1<br>st Mode 0 |     |    |  |

| 57             | Data Set<br>Selectio                        |              | Time         |              |              | ormal S<br>igh Spe |                        |     |    |  |

| 56             | System C<br>Selection                       | ontrol<br>n  | ler.         | UP           |              |                    | Controller<br>Contro   |     |    |  |

| S1 - S5        | HP-IB Ac<br>Selectic<br>Controll<br>Charge) | n (whe       |              | UP           | = L:<br>= L: |                    |                        |     |    |  |

| The fac        | tory sett                                   | ings         | for th       | ne cor       | nfigur       | ation              | switches               | are | as |  |

| 51<br><br>DOWN | S2 S3<br><br>UP UP                          | S4<br><br>UP | S5<br><br>UP | S6<br><br>UP | S7<br><br>UP | 58<br><br>DOWN     |                        |     |    |  |

The foregoing switch settings correspond to:

Test Mode - 1

Speed - STANDARD

System Controller - ON

Address - 30 DECIMAL

# Self-Test Mode Selection

Switch S8 selects self-test mode 1 or mode 2. This switch should be DOWN, for self-test mode 1.

# **Data Settling Time Selection**

Switch S7 determines the time delay between the assertion of the data on the bus and the assertion of the Data Valid (DAV) signal. With the switch in the standard (up) position, a delay of approximately 500 nsec is selected. When the switch is set to the high-speed (down) position, the delay is reduced to approximately 350 nsec. This delay time satisfies IEEE Standard 488-1978 for fast settling time required for high-speed operation. Refer to the paragraph "High-Speed Operation" for additional information on high-speed operation.

# **System Controller Selection**

Switch S6 determines if the HP-IB card will be the System Controller for the HP-IB bus. If the switch is open (up), the card will function as the System Controller.

#### HP-IB Address Selection

Switches S1 through S5 determine the HP-IB card address when the card is not Controller-In-Charge. An open (up) switch represents a logic one and a closed (down) switch represents a logic zero. Switch S4 selects the Most Significant Bit (MSB) and S8 selects the Least Significant Bit (LSB). The switches are set to decimal 30 at the factory. Note that decimal 31 is not a legal address and results in a flashing LED on the HP-IB card.

# **EXTERNAL MEMORY SELECTION**

Three 28-pin sockets on the HP-IB printed circuit card accommodate external, byte-wide memory. One socket (U61) is used for program memory (ROM/EPROM), and the other two (U41 and U51) are used for data memory (RAM). The HP-IB card is shipped from the factory with the correct ROM/RAM circuits installed and strapped for correct operation. Memory updates are performed by changing/adding appropriate memory components and changing the memory jumpers located on the 18-pin DIP (Dual Inline Package) socket, U71. Jumper configurations for external memory updates are shown on the next page.

| ROM<br>SIZE<br>(bytes) | INSTALL                | RAM1<br>SIZE | INSTALL | RAM2<br>SIZE | INSTALL |

|------------------------|------------------------|--------------|---------|--------------|---------|

| 8K                     | M3                     | 2K           | W6      | 2K           | WB      |

| 4K                     | No jumper<br>installed | 8K           | W7      | <b>8</b> K   | ew      |

# I/O CHANNEL INTERFACE

All interface between the HP-IB and the host computer occurs on the I/O channel. An 80-pin connector (J1) located on the HP-IB card mates with a receptacle on the I/O channel. Connections to J1 are listed in table 2-2.

# PERIPHERAL DEVICE INTERFACE CABLE

As listed below, several cables are available with the HP 27110A product. The selected cable connects from the 26-pin connector (J2) on the HP-IB card to the HP-IB-compatible peripheral device. Connections to J2 are listed in table 2-3.

| HP-IB CABLE | LENGTH (meters) |

|-------------|-----------------|

|             |                 |

| 10833A      | 1               |

| 10833B      | 2               |

| 10833C      | 4               |

| 10833D      | 0.5             |

Table 2-2. I/O Channel Bus Connector J1

| PIN NO. | SIGNAL MNEMONIC | SIGNAL DEFINITION    |

|---------|-----------------|----------------------|

|         |                 |                      |

| A1      | SAFETY          | Safety Ground        |

| A2      | DB14            | Data Bus, bit 14     |

| A3      | DB12            | Data Bus, bit 12     |

| A4      | GND             | Ground               |

| A5      | DB10            | Data Bus, bit 10     |

| A6      | DB8             | Data Bus, bit 8      |

| A7      | GND             | Ground               |

| A8      | DB6             | Data Bus, bit 6      |

| A9      | DB4             | Data Bus, bit 4      |

| A10     | GND             | Ground               |

| A11     | DB2             | Data Bus, bit 2      |

| A12     | DB0             | Data Bus, bit 0      |

| A13     | GND             | Ground               |

| A14     | AD2             | Address Bus, bit 2   |

| A15     | AD0             | Address Bus, bit 0   |

| A16     | GND             | Ground               |

| A17     | DOUT            | Data Out             |

| A18     | BP0             | Bus Primitive, bit 0 |

| A19     | CEND            | Channel End          |

| A20     | SYNC            | Synchronize          |

| A21     | GND             | Ground               |

| A22     | CCLK            | Common Clock         |

| A23     | GND             | Ground               |

| A24     | BR              | Burst Request        |

| A25     | DBYT            | Device Byte          |

| A26     | MYAD            | My Address           |

| A27     | GND             | Ground               |

| A28     |                 | Not used             |

| A29     |                 | Not used             |

| A30     |                 | Not used             |

| A31     |                 | Not used             |

| A32     |                 | Not used             |

| A33     | PPON            | Primary Power On     |

| A34     | GND             | Ground               |

| A35     |                 | Not used             |

| A36     |                 | Not used             |

| A37     |                 | Not used             |

| A38     | +12             | +12V                 |

| A39     |                 | Not used             |

| A40     | +5              | +5V                  |

|         | l               |                      |

Table 2-2. I/O Channel Bus Connector J1 (Continued)

| PIN NO.    | SIGNAL MNEMONIC | SIGNAL DEFINITION    |

|------------|-----------------|----------------------|

| B1         | SAFETY          | Safety Ground        |

| B2         | DB15            | Data Bus, bit 15     |

| B3         | DB13            | Data Bus, bit 13     |

| B4         | GND             | Ground               |

| B5         | DB11            | Data Bus, bit 11     |

| B6         | DB9             | Data Bus, bit 9      |

| B7         | GND             | Ground               |

| B8         | DB7             | Data Bus, bit 7      |

| B9         | DB5             | Data Bus, bit 5      |

| B10        | GND             | Ground               |

| B11        | DB3             | Data Bus, bit 3      |

| B12        | DB1             | Data Bus, bit 1      |

| B13        | GND             | Ground               |

| B14        | AD3             | Address Bus, bit 3   |

| B15        | AD1             | Address Bus, bit 1   |

|            |                 | ,                    |

| B16        | GND             | Ground               |

| B17        | UAD             | Unary Address        |

| B18        | BP1             | Bus Primitive, bit 1 |

| B19        | CBYT            | Channel Byte         |

| B20        | POLL            | Pol1                 |

| B21        | GND             | Ground               |

| B22        | IOSB            | I/O Strobe           |

| B23        | GND             | Ground               |

| B24        | ARQ             | Attention Request    |

| B25        | DEND            | Device End           |

| B26        | RST             | Reset                |

| B27        | GND             | Ground               |

| B28        |                 | Not used             |

| B29        |                 | Not used             |

| B30        |                 | Not used             |

| B31        |                 | Not used             |

| B32        |                 | Not used             |

| B33        | 0110            | Not used             |

| B34        | GND             | Ground               |

| B35        |                 | Not used             |

| B36        |                 | Not used             |

| B37        |                 | Not used             |

| B38        | +12             | +12V                 |

| B39<br>B40 | +5              | Not used<br>+5V      |

| טוים       | ם ד             | 750                  |

| L          | l               | 1                    |

Table 2-3. Device Connector J2

| PIN NO.                                                                        | SIGNAL MNEMONIC                                         | SIGNAL DEFINITION                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12        | GND ATN SRQ IFC NDAC NRFD DAV EOI DIO4 DIO3 DIO2 DIO1   | Ground Not used Attention Service Request Interface Clear Not Data Accepted Not Ready For Data Data Valid End Or Identify Data Input/Output, Bit 4 Data Input/Output, Bit 3 Data Input/Output, Bit 2 Data Input/Output, Bit 1 |

| B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>B8<br>B9<br>B10<br>B11<br>B12<br>B13 | GND GND GND GND GND GND GND GND GND DI08 DI07 DI06 DI05 | Ground  Ground  Ground  Remote Enable  Data Input/Output, Bit 8  Data Input/Output, Bit 7  Data Input/Output, Bit 6  Data Input/Output, Bit 5                                                                                 |

# GENERAL GUIDELINES FOR HP-IB OPERATION

The following general guidelines should be observed when configuring an HP-IB system:

1. Devices or cable segments should not be added to an HP-IB system that is active.

If a device is to be added to an active HP-IB system, the possibility of errors will be minimized if the following procedure is used:

- a. Attach all new cables to the new device (the device to be added). Do not attach any unterminated cables to the existing bus.

- b. Power on the new device.

- c. Attach the new device (with power on) and its cable to the existing bus as a unit.

- 2. Devices which talk at a slower rate may be configured in the same system as high-speed devices, provided all of the requirements for high-speed operation are met.

- 3. If the card is NOT being used as the System Controller (SCTL switch DOWN), the high-speed load resistors should NOT be installed, regardless of speed configuration. In an HP-IB system, it is the duty of the System Controller to provide the necessary additional high-speed termination resistors. ADDING TERMINATION RESISTORS TO MORE THAN ONE CARD IN AN HP-IB SYSTEM MAY RESULT IN PERMANENT DAMAGE TO ANY OR ALL CARDS IN THE SYSTEM. Also, a powered-down System Controller will not allow the system to be used (as long as the System Controller is connected) because HP-IB bus drivers cannot drive the powered-down termination resistors.

- 4. Bus configuration is unimportant as long as the guidelines in the following paragraphs are observed

# **MEDIUM-SPEED OPERATION**

In order to ensure proper operation of the HP-IB bus, some rules must be observed regarding the total length of cables being used, as follows:

- 1. The total length of cable permitted to be used with one interface card must be less than or equal to two meters times the number of devices connected together for standard speed operation (the interface card is counted as one device).

- 2. The total length of cable in standard speed systems must not exceed 20 meters.

- 3. At least four out of every five devices should be powered on.

- 4. Refer to the following paragraph for high-speed operation.

# **HIGH-SPEED OPERATION**

To achieve the maximum possible data transfer rate within a system, the following guidelines must be followed:

- 1. Switch S7 should be set to high speed (down). Switch S7 determines the delay between data assertion and DAV during an HP-IB write from the computer to the device. With the switch in normal (up) position, a delay of approximately 500 nsec is realized. In the high-speed (down) position, the delay is reduced to approximately 350 nsec.

- 2. All devices expected to talk at high speed must use a settling time of 350 nsec or less.

- 3. All devices expected to talk at the higher rates should use 48 mA three-state drivers.

- 4. The device capacitance on each HP-IB line (except REN and IFC) should be less than 50 pF per device. In a system configuration, the total device capacitance should be no more than 50 pF for each equivalent resistive load in the system.

- 5. The optional load resistor pack must be installed for high-speed operation. The 18-pin Dual In-line Package (DIP) is marked 1810-0081, and is carried in a socket on the interface card marked "LOAD RESISTOR STORAGE". Remove the load resistor pack from the storage socket and install it in the socket directly behind connector J2 (peripheral device cable connector), with pin 1 on the package oriented toward the U82 marking next to the socket.

- 6. Interconnecting cable links should be as short as possible, with a maximum of 15 meters total length per system, and should have at least one equivalent resistive load per meter of cable (the high-speed resistor pack adds seven equivalent resistive loads).

| Number of<br>Devices | Maximum Total<br>Cable Length<br>(meters) | Maximum Average Cable<br>Length Between Devices<br>(meters) |

|----------------------|-------------------------------------------|-------------------------------------------------------------|

| 1                    | 9                                         | 9                                                           |

| 2                    | 10                                        | 5                                                           |

| 3                    | 11                                        | 3                                                           |

| 4                    | 1.2                                       | 3                                                           |

| 5                    | 13                                        | 2                                                           |

| 6                    | 14                                        | 2                                                           |

| 7 (maxir             | num) 15                                   | 2                                                           |

No more than eight devices are allowed in the system (the HP-IB interface card counts as one device). A maximum system would therefore be composed of the System Controller, with its high-speed resistor pack, and seven peripherals.

7. All devices should be powered on.

# INSTALLATION

# CAUTION

SOME OF THE COMPONENTS USED ON THE PRINTED CIRCUIT CARD ARE SUSCEPTIBLE TO DAMAGE BY STATIC DISCHARGE. REFER TO THE SAFETY CONSIDERATIONS INFORMATION AT THE FRONT OF THIS MANUAL BEFORE HANDLING THE CARD.

To install the HP-IB card, proceed as follows:

- 1. Determine if your computer system can supply the power needed for the HP-IB card. Refer to table 1-1 for power requirements.

- 2. Set switch S7 up (standard speed) or down (high speed) depending on whether or not the card is going to require the normal or fast settling mode of operation. All high-speed devices should be labeled appropriately. Check that the optional load resistor pack (see the "HIGH-SPEED OPERATION" paragraph) is installed if high-speed devices are going to be connected to the card.

- 3. Set switch S6 up (System Controller ON) or down (System Controller OFF) depending on whether the card is going to operate as the System Controller.

- 4. Set switches S1 through S5 to the card's HP-IB address. If the card is to be the System Controller (switch S7 UP), set the address to 30 decimal (S1 DOWN, S2 through S5 UP).

- 5. Turn off power to the computer and the HP-IB devices. Insert the HP-IB card into the desired slot in the I/O channel. Make sure that the components on the card are on the same side as the other installed cards. When installing the card, use care not to damage the components or traces on the card or on adjacent cards. Press the card firmly into place.

- 6. Connect the appropriate cable from J2 on the card to the device. See the paragraph "PERIPHERAL DEVICE INTERFACE CABLES" for cable information.

# START-UP

To start-up and verify correct operation of the HP-IB card, perform the following:

- 1. Turn on computer system power.

- 2. A self-test is contained on the card. The host computer system determines if the self-test is run automatically at power-on or must be invoked by the user. Refer to the appropriate manual for your system for a description of self-test initiation.

When the self-test executes, the LED located on the card should light briefly and go out. This indicates that the card passed self-test. If the LED does not light at all, the card is defective. If the LED stays on, the card did not pass self-test.

If the LED flashes continuously, the address switches have been set to an illegal address (31 decimal, all address switches UP). Set the address switches (S1 through S5) to a valid address (zero through 30) and issue a system reset. The LED should go out, indicating a valid address has been read and the card has passed self-test.

If the self-test indicates that the card is defecive, it is recommended that you return the card to Hewlett-Packard; refer to the next paragraph for reshipment information. If you wish to perform maintenance on the card, however, refer to Sections 5, 6, and 7 for maintenance information, replaceable parts lists, and schematic logic diagrams, respectively.

# **RESHIPMENT**

If the HP-IB is to be shipped to Hewlett-Packard for any reason, attach a tag identifying the owner and indicating the reason for shipment. Include the part number of the HP-IB.

Pack the HP-IB in the original factory packing material, if available. If the original material is not available, good commercial packing material should be used. Reliable commercial packing and shipping companies have the facilities and materials to repack the item. BE SURE TO OBSERVE ANTI-STATIC PRECAUTIONS.

# PRINCIPLES OF OPERATION

The HP 27110A HP-IB Interface card provides an interface between a Hewlett-Packard computer system and an HP-IB system of up to 14 devices. Several such HP-IB systems, each connected to an HP-IB interface card, can be connected to one host computer.

## **OVERVIEW**

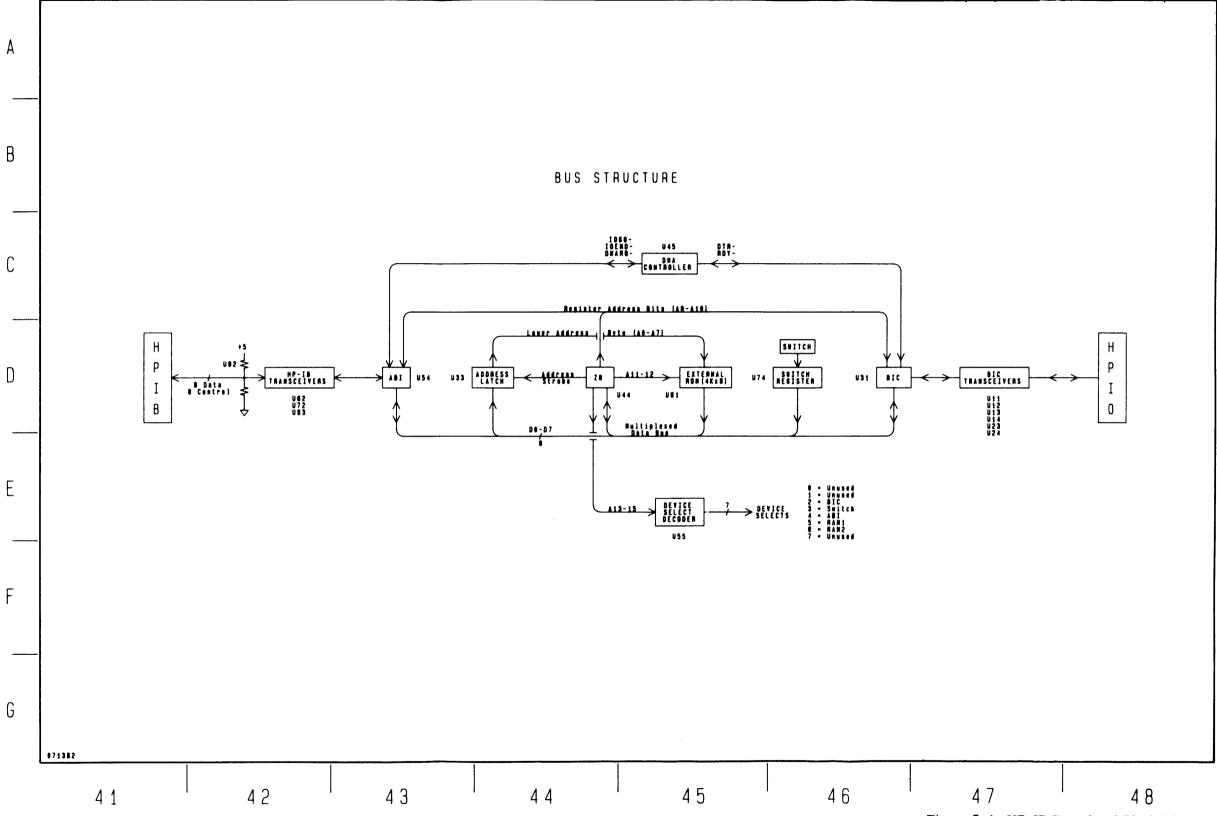

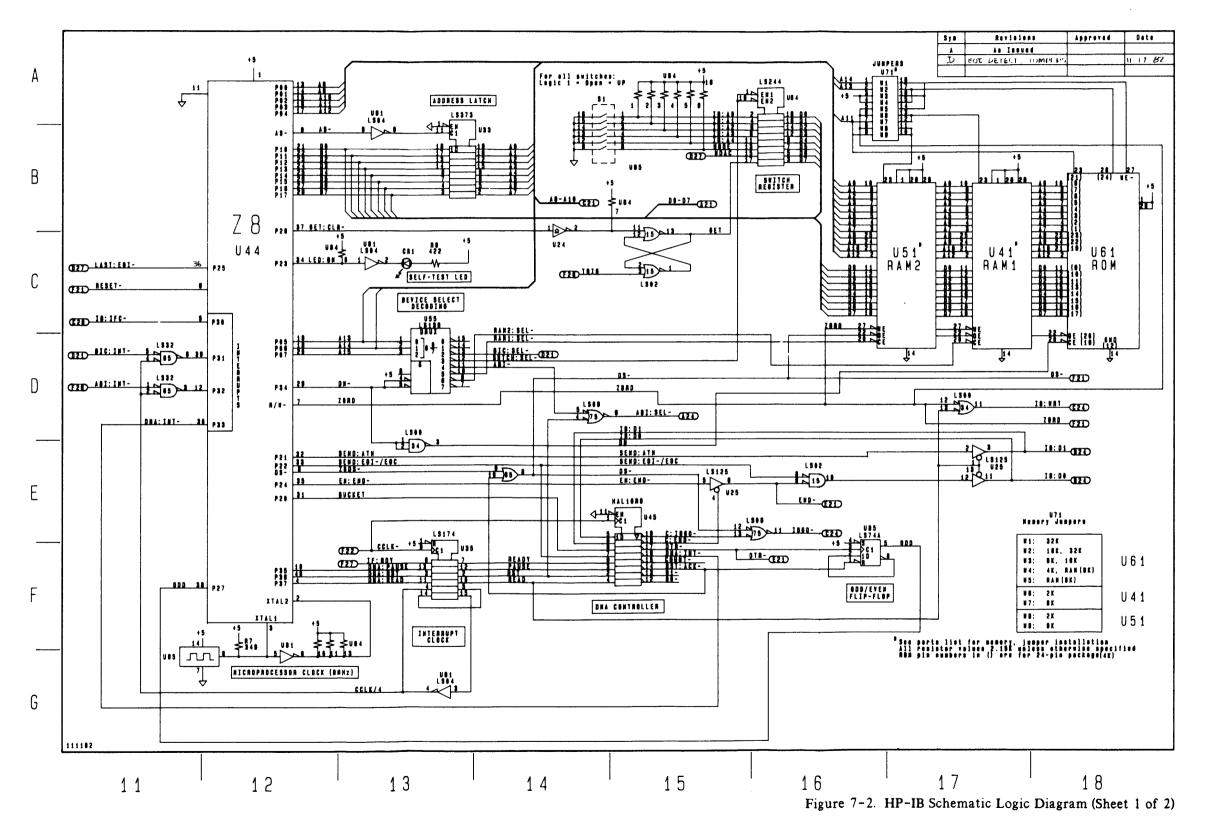

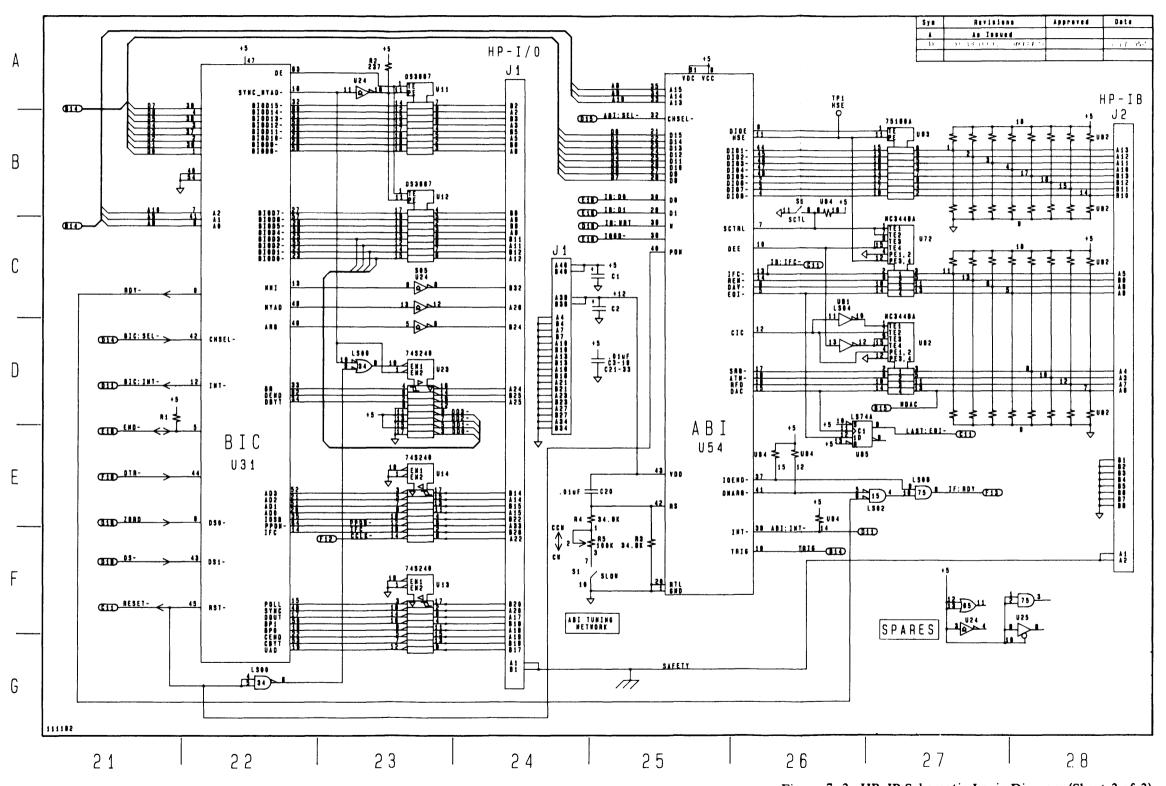

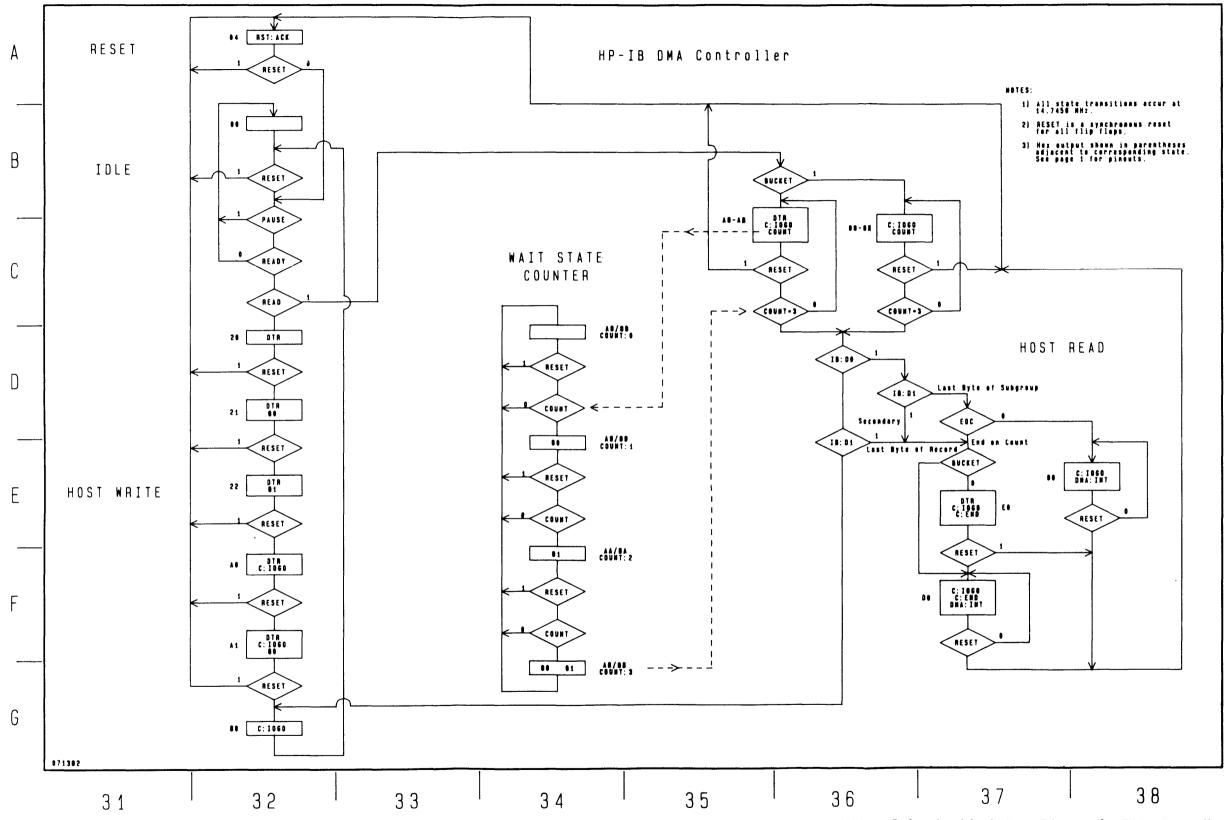

Block and schematic diagrams for the HP-IB card are contained in Section VII. The functional block diagram of the HP-IB card is shown in figure 7-1; the schematic logic diagram is shown in figure 7-2. Reference is made to these two figures during the following discussions. Note that figure 7-2 consists of two sheets. References to this figure will be as follows: 1-A11, 7-2; 2-C23, 7-2, etc., where the first number, 1 or 2, refers to the sheet number, the combination of letters A through G and numbers 11 through 28 (A11, C23, etc.) refer to the quadrants on the individual sheets, and 7-2 refers to the figure number.

As shown in figure 7-1, six devices have access to all eight lines of the data bus as follows:

| Device              | Access Direction                      |

|---------------------|---------------------------------------|

| <del></del>         | · · · · · · · · · · · · · · · · · · · |

| HP-IB Circuit       | Read/Write                            |

| Address Latch       | Write                                 |

| Z8 Microcomputer    | Read/Write                            |

| External ROM        | Read                                  |

| Switch Register     | Read                                  |

| Backplane Interface | Read/Write                            |

| Circuit (BIC)       |                                       |

The devices are controlled by the Z8 or the DMA controller (see figure 7-1.)

Interface between the HP-IB card and the I/O channel is accomplished via the Backplane Interface Circuit (BIC, see 7-1 and 2-A22, 7-2) gate array and transceivers. Interface between the card and the HP-IB bus is accomplished via the HP-IB circuit (see 7-1 and 2-A25, 7-2).

Direct memory access (DMA) is used on HP-IB data transfers, and is accomplished via a DMA state machine controller contained in a programmable logic array (see 7-1 and 1-E15, 7-2), and controlled by the Z8 microcomputer (7-1 and 1-A12, 7-2). The Z8 does not allow other devices (including itself) to use the data bus while DMA is in progress.

The Address Latch (7-1 and 1-B13, 7-2) latches the lower eight address bits (A0 - A7) from the multiplexed Address/Data bus. Only the memory components (ROM, RAM) require these address bits - all other devices are addressed via A8 - A12.

The Switch Register (1-A16, 7-2) buffers the HP-IB address of the card to the Z8.

## **BACKPLANE INTERFACE**

The Backplane Interface Circuit (BIC, a CMOS gate array chip, see 2-A22, figure 7-2) provides a standard method of interfacing to the I/O channel (backplane).

From a hardware standpoint, the BIC performs as a simple microprocessor peripheral. As used in the HP-IB card, the BIC has the following standard signal lines:

- \* Eight-bit bidirectional tri-state data bus

- \* Three-bit address bus

- \* Chip Select line to enable the chip for addressed data transfers

- \* Data Strobe line to strobe incoming data

- \* Read/Write line to specify data transfer direction

- \* Interrupt line to alert the Z8 of important events occurring on the I/O channel

Table 3-1 lists pin connections and describes signals to the BIC.

Table 3-1. BIC Chip Pin Connections

| PIN<br>NO. | SIGNAL<br>MNEMONIC | BIC<br>MMEMONIC  | DESCRIPTION                                            |

|------------|--------------------|------------------|--------------------------------------------------------|

| 1 2        | D0<br>D2           | D0<br>D2         | Data Bus, Bit 0<br>Data Bus, Bit 2                     |

| 3          | D4                 | D4               | Data Bus, Bit 4                                        |

| 4          | D6                 | D6               | Data Bus, Bit 6                                        |

| 5          | END-               | END-             | Indicates end of data read or                          |

|            |                    |                  | write                                                  |

| 6          | A8                 | A0               | Register Address, Bit 0                                |

| 7          | A10                | A2               | Register Address, Bit 2                                |

| 8          | Z8RD               | DSO-             | Z8 Read (Read Data Strobe)                             |

| 9          | RDY-               |                  | Asserted by BIC when ready for                         |

|            |                    |                  | data transfer                                          |

| 10         |                    |                  | Not used                                               |

| 11         |                    |                  | Not used                                               |

| 12         | BIC: INT-          | INT-             | BIC Interrupt                                          |

| 13         | NMI                | NMI              | Non-Maskable Interrupt                                 |

| 14         | IFC (RST)          | IFC              | Interface Clear (Reset)                                |

| 15         | POLL               | POLL             | Poll                                                   |

| 16         |                    | SYNC_MYAD-       | In conjunction with DE, determines                     |

|            |                    |                  | data bus drivers mode of operation                     |

| 17         | DOUT               | DOUT             | Data Out, specifies data bus                           |

|            |                    |                  | direction                                              |

| 18         | BP0                | BP0              | Bus Primitive, Bit O. With BP1,                        |

| 1.0        |                    |                  | specifies bus primitive operation                      |

| 19         | UAD                | UAD              | Unary Address, latches BIC channel                     |

| 00         | 420                | 420              | address after a PPON or IFC                            |

| 20         | AD0                | AD0              | Address Bus, Bit 0                                     |

| 21         | AD2                | AD2              | Address Bus, Bit 2                                     |

| 22         | CEND               | CEND             | Channel End                                            |

| 23<br>24   | DB0<br>DB1         | BIODO-           | Backplane I/O Data, Bit 0                              |

| 25         | DB3                | BIOD1-<br>BIOD3- | Backplane I/O Data, Bit 1<br>Backplane I/O Data, Bit 3 |

| 26         | DB5                | BIODS-           | Backplane I/O Data, Bit 5                              |

| 27         | DB7                | BIOD7-           | Backplane I/O Data, Bit 7                              |

| 28         | DB9                | BIOD9-           | Backplane I/O Data, Bit 9                              |

| 29         | DB10               | BIOD10-          | Backplane I/O Data, Bit 10                             |

| 30         | DB10               | BIOD11-          | Backplane I/O Data, Bit 11                             |

| 31         | DB13               | BIOD13-          | Backplane I/O Data, Bit 13                             |

| 32         | DB15               | BIOD15-          | Backplane I/O Data, Bit 15                             |

| 33         | BR                 | BR               | Burst Request - at least one more                      |

|            |                    |                  | transfer after current one                             |

| 34         | DBYT               | DBYT             | Device Byte, indicates current                         |

|            |                    |                  | transfer is a byte                                     |

| 35         | IOSB               | IOSB             | I/O Strobe                                             |

|            |                    | L                | ·                                                      |

Table 3-1. BIC Chip Pin Connections (Continued)

| PIN<br>NO.   | SIGNAL<br>MNEMONIC | BIC<br>MNEMONIC        | DESCRIPTION                            |

|--------------|--------------------|------------------------|----------------------------------------|

| '''          | THILL ISTITU       | 1 11 12 12 11 10 11 10 | DESONT TION                            |

|              |                    |                        | ,                                      |

| 36           | D1                 | D1                     | Data Bus, Bit 1                        |

| 37           | D3                 | D3                     | Data Bus, Bit 3                        |

| 38           | D5                 | D5                     | Data Bus, Bit 5                        |

| 39           | D7                 | D7                     | Data Bus, Bit 7                        |

| 40           | GND                | GND                    | Ground                                 |

| 41           | A9                 | A1                     | Register Address, Bit 1                |

| 42           | BIC:SEL-           | CHSEL-                 | BIC Select, enables the BIC to         |

| }            |                    |                        | read or write                          |

| 43           | DS-                | DS1 -                  | Data Strobe (Write Data Strobe)        |

| 44           | DTR-               | DTR-                   | Data Transfer Request                  |

| 45           | RESET-             | RST-                   | Reset                                  |

| 46           | ARQ                | ARQ                    | Attention Request                      |

| 47           | +5                 |                        | +5 V                                   |

| 48           | SYNC               | SYNC                   | Synchronize, signals that an           |

|              |                    |                        | addressed bus operation will occur     |

| 49           | MYAD               | MYAD                   | My Address                             |

| 50           | BP1                | BP1                    | Bus Primitive, Bit 1 - with BPO,       |

| -,           | 454                | A.D.4                  | specifies bus primitive operation      |

| 51           | AD1                | AD1                    | Address Bus, Bit 1                     |

| 52           | AD3                | AD3                    | Address Bus, Bit 3                     |

| 53           | CBYT               | CBYT                   | Channel Byte, indicates that           |

|              | 0112               | 0112                   | current transfer is a byte             |

| 54           | GND                | GND                    | Ground                                 |

| 55           | DB2<br>DB4         | BIOD2-                 | Backplane I/O Data, Bit 2              |

| 56<br>57     |                    | BIOD4-                 | Backplane I/O Data, Bit 4              |

| 58           | DB7<br>DB8         | BIOD7-                 | Backplane I/O Data, Bit 7              |

| 59           | DB12               | BIOD8-<br>BIOD12-      | Backplane I/O Data, Bit 8              |

| 60           | DB14               | BIOD12-                | Backplane I/O Data, Bit 12             |

| 61           | ופע                | -11עטום                | Backplane I/O Data, Bit 14<br>Not used |

| 62           | DEND               | DEND                   | Device End, indicates end of           |

| ا ا          | שנוע               | שנוזט                  | transfer                               |

| 63           | DE                 | DE                     | Direction Enable                       |

| 64           | PPON               | PPON-                  | Primary Power On                       |

| <u>ا</u> ٽ ٰ |                    | 110/1                  | 11 211 y 1 0 w C 1 011                 |

A set of eight BIC registers, addressed by the 3-bit address bus, perform the following functions:

| Register Number | Write Direction  | Read Direction    |

|-----------------|------------------|-------------------|

| 0               | <====== DA       | TA ======>        |

| 1               | COMMAND          | SRQ ADDRESS       |

| 2               | ORDER            | BIC STATUS        |

| 3               | BACKPLANE STATUS | BACKPLANE CONTROL |

| 4               | <====== CONFIG   | JRATION =====>    |

| 5               | <====== INTERR   | JPT ======>       |

| 6               | <===== INTERRUP  | T MASK =====>     |

| 7               | <====== RESER'   | /ED ======>       |

In addition to the eight registers, the BIC provides:

A "ninth" data bit called END-. This open collector line is bi-directional. When the HP-IB card is performing a host write, this data bit is set true (LOW) to indicate the associated data byte is the last of that transfer. When reading from the host, the BIC drives END- true when the data byte on the 8-bit bus is the last of the transfer. Timing for END- is identical to data bus timing, thus the term "ninth data bit".

DMA lines DTR- (Data Transfer Request) and RDY- (Ready) for unaddressed data transfers. These lines allow the BIC to transfer data in or out quickly without the necessity of repeatedly addressing the FIFO (First In First Out) data register in the HP-IB circuit. The DTR- and RDY- lines provide a 2-wire handshake for performing unaddressed FIFO data transfers (DMA). DTR- is driven by the DMA controller when the controller is ready to begin a DMA transfer. RDY- is driven by the BIC when it is ready to begin a data transfer (when the FIFO data register has room on a host read or the FIFO is not empty on a host write). DTR- is not allowed to be driven true unless RDY- is true.

A reset line (RESET-) to initialize the Z8. RESET- informs the Z8 that one or more of the following events has occurred:

- \* Primary power has been turned on

- \* A CHANNEL I/O Interface Clear has been issued (global reset)

- \* A CHANNEL I/O Device Clear has been issued (addressed reset)

RESET- connects directly to the Z8 reset input. By polling the BIC registers after a reset, the Z8 can determine which of the three types of reset occurred, and take the appropriate action.

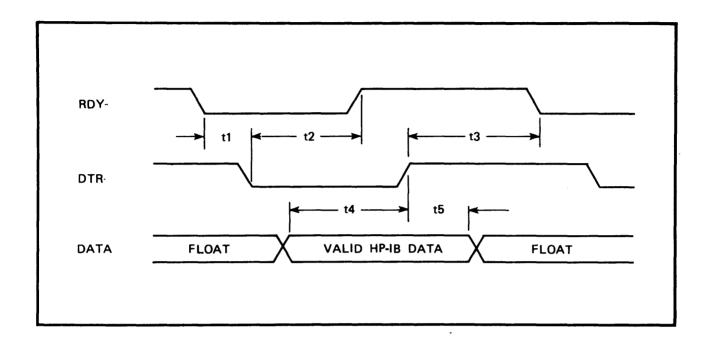

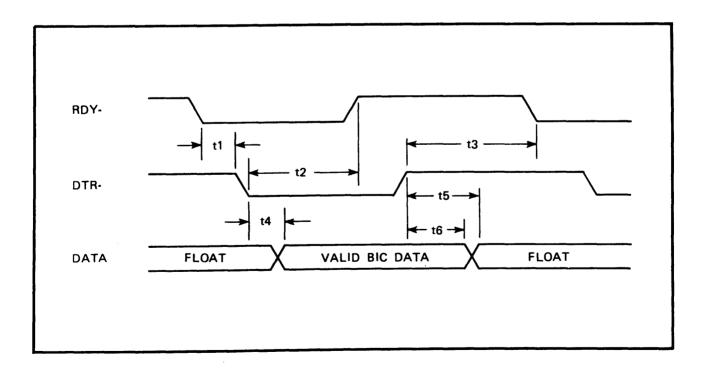

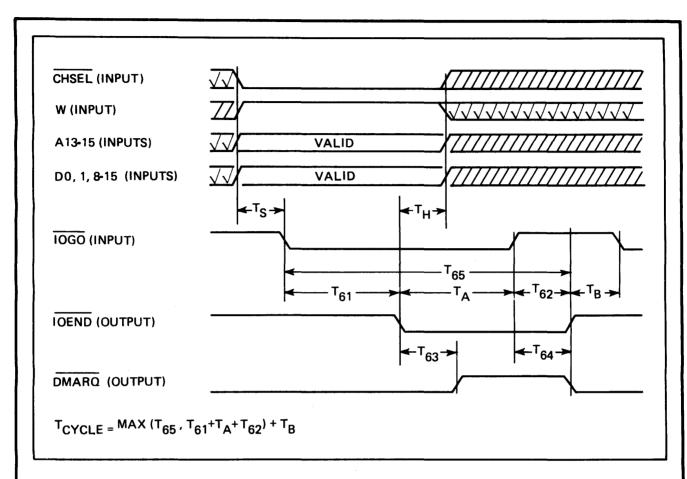

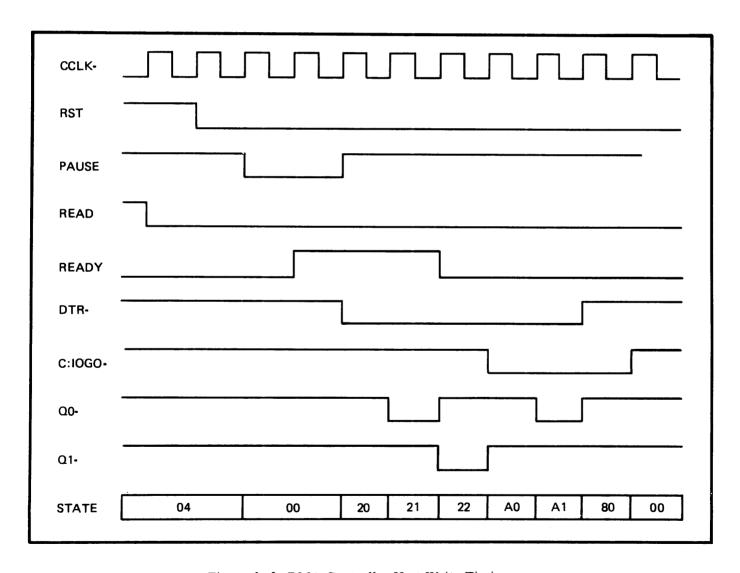

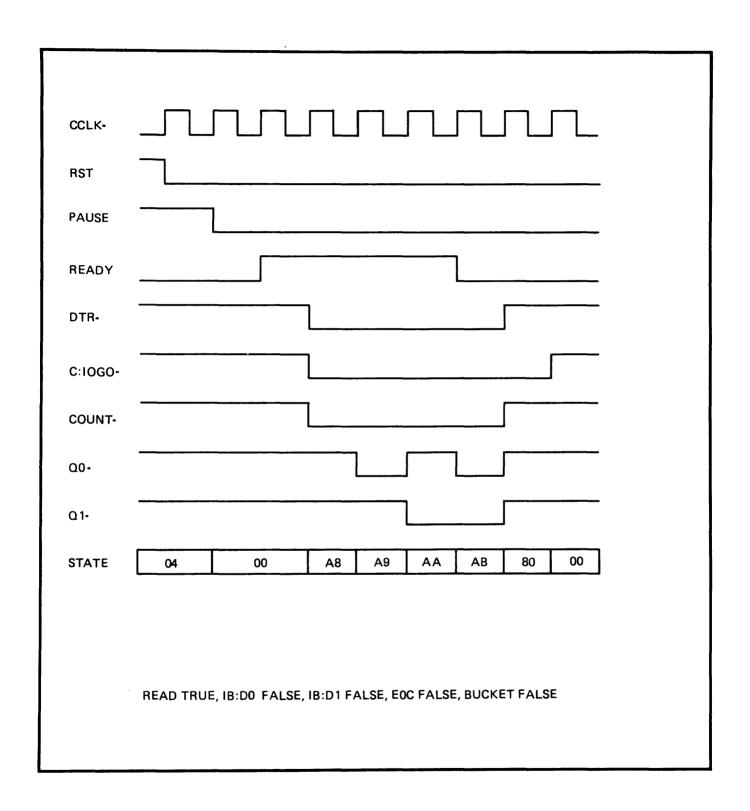

A timing diagram for a BIC DMA - host read is shown in figure 3-1. BIC DMA - host write timing is shown in figure 3-2.

Figure 3-1. BIC DMA - Host Read Timing Diagram

Figure 3-2. BIC DMA - Host Write Timing Diagram

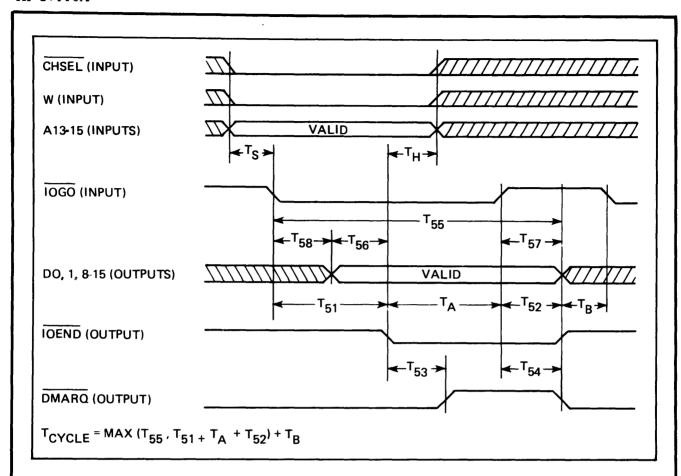

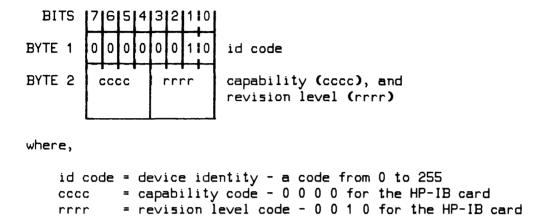

# **HP-IB INTERFACE**