H 112 Series Instruction Manual

# H 112 DIGITAL CONTROLLER

Central Processor Description

Volume I

# Honeywell

COPYRIGHT © 1970, by Honeywell Inc., Computer Control Division, Framingham, Massachusetts. Contents of this publication may not be reproduced in any form, in whole or in part, without permission of the copyright owner. All rights reserved.

Printed in U.S.A.

Published by the Publications Department, Honeywell Inc. Computer Control Division

## **CONTENTS**

|                                         | Page |                                           | Page |

|-----------------------------------------|------|-------------------------------------------|------|

| SECTION I                               |      | Instruction Decoding                      | 3-4  |

| INTRODUCTION                            |      | Memory Reference Group Decoding           | 3-4  |

|                                         |      | Input/Output Group Decoding               | 3-5  |

| Scope                                   | 1-1  | Shift Group Decoding                      | 3-6  |

| H112 Controller Characteristics         | 1-1  | Generic Group Decoding                    | 3-6  |

| References                              | 1-1  | Skip Group Decoding                       | 3-6  |

| Machine Instructions                    | 1-1  | Shift Counter Operations (LBD 12.04)      | 3-6  |

| Addressing                              | 1-1  | Adder Operations (LBD 12.03)              | 3-7  |

| Memory Organization                     | 1-1  | Instruction Execution                     | 3-7  |

| 4K Memory Addressing                    | 1-2  | STA and LDA Instructions                  | 3-7  |

| 8K Memory Addressing                    | 1-2  | ADD and ANA Instructions                  | 3-8  |

| Maintenance Drawings                    | 1-2  | IRS Instruction                           | 3-9  |

|                                         |      | Shift Instructions (LGR, ARS, RAR)        | 3-13 |

| SECTION II                              |      | I/O Instructions                          | 3-14 |

| BLOCK DIAGRAM DISCUSSION                |      | Generic Instructions                      | 3-15 |

|                                         |      | Interrupt Operation                       | 3-20 |

| Timer (T)                               | 2-1  | Load Mode                                 | 3-20 |

| Register Transfer Bus (RB)              | 2-1  | Single Step Mode                          | 3-24 |

| Memory (M)                              | 2-1  | Control Panel Functions                   | 3-24 |

| Memory Address Register (Y)             | 2-1  | Remote Machine Control                    | 3-26 |

| Program Counter (P)                     | 2-1  | Power Distribution                        | 3-27 |

| Working Register (W)                    | 2-2  | Major Instruction Group Operations        | 3-27 |

| Accumulator (A)                         | 2-2  | 1 1 1                                     |      |

| Adder (AD)                              | 2-2  | SECTION IV                                |      |

| Shift Counter (C)                       | 2-2  | SIGNAL MNEMONICS                          |      |

| Function Register (F)                   | 2-2  |                                           |      |

| Decoder (D)                             | 2-2  | SECTION V                                 |      |

| Bank Register (B)                       | 2-2  | H112 MAGNETIC CORE MEMORY                 |      |

| Z-Register (Z)                          | 2-2  |                                           |      |

| Machine Operation                       | 2-5  | Description                               | 5-1  |

| Instruction Fetch                       | 2-5  | System Layout                             | 5-1  |

| Indirect Addressing                     | 2-5  | Specifications                            | 5-1  |

| Instruction Execution                   | 2-5  | Memory Cycle Timing                       | 5-1  |

| Interrupts                              | 2-7  | Principles of Operation                   | 5-1  |

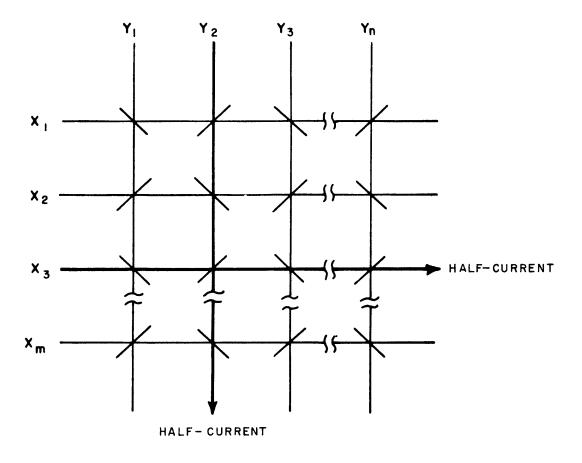

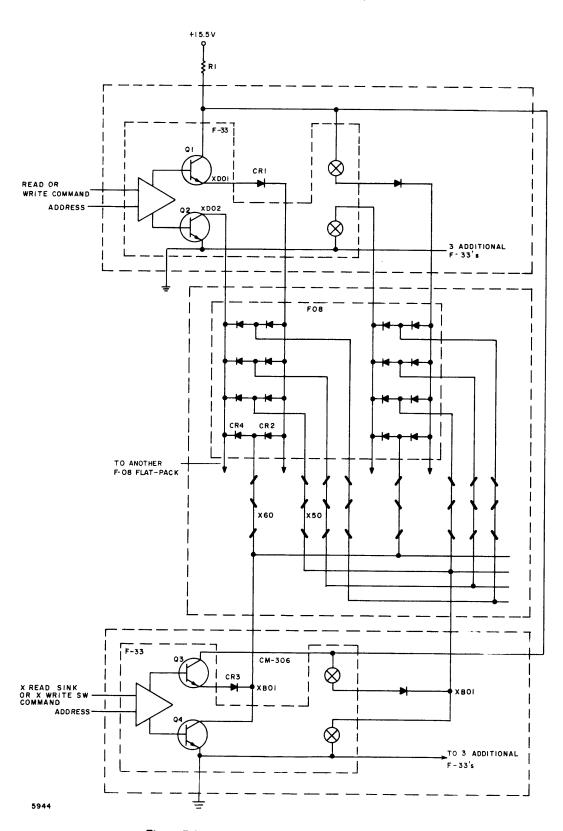

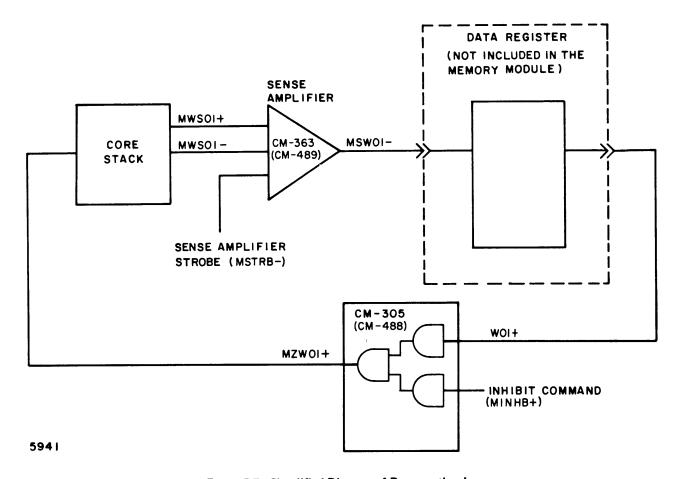

| Direct Data Channel                     | 2-8  | Principles of Magnetic Core Memories      | 5-1  |

|                                         | 20   | Addressing and Selection                  | 5-7  |

| SECTION III                             |      | Timing and Control                        | 5-7  |

| DETAILED THEORY OF OPERATION            |      | Operating Modes                           | 5-7  |

|                                         |      | Interface Timing                          | 5-10 |

| Register Construction                   | 3-1  | Voltage Sequencing                        | 5-10 |

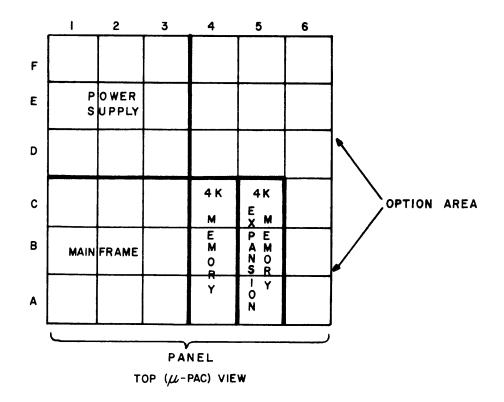

| Memory Address Register (LBD 12.07)     | 3-1  | Installation of Expansion Memory          | 5-11 |

| Program Counter (LBD 12.06)             | 3-1  | 1                                         |      |

| Accumulator (LBD 12.09)                 | 3-1  | SECTION VI                                |      |

| Working Register (LBD 12.08)            | 3-1  | MAINTENANCE                               |      |

| Function (Op Code) Register (LBD 12.07) | 3-1  | · <del> · ·</del>                         |      |

| Fimer (LBD 12.02)                       | 3-2  | μ-PAC Complement, Spare Parts, and        |      |

| Instruction Fetch                       | 3-3  | Equipment                                 | 6-1  |

| Fetch With Direct Addressing            | 3-3  | μ-PAC Maintenance, Extraction, and Repair | 6-1  |

| Fetch With Indirect Addressing          | 3-4  | Preventive Maintenance                    | 6-1  |

## **CONTENTS** (Cont)

|       |                                     | Page |             |                                                    | Page         |

|-------|-------------------------------------|------|-------------|----------------------------------------------------|--------------|

| Ins   | erting and Removing System μ-PACs   | 6-3  | 5-7         | Simplified Diagram of Regeneration                 |              |

| μ-P   | AC Troubleshooting                  | 6-3  |             | Loop                                               | 5-10         |

|       | mponent Checking                    | 6-3  | 5-8         | Module Locations                                   | 5-11         |

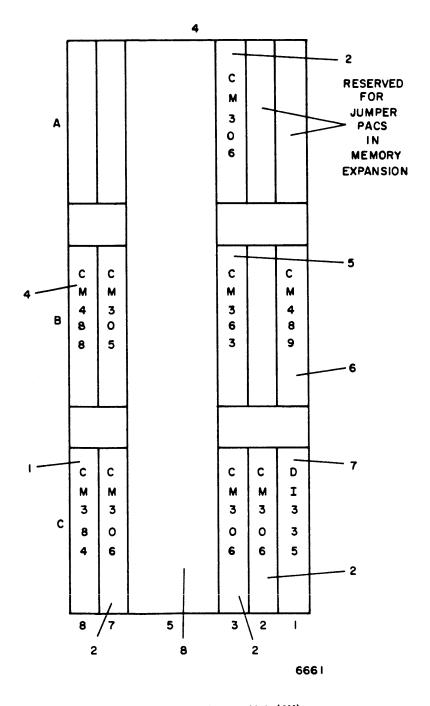

| Co    | mponent Replacement                 | 6-3  | 5-9         | 4K Expansion Memory                                | 5-12         |

| Memo  | ory Troubleshooting                 | 6-3  | 6-1         | Normal Waveforms at Test Points and                |              |

| Me    | mory Drive and Inhibit Voltage      |      |             | μ-PAC Connector Pins                               | <b>6-6</b>   |

| C     | Calibration                         | 6-3  |             | Coding Drawing 70026048                            |              |

| Me    | mory Strobe Timing Calibration      | 6-3  |             | (Sheet 1 of 3)                                     | 7-3          |

| Co    | rrective Maintenance Procedures     | 6-3  |             | (Sheet 2 of 3)                                     | 7-4          |

| Ma    | gnetic Core Stack Maintenance       | 6-5  |             | (Sheet 3 of 3)                                     | 7-5          |

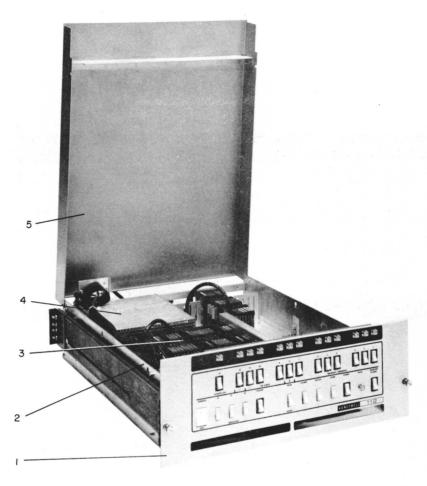

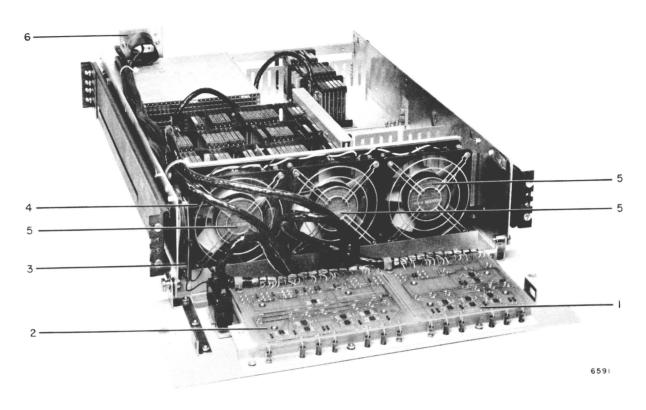

|       |                                     |      | 7-1         | H112-01 Digital Controller                         | 7-7          |

|       | SECTION VII                         |      | 7-2         | Panel Front Assembly                               | 7-8          |

| ILI   | LUSTRATED PARTS BREAKDOWN (IPI      | 3)   | 7-3         | Drawer Main Assembly                               | 7-9          |

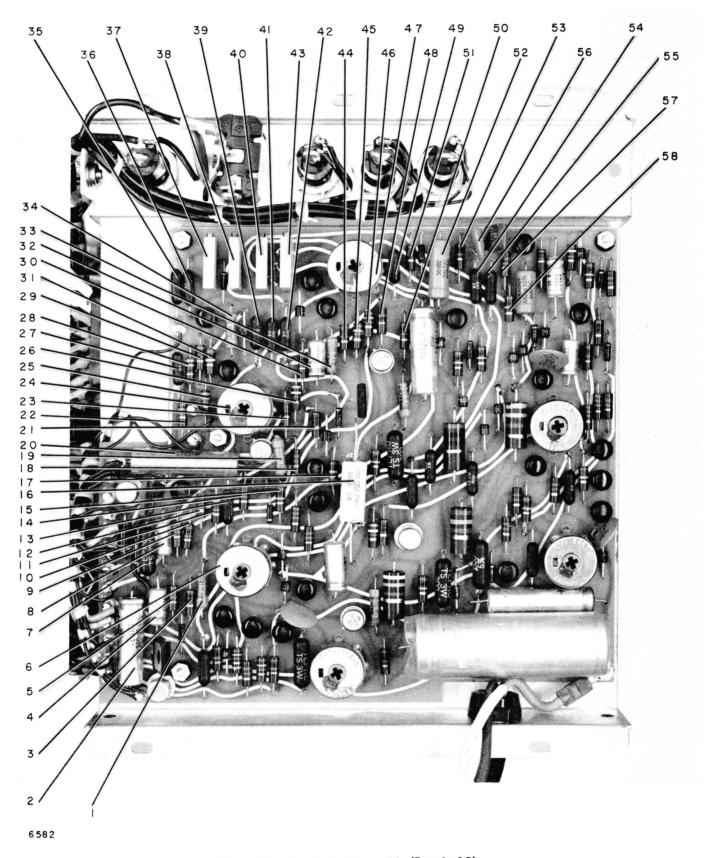

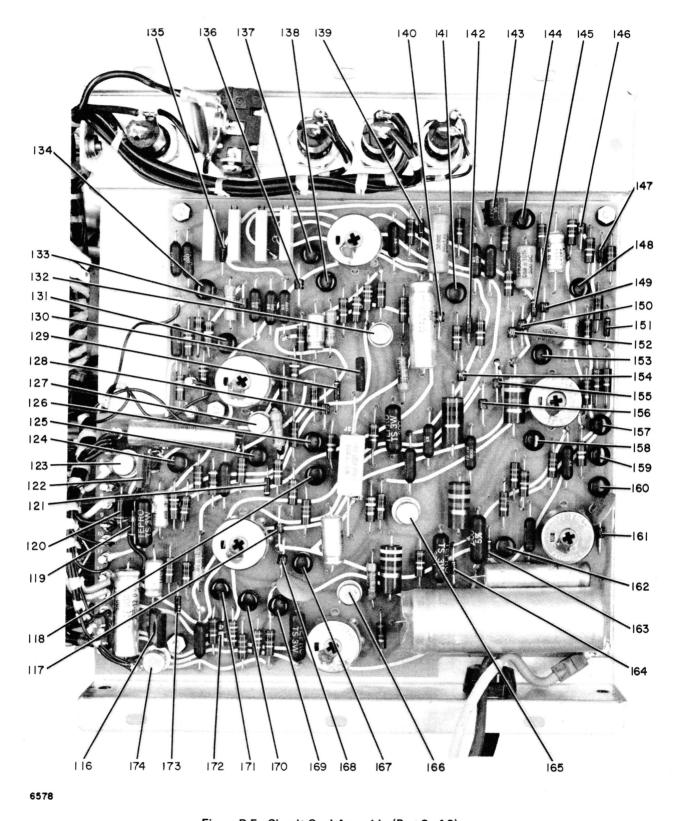

|       |                                     |      | 7-4         | Printed Circuit Board Assembly A                   | 7-10         |

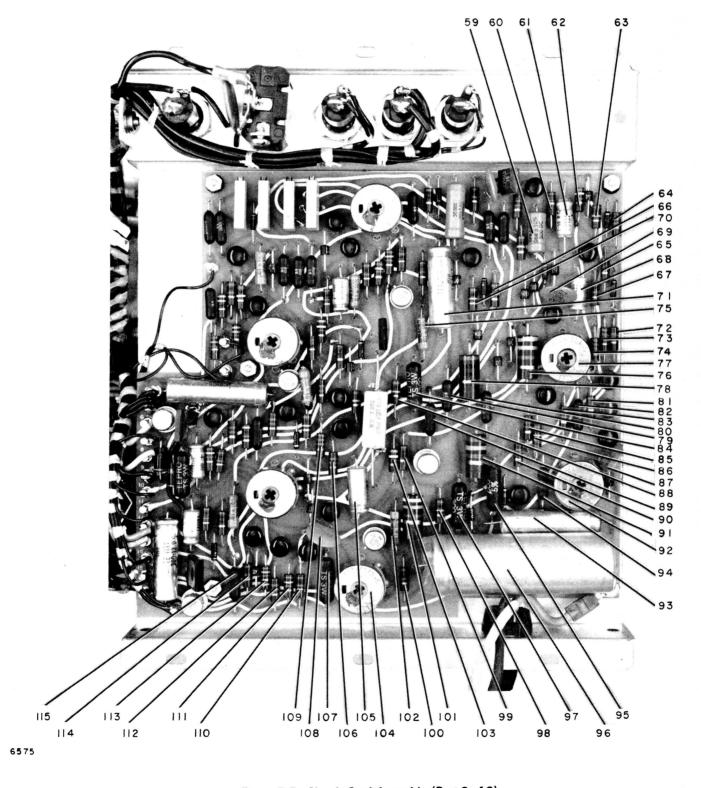

| Intro | duction                             | 7-1  | 7-5         | Printed Circuit Board Assembly B                   | 7-12         |

|       | rpose                               | 7-1  | <b>7-</b> 6 | Logic and Memory (4K) Assembly                     | 7-14         |

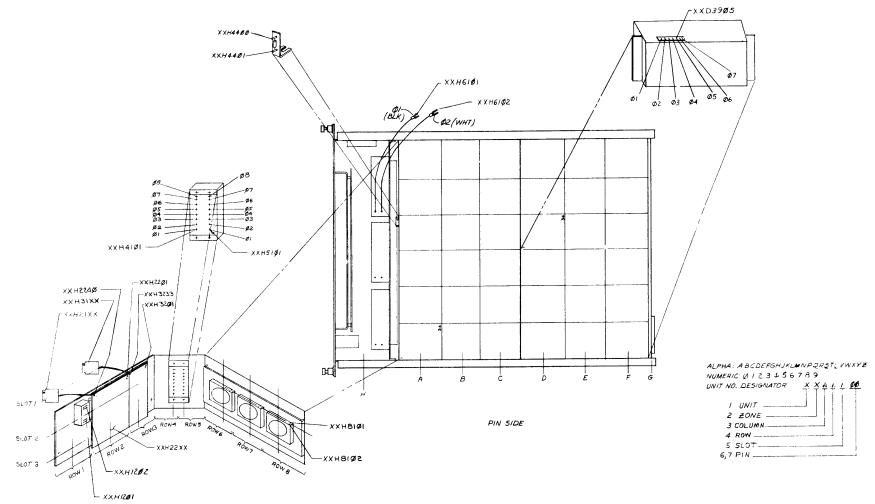

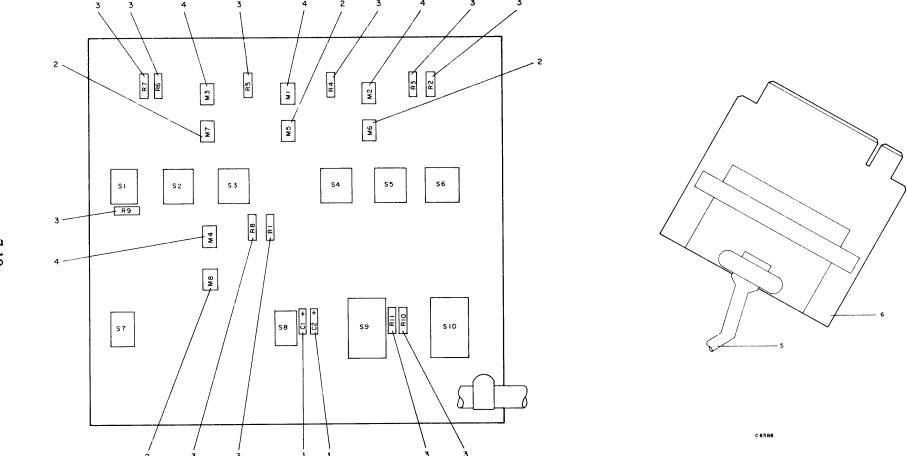

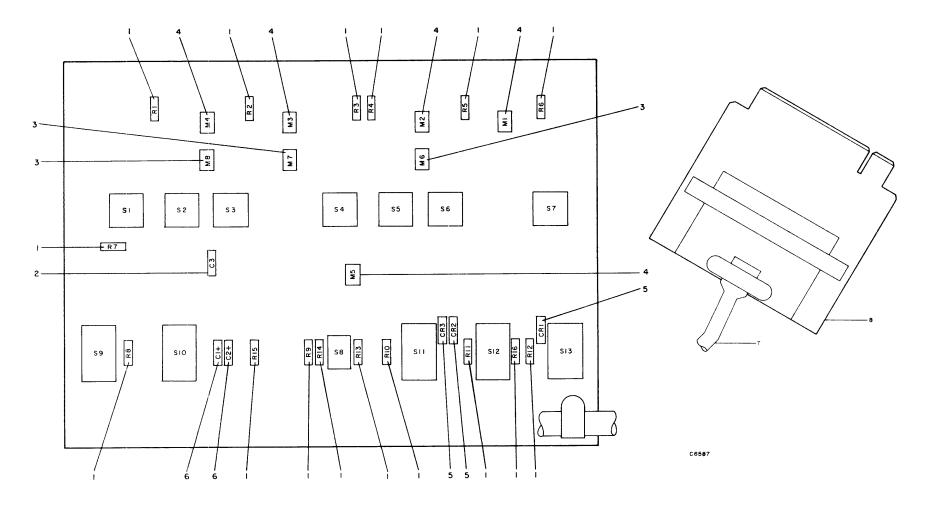

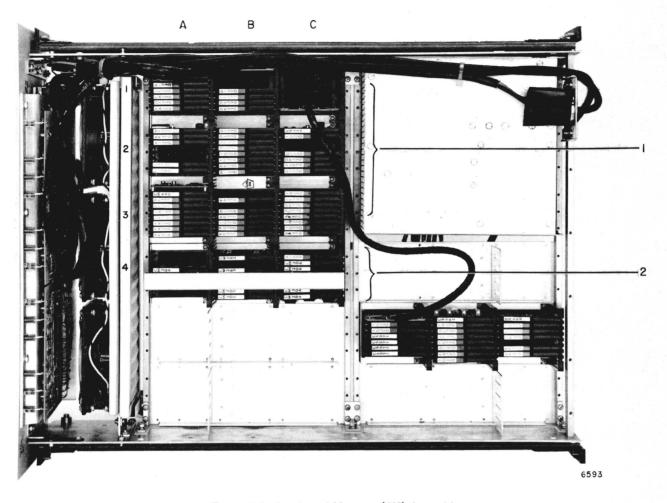

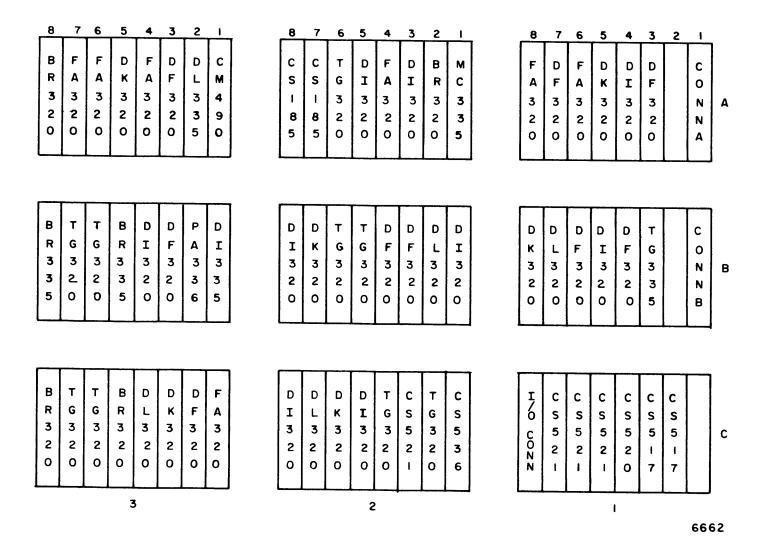

|       | uipment Coding                      | 7-1  | 7-7         | Logic PAC Layout                                   | 7-15         |

|       | thods of Use                        | 7-1  | 7-8         | Core Memory Unit (4K)                              | 7-18         |

|       | rts Procurement Guide               | 7-2  | 7-9         | Cabling Block Diagram                              | 7-20         |

| Grou  | p Assembly Parts List               | 7-6  |             |                                                    |              |

|       |                                     |      |             | TABLES                                             |              |

|       | APPENDICES                          |      |             |                                                    | Page         |

| A     | Description of Special $\mu$ -PACs  | A-1  | 1 1         | M. I. T. A. Allena                                 | 1.2          |

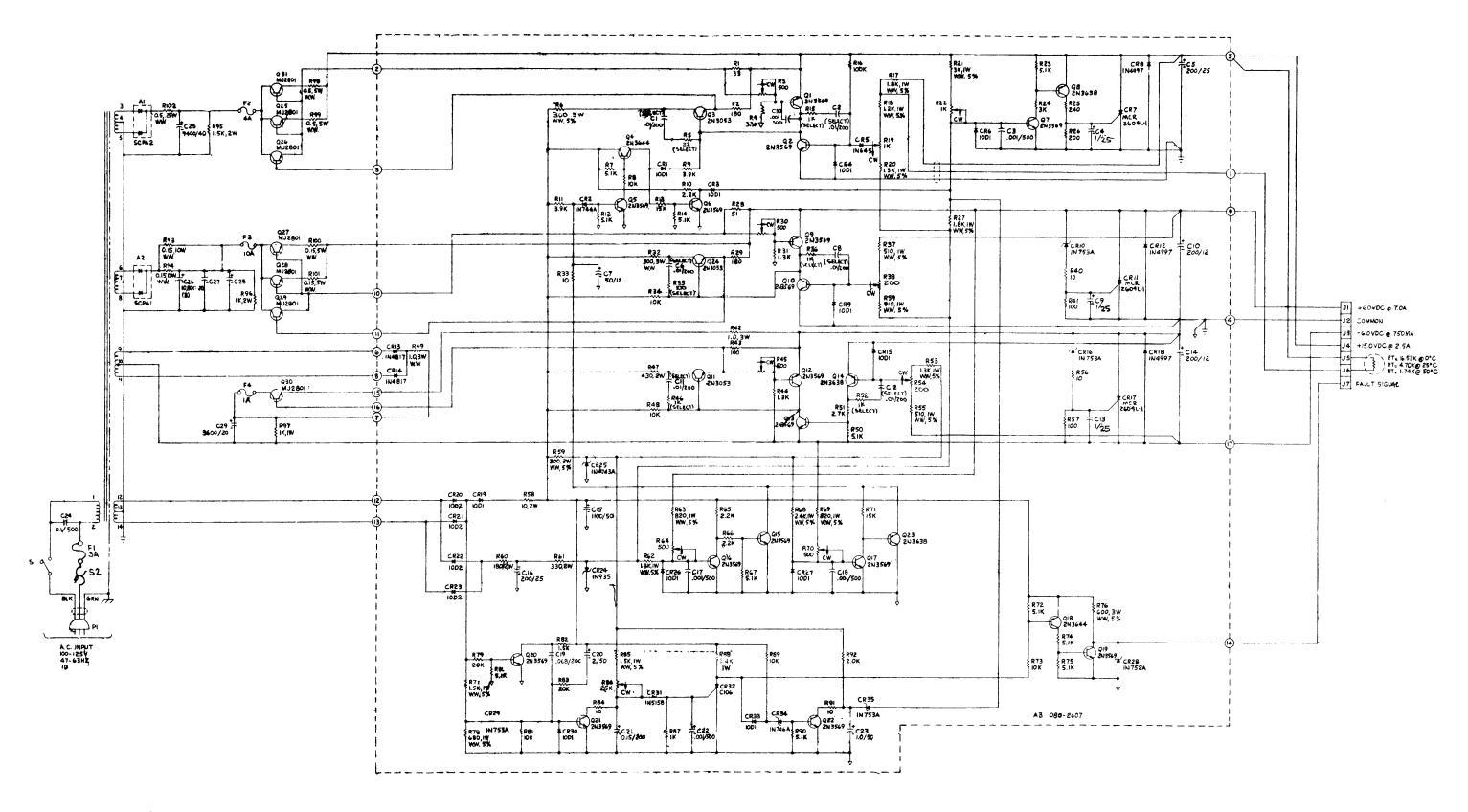

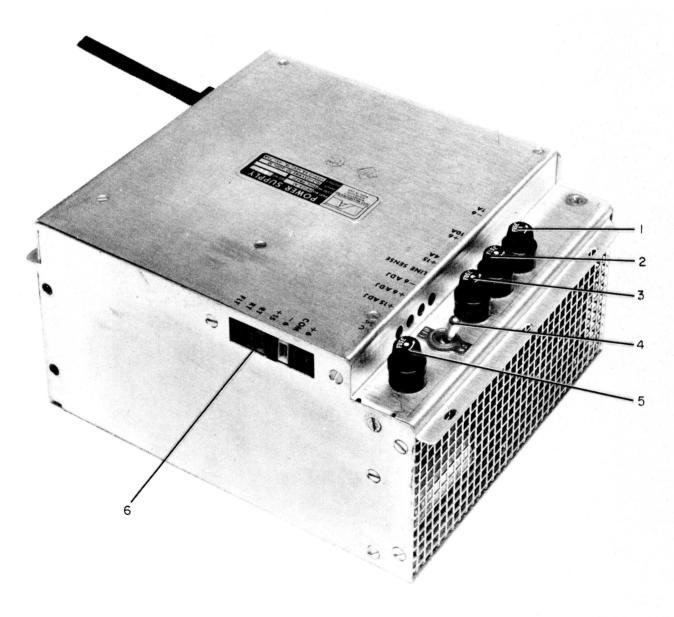

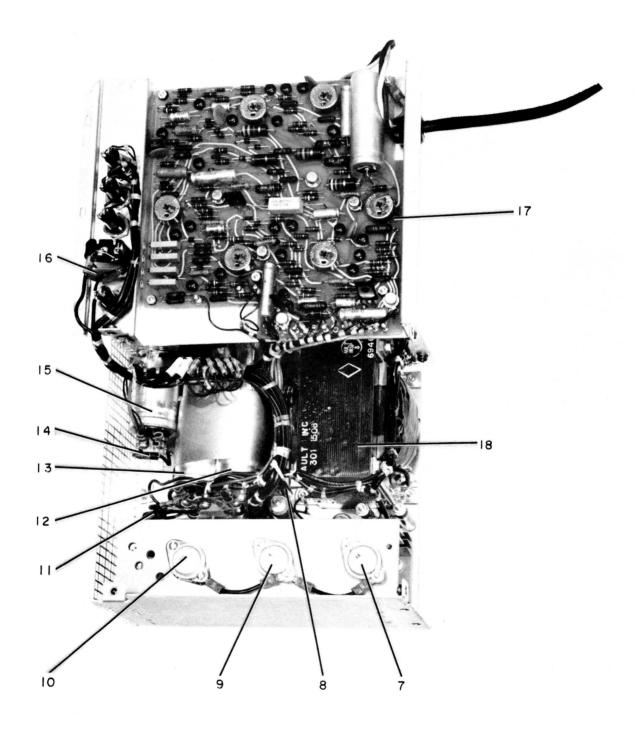

| В     | H112 Power Supply                   | B-1  | 1-1         | Machine Instructions                               | 1-3          |

|       |                                     |      | 1-2         | Memory Referencing in 4K Mode                      | 1-5<br>1-5   |

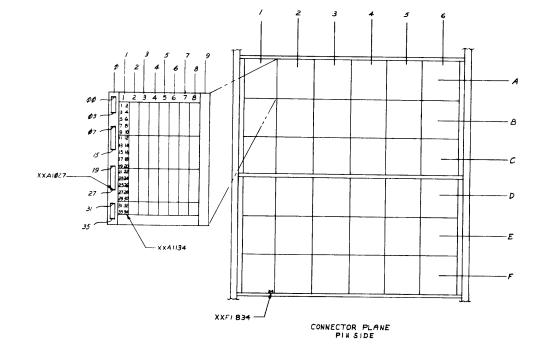

|       | ILLUSTRATIONS                       |      | 1-3         | LBD List                                           | 1-3<br>1-6   |

|       |                                     |      | 1-4         | FTD List                                           | 3-5          |

|       |                                     | Page | 3-1         | Instruction Coding                                 | 3-3<br>3-21  |

|       |                                     |      | 3-2         | Signal Functions                                   |              |

| 2-1   | Block Diagram of Central Processor  |      | 3-3         | Fetch Cycle Operations                             | 3-27<br>3-27 |

|       | and Expanded Address Option         | 2-3  | 3-4         | Indirect Addressing Operations                     | 3-27         |

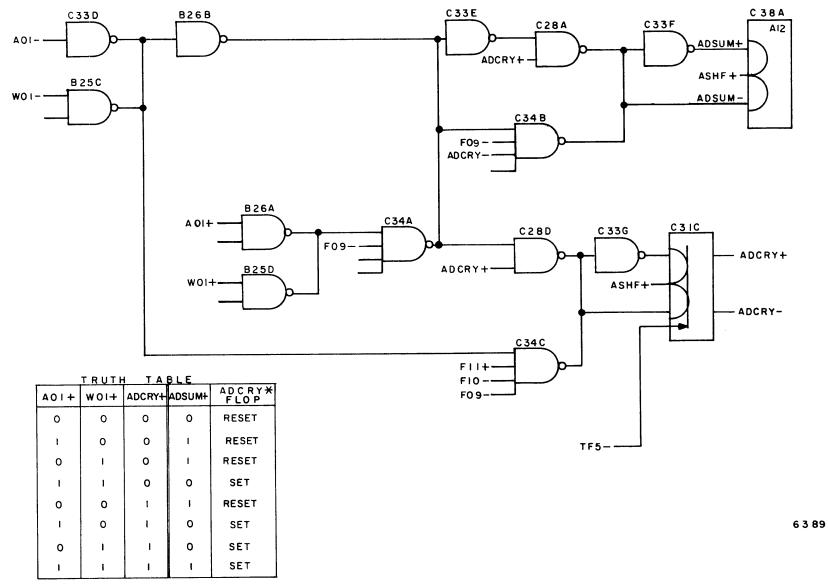

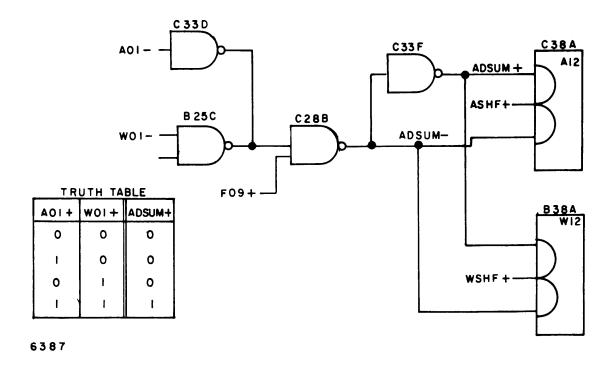

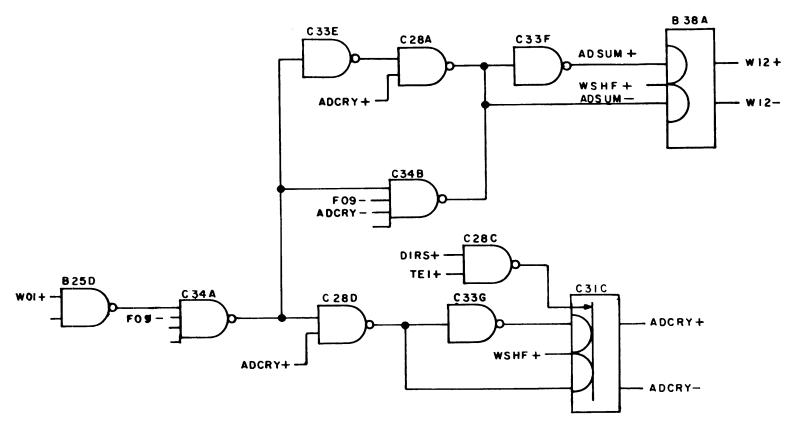

| 3-1   | ADD Simplified Diagram              | 3-10 | 3-5         | LDA Operations                                     | 3-30         |

| 3-2   | ANA Simplified Diagram              | 3-11 | 3-6         | STA Operations                                     | 3-30         |

| 3-3   | IRS Simplified Diagram              | 3-12 | 3-7         | JMP Operations                                     | 3-30         |

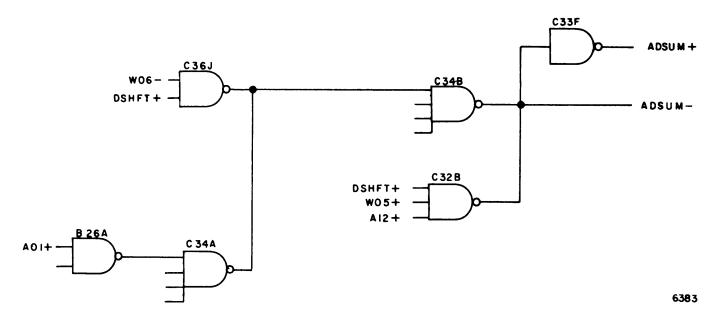

| 3-4   | Simplified Shift Diagram            | 3-13 | 3-8         | ADD and ANA Operations                             | 3-31         |

| 3-5   | OCA and TCA Simplified Diagram      | 3-17 | 3-9         | IRS Operations                                     | 3-31         |

| 3-6   | Timing for Load Mode                | 3-22 | 3-10        | I/O Group Operations                               | 3-32<br>3-33 |

| 3-7   | Remote Control Functions            | 3-28 | 3-11        | Generic Group Operations                           | 3-33<br>3-34 |

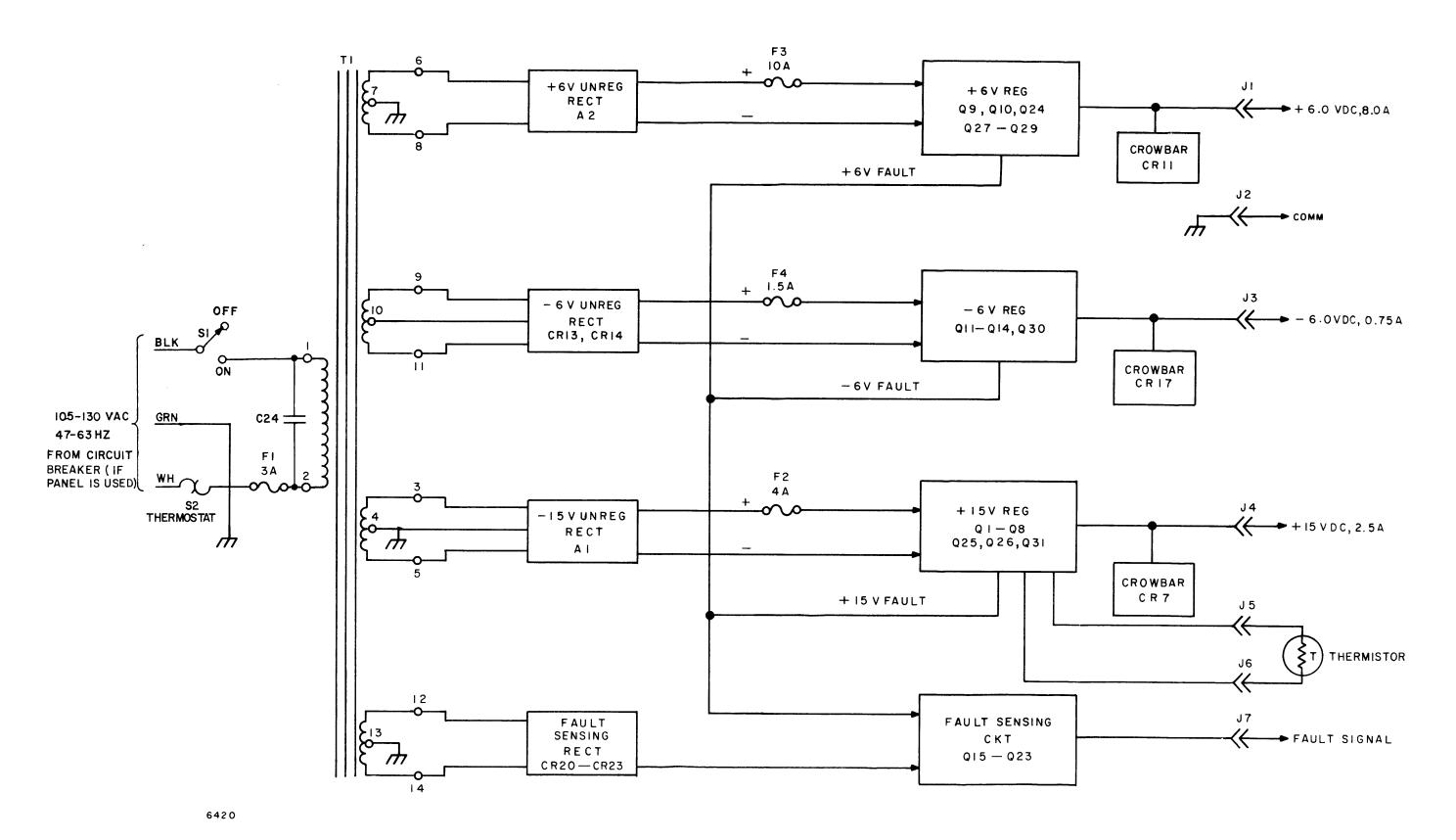

| 3-8   | Primary Power Distribution          | 3-29 | 3-12        | Shift Instruction Operations                       | 3-34<br>3-34 |

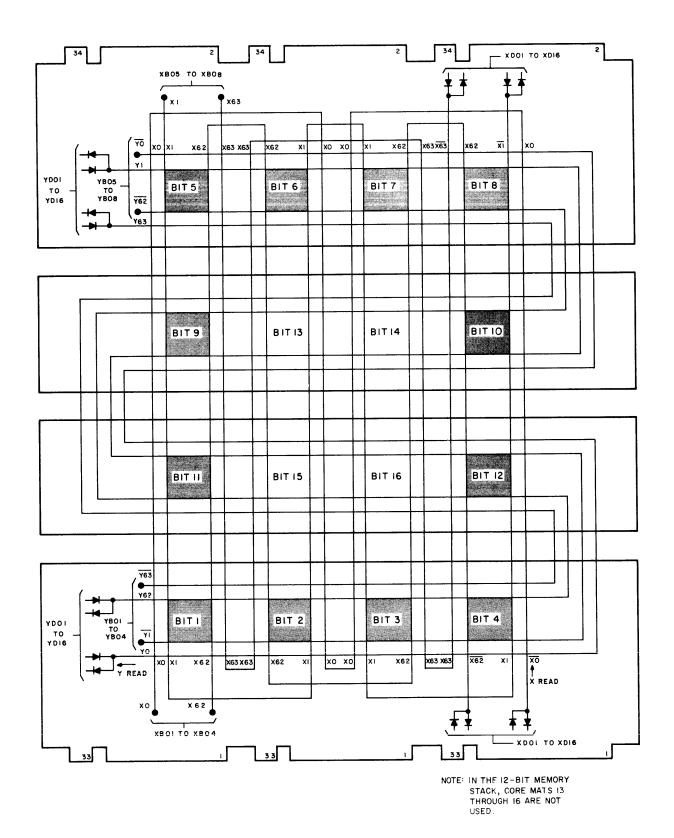

| 5-1   | Stack Coding Diagram                | 5-2  | 3-13        | JST Operations                                     |              |

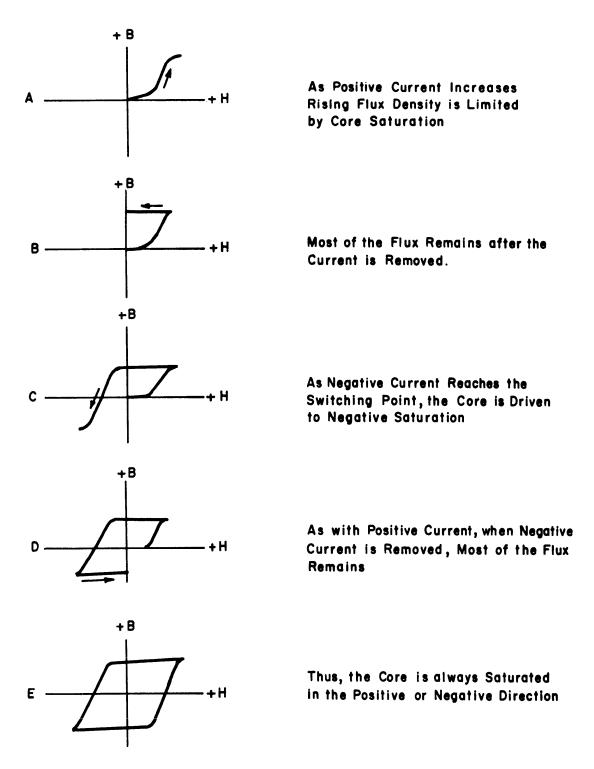

| 5-2   | Ferrite Core Hysteresis Loop        | 5-4  | 3-14        | Load Mode Operations                               | 3-35         |

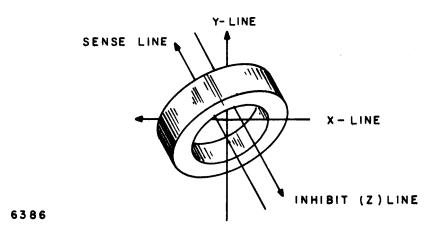

| 5-3   | Core Control Windings               | 5-5  | 3-15        | Interrupt Operations                               | 3-35         |

| 5-4   | Coincident-Current Selection        | 5-5  | 4-1         | Signal Mnemonic Prefixes                           | 4-1          |

| 5-5   | Simplified Block Diagram of Address |      | 4-2         | Function List                                      | 4-2<br>5-1-1 |

|       | Decoding and Selection              | 5-8  | 5-1         | Location of Optional $\mu$ -PACs                   | 5-11         |

| 5-6   | Simplified Schematic of Decoding    |      | 5-2         | Location of Electrical Connections                 | 5-11         |

|       | and Selection Matrix                | 5-9  | 6-1         | Basic H112 μ-PAC Complement and Recommended Spares | 6-1          |

## TABLES (Cont)

|             |                                  | Page |

|-------------|----------------------------------|------|

| 6-2         | Recommended Spare Parts          | 6-2  |

| 6-3         | Tools and Test Equipment         | 6-2  |

| 6-4         | Operational Failures             | 6-4  |

| 6-5         | Partial Data Word Failures       | 6-4  |

| 6 <b>-6</b> | Address, Decoding, and Selection |      |

|             | Failures                         | 6-5  |

| 6-7         | Sense Winding Checklist          | 6-5  |

| 6-8         | Inhibit Winding Checklist        | 6-7  |

| 7-1         | Cross Reference for Figure and   |      |

|             | Page Number                      | 7-6  |

#### SECTION I INTRODUCTION

The Honeywell H112 Digital Controller is a low cost processor which features high speed, efficient use of memory, and adaptability to a wide variety of on-line, real-time control, data collection, and data reduction applications. Honeywell has configured the H112 to meet the varied needs of control and systems engineers. It can be tailored to practically any application by the use of standard, off-the-shelf, plug-in modules. Memory is field expandable from 4K to 8K by use of a standard 4K plug-in module. The plug-in approach also allows a user to share one control panel among several H112 installations, by unplugging the panel once each unit is on-line.

#### **SCOPE**

This manual contains information which will enable maintenance personnel to troubleshoot and repair the H112 central processor. It is written with the assumption that the personnel are familiar with typical computer logic and state-of-the-art integrated circuit maintenance procedures. It makes no attempt to describe basic logic or circuit functions.

#### H112 CONTROLLER CHARACTERISTICS

Type - Parallel, binary, stored program

Addressing — Single-word addressing with single-level indirect addressing

Number System – Two's complement

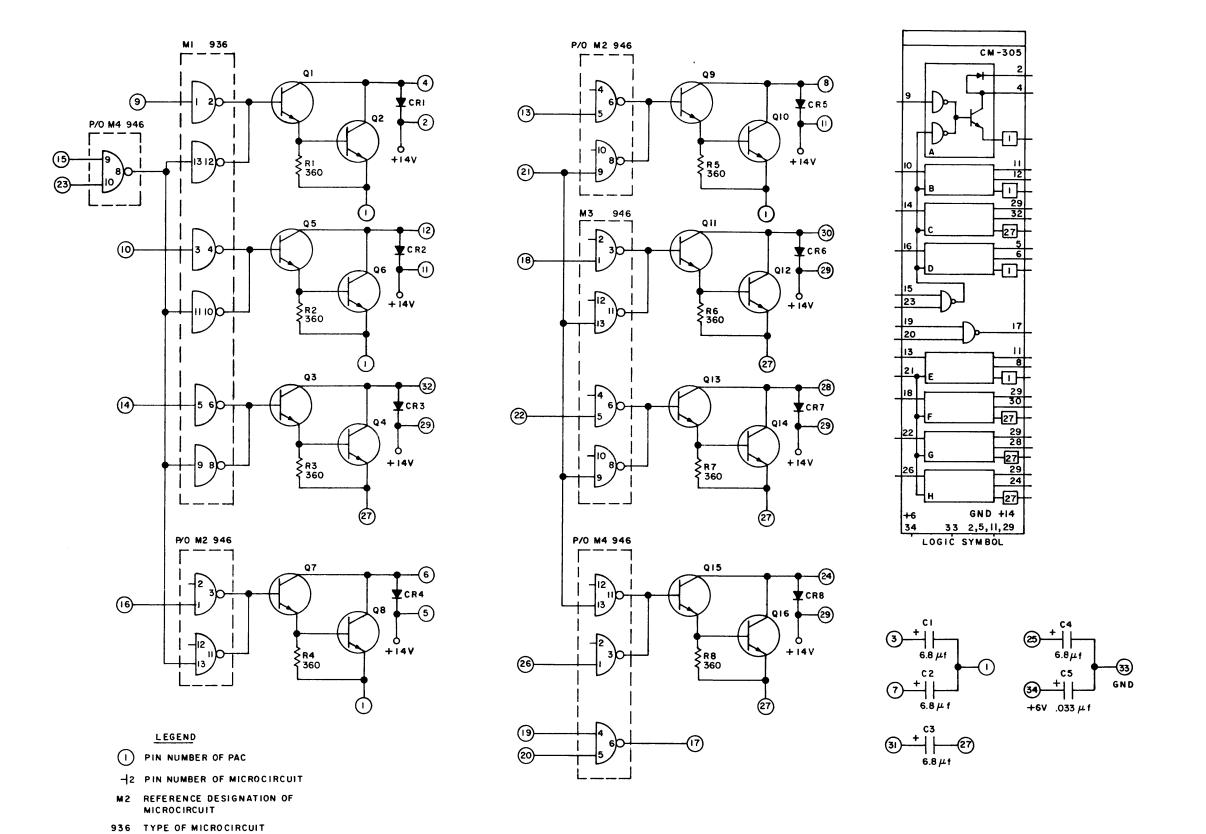

Circuitry – Integrated, DTL

Instruction Complement – Five instruction types, making up 37 standard instructions; microprogrammable skip instructions

Word Length -12 bits

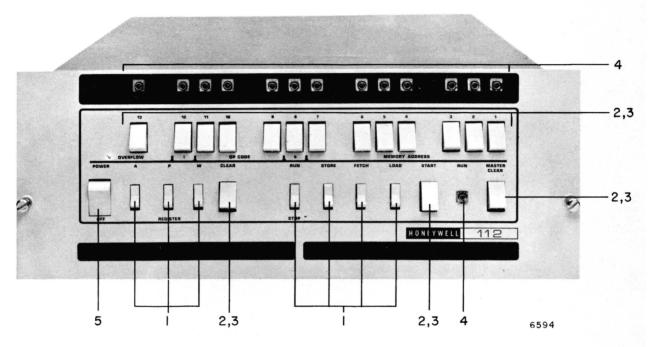

Control Panel — Plug-in optional control panel, with facilities for display of A-, P-, or W-registers, as well as RUN/STOP, STORE, FETCH, START, and MASTER CLEAR functions, plus interlocks to prevent accidental entry

Input/Output Rate — One 12-bit word/3.39 μs, or 295K words/sec (Direct Data Channel Option)

Input/Output Bus — Party line with priority interrupt structure; optional bidirectional direct data channels (2)

Memory — Coincident current, random access, ferrite core, 12-bit word length; one or two 4K modules, field expandable to 8K

Memory cycle time  $-1.69 \mu s$

#### REFERENCES

Other publications which will assist maintenance personnel in servicing, installing, and operating the H112 Central Processor are listed below:

H112 Programmers Reference Manual, Doc. No. 70130072242, M-1164

H112 Interface and Installation Manual, Doc. No. 70130072243, M-1166

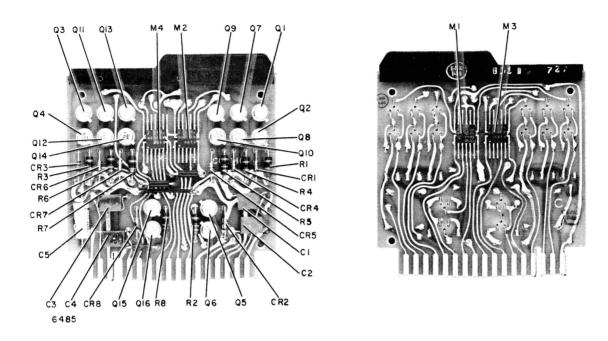

μ-PAC Integrated Circuit Modules, Vol. I, Doc. No. 130071369, M-135

H112 Central Processor Description, Vol. II, Doc. No. 70130072346, M-1421.

#### **MACHINE INSTRUCTIONS**

The various machine instructions used when programming the H112 are included in Table 1-1, following. Five groups of instructions make up the set, for a total of 37 words. All operation codes are in octal format.

#### **ADDRESSING**

#### **Memory Organization**

Each of the seven H112 memory reference instructions (LDA, STA, ADD, ANA, IRS, JMP, JST) contains a 7-bit address field. This allows 128 locations (0-177<sub>8</sub>) to be directly referenced. As a

result, memory is divided into sectors of 128 words each. The sectors begin at addresses  $0, 200_8, 400_8, 600_8$ , etc. A 4K H112 memory contains 32 sectors numbered 0-37<sub>8</sub>; an 8K H112 memory contains 64 sectors numbered 0-77<sub>8</sub>.

#### 4K Memory Addressing

Each memory reference instruction contains a sector bit. This bit determines the sector in which the direct address is located. If the bit is ZERO, the direct address is located in a primary sector (sector 0 or  $40_8$ ); if the bit is ONE, the direct address is located in the same sector as the instruction.

Each memory reference instruction contains an indirect bit. If this bit is ZERO, the instruction operates on the contents of the direct address; i.e., the effective address equals the direct address. If the indirect bit is ONE, the instruction operates on the contents of the location specified by the direct address; i.e., the effective address equals the contents of the location specified by the direct address.

In a 4K machine, or when the bank bit in an 8K machine is ZERO, memory referencing occurs as shown in Table 1-2.

#### **8K Memory Addressing**

In an H112 with 8K memory, the bank bit is included in the calculation of the effective address. If the instruction is located in the lower 4K and

the bank bit is ZERO, memory referencing occurs exactly as shown in Table 1-2. If the instruction is located in the upper 4K and the bank bit is ONE, memory referencing occurs in a manner similar to that shown in Table 1-2 except that  $10000_8$  ( $4096_{10}$ ) is added to each address. For example, if the instruction location is  $10204_8$ , the instruction address is  $134_8$ , and the sector and indirect bits are both ONE (see example 3), then the effective address is all 12 bits at location  $10334_8$ .

If the instruction is in the lower bank and the bank bit is ONE, all direct addresses are in the lower bank, but all indirect addresses are increased by  $10000_8$ . Using example 3 under this condition, the instruction location is  $204_8$ , the instruction address is  $134_8$ , and the effective address is the contents of location  $334_8$  plus  $10000_8$ . If  $334_8$  contains  $1234_8$ , the effective address is  $11234_8$ .

If the instruction is in the upper bank and the bank bit is ZERO, all direct addresses are in the upper bank, but all indirect addresses are in the lower bank. Again referring to example 3, the instruction location is  $10204_8$ , the instruction address is  $134_8$ , and the effective address is the contents of location  $10334_8$ . If  $10334_8$  contains  $1234_8$ , the effective address is  $1234_8$ .

#### **MAINTENANCE DRAWINGS**

Maintenance drawings include Logic Block Diagrams (LBDs) and Flow and Timing Diagrams (FTDs). They are listed in Tables 1-3 and 1-4 respectively, and are given in Volume II of this manual.

TABLE 1-1.

MACHINE INSTRUCTIONS

|                  |                     | MACHINE INSTRUCTIONS                                                          |                     |

|------------------|---------------------|-------------------------------------------------------------------------------|---------------------|

| C                | p Code              |                                                                               |                     |

| Octal            | Mnemonic            | Instruction                                                                   | Execution Time (μs) |

| N                | lemory Referenc     | e Instruction:                                                                |                     |

|                  | INDIRE<br>Address I |                                                                               |                     |

| 1                | LDA                 | Load A (Direct)                                                               | 3.39                |

| 2                | LDA*<br>STA         | Load A (Indirect) Store A (Direct)                                            | 5.09<br>3.39        |

| 3                | STA*<br>JMP         | Store A (Indirect) Jump (Direct)                                              | 5.09<br>3.39        |

|                  | JMP*                | Jump (Indirect)                                                               | 5.09                |

| 4                | ADD<br>ADD*         | Add (Direct) Add (Indirect)                                                   | 7.63<br>9.33        |

| 5                | ANA<br>ANA*         | AND A (Direct) AND A (Indirect)                                               | 7.63<br>9.33        |

| 6                | IRS<br>IRS*         | Increment, Replace, and Skip (Direct) Increment, Replace, and Skip (Indirect) | 9.33<br>11.02       |

| 7                | JST<br>JST*         | Jump and Store P (Direct) Jump and Store P (Indirect)                         | 4.66<br>6.36        |

| Input            | Output Instruct     | ·                                                                             |                     |

|                  |                     | 10 9 8 7 6 5 4 3 2 1<br>CODE ADDRESS (XX IN OP CODE)                          |                     |

| 40XX             | INA                 | Input Transfer to Accumulator                                                 | 4.66                |

| 41XX<br>42XX     | SKS<br>OTA          | Skip if Set<br>Output Transfer from Accumulator                               | 4.66<br>4.66        |

| 43XX<br>4300 ≀   | OCP                 | Output Control Pulse                                                          | 4.66                |

| 4301             | SMK                 | Set Mask                                                                      | 4.66                |

| Shift I          | nstructions:        |                                                                               |                     |

|                  | 0                   | P CODE SHIFT COUNT (N) (BITS 1-3 = X IN OP CODE)                              |                     |

| 010X }<br>011X } | LGR                 | Logical Right Shift                                                           | 3.4+N(0.424)        |

## TABLE 1-1. (CONT) MACHINE INSTRUCTIONS

## Op Code

| Octal            | Mnemonic | Instruction            | Execution<br>Time (µs) |

|------------------|----------|------------------------|------------------------|

| 012X {<br>013X } | ARS      | Arithmetic Right Shift | 3.4+N(0.424)           |

| 014X }<br>015X } | RAR      | Rotate A Right         | 3.4+N(0.424)           |

#### Skip Instructions:

| 0200 | NOP | No Operation                      | 3.39 |

|------|-----|-----------------------------------|------|

| 0201 | SMI | Skip if Accumulator is Minus      | 3.39 |

| 0202 | SZE | Skip if Accumulator is ZERO       | 3.39 |

| 0203 | SMZ | Skip if Minus or ZERO             | 3.39 |

| 0204 | SOV | Skip if Overflow Flip-Flop is Set | 3.39 |

| 0300 | SKP | Skip Unconditionally              | 3.39 |

| 0301 | SPL | Skip if Accumulator is Plus       | 3.39 |

| 0302 | SNZ | Skip if Accumulator is Non-ZERO   | 3.39 |

| 0303 | SPN | Skip if Positive and Non-ZERO     | 3.39 |

| 0304 | SNO | Skip on no Overflow               | 3,39 |

#### **Generic Instructions:**

| 0000 | HLT | Halt                                  | 2.54      |

|------|-----|---------------------------------------|-----------|

| 0003 | OCA | One's Complement Accumulator          | 7.63      |

| 0005 | TCA | Two's Complement Accumulator          | 7.63      |

| 0021 | STL | Stall On-Line                         | 3,39+wait |

| 0022 | TBA | Transfer Bank Register to Accumulator | 3.39      |

| 0024 | ITS | Interrupt Save                        | 3.39      |

| 0030 | TOA | Transfer Overflow to Accumulator      | 3.39      |

| 0041 | TAB | Transfer Accumulator to Bank Register | 2.54      |

| 0042 | itr | Interrupt Return                      | 2.54      |

| 0044 | ENB | Enable Interrupts                     | 2.54      |

| 0050 | INH | Inhibit Interrupts                    | 2.54      |

| 0060 | CRA | Clear Accumulator                     | 2.54      |

TABLE 1-2.

MEMORY REFERENCING IN 4K MODE

| Example<br>No. | Current<br>Program<br>Location <sub>8</sub> | Address Assembled in Instruction <sub>8</sub> (7-bits) | [plus] | Sector<br>Bit of: | [and] | Indirect<br>Bit of: | [yields] | Effective<br>Address& of:           |

|----------------|---------------------------------------------|--------------------------------------------------------|--------|-------------------|-------|---------------------|----------|-------------------------------------|

| 1              | 204                                         | 134                                                    |        | 1                 |       | 0                   |          | 334                                 |

| 2              | 204                                         | 134                                                    |        | 0                 |       | 0                   |          | 134                                 |

| 3              | 204                                         | 134                                                    |        | 1                 |       | 1                   |          | (all 12 bits<br>at location<br>334) |

| 4              | 204                                         | 134                                                    |        | 0                 |       | 1                   |          | (all 12 bits<br>at location<br>134) |

TABLE 1-3. LBD LIST

| LBD<br>No. | Title                                              | Dwg. No.   |

|------------|----------------------------------------------------|------------|

| 12.00      | Register Control                                   | 70 026 909 |

| 12.01      | Register Bus Control (RB)                          | 70 026 910 |

| 12.02      | Timer (T)                                          | 70 026 911 |

| 12.03      | Adder and Interrupt (AD,INT)                       | 70 026 912 |

| 12.04      | Shift Counter and Memory Load (C,L)                | 70 026 913 |

| 12.05      | Decoder (D)                                        | 70 026 914 |

| 12.06      | Program Counter (P)                                | 70 026 915 |

| 12.07      | Memory Address Register and Op Code Register (Y,F) | 70 026 916 |

| 12.08      | Working Register (W)                               | 70 026 917 |

| 12.09      | Accumulator (A)                                    | 70 026 918 |

| 12.10      | Cable Data Bus and Register Transfer Bus (K,RB)    | 70 026 919 |

| 12.11      | Cable Control Bus (K) and System Normalizer (N)    | 70 026 920 |

| 12.12      | Expanded Address Option                            | 70 026 921 |

| 12.13      | CSM-160 Timing and Control                         | 70 026 922 |

| 12.14      | CSM-160 Timing and Control                         | 70 026 923 |

| 12.15      | CSM-160 Sense Amplifiers                           | 70 026 924 |

| 12.16      | CSM-160 Inhibit Drivers                            | 70 026 925 |

| 12.17      | CSM-160 X Selection Sinks and Switches             | 70 026 926 |

| 12.18      | CSM-160 Y Selection Sinks and Switches             | 70 026 927 |

| 12.19      | CSM-160 X and Y Selection Diode Matrix             | 70 026 928 |

| 12.20      | Cable Chart                                        | 70 026 929 |

| 12.21      | PAC Complement/Allocation                          | 70 024 852 |

| 12.22      | Control Panel Circuit Board A                      | 70 026 930 |

| 12.23      | Control Panel Circuit Board B                      | 70 026 931 |

TABLE 1-4. FTD LIST

| FTD<br>No.     | Title                                                          | Dwg. No.           |

|----------------|----------------------------------------------------------------|--------------------|

| 12.75          | Fetch, Flow and Timing                                         | 70027847           |

| 12.76          | Indirect Fetch, Panel Fetch/Store,                             |                    |

|                | Flow and Timing                                                | 70027848           |

| 12.77          | LDA, STA, TOA, Flow and Timing                                 | 70027849           |

| 12.78          | IRS, Flow and Timing                                           | 70027850           |

| 12.79          | ADD and ANA, Flow and Timing                                   | 70027851           |

| 12.80          | JMP, JST, Flow and Timing                                      | 70027852           |

| 12.81          | OCA, TCA, RAR, LGR, ARS, Flow and Timing                       | 70027853           |

| 12.82          | INH, TAB, ITR, HLT, ENB, CRA, TBA, ITS,                        |                    |

|                | Flow and Timing                                                | 70027854           |

| 12.83          | NOP, SMZ, SZE, SNZ, SMI, SPL, SOV, SNO, SKP,                   |                    |

| 12.00          | SPN, STL, Flow and Timing                                      | 70027855           |

| 12.84          | INA, OTA, SKS, OCP, SMK, Flow and Timing                       | 70027856           |

|                |                                                                |                    |

| 12.84<br>12.85 | INA, OTA, SKS, OCP, SMK, Flow and Timing Load, Flow and Timing | 7002785<br>7002785 |

#### SECTION II BLOCK DIAGRAM DISCUSSION

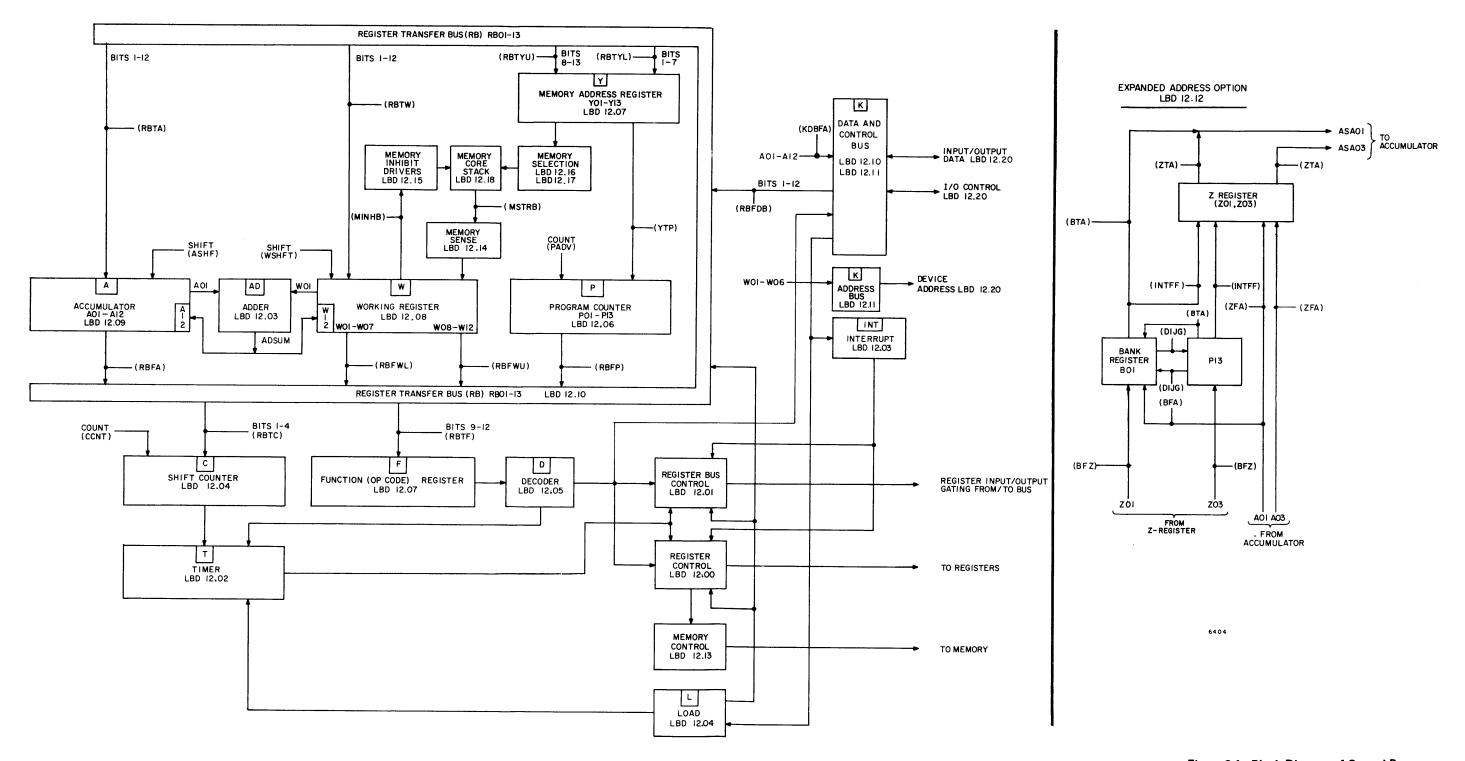

The H112 Central Processor (CPU) contains a group of registers connected to a common register transfer bus and the control logic necessary to perform the required functions. The registers provide the temporary storage required to move data to and from the main memory storage, perform arithmetic operations on this data, control the program sequence, and control the execution of instructions,

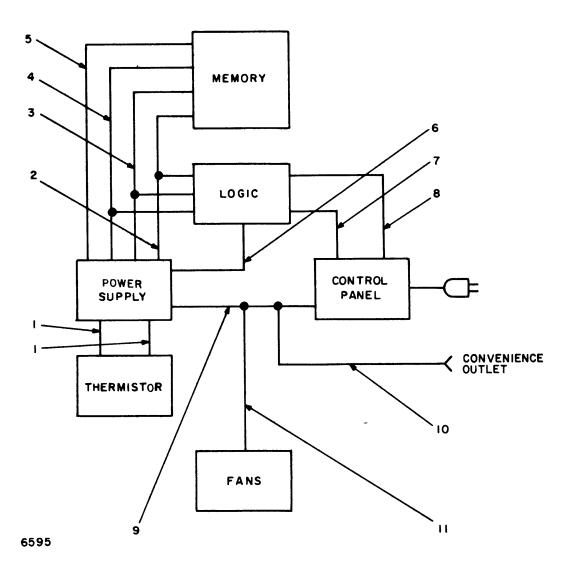

Figure 2-1 contains a block diagram of the H112. This section of the manual will describe the functions of the major blocks and then provide a functional description of machine operation at the block diagram level.

#### TIMER (T)

The timer contains the master clock and time state generator which control CPU operations. The master clock is a free-running crystal-controlled oscillator that generates and distributes the clock pulses. The time state generator is essentially an 11-bit shift register that normally has only one flip-flop on at a time. Flip-flops 1 through 5 define the TF1 through TF5 times of the fetch cycle, and the remaining six flip-flops define the TE1 through TE6 times of the execute cycle. The time states and clock pulses are used with the various decoder outputs to generate the required control signals.

#### REGISTER TRANSFER BUS (RB)

The register transfer bus consists of 13 lines interconnecting the registers of the CPU. Capabilities for input transfers from the RB and output transfer to the RB are provided for both the accumulator and the working register. The shift counter, function register, and memory address register are capable of receiving data from the RB, while the program counter is capable of transferring data to the RB. The register bus control generates the transfer signals at the appropriate times to gate the data to the RB or into the appropriate register. A typical example of a data transfer is as follows: the Register Bus From Program counter (RBFP) pulse gates the address stored in the program counter to the RB during TF1 time of a fetch cycle. Then the Register Bus To memorY address register Lower (RBTYL) gates bits 1 through 7 of the RB into bits 1 through 7 of the Y-register. The Register Bus To memorY address register Upper (RBTYU) gates bits 8 through 12 of the RB into bits 8 through 12 of the Y-register during TF1 time of a fetch cycle. Thus, the contents of the program counter have been transferred to the memory address register.

#### MEMORY (M)

The memory in the H112 is a 4096 x 12-bit, random-access, ferrite-core, coincident-current memory. Patterns are written into memory locations by using memory selection and inhibit drivers. Patterns are read from memory locations by using memory selection and sense amplifiers.

The address of the selected memory location is routed to the memory selection circuits from the Y-register. Data read from memory is loaded into the working register, and the data stored in the working register is written back into memory.

#### MEMORY ADDRESS REGISTER (Y)

The address register is a 12-bit (13 bits with the 8K memory option) parallel register that stores the address of the memory location to be accessed. The Y-register is loaded by a transfer from the register bus. Output lines from the Y-register are routed to the memory selection circuits and the program counter.

#### PROGRAM COUNTER (P)

The 12-bit (13 bits with the 8K memory option) program counter stores the address of the next

instruction to be executed. At the start of a fetch cycle, the address stored in the program counter is gated onto the register bus and transferred into the address register. Then, the program counter is incremented, conditioning it for the next instruction. The contents of the program counter are also changed by a transfer from the register bus through the Y-register. This occurs during JMP and JST instructions.

#### **WORKING REGISTER (W)**

The working register is a 12-bit parallel/serial shift register. Data words read from memory are loaded into the W-register, and data words to be written into memory are routed to memory via the W-register. The data on the register bus can be gated into the W-register, and data in the W-register can be gated onto the register bus. The W-register is also used to perform arithmetic operations on the stored data by shifting the data through the adder.

#### ACCUMULATOR (A)

The accumulator is a 12-bit parallel/serial shift register used as the primary arithmetic register of the CPU. Data stored in the accumulator is shifted into the adder with or without the W-register during arithmetic operations. The results of the arithmetic operations are returned to the accumulator. Gating logic associated with the accumulator allows data to be gated onto and off the register bus. The accumulator is also used to receive data from and route data to the I/O data bus via the register bus.

#### ADDER (AD)

The adder is a 1-bit element used in performing the arithmetic operation of the CPU. It performs the prescribed function on the bits shifted out of the A-register and/or the W-register and gates the results back into the A-register and/or the W-register. The following functions are performed by the adder: complementing numbers in the A-register, rotating numbers in the A-register, adding numbers in the A- and W-registers together, ANDing numbers in the A- and W-registers together, and incrementing numbers in the W-register.

In several of the preceding operations, a carry from the add of one bit position must be propagated and included in the add of the next bit position. This function is performed by the carry flip-flop (ADCRY). The carry flip-flop is set before an increment instruction (IRS or TCA), and reset before a rotate (RAR), complement (OCA), or logical add (ANA) instruction. This allows the overflow of an add operation to be tested (by an SOV instruction) or saved (by a TOA instruction) for multiple precision arithmetic.

## SHIFT COUNTER (C)

The shift counter is a 4-bit counter used to count the number of shifts during a shift command and to control certain other operations (ADD, ANA, IRS, OCA, TCA, and Load Mode). During shifts the complement of the required number of right shifts is loaded into the shift counter via the register bus, and the counter is counted down. When the counter reaches all ZEROs, the instruction is terminated. When the counter is used for control of other functions, the appropriate count is detected.

#### **FUNCTION REGISTER (F)**

The function (Op Code) register is a 4-bit storage register which receives the Op Code portion of the instruction. During TF4 time of the fetch cycle, bits 9 through 12 of the instruction are gated onto the register bus and transferred into the F-register. The outputs from the F-register are routed to the decoder.

#### DECODER (D)

The decoder generates the various Op Codes depending upon the data stored in the F-register and/or the W-register. The Op Codes condition the various control gates which select the CPU operations.

#### **BANK REGISTER (B)**

The bank register is a 1-bit register used as the most significant bit of an indirect address word. It is also loaded with P13 during indirect JMP and indirect JST instructions. This register is supplied in the 8K version only.

#### Z-REGISTER (Z)

The Z-register is a 2-bit register used for intermediate storage during transfers between P13 and B01 and the accumulator. During an interrupt, Z is loaded with P13 and B01. During an interrupt return sequence, P13 and B01 are loaded from Z. This register is supplied in the 8K version only.

Figure 2-1. Block Diagram of Central Processor and Expanded Address Option

#### MACHINE OPERATION

From the time the CPU is started until it is stopped (by the STOP button or a HLT instruction), fetch and execute cycles are repeated one after another. During the fetch cycle, the instruction is read, the program counter is advanced by one, and the CPU is made ready to execute the instruction. At the end of the fetch cycle, the execute cycle is entered and the desired functions are performed. In this discussion, a typical machine operation is described, and operations during input/output instructions, interrupt conditions, and direct data channel operation are explained.

#### **Instruction Fetch**

A fetch cycle is performed to read the instruction out of memory. Each fetch cycle is divided into five time periods (TF1 through TF5) of 424 ns each. The fetch cycle is entered when the START switch on the panel is depressed or when the preceding instruction is completed. In TF1 time. the contents of the program counter (which identifies the address of the next instruction) are gated onto the register bus, and the data on the register bus are gated into the address (Y-) register. During TF2, the program counter is advanced by one and the memory cycle initiated. During TF3 time, the working register (W) is reset and the contents of the selected memory location are read and loaded into the W-register. Then the data in the W-register are used during the write portion of the memory cycle to restore the instruction in memory.

The contents of the W-register are gated onto the register bus during TF4 time. Bits 9 through 12 are gated into the function register (F), and the contents of the F-register are decoded to determine the function to be performed during the execute cycle.

During TF5, bits 1 through 7 of the W-register are gated into the Y-register via the register bus to identify the location addressed within the selected sector. Also in TF5 time, bit 8 of the W-register is sampled by the control logic to determine the selected sector. When bit 8 is a ONE, the selected sector is the same as the sector which was addressed during TF1. If bit 8 is a ZERO, the selected sector is a primary sector. Therefore, gating logic is enabled to gate all ZEROs into bits 8 through 12 of the Y-register.

The indirect address bit contained in bit 12 of the W-register is also sampled during TF5. The execute cycle is entered if bit 12 is a ZERO. The indirect addressing cycle is entered if bit 12 is a ONE and the instruction is a memory reference instruction.

#### **Indirect Addressing**

The indirect addressing cycle is enabled when a ONE is detected in bit 12 of the W-register during TF5 of the normal fetch cycle of a memory reference instruction. During the indirect cycle, a modified fetch cycle is performed. The fetch counter is started at TF2 time to prevent the reading of the P-counter into the Y-register. During TF2, the P advance pulse (PADV) is inhibited to prevent the incrementing of the P-counter. The address contained in the Y-register at the end of the normal fetch cycle is regarded as the address of a pointer. When the memory cycle is initiated during TF2 time, the data stored in this address are read into the W-register. The contents of bits 9 through 12 of the W-register are prevented from entering the F-register during TF4 time. During TF5 time, the contents of the W-register are gated onto the register bus and transferred into the Y-register. The new contents of the Y-register are used as the effective address during the following execute cycle. Single level indirect addressing only is provided. The indirect bit, therefore, is not examined again and an execute cycle will always follow the indirect cycle.

#### **Instruction Execution**

The operation prescribed by the contents of the F-register is performed during the execute cycle. The output signals from the decoder, along with the contents of the F-register and the timer outputs, generate the control signals required to perform the operations. During the execution of a non-memory reference instruction, the contents of the W-register along with the timer outputs are used to generate the required control signals.

Timing for the execute portion of an instruction is provided by a six-stage counter. The actual length of the execute cycle varies with the type of instruction under execution. An instruction requiring six execute timer pulses takes a total of  $4.66 \mu s$ . Instructions which do not require the full six execute timer generate control signals that terminate the execute cycle in either TE1 or TE3 time and start the next fetch cycle. Some instructions require more than the  $4.66 \mu s$  to perform

arithmetic operations. These instructions generate control signals which hold the execute counter in TE4 time and restart it at the proper time.

The following general operations are executed by the instructions: referencing memory, shifting through the adder for arithmetic and shift operations, changing the contents of the program counter to alter normal sequencing, transferring data between the accumulator and the I/O bus, performing control actions on registers, or operating condition flip-flops. Some instructions perform combinations of these basic operations to complete their required function.

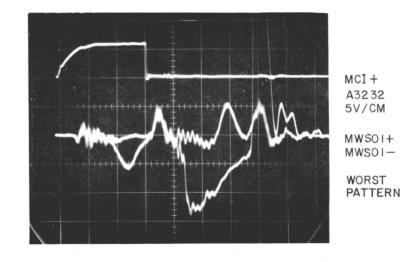

Memory Reference (ADD, ANA, STA, LDA, IRS, JST).—Instructions which reference memory cause a memory read/restore or clear/write cycle to occur by enabling the Memory Cycle Initiate control function (MCI), and by setting or resetting the read control flip-flop (MREAD). The memory location accessed is determined by the Y-register which was loaded during the fetch cycle. The data is read into or written from the W-register. Therefore, the W-register must be loaded with the data to be written or cleared before receiving the read data.

The ADD, ANA, and LDA instructions cause a read cycle of memory. The STA and JST instructions cause a write cycle. The IRS instruction causes a read and then a write cycle to occur at the same memory address.

The JMP, while not a memory reference instruction, is usually included in this category because of the need to form a new effective address during the execution.

Arithmetic and Shift (ADD, ANA, IRS, ARS, LGR, RAR, OCA, TCA).—The arithmetic and shift instructions modify the accumulator (A) or a memory location by the prescribed action. In order to accomplish this function, the contents of the A-register or the W-register or the contents of both registers are shifted through the 1-bit adder. Bit 1 of each register feeds the adder, and the adder output feeds bit 12 of the A-register. (It also feeds the W-register during an IRS.)

Sequence Change (JMP, JST, SPL, SMI, SZE, SNZ, SOV, SNO, SPN, SMZ, SKP, IRS).—A sequence-changing instruction is executed to change the normal sequencing from one instruction to the

next. This type of an instruction causes the program counter to be changed during the execute cycle.

The skip instructions (SPL, SMI, SZE, SNZ, SOV, SNO, SPN, SMZ, SKP, IRS) cause the program counter to be advanced by one if the indicated test condition is true (i.e., SPL skips the next instruction if the accumulator is plus). Otherwise, the program counter is not advanced.

During a jump instruction (JMP), the Y-register is loaded with the effective address to be accessed during the nex t fetch cycle. The program counter is then reset and the contents of the Y-register are gated into the program counter. The program continues from the new location.

During a jump and store instruction (JST), the Y-register is loaded with the effective address to be accessed during the next fetch cycle. When the execute cycle is started, the W-register is reset and the contents of the program counter are gated onto the register bus. The data on the register bus, which identify a memory location that is one greater than the location of the JST instruction, are gated into the W-register. The memory cycle is initiated and the contents of the W-register are stored in the memory location specified by the contents of the Y-register. The program counter is reset and the contents of the Y-register are gated into the program counter. The program counter is incremented by one, and the program continues from this new location.

I/O Control (OTA, INA, OCP, SKS, SMK).—The instructions in this group are used by the controller to communicate with peripheral devices. The address of the selected device, contained in bits 1 through 6 of the W-register, is routed to the peripheral devices via the address lines, and the I/O control signals are routed to the peripheral devices via the I/O control lines. Some instructions require the selected device to respond to the address and I/O control signals by a test signal from the device indicating that the device is ready. After the CPU detects the test signal (test line in the true condition) a strobe signal is routed to the device.

During an OTA instruction, the contents of the accumulator are gated onto the data bus and routed to the device. If the test line is true, the program counter is incremented by one to skip the next instruction, and a strobe signal is routed to

the device. The device uses the strobe signal to complete the transfer. If the test line is false during an OTA instruction, the program counter is not advanced and the next instruction is executed.

When an INA instruction is executed, the accumulator is cleared and the condition of the test line is checked. If the test line is true, the data on the data bus are gated into the accumulator via the register bus, the program counter is incremented by one, and the next instruction is skipped. The strobe signal then goes true, indicating that the data transfer is complete. If the test line is false during an INA, the A-register is cleared, the program counter is not advanced, and the next instruction is executed.

The SKS instruction is executed to check the condition of the test line from a specific device. If the test line is true, a pulse is issued on the strobe line and the program counter is incremented by one, causing the next instruction to be skipped.

During an OCP instruction, the address, control, and strobe signals are used to perform a function in the selected device irrespective of the condition of the test line. The program counter is not advanced by this instruction.

The SMK instruction is similar to an OCP instruction, except that the contents of the accumulator are used to set the interrupt mask flip-flops in the peripheral devices. Generally, one accumulator bit is assigned to each device. A ONE in an accumulator bit permits an interrupt, while a ZERO inhibits further interrupts and temporarily removes an interrupt request from a particular device. This instruction is not contingent upon the state of the test line and hence will never skip.

Run State Control (NOP, HLT, STL).—The NOP instruction performs no action. It is used to consume approximately 3.4  $\mu$ s of time. Under some conditions, it is used as an instruction that is replaced by some other instruction.

The HLT instruction stops the CPU by resetting the run flip-flop in the timer. The START button must be depressed to restart the unit.

The STL instruction causes the CPU to stop performing instructions temporarily, until released from this condition by an external signal. The timer is held in state TE2 until the stall line (KSTAL) goes active (0V). The KSTAL line has no

effect on processor operation until the STL instruction is executed.

Interrupt Control (ENB, INH).—The enable (ENB) and inhibit (INH) instructions set and reset, respectively, the interrupt control flip-flop. When an interrupt occurs, the interrupt control flip-flop is automatically reset. Therefore, an ENB instruction must be executed to re-enable the interrupt logic.

Accumulator Control (CRA, TOA).—The CRA instruction causes the accumulator to be cleared. When a TOA instruction is executed, the accumulator is cleared, the contents of the overflow flip-flop are transferred to bit 1 of the accumulator, and the overflow flip-flop is cleared (if in the set condition).

Expanded Address Option Instructions (TBA, TAB, ITS, ITR).—These instructions are used with the 8K memory option only and are treated as NOP or CRA instructions by the 4K version. During a TBA instruction, the accumulator is cleared, the contents of the bank register (B01) are transferred to bit 1 of the accumulator, and the contents of P13 are transferred to B01. The TAB instruction loads the contents of accumulator bit 1 into the bank register (B01).

When an interrupt occurs, the contents of the bank register are gated into Z01 and the contents of P13 into Z03. The ITS instruction will clear and transfer the contents of the Z-register into the accumulator. The contents of the accumulator can be stored to retain these conditions.

After the interrupt has been serviced, the contents of the bank register and P13 are restored. The previously saved data are loaded into the accumulator. The ITR instruction will clear and transfer the contents of the accumulator into the Z-register and precondition the interrupt return logic. During the next indirect JMP or indirect JST instruction, the contents of the Z-register will be transferred into P13 and the bank register.

#### Interrupts

An interrupt occurs when one of the devices on the I/O bus grounds the (KINTL) line. If interrupts have been enabled in the controller, the present instruction is completed and the instruction stored in dedicated location 00002 is then executed. Additional interrupts will be inhibited by this

action. This instruction must be a JST or indirect JST (JST\*). The address of the next sequential instruction in the original program being run is stored in the memory cell at the effective address of the JST. The previous contents of the memory cell at this address are lost. In the 8K version the normal exchange of P13 and the bank register during an indirect JST is inhibited. Instead the contents of the bank register and P13 are transferred to the Z-register, and the bank register and P13 are cleared.

#### **Direct Data Channel**

When the DDC option makes a transfer request,

instruction execution is temporarily suspended after the completion of the instruction in process. The Y-register is loaded with an address supplied by the direct data channel, and a memory cycle is initiated. An input or an output data transfer between memory and the channel takes place at this time, depending on the nature of the request. If a second request is made prior to the end of the present DDC cycle, another transfer occurs. If no request is waiting at the completion of the DDC cycle, instruction execution is resumed from the point of suspension with no alteration of programmable registers.

#### SECTION III DETAILED THEORY OF OPERATION

This section describes the logic, timing, and functional operations of the H112. Each major functional block is described by use of the logic block diagrams (LBDs). The logic used to perform the fetch cycle is explained by use of both the LBDs and the flow and timing diagrams (FTDs). Instructions are grouped according to the operations performed during the execute cycle, and detailed descriptions of the different execute cycles are provided. In these descriptions, the term "passive" is used when a signal goes to +6V, and the term "active" is used when a signal goes to 0V. An assertion signal (e.g., TICYL+) is true if it is at +6V and false if it is at 0V, while a negation signal (e.g., TF5-) is true if it is at 0V and false if it is at +6V. Mnemonics are listed in Table 4-2.

#### REGISTER CONSTRUCTION

Five registers are used in the H112 processor, and the construction of each is discussed briefly in this section.

#### Memory Address Register (LBD 12.07)

The memory address (Y-) register in the basic H112 is a 12-bit parallel storage register with parallel transfer input gating. An additional bit is provided as Y13 (LBD 12.12) if the expanded address option is used. Data are transferred off the register bus and into the register in two parts. The information in bits 1 through 7 is transferred into the register by RBTYL+, and bits 8 through 13 are transferred into the register by RBTYU+, The dc set input of bit 2 (YSY02-) is used to select location 00002 during an interrupt routine.

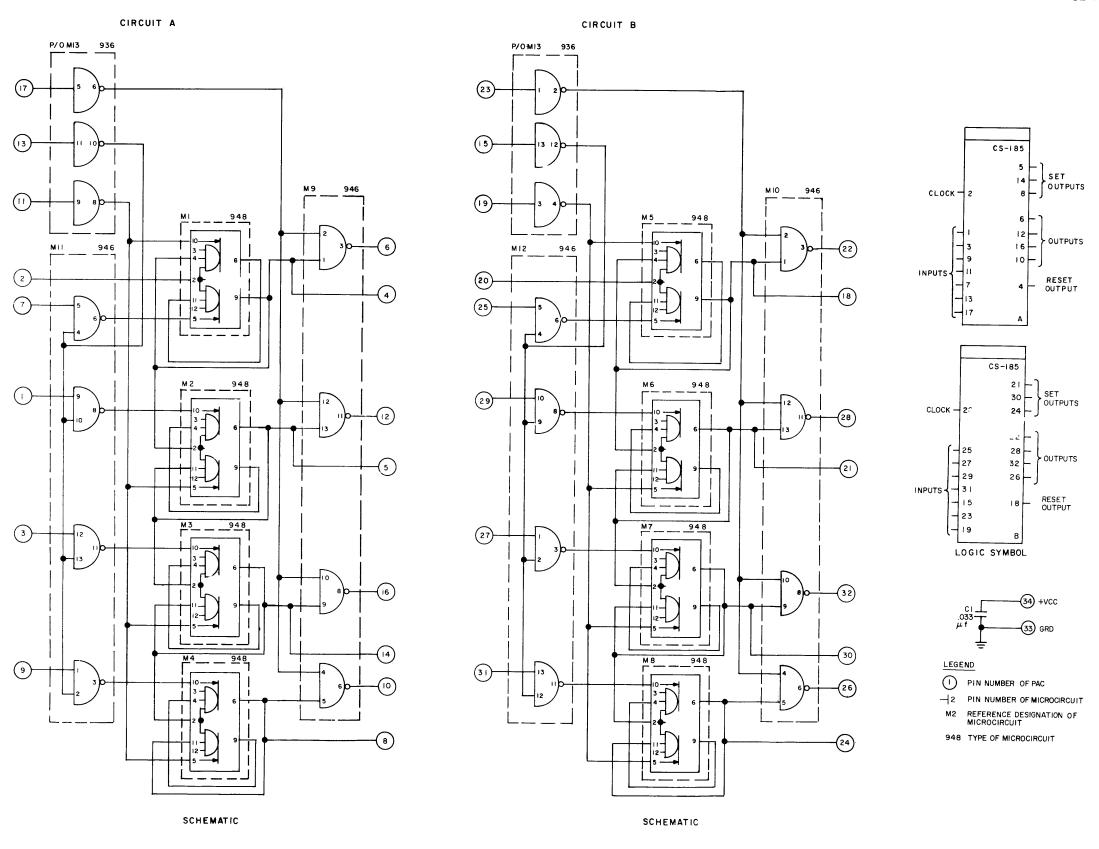

#### Program Counter (LBD 12.06)

The program counter (P) is a 12-bit counter consisting of three CS-185 PACs. An additional bit is provided as P13 (LBD 12.12) if the expanded address option is used. The count stored in the

counter is incremented by one each time PADV-goes true (0V), moving the counter to the next sequential address. The dc set inputs are used to load an address from the Y-register and change the normal counting sequence. The contents of P are available at the set outputs or can be gated onto the register bus via output gating logic enabled by RBFP-. P is cleared via the dc reset inputs of the flip-flops (PR-).

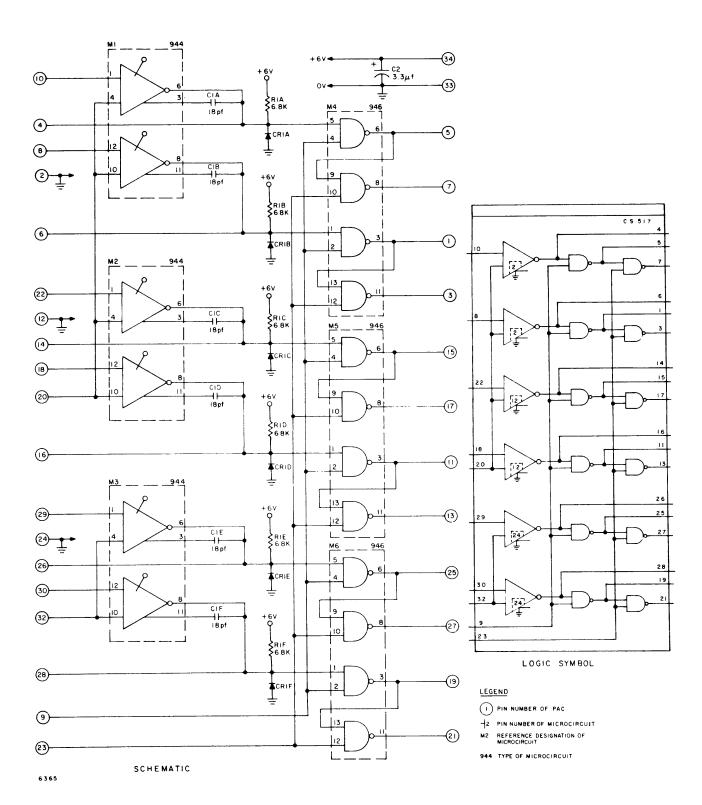

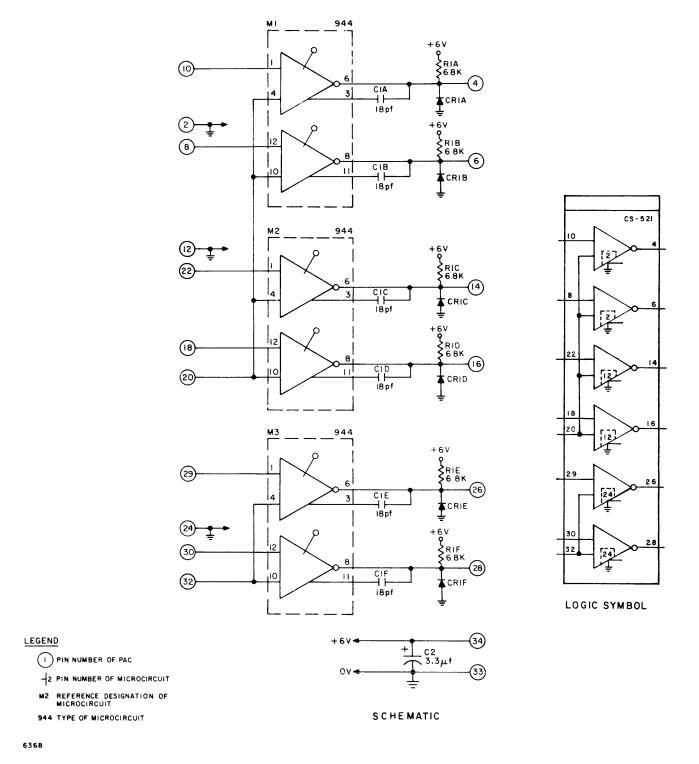

#### Accumulator (LBD 12.09)

The accumulator (A-register) is a 12-bit parallel/serial shift register consisting of two BR-320 Buffer Register PACs. The dc set inputs of the flip-flops are used for a parallel transfer of data from the register bus via input gating logic. Output gating logic is used to transfer the data at the set outputs of the flip-flops onto the register in a parallel fashion. Serial transfers are shift transfers, with new data from the adder (ADSUM) entering bit 12. Resetting the accumulator is accomplished via the dc reset inputs of the flip-flops (AR-).

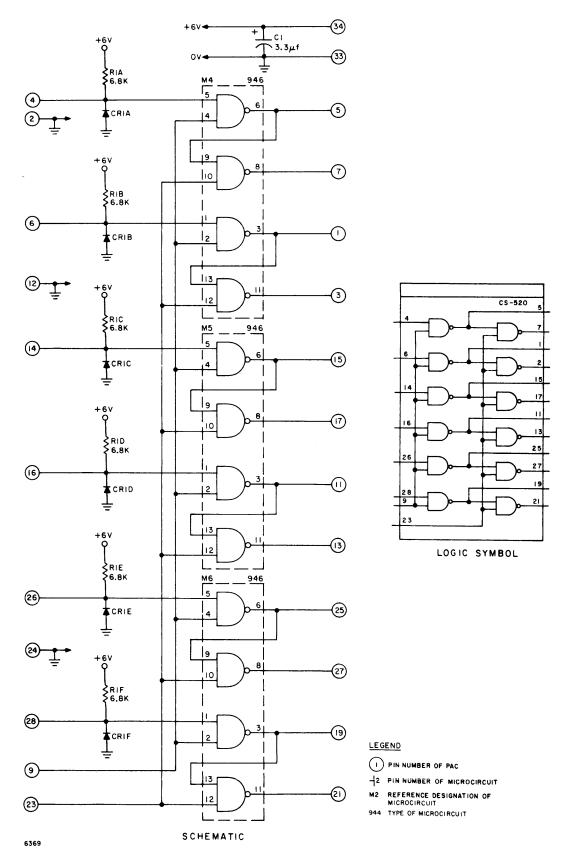

#### Working Register (LBD 12.08)

The working (W-) register is a 12-bit parallel/serial shift register similar to the accumulator. The two BR-335 Buffer Register PACs and the control logic are connected to allow parallel input and output transfers via the register bus. The dc set inputs are also used to accept the data from the sense amplifiers of the memory during a memory read cycle. Output gating from the W-register is accomplished in two parts. Bits 8 through 12 are gated by RBFWU+, and bits 1 through 7 are gated by RBFWU+.

### Function (Op Code) Register (LBD 12.07)

The function register (F) is a 4-bit parallel storage register which stores bits 9 through 12 of the instruction. Data on bits 9 through 12 of the register bus are transferred into the F-register at the end of TF4 time and remain in the register until the fetch cycle of the next instruction. The contents of the F-register are directly taken from the outputs of the flip-flops and are used in the decoder. When data is loaded in the load mode, XLDSW- is applied to the dc set input of F10, generating an STA Op Code.

#### **TIMER (LBD 12.02)**

The time states required to control the CPU operations are generated in the timer. An 11-stage shift register and the necessary control logic generate 5 fetch times (TF1 through TF5) and 6 execute times (TE1 through TE6). Normally, only one time state is on at a time. The functions performed by the fetch time states are the same for all instructions, while the functions performed by the execute time states depend on which instruction was fetched.

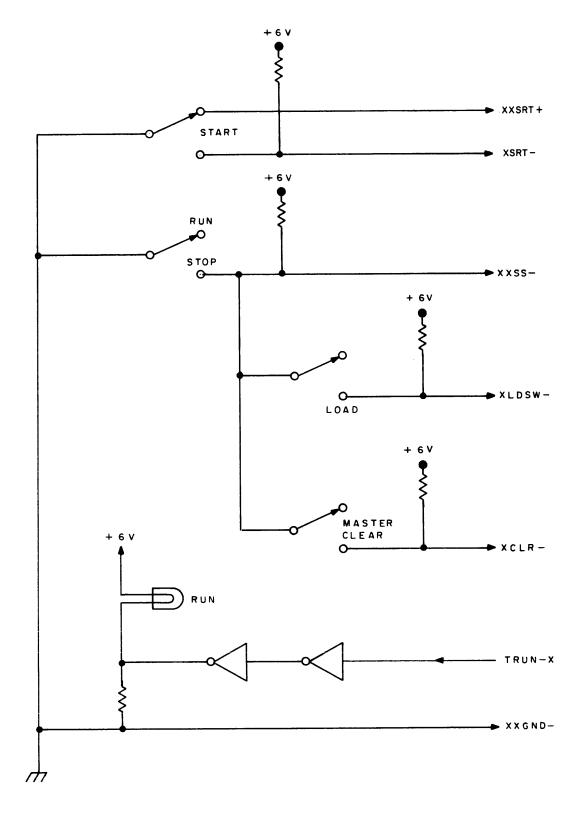

The master clock PAC (A21A) generates and distributes the clock pulses (TCLK). TCLK+ remains active (0V) for 0.270 µs and passive (+6V) for  $0.154 \mu s$ . The run logic receives signal XSRT+ from the START switch on the control panel, XXSRT+ from the START switch on the remote panel (if used), and a common line (XSRT-) from both switches. The level at A15C-25 goes passive (+6V) when one of the switches is depressed and active (0V) when the switch is released. Gates A23A and A23B are used to eliminate switch bounce. If the TRUN flip-flop is reset, the negative-going transition at A15C-25 enables the run condition by setting TRUN. TRUN- is inverted by A15G-29, enabling the set input of the TF1 flip-flop (A18A-26). The TF1 flip-flop is set when the next TCLK+ goes from the passive (+6V) to the active (0V) state and remains set for 0.424 µs. During this time, signals TF1+ and TF1- are used to condition CPU control logic (e.g., gate B34E on LBD 12.01). Gate B21K disables the set input to the TF1 flip-flop until the CPU is ready to enter the next fetch cycle (B21K-32 goes active - 0V). A23H and B26E form a flip-flop (TRUNS) which is used for synchronization on starting.

The TF1- signal is inverted by B15G-25, and the resultant signal conditions the set input to the TF2 flip-flop (the input to B15G-23 is explained in the indirect cycle discussion). Flip-flop TF2 is set by the trailing edge of the next TCLK+ pulse, and TF2 time is entered. Every  $0.424 \,\mu s$  the fetch time is set and the previous fetch time reset until the end of TF4.

The contents of bits 9 through 12 of the W-register are checked for the memory reference indirect cycle (A17E and A15L). If the instruction uses indirect addressing, A15L-26 goes passive (+6V), conditioning the set input to the TICYL flip-flop and the input to A17D-3. When the TF5 flip-flop is set, A17D-11 goes active (0V), conditioning the set input to the TF2 flip-flop. At the same time, the output at B15C-13 goes active (0V), inhibiting the set input to the TE1 flip-flop. At the end of TF5 time, the TICYL flip-flop is set, the TF2 flip-flop is enabled, and the timer re-enters the fetch cycle at TF2.

During the first TF5 time if indirect addressing is not used, or during the second TF5 time if indirect addressing is used, the set input to the TE1 is conditioned. Then the next TCLK+ pulse following the appropriate TF5 time sets the TE1 flip-flop, and the execute cycle is entered. The length of the execute cycle depends on the type of instruction. It can be terminated at the end of TE1, TE3, or TE6 time. It can also be stalled in TE2 time or held in TE4 time.

The execute cycle is terminated and the next fetch cycle is started by the TSF1 signal. TSF1 can be generated in seven different ways, which will be explained later. To terminate the execute cycle at the end of TE1 time, TSF1- is used to inhibit the set input of the TE2 flip-flop, and TSF1+ is used to enable the set input of the TF1 flip-flop. Then the TCLK+ pulse at the end of TE1 time resets the TE1 flip-flop and sets the TF1 flip-flop. The execute cycle is terminated at the end of TE3 time in a similar manner, except that the TE4 flip-flop is inhibited.

Operations during a stall (STL) instruction are slightly different. During this instruction, the CPU is held in TE2 time until the STALN- signal goes active (0V). The output at A13G-25 prevents the setting of the TE3 flip-flop, and the output at A17H-26 prevents the resetting of the TE2 flip-flop. When STALN- goes active (0V), the set input to TE3 is enabled and the next TCLK+ pulse sets the TE3 flip-flop. The second TCLK+ pulse resets both TE2 and TE3 flip-flops, and the remainder of the operation is the same.

During instructions which require shifting operations, the CEE4+ signal goes active (0V), inhibiting the reset side of the TE4 flip-flop and the set sides of the TE5 and TF1 flip-flops. At the same time, the output from B17B-20 goes active, generating

TSF1-. After the required shift operations are performed, the CEE4+ signal goes passive (+6V), enabling the above listed flip-flop inputs. The next TCLK+ pulse resets the TE4 flip-flop and sets the TE5 and TF1 flip-flops. In this case, the next fetch instruction is started before the execute cycle is completed.

Instructions are performed in sequence until a halt (HLT) instruction is received, the STOP switch on either panel is depressed, or one of the various stop conditions is detected. Under these conditions the TSTOP- signal goes active, resetting the TRUN flip-flop. The remainder of the instruction is completed, but the output from A15G-29 goes active (0V), inhibiting the set input to the TF1 flip-flop. The timer remains in this condition until the START switch on either panel is depressed and operations are resumed.

#### **INSTRUCTION FETCH (See Tables 3-3, 3-4)**

#### Fetch With Direct Addressing (See FTD 12.75)

The fetch cycle is entered when the TF1 flip-flop in the timer is set. The Register Bus From P-counter (RBFP-) (LBD 12.01) goes active (0V) during TF1 if there is no interrupt waiting to be serviced (INTFF-A is passive: +6V). The output gates of the program counter (LBD 12.06) are enabled by RBFP-, and the address in P is gated onto the register bus. The data on the register bus are allowed to settle and the transfer gates of the Y-register (LBD 12.07) are conditioned. Near the end of the TF1 state, TCLK+B goes passive, generating the Register Bus To Y-register Upper and Lower signals (RBTYU+ and RBTYL+) (LBD 12.01). The trailing edge of RBTYU+ and RBTYL+ transfers the address on the register bus into the Y-register.

During TF2 time, memory control signals required for the read/regenerate mode are generated and routed to the memory (see LBD 12.00). When the TF2 flip-flop is set, MREAD+A goes passive (+6V), indicating that the memory location whose address is in the Y-register will be read. The address logic in memory is reset by MARP-A, which is active (0V) from the start of TF2 to the setting of the Memory Cycle Initiate (MCI) flip-flop. When MARP-A goes passive (+6V), the address in the Y-register is valid in the memory address logic.

At the start of TF2, MCILC+ goes passive (+6V), conditioning the set side of the MCI flip-flop. The

leading edge of TCLK-, which occurs near the middle of TF2, sets the MCI flip-flop, initiating the memory cycle. The program counter is incremented by PADV-, which is generated by B22E (LBD 12.00).

The memory cycle continues during TF3 time, with the read cycle being performed first. WR-, which clears the W-register, goes active (0V) at the start of TF3 and passive (+6V) when TCLK- goes active (0V). The read cycle is completed, and the instruction in the addressed memory location is strobed onto the dc set lines (MSW01- through MSW12-) of the W-register (LBD 12.08). The contents of the W-register are used during a memory write cycle to restore the instruction in the addressed memory location.

At the start of TF4, bits 8 through 12 of the W-register are copied onto the register bus by the Register Bus From W-register Upper signal (RBFWU+) (LBD 12.01). After the lines are allowed to settle, the Op Code portion of the instruction (bits 9 through 12) is transferred into the F-register by the negative-going edge of the Register Bus To Function (Op Code) register signal (RBTF+) at the end of TE4.

The functions performed during TF5 depend on the mode of address and the condition of the sector bit (bit 8 in the W-register). Direct addressing is described in this section, indirect addressing in the next. The logic described is contained on LBD 12.01.

Irrespective of other conditions, bits 1 through 7 of the W-register are gated onto the register bus when TF5- goes active (0V), causing the Register Bus From W-register Lower signal (RBFWL+) to go passive (+6V). The contents of these 7 bits identify a location within a sector of memory. When TCLK+B goes passive (+6V), RBTYL+ is generated and its trailing edge transfers the address into bits 1 through 7 of the Y-register.

Bit 8 of the W-register is sampled to determine the sector of memory being addressed. If the primary sector (sector 0 or 32) is addressed, W08+ is active (0V), conditioning B24B-24. In this case, TCLK+B goes passive (+6V), which enables the gate and generates RBTYU+. Since bits 8 through 12 of the register bus contain ZEROs, the trailing edge of RBTYU+ transfers ZEROs into bits 8 through 12 of the Y-register. Under these conditions, the

addressed location is one of the 128 addresses in sector 0 or sector 32.

If the addressed location is in the same sector as the instruction, bits 8 through 12 of the Y-register must remain unchanged. To accomplish this function, W08+ must be passive (+6V), causing B24-16 to go active (0V). In this case, gate B24B is inhibited, RBTYU+ is not generated, and the upper 5 bits of the address remain the same.

At the end of TF5, the execute cycle is started if direct addressing is used, or the extended fetch cycle is entered if indirect addressing is used.

#### Fetch With Indirect Addressing (See FTD 12.76)

The indirect addressing mode is activated at the end of TF5 time if bit 12 of a memory reference instruction is set (LBD 12.02). Under these conditions, the set inputs to the TF2 and TICYL flip-flops are enabled, the set input to the TE1 flip-flop is disabled, and the reset input to the TF5 flip-flop is enabled. The trailing edge of TCLK+A resets the TF5 flip-flop and sets the TF2 flip-flop. When TF5+ goes false, the TICYL flip-flop is set, and the indirect fetch cycle is entered at TF2 time.

To prevent the incrementing of the program counter, TICYL- inhibits gate B22E (LBD 12.00) during TF2 of the indirect fetch cycle. MREAD+A and MARP-A are generated and used to condition the memory for a read/regenerate mode. The next TCLK- pulse sets the MCI flip-flop, and the memory read cycle is initiated. The address in the Y-register (loaded during the preceding TF5 time) is regarded as the address of a pointer. The W-register is cleared when TF3- goes true (0V). The contents of the addressed memory location are then read and strobed onto the dc set lines of the W-register.

The F-register, which contains the Op Code of the instruction, must not be changed during the indirect fetch cycle. Therefore, TICYL- disables gate C27C (LBD 12.01), inhibiting the generation of RBFWU+ and RBTF+ during TF4 of the indirect fetch cycle.

At this time, the W-register contains the address of the memory location to be referenced, and this data has to be transferred to the Y-register. To perform this function, TICYL+ conditions gate C32G. RBFWU+ and RBFWL+ are generated, gating the contents of the W-register onto the register bus while TF5+ is true (+6V). TICYL-

causes B24A-16 to go passive (+6V), conditioning gate B24B. RBTYU+ and RBTYL+ are then generated by TCLK+B. When TCLK+B goes false (0V), the trailing edges of RBTYU+ and RBTYL+ transfer the data on the register bus into the Y-register. The new contents of the Y-register are used as the effective address during the execute cycle.

#### INSTRUCTION DECODING

The H112 instruction repertoire contains five basic instruction groups. Bit patterns of the instructions are decoded to obtain the control signals required to perform the desired functions. The major portion of the decoding logic is contained on LBD 12.05. Additional decoding appears on the other LBDs. The most efficient use of the decoding logic is obtained by decoding different bit combinations and using the decoded signals wherever they are applicable. Where this technique is impractical, the Op Code of a specific instruction is decoded (e.g., DIRS for an IRS instruction). Table 3-1 groups the instructions and lists the bit patterns used in decoding.

#### **Memory Reference Group Decoding**

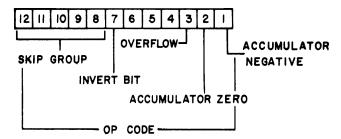

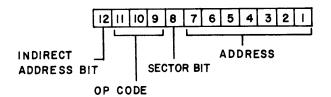

The instruction word format for a memory reference instruction is as follows:

Bits 9 through 12 of the instruction are transferred into the F-register during TF4 time, and the contents of the F-register remain unchanged until TF4 time of the next instruction. An Op Code of three bits allows a maximum of seven instructions in the memory reference group plus an all-ZERO combination for all non-memory reference instructions. The decoding of these instructions is shown throughout the LBDs and will be explained in the discussion of the specific instructions.

The JMP instruction, though not a true memory reference instruction, is included in this group for decoding convenience only. The indirect address bit, also contained in the F-register, is used to extend the fetch cycle during the execution of an indirect instruction in this group.

TABLE 3-1. INSTRUCTION CODING

| Group               | Mnemonic                                                           | Instruction                                                                                                                                                                                                                                                  | 12                              | 11                              | 10                              | 9                                         | 8                                         | 7                                         | 6                                              | 5                                                   | 4                                                   | 3                                              | 2                                                   | 1                                              |

|---------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|---------------------------------|-------------------------------------------|-------------------------------------------|-------------------------------------------|------------------------------------------------|-----------------------------------------------------|-----------------------------------------------------|------------------------------------------------|-----------------------------------------------------|------------------------------------------------|

| Memory<br>Reference | LDA<br>STA<br>JMP<br>ADD<br>ANA<br>IRS<br>JST                      | Load A<br>Store A<br>Jump<br>Add<br>AND A<br>Increment, Replace, and Skip<br>Jump and Store P                                                                                                                                                                | X<br>X<br>X<br>X<br>X           | 0<br>0<br>0<br>1<br>1<br>1      | 0<br>1<br>1<br>0<br>0<br>1      | 1<br>0<br>1<br>0<br>1<br>0                | X X X X X X X                             | X<br>X<br>X<br>X<br>X                     | XXXX                                           | X<br>X<br>X                                         | X<br>X<br>X<br>X                                    | X<br>X<br>X<br>X                               | X<br>X<br>X<br>X                                    | X<br>X<br>X<br>X                               |

| Input/Output        | OTA<br>INA<br>SKS<br>OCP<br>SMK<br>SMK                             | Output Transfer from A Input Transfer to A Skip if Set Output Control Pulse Set Mask SMK00 Set Mask SMK01                                                                                                                                                    | 1<br>1<br>1<br>1<br>1           | 0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>0                     | 1<br>0<br>0<br>1<br>1<br>1                | 0<br>0<br>1<br>1<br>1                     | X<br>X<br>X<br>0<br>0                          | X<br>X<br>X<br>0<br>0                               | X<br>X<br>X<br>0<br>0                               | X<br>X<br>X<br>0<br>0                          | X<br>X<br>X<br>0<br>0                               | X<br>X<br>X<br>X<br>0                          |

| Shift               | LGR<br>ARS<br>RAR                                                  | Logical Right Shift<br>Arithmetic Right Shift<br>Rotate A Right                                                                                                                                                                                              | 0<br>0<br>0                     | 0<br>0<br>0                     | 0<br>0<br>0                     | 0<br>0<br>0                               | 0<br>0<br>0                               | 1<br>1<br>1                               | 0<br>0<br>1                                    | 0<br>1<br>0                                         | X<br>X<br>X                                         | X<br>X<br>X                                    | X<br>X<br>X                                         | X<br>X<br>X                                    |

| Generic             | CRA OCA TOA ENB INH STL HLT TAB TBA ITS                            | Clear A One's Complement A Two's Complement A Transfer Overflow to A Enable Interrupt Inhibit Interrupt Stall On Line Halt Transfer A to Bank Transfer Bank to A Interrupt Save Interrupt Return                                                             | 0 0 0 0 0 0 0 0 0 0             | 0 0 0 0 0 0 0 0 0 0 0           | 0000000000                      | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 1<br>0<br>0<br>0<br>1<br>1<br>0<br>0<br>1<br>0 | 1<br>0<br>0<br>1<br>0<br>0<br>1<br>0<br>0<br>1<br>0 | 0<br>0<br>0<br>1<br>0<br>1<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>0<br>1<br>0<br>0<br>0<br>0<br>0 | 0<br>1<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1<br>0 | 0<br>1<br>1<br>0<br>0<br>0<br>1<br>0<br>1<br>0 |

| Skip                | SPL<br>SMI<br>SZE<br>SNZ<br>SOV<br>SNO<br>SPN<br>SMZ<br>NOP<br>SKP | Skip if A is Positive Skip if A is Negative Skip if A is ZERO Skip if A is Non-Zero Skip if Overflow Flip-Flop is Set Skip if Overflow Flip-Flop is Reset Skip if A is Positive and Non-ZERO Skip if A is ZERO or Negative No Operation Skip Unconditionally | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0 | 0 0 0 0 0 0 0 0 0                         | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1      | 1<br>0<br>0<br>1<br>0<br>1<br>1<br>0<br>0 | 0 0 0 0 0 0 0 0 0                              | 0 0 0 0 0 0 0 0                                     | 000000000                                           | 0<br>0<br>0<br>0<br>1<br>1<br>0<br>0           | 0<br>0<br>1<br>1<br>0<br>0<br>1<br>1<br>0<br>0      | 1<br>1<br>0<br>0<br>0<br>0<br>1<br>1<br>0      |

#### Input/Output Group Decoding

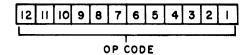

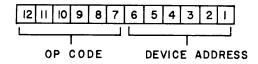

The format of the I/O group is as follows:

An instruction is identified as being in this group when bits 9 through 11 in the F-register are ZEROs and bit 12 is a ONE. Under these conditions, DGEN+ and F12+ are true (+6V), causing DIOG+ to

go true (+6V) (LBD 12.05). Then, bits 7 and 8 of the W-register are decoded, generating the required I/O control signals. These are routed to the peripheral devices via the I/O bus. For example, DO78+ (LBD 12.05), which is true (+6V) when W07 and W08 both are ZEROs, causes the KINAL- line to go true (0V) (LBD 12.11). The signals decoded from the contents of the W- and F-registers are combined to generate CPU control signals. For example, DIOG+ and DO78+ generate DIAG+ (LBD 12.05), which allows RBFDB+ to go true (+6V) during TE4 time (LBD 12.01). Additional decoding is explained in the discussion of the instruction execution.

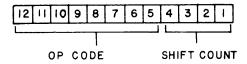

#### **Shift Group Decoding**

The shift group instruction format is as follows:

A shift instruction is identified when F09 through F12 and W08 are ZEROs and W07 is a ONE. Under these conditions, DSHFT- is 0V and DSHFT+ is +6V (LBD 12.05). Then, the DSHFT signals are combined with the contents of W05 or W06 to perform the required CPU functions. For example, DSHFT+ and W06- cause ADSUM- (LBD 12.03) to be false (+6V) during an LGR shift.

#### **Generic Group Decoding**

All 12 bits of this instruction group constitute the Op Code, and the contents of the F- and W-registers are used in the decoding. Bits 7 through 12 are all ZEROs and DG78Z+ is true (+6V) (LBD 12.05). A 2-out-of-6 decoding of bits 1 through 6 provides 15 possible combinations, 11 of which are used with this machine. A further breakdown is obtained by gating W05 and W06 with DG78Z+, which generates DGG5+ and DGG6+, respectively. These signals are used to generate the control signals for the instruction under execution. When W05 or W06 is not used, DG78Z+ is used along with the two selected bits to generate the required control signal (e.g., DG78Z+ · W02+ · W01+ generates DOCA- during an OCA instruction). A 12th generic instruction (HLT) is identified when all bits are ZEROs (e.g., on LBD 12.02, DG78Z+ and W01- through W06- are combined, generating TSTOP-).

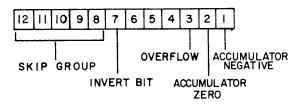

#### **Skip Group Decoding**