#### Mid Project Report on the Study of

#### TECHNOLOGY APPLICATIONS FOR TACTICAL DATA SYSTEMS

15 October 1965

Prepared for

Advanced Warfare Systems Division Naval Analysis Group Office of Naval Research

> under Contract Nonr-4910(00)

by Hobbs Associates, Inc.

## TABLE OF CONTENTS

| 1.                           | INTRO                                                      | ODUCTION AND SUMMARY                               |                                                                                           |                                                                  |  |  |  |

|------------------------------|------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| 2.                           | IMPACT OF NEW TECHNOLOGIES ON MAINTAINABILITY              |                                                    |                                                                                           |                                                                  |  |  |  |

|                              | 2.1                                                        | General                                            | General                                                                                   |                                                                  |  |  |  |

|                              | 2.2                                                        | .2 Status to Date and Plans for Remainder of Study |                                                                                           |                                                                  |  |  |  |

|                              | 2.3                                                        | Technic                                            | cal Discussion                                                                            |                                                                  |  |  |  |

|                              |                                                            | 2.3.1                                              | Elements of Maintainability 13                                                            |                                                                  |  |  |  |

|                              |                                                            | 2. 3. 2                                            | New Technologies that will Influence<br>Maintainability                                   |                                                                  |  |  |  |

|                              |                                                            | 2.3.3                                              | Effect of Batch Fabrication on Packaging<br>Concepts and Techniques                       |                                                                  |  |  |  |

|                              |                                                            |                                                    | 2. 3. 3, 1                                                                                | Batch Fabrication and Interconnection<br>Considerations,         |  |  |  |

|                              |                                                            |                                                    | 2. <b>3.</b> 3 <b>. 2</b>                                                                 | Factors Influencing the Determination<br>of Throw-Away Unit Size |  |  |  |

|                              |                                                            | 2, 3, 4                                            | 2.3.4 Throw-Away Unit Cost and Maintenance<br>Personnel Cost Trade-Offs in Future Systems |                                                                  |  |  |  |

| 3.                           | HARDWARE TECHNOLOGIES                                      |                                                    |                                                                                           |                                                                  |  |  |  |

|                              | 3.1 Criteria for Selecting Technologies to be Investigated |                                                    |                                                                                           |                                                                  |  |  |  |

| 3.2 Components and Packaging |                                                            |                                                    |                                                                                           | ackaging 35                                                      |  |  |  |

| •                            |                                                            | 3, 2, 1                                            | General.                                                                                  |                                                                  |  |  |  |

|                              |                                                            | 3, 2, 2                                            | Status to                                                                                 | Date and Plans for Remainder of Study 36                         |  |  |  |

|                              |                                                            | 3, 2, 3                                            | Technica                                                                                  | 1 Discussion 38                                                  |  |  |  |

|                              | 3, 3                                                       | Memories                                           |                                                                                           |                                                                  |  |  |  |

|                              |                                                            | 3. 3. 1                                            | General.                                                                                  | •••••••••••••••••••••••••••••••••••••••                          |  |  |  |

|                              |                                                            | 3.3.2                                              | Status to                                                                                 | Date and Plans for Remainder of Study45                          |  |  |  |

|                              |                                                            | 3. 3. 3                                            | Technica                                                                                  | l Discussion 48                                                  |  |  |  |

|    | 3.4                 | Displays                                                        |                     |                                                                 |  |  |  |

|----|---------------------|-----------------------------------------------------------------|---------------------|-----------------------------------------------------------------|--|--|--|

|    |                     | 3.4.1                                                           | General             |                                                                 |  |  |  |

|    |                     | 3. 4. 2                                                         | Status to           | Date and Plans for Remainder of Study 57                        |  |  |  |

|    |                     | 3. 4. 3                                                         | Technical           | Discussion                                                      |  |  |  |

|    | 3.5                 | Input/Ou                                                        | tput                | • • • • • • • • • • • • • • • • • • • •                         |  |  |  |

|    |                     | 3. 5. 1                                                         | General.            |                                                                 |  |  |  |

|    |                     | 3.5.2                                                           | Status to           | Date and Plans for Remainder of Study64                         |  |  |  |

|    |                     | 3, 5, 3                                                         | Technical           | Discussion                                                      |  |  |  |

|    |                     |                                                                 | 3. 5. 3. 1          | Improvements in Conventional Types<br>of Input/Output Equipment |  |  |  |

|    |                     |                                                                 | 3, 5, 3, 2          | New Types of Input/Output Equipment84                           |  |  |  |

|    |                     | :                                                               | 3, 5, 3, 3          | System Organization to Minimize<br>Input/Output                 |  |  |  |

| 4. |                     | CT OF NEW HARDWARE TECHNOLOGIES ON FUTURE<br>L TACTICAL SYSTEMS |                     |                                                                 |  |  |  |

| 5. | INFORMATION SOURCES |                                                                 |                     |                                                                 |  |  |  |

|    | 5.1                 | Organiza                                                        | nizations Contacted |                                                                 |  |  |  |

|    | 5.2                 | Bibliography                                                    |                     |                                                                 |  |  |  |

|    |                     | 2008<br>                                                        |                     |                                                                 |  |  |  |

#### 1. INTRODUCTION AND SUMMARY

This report presents the results at the mid point of a study of Technology Applications for Tactical Data Systems. The study is divided into two major phases. The first deals with the effect of new technologies on the maintainability of future tactical data systems and the ways in which maintainability considerations will influence the utilization of new technologies. The second covers the study and evaluation of new hardware technologies that will be used by systems planners in planning Navy and Marine tactical data systems for the 1970 to 1980 era. The study of hardware technology, while includes component and packaging techniques, memories, displays, and input/output equipment, in closely related to the MTACCS Phone for for II study by Myormatus, Inc. Meet ()

The over-all purpose of the study is to provide the necessary technical information and evaluations of new technologies to permit the systems planner to make proper decisions concerning the selection of hardware for implementing any necessary functions in 1970 to 1980 era systems. This study is intended to provide guidance for systems planners in both the selection of hardware to meet performance requirements and the proper utilization of new technologies to improve maintainability of future data systems operating in a tactical environment.

This report is preliminary in nature covering only the first half of the study. As a result, preliminary information, opinions, and conclusions are presented that may be altered by subsequent investigations and evaluations during the remainder of the study. This report is not intended to be complete in all areas. Greater detail is presented in some areas than in others depending upon the status of the work in particular areas and the information presented in previous reports,

The manner and extent to which technical information is presented is also influenced by the fact that part of this study is a follow-on to a previous study of hardware technology conducted last year in conjunction with Informatics as part of the ANTACCS study. The results of the investigations and evaluations of hardware technology last year are presented in great detail in Volume V of the ANTACCS Final Report. This is particularly true with respect to components and packaging techniques, memories, large screen displays, and conventional input/output equipment. Hence, in these areas this study has concentrated on the investigation and evaluation of newer research and development efforts and on monitoring, validating, and updating the status and expectations for the more important technologies that were covered in the ANTACCS Final Report.

Emphasis has been placed in the study this year on the relationship of new technologies and packaging techniques to maintainability and on new technologies for replacing conventional types of electromechanical input/output equipment. These topics are covered in greater detail in this Mid Project Report than are components, memories, and displays. In these latter three categories the material presented in this report primarily covers important conclusions, changes in a specific technology that have occurred since the end of 1964, and new technologies that were not adequately covered in the ANTACCS Final Report but which have subsequently shown greater importance or higher feasibility. The preliminary material presented in this Mid Project Report will be revised, updated, and expanded in the Final Report.

New electronic and magnetic technologies, particularly those based on batch-fabrication techniques, have advanced at a much faster rate than most of the industry had anticipated. Feasibility has already been proven for many new technologies and several of them have already

been utilized in production equipment. However, the products available today employing these new technologies represent only the initial steps in a revolutionary change in electronic and magnetic equipments. For example, a single monolithic integrated circuit mounted in a flat pack, which represents a major advance over equivalent circuits fabricated from discrete components on a printed circuit board a year or two ago, will be replaced within the next few years by large interconnected multi-circuit arrays fabricated on a silicon chip. Each such chip may contain hundreds or thousands of interconnected circuits. Several multi-circuit arrays of this type can be interconnected by vacuum deposited wiring patterns on substrates and packaged as a single large unit. This will make it possible to fabricate and interconnect major portions of a computer in a single replaceable unit, but logic design and machine organization techniques must be developed to permit computers to be organized in large functional blocks to a much greater extent than at present. This will be necessary in order to minimize the interconnections between functional blocks and the number of leads that must be brought out from each functional unit.

The solid state electronic and magnetic portions of large digital systems are more amenable to batch fabrication and hence will benefit from new technologies to a much greater extent. This includes central processors, internal memories, solid-state on-line auxiliary memories, and the digital logic, control, and storage portions of displays and input/output equipment. The portions of displays, input/output equipments, and mass memories that will require high voltage, high power, photographic equipment, optical equipment, or electromechanical equipment will continue to present major problems with respect to cost, size, weight, maintainability, and reliability. Hence, a serious system imbalance will result unless solid-state electronic or magnetic replacements are developed for present types

of displays (visual transducers), mass memories, and input/output equipments,

The impact of new technologies on Naval tactical systems by the early 1970's will be profound. Even if no performance or application requirements exist for the development of new systems, the significant improvements that new technologies will make possible in size, weight, reliability, and maintainability will justify the development of a new generation of tactical data systems.

The efficient utilization of batch-fabrication technologies will require a significant increase in the functional size and complexity of replaceable or throw-away units. Although the cost per component or per circuit will be only a fraction of present costs, the batch fabrication and interconnection of large arrays of circuits in a single package will probably cause an increase in the total cost of an individual package. If maximum advantage is to be taken of the capabilities of batch fabrication for small size, low cost, and high reliability, it will not be feasible to make repairs in a packaged unit on shipboard, and probably not at a state-side repair depot. Hence to realize the full potential of batch fabrication techniques will require increasing the functional size, complexity, and cost limits presently established for throw-away units. Any increase in the cost of the unit will be offset to a large extent by the increased reliability and hence lower failure rates.

Increasing the functional size and complexity of the throw-awy unit offers major advantages from the standpoint of maintainability. The training and skill levels required for maintenance technicians and the number of maintenance technicians required on shipboard will be reduced, supply and logistics problems will be reduced, fault isolation will be simplified, and down time will be minimized.

If the complete central processor is packaged in a total of 10 or 15 packages, maintenance will consist of locating the fault in one out of 10 or 15 units and replacing the unit. The fault location can be accomplished primarily by diagnostic programs. With significantly higher MTBF's, even this type of maintenance will be required very infrequently. It is reasonable to expect that some time during the 1970 to 1980 period a complete central processor will become a replaceable unit. A multi-computer system concept based on the use of identical small modular computers may facilitate this. In the 1975 to 1985 period such small modular computers may even become throw-away units.

To make these improvements in maintainability possible, changes in maintenance concepts and attitudes on the part of Navy systems planners, budgeters, and users will be necessary. A maintainability concept for future systems should be based on very large functional throw-away units and no shipboard repair except for any electromechanical equipment that may still be necessary.

By 1970 logical circuits are expected to be available in large interconnected circuit arrays costing 3 to 5¢ per circuit and capable of providing speeds in the order of .5 to 10 nanoseconds propagation delays and 10 to 50 megacycle clock rates. Main internal memories are expected to be available costing between 1 to 3¢ per bit and providing read/write cycle times in the order of 0.5 to 2 microseconds with capacities in the order of 100,000 words. Large-screen dynamic displays that do not depend upon electromechanical, photographic, or optical projection systems will be feasible along with flat-panel console type displays that are completely compatible with batchfabricated solid-state electronics.

New types of input/output equipment and solid state replacements for some conventional types of input/output equipment will be feasible, but input/output equipment and large capacity mass memories will represent the major problem areas in future tactical systems with respect to size, weight, cost, reliability, and maintainability. At present the best approach to overcoming these input/output problems seems to lie in developing system techniques that minimize the need for this type of equipment. Unless extensive additional research and development efforts are initiated in input/output equipment and large capacity mass memories, these devices will be the limiting factors in the capability and performance of future systems.

Major problem areas in 1970 to 1980 tactical data systems from the standpoint of hardware technology will be (in order of difficulty):

- 1. Input/output equipment

- 2. Very large capacity auxiliary storage

- 3. Large screen displays

- 4. Concepts and philosophies for maintenance of batchfabricated equipment.

New hardware technologies discussed in this report will have a significant impact on future Naval tactical systems. This impact will be reflected not only in lower cost and increased performance capability, but also in reduced size and weight and increased reliability and maintainability. Reductions in the order of 25:1 in the size and weight of certain parts of the system, such as the central processor, are anticipated. For the over-all data handling and display portions of typical NTDS installations, new technologies feasible for use in 1970 will permit reductions of approximately 2/3 in the size, weight, and power requirements. Implications of these reductions, particularly for small ships, are clear. The accompanying reductions in system down time and maintenance personnel make it imperative that the Navy plan to take advantage of these new hardware technologies at the earliest possible time.

#### 2. IMPACT OF NEW TECHNOLOGIES ON MAINTAINABILITY

#### 2.1 GENERAL

One phase of this study deals with the effect of new technologies on tactical military systems and the ways in which these technologies can be utilized to improve maintainability. The term maintainability is used here in the broad sense to include all aspects of field maintenance - repair time and repair costs, parts usage, parts inventory, logistics, test equipment, replacement costs, personnel, training, etc. Training and maintenance personnel (salary, food, and other support costs on station, dependence allowances, etc.) represent the major maintenance costs. Hence, in the maintainability study, major emphasis has been placed on factors that reduce the time required for maintenance, the skill level required for the maintenance technician, and the number of maintenance technicians required.

New technologies providing solid state electronic and magnetic components fabricated and interconnected by batch fabrication techniques offer the potential for truly significant improvements in reliability and maintainability. Reliability and maintainability of electromechanical peripheral equipment, such as mass memories and input/output equipment, will improve but only in an evolutionary manner. The improvements that can be achieved economically in this type of equipment are limited. Hence, this study of maintainability has dealt primarily with improvements that can be obtained in those portions of the system that can utilize solid-state electronic and magnetic components.

From the maintainability standpoint, the major improvements

that can be achieved in electromechanical peripheral equipment will be achieved by minimizing the need for this type of equipment and by finding solid-state electronic or magnetic replacements wherever possible. These questions are considered in greater detail in the memory, input/output, and display portions of the hardware technology part of this study.

It is in computers and central processors; digital logic, digital storage, and low level linear and video amplifiers in peripheral equipments; and solid-state on-line auxiliary storage that truly significant maintainability improvements can be achieved if new technologies that will be available by the early 1970's are properly utilized.

Maintainability considerations alone may justify the development of a new generation of tactical data systems. This study team believes the improved maintainability and reliability, coupled with reductions in size, weight, and power requirements which are discussed later, will necessitate the development of systems utilizing these new technologies even if performance requirements for new systems did not exist.

New concepts are needed to achieve the maximum improvement in maintainability commensurate with other system requirements such as performance, cost, size and weight, availability, etc. New attitudes and thought patterns are needed in considering equipment design and packaging, repair and inventory costs, and maintenance procedures and techniques.

Two specific examples of essential changes in attitudes and concepts illustrate this. One is the need for increasing the cost limit for throw-away units (presently in the order of \$100) by a factor of several times (possibly over an order of magnitude). Another is

the possible elimination of all shipboard repair for certain types of equipments. These changes in attitudes and concepts will be made possible by significant increases in reliability (i. e. reduced mean-time-between-failure) and significant reductions in the cost per element of the hardware involved.

A larger non-repairable unit is also required by the functional organization and interconnection and packaging techniques necessary to fully realize the reliability, cost, and size and weight potentials offered by new batch-fabrication technologies. Hence, some of the same changes in attitudes and concepts needed from the maintainability standpoint are also necessary to permit full realization of the advantages of batch fabrication.

Since cost, reliability, and maintainability considerations for batch fabricated units all favor a large functional throw-away unit, a difficult problem is raised with respect to flexibility. A particular large functional unit may be used in only one place in a computer. This creates a problem from both the manufacturing and spares standpoints. If a throw-away unit is a single flipflop, as has been the case in the past, a large number of these can be manufactured and an individual one can be used in any one of a large number of places in the computer. However, if the throwaway unit is a complete parallel adder, only one may be used in the entire computer.

One possible approach that looks attractive is the use of a multicomputer system in which each individual computer is relatively small. This would permit a higher volume of production for each type of unit and would permit the possibility of carrying a spare computer to further facilitate easy and rapid maintenance. It may be desirable to design all types of shipboard systems, including data handling systems, weapons systems, and sensors, to utilize identical small computers with the number of these in

each system being tailored to the requirements of the system. If the cost of logical components and storage drop as much as is anticipated, it may be relatively unimportant that one of these standard computers is less efficient in a particular system than a computer designed specifically for that system.

With the level of effort provided in this study, a maintainability investigation and analysis cannot be conducted in the depth of previous maintainability studies such as those of the Polaris program or other major Navy weapons programs, nor can this study delve as deeply into maintainability techniques, procedures, and data as the PACED program at NASL. Maintainability investigations of that magnitude require many tens, if not hundreds, of man years of effort. Fortunately, for the purposes of this study that level of effort and amount of detail are not necessary since a specific system and specific designs are not under consideration.

For a research study pointed toward the application of new technologies in 1970 to 1980 era tactical data systems, the important tasks are to determine relationships, guide lines, and criteria and to develop concepts for the utilization of these new technologies to achieve improvements in maintainability. The important results of this study will lie in the development of conceptual approaches to improved maintainability through the proper use of new technologies. It will call attention to and emphasize the need for new attitudes and thought patterns with respect to system design, packaging, and maintainability.

This study will develop criteria for determining the cost and functional size of throw-away units, will indicate the changes in maintainability concepts and attitudes necessary on the part of Navy personnel (systems planners, budgeters, and users), and will provide guidelines for Navy planners in utilizing new technologies to achieve improved maintainability.

2.2 STATUS TO DATE AND PLANS FOR REMAINDER OF STUDY Batch-fabrication techniques suitable for the fabrication of central processors and storage are emphasized in the components and packaging and memory investigations in the hardware technology phase of this study. Since these fabrication techniques are essential to significant cost reductions and reliability improvements, they are also given major emphasis in this study of maintainability. In general, the higher the degree of batch fabrication, the lower the cost per function and the higher the reliability - hence, improved maintainability. Lower component costs will permit larger functional throw-away units which in turn will facilitate fault isolation and minimize repair time. Higher reliability will facilitate maintainability by reducing the number of failures and the number of repairs necessary and by permitting a further increase in the size of the throw-away unit.

Major consideration is being given to batch-fabrication techniques for:

Logic circuits Low level amplifiers Memories Interconnections Packaging

Packaging techniques are directly related to the consideration of batch-fabrication techniques. Hence, detailed consideration is being given also to the criteria for selecting the size and configuration of throw-away units and the functional grouping within a throw-away unit. The effect of batch fabrication, reliability, redundancy, packaging techniques, and functional organization on the major elements of maintainability are being considered.

Present concepts, approaches, and problems in maintainability have been discussed with many Navy personnel. Attempts to obtain information on present maintenance costs have met with only partial success.

These investigations and analyses will be continued in the remainder of the study. Reliability will be considered from both the component and the system level. The effect of different levels of redundancy will be considered including:

No redundancy Component level Circuit level Function level Equipment level System level

The relationships of packaging techniques and functional organization to diagnostic programming, fault isolation, and self test and the effects on tactical systems of improved maintainability that can result from new technologies will be considered. Changes in concepts and attitudes towards maintainability will be recommended where these are necessary to effectively utilize new technologies from the maintainability standpoint.

The effects of new technologies on maintainability are being investigated by discussions with technical experts working in these areas of technology and with ones working on maintainability problems, by a study of the applicable literature, and by evaluation of the information concerning the different technologies in relation to maintainability problems in future Naval tactical systems. This portion of the study is closely related to that dealing with new batch-fabrication technologies and is being closely coordinated with those investigations and evaluations.

#### 2.3 TECHNICAL DISCUSSION

#### 2. 3.1 Elements of Maintainability

In considering the broad question of maintainability several different elements of the maintanance problem should be considered individually. These elements are not all affected in the same way by different approaches to maintainability or by changes in component or packaging technology. A technology change that may be advantageous with respect to one element of maintainability may be a disadvantage with respect to another.

The elements of maintainability include:

Maintenance cost Spares inventory costs Logistics or supply costs

Replacement part costs Repair costs

Personnel costs Reliability and failure rate Equipment down time System availability Fault location time **Repair** time

Personnel training and skill levels Number of maintenance personnel Spares inventory quantity Personnel availability Spares availability Spares commonality Frequency of spare parts usage Test equipment requirements Diagnostic programming requirements

These elements are all inter-related and, unfortunately, sometimes affect one another adversely. For example, increasing the functional size of a throw-away unit may reduce fault isolation time, maintenance time, down time, and personnel training requirements; but it may, on the other hand, increase the spares inventory cost and reduce the commonality. Hence in considering the effects of new technologies on maintainability one must be careful not to achieve improvements in some of the elements in maintainability at the expense of excessive costs or severe disadvantages in other elements. This leads to the necessity for making a careful trade-off analysis when conflicting effects are created by a change in maintenance concepts or equipment technology.

Although the effects on different elements of maintainability have been considered at all phases of the study, they are discussed in this report only where a significant advantage or disadvantage exists. This is illustrated in subsequent parts of this section by the consideration given to the effects of batch fabrication and larger throw-away unit packages and the resulting trade-offs that must be evaluated.

2. 3. 2 <u>New Technologies that will Influence Maintainability</u> In the technology sections of this report new technologies are analyzed and evaluated for components and packaging techniques, memories, displays, and input/output equipment. In the discussions of these different areas and individual technologies within each area, improvements in costs and reliability as well as performance are considered.

These new technologies will influence maintainability in two primary ways.

1. Increased reliability and reduced failure rates will reduce the maintenance effort required and will perm t increases in the costs of throw-away units. If the failure rate becomes low enough it will reduce the number of technicians required and may eliminate requirements for stocking certain units as spares on shipboard.

2. Lower cost components and the lower costs of batch-fabricated interconnection techniques will permit a significant increase in the functional size of a throw-away unit. This will in turn facilitate fault isolation and reduce the training requirements and the number of maintenance personnel required. At the same time, efficient utilization of batch-fabrication techniques in interconnections and packaging will necessitate larger throw-away units. Hence the achievement of cost and performance potentials, as well as

maintainability improvements, depends upon significantly increasing the size of the throw-away unit. Fortunately, components and interconnection costs and improved reliability and reduced failure rates will permit such increases in the functional size of a throw-away unit.

The new technologies that will influence maintainability most significantly are those that are suitable for batch fabrication, that reduce the cost per component (or circuit) materially, and that significantly increase reliability. Such technologies that appear both promising and feasible include:

Components and Packaging

Monolithic integrated circuits

Hybrid monolithic/thin-film integrated circuits

Metal-oxide-semiconductor (MOS) integrated circuits Memories

Integrated circuit arrays

MOS arrays

Planar magnetic thin-film arrays

Plated wire arrays

Permalloy sheet toroid arrays

Displays

Opto-magnetic displays

Crossed-grid electroluminescent displays with integrated storage Injection electroluminescence matrix displays

Although not adaptable to batch fabrication techniques, photochromic displays, thermoplastic and photoplastic light valves, laser displays, and solid-state light valves offer promise for maintainability improvements from the standpoint of both cost and reliability.

Some reliability improvements in electromechanical input/output equipment and mass memories are anticipated, but the major hope for significant improvements in maintainability for peripheral equipment lies in minimizing the need for equipment of this type and in finding replacements for some of the conventional types of equipments. The replacement of punched paper tapes by incremental magnetic tapes discussed in the input/output technology section will improve maintainability by increasing reliability. Solid-state mass memories discussed in the memory technology section will improve the maintainability and reliability of the system by serving as replacements for electromechanical mass memories and for some of the "input/output" functions performed by magnetic tape units in present systems.

The major improvements in maintainability will occur in the central processor, internal memory, and solid-state on-line auxiliary memories. However, the technologies and batch-fabrication techniques used in central processors and internal memories will also be applicable to portions of other equipment where similar functions are required and similar techniques are applicable. This includes the logic, control, and storage functions in display consoles and input/ output equipments such as magnetic tape units. By 1970 low-level linear circuits, such as deflection amplifiers and video amplifiers in CRT displays, can be implemented with integrated circuit techniques. High power or high voltage circuits, such as the final stages of the deflection drivers in CRT displays, are more questionable but not completely hopeless within the time frame covered by this study. Communication equipments are not within the scope of this study, but power amplifiers in transmitters will probably represent a problem area.

In computer and data handling systems, the major areas where significant improvements in maintainability do not appear likely are in very large capacity auxiliary storage and input/output equipment. The best approach in these areas from the systems standpoint is to minimize the need for equipments of this type. There is also some

question as to whether significant improvements in maintainability can be achieved in the viewing portions (i.e., the visual transducer) of displays - particularly large-screen displays. However, several potential display technologies, such as opto-magnetic panels and injection electroluminescence matrices, may permit significant improvements in maintainability for console displays, and possibly for large-screen displays.

2.3.3 Effect of Batch Fabrication on Packaging Concepts and Techniques The importance of batch fabrication in future systems design has been emphasized in both the maintainability and technology portions of this study. Batch fabrication is the key to lower costs, higher reliability, and reduced size and weight. However, effective utilization of batch fabrication technologies will require major changes in packaging concepts and techniques.

2.3.3.1 <u>Batch Fabrication and Interconnection Considerations</u> The packaging section of the ANTACCS Final Report discussed eight levels of packaging and interconnections in systems using integrated circuits:

1. Packaging and interconnection of the elements of each integrated circuit on a silicon chip.

2. Interconnection of separate circuits fabricated on the same silicon chip.

3. Interconnection between circuits on separate silicon chips that are packaged in the same module.

4. Interconnections between the silicon chips and the external leads of the package.

5. Interconnections between modules on a replaceable unit such as a printed circuit board.

6. Interconnections between replaceable packages in a modular subunit or a small equipment.

7. Interconnections between modular subunits in a unit of equipment.

8. Interconnections between separate pieces of equipment in a system.

The first and second level of interconnections are made in the initial processing of the silicon chip, although they may be made with separate masks and in separate vacuum deposition operations. To achieve the potential for improvements in both cost and reliability offered by batch fabrication, it will be necessary to continually strive to fabricate larger and larger arrays of interconnected circuits on the same silicon chip. Hence, emphasis will be placed on increasing interconnections at the second level and minimizing interconnections at higher levels - particularly at the fifth, sixth, and seventh levels which represent major elements of cost and lesser reliability. In fact, it is hoped that eventually a sufficiently large functional throw-away unit can be used that the fifth and seventh levels can be completely eliminated. In that case, the throw-away unit would consist of large arrays of integrated circuits on a limited number of silicon chips (first and second levels) that are interconnected by a wiring pattern on a substrate (third level) which also provides termination points for connecting to the external leads of the package (fourth level). Packages of this type would be either plugged or wired into the equipment containing the interconnections between the sockets or connectors (sixth level). These equipments would then be interconnected by cables to form the system (eighth level).

As semiconductor and batch fabrication techniques advance, the major limitation on the size of the functional unit (other than cost)

will be the number of external leads that can be provided on a package. Although packages with larger numbers of leads (in the order of 40 to 100) are being developed, additional research in machine organization is urgently needed to develop functional organizational concepts that will maximize the interconnections within a replaceable package and minimize the interconnections between packages. The way in which the computer is divided into functional modules can greatly increase or decrease the number of connections needed between such modules.

It will be necessary to use different criteria for design efficiency in batch fabricated systems. In the past, minimizing the number of logical elements has been a major goal of most logical design efforts. In future systems, it may be necessary to utilize logical elements inefficiently in order to minimize the number of interconnections needed between functional modules. For example. frequently in previous computers a given gate or flip-flop has supplied inputs to a number of logical elements in different parts of the machine; while in future systems the logical gate or flip-flop may be duplicated many times in different parts of the system to avoid the necessity for transferring the signal from one module to another. Emphasis must be placed on reducing the number of packages and the number of interconnections between packages - even at the expense of increasing the logical complexity of each package significantly.

From the standpoint of cost and maintainability future systems should use large integrated circuit arrays (either monolithic or MOS) on single chips of silicon with these chips then interconnected by a vacuum deposited thin-film interconnect pattern on a substrate (e.g. the NAFI thin-film circuit techniques). Thin-film resistors and capacitors can be fabricated on the interconnection substrate where high precision or large values are needed. This unit would

then become the replaceable or throw-away unit. The marriage of silicon integrated circuit techniques with thin-film fabrication techniques will combine the best advantages of both while maximizing the interconnections that can be made internally in the package. The importance of additional research efforts in computer design and machine organization to provide more highly functional organizations that will minimize interconnections between functional modules must be emphasized in order to take advantage of the potential offered by the combination of integrated circuit and thinfilm connection technologies.

2.3.3.2 Factors Influencing the Determination of Throw-Away Unit Size In establishing packaging trade-off criteria it is necessary to consider the effect on the initial cost of the system and on the major elements of maintainability. All of these factors except spares inventory cost, replacement part cost, and spares commonality favor a very large throw-away unit (large in the sense of complexity, not size) with shipboard and field repairs limited to the replacement of these large units. When replaced these units would usually be thrown away, but in certain special cases they might be returned to a state-side depot for repair.

The failure rate and the inventory cost of these large throw-away units will be sufficiently small, relative to present day failure rates and costs, to justify a quite large throw-away unit in preference to smaller ones. Although it is emotionally difficult to accept the idea of throwing away a \$2000 subunit in which only one component has failed, this can be justified if such failures occur infrequently (e.g. less than once per year) and if the use of throw-away units of this size can eliminate the need for one or more technicians on shipboard.

In batch-fabrication technologies the selection of a throw-away unit size involves many inter-related factors, but in general the larger the throw-away unit size (in terms of complexity) the higher the reliability, the smaller the size, and the lower the cost of the function

accomplished by the throw-away unit. Anything that is done in a large functional unit to make components, circuits, or subfunctions within the unit replaceable will tend to decrease the reliability, increase the size, and increase the over-all cost. Although there will undoubtedly be one or more intermediate steps before this is achieved, it is believed that a complete central processor with the capability of a USQ20B will likely become a replaceable unit without repair capability on shipboard, and possibly even a throw-away unit. However, it is too early to predict whether the cost and the mean-time-between-failure will be sufficiently low to permit discarding the unit or whether state-side repair will be required.

The need for a larger throw-away unit can be shown by listing some of the considerations that favor large throw-away units and some that favor small ones.

#### Considerations favoring large throw-away units:

1. With proper functional organization of the machine, large throw-away units minimize the number of interconnections required from package to package in the system. These interconnections (external to the package) are not as amenable to batch fabrication as those within the package and hence tend to be more expensive and less reliable. Since batch-fabricated interconnections can be more closely controlled and can be made very cheaply, a larger functional unit tends to improve reliability and reduce cost.

2. Making more of the interconnections within the package permits a smaller size and shorter lead lengths between circuits in a given logical function. This tends to permit higher speeds particularly where a large multi-circuit array is fabricated in a single chip with interconnections deposited on the chip.

3. Although large throw-away units may increase the number of different types of spares carried in inventory, they will significantly reduce the total number of items carried in spares.

4. Since packaging costs are a significant part of the cost of completed circuits, the larger the number of circuits in a single package the lower the initial cost. Continuing improvements in integrated circuitry technology will permit larger and larger arrays of circuits to be fabricated and interconnected in a single silicon chip. Interconnection of a number of these chips by printed or deposited wiring on a substrate will permit an even larger interconnected logical function in a single package.

5. Up to a certain point, the limit in putting more circuits in a package is imposed by the number of leads that can be brought out of the package. The ratio of external leads required to the number of circuits in the package is relatively high for smaller package sizes because of the connections that must be made to other packages. However, if the throw-away unit size is increased to the point that complete major logical functions can be contained in a single package, the total number of external connections in the system and the ratio of leads from the package to the number of circuits in the package are significantly reduced. For example, if a complete binary adder with associated registers is packaged in a single unit, the number of external leads required in relation to the number of circuits in the package would be quite small. A striking example of this is the use of several (e.g. 16 or 32) one word registers interconnected and addressed in a matrix fashion in a single unit compared to the packaging of individual one word registers with external interconnections to each.

6. The larger the throw-away unit the easier it is to isolate faults to a particular unit. For example, if the computer or central processor is a throw-away unit in the extreme case, it would be

relatively easy for a technician with minimum training to determine that the fault is in the computer with the aid of a simple diagnostic program. It is progressively more difficult for the maintenance technician to determine that the fault is in the arithmetic unit, in a particular register, in a particular flip-flop circuit, or in a particular diode or transistor on the other extreme. This is extremely important because it affects the training and skill level required of the technician, the repair time, the number of technicians required, and, perhaps even more important, the down time and availability of the system.

7. Easier fault isolation also reduces the length and complexity of the diagnostic programs required in the computer for automatic fault isolation. A diagnostic program to determine that the fault is in the arithmetic unit is considerable shorter than one required to indicate that the fault is in the third bit position of the adder.

8. Easier fault isolation and minimization of repairs made on shipboard as a result of large throw-away units tend to eliminate the need for special test equipment and check-out equipment. For example, if a throw-away unit is a printed circuit board containing a single flip-flop or a few gates, it is usually necessary to have a board tester capable of determining whether a replaced board is in fact malfunctioning. It should be noted also that this tends to encourage a sloppy form of maintenance which has unfortunate results on maintainability - the indiscriminate replacing of boards until one is found that starts the system working again. If a replaced board is to be repaired on shipboard, the test equipment must be even more complex.

The smaller the size of the throw-away unit, the greater the commonality and the ability to utilize one spare unit to replace any one of a large number of units in the system.

A printed circuit card containing a single flip-flop is a good example of a small unit with high commonality.

2. The higher commonality for small units also reduces the cost of spares inventory. This is certainly true if the cost per circuit is the same in a large functional unit as in a small one. However, it may not be true if a larger throw-away unit permits a significant reduction in the cost of a circuit (e. g. a flip-flop) compared to the cost of that same circuit as a single throw-away unit. If a complete computer using large throw-away units costs as much as an equivalent computer using small throw-away units, the cost of spares inventory required for the one using small units will be considerably less. On the other hand, since batch fabrication of large throw-away units should significantly reduce the total cost of the computer, the cost of the spares inventory may be less than for an equivalent system utilizing small throw-away units.

3. With manufacturing and fabrication techniques used to date, a small throw-away unit offers manufacturing economies - again due to commonality. A much larger production run of flip-flop boards can be made if the same flip-flop is used in a large number of places in each computer. On the other hand, if each replaceable or throw-away unit in a system is unique, the production volume of each unit would be limited to the number of computers. However, for some of the newer batch fabrication technologies being developed, this may not be a significant factor. This is illustrated by the possibility of making variable interconnect masks under computer control.

4. If replaceable units are to be repairable instead of throw-away, small units permit greater standardization. This facilitates the technicians ability to repair the units.

5. The lower cost of the small throw-away unit is a significant factor if the usage rate is high - i. e., if the reliability is low and the failure rate high. However, the low failure rates anticipated for batch-fabricated circuits minimize the importance of the cost of the unit in relation to other considerations.

6. A small throw-away unit gives greater flexibility in the organization and layout of the logic of the system. Additional research in machine organization for batch-fabricated systems is needed to overcome this disadvantage of large throw-away units.

Large non-repairable throw-away units(large in the sense of function or complexity rather than physical size and cost) containing complete major functional parts of the computer will improve reliability, simplify fault isolation, reduce down time, reduce the number of technicians required and their training and skill levels, permit higher speed operation, reduce logistics and repair costs, and improve the performance and availability of the system. On the negative side these larger units may increase the number of different types of spares required, the parts cost of replacing a failed unit, and perhaps the total inventory costs. The initial procurement cost of a system using a large throw-away unit will be less if adequate fabrication techniques (e.g., the fabrication of interconnection masks under computer control) for specialized units are developed.

#### 2.3.4 Throw-Away Unit Cost and Maintenance Personnel Cost Trade-Offs in Future Systems

In a new procurement initiated recently, the next AN/USQ-20B computers purchased will cost approximately \$125,000 per computer. By the early 1970s integrated circuit and other batch fabrication technologies will reduce the cost of computers with equivalent capability to \$25,000 or

less. This cost reduction will be accompanied by a significant reduction in size and increase in reliability. However, these improvements in cost, size, and reliability cannot be fully realized without changing maintainability concepts and attitudes to permit much larger functional throw-away units. For example, the \$25,000 central processor predicted above might be packaged in 10 to 15 non-repairable units each costing between \$1500 and \$3000. The reliability of electronics is expected to improve by two orders of magnitude with the rapid development of integrated circuit technologies. Hence, this increase in the cost of the throw-away unit could probably be justified on the basis of reduced usage resulting from higher reliability. Logistics costs would be reduced also as a result of reducing the number of items handled through the logistics system. The higher cost of the larger throw-away unit can certainly be justified in terms of fewer technicians required on station and reductions in their required training and skill levels. The elimination of one technician alone would pay for the cost of the complete computer, and hence a complete set of spare units, in one year.

On an NTDS ship visited by the study team, it was estimated that 10 of the 33 technicians in the NTDS section were devoted to the maintenance of the computers, their internal memories, and the limited amount of input/output equipment in the system. It is reasonable to believe that reducing the repair task to that of locating and replacing one of ten or fifteen major units comprising the computer would eliminate at least one technician. In fact, assuming that half

of these ten technicians are required by the peripheral equipment and half by the computers and internal memories, as many as four of the five technicians concerned with the computers and memories might be eliminated. With very significant reductions in failure rates and fault isolation time and with repairs reduced to merely replacing one of fifteen units, a single technician could easily maintain four computers including the central processors and internal memories.

The predictions and extrapolations from present technology made above may seem far out and perhaps unrealistic. However, based on the investigations and analyses of this study and lengthy discussions with integrated circuit, semiconductor, and batch-fabrication memory experts, these prognostications are believed to be conservative. In the early 1970's the three USQ20B computers and their internal memories, two magnetic tape units (four tape transports), punched paper tape reader, teletype printer and punch, and several large banks of mechanical interconnection switches in a typical NTDS installation can be replaced with three small batch fabricated computers and internal memories including internal electronic switching and gating, a large capacity solid-state random access mass memory, one magnetic tape unit (two tape transports), and a keyboard-printer unit with an associated incremental magnetic tape recorder. The keyboard printer unit may be a non-mechanical keyboard and non-impact printer with no moving parts except for paper feed. At the most, three maintenance technicians would be

required for this complete computer system compared to approximately ten at present. The savings from elimination of seven technicians would exceed the cost of the computer system in two years.

From the maintenance standpoint, the NTDS system on the ship visited by the study team was divided into three major areas - the computer system, the display/input consoles, and the communications terminals. The discussion above has dealt exclusively with the computer system where the greatest gains in maintainability can be achieved through the use of new technologies. However, the same considerations and reasonings apply to portions of the display/ input consoles and the communications terminals. For example, the analyses presented above are equally applicable to the digital control logic and storage in the display/input consoles. Hence, the proper utilization of new technologies will permit maintainability improvements in these other two areas also but to a lesser extent than in the computer system since major portions of the equipments in these areas are not as readily amenable to batch fabrication technologies in the near future.

It is important to point out that these discussions of improved maintainability are valid only if we assume the design of a new-generation system utilizing these new technologies. The fact that these capabilities and improvements will be possible in the early 1970's does not assure that they will be achieved. This depends on factors such as the willingness to obsolete and replace present equipment and the willingness of Navy systems planners, budgeters, and users to adopt the radically different attitudes toward maintenance procedures and costs called for by the maintainability concept advocated here. This maintainability concept is based on very large functional throw-away units and no shipboard repair, except for any electromechanical equipment that may still be necessary.

### 3. HARDWARE TECHNOLOGIES

3.1 CRITERIA FOR SELECTING TECHNOLOGIES TO BE INVESTIGATED Potential uses and advantages in future Naval tactical systems are the major criteria used in selecting technologies to be investigated in this study. Investigation is not considered justified merely because a technology is interesting or different. It must fill some need or offer some potential advantage to Navy systems planners for future tactical data systems.

The needs of the systems planner are influenced by both system requirements and systems design. The systems requirements determine functions that must be implemented, and the systems design determines the way in which these functions are implemented. Both affect the usefulness of a particular technology. Conversely, the characteristics of one type of technology compared to those of another type can influence the way in which the function is implemented. In fact, the availability of a new technology at a low cost and high reliability can make it feasible to implement functions that were not previously justifiable on a cost-effectiveness basis, thus changing the analysis of systems requirements.

After a requirements analysis and systems design based on those requirements have been completed, it is relatively easy to limit the scope of an investigation of technologies for implementing the system. However, since requirements analysis and preliminary systems design for future Navy and Marine Corps tactical systems are still underway, a good deal of judgement is necessary in determining which technologies are to be investigated. It is better to investigate a technology that may not be used than to overlook one that might offer significant advantages to planners of future systems, but it is necessary to limit the number of technologies to be considered in order to concentrate on those that offer the greatest potential for future tactical data

systems. In order to accomplish this, four specific criteria have been applied in selecting technologies for investigation:

1. Is the technology useful for implementing functions existing in the present Naval Tactical Data System or Marine Tactical Data System?

2. Is there some known Navy or Marine Corps operational task for which the technology offers potential advantages, even though the task may not presently be mechanized or may be implemented in a completely different manner?

3. Does the technology represent a sufficiently significant advance in the state-of-the art that systems planners will find a worthwhile use for the technology even though no requirement is known at present?

4. Does the technology offer important potential advantages over existing alternative technologies without suffering from any decided or overriding disadvantages within the context of a tactical operating environment?

# Is the technology useful for implementing functions existing in the present NTDS or MTDS?

Since the present operational systems have been designed on the basis of earlier analyses of requirements for tactical data systems, future systems will probably require the same types of hardware functions, although alternative technologies may be used where they offer advantages. For example, console displays are an integral part of the present NTDS system; hence, it is very likely that technologies for implementing console displays will be required in future tactical data systems. This type of justification also implies the need for most types of components and devices used in conventional computer systems. For example, implementing a computer or data processing system in accordance with known and foreseeable computer design concepts requires logical circuitry and internal storage.

The four major categories of technologies to be investigated components and packaging techniques, memories, displays, and input/output - were selected on this basis. This has also served as the first criteria in selecting specific technologies to be investigated in each of these categories including:

Components and packaging techniques

Logical circuits for implementing logic in the central

Linear circuits (e.g memory sense amplifiers) Interconnection techniques

processor and in peripheral equipment

Packaging techniques

Memories

Registers and high-speed control memories

Main internal memories

On-line auxiliary storage

Off-line auxiliary storage

Displays

Console displays

Input/output equipment

High speed block serial input

Low speed incremental serial input

Keyboard input

Character printers

Is there some known Navy or Marine Corps operational task for which the new technology offers potential advantages?

- Insent

Some technologies not used in the present NTDS or MTDS may offer advantages in implementing specific functions in future tactical systems. If functions or tasks in Navy and Marine Corps tactical systems can be identified for which a technology offers potential advantages, this is considered sufficient justification for investigation of that technology. Systems planners may or may not decide to use the technology in a future tactical data system, but the technology must be evaluated in order to provide technical information the system planner will need in order to make that decision.

For example, associative memories that permit addressing stored information by content rather than by physical location offer some advantages in track while scan and threat evaluation and weapon assignment operations. A system planner must have information about associative memories in order to decide whether those advantages justify the cost of an associative memory in contrast to alternate approaches such as programming a memory search in a conventional high-speed random access memory.

Hence, if a use for a technology can be identified in which it offers potential advantages to a systems planner, that technology will be investigated in this study.

The systems planner will then have the necessary information to properly evaluate the use of alternate approaches in the design of

a future system. Examples of such technologies and brief reasons for including them in the investigations in this study are:

Associative memories - potentially useful in several functional tasks including track while scan and threat evaluation and weapon assignment.

Read only memories - potentially useful for microprogrammed (stored logic) machine organizations, fixed program storage, and storage of data that is changed relatively infrequently (e.g. screen patterns in multi-ship ASW operations).

Large screen displays - potentially useful for Flag presentations and CIC plots.

Character recognition equipment - potentially useful for reading data initially entering the system in printed form.

Voice recognition and voice output equipment - potentially useful for direct communication with the computer without the need for manual operations such as keypunching.

Graphic input equipment - potentially useful for directly entering graphical information such as flight paths and formation and maneuver patterns.

The selection of technologies in this category assumes that the role of future tactical systems will expand beyond that of anti-air operations (the major function of the present NTDS and MTDS systems) and envisions the possibility of closer integration of tactical data systems with weapons systems and sensor systems in the future and the inclusion of functions such as intelligence data processing. Only by understanding the full range of technologies available can a systems planner adequately

determine the capabilities that can be implemented in a future tactical system and the alternative methods of accomplishing this.

# Does the technology represent a significant advance in the state-ofthe-art that will cause it to be used for functions not presently anticipated?

Some new technologies may be developed that advance the state of the computer art in a major way. If this occurs, it is very likely that designers of future systems will see ways of utilizing the new technology to achieve results that are not possible with present kinds of equipment. If such technologies appear, they should be investigated whether a specific requirement can be foreseen or not. However, none of the technologies investigated so far fall in this category.

Does the technology offer important potential advantages over existing alternative technologies without suffering from any decided or overriding disadvantages within the context of a tactical operating environment? This criteria is superimposed on the first three. Regardless of whether a use exists or is anticipated for a new technology, there is no point in considering it unless there is reason to believe that it may be better than existing well established technologies. For example, evaluating a new storage technology would be a waste of time unless it has some potential advantages over magnetic core memories.

Many technologies have been eliminated from consideration in this study because they did not offer sufficient advantages over better established approaches. Hence, a good deal of judgement has been exercised in limiting the study to those technologies that are useful, applicable to tactical environments, and worthwhile. No attempt has been made to evaluate in detail every different technique or approach.

#### 3.2 COMPONENTS AND PACKAGING

#### 3.2.1 General

For the past five to seven years discrete component semiconductor circuits have dominated the computer data processing field as logic components. A number of alternatives to transistor and diode electronic circuitry have been proposed but none of these have proven superior for the majority of applications. These alternatives include cryogenic logic, fluid logic, all magnetic logic, and optical logic. Cryogenic and optical logic are yet to be proven feasible. Fluid and magnetic logic offer some advantages in slow speed applications, such as the implementation of control functions in input/output equipment. However, semiconductor integrated circuits will be dominant for the foreseeable future - probably for the next ten to fifteen years at least.

Closely related to basic integrated circuit technology are the associated technologies for batch fabrication of interconnections. The two major techniques are vacuum deposition of metallic interconnect patterns through masks and printing of metallic interconnect patterns by processes similar to silk screening in the graphic arts. Batch fabrication is the key to low cost high reliability components and interconnections for both logical circuitry and internal memories. Major improvements in cost and reliability can be achieved by fabricating large arrays of circuits on a single silicon chip and interconnecting these on the chip. In order to minimize the number of interconnections brought from the chip it will be necessary to develop logical design and machine organization techniques that facilitate the organization of the machine into large functional units with a minimum number of interconnections required between these functional units. For example, either an adder or perhaps an entire arithmetic unit may be fabricated on a single large chip with external connections required only for input/output and control signals. Another approach is to fabricate

the unit on several large chips which are then interconnected by wiring deposited on a substrate and packaged as a single unit. This is directly related to the subject of throw-away unit size and maintainability discussed in Section 2.

The remainder of this section will present the status and future plans for the components and packaging portion of this study and then briefly summarize technical developments of importance to future tactical data systems. Most of the component and packaging techniques applicable to future systems were discussed in detail in Volume V of the ANTACCS Final Report. A separate report on component and packaging technology is being prepared that will revise and update the material in Volume V of the ANTACCS Report which is about nine months old at this time. Since that report will discuss these technologies in depth, only changes in the technology or in the anticipated progress of the technology (since the material prepared for the ANTACCS Report) will be presented briefly in the technical discussion in this section. The Final Report will contain material from the special report mentioned above and will present in greater detail the latest developments in this area.

3.2.2 <u>Status to Date and Plans for the Remainder of the Study</u> Particular attention is being given during this study to those component technologies for 1970 era systems that appeared most promising during the 1964 ANTACCS study including:

Monolithic integrated circuits Hybrid monolithic/thin-film integrated circuits Active thin-film integrated circuits MOS integrated circuits

Consideration will also be given to other component technologies whose feasibility or applicability appeared questionable during 1964 if subsequent developments indicate that the status appears to be changing. This category will include:

Optical logic All magnetic logic Fluid logic

However, no such changes have been detected to date.

The following levels of packaging and specific packaging techniques are being investigated:

Multi-circuit chips

Cellular logic

Multi-function logic

Variable interconnections

Fixed interconnections

Multi-chip substrates

Mother board and back board techniques

Printed circuit boards

Multi-layer printed circuit boards

Multi-layer deposited (or printed) wiring

Connectors

Bonding techniques are also being investigated including:

Flip-chips Welding

Soldering

These technologies are being investigated by discussions with technical experts working in these fields, by studying the applicable literature, and by evaluating information concerning the different technologies in relation to the requirements that will be imposed by future Naval tactical systems. This portion of the study is closely related to the part of the study dealing with the effect of new technologies on maintainability. In the evaluation of new technologies, the effect on reliability and maintainability is given major weight. A separate interim report is being prepared that updates the material presented in Volume V of the ANTACCS Report concerning components and packaging technology. That interim report will be further updated at the end of the study for inclusion in the Final Report.

#### 3, 2, 3 Technical Discussion

The investigations during the first half of this study have tended to confirm and support the evaluations, conclusions, and recommendations made during the ANTACCS study in 1964. The belief that future computers will utilize large arrays of interconnected logical circuits performing major logical functions has been greatly strengthened by discussions with semiconductor specialists and by published information. Although there was some controversy about this last year, the major questions now seem to be when this will be feasible (rather than if) and how large the arrays will be. Many technical experts were optimistically predicting these large interconnected arrays last year, but now even the managements of major semiconductor companies are publicly announcing that these will be available. For example, recently Dr. Robert N. Noyce, Group Vice President of Fairchild Camera and Instrument Corporation, addressing the San Diego Council of WEMA stated,

"However, from a point on the complexity scale now where 50 components in the cheapest level for an integrated circuit, I expect to move to 1000 by 1970....At the same time there will be new problems where it takes only 10 chips to make a computer and almost every circuit made will be different."

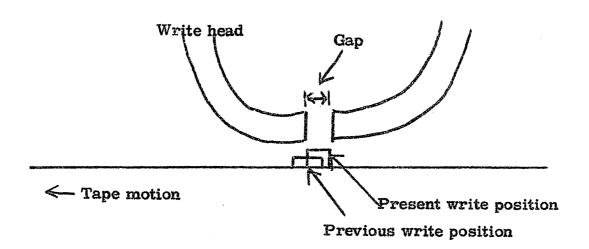

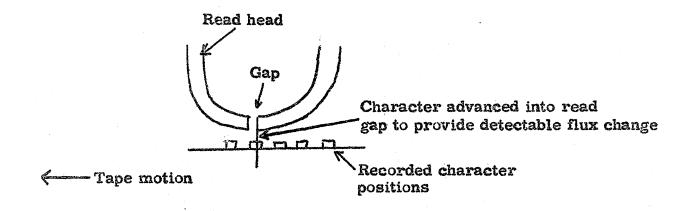

The major controversy now appears to be whether these large arrays will be fabricated primarily with monolithic silicon circuits (using bipolar transistors) or with metal-oxide-semiconductors (MOS). One interesting development since the investigation last year has been the rapid progress of MOS devices. Some in the semiconductor industry believe MOS technology will prove dominant where large arrays are required because of the somewhat simpler processing required. The smaller number of processing steps tends to make more feasible the high yield necessary for large arrays. However, in monolithic circuits is is necessary to control the thickness of the diffusion layer in the semiconductor, while in the MOS it is necessary to control the thickness of the oxide layer. Hence, the problem of process control is transferred from the body of the semiconductor to the surface. Many feel that surface effects will be a more difficult factor to control. Even if the large MOS arrays do prove easier to fabricate and hence cheaper, they will still suffer from one major disadvantage - speed. The MOS is a field-effect type device with more limited speed capability. Although progress in both technologies is expected, it appears likely that MOS devices will remain approximately one order of magnitude slower than monolithic integrated circuits. MOS devices may be utilized in applications where high speed is not required and in applications where very large standardized arrays can be used. Examples of the latter category are large integrated circuit storage arrays for main internal memory. Monolithic integrated circuit storage arrays will be faster, but slower speed MOS devices may be sufficiently cheaper to make their use in larger capacity memories more feasible.