GMX<sup>™</sup> Micro-20 68020 Single-board Computer

Hardware Technical Manual

The information in this document has been carefully checked and is believed to be entirely reliable. However, no responsibility is assumed for inacurracies. Furthermore, GMX Inc. reserves the right to make changes to any products described herein to improve reliability, function, or design. GMX Inc. does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights or the rights of others.

> Copyright 1985, 1986 by GMX Inc. 1337 West 37th Place Chicago, IL 60609 (312) 927-5510 \* TWX 910-221-4055

#### All rights reserved

Reproduction of this manual, in whole or part, by any means, without express written permission from GMX Inc. is strictly prohibited.

GMX<sup>™</sup> and GIMIX<sup>™</sup> are trademarks of GMX Inc. 020Bug<sup>™</sup> is a trademark of Motorola Inc. OS-9<sup>™</sup> is a trademark of Microware Systems Corp and Motorola Inc. OS-9/68000<sup>™</sup> is a trademark of Microware Systems Corp. UniFLEX<sup>™</sup> is a trademark of Technical Systems Consultants

# GMX™ Micro-20 68020 Single-board Computer Hardware Technical Manual

# Revision History

| Revision | Changes                | Date    |

|----------|------------------------|---------|

|          |                        |         |

| A        | First Complete Edition | 9/15/86 |

# GMX<sup>TM</sup> Micro-20 68020 Single-board Computer Hardware Technical Manual

# TABLE OF CONTENTS

| LISTOF                               | FIGURES                                                                                                                                    | vii               |  |  |  |  |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|--|--|

| SPECIFIC                             | SPECIFICATIONS:                                                                                                                            |                   |  |  |  |  |

|                                      | General<br>Jumper Option Summary<br>Connector Summary<br>Status Indicators (LEDs)                                                          | . ×<br>×i<br>×ii  |  |  |  |  |

| INTRODUC                             | CTION x                                                                                                                                    | iii               |  |  |  |  |

| Section                              | 1: 68020 Microprocessor                                                                                                                    |                   |  |  |  |  |

| 1-1:<br>1-2:<br>1-3:<br>1-4:<br>1-5: | General Description<br>Power-up/Hardware Reset Conditions<br>Using The RESET Instruction<br>Restart Vectors<br>Cache Disable Jumper (JA-4) | 1-1<br>1-1<br>1-2 |  |  |  |  |

| Section                              | 2: 68881 Floating-point Coprocessor                                                                                                        |                   |  |  |  |  |

| 2-1:<br>2-2:<br>2-3:<br>2-4:<br>2-5: | General Description<br>Coprocessor Interface<br>Coprocessor-installed Status Bit<br>Adding a Coprocessor<br>Clock Rate                     | 2-1<br>2-1<br>2-1 |  |  |  |  |

| Section                              | 3: RESET SWITCH                                                                                                                            |                   |  |  |  |  |

| 3-1:<br>3-2:                         | General Description<br>Connections (P7)                                                                                                    |                   |  |  |  |  |

| Section                              | 4: SINGLE-STEP/ABORT SWITCH                                                                                                                |                   |  |  |  |  |

| 4-1:<br>4-2:<br>4-3:<br>4-4:<br>4-5: | General Description<br>Connections (P7)<br>Single-step/Abort Option Jumper (JA-5)<br>Abort Mode<br>Single-step Mode                        | 4-1<br>4-2<br>4-2 |  |  |  |  |

| Section                              | 5: REMOTE POWER INDICATOR                                                                                                                  |                   |  |  |  |  |

| 5-1:<br>5-2:                         | General Description<br>Connections (P6)                                                                                                    |                   |  |  |  |  |

| Section                                                     | 6: HALT INDICATORS, ON-BOARD (LED1) AND REMOTE                                                                                                                                                                           |                                      |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 6-1:<br>6-2:                                                | General Description<br>Connections (P6)                                                                                                                                                                                  |                                      |

| Section                                                     | 7: POWER SUPPLY REQUIREMENTS AND CONNECTIONS                                                                                                                                                                             |                                      |

| 7-1:<br>7-2:<br>7-3:                                        | General Description<br>Voltage and Current Requirements<br>Connections (P8)                                                                                                                                              | 7-1                                  |

| Section                                                     | 8: SENSE SWITCH (SW1)                                                                                                                                                                                                    |                                      |

|                                                             | General Description<br>Accessing the Sense Switch                                                                                                                                                                        |                                      |

| Section                                                     | 9: RANDOM ACCESS MEMORY (RAM)                                                                                                                                                                                            |                                      |

| 9-1:<br>9-2:                                                | General Description<br>Access Restrictions                                                                                                                                                                               |                                      |

| Section                                                     | 10: READ-ONLY MEMORY (ROM) SOCKETS                                                                                                                                                                                       | •                                    |

| 10-1:<br>10-2:<br>10-3:<br>10-4:<br>10-5:<br>10-6:<br>10-7: | General Description<br>ROM Types Supported<br>Size Option Jumper (JA-1A)<br>Wait-state Option Jumper (JA-6)<br>Addressing<br>Data Organization<br>Processor Restart Vectors<br>11: SERIAL I/O PORTS                      | 10-1<br>10-1<br>10-2<br>10-3<br>10-3 |

| 11-1:<br>11-2:<br>11-3:<br>11-4:<br>11-5:<br>11-6:          | General Description<br>Accessing the DUART Registers<br>Baud Rate Clock<br>Connections (P2)<br>Powering Serial Adapter Boards<br>Interrupts                                                                              | 11-1<br>11-2<br>11-3<br>11-3         |

| 12-1:<br>12-2:<br>12-3:<br>12-4:<br>12-5:<br>12-6:          | 12: 68230 PARALLEL INTERFACE/TIMER (PI/T)<br>General Description<br>Accessing PI/T Registers<br>Register Addresses<br>Interrupts<br>I/O Pin Functions<br>Programming Considerations<br>13: General Purpose Parallel Port | 12-1<br>12-2<br>12-2<br>12-3         |

| 13-1<br>13-2<br>13-3<br>13-4<br>13-5                        | General Description<br>Connections (P3)<br>Buffer Direction Options (JA-3,7)<br>Interrupts<br>Electrical Characteristics                                                                                                 | 13-1<br>13-2<br>13-2                 |

(Con't)

Software ..... 13-3 13-6: Section 14: Time-of-Day Clock General Description ..... 14-1 14 - 1:14-2: Clock Registers ..... 14-1 14-3: Data and Control Signals ..... 14-1 14-4: Clock Register Access ..... 14-2 14-5: 14-6: Clock Rollover ..... 14-5 Preventing Unintentional Clock Accesses ..... 14-5 14-7: TEST Line ..... 14-6 14-8: 14-9: Battery Jumper (JA-2) ..... 14-6 Section 15: PERIODIC INTERRUPT GENERATOR 15-1: General Description ..... 15-1 15-2: Enabling Periodic Interrupts ...... 15-1 15-3: 15-4: Driving the PI/T Counter/Timer ..... 15-3 Section 16: FLOPPY DISK INTERFACE 16 - 1:General Description ..... 16-1 16-2: Accessing the 1772 FDC ..... 16-1 Control/Status Register Functions ...... 16-1 16-3: 16-4: Floppy Disk Interrupts ..... 16-4 Drive Ready Options (JA-8) ..... 16-5 16-5: 16-6: 16-7: Drive Select ..... 16-6 16-8: Stepping Rates ..... 16-7 16-9: Connections (P4) ..... 16-7 16-10: Drive Termination ..... 16-8 16-10: Status Indicator (LED2) ..... 16-9 Section 17: SASI/SCSI PERIPHERAL INTERFACE General Description ..... 17-1 17-1: Controller Compatibility ..... 17-2 17-2: SASI Status Register (SASR) ..... 17-2 17-3: 17-4: SASI Controller Select Register (SCSR) ..... 17-5 SASI Interrupt Enable Register (SIER) ..... 17-7 17-5: SASI Data Register (SADR) ..... 17-7 17-6: 17-7: Controller Reset ..... 17-8 Interface Timing ..... 17-8 17-8: Interrupts ..... 17-12 17-9: 17-10: Controller Addressing ..... 17-12 17-11: Connections (P5) ..... 17-16 17-12: 17-13: 17-14: Cable Termination ..... 17-17 Section 18: I/O EXPANSION PORT General Description ..... 18-1 18-1:

(Con't)

18-2:

Interface Protocol ..... 18-1

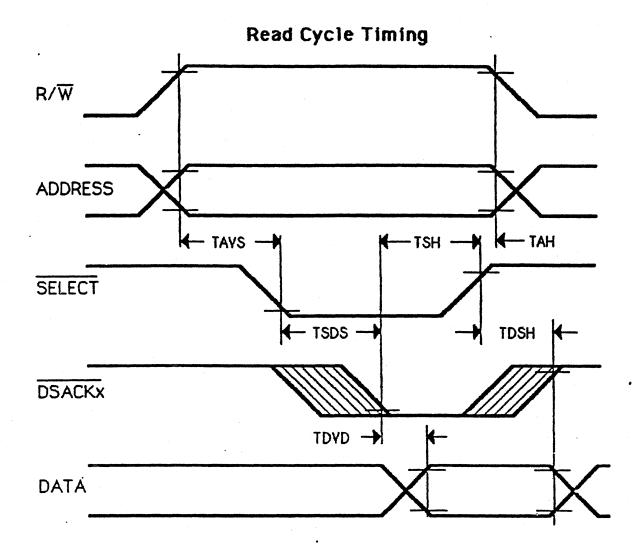

| 18-3:  | Read Cycle Timing               | 18-1  |

|--------|---------------------------------|-------|

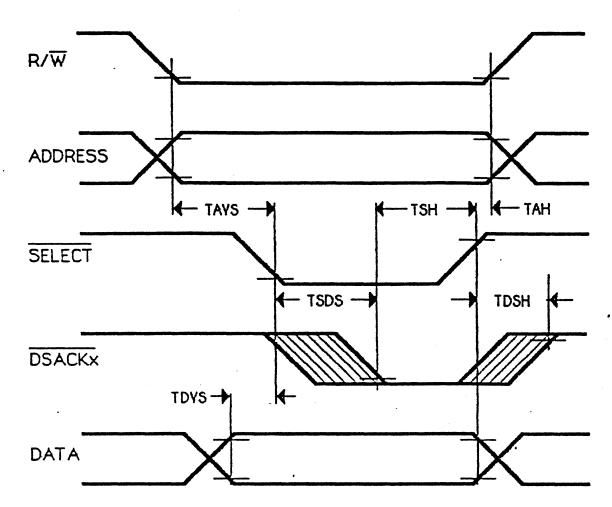

| 18-4:  | Write Cycle Timing              | 18-4  |

| 18-5:  | Data Bus Sizing and Alignment   | 18-4  |

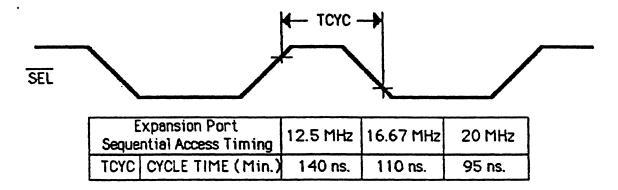

| 18-6:  | Peripheral Response Time        | 18-4  |

| 18-7:  | Signal Descriptions             | 18-5  |

| 18-8:  | Electrical Characteristics      | 18-8  |

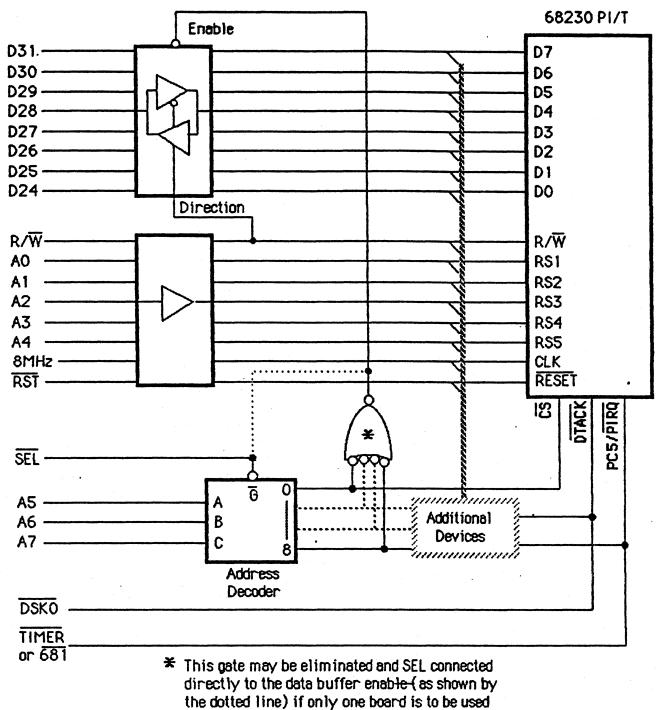

| 18-9:  | Interface Circuit Example       | 18-9  |

| 18-10: | Adding Address Lines            | 18-11 |

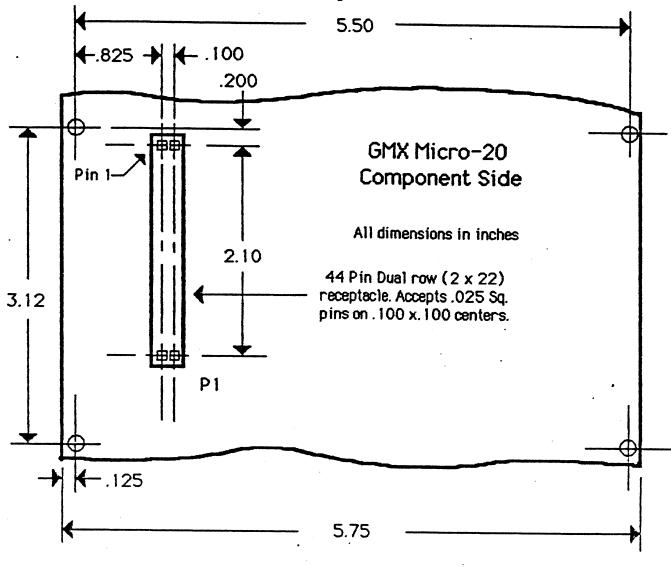

| 18-11: | Connector Pl Mechanical Details | 18-11 |

|        |                                 |       |

# APPENDICIES

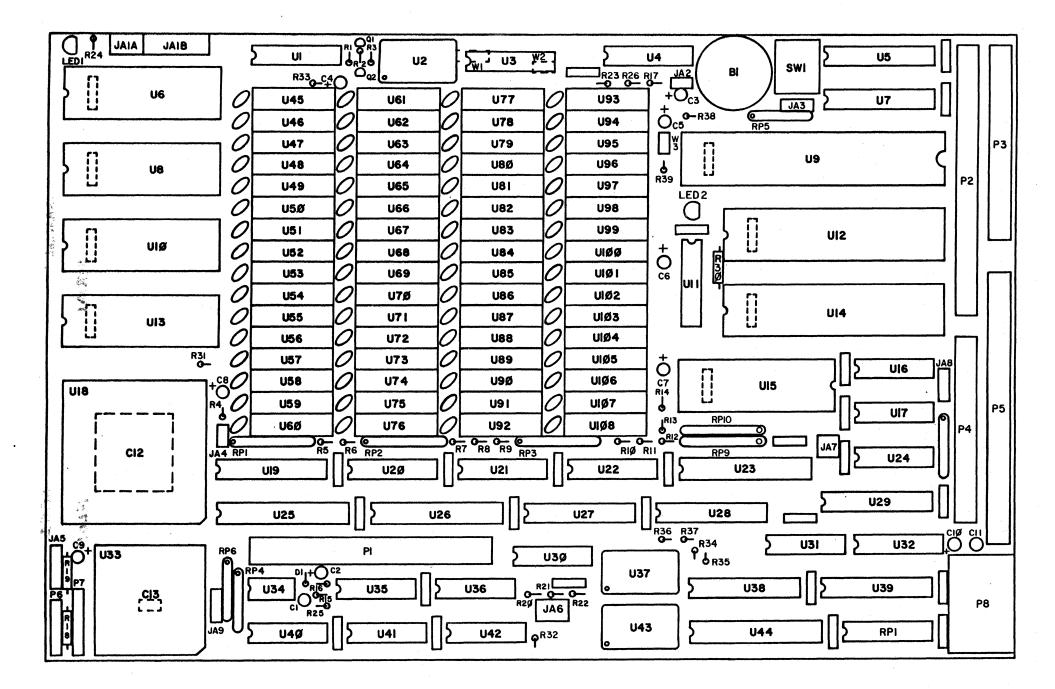

| A:        | Component Layout                 | a-l |

|-----------|----------------------------------|-----|

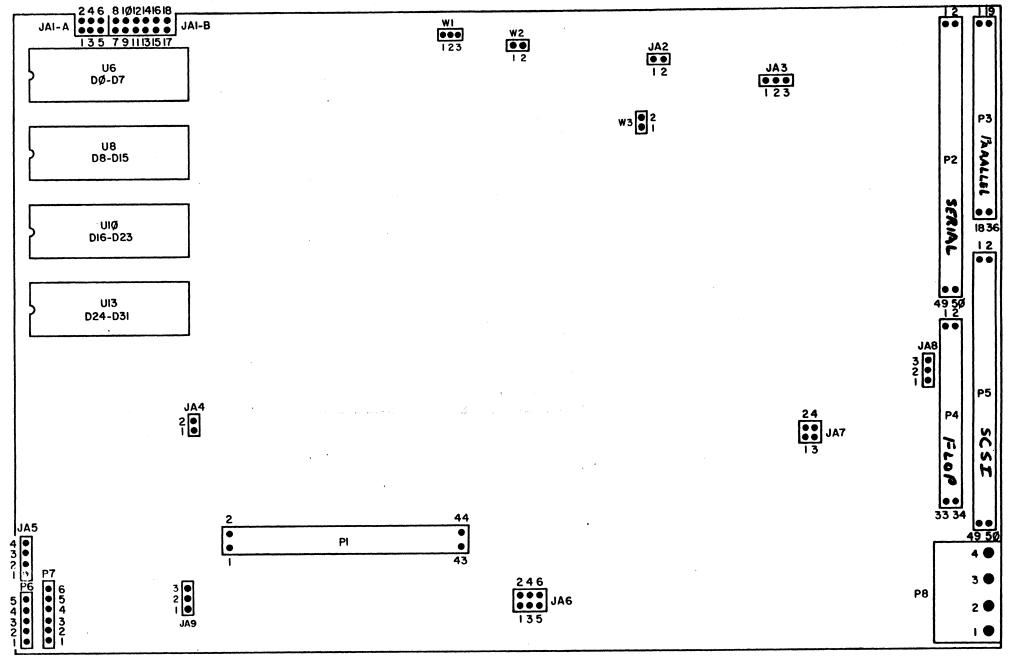

| B:        | Connector and Jumper Locations   | b-1 |

| <b>C:</b> | Memory Map                       | c-1 |

| D:        | Cotrol Register Functions        | d-1 |

| E:        | Interrupt Source Summary         | e-l |

| F:        | Compatible SASI/SCSI Controllers | f-1 |

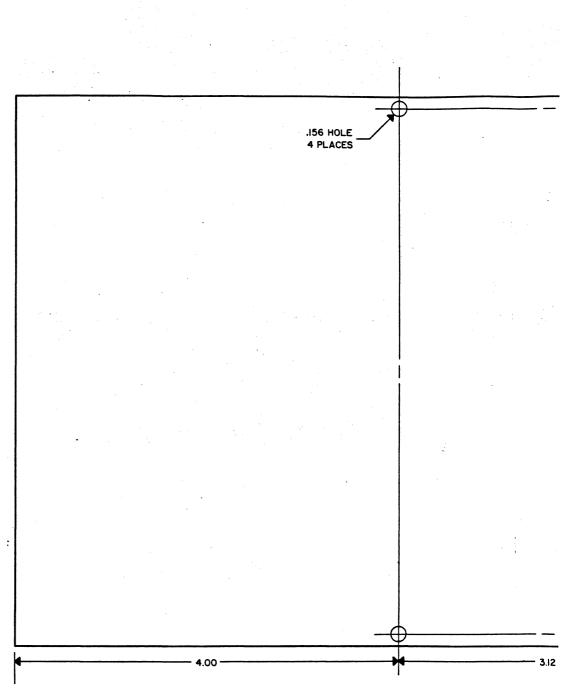

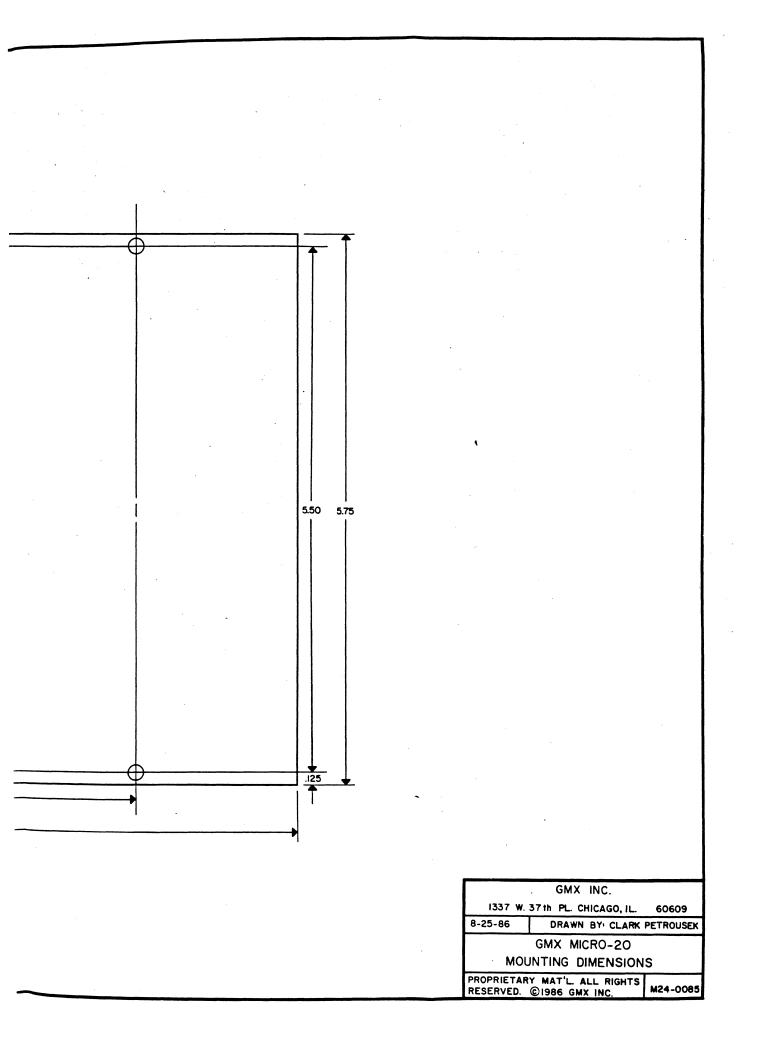

| G:        | Mounting Dimensions              | g-1 |

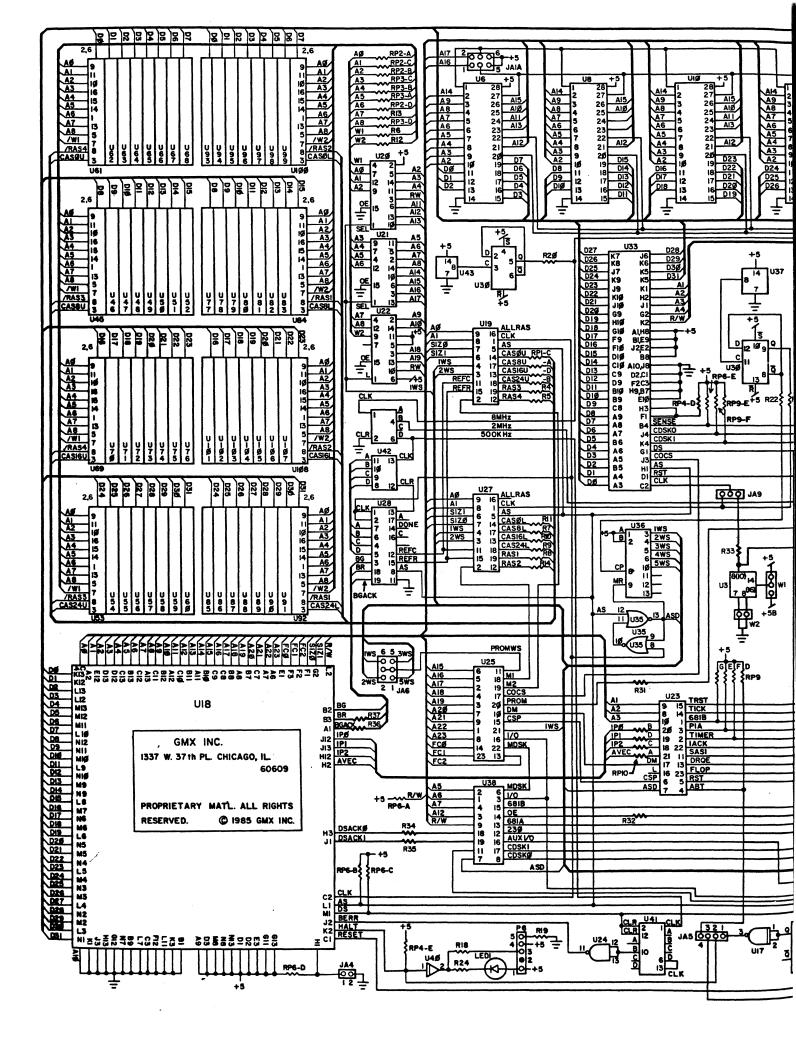

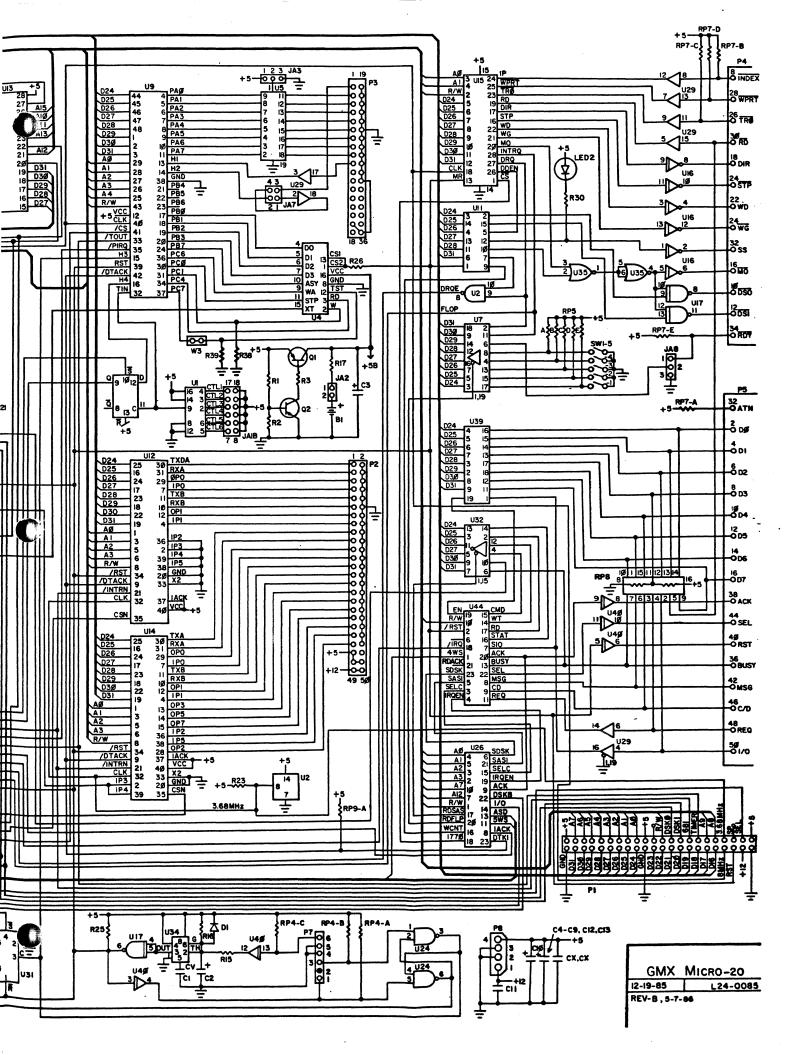

| H:        | Logic Diagram                    | h-l |

# LIST OF FIGURES

|         | Page                                                                                        |  |

|---------|---------------------------------------------------------------------------------------------|--|

| Section | 3: RESET SWITCH                                                                             |  |

| 3-1:    | Reset Switch Connections (P7) 3-1                                                           |  |

| Section | 4: SINGLE-STEP/ABORT SWITCH                                                                 |  |

|         | Single-step/Abort Switch Connections (P7) 4-1<br>Single-step/Abort Option Jumper (JA-5) 4-2 |  |

| Section | 5: REMOTE POWER INDICATOR                                                                   |  |

| 5-1:    | Remote Power Indicator Connections (P6) 5-1                                                 |  |

| Section | 6: HALT INDICATORS, ON-BOARD (LED1) AND REMOTE                                              |  |

| 6-1:    | Remote Halt Indicator Connections (P6) 6-1                                                  |  |

| Section | 7: POWER SUPPLY REQUIREMENTS AND CONNECTIONS                                                |  |

| 7-1:    | Power Connector Pinout (P8) 7-2                                                             |  |

| Section | 10: READ-ONLY MEMORY (ROM) SOCKETS                                                          |  |

|         | ROM Socket Size Options (JA-1A) 10-2<br>ROM Wait-state Options (JA-6) 10-2                  |  |

| Section | 11: SERIAL I/O PORTS, 68681 DUARTS                                                          |  |

| 11-1:   | Serial I/O Connector Pinout (P2) 11-4                                                       |  |

| Section | 13: General Purpose Parallel Port                                                           |  |

|         | Parallel Port Connector (P3) 13-1<br>Parallel Port Buffer Direction Options (JA-3,7). 13-2  |  |

| Section | 15: PERIODIC INTERRUPT GENERATOR                                                            |  |

| 15-1:   | Periodic Interrupt Gen. Rate Options (JA-1B) 15-2                                           |  |

| Section | 16: FLOPPY DISK INTERFACE                                                                   |  |

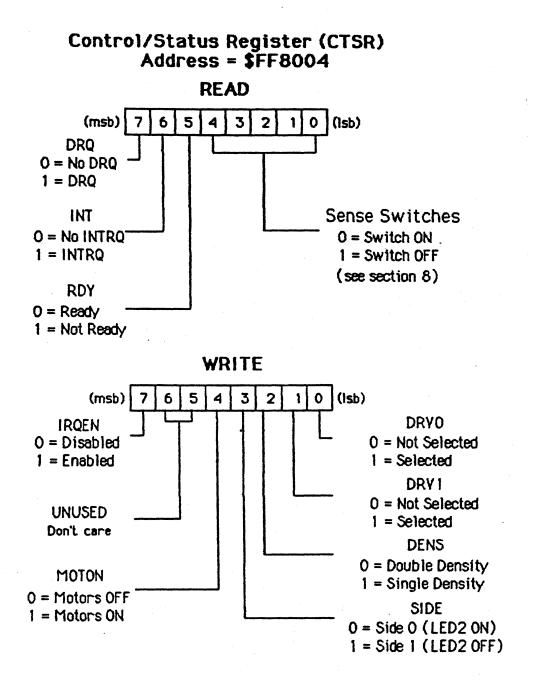

| 16-2:   | Control/Status Register (CTSR)                                                              |  |

(Con't)

16-3: Floppy Disk Interface Connector Pinout (P4) .... 16-8

# Section 17: SASI/SCSI PERIPHERAL INTERFACE

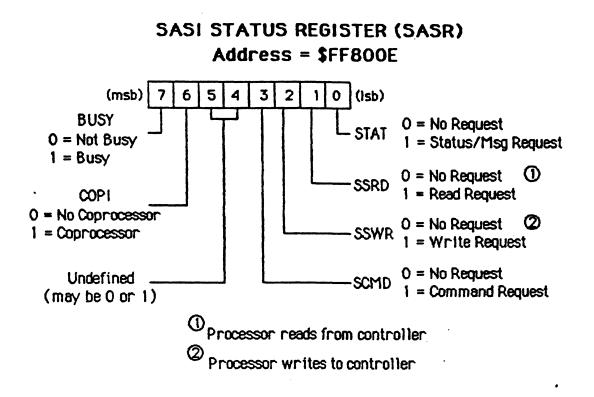

| 17-1: | SASI | Status Register (SASR) 17-3 | 3  |

|-------|------|-----------------------------|----|

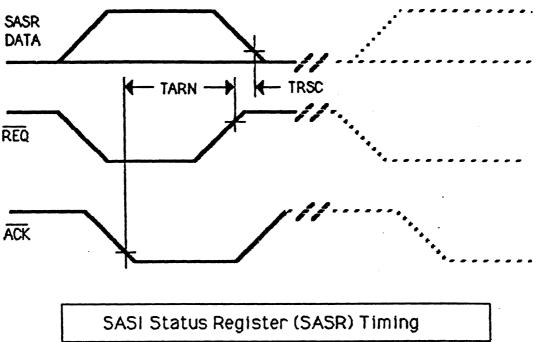

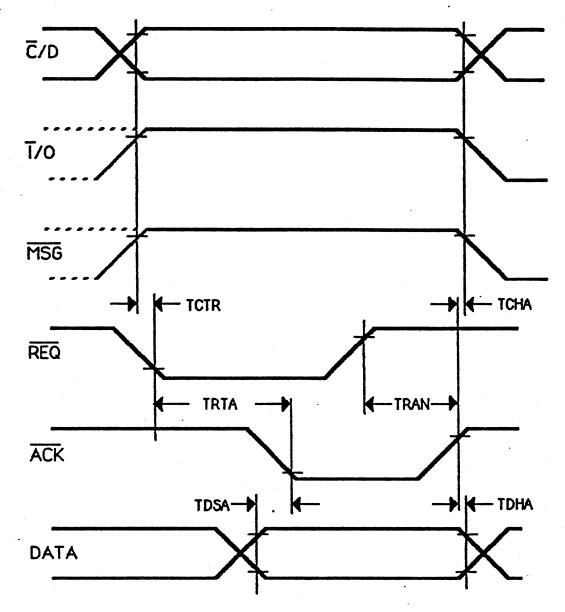

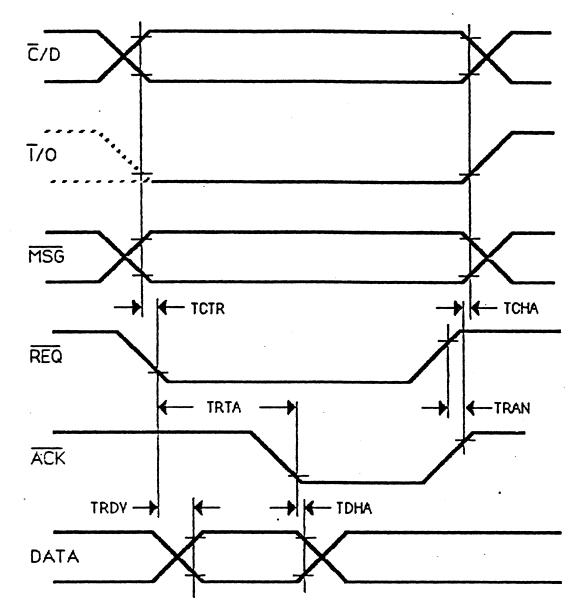

| 17-2: | SASI | Status Register Timing 17-5 | 5  |

| 17-3: | SASI | Select Timing 17-6          | 5  |

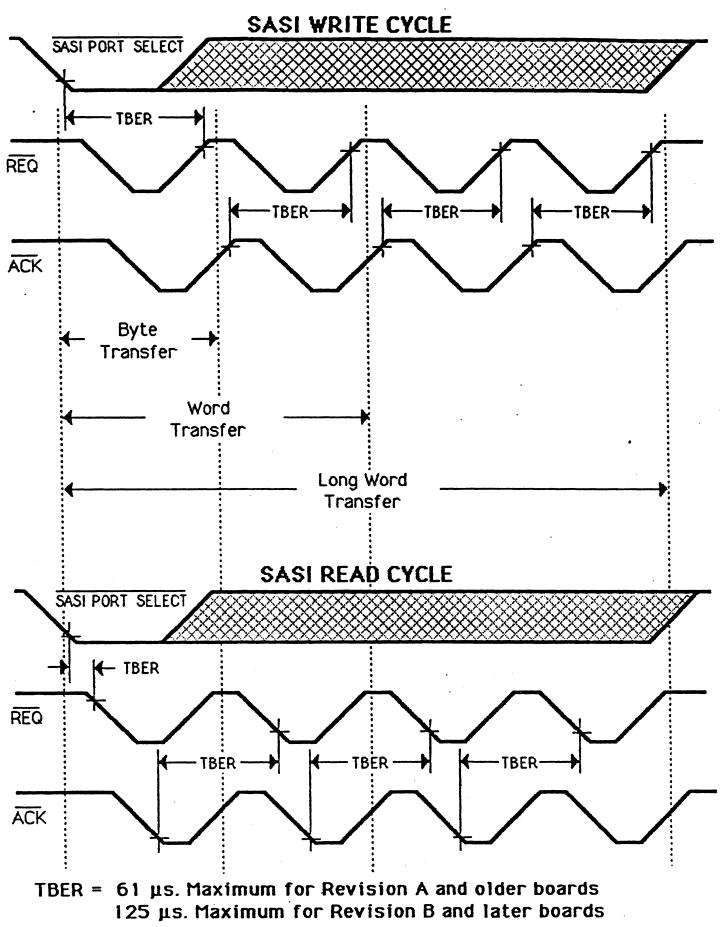

| 17-4: | SASI | Bus Error Timing 17-9       | )  |

| 17-5: | SASI | Write Timing 17-1           | 0  |

| 17-6: | SASI | Read Timing 17-1            | 11 |

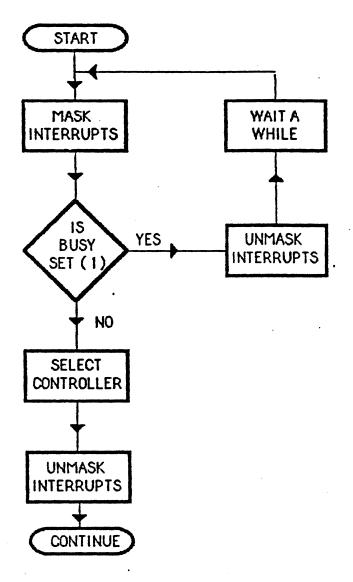

| 17-7: | BUSY | Test Flow Chart 17-1        | 13 |

| 17-8: | SASI | Connector Pinout (P5) 17-1  | 16 |

# Section 18: I/O EXPANSION PORT

| 18-1: | Read Cycle Timing                             | 18-2  |

|-------|-----------------------------------------------|-------|

| 18-2: | Write Cycle Timing                            | 18-3  |

| 18-3: | Sequential Access Timing                      | 18-5  |

| 18-4: | Expansion Connector Pinout (P1)               | 18-5  |

| 18-5: | Interface Circuit Example                     | 18-10 |

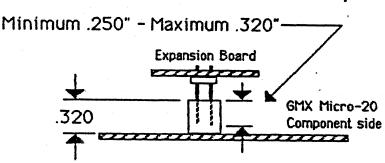

| 18-6: | Expansion Connector Insertion Depth           | 18-12 |

| 18-7: | Expansion Connector & Mounting Hole Locations | 18-13 |

Size: 8.8" x 5.75" x 0.68" (refer to Appendix E for mtg. hole locations)

DC Power Requirements: +5V and +12V DC Regulated (see Section 7 for current requirements)

Microprocessor: 12.5, 16.67, or 20 MHz 68020

Coprocessor: 12.5, 16.67, or 20 MHz 68881 FP Coprocessor (optional)

Random Access Memory: 2 Megabytes of high-speed (1 waitstate) DRAM, organized as 512K 32bit words.

Read-only Memory: Supports up to 256K bytes of ROM, organized as 32-bit words. Accepts four 2764, 27128, 27256, or 27512 EPROMs or equiv.

Serial Ports: Two 68681 DUARTs provide four asyncronous serial ports. Supports 50 to 38.4K baud; 5 to 8 data bits; odd, even, no parity. TTL level I/O is converted to RS-232 etc. by a separate board.

Parallel Interface: 68230 PI/T provides 8-bit parallel input or output port, and controls TOD clock interface, periodic interrupt generator and other misc. functions.

Periodic Interrupt Generates periodic interrupts at a Generator: jumper selectable interval from 10 microseconds to 20 minutes.

Floppy Disk Interface: WD1772 FDC or equiv., handles one or two std. 5 1/4" floppy disk drives.

SASI/SCSI Interface: SASI and SCSI (subset) compatible interface for hard disk and tape controllers, etc.

Time-of-Day Clock: RTC58321 or equiv. TOD clock with full clock/calendar functions and battery backup.

I/O Expansion Port: 16-bit data bus, 1K to 4K address space, two interrupt levels, and control signals for I/O expansion.

# Jumper Options Summary

| Jumper | Description                     | Page(s)   |

|--------|---------------------------------|-----------|

| JA-1A  | ROM Size Select                 | 10-2      |

| JA-IB  | Periodic Interrupt Gen. Rate Se | lect 15-2 |

| JA-2   | Battery Disconnect              | 14-6      |

| JA-3   | Parallel Port Data Direction    | 13-2      |

| JA-4   | 68020 Cache Disable             | 1-2       |

| JA-5   | Single-step/Abort Option        | 4-2       |

| JA-6   | ROM Wait-state Select           | 10-2      |

| JA-7   | Parallel Port Handshake Directi | on 13-2   |

| JA-8   | Floppy Disk Ready Option        | 16-2      |

| JA-9   | 68881 Coprocessor Clock Option  | 2-1       |

| Wl     | Spare IC (U3) VCC Select        | h-1       |

| W2     | Spare IC (U3) GND Options       | h-l       |

| W3     | TOD Clock TEST Disable          | h-1       |

x

| Connec | tor Description                                                                                                                                            | Page(s)          |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| P1     | I/O Expansion Connector, 44-pin dual-row<br>socket for .025" sq. pins on .1" centers.<br>Mates with: Samtec #SSQ-122-04-G-D, or eq.                        | 18-5             |

| P2     | Serial I/O Connector, 50-pin dual-row<br>header w/.025" Sq. pins on .1" centers.<br>Mates with: T&B Ansley #609-5030, or eq.                               | 11-4             |

| P3     | Parallel I/O Connector, 36-pin dual-row<br>header w/.025" sq. pins on .1" centers.<br>Mates with: T&B Ansley #609-3630, or eq.                             | 13-1             |

| · P4   | Floppy Disk Interface, 34-pin dual-row<br>header w/.025" sq. pins on .1" centers.<br>Mates with: T&B Ansley #609-3430, or eq.                              | 16-8             |

| P5     | SASI/SCSI Interface, 50-pin dual-row<br>header w/.025" sq. pins on .1" centers.<br>Mates with: T&B Ansley #609-5030, or eq.                                | 17–16            |

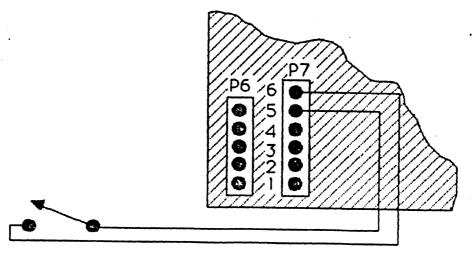

| P6     | Front panel indicators, 5-pin single-row<br>header w/.025" sq. pins on .l" centers.<br>Mates with: Molex #22-01-2051 using<br>#08-50-0114 contacts, or eq. | 5-1, 6- <u>1</u> |

| P7     | Front panel switches, 6-pin single-row<br>header w/.025" sq. pins on .1" centers.<br>Mates with: Molex #22-01-2061 using<br>#08-50-0114 contacts, or eq.   | 3-1, 4-1         |

| P8     | DC power connector, 4-pin 90 deg. header<br>Mates with: AMP #1-480424-0 using<br>#60617-1 contacts, or eq.                                                 | 7-2              |

xi

# On-Board Status Indicators

| Indicato                                                                                                                                                                                                                                        | Description                                                                                                                                         | Page(s)  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| LED1                                                                                                                                                                                                                                            | Processor HALT Indicator, lights when the<br>processor halts due to a double bus fault<br>or when processor is halted by the Single<br>step option. |          |  |

| LED2 Software Diagnostic indicator, flashes coded 16-8<br>fault messages if 020Bug power-up tests fail.<br>Also indicates state of floppy disk side<br>select line during normal operation. Refer<br>to the 020Bug User's manual for more info. |                                                                                                                                                     |          |  |

| Opt                                                                                                                                                                                                                                             | cional (user-supplied) Off-Board Status Ind                                                                                                         | dicators |  |

| Indicato                                                                                                                                                                                                                                        | Description                                                                                                                                         | Page(s)  |  |

| HALT                                                                                                                                                                                                                                            | An LED connected to P6 duplicates the function of LED1.                                                                                             | 6-1      |  |

| POWER                                                                                                                                                                                                                                           | An LED connected to P6 lights when +5V is applied to the board.                                                                                     | 5-1      |  |

This manual contains detailed information on the hardware features of the GMX Micro-20 68020 Single-Board Computer. It is primarily intended for those who are designing custom hardware to interface to the board, and for those who must write programs that directly access the on-board hardware.

For those using the board with the GMX Micro-20 Support ROM firmware or one of the optional disk operating systems, information on basic hardware setup can be found in the 'GMX Micro-20 Hardware Setup Manual', and in the software documentation.

Since the GMX Micro-20 can be ordered in several configurations, some of the information in this manual may not apply to a particular board. For example, not all boards include the 68881 Floating-point Coprocessor, and the information in section 2 does not apply.

The Micro-20 can be orderded configured for one of several processor speeds. Generally, processor speed is not significant except in terms of overall performance. However, certain parameters are clock speed dependent and, where necessary, information for each available speed is given in this manual. The processor speed of a given board can be determined by dividing the frequency of the master clock oscillator (U37) in half. For example, a clock oscillator frequency of 25 MHz, indicates a 12.5 MHz processor speed.

Some of the information in this manual only applies to a particular revision or revisions of the GMX Micro-20 printed circuit board. The revision level of a particular board is indicated by a single letter following the part number etched on the solder side of the PC board. For example, part number #24-0085B indicates a "B" revision board. Revision letters are assigned in alphabetical order, so that a revision "B" board is "newer" or "later" that a revision "A" board and "older" or "earlier" than a revision "C" board.

Every effort is made to maintain compatibility between various versions of the GMX Micro-20. Generally, hardware or software designed to work on older versions of the board will work with newer versions; however, the reverse may not be true. If it is necessary to maintain compatibility with older versions (e.g. an installed system base), the specifications for the older boards should be used whenever possible.

If you have any questions or comments concerning the GMX Micro-20, the documentation, or any other GMX product, please let us know.

#### \*\*\*\*\*\*\*\*\* CAUTION \*\*\*\*\*\*\*\*\*

The GMX Micro-20 includes a battery which provides backup capability for the on-board Time-of-Day clock. Because of this, parts of the circuitry are powered at all times, even when the external power source is disconnected.

Use caution when handling the board, to prevent short circuits

which can damage the board and components. NEVER place the GMX Micro-20 on a conductive surface, such as a metal table top, and NEVER wrap the board in metal foil for static protection. Use only high-resistance anti-static materials such as conductive plastic or cloth to protect the board from static discharge.

To minimize (but not eliminate) the possibility of damage from short circuits, remove battery jumper JA-2 when handling or servicing the board. Further information can be found in section 14 of this manual.

\*\*\*\*\*

This section provides specific information on the GMX Micro-20 implementation of the 68020 microprocessor. For complete information on the characteristics of the processor, refer to the 'MC68020 32-Bit Microprocesor User's Manual', Motorola publication number MC68020UM/AD.

### 1-2: Power-up/Hardware Reset Conditions

When power is first applied to the GMX Micro-20, on-board logic keeps the processor's RESET line asserted long enough for the power supplies and on-board logic to stabilize. After this initial power-up delay, RESET is deasserted an the processor begins normal operation. The processor and on-board logic can also be reset manually by a reset switch or by an external device connected to the I/O Expansion Port (refer to sections 3 and 18 of this manual for further information). These three forms of reset are called 'hardware resets'.

All hardware resets have essentially the same effect. The processor, coprocessor, serial ports (68681 DUARTs), parallel port (68230 PI/T), floppy disk controller (1772 FDC), and SASI interface are all reset as described in the device documentation and/or the appropriate sections of this manual. Any devices connected to the reset outputs from the SASI interface and the I/O Expansion Port are also reset. The contents of the on-board RAM, which is undefined on power-up, is unaffected by other forms of reset. Reset also causes the on-board ROMS to be mapped into low memory, as described in section 1-4.

# 1-3: Using the RESET Instruction

A 'software reset' is a reset caused when the processor executes the RESET instruction. The effects of a software reset are identical to those of a hardware reset, except that the processor itself is not reset. Instead of fetching the restart vectors and beginning execution at the restart address, the processor simply continues execution at the next instruction.

The on-board logic can not tell the difference between a software and a hardware reset, so both cause the ROMs to be mapped into low memory as described in section 1-4. This restricts the use of the processors RESET instruction to programs located in ROM.

The RESET instruction can NOT be executed from RAM. If used, the RESET instruction must be located in the ROMs. Immediately following the RESET instruction, a read of address \$00000004 must be performed. This read restores normal memory mapping by simulating the vector fetch that occurs after a hardware reset. The data read is the restart vector from ROM address \$00800004. Once this read is performed, normal operation can resume.

If it is necessary for programs in RAM to reset the system, a

1-1

subroutine to perform a reset can be placed in the ROMs. Any program that needs to reset the system can then do so by calling the ROM subroutine. The subroutine need only include the RESET instruction, followed by a read of address \$00000004 and an RTS instruction.

# 1-4: Restart Vectors

After a hardware reset, the processor expects the first two entries in the vector table (vector number zero, address \$0000000 and vector number one, address \$0000004) to contain initial values for the Interrupt Stack Pointer (ISP) and program counter (PC). Since these addresses are normally occupied by RAM on the GMX Micro-20, a reset causes the ROMs to appear temporarily in both their own address space and in low memory, overlaying the RAM. This dual mapping allows the processor to read the initial ISP and PC from the first two locations in the ROMs (\$00800000 and \$00800004). Normal mapping is restored as soon as the processor finishes reading the second vector. Refer to section 10 for further information.

# 1-5: Cache Disable Jumper (JA-4)

The 68020 has an input that disables its internal instruction cache, regardless of the state of the cache enable bit in the Cache Control Register (CACR). For normal cache operation, Cache Disable Option Jumper JA-4 must be open (no jumper). If a jumper is connected between the pins of JA-4, cache operation is inhibited.

This section provides information on the GMX Micro-20 implementation of the 68881 Floating-point Coprocessor. For complete information on the characteristics of the coprocessor, refer to the 'MC68881 Floating-point Coprocessor User's Manual', Motorola publication number MC68881UM/AD.

## 2-2: Coprocessor Interface

The coprocessor interface on the GMX Micro-20 is a full implementation of the M68000 family coprocessor interface defined by Motorola. Coprocessor instructions are coded in-line with 68020 instructions and the coprocessor registers are accessed as though they were part of the 68020 register set. The coprocessor is configured for coprocessor identification code (Cp-ID) 001, which is the recommended ID for the 68881. Software provided by GMX uses Cp-ID 001 by default when generating coprocessor instructions.

# 2-3: Coprocessor-installed Status Bit

A bit in the SASI Status Register (SASR) allows programs to determine whether or not a coprocessor is installed on the board. This bit simply indicates that there is a coprocessor in the socket, it is not used during normal coprocessor operations.

If there is no coprocessor installed, bit 6 of the SASR (address \$00FF800E) will be clear (0). If a coprocessor is installed, SASR bit 6 will be set (1). For further information on the SASR refer to section 17.

## 2-4: Adding a Coprocessor

In order to add a 68881 coprocessor to a board originally purchased without one, it may be necessary to change the Programmable Logic Device (PLD) that, among other functions, controls the coprocessor address decoding. Different versions of this PLD (U-25) are used, depending on whether or not the board has a coprocessor and on the memory configuration needed. For further information on adding a coprocessor, please contact the factory.

# 2-5: Clock Rate

Normally, the processor and coprocessor operate at the same basic clock rate. However, due to cost and/or parts availability, it may be necessary or desirable to operate the two at different clock rates.

Revision 'B' and later boards (the revision letter is appended to the part number etched on the solder side of the circuit board, e.g. 24-0085B) allow the use of an additional clock oscillator to provide a separate clock for the coprocessor. Jumper area JA-9 is used to select one of two sources for the coprocessor's clock. If JA-9 pins 1 and 2 are jumpered, the processor and coprocessor operate from the same clock. The clock rate is one-half of the master clock oscillator (U-37) frequency (e.g. for a 12.5 MHz processor/coprocessor, the oscillator frequency is 25 MHz).

If  $\cdot$  JA-9 pins 2 and 3 are jumpered, a separate clock oscillator, installed at location U-3, provides the coprocessor clock. The coprocessor clock oscillator frequency must equal the desired coprocessor clock rate and its output must have a 50% duty cycle. (e.g. a 12.5 MHz oscillator for a 12.5 MHz coprocessor).

Connector P7 is used to connect a user-supplied reset switch to the GMX Micro-20. The reset switch provides a manual means of resetting the processor and other hardware to a known state, without removing power from the board. When the switch is activated, the processors RESET input is asserted causing the processor to begin reset exception processing. It also resets the on-board logic and peripherals, devices connected to the SASI interface, and devices connected to the I/O Expansion Port RST line.

A monostable circuit on the board provides contact debouncing for the switch and insures that the duration of the reset signal is sufficient to be recognized by the processor.

There are three other ways in which the system can be reset. An external device connected to the I/O expansion port can drive the expansion port's RST line (refer to section 18), the processor can reset the system by executing the RESET instruction (refer to section 1), or the power can be turned off.

Almost any switch with one set of normally open contacts capable of handling logic-level signals can be used as a reset switch. RESET is asserted when the switch is closed, and deasserted approximately 500 milliseconds after the switch is opened.

# 3-2: Connections (P7)

Figure 3-1 shows the connections between P7 and the reset switch. Refer to the connector summary in the 'SPECIFICATIONS' section at the beginning of this manual for information on mating connectors.

# Reset Switch Connections (P7)

RESET SWITCH (SPST N.O. MOMENTARY)

Figure 3-1

3-1

A Single-step/Abort (SS/ABT) switch can be implemented by connecting a user-supplied momentary action switch to the appropriate terminals of connector P7. This switch serves one of two functions, depending on the configuration selected by jumper area JA-5.

When JA-5 is set for the abort mode, activation of the SS/ABT switch will cause a level 7 (non-maskable) autovectored interrupt to the 68020. This interrupt is commonly used by monitor and debugger software to stop program execution.

When JA-5 is set for the single-step mode, the processors HALT line is asserted, causing all processing to stop. Each time the SS/ABT switch is activated, the halt is released until the processor completes its next bus cycle. This mode can be used for low-level hardware debugging.

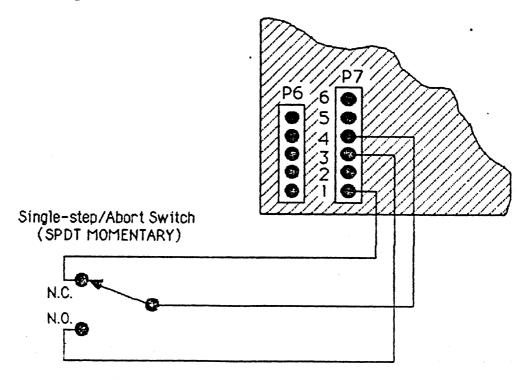

### 4-2: Connections (P7)

The Single-step/Abort switch must be a single-pole, double-throw switch capable of switching logic-level signals. Figure 4-1 shows the connections between the switch and connector P7. Refer to the connector summary in the 'SPECIFICATIONS' section at the beginning of this manual for information on mating connectors.

# Single-step/Abort Switch Connections (P7)

Figure 4-1

4-1

Jumper area JA-5 is used to configure the SS/ABT switch for either the single-step or the abort mode. Figure 4-2 shows the configuration of JA-5 for both modes.

# JA-5 Single-step/Abort Option Jumper

Abort Mode

Single-step Mode

# Figure 4-2

#### 4-4: Abort Mode

In this mode, activation of the SS/ABT switch causes a level 7 (non-maskable) interrupt to the processor. The only other device on the GMX Micro-20 capable of generating a level 7 interrupt is the floppy disk controller.

When a level 7 interrupt occurs, the interrupt handler can determine its source from the current status of the DRQ bit and the last value written to the IRQEN bit in the Control/Status Register (CTSR) at address \$00FF8004. These two bits share the same location (bit 7) in the register. Reading the CTSR returns the DRQ status and writing controls the IRQEN status. Since the state of the IRQEN bit can not be read directly by the processor, a copy of the last value written to the CTSR or a flag to indicate its current state must be available to the interrupt handler.

If DRQ interrupts are enabled (IRQEN = 1) and the DRQ bit is set (1), the interrupt was caused by the floppy disk controller. Otherwise, the interrupt was caused by the SS/ABT switch. For more information on floppy disk interrupts refer to the 'FLOPPY DISK CONTOLLER' section of this manual.

When an interrupt from the SS/ABT switch occurs, it is necessary to insure that only one interrupt is recognized for each activation of the switch. The interrupt condition is maintained as long as the SS/ABT switch is activated. When the processor services the interrupt it raises its interrupt mask level, precluding further interrupts. However, if the switch is still activated when the mask level is lowered, another level 7 interrupt will be recognized by the 68020.

To insure that only one interrupt is recognized each time the switch is activated, the interrupt handler must wait for the switch to be released before taking any action that lowers the interrupt mask level (e.g. executing an RTE or MOVE to SR instruction).

The H3 handshake line of the 68230 PI/T indicates the state of the SS/ABT switch. H3 will be low (0) when the switch is in its normal inactive position, and high (1) when the switch is activated. The state of H3 can be read directly as bit 6 of the PI/T Port Status Register (PSR) at address \$00FF90CD. Refer to section 12 for further information on the PI/T.

# 4-5: Single-step Mode

When the SS/ABT switch is configured for the single-step mode, the processor is normally halted (HALT line asserted) and no processing occurs. Each activation of the SS/ABT switch causes the processor to run to the end of the next bus cycle and then halt again.

In single-step mode, the processor halts at the completion of each bus cycle external to the processor, not necessarily at the completion of an instruction. Each 'step' may encompass more than one instruction, if the instructions do not require external bus cycles, or only a portion of an instruction if it causes multiple bus cycles. For example, a program in the processor's on-chip cache that does not generate external accesses can not be single-stepped using this method.

The single-step mode is useful for debugging very low-level hardware problems when even the simplest software routines fail to execute properly. By single-stepping while directly examining the processors address and control signals with an oscilloscope or logic analyzer, the actions of the processor can be traced.

When the single-step mode is selected, the halt indicators (LED1 and the optional remote halt LED) will light, indicating that HALT is asserted. Although HALT is released each time the SS/ABT switch is activated, the LEDs will appear to remain lit because HALT is only released for a short time.

I.

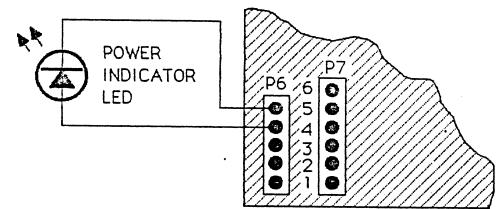

# 5-1: General Description

Connector P6 provides a way to connect a user-supplied, remotely mounted power-on indicator to the GMX Micro-20. The indicator can be almost any standard 1.2 Volt Light Emitting Diode (LED). The LED is connected across the +5V supply through a resistor on the GMX Micro-20, and simply indicates that power is being supplied to the board.

## 5-2: Connections (P6)

An on-board current limiting resistor (R19) between pin 5 of connector P6 and ground provides current limiting for the power indicator LED. The board is supplied with a 270 ohm resistor at R19, providing approximately 14 milliamps to the LED.

Figure 5-1 shows the connections between P6 and the power indicator LED. Refer to the connector summary in the 'SPECIFICATIONS' section at the beginning of this manual for information on mating connectors.

# Remote Power Indicator Connections (P6)

## Figure 5-1

## SECTION 6: HALT INDICATORS, ON-BOARD AND REMOTE

## 6-1: General Description

LED1 on the GMX Micro-20 provides an indication that the processor has halted. A second LED (user-supplied), which duplicates the function of LED1, can be wired to connector P6 and mounted in a convenient, easily visible location. The remote indicator can be almost any standard 1.2 Volt LED.

The halt indicator(s) are driven by the processor's HALT line. HALT is a bi-directional signal that is driven low by the processor to indicate that a double bus fault has occurred. HALT can also be driven by the on-board logic, providing the hardware single-stepping capability described section 4.

When the Single-step/Abort Option Jumper is set for the Abort mode, the halt indicator(s) will light if the processor halts due to a double bus fault. When the jumper is set for the Single-step mode, the halt indicator(s) appear to light continuously, although they actually turn off briefly each time the Single-step/Abort Switch is activated.

# 6-2: Connections (P6)

Both the on-board (LED1) and remote halt indicators are driven by one section of an open-collector TTL buffer (U-7, 7407), with separate current limiting resistors for each LED. A 270 ohm resistor is normally supplied at R18, providing approximately 14 milliamps to the remote LED.

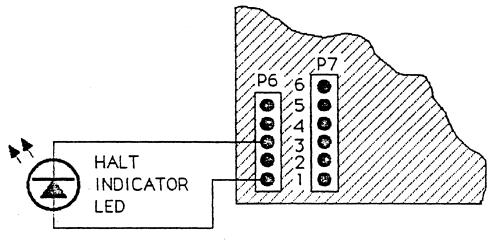

Figure 6-1 shows the connections between P6 and the remote halt indicator LED. Refer to the connector summary in the 'SPECIFICATIONS' section at the beginning of this manual for information on mating connectors.

# Remote Halt Indicator Connections (P6)

Figure 6-1

6-1

Power for the GMX Micro-20, the Serial I/O Adapter board, and most I/O expansion boards is supplied through power supply connector P8. Two supply voltages are normally required: +5 Volts for the logic and +12 Volts. The GMX Micro-20 itself does not use the +12 Volt supply; however, +12 Volts is required by some serial adapter and I/O expansion boards that derive their power from the GMX Micro-20.

#### 7-2: Voltage and Current Requirements

The GMX Micro-20 requires a well filtered and regulated +5 Volt (+/-5) D.C. supply (measured at connector P8). Refer to the serial adapter and I/O expansion board documentation for information on +12 Volt supply requirements.

The power supply current requirements vary, depending on the processor speed and whether or not a coprocessor is installed. Current requirements also depend on the serial adapter board used and on the number and type of I/O expansion boards installed. When calculating the total power supply current, the current requirements of the serial adapter board and any I/O expansion boards powered by the GMX Micro-20 must be added to the figures in the following table.

| Process<br>Speed |        |                   | 5 Volt Supply C<br>pical M | urrent<br>aximum |

|------------------|--------|-------------------|----------------------------|------------------|

| 12.5 M           | <br>Hz | NO 3              | .4 A ·                     | 4.1 A            |

| 12.5 M           | Hz     | YES 3             | .6 A                       | 4.3 A            |

| 16.67 M          | Hz     | NO <sup>·</sup> 3 | .6 A                       | 4.3 A            |

| 16.67 M          | Hz     | YES 3             | .8 A                       | 4.5 A            |

| 20 M             | Hz     | NO 3              | .8 A                       | 4.5 A            |

| 20 M             | Hz     | YES 4             | .0 A                       | 4.7 A            |

GMX Micro-20 Basic Power Supply Current

Note: The GMX Micro-20 does not directly use +12 Volts. The +12 Volt requirements depend entirely on the board(s) connected to the I/O expansion and serial I/O connectors (Pl and P2).

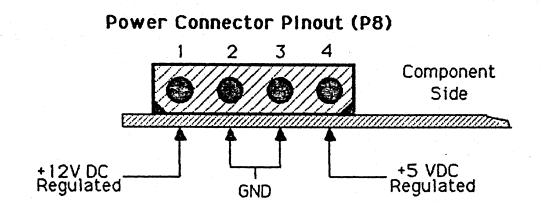

### 7-3: Connections (P8)

Connector P8 is physically and electrically the same as the power connector used on most standard 5 1/4" disk drives. Figure 7-1 shows the pinout of power supply connector P8. For information on mating connectors, refer to the 'SPECIFICATIONS' section at the beginning of this manual.

# \*\*\*\*\*\*\*\*\* CAUTION \*\*\*\*\*\*\*\*\*

Be sure that the power supply connector is wired properly and that the voltages are correct before applying power to the board! Incorrect polarity and/or supply voltages will cause extensive damage to the board and components!

\*\*\*\*\*

The Sense switch (SW1) is a 5-position DIP-switch that can be 'read' by the processor to determine the state of each of the 5 switches. Most of the software supplied by GMX uses the Sense switch at some point to control software options. For example, the 020Bug<sup>m</sup> Debugging Package reads switch #1 (SW1-1) to determine whether to enter the debugger on power-up/reset or to jump directly to a location in ROM where an operating system bootstrap loader or user program is located.

Two of the switches, SW1-1 and SW1-2, are dedicated to the 020Bug package and their function can not be user defined if 020Bug is retained. (SW1-1 can, however, cause a user program in ROM to be executed on power-up/reset.)

The remaining three switches (SW1-3,4, and 5) are used by the optional disk operating systems to select operating modes and to configure them for specific hardware options. Their function can not be user defined when one of these operating systems is used. For information on specific switch functions, refer to the software documentation.

#### 8-2: Accessing the Sense Switch

The Sense switch is accessed by reading the on-board Control/Status Register (CTSR) at address \$00FF8004. The CTSR is a read/write register that is also used by the floppy disk interface.

The most-significant three bits (b5 - b7) of the CTSR are used by the floppy disk interface and should be ignored when reading the sense switch. The least-significant five bits in the CTSR represent the state of the five sense switches. These bits are set (1) when the corresponding switch is ON (CLOSED) and clear (0) when it is OFF (OPEN). The following table shows the relationship between the CTSR bits and the Sense switches.

## CTSR Sense Switch Bits

| SW1-X | CTSR bit |                 |

|-------|----------|-----------------|

| 1     | <br>ъ0   | 0 = ON (CLOSED) |

| 2     | bl       |                 |

| 3     | b2       | 1 = OFF (OPEN)  |

| 4     | b3       |                 |

| 5     | b4       |                 |

The on-board RAM consists of 2 Megabytes (2,097,152 bytes) of high-speed dynamic memory, organized as 512K (524,288) 32-bit long words. The processors ability to perform unaligned bus transfers allows the RAM to be accessed without regard to data alignment. For example, word and long word transfers can be made to any byte, word, or long word address. The only restriction on alignment is that instructions must be aligned on word address boundaries.

Although the processor supports unaligned data transfers, such transfers may require multiple bus cycles and can have an adverse effect on performance. For maximum performance, data alignment (i.e. word accesses on word boundaries and long words on long word boundaries) should be maintained whenever possible.

Only one wait-state is added to each bus cycle that accesses the RAM. The RAM is refreshed continuously in a manner that is essentially transparent the user. Two 'CAS-before-RAS' refresh cycles are performed every 30 microseconds, regardless of the processor clock rate.

On power-up reset, the contents of the RAM are undefined. However, once powered up, data in the RAM is not affected by reset or halt conditions. All data in the RAM is lost when power is removed from the board.

# 9-2: Access Restrictions

Depending on the board configuration ordered, access to the RAM may or may not be restricted with respect to the processor's supervisor and user states.

Most boards, including those supplied with the OS-9/68000™ Operating System and those supplied without an operating system, impose no restrictions on RAM accesses. The entire RAM address space is accessible, for both program and data accesses, in both the user and supervisor states.

A special RAM configuration is used on boards supplied with the non-MMU version of the UniFLEX<sup>TM</sup> Operating System. These boards restrict user state accesses to the lower 512K bytes of the RAM (\$0000000-\$0007FFF). The entire RAM (\$0000000-\$001FFFFF) is accessible in the supervisor state. Access to all I/O devices (including the I/O Expansion Port) is also restricted to the supervisor state on these boards.

Access permissions for the RAM and I/O devices are controlled by a Programmable Logic Device (PLD), and can only be changed by replacing the PLD (U-25). For further information, contact the factory.

The GMX Micro-20 has four 28-pin sockets that will accept up to 256K bytes of Read-Only Memory (ROM). The ROM space is organized as 32-bit wide memory. Hardware jumpers configure the board for one of four different ROM sizes (8K x 8, 16K x 8, 32K x 8, or 64K x 8), and for the number of wait-states generated during ROM accesses. Because of the way the ROM is organized, all four sockets must always be used and all four devices must be the same size.

The ROMs are normally mapped high in the processors address space, allowing the system RAM to begin at address zero. However, after power-up or reset the ROMs are temporarily mapped into low memory so the processor can read the restart vector and initial stack pointer from them.

# 10-2: ROM Types Supported

The GMX Micro-20 can be configured for four different industry standard EPROM types: 2764 (8K x 8), 27128 (16K x 8), 27256 (32K x 8) and 27512 (64K x 8). Note: All four devices must be the same size. Although UV Erasable ROMs (EPROMs) are normally used with the GMX Micro-20, other devices (except RAMs) that are pin compatible with the listed EPROMs could also be used.

The maximum access time of the ROMs must be less than or equal to the maximum times listed in the 'ROM Speed Option Jumper' sub-section. Since slower ROMs require more wait-states, which results in slower program execution, the speed (access time) of the ROMs used can be an important factor in some applications. If the ROMs are used mainly to bootstrap programs that execute from RAM, then it may be possible to use slower ROMs without seriously affecting overall performance of the system. However, if the software executes mainly from ROM, then faster ROMs must be used to obtain maximum system performance.

In time or speed critical applications, the number of wait-states required by the ROMs must also be considered when programs developed and debugged in RAM will eventually be executed from ROM. Since the RAM only requires one wait-state and the ROMs may require up to 5, program execution times may be considerably slower when the program is moved to ROM.

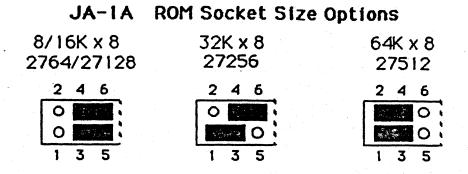

#### 10-3: Size Option Jumper (JA-1A)

Jumper area JA-lA is used to configure the ROM sockets for the size of the ROMs being used. All devices must be the same size and, because the ROM space is organized as 32-bit memory, four devices must always be used. Figure 10-1 shows the configuration of JA-lA for each of the four ROM sizes supported.

Figure 10-1

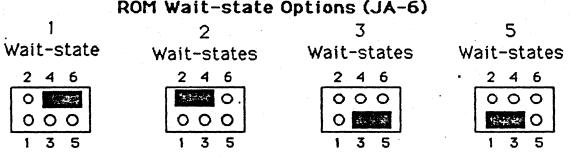

# 10-4: Wait-state Option Jumper (JA-6)

Jumper Area JA-6 is used to set the number of wait-states generated by ROM accesses. The jumper is set according to the access time of the ROMs and the 68020 clock speed.

Figure 10-2 shows the configurations of JA-6, the resulting number of wait-states and the maximum access times for different processor speeds. JA-6 must be set so that the access time obtained is greater than or equal to the maximum access time of the ROMs. For example, to use ROMs with a 300 nanosecond maximum access time, JA-6 must be set for either three wait-states (12.5 MHz 68020) or 5 wait-states (16.67 or 20 MHz 68020). Note: The processor clock speed is one-half of the master clock oscillator (U37) frequency.

| Maximu            |                    |                 |                         |

|-------------------|--------------------|-----------------|-------------------------|

| 12.5 MHz<br>68020 | 16.67 MHz<br>68020 | 20 MHz<br>68020 | Wait-states<br>Required |

| 205 ns            | 150 ns             | 120 ns          | 1                       |

| 285 ns            | 210 ns             | 170 ns          | 2                       |

| 365 ns            | 270 ns             | 220 ns          | 3                       |

| 525 ns            | 390 ns             | 320 ns          | 5                       |

# ROM Wait-state Options (JA-6)

Figure 10-2

## 10-5: Addressing

The ROM sockets occupy 256K bytes of the processor's address space, from address \$00800000 through address \$0083FFFF. The largest ROMs that the board supports are 64K x 8 devices, and four of them occupy the entire ROM address space. If smaller devices are used, they appear more than once in the ROM address space. For example, if 32K x 8 devices are used they appear from \$00800000 through \$0081FFFF and again from \$00820000 through \$0083FFFF.

### 10-6: Data Organization

The ROM sockets are organized as 32-bit memory, with each of the four sockets connected to 8 of the processors 32 data lines. The following table shows the relationship between the processor data bus and the ROM sockets.

| ROM    | 68020    |

|--------|----------|

| Socket | Data Bus |

| U-13   | D24-D31  |

| U-10   | D16-D23  |

| U-8    | D8-D15   |

| U-6    | D0-D7    |

This relationship is important since programs and data must be split into four parts and placed in the correct ROMs in order to be read properly by the processor. The following table shows how the long word values \$01234567 and \$89ABCDEF would be placed in the ROMs so they appear at addresses \$80000000 and \$80000004 (the first two locations in the ROM space).

| ROM<br>ADDRESS | U-13 | U-10 | U-8  | U- <u>6</u> |

|----------------|------|------|------|-------------|

| 0              | \$01 | \$23 | \$45 | \$67        |

| 1              | \$89 | \$AB | \$CD | \$EF        |

#### 10-7: Processor Restart Vectors

The first two long words in the ROMs (addresses \$00800000 and \$00800004) must contain the initial stack pointer and program counter values to be used by the processor on power-up and reset. The processor expects to find these values at addresses \$00000000 and \$00000004, which are normally occupied by RAM on the GMX Micro-20. However, immediately after power-up or reset the ROMs are mapped into low memory so the data read from addresses \$0000000 and \$0000000 will be the data in the first two long words of the ROMs. Once these two long words have been read, normal memory mapping is restored and subsequent reads and writes of these addresses access the RAM.

## 11-1: General Description

The GMX Micro-20 uses two 68681 Dual Asynchronous Receiver/Transmitters (DUARTs) to provide four asynchronous serial I/O ports. These ports support a variety of transmission formats, including: 5 to 8 data bits; odd parity, even parity, no parity, or force parity; one, one and one-half, or two stop bits; and eighteen software selectable baud rates from 50 to 38,400 baud.

Serial data and flow control (handshake) lines are accessed through the serial I/O connector (P2). Each port provides transmit and receive data lines and two handshake lines; one input and one output. One of the ports also has six additional handshake lines (eight total) that can be used in applications such as modem control.

The I/O lines from the DUARTS are unbuffered and connect directly to I/O connector P2, making it possible to adapt the serial ports to almost any serial interface standard (RS-232, RS-422, etc.) by using an appropriate external adapter. Standard adapter boards are available to provide RS-232 level translation.

#### 11-2: Accessing the DUART Registers

Each DUART is controlled by sixteen internal 8-bit read/write registers. These registers are accessed by the processor at sixteen consecutive byte addresses, using standard byte-wide instructions (move.b, clr.b, etc.). The special 'move peripheral' (movep) instructions are not required and should not be used when accessing the DUARTs.

#### \*\*\*\*\*\*\*\*\*\* NOTE \*\*\*\*\*\*\*\*\*\*

Due to the speed of the 68020 processor, accessing the DUARTS using multiple byte instructions (move.w, clr.l, etc.) or accessing them with consecutive byte-wide instructions, will violate the timing constraints of the device. For this reason, only byte-wide instructions should be used to access the DUARTS, and a 'No Operation' instruction (NOP) must be inserted between any two consecutive instructions that access DUART registers.

#### \*\*\*\*\*

The following table lists each of the DUART registers and its corresponding address. Port numbering follows the conventions used in the GMX serial adapter board documentation. Port 0 (U-12, side A) is used as the system console port by software supplied by GMX. For a complete functional description of the registers, refer to the manufacturer's data sheet for the 68681 DUART.

| · · ·       | gister      | DUART #1 (U12)    | ••••              |

|-------------|-------------|-------------------|-------------------|

| Read        | Write       | Ports 0(A) & 1(B) | Ports 2(A) & 3(B) |

| MRIA/2A     | MRIA/2A     | \$00FF8080        | \$00FF80A0        |

| SRA         | CSRA        | \$00FF8081        | \$00FF80A1        |

| 1 1 🗶 🖈 👘 🖓 | CRA         | \$00FF8082        | \$00FF80A2        |

| RBA         | TBA         | \$00FF8083        | \$00FF80A3        |

| IPCR        | ACR         | \$00FF8084        | \$00FF80A4        |

| ISR         | IMR         | \$00FF8085        | \$00FF80A5        |

| CUR         | CTUR        | \$00FF8086        | \$00FF80A6        |

| CLR         | CTLR        | \$00FF8087        | \$00FF80A7        |

| MR1B/2B     | MR1B/2B     | \$00FF8088        | \$00FF80A8        |

| SRB         | CSRB        | \$00FF8089        | \$00FF80A9        |

| ★^          | CRB         | \$00FF808A        | \$00FF80AA        |

| RBB         | TBB         | \$00FF808B        | \$00FF80AB        |

| IVR         | IVR         | \$00FF808C        | \$00FF80AC        |

| Input P     | ort OPCR    | \$00FF808D        | \$00FF80AD        |

| Start C     | TR OPR Set  | \$00FF808E        | \$00FF80AE        |

| Stop CI     | R OPR Reset | \$00FF808F        | \$00FF80AF        |

\* These locations are used for factory testing and must not be read.

Note: Each DUART actually occupies 32 bytes of address space, with each of the registers repeated twice. (e.g. DUART #1 MR1A/2A also appears at \$00FF8090)

## 11-3: Baud Rate Clock

Each DUART is provided with a 3.6864 MHz clock on its CLK input pin, allowing any of the 18 standard baud rates supported by the part to be selected under program control.

The standard baud rates are divided into two sets and, while the baud rate for each half of the DUART can be selected separately, both rates must be selected from the same set. Many baud rates are common to both sets; however, some are only available in one of the two. For this reason, it is not possible to select certain combinations of baud rates directly from the standard sets. For example, if set #2 is being used, 19.2K baud is available but 38.4K is not.

In order to overcome this potential problem, the DUARTS built-in counter/timer can be used to add an additional baud rate to either of the standard sets. This is accomplished by programming the timer to use the external clock (X1/CLK), programming it for the appropriate division ratio, and selecting it as the baud rate clock for the desired port.

Since the baud rate clock is normally sixteen times the actual baud rate, the correct division ratio can be found by dividing the input clock frequency (3.6864 MHz) by sixteen times the desired baud rate. For example, the correct divisor for 38.4K baud is: 3,686,400 / (16 \* 38,400) = 6. Since the value placed in the counter/timer registers (CTUR and CTLR) must be one-half of the desired divisor, a zero (0) would be written to the upper byte (CTUR), and a three (3) would be written to the lower byte (CTLR) to obtain the correct clock frequency for 38.4K baud.

In addition to the standard 3.6864 MHz clock input, DUART #2 (U-14) also has a 2 MHz clock connected to its IP3 and IP4 input lines. This clock can be used to provide special clock rates for applications such as networking.

#### 11-4: Connections (P2)

Connector P2 on the GMX Micro-20 provides access to the data and selected handshake signals from both DUARTS. Figure 11-1 lists the signals available, and the pinout of connector P2. Be sure to observe proper polarity (pin 1) when making connections to the board.

For information on mating connectors, refer to the connector summary in the 'SPECIFICATIONS' section at the beginning of this manual.

#### \*\*\*\*\*\* CAUTION \*\*\*\*\*\*\*

The serial I/O signals at connector P2 are TTL level signals which must normally be converted to appropriate levels (such as RS-232 levels) by an external adapter board. Damage to the GMX Micro-20 may occur if non-TTL level signals are connected directly to the board.

#### \*\*\*\*

Either a standard GMX interface adapter board or a custom designed board can be used to convert the TTL level signals to the levels required by the interface standard being used. The GMX Micro-20 normally includes an adapter board that converts the signals to RS-232 levels and provides separate I/O connectors for each port. Refer to the interface adapter board documentation for more information.

The actual function of each I/O signal is determined by the by the software being used. For information on signal functions, refer to the software documentation.

#### 11-5: Powering Serial Adapter Boards

As shown in Figure 11-1, both +5 Volts and +12 Volts DC are available at connector P2 on the GMX Micro-20. These supplies are used to power the serial adapter boards supplied by GMX and may also be used to power custom adapters, provided that the current requirements of the adapter do not exceed 1 Amp from the +5 Volt supply and 500 ma. from the +12 Volt supply.

# Serial I/O Connector (P2)

| Port  | 68681<br>Signal                         | Signa)<br>Name | Direct        | ion     | Pin            |

|-------|-----------------------------------------|----------------|---------------|---------|----------------|

|       | TxDA                                    | TX (0)         | From Co       | omputer | 1              |

| Port  | RxDA                                    | RX (0)         | To Comp       | outer   | 3              |

| 0     | OP O                                    | DTR (0)        | From Co       | mputer  | 5              |

| U12-A | IPO                                     | CTS (0)        | To Comp       | outer   | 7              |

|       | TxDB                                    | TX (1)         | From Co       | omputer | 9              |

| Port  | RxDB                                    | RX (1)         | To Comp       | outer   | 11             |

| 1     | 0P 1                                    | DTR (1)        | From Co       | mputer. | 13             |

| U12-B | IP 1                                    | CTS (1)        | To Comp       | outer   | 15             |

|       | TxDA                                    | TX (2)         | From Co       | omputer | 17             |

| Port  | RxDA                                    | RX (2)         | To Comp       | outer   | 19             |

| 2     | OPO                                     | DTR (2)        | From Co       | omputer | 21.            |

| U14-A | IPO                                     | CTS (2)        | To Computer   |         | 23             |

|       | TxDB                                    | TX (3)         | From C¢       | mputer  | 25             |

|       | RxDB                                    | RX (3)         | To Computer   |         | 27             |

|       | OP 1                                    | DTR (3)        | From Computer |         | 29             |

|       | IP1                                     | CTS (3)        | To Computer   |         | 31             |

| Port  | 0P3                                     | RTS (3)        | From Co       | omputer | 33             |

| 3     | OP5                                     | 0P5            | From C        | omputer | 35             |

| U14-B | 0P7                                     | 0P7            | From C        | omputer | 37             |

|       | IP2                                     | DCD (3)        | To Com        | outer   | 39             |

|       | IP5                                     | IP5            | To Com        | outer   | 41             |

|       | OP2                                     | OP2            | From C        | omputer | 43             |

|       | I Stangland Doulon Geoling Dotlings I   |                |               |         | nbered<br>- 44 |

| A11   | +5 Volt DC                              | Supply from (  | Computer      | 45,47   | ,48            |

|       | Not conne                               | cted, spare    |               | 46      |                |

|       | + 12 Volt DC Supply from Computer 49,50 |                |               |         | 0              |

# Figure 11-1

Note: Pin 46 of connector P2 is not connected and may be used as an additional signal line in special applications.

#### 11-6: Interrupts

The Interrupt Request (IRQ) outputs of both DUARTs is permanently connected to the interrupt logic on the GMX Micro-20. A level 3 autovectored interrupt will be generated when either device asserts its IRQ line. Since autovectored interrupts are used, there is no need to program the DUART Interrupt Vector Registers.

Level 3 autovectored interrupts can also be generated by external sources, connected to pin 30 (/681) of the GMX Micro-20 I/O Expansion Connector (P1). When a level 3 interrupt occurs, the interrupt handler must poll the DUARTs, and any devices connected to the expansion connector, to determine the source of the interrupt. The interrupt condition is cleared by taking whatever action is necessary to make the device causing the interrupt deassert its interrupt request output.

#### 12-1: General Description

The 68230 Parallel Interface/Timer (PI/T) is a multi-function peripheral device that performs four separate functions on the GMX Micro-20. It includes two 8-bit parallel I/O ports, a counter/timer, and miscellaneous handshake and control lines.

One 8-bit port is used as a general purpose parallel I/O port. This port has eight data lines and two handshake lines, and can be configured for either input or output. External devices such as parallel printers can be connected to this port through the parallel port connector P3.

The second 8-bit port and several of the control lines are used to access the built-in time-of-day clock/calendar on the GMX Micro-20. All of the functions needed to set and read the clock are performed through the PI/T.

The counter/timer and one of the control lines are used to control the GMX Micro-20's periodic interrupt (tick) generator. The control line is used to enable or disable CPU interrupts from the tick generator and the counter/timer can be used to count "ticks" as they occur.

One of the miscellaneous control lines , is used to sense the status of the front panel Single-step/Abort switch, allowing software to differentiate between interrupts caused by the switch and those caused by the floppy disk controller.

The remainder of this section describes the basic methods used to access the PI/T and the signal lines used by each of the functions it performs. More detailed information on specific functions, such as accessing the time-of-day clock, is located in the corresponding sections of this manual. For a complete description of the 68230 refer to the manufacturer's data sheet for the device.

#### 12-2: Accessing PI/T Registers

Most of the PI/T registers are byte values and are usually accessed using the appropriate byte-oriented instructions (move.b, clr.b, etc.). However, the timer count and preload registers return 24-bit values from three consecutive registers. Since both of these groups of registers are preceded by a null register, a long word read or write can be used to access the entire 24-bit value with a single instruction (e.g. move.l). Word or long word instructions can also be used to access any two or four consecutive registers in a single instruction.

Note: Since the PI/T registers occupy consecutive byte addresses, the special peripheral access instructions (i.e. MOVEP) are NOT used to access the PI/T.

## 12-3: Register Addresses

The PI/T has 32 internal 8-bit registers accessible to the user. They appear in 32 consecutive bytes of the processors address space from \$00FF80C0 through \$00FF80DF. Nine of these registers are unused, and are defined as "null registers". Null registers always return all zeros when read. Writing to a null register has no effect. The following table lists each of the registers and its address. Standard Motorola naming conventions are used. For complete functional descriptions of the registers, refer to the manufacturer's data sheet for the 68230 PI/T.

## 68230 PI/T Register Addresses

| Register Name                   | Mnemonic | Address    |

|---------------------------------|----------|------------|

| Port General Control Register   | PGCR     | \$00FF80C0 |

| Port Service Request Register   | PSRR     | \$00FF80C1 |

| Port A Data Direction Register  | PADDR    | \$00FF80C2 |

| Port B Data Direction Register  | PBDDR    | \$00FF80C3 |

| Port C Data Direction Register  | PCDDR    | \$00FF80C4 |

| Port Interrupt Vector Register  | PIVR     | \$00FF80C5 |

| Port A Control Register         | PACR     | \$00FF80C6 |

| Port B Control Register         | PBCR     | \$00FF80C7 |

| Port A Data Register            | PADR     | \$00FF80C8 |

| Port B Data Register            | PBDR     | \$00FF80C9 |

| Port A Alternate Register       | PAAR     | \$00FF80CA |

| Port B Alternate Register       | PBAR     | \$00FF80CB |

| Port C Data Register            | PCDR     | \$00FF80CC |

| Port Status Register            | PSR      | \$00FF80CD |

| Null Register                   | NULL     | \$00FF80CE |

| Null Register                   | NULL     | \$00FF80CF |

| Timer Control Register          | TCR      | \$00FF80D0 |

| Timer Interrupt Vector Register | TIVR     | \$00FF80D1 |

| Null Register                   | NULL     | \$00FF80D2 |

| Counter Preload Register High   | CPRH     | \$00FF80D3 |

| Counter Preload Register Middle | CPRM     | \$00FF80D4 |

| Counter Preload Register Low    | CPRL     | \$00FF80D5 |

| Null Register                   | NULL     | \$00FF80D6 |

| Count Register High             | CNTRH    | \$00FF80D7 |

| Count Register Middle           | CNTRM    | \$00FF80D8 |

| Count Register Low              | CNTRL    | \$00FF80D9 |

| Timer Status Register           | TSR      | \$00FF80DA |

| Null Register                   | NULL     | \$00FF80DB |

| Null Register                   | NULL     | \$00FF80DC |

| Null Register                   | NULL     | \$00FF80DD |

| Null Register                   | NULL     | \$00FF80DE |

| Null Register                   | NULL     | \$00FF80DF |

## 12-4: Interrupts

The PI/T can be programmed to directly cause two different autovectored interrupts to the CPU. If the timer interrupt output (PC3/TOUT) is asserted (active low), a level 4 autovector interrupt is generated. If the port interrupt output (PC5/PIRQ) is asserted (active low), a level 2 autovector interrupt is generated. The PI/T can also indirectly cause a third level of autovectored interrupt by enabling the periodic interrupt (tick) generator. When the PI/T H4 handshake output is asserted (active low), the tick generator is enabled and periodic level 6 autovector interrupts are generated. Refer to the section 15 of this manual for more information.

## 12-5: I/O Pin Functions

The following table lists each of the PI/T I/O pins and the function it performs on the GMX Micro-20. The table uses standard Motorola mnemonics for the pin names.

| Pin<br>No. | Name                                      | Function                     | Direction | Active<br>Leveĩ |  |  |

|------------|-------------------------------------------|------------------------------|-----------|-----------------|--|--|

| 4          | PAO                                       | Parallel Port Data Line D0   | I/O †     | ×               |  |  |

| 5          | PAl                                       | Parallel Port Data Line Dl   | I/O †     | ×               |  |  |

| 6          | PA2                                       | Parallel Port Data Line D2   | I/O †     | x               |  |  |

| 7          | PA3                                       | Parallel Port Data Line D3   | I/O †     | ×               |  |  |

| 8          | PA4                                       | Parallel Port Data Line D4   | I/0 †     | x               |  |  |

| 9          | PA5                                       | Parallel Port Data Line D5   | I/O †     | ×,              |  |  |

| 10         | PAG                                       | Parallel Port Data Line D6   | I/O †     | x               |  |  |

| 11         | PA7                                       | Parallel Port Data Line D7   | I/O †     | x               |  |  |

| 13         | Hl                                        | Parallel Port Handshake      | I         | x               |  |  |

| 14         | H2                                        | Parallel Port Handshake      | I/O †     | ×               |  |  |

| 17         | PB0                                       | TOD Clock Data/Address 0     | I/O       | ×               |  |  |

| 18         | PB1                                       | TOD Clock Data/Address l     | I/O       | x               |  |  |

| 19         | PB2                                       | TOD Clock Data/Address 2     | I/0       | x               |  |  |

| 20         | PB3                                       | TOD Clock Data/Address 3     | I/0       | ×               |  |  |

| 24         | PB7                                       | TOD Clock BUSY               | I         | L               |  |  |

| 30         | PC0                                       | TOD Clock STOP               | 0         | H               |  |  |

| 31         | PCl                                       | TOD Clock WRITE              | 0         | -H              |  |  |

| 34         | PC4                                       | TOD Clock READ               | 0         | Н               |  |  |

| 36         | PC6                                       | TOD Clock WRITE ADDRESS      | 0         | Н               |  |  |

| 37         | PC7                                       | TOD Clock TEST               | 0         | Н               |  |  |

| 32         | PC2/TIN                                   | Periodic Interrupt Clock In  | I         | ×               |  |  |

| 16         | <b>H4</b>                                 | Periodic Interrupt Enable    | 0         | Ľ.              |  |  |

| 15         | НЗ                                        | ABORT Switch sense           | I         | Н               |  |  |

| 33         | PC3/TOUT                                  | Level 4 Autovector Interrupt | 0         | L               |  |  |

| 35         | PC5/PIRQ                                  | Level 2 Autovector Interrupt | 0         | L               |  |  |

| 21         | PB4                                       | Unused, No Connection        | _         | -               |  |  |

| 22         | PB5                                       | Unused, No Connection        | -         | -               |  |  |

| 23         | PB6                                       | Unused, No Connection        |           | <u> </u>        |  |  |

|            | t Jumper programmable for input or output |                              |           |                 |  |  |

## 68230 PI/T I/O Pin Functions

#### 12-6: Programming Considerations