## GE-645

# SYSTEM MANUAL

January 1968

In the construction of the equipment described, the General Electric Company reserves the right to modify the design for reasons of improved performance and operational flexibility.

## GENERAL ELECTRIC

# INFORMATION SYSTEMS EQUIPMENT DIVISION

## PREFACE

Part I of this manual provides an introduction to the GE-645 Information Processing System. The first two chapters trace the thinking which brought about the development of an advanced information processing service concept. This concept assumes computer service available in the same way electricity is made available simultaneously to many users. The GE-645 is aimed at providing this type of service. Chapter 3 provides a summary which allows the readers to obtain a general

understanding of how the GE-645 approaches this problem.

Part II provides moderately detailed information about the major hardware components of the GE-645 System and contains a generalized description of the objectives and planned operational features of the Multics Operating System and related software as currently being developed for the GE-645 System.

## **ACKNOWLEDGEMENT**

Multics (Multiplex Information and Computing Service) is an operating system concept developed from research by the Massachusetts Institute of Technology, Bell Telephone Laboratories and the General Electric Company. It draws upon the design and operating experience gained with CTSS (Compatible Time-Sharing System) at the Computation Center and Project MAC of the Massachusetts

Institute of Technology, and upon programming language research and system principles from Bell Telephone Laboratories.

The descriptive material on Multics contained in this document is derived from the technical objectives established by the above organizations for the continuing implementation of that concept on the GE-645 System.

# CONTENTS

|    | PART I. Introduction to the GE-645 System                                                                                                                                                                | Page                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1. | PROBLEM STATEMENT                                                                                                                                                                                        | . ,1                                                 |

| 2. | DESIGN CONCEPTS                                                                                                                                                                                          | . 3                                                  |

| 3. | SYSTEM SUMMARY                                                                                                                                                                                           | . 5                                                  |

|    | Total System                                                                                                                                                                                             | . 5<br>. 7                                           |

|    | Operating System                                                                                                                                                                                         | . 7                                                  |

|    | PART II. GE-645 System Description                                                                                                                                                                       |                                                      |

| 4. | HARDWARE SYSTEM CHARACTERISTICS                                                                                                                                                                          | . 9                                                  |

|    | Hardware System Organization                                                                                                                                                                             |                                                      |

| 5. | SYSTEM CONTROLLER MODULE                                                                                                                                                                                 |                                                      |

|    | Storage Function                                                                                                                                                                                         | . 15                                                 |

|    | Connect Instruction                                                                                                                                                                                      | . 15                                                 |

|    | System Clock                                                                                                                                                                                             | . 16                                                 |

| 6. | PROCESSOR MODULE                                                                                                                                                                                         | . 17                                                 |

|    | Modes of Operation Register Descriptions Instruction Repertoire Address Modification Segmentation Descriptor Segment Paging Associative Memory Faults and Interrupts Privileged Operation Access Control | . 17<br>. 18<br>. 19<br>. 20<br>. 21<br>. 27<br>. 29 |

| 7. | GENERALIZED INPUT/OUTPUT CONTROLLER                                                                                                                                                                      |                                                      |

|    | Channels                                                                                                                                                                                                 | . 37<br>. 37<br>. 42                                 |

| 8. | EXTENDED MEMORY MODULE                                                                                                                                                                                   | . 45                                                 |

|    | Organization                                                                                                                                                                                             |                                                      |

|    | COMPATIBLES / 600                                                                                                                                                                                        |                                                      |

|     | CONTENTS (Cont)                                                                                                                                                                                                                                                                                                                                       | ٠ | P | age                              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|----------------------------------|

|     | Performance Characteristics                                                                                                                                                                                                                                                                                                                           | • | • | 45                               |

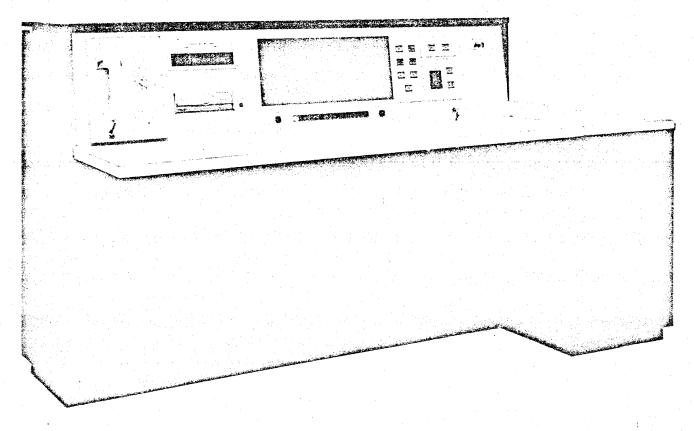

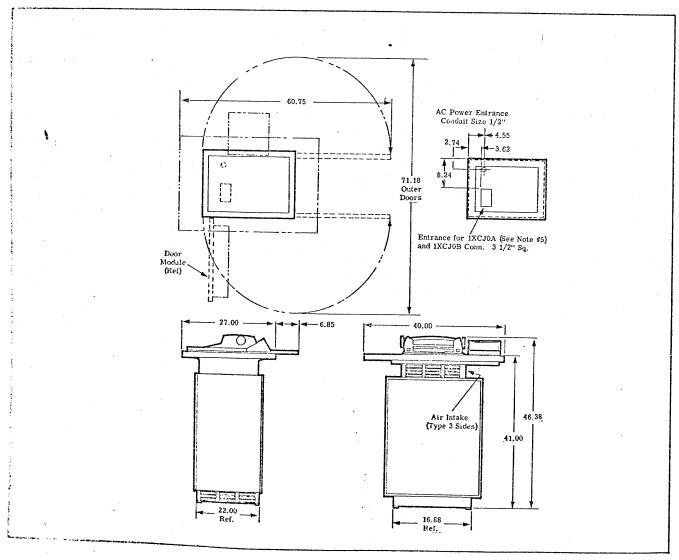

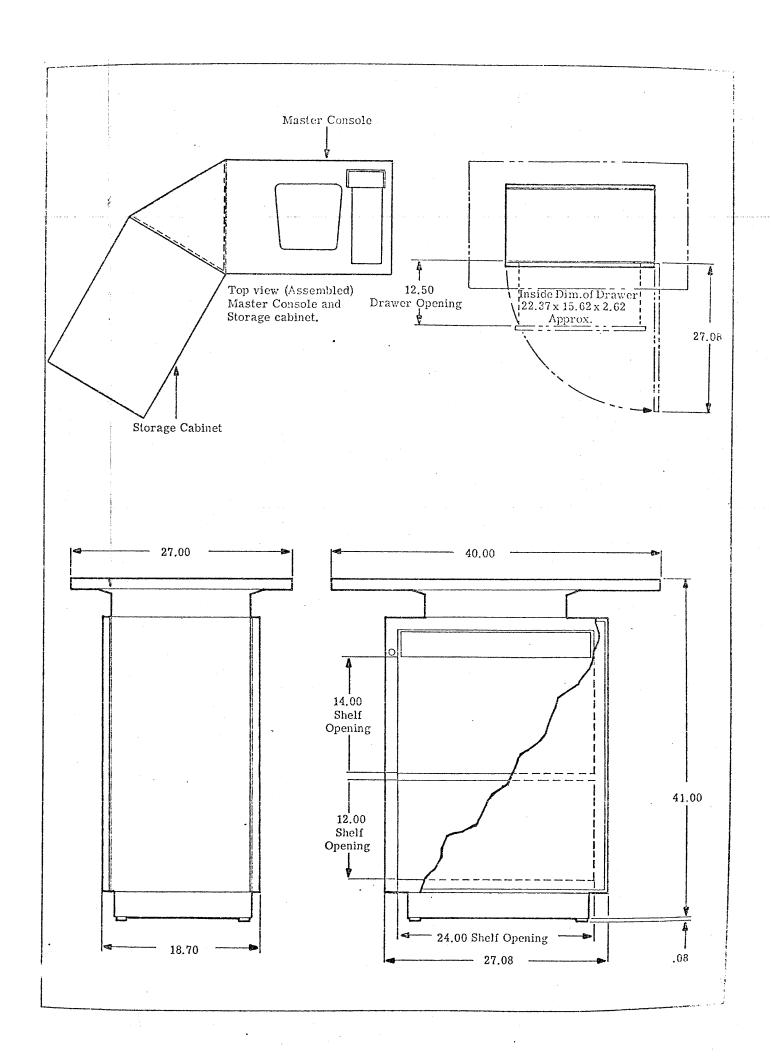

| 9.  | SYSTEM CONFIGURATION CONSOLE                                                                                                                                                                                                                                                                                                                          |   | • | 47                               |

|     | Reconfiguration                                                                                                                                                                                                                                                                                                                                       |   |   | 49<br>49<br>49<br>49             |

| 10. | PERIPHERAL AND TERMINAL EQUIPMENT                                                                                                                                                                                                                                                                                                                     | • |   | 51                               |

|     | Peripheral Equipment                                                                                                                                                                                                                                                                                                                                  | • | • | 51                               |

|     | Disc Storage Unit (DSU10F) Disc Storage Unit (DSU204) Magnetic Drum Storage Unit (MDU200) Mass Storage Unit (MSU388) Magnetic Tape Subsystem Card Reader and Control (CRZ201) Card Punch and Control (CPZ201) ASCII Extended Character Set Printer (PRT202) Perforated Tape Subsystem (PTS200) Peripheral Switch Console (PSC200)  Terminal Equipment |   |   | 58<br>59<br>61<br>62<br>64<br>65 |

|     | GE-115 Information Processing System                                                                                                                                                                                                                                                                                                                  |   |   | 66                               |

| 11. | MULTICS                                                                                                                                                                                                                                                                                                                                               | • |   | 71                               |

|     | Concepts            User Interaction with Multics            Supervisor            Command System            File System            File Structure            Basic File System            Multilevel and Backup System            I/O System                                                                                                         |   |   | 71<br>72<br>73<br>74<br>75       |

| Å.  | INSTRUCTION REPERTOIRE                                                                                                                                                                                                                                                                                                                                |   |   | 81                               |

| В.  | HARDWARE SUMMARY                                                                                                                                                                                                                                                                                                                                      | • |   | 89                               |

GE-645 SYSTEM

# PART 1. INTRODUCTION TO THE GE-645 SYSTEM

#### 1. PROBLEM STATEMENT

During the early growth period of computers, a computer was a unique and complex piece of equipment, but was too expensive to give to each person with a problem. In order to justify the cost of a computer and to take advantage of its speed, batch processing became the standard mode of operation. A staff of experts was required to manage, program, and operate the computer. As a result, the man with the problem gradually had barriers placed before him, and he became more removed from the computer.

The computer language was a primary barrier. The man with the problem didn't know how to state the problem in a language acceptable to the computer. Specialists were called in who understood the computer languages, but didn't understand the problem. As the problem passed from specialist to specialist, it went through several stages of translation. The elapsed time from problem statement to problem solution was lengthened, and often a clear statement of the original problem was lost in the several translations. As the layers of computer specialists became thicker, the computer gradually became less accessible to the man with a problem.

Computer technology developed at a rapid pace. However, much of the development was concerned with computer equipment and computer techniques, and very little was concerned with the techniques required to make the computer a convenient tool for solving individual problems. Many times, the person with a problem must have said, "I'd put more work on the computer if it weren't such a chore." In frustration, he used methods not well suited to the needs of the problem.

The computer schedule was another barrier placed between the computer and the man with a problem. A computer was scheduled in order to get maximum use of the equipment. However, the tight schedules set for maximum use of equipment were not realistic, were difficult to enforce, and caused almost everyone to endure a long turnaround time waiting for the results. Additionally, all jobs, regardless of priorities, were put aside for demonstrations, maintenance, and real-time problems.

Despite the best scheduling efforts; full equipment utilization could not be maintained. The entire computer system became unavailable when certain peripherals (e.g., typewriter or card reader) locame unavailable. At other times the computer system was idle for many minutes waiting for tapes to be mounted or cards to be placed in the card reader. When performance characteristics of separate computer components were examined in conjunction with the requirements of the particular problems being solved, it was found that some parts were idle while other parts operated at full speed. During

calculations for a scientific problem, the input/output section worked only intermittently while the processor worked continuously; however, during calculations for a business problem, the processor worked part time while the input/output was kept busy.

The allocation of storage media was another problem closely associated with scheduling. Did management really have control of the costs in the computer system? A junior programmer could easily accumulate 50 reels of magnetic tape and collect drawer after drawer of cards. Who determined when it was more economical to store data in magnetic core, on magnetic tape, or on magnetic drum? Decisions were based on an individual's past experience rather than on statistics gathered from group experience over a longer period of time.

As middle and upper management took a broader view of the problems, the need to share programs and data files among several groups became apparent. In some instances, different groups worked on separate portions of the same large problem and each group developed its own set of programs and data files. In other situations, hardware and software limitations made it difficult for one group to utilize the files of another. A tremendous amount of this information should have been centralized and made available to several different groups at the same time. This lack of integration led to wasteful duplication of effort and fell short in supplying the total information overview sought by management.

Periodically, new and expanding computer applications required users to increase the size of their hardware systems. However, this was difficult and expensive when whole systems had to be added or replaced. Without hardware modularity, an entire hardware system consisting of all three capabilities (processing, storage, input/output) had to be added to provide more of any one capability. To take advantage of the new hardware configuration, applications had to be reprogrammed, often at considerable cost to the user.

The evolution and growth of the computer has not stopped. The technology associated with computers and their application continues to evolve at an ever increasing rate. In order for the computer to continue to serve the needs of business, industry, science, education, and government, the above problems must be solved, and the barriers between the computer and the man with a problem must be eliminated.

Specifically the next generation information processing service must provide:

• Dependable operation

- Remote terminals to communicate with the utility center

- Simple user-oriented languages for communication of problems and solutions

- Short turnaround time to permit direct interaction with the computer

- Full multiprogramming batch processing capability

- Concurrent operation of interactive jobs and batch processing jobs with high efficiency

- Memory management that frees the user from any concern about how to fit his program and data into the system

- Input/output management that frees the user from any concern about input/output operations, unless he wishes otherwise

- A storage system which permits easy sharing of data and programs

- File protection mechanisms to ensure that access to files is restricted as specified by the owners

- Modular hardware to meet the user's changing needs

- Modular software to permit its dynamic modification

- Mechanisms to permit management control over resource usage

- Bookkeeping procedures to record resource usage and charge users appropriately

- Clear, readable reference and training material to guide users, operators, maintenance engineers, and administrators in the use and control of the system.

Much of the necessary technology already exists. Many types of input/output terminals can be connected to the computer. Remote terminals (e.g. unit record devices, teletypewriters, graphic displays) can be placed at locations convenient for the user. Many users can have access to a computer and to its resources from different locations at the same time. The problem is to integrate the existing and developing technologies into a complete, reliable, and economical system.

#### 2. DESIGN CONCEPTS

New and carefully integrated system designs were needed for both hardware and software to approach the objectives of the next generation information processing service. Hardware features had to be provided to enable software supervisors to achieve their goals with required efficiency. Software systems had to be developed to exploit these hardware capabilities and to provide new levels of user service. As a result there evolved the GE-645 Computer System which uses the Multics Operating System. The following paragraphs outline the resulting design and functional concepts established for the overall GE-645 Computer System with the Multics Operating System.

The tasks which the man with a problem requests to be performed will normally take very little computer time to execute. Thus each user can proceed in the solution of his problem without being delayed by the computer. He is allowed to interact with the computer as it achieves the results he desires. The vast resources of the system are his to command. While using these resources, he has the impression that he is the sole user.

Once he has learned a few simple rules and system comands, the man with a problem can guide the computer through the steps of his problem solution from the keyboard of his remote terminal. If he is a novice in programming, he can obtain a useful knowledge of one of the simpler programming languages in a few hours. If he is an experienced programmer and wants greater power and flexibility, he can employ any of the widely used languages in the industry. Even when the GE-645, operating under Multics, is interacting with users at remote terminals, it can concurrently serve users with batch processing work.

When operating under control of Multics, a user is not concerned about the size of his program or data storage. Multics automatically moves unused parts of his program to secondary storage. Hence, both the information currently in core memory and that which Multics has placed in secondary storage are available to the user. In spite of the actual physical location of user programs and data, they appear to him as if they were all in core memory.

Multics allows a user to declare the degree of privacy to be observed in the use of each of his files. He may declare a file to be private, public, or accessible only to a specific list of other users. He can further restrict the use of a file by declaring the manner in which it may be accessed. For example, a file containing a program could be made public for purposes of execution but private for purposes of reading and modification.

A user may find it convenient to use subprograms or data which are provided by Multics or made available to him by other users. In fact, some programs and data files may be needed concurrently by many users. Multics enables many users to share programs and data files. In essence, the system provides storage facilities analogous to the combined resources of a public library (public system files), the library of co-workers (shared files), and a personal library (private files).

Multiprogramming allows adequate service to be provided to all classes of users. It permits processing part of one program, then part of a second, then part of a third, etc. This allows multiple programs to receive service in rapid succession giving the appearance that they are all being executed simultaneously. If this technique were not used, each user would need to await the completion of many other user programs before having an opportunity to utilize a processor. Without multiprogramming, interactive users would experience intolerable delays.

The total processing capability of the system is increased by having multiple processors execute multiple programs concurrently. This technique is known as multiprocessing.

The control of the processors is directed from one user program to another by Multics. Every time a new program is placed in execution, special registers are initialized which prevent damage to information belonging to any other user or the operating system.

Large memories are made available in the GE-645 hardware. Through their use, many programs and their data may be stored concurrently awaiting execution. Even with the large memories available on the GE-645, it is generally impossible to allow the programs and data of all users to reside in core memory throughout their execution. The number of users that can be serviced by the GE-645 is made large by providing a high-speed fixed-head magnetic disc unit for moving information rapidly into and out of core memory. The number of users that can be serviced is also increased by employing the techniques of paging and segmentation.

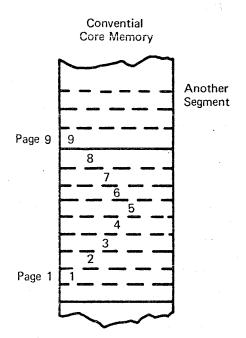

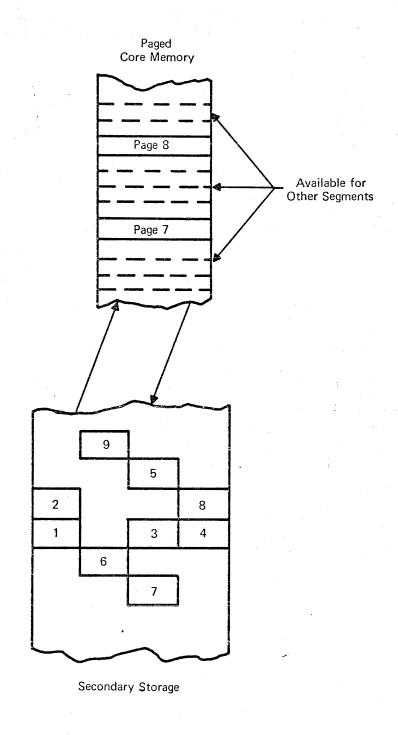

In the concept of paging, a program is divided into pieces of equal size called pages. When the program is in execution, only its most active pages reside in core storage. Its less active pages are stored in the secondary storage hierarchy.

In the GE-645 the management of paged programs is facilitated by special hardware which makes the pages appear to be in contiguous locations even though they may be widely separated in core memory. The hardware also keeps track of which pages have been altered while they are in core memory so that unaltered pages need not be rerecorded in secondary storage when they are removed from core memory.

Segmentation allows a program to be divided into separate parts called segments. Each segment can be thought of as a separate core memory with its own origin and maximum size. One of the important features of segments is that they may be shared among many users. Hence, only a single copy of a program or data file need exist if these are properly stored in the segment being accessed by many users.

A second important property of segments is that they allow a user to collect in effectively separate memories information with like characteristics. For example, some or all of the unalterable information of a program can be brought together into a "read only" segment. This not only protects the information from inadvertent modification but also collects information which will never need to be rewritten to secondary storage during the paging operation.

Modular hardware lets the user reconfigure a system to fit the changing needs brought about by growth. A system can consist of multiple memory, processor, and input/output controller modules. The modular hardware lets the user assemble a combination of modules that most closely fits his current need. This reconfiguration can take place without providing an excess of unwanted modules. For example, one processor module can be added when additional processing is needed, or one input/output controller and/or peripheral devices can be added when greater input/output capability is needed.

Modular software is a direct result of segmentation, and makes it practical to alter the operating system to fit computing needs. It also allows the operating system maintenance group to make appropriate improvements and modifications that are of benefit to the user. The same programming standards are used in Multics as in user programs so that maximum consistency and flexibility is achieved within the system.

#### 3. SYSTEM SUMMARY

The previous chapters have discussed the general problems facing the user, the objectives of the GE-645 system, and the design concepts which enable the system to solve the user's problems. This chapter contains a brief view of the total hardware-software system followed by descriptions of the hardware and its components, and the software system and its components. Should the reader desire more information than is contained in this chapter, he may refer to Part II.

#### TOTAL SYSTEM

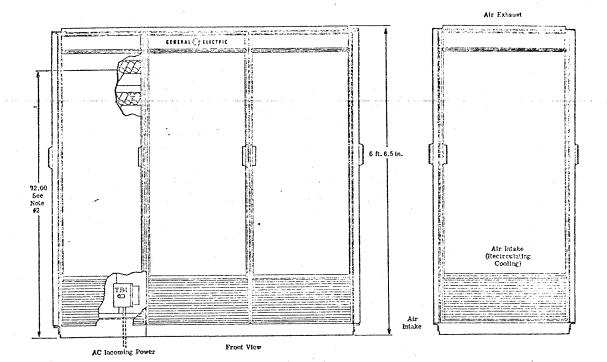

The GE-645 is a large-scale, high-performance, binary computing system that operates with the Multics operating system, several language processors, and a wide variety of application packages. Most of the equipment is located at the computer center, while terminals are placed in locations convenient for the users of the system.

#### **HARDWARE**

The hardware consists of four types of modules, peripheral and terminal equipment, and common carrier facilities for the terminals. The four module types are processor, generalized input/output controller (GIOC), system controller (memory), and extended memory. A full range of peripherals is available, from perforated tape units to large, high-speed discs. Terminals that may be used range from slow speed teletypewriters to complex display consoles and computers. Terminals are connected to the system with standard, presently-available communication equipment.

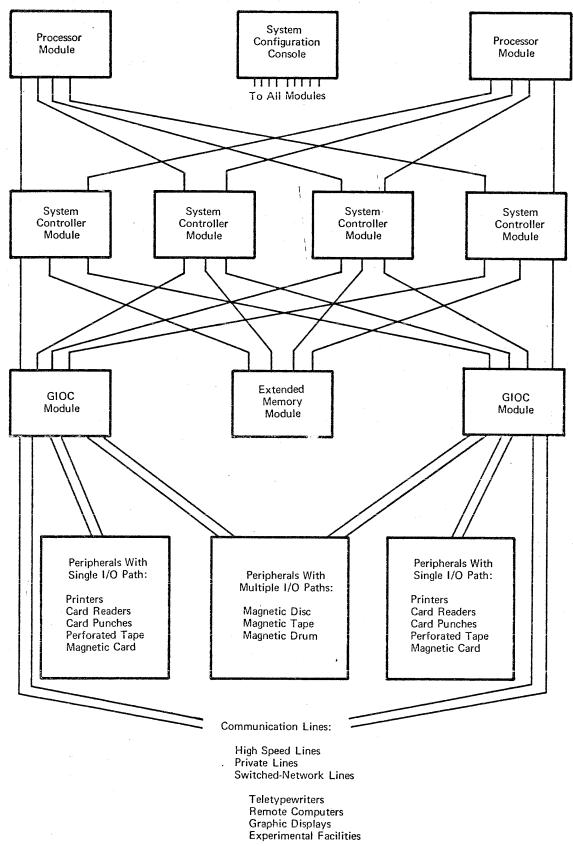

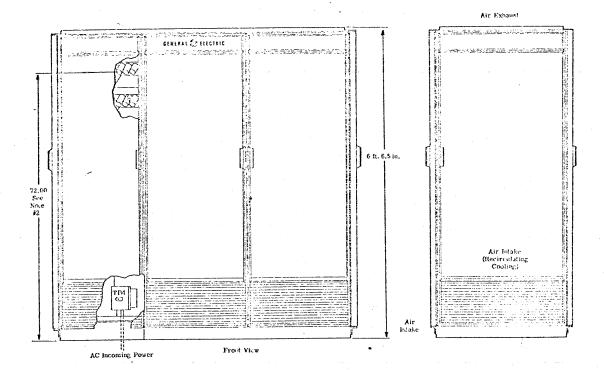

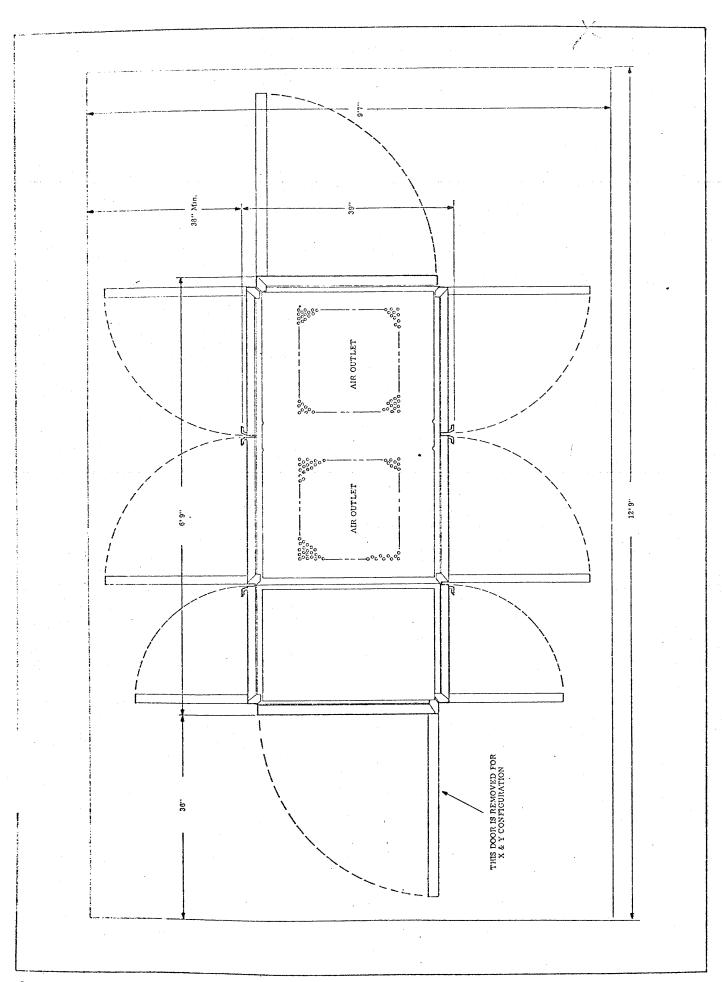

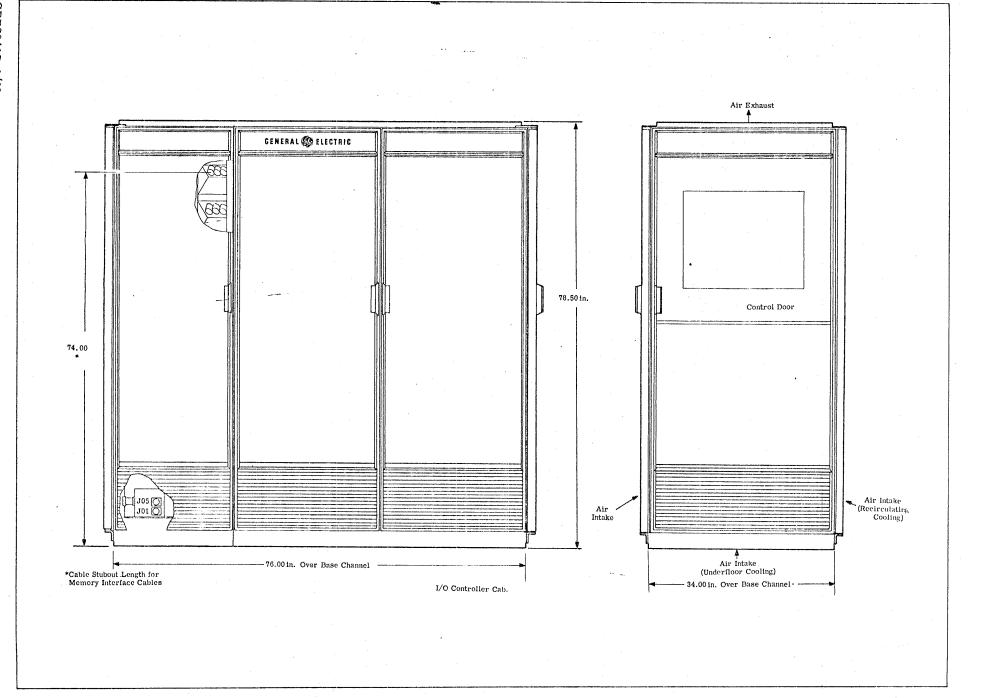

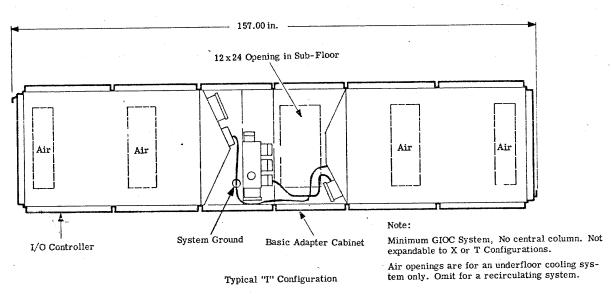

A typical hardware system organization is shown in Figure 1. In this example, two processors, four system controllers, two GIOCs, and one extended memory module are combined to form a nine-module system, together with a system configuration console. The figure shows the interconnections between the nine modules and the way that the peripherals and terminals are connected to the system.

The system configuration console establishes the basic parameters of the system configuration that make it possible for the modules to communicate with one another through the system controllers. The SCC also provides the means for rapid re-configuration of these parameters and for initiating the bootloading operation for placing the system in operation. A teletypewriter can be connected to the SCC to provide a printed copy of the "conversations" between the operator and the operating system.

The processor modules do the computation and decisionmaking in the system. Many registers and an associative (content-addressable) memory are provided in each processor to facilitate rapid execution of powerful instructions. Performance is also enhanced with instruction overlap: that is, address preparation for the next instruction and fetching of subsequent instructions continue while the current instruction is being executed. The instruction repertoire is large and varied, and has 404 operation codes currently defined. (This leaves 108 operation codes reserved for future upward growth.) A wide range of conventional instructions is supplemented with many special-purpose instructions and several instructions specifically for character manipulation. Address modification includes conventional register modification and multilevel indirect addressing plus several variations particularly aimed at character manipulation and operating on stacks. All hardware manipulation related to segmentation and paging is done by a processor.

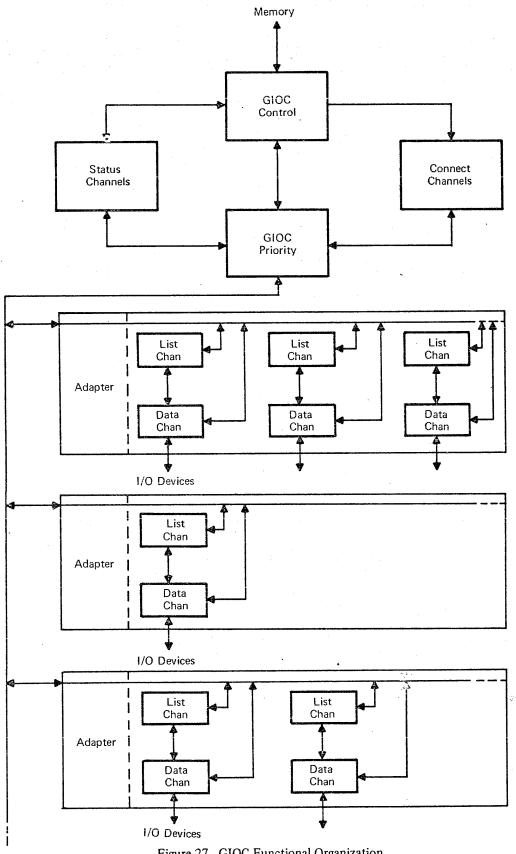

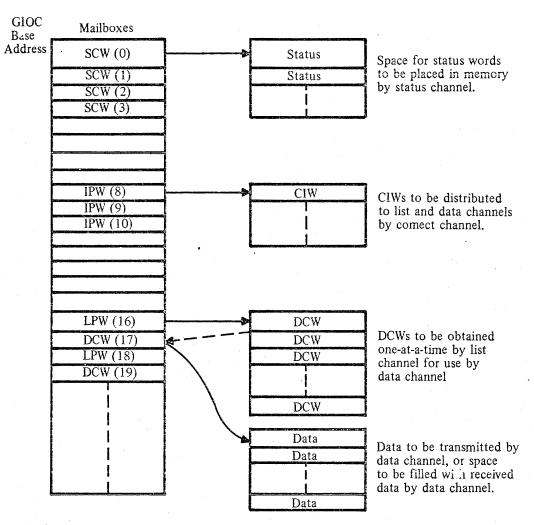

The GIOC modules handle all input/output for peripherals and terminals. (Note that the extended memory module is independent of the GIOC.) Input/output operations on a given GIOC are performed concurrently but independently of each other. The detailed actions to be performed during an input/output operation are specified in a list of control words stored in memory. Once a processor sets up the control words and initiates an input/output operation, the GIOC obtains the control words from memory and transfers data without any further processor action.

System controller modules contain the system's high-speed storage, the system's time clocks, and serve as control communication paths between the processor, GIOC, and extended memory modules. A system controller module consists of 32k, 64k, or 128k 36-bit words with a storage cycle time of one microsecond. The system can move data in groups of 6, 9, 18, 36, or 72 bits into or out of memory. The system clock consists of a calendar clock and an alarm register. The clock is located in a system controller module so that all processors can use the same clock. Thus, all processors use the same time base and perform time calculations in a consistent manner. Each system controller also contains a group of interrupt cells. These cells are used by a processor, GIOC, and extended memory module to notify the operating system of the occurrence of special events.

Memory is addressed in an interlaced manner. When a block of data is transferred into or out of memory, the data accesses are distributed among the system controller modules. This prevents a data transfer to the extended memory module, for example, from putting a heavy load on just one system controller and thereby effectively preventing other modules from using that system controller.

The extended memory module is a fixed-head disc which is used as an extension of memory. The capacity is four million words. The disc performance characteristics were carefully designed to match it to the GE-645 system. The

Figure 1. Hardware System Organization

block sizes used for information transfer are the same size as the pages handled by the processor: 64 or 1024 words. A transfer rate of 470,000 words per second was chosen to minimize the time required to move a block of data, yet not be so fast that memory is overloaded when the extended memory unit is transferring data.

The kinds of peripheral and remote terminal equipment associated with the GE-645 are:

Large moving-head disc

Magnetic drum

Magnetic card

Magnetic tape

Card reader

Card punch

Printer

Perforated tape

Typewriter-like devices

Other computers (for both normal I/O and for experimental facilities.)

Graphic displays

The system shown in Figure 1 has nine modules. The system can be expanded to a maximum of sixteen modules: eight system controller modules and a combination of processor, GIOC, and extended memory modules.

The separation of the major system functions into several modules provides hardware redundancy in case of equipment failure and facilitates system growth. The proper quantities of the various types of modules may be combined to create a system that is well suited to the workload. Peripherals and terminals also have this modular property. Peripherals which operate at high speeds and require little operator attention are connected to both GIOCs to improve system performance and provide more than one path in case a GIOC should ever malfunction.

#### **SOFTWARE**

The GE-645 software consists of the Multics operating system, language processors, application packages, and compatible GE-625/635 series programs. The general capabilities of the operating system will be described briefly.

### **OPERATING SYSTEM**

Multics (Multiplex Information and Computing Service) is an operating system being developed from research by Massachusetts Institute of Technology, Bell Telephone Laboratories, and General Electric. It draws upon the design and operating experience gained with CTSS (Compatible Time-Sharing System) at the Massachusetts Institute of Technology Computation Center and Project MAC.

The four major elements of Multics are the supervisor, the command system, the file system, and the input/output system. The operational features and objectives of these major elements are briefly described below.

The supervisor determines the sequence in which various user programs and the Multics modules serving them are executed. Each user is alloted a fair share of available processor time by the supervisor. The supervisor contains the scheduler. Under normal circumstances the scheduler guarantees that interactive users may proceed at full speed and that batch processing jobs are completed before the specified deadlines. The supervisor also measures and records the amount of system resources expended by each user.

The command system examines the input from a user's terminal looking for a command and its arguments, such as "typeout mydata". When a command and its arguments are found, they are changed from user-oriented format into hardware-executable format. The module that executes the command is then called. The command system can be used by batch users by substituting a file containing commands for a terminal.

The file system frees the user from concern over the physical location of any of his information. He refers to his programs or data by name. The file system stores and catalogs them in its storage hierarchy. If the program or data is not in core memory when it is referenced, it is automatically retrieved and made available. The file system allows all users to retain as much information as they wish in machine-accessible secondary storage. In most cases the use of removable media such as cards and magnetic tape is unnecessary. It moves little-used information to devices with longer access time to allow ample space on faster devices for more frequently-used files. The file system provides information to a user when he requests it and protects it from accidental destruction. At the same time the file system allows files to be shared among authorized users.

The input/output system uses the GIOC to perform all reading and writing of information to peripheral and terminal devices. It provides a way for users to communicate with specific devices in cases where the device-independent input/output of the file system is not suitable. The input/output system performs the code conversion, queuing, and buffering needed by specific devices.

# PART II. GE-645 SYSTEM DESCRIPTION

#### 4. HARDWARE SYSTEM CHARACTERISTICS

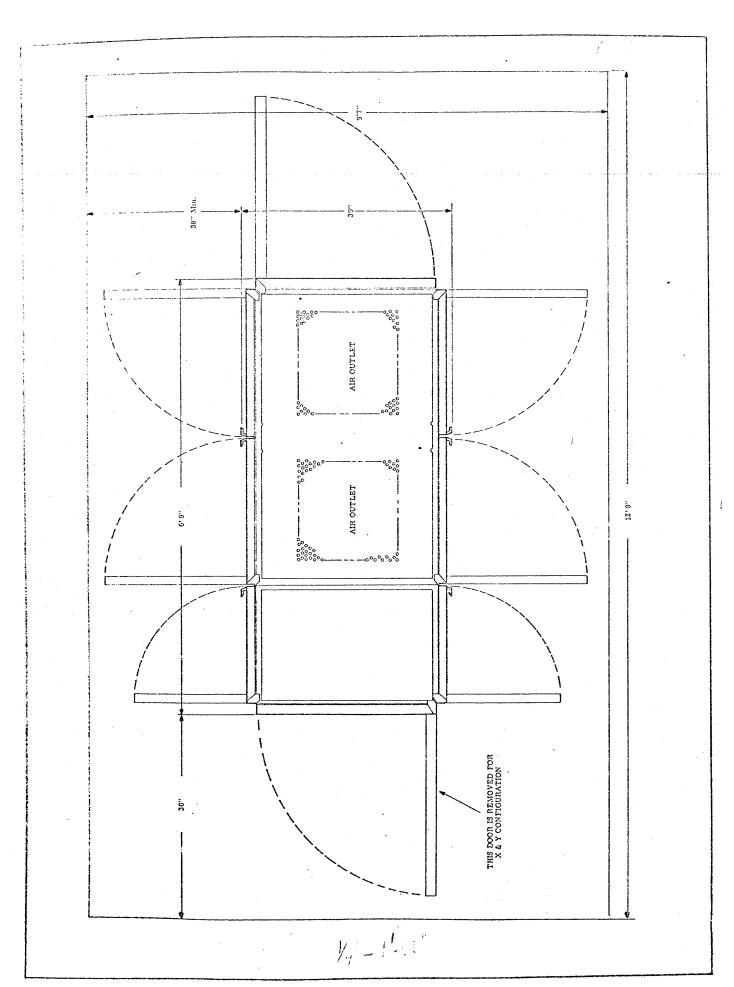

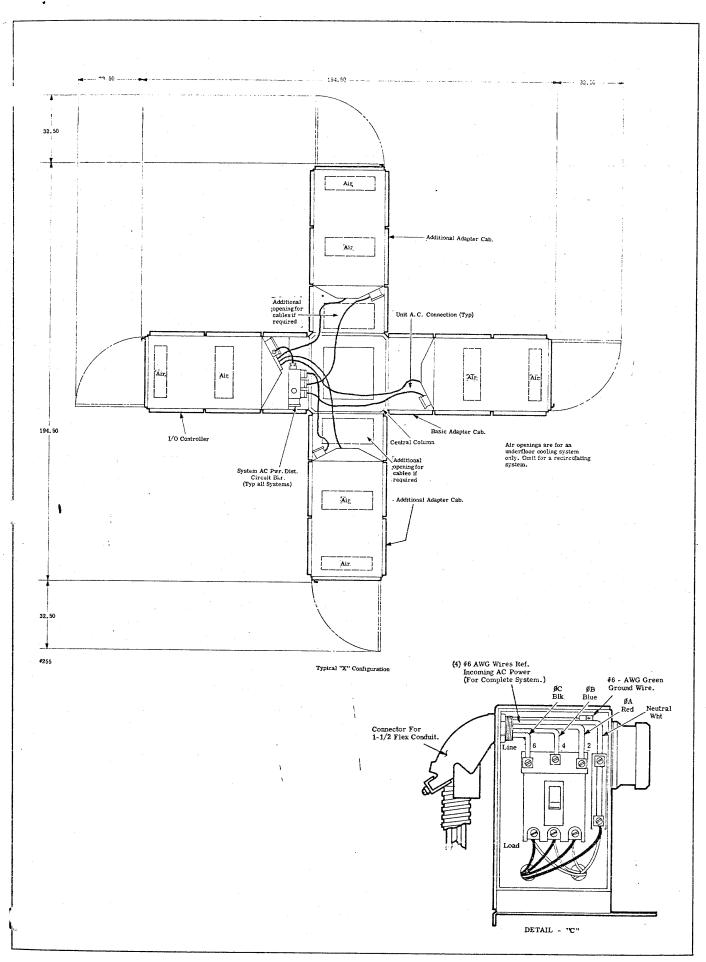

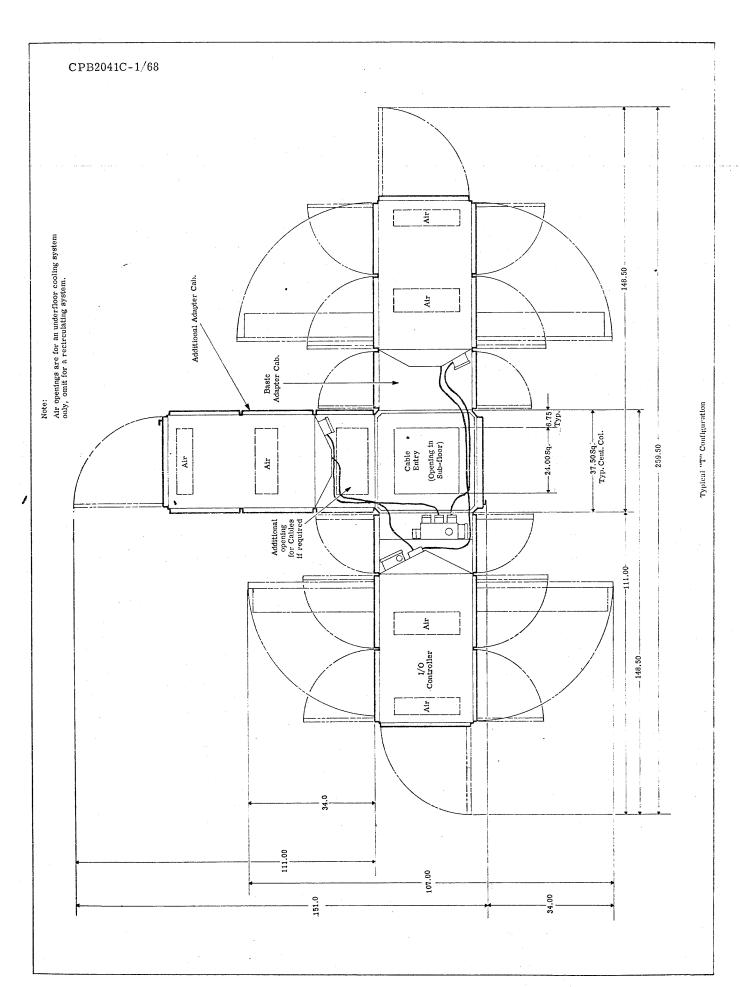

This chapter discusses several overall system features and implications so that the reader may better understand the total hardware system. The topics covered in this chapter include hardware system organization, various system configurations, and connecting input/output devices to the system.

#### HARDWARE SYSTEM ORGANIZATION

Considerable modularity is provided in the system for several reasons. The user may select various modules and peripherals in order to tailor his system to his particular work load. Modules and peripherals may be added to a system at any time without changing the users' programs or the software. Only configuration tables in Multics need to be changed. The user system may also grow in a different way. An existing module or peripheral may be replaced by a higher performance module or peripheral of the same type, yielding improved system performance. Considerable hardware redundancy also exists in a typical system so that if, for example, a processor module should malfunction and have to be removed from the system, a processor module is still left ir the system so that the system can continue operation.

The system in Figure 1 has multiple paths to many of the modules, peripherals, and terminals. Multiple paths between modules increase system performance by permitting memory interlacing. (See Chapter 5, System Controller Module, for details.) Multiple paths to peripherals also increase system performance. For example, both GIOCs can perform input/output operations with a disc subsystem simultaneously. Another significant advantage of multiple paths becomes evident when one considers hardware malfunctions. Most components of the system have more than one path to them; therefore, the malfunctioning of one component does not isolate any multiple-path component.

Peripherals such as printers and card readers are ordinarily connected to only one GIOC because they are allocated to only one user at a time. An operator can, for example, move an operation from a printer on one GIOC to a printer on a different GIOC if the first printer or its GIOC should have a problem. If desired, a single input/output path peripheral can be connected to both GIOCs. This requires another hardware unit, a peripheral switch, which is discussed later in this chapter.

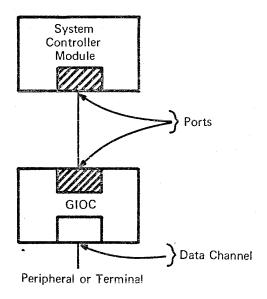

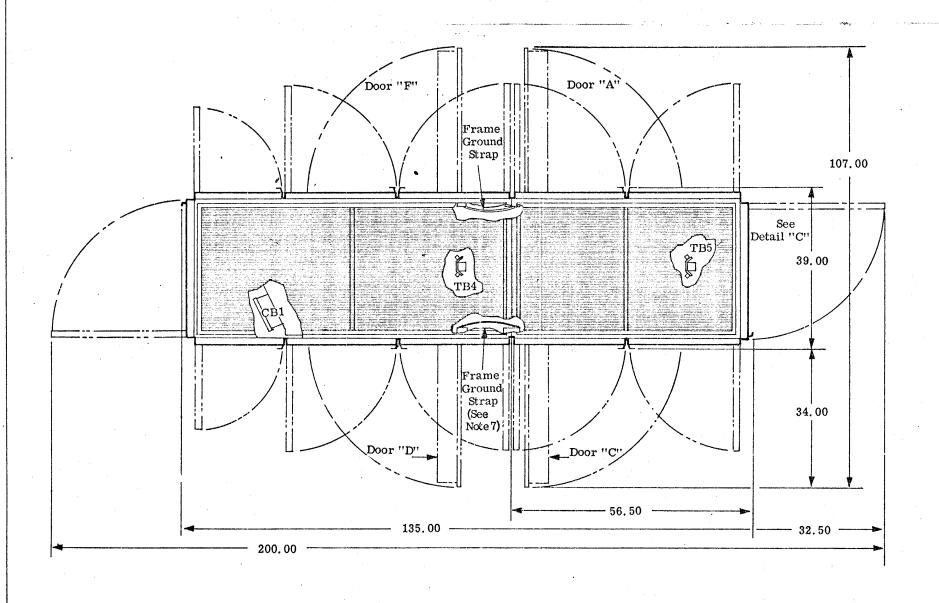

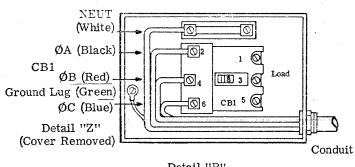

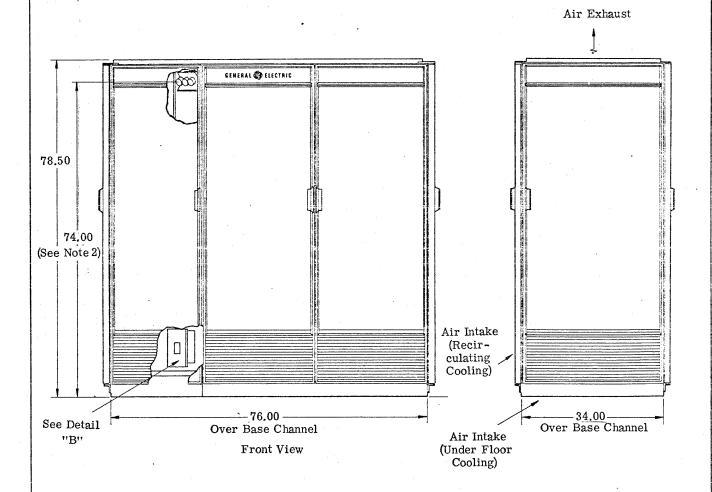

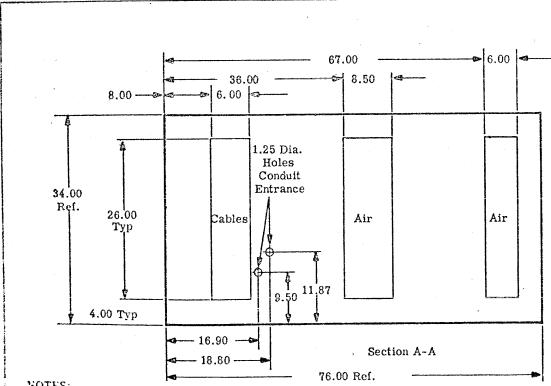

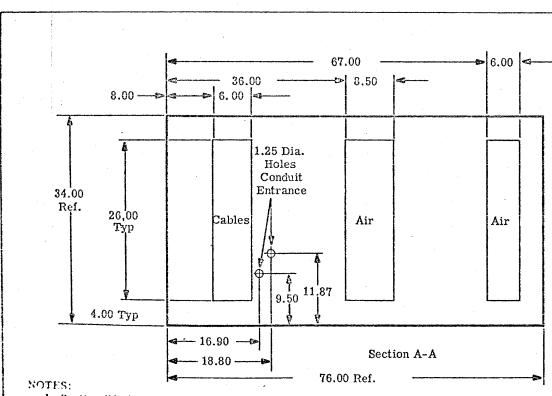

The paths between modules, peripherals, and terminals pass through "ports" in modules and "data channels" in GIOCs. Ports and data channels are terms for the hardware at the boundary of a module and are illustrated in Figure 2.

Figure 2. Distinction Between Ports and Data Channels

All types of modules — processor, GIOC, system controller and extended memory — can have up to eight ports. Thus, the maximum number of modules in a system is sixteen: eight system controller modules, and eight modules of some combination of processors, GIOCs, and extended memory units.

Multiple processors, GIOCs and extended memory modules (EMMs) allow simultaneous functions to be occurring, however a priority scheme must exist for access to a system controller. The ports on a system controller are lettered A through H and A has a higher priority than B, B higher than C, etc. The order of active module priority is established by the order in which the cables are connected to the system controller. For best system operation the priority order should be EMM, GIOC, processor. The extended memory module is highest because it has a high transfer rate and delay can result in transfer timing errors. The GIOCs are next for the same reason, except the transfer rates are lower. Under normal circumstances the processor does not experience transfer timing errors.

Control of the system involves the system configuration console and one or more teletypewriters. The system configuration console displays a summary of the configuration status of every module at the computer center. Portions of the display will be of interest to the operator. Another major function of the system configuration console is the provision of a way to initialize the system and start the bootloading operation from one central point.

Although a teletypewriter is not physically part of the system configuration console, it is a necessary part of the total system control. More than one teletypewriter may be used, with messages for certain units sent to a teletypewriter that is physically located near those units. Thus, printer messages would be typed near the printers and messages for overall control of the system would be typed near the system configuration console. The printed record of the conversations between the operator and the operating system can be quite valuable in monitoring system performance and in troubleshooting certain malfunctions. Each of the teletypewriters is connected to a GIOC through a standard communication line interface. Chapter 9 covers the system configuration console.

Processors, GIOCs and extended memory modules all form 24-bit absolute addresses. This permits use of over

16 million words of memory. Memories of this size are not available for initial GE-645 systems. The 16-million-word addressing capability exists to facilitate future growth of the system.

#### SYSTEM CONFIGURATIONS

Most of the discussions so far in this manual have centered around Figure 1. Although this figure represents a typical system, there are obviously many other possible system configurations. Some of these are shown in Table 1, where the middle column indicates the quantities that might be present in the typical system of Figure 1. Since the number of terminals that may be connected to the system is not directly reflected in the amount of hardware present in the computer center, what is shown in the table for terminals is the number of terminal-type input/output channels in the total system.

TABLE 1 SYSTEM CONFIGURATIONS

|                                                                                               | Small       | Quantities Typical Fig. 1 | Large      |

|-----------------------------------------------------------------------------------------------|-------------|---------------------------|------------|

| System Configuration Console                                                                  | 1           | 1,                        | 2          |

| Processor                                                                                     | 1           | 2                         | 4          |

| GIOC                                                                                          | 1           | 2                         | 3          |

| System Controller Number of modules Total capacity (Words)                                    | 2<br>128k   | 4<br>256k                 | 8<br>1024k |

| Extended Memory Unit<br>Number of modules<br>Total capacity (Words)                           | 1<br>4096k  | 1<br>4096k                | 1<br>4096k |

| Fixed disc (words)                                                                            | 33M         | 67M                       | 134M       |

| Magnetic card (words)                                                                         | <del></del> | 113M                      | . 226M     |

| Magnetic tape handlers                                                                        | 4           | 16                        | 32         |

| Printers                                                                                      | 2           | 4                         | 6          |

| Card Readers                                                                                  | 1           | 2                         | 3          |

| Card Punches                                                                                  | 1           | . 2                       | 2          |

| Perforated Tape                                                                               |             | . 1                       | 2          |

| Channels for teletypewriters                                                                  | 64          | 192                       | 384        |

| Channels for voice-grade communication lines for remote terminals such as DATANET*-760 GE-115 | . —         | 12                        | 18         |

\* Reg. Trademark of General Electric Company

\* Reg. Trademark of General Electric Company

\* M = million

It is quite important that the reader realize that the quantities shown in Table 1 illustrate only three of the many possible system configurations. The actual quantities to order for a particular installation depend strongly on the workload and applications to be run at that installation. One installation may need more mass storage and fewer terminal channels than the quantities shown, while another installation might need more printers and magnetic tapes and fewer terminal channels. A dedicated time sharing system might require more terminal channels and disc storage but fewer tapes, printers and card equipment. Also, the functional configuration of a particular installation can be changed from hour to hour from the system configuration console.

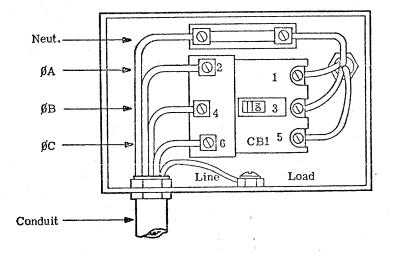

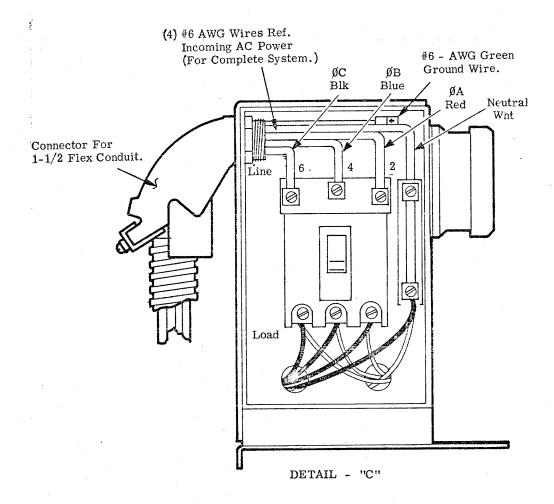

# CONNECTING INPUT/OUTPUT DEVICES TO THE SYSTEM

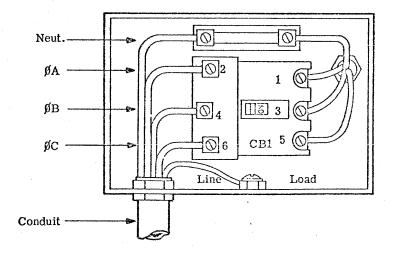

There are several ways to connect both peripherals and terminals to a GE-645 system. These are briefly discussed to show the reader how peripherals and terminals may be connected to best suit his needs.

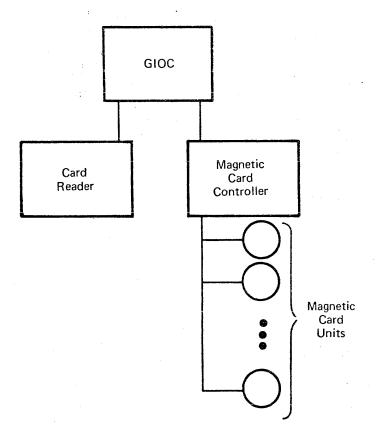

Figure 3 illustrates the connection of single-channel peripherals to a GIOC. Both single device (card reader) and multiple device (magnetic card) subsystems are shown.

Figure 3. Single-Channel Peripherals Connected to a GIOC

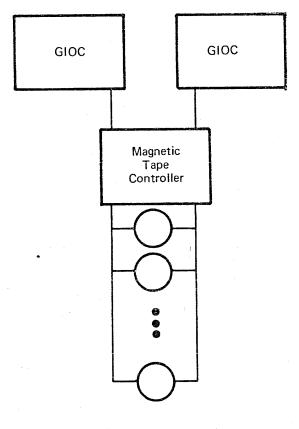

System performance is improved by using more than one input/output channel for multiple-device subsystems. An example is the dual channel magnetic tape subsystem shown in Figure 4. Two independent operations may take place simultaneously, and either GIOC may use any tape handler.

Figure 4. Multiple-Channel Peripheral Connected to two GIOC's

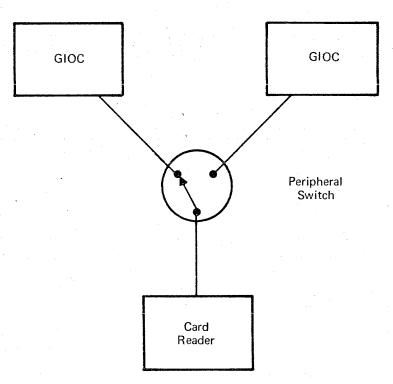

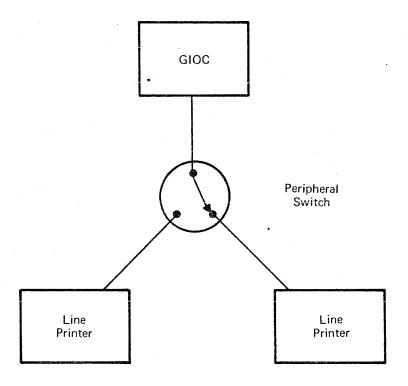

Additional flexibility is available by using a peripheral switch. Details on peripheral switches are given in Chapter 10. Briefly, a peripheral switch provides a rapid way to disconnect a peripheral from one GIOC and connect it to another GIOC and vice-versa. Two examples of this are given in Figures 5 and 6. With these basic elements more complex switching configuration (i.e. cross bar) can be produced to meet specific site requirements.

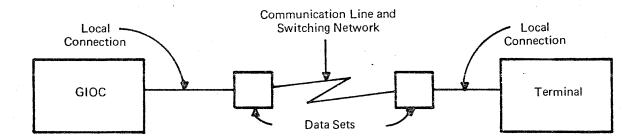

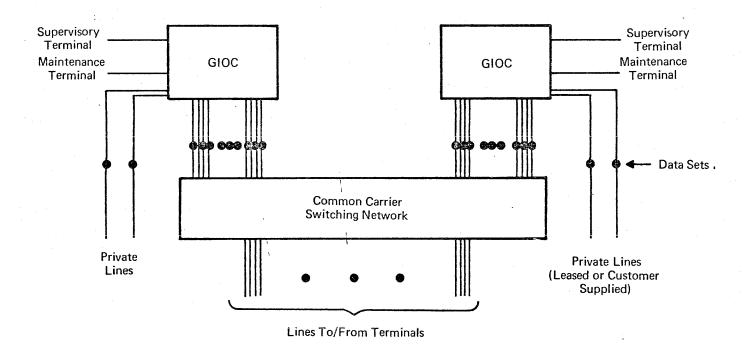

Terminals may also be connected to the system in several ways. In general, the user at a terminal will dial into the system in order to become connected. There are many possible paths through the switching network. Depending on the path taken, the user may be connected to either GIOC. And since many of the paths go to the same GIOC, his connection may be to any one of several channels within the GIOC. In order to dial in, the user must have a data set in his terminal. The general data set usage is illustrated in Figure 7.

Figure 5. A Peripheral Switch and Two GIOC's

Figure 6. A Peripheral Switch and Two Peripherals

Figure 7. General Data Set Usage

A distinction must be made between the number of terminals which have the capability of being connected to the system and the maximum number of terminals which may be connected at any given time. The former may be far larger than the latter. As an example, suppose that a system is capable of connecting and operating 200 terminals simultaneously. There could be 2,000 terminals which, at one time or another, are able to be connected to the system. However, as long as not more

than 10 percent of these users wish to be connected to the system at any given moment, there is no problem or conflict.

Normally a terminal is connected to a GIOC through a common carrier switching network as has been discussed. In certain situations, the terminal may bypass the switching network and utilize a private line (see Figure 8).

Figure 8. Bypassing the Switching Network

### 5. SYSTEM CONTROLLER MODULE

The system controller modules serve as the center for communications between the other modules in the GE-645 system by providing the following functions:

- Core memory for storage of instructions, control words, and data.

- Central point for forwarding control signals from one active module to another.

- System clock for providing data and time-of-day information, together with the ability to interrupt a processor module at a predetermined time.

Each system controller has up to eight ports for connection to processors, GIOCs and extended memory modules. One of these ports is designated as the control port, and the processor connected to that port is called the control processor. Thus each system controller has a control processor.

#### STORAGE FUNCTION

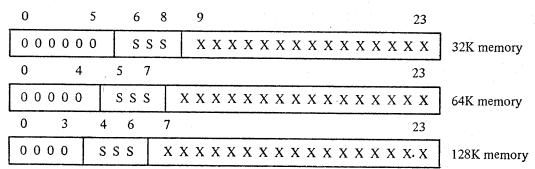

A system controller may contain 32k, 64k, or 128k of 36-bit words (plus parity), and has a cycle time of one microsecond. Either one or two words can be read or written in one memory access. It is also possible to store one 6-bit or 9-bit character in a word without disturbing the other characters in the same word.

In order to store or retrieve information, a processor, GIOC, or extended memory module sends a command, and address, and the necessary data to the appropriate system controller. The system controller executes the command and either stores the received data or sends the desired data to the requesting module. The requesting module performs the conversion from relative to absolute addresses, when this conversion is necessary, before the address is sent to the system controller.

Five commands are used by the processors, GIOCs, and extended memory controllers for data transfer:

Read Restore, Single precision (not used by extended controllers)

Read Restore, Double precision

Clear Write, Single precision

Clear Write, Double precision

Read Alter Rewrite (used only by processor)

The Read Alter Rewrite command makes it possible for a processor to read and alter the contents of a memory location during a single memory cycle, so that no other active unit can gain access to that location while it is being altered. This is a very useful characteristic of the GE-645 in a multi-processor environment.

A typical GE-645 system has more than one system controller. Memory access requests are distributed among the various system controllers by a memory interlace technique. This equalizes the load among the system controllers and increases system performance by decreasing the competition and queueing of requests for the same physical system controller. Although the circuitry that controls interlacing is located in the processors, GIOCs, and extended memory modules, interlacing is discussed in this chapter because of its close connection with the storage function.

There can be two-way interlace, four-way interlace, or no interlace. The choice is a basic parameter of the system configuration, normally established at the system configuration console. Memory addressing by the hardware is actually done by pairs of words, so it is more correct to speak of pairs of memory addresses. Therefore, with four system controllers, A, B, C, and D, and no interlacing, sequential pairs of addresses fall in succession into system controller A until it has been filled, then start filling system controller B, etc. Two-way interlace has sequential pairs of addresses located so that the first pair is in system controller A, the second pair in B, and the third pair in A, etc. With four-way interlace, the location of sequential pairs of addresses rotates among the four system controllers — A, B, C, D, A, B, C, D, etc. The effect of the types of interlace is summarized in Table 2, with system controller A arbitrarily selected as the initial system controller.

#### CONTROL SIGNALS

#### **CONNECT INSTRUCTIONS**

When a processor executes a Connect instruction, the system controller which contains the Connect Operand Word immediately forwards the Connect Operand Word and a Connect signal to the module specified in Connect Operand Word. The recipient module may be a GIOC, an extended memory unit, or another processor.

# INTERRUPT CELLS

A group of 32 interrupt cells are located in each system controller. These interrupt cells are used by the GE-645 hardware modules to notify Multics that some event has occurred which needs attention. An interrupt cell may be set by a GIOC, an extended memory unit, a processor, or by the system clock. When an interrupt cell is set, the system controller notifies its control processor of

COMPATIBLES / 600 \_\_\_

# TABLE 2 EXAMPLE OF TYPES OF INTERLACE

| Word Pair     | None              |                      | Type of Interlace<br>Two-Way | Four-Way          |                  |

|---------------|-------------------|----------------------|------------------------------|-------------------|------------------|

| START+ 0, 1   | System Controller | Α .                  | System Controller A          | System Controller | A                |

| START+ 2, 3   |                   | A                    | В                            |                   | В                |

| START+ 4, 5   |                   | Α                    | Α                            |                   | $\mathbf{C}^{-}$ |

| START+ 6, 7   |                   | <b>A</b>             | В                            |                   | D                |

| START+ 8, 9   |                   | $\mathbf{A}^{\cdot}$ | Α                            |                   | A                |

| START+ 10, 11 |                   | Α                    | В                            | •                 | В                |

| START+ 12, 13 |                   | A                    | A                            |                   | C                |

| START+ 14, 15 |                   | A                    | В                            |                   | D                |

this fact, along with the cell number, so that the source of the interrupt can be identified. The control processor stops what it is doing and jumps to a software routine designed for handling that particular interrupt cell. Multics can temporarily inhibit the interrupting action of any interrupt cell or cells with the aid of a 32-bit interrupt mask register that is also located in each system controller, or by making use of the interrupt-inhibit bit in each instruction.

#### SYSTEM CLOCK

The system clock consists of a calendar clock and an alarm register. The calendar clock is a 52-bit binary counter which counts at one microsecond intervals, providing a capacity greater than 142 years without overflowing. The program can read the contents of the calendar clock with a precision of one microsecond. The clock accuracy is better than 5 parts per million (3 seconds/week) and can be improved by using an external stable reference.

The 142-year capacity of the calendar clock makes it possible for the software to operate on Universal Time. To accomplish this the General Electric field engineer must set the calendar clock to the number of microseconds since midnight, January 1, 1901, Greenwich Mean Time. Although a processor can read the calendar clock at any time, provision for setting it under program control is deliberately omitted, so that programming errors or hardware malfunctions outside the clock cannot destroy the current time.

The alarm register has the same 142-year capacity and can be set by the software. The value in the alarm register has a resolution of 64 microseconds and is continuously compared to the changing time in the calendar clock by special hardware in the system clock. When the calendar clock reaches the time preset in the alarm register, an interrupt cell is set. This causes a program interrupt and notifies Multics that the desired instant of time has arrived.

#### 6. PROCESSOR MODULE

Most of the advanced capabilities of the GE-645 which are seen by its users are provided by the processor. The processor module has full program execution capability and conducts all actual computational processing within the GE-645 system. The processor performs instruction fetching, address preparation, memory protection, data fetching and data storing. These functions are overlaped to provide the highest rate of instruction execution.

The GE-645 Processor (CP8031) contains all the general features of the GE-635 Processor except for Base Address Register and the two associated instructions (See Appendix A) plus the following additional features:

- hardware for handling segments and pages.

- hardware to generate 24-bit memory addresses.

- an associative memory to speed up address generation for segments and pages.

- ten program addressable registers used in segment and page address preparation.

- more extensive address modification capability.

- instructions to handle the segmentation and paging hardware and the system clock.

- several levels of memory access permission.

- several new processor faults.

- a modified Timer Register to also count memory accesses.

- a maximum of eight ports for connection to System Controller modules.

- logic for remote configuration from system configuration console.

- storage for up to four instructions within the processor in various stages of address preparation and execution.

#### MODES OF OPERATION

The processor has three modes of operation: absolute, master and slave. All instructions are available in absolute and master modes. Most, but not all, of the instructions are available in slave mode. General users are restricted to the slave mode and hence are prevented from executing any instructions that will damage other programs or Multics. Privileged instructions such as those which operate upon the descriptor base register, the system clocks, and input/output devices are available only in the absolute and master modes.

The full segmentation and paging capability of the processor is used in the master and slave modes for fetching instructions and operands. The addressing in the absolute mode does not use any of the segmentation and paging capability except for a limited case of operand references.

#### REGISTER DESCRIPTIONS

The program-accessible processor registers are:

| Quantity | Name                     | Length       |

|----------|--------------------------|--------------|

| . 1      | Accumulator Register     | 36 bits      |

| 1        | Quotient Register        | 36 bits      |

| 1        | Exponent Register        | 8 bits       |

| 8 •      | Index Registers          | 18 bits each |

| . 1      | Timer Register           | 24 bits      |

| 1        | Instruction Counter      | 18 bits      |

| 1        | Indicator Register       | 18 bits      |

| 1        | Descriptor Base Register | 29 bits      |

| 1        | Procedure Base Register  | 18 bits      |

| 8        | Address Base Registers   | 24 bits each |

#### The Accumulator (A) Register is used:

- As an operand register for all classes of single-precision (36 bit) operations. For floating-point operations, the fixed point part is in the A register and the exponent is in the Exponent Register.

- For address modification. Each half of the A register can hold an index value. The left half is called A Upper (AU) and the right half A Lower (AL).

The Quotient (Q) Register is used in the same ways as the A register, with the halves called QU and QL.

The AQ Register, which is the combined A and Q registers, is used as the operand register for all double-precision (72 bit) operations. For floating-point operations, the fixed point part is in the A or AQ register and the exponent is in the exponent register.

The Exponent Register holds the exponent in floating-point operations with the fixed point part in either the A or the AQ register.

COMPATIBLES / 600.

The <u>Index Registers</u> are used during address modification. These registers can also be used as half-precision fixed point operand registers.

The <u>Timer Register (TR)</u> counts a 64 kHz clock (15.625 microsecond interval) as in the GE-635, or can be switched to count the number of memory access cycles. Multics uses the timer register to count memory accesses for a measurement of processor utilization. The register can be set to an initial value which, when counted down to zero, causes a processor fault in the slave mode. This register should not be confused with the system clock in the System Controller Module.

The <u>Instruction Counter (IC)</u> partially specifies the next instruction to be executed. Details will be discussed in the segmentation portion of this chapter.

The <u>Indicator Register</u> contains a group of indicators that specify or hold certain processor states.

The various indicators are:

Zero

Negative

Carry

Overflow

**Exponent Overflow**

Exponent Underflow

Overflow Mask (can inhibit overflow recognition)

Tally Runout

Parity Error

Parity Mask (can inhibit parity error recognition)

Absolute Mode (use only IC for instruction fetching)

The Descriptor Base Register (DBR), Procedure Base Register (PBR), and Address Base Registers (ABRn) are used in performing relative addressing. Their description is postponed until segmentation is discussed later in this chapter.

#### INSTRUCTION REPERTOIRE

For the GE-645, there are a possible 512 instructions of which 404 have been assigned. This leaves 108 operation codes for upward growth. A list of the assigned instructions is included in Appendix A.

The GE-645 instructions are listed and described according to operations for: data movement, arithmetic, logical, comparison, control, shifting, and special operations. Many of the GE-645 instructions are familiar to experienced programmers of large scale computers. In addition to the familiar ones, there are other instructions to facilitate: segmentation and paging, saving and restoring of registers, character handling, decision making, and list processing.

#### INSTRUCTION FORMAT

Most of the instructions have the following format. A few special instructions have a format adapted to their unique functions.

| <br>0 1            | 17 | 18 |         | 26 | 27 | 28 · | 29 | 30    | 35  |

|--------------------|----|----|---------|----|----|------|----|-------|-----|

| Address or operand |    | •  | Op Code |    | 0  | i    | r  | Modif | ier |

| 18 bits            |    |    | 9 bits  |    |    |      |    | 6 bit | s   |

The address or operand field specifies information used in addressing an operand or contains the operand.

The operation code field specifies the operation to be performed and the registers to be used.

Bit 27 is not used and must be zero for upward compatibility with future systems.

Bit 28 is used under certain conditions to inhibit a program interrupt.

Bit 29 specifies how the address field is to be interpreted. See Base Registers, Page 22.

The modifier field specifies the kind of address modification to be used. Possibilities include: (1) no modification, (2) which register to use, (3) indirect or not, and (4) several special-purpose modification methods that significantly increase the power of the instructions.

#### DATA MOVEMENT OPERATION

These instructions move data between the system's core memory and the processor registers, indicators, and associative memory. They include half, single, and double-precision operations. Also 6 and 9 bit characters can be handled.

#### ARITHMETIC OPERATIONS

These instructions include fixed and floating point; half, single, and double-precision; and placement of results in registers or memory.

BOMPATIBLES/600

#### LOGICAL OPERATIONS

These instructions include single and double-precision, and placement of results in registers or memory.

#### COMPARISON OPERATIONS

These instructions include logical, fixed, and floating-point comparisons on half, single, and double-precision operands. The results of a comparison are saved in certain indicators for later testing by control instructions.

#### CONTROL OPERATIONS

These instructions include normal transfers, conditional transfers, and some special instructions which simultaneously transfer control and restore various registers.

#### SHIFTING OPERATIONS

These operations include shift and rotate instructions using the A, Q, and AQ registers.

#### SPECIAL OPERATIONS

An important instruction in this class is the Connect, which initiates all input/output operations and provides a method of communicating between processors. Another group of instructions enables one or two instructions to be repeated without having to continually fetch the instruction(s) from memory. Other instructions provide a way to execute one or two instructions which are not in the sequential string of instructions being executed, provide entries to the operating system, convert a binary number to its binary-coded-decimal equivalent, and convert a Gray Code word to a binary equivalent.

#### ADDRESS MODIFICATION

A comprehensive set of address modification features includes both modification of addresses by the contents of registers and multi-level indirect addressing. The general format of the indirect words is:

| _ | 0       | 17 | 18 |       | 29 | 30   | 35   |

|---|---------|----|----|-------|----|------|------|

|   | Address |    |    | Tally |    | Modi | fier |

There are four classes of address modification: (1) register, (2) register then indirect, (3) indirect then register, and (4) indirect then tally. These are described briefly below. Modification registers are the 8 index registers, plus the AU, AL, QU, QL, and IC registers. Direct operand modifiers may be used to treat the address directly as the operand.

#### REGISTER MODIFICATION (R)

An effective address is produced by adding the contents of a modification register to the contents of the instruction's address field.

#### REGISTER THEN INDIRECT (RI)

The **indicated** register modification of the address is performed (as with R) to obtain an indirect word, then **the** modification specified in the indirect word is conducted. Address modification in an indirect word is specified in the same manner as in an instruction word.

#### INDIPECT THEN REGISTER (IR)

The indirect word is obtained using the original address, then the modification specified in the indirect word is conducted. Upon completion of the indirect addressing string the indicated register modification in the last IR word (instruction or indirect word) encountered is performed.

#### INDIRECT THEN TALLY (IT)

The indirect word is obtained using the original address. Then one of the 15 possible sequences below is performed.

#### Mnemonic

- I Indirect The address field of the indirect word is used for the operand address without further change. Tally and modifier fields are unused.

- ID Increment Address, Decrement Tally The address field of the indirect word is incremented by 1 and the tally is decremented by 1 after the address field is used for the operand address. The modifier field is unused.

- AD Add Delta This is the same as ID except delta is added to the address. Delta is the value in the modifier field of the indirect word.

- IDC Increment Address, Decrement Tally and Continue This is the same as ID except the address field in the indirect word specified another indirect word and the modifier field is interpreted in the normal manner.

- DI Decrement Address, Increment Tally The address field of the indirect word is decremented by 1 and the tally is incremented by 1 before the address field is used for the operand address. The modifier field is unused.

COMPATIBLES / 600.

- SD <u>Subtract Delta</u> This is the same as DI except delta is subtracted from the address. Delta is the value in the modifier field of the indirect word.

- Decrement Address, Increment Tally and Continue This is the same as DI except the address field in the indirect word specifies that of another indirect word and the modifier field is interpreted in the normal manner.

- CI <u>Character from Indirect</u> The indirect word specifies an address and a character position which are used for an operand character address without change. The character size (6 or 9 bits) and position is specified by the modifier field. The tally field is unused.

- SC Sequence Character The character position (in modifier field) is incremented by 1 and the tally is decremented by 1 after the indirect word address field and character position are used for the operand character address. When the character position tries to exceed the maximum value (3 or 5) it is reset to 0, and the address field is incremented by 1. The character size is also specified in the modifier field.

- SCR Sequence Character Reversed This is the reverse of SC. The character position is decremented by 1 and the tally is incremented by 1 before the indirect word address field and character position are used for the operand character address. When the character position tries to go negative it is set to the maximum value (3 or 5), and the address field is decremented by 1. The character size is also specified in the modifier field.

- Fault 1 This modifier causes Processor Fault Tag 1. (See Interrupt and Fault section of this chapter.)

- F2 Fault 2 This modifier causes Processor Fault Tag 2.

- F3 Fault 3 This modifier causes Processor Fault Tag 3.

- ITS Indirect to Segment This will be discussed in the Segmentation section of this chapter.

- ITB Indirect to Base This will be discussed in the Segmentation section of this chapter.

#### **SEGMENTATION**

Segmentation has been used in some form or other throughout the fields of computation and information processing for several years. In the GE-645, this familiar

concept takes on added power and increased significance. In the past, program segments have generally consisted of subprograms and/or storage areas, and were combined into a single program by a loader prior to execution. This method of operation provided several important advantages over compiling or assembling entire programs prior to their execution. These advantages are preserved in the GE-645 segmentation, and other capabilities are added. Some of the added capabilities are:

- The ability for the same copy of a segment to be simultaneously shared by many users without making special prearrangements.

- The ability to allow individual segments to vary dynamically in size without influencing the addressing of other segments.

- The ability to address programs larger than available core memory.

- The ability for each segment to possess unique attributes to prevent misuse.

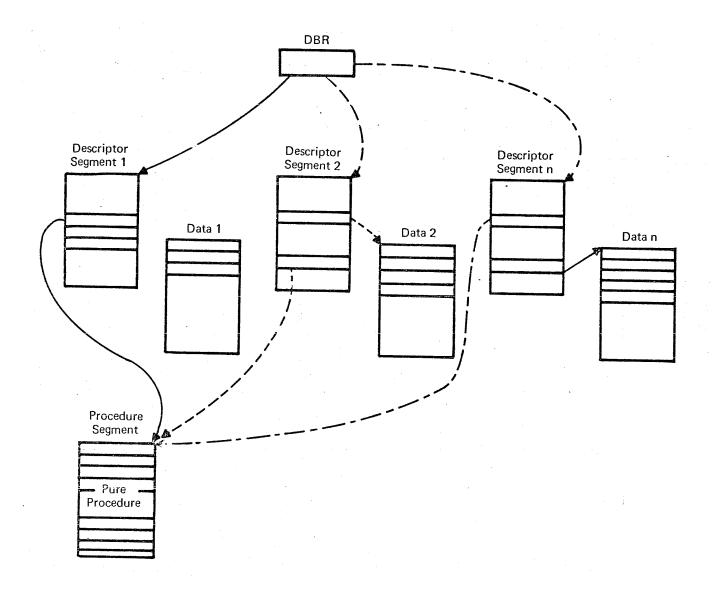

Significant among the advantages of segmentation is the facility it supplies for use of pure procedures. These are procedures which are not altered during their execution. As used in the GE-645, a segment can be identified as pure procedure and invoked by any user to perform its function on his own data. This provides two economies in the multi-user GE-645. First, only one copy of a pure procedure need exist to be shared by all its users; second, pure procedures constitute an important class of information that need never by rewritten to secondary storage.

It is often desirable to write a program that can operate on variable size data arrays. In previous computer systems it has been necessary to use complex overlaying techniques or to place an upper bound on the size of arrays that could be handled by such programs. In the GE-645, variable arrays can be assigned to separate segments so that each can vary in size from one up to 218 words without any special provision being made by the computer users.

A GE-645 program consists of a variety of segments, each of which has a unique name. These names are converted to a segment number of Multics at execution time. The user may view each of his segments as if it were stored in an independent core memory. Each segment has its own origin which can be addressed as location zero. The size of each segment may vary without affecting the addressing in other segments.

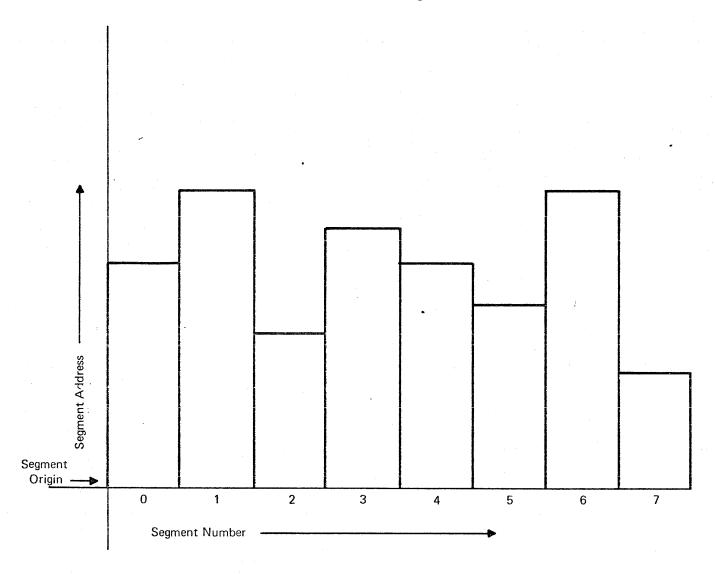

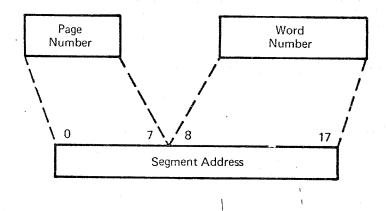

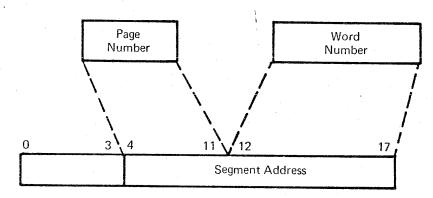

The words contained within a segment are addressed by an 18-bit segment address. If a program consists of several segments, the GE-645 refers to any word in any segment according to a segment number and a segment address. Figure 9 represents schematically the GE-645 memory topology. The individual segments of a program are shown as consisting of independent variable

size storage arrays. In analogy to a rectangular coordinate system, it suggests that the location of any word may be specified by two coordinates: a segment number and a segment address.

Figure 9. Two-Coordinate Addressing in the GE-645

#### **DESCRIPTOR SEGMENT**

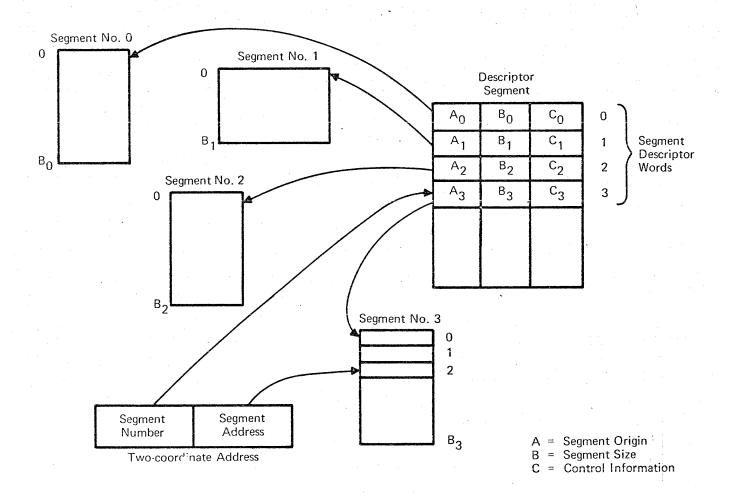

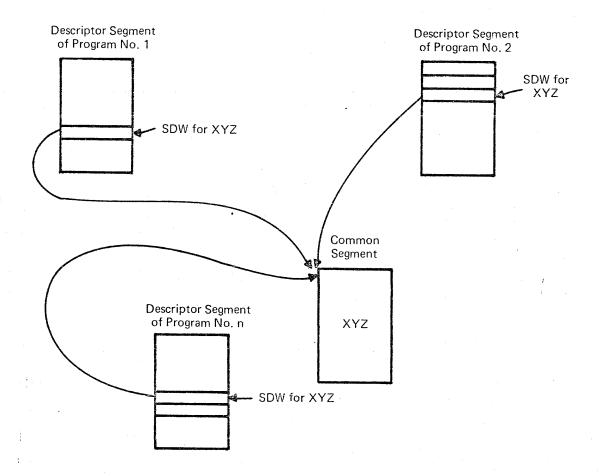

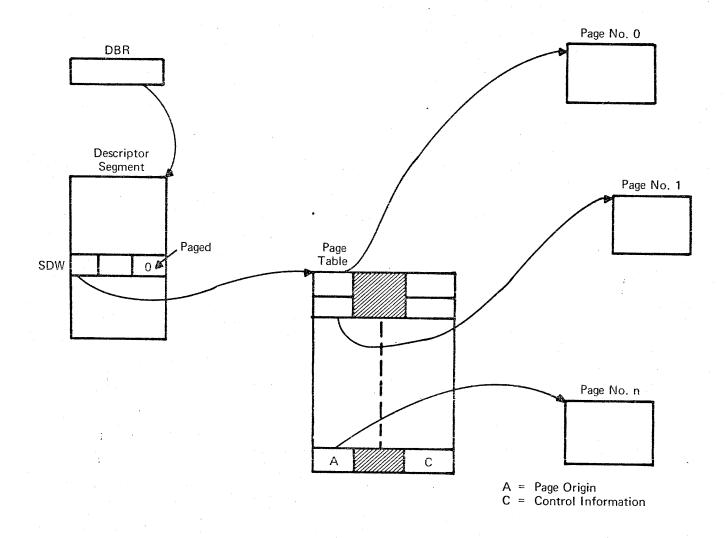

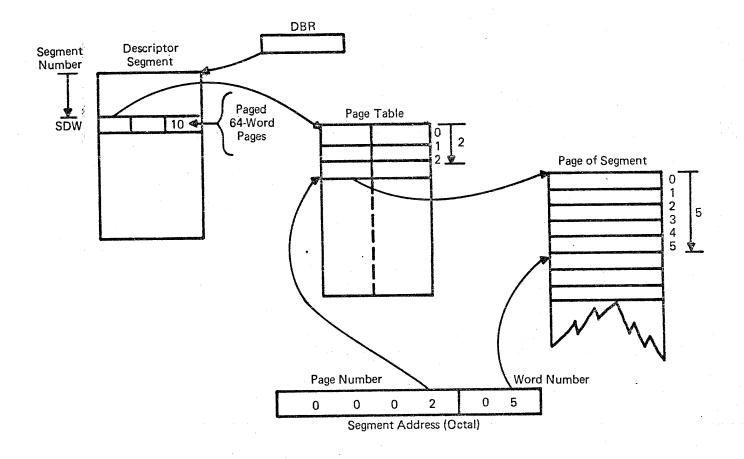

A descriptor segment is the processor's means of relating program references to absolute memory locations. Multics provides a descriptor segment for each program. The descriptor segment contains one word called a segment descriptor word (SDW) for each segment being used by the program. Each SDW in the descriptor segment indicates the absolute location of the origin, and gives size and control information about the segment to which it corresponds (See Figure 10).

The segment number used in locating a segment refers to the location of SDW in the descriptor segment. This SDW contains the segment origin. When a reference is made using a two-coordinate address, the processor retrieves the segment origin from the descriptor segment and adds the segment address to it. The result is the absolute address of the desired word. This is illustrated in Figure 10 and in numerous examples which follow. The segment address is compared to the segment size to verify that the reference is within the specified allowable address range of the segment.

Figure 10. The Descriptor Segment Facilitates Two-Coordinate Addressing

Since the descriptor segment can be up to  $2^{18}$  words long, the two-coordinate addressing of the GE-645 allows a program to reference up to  $2^{18}$  segments.

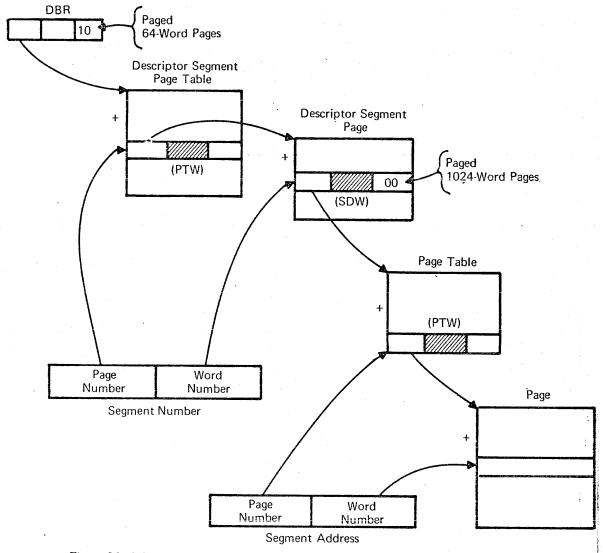

#### BASE REGISTERS

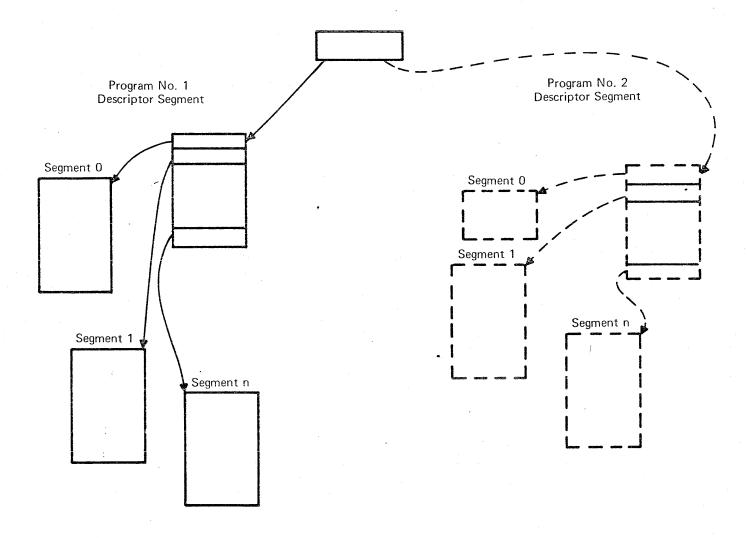

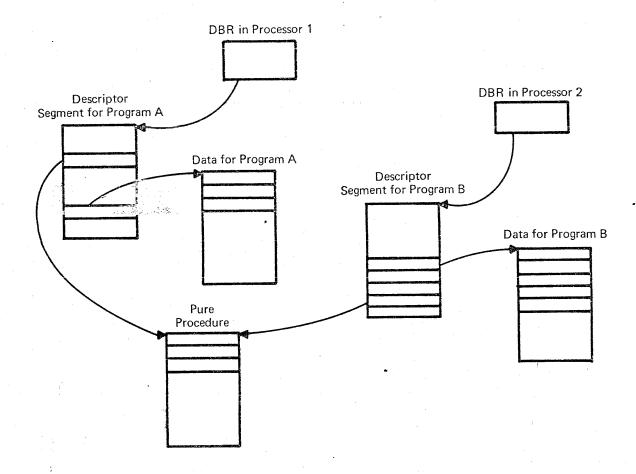

The location of the descriptor segment for the process in execution is always known to the processor. Its origin and size are stored in a special high-speed register called the descriptor base register (DBR). (See Figure 11.) When control of the processor is switched from one user to another, the DBR is reloaded to point to the descriptor segment belonging to the new user. In this way all of the relative addressing information for all of the segments accessible to the program in execution are changed by simply changing the contents of one register.

The DBR, like the descriptor segment, is accessible only to Multics. This means it cannot be manipulated in order

to gain unauthorized access to segments of another program. Also, storage belonging to another program cannot be accidentally damaged.

A user may utilize segments in various ways depending upon his objectives. A simple way of using segments is to place instructions in one class of segments called procedure segments, and variable information in another class of segments called data segments. The GE-645 provides convenient methods for performing necessary references between such segments.

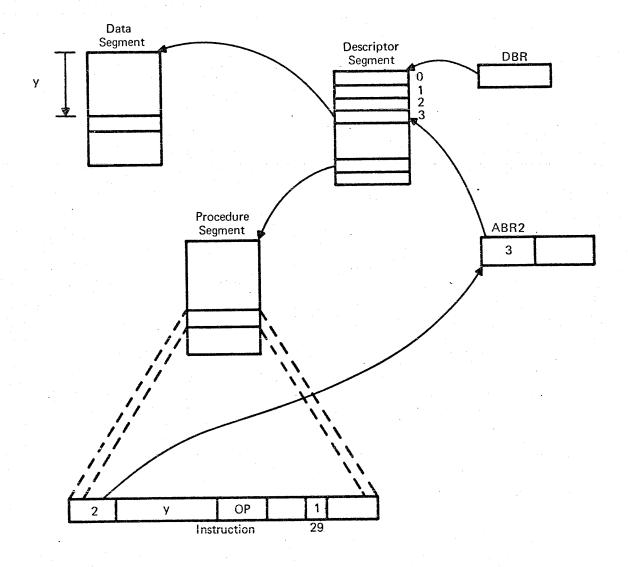

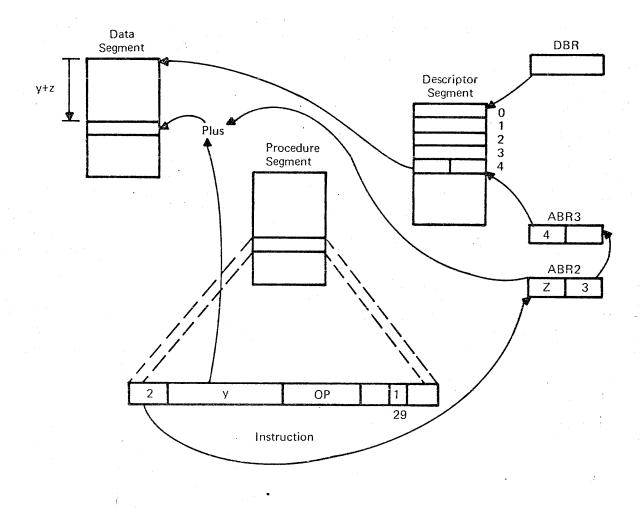

There are eight address base registers (ABR's) in each processor. They may be used to specify the segment number portion of a two-coordinate address as in Figure 12. If bit 29 of an instruction is set to 1, this signals the processor to interpret the three high-order bits of the address field as an address base register number. The ABR will contain the segment number to be addressed, and bits three through seventeen of the instruction (y in the figure) will contain the segment address.

Figure 11. The DBR Determines which Segments the Processor May Access

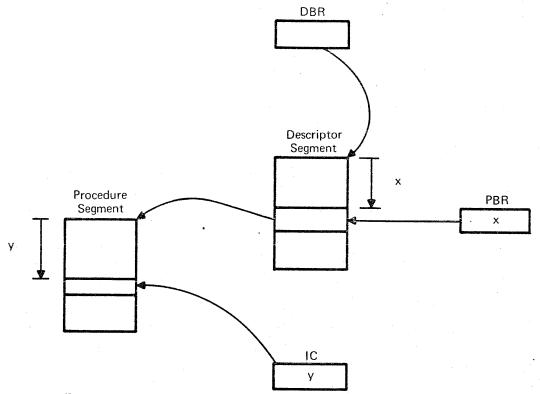

The procedure base register (PBR) contains the segment number of the segment from which the processor is to retrieve instructions. The PBR functions exactly like an ABR except the PBR is never referenced explicitly in a user program. The processor automatically refers to the PBR in the execution of every instruction. The instruction counter (IC) contains the segment address and the PBR contains the segment number of the two-coordinate address of the next instruction. See Figure 13.

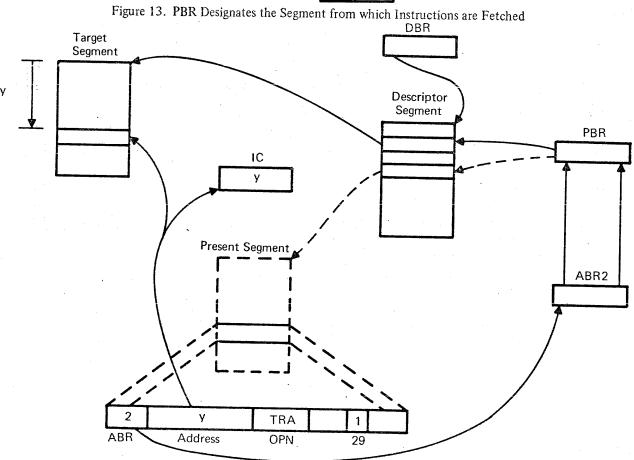

The PBR is automatically changed to contain the segment number of the target segment when a transfer between segments is performed. Figure 14 illustrates this process. In this case ABR2 contains the segment number which is placed in the PBR as part of the intersegment transfer operation.

#### INDIRECT TO PAIR MODIFIERS.

An additional method of addressing between segments is provided in the GE-645. This is the indirect to pair (IP) address modifier. The IP modifier has two variations: indirect to segment modification (ITS), and indirect to base modification (ITB).

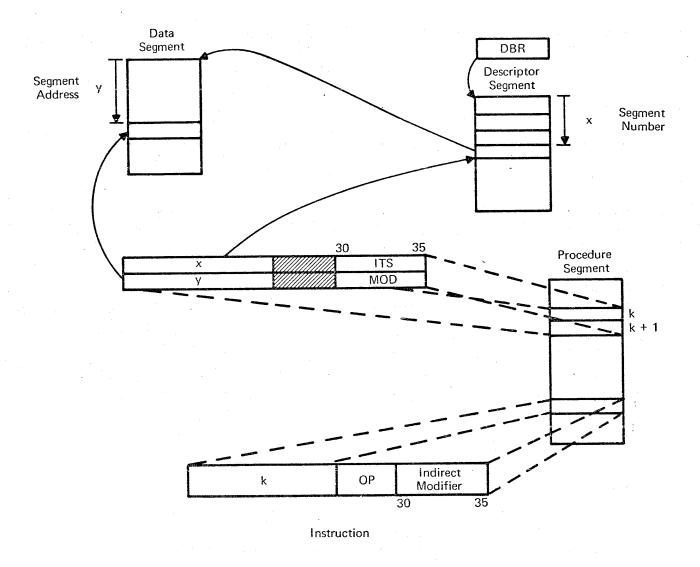

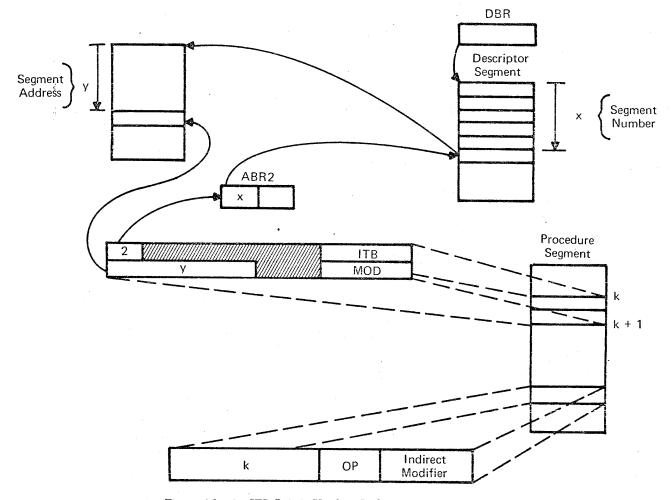

If an instruction refers indirectly (IR or RI) to a word located in an even addressed location in core memory and if the indirect word contains the bit configuration corresponding to the ITS modifier in its modifier field (bits 30-35), then the following occurs (See Figure 15).

1. Bits 0 through 17 of the indirect word are interpreted as a segment number.

Figure 12. An ABR is Used in Specifying a Two-Coordinate Address to Refer to Another Segment

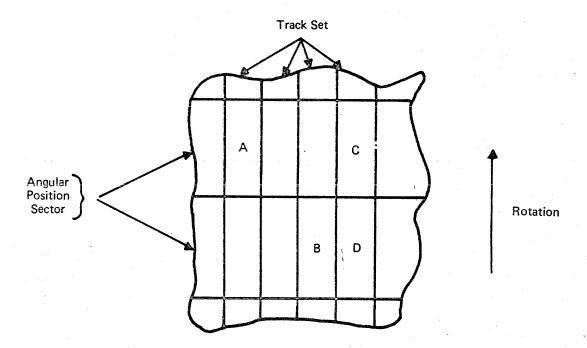

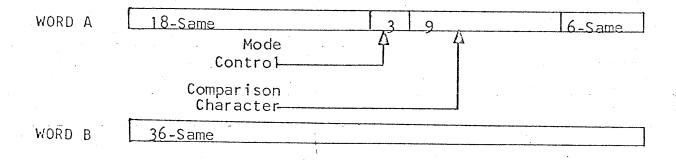

- 2. Bits 0 through 17 of the word following the indirect word are interpreted as a segment address.