## **DATA BOOK 1988**

|     | General Information |

|-----|---------------------|

|     | 16 Bit CPU Boards   |

|     | 32 Bit CPU Boards   |

|     | Memory Boards       |

|     | Controller Boards   |

|     | I/O Boards          |

|     | Development Systems |

| FRE | Software            |

|     |                     |

Accessories

UNIX is a trademark of AT&T Bell Laboratories PDOS is a trademark of Eyring Research Institute VMEPROM, FORCEbug are registered trademarks of FORCE Computers Ethernet is a registered trademark of Xerox Corporation SASI is a registered trademark of Shugart Associates

The information in this book has been carefully checked and is believed to be accurate; however, no responsibility is assumed for inaccuracies.

FORCE Computers reserves the right to make changes without further notice to any products herein to improve reliability, function or design. FORCE Computers does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. The software described herein will be provided on an "as is" basis and without warranty. FORCE Computers accepts no liability for incidental or consequential damages arising from use of the software. This Disclaimer of warranty extends to FORCE's licensee, to licensee's transferees and to licensee's customers or users and is in lieu of all warranties whether expressed, implied or statutory, including implied warranties of merchantability or fitness for a particular purpose.

© FORCE Computers All Rights Reserved First Edition November 1986 Second Edition October 1987

## **DATA BOOK 1988**

## **VMEbus Products**

# Table of contents

| General Informa  | ation                             |

|------------------|-----------------------------------|

|                  | Manufacturing                     |

|                  | Quality Assurance                 |

|                  |                                   |

| 16 Bit CPU Boar  | rds 23                            |

| 10 510 01 0 500. | Introduction                      |

|                  | Overview(s)                       |

|                  |                                   |

|                  |                                   |

|                  | SYS68K/CPU-2 3                    |

|                  | SYS68K/CPU-3 45                   |

|                  | SYS68K/CPU-4 53                   |

|                  | SYS68K/CPU-5 6                    |

|                  | SYS68K/CPU-6 69                   |

|                  |                                   |

| 32 Bit CPU Boar  | rds 7                             |

| OZ DIL OI O DOGI | Introduction                      |

|                  |                                   |

|                  | Overview(s)                       |

|                  | SYS68K/FMB 85                     |

|                  | SYS68K/CPU-21 93                  |

|                  | SYS68K/CPU-22105                  |

|                  | SYS68K/CPU-25                     |

|                  | SYS68K/CPU-26                     |

|                  | SYS68K/CPU-29                     |

|                  | SYS68K/CPU-30                     |

|                  |                                   |

|                  | SYS68K/CPU-31                     |

|                  | SYS68K/CPU-32197                  |

|                  | SYS80K/CPU-386                    |

|                  |                                   |

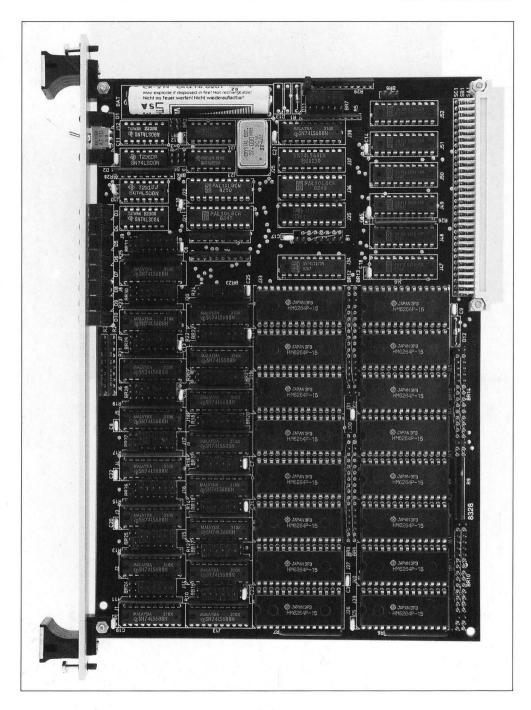

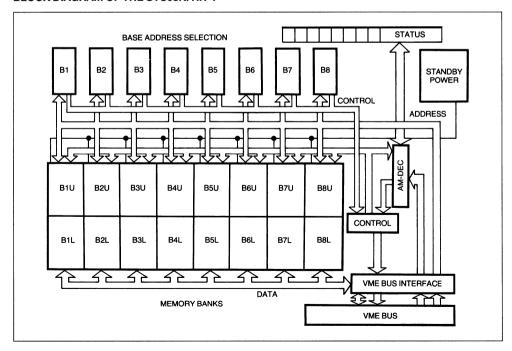

| Memory Boards    | <b>3</b> 22 <sup>.</sup>          |

|                  | Introduction                      |

|                  | Overview(s)                       |

|                  | SYS68K/DRAM-1/2                   |

|                  |                                   |

|                  | SYS68K/DRAM-E3M/S                 |

|                  | SYS68K/DRAM-E4M/S 239             |

|                  | SYS68K/DRAM-6                     |

|                  | SYS68K/SRAM-3B                    |

|                  | SYS68K/SRAM-4B                    |

|                  | SYS68K/SRAM-5/6                   |

|                  | SYS68K/RR-1                       |

|                  | SYS68K/RR-2                       |

|                  |                                   |

|                  | SYS68K/RR-3285                    |

|                  |                                   |

| Controller Boar  | <b>ds</b>                         |

|                  | Mass Memory Controller Boards 293 |

|                  | Introduction                      |

|                  | Overview(s)                       |

|                  | SYS68K/WFC-1                      |

|                  | SYS68K/ISCSI-1                    |

|                  |                                   |

|                  |                                   |

|                  |                                   |

|                  | Graphics Controller Boards        |

# Table of contents

|                  | General Controller Boards Introduction Overview(s) SYS68K/ASCU-1/2 SYS68K/ILANC-1                                                               | 343<br>344<br>347                      |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| I/O Boards       | Serial and Parallel I/O Boards Introduction Overview(s) SYS68K/PIO-1 SYS68K/OPIO-1 SYS68K/SIO-2 SYS68K/ISIO-1 SYS68K/ISIO-2 SYS68K/ISIO-2       | 361<br>363<br>364<br>367<br>373<br>385 |

|                  | Analog I/O Boards Introduction Overview(s) SYS68K/AD-10/11 SYS68K/DA-1/2                                                                        | 409                                    |

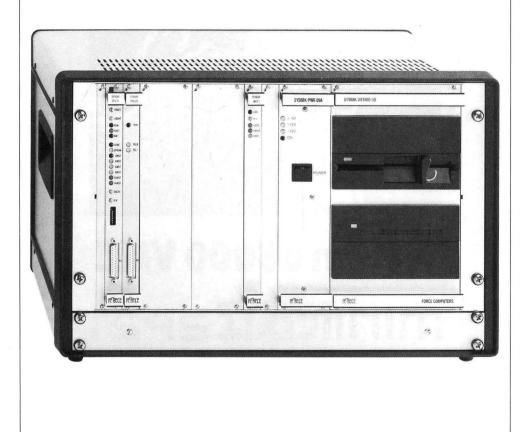

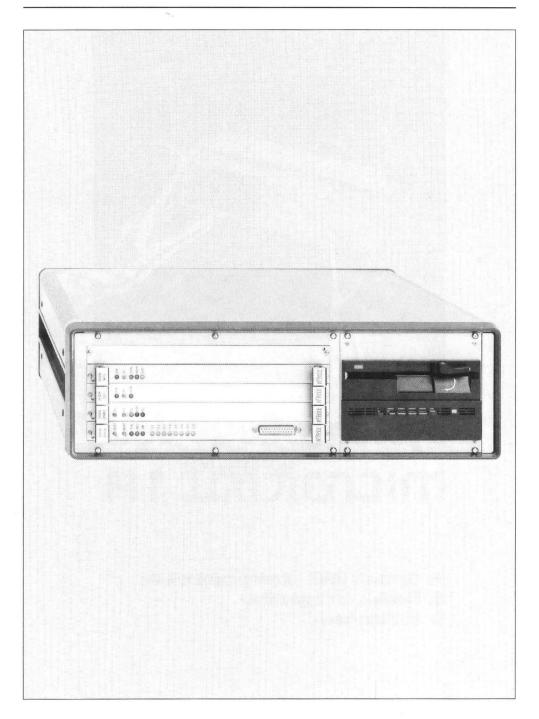

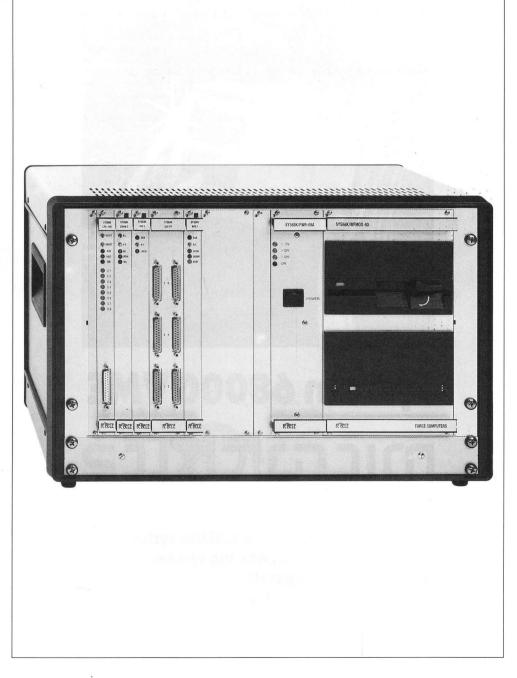

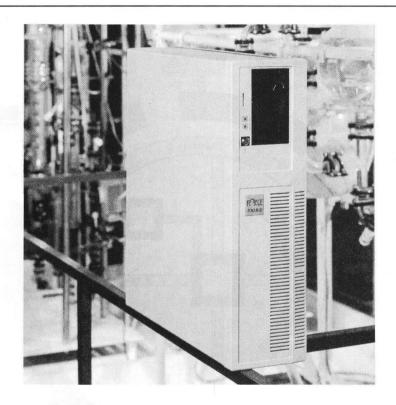

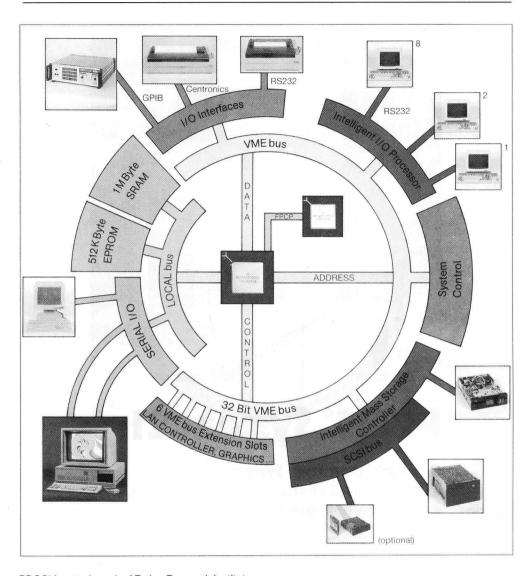

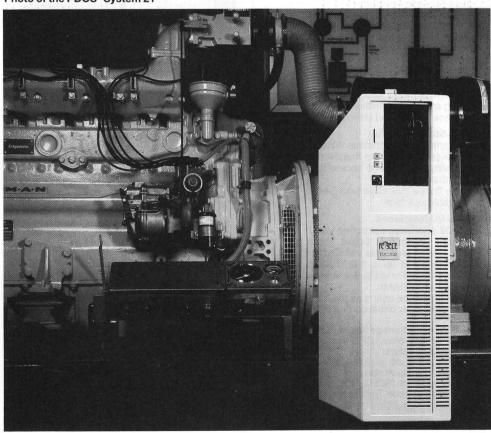

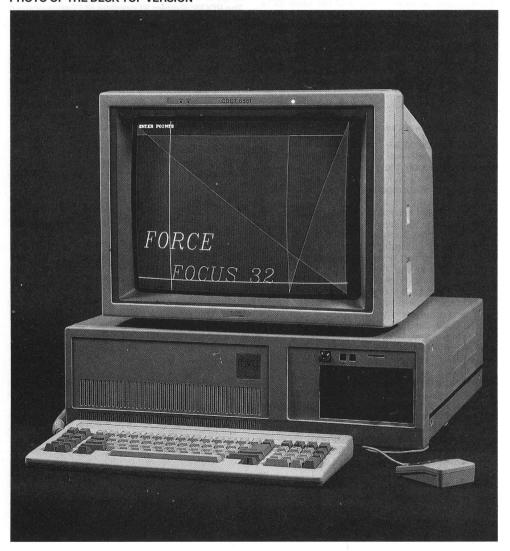

| Development S    | ystems Introduction Overview(s) miniFORCE 1P6 miniFORCE 2 miniFORCE 2P21 microFORCE 1A microFORCE 2 FOCUS 32 PDOS System 21 FOCUS 32 System 25U | 429<br>431<br>435<br>445<br>453<br>457 |

| Software         | PDOS                                                                                                                                            | 487<br>495<br>507                      |

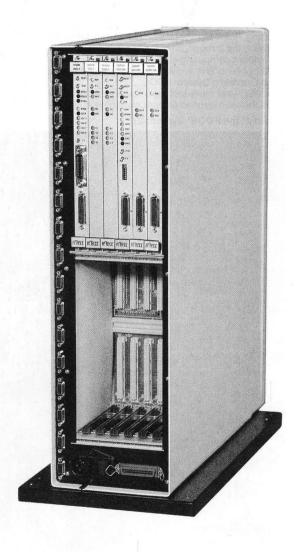

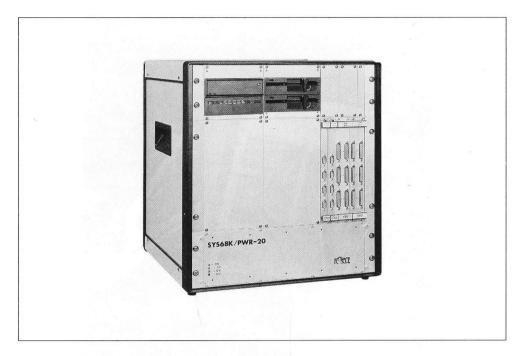

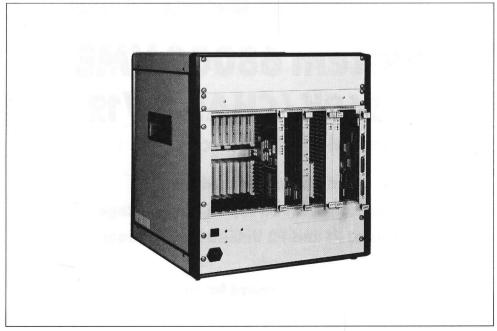

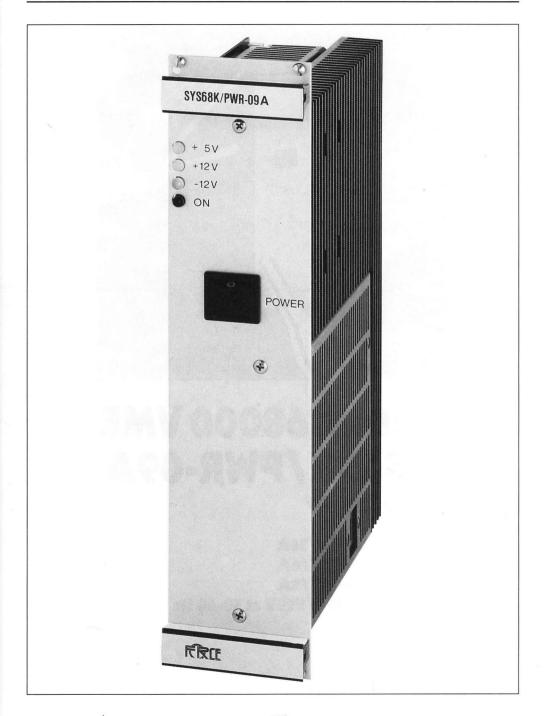

| Accessories .    | SYS68K/MOTH<br>SYS68K/CHAS-19/7<br>SYS68K/CHAS-19/12<br>SYS68K/PWR-09A<br>SYS68K/PWR-20<br>SYS68K/WFMOD                                         | 523<br>527<br>531<br>535               |

| Dietributore & F | Renresentatives                                                                                                                                 | 5/17                                   |

## Introduction to FORCE COMPUTERS Product Guide

Listed here you will find the FORCE COMPUTERS 1988 product guide. As you will see, in addition to the name of the product and the page on which information can be found, there are two additional columns.

These two additional columns signify that some of FORCE COMPUTERS' older products are not recommended for new designs. This means that if a product is not recommended for new design, you should consider using the suggested alternative in order to guarantee increased performance and functionality. FORCE COMPUTERS will continue to produce products that are not recommended for new designs for existing customers of those products. You will note that the products offered as suggested alternatives offer the same functionality and are often compatible. This ensures that you as a valued FORCE COMPUTERS customer are guaranteed product compatibility growth paths.

## **Product Guide**

| Part No.         | Product                        | Description                         | Recom-<br>mended for<br>new Designs | Suggested<br>Alter-<br>native | Details<br>on<br>Page |

|------------------|--------------------------------|-------------------------------------|-------------------------------------|-------------------------------|-----------------------|

|                  |                                | 16 bit CPU Boards                   |                                     |                               |                       |

| 100100           | SYS68K/CPU-1B                  | 68000/ 8.0 MHz/ 128 KB              | No                                  | CPU-6                         | 69                    |

| 100101           | SYS68K/CPU-1C                  | 68000/10.0 MHz/ 128 KB              | No                                  | CPU-6                         | 69                    |

| 100102           | SYS68K/CPU-1D                  | 68000/10.0 MHz/ 512 KB              | No                                  | CPU-6                         | 69                    |

| 100200           | SYS68K/CPU-2                   | 68000/ 8.0 MHz/ 256 KB              | No                                  | CPU-2B                        | 37                    |

| 100201           | SYS68K/CPU-2A                  | 68000/10.0 MHz/ 256 KB              | No                                  | CPU-2B                        | 37                    |

| 100202           | SYS68K/CPU-2B                  | 68000/10.0 MHz/ 512 KB              | Yes                                 | 0.0.0                         | 1                     |

| 100220           | SYS68K/CPU-2D                  | 68000/ 8.0 MHz/ 128 KB              | No                                  | CPU-2B                        | 37                    |

| 100205           | SYS68K/CPU-2F                  | 68000/10.0 MHz/1024 KB              | Yes                                 | 0. 0 22                       | 1 .                   |

| 100211           | SYS68K/CPU-2VA                 | 68010/10.0 MHz/ 256 KB              | No                                  | CPU-2VB                       | 37                    |

| 100212           | SYS68K/CPU-2VB                 | 68010/10.0 MHz/ 512 KB              | Yes                                 | 0.0210                        | 101                   |

| 100213           | SYS68K/CPU-2VC                 | 68010/10.0 MHz/1024 KB              | Yes                                 |                               | 1                     |

| 100300           | SYS68K/CPU-3                   | 68000/ 8.0 MHz/ 32 KB               | No                                  | CPU-3VB                       | 45                    |

| 100310           | SYS68K/CPU-3V                  | 68010/ 8.0 MHz/ 32 KB               | No                                  | CPU-3VB                       | 45                    |

| 100310           | SYS68K/CPU-3VA                 | 68010/10.0 MHz/ 32 KB               | No                                  | CPU-3VB                       | 45                    |

| 100311           | SYS68K/CPU-3VB                 | 68010/10.0 MHz/ 128 KB              |                                     | CFU-3VB                       | 45                    |

| 100312           | SYS68K/CPU-4A                  | 68000/12.5 MHz/ 32 KB               | Yes<br>No                           | CPU-4VC                       | 53                    |

| 100401           | SYS68K/CPU-4V                  | 68010/10.0 MHz/ 32 KB               | No                                  | CPU-4VC                       | 53                    |

|                  |                                |                                     |                                     |                               |                       |

| 100411           | SYS68K/CPU-4VA                 | 68010/12.5 MHz/ 32 KB               | No                                  | CPU-4VC                       | 53                    |

| 100412           | SYS68K/CPU-4VB                 | 68010/12.5 MHz/ 128 KB              | No                                  | CPU-4VC                       | 53                    |

| 100413           | SYS68K/CPU-4VC                 | 68010/12.5 MHz/ 128 KB/BBU          | Yes                                 |                               | )                     |

| 100501           | SYS68K/CPU-5A                  | 68000/16.7 MHz/ 128 KB/FPU          | Yes                                 |                               | 1                     |

| 100502           | SYS68K/CPU-5V                  | 68010/12.5 MHz/ 128 KB/FPU          | No                                  | CPU-5A                        | 61                    |

| 100601           | SYS68K/CPU-6                   | 68000/ 8.0 MHz/ 512 KB              | Yes                                 |                               |                       |

| 100602           | SYS68K/CPU-6A                  | 68000/12.5 MHz/ 512 KB              | Yes                                 |                               | ]                     |

| 100610           | SYS68K/CPU-6VA                 | 68010/12.5 MHz/ 512 KB              | Yes                                 |                               |                       |

| 100611           | SYS68K/CPU-6VB                 | 68010/12.5 MHz/ 512 KB/FPU          | Yes                                 |                               |                       |

|                  |                                | 32 bit CPU Boards                   |                                     |                               |                       |

| 101041           | SYS68K/CPU-21S                 | 68020/12.5 MHz/ 512 KB/FPU          | Yes                                 |                               |                       |

| 101001           | SYS68K/CPU-21                  | 68020/16.7 MHz/ 512 KB/FPU          | Yes                                 | ļ                             |                       |

| 101011           | SYS68K/CPU-21A                 | 68020/20.0 MHz/ 512 KB/FPU          | Yes                                 |                               | 1                     |

| 101021           | SYS68K/CPU-21B                 | 68020/25.0 MHz/ 512 KB/FPU          | Yes                                 | ļ                             | 1                     |

| 101100           | SYS68K/CPU-22                  | 68020/16.7 MHz/ 256 KB/FGA-002      | Yes                                 |                               |                       |

| 101101           | SYS68K/CPU-22A                 | 68020/20.0 MHz/ 256 KB/FGA-002      | Yes                                 |                               | }                     |

| 101102           | SYS68K/CPU-22XA                | 68020/20.0 MHz/ 1 MB/FGA-002        | Yes                                 |                               |                       |

| 101210           | SYS68K/CPU-25                  | 68020/16.7 MHz/ 512 KB/MMU/FPU      | Yes                                 |                               | }                     |

| 101210           | SYS68K/CPU-26X                 | 68020/16.7 MHz/ 312 KB/MMO/FF0      | Yes                                 | 1                             | 1                     |

| 101131           | SYS68K/CPU-26XA                | 68020/20.0 MHz/ 256 KB/SCSI/FGA-002 | Yes                                 |                               | 1                     |

| 101131           | SYS68K/CPU-26ZA                | 68020/20.0 MHz/ 256 KB/SCSI/FGA-002 | Yes                                 |                               | 1                     |

| 101152           | SYS68K/CPU-29XS                | 68020/12.5 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101152           | SYS68K/CPU-29X                 | 68020/12.5 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | [                     |

| 101152           | SYS68K/CPU-29XB                | 68020/16.7 MHz/ TMB/FPU/FGA-001     | Yes                                 |                               | 1                     |

| 101153           | SYS68K/CPU-29XB                |                                     |                                     |                               | 1                     |

|                  |                                | 68020/30.0 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101323           | SYS68K/CPU-32XS                | 68030/12.5 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101324           | SYS68K/CPU-32X                 | 68030/16.7 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101321           | SYS68K/CPU-32XA                | 68030/20.0 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101322           | SYS68K/CPU-32XB                | 68030/25.0 MHz/ 1 MB/FPU/FGA-001    | Yes                                 |                               | 1                     |

| 101333           | SYS68K/CPU-32XC                | 68030/30.0 MHz/ 1 MB/FPU/FGA-001    | Yes                                 | 1                             | 1                     |

| 105000           | SYS80K/CPU-386-1               | 80386/16.0 MHz/ 2 MB                | Yes                                 |                               | 1                     |

| 105001           | SYS80K/CPU-386-1A              | 80386/16.0 MHz/ 2 MB/FPU            | Yes                                 | <u> </u>                      | <u> </u>              |

|                  | <b>,</b>                       | 16 bit Memory Board Products        |                                     |                               |                       |

|                  | 0)/0001//000444                | 512 KB DRAM A24 : D16               | Yes                                 |                               |                       |

| 200000           | SYS68K/DRAM-1                  |                                     |                                     | 1                             | 1                     |

| 200000           | SYS68K/DRAM-1<br>SYS68K/DRAM-2 | 2 MB DRAM A24 : D16                 | Yes                                 | 1                             |                       |

|                  | SYS68K/DRAM-2                  |                                     |                                     |                               | 1                     |

| 200001           | SYS68K/DRAM-2<br>SYS68K/RR-1   | NAKED ROM/PROM/EPROM/SRAM           | Yes                                 |                               |                       |

| 200001<br>200010 | SYS68K/DRAM-2                  |                                     |                                     | SRAM-5                        | 265                   |

| Part No.                                                                                                                                                     | Product                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Recom-<br>mended for<br>new Designs                                           | Suggested<br>Alter-<br>native    | Details<br>on<br>Page    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------|--------------------------|

|                                                                                                                                                              | <del></del>                                                                                                                                                                                                                                                                                                                                                                            | 32 bit Memory Board Products                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |                                  |                          |

| 200004<br>200103<br>200110<br>200113<br>200130<br>200300<br>200600<br>200401<br>200402<br>200501<br>200502<br>200504<br>201000<br>201040<br>201010<br>201020 | SYS68K/DRAM-E-3M1<br>SYS68K/DRAM-E-3S3<br>SYS68K/DRAM-E-4M4<br>SYS68K/DRAM-E-4S12<br>SYS68K/DRAM-E-4S12<br>SYS68K/DRAM-E-3<br>SYS68K/RR-3<br>SYS68K/SRAM-3A<br>SYS68K/SRAM-3A<br>SYS68K/SRAM-4A<br>SYS68K/SRAM-4B<br>SYS68K/SRAM-4B<br>SYS68K/SRAM-5<br>SYS68K/SRAM-22<br>SYS68K/SRAM-22<br>SYS68K/SRAM-22<br>SYS68K/SRAM-22S<br>SYS68K/SRAM-22S<br>SYS68K/SRAM-22A<br>SYS68K/SRAM-22B | 1 MB DRAM A32: D32 MASTER 3 MB DRAM EXTENSION SLAVE 4 MB DRAM A32: D32 MASTER 12 MB DRAM A32: D32 MASTER 12 MB DRAM A32: D32 VERY FAST NAKED PROM/EPROM/EEPROM NAKED PROM/EPROM/EEPROM 512 KB SRAM A32: D32 VME/VMX 1 MB SRAM A32: D32 VME/VMX 512 KB SRAM A32: D32 VME/VMX 512 KB SRAM A32: D32 VME 1 MB SRAM A32: D32 VME 512 KB SRAM A32: D32 VME 512 KB SRAM A32: D32 VME 512 KB MEM. EXP. CPU-21/25 512 KB MEM. EXP. CPU-218 512 KB MEM. EXP. CPU-21A 512 KB MEM. EXP. CPU-21B                                                                                                                                               | Yes Yes Yes Yes Yes Yes Yes No Yes No Yes | SRAM-5<br>SRAM-5                 | 265<br>265               |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                        | Controller Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                               |                                  |                          |

| 300000<br>300001<br>300020<br>300023                                                                                                                         | SYS68K/SASI-1<br>SYS68K/WFC-1<br>SYS68K/ISCSI-1<br>SYS68K/ISCSI-1A                                                                                                                                                                                                                                                                                                                     | SASIBUS HOST CONTR.<br>WINCH/FLOPPY CONTR.<br>INTELL. SCSI CONTR., 128 KB SRAM<br>INTELL. SCSI CONTR., 512 KB SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | No<br>Yes<br>Yes<br>Yes                                                       | ISCSI-1                          | 301                      |

| 400010<br>400004<br>400007<br>400008<br>400020<br>400022<br>400023                                                                                           | SY568K/CMC-1<br>SY568K/GDC-1M+1S<br>SY568K/GDC-152<br>SY568K/GDC-153<br>SY568K/AGC-1<br>SY568K/AGC-1<br>SY568K/AGC-2                                                                                                                                                                                                                                                                   | COLOR MONITOR CONTR. GRAPH. MASTER CONTR. + GDC-1S GRAPH. SLAVE POS. 2 GRAPH. SLAVE POS. 3 ADVANCED GRAPHICS CONTR. ADVANCED GRAPHICS CONTR. EXT. GRAPHICS CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                             | No<br>No<br>No<br>Yes<br>Yes                                                  | AGC-2<br>AGC-2<br>AGC-2<br>AGC-2 | 331<br>331<br>331<br>331 |

| 700006<br>700007<br>300100                                                                                                                                   | SYS68K/ASCU-1<br>SYS68K/ASCU-2<br>SYS68K/ILANC-1                                                                                                                                                                                                                                                                                                                                       | ADVANCED SYS. CONT. UNIT<br>ADVANCED SYS. CONT. W GPIB<br>INTELLIGENT ETHERNET CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Yes<br>Yes<br>Yes                                                             |                                  |                          |

|                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                        | INPUT/OUTPUT Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                               |                                  |                          |

| 310000<br>310004<br>310005<br>310030<br>310035<br>310031<br>310036<br>310011<br>310010                                                                       | SYS68K/SIO-1<br>SYS68K/SIO-2<br>SYS68K/SIO-2<br>SYS68K/ISIO-1<br>SYS68K/ISIO-1A<br>SYS68K/ISIO-2<br>SYS68K/ISIO-2A<br>SYS68K/OPIO-1<br>SYS68K/PIO-1                                                                                                                                                                                                                                    | 6 CHANNEL SER. I/O 6 CHANNEL SER. I/O 6 CHANNEL SER. I/O, OPTICAL LINKS 8 CHANNEL SER. I/O, 128 KB SRAM 8 CHANNEL SER. I/O, 512 KB SRAM 8 CHANNEL SER. I/O, 128 KB SRAM 8 CHANNEL SER. I/O, 128 KB SRAM 8 CHANNEL SER. I/O, 128 KB SRAM PAR. I/O: OPTO. COUP. PARALLEL I/O: TTL                                                                                                                                                                                                                                                                                                                                                   | No<br>Yes<br>Yes<br>Yes<br>Yes<br>Yes<br>Yes<br>Yes<br>Yes                    | SIO-2                            | 379                      |

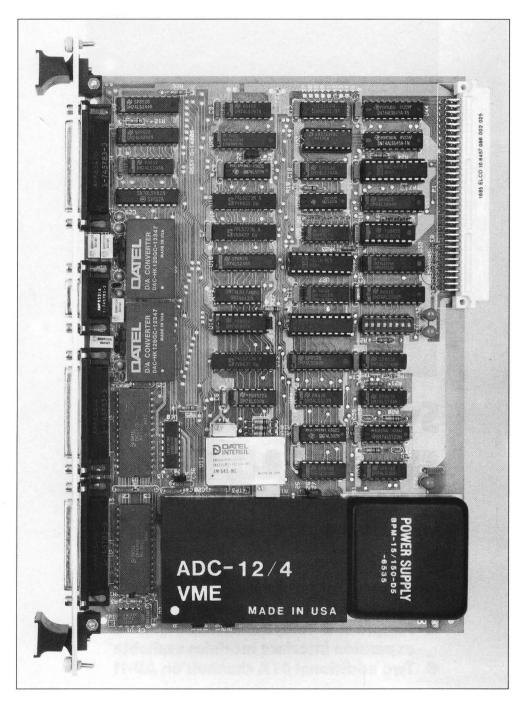

| 320002<br>320003<br>320004<br>320006<br>320007<br>320009<br>320010<br>320012<br>320013<br>320013<br>320014<br>320015<br>320016<br>320017                     | SYS68K/AD-10A<br>SYS68K/AD-10B<br>SYS68K/AD-10D<br>SYS68K/AD-11D<br>SYS68K/AD-11A<br>SYS68K/AD-11B<br>SYS68K/AD-11C<br>SYS68K/AD-11D<br>SYS68K/AD-12<br>SYS68K/AD-12<br>SYS68K/AD-14<br>SYS68K/AD-14<br>SYS68K/AD-14<br>SYS68K/DA-1A<br>SYS68K/DA-1B<br>SYS68K/DA-2B                                                                                                                   | 12 BIT A/D CONV., 20 MICROSEC. 12 BIT A/D CONV., 4 MICROSEC. 14 BIT A/D CONV., 35 MICROSEC. 16 BIT A/D CONV., 35 MICROSEC. 12 BIT A/D CONV., 400 MICROSEC., 2 D/A 12 BIT A/D CONV., 20 MICROSEC., 2 D/A 14 BIT A/D CONV., 35 MICROSEC., 2 D/A 16 BIT A/D CONV., 400 MICROSEC., 2 D/A 16 BIT A/D CONV., 400 MICROSEC., 2 D/A 16 BIT A/D CONV., 400 MICROSEC., 2 D/A 16 CHANNEL S/H EXPANS. FOR AD-10/11 8 CHANNEL HIGH VOLTAGE EXP. FOR AD-10/11 3 CHANNEL HIGH LEVEL INPUT EXP. FOR AD-10/11 8 CHANNEL D/A CONV., 12 BIT 8 CHANNEL D/A CONV., 12 BIT, CURRENT LOOP OUTPUT 6 CHANNEL D/A CONV., 16 BIT 6 CHANNEL D/A CONV., 16 BIT | Yes                                       |                                  |                          |

| Part No. | Product                      | Description                                      | Recom-<br>mended for<br>new Designs | Suggested<br>Alter-<br>native | Details<br>on<br>Page |

|----------|------------------------------|--------------------------------------------------|-------------------------------------|-------------------------------|-----------------------|

|          |                              | System Products                                  |                                     |                               |                       |

| 620510   | miniFORCE 1P1                | PDOS SYSTEM/CPU-1D/3U                            | No                                  | miniFORCE 1P6                 | 433                   |

| 620550   | miniFORCE 1P5                | PDOS SYSTEM/CPU-5V/3U                            | No                                  | miniFORCE 2P5                 | 435                   |

| 620560   | miniFORCE 1P6                | PDOS SYSTEM/CPU-6/3U                             | Yes                                 |                               |                       |

| 620610   | miniFORCE2P1                 | PDOS SYSTEM/CPU-1D/7U                            | No                                  | miniFORCE 2P6                 | 435                   |

| 620620   | miniFORCE2P2                 | PDOS SYSTEM/CPU-2VC/7U                           | Yes                                 | THE STREET                    | 100                   |

| 620640   | miniFORCE 2P4                | PDOS SYSTEM/CPU-4VC/7U                           | Yes                                 |                               |                       |

| 620650   | miniFORCE2P5                 | PDOS SYSTEM/CPU-5A/7U                            | Yes                                 |                               |                       |

| 620660   | miniFORCE2P6                 | PDOS SYSTEM/CPU-6VB/7U, WFC                      | Yes                                 |                               |                       |

| 620662   | miniFORCE2P6I                | PDOS SYSTEM/CPU-6VB/7U, ISCSI                    | Yes                                 |                               | }                     |

| 620700   | miniFORCE2P21                | PDOS SYSTEM/CPU-21/7U                            | Yes                                 |                               | 1                     |

| 620710   | miniFORCE2P21S               | PDOS SYSTEM/CPU-21S/7U                           | Yes                                 | 1                             |                       |

| 620720   | miniFORCE2P21A               | PDOS SYSTEM/CPU-21A/7U, WFC                      | Yes                                 |                               | ļ                     |

| 620722   | miniFORCE 2P21Al             | PDOS SYSTEM/CPU-21A/7U, ISCSI                    | Yes                                 |                               |                       |

| 630005   | microFORCE 1A                | UNIX SYSTEM/CPU-3VB/3U                           | Yes                                 |                               |                       |

| 630010   | microFORCE2                  | UNIX SYSTEM/CPU-3VB/7U                           | Yes                                 |                               |                       |

|          |                              |                                                  |                                     |                               |                       |

| 640021   | FORCE FOCUS 32               | PDOS SYSTEM/CPU-21A                              | Yes                                 |                               |                       |

| 0.40000  | PDOS SYSTEM 21A              | DDGG GVGTEN (CDL) G4D                            | 1,                                  | 1                             |                       |

| 640022   | FORCE FOCUS 32               | PDOS SYSTEM/CPU-21B                              | Yes                                 | 1                             |                       |

| 044005   | PDOS SYSTEM 21B              |                                                  | 1                                   | 1                             |                       |

| 641025   | FORCE FOCUS 32<br>SYSTEM 25U | UNIX SYSTEM/CPU-25                               | Yes                                 |                               |                       |

|          | <del>4 </del>                | Software Products                                |                                     |                               | L                     |

| 140020   | SYS68K/PDOS-PAS              | PDOS PASCAL                                      | Yes                                 |                               |                       |

|          |                              |                                                  |                                     | 1                             |                       |

| 140021   | SYS68K/PDOS-PAS020           | PDOS PASCAL FOR 68020                            | Yes                                 | 1                             |                       |

| 140040   | SYS68K/PDOS-FOR              | PDOS FORTRAN-77                                  | Yes                                 | }                             |                       |

| 140041   | SYS68K/PDOS-FOR020           | PDOS FORTRAN-77 FOR 68020                        | Yes                                 | 1                             |                       |

| 140030   | SYS68K/PDOS-C                | PDOS "C" COMPILER<br>PDOS "C" COMPILER FOR 68020 | Yes                                 | 1                             |                       |

| 140031   | SYS68K/PDOS-C020             | PDOS "C" COMPILER FOR 68020                      | Yes                                 | }                             |                       |

| 140044   | SYS68K/PDOS-BAS              | PDOS BASIC FOR 68000/68010                       | Yeş                                 | ]                             |                       |

| 140045   | SYS68K/PDOS-BAS020           | PDOS BASIC FOR 68020                             | Yes                                 | 1                             |                       |

| 150005   | SYS68K/UNIX-PAS              | UNIX PASCAL                                      | Yes                                 | i i                           |                       |

| 150006   | SYS68K/UNIX-PAS020           | UNIX PASCAL                                      | Yes                                 | 1                             |                       |

| 160000   | SYS68K/GKSGRAL-P2B1          | GKS SOFTWARE FOR PDOS                            | Yes                                 | 1                             |                       |

| 160001   | SYS68K/GKSGRAL-P2B1          | GKS SOFTWARE FOR UNIX                            | Yes                                 | Ĺ                             |                       |

|          |                              | Accessory Products                               |                                     | ,                             |                       |

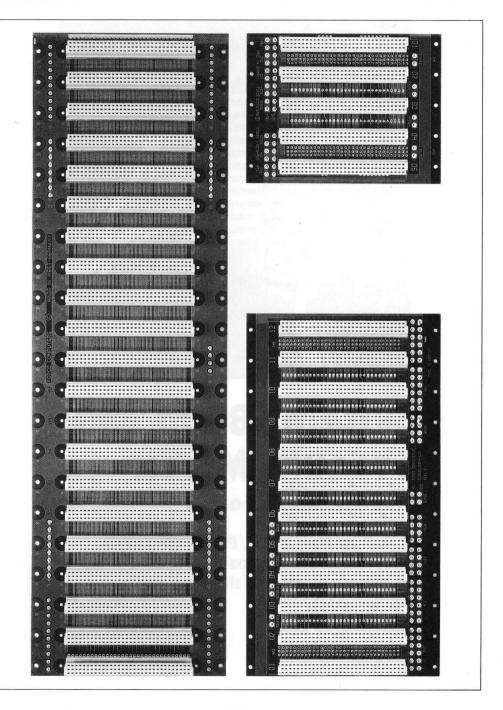

| 500005   | SYS68K/MOTH-05A              | 5 SLOT MOTHERBOARD                               | Yes                                 |                               |                       |

| 500011   | SYS68K/MOTH-09A              | 9 SLOT MOTHERBOARD                               | Yes                                 |                               |                       |

| 500006   | SYS68K/MOTH-12A              | 12 SLOT MOTHERBOARD                              | Yes                                 | 1                             |                       |

| 500013   | SYS68K/MOTH-20A              | 20 SLOT MOTHERBOARD                              | Yes                                 | 1                             |                       |

| 500007   | SYS68K/MOTH-21A              | 21 SLOT MOTHERBOARD                              | Yes                                 |                               |                       |

| 500008   | SYS68K/MOTH-E05A             | 5 SLOT 32 BIT EXTENSION                          | Yes                                 |                               |                       |

| 500012   | SYS68K/MOTH-E09A             | 9 SLOT 32 BIT EXTENSION                          | Yes                                 | i                             |                       |

| 500009   | SYS68K/MOTH-E12A             | 12 SLOT 32 BIT EXTENSION                         | Yes                                 |                               |                       |

| 500014   | SYS68K/MOTH-E20A             | 20 SLOT 32 BIT EXTENSION                         | Yes                                 |                               |                       |

| 500010   | SYS68K/MOTH-E21A             | 21 SLOT 32 BIT EXTENSION                         | Yes                                 |                               |                       |

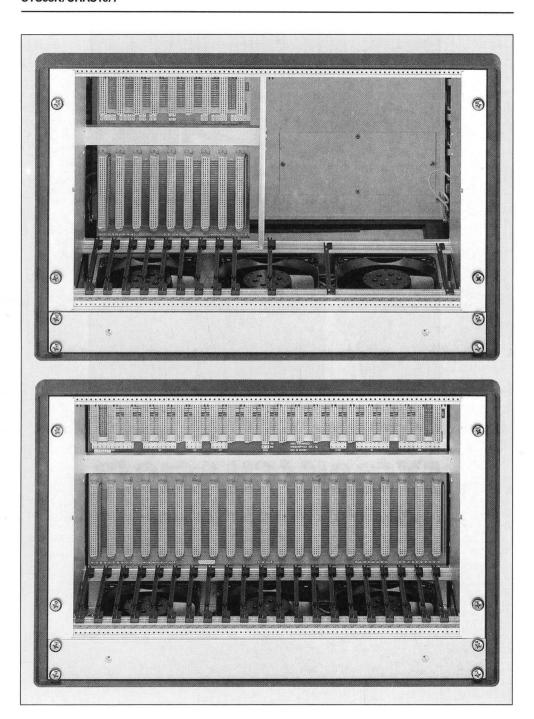

| 610101   | SYS68K/CHAS 19-09E/<br>7HE   | CHAS 19-09/7HE PLUS P2 MOTH                      | Yes                                 |                               |                       |

| 610105   | SYS68K/CHAS 19-21E/<br>  7HE | CHAS 19-21/7HE PLUS P2 MOTH                      | Yes                                 |                               |                       |

| 610191   | SYS68K/CHAS 19-21E/<br>12HE  | 12HE CHASSIS W 21 SLOTS                          | Yes                                 |                               |                       |

| 610005   | SYS68K/RACK 19-09A           | 19" RACK WITH 9 SLOT MOTH                        | Yes                                 |                               |                       |

| 610025   | SYS68K/RACK 19-21A           | 19" RACK WITH 21 SLOT MOTH                       | Yes                                 | 1                             |                       |

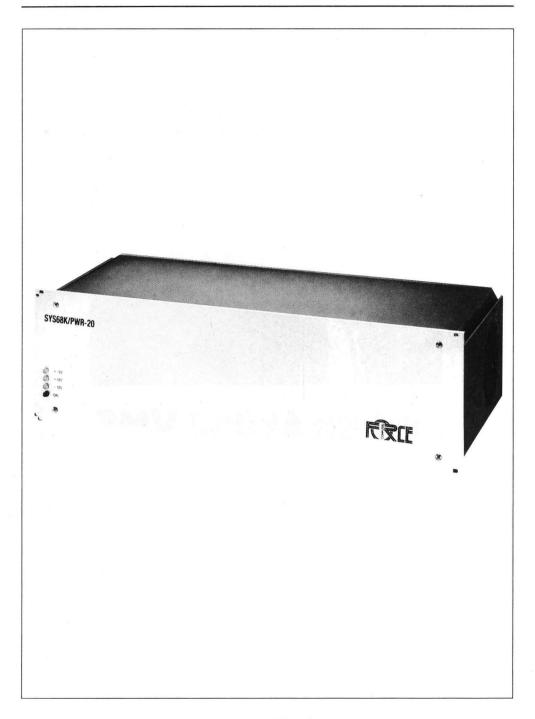

| 700008   | SYS68K/PWR-09A               | 280 W PWR SUPPLY                                 | Yes                                 | [                             |                       |

| 700018   | SYS68K/PWR-09AC              | PWR-09A POWER CABLE                              | Yes                                 | [                             |                       |

| 700009   | SYS68K/PWR-20                | 750 W PWR SUPPLY                                 | Yes                                 |                               |                       |

| 700030   | SYS68K/PWR-20C               | PWR-20 POWER CABLE                               | Yes                                 | 1                             | l                     |

| 700040   | SYS68K/STR-120               | 120 MB STREAMER FOR FOCUS 32                     | Yes                                 |                               |                       |

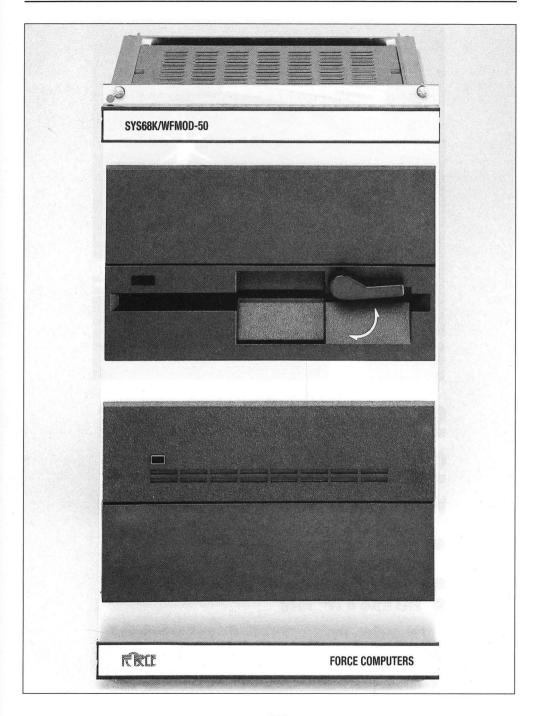

| 700002   | SYS68K/WFMOD-20              | 20 MB WIN/1 MB FLOPPY                            | Yes                                 |                               |                       |

| 700020   | SYS68K/WFMOD-50              | 50 MB WIN/1 MB FLOPPY                            | Yes                                 |                               |                       |

| 700020   | SYS68K/WFMOD-85              | 80 MB WIN/1 MB FLOPPY                            | Yes                                 |                               |                       |

|          |                              |                                                  |                                     | 1                             | I                     |

| 700022   | SYS68K/WFMOD-175             | 175 MB WIN/1 MB FLOPPY                           | Yes                                 |                               |                       |

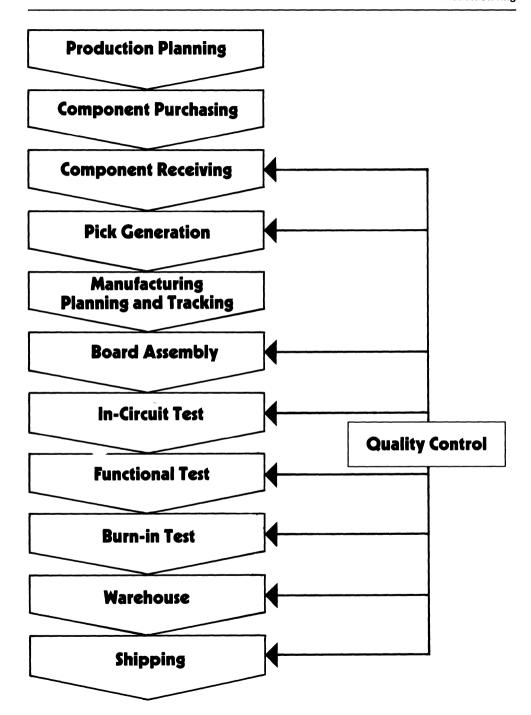

## Manufacturing

The task of the Manufacturing Department is to convert the high-tech designs developed by the Engineering Department into top-quality, long-lived products. The manufacturing system at each working location is defined by considerations of "integrated quality" (see the Q.A. section of the Data Book). Capacity shortages caused by a large backlog or by machine down times must be absorbed by overtime and may not lead to any degradation of production quality.

The major elements of production planning are to ensure a timely delivery of the backlog and to provide a sufficient number of products for the activities of the Sales Organization. This is based on the sales forecast and the sales volume of the past months. Additional customer orders which are very urgent should be shipped from a specified minimum stock acting as a buffer.

The production schedule must always be adjusted to the limited manufacturing capacities of the various steps in a simultaneous planning action. The capacities of the Testing and Manufacturing Departments are continuously expanded with the growth of the company. This results in a timely reaction to the steadily increasing manufacturing volume. Therefore, it is easier to allow for short-time utilization peaks and urgent OEM orders in the production environment.

## **Production Planning**

In every design, the manufacturers for the components used are approved by the Engineering Department. Only components of leading suppliers will be approved. If the Manufacturing or Purchasing Department suggests additional suppliers for specific components, a very strict approval procedure is applied under Q.A. control.

The demand for each component is determined by the MRP Computer System (Manufacturing Requirement Planning) based on the current Production Schedule. Generally, OEM delivery contracts are made with large and renowned manufacturers to ensure that the end products can be manufactured and sold at a low cost. The secured delivery due to the long-term delivery dates is an additional feature of these contracts. With the exception of "sole-source products", a risk spreading results from the availability of strategically important products from different suppliers. A lot of emphasis is put on the purchasing procedures, as this element accounts for a major part of the company's profits.

## **Component Purchasing**

## Component Receiving Quality Control

The Component Receiving Department utilizes its own quality control regulations. Apart from the outward appearance of the incoming products, the internal manufacturer approval, the date codes, the mask revisions etc. will be checked. Special emphasis is put on PCB control, as any inadequate quality which is not detected at this point may lead to major problems in the production flow. Thus, significant time is dedicated to this task.

The component storage is exactly defined and controlled (e.g. the tested printed circuit boards must be hermetically sealed).

## **Pick Generation**

The production lots are approved by the Manufacturing Planning according to the production plan so that the picks may be generated in the component warehouse. First, the PALs and EPROMs are transferred to the production floor to be programmed in parallel to the pick generation. Thus, completed picks will leave the warehouse.

if any parts are missing, the Purchasing Department intervenes in order to identify the whereabouts of the respective products. A second warehouse employee will check the completed pick for 100% completeness before it is transferred to the production area. Thus, production delays due to missing parts have been reduced to a minimum.

## Manufacturing Planning Tracking

Here, the production documents are generated, updated and checked in coordination with the Product Engineering. Based on detailed, controlled procedures, this department implements the Engineering Change Orders (ECO's) in order to ensure a maximum degree of transparency as far as board and product revision is concerned. The implementation of ECO's is organized worldwide and is monitored by Q.A. At the individual levels, the material and product flow is controlled by Manufacturing Planning based on deadlines and lot sizes.

Assembly is carried out according to strict quality regulations for insertion. Depending on the complexity, manual, semi-automatic or automatic insertion is used. All Q.A. measures which are a standard in advanced insertion companies are implemented in the production floors.

A detailed Quality Report is submitted to each assembly area at the end of each month in order to maintain and improve the quality level.

Initial products for SMT (Surface Mount Technology) have been integrated into the production on a mixed-insertion basis. Future designs will significantly expand this production area, and the production floors are well prepared for these enhancements.

Currently, all boards are tested in-circuit using Genrad testing equipment. The bed of nails and the test program for each product are generated, modified and improved at the Design Center which developed the product. All other in-circuit test facilities are supplied with adapters and programs from one central source. Thus, uniform testing is ensured at FORCE Computers facilities all over the world. Dedicated software in the test computer generates test reports at the product and component levels. Among others, this information is available to the Q.A. or the Purchasing Department. Hence, specific component suppliers may be excluded from further delivery if any inadequate quality should be detected.

If a proprietary customer-specific production lot cannot be tested with the ICT Program of the standard FORCE product, the ICT program (and the test adapter sometimes even) will be modified. An electrically tested product is to be delivered to the customer.

## **Board Assembly**

## **Incircuit Test**

## **Functional Test**

Burn-in tests are carried out for at least 48hrs. at a minimum of 50° C. For this purpose, test racks have been developed which provide a VME operating environment for the boards under test. A high-performance control system operating in a real-time, multi-tasking mode controls and monitors the test racks and the testing tasks.

All burn-in test departments all over the world are equipped with these test racks along with the control unit.

After passing the burn-in test, the board is provided with its default setting and submitted to the Q.A. Outgoing Inspection.

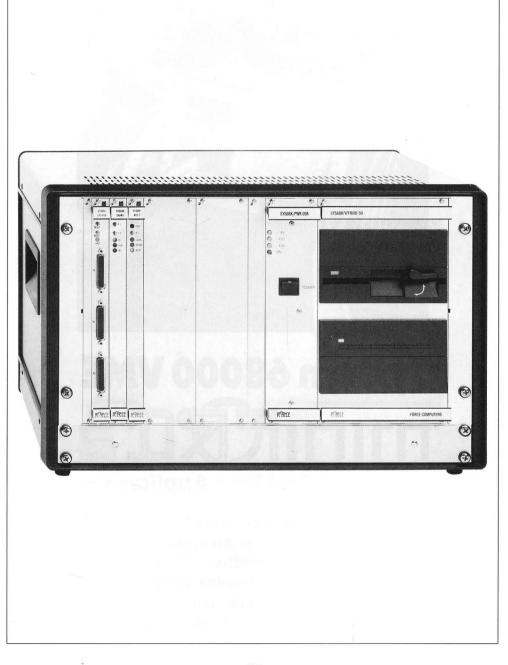

Apart from board-level products, FORCE also offers entire control and development systems.

In the System Generation Department, Systems are mounted in standard configurations or according to the customer's specifications. In addition, the software is loaded (the user has the choice among several operating systems), tested and approved by the Q.A. Each system passes a functional test and a burn-in test of at least 16hrs. As the FORCE boards for these systems are taken from the Finished Goods Warehouse, only entirely tested products are used.

The System Generation Department is expanding rapidly, not least as a result of the new System Generation. Thus, it is especially in this department that methods are sought which promise to increase productivity (improved material flow, use of production components, standardizations, etc). In spite of the dramatic increase in the system-level business, FORCE Computers is still a company which sees itself as a board-level supplier in the first instance.

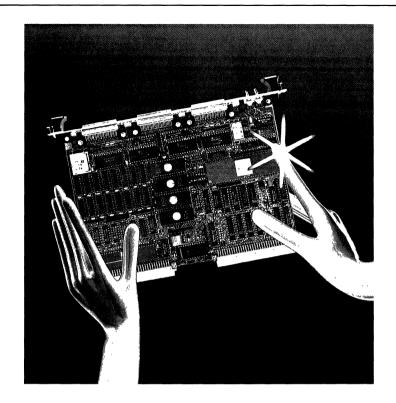

Following the outgoing inspection carried out by the Q.A., the boards and systems are transferred to the Finished Goods Warehouse, where the products are stored in antistatic and dust-proof packages.

The backlog determines when the goods are prepared for shipping, when the documentation is included and when they are put into the shipping boxes.

Generally, the customer will specify the shipment procedure. However, in case of very urgent orders, FORCE provides its expertise and connections to the optimum means of transportation in order to ensure a timely delivery. For this purpose, FORCE has set up a special customs service.

Practical packaging, professional documentation and fast delivery are additional features which give the final touch to FORCE Computer's high-tech products.

## **Burn-in Test**

## **System Generation**

## **Warehouse Shipping**

## **Quality Assurance**

FORCE Computers' quality system incorporates a total quality assurance concept encompassing management, design, purchasing, manufacturing, test, inspection, and documentation. The quality control program established and maintained insures that products conform to published specifications and customer quality requirements. Records demonstrating the effective operation of the quality system are available for review at FORCE Computers by designated purchasing authorities and source inspectors.

#### I. Organization

Quality is the responsibility of management and it is the policy of management that quality needs to be controlled. A quality assurance organisation must be independent of other organisations in order to function effectively.

FORCE Computers' quality assurance manager reports directly to the general manager and has the authority to resolve matters pertaining to quality. Responsibility and authority is delegated to those personnel performing quality functions in order to identify and evaluate quality problems, and to iniate, recommend, or provide solutions. Management regularly reviews the status and adequacy of the quality program.

#### II. Records

Records are one of the prinicipal forms of objective evidence of quality. FORCE Computers maintains and uses records for inspection and test, corrective actions, and calibration.

Test and inspection records are maintained indicating the nature or type of observation, the number of observations made, and number and type of deficiencies found. Corrective action records detail the nature of the action and effective dates of correction. Records showing calibration history and status are maintained for test and measurement equipment.

#### III. Documentation and Change Control

In industries where innovation, redesign, and product improvement are continuously practiced, control of documentation is of critical importance to product quality and reliability.

FORCE Computers maintains control of all documentation relating to the design and manufacture of its products. Current issues of appropriate documents are available at all locations where operations essential to the effective functioning of the quality system are performed. All changes to documentation are in writing and records of changes made are maintained.

#### IV. Statistical Quality Control and Analysis

FORCE Computers utilizes statistical analysis and tests to maintain the required control of quality. Sampling inspection is performed in accordance with MIL-STD-105D, table II-A.

Acceptable quality levels (AQL) are applied at receiving inspection and final electrial and mechanical/visual inspection.

Utilizing modern test equipment, data is generated and analyzed pertaining to yields and product quality trends. As a result, causes of defects or significant variations in manufacturing operations can be identified and the necessary corrective actions implemented in a timely manner.

## V. Control of Inspection, Measuring, and Test Equipment.

All test and measurement equipment is maintained and controlled to insure product conformance to specifications and required quality levels. Calibration records are maintained and equipments are labeled showing calibration intervals and status. The calibration system conforms with »Nato Measurement and Calibration System Requirements for Industry« (AQAP-6).

## VI. Test Programs and Procedures

FORCE Computers has developed sophisticated test programs utilizing state-of-the-art test and measurement equipment for its board level and system products.

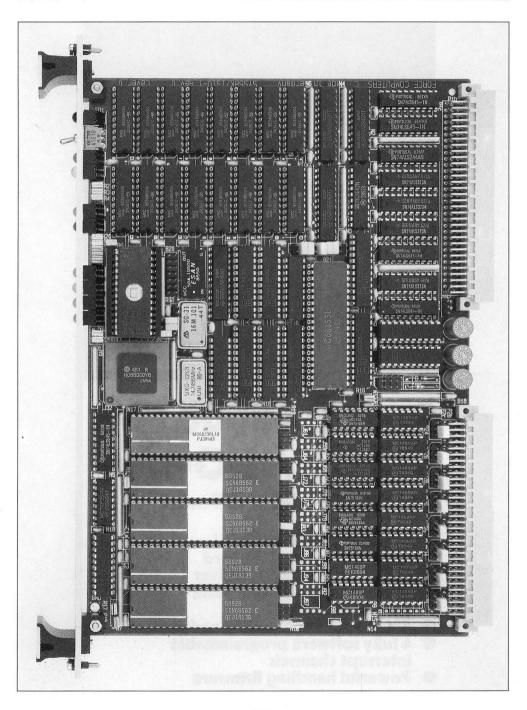

Board level products are subjected to 100 percent in-circuit test using a GENRAD 2276E or equivalent automatic tester (bed of nails). Data related to yields and product quality trends is collected, analysed, and used as a basis for product improvement programs. Defect data feedback is used to initiate corrective actions.

Utilizing proprietary test programs in imbedded software, all board level products are tested for functionality in a VME System environment simulating the end use of the product. Processor, memory, and controller chips, for example are exercised to test performance in the intended application. In order to screen out infant mortalities all CPU I/O and RAM boards are subjected to a dynamic burn-in for 48 hours at 50 degrees centigrade, minimum.

Real-time software driven test programs have been developed enabling board level products to be tested in functional environments at elevated ambient temperatures.

A post test electrical and visual sample inspection is performed on all finished products to verify that all tests have been completed as specified.

All systems are functionally tested and a minimum 24 hour duration test is performed at room ambient temperatures. Prior to shipment a final q.c. electional and visual inspection is performed on all systems.

### VII. Standards and Specifications

The quality system implemented at FORCE Computers conforms with and applies the following standards and specifications.

| BS5750 - Part 1 | Specification for design, manufacture and installation.   | IPC-A-600C      | Acceptability of printed wiring boards.  |

|-----------------|-----------------------------------------------------------|-----------------|------------------------------------------|

| MIL-Q-9858A     | Quality program requirements.                             | IPC-ML-910A     | Design and end production                |

| AQAP-1          | NATO Quality Control System                               |                 | spec. for rigid multi-layer              |

|                 | Requirements for Industry.                                |                 | boards.                                  |

| AQAP-6          | NATO Measurement and Cali-<br>bration System Requirements | MIL-STD-275D    | Printed wiring for electronic equipment. |

|                 | for Industry.                                             |                 |                                          |

| IPC-SM-840      | Qualification and performance                             | Workmanship sta | indards as published by Martin           |

Marietta Aerospace.

inas. MIL-P-55110C Military specification printed wiring boards.

of permanent polymer coat-

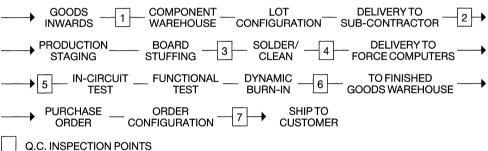

## VIII. Material Flow Chart

- 1. Sample Visual AQL 1.0

- 2. Sample Visual AQL 1.0

- 3. Sample Visual AQL 1.0

- 4. 100% Visual

- 5. Sample Visual AQL 1.0

- 6. Sample Electrical AQL 1.0/100% Visual

- 7. Purchase Order, Documentation, Packaging

A comprehensive description of the quality system implemented by FORCE Computers is available in handbook form:

Quality Assurance and Reliability Handbook First Edition, June 1987

Part No. 800450

## **16 Bit CPU Boards**

## FORCE Computers 16 bit CPU Board Introduction

There are six basic designs in the FORCE family of 16 bit CPU boards. All the designs are available with a variety of options, which makes this family of boards one of the broadest and most comprehensive available in today's 16 bit CPU marketplace.

#### **General Feature Overview**

For general purpose flexibility and functionality, the SYS68K/CPU-6 and the SYS68K/CPU-1 families provide all the features that the user could ever need. The CPU-6 family was designed as a functional update for the extremely popular CPU-1 family. The CPU-1 family was designed to rev. B of the VMEbus specification and provides ample RAM and EPROM areas for most small to medium sized applications. The family also includes 3 serial I/O ports as standard. The CPU-6 was designed to provide complete S/W compatibility to the CPU-1 family, provides all the same features, whilst conforming fully to the IEEE 1014 standard (Rev C. specification). In addition an optional 68881 floating point co-processor was included. The CPU-1 and CPU-6 families are the general purpose solution.

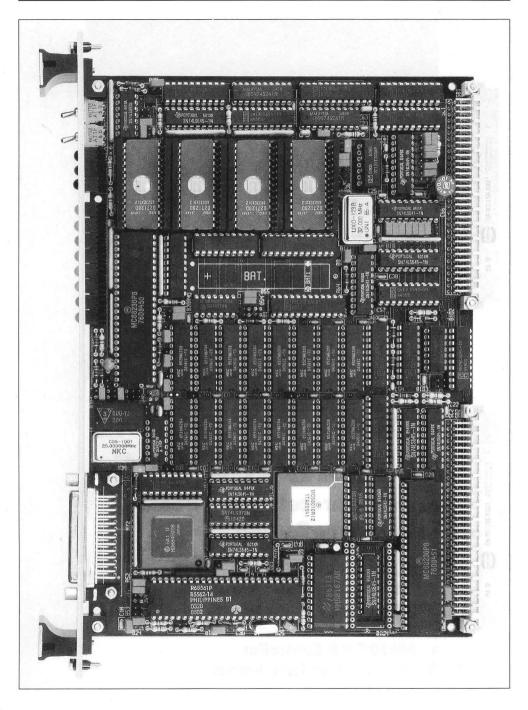

If you require a standalone CPU board with sufficient memory and I/O capability to manage small applications without the need for extra boards, then the SYS68K/CPU-2 family of boards may suit your requirements. The board has up to 512 Kbyte of memory, optional floppy disk controller, 32 Kbyte EPROM and serial and parallel I/O capabilities. The CPU-2 is the single board solution.

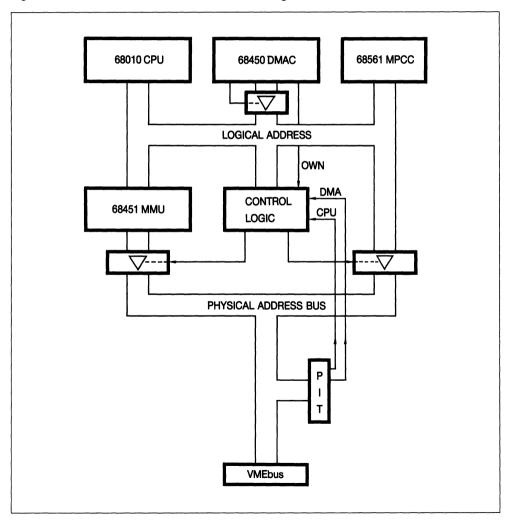

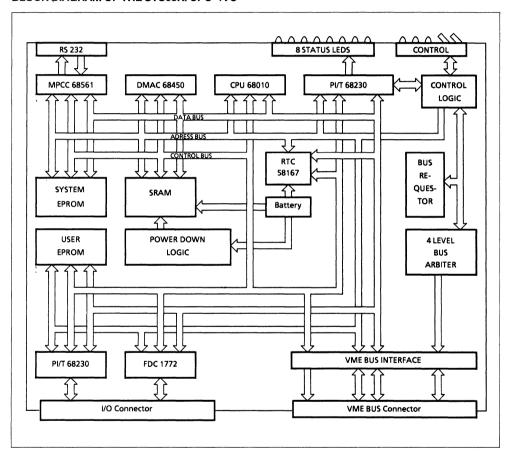

If memory management and data protection is in your specification, then the SYS68K/CPU-3 family is the product for you. The 68010 CPU coupled with the 68451 memory management unit (MMU) and the 68450 DMA controller means that this board is ideally suited to UNIX type environments. The CPU-3 family is the memory managed solution.

If your application requires that small to medium sized applications be committed to EPROM, then the SYS68K/CPU-4 family is designed especially for you. With 8 JEDEC compatible sockets, the user is provided with a potential 512 Kbyte of EPROM space. Coupled with the powerful 68010 microprocessor, DMA controller with optional floppy dosk controller and serial and parallel I/O, the CPU-4 family is the standalone solution.

For true raw performance, the SYS68K/CPU-5 family provides the maximum computing power available with a 16 bit 68000 microprocessor. With the local CPU and floating point co-processor running at a blistering 16.67MHz and with the 128 Kbyte of local RAM inducing no wait states on the CPU, the CPU-5A is the 68000 performance standard.

All the 16 bit CPU boards are available in system configurations which take full advantage of all their features. These configurations may be found in the systems pages towards the end of this data book.

Overview

| FAMILY                                   | CPU-1                    | CPU-2                     | CPU-2V                    | CPU-3V                    | CPU-4VC                       | CPU-5A                        | CPU-6                      | CPU-6V                        |

|------------------------------------------|--------------------------|---------------------------|---------------------------|---------------------------|-------------------------------|-------------------------------|----------------------------|-------------------------------|

| Processor Type<br>Frequency min.<br>max. | 68000<br>8 MHz<br>10 MHz | 68000<br>10 MHz<br>10 MHz | 68010<br>10 MHz<br>10 MHz | 68010<br>10 MHz<br>10 MHz | 68010<br>12.5 MHz<br>12.5 MHz | 68000<br>16.7 MHz<br>16.7 MHz | 68000<br>8 MHz<br>12.5 MHz | 68010<br>12.5 MHz<br>12.5 MHz |

| FPCP Type<br>Frequency                   |                          | -                         | _<br>_                    |                           |                               | 68881<br>16.7 MHz             | _                          | 68881<br>12.5 MHz             |

| DMAC Type<br>Frequency                   | =                        | _                         |                           | 68450<br>10 MHz           | 68450<br>8 MHz                | 68450<br>8 MHz                |                            | _                             |

| MMU Type<br>Frequency                    | _                        | =                         | <u>-</u>                  | 68451<br>10 MHz           |                               |                               |                            |                               |

| DRAM on Board min.<br>max.               | 128 Kbyte<br>512 Kbyte   | 512 Kbyte<br>1 Mbyte      | 512 Kbyte<br>1 Mbyte      | <u>-</u>                  |                               |                               | 512 Kbyte<br>512 Kbyte     | 512 Kbyte<br>512 Kbyte        |

| SRAM on Board min.<br>max.               | =                        | 16 Kbyte<br>16 Kbyte      | 16 Kbyte<br>16 Kbyte      | 128 Kbyte<br>128 Kbyte    | 128 Kbyte<br>128 Kbyte        | 128 Kbyte<br>512 Kbyte        | =                          | _                             |

| Sockets for<br>EPROMs/SRAMs              | 4                        | 4                         | 4                         | 4                         | 8                             | 4                             | 4                          | 4                             |

| Debugger                                 | X                        | X                         | X                         | X                         | _                             | _                             | _                          | -                             |

| VMEPROM                                  | _                        | _                         | -                         | -                         | ×                             | X                             | ×                          | Х                             |

| Serial Ports (RS232)                     | 3 (ACIA)                 | 1 (MPCC)                  | 1 (MPCC)                  | 1 (MPCC)                  | 1 (MPCC)                      | 2 (MPCC)                      | 3 (ACIA)                   | 3 (ACIA)                      |

| Parallel Interface                       | 2x 8bit                  | 2x 8bit                   | 2x 8bit                   | -                         | 2x 8bit                       | _                             | 2x 8bit                    | 2x 8bit                       |

| Timer                                    | 1 x 24 bit               | 1 x 24 bit                | 1 x 24 bit                | 1 x 24 bit                | 2 x 24 bit                    | 1 x 24 bit                    | 1 x 24 bit                 | 1 x 24 bit                    |

| RTC                                      | х                        | Х                         | Х                         | Х                         | Х                             | _                             | x                          | Х                             |

| Floppy Disk Controller<br>Bus Arbiter    | _<br>Single Level        | X<br>Single Level         | X<br>Single Level         | –<br>Four Level           | (optional)<br>Four Level      | –<br>Single Level             | –<br>Single Level          | –<br>Single Level             |

| Watch Dog Timer                          | X                        | Х                         | Х                         | Х                         | Х                             | Х                             | Х                          | Х                             |

| VMXbus Interface                         | _                        | _                         | _                         | -                         | _                             | Х                             | _                          | -                             |

| Detailed Description on Page:            | 29                       | 39                        | 39                        | 45                        | 53                            | 61                            | 69                         | 69                            |

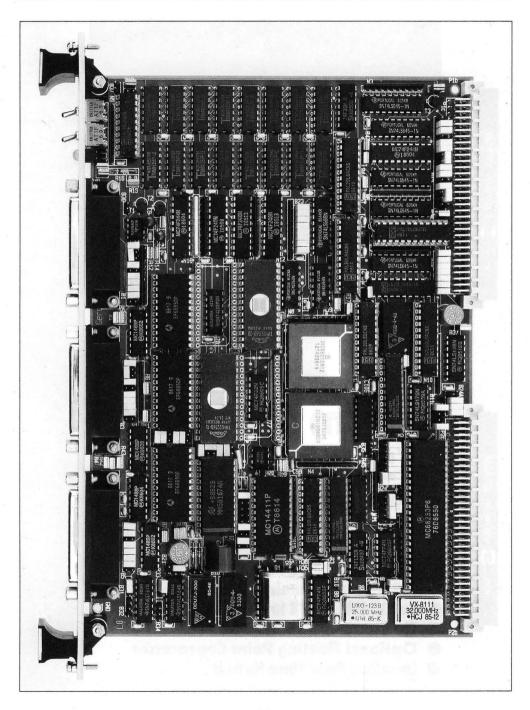

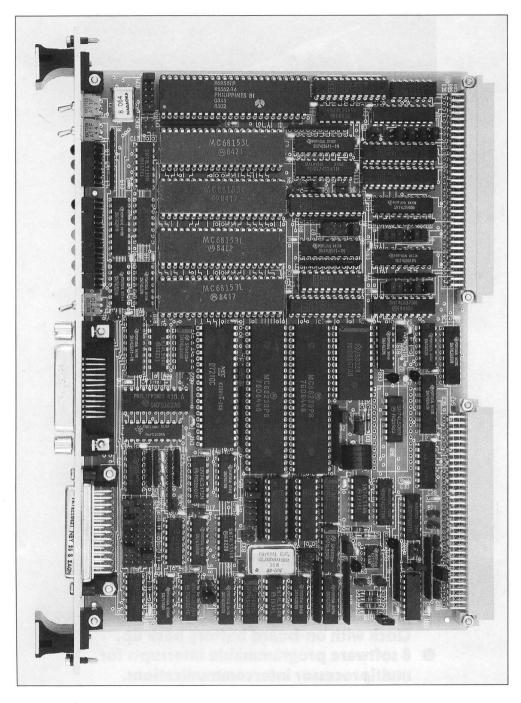

## System 68000 VME SYS68K/CPU-1B/D

## **Universal CPU-Board**

- 68000 CPU

- 512 Kbyte DRAM

- 3 Serial I/O Interfaces

- Real Time Clock

- Parallel I/O Interface

- 128 Kbyte EPROM space

### General Description SYS68K/CPU-1B

The SYS68K/CPU-1B Board is a high performance, low-cost system computer board based on the 68000 CPU and the VMEbus for high speed real time applications.

It contains 128 Kbyte of DRAM, up to 128 Kbyte of EPROM/ROM, parallel I/O, a real-time clock, 3 serial communications interfaces and the system monitor.

The implemented VMEbus interface is VMEbus Rev. B compatible and includes the slave bus arbitration as well as a single level bus arbiter.

### SYS68K/CPU-1B Features

- 68000 CPU ( 8 MHz) on CPU-1B

- 128 Kbyte of dynamic RAM with distributed refresh every 15µsec.

- 16 Kbyte of firmware in ROM/EPROM expandable to 64 Kbyte

- 64 Kbyte of USER EPROM area or 16 Kbyte of USER SRAM area

- Memory access times

PROM 200 – 500 ns (jumper selectable) DRAM 280 ns (typ.)

- Three serial communication ports with RS232 compatible interface

- Strap selectable I/O signal assignment

- Parallel I/O with 2 ports 8 bit each

- 24 bit Timer with 5 bit prescaler

- Real Time Clock with on-board battery back-up

- Auto Interrupt Vectoring for all on-board devices (6 different interrupt levels and vectors)

- Fully VMEbus compatible (Rev. B)

- 7 interrupt levels from the VMEbus

- Slave bus arbitration

- Single level bus arbiter

- RESET and ABORT function switches

- HALT mode indication LED

- Indirect connection on all connectors

- Double Eurocard form factor with front panel

- Self contained operating firmware that provides monitor, debug, one-line assembly/disassembly, and I/O control functions.

- Operating system software for different applications available.

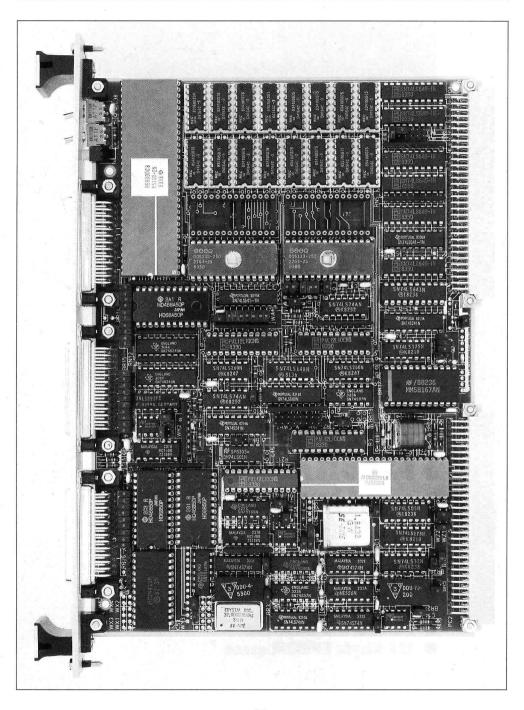

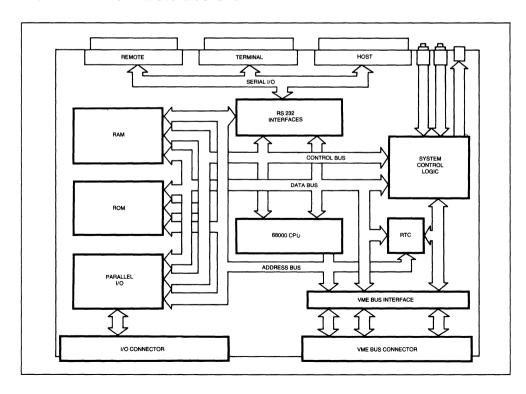

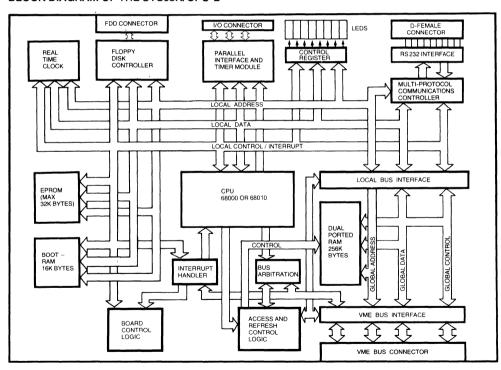

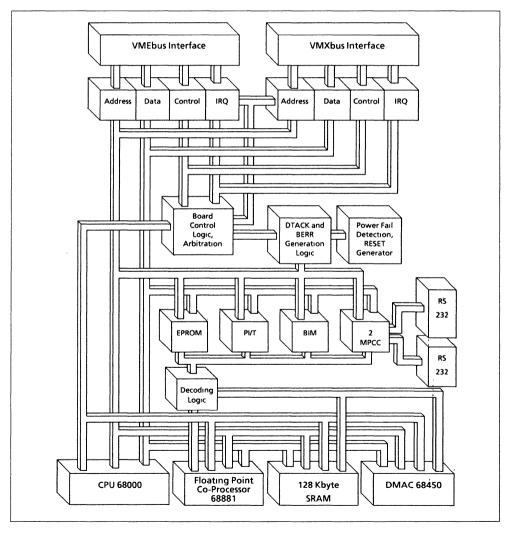

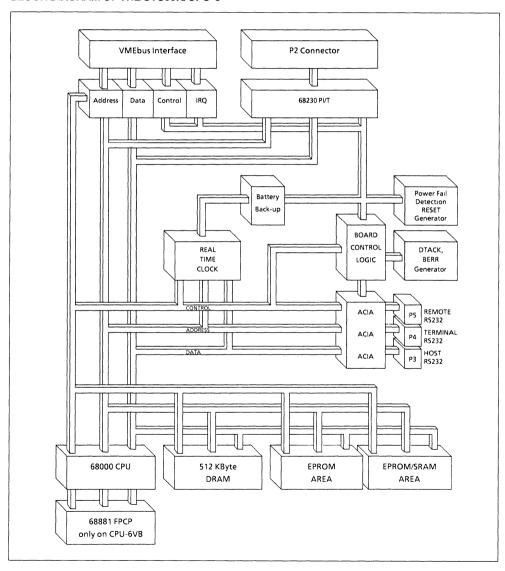

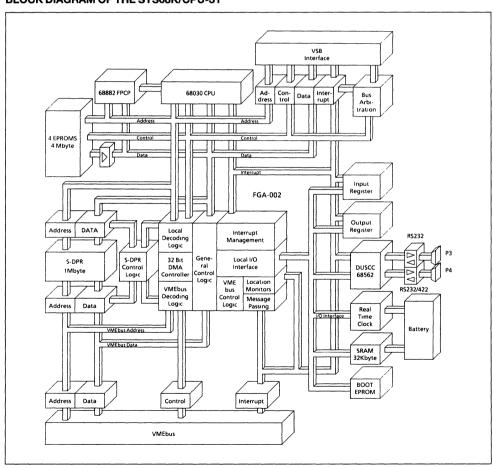

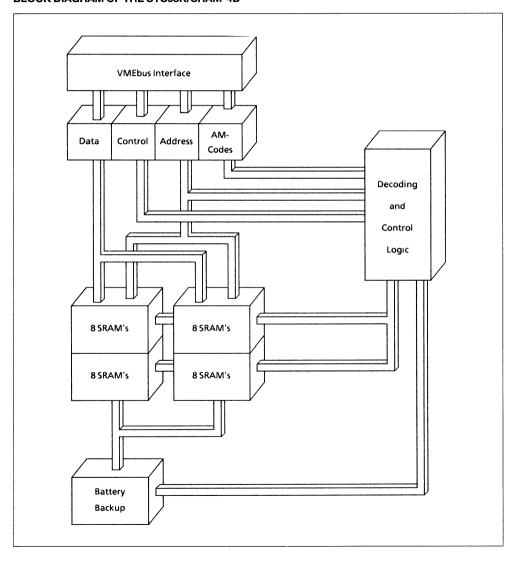

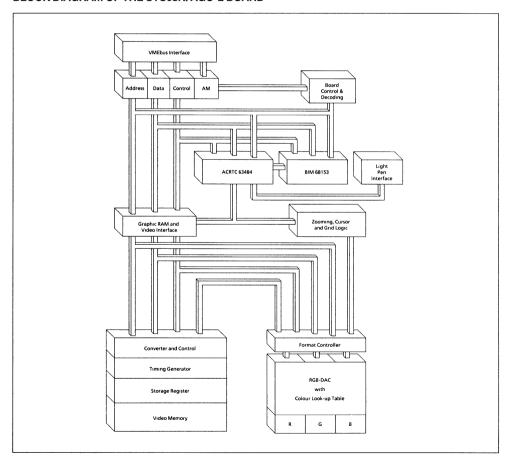

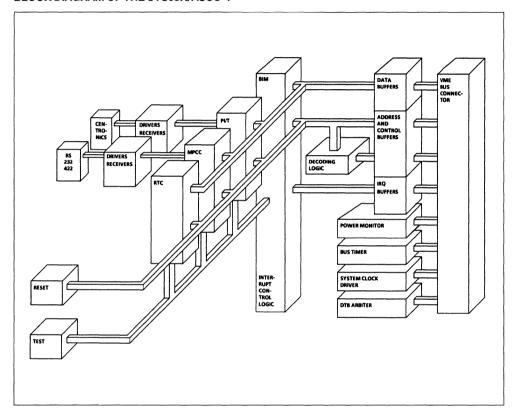

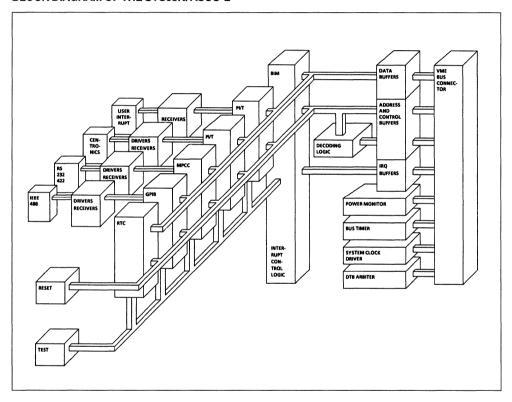

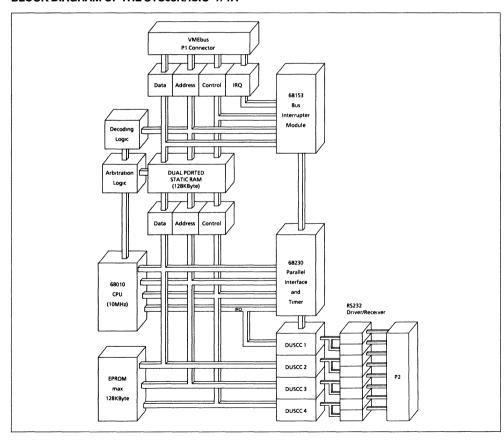

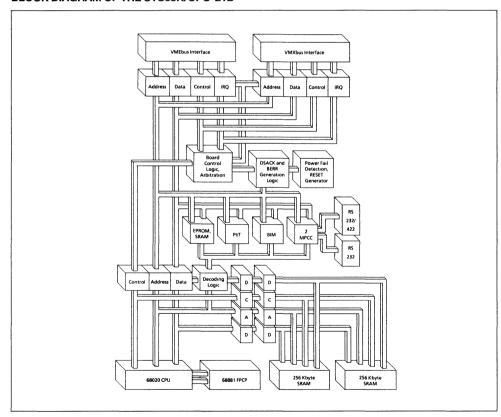

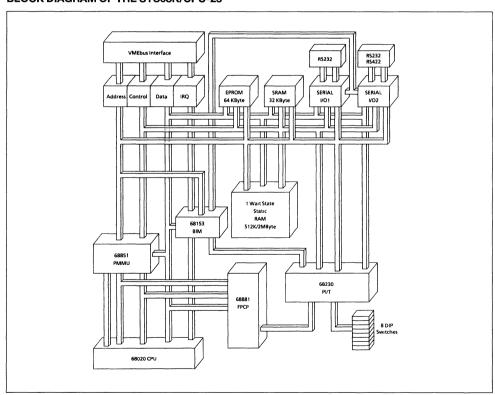

### **BLOCK DIAGRAM OF THE SYS68K/CPU-1B**

#### Features of the SYS68K/CPU-1D

- The CPU-1D contains the same features as the CPU-1B

- The dynamic memory capacity is increased to 512 Kbyte

#### **Functional Description**

Memory, real time clock, serial and parallel I/O communicate with the MPU via their common internal system bus.

Table 1. shows the global memory layout. The various functional areas of the board are described briefly in the following paragraphs.

#### Address

| 000        | 000<br>007 | Initialisation vectors from system EPROM |

|------------|------------|------------------------------------------|

| 000<br>01F | 008<br>FFF | Dynamic RAM on CPU-1B                    |

| 000<br>07F | 008<br>FFF | Dynamic RAM on CPU-1D                    |

| 080<br>09F | 008<br>FFF | SYSTEMEPROMArea                          |

| 0A0<br>0BF | 000<br>FFF | USER EPROMArea                           |

| 0E0<br>0FF | 000<br>FFF | I/O Interfaces                           |

| 100<br>FEF | 000<br>FFF | VMEbus addresses (A24)                   |

| FF0<br>FFF | 000<br>FFF | VMEbus Short I/O (A16)                   |

#### 1. 68000 CPU (8 or 10 MHz)

The 68000 CPU has a 16-bit data bus and a 23-bit address bus. The address bus provides a direct memory addressing range of 16 Mbytes. The processor has eight 32-bit data registers, seven 32-bit address registers, two 32-bit stack-pointers, a 32-bit program counter, and a 16-bit status register. Seven interrupt levels allow an auto- and a non-auto-interrupt vector mode (192 vectors). The 68000 Data Sheet and the User's Manual describe the device in detail.

## 2. The Dynamic RAM

The local addresses space consists of 128 Kbyte with a typical access time of 280 ns. With the use of 256K x 1 oriented DRAM's the memory capacity is increased to 512 Kbyte (on CPU-1D).

For critical real time applications the distributed »RAS only« refresh can delay every 15 micro sec a pending access for a maximum of 290 ns. The refresh works totally asynchronous to the CPU. Therefore, no time delay is required if the CPU accesses other memory areas.

#### 3. The SYSTEM Area

The SYSTEM area contains two sockets (28 pins) with a JEDEC compatible pin-out. This allows the use of different ROM's and EPROM's with a maximum capacity of 64 Kbyte. The access time of the SYSTEM area and of the USER area is jumper selectable from 150 to 500 ns.

Table 2. shows the list of usable devices.

The SYS68K DEBUGGER firmware package resides in two 2764 EPROM's (included in the shipment).

| Table 2  |          | EPROM |

|----------|----------|-------|

| 2K x 16  | 4 Kbyte  | 2716  |

| 4K x 16  | 8 Kbyte  | 2732  |

| 8K x 16  | 16 Kbyte | 2764  |

| 16K x 16 | 32 Kbyte | 27128 |

| 32K x 16 | 64 Kbyte | 27256 |

#### 4. The USER Area

The USER area contains two 28 pin sockets with JEDEC compatible pin out. To allow the usage of static RAM's, the access to the USER area is byte oriented.

Table 3. lists the usable device types.

| Table 3  |          | EPROM | SRAM |

|----------|----------|-------|------|

| 2K x 16  | 4 Kbyte  | 2716  | 6116 |

| 4K x 16  | 8 Kbyte  | 2732  | _    |

| 8K x 16  | 16 Kbyte | 2764  | 6264 |

| 16K x 16 | 32 Kbyte | 27128 | _    |

| 32K x 16 | 64 Kbyte | 27256 | _    |

|          |          |       |      |

### 5. Serial Communication Ports

Three asynchronous serial communication ports, designated Port 1 for the terminal, Port 2 for the host, and Port 3 for user applications, are provided on the board. All of these ports are RS232C compatible (E.I.A. standard). The terminal acts as a user interface and works in conjunction with the monitor. Port 2 interfaces to a modem or directly to a host computer. The host computer may be used to provide more powerful software capabilities, such as program assembly and downloading of programs. Also an operational transparent mode condition is callable via the system monitor. This transparent mode effectively bypasses the board and

allows the terminal to communicate directly with the host. The third serial communication port interfaces either to a printer or acts as a remote link to another computer. All serial ports are jumper selectable for various data transmission rates (110-9600 or 600-19200 baud).

For each serial port the I/O signals can be assigned to one of the 25 pins of the D-sub female connector on the front panel.

#### 6. Parallel I/O

The board contains a Parallel Interface and Timer chip PI/T 68230 with a clock frequency of 8 MHz. The PI/T operates in uni- or bi-directional mode either 8 or 16 bits wide.

Each of the 24 I/O lines may be configured as an input or as an output.

For asynchronous software control the third 8 bit port can be configured to drive two interrupts on level 5, one for the handshake interface and one as a timer output.

### 7. Programmable Timer

The PI/T 68230 (Parallel Interface and Timer) includes a 24-bit programmable timer. The timer is a synchronous counter to be used for generating or measuring time delays and various frequencies. The timer is either clocked by a 5-bit prescaler or directly, and the clock source can either be the 8 MHz CPU clock or an external clock.

### 8. Programmable Real Time Clock

The on-board Real Time Clock (RTC) allows various applications, such as time scheduling, time comparison, time-out counter, etc. Additionally, the real time clock may act as an actual time base providing month, day of month and day of week. An on-board battery ensures time base operation during power down times.

#### 9. On-Board Interrupt Handling

All on-board devices are able to force interrupts on different levels to the CPU. In this case the auto-interrupt vector of the 68000 will be forced and each device has its own interrupt vector.

Table 4. shows the interrupt structure of the CPU-1B/D.

| Description        | Device | Level | Vector No. |

|--------------------|--------|-------|------------|

| ABORT              | Switch | 7     | 31         |

| Real Time Clock    | 58167A | 6     | 30         |

| Parallel Interface | 68230  | 5     | 29         |

| and Timer Chip     |        |       |            |

| Terminal ACIA      | 6850   | 4     | 28         |

| Remote ACIA        | 6850   | 3     | 27         |

| Host ACIA          | 6850   | 2     | 26         |

#### 10. The VMEbus

The implemented VMEbus Interface includes 24 address, 16 data, 6 address modifier and the asynchronous control signals.

A single level bus arbiter is provided to build multi master systems. In addition to the bus arbiter, a separate slave bus arbitration allows selection of the arbitration level (0-3).

The address modifier range »Short I/O Access« can be selected via a jumper for variable system generation.

The 7 interrupt request levels of the VMEbus are fully supported from the SYS68K/CPU-1B/D. For multi-processing, each IRQ signal can be enabled/disabled via a jumper field.

Additionally, the SYS68K/CPU-1B/D supports the ACFAIL, SYSRESET, SYSFAIL and SYSCLK signal (16 MHz).

#### 11. The DEBUGGER Firmware