# GENERAL PURPOSE ANALOG COMPUTATION

GENERAL SECTION

COMPUTING TECHNIQUES: 1.3.4a

# AUTOMATIC ITERATIVE OPERATION ON AN ANALOG COMPUTER

by

George Hannauer, Omri Serlin, and Peter J. Holsberg

Recent developments in analog computers have aroused fresh interest in automatic iterative computation. While the technique is not new, it has not been widely used with analog computers in the past, and is therefore unfamiliar to many analog programmers. It is the purpose of this report to provide an introduction to the techniques involved and to suggest representative applications.

While the analog computer is, in many ways, well-suited for this mode of operation, many of the basic concepts (logical decision, storage, discrete variables) are more familiar to users of digital computers. Iterative analog computation is, in fact, a form of hybrid computation, employing both analog and digital techniques, and large and complex iterative problems are most effectively attacked by combining digital devices (flip-flops, shift registers, gates, etc.) with conventional analog components. Nevertheless, a good many problems can be solved with analog components alone, and this report will deal almost exclusively with this type of problem. Specifically, the report will be concerned with what can be done with existing components on a medium sized general purpose analog computer such as the PACE ® TR-48.

Of particular interest in this regard, however, is the hybrid implementation (described in Appendix 3) of the illustrative analog problem solved in the body of the study. Using the EAI DES-30 Digital Expansion System ... a general purpose, patchable digital logic package ... to provide digital expansion of the TR-48 analog computer, the all-analog simulation of this one-parameter optimizer or boundary value problem is modified so that the necessary logic functions are performed by the synchronous logic elements of this completely self-contained unit.

Although capable of operating autonomously as an aid to digital instruction or design, the DES-30 digital logic system provides basic hybrid capabilities to the small computer facility. It is readily combined also with other general purpose analog or digital computers to provide extended control functions.

# TABLE OF CONTENTS

|    |                                                                                           | Page |  |

|----|-------------------------------------------------------------------------------------------|------|--|

| 1. | DEFINITION OF ITERATIVE COMPUTATION                                                       | 3    |  |

| 2. | TYPICAL APPLICATIONS                                                                      | 4    |  |

|    | a) Parameter Sweep                                                                        | 4    |  |

|    | b) Optimization                                                                           | 4    |  |

|    | c) Boundary-Value Problems                                                                | 4    |  |

|    | d) Curve-Fitting                                                                          | 5    |  |

|    | e) Serial Solution of Partial Differential Equations                                      | 5    |  |

| 3. | ITERATIVE REQUIREMENTS AND CIRCUITS USING ONLY ANALOG INTEGRATORS                         |      |  |

|    |                                                                                           |      |  |

|    | a) Storage                                                                                | 7    |  |

|    | b) Relay Logic                                                                            | 9    |  |

|    | c) Automatic Parameter Adjustment                                                         | 9    |  |

|    | d) Mode Control                                                                           | 10   |  |

| 4. | ITERATION SCHEMES                                                                         | 12   |  |

|    | a) Correction Proportional to Error                                                       | 12   |  |

|    | b) Fixed-Step-Size Iteration                                                              | 12   |  |

| 5. | PROGRAM FOR ITERATIVE SOLUTION OF BOUNDARY-VALUE PROBLEM USING ONLY                       |      |  |

|    | ANALOG COMPONENTS:                                                                        |      |  |

|    | (The Trajectory of a Bullet)                                                              | 14   |  |

| AΡ | PENDIX I                                                                                  |      |  |

|    | Parameter Sweep Circuit                                                                   | 18   |  |

| AΡ | PENDIX II                                                                                 |      |  |

|    | TR-48 Relay Mode Control                                                                  | 19   |  |

| ΑP | PENDIX III                                                                                |      |  |

|    | TR-48/DES-30 Hybrid Implementation of One<br>Parameter Optimizer (Boundary Value Problem) | 21   |  |

| ΑP | PENDIX IV                                                                                 |      |  |

|    | The Combination Summer and Track-Store Unit                                               | 24   |  |

# AUTOMATIC ITERATIVE OPERATION ON AN ANALOG COMPUTER

by

George Hannauer, Omri Serlin, and Peter J. Holsberg

# 1. DEFINITION OF ITERATIVE OPERATION

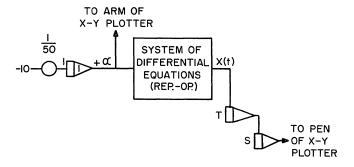

By iterative operation of an analog computer will be meant any sequence of operations that involves: (1) automatic cycling of the computer mode so that the computer goes through a number of OPERATE cycles, and (2) automatically changing some condition of the problem — an input, a parameter value, or an initial condition — between successive OPERATE cycles so that a slightly different problem is solved with each iteration

The second condition is important. It distinguishes true iterative operation from repetitive operation, which satisfies only the first condition. Repetitive operation, in fact, is not a computational technique at all, but merely a form of readout, or display. No special techniques are involved in programming a rep-op problem; in fact, programming a problem is the same for rep-op as for "real time" readout, with the exception that the programmer must restrict himself to high-speed components (e.g. quarter-square multipliers instead of servos).

In repetitive operation, much of the information generated is redundant; except for occasional

manual parameter changes, the same problem is solved again and again, and the same curve generated repeatedly. In contrast, each OPERATE cycle in iterative computation investigates a slightly different set of parameter values, and produces slightly different results. In a given number of cycles, therefore, iterative operation generates considerably more information, utilizing more fully and efficiently the analog computer's ability to produce a large amount of data in a short period of time.

The word "automatic" is also an important distinction in the above definition. In a loose sense, almost all operations of an analog computer may be classed as iterative, since rarely if ever is an operator satisfied with a single run. More typically, he will make many runs, varying parameter values from one run to the next, and observing the effect on the solution. What distinguishes iterative computation, as defined above, is the possibility of automating this procedure.

# ) or the house of property of house. Quantity of the state of the sta

Parameter Sweep. For a simple example of automatic iterative operation, consider the effect of an adjustable parameter, a, on an analog computer solution. It might be desirable to study the steady-state error of a position servo as a function of controller gain or some other control parameter, or the area of interest might be in the miss distance of a missile as a function of initial launching error. In either case, prime interest is in a single number, X. (steady-state error, miss distance, etc.) which is computed during an OPERATE cycle using a particular value of some parameter, ~ (controller gain, launching error, etc.). A value of 'a is chosen at the beginning of the OPERATE cycle, and the corresponding value of X is computed (usually X will be a final value, i.e. the output of some component at the end of the OPERATE cycle). It is desired to obtain a plot of X versus ...

Obtaining such a plot manually can be quite time-consuming. The operator has to choose several values of  $^{\circ}$ , changing pots manually between runs and tabulating the result X after each run. He can then make a point-plot of X versus  $^{\circ}$  and connect the points by a smooth curve. The procedure outlined below replaces this tedious work with a single computer run, in which the desired graph is automatically produced by an X-Y plotter. The necessary circuit is described in Appendix 1.

b) Optimization. Optimization problems arise quite frequently in design studies. In many cases, a long sequence of computer runs is made, with parameter adjustments between runs to achieve some optimum condition such as maximum profit, minimum cost, minimum error, etc.

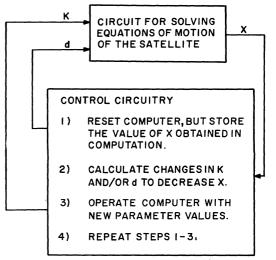

For example, consider the design of a control system to stabilize the orientation of a satellite. Suppose the system is characterized by two parameters: a gain  $\underline{K}$  and a dead-zone  $\underline{d}$ . The problem is to correct a given orientation error with minimum fuel consumption. The general approach is given in Figure 2-1.

The computer is placed in the OPERATE mode for a sufficient length of time to correct the initial error, and the amount of fuel used is "remembered" by a storage device. The values of X from several successive OPERATE cycles may be stored if needed. On the basis of these

d = WIDTH OF DEADZONE IN ERROR SENSING DEVICE

K = CONTROLLER GAIN

X = AMOUNT OF FUEL USED IN THE CORRECTING MANEUVER

Figure 2-1

results, changes are made in dor Kor both, and the problem is re-run. The process is continued until a minimum is reached.

This type of problem differs from parameter sweep in that the former is purely "openloop" i.e. the changes in parameter values are determined in advance, while in optimization problems the parameter changes are allowed to depend on the results of previous runs. The circuitry for performing the required storage, parameter changes, etc. will be discussed in Sections 3 and 4.

Boundary-Value Problems. The analog computer is essentially an initial-value device; that is, from the many possible solutions to a given set of differential equations, a single one is determined by specifying initial values for the variables, i.e. values at time zero. In contrast, many problems are stated in terms of boundary values, which must be met by trial and error, i.e. by some sort of iteration process.

The most common examples of boundary value problems arise in the solution of partial differential equations which are discussed below. However, occasionally one runs into the same problem with ordinary differential equations, as in the following example:

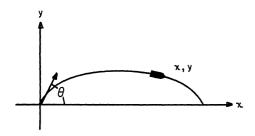

A bullet is fired from a cannon at an inclination  $\theta$  from the horizontal, and with a muzzle

velocity  $V_{\text{O}}$ . In the absence of air resistance, the trajectory of the bullet is described by the equations:

$$\dot{\mathbf{x}} = \mathbf{V_0} \, \cos \theta \quad \mathbf{x(0)} = 0 \tag{2-1}$$

$$\ddot{y} = -g$$

$y(0) = 0; \ \dot{y}(0) = V_0 \sin \theta$  (2-2)

where x and y are the horizontal and vertical coordinates of the bullet respectively, as in Figure 2-2.

Figure 2-2

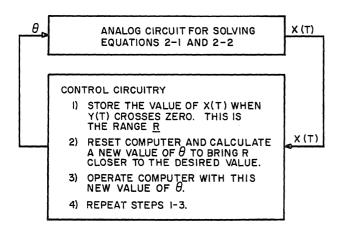

The problem is to find the firing angle  $\theta$  that will make the bullet strike a target at ground level, at a distance R from the point of firing. Thus, the problem is to find the value of x(t) when y(t) becomes zero. Figure 2-3 gives a general flow diagram for solving this type of problem. Sections 3 and 4 contain descriptions of the necessary circuits. Section 5 contains the solution of this problem.

Figure 2-3

d) Curve-Fitting. In many applications, a mathematical model with free parameters must be fitted to empirical data, i.e. a theoretical curve must be passed through a number of experimental points. As an example, suppose bench-scale experiments provide data on the decomposition of a component in a chemical reaction. Chemical theory and/or experience

suggest that the decay should satisfy the differential equation.

$$\dot{\mathbf{C}} = -k\mathbf{C}^{\mathbf{n}} \tag{2-3}$$

where C (t) is the concentration of the chemical at time t. The problem is to find numerical values of k and n so as to provide the closest agreement between the theoretical curve and the experimental data.

Let C(t) be the solution to the equation (with given values of k and n) and  $C^*(t)$  be the experimental curve. Then, it is desired to choose k and n so as to make C(t) and  $C^*(t)$  as close as possible.

To automate this, it is necessary to define some measure of the error. Defining

$$\epsilon = \int \left[ C(t) - C^*(t) \right]^2 dt \qquad (2-4)$$

the computer can be programmed to make  $\epsilon$  as small as possible. Thus, curve-fitting problems can be treated as a special case of optimization problems.

Serial Solution of Partial Differential Equae) tions. The solution of partial differential equations on a general-purpose analog computer by the usual finite-difference techniques involves a large number of similar circuits operating simultaneously. If the mesh size is small or the number of independent variables is large, then the duplication of equipment may make this approach prohibitively expensive. The simularity of circuits leads to the idea of using a single "time-shared" circuit; that is, a single circuit which performs sequentially the calculations that would otherwise be performed simultaneously by many similar circuits.

Consider the heat equation

$$\frac{\partial^2 T}{\partial x^2} = K \frac{\partial T}{\partial t}$$

(2-5)

with boundary conditions

$$T(0, t) = f(t)$$

$$T(L, t) = g(t)$$

$$T(x, 0) = h(x)$$

This system describes the temperature T(x, t) at position x and time t in a thin, homogeneous

rod of length L with an initial temperature distribution h(x) and time-varying temperatures f(t) and g(t) established at the ends.

The usual approach to analog solution of this problem is to treat x as a <u>discrete</u> variable, replace partial derivatives with respect to x by finite-difference approximations, and solve the resulting ordinary differential equations in the conventional manner.

For serial solution, the best approach is to treat t as a discrete variable and work with a system of ordinary differential equations in x. (If the reader doubts this, he may attempt serial solution with discrete x and continuous t and struggle with the boundary conditions.)

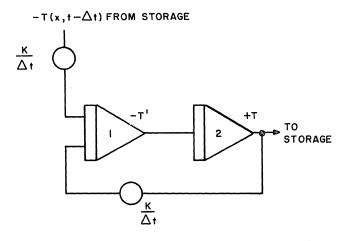

Replacing the time-derivatives with finite-difference approximations, the following equation is obtained:

$$T''(x, t) + K \frac{T(x, t) - T(x, t - \Delta t)}{\Delta t}$$

(2-6)

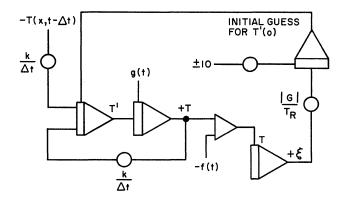

where T', T'' refer to derivates with respect to x (not t). Since the integrators on an analog computer integrate with respect to time, it is necessary to represent distance in the heat equation by time on the machine. The circuit for solving equation 2-6 is given in Figure 2-4.

Figure 2-4. Circuit for Solving Equation 2-6

The fact that computer time represents <u>distance</u> in the original equation must be taken into account in interpreting the results.

The length of the OPERATE cycle is proportional to the length of the rod. The graph produced by the

computer during a single OPERATE cycle is an instantaneous temperature profile. Establishing boundary values T (o,t) and T (L,t) for T at both ends of the rod means establishing initial and final values for the output of integrator 2.

Establishing the initial value is no problem since this means putting an initial condition directly on integrator #2. To establish a final value, an appropriate initial condition must be picked for integrator #1. This requires an iterative procedure similar to the one used for the missile trajectory problem described above. The sequence of steps would be as follows:

- 1) Use the circuit in Figure 2-4 to calculate  $T(x, \Delta t)$  with the given function h(x) = T(x, 0) as an input. Use  $f(\Delta t) = T(0, \Delta t)$  as an initial condition on amplifier 2, and guess at an initial condition for amplifier 1.

- 2) At the end of the OPERATE cycle, compare the final value T (L,  $\Delta t$ ) with the desired value g( $\Delta t$ ), and change the IC on amplifier #1 accordingly.

- 3) Iterate until the condition  $T(L, \Delta t) = g(\Delta t)$  is met.

- 4) When this condition is met, store the complete curve  $T(x, \Delta t)$  and repeat steps 1-3 with  $T(x, \Delta t)$  as an input to generate  $T(x, 2\Delta t)$ .

Continuing in this manner, a sequence of temperature profiles is obtained: T(x, o) (given),  $T(x, \Delta t)$ ,  $T(x, 2 \Delta t)$ ... $T(x, n \Delta t)$ .

NOTE that this application involves an iteration within an iteration. Such computations are referred to as nested computations.

All of these problems, with the possible exception of the last, can be solved on the TR-48 provided the number of adjustable parameters involved is not too great. What distinguishes the last example is the need for curve storage — the entire curve  $T(x,\Delta t)$  must be stored and used as an input to generate  $T(x,t+\Delta t)$  in the next OPERATE cycle. In contrast, only a few numbers need be remembered at any one time to solve the other problems.

Curve storage is possible on the TR-48 but the equipment requirements are severe. At present, it is more practical to solve problems requiring curve storage on a larger machine such as the 100 amplifier 231-R. VA number of circuits are available, (References 2, 3, and 4).

Frome come touch system is been.

# 3. ITERATIVE REQUIREMENTS AND CIRCUITS USING ONLY ANALOG INTEGRATORS

In each of the preceding applications the conventional analog circuit that solves the dynamic equations of the basic problem is supplemented by a number of additional components to perform the iteration. These additional components must be capable of performing the following functions:

Storage: The computer must "remember" the results of previous computations, using them, if necessary, in the computation of new parameter values for successive runs.

Logic: The computer must decide which parameter(s) to alter, and must route signals into and out of storage in response to the results of past computations.

Automatic Parameter Adjustment: The computer must be able to change the values of important parameters and initial conditions.

Mode Control: The computer must be automatically cycled through a sequence of modes. Normally, the RESET and OPERATE modes will alternate, but more complicated sequences are sometimes desirable.

The ability of a computer to store information, make logical decisions, and alter its own program has long been a familiar concept to digital computer users. What is not so well known is that an analog computer can also perform these functions, as the following pages will indicate.

This section will deal with the above requirements and how they can be met on an analog computer. The circuits given below are not necessarily the best or most economical. They have been chosen with one overriding consideration in mind — they can be mechanized by ordinary general-purpose analog components, without special-purpose external equipment.

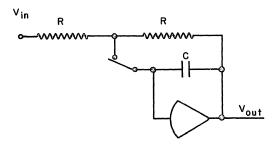

a) Storage. Since an analog signal is a voltage, it may be stored on a charged capacitor. Readout of the stored information must take place without drawing appreciable current from the capacitor, as drawing current will partially discharge it, resulting in an erroneous reading. This requirement for 'nondestructive readout' implies that an amplifier will be necessary.

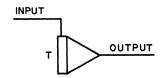

Consider the circuit in Figure 3-1 in which an amplifier and a capacitor are combined. Were it

not for the presence of the capacitor, this circuit would simply be an inverter with the relation  $V_{out} = -V_{in}$ .

The effect of the capacitor is to make  $V_{out}$  lag slightly behind  $-V_{in}$ , but this lag will be negligible provided  $V_{in}$  is not changing too rapidly, and the capacitor is sufficiently small. (The transfer function of the circuit is

$$\frac{V_{out}}{V_{in}} = -\frac{1}{1 + RSC}$$

and this is nearly -1 as long as the time constant RC is small.)

If the relay is opened, the amplifier behaves like an integrator in the HOLD mode, and  $V_{out}$  remains constant at the value it had when the relay opened. The amplifier is said to  $\underline{\text{track}}$ , or follow its input voltage when the relay is closed, and  $\underline{\text{store}}$ , or hold its value when the relay is opened.

Figure 3-1

The circuit in Figure 3-1 is essentially the initial condition circuit of an integrator. If an input variable is patched into the IC terminal of an integrator, the integrator will track that variable in the RESET mode and store it in the HOLD mode (and even in the OPERATE mode if the integrator has no other inputs).

Since switching an integrator from tracking to storing is accomplished by changing its mode, it is necessary to be able to control the integrator modes individually. This can be done on the TR-48, as the integrator relay coils appear on the patch panel. A detailed description of TR-48 mode control is given in Appendix 2. The devices described below all use the track-store principle outlined above but they differ in their mode control.

TRACKING AMPLIFIER

Patch RESET coil to OPERATE bus

Patch OPERATE coil to RESET bus

Remove β plug

(Tracks when computer is in OPERATE; stores

when computer is in RESET)

STORAGE AMPLIFIER Patch OPERATE and RESET coils normally Remove  $\beta$  plug (Stores when computer is in OPERATE; tracks when computer is in RESET)

COMPARATOR CONTROLLED TRACK-STORE UNIT

Omit mode control connections Connect SJ' ( $\underline{not}$  SJ) to B through comparator contacts

(Stores when comparator is open, tracks when comparator is closed)

Remove  $\beta$  plug

### Notes:

- 1) The T and S amplifiers are named after what they do in <u>OPERATE</u> T tracks and S stores. In RESET, they do the opposite.

- 2) Input resistor networks need not be patched.

- 3) Removal of  $\beta$  plug reduces the tracking error by shortening the time constant.

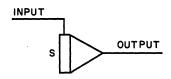

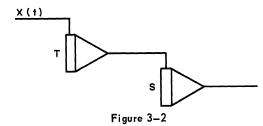

In order to store a result from a previous computation cycle, a tracking amplifier and a storage amplifier in cascade are used, as in Figure 3-2. The problem variable, X (t), is tracked during an OPERATE cycle, and its final value is stored between OPERATE cycles. The result is shown in Table 3-1; after every OPERATE cycle except the first, the output of amplifier S is the final value of X from the previous computer run. If it is desired to store a value of X other than a final value, the T amplifier can be replaced with a comparator-controlled track-store unit.

In OPERATE, T tracks and S stores. In RESET, their functions are reversed.

Table 3-1 indicates the behavior of T and S amplifiers, where  $X_1$ ,  $X_2$ ,  $X_3$  are the solutions produced during the 1st, 2nd, 3rd OPERATE cycle.

TABLE 3-1

| Computer<br>Mode | Behavior of<br>Amplifier T            | Behavior of<br>Amplifier S          |

|------------------|---------------------------------------|-------------------------------------|

| R                | Stores (output = O)                   | Tracks (output = O)                 |

| 0                | Tracks - X <sub>1</sub>               | Stores (output is still O)          |

| R                | Stores - X <sub>1</sub> (final value) | Tracks X <sub>1</sub> (final value) |

| 0                | Tracks - X <sub>2</sub>               | Stores X <sub>1</sub> (final value) |

| R                | Stores - X2 (final value)             | Tracks X <sub>2</sub> (final value) |

| <b>O</b>         | Tracks - X <sub>3</sub>               | Stores X <sub>2</sub> (final value) |

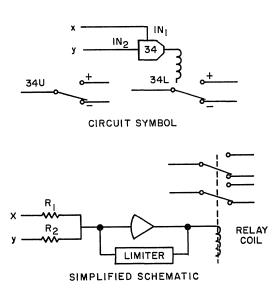

b) Relay Logic. Logical decisions on the analog computer are often made by relay comparators. The relay comparators consists of a highgain amplifier whose output drives the coil of a DPDT relay. The relay contacts normally make to the side marked "+"; they transfer to the side marked "-" when the sum of the input voltages becomes negative. (See Figure 3-3.)

Figure 3-3. The Relay Comparator

It should be noted that the input resistors on the TR-48 comparator are <u>not</u> equal. Therefore, a pot may be necessary to attenuate one of the inputs and assure that the switching occurs exactly when X + Y crosses zero.

The comparator is numbered with the number of the amplifier immediately to its <u>left</u> on the patch panel; this convention makes it easy to locate the comparator when patching. The letters "U" and "L" on circuit diagrams refer to the upper and lower sets of contacts respectively.

eter in an analog computer circuit is a number which is constant during any single OPERATE cycle, but which is allowed to change value between successive OPERATE cycles. Usually such parameters are represented by pot-settings, and the pots are adjusted manually between computations. However, in automatic iterative computation, the parameter value is changed by the computer itself, which means that the parameter must be regarded as a computer variable, that is, as an amplifier output voltage.

Let  $\alpha$  be the parameter that must be maintained constant during a computer run and vary between runs by an amount  $\Delta \alpha$ . The value of  $\Delta \alpha$ , i.e. the magnitude and direction of the change in  $\alpha$ , can be made to depend on the results of previous computations. Hence,  $\Delta \alpha$  will also be an amplifier output voltage. Methods of calculating  $\Delta \alpha$  are discussed in Section 4.

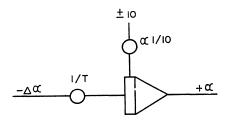

The easiest way to change  $\alpha$  in the desired manner is to use an integrator, as in Figure 3-4.

Figure 3-4

Since  $\alpha$  is to be constant during a computer run, the integrator must be in the HOLD mode when the rest of the computer is in the OPERATE mode. Since  $\alpha$  is supposed to change between computer runs, the integrator must be in the OPERATE mode when the rest of the computer is in RESET and the problem is being reset for the next run. This type of mode behavior can be achieved on a TR-48 by patching the OPERATE coil to the RESET bus. (See Appendix 2 for an explanation of TR-48 mode control.)

An "initial condition" must be chosen for a, that is a value for the first run. This is, of course, an initial condition on the integrator. The mode control must be arranged so that the integrator is in the RESET mode at the beginning of the iteration. A method of accomplishing this is given in Section 3d.

The three most common uses of the signal are:

- 1) as an initial condition

- 2) as an additive constant, or bias voltage

- 3) as a coefficient

In cases 1) and 2) the voltage  $\alpha$  may be fed directly to the problem, as a voltage input is what is required. In the third case,  $\alpha$  exists as a voltage, but a coefficient is needed. This means that a quarter-square multiplier must be used, as shown below.

Figure 3-5

The net result is that an input is multiplied by a constant coefficient,  $\alpha/10$ , which is a number between zero and one (in magnitude). This circuit is, therefore, equivalent to feeding x through a pot, except that changing the value of  $\alpha$  will "reset the pot" automatically.

- d) Mode Control. For the purposes of iterative computation, it is necessary to cycle the computer mode automatically between RESET and OPERATE. The repetitive operation unit does exactly this, and can be used in some forms of iterative computation. However, its use suffers from a number of limitations:

- 1) For some purposes it is too fast the longest OPERATE cycle obtainable is 200 milliseconds, which makes readout on an X-Y plotter impractical. Also, manyprograms rely heavily on relay comparators to make the necessary logical decisions, and a 200 millisecond OPERATE cycle followed by a 10 millisecond RESET cycle does not always allow these relays sufficient throwing time.

- 2) When using the rep-op drive, there is some uncertainty about the first and last cycles. Switching transients may destroy the accuracy of the first computation. In "open-loop" iteration, (parameter sweep) this is not a serious defect, but in "closed loop" iteration, in which the parameter values for a given OPERATE cycle depend on the stored results from previous cycles, the effect can be serious.

- 3) It is desirable to have a means of cycling the computer mode on machines not equipped with rep-op.

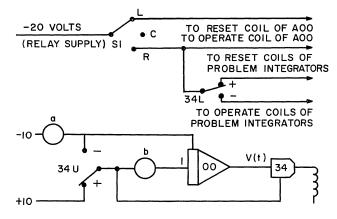

The circuit below meets all these requirements. The RESET and OPERATE times are individually adjustable over a wide range. The iteration is started and stopped by a manual switch. This switch allows the entire iteration to be switched through RESET, HOLD, and OPERATE modes.

Finally, this circuit, which involves only one integrator, two pots, and a comparator, can be used on machines not equipped for repetitive operation.

When using this form of relay switching, the individual integrator coils should be patched directly to the switch and relay contacts. The regular mode busses are not used.

Switch S1 is initially in the LEFT position putting A00 in RESET and all integrators which are patched to the relay contacts in HOLD.

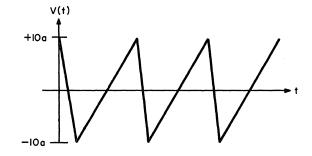

Putting switch S1 to the CENTER position puts every integrator in HOLD. When S1 is thrown to the RIGHT position, A00 integrates and produces an asymmetrical sawtooth, as shown in Figure 3-6. A00 starts from an initial condition + 10a and integrates down at the rate of -10b volts per second. When it reaches -10 volts, comparator 34 switches, and A00 integrates up at the rate of + 10ab volts per second until it reaches + 10a, when comparator 34 switches again. The integrators patched to the comparator contacts are cycled between RESET and OPERATE.

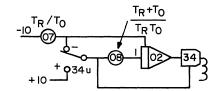

Figure 3-6. Output of A00 Versus Time

The output of A00 varies from + 10a to -10 volts. The total voltage variation is 10a + 10 or 10 (a+1) volts. With Comparator 34 in the "+" position (which puts the computer on RESET) the rate of integration is -10b volts per second, and hence if  $T_R$  is the length of the RESET cycle the result is 10b  $T_R$  = 10 (a+1) or

$$T_R = \frac{a+1}{b}$$

Similarly, the integration rate of A00 is +10ab volts per second when comparator 34 is in the "-" position and the computer is in OPERATE. So, therefore, 10ab  $T_{O} = 10$  (a+1) or

$$T_O = \frac{a+1}{ab}$$

. . .where  $T_{O}$  is the length of the OPERATE cycle.

Solving for a and b,

$$a = T_R/T_O$$

$$b = \frac{T_R + T_O}{T_R T_O}$$

If a ten-second OPERATE cycle followed by a one-second RESET cycle is wanted, a = 0.100 and b = 1.100 is necessary. Since a pot-setting greater than 1 is impossible, a gain of 10 on the integrator is used and the "b" pot is set for b/10 = 0.110.

The operational procedure is as follows: put the manual switch to the left, and select the HOLD mode on the pushbutton mode-control panel. It can be regarded that the L, C, and R switch positions represent RESET, HOLD, and OPERATE cycles for the entire iteration; RESET and OPERATE for the individual runs are obtained by the switching of comparator 34.

In section 3C an integrator was used for automatic parameter adjustment. This integrator must cycle between HOLD and OPERATE during the iteration, but should be reset at the <u>beginning</u> of the iteration. This object can be achieved by patching its OPERATE coil to the + contacts and its RESET coil to the left contact on the manual switch. The integrator will then be reset with A00.

Since the iteration commences with a RESET cycle, the parameter,  $_{\alpha}$ , will be updated by an amount  $\Delta_{\alpha}$  before the first run. If  $_{\alpha}$  is the desired value of  $_{\alpha}$  for the first run, the IC on the integrator should be  $_{\alpha}_{1}$  - $\Delta_{\alpha}$ .

#### 4. ITERATION SCHEMES

In cases where a parameter,  $\alpha$ , is being used to meet a boundary value or a minimum condition, it must be decided what change to make in  $\alpha$  for the next run. A formula for calculating the parameter value for the next run from the results of previous runs is called an <u>interation scheme</u>. Two iteration schemes will be considered here. For simplicity, they will be limited to the case of a single parameter,  $\alpha$ . Iteration with several parameters is considered in References 6 and 7.

a) Correction Proportional to Error. Suppose it is necessary to vary a parameter or initial condition,  $\alpha$ , to meet the boundary condition  $X_f = a$ , where  $X_f$  is the final value of a variable X, such as the horizontal displacement of the bullet in the missile trajectory problem or the temperature T in the heat equation.

If an error is defined by  $\epsilon = X_f - a$ , then a reasonable change in  $\alpha$  would be

$$\Delta \propto = \mathbf{G}$$

where G is a constant. This scheme makes large corrections for large errors and small corrections for small ones, which is reasonable. If  $\alpha$  eventually settles down to a steady value, then  $\Delta$  will approach zero, and therefore  $\epsilon$  will approach zero, which is what is wanted.

If  $\epsilon$  is an increasing function of  $\alpha$ , then the constant G should be negative so as to change  $\alpha$  in the right direction to decrease  $\epsilon$ . On the other hand, if  $\epsilon$  is a decreasing function of  $\alpha$ , then G should be positive. This means that the method is most useful in cases where it is known a priori whether  $\epsilon$  is increasing or decreasing with  $\alpha$ . This is the case with the heat equation. Figure 4-1 shows how Figure 2-4 may be modified by adding storage and parameter change circuits to effect the iteration scheme. The parameter  $\alpha$  to be varied is  $\alpha=T$  (0) and the computer effects the change in  $\alpha$  by integrating the error  $\epsilon$  during the RESET cycle, whose length is  $T_R$ .

In cases where  $\epsilon$  is sometimes an increasing function of  $\alpha$  and sometimes decreasing, the above scheme is less practical. In these cases an alternative is to minimize the absolute error  $|\epsilon|$ . This approach reduces the boundary value problem to a problem in optimization.

b) <u>Fixed-Step-Size Iteration</u>. Consider the problem of choosing a value for the parameter  $\alpha$  to minimize the result X. X may be the absolute

Gradualt byoc

Figure 4–1. Iterative Circuit for Solving the Boundary-Value Problem in Section 3e, Using the Iteration Scheme  $\Delta \approx \mathbf{G} \in \mathbf{G}$

error in a boundary value problem, as described in Section 4a above, it may be the error in a curve fitting problem, as in Section 2d, or the amount of fuel consumed during a satellite maneuver, as in Section 2b. Many iteration schemes are possible, but the following one is probably the simplest to mechanize. (In the following paragraph, subscripts refer to computer runs. Thus  $\alpha_1$  is the value of  $\alpha$  used in the first run,  $X_1$  is the result obtained from the first run, etc.)

- 1) Pick a starting value for  $\alpha$ , say  $\alpha_1$

- Make a run with this value and store the result X<sub>1</sub>

- 3) Change  $\alpha$  by a fixed amount  $\Delta_{\alpha}$  and make a new run with the value  $\alpha_2 = \alpha_1 + \Delta_{\alpha}$ . Store the result  $X_2$ .

- 4) Compare the values  $X_1$  and  $X_2$ . If  $X_2$  <  $X_1$ , increase  $\alpha$  by the same amount  $\Delta \alpha$  and repeat.

- 5) Continue as long as X decreases with each successive change in  $_{\alpha}$ .

- 6) When finally an <u>increase</u> in X is obtained this is an indication that the minimum value has been overshot. When this happens, cut the step-size  $\Delta = 1$  in half, and reverse its sign.

The following table gives an indication of what to expect when this procedure is followed. In this table, X,  $\alpha$ , and  $\Delta \alpha$  are all computer variables and are given in volts.

| Run # | _ α   | <u>X</u> | $\Delta \propto$ for next run |

|-------|-------|----------|-------------------------------|

| 4     | 1.00  | . 0. 00  | . 1 00                        |

| 1     | 1.00  | +9.82    | +1.00                         |

| 2     | 2.00  | +7.17    | +1.00                         |

| 3     | 3.00  | +6.61    | +1.00                         |

| 4     | 4.00  | +6.29    | +1.00                         |

| 5     | 5.00  | +6.73    | -0.50                         |

| 6     | 4.50  | +6.10    | -0.50                         |

| 7     | 4.00  | +6.29    | +0.25                         |

| 8     | 4.25  | +6.07    | +0.25                         |

| 9     | 4.50  | +6.10    | -0.125                        |

| 10    | 4.375 | +6.02    | etc                           |

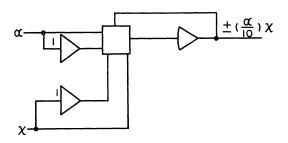

Note that some of the runs are redundant; run 7 duplicates run 4 and run 9 duplicates run 6, but this duplication is not a serious drawback. To mechanize the reversal of sign, the following circuit can be used:

The mode control relays on integrators 1 and 2 are patched so that they integrate in RESET and hold in OPERATE. The comparator contacts assure that the integrators will receive inputs only when  $X_n > X_{n-1}$ ; that is, only when the last parameter change made things worse instead of better. When  $X_n > X_{n-1}$ , the integrators will integrate for one RESET cycle, and then HOLD.

The system in Figure 4-2 produces a damped sinewave output. The pot-settings can be chosen so that the half-period of this damped sinewave is equal to the RESET time, and the amplitude decays by a factor of 1/2 in this time. At the end of the RESET cycle, the integrators hold the new value of  $\Delta \infty$ , which is - 1/2 times the previous value. Hence, in a given RESET cycle, one of two things

will happen: If  $X_n < X_{n-1}$  the value of  $\alpha$  will be updated by an amount  $\Delta \alpha$ . If  $X_n > X_{n-1}$ , the stepsize,  $\Delta \alpha$ , is halved in magnitude and reversed in direction.

Figure 4-2

Note that in this second case, the value of  $\Delta \approx$  is changed, but the value of  $\approx$  is not. Hence, the next run will be made with the same value of  $\approx$ , and should yield the same value of X.

The comparator will then be comparing two equal voltages, and it becomes a matter of chance whether it will decide to update  $\alpha$  or reverse  $\Delta\alpha$  during the next RESET cycle. To avoid this difficulty, the comparator is slightly biased so that when in doubt, it updates  $\alpha$ .

# 5. PROGRAM FOR ITERATIVE SOLUTION OF A BOUNDARY-VALUE PROBLEM USING ONLY ANALOG COMPONENTS

In this section the trajectory problem given in section 2c is solved. The circuit is described in detail and a typical set of results is given.

The dynamic equations of the bullet, which were given in Section 2c, are repeated here for reference:

$$\dot{\mathbf{x}} = \mathbf{V}_{\mathbf{O}} \cos \theta \quad \mathbf{x}(\mathbf{0}) = 0 \tag{5-1}$$

$$\ddot{y} = -g$$

$y(0) = 0; \dot{y}(0) = V_{O} \sin \theta$  (5-2)

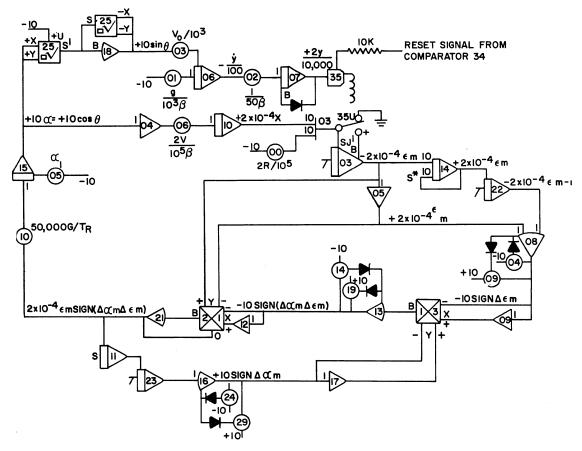

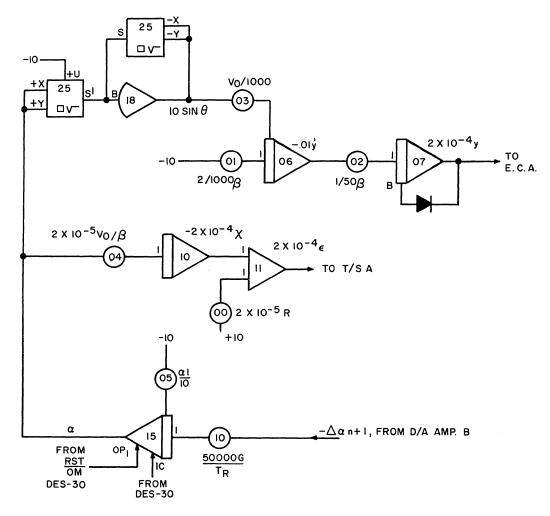

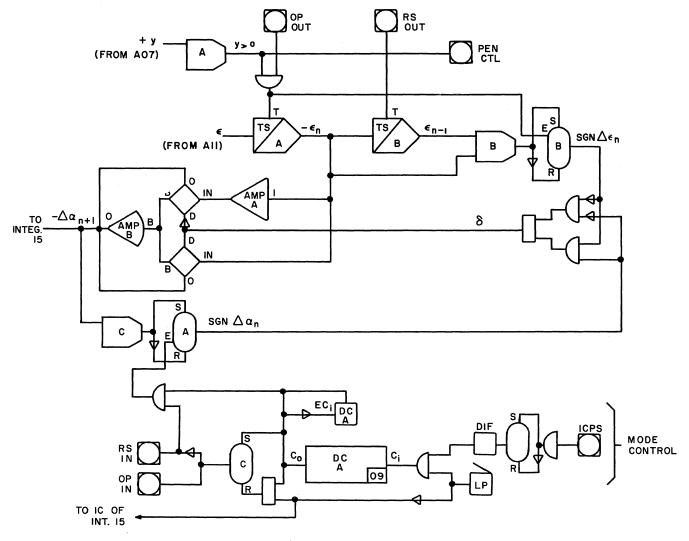

The solution of these equations on an analog computer is straightforward. Equation 5-1 requires one integrator and equation 5-2 requires two. An inspection of figure 5-1 indicates that an additional fifteen amplifiers and three multipliers are required to effect the iteration scheme. In view of the triviality of the differential equations (Eq. 5-1 and Eq. 5-2 may be solved analytically by direct integration) it appears ridiculous (and indeed it is) to use such a sophisticated and expensive iteration scheme. However, the circuit is intended as a general illustration, not as a solution of a specific practical problem. The following points should be noted:

- 1) The circuit was chosen to illustrate a number of interesting techniques. A number of modifications could have been made in the interest of equipment economy, but the present circuit illustrates the individual operations better.

- 2) The interest here is in the iteration scheme, not in the differential equations. Hence a trivial set of differential equations, which leads to an interesting and complex iteration scheme, was deliberately chosen. The dynamic equations could have been made considerably more complex by the addition of aerodynamic forces on the projectile. Some of these aerodynamic terms are quite complex and nonlinear, and would result in the bulk of the computing capacity being used to solve the differential equations. The iteration scheme would, of course, remain the same. However, from the point of view of illustrating the iterative techniques nothing would be gained by making the differential equations more complex.

Figure 5-1. Program for Iterative Solution of Boundary-Value Problem

3) Most of the amplifiers (and two of the three multipliers) are performing essentially digital functions — storage, gating, logic, etc. The use of a few digital devices (AND gates, flip-flops, etc.) would materially simplify the program. Such components are available for larger computers, such as the 100-amplifier PACE 231-R.

The EAI DES-30 Digital Expansion System, a general-purpose, patchable digital logic package, provides digital expansion of the TR-48 analog computer used here. Appendix 3 describes this essentially hybrid implementation of the problem in which the all-analog simulation is modified so that the logic functions are performed by DES-30 logic elements.

In many practical cases, it is possible to use a far simpler iteration scheme than the one shown here. The iteration circuit in Figure 4-1, for solving the heat equation, should be regarded as more typical of a large number of one-point boundaryvalue problems. In this example also, the differential equation would be made more complex if appropriate non-linearities were introduced-such as a temperaturedependent thermal conductivity. Such a nonlinearity would result in the addition of a diode function generator and a multiplier to the circuit for solving the differential equation, but the iteration scheme would remain the same.

#### ANALYSIS OF THE CIRCUIT

The parameter to be controlled is the firing angle  $\theta$ . However, the equations require  $\sin\theta$  and  $\cos\theta$ . If  $\theta$  were chosen as the iteration parameter, it would be necessary to use two DFG's to generate  $\sin\theta$  and  $\cos\theta$ . The equipment requirement is reduced by defining  $\alpha=\cos\theta$  and iterating on  $\alpha$ . Then,  $\sin\theta$  can be obtained from the relation

$\sin \theta = \sqrt{1-\cos^2 \theta}$ , which holds when  $\theta$  is in the first quadrant. This relation can be mechanized by a single amplifier and one multiplier (see amplifier 18, figure 5-1). This circuit makes use of the possibility of separating the TR-48 quarter-square multiplier into two independent  $X^2$  generators. The iteration scheme used is proportional correction:

$$\Delta \alpha_{n+1} = \pm G \epsilon_n$$

where  $\alpha_n$  and  $\epsilon_n$  are the values of  $\alpha$  and  $\epsilon$  for the nth run.

$$\Delta \alpha_{n+1} = \alpha_{n+1} - \alpha_n$$

$$\Delta \epsilon_n = \epsilon_n - \epsilon_{n-1}$$

$$\Delta \alpha_n = \epsilon_n - \alpha_{n-1}$$

The use of the plus or minus sign is determined by the following rule: The signs of  $\Delta \alpha_n$  and  $\Delta \epsilon_n$  are compared; if they are alike, this is taken as an indication that  $d\alpha/d\epsilon$  is positive, and the - sign is used. If they are unlike, the + sign is used.

Figure 5-1 gives the appropriate circuit. Amplifiers 06, 07, and 10 solve the dynamic equations. The value of x is to be sampled when y crosses zero. This will not happen at the end of an operate cycle, but at some time during the cycle. Hence a comparator-controlled track-store unit is used. When y crosses zero, comparator 35 flips to the minus side, switching amp 03 from TRACK to STORE. Amplifier 07 continues to integrate downward (this means a negative value of y, which has no physical significance). A feedback diode is used to prevent the output of amp 07 from becoming more negative than about half a volt. This is to prevent overload in case the OPERATE cycle continues for a long time beyond the collision point (the length of the OPERATE cycle is fixed).

Amplifier 03 is a combination summer and trackstore unit (see Appendix 4). The desired value of the range R is set in on pot 00, and amplifier 03 tracks and stores the error. At some point in the OPERATE cycle amplifier 03 is switched from the TRACK mode to the STORE mode, and it should remain in this mode throughout the rest of the OPERATE cycle and the following RESET cycle. However, during this RESET cycle, the control signal, which is derived from amplifier 07, will be reset to zero, which will flip the comparator to "+" and return amplifier 03 to the TRACK mode prematurely. To prevent this, the second input to comparator 35 is connected to the RESET signal from comparator 34 (see figure 5-2) which is performing the mode cycling. When the main problem integrators 06, 07, and 10 are being reset, a -20 volt signal appears at this terminal, latching the comparator in the "-" state and assuring that amplifier 03 remains in the STORE mode throughout the RESET cycle. Since the -20 volt relay power supply is a larger signal than is normally used on the TR-48 patch panel, an input resistor of 10K is used to cut down comparator sensitivity. This resistor may be a "gain 10" resistor from any of the unused amplifier networks.

Amplifiers 14 and 22 delay the stored error by one cycle (see Table 3-1 and Figure 3-2). Amplifier 14 (marked S\*) behaves like an ordinary S (Storage) amplifier, but its mode control is a bit different from that described in section 3a. It cycles between OPERATE and HOLD instead of OPERATE and RESET. An ordinary Storage amplifier, as described in section 3a, could have been used, but this trick enables the amplifier to share a dual integrator network with amplifier 15, reducing the number of integrator networks required.

Amplifier 08 is a high-gain amplifier. Instead of a feedback resistor, it has a feedback limiter circuit designed to limit it to approximately ±10 volts. The output of amp 08 may be thought of as essentially a digital signal, having the value -10 when  $\epsilon_n > \epsilon_{n-1}$ and +10 when  $\epsilon_n < \epsilon_{n+1}$ , or in more concise terms, its output is -10 sign ( $\Delta \epsilon_n$ ). Similarly, the output of amplifier 16 is +10 sign  $\Delta \alpha_n$ , which has been computed from the value of  $\Delta\alpha$  for the last run, delayed one cycle. The signs of  $\Delta \alpha_n$  and  $\Delta \epsilon_n$ are compared by multiplier 13, which acts as a "coincidence gate" or "exclusive OR" circuit. The output of amplifier 13 is -10 volts if  $\Delta \alpha_n$  and  $\Delta \epsilon_n$  have the same sign, and +10 volts if they have opposite signs. Multiplier 21 multiplies this logic signal by  $\epsilon_n$ , so that the output of amplifier 21 is proportional to  $\pm \epsilon_n$ , the sign depending on the relative signs of  $\Delta \alpha_n$  and  $\Delta \epsilon_n$ . The signs on the multipliers are chosen so that the output is proportional to  $-\Delta \alpha_{n+1}$ . This signal is delayed by amplifiers 11 and 23 and converted to a binary signal by amplifier 16, so that it can be used to determine the direction of change for the next run.

The output of amplifier 21 is just what is needed for the iteration scheme  $\Delta \alpha_{n+1} = \pm G \epsilon_n = -G \epsilon_n$ SIGN  $(\Delta \alpha_n \Delta \epsilon_n)$ . Pot 10 introduces the constant G and the appropriate scale factor. Its output is -10  $\Delta \alpha_{n+1}/T_R$ . Amplifier 15, the parameter updating integrator, is connected so that it operates when the main problem is in RESET and holds when the main problem is in the OPERATE mode. It integrates the constant  $-10 \Delta \alpha_{n+1}/T_R$  for a constant interval T<sub>R</sub> (the RESET time) and its output changes by an amount +10  $\Delta\alpha_{n+1}$  in this time. Thus its output,  $+10\alpha = +10\cos\theta$  is appropriately updated during the RESET cycle and its new value is held during the following OPERATE cycle. Multiplier 25 and amplifier 18, as described above, provide the necessary squaring, subtraction, and square root functions to generate  $10 \sin \theta$  from the input  $10\cos\theta$ .

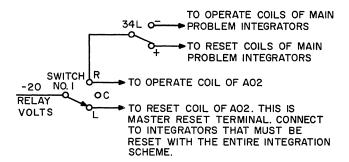

Figure 5-2 gives the circuit for the mode control cycling. The operation of this circuit was analyzed in detail in section 3-d. Note that the MASTER

Figure 5—2. Mode Control Circuitry for Boundary-Value

Problem

RESET terminal on switch #1 may be patched to the RESET coil of the parameter-updating integrator 15, to enable a first-run value  $\alpha_1$  to be established on the integrator. The computer mode busses are completely unused, and all mode control signals are obtained from the manual switch and the comparator. The -20 volt relay power supply is terminated on the TR-48 patch panel in a terminal marked RV (relay voltage). This terminal is in the lower left corner of the readout panel.

Since the RESET and OPERATE busses are not used in this circuit, the operation of the circuit will be independent of the mode pushbuttons on the control panel, except for the POT-SET mode, which closes a relay around every amplifier. The POT-SET mode is therefore a convenient one for setting all storage amplifiers to zero before the start of the iteration. The sequence of operations to be performed by the operator is as follows:

- Put the computer in the POT-SET mode to clear all storage to zero.

- Put SWITCH #1 to left position.

- 3) Depress the HOLD pushbutton to bring the computer out of the POT-SET mode.

- 4) Put SWITCH #1 to the right position.

The computer will now cycle back and forth between RESET and OPERATE, updating the value of the parameter  $\alpha$  each time. The results may be recorded on a X-Y plotter, and the convergence observed.

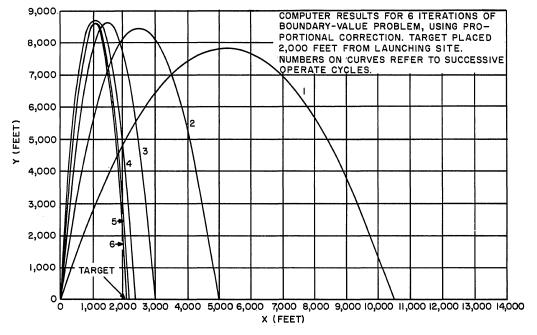

Results for a typical series of runs are given in figure 5-3. The target was placed at 2,000 feet, and a first-run value of  $\alpha$  was chosen that gives an extremely large initial overshoot. Note that the results of successive runs approach the target monotonically, and that the amount of the correction decreases as the larget is approached.

Table 5-1. Potentiometer Settings

| Pot    | Parameter                          | Numerical | _                                                                     | , up to a point, but excessive gain produces                     |

|--------|------------------------------------|-----------|-----------------------------------------------------------------------|------------------------------------------------------------------|

| Number | Description                        | Setting   | divergend                                                             | ce.                                                              |

| 00     | 2R/10 <sup>5</sup>                 | 0.040     | Table 5-2                                                             | 2. Summary of Integrator Mode Patching                           |

| 01     | $g/10^3/\beta$                     | 0.161     | 02, 03                                                                | From SWITCH 1.                                                   |

| 02     | 1/50eta                            | 0.100     |                                                                       |                                                                  |

| 03     | $v_{o}/10^{3}$                     | 0.750     | 06, 07                                                                | From lower contacts on comparator 34 RESET coils from + terminal |

| 04     | Limiter                            | 0.470     | 10, 11 OPERATE coils from - terminal                                  |                                                                  |

| 05     | α <sub>1</sub>                     | 0.100     | 14, 15                                                                | RESET coil patched to SWITCH 1, left                             |

| 06     | $2\overline{V_0}/10^5\beta$        | 0.075     |                                                                       | terminal.                                                        |

| 07     | T <sub>R</sub> /T <sub>op</sub>    | 0.500     |                                                                       | OPERATE coil from + terminal, com-                               |

| 08     | $(T_R + T_{op})/T_R T_{op}$        | 0.300     |                                                                       | parator 35                                                       |

| 09     | Limiter Limiter                    | 0.470     | 21, 23                                                                | From lower contacts on comparator 34                             |

| 10     | $50,000 \mathrm{G/T}_{\mathrm{R}}$ | 0.040     |                                                                       | DDCDD as the forest Associated                                   |

| 14     | Limiter                            | 0.470     |                                                                       | RESET coils from - terminal.                                     |

| 19     | Limiter                            | 0.470     |                                                                       | OPERATE coils from + terminal.                                   |

| 24     | Limiter                            | 0.470     | (The mode of these integrators is complementary to the mode of the ma |                                                                  |

| 29     | Limiter                            | 0.470     |                                                                       | problem integrators)                                             |

It is worthwhile to pay some attention to the mean-

ing of the constant G. The entire iteration scheme

may be thought of as a feedback control system con-

trolling the parameter  $\alpha$ . The correction is pro-

portional to the error  $\epsilon$ , and the constant G may be thought of as the gain of the iteration scheme.

It is interesting to run the iteration scheme several times and observe the effect of the gain G on the convergence. As expected, low gain leads to slow

convergence. Increasing the gain speeds the con-

Figure 5-3. Results for a Typical Series of Runs

### APPENDIX 1

#### PARAMETER SWEEP CIRCUIT

The NORMAL/SPECIAL option on the TR-48 integrator enables us to construct a very simple circuit for the parameter sweep problem in Section 3a. In Figure A2-1, integrator #1 is a SPECIAL integrator, while all the others, including the T and S (track and store) integrators are operating in rep-op.

Figure A2-1

After every rep-op cycle, the S-amplifier stores the final value of the variable X. This final value will change gradually as  $\times$  changes. Since  $\alpha$  is changing very slowly (it takes 50 seconds to go from zero to +10 volts) it will appear very nearly constant from the point of view of the rep-op circuit. In particular, if the rep-op rate is 20 solutions per second,  $\alpha$  will change by only 0.1 volt during a single computation. This is the smallest change that can be detected on the TR-48.

Thus, the rep-op circuit will solve the differential equations of the system for a virtually constant value of  $_{\alpha}$ , and the S-amplifier will store the final value X. After the next solution, the slightly different value of  $_{\alpha}$  will cause a small change in the value of X, and the output of the S-amplifier will change accordingly. With the  $_{\alpha}$ -integrator connected to the arm and the S-amplifier connected to the pen, the X-Y plotter will produce a graph of the final value X versus the parameter  $_{\alpha}$ .

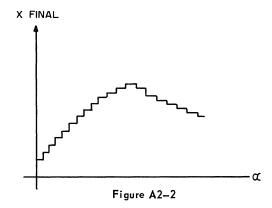

The graph should look something like Figure A2-2; that is, the graph will not be smooth, but will consist of many small steps. However, if  $\alpha$  varies over the desired range in 50 seconds, and the rep-op rate is 20 solutions per second, the graph should consist of 1,000 steps, and they should be so small as to be barely noticeable.

### APPENDIX 2

# TR-48 RELAY MODE CONTROL

The mode control on the RMC TR-48 is accomplished with relays which are energized from a -20 volt DC power supply. The individual relay coils appear on the patch panel, which allows for independent control of integrator mode.

The relays normally receive inputs from two mode control busses, called the RESET bus and OP-ERATE bus. Each bus is energized from the corresponding pushbutton on the mode control panel:

- When the RESET mode is selected with a pushbutton, the RESET bus is energized with -20 volts and the OPERATE bus is de-energized.

- When the OPERATE mode is selected, the OPERATE bus is energized, and the REset bus de-energized.

- 3) In the REP-OP mode, the RESET and OPERATE busses are energized alternately, thus cycling the computer between RESET and OPERATE.

- 4) When the HOLD mode is selected, both busses are de-energized.

Each dual integrator network has two input terminals on the patch panel which go to relay coils. These terminals will be referred to as the RESET coil and the OPERATE coil. (This is an over simplification — actually, one of the terminals energizes two relay coils, but this is not important from a programmer's point of view):

- 1) When the RESET coil is energized, the integrator is in the RESET mode.

- 2) When the OPERATE coil is energized, the integrator is in the OPERATE mode.

- When neither coil is energized, the integrator is in HOLD.

- 4) If both coils are energized simultaneously, the integrator may be in any of several modes. Because of this uncertainty, the programmer should avoid simultaneously energizing both coils.

In normal operation, each coil is patched to the corresponding bus. The mode of the integrator

is then selected by the pushbuttons in the normal manner. This standard mode control connection can be made with a double horizontal bottle plug. If this plug is removed, the coils can be patched in many different ways. For example, reversing the connections (RESET coil to OPERATE bus and OPERATE coil to RESET bus) gives a tracking unit, as described in Section 3a. Integrator coils may also be energized directly from the -20 volt relay power supply or through comparators or manual switches. The relay power supply appears on the patch panel in the lower left-hand terminal of the readout panel, at the terminal marked RV (relay volts).

For some applications, it is desirable to have some integrators running in Rep-op and some in real time simultaneously. This result can be achieved on the TR-48 as follows: a shaded portion of the integrator network contains two holes marked NORMAL and two holes marked SPECIAL.

When the holes marked SPECIAL are patched together, the integrator operates normally. (When a bottle plug is used for this connection, the word SPECIAL is covered up. Hence the operator sees the word NORMAL when the integrator is operating normally). When the holes marked NORMAL are covered with a bottle plug and the word SPECIAL is exposed, the integrator operates in a special manner, i.e., it goes into the OPERATE mode as soon as the REP-OP mode button is depressed, and remains in OPERATE (with a real-time capacitor, not a rep-op capacitor) as long as the computer is in repetitive operation. An application of such an integrator is given in Appendix 1.

The mode control relays on the TR-48 are shared. by the two integrators in a dual integrator network. Hence the two integrators in a dual network must be in the same mode at any given time. The programmer must keep this in mind when assigning numbers to various components. Occasionally an integrator network will be wasted (if an odd number of integrators with a special nonstandard mode logic are required one extra network will have this same logic, whether it is needed or not). However, the waste will never amount to more than a few integrator networks. Note that an S-amplifier (storage amplifier) has the same mode logic as a conventional integrator. Hence if three S-amplifiers are needed in an iteration, the odd network can be used in the problem itself.

One other feature of the TR-48 integrator network has been used in this article. This is the possibility of changing the feedback capacitor on an integrator to increase its integration rate. This feature allows a wider range of time-scale factors than would otherwise be the case. A bottle plug, called the  $\beta$  plug, is normally patched into each integrator. Removing this plug replaces the feedback capacitor by a capacitor of 1/10 the value, increasing the integration rate by a factor of 10. This feature operates independently of mode control patching. rep-op, NORMAL/SPECIAL connections or anything else. Whatever feedback capacitor the integrator would have with the  $\beta$  plug (a rep-op or "real-time" capacitor) is replaced by a capacitor of 1/10 the value. In contrast to the mode control connections, the dual integrator has two separate  $\beta$  plugs — one for each integrator in the network.

Note: The TR-48 with Electronic Mode Control (EMC) differs only slightly from the RMC Computer in so far as the programmer is concerned, despite its completely different system of controlling the modes of integrators. The electronic switches, which replace the mode-control relays, are operated from logic signals, i.e., on the TR-48, a logical 1 = +5V and a logical 0 = 0V. Hence, the busses which feed the mode switches operate at these two levels just as the RMC busses operate at -20V and 0V levels.

The following table illustrates EMC operation.

| INPUTS |    | RESULTING   |

|--------|----|-------------|

| IC     | OP | MODE        |

| 7      | О  | RESET       |

| 0      | 1  | OPERATE     |

| 0      | 0  | HOLD        |

| 7      | 1  | NOT ALLOWED |

These inputs can be obtained by depressing the proper mode control buttons if the mode-control bottle plugs are patched, or by patching from devices which produce these levels (electronic comparators, gates, flip-flops, etc.). There is a terminal in the readout panel labeled +5V which can be used as a logical 1 level "supply".

All other components on TR-48 dual integrator networks apply to the EMC network as well as the RMC network.

In addition, EMC TR-48's are usually available with Electronic Comparator modules, which comprise one electronic comparator network, two digitally-controlled analog switch networks, and two trackstore amplifier networks. The latter obviate the need for using standard integrators as track-store devices and thus add to the flexibility of the computer. Electronic Comparator modules are also available for the RMC computer.

#### Symbols

1. Electronic Comparator (EC)

When  $e_1 + e_2 > 0$ , the "1" output is at the "1" level When  $e_1 + e_2 < 0$ , the "1" output is at the "0" level

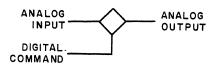

2. D/A Switch

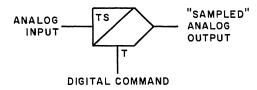

3. T/S Amplifier

## APPENDIX 3

# TR-48/DES-30 HYBRID IMPLEMENTATION OF

# ONE PARAMETER OPTIMIZER (BOUNDARY VALUE) PROBLEM

The all-analog simulation of the trajectory problem given in Section 2c is modified for hybrid implementation. The necessary logic functions are performed by the logic elements of the EAI DES -30 Digital Expansion System

# ANALOG PORTION

The analog portion of this problem is the part of figure 5-1 used to solve the equations 5-1 and 5-2. It is repeated here for reference.

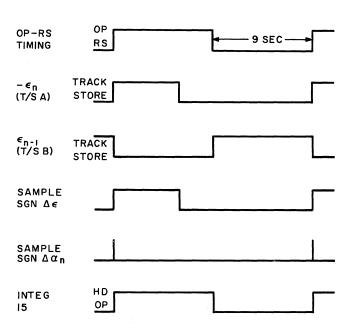

## MODE CONTROL

The mode control program (see Figure A3-2) consists of DC A and FF C. Its purpose is to provide signals to alternately throw the TR-48 into

OP (9 seconds) and RS (9 seconds). The 9 sec period is dictated by the problem solution time — longer periods may be used if desired, but not shorter periods. The program also provides the signal necessary to control the OP-HD mode of integrator 15 — the one that operates  $\alpha = \cos \theta$  from  $\Delta \alpha_{n+1}$  during the time that the problem is in RS, and goes to HD when the problem is in OP. See the timing diagram in Figure 3A-3.

The LP permits manual start-stop. When the LP is pushed, DC A counts down at the rate of 1 count per second, producing a  $C_0$  blip and reloading itself to 9. The  $C_0$  blip <u>triggers</u> FF C so that its output is high for 9 seconds and low for another 9 seconds. Thus, the complementary outputs of FF C are just the signals necessary to control the OP, RS mode inputs.

Figure A3-1: Analog Program for Equations 5-1 and 5-2

Figure A3-2: Mode Control and Optimization Logic

## OPTIMIZATION LOGIC

T/S A tracks the error,  $\epsilon_n$ , during the OP mode, while the altitude y is still positive (above ground). When y goes negative (the projectile hits the ground), comparator A goes low, and T/S unit A holds.

After the OP period is finished, the RS mode output throws T/S B into TRACK. It then tracks the output of T/S A (with sign inversion). Thus, on the next OP cycle, T/S A tracks the present error,  $\epsilon_n$ , while T/S B holds the old value,  $\epsilon_{n-1}$ . See timing diagram in Figure 3A-3.

Comparator B goes high whenever  $\epsilon_{n-1} - \epsilon_n > 0$  (that is, when  $\Delta \epsilon$  is positive) and remains low when  $\Delta \epsilon$  is negative. Thus, its output may properly be called "sgn  $\Delta \epsilon$ ". Flip flop B stores this information as of the instant when T/S A goes to STORE—that is, at the earliest instant both T/S A and T/S B are storing. This is achieved by disabling this

Figure 3A-3: Timing

FF when T/S A goes to STORE. The same effect can be achieved by enabling FF B by a blip obtained from differentiating the trailing edge of Comp. A output, but this would require a differentiator.

Note that FF B "tracks" sgn  $\Delta \epsilon$  throughout the time when y>0. It might be asked whether this has any adverse effect. It can be seen that this is not the case because integrator 15 is in HD throughout the period y>0, so that it doesn't care about sgn  $\Delta \epsilon$  (or anything else, for that matter).

FF A is enabled by a blip which is the AND of  $C_0$  and  $\overline{\text{FF C}}$  — that is, a blip occurring just prior to going into the OP mode. At this time, the output of amplifier B has  $\Delta\alpha_n$  on it, comparator C output is sgn  $\Delta\alpha_n$ , and so FF A stores sgn  $\Delta\alpha_n$ . Recall that  $\Delta\alpha_n$  is the quantity used to generate the parameter of interest,  $\alpha_{n+1}$ , that is,  $\Delta\alpha_n$  is determined during the OP mode of the previous run, not the one we are just going into.

The outputs of flip flops A and B are compared in a negated XOR (Exclusive-Or) program. An XOR is basically a digital comparator — its output is high whenever the two inputs are unequal (one is low while the other is high). Thus the negated XOR output is high whenever the inputs are equal — both high or both low. That is, the signal  $\delta$  in Figure 3A-2 is high whenever  $\operatorname{sgn} \Delta \epsilon_n$  and  $\operatorname{sgn} \Delta \alpha_n$  are equal; in Boolean notation  $\delta = (\operatorname{sgn} \Delta \epsilon_n) \cdot (\operatorname{sgn} \Delta \alpha_n)$ ; in algebraic notation  $\delta = (\operatorname{sgn} \Delta \epsilon_n) \cdot (\operatorname{sgn} \Delta \alpha_n)$ . Thus, the XOR programs replaces multiplier 13 in the all-analog implementation of this program.

Amplifier B and the associated electronic switches control the selection of the sign in the equation  $\Delta\alpha_{n+1}=\pm~G_{\varepsilon_n}$  in accordance with the signal  $\delta$  just described: when  $\delta=1$ , indicating that  $\mathop{\rm sgn}\Delta\varepsilon_n$  and  $\mathop{\rm sgn}\Delta\alpha_n$  are equal, the output of amplifier B is  $+\varepsilon_n$ ; when  $\delta=0$ ,  $-\varepsilon_n$ . (Recall that integrator 15 requires  $-\Delta\alpha_{n+1}$  at its input). Thus, amplifier B and its switches replaces multiplier 21 in the all-analog simulation.

## INITIALIZATION

In all programs of this type, initialization should carefully be considered. Initialization consists of two problems: 1) How does one get the problem started? (This is no more a simple analog set-up; we also have a digital section to worry about, and simply pushing the OP button on the TR-48

won't do!) 2) How does one make sure that all initial conditions are proper, both analog and digital?

The question of starting (and, incidentally, the related question of stopping) has been taken care of by the LP in the mode control section. When the LP is released, FF C is cleared, and the TR-48 is in RS. This assumes that the clock is running and the TR-48 is in SLAVE — which is the normal state of affairs in hybrid simulations when running. When the LP is latched, DDC A starts counting and the simulation is under way.

The question of digital initial conditions is that of the correct initial states of flip flops (GPR FF. DC FF, MT & DIF FF, etc.) For example, we may wish to set DC A to 09 manually so the cycle starts in the RS mode. If DC A is cleared, the cycle starts with OP mode. But most importantly. we must decide whether FF's A and B should be cleared or set to begin with. If we know what sgn  $\Delta_{n}$  and sgn  $\Delta_{n}$  are for the first two run (and in this problem we can find this out because it happens to be a very simple one), then we can set FF's A and B accordingly. If we do not know, as will be the case in a more sophisticated problem, then we must program an initialization run to determine the initial quantities. In this particularly simple situation, we can ignore the initial setting of FF's A and B altogether. This results in at most 2 bad runs (the first two) in which the optimization may go in the "wrong direction". However, after T/S A and T/S B have had a chance to operate once, things will quiet down.

## A LIST OF MNEMONICS (DES-30)

| Co  | Carry Out                |

|-----|--------------------------|

| DC  | Down Counter             |

| DIF | Differentiator           |

| EMC | Electronic Mode Control  |

| FF  | Flip Flop                |

| GPR | General Purpose Register |

| HD  | Hold Mode                |

| LP  | Latching Pushbutton      |

| MP  | Momentary Pushbutton     |

| MT  | Monostable Timer         |

| OP  | Operate Mode             |

| RS  | Reset Mode (IC)          |

| T/S | Track/Store              |

|     |                          |

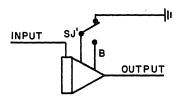

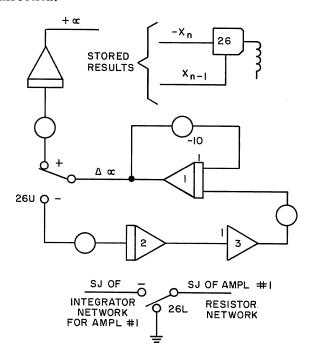

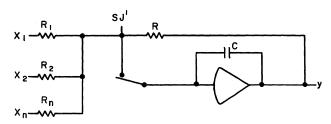

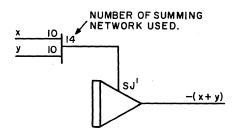

# APPENDIX 4: THE COMBINATION SUMMER AND TRACK-STORE UNIT

In many applications, it is necessary to store the sum of two or more signals. This can, of course, be accomplished with two amplifiers – a summer, and a track-store unit. However, the functions of both may be combined in a single track-store unit with several input resistors (Figure A4-1).

Figure A4-1

When the switch is closed, we have

$$y = -\frac{1}{1 + RCS} \sum_{i=1}^{n} \frac{R}{R_{i}} x_{i}$$

...and the unit acts as a combination tracksummer.

The point marked SJ' in Figure A4-1 appears on the patch panel area of a TR-48 integrator network so

that additional IC input resistors can be patched in to take advantage of this capability. In many cases, this feature saves one or more amplifiers.

Since the input resistor network of a track-store integrator is not normally used, it can be patched to the SJ' and used for multiple inputs. A symbol for this type of patching is given in Figure A4-2.

Figure A4-2

Note that a "gain of 10" on a TR-48 means a 10K input resistor, which produces an actual gain of one in this case, since the feedback resistor is also 10K. (Some TR-48's have 50K input and feedback resistors in the integrator IC networks. The individual computer should be checked for this before the circuit is used.)

## REFERENCES

- 1) Wadel, Louis B. (Chance Vought Aircraft, Inc.).

<u>Automatic Iteration on an Electronic Analog</u>

Computer. Presented at Wescon, 1954

- 2) Landauer, J.P. <u>Automatic Storage PCC#130</u>, July 1958.

- 3) Brunner, Walter. <u>Boundary-Value Problems</u> PCC#154, April, 1960.

- 4) Berthiaume, Paul. <u>Analog Computer Storage</u> Techniques and Applications PCC#170, 1961.

- Rogers, A.E. and Connolly, T.W.; <u>Analog Computation in Engineering Design McGraw-Hill</u>, New York, 1960.

- 6) Witsenhausen, Hans. <u>Fixed Step-Size Opti-mization with Several Parameters PCC#169</u>, August, 1961.

- 7) Witsenhausen, Hans. <u>Hybrid Techniques Applied to Optimization Problems</u>, Presented at Spring Joint Computer Conference, San Francisco, May 1962.

References 2, 3, 4, and 6 are PCC Reports and may be obtained from Electronic Associates, Inc., Princeton Computation Center Box 582, Princeton, New Jersey.