1

1

# ANALOG/HYBRID COMPUTING SYSTEM

# REFERENCE HANDBOOK

# ANALOG/HYBRID COMPUTING SYSTEM

# REFERENCE HANDBOOK

# **RELATED PUBLICATIONS**

The table below lists other publications which may be of interest to the readers of this manual. Unless otherwise indicated by title or footnote, all are maintenance handbooks. Note that maintenance handbooks directly applicable to a particular system are normally supplied with the system.

**Publication** Number

# Title

| Handbook of Analog Computation                                            | 00 800.0001-3  |

|---------------------------------------------------------------------------|----------------|

| Basics of Parallel Hybrid Computation                                     | 07 800.0016-0  |

| 580 Reference Handbook                                                    | 00 800.2055-0  |

| 580 Console Components Manual                                             | 00 800. 2056-0 |

| 580 Computing Components Manual                                           | 00 800. 2057-0 |

| 580 Logic Expansion Group                                                 | 00 800.2058-0  |

| 580/680 Digital Voltmeter, Model 26.268                                   | 00 800.2059-0  |

| TR20/TR48 Repetitive Operation Display Units,<br>Models 34.034 and 34.035 | 00 800.2024-1  |

### NOTICE

In order to enable us to process your requests for spare parts and replacement items quickly and efficiently, we request your conformance with the following procedure:

- 1. Please specify the type number and serial number of the basic unit as well as the EAI part number and description of the part when inquiring about replacement items such as potentiometer assemblies or cups, relays, transformers, precision resistors, etc.

- 2. When inquiring about items as servo multipliers, resolvers, networks, printed circuit assemblies, etc., please specify the serial numbers of the major equipment with which the units are to be used, such as: Console, Type 8811, Memory Module, Type 4.204, Serial No. 000, etc. If at all possible, please include the purchase order or the EAI project number under which the equipment was originally procured.

Your cooperation in supplying the required information will speed the processing of your requests and aid in assuring that the correct items are supplied.

It is the policy of Electronic Associates, Inc. to supply equipment patterned as closely as possible to the requirements of the individual customer. This is accomplished, without incurring the prohibitive costs of custom design, by substituting new components, modifying standard components, etc., wherever necessary to expedite conformance with requirements. As a result, this instruction manual, which has been written to cover standard equipment, may not entirely concur in its content with the equipment supplied. It is felt, however, that a technically qualified person will find the manual a fully adequate guide in understanding, operating, and maintaining the equipment actually supplied.

> Electronic Associates, Inc. reserves the right to make changes in design, or to make additions to or improvements in its product without imposing any obligation upon itself to install them on products previously manufactured.

#### UNITED STATES AND CANADIAN OPERATIONS

#### Marketing Division SALES OFFICE

#### EASTERN REGION

Eastern Regional Office: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764

Special System Department: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764

Customer Services: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764

Northeastern District Office: 875 Providence Highway, Dedham, Massachusetts 02026, Tel: 617-326-6756 Syracuse District Office: Pickard Building, Room 144-147, 5858 East Malloy Road, Syracuse, New York 13211, Tel: 315-455-5521

SOUTHEASTERN REGION

Southeastern Regional Office: 12260 Wilkins Avenue, Rockville, Maryland 20852, Tel: 301-933-4100

CENTRAL REGION Central Regional Office: 33166 Des Plaines Ave., Des Plaines, Illinois 60018, Tel: 312-296-8171

Cleveland District Office: 6741 Ridge Road, Parma, Ohio 44129, Tel: 216-842-1840

SOUTHERN REGION

Southern Regional Office: 3514 Cedar Springs Road, Room 211, Dallas, Texas 75219, Tel: 214-528-4920 Houston District Office: 7007 Gulf Freeway, Room 128, Houston, Texas 77017, Tel: 713-MI 4-3678 Huntsville District Office: Holiday Office Center, Suite 2, 3322 South Memorial Parkway, Huntsville, Alabama 35801, Tel: 205-881-7031

WESTERN REGION

FASTERN REGION

Western Regional Office: 1500 East Imperial Highway, El Segundo, California 90245, Tel: 213-322-3124, TWX 910-348-6284 San Francisco District Office: 4151 Middlefield Road, Palo Alto, California 94303, Tel: 415-321-0363, TWX 910-373-1241 Northwestern District Office: 1107 Northeast 45th St., Room 323, Seattle, Washington 98105, Tel: 206-632-7470

#### CUSTOMER SERVICES OFFICES

Eastern U.S. Headquarters: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764

Northeastern District Office: 875 Providence Highway, Dedham, Massachusetts 02026, Telephone: 617-326-6756 Princeton, New Jersey: U.S. Route No. 1, P.O. Box 582, Princeton, New Jersey 08541, Telephone: 609-452-2900

Resident Field Engineers: Bedford, Mass./Florham Park, N. J./Washington, D. C./Baltimore, Md./Eatontown, N. J. SOUTHEASTERN REGION Southeastern Regional Office: 12260 Wilkins Avenue, Rockville, Maryland 20852, Telephone: 301-933-4100

CENTRAL REGION

Central Regional Office: 3166 Des Plaines Avenue, Des Plaines, Illinois 60018, Telephone: 312-296-8171 Cleveland District Office: 6741 Ridge Road, Parma, Ohio 44129, Telephone: 216-842-1840 Resident Field Engineers: Detroit, Michigan/Pittsburgh, Pennsylvania/Dayton, Ohio/Warren, Michigan

SOUTHERN REGION Southern Regional Office: 3514 Cedar Springs Road, Room 211, Dallas, Texas 75219, Telephone: 214-528-4920

Houston District Office: 7007 Gulf Freeway, Room 128, Houston, Texas 77017, Tel: 713-MI 4-3678 Houston District Office: Holiday Office Center, Suite 2, 3322 South Memorial Parkway, Huntsville, Alabama 35801, Telephone: 205-881-7031

Resident Field Engineers: San Antonio, Texas/Alamogordo, New Mexico/Tulsa, Oklahoma/Houston, Texas WESTERN REGION

Western U.S. Headquarters: CUSTOMER REPAIR FACILITY, 1500 East Imperial Highway, El Segundo, California 90245, Telephone: 213-322-3220, TWX 910-348-6284 Western U.S. Headquarters: CUSTOMER SERVICES FACILITY, 1500 East Imperial Highway, El Segundo, California 90245, Telephone: 213-322-3220, TWX 910-348-6284

San Francisco District Office: 4151 Middlefield Road, Palo Alto, California 94303, Tel: 415-321-0363, TWX 910-373-1241

Resident Field Engineers: Edwards, California/Pasadena, California/Moffet Field, California/Martin Marietta Corp., Denver, Colorado/Ryan Aeronautical, San Diego, California CANADA

Toronto Office: Allan Crawford Associates, Ltd., 65 Martin Ross Avenue, Downsview Ontario, Canada, Tel: 416-636-4910

#### ANALYSIS AND COMPUTATION CENTERS

Princeton Analysis and Computation Center: U.S. Route No. 1, P. O. Box 582, Princeton, New Jersey 08541, Telephone: 609-452-2900 Los Angeles Analysis and Computation Center: 1500 East Imperial Highway, El Segundo, California 90245, Telephone: 213-322-3220, TWX 910-348-6284 San Francisco Analysis and Computation Center: 4151 Middlefield Road, Palo Alto, California 94303, Tel: 415-321-0363, TWX 910-373-1241 Washington, D. C. Analysis and Computation Center: 12260 Wilkins Avenue, Rockville, Maryland 20852, Tel: 301-933-4100 Houston Analysis and Computation Center: 7007 Gulf Freeway, Room 128, Houston, Texas 77017, Tel: 713 MI 4-3678

#### Engineering and Manufacturing Division

Engineering Department: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764 Manufacturing Department: West Long Branch, N. J. 07764, Tel: 201-229-1100, TWX 710-722-6597, Telex 01-26655, Cable: PACE West Long Branch, N. J. 07764

#### Other Departments, Divisions and Subsidiaries

Instrument Division: Long Branch, N. J. 07740, Tel. 201-229-4400, TWX 710-722-6597, Cable: PACE West Long Branch, N. J. 07740 Pacific Data Systems, Inc.: 644 Young Street, Santa Ana, California 92705, Tel. 714-540-3610, TWX 714-546-3049 Scientific Instruments Department: 4151 Middlefield Road, Palo Alto, California 94303, Tel: 415-321-7801, TWX 910-373-1241

#### INTERNATIONAL SALES & CUSTOMER SERVICES OFFICES

UNITED KINGDOM & SCANDINAVIA Electronic Associates, Ltd.: Burgess Hill, Sussex, England, Tel: Burgess Hill (Sussex) 5101-10, 5201-5, Telex: 87183, Cable: PACE Burgess Hill

Northern Area Office: Roberts House, Manchester Road, Altrincham, Cheshire, Tel: Altrincham 5426 SWEDEN

EAI-Electronic Associates-AB: Hagavagen 14, Solna 3, Sweden, Tel: Stockholm 82-40-96; 82-40-97, 83-38-60, Telex Stockholm 10064, Cable: PACE STOCKHOLM EUROPEAN CONTINENT

EAI-European Continental Regional Office: Centre International, 22nd Floor, Place Rogier, Brussels 1, Belgium, Tel: Brussels 18-40-04, Telex: 2.21-106, Cable: PACEBELG Brussels

FRANCE EAI Electronic Associates SARL: 72-74, rue de la Tombe Issoire, Paris 14e, France, Tel: 535.01.07, Telex 27610

GERMANY

EAI-Electronic Associates GMBH: 5100 Aachen, Bergdriesch 37, West Germany, Tel: Aachen 2 60 42; 2 60 41, Telex 832.676 eai d AUSTRALIA & NEW ZEALAND

EAI-Electronic Associates, Pty., Ltd.: 26 Albany St., Leonards, N.S.W. Australia, Tel: 43-7522, Cable: PACEAUS, Sydney Victorian Office: 34 Queens Road, Melbourne S. C. 2, Australia, Tel: 26-1329, Cable: PACEAUS, Melbourne JAPAN

EAI-Electronic Associates (Japan), Inc.: 9th Mori Building, 1-3 Shiba-Atago-cho, Minato-Ku, Tokyo, Japan, Tel: 433-4671, Telex: 7814285, Cable: EAIJAPACE ENGINEERING AND MANUFACTURING

Electronic Associates, Ltd.: Burgess Hill, Sussex, England, Tel: Burgess Hill (Sussex) 5101-10, 5201-5, Telex: 87183, Cable: PACE BURGESS HILL MEXICO

EAI-Electronic Associates, S.A. de C.V.: Darwin #142, Planta Baja, Col. Anzures, Mexico 5, D.F., Tel: 28-55-13, Cable: PACEMEX

#### COMPUTATION CENTERS

European Computation Center: Centre International, 22nd Floor, Place Rogier, Brussels 1, Belgium, Tel: Brussels 18-40-04, Telex: 2.21-106, Cable: PACEBELG Brussels United Kingdom Computation Center: Electronic Associates, Ltd., Burgess Hill, Sussex, England, Tel: Burgess Hill (Sussex) 5101-10, Telex: 871-183, Cable: PACE BURGESS HILL stralian Computation Center: 34 Queens Road, Melbourne S. C. 2, Australia, Tel: 26-1329, Cable: PACEAUS, Melbourne

ELECTRONIC ASSOCIATES, INC. West Long Branch, New Jersey 07764

ADVANCED SYSTEMS ANALYSIS AND COMPUTATION SERVICES/ANALOG COMPUTERS/DIGITAL COMPUTERS/HYBRID ANALOG-DIGITAL COMPUTATION EQUIPMENT/ANALOG AND DIGITAL PLOTTERS/SIMULATION SYSTEMS/SCIENTIFIC AND LABORATORY INSTRUMENTS/INDUSTRIAL PROCESS CONTROL SYSTEMS/PHOTOGRAMMETRIC EQUIPMENT/ANALOG INSTRUMENTA TION SYSTEMS/TEST AND CHECKOUT SYSTEMS/MILTRAY AND INDUSTRIAL PRSACH AND DEVELOPMENT SERVICES/FILED REVINEERING AND GUIPMENT MAITEMANCE SERVICES

# CONTENTS

|                                                                                            | Page         |

|--------------------------------------------------------------------------------------------|--------------|

| CHAPTER 1 - GENERAL DESCRIPTION AND OPERATION OF THE<br>580 ANALOG/HYBRID COMPUTING SYSTEM |              |

| 1.1 GENERAL DESCRIPTION                                                                    | 1-1          |

| 1.2 OPERATING CONSIDERATIONS                                                               | 1-1          |

| 1.3 KEYBOARD PANEL                                                                         | 1-14         |

| 1.4 ANALOG READOUT PANEL                                                                   | 1-21         |

| 1.5 THE AUXILIARY CONTROL PANEL                                                            | <b>1-</b> 21 |

| 1.6 THE LOGIC CONTROL AND INDICATOR PANEL                                                  | 1-25         |

| 1.7 READOUT DEVICES                                                                        | 1-28         |

| CHAPTER 2 - OPERATIONAL AMPLIFIERS                                                         |              |

| 2.1 INTRODUCTION                                                                           | 2-1          |

| 2.2 DUAL DC AMPLIFIER PATCHING                                                             | 2 <b>-</b> 1 |

| 2.3 QUAD DC AMPLIFIER PATCHING                                                             | 2-4          |

| CHAPTER 3 - ATTENUATORS AND FEEDBACK LIMITERS                                              |              |

| 3.1 ATTENUATORS                                                                            | 3-1          |

| 3.2 FEEDBACK LIMITER                                                                       | 3-1          |

| CHAPTER 4 - INTEGRATORS                                                                    |              |

| 4.1 INTRODUCTION                                                                           | 4 <b>-</b> 1 |

| 4.2 INTEGRATOR TRAYS                                                                       | 4-1          |

| CHAPTER 5 - QUARTER-SQUARE MULTIPLIERS                                                     |              |

| 5.1 INTRODUCTION                                                                           | 5-1          |

| 5.2 MODEL 0.7.0146 AND 0.7.0148 QUARTER-SQUARE<br>MULTIPLIERS                              | 5 <b>-</b> 1 |

| 5.3 MODEL 0.7.0150 QUARTER-SQUARE MULTIPLIER                                               | 5 <b>-</b> 8 |

i

# CONTENTS (Cont)

|                                              | Page          |

|----------------------------------------------|---------------|

| CHAPTER 6 - LOG X DIODE FUNCTION GENERATORS  |               |

| 6.1 INTRODUCTION                             | 6-1           |

| 6.2 OPERATING CONSIDERATIONS                 | 6-1           |

| 6.3 OPERATING INSTRUCTIONS                   | 6-1           |

| CHAPTER 7 - THE TRACK-STORE, D/A SWITCH TRAY |               |

| 7.1 INTRODUCTION                             | 7-1           |

| 7.2 THE TRACK-STORE CIRCUIT                  | 7-1           |

| 7.3 THE D/A SWITCH                           | 7-1           |

| CHAPTER 8 - THE MDFG                         |               |

| 8.1 INTRODUCTION                             | 8-1           |

| 8.2 LOCATION AND ADDRESSING                  | 8-1           |

| 8.3 APPLICATIONS                             | 8-1           |

| 8.4 SETUP PROCEDURE                          | 8-1           |

| CHAPTER 9 - COMPARATORS AND FUNCTION RELAYS  |               |

| 9.1 INTRODUCTION                             | 9 <b>-</b> 1  |

| 9.2 THE COMPARATOR                           | 9 <b>-</b> 1  |

| 9.3 FUNCTION RELAYS                          | 9 <b>-</b> 1  |

| CHAPTER 10 - CONTROL TRAY                    |               |

| 10.1 INTRODUCTION                            | 10 <b>-</b> 1 |

CONTENTS (Cont)

| CHAPTER 10 - | CONTROL TRAY (Continued)                         |               |

|--------------|--------------------------------------------------|---------------|

| 10.2         | DVM PATCH TERMINAL                               | 10-1          |

| 10.3         | VM PATCH TERMINAL                                | 10-1          |

| 10.4         | IC AND OP PATCH TERMINALS                        | 10-1          |

| 10.5         | SCOPE PATCH TERMINALS                            | 10-3          |

| 10.6         | PLOTTER PATCH TERMINALS                          | 10-3          |

| 10.7         | CHT ON PATCH TERMINALS                           | 10-3          |

| 10.8         | RDAC PATCH TERMINAL                              | 10-3          |

| 10.9         | A SEL PATCH TERMINAL                             | 10-3          |

| 10.10        | TIMER PATCH TERMINALS                            | 10-3          |

| 10.11        | OVD, ORH, AND OLS PATCH TERMINALS                | 10 <b>-</b> 4 |

| 10.12        | PP PATCH TERMINAL                                | 10 <b>-</b> 4 |

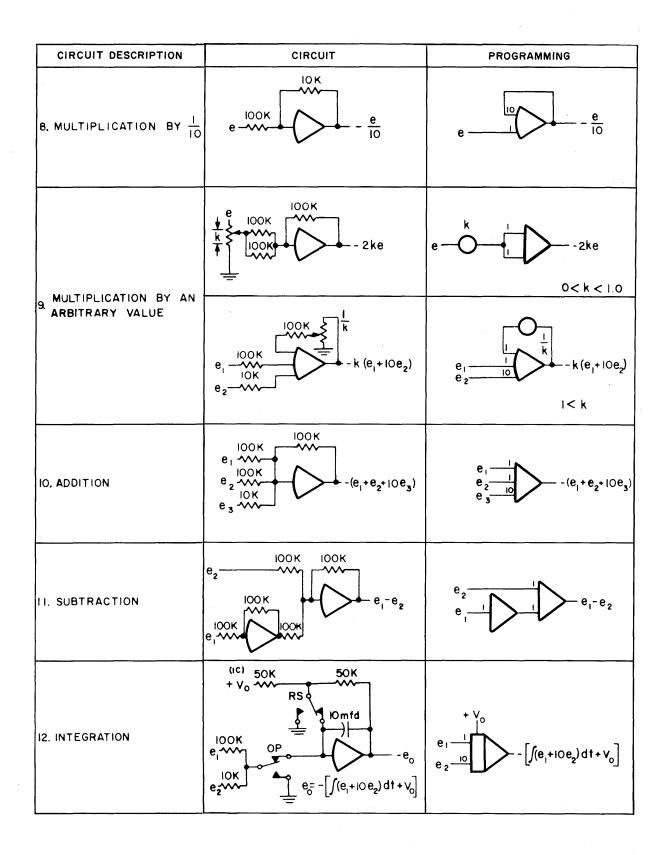

| APPENDIX 1 - | SIMPLE CIRCUITS USING AMPLIFIERS AND ATTENUATORS | A1-1          |

| APPENDIX 2 - | UNITY SCALING                                    | A2-1          |

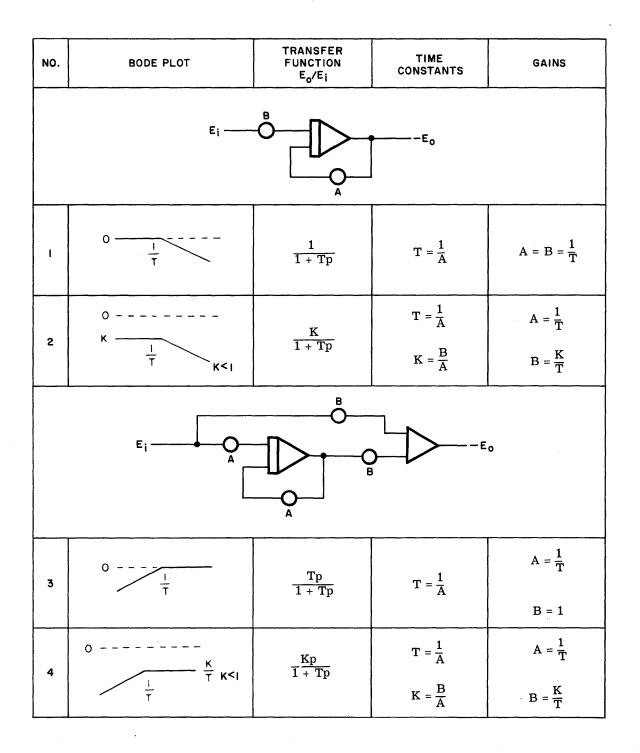

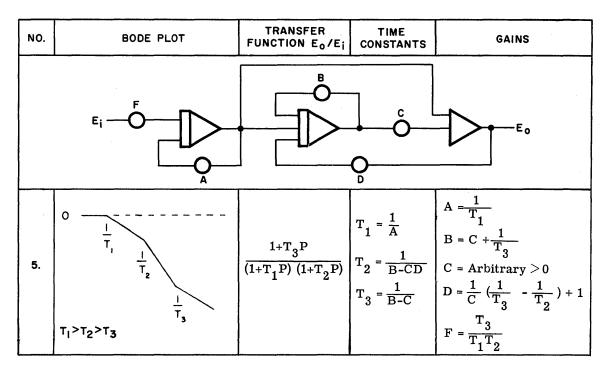

| APPENDIX 3 - | TRANSFER FUNCTION SIMULATION                     | A3-1          |

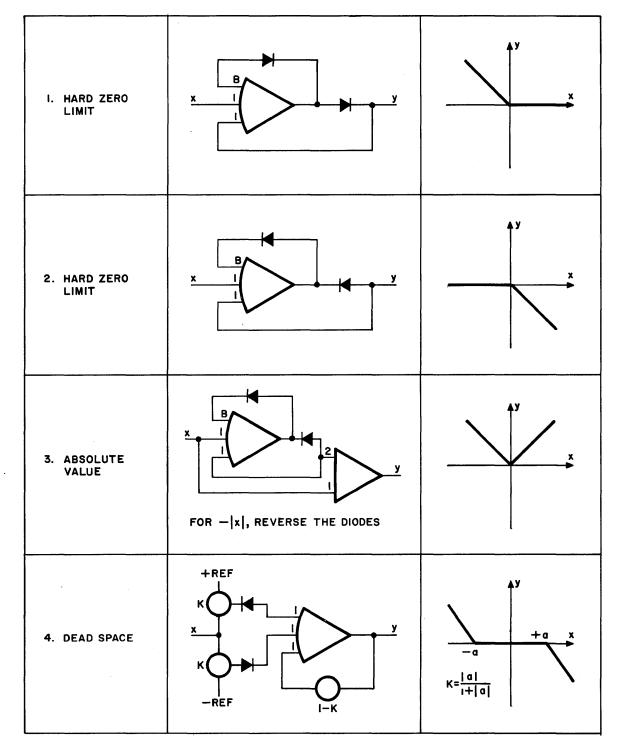

| APPENDIX 4 - | REPRESENTATION OF CONSTRAINTS AND NONLINEARITIES | A4-1          |

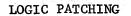

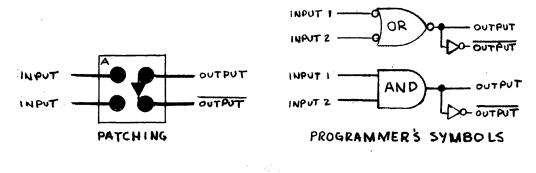

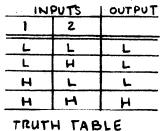

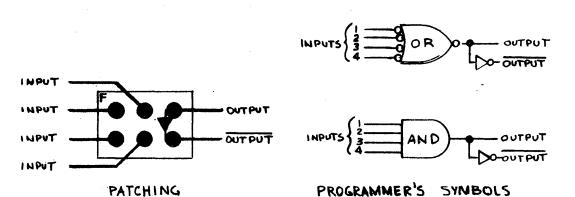

| APPENDIX 5 - | LOGIC PATCHING                                   | A5-1          |

| APPENDIX 6 - | BIBLIOGRAPHY                                     | A6-1          |

.

# ILLUSTRATIONS

| Figure<br><u>Number</u> | Title                                                                     | Page         |

|-------------------------|---------------------------------------------------------------------------|--------------|

| 1.1                     | 580 Analog/Hybrid Computing System                                        | viii         |

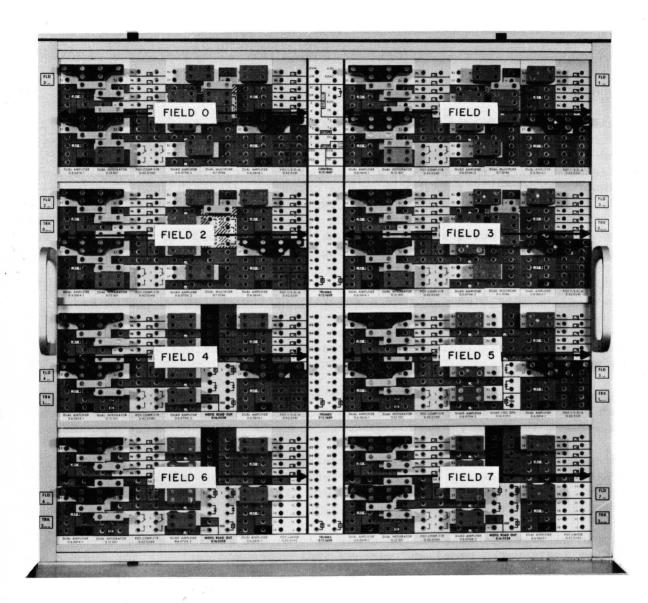

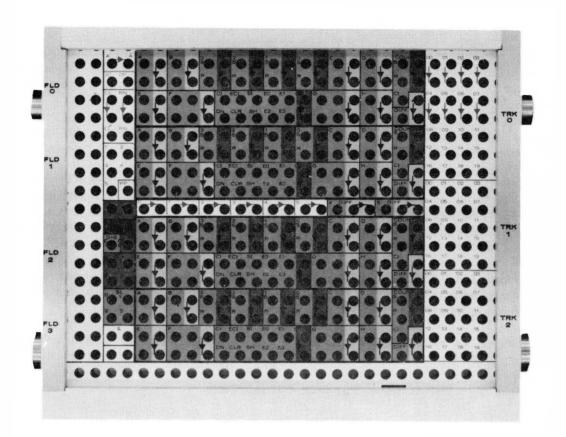

| 1.2                     | Typical Pre-Patch Panel Field Layout                                      | 1-2          |

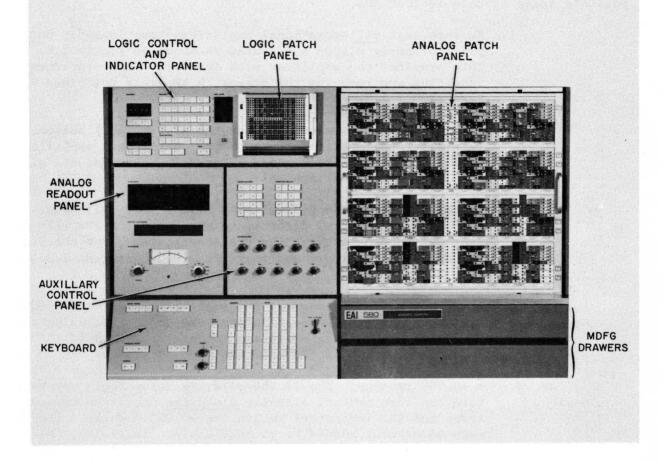

| 1.3                     | Physical Layout of the 580 Computer                                       | 1-3          |

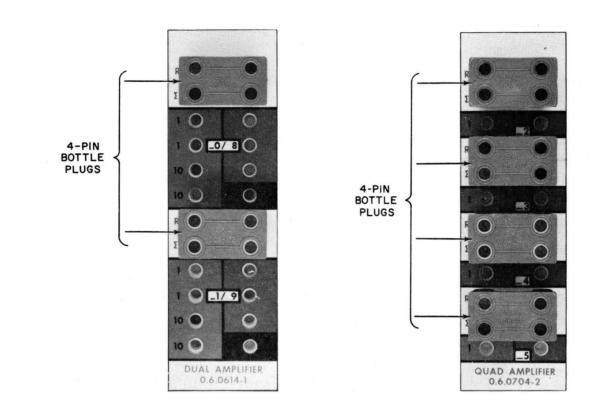

| 1.4                     | Amplifiers with Four-Pin Bottle Plugs Providing<br>Feedback               | 1 <b>-</b> 5 |

| 1.5                     | DVM Zero Adjustment Location                                              | 1-6          |

| 1.6                     | Pre-Patch Panel Insertion                                                 | 1-8          |

| 1.7                     | Amplifier Balance Control Locations                                       | 1-9          |

| 1.8                     | Computer Component - Field Assignment Areas                               | 1-10         |

| 1.9                     | Removal of Computing Component                                            | 1-12         |

| 1.10                    | Patching Block Replacement                                                | 1-13         |

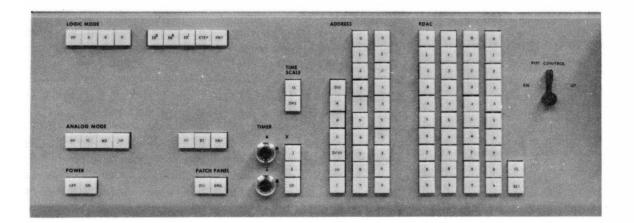

| 1.11                    | Keyboard                                                                  | 1-15         |

| 1.12                    | Analog Readout Panel                                                      | 1-22         |

| 1.13                    | Auxiliary Control Panel                                                   | 1-23         |

| 1.14                    | Logic Control and Indicator Panel                                         | 1-26         |

| 1.15                    | Digital Patch Panel                                                       | 1-27         |

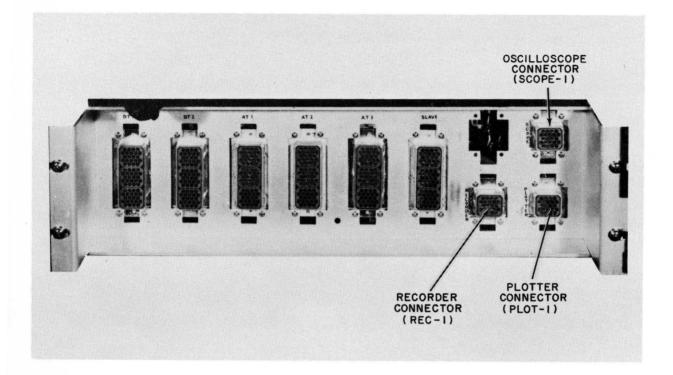

| 1.16                    | Readout Device Connectors                                                 | 1-30         |

| 2.1                     | 580 Operational Amplifiers (Patch Block Layout and Simplified Schematics) | 2-2          |

| 2.2                     | Dual Amplifier, Typical Patching Configurations                           | 2-3          |

| 2.3                     | Quad Amplifier Patching Configuration                                     | 2-4          |

| 3.1                     | Attenuators                                                               | 3-2          |

v

# ILLUSTRATIONS (Cont)

| Figure<br><u>Number</u> | <u>Title</u>                                                      | Page |

|-------------------------|-------------------------------------------------------------------|------|

| 3.2                     | Potentiometer Configurations                                      | 3-3  |

| 3.3                     | Feedback Limiter Patching Block                                   | 3-5  |

| 3.4                     | Typical Limiter Patching                                          | 3-5  |

| 3.5                     | Limit Curve                                                       | 3-6  |

| 4.1                     | Integrator Patching Blocks                                        | 4-2  |

| 4.2                     | Typical Integrator Patching                                       | 4-3  |

| 4.3                     | Integrator Used as a D/A Switch                                   | 4-5  |

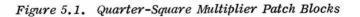

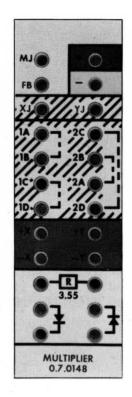

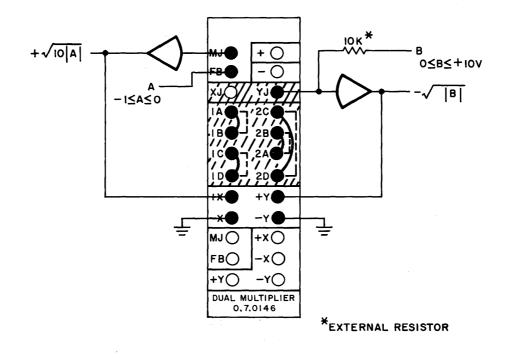

| 5.1                     | Quarter-Square Multiplier Patch Blocks                            | 5-2  |

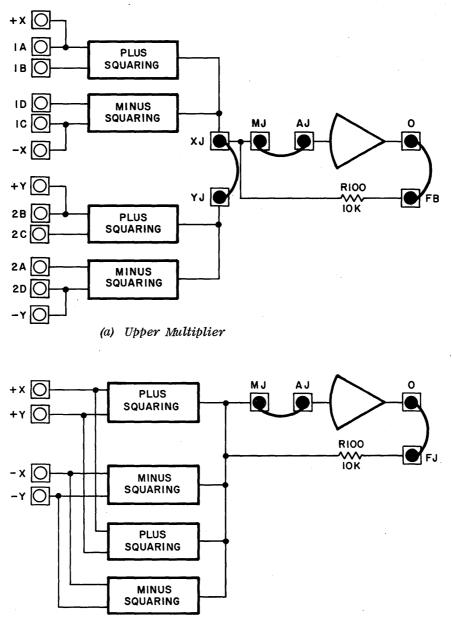

| 5.2                     | Quarter-Square Multiplier, Simplified Diagram .                   | 5-3  |

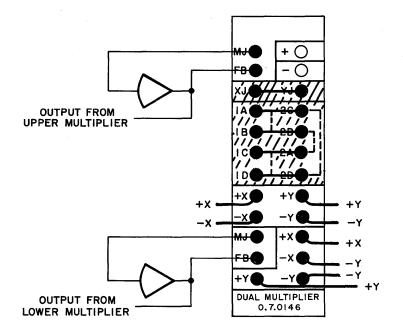

| 5.3                     | Multiplier Patching for Multiplication                            | 5-4  |

| 5.4                     | Multiplier Patching for Division                                  | 5-5  |

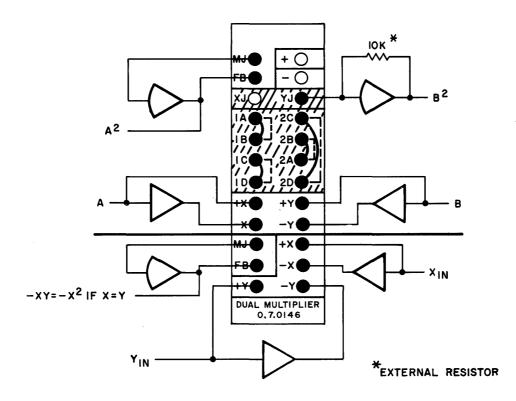

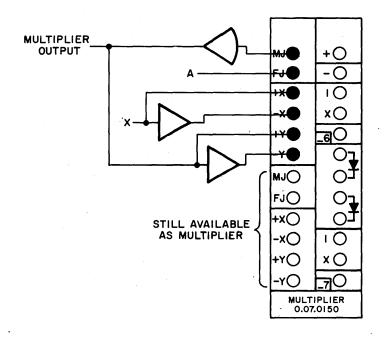

| 5.5                     | Multiplier Patching for Squaring (Two Squaring<br>Circuits Shown) | 5-6  |

| 5.6                     | Multiplier Patching for Square Root                               | 5-7  |

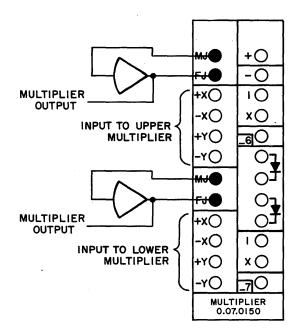

| 5.7                     | Multiplier Patching for Multiplication                            | 5-9  |

| 5.8                     | Multiplier Patching for Division                                  | 5-10 |

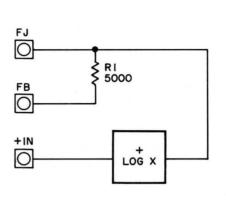

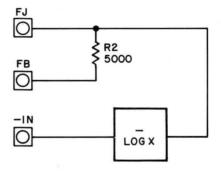

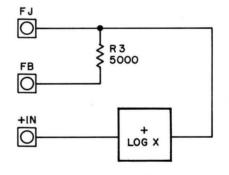

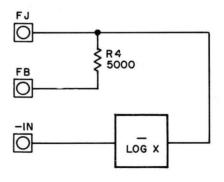

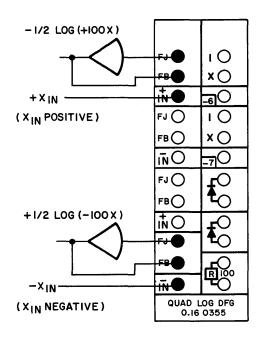

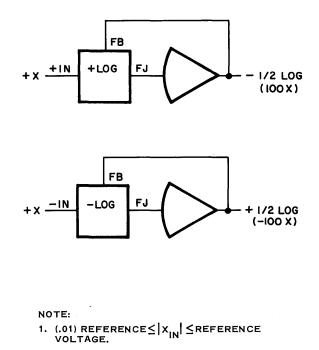

| 6.1                     | Log X DFG, Simplified Schematic and Patch Block                   | 6-2  |

| 6.2                     | Log X DFG Patching                                                | 6-3  |

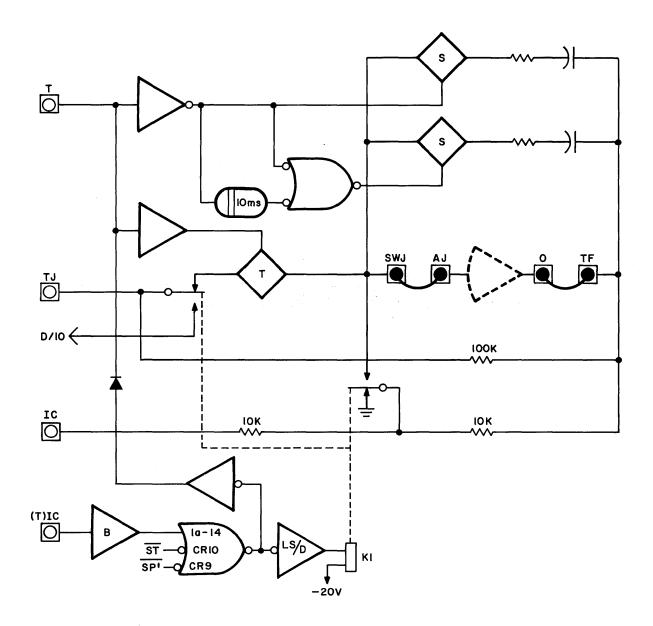

| 7.1                     | Track/Store, D/A Switch Patch Block                               | 7-2  |

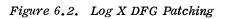

| 7.2                     | Track/Store Circuit, Simplified Diagram                           | 7-3  |

# ILLUSTRATIONS (Cont)

| Figure<br><u>Number</u> | Title                                          | Page          |

|-------------------------|------------------------------------------------|---------------|

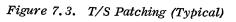

| 7.3                     | T/S Patching (Typical)                         | 7-4           |

| 7.4                     | D/A Switch Patching (Typical)                  | 7 <b>-</b> 5  |

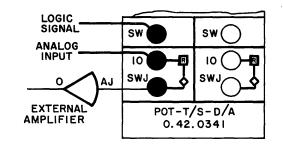

| 8.1                     | MDFG Patching Terminations                     | 8-2           |

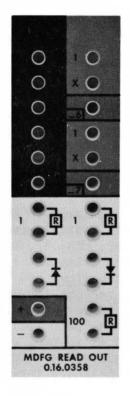

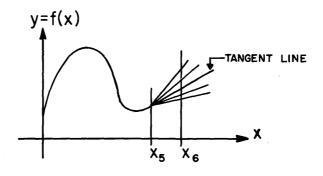

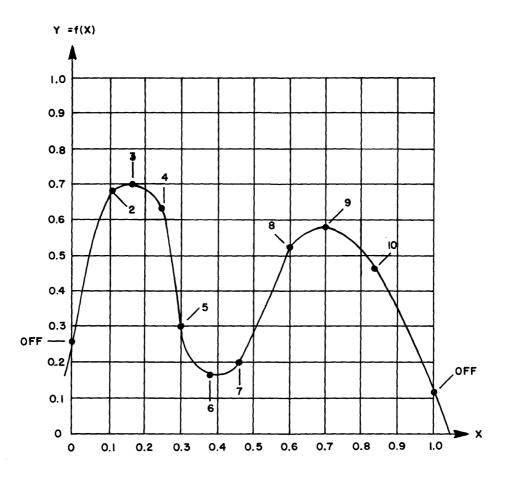

| 8.2                     | Typical Ten-Segment Function                   | 8 <b>-</b> 5  |

| 8.3                     | Effect of Changing Slope Pot 5 on DFG Output . | 8-7           |

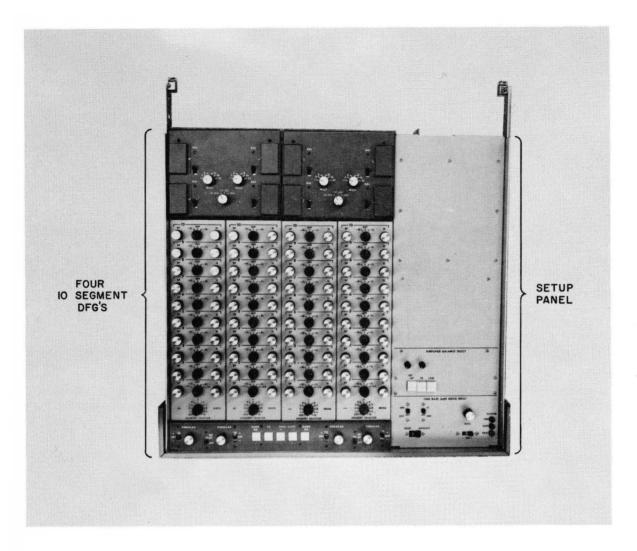

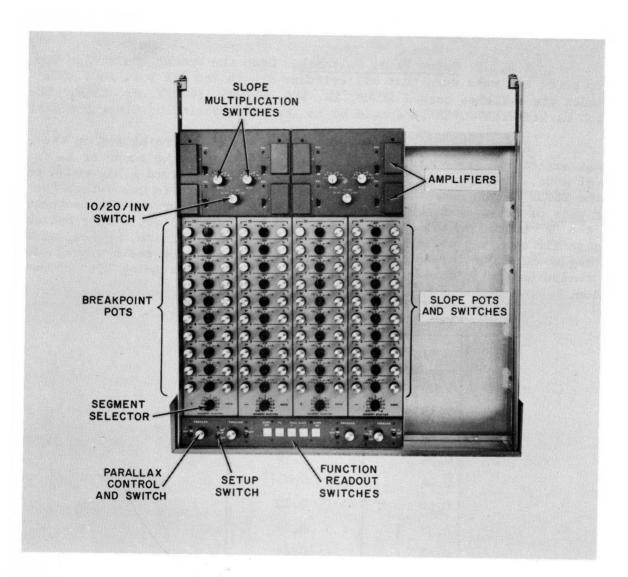

| 8.4                     | DFG Setup Panel (Lower DFG Drawer)             | 8-8           |

| 8.5                     | Upper DFG Drawer                               | 8-10          |

| 8.6                     | Typical Function Requiring Slope Amplification | 8 <b>-</b> 15 |

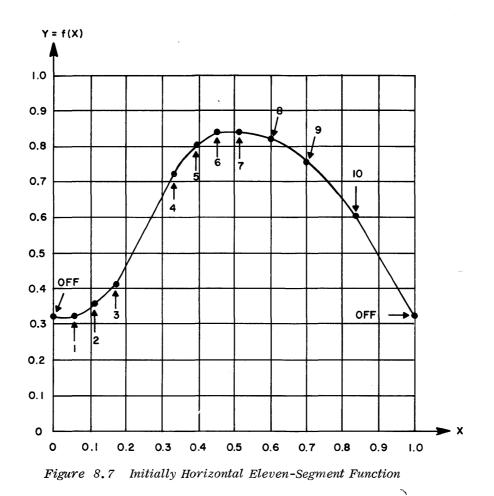

| 8.7                     | Initially Horizontal Eleven-Segment Function   | 8-17          |

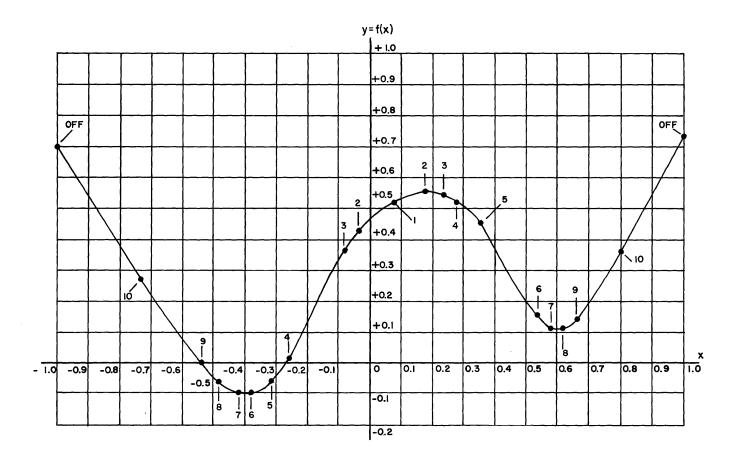

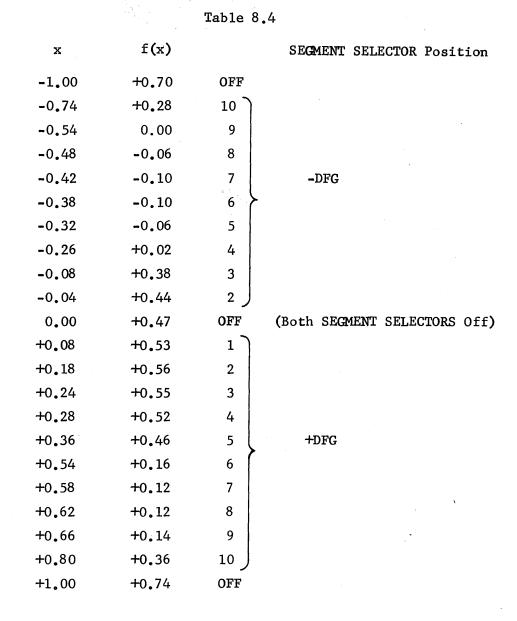

| 8.8                     | A Typical Twenty-Segment Function              | 8-21          |

| 9.1                     | Comparator and Function Relay Patching Area    | 9-2           |

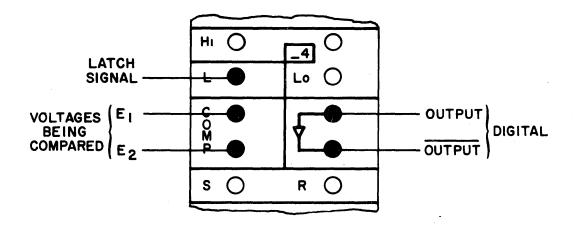

| 9.2                     | Typical Comparator Patching                    | 9-3           |

| 10.1                    | Control Tray Patch Panel                       | 10-2          |

Figure 1.1. 580 Analog/Hybrid Computing System

## CHAPTER 1

### GENERAL DESCRIPTION AND OPERATION OF THE

# 580 ANALOG/HYBRID COMPUTING SYSTEM

#### 1.1 GENERAL DESCRIPTION

The EAI 580 Analog/Hybrid Computing System (Figure 1.1) is composed of solid state computing components. The 580 (categorized as a desk-top computer) is compact in size and operates with stability and precision in a normal office or classroom environment as well as a computer laboratory. Each component has input and output terminations on the computer pre-patch panel for interconnection by bottle plugs and patch cords. The pre-patch panel is arranged in a series of 8 similar patching fields (Figure 1.2), with each field separated horizontally by either a control or trunk trays. The modular design tends to eliminate patching clutter caused by long across-the-panel patching.

The main control panel is located to the lower left of the analog patch panel (Figure 1.3). This area contains a majority of the operating controls.

The analog readout panel, located to the far left of the analog patch panel, contains the overload indicators, DVM readout (an expansion) and a multi-range voltmeter.

The Auxiliary Control Panel, immediately to the left of the analog patch panel, includes 10 handset potentiometers, and override controls for both the comparators and the function relays.

The area below the analog patch panel contains two manual diode function generator (MDFG) drawers. The lower drawer contains the set-up amplifier and controls, and up to four, 10-segment MDFGs. The upper drawer is used to house additional segments as required.

The logic package, located at the upper left of the analog patch panel, contains the logic patch panel and various indicators and controls for the logic components.

## 1.2 OPERATING CONSIDERATIONS

1.2.1 General

The 580 is completely tested and calibrated at the time of manufacture and is shipped with all components in place. After performing the installation check-out procedure outlined in the 580 Maintenance Manual, the computer is ready for operation.

It should be noted that the low voltage levels used in the 580 eliminate any shock hazard when patching with the pre-patch panel in the computer. Currentlimiting circuits protect the reference supplies from damage when they are in-

Figure 1.2. Typical Pre-Patch Panel Field Layout

Figure 1.3. Physical Layout of the 580 Computer

advertantly patched to ground or to each other. (Dangling patch cords rarely short to ground because of the plastic patching blocks and because the metal strips between the patching block are covered with a scratch-resistant, nonconductive paint.)

#### 1.2.2 Preliminary Operating Considerations

The following steps are recommended prior to operating the 580 to prevent possible false trouble indications.

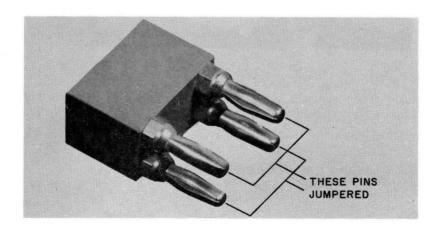

- Be sure that <u>all</u> operational amplifiers have four-pin bottle plugs properly placed and seated as shown in Figure 1.4. This provides the amplifier with feedback. The procedure for inserting and removing the pre-patch panel is described in Paragraph 1.2.3.

- Turn the computer on and depress the SP (set pot) button. Initially, the overload lamps of the operational amplifiers will light due to transients; after a few seconds, all of the lamps should extinguish.

- 3. Check the various supply voltages of the 580. All power supply outputs are connected directly to the voltmeter FUNCTION switch (through appropriate scaling resistors); thus, the check may be accomplished simply and rapidly. (See Paragraph 1.3.5 of this section.)

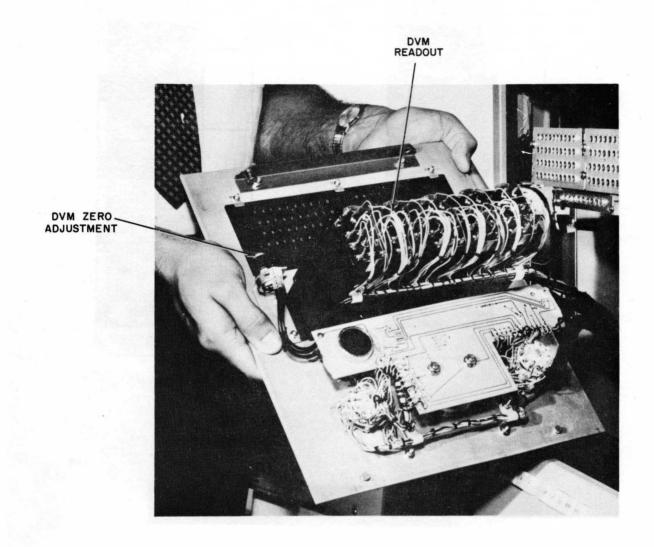

- 4. Allow a few minutes warm-up (at least 1/2 hour for the DVM) time to assure that the computing components (including the DVM) are up to normal operating temperature. Ground the input termination in "PP" address mode designated DVM on the control tray and adjust the DVM zero control (Figure 1.5) for a +0.000 reading. Should the polarity relay begin to chatter, turn the zero control slightly <u>clockwise</u> until the chatter stops and the indicators retain the +0.000 display. The DVM zero adjustment should be checked daily. Initially, this adjustment may be required more frequently due to aging of the components.

- 5. Closed relay contacts provide a  $100\Omega$  feedback resistor for the operational amplifiers when in the <u>set pot</u> mode of the computer (SP button on the control panel depressed). (This feature permits pre-patch panel removal without overloading the amplifiers.) However, when the computer is switched from <u>set pot</u> to another mode, the relay contacts open and the amplifier feedback loop is determined by the patching on the prepatch panel. The amplifier overload indicators may be triggered momentarily during the switching time. This is of no consequence since the computer should always be placed in the initial condition mode before going to the <u>operate</u> mode.

Figure 1.4. Amplifiers with Four-Pin Bottle Plugs Providing Feedback

Figure 1.5. DVM Zero Adjustment Location

## 1.2.3 Pre-Patch Panel Insertion and Removal

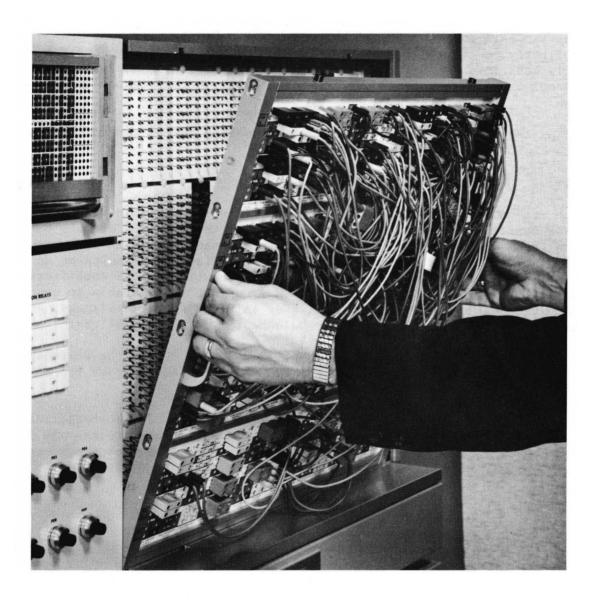

To insert the pre-patch panel, align the lugs on the bottom of the pre-patch panel frame with the slots in the bottom rail of the patch bay (Figure 1.6). Push the pre-patch panel forward until the lugs on the top of the frame mate with the slots on the top rail of the patch bay. Gently slide the pre-patch panel slightly to the right. Depress the ENG switch. (The computer automatically goes into the <u>set pot</u> mode when the ENG switch is depressed.) The patch panel drive system faces the pre-patch panel to the right into the locked position.

Depressing the DIS pushbutton disengages the locking system and forces the prepatch panel to the left for removal.

#### 1.2.4 Amplifier Balance

For accurate computation, the operational amplifier must remain balanced. The amplifier must produce a zero output voltage when the combined effects of the input voltages or the absence of input voltages demand it. With this requirement in mind, the amplifiers contain chopper stabilization circuits to minimize the effect of component drift. Under normal circumstances, the amplifiers do not require balancing for several weeks. However, it is desirable to <u>check</u> this condition periodically; if an amplifier is found to be unbalanced, an adjustment is required. The amplifier balance is checked as follows:

- 1. Allow a warm-up of 15 to 30 minutes. Place the voltmeter FUNCTION switch in the ABAL position and depress the SP pushbutton of the MODE switch.

- 2. Use the signal selector system to connect the stabilizer output of each amplifier to the voltmeter. Select A00 and proceed in order. In each case, the voltmeter should register a deflection that is less than 1/2 division on the meter scale.

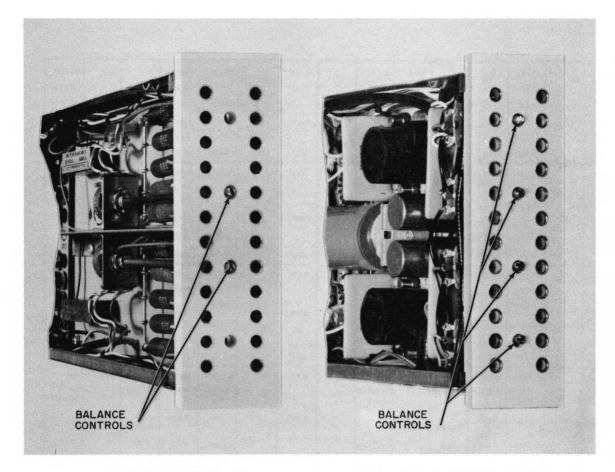

- 3. If an amplifier causes a larger deflection, the amplifier should be balanced. The balance controls for amplifiers are located behind the pre-patch panel on the front block of the amplifiers (Figure 1.7). Adjust these controls for a zero reading on the voltmeter.

#### 1.2.5 Changing Computational Components

In the solution of some problems, it may be necessary to add a computing component to the existing complement. Since some of the module positions are designed to handle more than one type of computing component, a component not required in the problem investigation may be removed and another unit inserted in its place. Figure 1.8 illustrates the various positions of the computing component in the 580 field area. The diagram shows which type of computing component is compatible with each position. The procedure for replacing a computing component and changing the pre-patch panel patching block is described in the following paragraphs.

Figure 1.6. Pre-Patch Panel Insertion

(a) 0.6.0614 Dual DC Amplifier

(b) 0.6.0704-2 Quad DC Amplifier

Figure 1.7. Amplifier Balance Control Locations

|      | · · · · · · · · · · · · · · · · · · · |       |       | -      |       |         |        |      |     |          |      |         |       |         |

|------|---------------------------------------|-------|-------|--------|-------|---------|--------|------|-----|----------|------|---------|-------|---------|

| A00  |                                       | ATTEN | A O 2 |        | A08   | AT TEN  | c      | A 10 |     | ATTEN    | A12  |         | A18   | ATTEN   |

|      |                                       | P00-  | A03   |        |       | P05-    | O<br>N |      |     | P10-     | A13  |         |       | P15-    |

|      |                                       | P04   |       |        |       | P09     | T<br>R |      |     | P14      |      | 1 · · · | · ·   | P19     |

| AMPL | INT                                   |       | AMPL  | MULT   | AMPL  |         | Ö      | AMPL | INT |          | AMPL | MULT    | AMPL  |         |

|      |                                       | COMP. | A04   |        |       | T/S     | TRAY   |      |     | COMP.    | A14  |         |       | T/S     |

| AOI  |                                       | F/R   | A05   |        | A09   | D/A     | IRAI   | AII  |     | F/R      | A15  |         | A19   | D/A     |

| A20  |                                       | ATTEN | A22   |        | A28   | ATTEN   | т      | A30  |     | ATTEN    | A32  |         | A38   | ATTEN   |

|      |                                       | P20-  | A23   |        |       | P25-    | R      |      |     | P30-     | A33  | ļ       |       | P35-    |

|      |                                       | P24   |       |        |       | P29     | UN     |      |     | P34      |      | ļ       |       | P39     |

| AMPL | INT                                   |       | AMPL  | MULT   | AMPL  |         | к      | AMPL | INT |          | AMPL | MULT    | AMPL  |         |

|      |                                       | СОМР  | A24   |        |       | T/S     | S      |      |     | COMP.    | A34  |         |       | T/S     |

| A21  |                                       | F/R   | A25   |        | A2 9  | D/A     |        | A31  |     | F/R      | A35  |         | A39   | D/A     |

| A40  |                                       | ATTEN | A42   | QUAD   | A 4 8 | ATTEN   |        | A50  |     | ATTEN    | A 52 | QUAD    | A 5 8 | ATTEN   |

|      |                                       | P40-  | A43   | LOG    |       | P45-    | TR     |      |     | P50-     | A 53 | LOG     |       | P55     |

|      |                                       | P44   |       | DFG    |       | P49     | υ      |      |     | P54      |      | DFG     |       | P59     |

| AMPL | INT                                   |       | AMPL  | MDFG   | AMPL  |         | N<br>K | AMPL | INT |          | AMPL | MDFG    | AMPL  |         |

|      |                                       | COMP  | A44   | A46    |       | T∕S     | S      |      |     | COMP.    | A54  | A56     |       | T/S     |

| A4i  |                                       | F/R   | A45   | A47    | A49   | D/A     |        | A51  |     | F/R      | A5 5 | A57     | A 5 9 | D/A     |

| A 60 |                                       | ATTEN | A 6 2 | SINE/  | A68   | ATTEN   | Ţ      | A70  |     | ATTEN    | A72  | SINE/   | A7 8  | ATTEN   |

|      |                                       | P60-  | A 6 3 | COSINE |       | P65-    | T<br>R |      |     | P70-     | A73  | COSINE  |       | P75     |

|      |                                       | P64   |       |        |       | P69     | υ      |      |     | P74      |      |         |       | P79     |

| AMPL | INT                                   |       |       | MDFG   | AMPL  |         | N<br>K | AMPL | INT |          | AMPL | MDFG    | AMPL  |         |

|      |                                       | COMP  | A64   | A66    |       | LIMITER | S      |      |     | COMP.    | A74  | A76     |       | LIMITER |

| A61  |                                       | F/R   | A65   | A67    | A69   |         |        | A71  |     | F/R      | A75  | A77     | A79   |         |

|      |                                       |       |       |        |       |         |        |      | L   | <u> </u> | l    | L       |       |         |

Figure 1.8. Computer Component - Field Assignment Areas

# 1.2.5.1 Computing Module Replacement

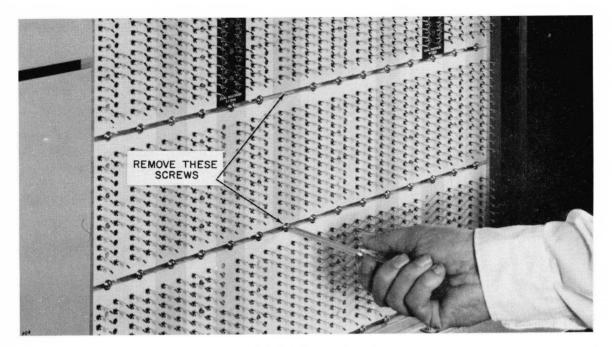

- 1. Remove the pre-patch panel to expose the computing component modules. Remove the two Phillips head retaining screws from the top and bottom of the module to be removed (Figure 1.9a).

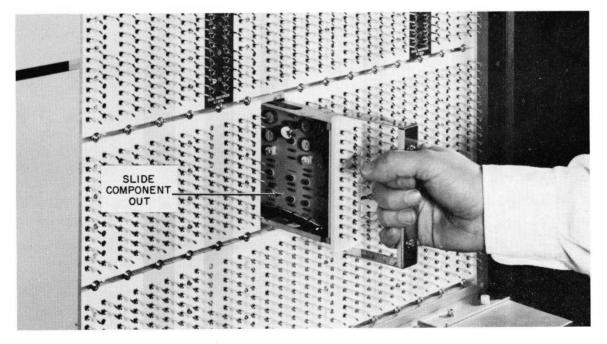

- 2. Insert the special module extraction tool on the ends of the tray (Figure 1.9b). Pull the tray forward, removing it from the computer.

- 3. Place the new component in place; be sure the guide pins are properly seated in the guide-pin holes before mating the connectors to the rear of the module.

- 4. Check that the module is properly installed (connector firmly mated, etc.,) and replace the two retaining screws.

### 1.2.5.2 Patching Block Replacement

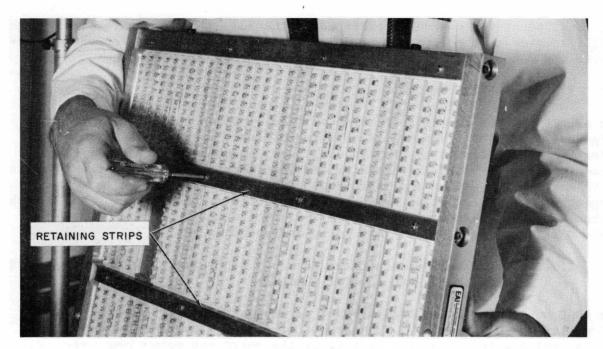

- 1. The patching blocks of the computing components are held securely in place by the retaining strips on the front of the pre-patch panel (Figure 1.10a).

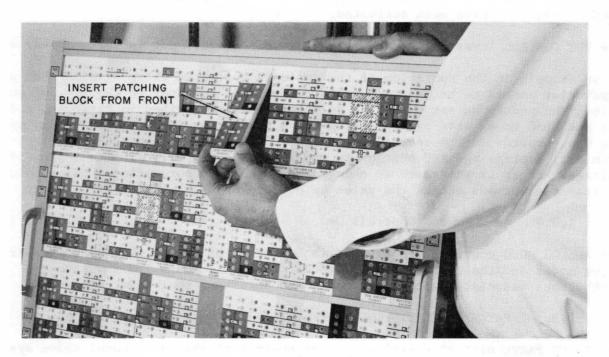

- 2. The retaining strip above or below the patching block may be removed to change blocks. The retaining strip is released by removing the four screws directly behind the strip on the rear of the pre-patch panel (Figure 1.10b). If blocks on two adjacent horizontal rows are to be replaced, remove only the retaining strip between the two rows. The patching blocks can then be removed from the rows above and below the strip.

- 3. Once the retaining strip is free, remove the original patching block and replace it with the new block (Figure 1.10b). Secure the retaining strip with the four screws. The pre-patch panel is now ready for problem patching.

#### NOTE

Failure to change the patching block when computing components are changed may prevent proper operation because of the arrangement of the jumpers on the rear of the patching block.

(a) Retaining Screw Location

(b) Using Extraction Tool

Figure 1.9. Removal of Computing Component

(a) Removal

(b) Replacement

Figure 1.10. Patching Block Replacement

#### 1.3 KEYBOARD PANEL

#### 1.3.1 General

The focal point for control facilities of the 580 is the keyboard panel (Figure 1.11), located to the left of the MDFG drawers. The following paragraphs describe the function and use of the various controls and components.

#### 1.3.2 ADDRESS Switch

The ADDRESS switch consists of three vertical rows of pushbutton switches (Figure 1.11). The first row, consisting of seven pushbuttons, is used to select the type of unit to be read out, i.e., A equals Amplifier, P equals Potentiometer. Table 1.1 identifies and describes the function of each switch in this row. The second and third rows contain the tens and units switches respectively. Note that if the position selected is less than 10, the 0 pushbutton in the 10 column must be depressed. For example, if amplifier 4 in field 0 is to be read out, it has to be addressed as AO4.

# 1.3.3 Servo Set Potentiometer Controls (Including RDAC Switches, CL/SET Switches, and the POT CONTROL)

The RDAC switches consist of 4 columns of 10 pushbutton switches with each column labeled 0 through 9. The purpose of these switches is to provide a precise voltage for automatic setting of the servo set potentiometers.

The CL/SET pushbuttons are used to <u>clear</u> or to <u>set</u> an addressed pot once the RDAC pushbuttons have been activated.

The POT CONTROL lever allows adjustment of an addressed pot in any computer mode.

As an example of the operation of the controls described above, assume that a particular pot is to be set to 8 volts. Place the computer in the <u>set pot</u> mode. Select the pot to be set using the selector system described in Paragraph 1.3.1. Set the RDAC to 8 volts by depressing the 8 pushbutton in the first column and the 0 pushbutton in the second, third and fourth columns. Once the RDAC has been set, depress the SET button and the addressed pot will slew to the proper voltage. If it is necessary to change the value of a pot during problem solution, address the pot and change the value up or down using the POT CONTROL lever.

1.3.4 ANALOG MODE Controls

The ANALOG MODE controls are divided in two types of modes; the computer operating modes and the computer set-up modes. Tables 1.2 and 1.3 indicate the pushbuttons associated with these modes and describes their functions.

#### 1.3.5 PATCH PANEL DIS/ENG Switches

The PATCH PANEL DIS/ENG switches provide control of the patch panel drive system when inserting or removing the pre-patch panel (see Paragraph 1.2.3).

Figure 1.11. Keyboard

Table 1.1

| Pushbutton | Function                                                                                                                                                                                                                                     |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DIG I/O    | Depressing this pushbutton transfers control of the readout selection system to a digital computer when the 580 is installed in a hybrid configuration.                                                                                      |  |  |  |

| PP         | This pushbutton is used to connect the DVM patch terminal on the 0.12.1607 Control Tray to the DVM input.                                                                                                                                    |  |  |  |

| F          | Depressing this pushbutton and the appropriate push-<br>button on the Amplifier Balance Panel, located in the<br>lower MDFG drawer, allows the amplifiers, located in the<br>0.12.1345 MDFG Amplifier Network, to be balanced on the<br>DVM. |  |  |  |

| D          | This pushbutton is used for a derivative readout from the summing junctions of the integrators and track/store units.                                                                                                                        |  |  |  |

| D/10       | Same as the D (derivative) pushbutton except that in voltage readout is divided by a factor of 10.                                                                                                                                           |  |  |  |

| Р          | The P (potentiometer) pushbutton connects the arm of the potentiometer addressed to the DVM.                                                                                                                                                 |  |  |  |

| A          | The A (amplifier) pushbutton when depressed switches the<br>output of the selected amplifier or MDFG setup amplifier<br>to the DVM input.                                                                                                    |  |  |  |

Table 1.2. Definitions of Computer Operating Modes

| Mode                                 | Function                                                                                                  |  |  |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|

| OPERATE<br>( <u>OP</u> )             | Integrators operate; computer produces a dynamic solution to a patched problem.                           |  |  |

| HOLD<br>( <u>HD</u> )                | Integrators do not operate; all values present at the time the <u>hold</u> mode is selected are returned. |  |  |

| INITIAL CON-<br>DITION ( <u>IC</u> ) | Integrators are set to initial values.                                                                    |  |  |

| REMOTE<br>( <u>RMT</u> )             | Parallels mode control of computer to external devices.                                                   |  |  |

۰,

### Table 1.3. Definition of Computer Set-Up Modes

| Mode .                         | Function                                                                                                                                                                                                                                                                                                                           |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATIC TEST<br>( <u>ST</u> )   | Similar to <u>initial condition</u> . Static test voltages can<br>be applied to integrators not normally provided with ini-<br>tial condition voltages, to permit checking computed<br>levels at other parts of the program via Function Relays.<br>All INT and T/S are forced to IC mode.                                         |

| SET POT<br>( <u>SP</u> )       | All amplifiers provided with low impedance feedback to<br>provide correct attenuator loading. Reference voltage<br>applied to high end of any pot selected for readout, so<br>that the pot coefficient may be read out. The servo am-<br>plifier is connected to the motor of an addressed pot, per-<br>mitting the pot to be set. |

| PROGRAM PANEL<br>( <u>PP</u> ) | When this button is depressed the <u>IC</u> , <u>HOLD</u> , and <u>OPERATE</u><br>modes may be controlled by logic signals applied to the<br>0.12.1607 Control Tray patch block. This mode also causes<br>the internal timer to automatically start operation.                                                                     |

### 1.3.6 TIME SCALE Switches and Controls

The TIME SCALE and X switches along with the TIMER controls are used to control the analog timer (repetitive operation) circuit. The timer circuit generates the precise time intervals necessary to control the analog modes of the computer for iterative or repetitive operation. The TIME SCALE pushbuttons provide a 500 to 1 speed-up of the entire computer.

The repetitive operation (Rep-Op) circuit allows both high-speed, and low-speed repetitive operation. Any OPERATE or IC period from 100  $\mu$ sec to 100 sec may be selected by the pushbuttons and Vernier controls provided to "bridge the gap" between pushbutton settings. Separate Vernier controls are provided for adjustment of the A (IC) and  $\overline{A}$  (OP) periods.

The timer has the following inputs, outputs, and controls:

1.3.6.1 <u>Input</u>. The "RUN" terminal on the analog patch panel terminates in the control tray in the center of the first row. This input starts and stops the timer, and allows rep-op runs to be terminated by some condition other than elapsed time. For example, if it is desired to operate the analog simulation until some analog variable crosses zero, the RUN input may be patched from a comparator.

When RUN = 0, the timer does not run; its output remains in the A (IC) state. When RUN becomes high (logic ONE) the timer starts to run, starting with a full A (IC) period, followed by an  $\overline{A}$  (OP) period. It continues to cycle between A and  $\overline{A}$  as long as RUN = 1. In ordinary repetitive operation, where the OPERATE period is fixed in advance by the operator, there is no need to patch the RUN input. It is internally connected to the "PP" signal, which is controlled by the ANALOG MODE button labeled "PP" (Paragraph 1.3.3). Thus, ordinary repetitive operation requires no special patching; the operator simply selects the desired A (IC) and  $\overline{A}$  (OP) periods, and depresses the "PP" button. However, if the operator desired to control the timer from an arbitrary logic signal, local patching at the RUN terminal overrides the internal connection.

1.3.6.2 <u>Outputs</u>. The timer has two logic outputs (A and  $\overline{A}$ ) and an analog output TB (Time Base). The terminals are connected to the 0.12.1607 Control Tray. The A and  $\overline{A}$  outputs normally control the IC and OP buses respectively. The IC and OP patch terminals, connected internally to the A and  $\overline{A}$  terminals, act as inputs to the IC and OP buses. Logic signals at these terminals override the internally generated signals and provide external control of the IC and OP buses.

The <u>TB</u> output is an analog ramp generated by an internal integrator and provides a voltage proportional to time. The ramp output may be used to drive the horizontal axis of readout devices (Plotting Board, Oscilloscope, etc.,) or may be used as an analog signal for problems requiring a signal proportional to time. The ramp integrates from zero to plus reference voltage during a given operate cycle. Thus, the scaled output is  $(t/t_{max})$ , where  $t_{max}$  is the length of the operate cycle. (This is a unit scaled notation; the run terminates when  $t = t_{max}$ , which means  $(t/t_{max}) = 1.0$  unit, or 10 volts.)

1.3.6.3 <u>Controls</u>. The period of the timer is determined by three sets of controls: a pair of dials (one for A, one for  $\overline{A}$ ), a group of three X (multiplier) pushbuttons (.1, 1, 10), and two TIME SCALE pushbuttons (2 msec, 1 sec). Note that the dials and the multiplier pushbuttons affect the rep-op timer <u>only</u>, while the TIME SCALE pushbuttons control the timer integrator as well as the capacitors in the computer integrators.

The A and  $\overline{A}$  controls utilize ten-turn Vernier dials with a built-in turn counter. A window at the top of each dial displays an integer representing the number of complete revolutions of the dial. The graduations around the dial allows a fractional part of a revolution to be set to two figures. Thus, the dial can be set for 5.20 turns, 8.75 turns, etc. The dial has been offset by 0.50 turns. Consequently the minimum position is 0.50 turns while the maximum position is 10.5 turns.

The multiplier pushbuttons are a series of momentary contact switches connected in such a manner that when one is depressed it electrically clears any previously selected pushbutton.

The length of the A and  $\overline{A}$  periods is the product of three factors: the number of turns on the Vernier dial, the multiplier setting, and the TIME SCALE selected. A simple equation for determining the lengths of either the A or  $\overline{A}$  periods is TIME SCALE X Multiplier X Vernier = Length of Period. The following table gives the minimum and maximum time periods for each range. A 500 to 1 speedup of the entire computer is also provided by the TIME SCALE pushbuttons. The TIME SCALE pushbuttons control the time scale relays located in each integrator tray through the time scale bus system. The 500 to 1 speed-up controls both integrators in a dual integrator tray. In the 2 ms range, the time scale bus is at a logic ZERO level energizing the time scale relay. Energizing this relay switches capacitance from 10  $\mu$ f to 0.02  $\mu$ f, speeding up the problem by a factor of 500. (The problem is automatically rescaled when speeded up by a factor of 500.) The 1 SEC pushbutton switches the time scale bus to a high (+5v) logic level, the relays are de-energized and the computer resumes normal problem speed.

Note that the TIME SCALE pushbuttons only affect the <u>normally patched</u> integrators. By local patching, it is possible to control the time scale input of the integrators, located in a particular tray, independent of the master time scale selection system. In addition, it is possible, by local patching, to speed up a factor of 10 to 1 individual integrators.

| TIME SCALE | X<br>(Multiplier) | Vernier     | Time                 |

|------------|-------------------|-------------|----------------------|

| 2 MS       | X0.1              | 0.5 to 10.5 | 100 $\mu$ S to 2 MS  |

| 2 MS       | X1.0              | 0.5 to 10.5 | 1 MS to 20 MS        |

| 2 MS       | x10.0             | 0.5 to 10.5 | 10 MS to 200 MS      |

| 1 SEC      | X0.1              | 0.5 to 10.5 | 50 MS to 1.0 SEC     |

| 1 SEC      | X1.0              | 0.5 to 10.5 | 0.5 Sec to 10.0 SEC  |

| 1 SEC      | X10.0             | 0.5 to 10.5 | 5.0 Sec to 100.0 SEC |

Table 1.4. Time Periods

### 1.3.7 POWER Pushbuttons

The POWER pushbuttons control the power for the entire computer. To activate the computer, depress the ON pushbutton. To turn the computer off, depress the OFF pushbutton. The ON pushbutton contains an indicator lamp which lights to indicate that the computer is "ON".

### 1.3.8 LOGIC MODE Pushbuttons

The LOGIC MODE pushbuttons consist of four momentary pushbutton switches used to control the 580 Logic Package. These switches are connected in such a manner that when one is depressed it electrically clears any previously selected modes. An indicator lamp in each pushbutton indicates, when lit, which mode is selected. The LOGIC MODE pushbuttons are included only when a logic package is installed in the computer. Table 1.5 lists the description and function of each LOGIC MODE pushbutton.

# Table 1.5. LOGIC MODES

| LOGIC MODE       | Function                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| PP (Patch Panel) | Transfers control of logic mode to the logic patch panel.                                                                                              |

| C (Clear)        | Clears all flip-flops in the logic package including<br>those in the counters and registers. (Clear line re-<br>mains high preventing initialization.) |

| S (Stop)         | Stops the logic clock preventing flip-flops and reg-<br>isters from reacting to patched inputs. (Clocked<br>devices may still set and reset manually.) |

| R (Run)          | Normally used for computation. Clocked devices (flip-<br>flops, registers) respond to patch panel inputs.                                              |

# 1.3.9 Logic Clock Rate Pushbuttons

The four clock rate pushbuttons  $(10^6, 10^5, 10, \text{ and STEP})$  select the clock rate for the synchronized logic elements in the logic package. The pushbuttons are momentary contact switches which, when depressed, select a new clock rate and electrically clear the previously selected clock rate. The  $10^6, 10^5$ , and 10pushbuttons include lamps which indicate which clock rate has been selected. Table 1.6 lists the function of each clock rate pushbutton.

| Table 1.6. Clock Rate Pushbutton | Functions |  |

|----------------------------------|-----------|--|

|----------------------------------|-----------|--|

| Clock Rate      | Function                                                                                                  |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| 10 <sup>6</sup> | Considered normal clock rate. One clock pulse every micro-<br>second.                                     |

| 10 <sup>5</sup> | One clock pulse every 10 microseconds.                                                                    |

| 10              | Ten clock pulses every second.                                                                            |

| STEP            | Inhibits all clock pulses when initially depressed. Provides one clock pulse when subsequently depressed. |

# 1.3.10 Logic RMT (Remote) Pushbutton

The RMT (remote) pushbutton is a latching type pushbutton which parallels both logic mode control and clock rate control with a remote source. The remote source may be a digital computer in a hybrid configuration or another 580 Computer when two or more are connected in a slaved configuration.

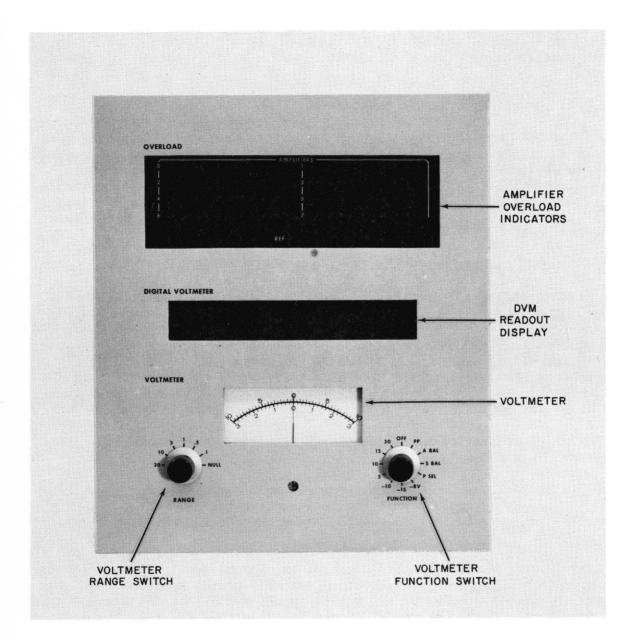

#### 1.4 THE ANALOG READOUT PANEL

The analog readout panel (Figure 1.12) consists of amplifier OVERLOAD indicators, a multi-range VOLTMETER. A DIGITAL VOLTMETER readout display is also located on this panel if a digital voltmeter (DVM) is provided with the computer. The following paragraphs describe the function and use of the various controls and components.

## 1.4.1 Amplifier OVERLOAD Indicators

The amplifier OVERLOAD indicators provide a graphic overload display for each individual amplifier. The indicators are numbered (A00 to A79) to correspond with each amplifier position in the computer. The overload indicators are normally extinguished. A lit position indicates that the corresponding amplifier is in an overload condition. During warm-up periods, various overload lamps may light but should be extinguished once the corresponding amplifiers have settled down.

# 1.4.2 The DIGITAL VOLTMETER (DVM) Readout

The DVM readout displays four digits, a polarity sign, and a fifth digit for overrange. The output of any selected amplifier in the coefficient of any selected potentiometer can be displayed on the DVM. The reading may range from  $\pm 0.0000$  to  $\pm 1.1999$  which, when multiplied with the reference voltage, represents the voltage into the DVM. As an example a reading of 1.1999 is equivalent to 11.999 volts (UNITS DISPLAYED X REFERENCE VOLTAGE).

# 1.4.3 The VOLTMETER

The VOLTMETER is controlled by the RANGE and FUNCTION rotary switches located directly below the meter.

The RANGE switch selects the voltage range of the meter. The ranges provided are: 30, 10, 3, 1, 3, and 0.1 volt for full scale meter deflection. A NULL position is also provided on this switch to convert the VOLTMETER to a null meter.

The FUNCTION switch determines the source of the input signal. Note that many positions on the switch are primarily used for maintenance purposes. However, these positions enable the operator to quickly check all power supply voltages to ensure proper computer operation. Table 1.7 describes the function of each RANGE switch position.

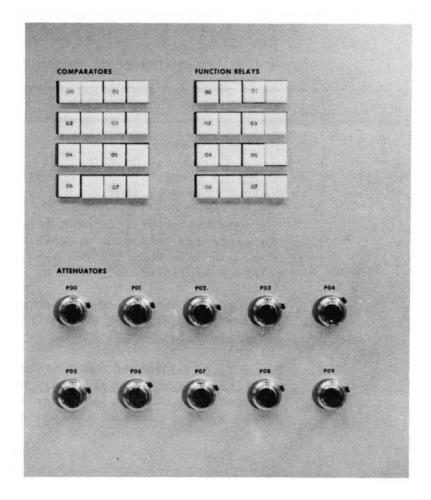

### 1.5 THE AUXILIARY CONTROL PANEL

The auxiliary control panel (Figure 1.13) contains the pushbutton controls and indicators for the interface components (comparator and function relays), and the ten handset pots (PO through P9).

1.5.1 The COMPARATOR Controls

A pair of pushbuttons (one numbered, one blank) is provided for each of the eight comparators in the computer. These pushbuttons are used to force the

Figure 1.12. Analog Readout Panel

Figure 1.13. Auxiliary Control Panel

comparator output to a particular state regardless of its analog inputs. When the pushbutton is released, the corresponding comparator returns to the state dictated by the patch panel inputs. The numbered pushbutton, when depressed, forces the patch panel output of the corresponding comparator high. Similiarly depressing the blank pushbutton forces the comparator output low.

The numbered pushbutton contains an indicator lamp that lights when the comparator output is high. When the comparator has a low output the lamp is extinguished.

| Switch Position                                                                                               | Function                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OFF                                                                                                           | Disconnects the meter input.                                                                                                                                                                          |

| PP (Patch Panel)                                                                                              | VOLTMETER receives input from VM patch terminal on<br>Control Tray 0.12.1607.                                                                                                                         |

| A BAL (Amplifier<br>Balance)*                                                                                 | Connects the stabilizer of a selected amplifier to<br>the meter for balancing purposes. Meter deflection<br>should be less than 1/2 division deflection for<br>balanced amplifier.                    |

| S BAL (Stabilizer<br>Balance)*                                                                                | Connects the stabilizer of either the servo ampli-<br>fier or the amplifiers on the DFG setup panel to the<br>meter for balancing.                                                                    |

| P SEL                                                                                                         | Connects an addressed pot to the meter for setting.<br>This position is used primarily when computer does<br>not contain a DVM and is operable only when the<br>RANGE switch is in the NULL position. |

| 30 (Volts)*<br>15 (Volts)*<br>10 (Volts)*<br>5 (Volts)*<br>-10 (Volts)*<br>-15 (Volts)*<br>-RV (Relay Volts)* | These switch positions connect the various dc volt-<br>ages in the computer directly to the meter.                                                                                                    |

Table 1.7. VOLTMETER RANGE Switch Functions

#### 1.5.2 The FUNCTION RELAY Controls

The pushbutton controls for the eight function relays operate in a manner similiar to the comparator controls. Two pushbuttons (one numbered, one blank) are associated with each function relay. The numbered pushbutton, when depressed, forces the relay to the set condition regardless of the patched logic inputs. The blank pushbutton, when depressed, resets the relay. When the pushbutton is released, the function relay returns to the state dictated by the patch panel inputs. If the patch panel inputs are not patched they remain in the state selected by the pushbuttons. Consequently, with no logic signals patched to its inputs, the function relay can be used as a manual function switch controlled by its associated pushbuttons.

# 1.5.3 The Handset ATTENUATORS

Ten handset ATTENUATORS (P00 to P09) are provided on the auxiliary control panel. Each ATTENUATOR is addressable on the signal selector system and is set in a manner similar to the servo set attenuators except that they are manually adjusted. Set each ATTENUATOR to the desired value using the DVM as a readout device. If the computer does not contain a DVM, the ATTENUATORS have to be set using the nulling method on the VOLTMETER.

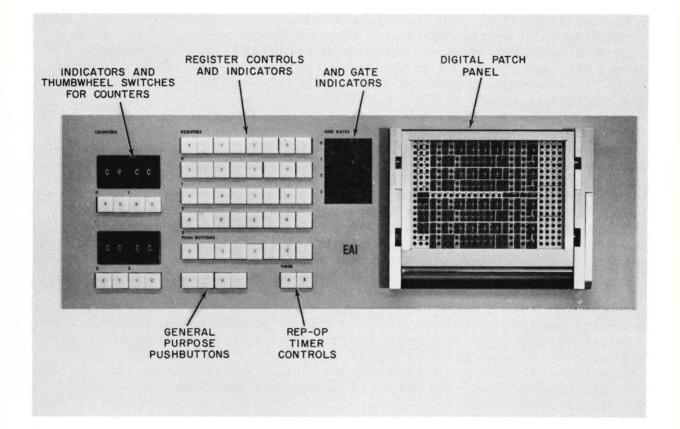

#### 1.6 THE LOGIC CONTROL AND INDICATOR PANEL

The logic control and indicator panel (Figure 1.14) is located at the upper left of the analog patch panel. The panel contains the digital patch panel, AND gate indicators, the REGISTER indicators and pushbutton controls, the indicators and thumbwheel controls for the COUNTERS, the general purpose PUSH-BUTTONS and repetitive operation TIME controls (A and  $\overline{A}$ ). The operation of the various controls and indicators mentioned above are described in the following paragraphs.

### 1.6.1 The Digital Patch Panel

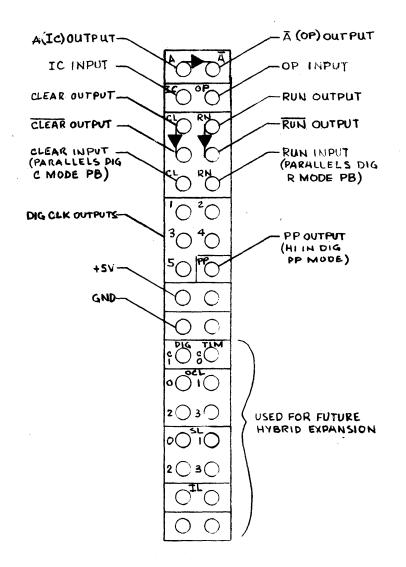

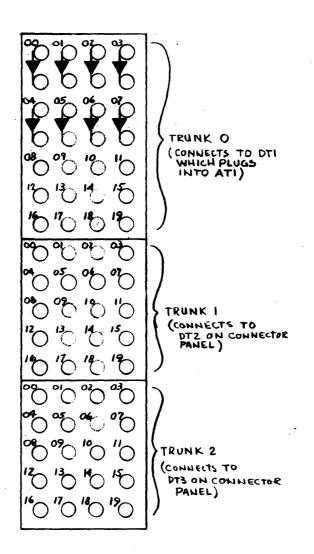

The digital patch panel (Figure 1.15) is used to provide access to the inputs and outputs of the logic devices in the logic package. Physically the logic patch panel is divided into four fields (0 through 3) and three trunk areas (0 through 2). Each of the fields and trunk areas are similar in layout. The particular patching areas and the patch termination functions are described with their associated units.

1.6.2 The AND Gate Display

The AND gate display is provided to indicate the output state of each individual AND gate. When the indicator is lit, the output of the gate is high. The indicator is numbered and lettered to correspond to the gates, and in addition, is laid out in the same configuration as the terminations on the patch panel.

# 1.6.3 The REGISTER Controls and Indicators

A fully expanded 580 Computer logic package contains four registers of four bits each for a total of 16 flip-flops. A numbered pushbutton and the adjacent blank pushbutton are provided as manual controls and indicator for each flipflop. The numbered pushbutton lights when the flip-flop is set and is extinguished when cleared. The numbered pushbutton also serves as a manual control; depressing it sets the flip-flop. The blank pushbutton is not used as an indicator but serves as a manual clear control for its associated flip-flop.

Figure 1.14. Logic Control and Indicator Panel

Figure 1.15. Digital Patch Panel

The registers are numbered 0, 1, 2 and 3 while the flip-flops within the registers are numbered in the reverse order. The reverse order of the flip-flops is necessary since, by convention, the most significant bit of a counter is considered to be on the left.

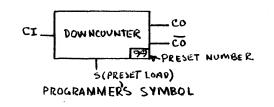

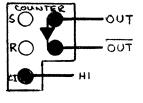

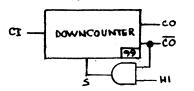

## 1.6.4 The COUNTER Controls and Indicators

A fully expanded 580 Computer logic package contains four counters which may be used for counting or timing functions. Manual control of the counter is provided by pushbuttons S (set) and R (reset). Pushbutton S contains an indicator lamp; it lights whenever the counter output is high.

Depressing pushbutton S sets the output flip-flop and loads the counter. When the count reaches 00, the output flip-flop is reset, and the counter output goes low. The output stays low until the output flip-flop is again set (the counter is loaded). Automatic loading of the counter is accomplished by patching the output through an AND gate (for time delay) to the S patch terminal. The second input for the patched AND gates serves as a controlling input; that is the AND gates can be patched to make the counter operation dependent on two or more separate output functions.

The preset load value is simply a matter of selecting the proper count while the left thumbwheel represents the tens count. In the event the count is less than 10 (0 through 9) the left thumbwheel is set to zero.

The counter is reset by patching a high to the R (reset) patch terminal or depressing the manual reset (R) pushbutton on the computer keyboard.

#### 1.6.5 The General Purpose PUSHBUTTONS

The six general purpose PUSHBUTTONS provided in the 580 Computer logic package are latching-type switches whose outputs are terminated on the patch panel. Two pushbutton controls are provided for each switch. The numbered pushbutton is used to set the switch (output is high), and the adjacent pushbutton (blank) is used to reset the switch (output low). The numbered pushbutton also contains an indicator which, when lit, indicates that the associated output is high. When the output of a PUSHBUTTON is zero, depressing the blank pushbutton associated with that output, generates a synchronized pulse (one clock period in length) available at the output terminal.

### 1.6.6 The TIMER Controls

The rep-op TIMER controls (A and  $\overline{A}$ ) are used to manually force the timer into the corresponding modes (A = IC,  $\overline{A}$  = OP). The A pushbutton contains an indicator circuit which lights when the timer is in the IC mode.

## 1.7 READOUT DEVICES

The problem solution obtained with the 580 may be permanently recorded or temporarily displayed on several types of readout devices. The DVM or VOLT-METER, discussed previously, may be used to measure steady-state computational voltages. In repetitive operation, the computer solution is displayed on an

oscilloscope and a permanent record can be obtained by photographing the oscilloscope trace. X-Y plotters, such as the EAI 1110 VARIPLOTTER<sup>®</sup>, or strip chart recorders, such as the EAI 8875 RECORDER, can also be used to display problem variables. These readout devices are connected to the 580 Computer by means of the connectors provided on the connector panel (Figure 1.16) located at the rear of the computer.

Figure 1.16. Readout Device Connectors

.

#### CHAPTER 2

### OPERATIONAL AMPLIFIERS

## 2.1. INTRODUCTION

The operational amplifier is the basic computing element in an analog computer. The amplifier may be used in conjunction with appropriate networks to perform linear computations such as summation, integration, multiplication by a constant, and inversion. Accessory components permit use of the amplifier for nonlinear operations such as multiplication and division of variables, and the generation or analytic or arbitrary functions.

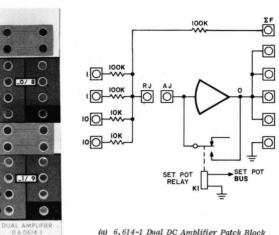

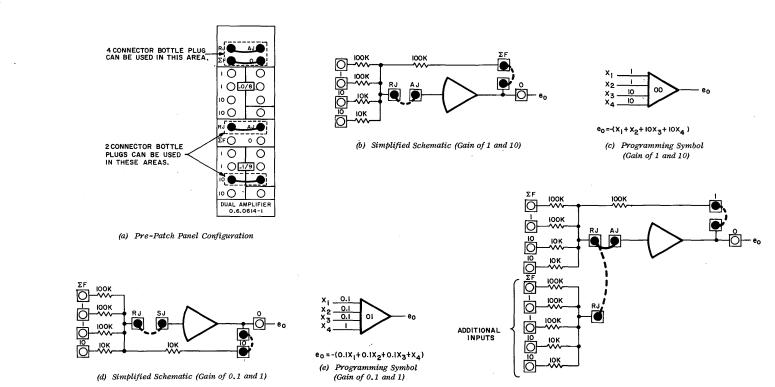

There are two amplifiers used in the 580. These are:Dual DC Amplifier, Model 0.6.614-1 and Quad DC Amplifier, Model 6.704-2. Figure 2.1 shows the patch block layout and simplified schematic of each amplifier type and the associated resistor network.

2.2 DUAL DC AMPLIFIER PATCHING

The input and output terminations of the dual amplifier and dual resistor networks are terminated at the pre-patch panel and are arranged for ease of patching. The nonlinear components are also located in close proximity to the amplifiers for ease of patching and short patch cord runs.

Patching an amplifier for use with an integrator network, or one of the nonlinear components, is covered in the separate sections of this manual pertaining to the particular component. This section is limited to the description of the amplifier used in conjunction with a resistor network.

Figure 2.2 illustrates two of the more common patching arrangements for the Model 0.6.614-1 Amplifier. The patching shown for the upper amplifier (Figure 2.2a) makes use of the standard 4-pin bottle plug and provides the summing circuit shown schematically in Figure 2.2b. This configuration has two gainof-one and two gain-of-ten inputs. The basic programming symbol for this circuit is shown in Figure 2.2c. Note that the amplifier address number is normally placed in the triangle. Normally, only those inputs to be used are shown.

The lower amplifier (Figure 2.2a) is patched for one gain-of-one and three gainof-one-tenth inputs using two 2-pin bottle plugs. The simplified schematic and programming symbol for this configuration are illustrated in Figures 2.2d and e. Additional input resistors can be made available by connecting the RJ terminations of different resistor networks together as shown in Figure 2.2f.

Resistors may be patched in series or parallel in the input or feedback circuit to obtain desired gains. Some of these configurations are summarized in Appendix 1.

(a) 6.614-1 Dual DC Amplifier Patch Block and Simplified Schematic (One Channel)

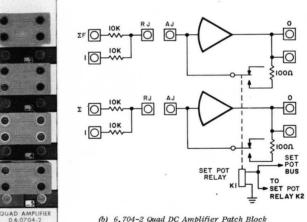

(b) 6.704-2 Quad DC Amplifier Patch Block and Simplified Schematic

NOTES:

1. SET POT RELAYS SHOWN IN DE-ENERGIZED CONDITION.

2. DUAL AMPLIFIERS HAVE 1 SET POT RELAY EACH. QUAD AMPLIFIERS HAVE 2 SET POT RELAYS EACH.

Figure 2.1. 580 Operational Amplifiers (Patch Block Layout and Simplified Schematics) Figure 2.2. Dual Amplifier, Typical Patching Configurations

<sup>(</sup>f) Simplified Schematic Showing Additional Inputs

2-3

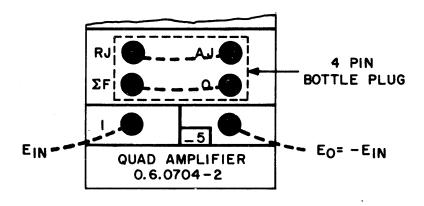

# 2.3 QUAD DC AMPLIFIER PATCHING

The 580 Computer has provisions for up to eight Quad DC Amplifiers, Model 0.6.704-2 installed in the patch bay. The quad amplifiers have 10K ohm input and feedback resistors for each amplifier circuit. This permits wide bandwidth, low offset, inversion. The 10K ohm resistors are accurately matched to ensure true unity gain inversion. Figure 2.3 shows the normal patch configuration for one amplifier of a quad.

Figure 2.3. Quad Amplifier Patching Configuration

#### CHAPTER 3

#### ATTENUATORS AND FEEDBACK LIMITERS

## 3.1 ATTENUATORS

### 3.1.1 Introduction

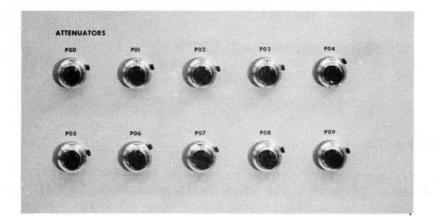

The 580 Computers have provisions for 10 handset attenuators (Figure 3.1a) and 70 servo set attenuators (Figure 3.1b) when fully expanded. Each row of attenuators (one row of handset attenuators and seven rows of servo set attenuators) is terminated in a particular field on the patch panel. The first digit in the attenuator address indicates the field number. For example, the handset attenuators are all terminated in FIELD 0 and are numbered 00 through 09. Each row of the seven rows of servo set attenuators is terminated in a particular field. With the exception of the ungrounded attenuator in each \_4 position, all attenuators in a particular field have one end internally grounded with the ungrounded end and the wiper terminated on the patch panel. The ungrounded pot in each field has both ends and the wiper terminated on the patch panel.

The standard potentiometers are ten-turn, wirewound, 5000 ohm units. The handset attenuators are equipped with vernier dials that have a locking mechanism.

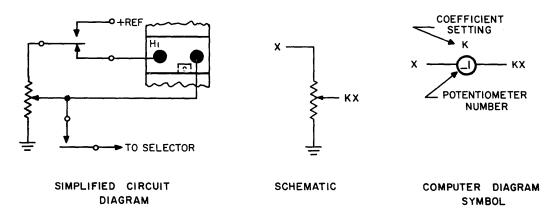

## 3.1.2 Grounded Attenuators

Figure 3.2a shows the circuits used in the 580 for setting grounded attenuators under load. Relay Kl is energized when the computer is placed in <u>set pot</u> mode and applies reference voltage to the high end of all grounded attenuators. Relay K2 is energized when the attenuator is addressed by the signal selector system. The wiper voltage is connected to the input of the DVM. The wiper is still connected to the patch panel and is patched to the load it sees when in use. The wiper of the attenuator is adjusted until the desired coefficient is obtained on the DVM.

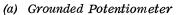

# 3.1.3 Ungrounded Attenuators

The operation of the ungrounded attenuators (Figure 3.2b) is similar to the grounded attenuators except that the lower terminal is not internally grounded. Prior to setting an ungrounded attenuator, the lower terminal must be patched to ground. If setting is attempted without the ground connection, the servo drives the attenuator to its highest resistance. The attenuator is held in this position until the CLR pushbutton is depressed and the attenuator is grounded. The ground can be removed from the attenuator once it is set and its address removed.

## 3.2 FEEDBACK LIMITER

#### 3.2.1 General

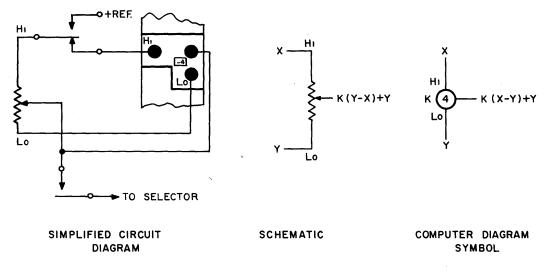

Feedback Limiter, Model 0.42.0342 provides three variable and accurate feedback limiters capable of limiting either or both the positive and negative amplifier outputs.

(a) Handset Attenuators

(b) Servo Set Attenuators

Figure 3.1. Attenuators

(b) Ungrounded Potentiometer

Figure 3.2. Potentiometer Configurations

The 0.42.0342 Module may be installed in any Track/Store potentiometer module slot in the pre-patch panel area. In addition to the limiter terminations, this module retains the patching terminations for the potentiometer group normally terminated in the area used. The patch block configuration is illustrated in Figure 3.3. The five potentiometers are all available for standard potentiometer use when the limiters are not in use. When the limiters are in use, the potentiometers become the limit adjustment controls. When all limiters are used for + limiting a sixth attenuator has to be patched from another position.

## 3.2.2 Patching Configuration

Whether used in conjunction with the limiter or not, the five potentiometers can be selected for readout and/or setup using the standard procedure.

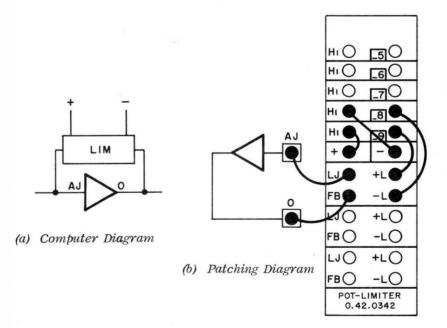

Figure 3.4 illustrates a typical patching configuration for the upper limiter of the network. The amplifier to be limited is patched in its normal circuit configuration. The limiter is then patched around the amplifier with the LJ to AJ and FB to 0 connections as shown. The patching is completed by connecting the Hi-side (top) of two potentiometers to the appropriate reference levels and the wipers to the proper limiter inputs.

### 3.2.3 Setting the Limit Value

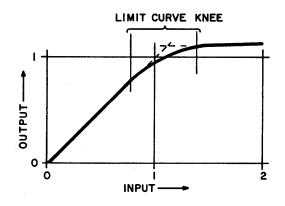

The diode action of the base-emitter junction causes a small amount of "rounding" (or knee) in the amplifier limited output waveform as shown in Figure 3.5. The procedure for setting the limiter depends on whether the programmer prefers the knee to fall above or below the limit value. To set the knee below the limit value proceed as follows: Apply reference as the input to the amplifier (opposite in polarity to the output voltage to be limited). Adjust the limit pot to the desired limit value. The knee will start before the limit value is reached, and the amplifier output will not exceed the set value. To set the knee above the limit value proceed as follows: Apply an input that provides the amplifier with an <u>unlimited</u> output equal to the desired limit value. Adjust the limit pot to the point where the limiter just starts to function and then "back-off" the control slightly. The knee will start at the set limit value.

If it is desired to limit the amplifier output at  $\pm$  reference, the  $\pm$ L potentiometers can be eliminated from the circuit by patching + reference directly to -L (- reference output limit) or - reference directly to +L (+ reference output limit).

Figure 3.3. Feedback Limiter Patching Block

Figure 3.4. Typical Limiter Patching

Figure 3.5. Limit Curve

### CHAPTER 4

#### INTEGRATORS

# 4.1 INTRODUCTION

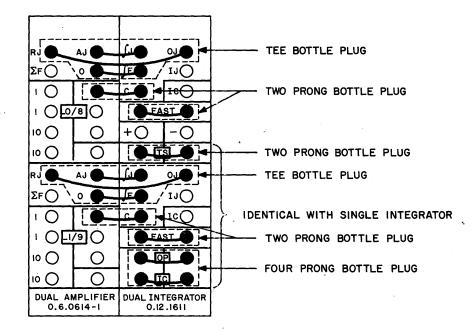

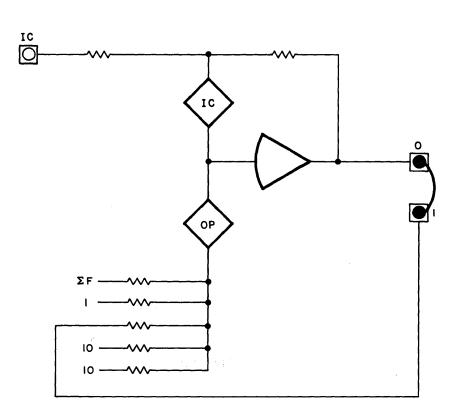

This chapter includes operating information for the 0.12.1611 Dual Integrator Tray and the 0.12.1675 Potentiometer, Integrator Tray. The patching blocks for these integrators are shown in Figure 4.1. This chapter also includes operation of the repetitive operation group, which controls the integrators when the computer is in the rep-op mode.

#### 4.2 INTEGRATOR TRAYS

The 0.12.1611 Dual Integrator Tray and the 0.12.1675 Potentiometer, Integrator Tray are similar except that the 0.12.1675 contains only one integrator while the 0.12.1611 contains two. The operation of each integrator section of each tray is identical. Consequently only the dual integrator is discussed in this chapter.

The integrators are typically patched as shown in Figure 4.2. Note that in each field, the integrator trays are physically located adjacent to a dual dc amplifier to facilitate the usage of bottle plugs for patching.

#### 4.2.1 Integrator Mode Control

The initial condition (IC), operate (OP), and hold (HD) integrator modes are controlled by logic signals. The table below gives the necessary logic levels at the various control terminals to establish the control modes.