# EXPERIMENTAL DISPLAY SYSTEM

# COPY NO. 0013

This manual contains proprietary information. It is provided to the customers of Digital Equipment Corporation to help them properly use and maintain DEC equipment. Revealing the contents to any person or organization for any other purpose is prohibited.

#### PREFACE

This manual is one of a series of documents needed for understanding and operating the General Purpose Experimental Display System. Included in this manual are descriptions of the system and its programming language, an explanation of those parts of the system which are not contained in other Digital publications, and reproductions of the engineering drawings used in this explanation.

This display system consists of a modified Program Data Processor-4, a modified Type 340 Incremental Display, and special interface and control equipment. The PDP-4 and 340 maintenance manuals should be consulted for all information on the operation and maintenance of their respective equipment. In addition, the subsidiary documents listed in these manuals are necessary adjuncts to the system documentation.

| Section |                                              | Page |

|---------|----------------------------------------------|------|

| 1       | DESCRIPTION                                  | 1-1  |

|         | Introduction                                 | 1-1  |

|         | Computer                                     | 1-1  |

|         | Display                                      | 1-3  |

| 2       | PROGRAMMING                                  | 2-1  |

|         | Type 340 Incremental Display                 | 2-1  |

|         | Control Mode (000)                           | 2-1  |

|         | Point (XY) Mode (001)                        | 2-3  |

|         | Vector Mode (100)                            | 2-3  |

|         | Vector Continue Mode (101)                   | 2-3  |

|         | Increment Mode (110)                         | 2-3  |

|         | IOT 7X05Y4, Resume                           | 2-3  |

|         | IOT 0912, Display Read Address Counter (DRA) | 2-4  |

|         | PDP-4 Computer                               | 2-5  |

|         | PDP-4/340 System                             | 2-5  |

|         | Knob and Track Ball Counters                 | 2-9  |

|         | Sample Interruption Saving Program           | 2-10 |

| 3       |                                              | 3-1  |

|         | Preventive Maintenance                       | 3-2  |

|         | Marginal Voltage Checks                      | 3-3  |

|         | 1604A Simulation                             | 3-4  |

|         | Operation of Extra Equipment                 | 3-8  |

|         | Standard Options                             | 3-8  |

|         | Modifications                                | 3-11 |

|         | Real Time Control                            | 3-11 |

|         | 340 Display                                  | 3-19 |

|         | Operator's Console                           | 3-22 |

# CONTENTS

# CONTENTS (continued)

| Section |                              | Page |

|---------|------------------------------|------|

|         | Interface Electronics        | 3-25 |

|         | Control and Status Flip-Flop | 3-34 |

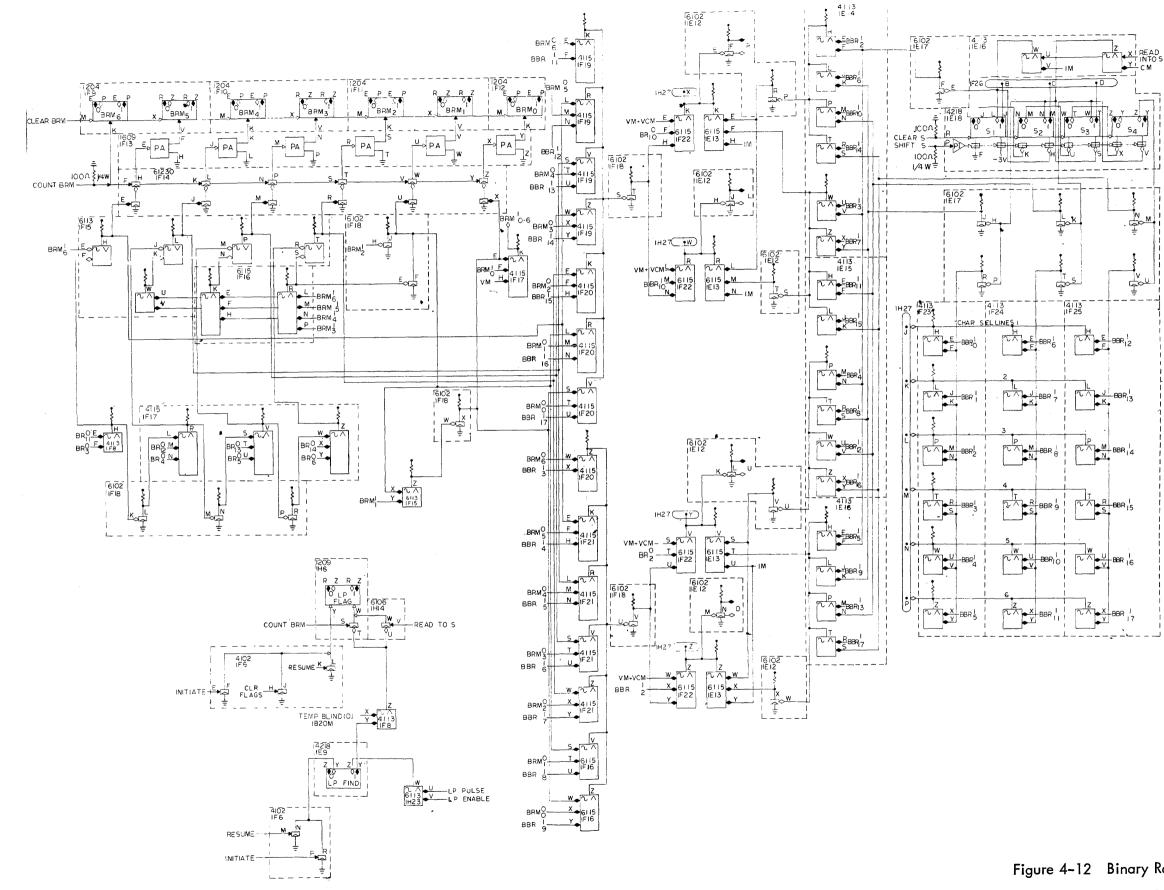

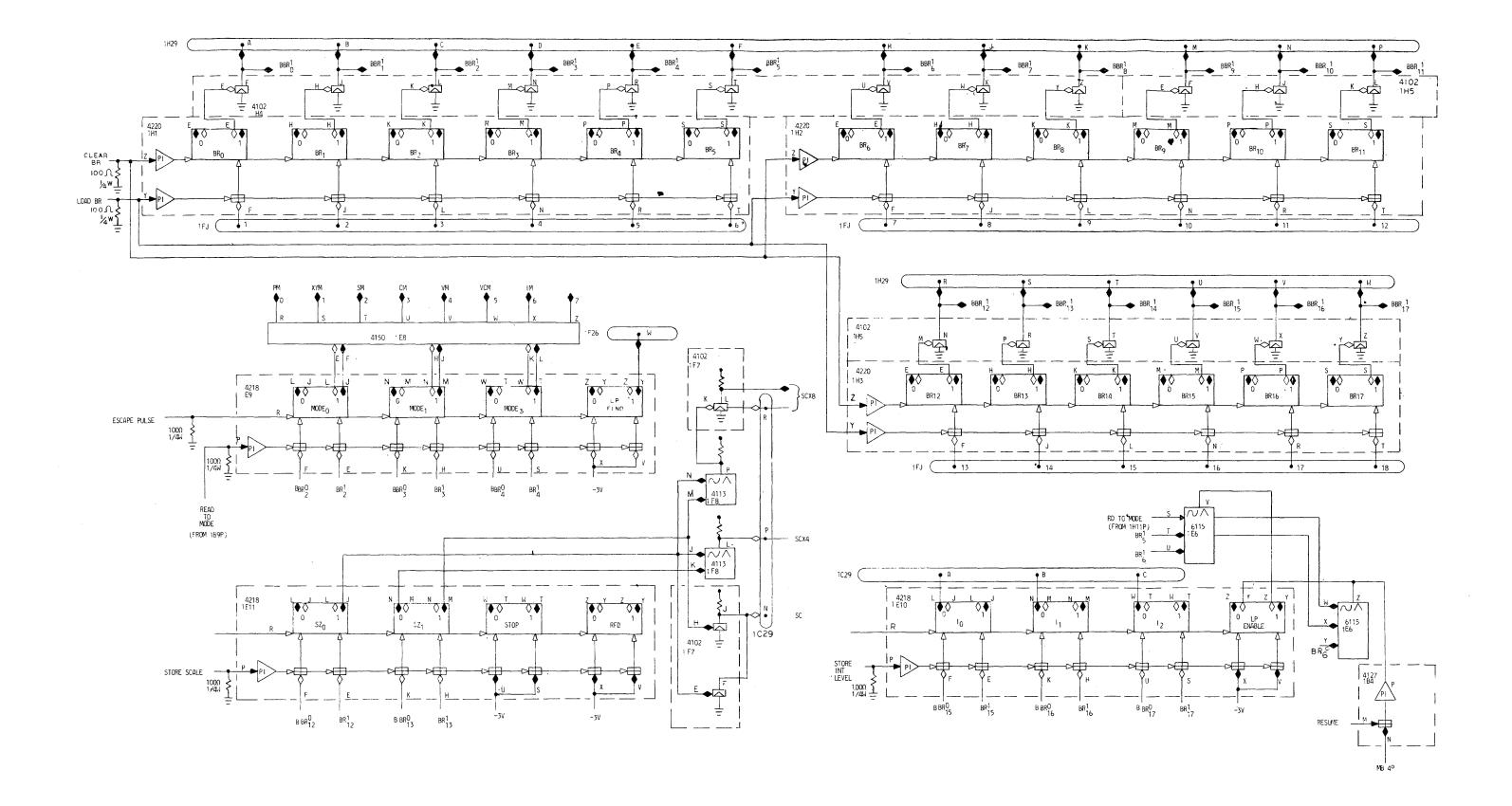

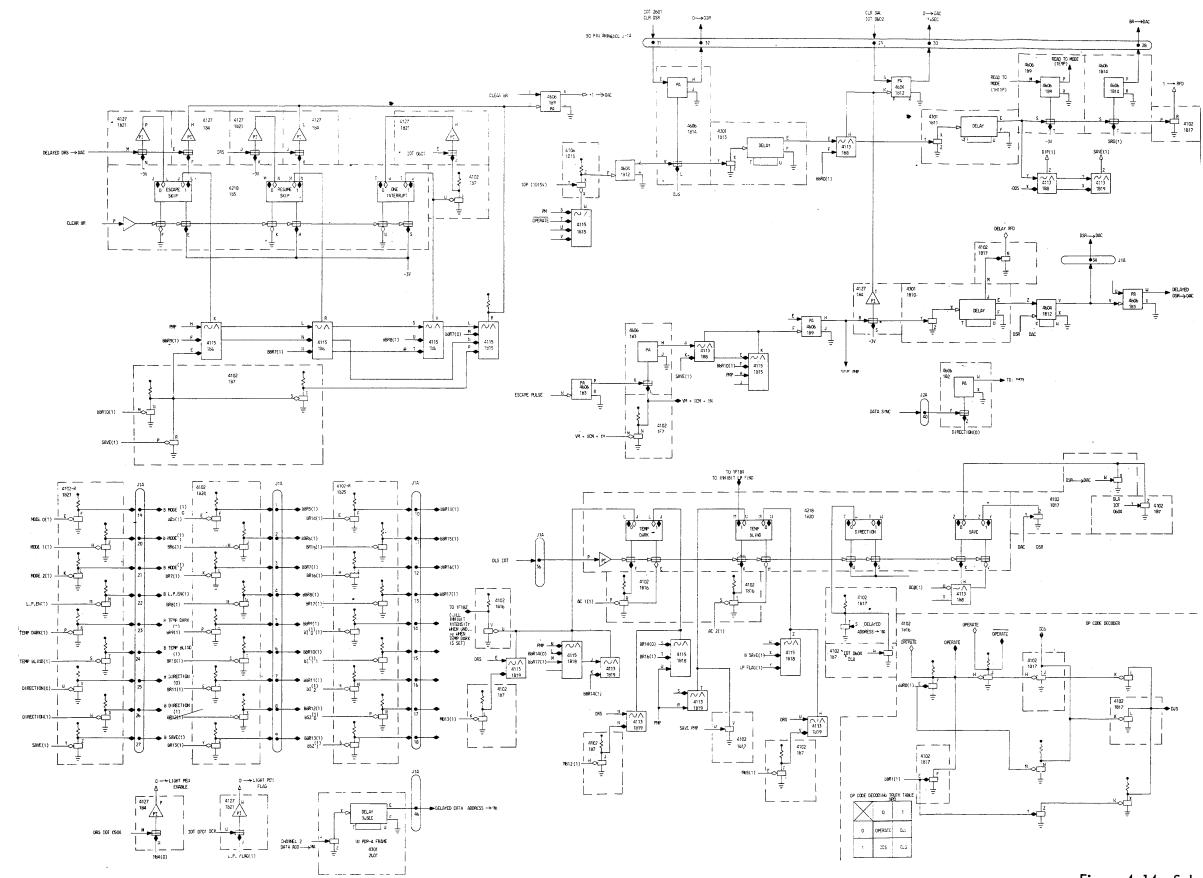

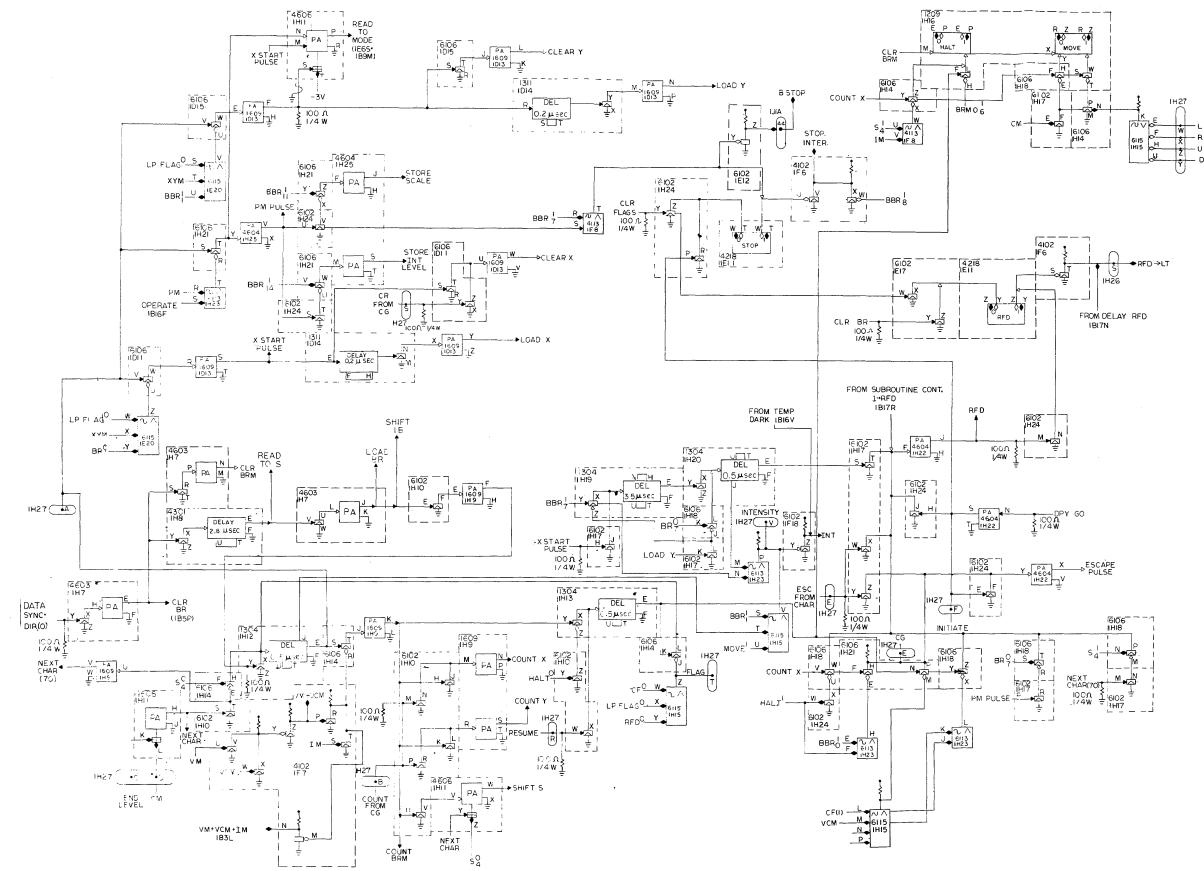

| 4       | ENGINEERING DRAWINGS         | 4-1  |

# ILLUSTRATIONS

# Figure

| 1-1 | PDP-4C-24 Rack Layout                                   | 1-2  |

|-----|---------------------------------------------------------|------|

| 1-2 | General Purpose Experimental Display Operations Console | 1-3  |

| 1-3 | Modified Type 340 Display Rack Layout                   | 1-4  |

| 3-1 | Type 140 Relay Buffer and Control Register              | 3–3  |

| 3-2 | 1604A Simulation Block Diagram                          | 3-6  |

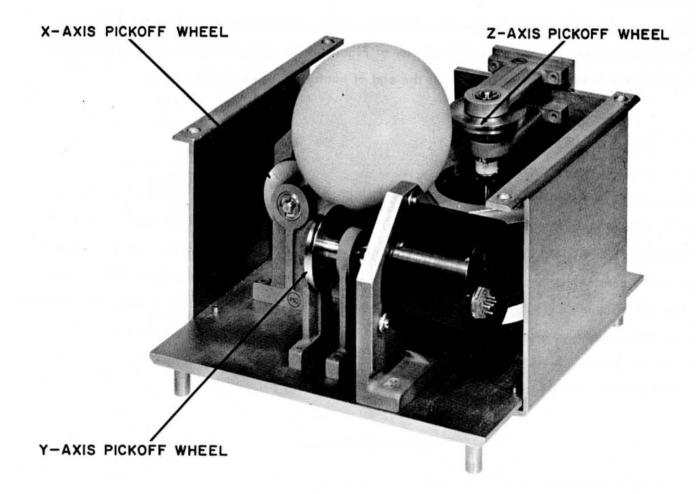

| 3-3 | Track Ball Assembly                                     | 3-23 |

# TABLES

# <u>Table</u>

| 2-1 | Resume Family of IOT's                        | 2-5  |

|-----|-----------------------------------------------|------|

| 2-2 | PDP-4/340 Instructions                        | 2-6  |

| 2-3 | Knob and Track Ball Counting Sequence         | 2-9  |

| 3-1 | Simulated 1604A Input Signal Bit Assignments  | 3-5  |

| 3-2 | Simulated 1604A Output Signal Bit Assignments | 3-7  |

| 3-3 | Function Bit Assignment                       | 3-36 |

| 4-1 | Engineering Drawings                          | 4-1  |

#### **SECTION 1**

#### DESCRIPTION

#### INTRODUCTION

The General Purpose Experimental Display System described in this manual consists of a PDP-4C computer with 8192 words of core memory, a perforated tape reader, and a modified high-speed data multiplexer; a modified 340 Incremental CRT Display; a special operator's console and associated electronic circuitry; and interface equipment for connecting the system to a CDC 1604A digital computer. The PDP-4/340 system is normally operated as a piece of input-output equipment by the 1604A, but is also capable of independent operation.

This display system presents information that has been stored in the PDP-4's memory to the operator as dots, lines, curves, and characters on the face of a cathode ray tube. The operator may generate new data by depressing various buttons and keys on the console, moving knobs or a track ball, and placing a light pen over a particular displayed area. This information is placed in either the memory or the accumulator of the PDP-4, where it may be used to modify the display, indicate various conditions, or cause the system to perform different operations.

#### COMPUTER

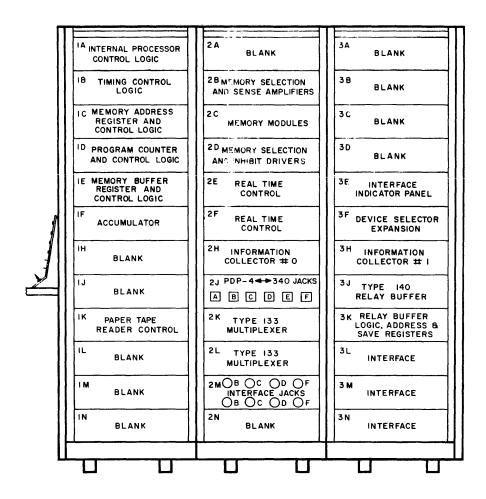

The computer used in this system is Digital Equipment Corporation's standard PDP-4C with slight modifications and additional equipment, some of it standard Digital options and some unique to this system. An extra bay has been added to the computer to house the additional equipment. Figure 1–1 shows the rack layout of the computer.

The standard PDP-4C consists of a central processor, an operator's console, a 4096-word core memory, a real time control (referred to as the Type 25 Real Time Option in the PDP-4 Maintenance Manual), and a paper tape reader. The standard options added to the central processor include a 133 Data Interrupt Multiplexer, a 134 Core Memory Module, and a 140 Relay Buffer and Control, as well as 728 Power Supplies.

Figure 1-1 PDP-4C-24 Rack Layout

The modifications to the standard PDP-4C are in the real time control, and affect the real time clock and the information collector. The real time clock's overflow flag circuit has been disabled, and circuits have been added to include a gatable variable-frequency clock, a program servicing condition, and a new computer state (limbo).

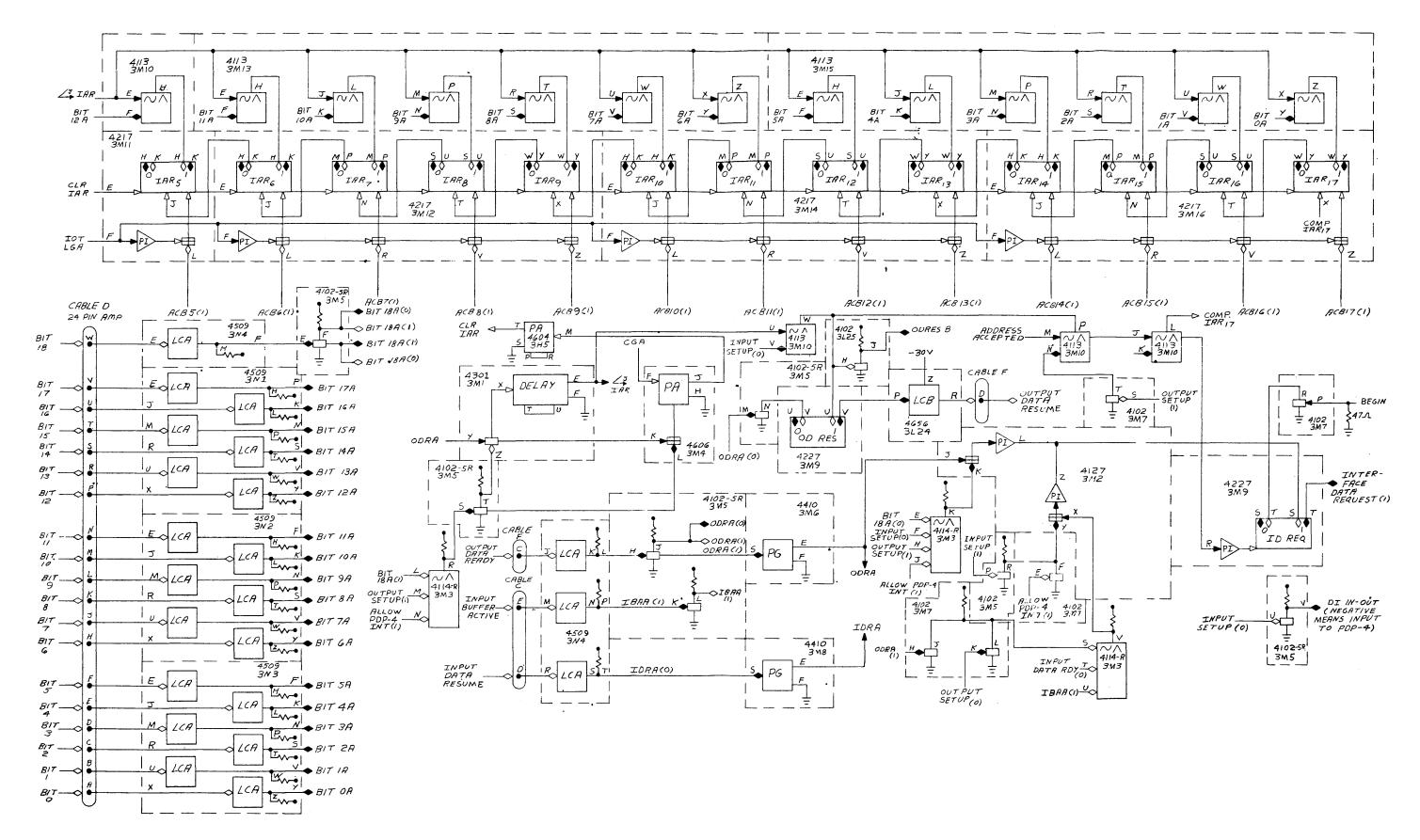

The additional equipment added to the central processor includes address and save registers for the 340 Display, and interface control and status circuits to permit this system to be operated by CDC's 1604A computer. The latter circuits consist of an information buffer register for the 1604A's input, an interface address register for the PDP-4's memory location, level changing amplifiers to convert between CDC and Digital logic levels, a decoding network to allow the 1604A to correspond with this or other systems via the same buffer channels, and a group of status flip-flops for exchanging control information between the two computers.

#### DISPLAY

The CRT display used in this system is a standard Digital Type 340 Precision Incremental Display with slight modifications and additional equipment. Most of the extra equipment is specially designed for this system, and the standard items are a Type 370 Light Pen and Type 728 Power Supplies.

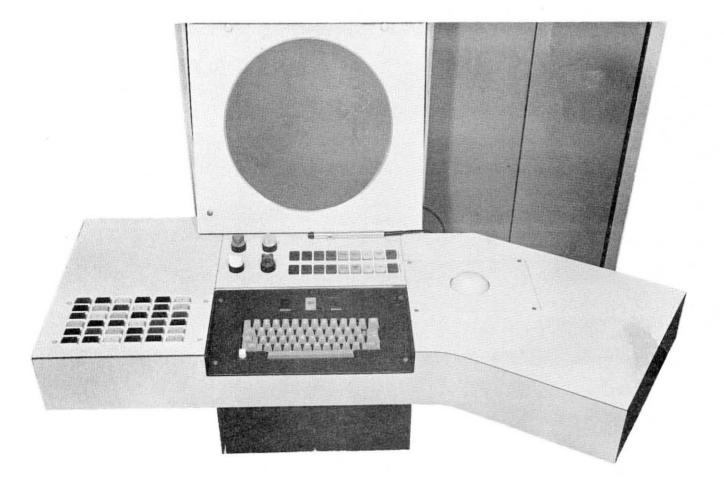

The special equipment added to the display consists of an operator's table with pushbuttons, lights, a keyboard, knobs, and a track ball; and the electronic control circuits associated with these items. Figure 1-2 shows the location of these various items on the operator's table. This equipment is not connected directly to the 340, but only obtains information which can be placed in the memory or accumulator of the PDP-4, and used by a program to change data or modify the display file.

Figure 1-2 General Purpose Experimental Display Operator's Console

The extra electronic circuits consist of switch input filters for smoothing switch input signals; light driver registers that select and control the indicator lights within the pushbuttons; knob and track ball counters that convert and store physical movements; and an information collector that processes data from the above items and applies it to the accumulator of the PDP-4 on command.

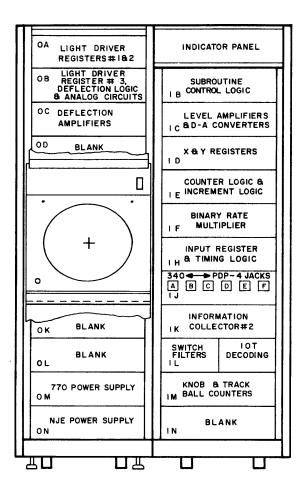

The modifications to the 340 consist of adding a circuit which enables the display to decode input information and perform various operations based on this information. In this way the display acts as a small computer, using the same memory as the PDP-4. Figure 1-3 shows the rack layout of the display.

Figure 1-3 Modified Type 340 Display Rack Layout

#### SECTION 2

#### PROGRAMMING

#### TYPE 340 INCREMENTAL DISPLAY

The 340 Display employed in the general purpose experimental display system interprets the 18-bit input word in one of five modes as directed by the mode information contained in the mode register. The five modes which the 340 recognizes are: control mode, point mode, vector mode, vector continue mode, and increment mode. The operation of these modes is described in the Type 340 Incremental Display Maintenance Manual, H-340. The operation of the display in this system is somewhat different from that of the standard 340. The differences are explained below.

#### Control Mode (000)

This is a combination of the parameter and subroutine modes for the standard 340. Bits 0 and 1 compose the operation code for the control mode. When they are 00, the display operates similarly to the regular parameter mode. When the bits are other than 00, the display operates similarly to the subroutine mode.

#### Mode 000, OP Code 00

In the standard 340, bits 9 and 10 are unused in the parameter mode. The display in this system interprets these two bits in the following manner:

<u>Bit 9</u> – Bit 9 is the skip bit. If bit 9 is set, the contents of the DAC are incremented by one count, fetching the next instruction from location N+2, (where N is the location containing the skip instruction) rather than from N+1.

<u>Bit 10</u> - If bit 10 is set and the save flip-flop is set indicating that the 340 is in the process of performing a subroutine, the 340 escapes from the subroutine. The contents of the DAC are replaced by the contents of the DSR (which is not altered) and the save flip-flop is cleared. As

a result of this action, the 340 takes its next instruction from the memory address following the one which initiated entry into the subroutine. The effect is the same as if a DDS had been executed. Note that this action takes place only if the save flip-flop is set.

If both bit 7 (the stop bit) and bit 9 (the skip bit) are set, the display stops as a result of bit 7 being set. The skipping action is not performed until the PDP-4 issues the resume IOT, 700504. This allows the PDP-4 program to interrupt the DAC after the stop has occurred. Then, when the resume IOT is issued, the display requests data from a location one greater than the address read from the DAC.

If both bits 9 and 10 are set and the save flip-flop is set, the subroutine escape process is performed before the skipping action. When the above conditions are met, the 340 requests data from a location two greater than the instruction that caused entry into the subroutine. The subroutine escape has precedence over the skipping action.

NOTE: The above actions can be microprogrammed with the other actions possible in a control mode word.

#### Mode 000, OP Code 01 - DDS (Display Deposit Save Register in A)

In PDP-4 memory register A, deposit a display Jump to the C (Display Save Register) instruction, replaces the mode register contents with bits 2 through 4 and clears the save flip-flop. This instruction generates an exit from a subroutine. The exit transfers the 340 program sequence to the location following the one which contained the DJS at the start of the subroutine.

#### Mode 000, OP Code 10 - DJP (Display Jump to A)

The contents of the 13-bit display address counter (DAC) are replaced with bits 5 through 17 of the BR. The present contents of the DAC are lost. The contents of the mode register are replaced with bits 2 through 4 of the BR. This instruction allows the 340 to receive its next word from the PDP-4 cell whose address corresponds to A, rather than from the address following the one containing the DJP instruction. The contents of the 13-bit DAC are replaced with bits 5 through 13 of the BR. The present contents of the DAC are saved in the 13-bit display save register (DSR). This is signified by Setting the save flip-flop, and replacing the present mode register contents with bits 2 through 4. This instruction allows multi-level subroutining to be performed by the 340 since the contents of the DSR are accessible for generating an exit from the subroutine.

#### Point (XY) Mode (001)

Operation of the point mode is described in the 340 Maintenance Manual.

#### Vector Mode (100)

Operation of the vector mode differs from that described for the standard 340 in that violating an edge does not cause the display to escape to the control (parameter) mode. When a vector word with the escape bit set is encountered and the save flip-flop is set, the 340 performs the subroutine escape described previously.

#### Vector Continue Mode (101)

Operation of the vector continue mode differs from that described for the standard 340 only when the save flip-flop is set. If the save flip-flop is set and an edge is violated, the 340 performs the subroutine escape action. Violating an edge causes the mode to be changed to the control mode regardless of the setting of the save flip-flop.

#### Increment Mode (110)

Operation of the increment mode differs from that described for the standard 340 in that incrementing beyond the edge does not cause the display to escape to the control mode. Also, if an increment word is encountered with the escape bit set and the save flip-flop is set, the subroutine escape action takes place.

#### IOT 7X05Y4, Resume

In the standard 340, the IOT resume is used only following the detection of light by the light pen, when it causes the picture that is interrupted at the time of light detection to be continued.

1. If the display is interrupted by the light pen while drawing a vector, resume causes the vector to be continued as in normal 340 operation.

2. If the display is stopped by a control parameter mode stop (bit 7 set), resume causes the display to request new data from the address in the DAC (the word following the stop instruction).

3. If the display is stopped due to control mode stop and the word that caused the stop also had the skip bit (bit 9) set, the skip is performed and data is requested from the address which is one location beyond that containing the stop and skip word.

4. If bit 4 (MB4) is set, resume does not affect state of LP enable (i.e., if set it remains set; if cleared, it remains cleared). If bit 4 is cleared, LP enable is cleared. Note that resume does not automatically reset LP enable.

5. If bit 5 (MB5) is set, resume will set the temporary blind flip-flop, effectively disabling the light pen.

6. If bit 12 (MB12) is set, resume will set the temporary dark flip-flop, preventing a spot from being displayed on the CRT.

The various microprogramming instructions possible with the resume family of IOT's is given in Table 2–1.

#### IOT 0912, Display Read Address Counter (DRA)

Issuing the IOT display read address counter (DRA) reads the C(DAC) = AC and also stops the 340, since DRA sets the 340 lockout flip-flop. This prevents the display from requesting data cycles and gives the programmer the ability to determine the current location of the display program while the display is running.

| Octal Value | /alue LP Enable Temp Blind |     | Temp Dark |  |

|-------------|----------------------------|-----|-----------|--|

| 700504      | cleared                    |     | ÷=        |  |

| 700524      | cleared                    |     | cleared   |  |

| 700544      | cleared                    |     | set       |  |

| 710504      | cleared                    | set |           |  |

| 710524      | cleared                    | set | cleared   |  |

| 710544      | cleared                    | set | set       |  |

| 720504      |                            |     |           |  |

| 720524      |                            |     | cleared   |  |

| 720544      |                            |     | set       |  |

| 730504      |                            | set |           |  |

| 730524      |                            | set | cleared   |  |

| 730544      |                            | set | set       |  |

#### TABLE 2-1 RESUME FAMILY OF IOT's

#### PDP-4 COMPUTER

Almost all of the PDP-4 instructions will operate the PDP-4/340 system as they are described in the PDP-4 Handbook. The only exceptions are the IOT clock skip on flag, 700001, and the IOT's for the paper tape punch, teleprinter, Type 30 displays, magnetic tape, card reader, card punch, and line printer.

#### PDP-4/340 SYSTEM

Many of the standard instructions and all of the special instructions have been given new mnemonic names, generally three digits long. Table 2-2 lists these instructions by name, gives their octal numerical values, and describes their functions. All possible instructions are not named or listed because some additional microprogramming is possible.

| Mnemonic | Octal  | Name/Remarks                                                     |  |  |  |  |  |

|----------|--------|------------------------------------------------------------------|--|--|--|--|--|

| 1        | 020000 | /INDIRECT BIT                                                    |  |  |  |  |  |

| 6S       | 77     | BCD MASK                                                         |  |  |  |  |  |

| 135      | 17777  | ADDRESS MASK                                                     |  |  |  |  |  |

| ADD      | 300000 | ADD/1'S COMPLEMENT, ADDRESS AND AC                               |  |  |  |  |  |

| AGI      | 702244 | ALLOW GENERATOR INTERRUPT/ALLOW INTERRUPT FROM INTERFAC          |  |  |  |  |  |

| AND      | 500000 | AND/LOGICAL AND, ADDRESS AND AC                                  |  |  |  |  |  |

| API      | 700044 | ALLOW PERIODIC INTERRUPT                                         |  |  |  |  |  |

| CAL      | 000000 | CALL SUBROUTINE/IN ADDRESS                                       |  |  |  |  |  |

| CGI      | 702401 | CLEAR GENERATOR FLAG I/CLEAR 1604 INPUT CHANNEL INTERRUPT        |  |  |  |  |  |

| CGO      | 702402 | CLEAR GENERATOR FLAG)/CLEAR 1604 OUTPUT CHANNEL INTERRUI<br>FLAG |  |  |  |  |  |

| CGP      | 702202 | CLEAR GENERATOR FLAG P/CLEAR INTERFACE FLAG                      |  |  |  |  |  |

| CLA      | 750000 | CLEAR AC                                                         |  |  |  |  |  |

| CLC      | 750001 | CLEAR AND COMPLEMENT AC                                          |  |  |  |  |  |

| CLF      | 700004 | CLOCK OFF AND FLAG CLEARED                                       |  |  |  |  |  |

| CLL      | 744000 | CLEAR LINK                                                       |  |  |  |  |  |

| CL1      | 703101 | CLEAR LIGHT BUFFER 1/ NUMBERS 1-18                               |  |  |  |  |  |

| CL2      | 703121 | CLEAR LIGHT BUFFER 2/ NUMBERS 19-30                              |  |  |  |  |  |

| CL3      | 703141 | CLEAR LIGHT BUFFER 3/ INSTRUCTIONS                               |  |  |  |  |  |

| CLN      | 700044 | CLOCK ON AND FLAG CLEARED                                        |  |  |  |  |  |

| CMA      | 740001 | COMPLEMENT AC                                                    |  |  |  |  |  |

| CME      | 000200 | CONTROL MODE, ESCAPE BIT SET                                     |  |  |  |  |  |

| CML      | 740002 | COMPLEMENT LINK                                                  |  |  |  |  |  |

| CRR      | 703161 | CLEAR RELAY REGISTER                                             |  |  |  |  |  |

| CSI      | 000010 | CONTROL MODE, INTENSITY BIT SET                                  |  |  |  |  |  |

| CSS      | 000100 | CONTROL MODE, SCALE BIT SET                                      |  |  |  |  |  |

| DAC      | 040000 | DEPOSIT IN AC/FROM ADDRESS                                       |  |  |  |  |  |

| DCA      | 700604 | DISPLAY CLEAR ADDRESS COUNTER                                    |  |  |  |  |  |

| DCE      | 703302 | DISPLAY CLEAR EDGE FLAGS                                         |  |  |  |  |  |

| DCF      | 700704 | DISPLAY CLEAR FLAGS                                              |  |  |  |  |  |

| DCL      | 702701 | DISPLAY CLEAR 340 LOCKOUT                                        |  |  |  |  |  |

| DCM      | 000000 | DISPLAY CONTROL MODE/SETS MODE BITS TO CONTROL MODE              |  |  |  |  |  |

| DCS      | 702601 | DISPLAY CLEAR SAVE REGISTER                                      |  |  |  |  |  |

| DDS      | 200000 | DEPOSIT DISPLAY SAVE REGISTER/IN ADDRESS                         |  |  |  |  |  |

| DGI      | 702204 | DISALLOW GENERATOR INTERRUPT/DISALLOW INTERRUPT FROM 160         |  |  |  |  |  |

| DHI      | 003000 | DISPLAY HALT AND INTERRUPT                                       |  |  |  |  |  |

| DHQ      | 002000 | DISPLAY HALT QUIETLY/WITHOUT INTERRUPT                           |  |  |  |  |  |

| DIM      | 140000 | DISPLAY INCREMENT MODE/SETS MODE BITS TO INCREMENT MODE          |  |  |  |  |  |

| DJP      | 400000 | DISPLAY JUMP/TO SUBROUTINE                                       |  |  |  |  |  |

### TABLE 2-2PDP-4/340 INSTRUCTIONS

# TABLE 2-2 PDP-4/340 INSTRUCTIONS (continued)

| Mnemonic | Octal  | Name/Remarks                                                                   |  |  |  |  |  |

|----------|--------|--------------------------------------------------------------------------------|--|--|--|--|--|

| DJS      | 600000 | DISPLAY JUMP AND SAVE/DISPLAY JUMP TO SUBROUTINE                               |  |  |  |  |  |

| DLA      | 700606 | DISPLAY LOAD ADDRESS COUNTER AND START DISPLAY                                 |  |  |  |  |  |

| DLS      | 702603 | DISPLAY LOAD ADDRESS SAVE REGISTER                                             |  |  |  |  |  |

| DNP      | 000000 | DISPLAY NO OPERATION                                                           |  |  |  |  |  |

| DPI      | 700004 | DISALLOW PERIODIC INTERRUPTS                                                   |  |  |  |  |  |

| DPM      | 020000 | DISPLAY POINT MODE/SETS MODE BITS TO POINT MODE                                |  |  |  |  |  |

| DRA      | 700512 | DISPLAY READ ADDRESS COUNTER AND STOP                                          |  |  |  |  |  |

| DRP      | 702712 | DISPLAY READ PARAMETERS                                                        |  |  |  |  |  |

| DRS      | 700504 | DISPLAY RESUME/FAMILY OF EIGHT                                                 |  |  |  |  |  |

| DRX      | 702512 | DISPLAY READ X COORDINATE                                                      |  |  |  |  |  |

| DRY      | 702514 | DISPLAY READ Y COORDINATE                                                      |  |  |  |  |  |

| DSI      | 700601 | DISPLAY SKIP ON INTERRUPT FLAG AND CLEAR                                       |  |  |  |  |  |

| DSK      | 000400 | DISPLAY SKIP                                                                   |  |  |  |  |  |

| DSP      | 700701 | DISPLAY SKIP ON LIGHT PEN FLAG AND CLEAR                                       |  |  |  |  |  |

| DSQ      | 002000 | DISPLAY STOP QUIETLY/WITHOUT INTERRUPT                                         |  |  |  |  |  |

| DSR      | 702614 | DISPLAY READ SAVE REGISTER                                                     |  |  |  |  |  |

| DSS      | 702501 | DISPLAY SKIP ON STOP INTERRUPT                                                 |  |  |  |  |  |

| DSX      | 700501 | DISPLAY SKIP ON X EDGE                                                         |  |  |  |  |  |

| DSY      | 703301 | DISPLAY SKIP ON Y EDGE                                                         |  |  |  |  |  |

| DVC      | 120000 | DISPLAY VECTOR CONTINUE MODE/SETS MODE BITS TO VECTOR CONTINUE MODE            |  |  |  |  |  |

| DVM      | 100000 | DISPLAY VECTOR MODE/SETS MODE BITS TO VECTOR MODE                              |  |  |  |  |  |

| DZM      | 140000 | DEPOSIT ZERO IN MEMORY/AT ADDRESS                                              |  |  |  |  |  |

| GLK      | 750010 | GET LINK                                                                       |  |  |  |  |  |

| HLT      | 740040 | HALT                                                                           |  |  |  |  |  |

| IGI      | 702441 | SET GENERATOR'S INPUT INTERRUPT, FLAG I/1604 INPUT CHANNEL<br>INTERRUPT FLAG   |  |  |  |  |  |

| IGO      | 702442 | SET GENERATOR'S OUTPUT INTERRUPT, FLAG O/1604 OUTPUT<br>CHANNEL INTERRUPT FLAG |  |  |  |  |  |

| IGP      | 702242 | SET GENERATOR'S PERMIT INTERRUPT FLAG P/1604 INTERRUPT<br>PERMIT FLAG          |  |  |  |  |  |

| IOF      | 700002 | TURN OFF INTERRUPT                                                             |  |  |  |  |  |

| ION      | 700042 | TURN ON INTERRUPT                                                              |  |  |  |  |  |

| IOT      | 700000 | BASIC INPUT-OUTPUT INSTRUCTION                                                 |  |  |  |  |  |

| ISZ      | 440000 | INDEX AND SKIP IF 0                                                            |  |  |  |  |  |

| JMP      | 600000 | JUMP                                                                           |  |  |  |  |  |

| JMS      | 100000 | JUMP TO SUBROUTINE                                                             |  |  |  |  |  |

| LAC      | 200000 | LOAD AC                                                                        |  |  |  |  |  |

| LAM      | 000000 | /USED IN DEC DISTRIBUTED PROGRAMS                                              |  |  |  |  |  |

| LAS      | 750004 | LOAD AC FROM SWITCHES                                                          |  |  |  |  |  |

| LAW      | 760000 | LOAD AC WITH THIS INSTRUCTION/INCLUDING ADDRESS                                |  |  |  |  |  |

| LGA      | 702303 | LOAD GENERATOR'S ADDRESS COUNTER                                               |  |  |  |  |  |

| LL1      | 703105 | CLEAR AND LOAD LIGHTS IN BUTTONS OF RB1/ NUMBERS 1-18                          |  |  |  |  |  |

| Mnemonic    | Octal  | Name/Remarks                                                          |  |  |  |  |  |

|-------------|--------|-----------------------------------------------------------------------|--|--|--|--|--|

| LL2         | 703125 | /CLEAR AND LOAD LIGHTS IN BUTTONS OF RB2, NUMBERS 19-36               |  |  |  |  |  |

| LL3         | 703144 | /CLEAR AND LOAD LIGHTS IN BUTTONS OF RB3/INSTRUCTIONS                 |  |  |  |  |  |

| LRR         | 703165 | LOAD RELAY REGISTER/BIT 17 CLEARS THE RELAY REGISTER                  |  |  |  |  |  |

| NOP         | 740000 | NO OPERATION                                                          |  |  |  |  |  |

| OAS         | 740004 | INCLUSIVE OR AC AND SWITCHES                                          |  |  |  |  |  |

| OPR         | 740000 | OPERATE                                                               |  |  |  |  |  |

| POF         | 010000 | LIGHT PEN OFF                                                         |  |  |  |  |  |

| PON         | 014000 | LIGHT PEN ON                                                          |  |  |  |  |  |

| RAL         | 740010 | ROTATE AC AND LINK LEFT ONE PLACE                                     |  |  |  |  |  |

| RAR         | 740020 | ROTATE AC AND LINK RIGHT ONE PLACE                                    |  |  |  |  |  |

| RB1         | 703112 | READ BUTTON BANK 1/NUMBERS 1-18                                       |  |  |  |  |  |

| RB2         | 703132 | READ BUTTON BANK 2/NUMBERS 19-30                                      |  |  |  |  |  |

| RB3         | 703152 | READ BUTTON BANK 3/INSTRUCTION                                        |  |  |  |  |  |

| RB4         | 703172 | READ BUTTON BANK 4/SPECIAL FUNCTION BUTTONS                           |  |  |  |  |  |

| RB5         | 703212 | READ BUTTON BANK 5/0-9, A-H                                           |  |  |  |  |  |

| R <b>B6</b> | 703232 | READ BUTTON BANK 6/1-Z                                                |  |  |  |  |  |

| RCF         | 700102 | CLEAR THE READER FLAG                                                 |  |  |  |  |  |

| RCL         | 744010 | CLEAR LINK THEN RAL                                                   |  |  |  |  |  |

| RCR         | 744020 | CLEAR LINK THEN RAR                                                   |  |  |  |  |  |

| RGA         | 702314 | READ GENERATOR'S ADDRESS COUNTER                                      |  |  |  |  |  |

| RIF         | 702414 | READ 8 INTERFACE FLAGS                                                |  |  |  |  |  |

| RKN         | 703256 | READ KNOBS 1, 2, AND 3 AND CLEAR FLAG/BIT 15 CLEARS KNOB<br>REGISTERS |  |  |  |  |  |

| RRB         | 700112 | READ READER BUFFER INTO AC, CLEAR READ FLAG                           |  |  |  |  |  |

| RSA         | 700104 | SELECT READER FOR ALPHANUMERIC, CLEAR RDR FLAG                        |  |  |  |  |  |

| RSB         | 700144 | SELECT READER FOR BINARY, CLEAR READER FLAG                           |  |  |  |  |  |

| RSF         | 700101 | SKIP ON READER FLAG                                                   |  |  |  |  |  |

| RSR         | 700314 | READ STATUS OF IO EQUIPMENT                                           |  |  |  |  |  |

| RTB         | 703276 | READ TRACK BALL AND CLEAR FLAG/BIT 15 CLEARS TRACK BALL<br>REGISTER   |  |  |  |  |  |

| RTL         | 742010 | ROTATE AC LEFT TWICE                                                  |  |  |  |  |  |

| RTR         | 742020 | ROTATE AC RIGHT TWICE                                                 |  |  |  |  |  |

| SAD         | 540000 | SKIP IF AC AND Y ARE DIFFERENT                                        |  |  |  |  |  |

| SGI         | 702201 | /INTERFACE INTERRUPT SKIP ON GENERATOR INTERRUPT/                     |  |  |  |  |  |

| SGP         | 702242 | SET PDP-4 INTERFACE INTERRUPT FLAG/FLAG P                             |  |  |  |  |  |

| SKO         | 703201 | SKIP ON KNOB OVERFLOW                                                 |  |  |  |  |  |

| SKP         | 741000 | SKIP ALWAYS                                                           |  |  |  |  |  |

| SMA         | 740100 | SKIP ON MINUS AC/NEGATIVE                                             |  |  |  |  |  |

| SNA         | 741200 | SKIP ON NON-ZERÓ AC                                                   |  |  |  |  |  |

| SNL         | 740400 | SKIP ON NON-ZERO LINK                                                 |  |  |  |  |  |

| SPA         | 741100 | SKIP ON POSITIVE AC                                                   |  |  |  |  |  |

| SPI         | 700001 | SKIP ON PERIODIC INTERRUPT                                            |  |  |  |  |  |

# TABLE 2-2 PDP-4/340 INSTRUCTIONS (continued)

. . . . . . .

| Mnemonic | Octal  | Name/Remarks                       |

|----------|--------|------------------------------------|

| SPL      | 741400 | /USED IN DEC DISTRIBUTED ROUTINES  |

| SRF      | 700101 | SKIP ON READER FLAG                |

| STL      | 744002 | SET THE LINK                       |

| SZA      | 740200 | SKIP ON ZERO AC                    |

| SZL      | 741400 | skip on zero link                  |

| TAD      | 340000 | TWOS COMPLEMENT ADD/ADDRESS AND AC |

| XCT      | 400000 | EXECUTE INSTRUCTION IN ADDRESS     |

| XFL      | 002000 | POSITION X AND FLASH               |

| XNF      | 000000 | POSITION X AND DON'T FLASH         |

| XOR      | 240000 | EXCLUSIVE OR/ADDRESS WITH AC       |

| YFL      | 202000 | POSITION Y AND FLASH               |

| YNF      | 200000 | POSITION Y AND DON'T FLASH         |

| ZRO      | 000000 | ZERO                               |

TABLE 2-2 PDP-4/340 INSTRUCTIONS (continued)

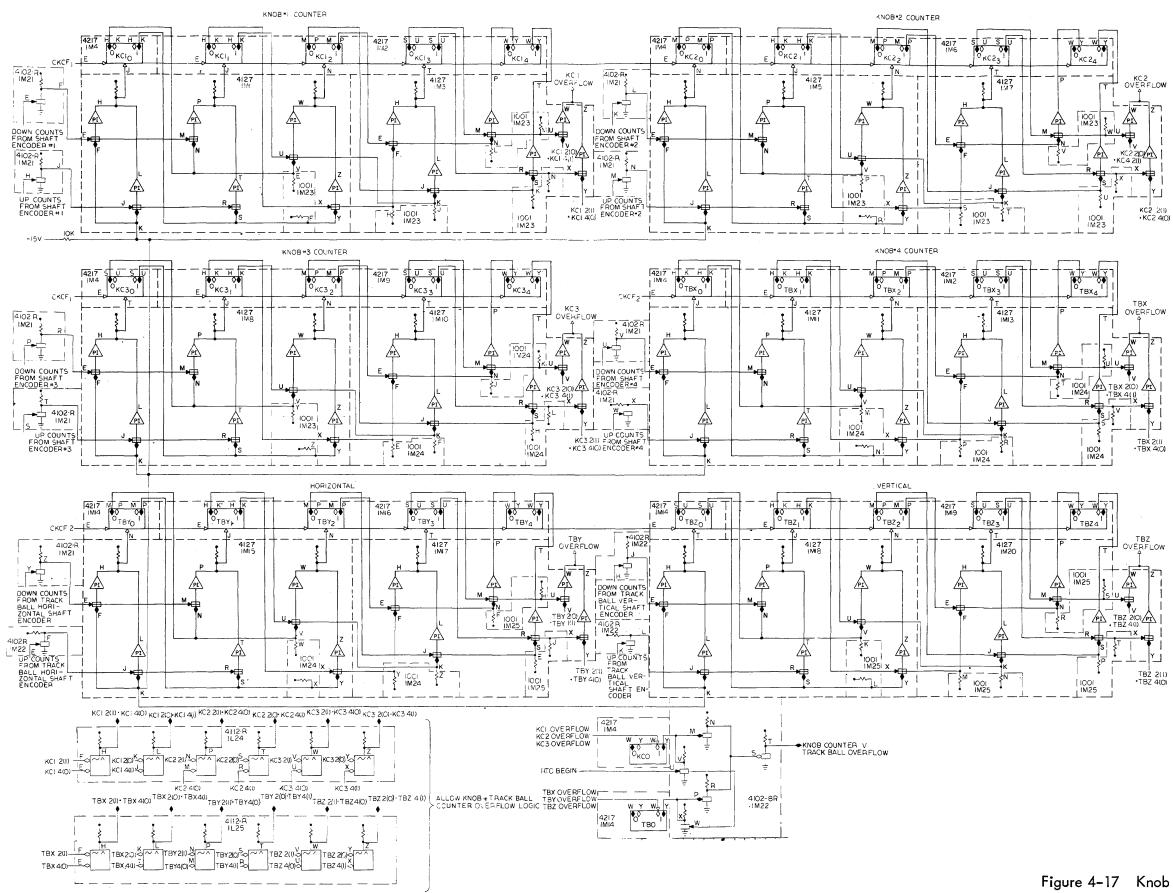

#### Knob and Track Ball Counters

It is possible for the knob or track ball counters to overflow after the interrupt generated when  $\pm 8$  was reached and before the interrupt program can read and reset the counters. However, the sign bit is still valid for an additional count of 8 so the programmer can obtain some data if this event occurs. The counting sequence is given in Table 2-3.

| ign | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Value | Comments |

|-----|-------|-------|-------|-------|-------|----------|

TABLE 2-3 KNOB AND TRACK BALL COUNTING SEQUENCE

| Sign | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Value | Comments             |

|------|-------|-------|-------|-------|-------|----------------------|

|      | ^     |       |       |       |       |                      |

|      | 0     | 0     | 0     | 0     | +16   | Next clockwise count |

| 0    | 1     | ]     | 1     | 1     | +15   |                      |

| 0    | 1     | 1     | 1     | 0     | +14   |                      |

| 0    | 1     | 1     | 0     | 1     | +13   |                      |

| 0    | 1     | 1     | 0     | 0     | +12   | Clockwise Counts     |

| 0    | 1     | 0     | 1     | 1     | +11   | Clockwise Counts     |

| 0    | 1     | 0     | 1     | 0     | +10   |                      |

| 0    | 1     | 0     | 0     | 1     | + 9   |                      |

| 0    | 1     | 0     | 0     | 0     | + 8   |                      |

| 0    | 0     | 1     | 1     | 1     | + 7   | <u>}</u>             |

| Sign | Bit 1 | Bit 2 | Bit 3 | Bit 4 | Value | Comments                     |

|------|-------|-------|-------|-------|-------|------------------------------|

| 0    | 0     | 1     |       | 0     | + 6   | <u>`</u>                     |

| 0    | 0     | 1     | 0     | 1     | + 5   |                              |

| 0    | 0     | 1     | Õ     | 0     | + 4   |                              |

| 0    | 0     | 0     | -     | ' 1   | + 3   | Clockwise Counts             |

| 0    | Ō     | Ō     | Ì     | 0     | + 2   |                              |

| 0    | 0     | 0     | 0     | 1     | + 1   | ) ·                          |

| 0    | 0     | 0     | 0     | 0     | 0     | (cleared to this value)      |

| 1    | 1     | 1     | 1     | 1     | - 1   |                              |

| 1    | 1     | 1     | 1     | Ó     | - 2   |                              |

| 1    | 1     | 1     | 0     | 1     | - 3   |                              |

| 1    | 1     | 1     | 0     | 0     | - 4   |                              |

| 1    | 1     | 0     | 1     | 1     | - 5   |                              |

| 1    | 1     | 0     | 1     | 0     | - 6   |                              |

| 1    | 1     | 0     | 0     | 1     | - 7   |                              |

| 1    | 1     | 0     | 0     | 0     | - 8   | Counterclockwise Counts      |

| 1    | 0     | 1     | 1     | 1     | - 9   | (                            |

| 1    | 0     | 1     | 1     | 0     | -10   |                              |

| 1    | 0     | 1     | 0     | 1     | -11   |                              |

| 1    | 0     | 1     | 0     | 0     | -12   |                              |

| . 1  | 0     | 0     | 1     | 1     | -13   |                              |

| 1    | 0     | 0     | 1     | 0     | -14   |                              |

| 1    | 0     | 0     | 0     | 1     | -15   |                              |

| 1    | 0     | 0     | 0     | 0     | -16   | J                            |

| 1    | 1     | 1     | 1     | 1     | -17   | Next counter clockwise count |

TABLE 2-3 KNOB AND TRACK BALL COUNTING SEQUENCE (continued)

#### Sample Interruption Saving Program

When it is desired to interrupt the 340's background program to flash a short message and then to return to the main program at the point of interruption, it is necessary that the interrupting program have the ability to restore the conditions of the various registers in the 340. A basic program which allows the interrupting routine to save the contents of the important 340 registers and then to restore these register is as follows:

| (Saving Routine:)                                   |                                                                       |  |  |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|--|

| DSR                                                 | /READ SAVE REGISTER                                                   |  |  |  |  |  |

| DAC SAVE<br>DRA<br>DAC JUMP<br>DRP<br>DAC GO<br>DRY | /READ DISPLAY ADDRESS COUNTER AND SET 340 LOCKOUT                     |  |  |  |  |  |

|                                                     | /READ DISPLAY PARAMETERS                                              |  |  |  |  |  |

|                                                     | /READ DISPLAY Y COORDINATE                                            |  |  |  |  |  |

| DAC GO+1<br>DRX                                     | /READ DISPLAY X COORDINATE                                            |  |  |  |  |  |

| DAC GO+2                                            | •••                                                                   |  |  |  |  |  |

| Interrupting Message                                |                                                                       |  |  |  |  |  |

| ( <u>Restoring Routine:</u> )                       | •••                                                                   |  |  |  |  |  |

| LAW GO                                              |                                                                       |  |  |  |  |  |

| DLA<br>DCL                                          | /LOAD DISPLAY ADDRESS COUNTER AND START DISPLAY<br>/RESET 340 LOCKOUT |  |  |  |  |  |

| DSS<br>JMP1                                         | WAIT FOR DISPLAY TO STOP                                              |  |  |  |  |  |

| LAC SAVE                                            | , , , , , , , , , , , , , , , , , , ,                                 |  |  |  |  |  |

| D LS<br>DRS+20000                                   | /LOAD DISPLAY SAVE REGISTER ACCORDING TO AC                           |  |  |  |  |  |

| (Display File:)                                     |                                                                       |  |  |  |  |  |

| GO,                                                 | /STORAGE LOCATION FOR PARAMETER INFORMATION                           |  |  |  |  |  |

| GO+1,                                               | STORAGE LOCATION FOR Y COORDINATE INFORMATION                         |  |  |  |  |  |

| GO+2,                                               | STORAGE LOCATION FOR X COORDINATE INFORMATION                         |  |  |  |  |  |

| GO+3,                                               | /DISPLAY HALT                                                         |  |  |  |  |  |

| JUMP,                                               | /STORAGE LOCATION FOR DAC CONTENTS. WILL BE EXECUTED /AS DJP (DAC)    |  |  |  |  |  |

| SAVE                                                | STORAGE LOCATION FOR CONTENTS OF SAVE REGISTER                        |  |  |  |  |  |

ş

#### SECTION 3

#### MAINTENANCE

In any complicated logic system which includes a digital computer, it is useless to attempt to list all the possible problems which might occur and their probable causes. However, efficient maintenance is still possible, because all malfunctions are either caused by operator error or equipment failure. Operator error, which includes programming bugs, is by far the most common. Complete familiarity with the system minimizes this source of trouble.

Equipment failures fall into three catagories: mechanical; power; and logic. A mechanical failure is due either to misadjustment, wear, or breakdown. These failures can almost always be spotted by a visual check of the equipment or by operation of the equipment. Power failures are caused either by no power or the wrong power, or else by a condition which causes the regulation and filtering of the power supplies to exceed their specifications. The former cases are usually due either to the main switch on the power supply being turned off or to a marginal voltage switch on some rack being thrown to the marginal (up) position. The latter case usually indicates either to o great a load on the power supply (as a low-resistance short), or not enough load (such as some circuits not connected). A logic failure is a failure of a logical circuit to operate in its normal manner. It is usually caused by a bad component or connection in a module. This may be a random failure, but is usually caused by aging.

An equipment failure can be found by a method based on thorough understanding of the system's operation, common sense and logical thinking, and an organized step-by-step procedure. If a mechanical failure is suspected, a thorough visual check of the equipment should be made first. Then, if no more danger to the equipment will result, an operational check should be made. The only complicated mechanical equipment in this system is the perforated tape reader. Procedures for adjusting this equipment are given in Paragraph 11-4 (d) of the PDP-4 Mainten-ance Manual and the perforated tape reader maintenance manual. Equipment power failures can usually be found by oscilloscope checking of the power supply to each rack. Logical failures of the equipment are most easily found by using a repetitive diagnostic program loop to exercise the desired function or operation, and tracing the signal path through the circuits

of the equipment with an oscilloscope. Special attention should be paid to noise and extra signals, or to signals whose timing is wrong. If a signal is found to be missing, the input to that circuit should be investigated both for amplitude and duration. A marginal voltage check should be made to determine if the preceding circuit is a causative or aiding agent of the failure.

The operation of the vast majority of this system is covered in the PDP-4, 340, and 370 maintenance manuals. The operation of the standard options, modifications of the standard equipment, and the special equipment is given later in this section. An explanation of each MAINDEC program is given in the associated MAINDEC manual. With this information it should be possible to set up any repetitive testing loop program to check any part of this system. As an additional aid in maintaining this system, two special test cables are provided which allow the light buffers and pushbutton groups to simulate the operation of the 1604A.

#### PREVENTIVE MAINTENANCE

The best way to insure troublefree operation is to locate and correct all potential failures before they occur in normal operation. This can be done by running a MAINDEC or other diagnostic test program in the system and/or operating various portions of the equipment under marginal voltage conditions until a failure occurs. When this is done routinely and a record kept of the voltages at which failures occur, it is possible to note any progressive deterioration due to aging. Any particular circuit or module which may later cause a failure is often noticed by a steadily decreasing margin voltage. Replacement of the module and/or correction of the aging component is indicated when such a long-term drift is detected, even though the margin at which failure occurs has not exceeded normal limits.

> NOTE: Before attempting to replace any module with a spare, check to see if the module has any jumpers or adjustments. Modules which have jumpers can only be replaced with similar modules with the same jumper connections. Modules which have adjustments require that these be set for the same operating conditions as the replaced module.

page missing from original document

When the switch is in the up position, it connects the associated terminals on its rack to the output of a 734 Power Supply located at the top of the plenum door behind bay 1 of the PDP-4. The 734 supplies power between 0 and ±20 volts dc, as shown on its voltmeter. The polarity of this voltage is determined by the MARGINAL CHECK switch. This switch must be in the +10 MC position when marginal checking either a +10 volt A or a +10 volt B line, and in the -15 MC position when checking the -15 volt C line. When this switch is in the OFF position, normal voltages are applied to all three lines in every panel, regardless of the setting of the marginal voltage switches on the panels.

Raising the bias voltage above +10 volts increases the cutoff bias that must be overcome by the previous driving transistor, causing low-gain transistors to fail. Lowering the bias voltage below +10 volts reduces the transistor base bias at noise rejection and thus provides a test to provide high-leakage transistors and stimulates high temperature conditions (to check for thermal runaway). All Digital modules should operate normally when the +10 volt bias varies by more than ±5 volts (unless there is exceptional noise on the line).

Since the -15 volt supply is the collector load voltage (which is clamped at -3 volts in most modules), raising and lowering this source has little effect upon the logic circuits. Therefore, the -15 volt marginal testing is only done on pulse amplifiers and other equipment which produces pulses through a pulse transformer. Raising and lowering the -15 volt supply increases and decreases the output pulse, respectively. These modules should operate normally with the -15 volts varying between -8 and -18 volts.

#### CAUTION

Do not increase the -15 volt supply beyond -18 volts. Damage to the electronic circuit may result if this voltage exceeds -18 volts.

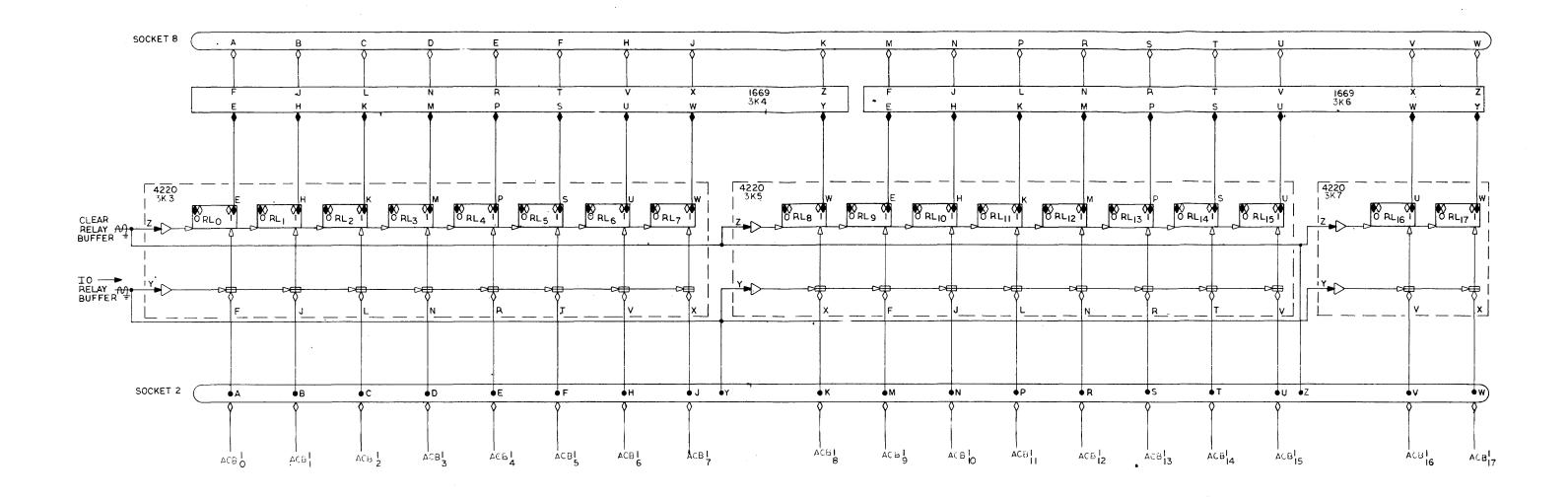

#### 1604A Simulation

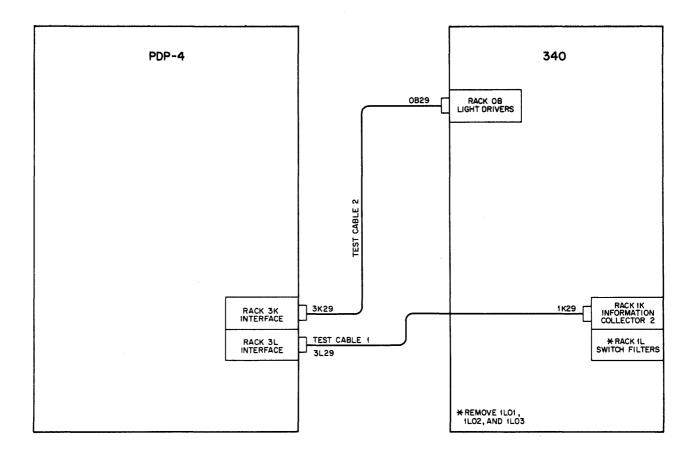

As an aid in maintaining this system, two special test cables are supplied which allow the PDP-4 to simulate the output signals from the 1604A and to test the response of the interface electronic circuits to these signals. When using these test cables, the four cables from the 1604A are removed, and a diagnostic test program is run by the PDP-4. The only part of the

interface equipment not tested is the Digital  $\rightarrow$  CDC level converting portion. This may be checked with a dc voltmeter or oscilloscope directly on the pins of 2MB, 2MC 2MF.

NOTE: Type 1703 Switch Filters located in 1L01, 1L02, and 1L03 in the display must be removed when performing the simulation tests.

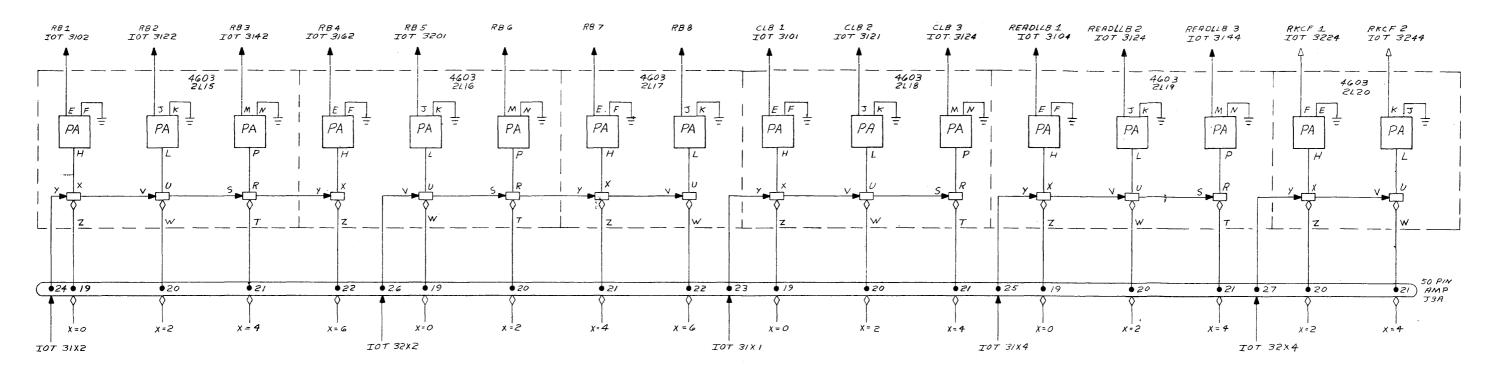

Test cable 1 connects the input signals of the Digital  $\rightarrow$  CDC level converters to the conditioning level inputs of the remote information collector 2, as shown in Figure 3-2. Plug 3L29 is connected to the jack at the right rear of rack 3L in the PDP-4 and plug 1K29 is connected to the jack at the right rear of rack 1K in the 340. Jack 1K29 is connected to the remote information collector 2 in parallel with the inputs from the group of 36 pushbuttons. The IOT 703102 (read button group 1) inclusive ORs the simulated 1604A input data bits with the contents of the accumulator, and IOT 703122 (read button group 2) inclusive ORs the simulated 1604A input sense response bits with the contents of the accumulator. Table 3-1 lists the bit allocations for these simulated functions.

| "read pushbutton group 1"<br>IOT 703102 |                    | "re    | "read pushbutton group 2"<br>IOT 703122         |  |  |

|-----------------------------------------|--------------------|--------|-------------------------------------------------|--|--|

| AC Bit                                  | Simulated Function | AC Bit | Simulated Function                              |  |  |

| 0                                       | Input Data Bit 17  | 0      | Not Used                                        |  |  |

| 1                                       | Input Data Bit 16  | 1      | Not Used                                        |  |  |

| 2                                       | Input Data Bit 15  | 2      | Sense Response                                  |  |  |

| 3                                       | Input Data Bit 14  | 3      | Output Data Resume                              |  |  |

| 4                                       | Input Data Bit 13  | 4      | Input Interrupt and All on<br>Input Interrupt   |  |  |

| 5                                       | Input Data Bit 12  | 5      | Output Interrupt and All<br>on Output Interrupt |  |  |

| 6                                       | Input Data Bit 11  | 6      | Not Used                                        |  |  |

| 7                                       | Input Data Bit 10  | 7      | Input Data Ready                                |  |  |

| 8                                       | Input Data Bit 9   | 8      | Not Used                                        |  |  |

| 9                                       | Input Data Bit 8   | 9      | Not Used                                        |  |  |

TABLE 3-1 SIMULATED 1604A INPUT SIGNAL BIT ASSIGNMENTS

| "read pushbutton group 1"<br>IOT 703102 |                    | "read pushbutton group 2"<br>IOT 703122 |                    |  |

|-----------------------------------------|--------------------|-----------------------------------------|--------------------|--|

| AC Bit                                  | Simulated Function | AC Bit                                  | Simulated Function |  |

| 10                                      | Input Data Bit 7   | 10                                      | Not Used           |  |

| 11                                      | Input Data Bit 6 , | 11                                      | Not Used           |  |

| 12                                      | Input Data Bit 5   | 12                                      | Not Used           |  |

| 13                                      | Input Data Bit 4   | 13                                      | Not Used           |  |

| 14                                      | Input Data Bit 3   | 14                                      | Not Used           |  |

| 15                                      | Input Data Bit 2   | 15                                      | Not Used           |  |

| 16                                      | Input Data Bit 1   | 16                                      | Not Used           |  |

| 17                                      | Input Data Bit 0   | 17                                      | Not Used           |  |

TABLE 3-1 SIMULATED 1604A INPUT SIGNAL BIT ASSIGNMENTS (continued)

Figure 3–2 1604A Simulation Block Diagram

Test cable 2 connects the outputs of the three light driver registers to the inputs of the CDC  $\rightarrow$  Digital level converters. The signals from the light drivers are ground or -15 volts instead of -0.5 or -16 volts, so these circuits receive slightly attenuated simulated inputs. Plug 0B29 is connected to the jack at the right rear of rack 0B in the 340, and plug 3L29 is connected to the jack at the right rear of rack 3L in the PDP-4. IOT 703105 (clear and load light buffer 1) transfers a word from the accumulator into light driver register 1, simulating the 1604A output data bits. IOT 703125 (clear and load light buffer 2) transfers another word from the accumulator into light driver register 2, simulating the 1604A output sense levels and data bit 18. IOT 703145 (clear and load light buffer 3) transfers a third word from the accumulator into light driver register 3, simulating the 1604A function bits. Table 3-2 lists the bit allocations for the simulated function.

| "clear and load<br>light buffer 1"<br>IOT 703105 |                    | "clear and load<br>light buffer 2"<br>IOT 703125 |                       | "clear and load<br>light buffer 3"<br>IOT 703145 |                    |

|--------------------------------------------------|--------------------|--------------------------------------------------|-----------------------|--------------------------------------------------|--------------------|

| Bit                                              | Simulated Function | Bit                                              | Simulated Function    | Bit                                              | Simulated Function |

| 0                                                | Output Data Bit 17 | 0                                                | Master Clear          | 0                                                | Not Used           |

| 1                                                | Output Data Bit 16 | 1                                                | Output Function Ready | 1                                                | Not Used           |

| 2                                                | Output Data Bit 15 | 2                                                | Output Sense Ready    | 2                                                | Not Used           |

| 3                                                | Output Data Bit 14 | 3                                                | Output Data Ready     | 3                                                | Not Used           |

| 4                                                | Output Data Bit 13 | 4                                                | Input Function Ready  | 4                                                | Not Used           |

| 5                                                | Output Data Bit 12 | 5                                                | Input Sense Ready     | 5                                                | Not Used           |

| 6                                                | Output Data Bit 11 | 6                                                | Input Buffer Active   | 6                                                | Function Bit 11    |

| 7                                                | Output Data Bit 10 | 7                                                | Input Data Resume     | 7                                                | Function Bit 10    |

| 8                                                | Output Data Bit 9  | 8                                                | Not Used              | 8                                                | Function Bit 9     |

| 9                                                | Output Data Bit 8  | 9                                                | Not Used              | 9                                                | Function Bit 8     |

| 10                                               | Output Data Bit 7  | 10                                               | Not Used              | 10                                               | Function Bit 7     |

| 11                                               | Output Data Bit 6  | 11                                               | Not Used              | 11                                               | Function Bit 6     |

| 12                                               | Output Data Bit 5  | 12                                               | Not Used              | 12                                               | Function Bit 5     |

| 13                                               | Output Data Bit 4  | 13                                               | Not Used              | 13                                               | Function Bit 4     |

TABLE 3-2 SIMULATED 1604A OUTPUT SIGNAL BIT ASSIGNMENTS

| "clear and load<br>light buffer 1"<br>IOT 703105 |                    | "clear and load<br>light buffer 2"<br>IOT 703125 |                    | "clear and load<br>light buffer 3"<br>IOT 703145 |                    |

|--------------------------------------------------|--------------------|--------------------------------------------------|--------------------|--------------------------------------------------|--------------------|

| Bit                                              | Simulated Function | Bit                                              | Simulated Function | Bit                                              | Simulated Function |

| 14                                               | Output Data Bit 3  | 14                                               | Not Used           | 14                                               | Function Bit 3     |

| 15                                               | Output Data Bit 2  | 15                                               | Not Used           | 15                                               | Function Bit 2     |

| 16                                               | Output Data Bit 1  | 16                                               | Not Used           | 16                                               | Function Bit 1     |

| 17                                               | Output Data Bit 0  | 17                                               | Output Data Bit 18 | 17                                               | Function Bit 00    |

TABLE 3-2 SIMULATED 1604A OUTPUT SIGNAL BIT ASSIGNMENTS (continued)

#### **OPERATION OF EXTRA EQUIPMENT**

If any malfunction should occur in the logic portions of the system, a deductive reasoning approach is recommended to find the faulty circuit. This requires knowledge of how the various portions of the logical circuitry operate in order to compare the actual operation with the normal operation. When a discrepancy is found, the faulty circuit can be isolated and repairs made.

Most of the logical circuits in the general purpose experimental display are described in either the PDP-4, 340, or 370 maintenance manuals. Those which are not, are described in the following portion of this section. They are divided into the standard Digital options, modifications of the standard equipment normally in the PDP-4 and 340, and the special equipment used in this system.

#### **Standard Options**

#### Type 133 Data Interrupt Multiplexer

This standard option allows up to three external devices to have access to the PDP-4 core memory in order to receive data from or deliver data to the memory. The data transfer is directly to or from the memory buffer register (MB) to the input or output register of the external device, therefore none of the working registers of the PDP-4 are disturbed. The transfer of data takes one memory cycle from the PDP-4. Each device is assigned to a unique channel in the 133. The three external devices are set up in a priority network. The device attached to channel 0 has highest priority.

The external device must provide three things:

1. A signal denoting that the device is ready for a data transfer. This is a negative level, usually denoted as "data request" or "request for data", etc.

2. A signal to denote the desired direction of transfer (to or from memory in the PDP-4). An input device goes to memory, while an output device receives from memory. This is a negative level if the direction is toward the PDP-4. (It is not necessary for a device which only receives information to present this signal.)

3. A register of some sort to store the address of the desired PDP-4 memory location.

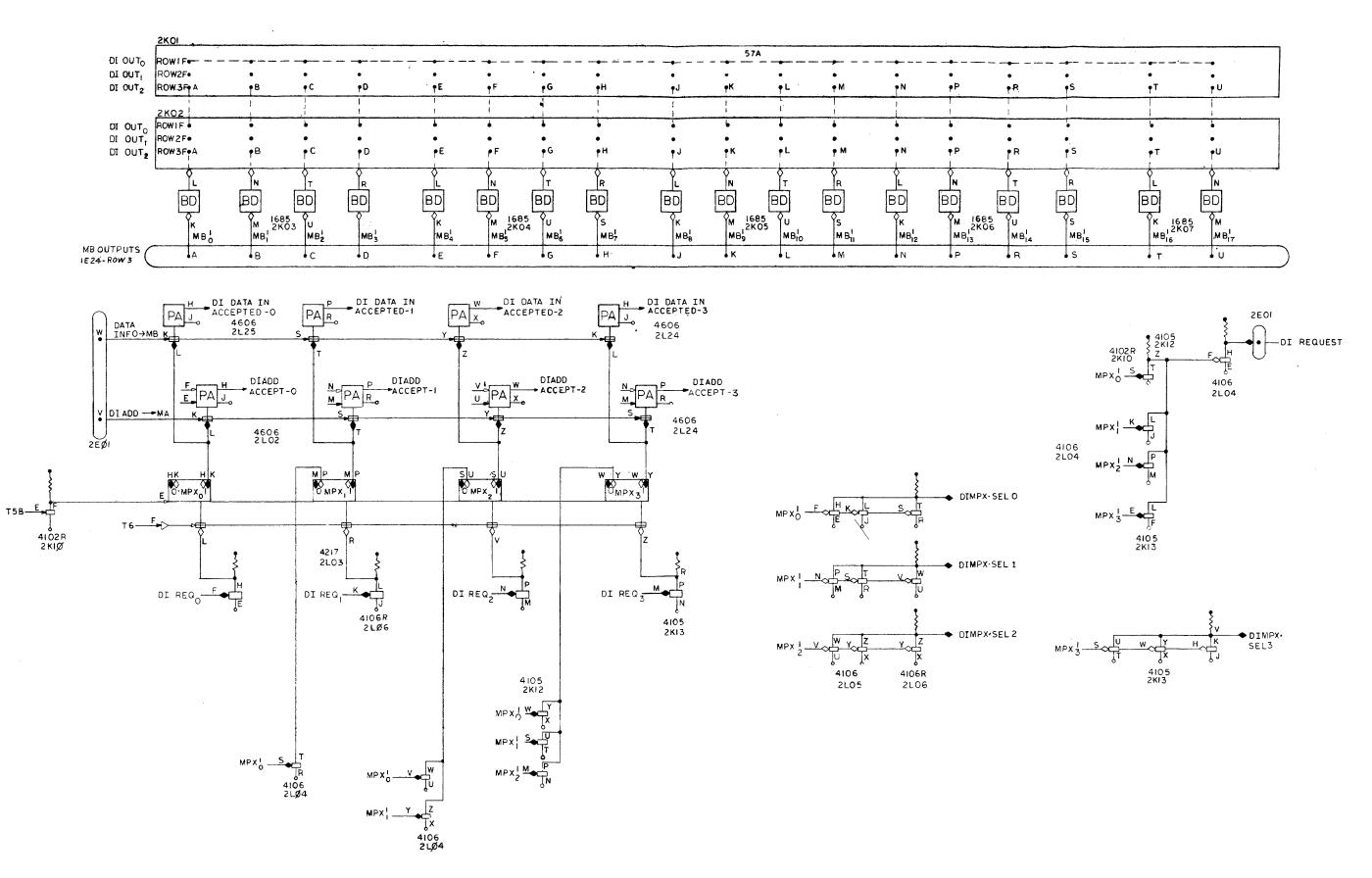

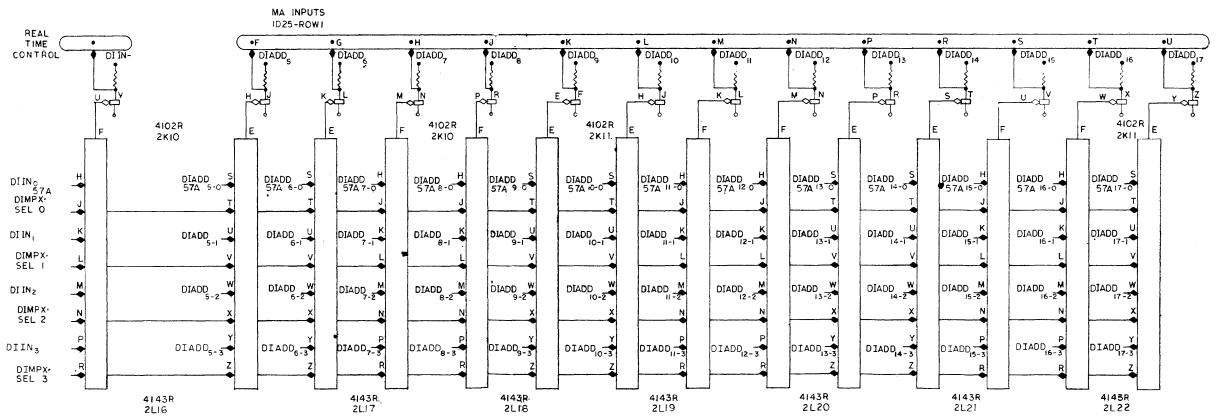

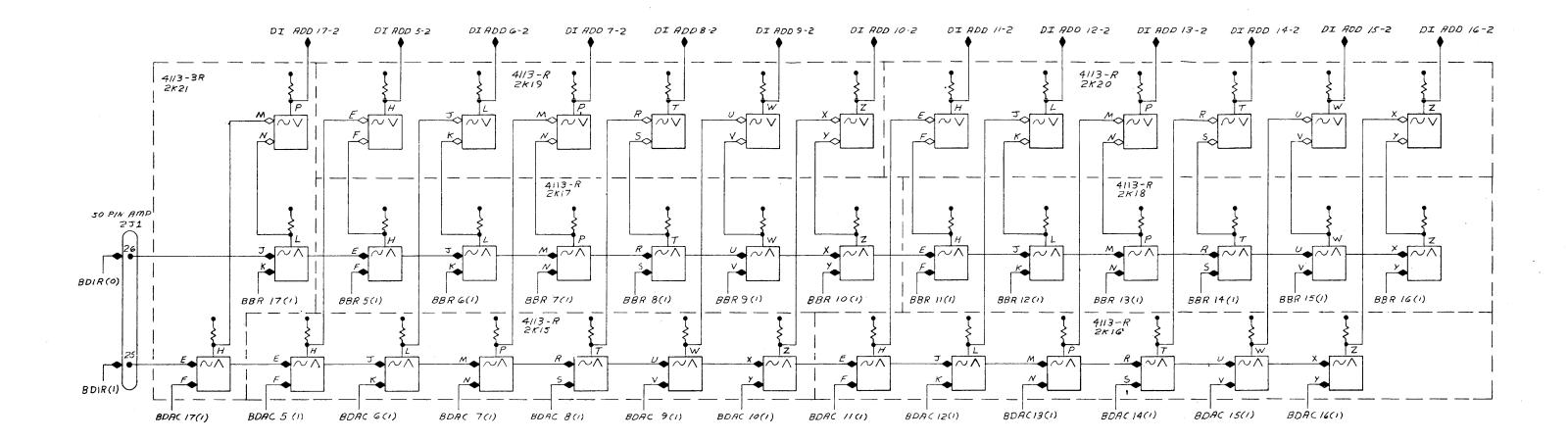

Example - An external device on channel 0 wishes to present a word to the PDP-4 memory. When the timing of this device says that conditions are proper for the transfer, the device produces a request for a data cycle. This negative level comes into Figure 4-1 (BS-D-133-0-2) at the lower left side. The data interrupt request signal, DI REQ<sub>0</sub>, turns on an inverter in 2L06, generating a ground level that enables the capacitor-diode gate at the 1 input of flipflop MPX<sub>0</sub>. Time pulse T6 then sets MPX<sub>0</sub> to the 1 state. It is possible that channels 1 and 2 also had requests at T6, but as soon as MPX<sub>0</sub> is set, it resets all lower priority MPX flipflops by the inverters in 2L04, bottom left, which constitute the priority chain. MPX<sub>0</sub> stays set until the PDP-4 is in a condition in which it recognizes data request (at the end of the instruction). The ground MPX<sub>0</sub> output is applied to three parallel inverters at right center, producing the output labeled DIMPX·SEL 0. The DI REQ<sub>0</sub> signal also cuts off an inverter at left center, producing the DI REQUEST signal.

This signal is applied to the data interrupt control at the upper left corner of Figure 4-2 (BS-D-125-0-1) (labeled 57A and DATA REQ). At time T5 this signal causes the data sync flip-flop to be set to its ONE state, applying a ground to a positive NOR gate at the center of

Figure 4-2. This produces a break request signal (BK RQ) that is sent to the major states section and produces the break cycle at time T7. When the break cycle flip-flop is set (-3 volt signal, B), the function DATA·B is produced by the negative NAND gate at the upper left corner.

At T1 of the following cycle the signal D1 ADD  $\rightarrow$  MA is produced, strobing the address information presented by the requesting channel into the memory address (MA) register of the PDP-4. This information is found on Figure 4-3 (BS-D-133-0-1), and labeled D1 ADD<sub>5-0</sub> through D1 ADD<sub>17-0</sub>. (The function D1MPX SEL zero gates the proper address information for the channel.) The D1 ADD  $\rightarrow$  MA pulse also goes to the left center of Figure 4-1 (BS-D-133-0-2); and, since MPX<sub>0</sub> is set to a 1, produces a signal called D1ADD ACCEPT-0, signifying to the external device that the PDP-4 has acknowledged its request and that the external device can now remove the request.

Since the external device is presenting information to the memory, a signal labeled DI IN-OUT<sub>0</sub> at the left center of Figure 4-1 (BS-D-133-0-2), is applied to the data interrupt section of the real time control. This signal (labeled DATA IN) is inverted at the left center of Figure 4-2 (BS-D-125-0-1), producing the DATA IN signal. The purpose of this level is to inhibit the strobing of the memory, since data is to be placed in memory. If DATA IN is ground and DATA  $\cdot$ B is also ground, the function DATA  $\cdot$ B  $\cdot$ DATA IN is produced, enabling a capacitor-diode gate in 2E18. At time T3 this gate is triggered, activating a pulse amplifier (PA) which produces the DATA INFO  $\rightarrow$  MB signal. This pulse transfers the information presented by the external device into the memory buffer (MB). This information is shown on top of Figure 4-3 (BS-D-133-0-1) as DI IN<sub>0-0</sub> through DI IN<sub>17-0</sub>. At time T5 the flip-flop MPX<sub>0</sub> is reset to 0.

If this had been an output device rather than an input device, the signal DI IN-OUT<sub>0</sub> would not have been produced, memory would have been strobed, and the external device would receive its data from the memory buffer bus drivers (BD) located on top of Figure 4-1 (BS-D-133-0-2).

#### Type 140 Relay Buffer and Control Register

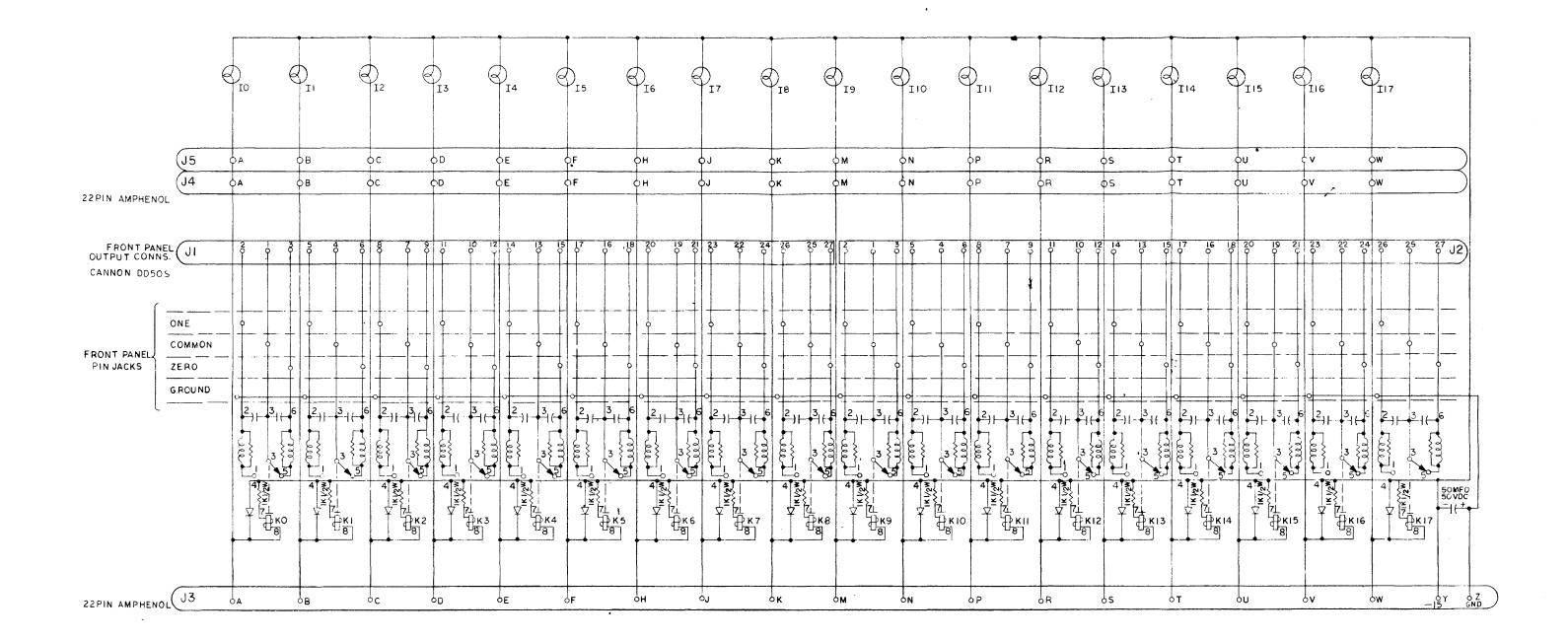

The relay buffer and control register are located in the PDP-4. The relay buffer, which consists of 18 single-pole double-throw relays, is located in rack J of bay 3. The control register, which consists of 18 unbuffered flip-flops, is located in part of rack K of bay 3. Figure 3-1 shows these items in the machine. The input and both outputs of each form "D" relay contact are available at two connectors on the back of the panel, and at test points on the front of the panel. Each output is filtered to smooth out contact bounce. A separate indicator light is wired in parallel with each relay coil and is on when the coil is energized. The 140 Relay Buffer is shown schematically in Figure 4-4 (BS-D-24903).

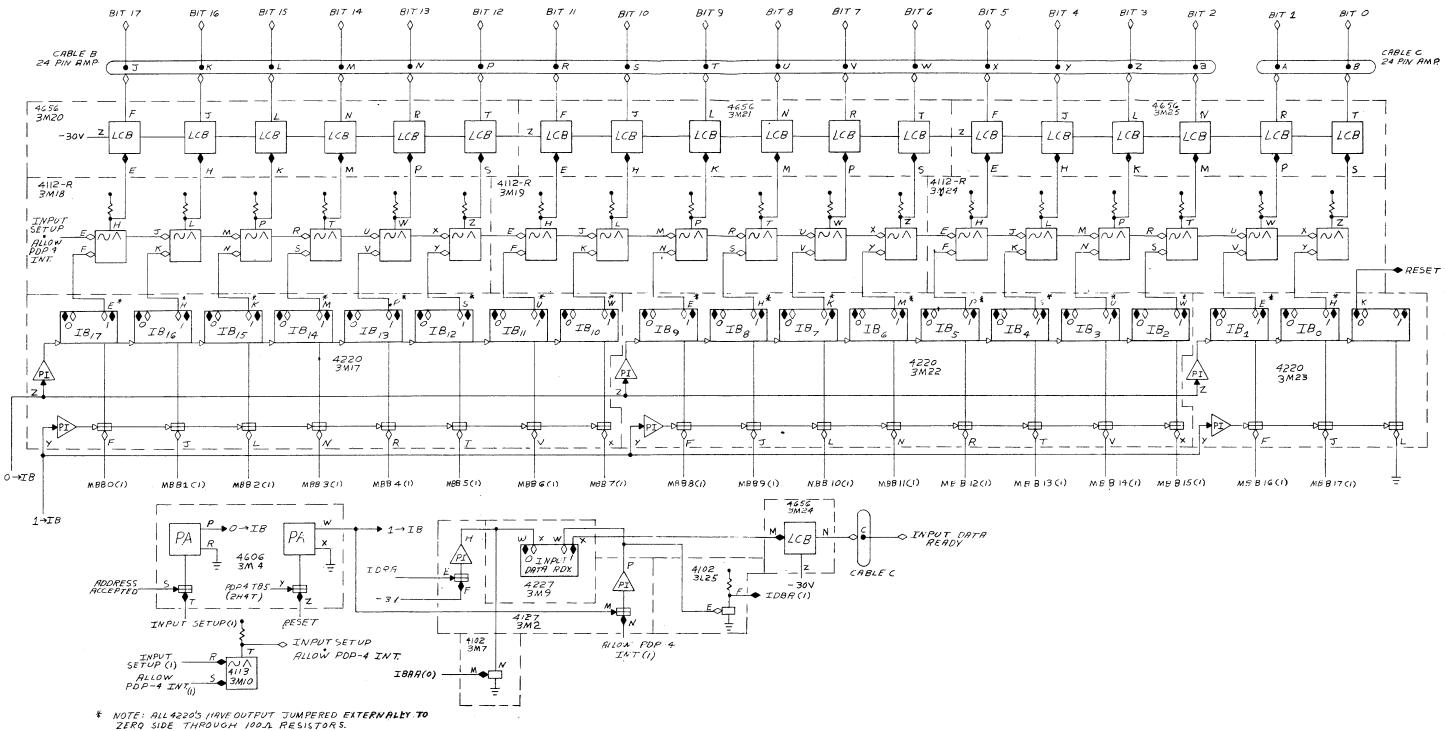

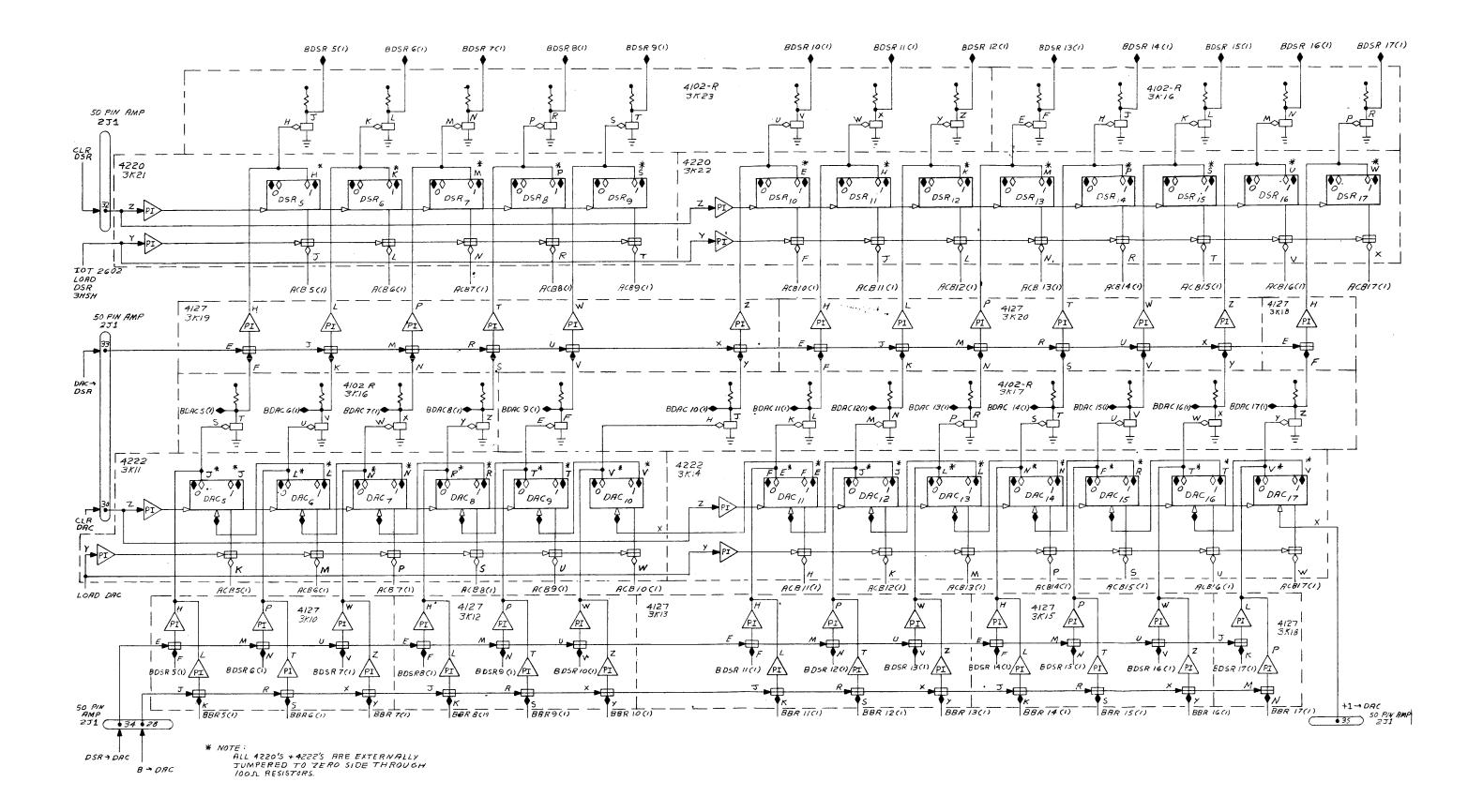

The relay buffer control register consists of 18 unbuffered flip-flops and indicator drivers. The 18 bits from the accumulator (AC) are applied to the conditioning level inputs of positive capacitor-diode gates in the 4220 modules located in 3K05 and 3K07, as shown in Figure 4-5 (BS-D-24902). When the PDP-4 issues the IOT 703165, clear and load pulses occur that first clear the register to zero, then set each flip-flop, whose corresponding bit in the AC is a logic 1 (ground), to the 1 state. When any flip-flop is set to 1, its 1 output (internally jumpered) goes to -3 volts and activates the associated indicator driver in 3K04 and/or 3K06. The indicator driver outputs then go to ground and complete a circuit from the -15 volt supply through the relay coil, energizing the relay and turning on the indicator light.

#### MODIFICATIONS

#### Real Time Control

The real time control has been modified:

1. By adding a variable-frequency clock and a programmable gating circuit for generating periodic interrupt signals.

2. By removing the overflow flag circuit by modifying the real time clock circuit.

3. By adding a circuit which precludes the 340 Display from requesting data while the PDP-4 is in a break cycle.

4. By adding a circuit that allows the 1604A to set the PDP-4 into a continuous break cycle (limbo state).

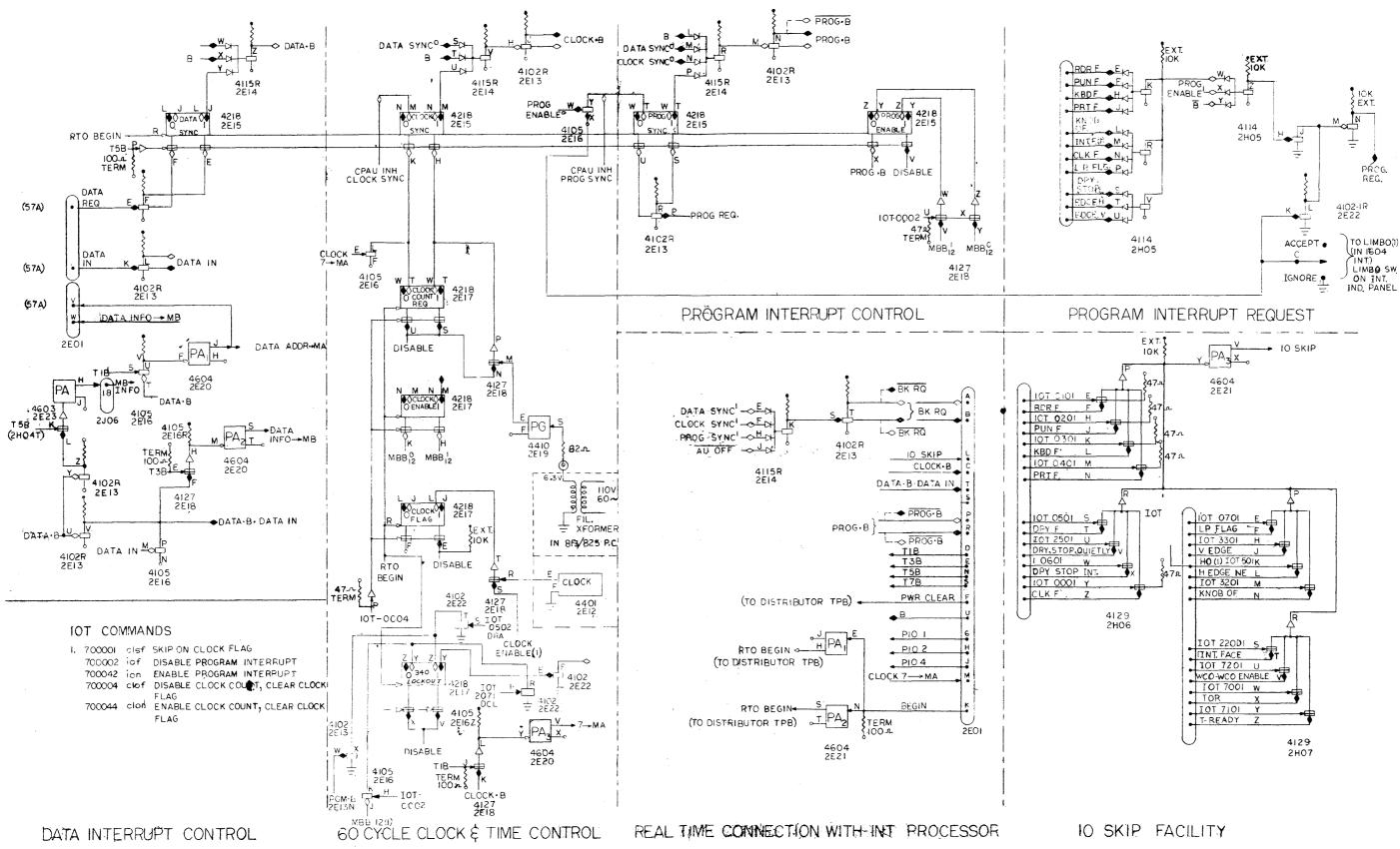

5. By increasing the number of inputs to the information collector. These changes are shown in Figure 4-2 (BS-D-125-0-1).

#### Periodic Interrupt

The source of pulses which cause the periodic interrupts is a 4401 Variable Clock located at 2E12. This produces negative pulses that are applied to the trigger pulse input of a capacitordiode gate located at 2E18. The conditioning level input of the capacitor-diode gate is fed from the clock enable flip-flop in 2E17. This input is negative when the clock enable flipflop is set, allowing a negative pulse from the 4401 to produce a positive pulse at the output of the pulse inverter. This pulse is applied to the clock flag flip-flop, setting it to 1 and producing a negative output level. This is sent to two places: the program interrupt request logic; and the I/O skip logic. The action of the program interrupt request logic and the I/O skip logic is described in the PDP-4 program and maintenance manuals. The clock enable flip-flop is set and cleared under program control by MB<sub>12</sub> in the IOT 700004 (clock off), or IOT 700044 (clock on). The clock flag flip-flop is turned off by both IOT's 700004 and 700044.

#### **Real Time Clock**

The real time clock pulses are derived from a filament transformer located in the 813 Power Control Panel of the PDP-4. The 60-cycle sine wave is converted into pulses by the 4410 module at 2E19, and applied to a capacitor-diode gate in 2E18. The conditioning level input of this gate is always enabled by -3 volts; so the clock pulses (occurring at approximately a 16.7 millisecond repetition rate) continually set the clock count request flip-flop to the 1 state, causing the clock sync flip-flop in 2E15 to be set by timing pulse T5. The clock sync flip-flop causes the PDP-4 to go into a clock break cycle, during which location 7 in memory is addressed and the contents incremented by one. The difference between this operation and that described in the PDP-4 maintenance manual is no flag signal is generated if an overflow occurs when the contents of location 7 are incremented.

#### 340 Lockout

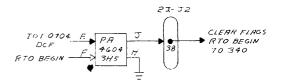

The normally unused flip-flop in the 4218 module in 2E17, shown in the lower left of Figure 4-2, is the 340 lockout flip-flop. The capacitor-diode input gates of this flip-flop are permanently disabled by a negative potential, preventing the IOT 700004 from setting or clearing it. The flip-flop is initially cleared by the RTO BEGIN pulse, the IOT enable program interrupt, 700042,

or the IOT display clear lockout, 702701. These IOT's apply a negative pulse to the base of an inverter gate (the inverter gate in 2E16 is enabled by a ground on its emitter from MB12 (1)), producing a temporary ground output that is applied to terminal Y of the 340 lockout flip-flop that clears it to 0.

Whenever the PDP-4 grants a program break cycle to an interrupting device, the program sync flip-flop enables a NAND gate in 2E14 which produces the ground PGM·B signal. This is complemented by an inverter in 2E13 and applied to terminal Z of the 340 lockout flip-flop, setting it to 1. A -3 volt signal is then produced and applied to an inverter in 2E22, whose collector is connected to the 340 data request input. This grounds the request for data line and prevents the -3 volt request from being generated. The IOT display read address counter, 700502, also sets the 340 lockout flip-flop.

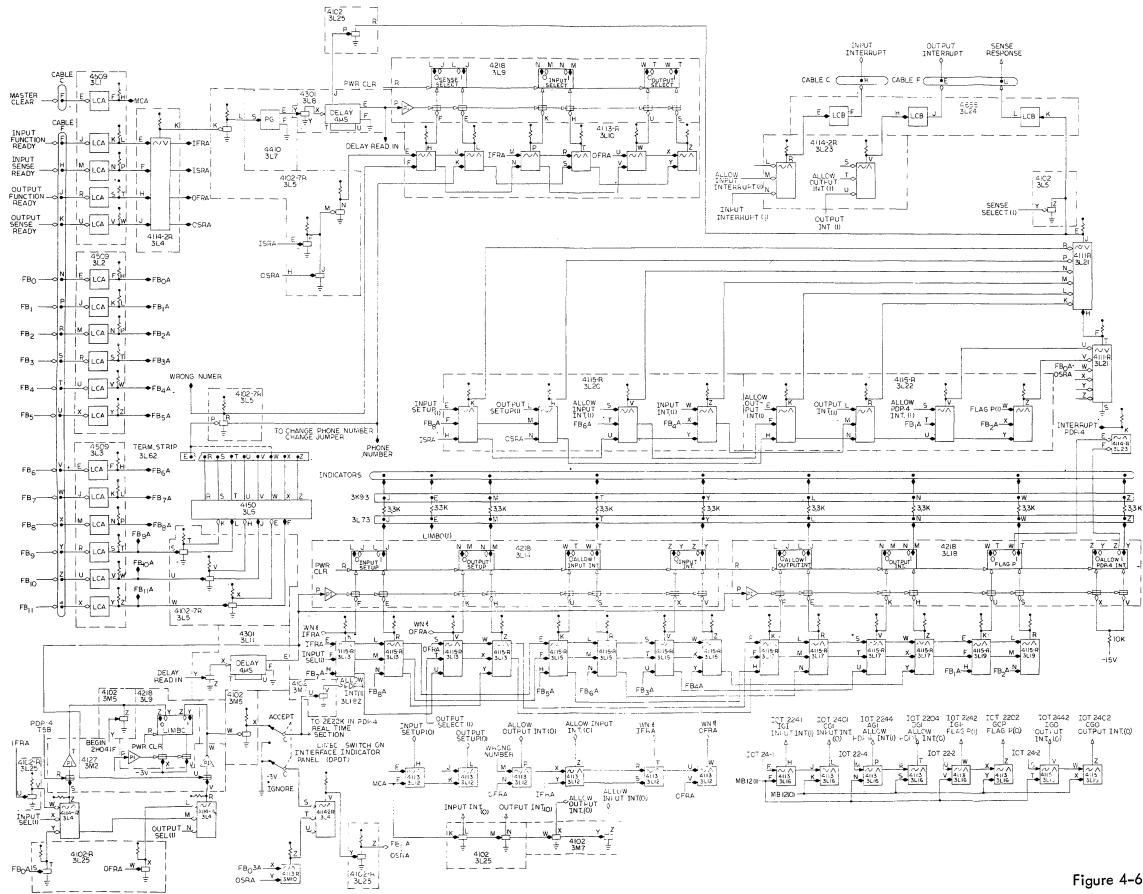

#### Limbo State

The PDP-4 used in this system can be placed into a fifth major state by the external 1604A computer if allowed by the operator. In the limbo state the computer continuously repeats break cycles. The circuits which control the limbo state are located both in the interface control section and the real time control.

If the operator wishes to allow the 1604A to place the PDP-4 in the limbo state, he must throw the LIMBO switch on the interface indicator panel, 3E, to the RECOGNIZE position. This places a -3 volt enabling potential on a 3-input negative NAND gate in 2L19, Figure 4-6 (BS-E-4C-24-2), allowing the 1604A to sense the state of the switch with the output sense command EXF765010, and connects the buffered output of the limbo flip-flop to the real time control. When the LIMBO switch is in the LOCKOUT position, ground potentials are applied to both the limbo switch sensing gate and the real time control, which then operates in the normal fashion.

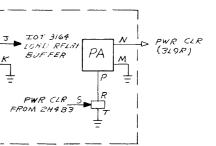

The 1604A can set the limbo flip-flop in 3L09 to its ONE state with the command EXF065001, which applies a ground input to the buffer inverter in 3L25. This causes a -3 volt LIMBO signal to be applied to one part of the LIMBO switch. The limbo flip-flop is initially cleared by the power clear (PWR CLR) pulses, which occur when the PDP-4 is first turned on, and thereafter is cleared by the EXF055001 instruction from the 1604A.

When the limbo flip-flop is set and the LIMBO switch is on RECOGNIZE, the -3 volt LIMBO signal is applied to the emitter of the program enable inverter in 2E16, shown in Figure 4-2 (BS-D-125-0-1) near the prog sync flip-flop. This disables the inverter and prevents the program enable flip-flop from clearing the prog sync flip-flop, which would normally occur at time T5 of the first break cycle. The prog sync flip-flop can now only be set or cleared by pulse T5 according to the PROG REQ signal.

The -3 volt LIMBO (1) signal is also applied to a negative OR gate at the upper right of Figure 4-2, producing a -3 volt PROG REQ signal. This signal is complemented by an inverter in 2E13, and both potentials are applied to the conditioning level inputs of the capacitor-diode gates which control the prog sync flip-flop. The first T5 pulse which occurs then sets the flip-flop to the 1 state, causing the computer to enter a break cycle.

As long as the limbo flip-flop remains set and the switch is closed, the computer remains in the limbo state. The 1604A must clear the limbo flip-flop to release the PDP-4 from this condition. When this is done, the PDP-4's program counter (PC) is set to 1; so the computer executes that instruction which is in memory location 1.

While the PDP-4 is in the limbo state, data or clock breaks are granted during a break cycle, with data breaks having priority over clock breaks. After granting these breaks, the computer reverts back to the limbo state. Since the 340 lockout flip-flop can prevent the display from generating a data request, it is possible for the 1604A to monopolize the data break cycles of the PDP-4.

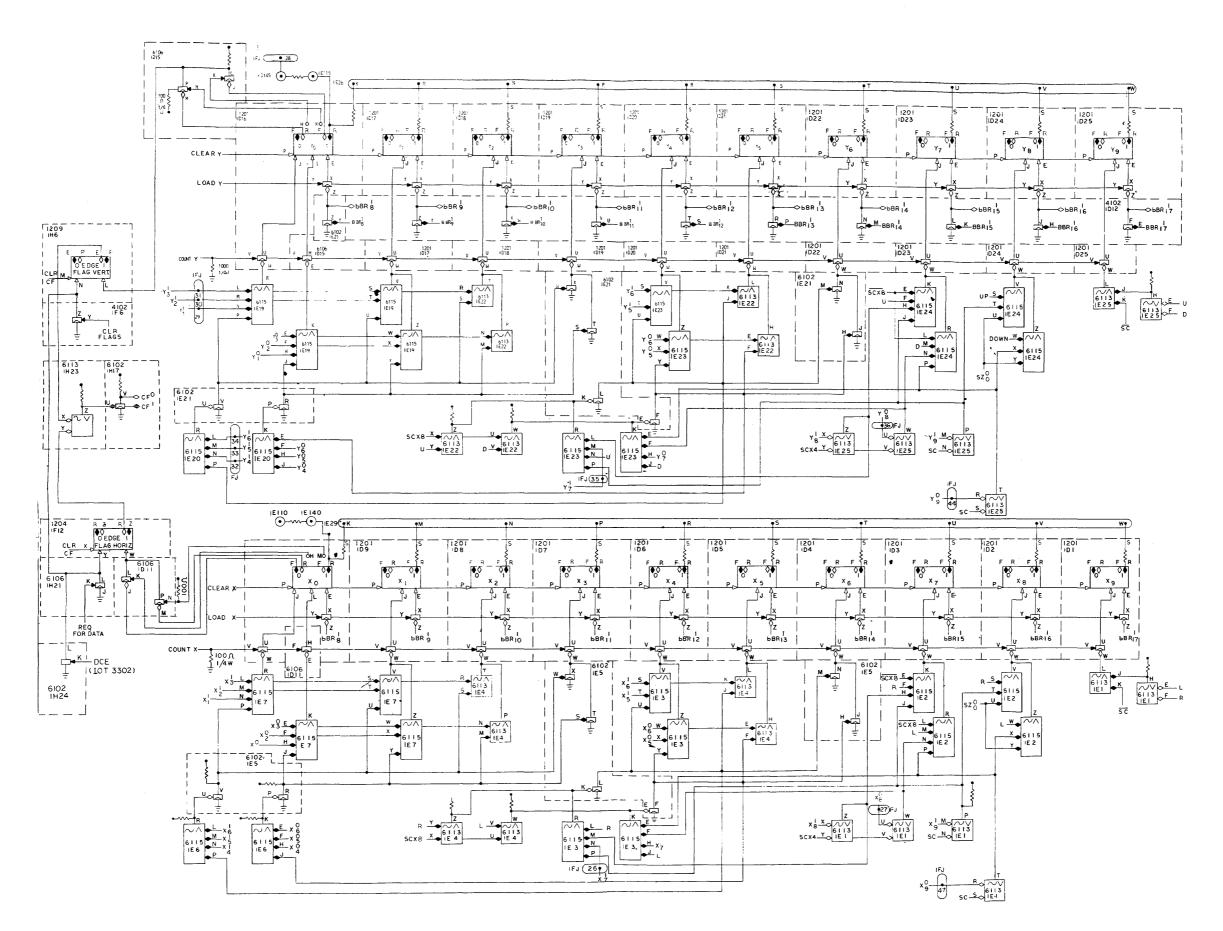

#### Information Collector

The information collector in this system consists of three sections; information collector 0, information collector 1, and information collector 2. Essentially the information collector consists of a group of 18 pulse amplifiers, each one controlled by 24 gated inputs. Most of these gates (not all are used) continually monitor the state of various flip-flops throughout the system and, when a particular IOT occurs, produce output pulses if the controlling flip-flops are in the 1 state. These pulses activate the pulse amplifiers which are connected to the set input gates of the accumulator (AC). The IOT therefore causes the information in the selected flip-flops to be read into the AC for future use. Refer to paragraphs 7-2a and 9-2c in the PDP-4 manual for further description.

Information Collector 0 – This is the standard information collector for the real time control. The block schematic is shown in Figure 9–3, page A–100 in the PDP-4 manual. However, only the IOT's 700102 (read and clear flag) and 700304 (read status register) are valid because no paper tape punch or console typewriter is used in this system.

Information Collector 1 – This section is just like the gates of information collector 0 except that no load resistors are used. The outputs of the two pulse inverters in each bit are in parallel with the corresponding two pulse inverters in information collector 0. Since these four pulse inverters share a common clamped load resistor, their positive pulse outputs are ORed together. Figure 4-7 (BS-D-4C-24-14) shows this section. Each pulse inverter is controlled by four negative capacitor-diode gates, whose outputs are ORed together. Each gate is enabled by a -3 volt level (or negative potential) approximately 1 microsecond after it occurs, and is disabled by a ground level approximately 1 microsecond after it occurs. Seven IOT's are applied to the trigger pulse inputs, as follows:

1. DRP - Read Display Parameters, 702501. This IOT causes the current states of the light pen enable (bit 6), size (bits 12 and 13), and intensity level (bits 15, 16, and 17) flip-flops to be read into the indicated positions of the AC. Bits 4, 5, 11, and 14 are set to 1 and the remaining bits are cleared to 0.

2. DRX - Read Display's X Coordinate, 702502. This IOT causes the current states of the X coordinate counter flip-flops to be read into bits 8 through 17 of the AC. Bit 4 is set to 1 and the remaining bits are cleared to 0.

DRY - Read Display's Y Coordinate, 702504. This IOT causes the current states of the Y coordinate counter flip-flops to be read into bits 8 through 17 of the AC. Bit 7 is set to 1 and the remaining bits are cleared to 0.

4. DRA – Read Display's Address Counter, 700512. This IOT causes the current states of the flip-flops in the display address counter to be read into bits 5 through 17 of the AC and the current states of the three mode flip-flops to be read into bits 2, 3, and 4. Bit 0 is set to 1 and bit 1 is cleared to 0.

5. DSR – Read Address Save Register, 702604. This IOT causes the current states of the flip-flops in the address save register to be read into bits 5 through 17 of the AC; and reads the current state of the save flip-flop into bit 0, the temporary dark flip-flop into bit 1, the temporary blind flip-flop into bit 2, the X edge violated flip-flop into bit 3, and the Y edge violated flip-flop into bit 4.

6. RIF - Read Interface Flags, 702414. This IOT causes the current state of the interface flag flip-flops to be read into bits 0 through 8 of the AC. The remaining flip-flops are cleared to 0.

7. RGA – Read Generator's Address Register, 702304. This IOT causes the current state of the flip-flops in the interface address register to be read into bits 5 through 17 of the AC. The remaining bits are cleared to 0.

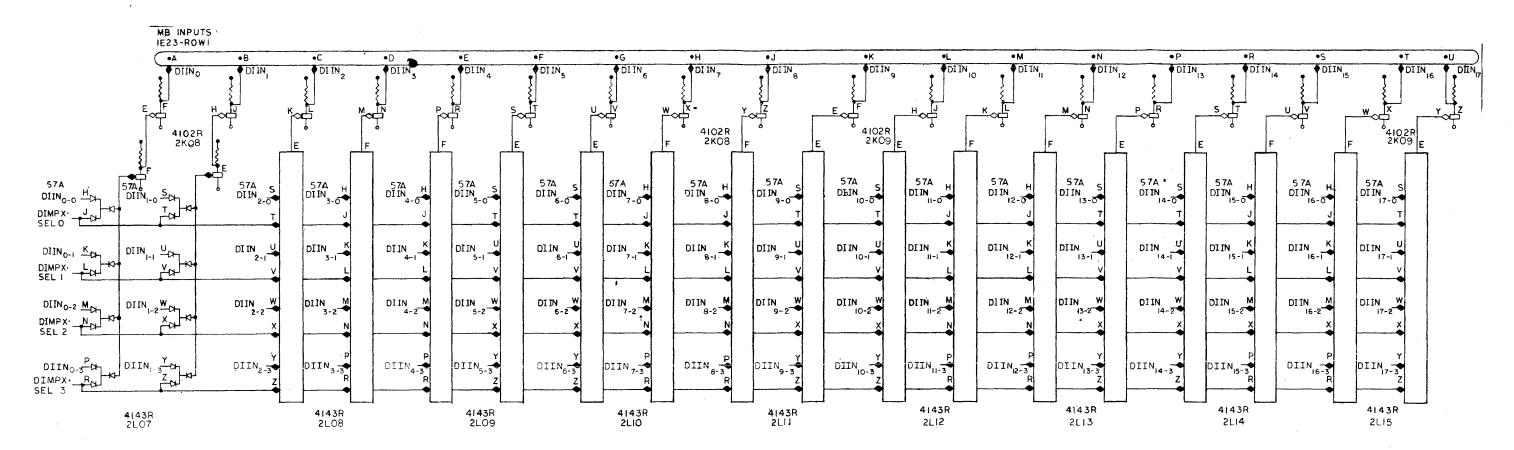

Information Collector 2 – This section is electrically identical with information collector 0 and operates in the same manner. The output of each pulse amplifier is applied to the negative input of the corresponding pulse amplifier in information collector 0, so the output of each gate can be considered to be ORed with the outputs of the gates of the other two sections.

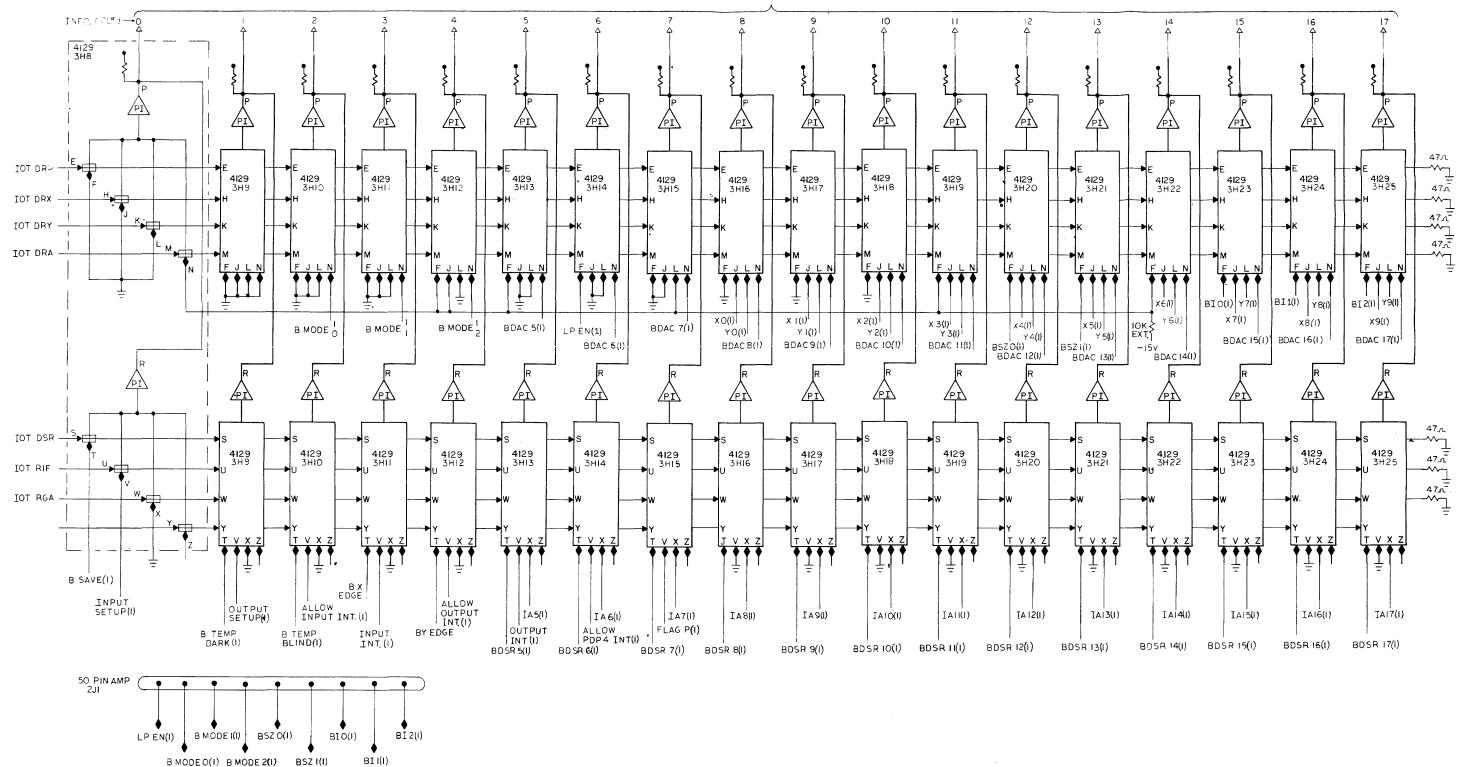

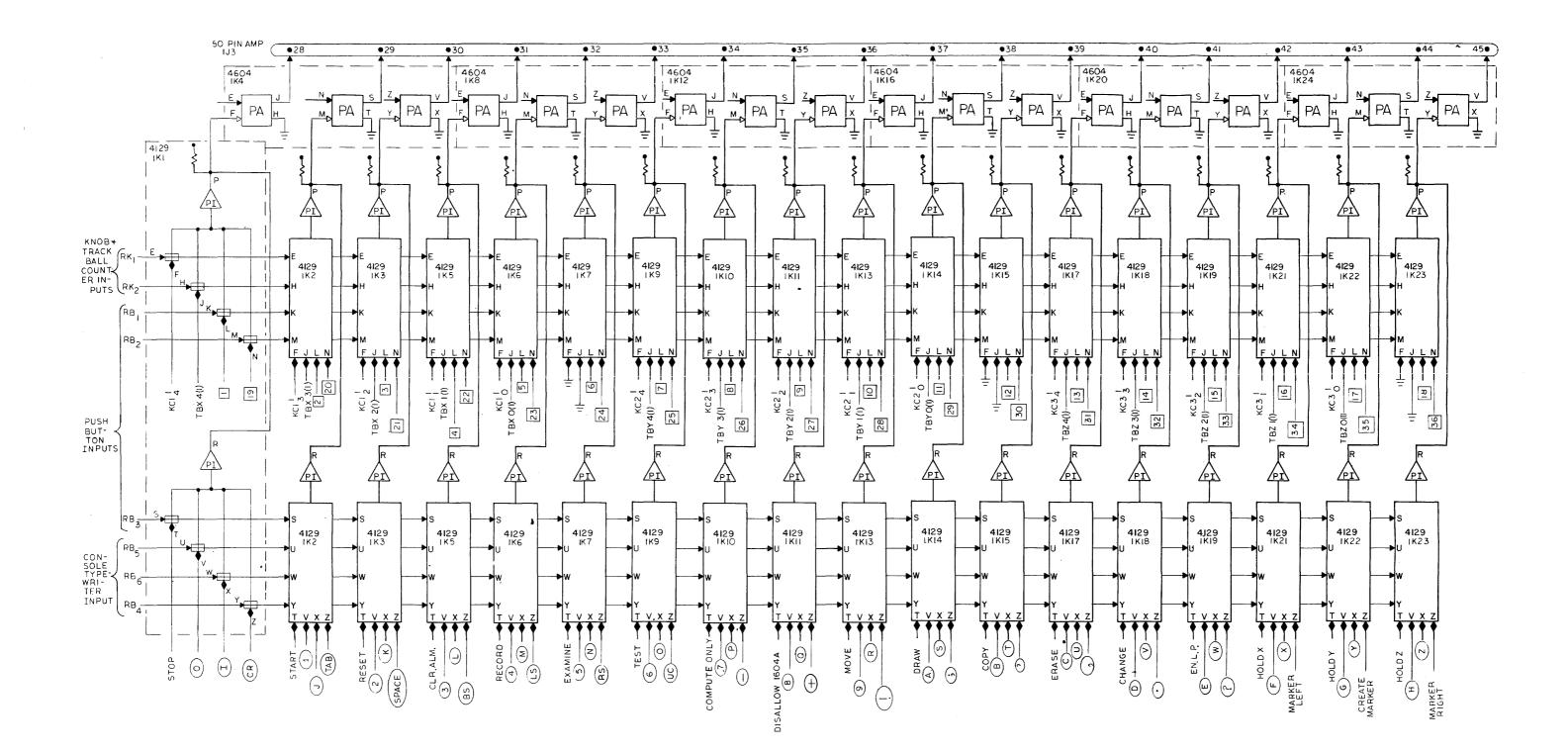

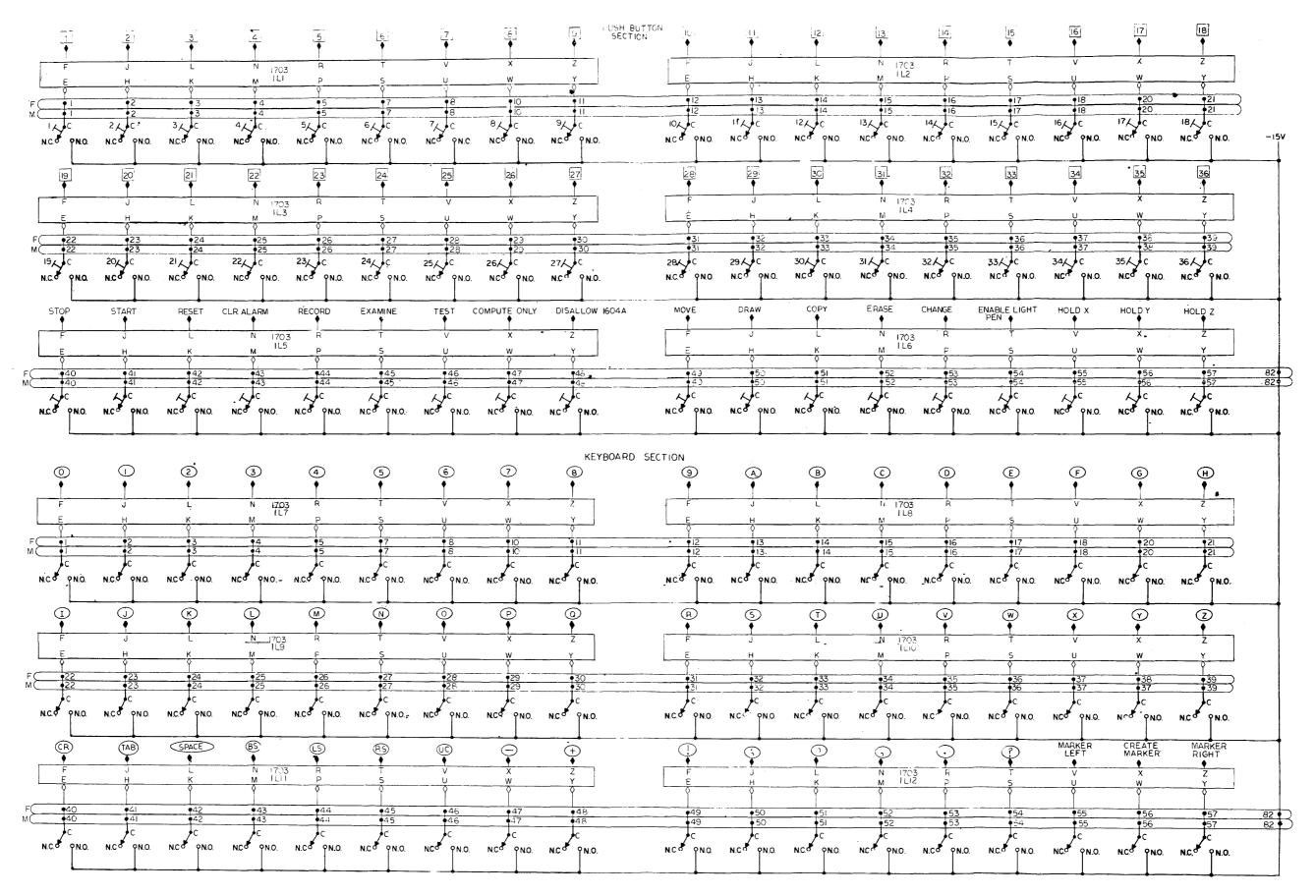

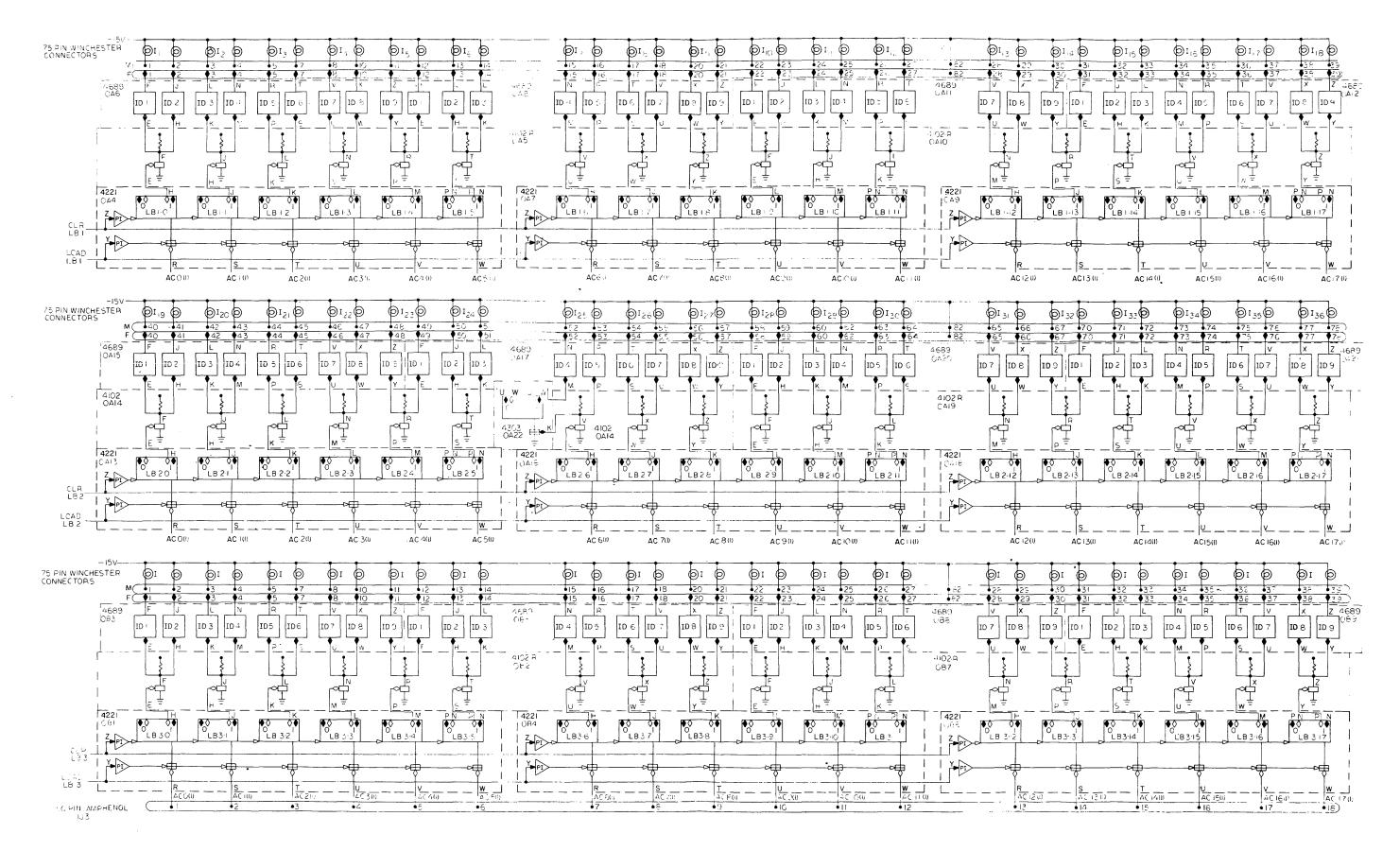

This information collector is shown in Figure 4-8 (BS-D-4C-24-4), and is located in rack K of bay 1 in the 340 Display. It senses the status of the 54 indicating pushbuttons, 54 type-writer keys, and the knob and track ball counters. When any pushbutton or key is depressed, -15 volts is applied to a switch filter, located in rack L of bay 1 in the 340 Display. The switch filter delays and smooths out any impulses in this signal to eliminate errors due to contact bounce, and reduces the signal to -3 volts. The console table switches and switch filters are shown in Figure 4-9 (BS-E-4C-24-3). The outputs of the switch filters are applied to the conditioning level inputs of the capacitor-diode gate in information collector 2.

When the computer issues an IOT to read a particular group of switches or keys during the time the capacitor-diode gates are enabled by -3 volt levels, pulses are produced which activate the associated pulse amplifiers. Since the pushbuttons and keys are activated manually, their contacts remain closed for approximately 100 milliseconds or more. Therefore, the computer must issue its information gathering IOT's at least ten times each second if no