# PROGRAMMER'S REFERENCE MANUAL

#### PROGRAMMER'S REFERENCE MANUAL

This publication is designed to be used as a reference manual by programmers using the Cogar System  $4^{(R)}$  Processor. The manual is divided into three parts. Part I defines the unique features of the machine which are relative to the programmer, as well as providing a machine specification summary. Part II provides general information on the usage of each group of instructions in the instruction set repertoire. Part III defines each instruction in detail, and provides the timing and an example of how each instruction may be used in context with surrounding instructions, in both Source and Object coding. A summation of all the instructions in the repertoire is contained on the Cogar System 4 Instruction Reference Card.

Other publications relating to software for the Cogar System 4 are:

Batch Assembler Operating Instructions; which contains the step-bystep instructions for creating a self-loading program tape, which has been assembled as part of an Object-String background.

<u>Standard Cogar Library Functions</u>; which contains descriptions and operating instructions for the Language Base Library and the I/O Libraries.

The programmer should be familiar with the content and design objectives of the above documents in order to make full use of the capabilities of the Cogar System 4 Processor.

COGAR SYSTEM 4 IS A REGISTERED TRADEMARK OF COGAR CORPORATION

### PROGRAMMER'S REFERENCE MANUAL

### Table of Contents

| COGAR INSTRUCTION DESCRIPTION INDEX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SECTION I. GENERALSystem FeaturesLanguage FeaturesIOS FeaturesAssembler FeaturesDisplayKeyboardCartridge Tapes4Operator Controls7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| SECTION II. INSTRUCTION USAGESubroutine Control8Registers11Addressing11Symbols13DPL-1 Instruction Classes14DPL Punctuation16Literal Notations16Standard C4 Program Record (Mini-Tape)17Subroutine Relocatability19Tape I/O Character Queue19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SECTION III. INSTRUCTION DESCRIPTIONS<br>General21<br>21<br>22<br>21<br>22<br>21<br>22<br>21<br>22<br>22<br>21<br>22<br>21<br>22<br>22<br>21<br>22<br>22<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>24<br>24<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>21<br>22<br>22<br>22<br>21<br>22<br>22<br>22<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>23<br>24<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>26<br>21<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22<br>22 <br< td=""></br<> |

| Group 1: I/O Functions62Group 2: Data Modify68Group 3: Compare73Group 3: Select74Group 4: Control Functions81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Notations for DPL-3B Constants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APPENDIX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Page

### COGAR INSTRUCTION SET INDEX

| Mnemonic     | Name                                                              | Format |         | Page |

|--------------|-------------------------------------------------------------------|--------|---------|------|

| ADA ····     | Add to Accumulator                                                | DPL-1  | • • •   | 50   |

| ADD ••••     | Add Storage to Storage                                            |        | • • •   | 69   |

| ADX ••••     | Add to Index Register                                             | DPL-1  | • • •   | 51   |

| ANA ••••     | Logical 'AND' to Accumulator                                      | DPL-1  | •••     | 54   |

| BRE ····     | Branch on Equal                                                   | DPL-1  | • • •   | 27   |

| BRH ····     | Branch on High                                                    |        | • • •   | 28   |

| BRL ····     | Branch on Low                                                     | DPL-1  | • • •   | 29   |

| BRU ····     | Branch Unconditional                                              | DPL-1  | • • •   | 25   |

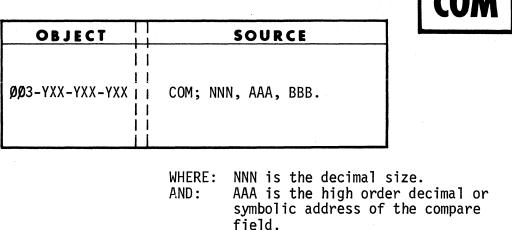

| COM ····     | Compare Storage to Storage                                        | DPL-2  | • • •   | 73   |

| СРА ••••     | Compare Accumulator                                               | DPL-1  | • • •   | 60   |

| CPI ····     | Clear Processor Interrupt                                         | DPL-1  | •••     | 45   |

| СРХ ••••     | Compare Index Register ······                                     | DPL-1  |         | 61   |

| DIV ····     | Divide ·····                                                      | DPL-2  | • • • • | 72   |

| DPI ····     | Disable Processor Interrupt                                       | DPL-1  | • • •   | 42   |

| EJT ····     | Eject to Top of Form                                              | DPL-1  | •••     | 94   |

| END ····     | End Segment                                                       | DPL-1  | • • •   | 93   |

| ENT ····     | Enter Control Function                                            | DPL-1  | • • •   | 88   |

| EPI ····     | Enable Processor Interrupt                                        | DPL-1  | •••     | 43   |

| EQU ····     | Equate Symbol                                                     | DPL-1  | •••     | 90   |

| ERA ····     | Exclusive 'OR' to Accumulator                                     | DPL-1  | •••     | 56   |

| EXB ····     | Exit and Branch                                                   | DPL-1  | • • •   | 34   |

| EXU ····     | Exit Unconditional                                                | DPL-1  | •••     | 35   |

| GET ····     | Get Data (Read) ·····                                             | DPI -2 | • • •   | 62   |

| IOC-C#3 ···  | I/O Keyboard ·····                                                | DPL-1  | • • •   | 98   |

| IOC-C#N ···  | I/O Mini-Tape ·····                                               | DPL-1  | • • •   | 95   |

| IOC-C#4 ···  | Display Control                                                   | DPL-1  | • • •   | 99   |

| IRA ····     | Inclusive 'OR' to Accumulator                                     | DPL-1  | • • •   | 58   |

| LDA ····     | Load Accumulator                                                  | DPL-1  | • • •   | 46   |

| LDX ····     | Load Index Register ·····                                         | DPL-1  | • • •   | 47   |

| LIA ····     | Load Instruction Address                                          | DPL-1  | • • •   | 48   |

| LPS ····     | Load Processor Status                                             |        | •••     | 41   |

| LSW ····     | Load Sense Switches                                               | DPL-1  | • • •   | 40   |

| MOV ••••     | Move Storage to Storage<br>Multiply                               | DPL-2  | • • •   | 68   |

| MUL ····     | Multiply ·····                                                    | DPL-2  | •••     | 71   |

| ORG ····     | Origin LOcation Counter<br>Overlay                                | DPL-1  | • • •   | 86   |

| 0VL ••••     | Overlay ·····                                                     | DPL-1  |         | 91   |

| PCL-PRT ···· | Line Printer Control                                              | DPL-2  | • • •   | 84   |

| PCL-TYP ···  | Typewriter Control ·····                                          | DPL-2  | • • •   | 83   |

| PUT ····     | Put Data (Write) ·····                                            | DPL-2  | •••     | 64   |

|              | Set Arithmetic Condition                                          |        | • • •   | 39   |

| SAN ····     | Shift & Logical 'AND' to Accumulator ····                         | DPL-1  | • • •   | 55   |

| SBE ····     | Stack and Branch on Equal                                         | DPL-1  | • • •   | 31   |

| SBH ····     | Stack and Branch on Equal ·····<br>Stack and Branch on High ····· | DPL-1  | •••     | 32   |

|              |                                                                   |        |         |      |

### COGAR INSTRUCTION SET INDEX

| Mnemonic                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Name                                                                                                                                                                                                                                                                                                                                                                                     | Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         | Page                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

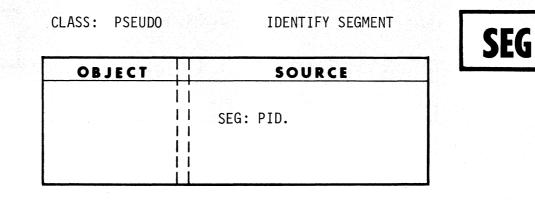

| SBL         SBU         SEG         SEL-EQL         SEL-HGH         SEL-NEQ         SEL-NEQ         SEL-NHG         SEL-NHQ         SEL-NLW         SEL-UNC         SER         SEL-NLW         SEL-NLW         SEL-SER         SER         SEL         SEL         SER         SER         SUR         SUB         SUX         TCL | NameStack and Branch on LowStack and Branch UnconditionalIdentify SegmentSelect EqualSelect HighSelect LowSelect Not EqualSelect Not EqualSelect Not LowSelect UnconditionalShift and 'EOR' AccumulatorSet PageShift and 'IOR' AccumulatorSet Memory SectionSet Memory Section and ControlSubtract from AccumulatorSubtract from Index RegisterTape Control CommandTest Literal and Jump | DPL-1<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-2<br>DPL-1<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-2<br>DPL-1<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-1<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL-2<br>DPL |                         | 33<br>30<br>87<br>76<br>77<br>75<br>79<br>78<br>80<br>74<br>57<br>81<br>59<br>37<br>36<br>38<br>49<br>52<br>70<br>53<br>82 |

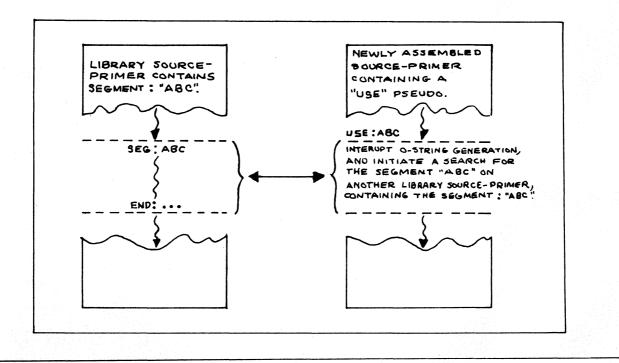

| TLX<br>TMJ<br>TMX                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Test Literal and Jump<br>Test Literal and Exit<br>Test Mask and Jump<br>Test Mask and Exit<br>Use External Source Segment                                                                                                                                                                                                                                                                | • DPL-1<br>• DPL-1<br>• DPL-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | • • •<br>• • •<br>• • • | 22<br>24<br>23<br>25<br>92                                                                                                 |

## SPECIFICATION SUMMARY

| Size10 inches high (25 cm)<br>18.5 inches wide (47 cm)<br>24 inches deep (60 cm)Weight60 pounds (27 kg)Power115 VAC ±10%, 220 VAC ±10%<br>48 to 62 Hz<br>2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 ine display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each<br>Write/Erase Protection                                                                                                                                                                          |                  |                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------|--|

| 18.5 inches wide (47 cm)<br>24 inches deep (60 cm)         Weight       60 pounds (27 kg)         Power       115 VAC ±10%, 220 VAC ±10%<br>48 to 62 Hz<br>2.5 amps average         Environment       10% to 80% relative humidity without<br>condensation         60°F to 95°F Operating Temperature<br>0°F to 150°F Storage Temperature         Ventilation       30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipation         Processor       45 instruction types plus I/O<br>3 to 6 μs instruction cycle time<br>1 Accumulator         Tidex Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap Loader         Memory       16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic Semiconductor         Keyboard       Software configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cue         Visual Display       5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program control         Tape System       10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind search         Tape Cartridges       100 ft. computer grade tape<br>900 records of 136 characters each                                                         | Size             | 10 inches high (25 cm)                |  |

| 24 inches deep (60 cm)Weight60 pounds (27 kg)Power115 VAC ±10%, 220 VAC ±10%<br>48 to 62 Hz<br>2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlook switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each |                  |                                       |  |

| Weight60 pounds (27 kg)Power115 VAC ±10%, 220 VAC ±10%<br>48 to 62 Hz<br>2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                               |                  | . ,                                   |  |

| Power115 VAC ±10%, 220 VAC ±10%<br>48 to 62 Hz<br>2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect kegs<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                      |                  | 24 mones deep (60 cm)                 |  |

| 48 to 62 Hz2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                             | Weight           | 60 pounds (27 kg)                     |  |

| 2.5 amps averageEnvironment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus 1/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Addible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                            | Power            | 115 VAC $\pm$ 10%, 220 VAC $\pm$ 10%  |  |

| Environment10% to 80% relative humidity without<br>condensation<br>60°F to 95°F Operating Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus 1/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                            |                  | 48 to 62 Hz                           |  |

| CondensationCondensation60°F to 95°F Operating Temperature0°F to 150°F Storage Temperature0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                           |                  | 2.5 amps average                      |  |

| 60°F to 95°F Operating Temperature<br>0°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus 1/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                               | Environment      | · · · · · · · · · · · · · · · · · · · |  |

| O°F to 150°F Storage TemperatureVentilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |                                       |  |

| Ventilation30 cubic feet per minute air flow<br>4 inches air flow clearance on all sides<br>1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 μs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                  |                                       |  |

| <ul> <li>A inches air flow clearance on all sides<br/>1000 BTU per hour heat dissipation</li> <li>Processor</li> <li>45 instruction types plus I/O<br/>3 to 6 µs instruction cycle time<br/>1 Accumulator<br/>7 Index Registers per 2K of memory<br/>16 Member Instruction Address Stack<br/>Hardware Bootstrap Loader</li> <li>Memory</li> <li>16K bytes capacity<br/>Random Access Read/Write<br/>Non-Destructive Read-Out<br/>Monolithic Semiconductor</li> <li>Keyboard</li> <li>Software configurable<br/>Hall effect keys<br/>N-Key rollover capability<br/>Audible cue</li> <li>Visual Display</li> <li>5 inch CRT</li> <li>4 or 8 line display, with interleave<br/>capability<br/>32 characters per line<br/>5 x 8 matrix under program control</li> <li>Tape System</li> <li>10 ips write tape speed<br/>1600 bpi density, phase modulation<br/>2 mechanically independent transports<br/>Read after Write, CRC, phase checks<br/>Automatic threading<br/>Write interlock switch<br/>Rewind: 40 ips rewind and forward or<br/>rewind search</li> <li>Tape Cartridges</li> <li>100 ft. computer grade tape<br/>900 records of 136 characters each</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            |                  | 0°F to 150°F Storage Temperature      |  |

| <ul> <li>4 inches air flow clearance on all sides<br/>1000 BTU per hour heat dissipation</li> <li>Processor</li> <li>45 instruction types plus I/O<br/>3 to 6 µs instruction cycle time<br/>1 Accumulator<br/>7 Index Registers per 2K of memory<br/>16 Member Instruction Address Stack<br/>Hardware Bootstrap Loader</li> <li>Memory</li> <li>16K bytes capacity<br/>Random Access Read/Write<br/>Non-Destructive Read-Out<br/>Monolithic Semiconductor</li> <li>Keyboard</li> <li>Software configurable<br/>Hall effect keys<br/>N-Key rollover capability<br/>Audible cue</li> <li>Visual Display</li> <li>5 inch CRT</li> <li>4 or 8 line display, with interleave<br/>capability<br/>32 characters per line<br/>5 x 8 matrix under program control</li> <li>Tape System</li> <li>10 ips write tape speed<br/>1600 bpi density, phase modulation<br/>2 mechanically independent transports<br/>Read after Write, CRC, phase checks<br/>Automatic threading<br/>Write interlock switch<br/>Rewind: 40 ips rewind and forward or<br/>rewind search</li> <li>Tape Cartridges</li> <li>100 ft. computer grade tape<br/>900 records of 136 characters each</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                            | Ventilation      | 30 cubic feet per minute air flow     |  |

| 1000 BTU per hour heat dissipationProcessor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  | -                                     |  |

| Processor45 instruction types plus I/O<br>3 to 6 µs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  |                                       |  |

| 3 to 6 μs instruction cycle time<br>1 Accumulator<br>7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                  |                                       |  |

| 1 Accumulator7 Index Registers per 2K of memory16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Processor        | 45 instruction types plus I/O         |  |

| 7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  |                                       |  |

| 7 Index Registers per 2K of memory<br>16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                  | · · ·                                 |  |

| 16 Member Instruction Address Stack<br>Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                                       |  |

| Hardware Bootstrap LoaderMemory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                                       |  |

| Memory16K bytes capacity<br>Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                                       |  |

| Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                                       |  |

| Random Access Read/Write<br>Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Memory           | 16K butos canacity                    |  |

| Non-Destructive Read-Out<br>Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | memory           |                                       |  |

| Monolithic SemiconductorKeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                                       |  |

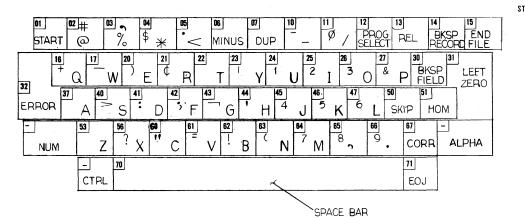

| KeyboardSoftware configurable<br>Hall effect keys<br>N-Key rollover capability<br>Audible cueVisual Display5 inch CRT<br>4 or 8 line display, with interleave<br>capability<br>32 characters per line<br>5 x 8 matrix under program controlTape System10 ips write tape speed<br>1600 bpi density, phase modulation<br>2 mechanically independent transports<br>Read after Write, CRC, phase checks<br>Automatic threading<br>Write interlock switch<br>Rewind: 40 ips rewind and forward or<br>rewind searchTape Cartridges100 ft. computer grade tape<br>900 records of 136 characters each                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  |                                       |  |

| <ul> <li>Hall effect keys<br/>N-Key rollover capability<br/>Audible cue</li> <li>Visual Display</li> <li>5 inch CRT         <ul> <li>4 or 8 line display, with interleave<br/>capability</li> <li>32 characters per line</li> <li>5 x 8 matrix under program control</li> </ul> </li> <li>Tape System         <ul> <li>10 ips write tape speed</li> <li>1600 bpi density, phase modulation</li> <li>2 mechanically independent transports</li> <li>Read after Write, CRC, phase checks</li> <li>Automatic threading</li> <li>Write interlock switch</li> <li>Rewind: 40 ips rewind and forward or<br/>rewind search</li> </ul> </li> <li>Tape Cartridges         <ul> <li>100 ft. computer grade tape</li> <li>900 records of 136 characters each</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                  | Monolithic Semiconductor              |  |