## PARALLEL INPUT/OUTPUT DIRECT MEMORY ACCESS

CGC 7900 SERIES COLOR GRAPHIC COMPUTERS

## CHROMATICS

CGC 7900 Parallel Input/Output Direct Memory Access

User's Manual

March 25, 1982

DOCUMENT NUMBER 070205 PUBLICATION DATE 1/82 COPYRIGHT © 1982 CHROMATICS, INC.

## TABLE OF CONTENTS

1

| PREFACE                          |                                                                                                                                                                                                                | 1-1                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| PIO                              | ONE - PIO/DMA GENERAL HARDWARE<br>GENERAL DESCRIPTION<br>GENERAL DESCRIPTION                                                                                                                                   | 1-1<br>1-2<br>1-3                                                            |

| MEMO<br>INTI<br>VEC              | TWO - PIO/DMA HARDWARE OPTIONS<br>ORY ADDRESS SELECTION<br>ERRUPT LEVEL SELECTION<br>FOR ADDRESS SELECTION<br>GRANT SELECTION                                                                                  | 2-1<br>2-2<br>2-3<br>2-4<br>2-5                                              |

| INT                              | THREE - HARDWARE EXPANSION<br>ERRUPT EXPANSION<br>MASTER EXPNASION                                                                                                                                             | 3-1<br>3-2<br>3-3                                                            |

| PRO<br>POLI<br>PIO<br>PIO<br>PIO | FOUR - PIO THEORY OF OPERATION<br>GRAMMABLE PORT CONTROL REGISTERS<br>LING THEORY OF OPERATION<br>POLLING TO WRITE<br>POLLING TO READ<br>WRITE OPERATIONS USING INTERRUPTS<br>READ OPERATIONS USING INTERRUPTS | $\begin{array}{c} 4-1 \\ 4-2 \\ 4-3 \\ 4-4 \\ 4-5 \\ 4-6 \\ 4-7 \end{array}$ |

| HARI<br>PIO<br>PIO               | FIVE - PIO HARDWARE DESCRIPTION<br>DWARE THEORY OF OPERATION<br>OPTIONING<br>INPUT/OUTPUT OPTION<br>CONNECTOR DEFINITION                                                                                       | 5-1<br>5-2<br>5-3<br>5-4<br>5-5                                              |

| DMA<br>DMA<br>DMA<br>DMA         | SIX - DMA THEORY OF OPERATION<br>TRANSFER MODES<br>THEORY OF OPERATION<br>REGISTER INITIALIZATION<br>BUS CYCLES<br>REGISTER DEFINITION                                                                         | 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6                                       |

| DMA<br>DMA<br>DMA                | SEVEN - DMA HARDWARE DESCRIPTION<br>SIGNAL DEFINITION<br>CONNECTOR PIN ASSIGNMENTS<br>JUMPER OPTIONS<br>CONFIGURATIONS                                                                                         | 7-1<br>7-2<br>7-3<br>7-4<br>7-5                                              |

| DMA                              | Sample User Program                                                                                                                                                                                            | Appendix A                                                                   |

PREFACE - The purpose of this document is to define the CGC 7900'S Parallel Input/Output, Direct Memory Access Circuit board (PIO/DMA). It describes the overall attributes of the board as well as goes into detail about the operation and design of the board.

1-1 PIO/DMA GENERAL HARDWARE - The CGC 7900 PIO/DMA consists of one standard size digital circuit board, which will occupy one card slot in the 7900 mother board. The circuit board has five connectors along its card edge, two for the PIO interface, two for the DMA interface and one for Interrupt and Bus Grant Level Prioritizing.

The PIO/DMA circuit board consists of four separate 16 bit parallel interfaces. Two are programmable ports which the processor has full control over and the other two are DMA ports which once activated perform all transfers independent of the CPU.

1-2 PIO GENERAL DESCRIPTION - The programmable port can be operated by way of polling or by way of interrupts. Polled operation requires the CPU to write or read data to or from the port and then test the PIO status register to determine the readiness of the port. The second mode of operation is interrupt driven I/O. When the interface has a data word or byte for the CPU or is ready to transfer another word or byte out the port it notifies the CPU via an interrupt forcing the CPU to stop what it is doing and service the parallel port.

The Parallel Port consists of two 16 bit data registers one for input and the other for output. Each of these two ports can be subdivided into two 8 bit ports each with its own status, interrupt, and control circuitry.

The main features of the Parallel Port are:

- Two 16 bit ports; one for input, one for output, each with its own control signals.

- 2) Word or byte transfers.

- 3) CPU interaction by polling or interrupts.

- 4) All receivers and drivers are differential according to RS-422 and RS-423 standards.

- 5) Transfer rates of up to 150K words or bytes per second.

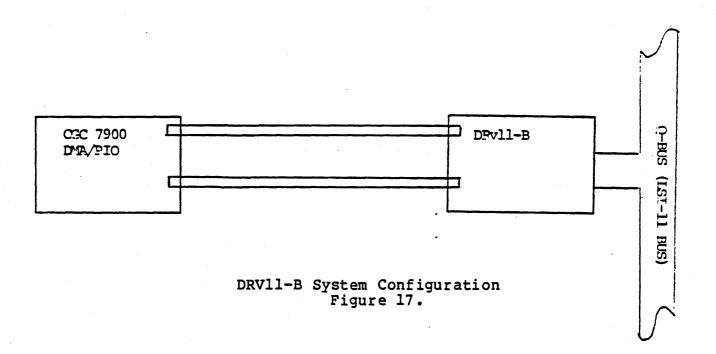

1-3 DMA GENERAL DESCRIPTION - The DMA interface is compatible with three DEC DMA interfaces, the DRV11-B, DR11-W and DR11-B, each being used with a different type of DEC computer. Below are listed the main features of the DMA interface.

- 1) Two 16 bit ports one for input and one for output.

- 2) Data transfers up to 500K per second.

- 3) Separate 40 pin connector for input and output.

- 4) Transfer of up to 64K words at once without processor intervention.

- 5) Capable of Burst or Single Cycle Operation.

2-1 PIO/DMA HARDWARE OPTIONS - The purpose of this section is to describe certain hardware options that are applicable to both PIO and DMA portions of the board. There are additional options which apply strictly to either the PIO or DMA hardware which will be discussed in the appropriate sections of this manual.

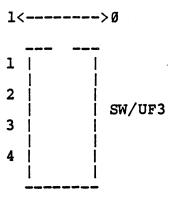

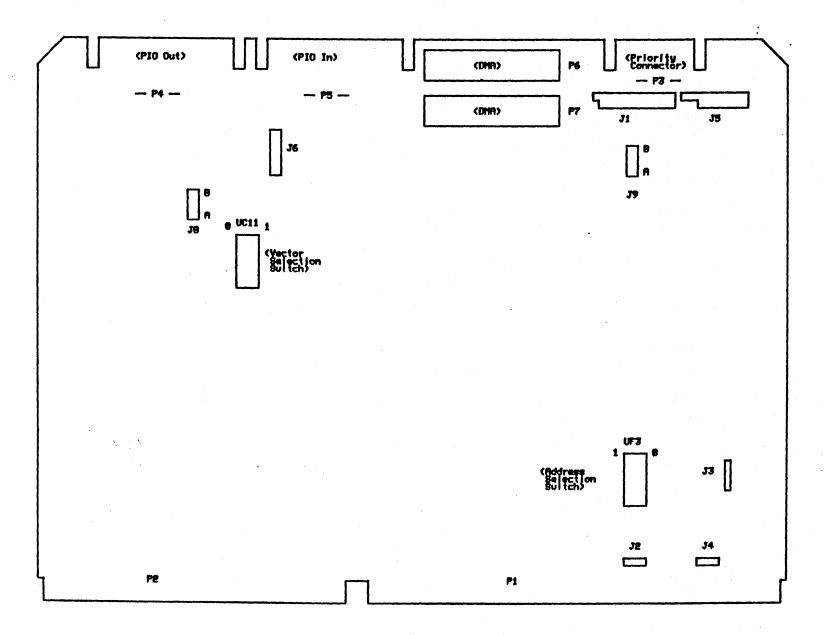

2-2 MEMORY ADDRESS SELECTION - By use of a switch located at UF3 on the board the starting base address of all the registers on the board can be relocated in memory between FF8400 to and FF84F0. See Table 1 for switch setting versus memory address information.

#### THIS SPACE LEFT BLANK INTENTIONALLY

Switch Position

| <br>Base<br>Address | 1 | 2   | 3 | 4   |  |

|---------------------|---|-----|---|-----|--|

| <br>FF8400          | ø | Ø   | Ø | ø   |  |

| FF841Ø              | 1 | Ø   | Ø | Ø   |  |

| FF842Ø              | Ø | 1   | Ø | Ø   |  |

| FF843Ø              | 1 | 1   | Ø | Ø   |  |

| FF844Ø              | Ø | Ø   | 1 | Ø   |  |

| FF846Ø              | Ø | 1 . | 1 | Ø   |  |

| FF847Ø              | 1 | 1   | 1 | Ø   |  |

| FF848Ø              | Ø | Ø   | Ø | 1   |  |

| FF849Ø              | 1 | Ø   | Ø | 1   |  |

| FF84AØ              | Ø | 1   | Ø | 1   |  |

| FF84BØ              | 1 | 1   | Ø | 1   |  |

| FF84CØ              | Ø | Ø   | 1 | 1 . |  |

| FF84DØ              | 1 | Ø   | 1 | 1   |  |

| FF84EØ              | Ø | 1   | 1 | 1   |  |

| FF84FØ              | 1 | 1   | 1 | 1   |  |

|                     |   |     |   |     |  |

Base Address Switch Postions Table 1. 2-3 INTERRUPT LEVEL SELECTION - If any of the interrupt capability on the board is to be used the two interrupt level jumpers must be installed. These jumpers select the interrupt level at which all the interrupts on the board will operate.

The interrupt levels that are available for use are levels 1, 2, 3 and 6. Levels 4 and 5 are reserved for the CPU board and level 7 is reserved for the power up interrupt. Jumpers J2 and J3 are the interrupt level jumpers. The level of interrupt desired must be reflected on both of these jumpers and must be the same. Example: if J2 has a jumper in position two J3 must also have its jumper in position two. Each header must have only one jumper. In order to complete interrupt acknowledge decoding there must also be a jumper installed on header J1 at position INØ. Refer to Section 5.0 HARDWARE EXPANSION if more than one board is to be installed at the same interrupt level.

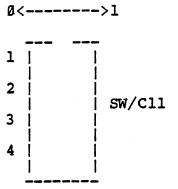

2-4 VECTOR ADDRESS SELECTION - The interrupt vector addresses of all the interrupts occurring on the board are switch selectable. Vector addresses between 100 and 13F are reserved for the interrupts on the CPU card. There is a possibility of eight interrupts occurring on the PIO/DMA board including the spare. Thus, the base address of the interrupt vectors must move at even intervals of eight. The switch used to select the vector addresses is located at position UC11. See Table 2 for vector address selection.

2-5 BUS GRANT SELECTION - The level of bus master control granted to each PIO/DMA board is selectable by means of jumpers located at J4 and J5. In a single board system there must be one jumper installed in both J4 and J5 headers and they must agree with each other. Example: If bus master level three is desired, J4 must have a jumper at three and J5 must have a jumper at three in the 2 thru 5 positions. Refer to Section 5.0 HARDWARE EXPANSION if more than one board is to share the same Bus Master level.

| Base<br>Vector<br>Adress |         |   | Switch<br>Position |   |   |                                       |  |

|--------------------------|---------|---|--------------------|---|---|---------------------------------------|--|

|                          | AUL 655 | 1 | 2                  | 3 | 4 |                                       |  |

|                          | 200H    | Ø | Ø                  | Ø | Ø | · · · · · · · · · · · · · · · · · · · |  |

|                          | 22ØH    | 1 | Ø                  | Ø | Ø |                                       |  |

|                          | 240H    | Ø | 1                  | Ø | Ø |                                       |  |

|                          | 26ØH    | 1 | 1                  | ø | Ø |                                       |  |

|                          | 28ØH    | Ø | Ø                  | 1 | Ø |                                       |  |

|                          | 2АØН    | 1 | Ø                  | 1 | Ø |                                       |  |

|                          | 2CØH    | Ø | 1                  | 1 | Ø |                                       |  |

|                          | 2EØH    | 1 | 1                  | 1 | Ø |                                       |  |

|                          | ЗØØН    | Ø | Ø                  | Ø | 1 |                                       |  |

|                          | 32ØH    | 1 | Ø                  | ø | 1 |                                       |  |

|                          | 34ØH    | Ø | 1                  | Ø | 1 |                                       |  |

|                          | 36ØH    | 1 | 1                  | Ø | 1 |                                       |  |

|                          | 38ØH    | Ø | Ø                  | 1 | 1 |                                       |  |

|                          | ЗАЙН    | 1 | Ø                  | 1 | 1 |                                       |  |

|                          | ЗСØН    | Ø | 1                  | 1 | 1 |                                       |  |

|                          | ЗЕЙН    | 1 | 1                  | 1 | 1 |                                       |  |

|                          |         |   |                    |   |   |                                       |  |

## Base Interrupt Vector Switch Positions Table 2.

3-1 HARDWARE EXPANSION - The purpose of this section is to describe methods in which more than one PIO/DMA board can be used in one system. The types of expansion referred to are Interrupt Expansion and Bus Master Expansion.

The first step to be taken when expanding either an interrupt level or a bus grant level is that of installing the Priority Cable between the two boards at position P3. This cable is a 26 pin card edge to card edge cable available from Chromatics (P/N 100428).

3-2 INTERRUPT EXPANSION - When selecting interrupt levels if it is desirable to have two boards share the same interrupt level the hardware priority cable must be installed between the two boards, see above. The interrupt priority jumpers must also be positioned properly on the two boards. The board which is to have the highest priority within the level must have a jumpers at positions IN 0 and OUT 1. The next board in the chain must have jumpers at positions IN 1 and OUT 2 and so on down the line. The maximum number of boards to share the same interrupt level is 10.

3-3 BUS MASTER EXPANSION - Bus Master Expansion is accomplished in much the same manner that Interrupt Expansion is. The board which is to have the highest priority within the bus grant level must have a jumper at position IN2 and position OUT1 on J5. The next board in the chain will have jumpers at position IN 5+1 and position OUT2 and so on. This sequence will continue up until the last board in the chain. All boards in the same level must have the jumper at J4 in the same position indicating a shared level. Thus, any board in the chain can request the bus causing the CPU to grant it. The first board in the chain will receive the bus grant signal from the processor and if it does not want the bus at the present time it will propagate the signal out to the next board and so on down the chain.

NOTE: It must be assured that there are no conflicts in the switch settings for either the memory or vector addresses. 4-1 PIO THEORY OF OPERATION - This section of the manual will describe functionally how the PIO portion the PIO/DMA board operates.

4-2 PROGRAMMABLE PORT CONTROL REGISTERS - The programmable parallel port consists of one 16 bit control register and two 16 bit data registers. The addresses of these registers are as follows:

FF84XØ low data byte read or write address FF84X1 high data byte read or write address FF84X2 Parallel Port Status byte (See Below) FF84X3 Parallel Port Interrupt mask (See Below)

Figure 1 is a definition of the Parallel Port Control Register. Following the figure is the definition of each bit.

THIS SPACE LEFT BLANK INTENTIONALLY

| Register name   | PROGRAMMAB | LE PORT CONTROL | REGISTER (PPCR) |

|-----------------|------------|-----------------|-----------------|

| Memory location | FF84X2     | (Base word addı | ess)            |

|                 | FF84X2     | Status Byte     | bits 8 - 15     |

| ~               | FF84X3     | Interrupt mask  | bits Ø - 7      |

|                 |            |                 |                 |

| Bit                                                   | position                                                                                                             |                         |

|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------|

| I I I I I I I<br>I151141131121111101<br>I I I I I I I | I I I I I I I I I I I<br>91 81 71 61 51 41 31 21 11 Ø1<br>I I I I I I I I I                                          | Bit Name                |

|                                                       |                                                                                                                      | Interrupt Enable 1 (IE1 |

|                                                       |                                                                                                                      | Interrupt Enable 2 (IE2 |

|                                                       |                                                                                                                      | Interrupt Enable 3 (IE3 |

|                                                       |                                                                                                                      | Interrupt Enable 4 (IE4 |

|                                                       |                                                                                                                      | Interrupt Enable 5 (IE5 |

|                                                       |                                                                                                                      | Interrupt Enable 6 (IE6 |

|                                                       |                                                                                                                      | Interrupt Enable 7 (IE7 |

|                                                       |                                                                                                                      | SPARE                   |

|                                                       |                                                                                                                      | Input Data Rdy Lo (IDR  |

|                                                       |                                                                                                                      | Input Data Rdy Hi (IDR  |

|                                                       | ه<br>مه مه بند ها ها ها به بنه ها کا ها یک ه | Input Data Rdy (IDR     |

|                                                       |                                                                                                                      | Output Data Rdy Lo (ODR |

|                                                       |                                                                                                                      | Output Data Rdy Hi (ODR |

|                                                       |                                                                                                                      | Output Data Rdy (ODR    |

| · · · · · · · · · · · · · · · · · · ·                 | -                                                                                                                    | Output Enable Hi (OEL   |

|                                                       |                                                                                                                      | Output Enable Lo (OEH   |

# Programmable Control Register Definition Figure 1.

\_\_\_\_\_

The interrupt enables bits located in the low byte of the control word are used to enable any one of seven interrupts and are defined as follows:

IE1 - Enables interrupts to occur when the present DMA transfer is complete. This indicates to the CPU that the interface must now be re-programmed in order to perform another transfer. ( $\emptyset$ =Interrupt Enabled, l=Interrupt Masked)

IE2 - Enables interrupts on the low byte of the out going data word. This interrupt indicates to the CPU that more data can now be sent out to this byte of the port. ( $\emptyset$ =Interrupt Enabled, 1=Interrupt Masked)

IE3 - Enables interrupts on the high byte of the out going data word. This interrupt indicates to the CPU that more data can now be sent out to this byte of the port. ( $\emptyset$ =Interrupt Enabled, 1=Interrupt Masked)

IE4 - Enables interrupts on the entire sixteen bit output word. This interrupt indicates to the CPU that the entire word is now ready to transmit more data. ( $\emptyset$ =Interrupt Enabled, 1=Interrupt Masked)

IE5 - Enables interrupts on the low byte of incoming data word. Indicates to the CPU that a byte has been received on input data bits  $\emptyset$ -7 and is ready to be read. ( $\emptyset$ =Interrupt Enabled, l=Interrupt Masked)

IE6 - Enables interrupts on the high byte of the incoming data word. Indicates to the CPU that a byte has been received on input data bits 8-15 and is ready to be read. ( $\emptyset$ =Interrupt Enabled, 1=Interrupt Masked)

IE7 - Enables interrupts on the incoming data word, indicates to the CPU that data has been received on input data bits 0-15 and is now ready to be read. (0=Interrupt Enabled, l=Interrupt Masked) The high byte of the input data buffers.(Active=1)

IDRLO - Status bit indicating to the CPU that there is data present at the low byte of the input data buffers.(Active=1)

IDR - Status bit indicates to the CPU that there is data present at the input word to the data buffers.(Active = 1)

ODRHI - Status bit indicates to the CPU that the data on the high byte of the output data buffers has been transferred and more data can now be written out to it.(Active=1)

ODRLO - Status bit indicates to the CPU that the data on the low byte of the output data buffers has been transferred and more data can now be written out to it.(Active=1)

ODR - Status bit indicates to the CPU that the entire output

word has been transferred and more data can now be written out to it. (Active=1)

OELO - This is a read write control bit which when set to one enables the output data drivers  $D\emptyset$  - Dll, which are otherwise tri- state.

OEHI - This is a read write control bit which when set to one enables the output data drivers D12- D15, which are otherwise tri- state.

NOTE: OELO and OEHI must be set to one's for output port to work at all.

4-3 POLLING THEORY OF OPERATION - This portion of the manual will describe how to use the programmable parallel port in polling mode. There are two polling sequences the CPU can go thru in relation to the programmable port, the first is polling waiting to write and the second is waiting to read.

4-4 PIO POLLING TO WRITE - When the CPU is ready to write out either a word or a byte, the appropriate status bit can be tested. If the bit is found to be in the active state it indicates to the CPU that the previous data has been transferred and more data can now be sent. This operation can continue as long as there is more data to be transmitted or until the device on the other end of the interface stops reading the data being transmitted.

4-5 PIO POLLING TO READ - When the CPU is expecting input data from the parallel port it may initiate a polling sequence on the appropriate byte or word status bit. If the status bit is found to be active the CPU may read the byte or word, store it and continue to poll for as long as is required.

All control signals to the interface are manipulated by hardware which is triggered from the CPU reads or writes.

4-6 PIO WRITE OPERATIONS USING INTERRUPTS - There are three types of interrupts which can trigger the CPU to transfer data out of the parallel output port. The first is the write word interrupt. This interrupt occurs when the PIO output hardware has transferred both the high and the low bytes out to the user device and can now accept another word for transmission. The second type of write interrupt which can occur is the write high byte interrupt. This interrupt occurs when the PIO output hardware has completed the transmission of the data on the high byte of the parallel output latch and can now accept more data to be transmitted out on that byte. The final type of write interrupt which can occur is the write low byte interrupt. This interrupt occurs when the parallel output hardware has completed the transmission of the data on the low byte of the parallel output latch and can now accept more data to be transmitted out on that byte. The final type of write interrupt which can occur is the write low byte interrupt. This interrupt occurs when the parallel output hardware has completed the transmission of the data on the low byte of the parallel output port and can now accept more data to be transmitted on that byte. For any of these interrupts the appropriate interrupt mask bit must be set to a zero in the control status word. (See above).

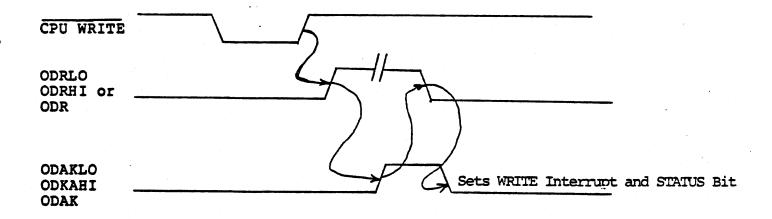

4-7 PIO READ OPERATIONS USING INTERRUPTS - Three types of interrupts exist from which the 7900 CPU can receive an interrupt from the parallel port. The first type is the Read Word Interrupt. This interrupt occurs when all 16 bits of input data have been presented to the parallel port input buffers and is ready to be read by the CPU. The second type of read interrupt which can occur is the read high byte interrupt. This interrupt occurs when data has been presented to the high input data buffer of the parallel port and is ready to be read by the CPU. The final type of read interrupt which can occur is the read low byte interrupt. This interrupt occurs when data has been presented to the high byte of the parallel port input buffers and is ready to be read by the CPU. 5-1 PIO HARDWARE DESCRIPTION - Once the CPU has determined that the output port desired is available for transfer a write operation is performed to the appropriate location in memory. On the trailing low to high transition of the write operation the output date is latched into the output buffers and the appropriate OUTPUT DATA READY signals are set active as follows:

ODRLO - Output Data Ready Low Byte ODRHI - Output Data Ready High Byte ODR - Output Data Ready Word

These signals will remain active until the appropriate Output Data Acknowledgements are received at the interface as follows:

ODAKLO - Output Data Acknowledge Low Byte ODAKHI - Output Data Acknowledge High Byte ODAK - Output Data Acknowledge Word

PIO Write Timing Figure 2.

Once the appropriate data acknowledgements go inactive, again status bits will be set to indicate to the CPU that another transfer can now be performed.

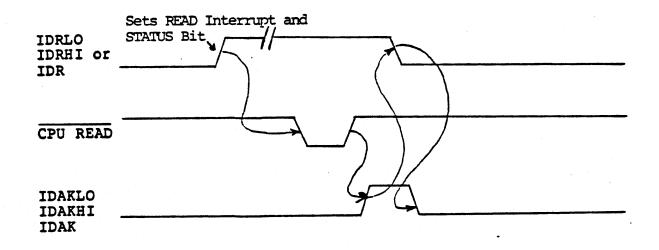

5-2 HARDWARE THEORY OF OPERATION - If a user device has data to be input to the CPU it must first set up the data at the appropriate data inputs. It must then bring the appropriate positive input data ready signal positive with the respect to the minus input as follows:

IDRLO - Input Data Ready Low Byte IDRHI - Input Data Ready High Byte IDR - Input Data Ready Word These signals as well as the data inputs must remain active until the data has been read by the CPU. On the low to high trailing edge of the CPU read of the input data port the appropriate input data acknowledges signals will be set active as follows:

IDAKLO - Input Data Acknowledge Low Byte IDAKHI - Input Data Acknowledge High Byte IDAK - Input Data Acknowledge Word

Signal timing should be as follows:

.

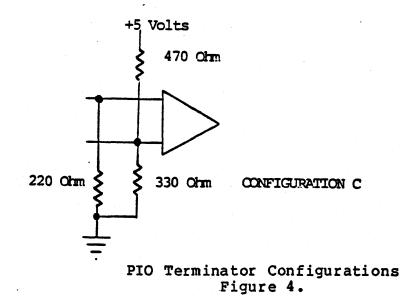

PIO Read Timing Figure 3. 5-3 PIO OPTIONING - There are three configurations which the PIO receivers can be operated under. One is as straight differential receivers with no bias or terminating resistors. The second is differential receivers with a shunt terminating resistor across the positve to minus inputs. The third configuration is that of a single ended receiver with terminating resistors at the minus input holding it at a threshold of approximately 3.0 volts and a single resistor terminator to ground on the positive input. To implement each of the three configurations see Table 3 for resistor pack values and locations.

| : ' | Configuration | A         | В   | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|---------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | R4            | -         | -   | т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R5            | -         | S   | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R6            | -         | S   | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R7            | -         | -   | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R8            | -         | -   | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R9            | -         | S   | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | RIØ           | -         | S   | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R11           | -         | -   | $\mathbf{T}$ . The second se |  |

|     | <b>R16</b>    | -         | S   | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R17           | -         | . 🖷 | P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|     | R18           | <b></b> . | -   | 1/4 W 330 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | R19           | -         | -   | 1/4 W 470 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | R20           |           | · - | 1/4 W 330 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | R21           | -         | -   | 1/4 W 330 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | R23           | -         | -   | 1/4 W 470 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|     | R24           | -         | -   | 1/4 W 330 ohm *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

### PIO Terminator Options Table 3.

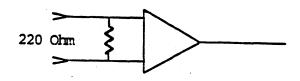

Configuration A is straight Differential with no resistors. Configuration B is straight Differential with shunt resistors. Configuration C is single ended receivers with 2.2 volt bias at the minus input and a terminator to ground on the PLU input.

Resistor S is an 8 pin 220 ohm series resistor pack Resistor P is an 8 pin 220 ohm common end resistor pack Resistor T is an 10 pin 470 ohm/330 ohm terminating resistor pack.

#### \* NOTE:

When configuration B is selected a 1/4 Watt 220 ohm resistor must be installed between the signal ends of R18 and R19, and R23 and R24. Below are three schematic representations of each of the available configurations that can exist on the input to the PIO card.

CONFIGURATION A

ς.

CONFIGURATION B

5-4 PIO INPUT/OUTPUT OPTIONING - On the P4 connector of the PIO port there are the 16 data outputs, three output control lines, three input control lines, three connections for ground, and three connections for +5 volts. These signals are all that is needed for the parallel port to operate in the mode that is described in the theory of operation of the parallel port. There are certain conditions with some interfaces that a static input is needed for some sort of status of a device. To accomplish this static input operation two mechanisms have been included in the design of the output parallel port. The first is the ability to tri-state the upper 4 bits of the sixteen output data bits and the second is the four pin header located at J6 on the circuit board. The upper four bits are made tri-state by the clearing of bit 6 in the PIO control register, this operation is described further in section 6.0 PIO Theory of Operation. Once these bits are tri-state the four jumpers located at J6 can be installed and thus the four most significant ouptuts bits on the P4 connector have been turned into static inputs that can be tested by the CPU.

5-5 PIO CONNECTOR DEFINITION - The PIO/DMA circuit has two 50 Pin card edge connectors which are designed to be used strictly for programmed parallel transfers to and from the CPU. The two connectors are designated P4 and P5, P4 being the data output connector and P5 being the data input connector. Below are lists of all the pins available at the connectors, the associated signal name for each pin and a brief description of each is given.

| Pin<br>Number                                                                                                                       | Signal<br>Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pin<br>Number                                                                            | Signal<br>Name                                                                                                                                                                                                                                                                                            |

|-------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | DATA OUT Ø<br>* DATA OUT Ø<br>DATA OUT Ø<br>DATA OUT 1<br>* DATA OUT 1<br>DATA OUT 1<br>DATA OUT 2<br>* DATA OUT 2<br>* DATA OUT 3<br>* DATA OUT 3<br>DATA OUT 3<br>DATA OUT 4<br>* DATA OUT 4<br>DATA OUT 4<br>* DATA OUT 5<br>* DATA OUT 5<br>DATA OUT 5<br>DATA OUT 5<br>* DATA OUT 6<br>* DATA OUT 6<br>* DATA OUT 6<br>* DATA OUT 7<br>* DATA OUT 7<br>* DATA OUT 7<br>DATA OUT 7<br>DATA OUT 8<br>* DATA OUT 8<br>* DATA OUT 9<br>* DATA OUT 9<br>* DATA OUT 10<br>DATA OUT 11<br>* DATA OUT 11 | 26 *<br>27<br>28 *<br>29<br>30 *<br>31<br>32 *<br>33<br>34<br>35<br>36<br>37<br>38<br>39 | DATA OUT 12<br>DATA OUT 13<br>DATA OUT 13<br>DATA OUT 13<br>DATA OUT 14<br>DATA OUT 14<br>DATA OUT 15<br>DATA OUT 15<br>DATA OUT 15<br>GND<br>+5 Volts<br>GND<br>+5 Volts<br>GND<br>+5 Volts<br>GND<br>+5 Volts<br>ODRHI<br>ODRHI<br>ODRHI<br>ODRLO<br>ODR<br>ODR<br>ODAKHI<br>ODAKHI<br>ODAKHI<br>ODAKLO |

| 25                                                                                                                                  | DATA OUT 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 50 *                                                                                     |                                                                                                                                                                                                                                                                                                           |

PIO/DMA P4 Connector Designation

## PIO/DMA P4 Connector Designation Table 4.

.

\*SIGNAL COMPLEMENT

| Pin<br>Number                                                                                                                       | Signal<br>Name                                                                                                                                                                                                                                                                                                                                                                                                             | Pin<br>Number                                        | Signal<br>Name                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24 | DATA IN Ø<br>* DATA IN Ø<br>DATA IN 1<br>* DATA IN 1<br>DATA IN 1<br>* DATA IN 1<br>DATA IN 2<br>* DATA IN 2<br>DATA IN 2<br>DATA IN 3<br>* DATA IN 3<br>DATA IN 4<br>* DATA IN 4<br>* DATA IN 4<br>* DATA IN 5<br>* DATA IN 5<br>* DATA IN 5<br>DATA IN 6<br>* DATA IN 6<br>DATA IN 7<br>* DATA IN 7<br>* DATA IN 7<br>DATA IN 8<br>* DATA IN 8<br>* DATA IN 9<br>DATA IN 9<br>DATA IN 10<br>* DATA IN 11<br>* DATA IN 11 | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | DATA IN 12<br>DATA IN 13<br>DATA IN 13<br>DATA IN 13<br>DATA IN 14<br>DATA IN 14<br>DATA IN 15<br>DATA IN 15<br>DATA IN 15<br>GND<br>+5 Volts<br>GND<br>+5 Volts<br>GND<br>+5 Volts<br>IDRHI<br>IDRHI<br>IDRHI<br>IDRLO<br>IDRLO<br>IDRLO<br>IDR<br>IDAKHI<br>IDAKHI<br>IDAKHI<br>IDAKLO<br>IDAKLO<br>IDAK |

| 25                                                                                                                                  | DATA IN 12                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                      | IDAK                                                                                                                                                                                                                                                                                                       |

PIO/DMA P5 Connector Designation

PIO/DMA P5 Connector Designation Table 5.

\*SIGNAL COMPLEMENT

6-1 DMA THEORY OF OPERATION - The purpose of this section is to describe how general purpose Direct Memory Transfers are accomplished to and from the CGC 7900.

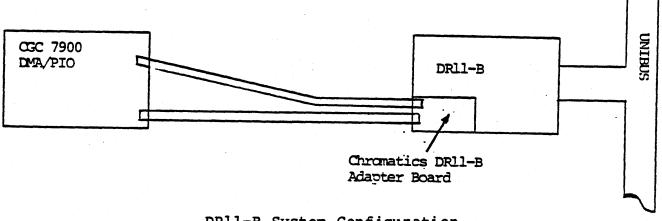

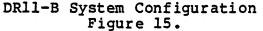

The DMA portion of the PIO/DMA card has been designed to be compatible with DEC's DR11-W, DRV11-B and DR11B DMA parallel interfaces. The details concerning the DMA hardware are in Section 7 "DMA Hardware Description". This section deals with the overall operation of the interface.

6-2 DMA TRANSFER MODES - There are two modes in which data can be transferred to or from the DMA interface. These are Burst Mode transfers and Single Cycle Mode transfers. In both modes of operation the interface is armed by the CPU, all subsequent transfers up until the end of the specified size are then done without further CPU transfer The difference lies in how the intervention. bus arbitration is handled between the CPU and the DMA board. In Burst Mode once the interface is armed the logic on the DMA board will acquire the system bus and not relinquish it until the entire transfer is complete. In Single Cycle Mode the DMA logic will share the system bus with the processor using every other memory cycle while the CPU uses the ones in between. Inside the Burst Mode and Single Cycle Mode there are two types of data transfers that can be performed, they are:

- 1 Write Words (7900 to DEC) 2 Read Words (DEC to 7900)

- NOTE: The DR11-W, DRV11-B and DR11-B interfaces also support read-modify write mode and byte transfers, these two modes are not supported on the CGC DMA board.

How each of these modes are selected and their effects on the system will be discussed in the control register definition.

6-3 DMA THEORY OF OPERATION - There are two types of transfers that can be performed to or from a DEC machine, one is a program controlled transfer and the other is a DMA type of transfer. The program controlled transfer is very similar to that of the PIO transfer in that all transfers are performed under control of the CPU. However, the protocol as to when data is valid and not valid is completely up to the user. Data is transferred via the data buffer registers using the STATUS and FUNCTION lines to determine data availability. The purpose of this section of the manual is to describe in detail how a DMA transfer operation is performed from the CGC 7900 to a receiving device. 6-4 DMA REGISTER INITIALIZATION - Before a DMA transfer is initiated by the CGC 7900 the following registers must be set up:

- 1) Word Count Register

- 2) Control Register

- 3) Bus Address Register

- 4) Extended Address Register

The final write to the Extended Address Register is the trigger to the interface to begin transferring data. Depending on whether the transfer is from CGC 7900 to DEC or from DEC to CGC 7900 the DMA logic will perform one of two sequences described in the following section.

#### 6-5 DMA BUS CYCLES

#### 7900 Bus Request Cycle

The DMA control circuitry will drive low the selected Bus Request Line on the CPU control bus and wait for the corresponding Bus Grant Signal from the CPU. Once the CPU has granted the bus and completed its present bus cycle the DMA control logic will remove its Bus Request and drive low the Bus Grant Acknowledge Signal (BGACK). The activation of this signal causes the CPU buffers to go tri-state and thus removes the CPU from the system bus. The BGACK signal causes the CPU card to remove its Bus Grant. The CPU is now completely off the bus and the DMA circuitry has full access to the entire system.

7900 DMA Logic Data Fetch Cycle

When the DMA control logic has been granted the bus by the CPU it immediately enables its output buffers, containing the address and all control bus information for the desired data. After a period of approximately 70 nanoseconds the DMA control logic asserts Address Strobe, Upper and/or Lower Data Strobe and then waits for the Data Transfer Acknowledge signal back from the selected memory (DTACK). When the DTACK signal is received the DMA logic will wait 200 nanoseconds and then latch the data into data output buffers. It will also remove Address Strobe, Upper and/or Lower Data Strobe, remove its address buffers from the bus, increment its word count register and bus address registers and release its hold of the bus by de-asserting BGACK. The CPU off will then begin normal execution exactly where it left before the bus was relinquished to the DMA control logic.

7900 Cycle Request to the DR11-W, DRV11-B or DR11-B

Once the data has been loaded into the output data buffers and is ready for transfer to the DEC interface the DMA control logic will assert CYCLE REQUEST. This will cause the DEC interface to initiate a bus cycle. This will be indicated to the 7900 DMA control logic by the assertion of the BUSY signal by the DEC interface. The 7900 DMA control logic will then remove its cycle request and wait for the BUSY signal to be de-asserted. The 7900 DMA control logic will then check to see if the transfer is complete. If not it will continue the transfer by once again requesting the system bus. If the transfer is complete the DMA logic can interrupt the CPU or can be polled by the CPU by testing the appropriate bit in the DMA Status Register.

If the transfer is to be from the DEC interface to the 7900 the 7900 Cycle Request is performed first, thus acquiring the data to be written into the 7900 memory. The 7900 DMA control logic will then perform a Bus Request Cycle as described above. Once the system bus has been acquired the following sequence will be performed:

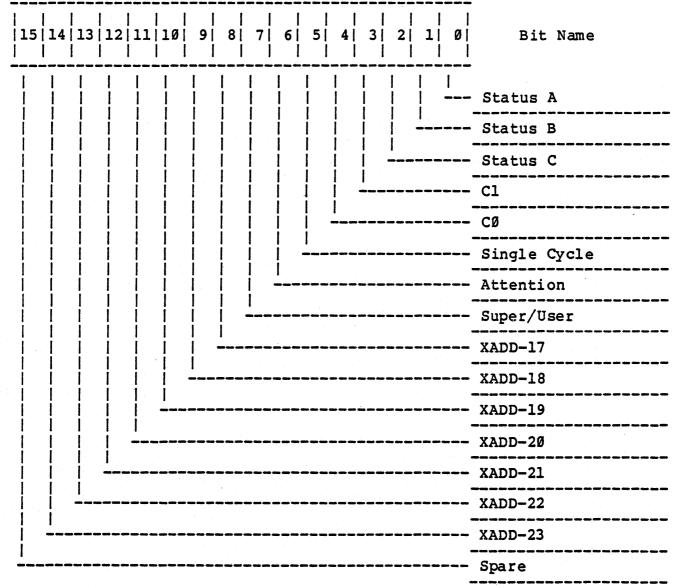

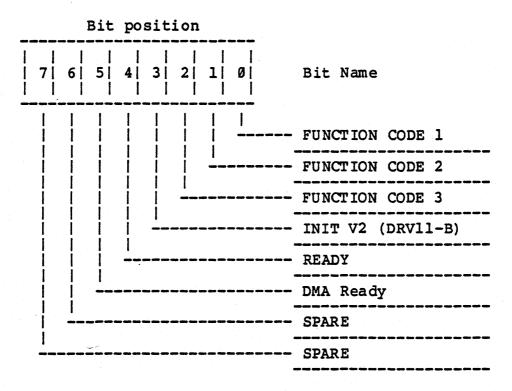

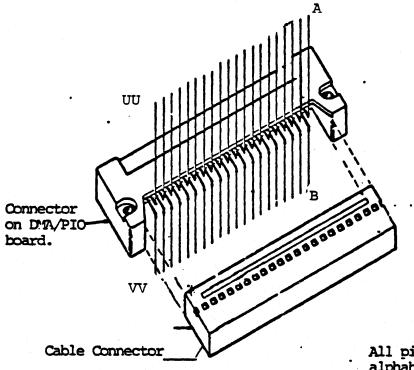

7900 Data Write Operation