CONTROL DATA®

FA722—A/B/C

DISK STORAGE CONTROLLER

DT220—C

SECOND CHANNEL FEATURE

DT716—A

DOUBLE DENSITY OPTION

GENERAL DESCRIPTION OPERATION THEORY OF OPERATION

Volume 1 of 3

HARDWARE MAINTENANCE MANUAL

|                             | REVISION RECORD                                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------|

| REVISION                    | DESCRIPTION                                                                                           |

| A                           | Manual released. Includes engineering change orders listed on correlation sheet.                      |

| (11-30-74)                  |                                                                                                       |

| В                           | Manual revised; includes Engineering Change Orders 35876 (B), 35758, and 35759. Pages 1-1,            |

| (2-5-75)                    | 6-279, 7-7, 7-11, and 7-12 are revised by ECO 35876. Pages viii (Volume 2), 4-4, 4-5, 4-8, 4-9,       |

|                             | 6-263, 6-265, 6-267, 6-269, 6-271, 6-273, 6-275, A-431, A-432, and A-433 are revised by ECO           |

|                             | 35758. Pages 6-13, 6-15, 6-17, 6-19, 6-21, 6-23, 6-25, 6-27, A-421, A-422, A-423, A-424,              |

|                             | A-425, A-426, and A-427 are revised by ECO 35759. Page 4-6 is deleted.                                |

| C                           | Manual revised; includes Engineering Change Order 35960. Page 6-261 is revised.                       |

| (2-5-75)                    |                                                                                                       |

| D                           | Manual revised; includes Engineering Change Order 35954. Pages 6-147, A-394, A-395, A-396,            |

| (2-5-75)                    | A-397, A-398, A-399, A-400, A-401, A-402, A-403, A-404, A-405, A-406, A-408, A-409, A-410,            |

|                             | A-411, A-412, A-413, A-414, A-415, A-416, A-417, A-418 and A-419 are revised.                         |

| E                           | Manual revised; includes Engineering Change Order 35681. Pages 6-1, 6-35, 6-67, 6-69, 6-75,           |

| (4-4-75)                    | 6-79, A-106, A-108, A-310, A-364, A-369 and A-406 are revised. An editorial correction is             |

|                             | made to page 4-9.                                                                                     |

| F                           | Manual revised; includes Engineering Change Order 36039. Pages vii, viii, 6-9, 6-11, 6-29, 6-31,      |

| (4-4-75)                    | A-6, A-7, A-8, A-9, A-11, A-12, A-14, A-15, A-16, A-32, A-33, A-34, A-137, A-138, A-139,              |

|                             | A-140, A-141, A-143, A-147, A-148, A-150, A-151, A-152, A-153, A-154, A-158, A-159, A-160,            |

| <u>,, </u>                  | A-162, A-163, A-165, A-184, A-194, A-195, A-196, A-197 and A-380 are revised. Miscellaneous           |

|                             | changes made to pages 6-13, 6-15, 6-17, 6-19, 6-21, 6-23, 6-25, 6-27, 6-61, 6-239, 6-241,             |

|                             | 6-243, 6-245, 6-247, 6-249, 6-251, A-29 and A-187. Pages 5-43 through 5-51 are added.                 |

| G                           | Engineering Change Order 36080. This information is included in Revision D.                           |

| (4-4-75)                    |                                                                                                       |

| H                           | Manual revised; includes Engineering Change Order 36247 (publications change only).                   |

| (4-30-75)                   | Title Page (Vol. 1). Revision Record, Correlation Sheet, vii (Vol. 1), 1-1, 3-2 through 3-7, 3-9      |

|                             | through 3-12, 3-229, 3-250, 3-287, 3-289, 3-292, 3-294, 3-300, Comment Sheet (Vol. 1), Title          |

|                             | Page (Vol. 2), Revision Record, Correlation Sheet, viii (Vol. 2), 4-11, 6-5, 6-147, 6-171, 6-205,     |

|                             | 6-210, 6-211, 6-212, 6-213, 6-217, 6-252 through 6-257, 6-259, 6-261, 6-277, Comment Sheet            |

|                             | (Vol. 2), Front Cover (Vol. 3), Title Page (Vol. 3), Revision Record, Correlation Sheet, vii (Vol. 3) |

|                             | A-3, Comment Sheet (Vol. 3), are the pages changed. New Pages added are 6-211.1, 6-213.1,             |

|                             | 6-257.0, 6-257.1, DT716-A Yellow Divider, A-437 through A-446. Appendix B Divider deleted.            |

| J                           | Manual revised; includes Engineering Change Order 36235. Pages 4-9, 6-1, 6-7, 6-9, 6-11, 6-15,        |

| (4-30-75)                   | 6-23, 6-29, 6-31, 6-33, 6-37, 6-39, 6-61 of (Volume 2), A-5, A-6, A-9, A-12, A-15, A-16, A-18         |

|                             | A-37, A-136, A-137, A-147, A-153, A-156, A-162, A-164, A-165, A-179, A-187, and A-204 of              |

|                             | (Volume 3) are revised. Engineering Change Order 35791 is included in this revision.                  |

| K                           | Manual revised; includes Field Change Order 36293. Pages 6-1, 6-9, 6-31, 6-61, and A-29 are           |

| (7-11-75)                   | revised. Miscellaneous changes are made to Cover, Title Page, v in Volumes 1, 2, and 3, 1-1,          |

| Publication No.<br>60428500 |                                                                                                       |

Address comments concerning this manual to:

Control Data Corporation

Publications and Graphics Division

4201 North Lexington Avenue

Arden Hills, Minnesota 55112

or use Comment Sheet in the back of this manual.

| EVISION   | DESCRIPTION                                                                                  |

|-----------|----------------------------------------------------------------------------------------------|

| K         | 7-1, and 7-2.                                                                                |

| (Cont'd)  | 1 2) (114 1 1)                                                                               |

| L         | Manual revised; includes Field Change Order 36377 and Engineering Change Order 36079. Field  |

| (7-23-75) | Change Order 36377. Pages 6-213, 6-219, A-88, A-354, and A-361 are revised. Engineering      |

| (1 20 10) | Change Order 36079. Pages A-440, A-441, A-442, A-443, and A-446 are revised. Miscellane      |

|           | changes are made to vii, 6-7, 6-13, 6-15, 6-17, 6-19, 6-21, 6-23, 6-25, 6-27, 6-33, 6-37, 6- |

|           | and 6-279. Pass On-Pass Back Wiring (Divider) and A-447 through A-454 are added.             |

| M         | Manual revised; includes Field Change Order 36470. Pages 6-1 and 6-61 are revised. Editoria  |

| (9-26-75) | correction is made to page 6-63.                                                             |

|           |                                                                                              |

|           |                                                                                              |

|           | ·                                                                                            |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           | 11.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11 1.11.                      |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

| -         |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

|           |                                                                                              |

- 1

# MANUAL TO EQUIPMENT LEVEL CORRELATION SHEET

| SHEET_1       | _OF1_      | EQUIPMENT |       |       |       |       |   |  |

|---------------|------------|-----------|-------|-------|-------|-------|---|--|

| MANUAL<br>REV | FCO OR ECO | FA722     | FA722 | DT220 | DT716 | FA722 |   |  |

| A             | Released   | A01       | В01   | C01   | A01   | A 01  |   |  |

| -             | ECO35758   | A 01      | B01   | C01   | A01   |       |   |  |

| -             | ECO35759   | A01       | B01   | C01   | A 01  |       |   |  |

| В             | ECO35876   | A 01      | B01   | C01   | A 01  |       |   |  |

| C             | ECO35960   | A 01      | B01   | C01   | A 01  |       | - |  |

| D             | ECO35954   | A 01      | B01   | C01   | A 01  | ļ     |   |  |

| E             | ECO35681   | A01       | B01   | C01   | A01   |       |   |  |

| $\mathbf{F}$  | ECO36039   | A01       | B01   | C01   | A01   |       |   |  |

| G             | ECO36080   | A01       | B01   | C01   | A01   |       |   |  |

| н             | ECO36247   | A01       | В01   | C01   | A01   |       |   |  |

| J             | ECO36235   | A02       | В02   | C02   | A01   | C02   |   |  |

|               | ECO35791   | A.02      | В02   | C02   | A.01  | C02   |   |  |

| K             | FCO36293   | A03       | В03   | C03   | A01   | C03   |   |  |

| L             | ECO36079   | A03       | B03   | C03   | A 01  | C03   |   |  |

|               | FCO36377   | A04       | B04   | C04   | A01   | C04   |   |  |

| M             | FCO36470   | A05       | B05   | C04   | A01   | C04   |   |  |

|               |            |           |       |       |       |       |   |  |

| 604285        | 00         |           |       |       |       |       |   |  |

#### PREFACE

This manual provides level 2 hardware maintenance information for the CONTROL DATA © FA722-A/B/C Disk Storage Controller and some of its related options. The FA722-A/B serves as the primary control element in CDC® 7054/844 Disk Storage Subsystems. Level 2 maintenance includes the following activities.

Preventive maintenance

Replacement of defective logic cards, power modules, and indicator lights

Adjustments

000000000

Cable and backpanel repair

The manual is divided into three volumes. Volume 1 contains equipment descriptions and operational theory. Volume 2 contains installation procedures, maintenance information, and diagrams. Volume 3 contains parts data, wire lists, and option information.

The following equipment manuals provide maintenance and reference information for equipment used in disk storage subsystems. The product manuals provide information pertaining to subsystem interaction with computer systems. Refer to the Literature Distribution Services catalog for the latest revisions of all manuals.

### EQUIPMENT MANUALS

| Control Data Publication                                       | Manual Type             | Publication No. |

|----------------------------------------------------------------|-------------------------|-----------------|

| FA710/FA719/FA720/FA722<br>Disk Storage Controller             | Hardware Reference      | 60364500        |

| DC144-A/B, DT198-A, DC401-A<br>Mass Storage Extender           | Customer Engineering    | 60392600        |

| BR30X Disk Storage Unit                                        | Maintenance             | 70618400        |

| BR30X Disk Storage Unit                                        | Diagrams and Wire Lists | 70618500        |

| BR30X Disk Storage Unit                                        | Parts List              | 70618600        |

| 84X/975X Disk Storage Unit                                     | Maintenance Aids        | 70619100        |

| TF201 Maintenance Console                                      | Customer Engineering    | 58032700        |

| BB372-A Core Storage Module/<br>FV444-A Power Regulator Module | Customer Engineering    | 60346500        |

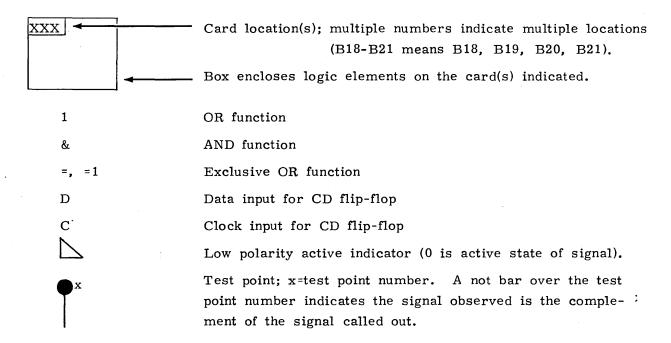

| TTL Key to Logic Symbols                                       | Customer Engineering    | 60406000        |

# PRODUCT MANUALS

| Control Data Publication                    | Manual Type               | Publication No. |

|---------------------------------------------|---------------------------|-----------------|

| Disk Storage Subsystem                      | General Information       | 60364400        |

| Disk Storage Subsystem                      | Operation and Programming | 60363900        |

| Section 2 Stations/Subsystems               | Site Preparation          | 60277500        |

| SCOPE 3.4 Operating System                  | Installation Handbook     | 60307400        |

| KRONOS 2.1 Operating System                 | Installation Handbook     | 60407500        |

| Network Operating System (NOS) 1.0.0        | Installation Handbook     | 60435700        |

| System Maintenance Monitor (SMM)            | Reference                 | 60160600        |

| Buffer Controller Diagnostics               | Reference                 | 60400300        |

| Buffer Controller Assembly Language (BUCAL) | Reference                 | 60372000        |

# CONTENTS

| VOLUME 1                          |     | Maintenance Console Interface                    | 3-13  |

|-----------------------------------|-----|--------------------------------------------------|-------|

|                                   |     | Block Transfer Interface                         | 3-13  |

| 1. GENERAL DESCRIPTION            |     | Coupler/Normal Channel Inter-                    | -     |

| Introduction                      | 1-1 | face                                             | 3-15  |

| Expansion Options                 | 1-1 | Control Logic/Subsystem Pro-<br>cessor Interface | 3-16  |

| Double Density Option             | 1-1 | Coupler/Control Logic Inter-                     |       |

| Controlware                       | 1-1 | face                                             | 3-19  |

| Functional Description            | 1-2 | Coupler Theory                                   | 3-22  |

| Coupler                           | 1-2 | Component Theory                                 | 3-22  |

| Subsystem Processor               | 1-3 | Operational Sequences                            | 3-33  |

| Control Logic                     | 1-3 | Subsystem Processor/Core Memor                   | у     |

| Core Memory                       | 1-4 | Theory                                           | 3-53  |

| Physical Description              | 1-4 | Component Theory                                 | 3-54  |

| Dimensions                        | 1-6 | Subsystem Processor Instruction Sequences        | 3-62  |

| Environmental Requirements        | 1-7 | Control Logic Theory                             | 3-160 |

| Power Requirements                | 1-7 | Component Theory                                 | 3-160 |

| 2. OPERATION                      |     | Operational Sequences                            | 3-185 |

| Introduction                      | 2-1 | VOLUME 2                                         |       |

| Auxiliary Operator Panel Controls | 0.1 |                                                  |       |

| and Indicators                    | 2-1 | 4. INSTALLATION AND CHECKO                       | UT .  |

| Power Controls and Indicators     | 2-2 |                                                  |       |

| Power-up/Power-down Procedure     | 2-3 | 5. MAINTENANCE                                   |       |

| Power-down                        | 2-3 |                                                  |       |

| Power-up                          | 2-4 | 6. DIAGRAMS                                      |       |

| Disk Storage Unit Controls        | 2-5 |                                                  |       |

| Disk Pack Exchange Procedure      | 2-5 | · ·                                              |       |

|                                   |     | VOLUME 3                                         |       |

| 3. THEORY OF OPERATION            |     | 7. PARTS DATA                                    |       |

| Introduction                      | 3-1 | ·· Imitis billi                                  |       |

| Interfaces                        | 3-1 | APPENDIX A. WIRE LISTS                           |       |

| PPU Interface                     | 3-1 | THE LINE TO IT                                   |       |

| Pass On/Pass Back Interfaces      | 3-3 | ·                                                |       |

| Control Logic/Disk Storage        | 3-4 |                                                  |       |

60428500 H

# FIGURES

| 1-1  | Controller Block Diagram                                    | 1-2                   | 3-24 | Common RAD Activity                                            | 3-67  |  |

|------|-------------------------------------------------------------|-----------------------|------|----------------------------------------------------------------|-------|--|

| 1-2  | Controller Component Locations                              | 1-5                   | 3-25 | Common ROP Activity                                            | 3-68  |  |

| 2-1  | Auxiliary Operator Panel                                    | 2-1                   | 3-26 | Common STO Activity                                            | 3-69  |  |

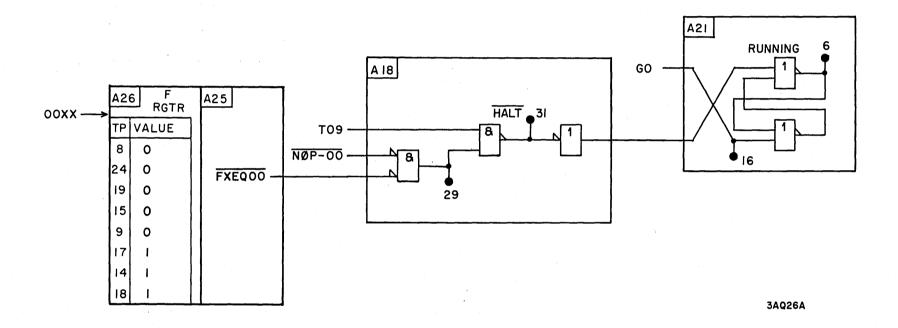

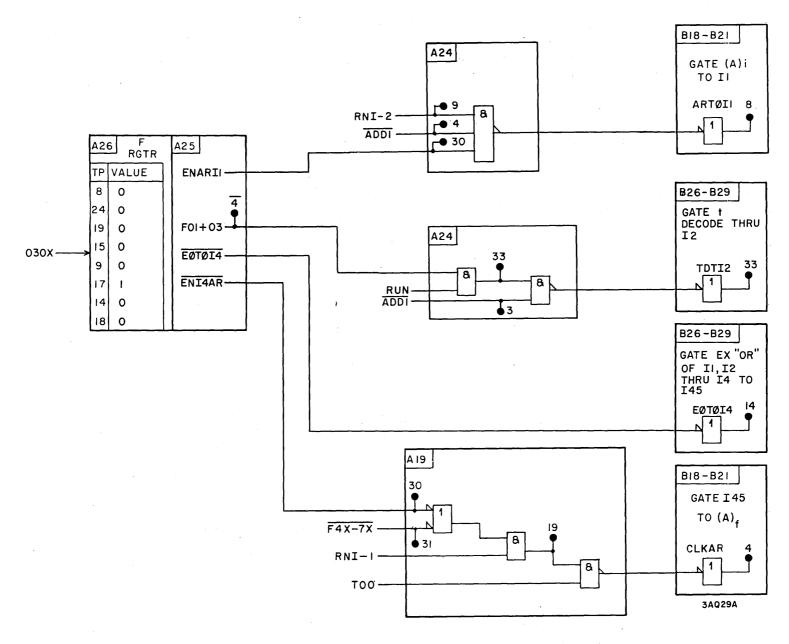

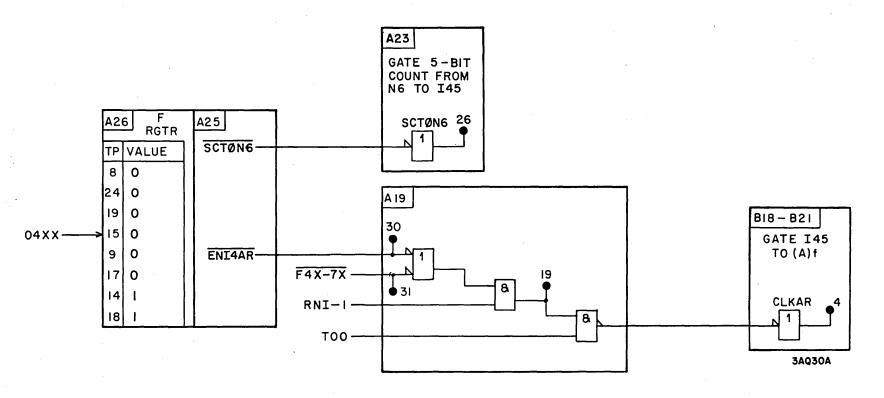

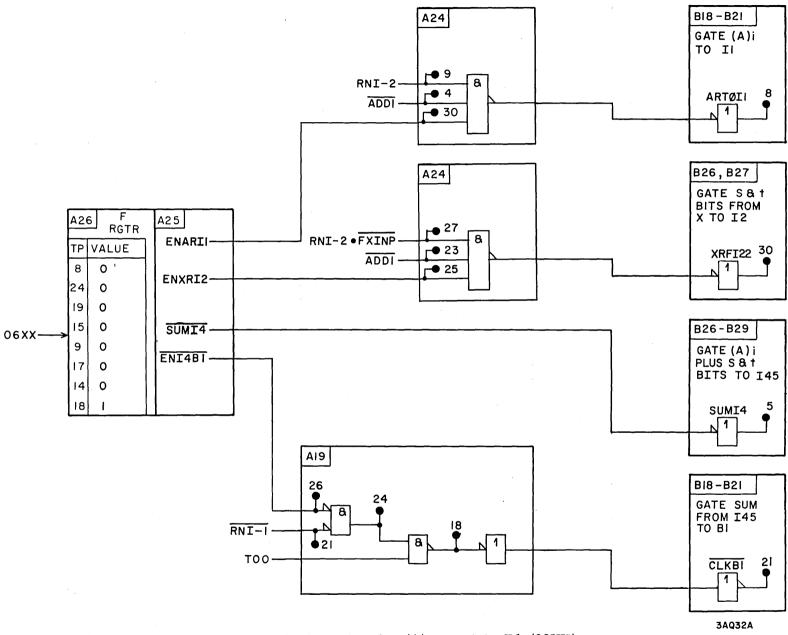

| 2-2  | Power Controls and Indicators                               | 2-3                   | 3-27 | Selective Stop (00XX)                                          | 3-71  |  |

| 2-3  | DSU Controls and Indicators                                 | 2-7                   | 3-28 | Selective Set Bit t of A (010X)                                | 3-72  |  |

| 3-1  | Interface Diagram                                           | 3-2                   | 3-29 | Selective Clear Bit t of A                                     | 0 = 4 |  |

| 3-2  | Coupler Block Diagram                                       | 3-23                  |      | (020X)                                                         | 3-74  |  |

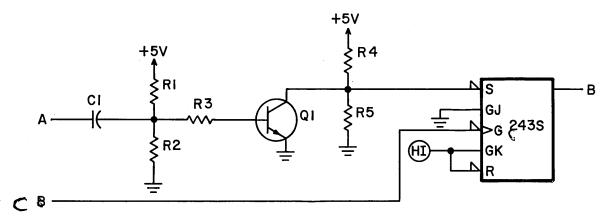

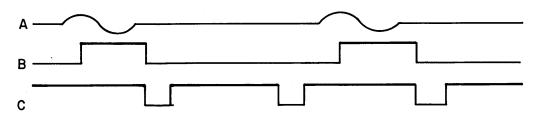

| 3-3  | Pulsed to TTL Converter                                     | 3-24                  | 3-30 | Selective Complement Bit t of A (030X)                         | 3-75  |  |

| 3-4  | Waveforms for Pulsed to TTL Converter                       | 3-24                  | 3-31 | Count of Leading Zeros in A; to A; (04XX)                      | 3-76  |  |

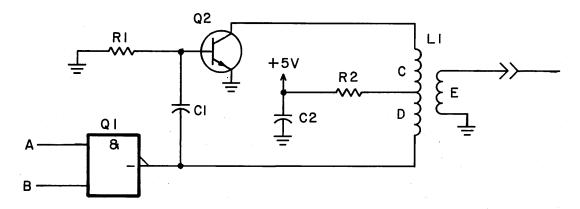

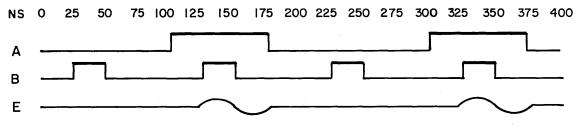

| 3-5  | TTL to Pulsed Converter                                     | 3-25                  | 3-32 | Shift (A) Right, t Places                                      |       |  |

| 3-6  | Waveforms for TTL to Pulsed Converter                       | 3-26                  | 3-33 | (05XX)                                                         | 3-78  |  |

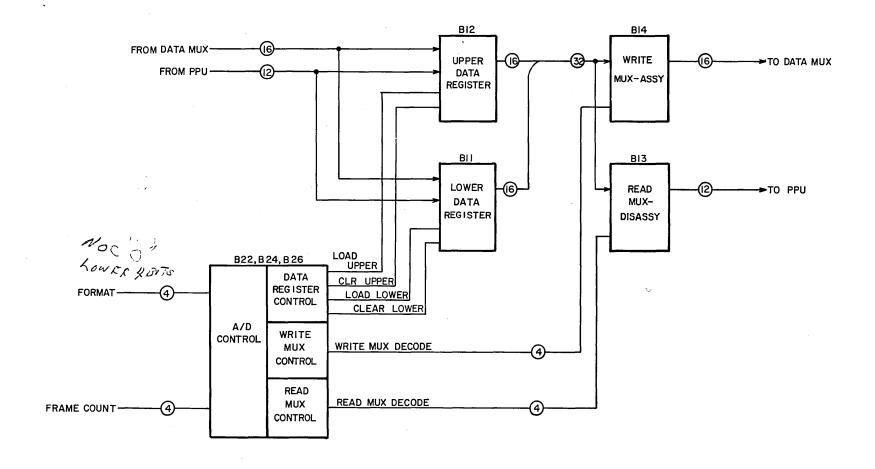

| 3-7  | Assembly/Disassembly Components                             | 3-28                  |      | (06XX) Transfer (A) + s, t to B2                               | 3-79  |  |

| 3-8  | Data Multiplexer Components                                 | 3-32                  | 3-34 | (07XX)                                                         | 3-80  |  |

| 3-9  | Connect Logic                                               | 3-34                  | 3-35 | Set Condition Equal: Internal                                  |       |  |

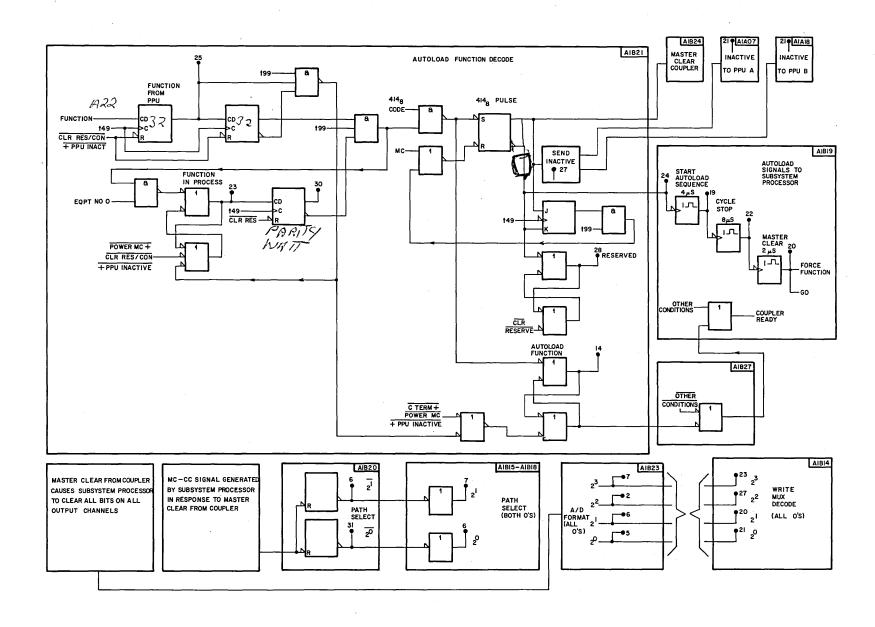

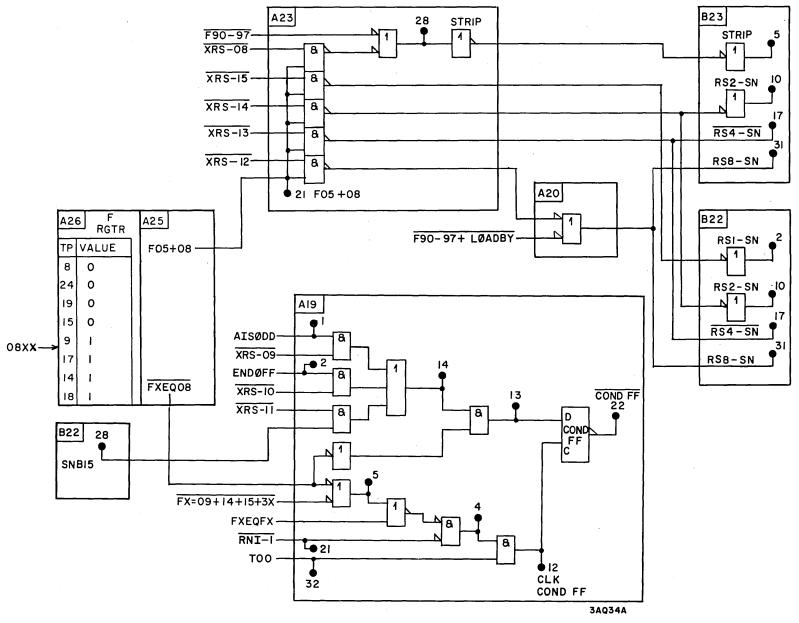

| 3-10 | Autoload Initiation Logic                                   | 3-37                  |      | Tests (08XX)                                                   | 3-81  |  |

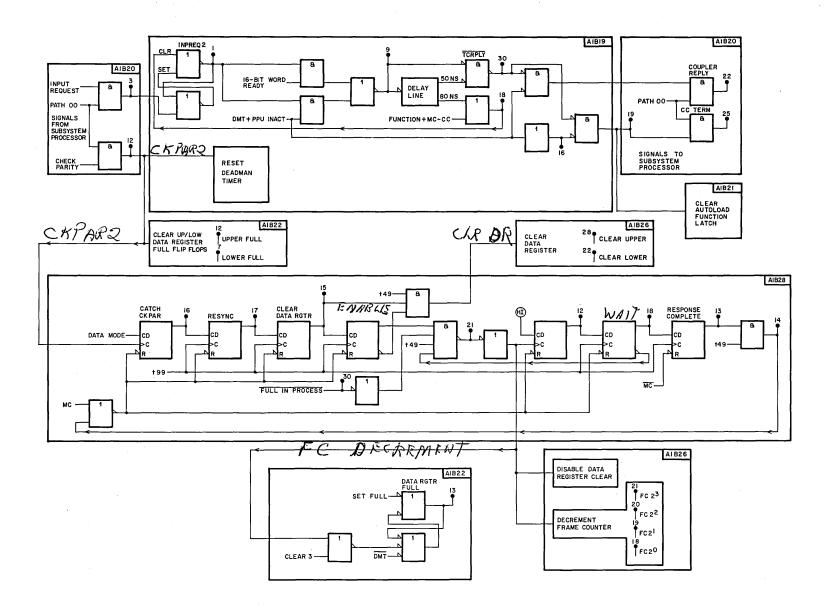

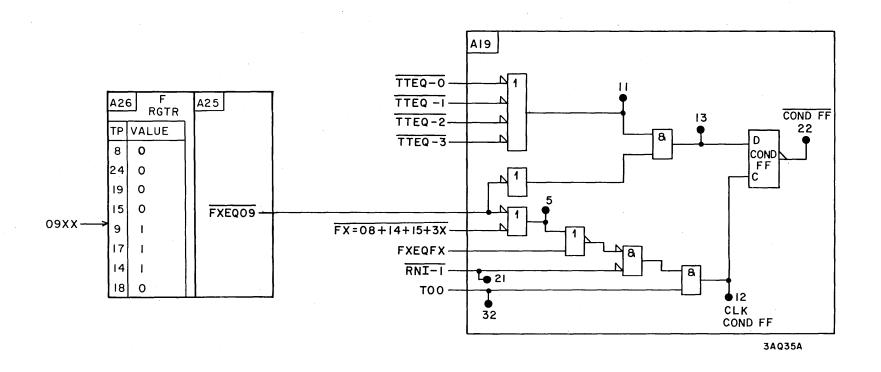

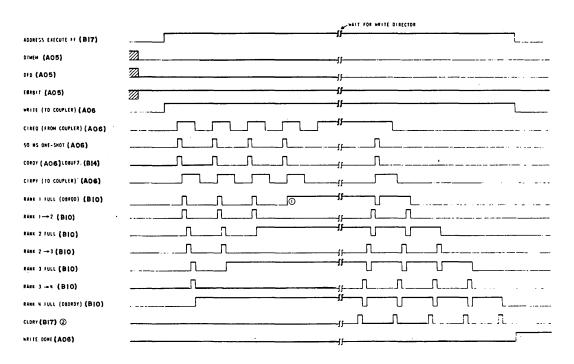

| 3-11 | PPU/Coupler Activity During<br>Autoload or PPU Write Opera- |                       | 3-36 | Set Condition Equal to Bit t of Channel s (09XX)               | 3-83  |  |

|      | tions                                                       | 3-38                  | 3-37 | Selective Set Bit t of Channel 0 (040X) or Set Bit t and Clear |       |  |

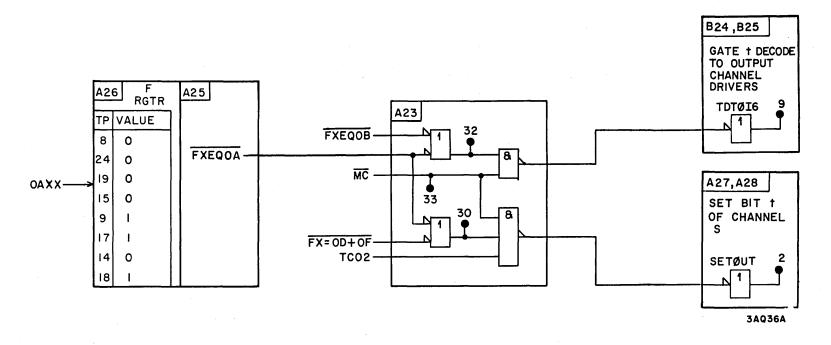

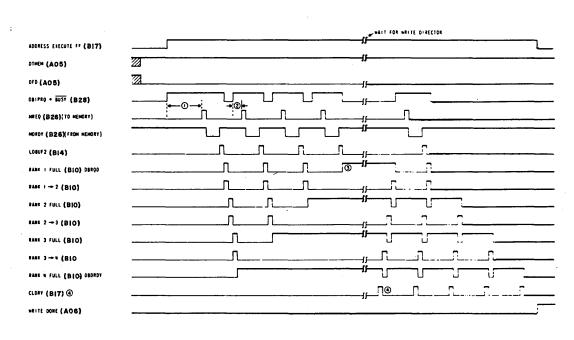

| 3-12 | Subsystem Processor/Coupler<br>Activity During Autoload     | 3-39                  |      | All Other Bits of Channel s (s \neq 0) (0AsX)                  | 3-84  |  |

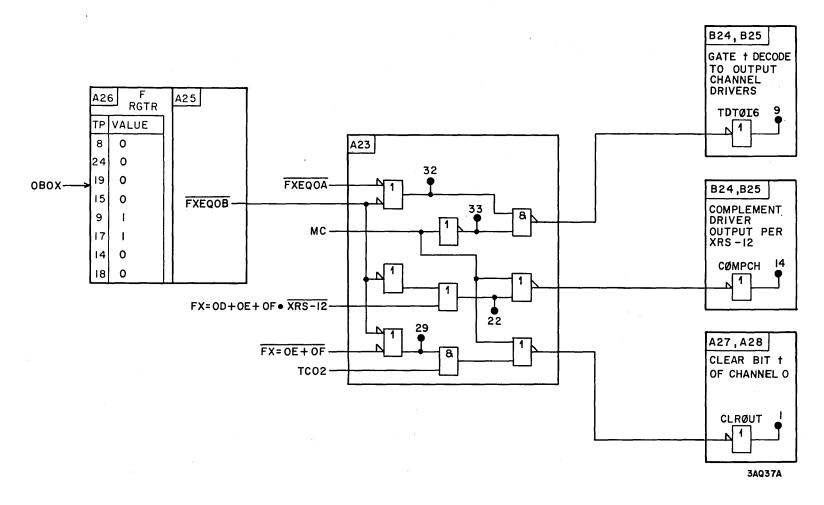

| 3-13 | Function Logic                                              | 3-42                  | 3-38 | Selective Clear Bit t of                                       |       |  |

| 3-14 | Subsystem Processor Generated Status Reply                  | 3-44                  |      | Channel 0 (0B0X) Input to A from Channel s                     | 3-85  |  |

| 3-15 | Coupler Generated Status Re-                                |                       | 0 00 | (0CX0)                                                         | 3-87  |  |

|      | ply                                                         | 3-46                  | 3-40 | Set Channel 0 from A (0DX0)                                    | 3-88  |  |

| 3-16 | Coupler to Control Logic Transfers                          | -<br>3 <b>-</b> 48    | 3-41 | Clear Channel 0 from A (0E0X                                   | )3-89 |  |

| 3-17 | Control Logic to Coupler Transfers                          |                       | 3-42 | Transfer (A) to Channel s (0FXX)                               | 3-91  |  |

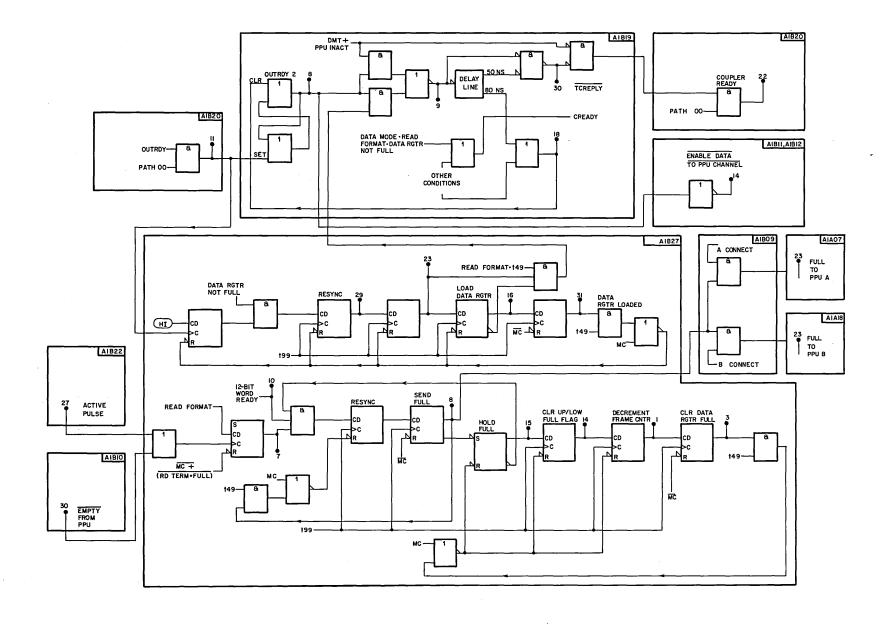

| 3-18 | Coupler to PPU Transfers                                    | 3-51                  | 3-43 | Add - No Address (10XX)                                        | 3-92  |  |

|      | Subsystem Processor/Core                                    | 0 01                  | 3-44 | Subtract - No Address (11XX)                                   | 3-94  |  |

|      | Memory Data Flow                                            | 3-55<br>3 <b>-</b> 60 | 3-45 | Exclusive OR - No Address (12XX)                               | 3-95  |  |

|      | Memory Interface Timing                                     | 3-00                  | 3-46 | Logical Product - No Address                                   |       |  |

| J-41 | Key to Instruction Sequence<br>Symbols                      | 3-62                  |      | (13XX)                                                         | 3-97  |  |

| 3-22 |                                                             | 3-65                  | 3-47 | Test Index B1 - No Address<br>(14XX)                           | 3-98  |  |

| 3-23 | Common RNI Activity                                         | 3-66                  | 3-48 | Test Index B2 - No Address                                     | 3-100 |  |

| 3-         | <b>4</b> 9 | Load A Complement - No Address (16XX)     | 3-101 | 3-81  | Unconditional Jump (B8XX -<br>BFXX)                 | 3-147          |

|------------|------------|-------------------------------------------|-------|-------|-----------------------------------------------------|----------------|

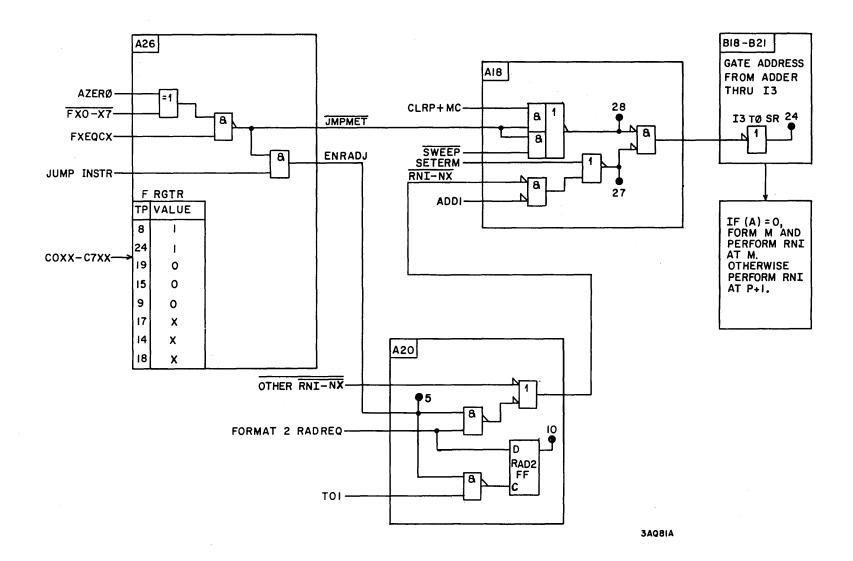

| 3 –        | 50         | Load from (A) (17XX)                      | 3-103 | 3-82  | A Zero Jump (C0XX - C7XX)                           | 3-148          |

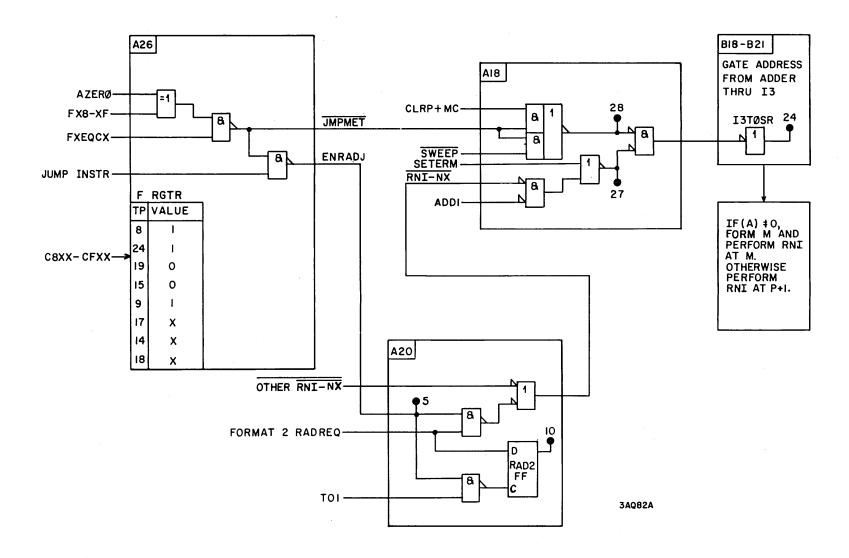

| 3-         | 51         | Direct (X0 or X8)                         | 3-106 | 3-83  | A Nonzero Jump (C8XX -                              |                |

| 3-         | 52         | Direct/Index B1 (X1 or X9)                | 3-107 |       | CFXX)                                               | 3-149          |

| 3-         | 53         | Direct/Index B2 (X2 + XA)                 | 3-108 | 3-84  | A Positive Jump (D0XX - D7XX)                       | 3-151          |

| 3-         | 54         | Relative Forward (X3 or XB)               | 3-109 | 3-85  | A Negative Jump (D8XX -                             | 0 10.          |

| 3-         | 55         | Indirect (X4 or XC)                       | 3-111 |       | DFXX)                                               | 3-152          |

| 3 -        | 56         | Indirect/Index B1 (X5 or XD)              | 3-112 | 3-86  | Condition True Jump (E0XX -                         |                |

| 3-         | 57         | Indirect/Index B2 (X6 or XE)              | 3-114 |       | E7XX)                                               | 3-154          |

| 3-         | 58         | Relative Backward (X7 or XF)              | 3-115 | 3-87  | Condition False Jump (E8XX - EFXX)                  | 3-155          |

| 3-         | 59         | Enter A with Address (18XX - 1FXX)        | 3-116 | 3-88  | Control Logic Block Diagram · Basic Data Path       |                |

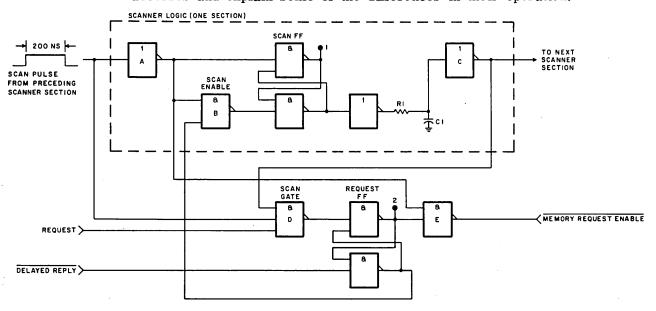

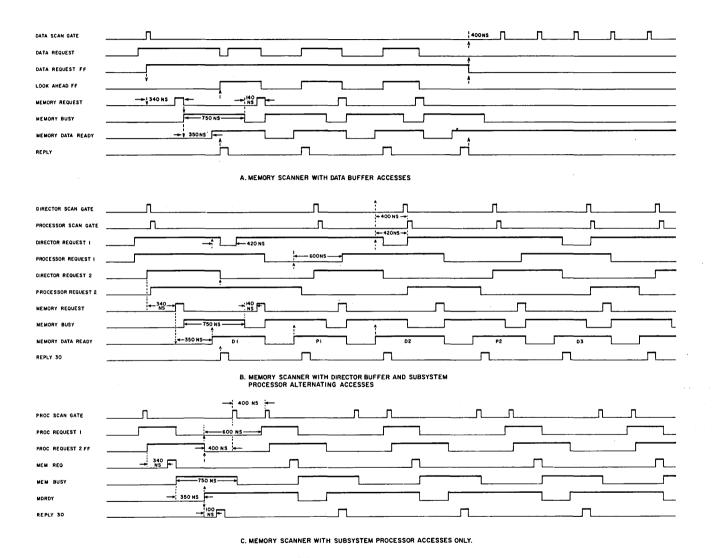

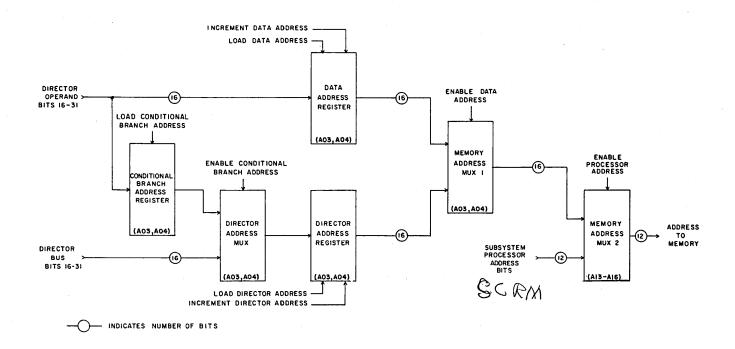

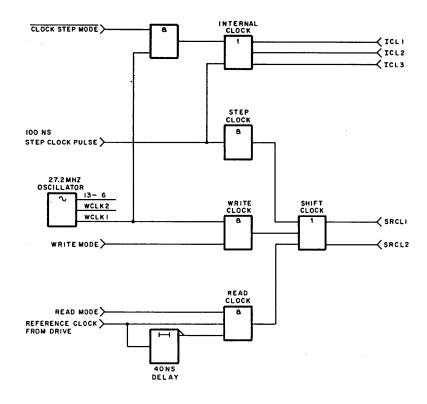

| 3-         | 60         | Enter B1 with Address (20XX - 27XX)       | 3-117 | 3-89  | Simplified Logic Diagram -<br>Memory Scanner        | 3-162          |

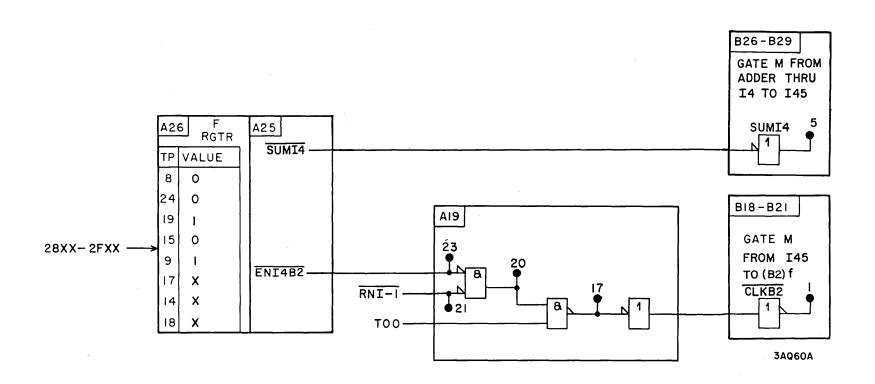

| 3-         | 61         | Enter B2 with Address (28XX - 2FXX)       | 3-119 | 3-90  | Memory Scanner Access Timing Diagram                | 3-163          |

| 3-         | 62         | Test Index B1 (30XX - 37XX)               | 3-120 | 3-91  | Address Multiplexer Block                           |                |

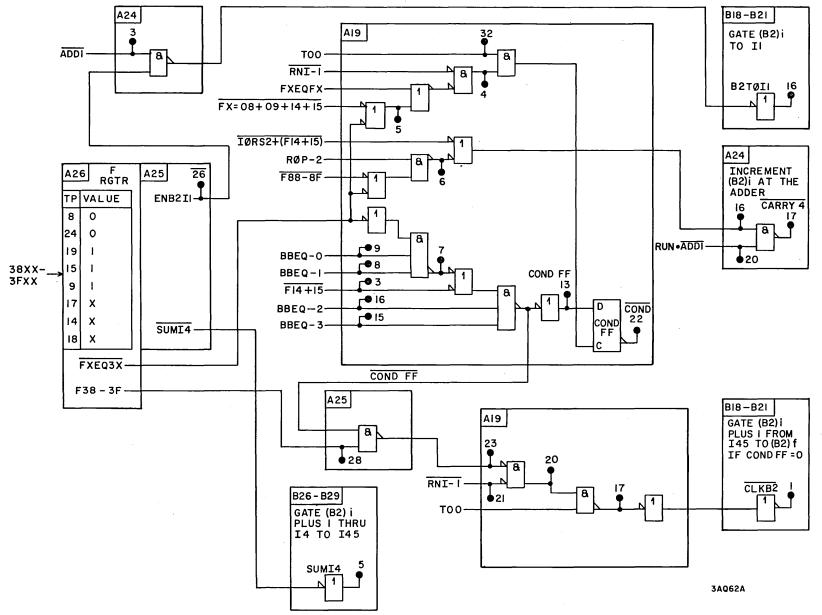

| 3-         | 63         | Test Index B2 (38XX - 3FXX)               | 3-121 |       | Diagram                                             | 3-167          |

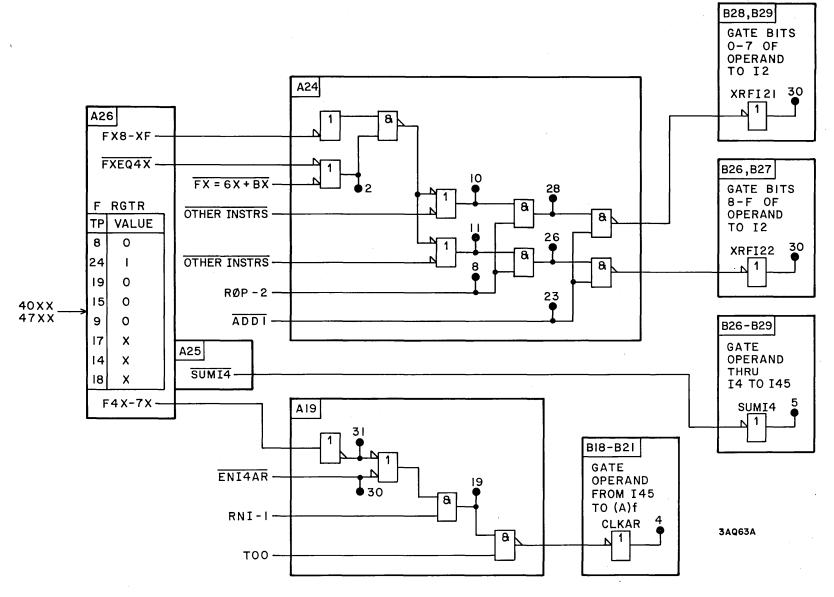

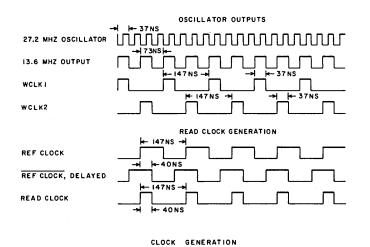

| 3-         | 64         | Load A (40XX - 47XX)                      | 3-123 | 3-92  | Clock Generation                                    | 3-174          |

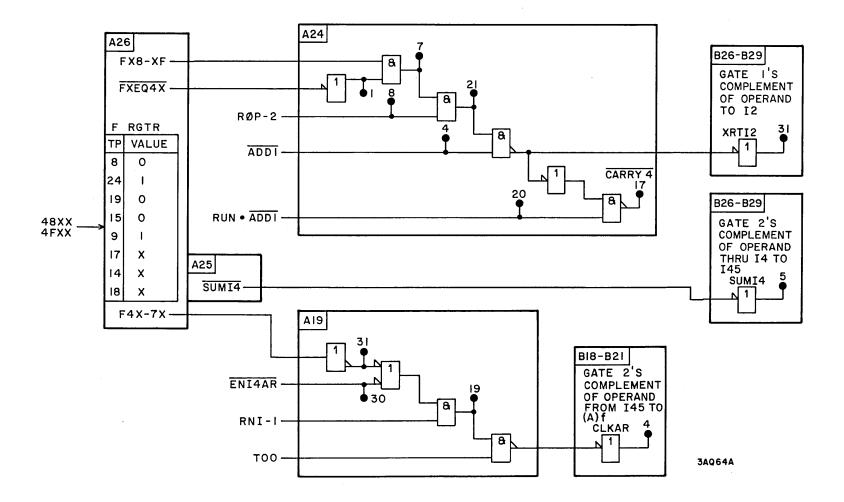

| 3-         | 65         | Load A Complement (48XX - 4FXX)           | 3-124 | 3-93  | Data Coding - Modified Frequency Modulation         | 3-175          |

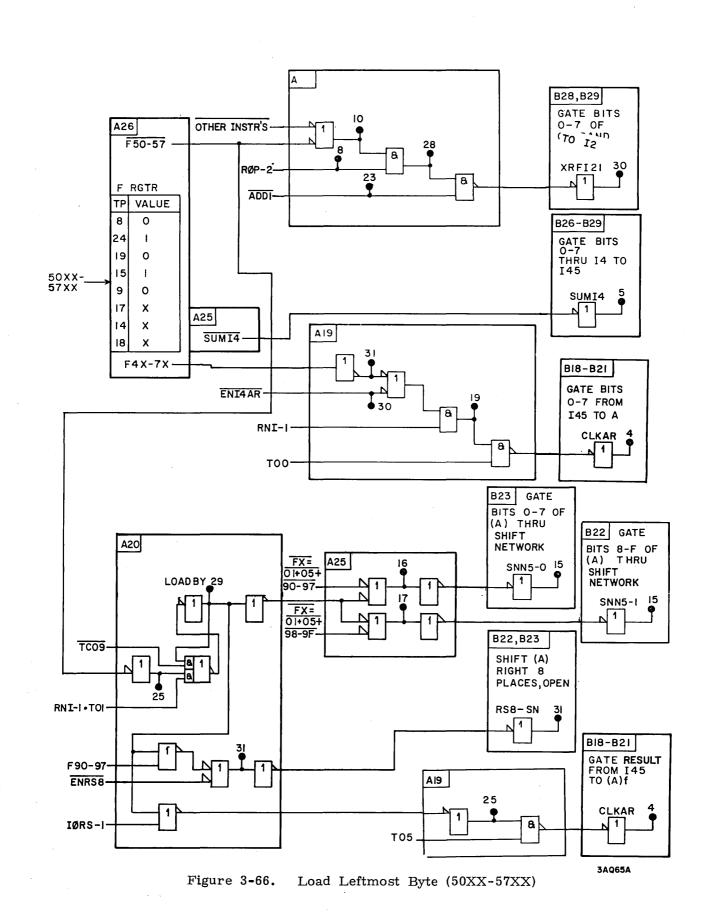

| 3-         | 66         | Load Leftmost Byte (50XX - 57XX)          | 3-125 | 3-94  | Open Cable Detector Current<br>Supply Block Diagram | 3-180          |

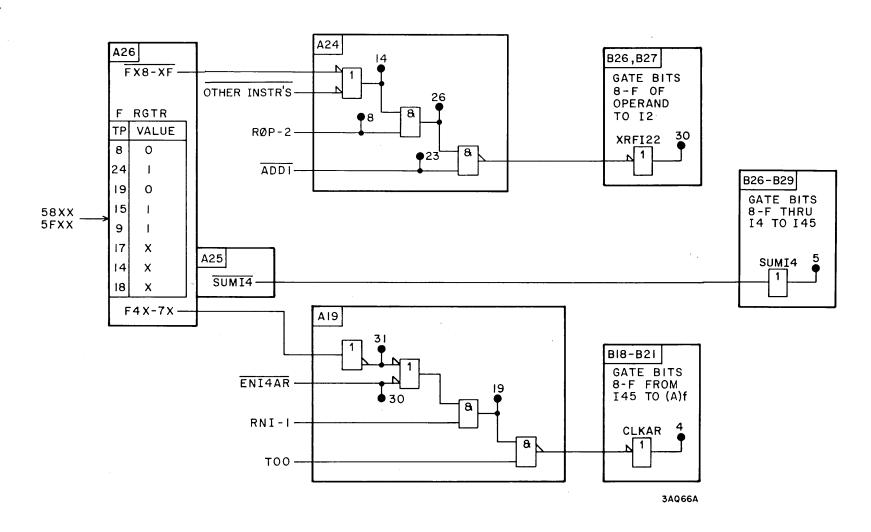

| 3-         | 67         | Load Rightmost Byte (58XX - 5FXX)         | 3-127 | 3-95  | Data Resynchronization Timing Diagram               | 3-182          |

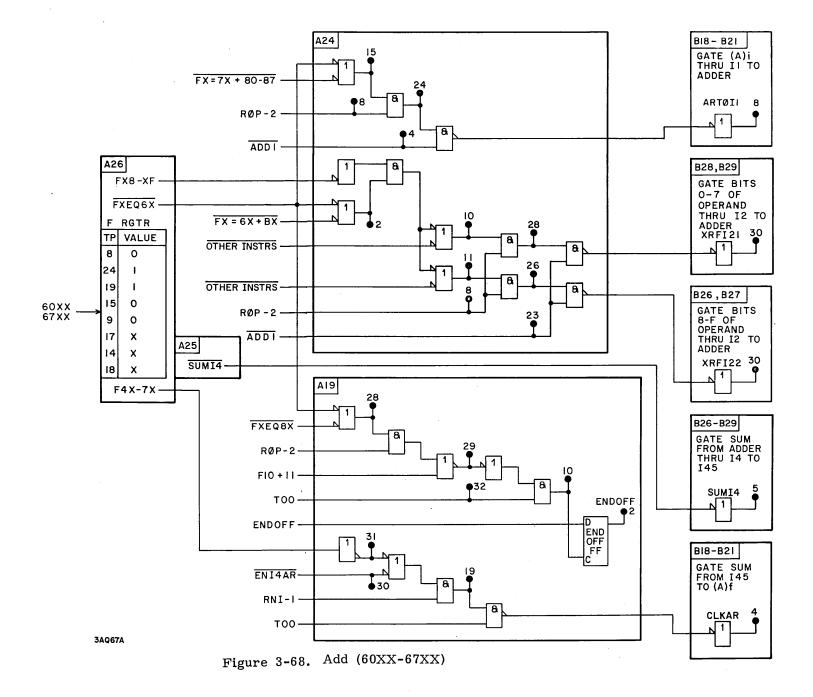

| 3-         | 8          | Add (60XX - 67XX)                         | 3-129 | 3-96  | Data Path Switching Block                           | 0.40           |

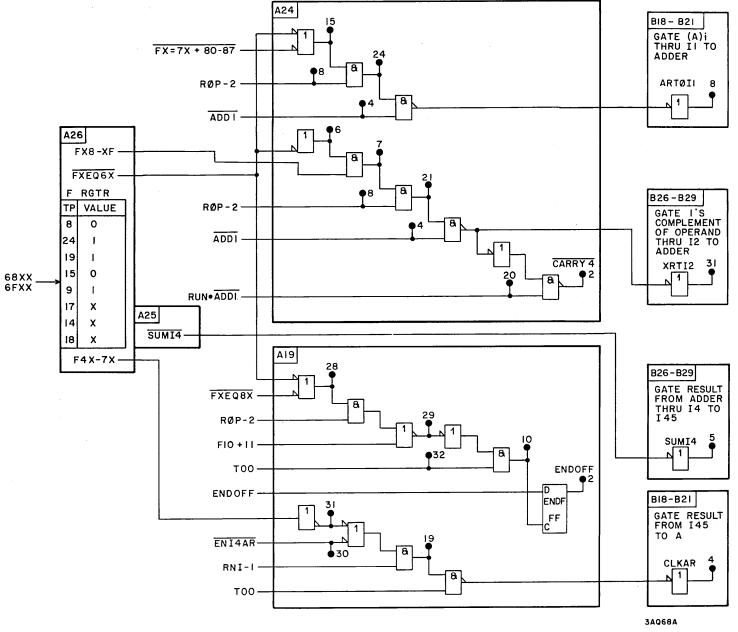

| 3-         | 69         | Subtract (68XX - 6FXX)                    | 3-130 |       | Diagram                                             | 3-184          |

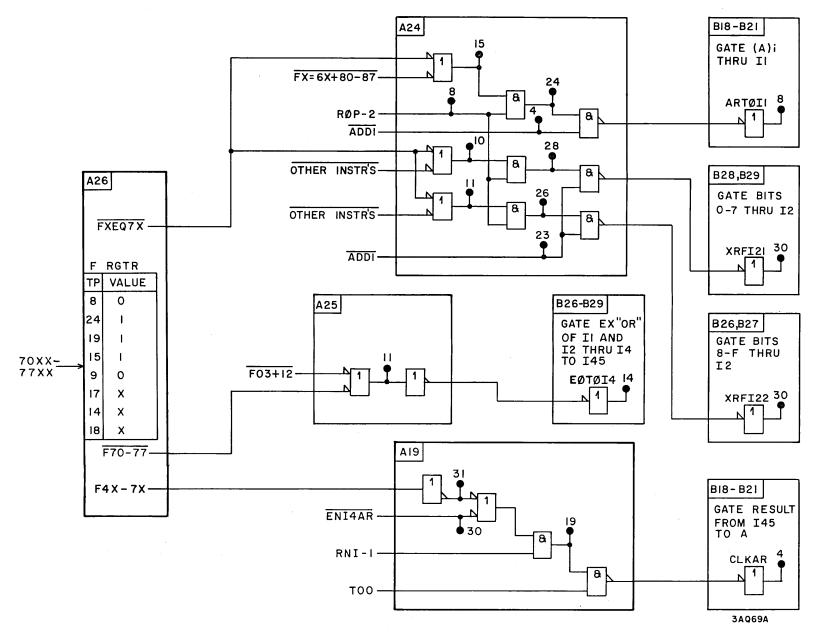

| 3-         | 70         | Exclusive OR (70XX - 77XX)                | 3-131 |       | Load Director Buffer - 0018                         | 3-188          |

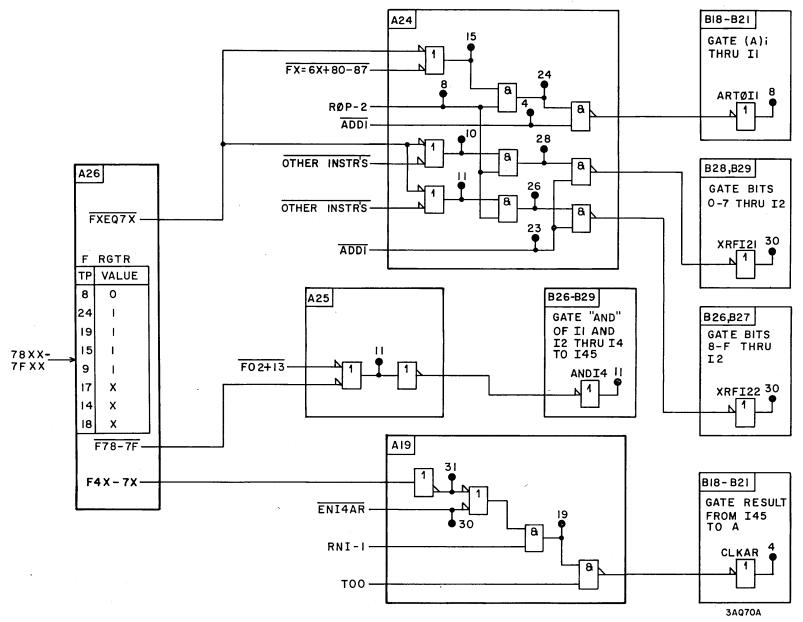

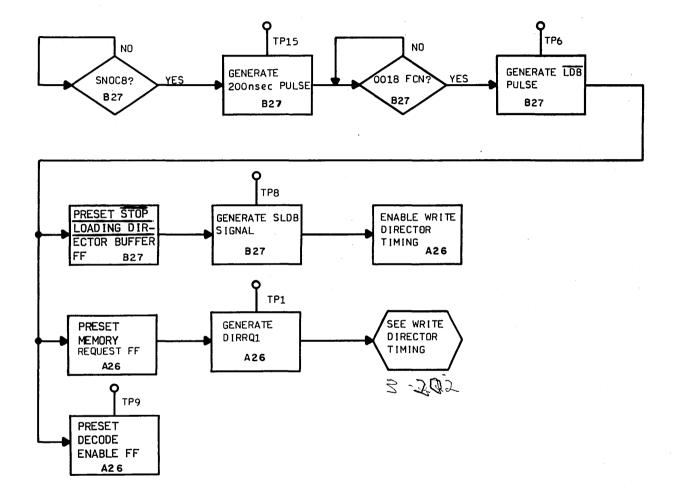

| 3-         | 71         | Logical Product (78XX - 7FXX)             | 3-133 |       | Function Master Clear - 0020                        | 3-189          |

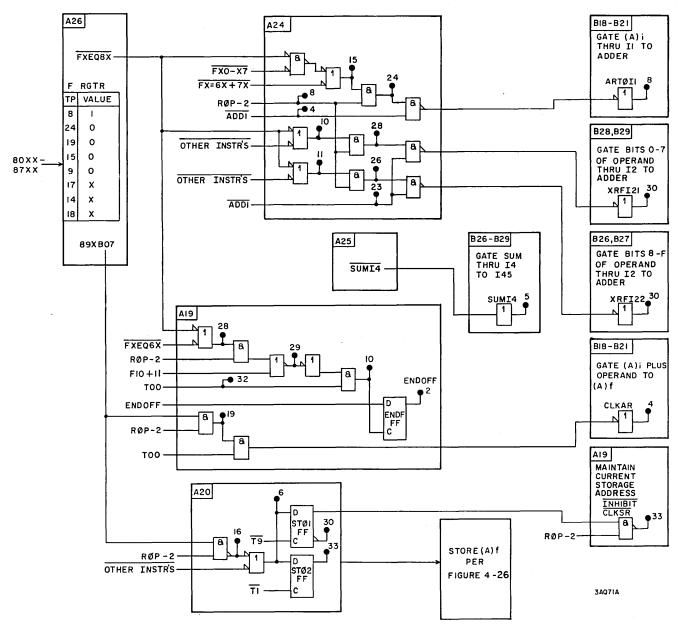

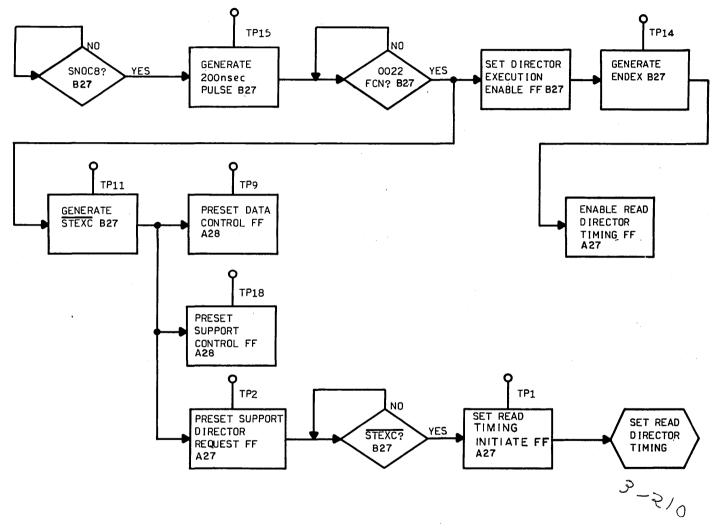

| 3-         | 72         | Replace Add (80XX - 87XX)                 | 3-134 | 3-99  | Start Director Execution - 0022                     | 3-190          |

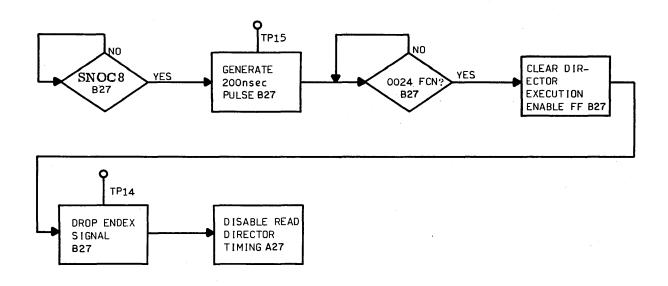

| 3-         | 73         | Replace Add One (88XX - 8FXX)             | 3-136 | 3-100 | Stop Execution - 0024                               | 3-191          |

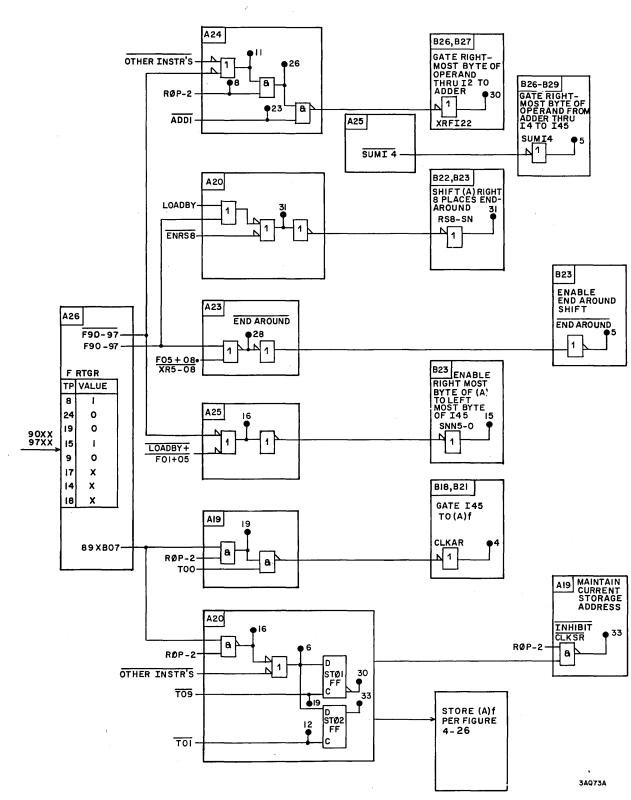

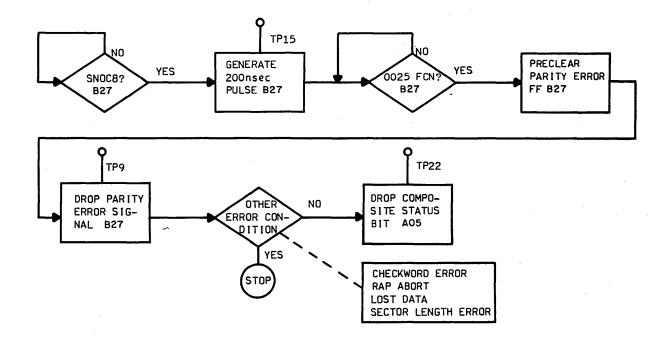

| 3-         | 74         | Replace Leftmost Byte (90XX - 97XX)       | 3-137 | 3-101 | Clear Parity Error - 0025                           | 3-192          |

| 3-         | 75         | Byte Flow for Replace Left-               |       |       | Enter Clock Step Mode - 0028                        | 3-193          |

|            |            | most Byte                                 | 3-138 |       | Exit Clock Step Mode - 0029                         | 3-194          |

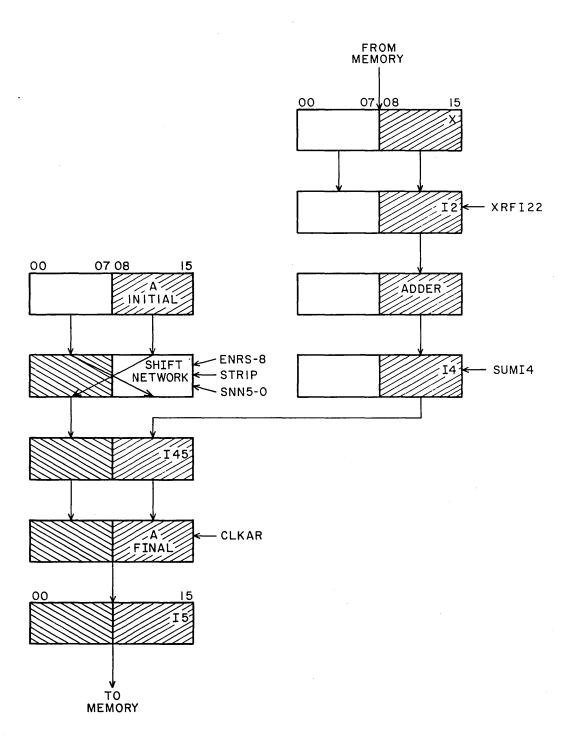

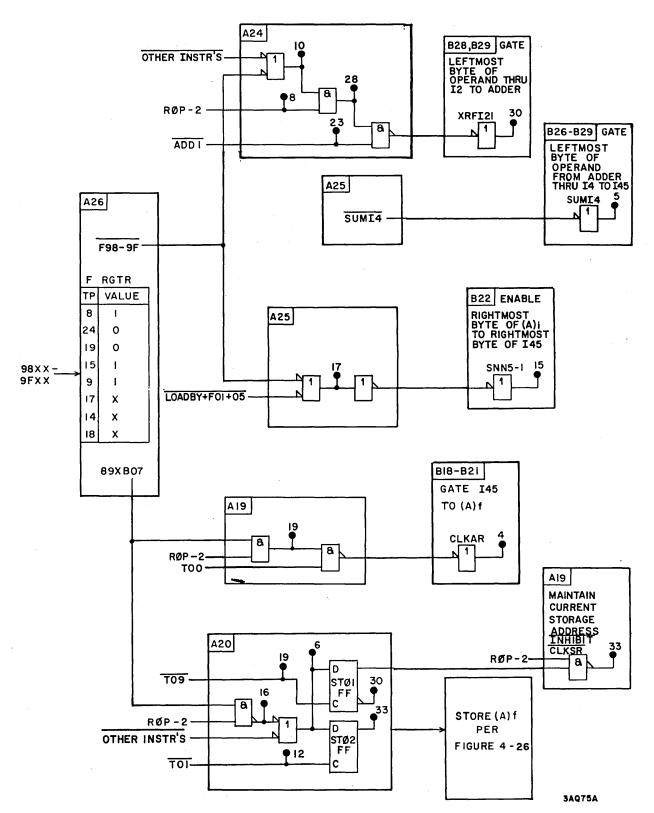

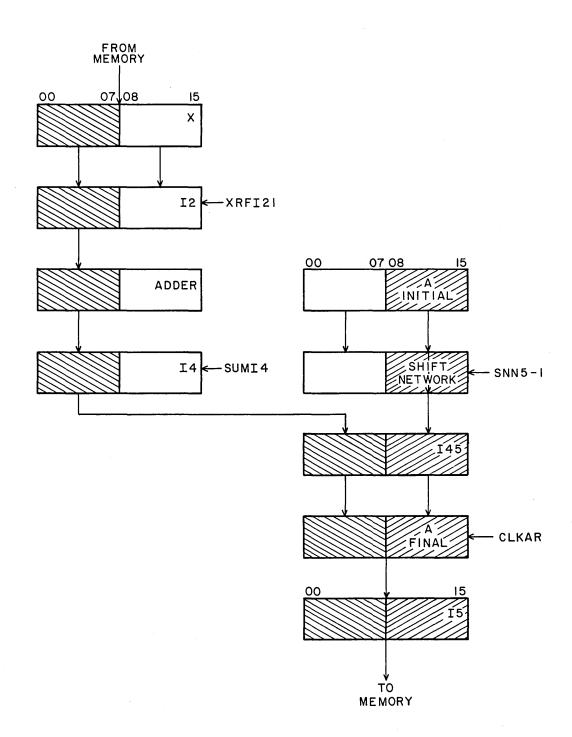

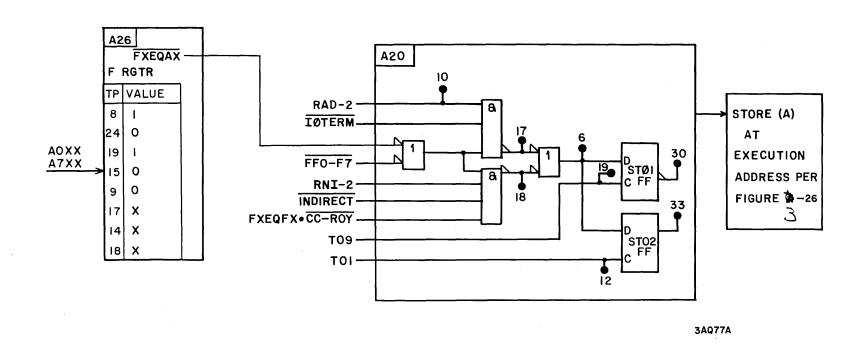

| 3-         | 76         | Replace Rightmost Byte (98XX - 9FXX)      | 3-140 | 3-104 | Step Clock - 002A                                   | 3-195          |

| 3_         | 77         |                                           | 3-140 | 3-105 | Stop Loading Directors - 0038                       | 3-196          |

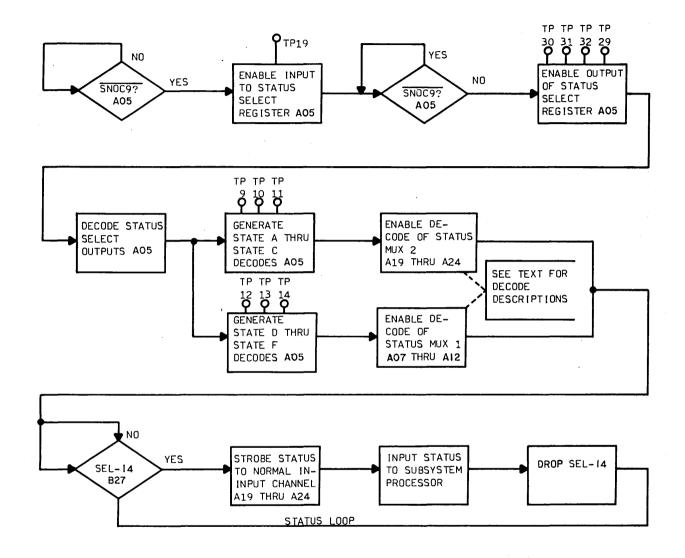

| J <b>-</b> |            | Byte Flow for Replace Right-<br>most Byte | 3-141 | 3-106 | Status Selection Flowchart                          | 3-198          |

| 3-         | 78         | Store (A0XX - A7XX)                       | 3-143 | 3-107 | Clear Internal Status Flow-                         | 3-199          |

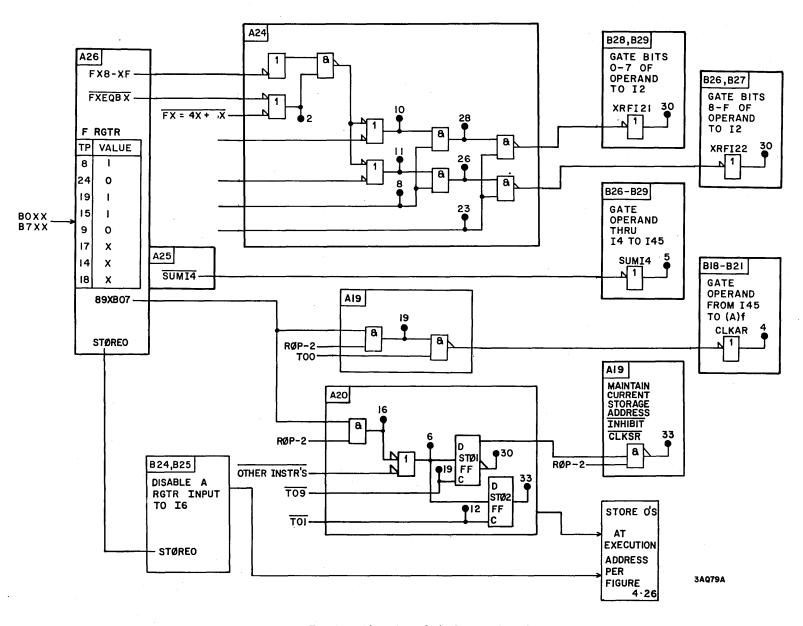

| 3-         | <b>7</b> 9 | Store Zeros (A8XX - AFXX)                 | 3-144 | Q_100 | chart                                               |                |

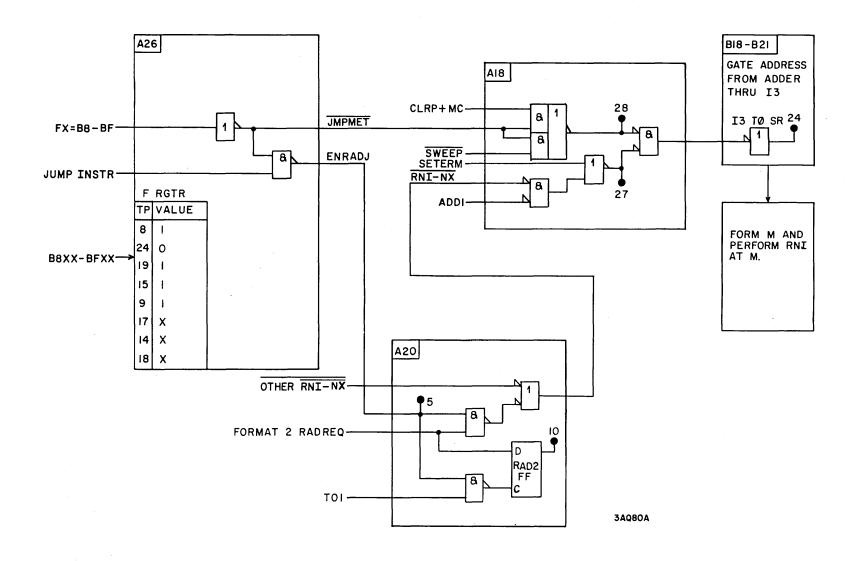

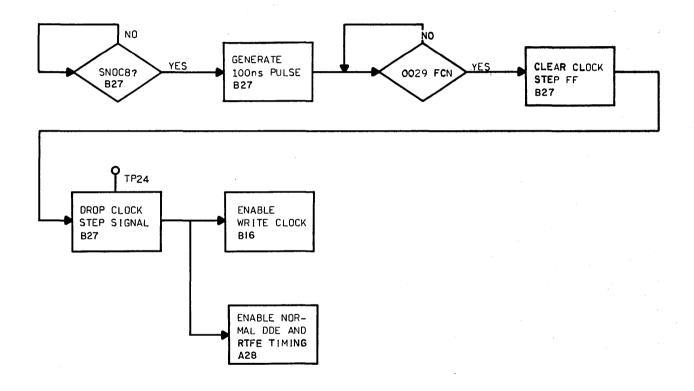

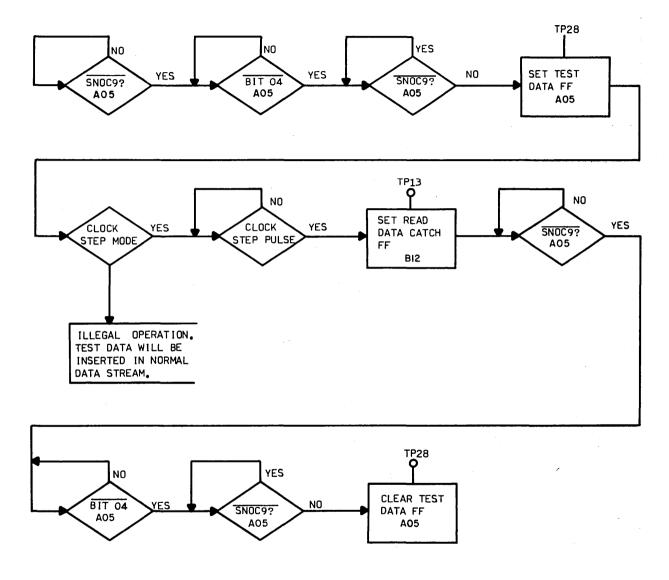

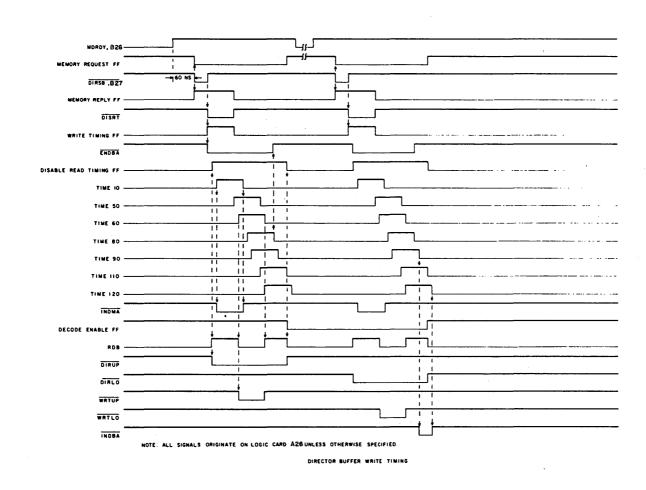

| 3-8        | 80         | Destructive Load (B0XX - B7XX)            | 3-145 |       | Test Data Flowchart Director Buffer Write Timing    | 3-200<br>3-203 |

|            |            |                                           |       |       |                                                     |                |

60428500 A

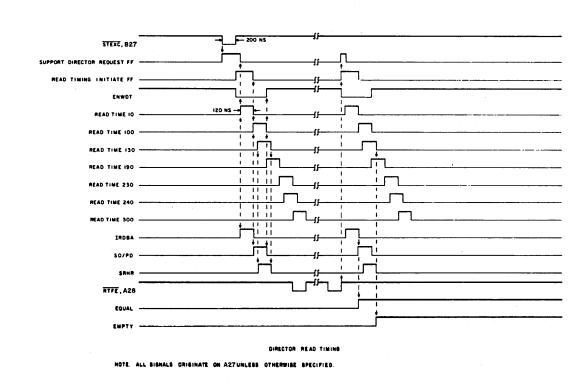

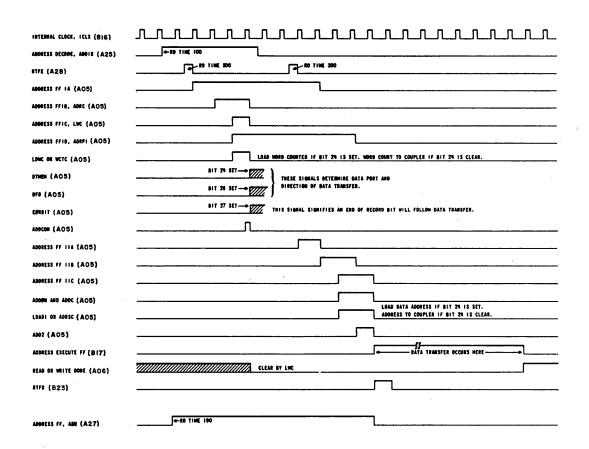

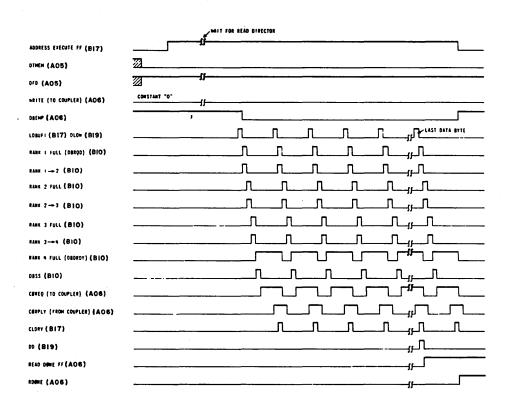

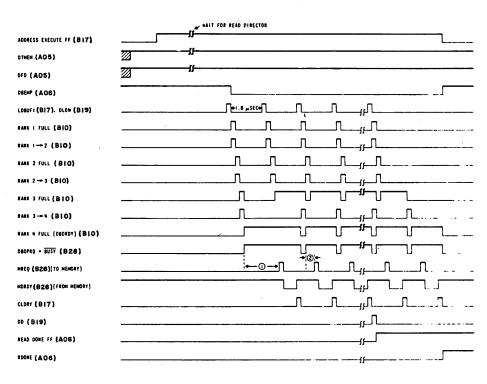

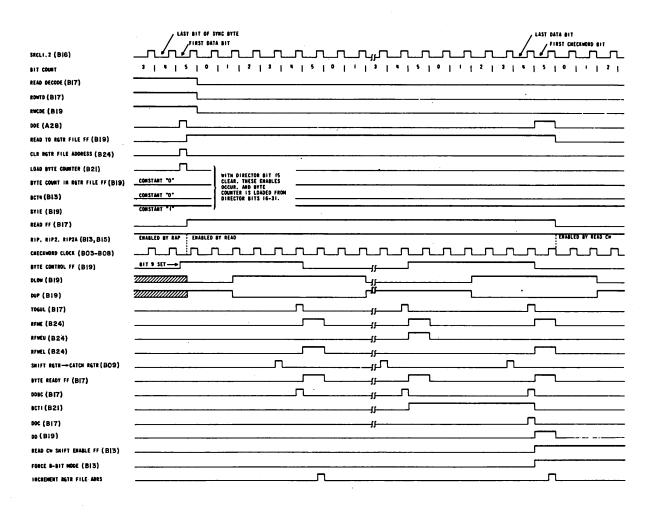

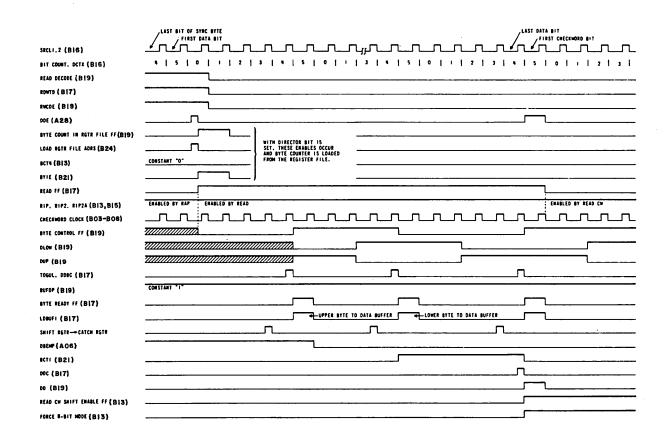

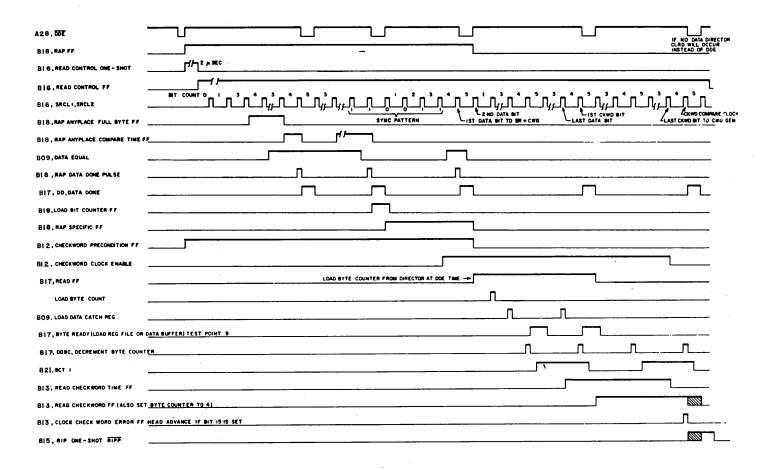

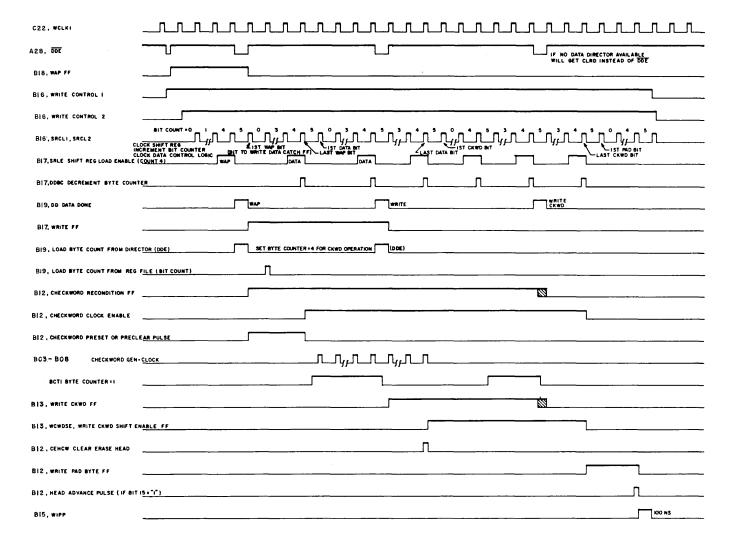

|       | Director Buffer Read Timing Address Director Execution | 3-211<br>3-218 | 3-119 | Read to Data Buffer Director Execution         | 3-264 |

|-------|--------------------------------------------------------|----------------|-------|------------------------------------------------|-------|

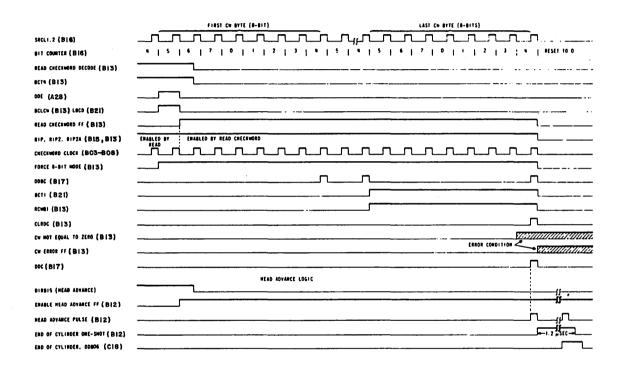

|       | Data Transfer - Data Buffer<br>to Memory               | 3-220          | 3-120 | Read Checkword Director<br>Execution           | 3-272 |

| 3-113 | Data Transfer - Data Buffer<br>to Coupler              | 3-221          | 3-121 | Read Address Pattern<br>Sequence               | 3-277 |

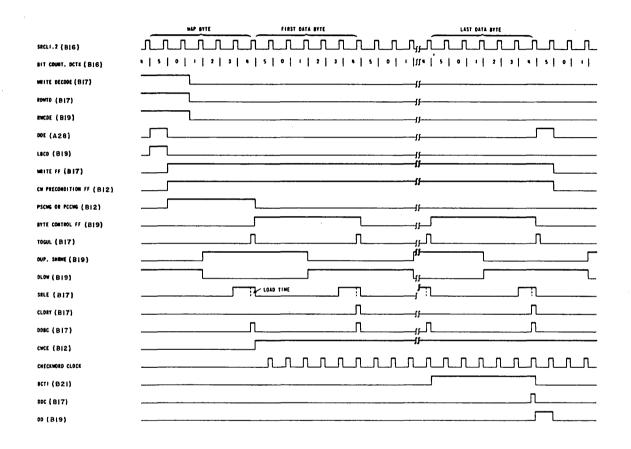

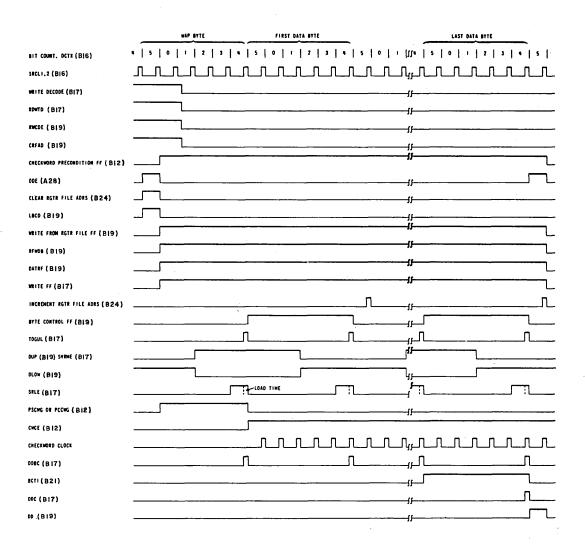

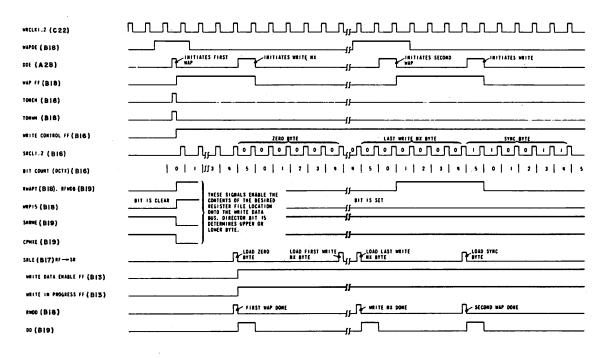

| 3-114 | Data Transfer - Coupler to Data Buffer                 | 3-222          | 3-122 | Write from Data Buffer<br>Director Execution   | 3-286 |

| 3-115 | Data Transfer - Memory to<br>Data Buffer               | 3-225          | 3-123 | Write from Register File<br>Director Execution | 3-290 |

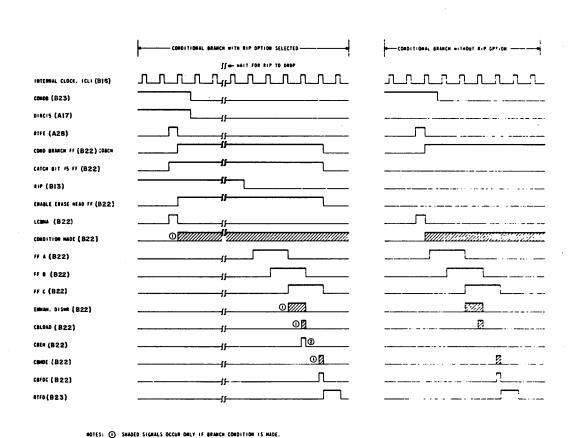

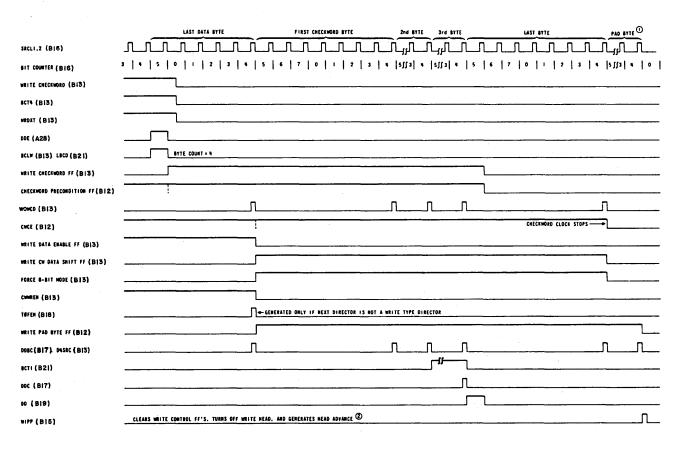

| 3-116 | Conditional Branch Director<br>Execution               | 3-231          | 3-124 | Write Checkword Director<br>Execution          | 3-295 |

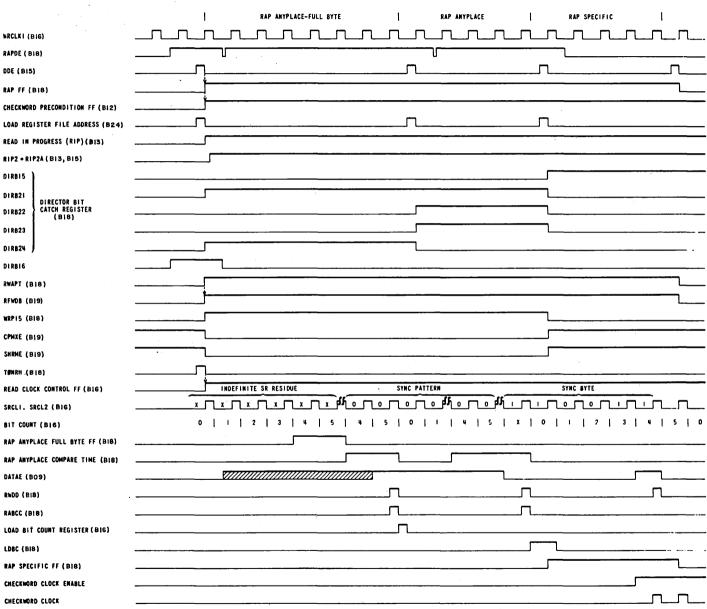

| 3-117 | Enable Disk Function Director Execution                | 3-251          | 3-125 | Write Address Pattern<br>Sequence              | 3-301 |

| 3-118 | Read to Register File Director Execution               | 3-261          | 3-126 | Complete Read Sequence<br>Timing               | 3-314 |

|       |                                                        |                | 3-127 | Complete Write Sequence<br>Timing              | 3-315 |

|       |                                                        |                |       |                                                |       |

# TABLES

| 2-1 | Auxiliary Operator Panel Con- |     | 3-1 | Status Select Line Functions | 3-4   |

|-----|-------------------------------|-----|-----|------------------------------|-------|

|     | trols and Indicators          | 2-2 | 3-2 | Tag Line Functions           | 3-5   |

| 2-2 | Power Controls and Indicators | 2-4 | 3-3 | A/D Control Signals          | 3-31  |

| 2-3 | Disk Storage Unit Controls    |     | 3-4 | Director Function Codes      | 3-186 |

|     | and Indicators                | 2-5 |     |                              |       |

SECTION 1

GENERAL DESCRIPTION

. .

#### GENERAL DESCRIPTION

#### INTRODUCTION

The FA722-A/B/C Disk Storage Controller (controller) interfaces up to eight CDC® BR302/BR303/BR308 Disk Storage Units with one peripheral processor unit (PPU) data channel from one of the following computer systems.

CDC 6000 Series

CDC® CYBER 70 Models 72, 73, 74

CDC® CYBER 170 Models 172, 173, 175

The FA722-A requires 60-Hertz (Hz) power, and the FA722-B may use either 50- or 60-Hz power. The FA722-C is functionally identical to the FA722-B. The difference between the B and C is in cabinet color, FA722-B is gold and the FA722-C is blue-gray.

#### EXPANSION OPTIONS

Options are available to increase the number of PPU data channels or disk storage units serviced by the controller. The DT220-C Second Channel Feature adds a second PPU data channel access to the controller. DC144-A/B, DT198-A, and DC401-A Mass Storage Extenders permit up to 64 standard density disk storage units to be attached logically to a controller. Double density disk storage units must connect directly to the controller. The second channel feature is described in this manual. Refer to the preface for publication numbers of mass storage extender manuals.

### DOUBLE DENSITY OPTION

The Double Density Option must be installed in the controller to permit operation with double density BR308 Disk Storage Units. The double density option requires wiring changes, the replacement of two control logic modules, and the addition of one control logic module.

CONTROLWARE MA >/OA

Many of the operating characteristics of the controller are determined by software which executes in the subsystem processor and control logic portions of the controller. This software is called controlware. The equipment configurator for controlware

1-1

60428500 K

designed to execute in the controller is MA710. Refer to the disk controller hardware reference manual listed in the preface for controlware reference information.

### FUNCTIONAL DESCRIPTION

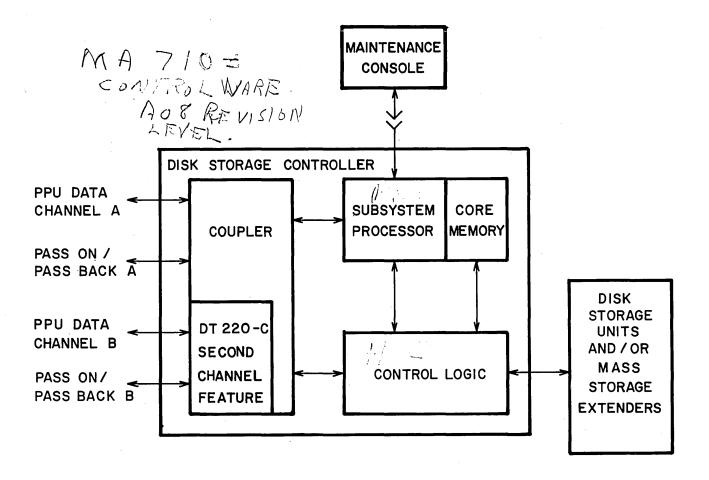

Figure 1-1 illustrates the relationship of major controller components.

#### COUPLER

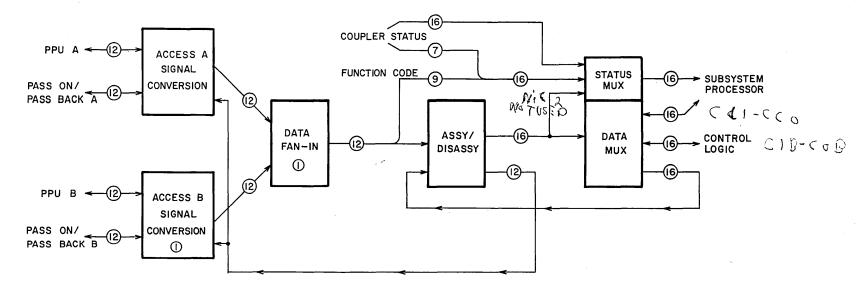

The coupler performs assembly/disassembly of 12-bit PPU words and provides an interface between the PPU and either the subsystem processor or the control logic.

Figure 1-1. Controller Block Diagram

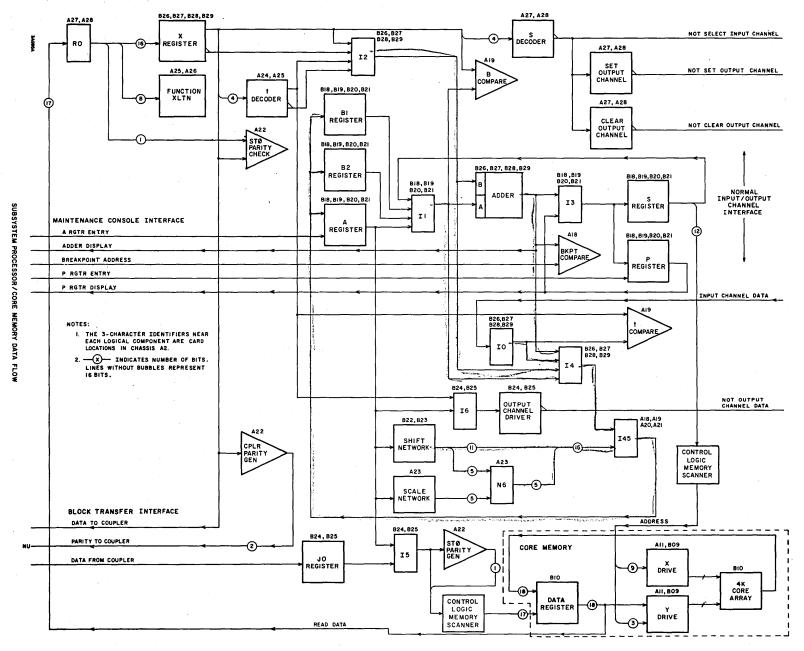

#### SUBSYSTEM PROCESSOR

The subsystem processor is a general purpose processor that uses a 16-bit instruction set and serves as the major control element of the controller. The subsystem processor communicates with a PPU via the coupler and controls the activities of the control logic. It receives function codes from the PPU and then selects a list of directors (control logic instructions) for execution by the control logic. The subsystem processor also passes status information from the control logic to the PPU. Although the subsystem processor controls data transfer operations, data passes directly between the control logic and the PPU via the coupler.

The subsystem processor has a control section, an arithmetic section, and various interfaces.

- The control section processes instructions and controls sequences.

- The arithmetic section performs two's complement arithmetic operations by means of an adder, two index registers, a shift network, and an accumulator register.

- A block transfer interface accommodates block transfers (such as autoload information) between the PPU and core memory.

- A normal channel interface provides communication with the PPU via the coupler and with the control logic. Control and status signals are exchanged on the normal channel interface.

- A storage interface links the subsystem processor to core memory through the memory scanner of the control logic.

- A maintenance interface provides for attachment of a portable maintenance console.

#### CONTROL LOGIC

The control logic is a special purpose processor that controls disk storage unit physical activity, transfers data to and from disk storage units, and performs error detection and correction. The control logic performs these functions by executing directors (control logic instructions) stored in core memory. The instructions are called directors to distinguish them from subsystem processor instructions. Directors vary in length from 16 to 64 bits.

60428500 A

1-3

When the subsystem processor has accepted a valid function code from the PPU, it selects a director sequence and informs the control logic. The control logic accesses core memory and begins loading the director sequence into its director buffer. The subsystem processor initiates execution of the director sequence which controls disk storage unit operation and data handling and processing. All data is passed directly between the control logic and the PPU (via the coupler) without being processed by the subsystem processor.

A memory scanner, which is part of the control logic, controls all accesses to the core memory and assigns priorities based on real-time constraints. The order of priority is:

- 1. Data handling references

- 2. Director buffer references

- 3. Subsystem processor references

Although the subsystem processor is assigned the lowest priority, it is normally not tied to real-time constraints and therefore has a larger proportion of access time available to it.

#### CORE MEMORY

The core memory contains 4096 16-bit words and is shared by the subsystem processor and the control logic. The subsystem processor uses the memory to control overall operation of the controller. The control logic references memory to obtain director sequences which control disk storage unit and data handling operations.

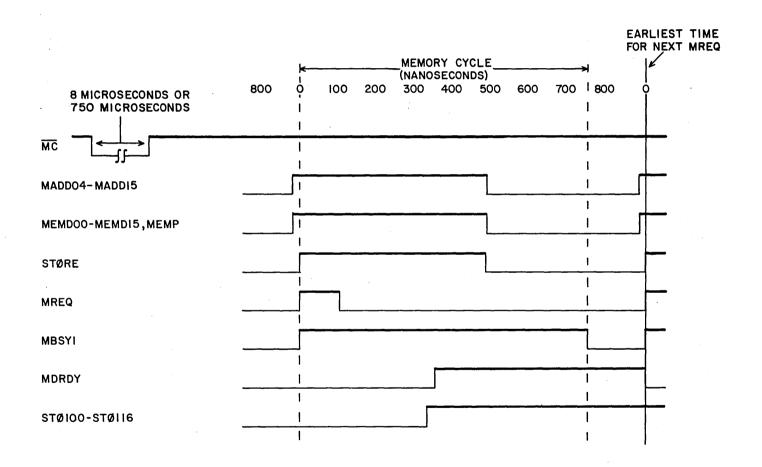

To avoid memory conflicts, all memory references are routed through the memory scanner in the control logic so that the highest priority references are handled first. Although the core memory has a potential cycle time of 750 nanoseconds, the effective cycle time depends upon the operations being performed by the subsystem processor and the control logic.

## PHYSICAL DESCRIPTION

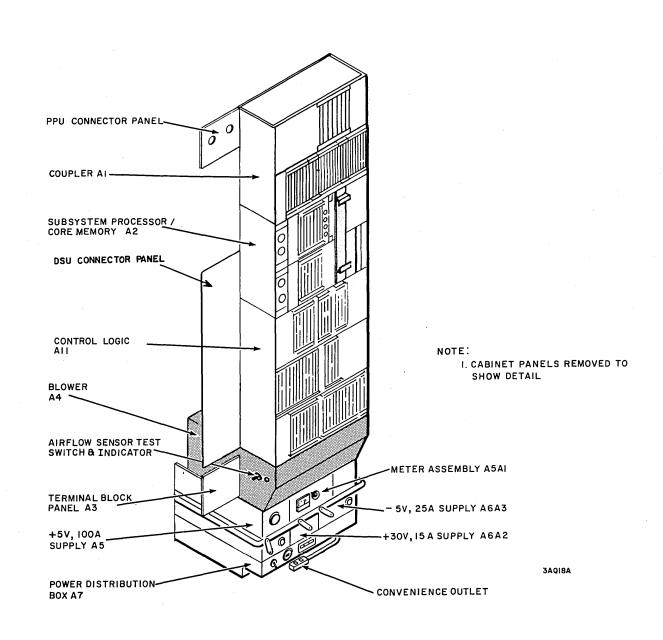

Figure 1-2 illustrates and identifies major controller components.

The logic consists of TTL integrated circuits encapsulated in 14-pin or 16-pin dual in-line packages (chips) which are mounted on printed circuit modules. A module con-

Figure 1-2. Controller Component Locations

tains up to 25 chips. These modules are called TTL 25-paks and plug into the logic chassis.

A logic chassis consists of two or three printed circuit boards mounted in a metal frame. Each board has several rows of pins which pass through the board and protrude from the front and back. Modules are inserted by sliding them over metal guides in the frame until they plug into the pins protruding from the front of the board. Backpanel pins are interconnected by a wirewrap method.

Doors and removable panels on the cabinet provide access to site maintainable components. Coupler logic occupies the top two rows of the cabinet and consists of 35 modules (including the second channel feature). The next two rows contain the subsystem processor, comprised of 23 modules, a core memory, a memory power regulator, a connector panel for the maintenance console, and an auxiliary operator panel. The lower three rows contain 71 modules of control logic. Most power related components are located in the base of the cabinet. A vertical bus bar carries +5 volts to horizontal bus bars in each logic chassis row. Individual power wires distribute other voltages to logic chassis bus bars.

Power supplies operate from 120/208-volt, 400-Hz, 3-phase power. The blower, elapsed time meter, and convenience outlet operate from 60-Hz or 50-Hz power.

### NOTE

Since the convenience outlet is protected by a 7-ampere circuit breaker, it is suitable for use only with low power equipment.

The blower draws room air through a filter, circulates it around the power supplies and logic modules, and forces it out through exhaust ducts at the top of the cabinet.

#### DIMENSIONS

| Height | 76 inches  | (193 centimeters)  |

|--------|------------|--------------------|

| Depth  | 25 inches  | (63.5 centimeters) |

| Width  | 39 inches  | (91.4 centimeters) |

| Weight | 300 pounds | (136 kilograms)    |

### ENVIRONMENTAL REQUIREMENTS

Cooling method

Heat dissipation 2800 Btu per hour (705.6 Kg-cal/hr)

Temperature

Operating 40°F (4.4°C) to 120°F (49°C)

Nonoperating -30°F (-34.4°C) to 150°F (65.6°C)

Forced air (blower)

Recommended operating 75°F (23.9°C)

Maximum gradient 20°F (11.0°C) per hour

Humidity (no condensation)

Operating 10% to 90% relative humidity

Nonoperating 5% to 95% relative humidity

Maximum operating 6000 feet (1830 meters) above sea level

altitude

### POWER REQUIREMENTS

120/208 volts 400 Hz 3-phase

120 volts 50/60 Hz 1-phase

SECTION 2

OPERATION

|  |  |   |  | · .              |

|--|--|---|--|------------------|

|  |  |   |  |                  |

|  |  |   |  | ·<br>•           |

|  |  |   |  |                  |

|  |  |   |  | <b>₹</b><br>\$ . |

|  |  |   |  | ,                |

|  |  |   |  | ,                |

|  |  |   |  |                  |

|  |  |   |  |                  |

|  |  |   |  | ·.               |

|  |  |   |  | /                |

|  |  |   |  | ·                |

|  |  |   |  |                  |

|  |  |   |  | ,                |

|  |  |   |  |                  |

|  |  |   |  | ,                |

|  |  |   |  | ·<br>•           |

|  |  |   |  |                  |

|  |  |   |  | <i>*</i>         |

|  |  |   |  | <i>'</i>         |

|  |  |   |  | 1                |

|  |  |   |  | <i>y</i> *       |

|  |  |   |  |                  |

|  |  |   |  | /                |

|  |  |   |  |                  |

|  |  | , |  |                  |

|  |  |   |  |                  |

|  |  |   |  |                  |

#### **OPERATION**

### INTRODUCTION

This section describes controls, indicators, and operating procedures for the controller and disk storage unit. For initial power-up and checkout procedures, refer to Installation and Checkout, section 4. For complete subsystem operating procedures, refer to the Disk Storage Subsystem Operation and Programming manual. For controlware and coupler reference information, refer to the disk controller hardware reference manual. These manuals are listed in the preface.

# AUXILIARY OPERATOR PANEL CONTROLS AND INDICATORS

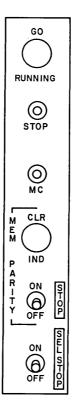

Figure 2-1 illustrates the auxiliary operator panel. Table 2-1 describes auxiliary operator panel controls and indicators.

Figure 2-1. Auxiliary Operator Panel

TABLE 2-1. AUXILIARY OPERATOR PANEL CONTROLS AND INDICATORS

| Nomenclature              | Device                                       | Function                                                                                                                                                                                                       |  |  |

|---------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GO/RUNNING                | Momentary close<br>switch/indicator<br>light | Pressing the switch causes the subsystem processor to start executing instructions. The indicator lights when the subsystem processor is running.                                                              |  |  |

| STOP                      | Momentary close<br>switch                    | Pressing the switch stops the subsystem processor.                                                                                                                                                             |  |  |

| MC                        | Momentary close<br>switch                    | Pressing this switch clears the subsystem processor's control section, addressable registers, and output channels. The GO/RUNNING indicator must be unlighted when the MC switch is pressed.                   |  |  |

| MEM PARITY<br>CLR/IND     | Momentary close<br>switch/indicator<br>light | The indicator lights when a memory parity error is detected. Pressing the switch clears the error status and causes the light to go out.                                                                       |  |  |

| MEM PARITY<br>STOP ON/OFF | Toggle switch                                | When this switch is ON, the subsysted processor stops running upon detection of a memory parity error. When the switch is OFF, the subsystem processor continues to run after detection a memory parity error. |  |  |

| SEL STOP<br>ON/OFF        | Toggle switch                                | When this switch is ON, the subsystem processor stops anytime it reads a 00XX instruction. When this switch is OFF, the subsystem processor ignores a 00XX instruction and goes to the next instruction.       |  |  |

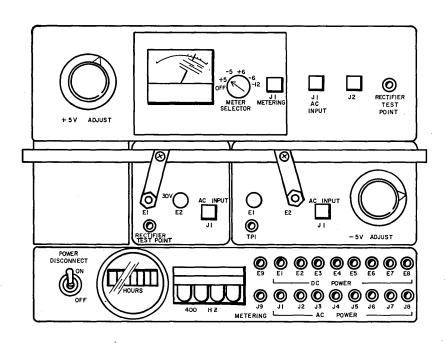

# POWER CONTROLS AND INDICATORS

Figure 2-2 illustrates the front panels of the power supplies and the power distribution box. Table 2-2 describes power indicators and controls.

Figure 2-2. Power Controls and Indicators

## POWER-UP/POWER-DOWN PROCEDURE

For this procedure, all logic voltages should be at their nominal values as described in the initial power-up procedure in section 4. The power-down sequence is listed first since it must be performed correctly for power-up to be effective.

### POWER-DOWN

- 1. Press the STOP switch on the auxiliary operator panel. The GO/RUNNING indicator should go out.

- 2. Turn OFF the POWER DISCONNECT switch.

## POWER-UP

- 1. Turn ON the 400 HZ circuit breaker and the POWER DISCONNECT switch. The blowers should operate.

- 2. Press the GO/RUNNING switch/indicator on the auxiliary operator panel. The indicator should light. The controller is now ready for operation.

TABLE 2-2. POWER CONTROLS AND INDICATORS

| Control/Indicator                                   | Function                                                                                                                                                                              |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| + 5V ADJUST rotary knob                             | Adjusts +5-volt power output. The adjustment is monitored on the percent meter.                                                                                                       |

| Percent meter                                       | Indicates the percent difference between the voltage input to the meter and the nominal voltage for that input. The METER SELECTION switch determines the voltage input to the meter. |

| - 5V ADJUST rotary knob                             | Adjusts -5-volt power output. The adjustment is monitored on the percent meter.                                                                                                       |

| POWER DISCONNECT switch                             | Applies power to the blowers, elapsed time meter, and 400 Hz circuit breaker.                                                                                                         |

| Elapsed time meter                                  | Indicates the amount of time that 50/60-Hz power has been applied to the controller.                                                                                                  |

| 400 HZ circuit breaker                              | Protects the power supplies from over-<br>load.                                                                                                                                       |

| AIRFLOW SENSOR BLOWER (on side of plenum)           | Disables 50/60-Hz power input to blower during airflow sensor test.                                                                                                                   |

| AIR FLOW SENSOR RELAY INDICATOR (on side of plenum) | Indicates that the 130°F (55°C) thermostat has opened the relay supplying power to the 400 Hz circuit breaker.                                                                        |

## DISK STORAGE UNIT CONTROLS

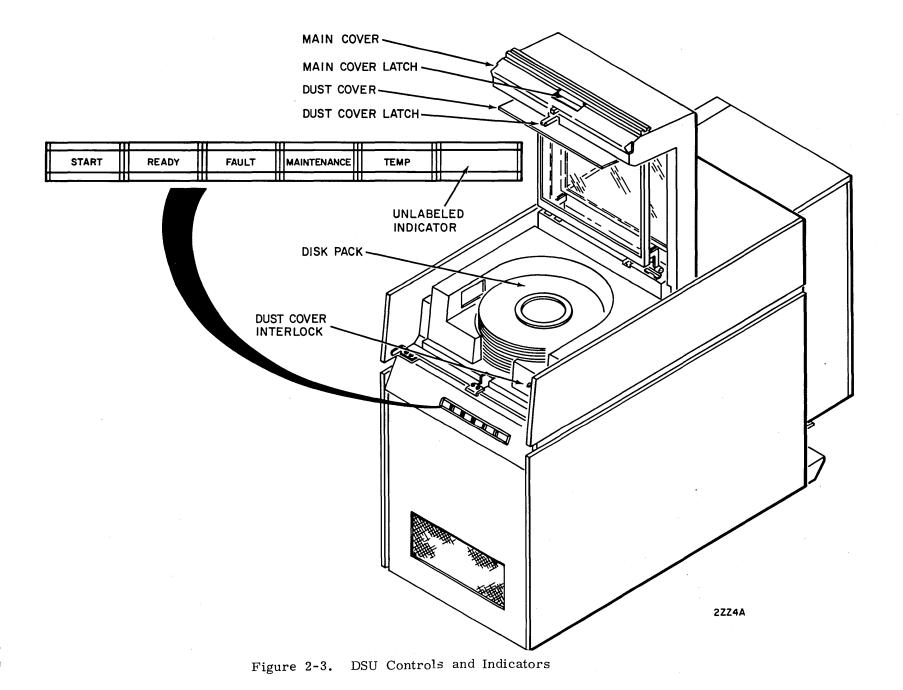

Figure 2-3 illustrates disk storage unit controls and indicators. Table 2-3 describes each of these items.

TABLE 2-3. DISK STORAGE UNIT CONTROLS AND INDICATORS

| Nomenclature        | Device                                | Function                                                                                                                                                                                                                                                                                      |

|---------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START               | Alternate action pushbutton/indicator | When the indicator is unlighted and all interlocks are properly set, pressing this switch applies power to the disk storage unit and initiates disk pack rotation. When the indicator is lighted, pressing this switch removes power from the disk storage unit and stops disk pack rotation. |

| READY               | Indicator                             | Lights when the disk pack has reached normal speed and the heads are loaded.                                                                                                                                                                                                                  |

| FAULT               | Pushbutton<br>switch/indicator        | Lights to indicate a fault condition in the disk storage unit. Pressing the switch clears the fault indication.                                                                                                                                                                               |

| MAINTENANCE         | Indicator                             | Lights when the controller is not controlling the power application to this disk storage unit.                                                                                                                                                                                                |

| TEMPERATURE         | Indicator                             | Lights when an overtemperature condition exists in the disk storage unit.                                                                                                                                                                                                                     |

| Unlabeled Indicator | Indicator                             | Lights when the controller selects the disk storage unit.                                                                                                                                                                                                                                     |

### DISK PACK EXCHANGE PROCEDURE

- Make certain that the START indicator is not lighted and that the disk pack is not spinning. If the START indicator is lighted, press it to turn off the light and stop the disk storage unit.

- 2. When the disk pack has stopped, press the main cover latch (Figure 2-3) and lift the main cover. The dust cover opens with the main cover.

3. Place a disk pack cover over the loaded disk pack so that it engages the spindle. Turn counterclockwise until the spindle clicks and lift the cover and disk pack from the disk storage unit.

Place one hand under the disk pack to prevent the disk pack from falling free of the cover.

- 4. Using its cover as a handle, place the new disk pack slowly over the spindle until it engages the spindle drive unit. Turn the disk pack cover clockwise until it reaches a stop. Lift the disk pack cover from the disk storage unit.

- 5. Close the main cover, making sure that it latches. If the cover is not securely latched, the dust cover interlock remains open and prevents power application.

- 6. Press the START switch. When the disk pack is at operating speed (heads loaded), the READY indicator lights. The disk storage unit is now ready for operation.

|  |   |  |  | 6  |

|--|---|--|--|----|

|  |   |  |  | Χ. |

|  | , |  |  |    |

|  |   |  |  |    |

|  |   |  |  |    |

|  |   |  |  |    |

|  |   |  |  |    |

|  |   |  |  | (  |

|  |   |  |  |    |

|  |   |  |  |    |

|  |   |  |  |    |

|  |   |  |  | (  |

SECTION 3

THEORY OF OPERATION

|   |   |  |   |  |   |   | *.                        |

|---|---|--|---|--|---|---|---------------------------|

|   |   |  |   |  |   |   | <i>2</i>                  |

|   |   |  |   |  |   |   | •                         |

|   |   |  |   |  |   |   | 20                        |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | 1                         |

|   |   |  |   |  |   |   | (                         |

|   |   |  | • |  |   |   |                           |

|   |   |  |   |  |   |   | ζ.                        |

|   |   |  |   |  |   |   | ,                         |

|   |   |  |   |  |   |   | \(\lambda_{\text{\chi}}\) |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   | • |                           |

|   |   |  |   |  |   |   | `                         |

|   |   |  |   |  |   |   | 1                         |

|   |   |  |   |  |   |   | 1                         |

| • |   |  |   |  |   |   | 1                         |

|   |   |  |   |  |   |   | `.                        |

|   |   |  |   |  |   |   | , ·                       |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  | , |   |                           |

|   |   |  |   |  |   |   | `                         |

|   |   |  |   |  |   |   | 1                         |

|   |   |  |   |  |   |   | *                         |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | ,                         |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | `                         |

|   |   |  |   |  |   |   | 1.                        |

|   |   |  |   |  |   |   | *                         |

|   |   |  |   |  |   |   |                           |

|   | • |  |   |  |   |   | N.                        |

|   |   |  |   |  |   |   | <u></u>                   |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | - 4                       |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | *                         |

|   |   |  |   |  |   |   |                           |

|   |   |  |   |  |   |   | ,                         |

### THEORY OF OPERATION

#### INTRODUCTION

This section provides component theory and operational sequences for each of the major assemblies in the disk controller. In addition, the first part of this section describes the PPU interface, pass on/pass back interfaces, DSU interface, maintenance console interface, and interfaces linking controller major assemblies.

## INTERFACES

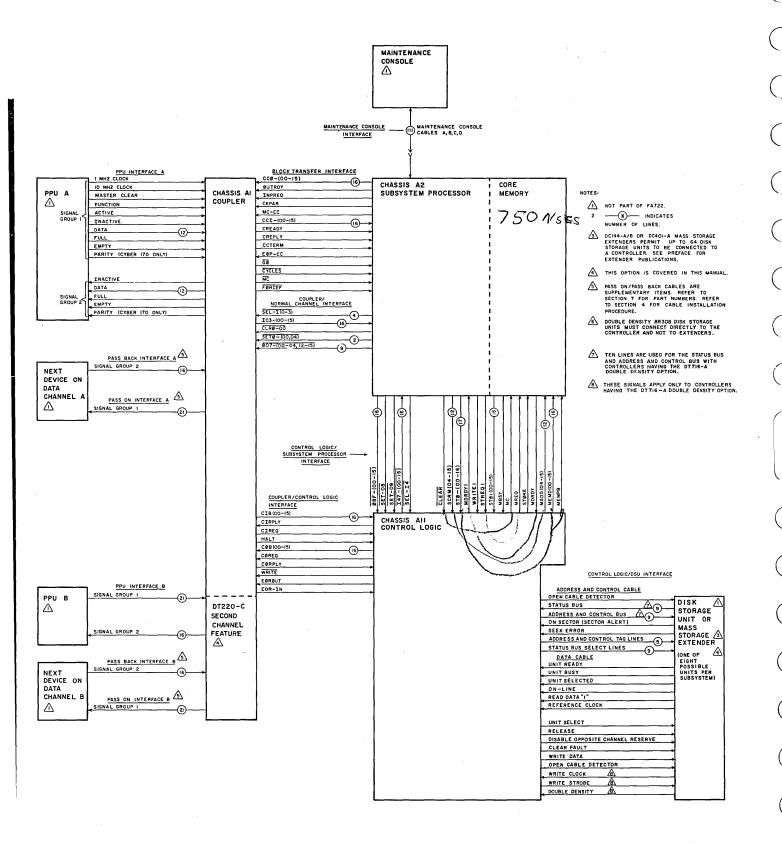

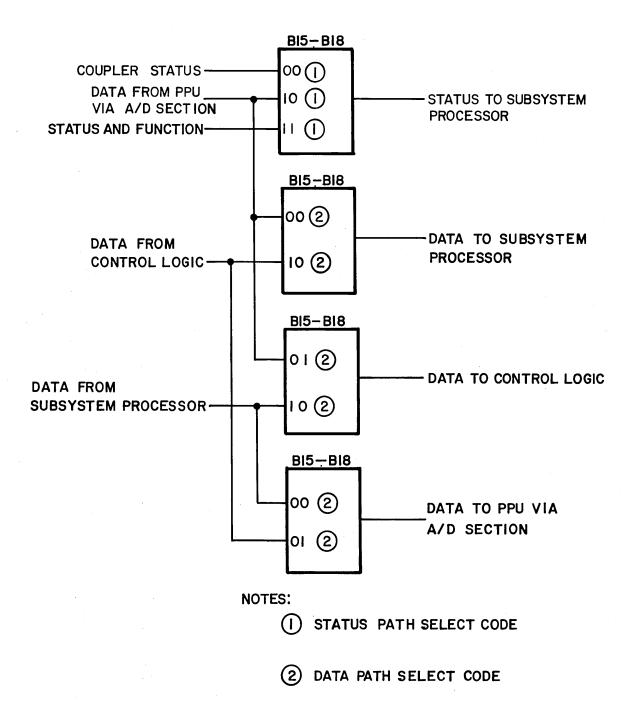

Figure 3-1 illustrates the interfaces described in the following paragraphs.

#### PPU INTERFACE

This interface connects the disk controller to a PPU. Dual access controllers have two PPU interfaces, one for each PPU. All data and control signals on the PPU interface are 25-nanosecond pulses which are synchronized with 1-MHz and 10-MHz clock signals also present on the interface.

### Signals From PPU Only

| 1 MHZ CLOCK/10 MHZ CLOCK | The controller uses these signals to synchronize all communication with a PPU.                                                        |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| ACTIVE                   | The PPU sends this signal to initiate or resume communication with the controller. An active signal accompanies each function signal. |

| FUNCTION                 | This signal identifies the accompanying 12 data signals as a function code.                                                           |

| MASTER CLEAR             | The PPU sends this signal to clear the con-                                                                                           |

troller just after a computer system deadstart.

60428500 A 3-1

Figure 3-1. Interface Diagram

# Bidirectional PPU Interface Signals

DA TA

These 12 signals carry data, function, and status words between the PPU and the controller.

PARITY (CDC CYBER 170 Only)

This signal provides odd parity for the 12 data signals it accompanies.

FULL

This signal indicates to the receiver that the word formed by the 12 data signals can be accepted.

EMPTY

This signal indicates to the transmitter that the receiver has accepted the word accompanying the last full signal.

INACTIVE

The controller replies to a function signal (and its associated function code) with an inactive signal. An inactive signal may also be used by either the PPU or the controller to terminate communication.

#### PASS ON/PASS BACK INTERFACES

These interfaces transfer all the signals described under HLP Interface between the PPU and other devices connected behind the controller on the same data channel. Signals on the pass on interface lag corresponding signals from the PPU by 100 nanoseconds. Likewise, signals on the pass back interface lag corresponding signals from the other device(s) on the data channel by 100 nanoseconds. Each access of dual access controllers may have pass on/pass back cables installed.

# CONTROL LOGIC/DISK STORAGE UNIT INTERFACE

Signals between the control logic and a disk storage unit or a mass storage extender are carried on cables A (the address and control cable) and B (the data cable).

# Address and Control Cable

#### Status Bus

The status bus consists of nine lines (10 lines for double density option) which carry status information from the unit to the controller. Information on the status bus is determined by status select signals sent from the controller to the unit. Table 3-1 shows the relationship of the status select lines to the status bus.

TABLE 3-1. STATUS SELECT LINE FUNCTIONS

|               |                      |                         |                      | Sta                   | atus Se              | lect Lines                 |                   |                            |                         |

|---------------|----------------------|-------------------------|----------------------|-----------------------|----------------------|----------------------------|-------------------|----------------------------|-------------------------|

| Status<br>Bus | Read<br>Cyl.<br>Sel. | Read<br>Diff.<br>Cnt.   | Read<br>Head<br>Reg. | Read<br>Sec.<br>Cntr. | Read<br>Sec.<br>Reg. | Read<br>Interlock          | Read<br>Position  | Read<br>Fault              | Read<br>Control         |

| Bit 0         | 1                    | 1                       | 1                    | 1                     | 1                    | Pack on                    | Forward           | W+E+R· (5)                 | Sector                  |

| Bit 1         | 2                    | 2                       | 2                    | 2                     | 2                    | Sector<br>block <b>2</b>   | Reverse           | (W+E)• R <b>©</b>          | Pack<br>unsafe          |

| Bit 2         | 4                    | 4                       | 4                    | 4                     | 4                    | Heads<br>loaded            | Cylinder<br>pulse | Current                    | Seek <b>Ø</b><br>error  |

| Bit 3         | 8                    | 8                       | 8                    | 8                     | 8                    | Brush<br>cycle             | End of<br>travel  | + Volt                     | On<br>cylinder          |

| Bit 4         | 16                   | 16                      | 16                   | 16                    | 16                   | Start<br>switch            | Fine<br>servo     | - Volt                     | Index                   |

| Bit 5         | 32                   | 32                      |                      |                       |                      | Local<br>remote            | Speed             | Seek                       | Amplitude®<br>monitor 1 |

| Bit 6         | 64                   | 64                      |                      |                       |                      | Spindle<br>motor on        |                   | AC write <b>O</b><br>fault | End of<br>cylinder      |

| Bit 7         | 128                  | 128                     |                      |                       |                      | Power ③ supply temperature |                   |                            | Amplitude monitor 2     |

| Bit 8         | 256                  | 256                     |                      | Cntr<br>Valid         |                      | Logic ① temperature        |                   |                            | Amplitude<br>monitor 3  |

| Bit 9①        | 512 <sup>①</sup>     | <sub>512</sub> <b>①</b> |                      |                       |                      |                            |                   |                            |                         |

① Used only with DT716-A Double Density Option.

This is Control Interlock for double density option.

This is Logic Temp. for double density option.

This is Logic Temp. for double density option.

This is W+R. On Cyl. for double density option.

This is W for double density option.

This is Seek Incomplete for double density option.

This is EOT Seek Error for double density option.

#### Address and Control Bus

The address and control bus consists of nine lines (10 lines for double density option) which carry information from the controller to the unit. Information on these lines is determined by address and control tag signals which are sent from the controller to the unit. Table 3-2 shows the relationship of the tag lines to the address and control bus.

#### On Sector (Sector Alert)

This is an unselected status line which indicates that the addressed sector is one sector away from the heads. The on sector signal is one sector in length and occurs once per revolution until a read gate, clear, or release is received. The on sector signal is disabled while a seek command is in process.

#### Seek Error

This is an unselected status line. It indicates that the unit was unable to complete a move within 500 milliseconds or that the carriage has moved to a position outside the recording field. A return to zero seek command cleans the seek error condition, returns the heads to cylinder zero, and enables an on cylinder signal to the controller.

TABLE 3-2. TAG LINE FUNCTIONS

| Address<br>and | Tag Line             |                    |                  |                |                   |  |

|----------------|----------------------|--------------------|------------------|----------------|-------------------|--|

| Control<br>Bus | Difference<br>Select | Cylinder<br>Select | Sector<br>Select | Head<br>Select | Control<br>Select |  |

| Bit 1          | 1                    | 1                  | 1                | 1              | Write gate        |  |

| Bit 1          | 2                    | 2                  | 2                | 2              | Read gate         |  |

| Bit 2          | 4                    | 4                  | 4                | 4              | Seek forward      |  |

| Bit 3          | 8                    | 8                  | 8                | 8              | Head advance      |  |

| Bit 4          | 16                   | 16                 | 16               | 16             | Erase gate**      |  |

| Bit 5          | 32                   | 32                 |                  |                | Seek reverse      |  |

| Bit 6          | 64                   | 64                 |                  |                | RTZ               |  |

| Bit 7          | 128                  | 128                | i .              |                | Data strobe early |  |

| Bit 8          | 256                  | 256                |                  |                | Data strobe late  |  |

| Bit 9 *        | 512                  | 512                |                  |                |                   |  |

<sup>\*</sup>Used only with DT716-A Double Density Option.

60428500 H 3-5

<sup>\*\*</sup>Not used in double density disk units.

Address and Control Tag Lines (Received by the Unit) (Refer to Table 3-2)

Difference Select: This signal indicates that the address and control bus contains positioning information (the difference between the unit's present cylinder address and the controller's new cylinder address).

Cylinder Select: This signal indicates that the address and control bus contains the controller's new cylinder address.

Sector Select: This signal indicates that the address and control bus contains the address of the sector which will generate the next on sector signal.

Head Select: This signal indicates that the address and control bus contains the address of the head which is to be selected.

Control Select: This signal indicates that the address and control bus contains control information with the following bit assignments.

| Sign  | nal          | Function                                                                                                                   |

|-------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| Bit 0 | Write gate   | Enables write driver.                                                                                                      |

| Bit 1 | Read gate    | Enables digital read data on the read data lines.                                                                          |

| Bit 2 | Seek forward | Initiates the positioning sequence in the forward direction if the difference counter contains a number greater than zero. |

|       |              | If the difference counter equals zero, a forward carriage offset results.                                                  |

| Bit 3 | Head advance | Increments the head counter by one.                                                                                        |

|       |              | NOTE  This signal occurring with the end of cylinder signal clears the head counter.                                       |

| Bit 4 | Erase gate   | Enables the erase driver. (Not used in double density disk units.)                                                         |

| Bit 5 | Seek reverse | Initiates the positioning sequence in the reverse direction if the difference counter contains a number greater than zero. |

|       |              | If the difference counter equals zero, a reserve carriage offset results.                                                  |

|       | Signal            | Function                                                                               |

|-------|-------------------|----------------------------------------------------------------------------------------|

| Bit 6 | Return to zero    | Initiates positioning to cylinder zero, and clears seek error condition if one exists. |

| Bit 7 | Data strobe early | When this signal is true, the data strobe is moved to the early margin position.       |

| Bit 8 | Data strobe late  | When this signal is true, the data strobe is moved to the late margin position.        |

Status Bus Select Lines (Refer to Table 3-1)

Read Cylinder Select (Controller to Unit): This signal gates the contents of the unit cylinder register to the controller on the status bus.

Interlock Select (Controller to Unit): This signal gates unit interlock status to the controller with the following bit assignments on the status bus.

|       | Signal                      | Function                                                                                                                                     |

|-------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0 | Pack on                     | Indicates a pack is mounted on the spindle.                                                                                                  |

| Bit 1 | Sector block<br>or          | Indicates the unit cover is closed and sec-tor block is in position to sense sector disk.                                                    |

|       | Control interlock           | Indicates the unit cover is closed, all do circuit breakers are closed, and the start switch is on. (Applies to double density option only.) |

| Bit 2 | Heads loaded                | Indicates heads have been loaded on the disk pack.                                                                                           |

| Bit 3 | Brush cycle                 | Indicates pack brush cycle is in progress.                                                                                                   |

| Bit 4 | Start switch                | Indicates start switch is on.                                                                                                                |

| Bit 5 | Local/remote                | Indicates unit sequencing power is under control.                                                                                            |

| Bit 6 | Spindle motor               | Power is applied to the spindle motor.                                                                                                       |

| Bit 7 | Power supply temperature or | Indicates power supply temperature normal.                                                                                                   |

|       | Logic temperature           | Indicates logic chassis temperature normal.  (Applies to double density option only.)                                                        |

| Bit 8 | Logic temperature           | Indicates logic chassis temperature normal.  (Not used with double density option.)                                                          |

Read Head Register Select: This signal gates the contents of the unit head register to the controller.

Read Difference Counter Select: This signal gates the one's complement of the contents of the unit difference counter to the controller on the status bus.

Read Sector Counter Select: This signal gates the contents of the unit sector counter to the controller on the status bus. Bit 8 is sector counter valid signal. When this line is true, the output of the sector counter is not in the process of changing. The counter contents are one number ahead of the actual sector count.

Read Sector Register Select: This signal gates the contents of the unit sector register to the controller on the data bus.

Read Position Status Select: This signal gates positioner control status to the controller on the data bus with bit assignment as follows:

| Sig   | nal            | Function                                                                                                                  |

|-------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| Bit 0 | Forward        | Indicates the forward latch is set.                                                                                       |

| Bit 1 | Reverse        | Indicates the forward latch is cleared.                                                                                   |

| Bit 2 | Cylinder pulse | Transmits cylinder pulses during a positioning function.                                                                  |

| Bit 3 | End of travel  | Indicates the heads have been positioned beyond the useable recording field in either the forward or reverse direction.   |

| Bit 4 | Fine servo     | Indicates the heads are being positioned under fine servo control and are less than 1/2 track from the final destination. |

| Bit 5 | Speed & mtr on | Indicates the pack is rotating at a speed safe for flying the heads.                                                      |

Read Fault Status Select: This signal gates the contents of the fault register to the controller on the status bus with the following bit assignments.

| Signal |                        | Function                                                                                                                                 |

|--------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0  | W+E+R.<br>On Cyl<br>or | Indicates a write, erase, or read gate has been received while unit was off cylinder.                                                    |

|        | W+R• On Cyl            | Indicates a write or read gate has been received while unit was off cylinder. (Applies to double density option only.)                   |

| Bit 1  | (W+E) · R              | Indicates a write or erase gate has been received while the read gate is true.                                                           |

|        | W· R                   | Indicates a write gate has been received while<br>the read gate is true. (Applies to double<br>density option only.)                     |

| Bit 2  | Current                | Indicates one or more of the following fault conditions.                                                                                 |

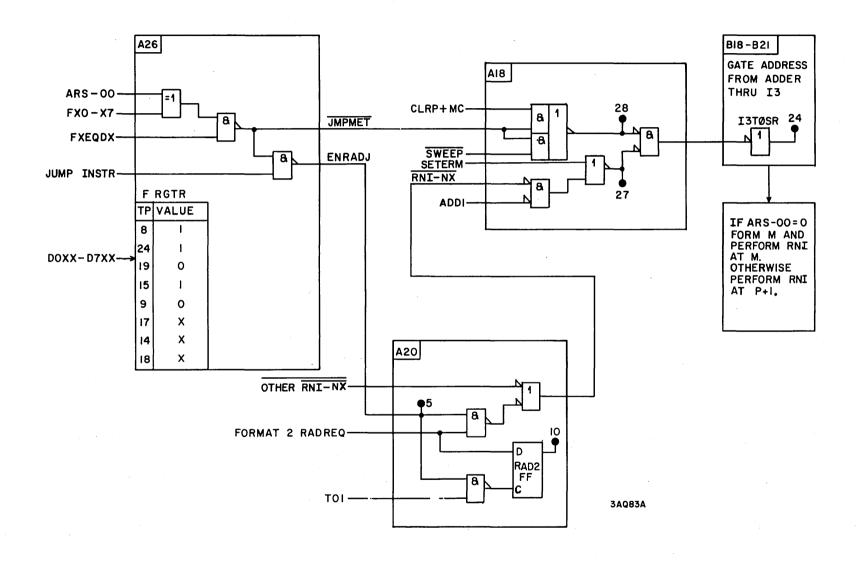

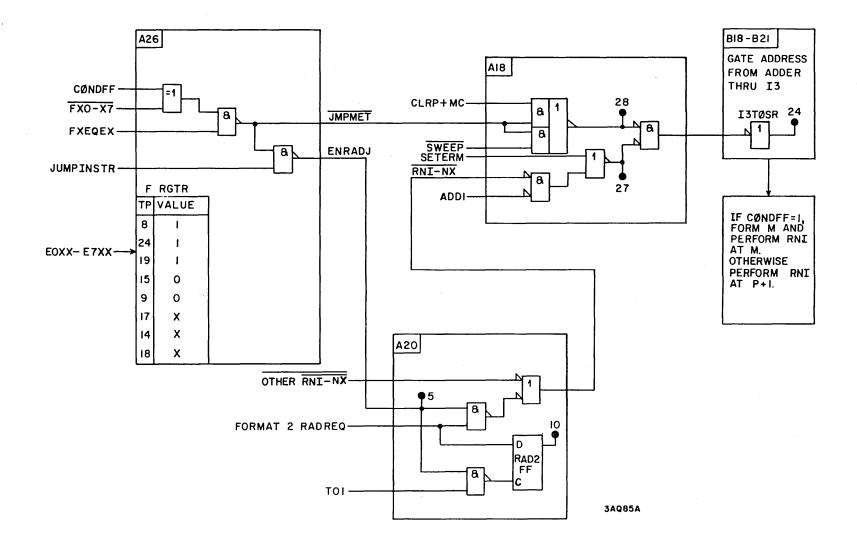

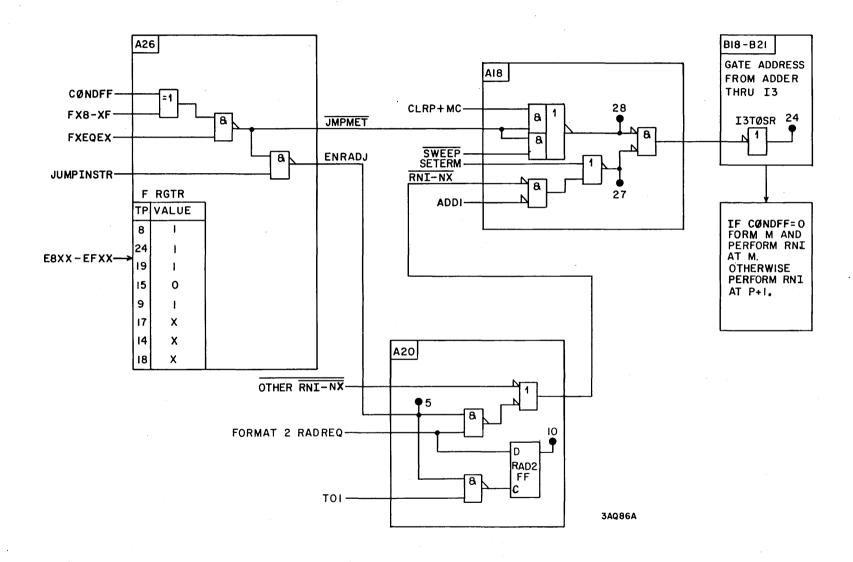

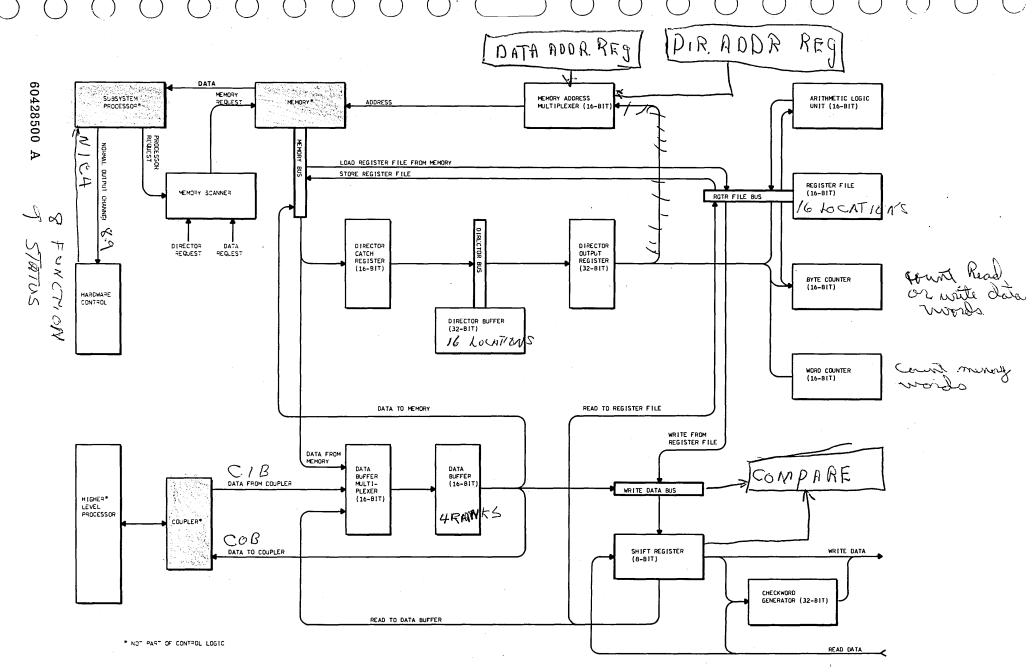

|        |                        | More than one head selected Erase and no write driver on Write drive on and no erase Both write drivers on Write gate without write data |